US 20010048500A1

(19) United States

(12) Patent Application Publication

Lim et al.

(10) Pub. No.: US 2001/0048500 A1

(43) Pub. Date: Dec. 6, 2001

(54) FRINGE FIELD SWITCHING MODE LIQUID CRYSTAL DISPLAY

(57)

## ABSTRACT

(76) Inventors: Kyu Hwan Lim, Seoul (KR); Hyang Yul Kim, Kyoungki-do (KR); Seung Hee Lee, Kyoungki-do (KR)

Correspondence Address:

LADAS & PARRY

224 SOUTH MICHIGAN AVENUE, SUITE

1200

CHICAGO, IL 60604 (US)

(21) Appl. No.: 09/870,971

(22) Filed: May 31, 2001

### (30) Foreign Application Priority Data

May 31, 2000 (KR) ..... 2000-29776

### Publication Classification

(51) Int. Cl.<sup>7</sup> ..... G02F 1/1343

(52) U.S. Cl. ..... 349/141

Disclosed is a fringe field switching mode liquid crystal display. The fringe field switching mode liquid crystal display of the present invention comprises a transparent insulating substrate; a plurality of gate bus line arranged in selected direction on the transparent insulating substrate, the gate bus line is arranged so that each element of the pair separated at a first distance is arranged a plurality of pairs at a second distance wider than a first distance; a plurality of common bus lines arranged on the centers of each gate bus line separated at the second distance, being in parallel with the gate bus line; a plurality of data bus lines arranged crossing with the gate bus line and common bus line to define a unit pixel; a thin film transistor disposed at the intersection of the gate bus line and data bus line; a counter electrode disposed in a unit pixel area and made of a transparent conductor, being in contact with the common bus line; and a pixel electrode overlapping with the counter electrode in the unit pixel and made of a transparent conductor, being in contact with the thin film transistor.

## FIG.1 (PRIOR ART)

FIG.2

FIG.3

FIG.4

## FRINGE FIELD SWITCHING MODE LIQUID CRYSTAL DISPLAY

### BACKGROUND OF THE INVENTION

#### [0001] 1. Field of the Invention

[0002] The present invention relates to a fringe field switching mode liquid crystal display, and more particularly a fringe field driving liquid crystal display in which the structure is transformed to prevent shorts between a gate bus line and a common bus line.

#### [0003] 2. Description of the Related Art

[0004] A thin film transistor liquid crystal display (hereinafter referred as TFT-LCD) generally has advantages of light weight, thin thickness and low power consumption. Therefore, it has been substituted for Cathode-ray tube (CRT) in a terminal of information apparatus and a video unit, and recently, it is widely used in a notebook PC and monitor market.

[0005] The TFT-LCD comprises an array substrate and a color filter, which are combined with a liquid crystal layer interposed between them. The array substrate has a structure that TFTs are disposed in each pixel arranged in a matrix type and the color filter substrate has a structure that a red, a green and a blue color filters are arranged corresponding to each pixel.

[0006] The TFT-LCD has been adopted TN (Twist Nematic) mode as a driving mode, however, the TN mode LCD has a disadvantage of narrow viewing angle. Accordingly, in order to solve the problem, an In-Plain Switching (hereinafter referred as IPS) mode has been proposed.

[0007] The IPS mode LCD has a wide viewing angle, however, it has disadvantages of a low aperture ratio and a low transmittance since a counter electrode and a pixel electrode are made of opaque metals. A fringe field switching (hereinafter referred as FFS) mode LCD has been proposed in order to improve the aperture ratio and transmittance of the IPS mode LCD.

[0008] In the FFS mode LCD, the counter electrode and the pixel electrode are made of transparent conductors and are designed which the distance between electrodes is narrower than that between substrates. And liquid crystals having negative dielectric anisotropy are used in the FFS mode LCD. Accordingly, a fringe field is formed between the electrodes and the liquid crystals on the electrodes are also driven by the fringe field, thereby realizing high brightness as well as wide viewing angle.

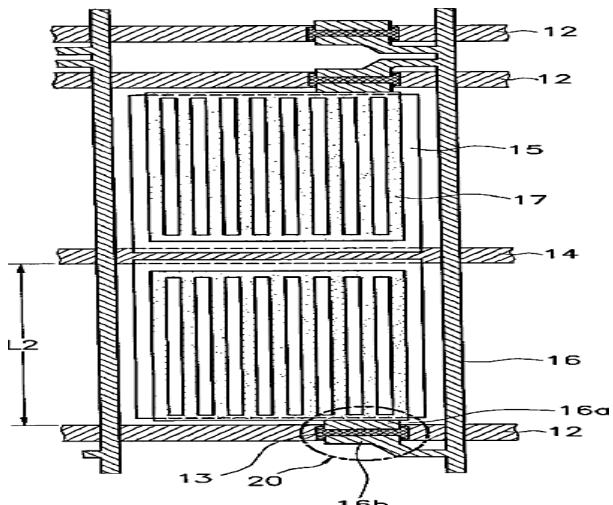

[0009] FIG. 1 shows an array substrate of a conventional FFS mode LCD. As shown in FIG. 1, a gate bus line (2) and a data bus line (6) are cross-arranged, thereby defining a unit pixel area. A TFT (10) is arranged as a switching device near the intersection of the gate bus line (2) and the data bus line (6). The TFT (10) comprises a gate electrode that is a part of the gate bus line, a semiconductor layer (3) on the gate electrode, a drain electrode (6b) overlapping with one side of the semiconductor layer (3), being protrude from the data bus line (6), and a source electrode (6a) overlapping with the other side of the semiconductor layer (3).

[0010] A counter electrode (5) is disposed in a unit pixel area. The counter electrode (5) made of a transparent con-

ductor and has a plate shape. A part of the counter electrode (5) is electrically in contact with a common bus line (4), thereby continuously applying common signals from the common bus line (4).

[0011] The common bus line (4) comprises a first part (4a) disposed in parallel with the gate bus line (2), being electrically in contact with the counter electrode (5) and a second part (4b) which is extended from the first part (4a) to be in parallel with the data bus line (6) in a unit pixel, being in contact with both edges of the counter electrode (5) to be a shading means.

[0012] A pixel electrode (7) is disposed in a unit pixel to overlap with the counter electrode (5). The pixel electrode (7) made of a transparent conductor and is formed in a slit shape comprising a plurality of slits disposed in parallel with the data bus line (6). The pixel electrode (7) is insulated with the counter electrode (5) by a gate insulating film (not illustrated) and is electrically in contact with a source electrode (6a) of TFT (10).

[0013] However, conventional FFS mode LCD has a narrow distance (L1) between a gate bus line and a common bus line, thereby increasing generation probability of shorts between them. As a result, the quality of product is degraded. That is, when a short is generated between the lines, a high voltage loaded on the gate bus line is loaded on the common bus line. Accordingly, the high voltage may cause the common bus line to be defective, thereby deteriorating the product quality.

### SUMMARY OF THE INVENTION

[0014] Therefore, an object of the present invention is to provide a FFS mode LCD preventing the generation of shorts between a gate bus line and a common bus line.

[0015] And, another object of the present invention is to provide a FFS mode LCD preventing degradation of products due to a short between the lines.

[0016] In order to achieve the above objects, the FFS mode LCD according to the present invention comprises: a transparent insulating substrate; a plurality of gate bus line arranged in selected direction on the transparent insulating substrate, the gate bus line is arranged so that each element of the pair separated at a first distance is arranged a plurality of pairs at a second distance wider than a first distance; a plurality of common bus lines arranged on the centers of each gate bus line separated at the second distance, being in parallel with the gate bus line; a plurality of data bus lines arranged crossing with the gate bus line and common bus line to define a unit pixel; a thin film transistor disposed at the intersection of the gate bus line and data bus line; a counter electrode disposed in a unit pixel area and made of a transparent conductor, being in contact with the common bus line; and a pixel electrode overlapping with the counter electrode in the unit pixel and made of a transparent conductor, being in contact with the thin film transistor.

[0017] The counter electrode may be disposed in each unit pixel area or one counter electrode of a body type may be disposed in two unit pixel areas defined by a gate bus line.

[0018] The common bus line may be formed in a line type or it may comprise a first part of a line type and a second part. The first part is disposed in parallel with the gate bus

line, being in contact with a part of the counter electrode and the second part is protruded from the first part in a unit pixel, disposed in parallel with the data bus line, being in contact with both edges of the counter electrode.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0019] The above objects, and other features and advantages of the present invention will become more apparent after a reading of the following detailed description when taken in conjunction with the referenced drawings.

[0020] FIG. 1 shows an array substrate of conventional FFS mode LCD.

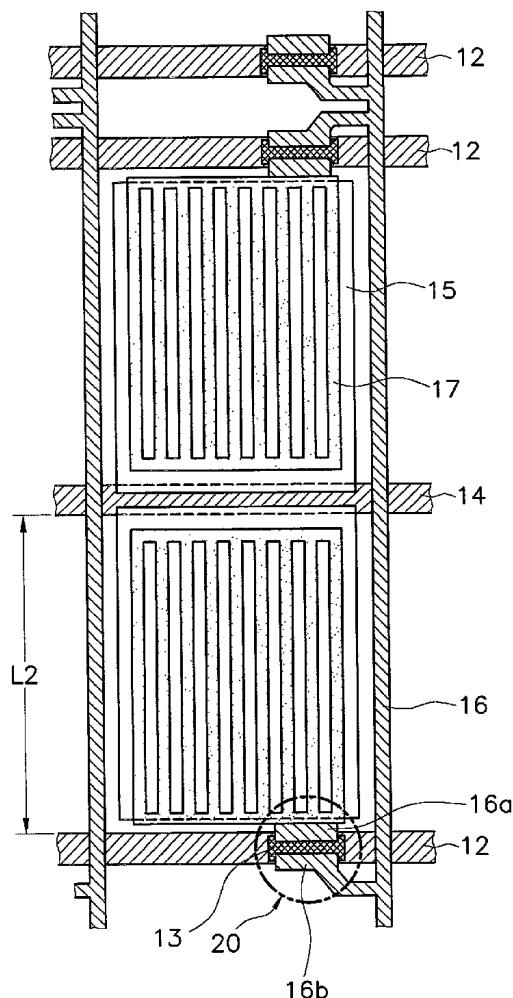

[0021] FIG. 2 shows an array substrate of FFS mode LCD according to a preferred embodiment of the present invention.

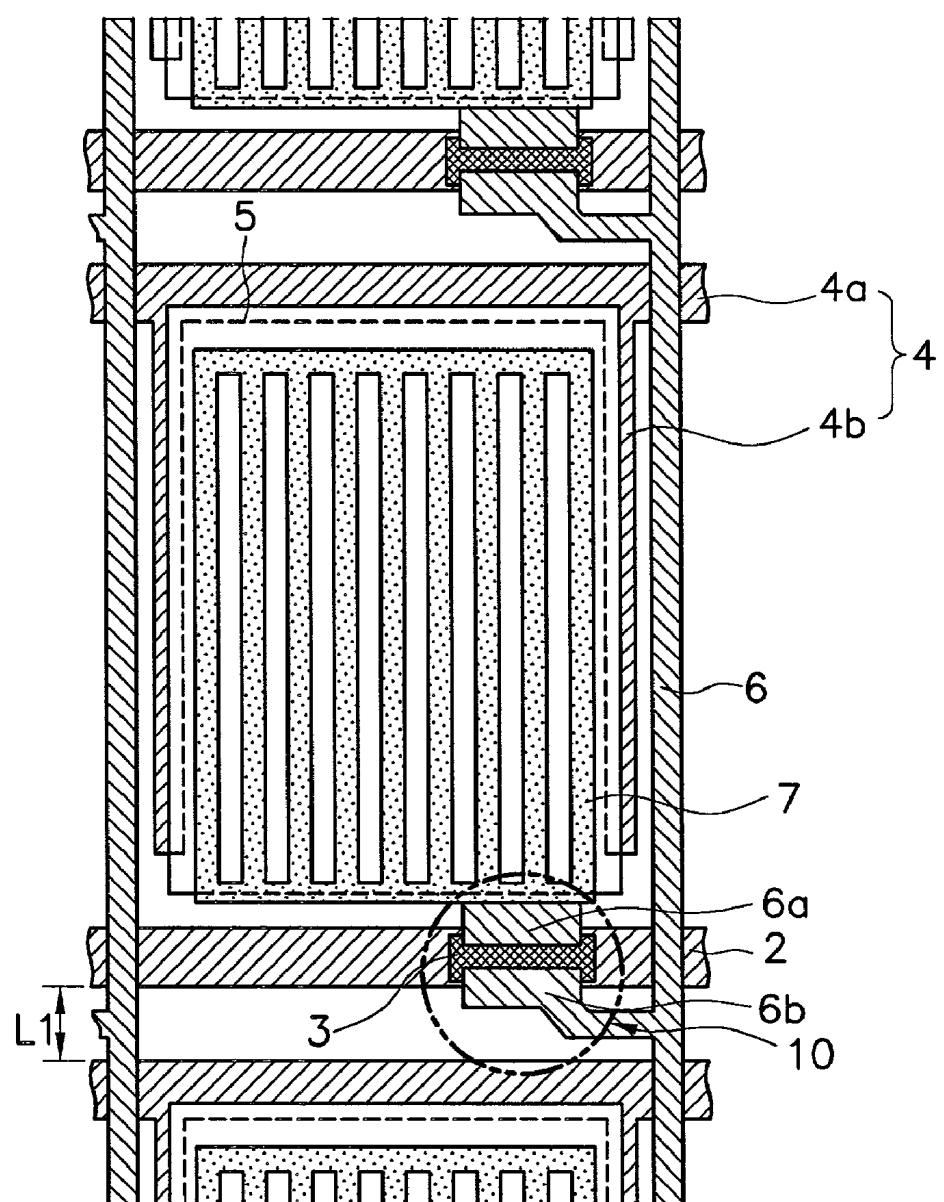

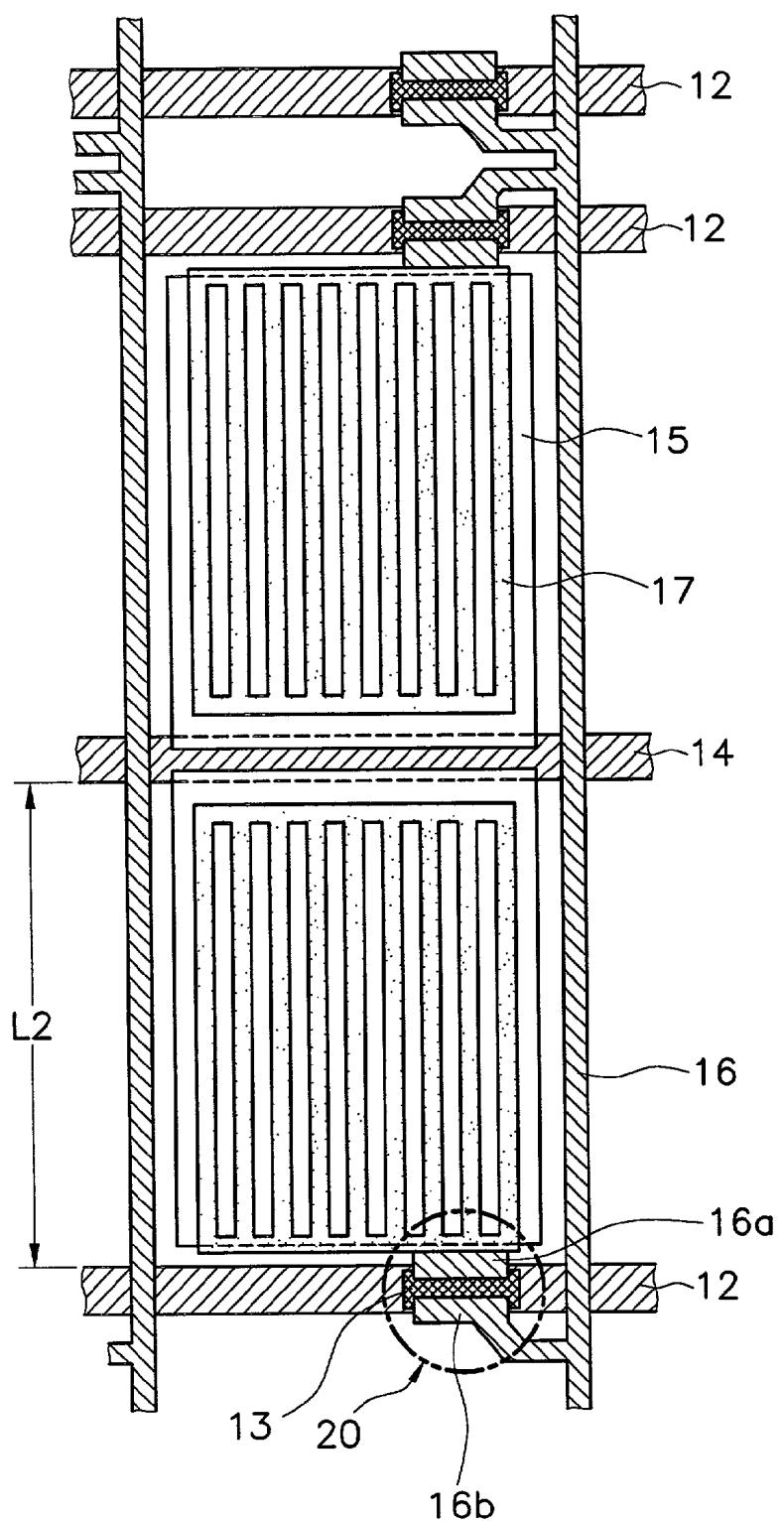

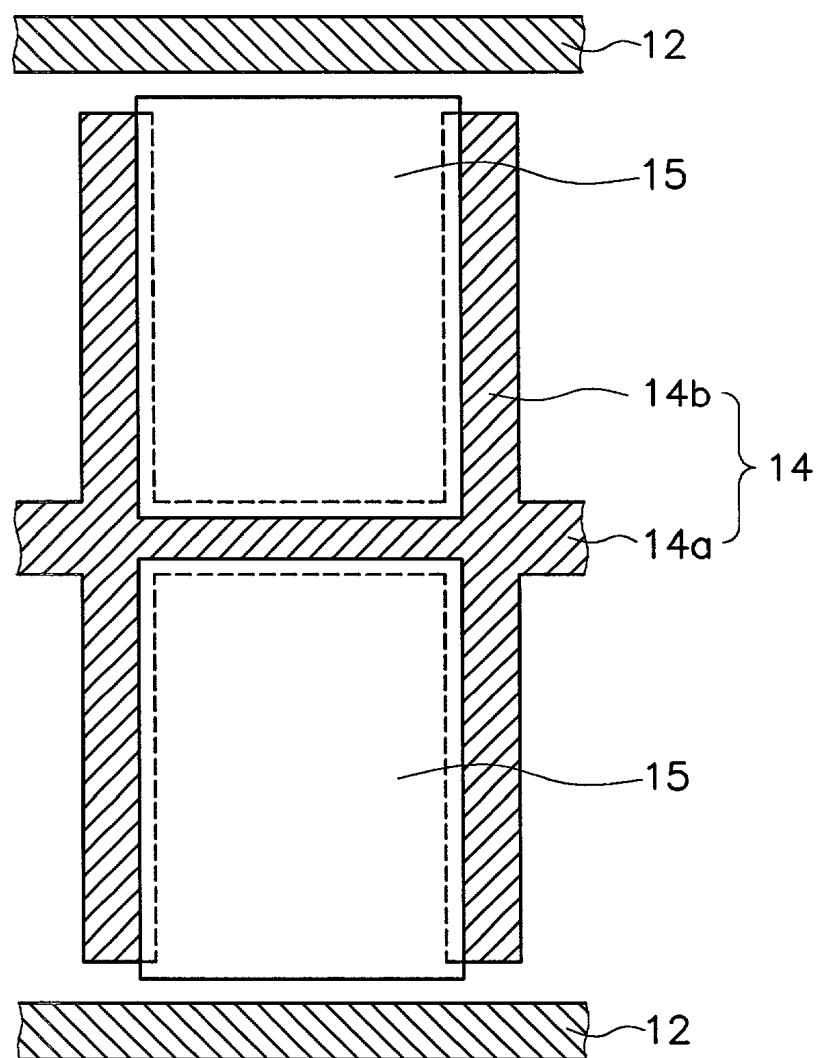

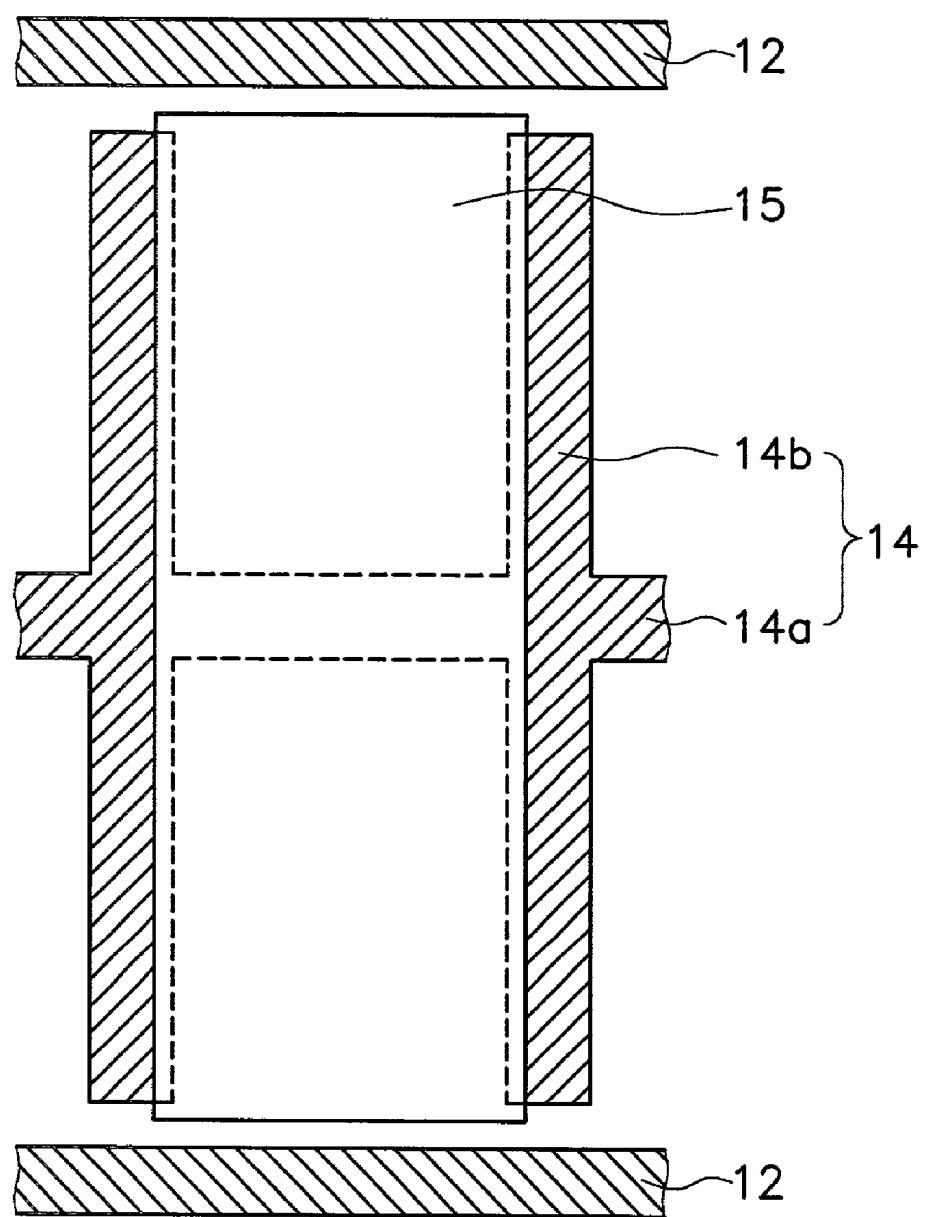

[0022] FIGS. 3 and 4 show a counter electrode and a common bus line of FFS mode LCD according to another preferred embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

[0023] FIG. 2 shows an array substrate of FFS mode LCD according to a preferred embodiment of the present invention.

[0024] Referring to FIG. 2, a plurality of gate bus lines (12) are arranged in a line on a transparent insulating substrate (not illustrated). The gate bus lines (12) are arranged so that each element of the pair separated at a first distance is arranged a plurality of pairs at a second distance wider than a first distance. Common bus lines (14) are arranged in parallel with the gate bus line (12) on the centers of each gate bus line (12) separated at a second distance. A plurality of data bus lines (16) are arranged crossing with the gate bus line (12) and the common bus line (14), thereby defining a unit pixel.

[0025] Herein, the unit pixel is defined by one gate bus line (12), one common bus line (14), and a pair of data bus lines (16). Therefore, the second distance between the gate bus lines corresponds to the size of two unit pixels and the common bus line (14) is disposed to define the size of each unit pixel.

[0026] A TFT (20) is then disposed as a switching device near the intersection of the gate bus line (12) and the data bus line (16). The TFT (20) comprises a gate electrode that is a part of the gate bus line (12), a semiconductor layer (13) disposed on the gate electrode, a drain electrode (16b) which is protruded from the data bus line (16) to overlap with one side of the semiconductor layer (13), and a source drain electrode (16a) overlapping with the other side of the semiconductor layer (13).

[0027] A counter electrode (15) is disposed in each unit pixel. The counter electrode (15) is made of a transparent conductor in a plate type. And, counter electrodes are in contact with one common bus line (14) even when the counter electrodes are disposed in two unit pixels defined by the gate bus lines (12) separated at the second distance.

[0028] A pixel electrode (17) is disposed in the unit pixel to overlap with the counter electrode (15). The pixel electrode (17) is made of a transparent conductor in a slit type.

And, the electrode (17) is insulated with the counter electrode (15) by a gate insulating film (not illustrated), being in contact with a source electrode (16a) of the TFT (20).

[0029] In the array substrate of the FFS mode LCD according to the present invention as described above, a distance (L2) between a gate bus line (12) and a common bus line (14) is wider when compared to the conventional distance (L1), thereby remarkably decreasing the generation probability of shorts between the lines.

[0030] While the gate bus lines (12) to be disposed at the first distance may cause a short between them. But since one common bus line (14) is disposed in two unit pixels unlike a conventional structure that one common bus line is disposed in one unit pixel, the distance between gate bus lines (12) may be increased. As a result, the distance between the gate bus lines (12) is increased, thereby preventing the short between the gate bus lines (12).

[0031] Consequently, according to a FFS mode LCD of the present invention, a short between a common bus line and a gate bus line may be prevented by optimizing the structure thereof, thereby improving a quality of common bus line and preventing deterioration of products.

[0032] FIGS. 3 and 4 show a counter electrode and common bus line of FFS mode LCD according to another embodiment of the present invention.

[0033] Referring to FIGS. 3 and 4, a common bus line (14) is formed in a H-shape in two adjacent unit pixels. That is, the common bus line (14) comprises a first part (14a) of a line type which is disposed in parallel with a gate bus line (12) to define a unit pixel and a second part (14b) which is protruded from the first part (14a) and is disposed in parallel with a data bus line (16), overlapping with both edges of the counter electrode to be a shading means.

[0034] The counter electrode (15) is formed in a plate-shape and may be disposed in each unit pixel as shown in FIG. 3 or disposed in a body type in two unit pixels defined by the gate bus lines (12). When the counter electrode (15) is disposed in a body type in two unit pixels, an etching margin to a transparent conductor is increased and the contact resistance is decreased by enlarging the contact area with the common bus line (14).

[0035] As described above, according to the present invention, the structure of a gate bus line and a common bus line is transformed to prevent generation of defects due to a short between the lines, thereby improving the yield.

[0036] While this invention has been particularly shown and described with reference to preferred embodiments thereof, it will be understood by those skilled in the art that various changes in form and details may be made to the described embodiments without departing from the spirit and scope of the invention as defined by the appended claims.

What is claimed is:

1. A fringe field switching mode liquid crystal display comprising:

a transparent insulating substrate;

a plurality of gate bus line arranged in selected direction on the transparent insulating substrate, the gate bus line is arranged so that each element of the pair separated at

- a first distance is arranged a plurality of pairs at a second distance wider than a first distance;

- a plurality of common bus lines arranged on the centers of each gate bus line separated at the second distance, being in parallel with the gate bus line;

- a plurality of data bus lines arranged crossing with the gate bus line and common bus line to define a unit pixel;

- a thin film transistor disposed at the intersection of the gate bus line and data bus line;

- a counter electrode disposed in a unit pixel area and made of a transparent conductor, being in contact with the common bus line; and

- a pixel electrode overlapping with the counter electrode in the unit pixel and made of a transparent conductor, being in contact with the thin film transistor.

**2.** The fringe field switching mode liquid crystal display according to claim 1, wherein the common bus line comprises a first part of line type disposed in parallel with the gate bus line, being in contact with a part of the counter electrode and a second part protruded from the first part in a unit pixel and disposed in parallel with the data bus line, being in contact with both edges of the counter electrode.

**3.** The fringe field switching mode liquid crystal display according to claim 1, wherein the counter electrode is formed in a plate shape.

**4.** The fringe field switching mode liquid crystal display according to claim 1, wherein the counter electrodes are disposed in each unit pixel area.

**5.** The fringe field switching mode liquid crystal display according to claim 4, wherein the counter electrodes disposed on the upper and lower parts of the common bus line are all in contact with the common bus line.

**6.** The fringe field switching mode liquid crystal display according to claim 1, wherein the counter electrode is disposed in a body type in two unit pixel areas between gate bus lines separated at the second distance.

**7.** The fringe field switching mode liquid crystal display according to claim 1, wherein the pixel electrode is formed in a slit shape.

\* \* \* \* \*

|                |                                                   |         |            |

|----------------|---------------------------------------------------|---------|------------|

| 专利名称(译)        | 边缘场切换模式液晶显示器                                      |         |            |

| 公开(公告)号        | <a href="#">US20010048500A1</a>                   | 公开(公告)日 | 2001-12-06 |

| 申请号            | US09/870971                                       | 申请日     | 2001-05-31 |

| [标]申请(专利权)人(译) | LIM KYU HWAN<br>金香YUL<br>李承HEE                    |         |            |

| 申请(专利权)人(译)    | LIM KYU HWAN<br>金香YUL<br>李承HEE                    |         |            |

| 当前申请(专利权)人(译)  | LIM KYU HWAN<br>金香YUL<br>李承HEE                    |         |            |

| [标]发明人         | LIM KYU HWAN<br>KIM HYANG YUL<br>LEE SEUNG HEE    |         |            |

| 发明人            | LIM, KYU HWAN<br>KIM, HYANG YUL<br>LEE, SEUNG HEE |         |            |

| IPC分类号         | G02F1/1343                                        |         |            |

| CPC分类号         | G02F1/134363                                      |         |            |

| 优先权            | 1020000029776 2000-05-31 KR                       |         |            |

| 其他公开文献         | US6646706                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a>   |         |            |

### 摘要(译)

公开了一种边缘场切换模式液晶显示器。本发明的边缘场开关模式液晶显示器包括透明绝缘基板;在透明绝缘基板上沿选定方向布置的多条栅极总线,栅极总线布置成使得以第一距离分开的该对中的每个元件以比第一距离宽的第二距离布置多对;多条公共总线,设置在每条栅极总线的中心,以第二距离分开,与栅极总线平行;多条数据总线,与栅极总线和公共总线交叉排列,以形成单位像素;薄膜晶体管,设置在栅极总线和数据总线的交叉点上;对置电极,配置在单位像素区域,由透明导体构成,与公共总线接触;像素电极与单位像素中的对电极重叠并由透明导体制成,与薄膜晶体管接触。