## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2004/0263755 A1 Kim et al.

### Dec. 30, 2004 (43) Pub. Date:

## (54) IN-PLANE SWITCHING MODE LIQUID CRYSTAL DISPLAY DEVICE AND MANUFACTURING METHOD THEREOF

(76) Inventors: Ik-Soo Kim, Gyeonggi-do (KR); Chang-Yeon Kim, Seoul (KR); Gi-Hong Kim, Gyeonggi-do (KR)

> Correspondence Address: MCKÊNNA LONG & ALDRIDGE LLP 1900 K STREET, NW WASHINGTON, DC 20006 (US)

10/893,951 (21) Appl. No.:

(22) Filed: Jul. 20, 2004

## Related U.S. Application Data

Continuation of application No. 09/987,038, filed on Nov. 13, 2001, now Pat. No. 6,784,965.

#### (30)Foreign Application Priority Data

| Nov. 14, 2000 | (KR) | 2000-67516 |

|---------------|------|------------|

| Jan. 18, 2001 | (KR) | 2001-2969  |

## **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

#### (57)**ABSTRACT**

In the typical IPS-LCD device with a wide viewing angle, since the metallic black matrix of the upper substrate affect the voltage between the common and pixel electrodes, the black matrix is made of resin and cannot be formed with a bent portion because of the limits of the processing technology. Therefore, the typical IPS-LCD device has a limit for effective realization and a low aperture ratio.

In the disclosed IPS-LCD device, since one of the common electrodes is formed to cover the data line and operate as the black matrix, the black matrix of the upper substrate can be made of resin and the driving voltage can be reduced. Therefore, actually, the multi-domain IPS-LCD device can be fabricated without the increase of driving voltage and decrease of aperture ratio.

Furthermore, since the common and pixel electrodes are formed on the same layer, the aperture ratio can be improved and the problems such as residual images or flicker can be

(related art) FIG. 1

(related art) FIG. 2

(related art) FIG. 3

(related art) FIG. 4

(related art) FIG. 5

(related art) FIG. 6

(related art) FIG. 7

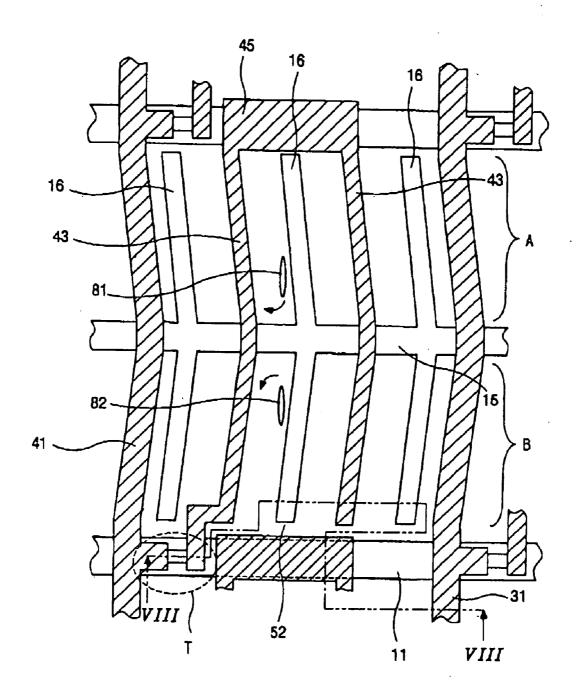

(related art) FIG. 8A

(related art) FIG. 8B

(related art) FIG. 8C

(related art) FIG. 8D

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 10B

FIG. 10C

FIG. 10D

FIG. 10E

FIG. 11

FIG. 12A

FIG. 12B

FIG. 13A

FIG. 13B

FIG. 13C

FIG. 13D

FIG. 13E

FIG. 14

FIG. 15A

FIG. 15B

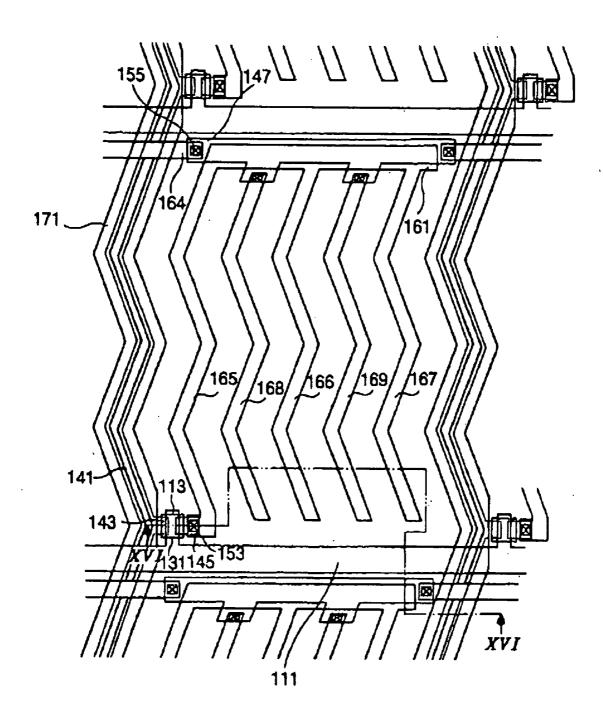

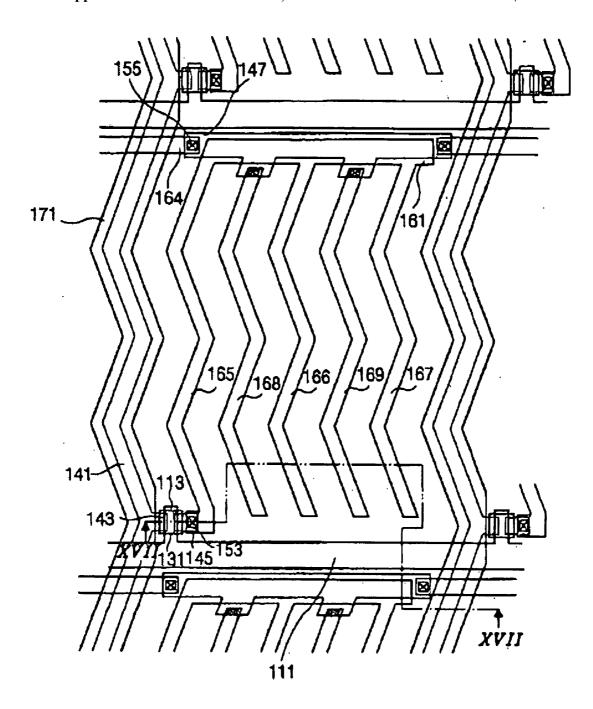

FIG. 16A

FIG. 16B

FIG. 16C

FIG. 16D

FIG. 16E

FIG. 16F

FIG. 17

# IN-PLANE SWITCHING MODE LIQUID CRYSTAL DISPLAY DEVICE AND MANUFACTURING METHOD THEREOF

[0001] This application claims the benefit of Korean Patent Applications No. 2000-0067516, filed on Nov. 14, 2000 and No. 2001-0002969, filed on Jan. 18, 2001, which are hereby incorporated by reference as if fully set forth herein.

## BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to a liquid crystal display device, and more particularly to a liquid crystal display device implementing in-plane switching. (IPS) where an electric field to be applied to liquid crystal is generated in a plane parallel to a substrate.

[0004] 2. Discussion of the Related Art

[0005] A typical liquid crystal display (LCD) device uses optical anisotropy and polarization properties of liquid crystal molecules. The liquid crystal molecules have a definite orientational order in alignment resulting from their thin and long shapes. The alignment direction of the liquid crystal molecules can be controlled by applying an electric field to the liquid crystal molecules. In other words, as the alignment direction of the electric field is changed, the alignment of the liquid crystal molecules also changes. Since the incident light is refracted to the orientation of the liquid crystal molecules due to the optical anisotropy of the aligned liquid crystal molecules, images are displayed.

[0006] Generally, typical LCD devices include upper and lower substrates with liquid crystal molecules interposed therebetween. The upper and lower substrates are generally referred to as color filter and array substrates, respectively. The upper and lower substrates respectively include electrodes disposed on opposing surfaces of the upper and lower substrates. An electric field is generated by applying a voltage to the electrodes, thereby driving the liquid crystal molecules to display images depending on light transmittance.

[0007] Of the different types of known LCDs, active matrix LCDs (AM-LCDs), which have thin film transistors and pixel electrodes arranged in a matrix form, are the subject of significant research and development because of their high resolution and superiority in displaying moving images. Driving methods for such LCDs typically include a twisted nematic (TN) mode and a super twisted nematic (STN) mode.

[0008] However, the operation mode of the TN- or STN-LCD panel has a disadvantage of a narrow viewing angle. That is to say, the TN liquid crystal molecules rotate with polar angles 0 to 90 degrees, which are too wide. Because of the large rotating angle, contrast ratio and brightness of the TN- or STN-LCD panel fluctuate rapidly with respect to the viewing angles.

[0009] To overcome the problem, an in-plane switching (IPS) LCD panel was developed. The IPS-LCD devices typically include a lower substrate where a pixel electrode and a common electrode are disposed, an upper substrate having no electrode, and a liquid crystal interposed between the upper and lower substrates. Therefore, the IPS-LCD

panel implements a parallel electric field that is parallel to the substrates, which is different from the TN- or STN-LCD panel and has advantages in contrast ratio, gray inversion, and color shift that are related to the viewing angle.

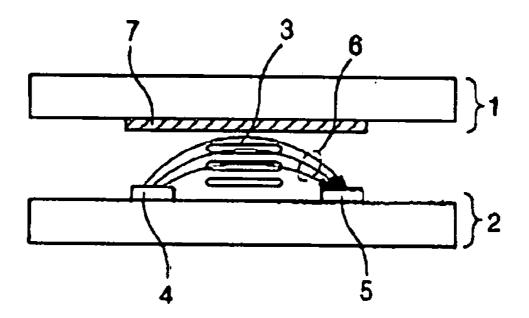

[0010] A detailed explanation about operation modes of a typical IPS-LCD device will be provided with reference to FIGS. 1 to 5.

[0011] As shown in FIG. 1, upper and lower substrates 1 and 2 are spaced apart from each other, and a liquid crystal 3 is interposed therebetween. The lower and upper substrates are called array and color filter substrates, respectively. Pixel and common electrodes 4 and 5 are disposed on the lower substrate 2. The pixel and common electrodes 4 and 5 are parallel with and spaced apart from each other. A color filter 7 is disposed on a surface of the upper substrate 1 and opposes the lower substrate 2. The pixel and common electrodes 4 and 5 apply an electric field 6 to the liquid crystal. The liquid crystal has a negative dielectric anisotropy, and thus it is aligned parallel with the electric field 6.

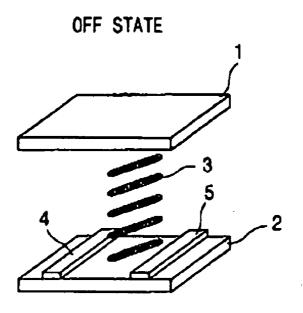

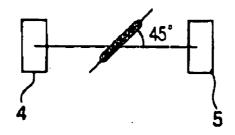

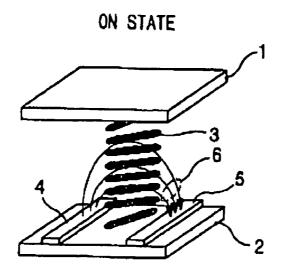

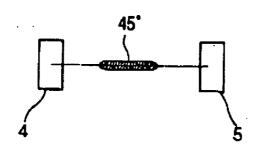

[0012] FIGS. 2 to 5 conceptually illustrate operation modes of a typical IPS-LCD device. When there is no electric field between the pixel and the common electrodes 4 and 5, the long axes of the liquid crystal molecules 3 maintain an angle, for example, the angle is 45 degrees, from a line perpendicular to the parallel pixel and common electrodes 4 and 5 as shown in FIG. 3. On the contrary, when there is an electric field between the pixel and common electrodes 4 and 5, there is an in-plane electric field 6 parallel to the surface of the lower substrate 2 between the pixel and common electrodes 4 and 5 because the pixel and common electrodes are formed on the lower substrate 2 as shown in FIG. 4. Accordingly, the liquid crystal molecules 3 are twisted so as to align the long axes thereof in the direction of the electric field, thereby being aligned such that the long axes thereof are parallel with the line perpendicular to the elongated direction of the pixel and common electrodes 4 and 5 as shown in FIG. 5. By the above-mentioned operation modes and with additional parts such as polarizers and alignment layers, the IPS-LCD device displays images. The IPS-LCD device has a wide viewing angle and low color dispersion characteristic. Specifically, the viewing angle of the IPS-LCD device is about 70 degrees in direction of up, down, right, and left. In addition, the fabricating processes of this IPS-LCD device are simpler than other various LCD devices.

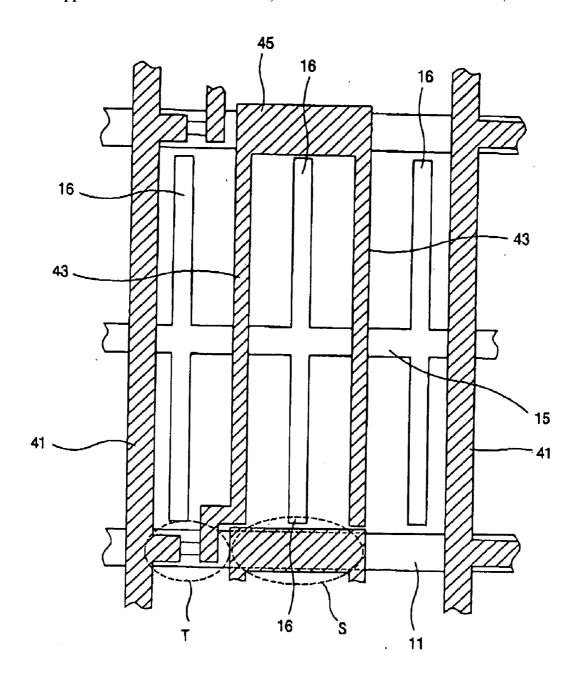

[0013] FIG. 6 is a schematic plan view of an array substrate of the typical IPS-LCD device.

[0014] As shown, a pixel area is defined by a row gate line 11 and a column data line 41. A TFT "T", the switching device, is formed at the crossing of gate and data lines. In the pixel area, a common line 15 is elongated along the direction of the gate line 11 and a plurality of common electrodes 16 connected to the common line 15 are elongated along the direction of the data line 41. Moreover, in the pixel area, a plurality of pixel electrodes 43, which are spaced apart from the common electrodes 16 and arranged in an alternating pattern, is connected to the TFT "T" and the pixel line 45. The pixel line 45 overlaps the gate line 11 to make a storage capacitor "S".

[0015] Therefore, in the IPS-LCD devices, since lateral electric field is formed between the common electrodes 16

and the pixel electrodes 43 of the same plane and the liquid crystal molecules are aligned parallel to the lateral electric field, the viewing angle can be improved. Furthermore, the IPS-LCD devices have low color dispersion qualities and the fabricating processes thereof are simpler than those of other various LCD devices.

[0016] However, because the common and pixel electrodes 16 and 43 are disposed on the same plane on the lower substrate, the transmittance and aperture ratio are low. In addition, a response time according to a driving voltage should be improved and a cell gap should be uniform because of the low alignment margin. A color shift problem according to the viewing angle still remains. These problems are dependent on the rotational direction of the liquid crystal molecules under the electric field over the threshold voltage and are generated from the increase or decrease of the retardation and of the liquid crystal layer according to the viewing angle.

[0017] FIG. 7 is a schematic plan view of an array substrate of the IPS-LCD device for solving the color shift problem.

[0018] As shown, upper and lower domains "A" and "B." are formed by bending the common and pixel electrodes 16 and 43 at an angle with respect to the common line 15. The electric field between two electrodes 16 and 43 rotates the liquid crystal molecules 81 and 82 of the domains "A" and "B" in opposite direction from each other. A liquid crystal molecule of the upper domain "A" is rotated clockwise and a liquid crystal molecule of the lower domain "B" is rotated counter-clockwise. Therefore, the liquid crystal molecules 81 and 82 of two domains "A" and "B" are aligned in different directions to compensate the color shift effectively.

[0019] Here, since the data line 41 is also bent at an angle with respect to the common line 15 and is patterned parallel to the common and pixel electrodes 16 and 43, the space between the data line 41 and the common electrode 16 can decrease, and the aperture ratio can be improved. To make the most of these advantages, a black matrix of an upper substrate also should have a bent portion. However, in the IPS-LCD device, since the metallic black matrix affects the voltage between the common and pixel electrodes 16 and 43, the black matrix is made of resin, which cannot be formed with a bent portion because of the limit of the processing technology. Therefore, the IPS-LCD device of FIG. 7 has a limit for effective realization.

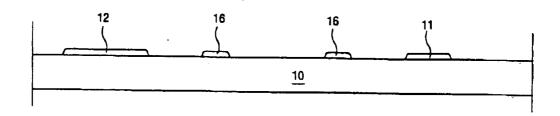

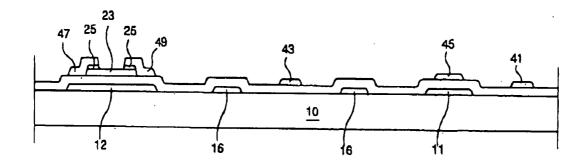

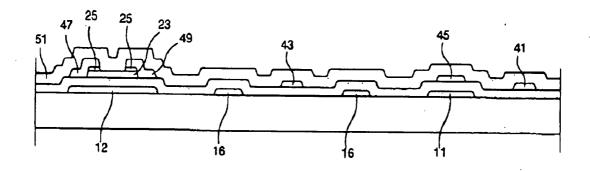

[0020] FIGS. 8A to 8D are sequential cross-sectional views taken along a line "VIII-VIII" of FIG. 7 showing the fabrication process for the array substrate of the typical IPS-LCD device.

[0021] FIG. 8A shows the step of patterning gate electrode 12, common and storage electrodes 16 and 11 of a first metal layer, which can be made of metal, for example, aluminum (Al) or chromium (Cr), on the substrate 10.

[0022] FIG. 8B shows the step of forming a gate insulator 21 and patterning an active layer 23 and an ohmic contact layer 25 on the first metal layer. The gate insulator 21 can be made of silicon nitride (SiNx) and the ohmic contact layer 25 is doped by impurities.

[0023] FIG. 8C shows the step of patterning another storage electrode 45 and source 47, drain 49, pixel 43,

electrodes and data line 41, of a second metal layer. The source and drain electrodes 47 and 49 are patterned on the ohmic contact layer 25 and the pixel electrodes 43 are spaced apart from the common electrodes 16 on the gate insulator 21.

[0024] FIG. 8D shows the step of forming a passivation layer 51, which prevents the active layer 23 from contamination of mists or impurities, on the entire surface of the substrate.

## SUMMARY OF THE INVENTION

[0025] Accordingly, the present invention is directed to an in-plane switching liquid crystal display device and manufacturing method thereof that substantially obviates one or more of problems due to limitations and disadvantages of the related art.

[0026] An object of the present invention is to provide an in-plane switching liquid crystal display device that has a wide viewing angle and a high aperture ratio and a manufacturing method thereof.

[0027] Another object of the present invention is to provide an in-plane switching liquid crystal display device that has an improved color shift and a manufacturing method thereof.

[0028] Additional features and advantages of the invention will be set forth in the description that follows, and in part will be apparent from the description, or may be learned by practice of the invention. The objectives and other advantages of the invention will be realized and attained by the structure particularly pointed out in the written description and claims hereof as well as the appended drawings.

[0029] To achieve these and other advantages and in accordance with the purpose of the present invention, as embodied and broadly described, an array substrate for an in-plane switching liquid crystal display device includes a substrate, a gate line extending along a first direction on the substrate, a data line extending along a second direction on the substrate and having at least one bent portion, a thin film transistor connected to the gate and data lines, a plurality of common electrodes extending along the second direction and having at least one bent portion, wherein at least one of the common electrodes overlaps a portion of the data line, a common line elongating along the first direction and connected to the plurality of common electrodes, a plurality of pixel electrodes alternated with the common electrodes and having at least one bent portion and a pixel line extending along the first direction and connected to the plurality of pixel electrodes.

[0030] In another aspect of the present invention, a method of fabricating an array substrate includes forming a common line extending along a first direction, a plurality of common electrodes extending along a second direction and having a substantially zigzag shape, a gate line extending along the first direction and a gate electrode on a substrate, forming a gate insulator on the gate and common lines, forming a semiconductor layer on the gate insulator, forming a data line extending along the second direction having a substantially zigzag shape and overlapping with at least one of the common electrodes and source and drain electrodes connected to the data line on the semiconductor layer, forming a passivation layer on the data line and the source

and drain electrodes and forming a plurality of pixel electrodes extending along the second direction, having a substantially zigzag shape and alternated with the common electrodes and a pixel line connected to the pixel electrodes.

[0031] It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory and are intended to provide further explanation of the invention as claimed.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0032] The accompanying drawings, which are included to provide a further understanding of the invention and are incorporated in and constitute a part of this application, illustrate embodiments of the invention and together with the description serve to explain the principle of the invention. In the drawings:

[0033] FIG. 1 is a schematic cross-sectional view of a typical IPS-LCD device;

[0034] FIGS. 2 and 3 are perspective views illustrating off state operation of the typical IPS-LCD device;

[0035] FIGS. 4 and 5 are perspective views illustrating on state operation of the typical IPS-LCD device;

[0036] FIGS. 6 and 7 are schematic plan views of array substrates of the typical IPS-LCD device;

[0037] FIGS. 8A to 8D are sequential cross-sectional views taken along a line "VIII-VIII" of FIG. 7;

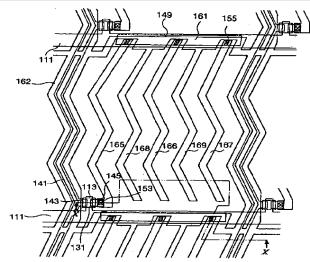

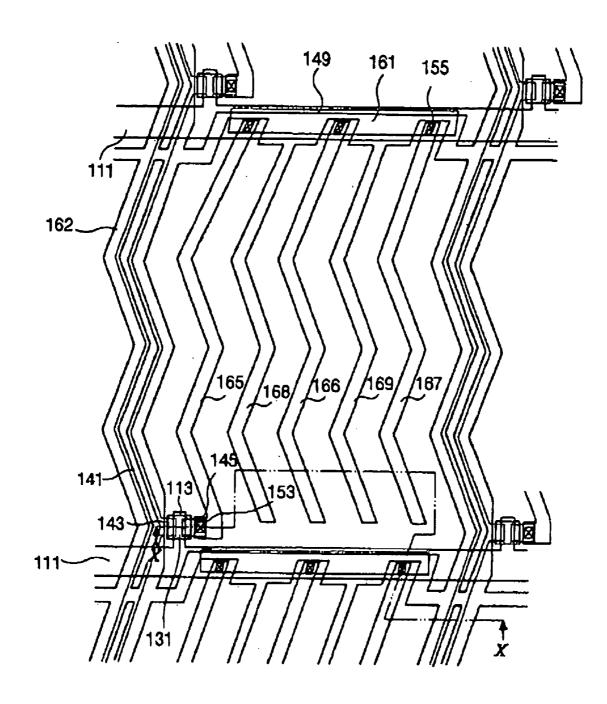

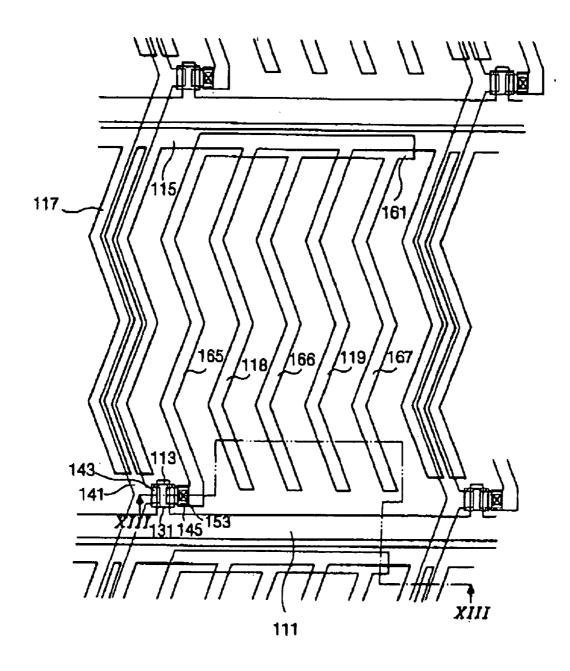

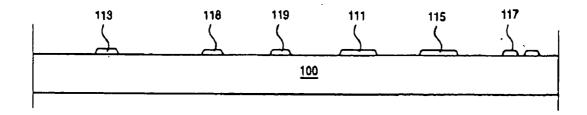

[0038] FIGS. 9A and 9B are schematic plan views of an array substrate of the IPS-LCD device according to the first and second embodiments of the present invention, respectively;

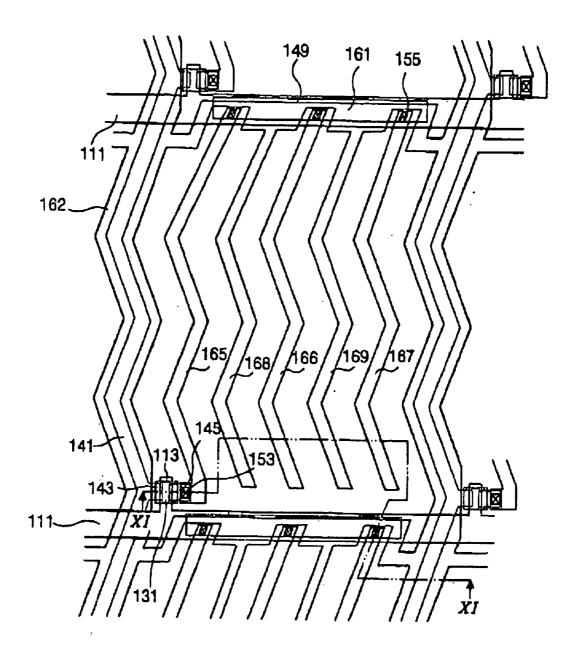

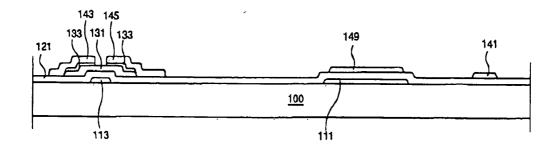

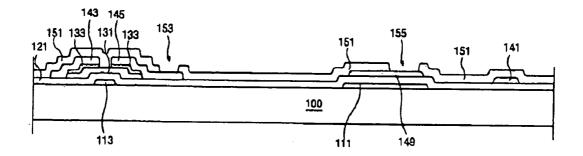

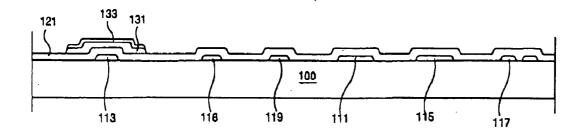

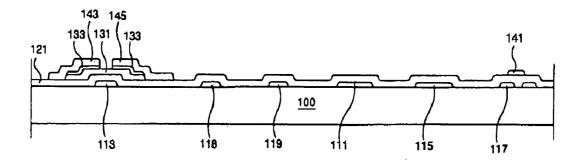

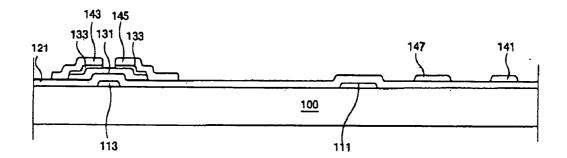

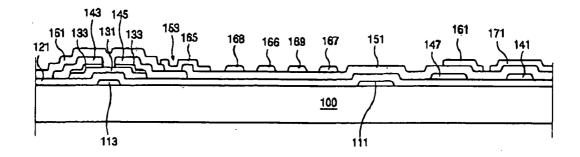

[0039] FIGS. 10A to 10E are sequential cross-sectional views taken along a line "X-X" of FIG. 9A;

[0040] FIG. 11 is a schematic cross-sectional view taken along a line "XI-XI" of FIG. 9B;

[0041] FIGS. 12A and 12B are schematic plan views of an array substrate of the IPS-LCD according to the third and forth embodiments of the present invention, respectively;

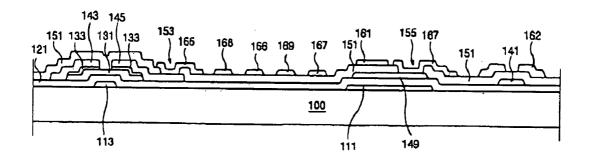

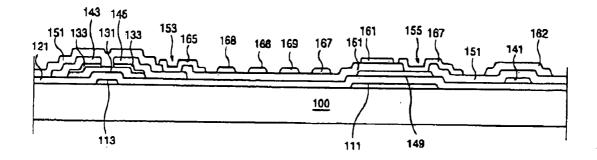

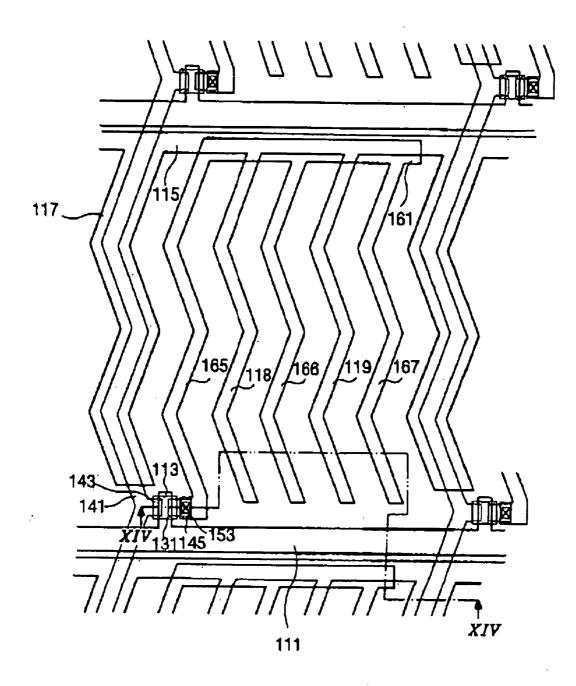

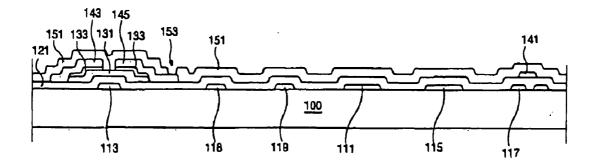

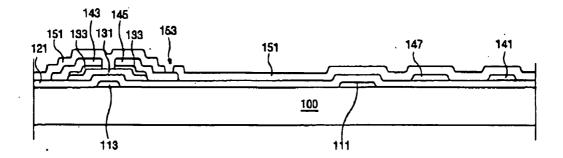

[0042] FIGS. 13A to 13E are sequential cross-sectional views taken along a line "XIII-XIII" of FIG. 12A;

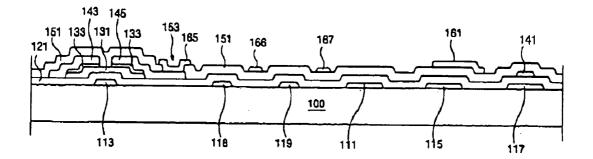

[0043] FIG. 14 is a schematic cross-sectional view taken along a line "XIV-XIV" of FIG. 12B;

[0044] FIGS. 15A and 15B are schematic plan views of an array substrate of the IPS-LCD device according to the fifth and sixth embodiments of the present invention, respectively;

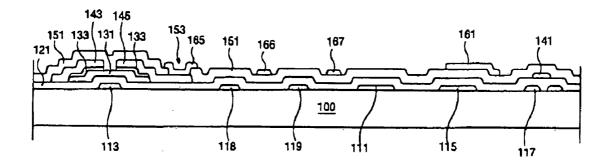

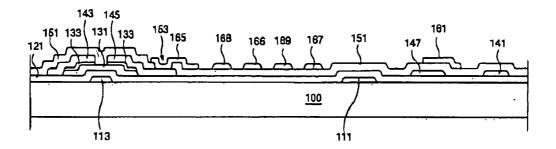

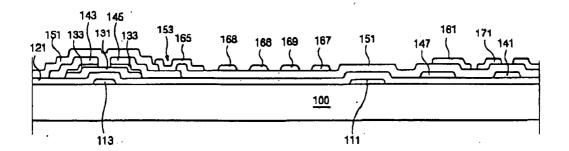

[0045] FIGS. 16A to 16F are sequential cross-sectional views taken along a line "XVI-XVI" of FIG. 15A; and

[0046] FIG. 17 is a schematic cross-sectional view taken along a line "XVII-XVII" of FIG. 15B.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0047] Reference will now be made in detail to the preferred embodiments of the present invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts.

[0048] FIGS. 9A and 9B are schematic plan views of an array substrate of the IPS-LCD device according to a first embodiment and a second embodiment of the present invention, respectively.

[0049] As shown in FIG. 9A and FIG. 9B, a gate line 111 and gate electrode 113 are patterned on an insulating substrate (not shown). A gate insulator (not shown), for example, silicon nitride film (SiNx) or silicon oxide film (SiO<sub>2</sub>), is formed thereon. An active layer 131 of amorphous silicon is patterned on the gate insulator of the gate electrode 113 and an ohmic contact layer of doped amorphous silicon is formed thereon. Then a data line 141, which defines a pixel region by crossing the gate line 111, and source and drain electrodes 143 and 145 are patterned thereon. The data line 141 has a substantially zigzag shape. The data line 141 and the source and drain electrodes 143 and 145 can be made of a metal. A passivation layer (not shown) is formed thereon and has a contact hole 153 exposing the drain electrode 145. Here, the passivation layer can be made of silicon nitride film (SiNx) or silicon oxide film (SiO2) like the gate insulator, or organic material such as benzocyclobutene (BCB), acrylate or polyimide. First to third pixel electrodes 165, 166 and 167 having a substantially zigzag shape and first to third common electrodes 162, 168 and 169 having a substantially zigzag shape are patterned in the pixel region on the passivation layer. In the context of FIGS. 9A and 9B, the pixel electrodes 165, 166 and 167 and the common electrodes 162, 168 and 169 extend vertically and are spaced apart from each other horizontally. The pixel electrodes 165, 166 and 167 are alternated with the common electrodes 162, 168 and 169. The first common electrode 162 overlaps a portion of the data line 141 in FIG. 9A or covers the data line 141 in FIG. 9B, and extends to another first common electrode of a neighboring pixel. A metal pixel line 149 is connected to the pixel electrodes 165, 166 and 167 through the contact hole 155 and overlaps with the common line 161 to form a storage capacitor (storage electrode). The first pixel electrode 165 is connected to the drain electrode 145 through a contact hole 153. Here, the first to third common electrodes 162, 168 and 169 and the pixel electrodes 165, 166 and 167 are formed of transparent conductive material such as indium-tin-oxide (ITO) or indium-zinc-oxide (IZO), so that the aperture ratio can be improved.

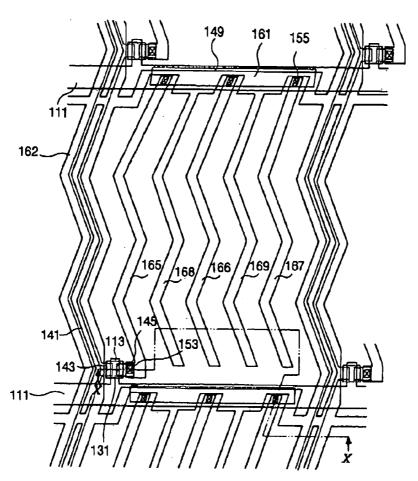

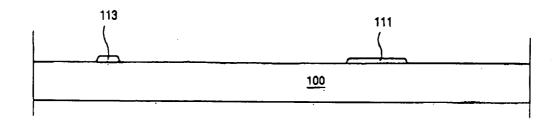

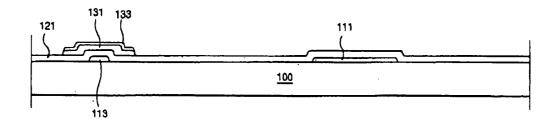

[0050] FIGS. 10A to 10E are sequential cross-sectional views taken along a line "X-X" of FIG. 9A.

[0051] As shown in FIG. 10A, a gate line 111 and a gate electrode 113 are patterned on a substrate 100 such as glass. As shown in the context of FIG. 9A, the gate line 111 extends horizontally.

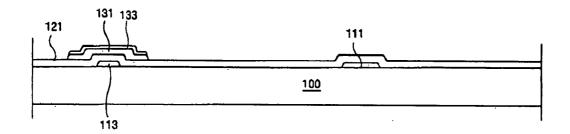

[0052] As shown in FIG. 10B, a gate insulator 121 is formed on the entire surface of the substrate 100, and then an active layer 131 of amorphous silicon or the like and an ohmic contact layer 133 of doped amorphous silicon, for example, are patterned. Here, the gate insulator 121 can be made of silicon nitride film (SiNx), silicon oxide film (SiO<sub>2</sub>) or organic material such as BCB, acrylate, polyimide.

[0053] As shown in FIG. 10C, a data line 141, source and drain electrodes 143 and 145 and a metal pixel line 149 of conductive material, such as metal or transparent conductive

material, are patterned. A pixel region is defined by the data line 141 crossing with the gate line 111. Source and drain electrodes 143 and 145 are adjacent to each other with the gate electrode 113 below them and below the space separating the source and drain electrodes 143 and 145. Here, the data line 141 has a substantially zigzag shape and the metal pixel line 149 operates as an upper electrode of a storage capacitor formed between the previous gate line 111 and the metal pixel line 149.

[0054] As shown in FIG. 10D, a passivation layer 151 of silicon nitride film (SiNx), silicon oxide film (SiO<sub>2</sub>) or organic material such as BCB, acrylate, or polyimide is formed on the entire surface of the substrate. Then contact holes 153 and 155, which expose the drain electrode 145 and the metal pixel line 149, respectively, are patterned.

[0055] As shown in FIG. 10E, first to third pixel electrodes 165, 166 and 167 and first to third common electrodes 162, 168 and 169 of transparent conductive material such as ITO or IZO are patterned. The first common electrode 162 overlaps a portion of the data line 141. In the context of the FIGS. 9A and 10A-E, the first to third pixel electrodes 165, 166 and 167 and the first to third common electrodes 162, 168 and 169 having a substantially zigzag shape are vertically elongated and horizontally spaced apart from each other alternately. Even though the storage capacitor is mainly formed between the metal pixel line 149 and the previous gate line 111, it can be formed by another structure as understood by one of skill in the art.

[0056] FIG. 11 is a schematic cross-sectional view taken along a line "XI-XI" of FIG. 9B, in which the first common electrode 162 covers the data line 141.

[0057] Here, since the common electrode 162 overlaps or covers the data line 141, the space between the data line 141 and the end of the common electrode 162 is narrow and the aperture ratio can be improved. To make the most of these advantages, a black matrix of an upper substrate also should have a bent or substantially zigzag portion. However, since the black matrix made of resin cannot be formed with a bent portion because of the limits of the processing technology, the IPS-LCD device of FIGS. 9A and 9B uses a metallic black matrix with a high driving voltage.

[0058] To improve this problem, other embodiments are suggested.

[0059] FIGS. 12A and 12B are schematic plan views of an array substrate of the IPS-LCD device according to a third embodiment and a fourth embodiment of the present invention, respectively.

[0060] As shown, a gate line 111 and gate electrode 113 are patterned on an insulating substrate (not shown). A common line 115 in substantially the same direction as the gate line 111 is patterned between a respective gate line 111 and first to third common electrodes 117, 118 and 119. The first to third common electrodes have a substantially zigzag shape and extend from the common line 115 roughly perpendicular to the gate line 111. A gate insulator, for example, silicon nitride film (SiNx) or silicon oxide film (SiO<sub>2</sub>), is formed thereon. An active layer 131 of amorphous silicon is patterned on the gate insulator of the gate electrode 113 and an ohmic contact layer of doped amorphous silicon is formed thereon. Then a data line 141, which defines a pixel region by crossing the gate line 111, and source and drain

electrodes 143 and 145 are patterned thereon. Here, the data line 141 has a substantially zigzag shape and overlaps the first common electrode 117 in FIG. 12A or covers the first common electrode 117 in FIG. 12B. The data line 141 and the source and drain electrodes 143 and 145 can be made of a metal. A passivation layer (not shown) is formed thereon and has a contact hole 153 exposing the drain electrode 145. Here, the passivation layer can be made of silicon nitride film (SiNx) or silicon oxide film (SiO<sub>2</sub>) like the gate insulator, or organic material such as BCB, acrylate, or polyimide. First to third pixel electrodes 165, 166 and 167 having a substantially zigzag shape are patterned in the pixel region on the passivation layer. In the context of FIGS. 12A and 12B, the first to third pixel electrodes 165, 166 and 167 and the first to third common electrodes 117, 118 and 119 extend roughly vertically and are spaced apart horizontally. A pixel line 161 is connected to the pixel electrodes 165, 166 and 167 and overlaps with the common line 115 to form a storage capacitor. The first pixel electrode 165 is connected to the drain electrode 145 through a contact hole 153. Here, the common and pixel electrodes 117, 118, 119, 165, 166 and 167 and the data line 141 can be patterned to have at least one bent portion.

[0061] FIGS. 13A to 13E and FIG. 14 are sequential cross-sectional views taken along a line "XIII-XIII" of FIG. 12A showing the fabrication process of the IPS-LCD of the third and fourth embodiments.

[0062] As shown in FIG. 13A, a gate line 111, a gate electrode 113, a common line 115 and first to third common electrodes 117, 118 and 119 are patterned on a substrate 100 such as glass. The first common electrode 117 has two branches. In the context of FIGS. 12A and 12B, the gate line 111 and the common line 115 extend horizontally. In the context of FIGS. 12A and 12B the common electrodes 117, 118 and 119 having a substantially zigzag extend vertically and are connected to the common line 115. In this embodiment, even though the number of common electrodes is three for simplicity of description, the number can be changed depending on the distance between the common electrodes or the slant angle of the common electrodes. The gate line 111, the common line 115 and the common electrodes 117, 118 and 119 can be made of non-transparent material such as metal, for example, chromium (Cr), aluminum (Al), aluminum alloy, molybdenum (Mo), tantalum (Ta), tungsten (W), antimony (Sb), an alloy or a double layer

[0063] As shown in FIG. 13B, a gate insulator 121 is formed on the entire surface of the substrate 100 and then an active layer 131 of amorphous silicon and an ohmic contact layer 133 of doped amorphous silicon are patterned. Here, the gate insulator 121 can be made of silicon nitride film (SiNx), silicon oxide film (SiO<sub>2</sub>) or organic material such as BCB, acrylate, or polyimide.

[0064] As shown in FIG. 13C, a data line 141, source and drain electrodes 143 and 145 of conductive material such as metal are patterned. A pixel region is defined by the data line 141 crossing with the gate line 111. Source and drain electrodes 143 and 145 are adjacent to each other and separated by a space, with the gate electrode 113 below the source and drain electrodes 143 and 145 and the space. Here, the data line 141 has a substantially zigzag shape and overlaps with the first common electrode 117.

[0065] As shown in FIG. 13D, a passivation layer 151 of silicon nitride film (SiNx), silicon oxide film (SiO<sub>2</sub>) or organic material such as BCB, acrylate, or polyimide is formed on the entire surface of the substrate and then a contact hole 153 exposing the drain electrode 145 is patterned

[0066] As shown in FIG. 13E, first to third pixel electrodes 165, 166 and 167 and a pixel line 161 of transparent conductive material such as indium-tin-oxide (ITO) or indium-zinc-oxide (IZO) are patterned. In the context of FIGS. 12A and 12B, the first to third pixel electrodes 165, 166 and 167 having a substantially zigzag shape extend vertically and are spaced apart from the corresponding common electrodes 117, 118 and 119 horizontally. The pixel line 161 and pixel electrodes 165, 166 and 167 can be made of non-transparent conductive material.

[0067] In the array substrate of the IPS-LCD device according to the third embodiment of the present invention, since the data line 141 overlaps the first common electrode 117 and the data line 141 and the first common electrode 117 operate as a black matrix, the black matrix of the upper substrate can have only the row line. Therefore, the black matrix of the upper substrate can be improved by using the area near the data line 141 as a pixel region. Moreover, in other embodiments, the common electrodes 117, 118 and 119 can be patterned on the gate insulator 121.

[0068] FIG. 14 is a schematic cross-sectional view of an array substrate of the IPS-LCD device taken along a line "XIV-XIV" of FIG. 12B, in which the data line 141 covers the first common electrode 117.

[0069] FIGS. 15A and 151B are schematic plan views of an array substrate of the IPS-LCD device according to a fifth embodiment and a sixth embodiment of the present invention with the more improved aperture ratio.

[0070] As shown, a gate line 111 and gate electrode 113 are patterned on an insulating substrate (not shown). A gate insulator (not shown), for example, silicon nitride film (SiNx) or silicon oxide film (SiO<sub>2</sub>), is formed thereon. An active layer 131 of amorphous silicon is patterned on the gate insulator of the gate electrode 113 and an ohmic contact layer of doped amorphous silicon is formed thereon. Then a data line 141, which defines a pixel region by crossing the gate line 111, and source and drain electrodes 143 and 145 are patterned thereon. The data line 141 has a substantially zigzag shape. The data line 141 and the source and drain electrodes 143 and 145 can be made of a metal. A passivation layer is formed thereon and has a contact hole 153 exposing the drain electrode 145. Here, the passivation layer can be made of silicon nitride film (SiNx) or silicon oxide film (SiO<sub>2</sub>) like the gate insulator, or organic material such as BCB, acrylate, or polyimide. First to third pixel electrodes 165, 166 and 167 and first to third common electrodes 171, 168 and 169 having a substantially zigzag shape are patterned in the pixel region on the passivation layer. In the context of FIGS. 15A and 15B, the pixel electrodes 165, 166 and 167 and the common electrodes 171, 168 and 169 extend roughly vertically and are spaced apart from each other horizontally. The pixel electrodes 165, 166 and 167 are alternated with the common electrodes 171, 168 and 169. The first common electrode 171 overlaps the data line 141 in FIG. 15A or covers the data line 141 in FIG. 15B and extends to another common electrode of a neighboring pixel. A pixel line 161 is connected to the pixel electrodes 165, 166 and 167 and overlaps with the metal common line 147, which is connected to the common line 164 through the contact hole 155, to form a storage capacitor. The storage capacitor can be made between the pixel line 161 and the previous or adjacent gate line. The first pixel electrode 165 is connected to the drain electrode 145 through a contact hole 153. Here, the first common electrode 171 is formed of non-transparent material such as metal and the other common electrodes 168 and 169, and the pixel electrodes 165, 166 and 167 and the pixel line 161 are formed of transparent conductive material such as ITO or IZO.

[0071] FIGS. 16A to 16F are sequential cross-sectional views taken along a line "XVI-XVI" of FIG. 15A showing the fabrication process.

[0072] As shown in FIG. 16A, a gate line 111 and a gate electrode 113 are patterned on a substrate 100 such as glass. The gate line 111 is horizontally elongated.

[0073] As shown in FIG. 16B, a gate insulator 121 is formed on the entire surface of the substrate 100 and then an active layer 131, of amorphous silicon and an ohmic contact layer 133 of doped amorphous silicon are patterned. Here, the gate insulator 121 can be made of silicon nitride film (SiNx), silicon oxide film (SiO<sub>2</sub>) or organic material such as BCB, acrylate, or polyimide.

[0074] As shown in FIG. 16C, a data line 141, source and drain electrodes 143 and 145 and a metal common line 147 of conductive material such as metal are patterned. The data line 141 defines a pixel region by crossing with the gate line 111 and source and drain electrodes 143 and 145 are adjacent to each other with the gate electrode 113 below the source and drain electrodes 143 and below a space separating the source and drain electrodes 143 and 145. Here, the data line 141 has a substantially zigzag shape and the metal common line 147 operates as a lower electrode of a storage capacitor.

[0075] As shown in FIG. 16D, a passivation layer 151 of silicon nitride film (SiNx), silicon oxide film (SiO<sub>2</sub>) or organic material such as BCB, acrylate, or polyimide is formed on the entire surface of the substrate, and then a contact hole 153 exposing the drain electrode 145 is patterned. In the case of using organic material of low dielectric constant such as BCB, acrylate or polyimide for the passivation layer, the interference of the first common electrode 171 voltage, which results from the overlap of the data line 141 and the first common electrode 171, can be minimized.

[0076] As shown in FIG. 16E, first to third pixel electrodes 165, 166 and 167, a pixel line 161 and second and third common electrodes 168 and 169 of transparent conductive material such as indium-tin-oxide (ITO) or indium-zinc-oxide (IZO) are patterned.

[0077] As shown in FIG. 16F, subsequently, the first common electrode 171 of conductive material such as metal is patterned, connected to the common line 164 as in FIGS. 15A and 15B and overlaps a portion of the data line 141. The first common electrode 171 can be made during the step of forming the gate electrode 113. The other common electrodes 168 and 169 and the pixel electrodes 165, 166 and 167 can be made of transparent conductive material such as ITO or IZO, so that the data line 141 also can be formed in

the substantially zigzag shape regardless of the material of the black matrix formed on the upper substrate, and the transmittance and the aperture ratio can be improved. Here, in the context of FIGS. 15A and 15B, the first to third pixel electrodes 165, 166 and 167 and the first to third common electrodes 171, 168 and 169 having a substantially zigzag shape extend in roughly a vertical direction and are spaced apart horizontally from each other in an alternating pattern. Even though first to third pixel electrodes 165, 166 and 167, a pixel line 161 and second and third common electrodes 168 and 169 are patterned and then the first common electrode 171 is patterned, the first common electrode 171 can be patterned before the third pixel electrodes 165, 166 and 167, the pixel line 161 and the second and third common electrodes 168 and 169, which can be patterned later. Even though the storage capacitor is formed between the metal common line 147 and the pixel line 161, another structure of storage capacitor can be adopted as one of skill in the art would understand.

[0078] FIG. 17 is a schematic cross-sectional view of an array substrate of the IPS-LCD device taken along a line "XVII-XVII" of FIG. 15B, in which the first common electrode 171 covers the data line 141.

[0079] In the array substrate of the IPS-LCD device according to the fifth and sixth embodiments of the present invention, even though the first common electrode 171 that overlaps or covers the data line 141 is made of opaque material such as Cr or Al, the second and third common electrodes 168 and 169 are made of transparent material such as ITO or IZO. Therefore, the aperture ratio can be improved by increase of transmittance. Moreover, since the common and pixel electrodes are formed on the same layer, the problem of residual images can be solved.

[0080] Consequently, in the IPS-LCD device for wide viewing angle, since the common electrodes are made of a transparent material such as ITO or IZO and at least one common electrode overlaps or covers the data line, the aperture ratio can be improved and the problems such as residual images or flicker can be solved with the metallic black matrix of the upper substrate. On the other hand, to

decrease the power consumption, a black matrix of the upper substrate should be made of resin. In other embodiments, one of the common electrodes can be formed to overlap partially or to cover the data line and operate as the black matrix, so that the black matrix of the upper substrate can be made of resin, and the driving voltage and the power consumption can be reduced. Therefore, since the data line can be made in a substantially zigzag shape regardless of the material of the black matrix formed on the upper substrate, the multi-domain IPS-LCD device actually can be fabricated without increasing the driving voltage or decreasing aperture ratio.

[0081] It will be apparent to those skilled in the art that various modifications and variation can be made in the method of manufacturing a flat pane display device of the present invention without departing from the spirit or scope of the invention. Thus, it is intended that the present invention cover the modifications and variations of this invention provided they come within the scope of the appended claims and their equivalents.

- 1. An array substrate for an in-plane switching liquid crystal display device, comprising:

- a substrate;

- a gate line and a data line on the substrate, the data line having at least one bent portion;

- a thin film transistor at a crossing portion of the gate and data lines:

- a plurality of common electrodes having at least one bent portion, at least one overlapping common electrode overlapping at least a portion of the data line;

- a common line connected to the common electrodes; and

- a plurality of pixel electrodes alternated with the common electrodes, each pixel electrode having at least one bent portion.

- 2-28. (Cancelled)

\* \* \* \* \*

| 公开(公告)号 US20040263755A1 公开(公告)日 2004-12-30 申请号 US10/893951 申请日 2004-07-20  [标]申请(专利权)人(译) IK KIM SOO 金昌YEON KIM GI HONG 申请(专利权)人(译) KIM IK-SOO 金昌YEON KIM GI-HONG  当前申请(专利权)人(译) LG DISPLAY CO., LTD.  [标]发明人 KIM IK SOO KIM CHANG YEON KIM GI HONG  发明人 KIM, IK-SOO KIM, GH-HONG  IPC分类号 G02F1/1335 G02F1/1343 G02F1/1362  CPC分类号 G02F1/133512 G02F1/134363 G02F1/136209 G02F1/136286  优先权 1020010002969 2001-01-18 KR 102000067516 2000-11-14 KR  其他公开文献 US7006189  外部链接 Espacenet USPTO | 专利名称(译)        | 面内切换模式液晶显示装置及其制造方法                                  |         |            |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------|---------|------------|--|--|

| 「标]申请(专利权)人(译)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)号        | <u>US20040263755A1</u>                              | 公开(公告)日 | 2004-12-30 |  |  |

| 金昌YEON KIM GI HONG  申请(专利权)人(译) KIM IK-SOO 金昌YEON KIM GI-HONG  当前申请(专利权)人(译) LG DISPLAY CO., LTD.  [标]发明人 KIM IK SOO KIM CHANG YEON KIM GI HONG  发明人 KIM, IK-SOO KIM, CHANG-YEON KIM, GI-HONG  IPC分类号 G02F1/1335 G02F1/1343 G02F1/1362  CPC分类号 G02F1/133512 G02F1/134363 G02F1/136209 G02F1/136286  优先权 1020010002969 2001-01-18 KR 1020000067516 2000-11-14 KR                                                                                                                            | 申请号            | US10/893951                                         | 申请日     | 2004-07-20 |  |  |

| 金昌YEON KIM GI-HONG  当前申请(专利权)人(译) LG DISPLAY CO., LTD.  [标]发明人 KIM IK SOO KIM CHANG YEON KIM GI HONG  发明人 KIM, IK-SOO KIM, CHANG-YEON KIM, GI-HONG  IPC分类号 G02F1/1335 G02F1/1343 G02F1/1362  CPC分类号 G02F1/133512 G02F1/134363 G02F1/136209 G02F1/136286  优先权 1020010002969 2001-01-18 KR 1020000067516 2000-11-14 KR                                                                                                                                                                       | [标]申请(专利权)人(译) | 金昌YEON                                              |         |            |  |  |

| 「「「「大大大」   KIM IK SOO   KIM CHANG YEON   KIM GI HONG                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请(专利权)人(译)    | 金昌YEON                                              |         |            |  |  |

| KIM CHANG YEON   KIM GI HONG                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 当前申请(专利权)人(译)  | LG DISPLAY CO. , LTD.                               |         |            |  |  |

| KIM, CHANG-YEON   KIM, GI-HONG     IPC分类号   G02F1/1335 G02F1/1343 G02F1/1362     CPC分类号   G02F1/133512 G02F1/134363 G02F1/136209 G02F1/136286     优先权   1020010002969 2001-01-18 KR   1020000067516 2000-11-14 KR     其他公开文献   US7006189                                                                                                                                                                                                                                                   | [标]发明人         | KIM CHANG YEON                                      |         |            |  |  |

| CPC分类号       G02F1/133512 G02F1/134363 G02F1/136209 G02F1/136286         优先权       1020010002969 2001-01-18 KR 1020000067516 2000-11-14 KR         其他公开文献       US7006189                                                                                                                                                                                                                                                                                                                  | 发明人            | KIM, CHANG-YEON                                     |         |            |  |  |

| 优先权     1020010002969 2001-01-18 KR<br>1020000067516 2000-11-14 KR       其他公开文献     US7006189                                                                                                                                                                                                                                                                                                                                                                                              | IPC分类号         | G02F1/1335 G02F1/1343 G02F1/1362                    |         |            |  |  |

| 其他公开文献     US7006189                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CPC分类号         | G02F1/133512 G02F1/134363 G02F1/136209 G02F1/136286 |         |            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 优先权            |                                                     |         |            |  |  |

| 外部链接 <u>Espacenet</u> <u>USPTO</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 其他公开文献         | US7006189                                           |         |            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 外部链接           | Espacenet USPTO                                     |         |            |  |  |

## 摘要(译)

在具有宽视角的典型IPS-LCD装置中,由于上基板的金属黑矩阵影响公共电极和像素电极之间的电压,因此黑矩阵由树脂制成并且不能形成弯曲部分,因为加工技术的局限性。因此,典型的IPS-LCD装置具有有效实现的限制和低孔径比。在所公开的IPS-LCD装置中,由于形成公共电极之一以覆盖数据线并作为黑矩阵操作,所以上基板的黑矩阵可以由树脂制成并且可以降低驱动电压。因此,实际上,可以在不增加驱动电压和降低孔径比的情况下制造多畴IPS-LCD器件。此外,由于公共电极和像素电极形成在同一层上,因此可以提高开口率并且可以解决诸如残留图像或闪烁的问题。