US 20010005252A1

(19) United States

(12) Patent Application Publication

Lee et al.

(10) Pub. No.: US 2001/0005252 A1

(43) Pub. Date: Jun. 28, 2001

(54) IN PLANE SWITCHING MODE LIQUID CRYSTAL DISPLAY DEVICE AND METHOD FOR MANUFACTURING THE SAME

(76) Inventors: Kyung Ha Lee, Kyoungki-do (KR); Jeong Geun Kim, Kyoungki-do (KR); Seung Yik Park, Seoul (KR)

Correspondence Address:

Thomas F. Peterson

c/o Ladas & Parry

Suite 1200

224 South Michigan Avenue

Chicago, IL 60604 (US)

(21) Appl. No.: 09/740,558

(22) Filed: Dec. 19, 2000

(30) Foreign Application Priority Data

Dec. 22, 1999 (KR) ..... 99-60328

Publication Classification

(51) Int. Cl.<sup>7</sup> ..... G02F 1/1343

(52) U.S. Cl. ..... 349/141; 349/139

(57) ABSTRACT

Disclosed is an in plane switching (IPS) mode LCD device and method for manufacturing the same. The IPS mode LCD device of the present invention includes a transparent insulating substrate, a gate bus line and a data bus line arranged in a cross fashion on the transparent insulating substrate to define a unit pixel area, a common electrode line disposed in parallel to the gate bus line while being spaced at most apart from the gate bus line in the unit pixel area, the common electrode line having a pair of shields respective disposed at both lateral edges of the unit pixel area, a thin film transistor disposed near an intersection of the gate bus line and the data bus line, a counter electrode arranged in the unit pixel area between the shield of the common electrode line and made of a transparent conductor, the counter electrode including a plurality of branches arranged in parallel to the data bus line, and a bar contacting the common electrode line and connecting respective one-side ends of the branches together, and a pixel electrode formed of a transparent conductor and including a pair of first electrode parts respectively overlapping with the shields of the common electrode line while extending in parallel to the data bus line, second electrode parts interposed each between adjacent ones of the branches included in the counter electrode, and a third electrode part contacting a part of the thin film transistor while connecting together respective one-side ends of the first and second electrode parts.

FIG.1

(PRIOR ART)

FIG.2

(PRIOR ART)

FIG.3

FIG.4

FIG.5

## IN PLANE SWITCHING MODE LIQUID CRYSTAL DISPLAY DEVICE AND METHOD FOR MANUFACTURING THE SAME

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The invention relates to a liquid crystal display (LCD) device, and more particularly to an LCD device of in plane switching mode (IPS mode) with an enhanced aperture ratio and an enhanced transmittance, and a method for manufacturing the same.

[0003] 2. Description of the Related Art

[0004] LCD devices have various advantages that they are light in weight, thin in thickness and low in power consumption, as compared to cathode ray tube (CRT) display devices. Therefore, such LCD devices are used in various terminals of information system and video units and the like, as a substitute for the CRT display devices. The LCD device typically adopts TN (Twist Nematic) mode as a LCD driving method. However, the widely utilized TN mode LCD device is disadvantageous in that its viewing angle is narrow. In order to eliminate the problem involved due to such a narrow viewing angle, therefore, plane switching (IPC) mode LCD devices have been proposed.

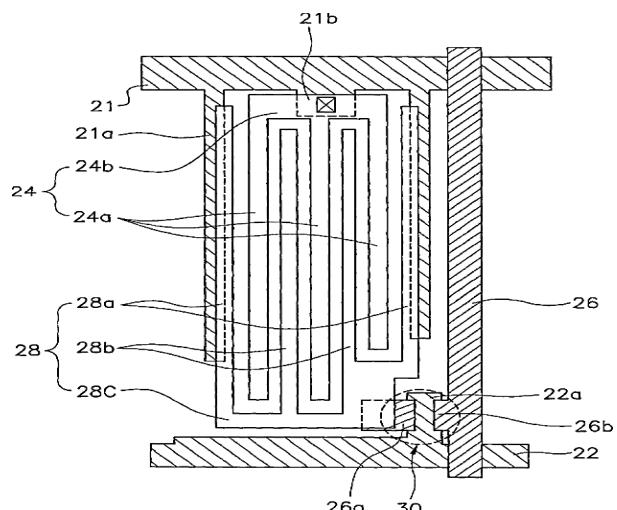

[0005] FIG. 1 shows a plan view of a conventional IPS mode LCD device. Its structure will now be described with reference to FIG. 1.

[0006] As shown in FIG. 1, a gate bus line 2 and a data bus line 6 are arranged in such a fashion that they cross each other, to define a unit pixel. A thin film transistor (TFT) 10 as a switching element is disposed near the intersection of the gate bus line 2 and the data bus line 6. As well known, the TFT 10 includes a gate electrode 2a, a channel layer (not shown), and source/drain electrodes 6a and 6b. A counter electrode 4 is also disposed in the unit pixel. The counter electrode 4 comprises a pair of first branches 4a disposed at the both sides of the unit pixel in parallel to the data bus line 6, second branches 4b interposed between the first branches 4a, and a bar 4c functioning as a common electrode line. The bar 4c extends in parallel to the gate bus line 2 while being spaced apart from the gate bus line 2 by a maximum distance in the unit pixel. The bar 4c connects respective one-side ends of the first branches 4a and second branches 4b together. A pixel electrode 8 is also disposed in the unit pixel. The pixel electrode 8 comprises a pair of first electrode parts 8a overlapping with respective first branches 4a of the counter electrode 4, second electrode parts 8b interposed between the second branches 4b of the counter electrode 4, and a third electrode part 8c connecting together respective ends of the first and second electrode parts 8a and 8b arranged near the gate bus line 2 while contacting the source electrode 6a of the TFT 10.

[0007] Meanwhile, although not shown, an upper substrate is disposed over the lower substrate having the above-described structure while being spaced apart from the lower substrate by a desired distance. A liquid crystal layer comprising a number of liquid crystal molecules is interposed between the upper substrate and the lower substrate.

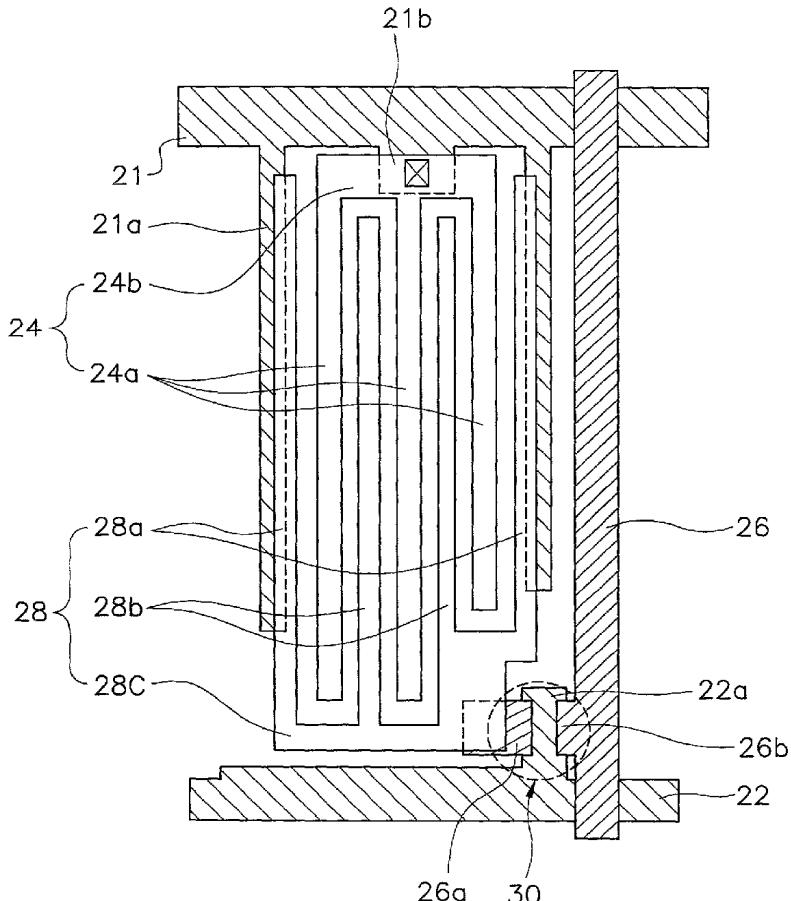

[0008] FIG. 2 shows a cross-sectional view of the conventional IPS mode LCD device. Referring to FIG. 2, the fabrication of this device will be described.

[0009] A certain opaque metal film is deposited on a glass plate 1. The opaque metal film is patterned according to a known photo process, thereby forming a gate bus line (not shown) including a gate electrode 2a, and a counter electrode 4 including first and second branches 4a and 4b and a bar (not shown). A gate insulating film 3 is then deposited over the entire upper surface of the glass plate 1 with the gate bus line and the counter electrode formed. A channel layer 5 is formed on a portion of the gate insulating film 3 covering the gate electrode 2a. A metal film for source/drain is deposited on the channel layer 5 and the exposed portion of the gate insulating film 3. By patterning the metal film for source/drain, a data bus line 6 having a source electrode 6a and a drain electrode 6b is formed. Thus, a TFT 10 is fabricated. An ohmic contact layer (not shown) is interposed between the channel layer 5 and the source/drain electrodes 6a and 6b.

[0010] A protection layer 7 is deposited over the resultant structure obtained after completion of the above process, followed by an etching treatment to expose a part of the protection layer 7. A transparent metal film, such as an ITO film is deposited on the protection layer 7 and patterned to form a pixel electrode 8 having first, second and third electrode parts 8a, 8b, and 8c. The third electrode part 8c of the pixel electrode 8 is arranged to contact the source electrode 6a of the TFT 10.

[0011] Such an IPS mode LCD device has a structure in which its counter electrode and its pixel electrode for driving liquid crystals are arranged in parallel to each other on a single substrate. Therefore, an electric field generated between the counter electrode and the pixel electrode is parallel to the main surface of the substrate. Consequently, since the liquid crystal molecules are aligned in such a fashion that their long axis are oriented in parallel to the electric field, users can see the long axes of the liquid crystal molecules in any directions. Thus, the IPS mode LCD device has improved characteristics in terms of the viewing angle, as compared to TN mode LCD device.

[0012] However, the above-mentioned conventional IPS mode LCD device fails to satisfactorily improve the aperture ratio and transmittance because the counter electrode and the pixel electrode are formed of opaque metals. Moreover, the IPS mode LCD device can have a desired brightness only at an increased intensity of back light resulting in an increased consumption of electric power.

### SUMMARY OF THE INVENTION

[0013] Therefore, in one aspect of the present invention, it is an object to provide an IPS mode LCD device with an enhanced aperture ratio and an enhanced transmittance.

[0014] Further, in another aspect of the present invention, it is an object to provide a method for manufacturing an IPS mode LCD device with an enhanced aperture ratio and an enhanced transmittance.

[0015] In accordance with one aspect, the present invention provides an in plane switching mode liquid crystal display device comprising: a transparent insulating substrate; a gate bus line and a data bus line arranged in a cross fashion on the transparent insulating substrate to define a unit pixel area; a common electrode line disposed in parallel to the gate bus line while being spaced at most apart from the

gate bus line in the unit pixel area, the common electrode line having a pair of shields respective disposed at both lateral edges of the unit pixel area; a thin film transistor disposed near an intersection of the gate bus line and the data bus line; a counter electrode arranged in the unit pixel area between the shield of the common electrode line and made of a transparent conductor, the counter electrode including a plurality of branches arranged in parallel to the data bus line, and a bar contacting the common electrode line and connecting respective one-side ends of the branches together; and a pixel electrode formed of a transparent conductor and including a pair of first electrode parts respectively overlapping with the shields of the common electrode line while extending in parallel to the data bus line, second electrode parts interposed each between adjacent ones of the branches included in the counter electrode, and a third electrode part contacting a part of the thin film transistor while connecting together respective one-side ends of the first and second electrode parts.

[0016] In accordance with another aspect, the present invention provides a method for manufacturing an in plane switching (IPS) mode LCD device comprising steps of: depositing a first opaque metal film over a transparent insulating substrate; patterning the first opaque metal film to form a gate bus line including a gate electrode and a common electrode line disposed in parallel to the gate bus line while being spaced at most apart from the gate bus line in a unit pixel and having a pair of shields disposed at both lateral edges of the unit pixel; forming a gate insulating film on the transparent insulating substrate to cover the gate bus line and the common electrode line; forming a channel layer on the gate insulating part over the gate electrode; forming source/drain electrodes on the channel layer to form a thin film transistor (TFT) and to define a unit pixel, and forming a data bus line to be arranged in a cross fashion with respect to the gate bus line; forming, on a structure obtained after completion of the formation of the source/drain electrodes and the data bus line, a protection layer having contact holes, through which the common electrode line and the thin film transistor are partially exposed, respectively; depositing a transparent conductor on the protection layer; and patterning the transparent conductor to form a counter electrode including a plurality of branches arranged in parallel to the data bus line and a bar contacting the common electrode line and connecting respective one-side ends of the branches together, and a pixel electrode having a pair of first electrode parts overlapping the shields of the common electrode line while being parallel to the data bus line, second electrode parts each interposed between adjacent ones of the branches of the counter electrode, and a third electrode part connecting to respective one-side ends of the first and second electrode parts together and contacting a portion of the thin film transistor.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0017] The above objects, and other features and advantages of the present invention will become more apparent after a reading of the following detailed description when taken in conjunction with the drawings, in which:

[0018] FIG. 1 is a plan view of a conventional IPS mode LCD device;

[0019] FIG. 2 is a cross-sectional view of the conventional IPS mode LCD device;

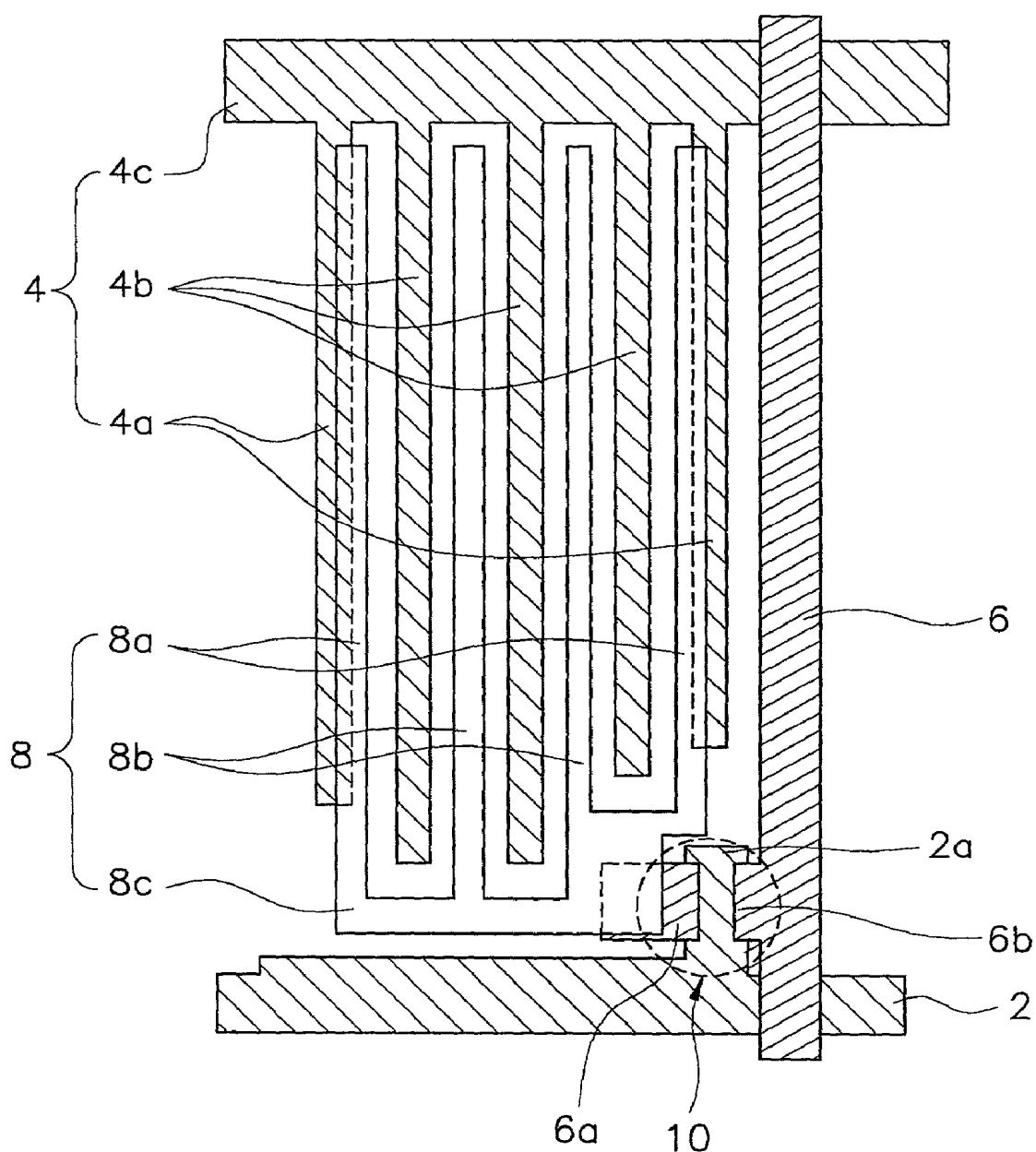

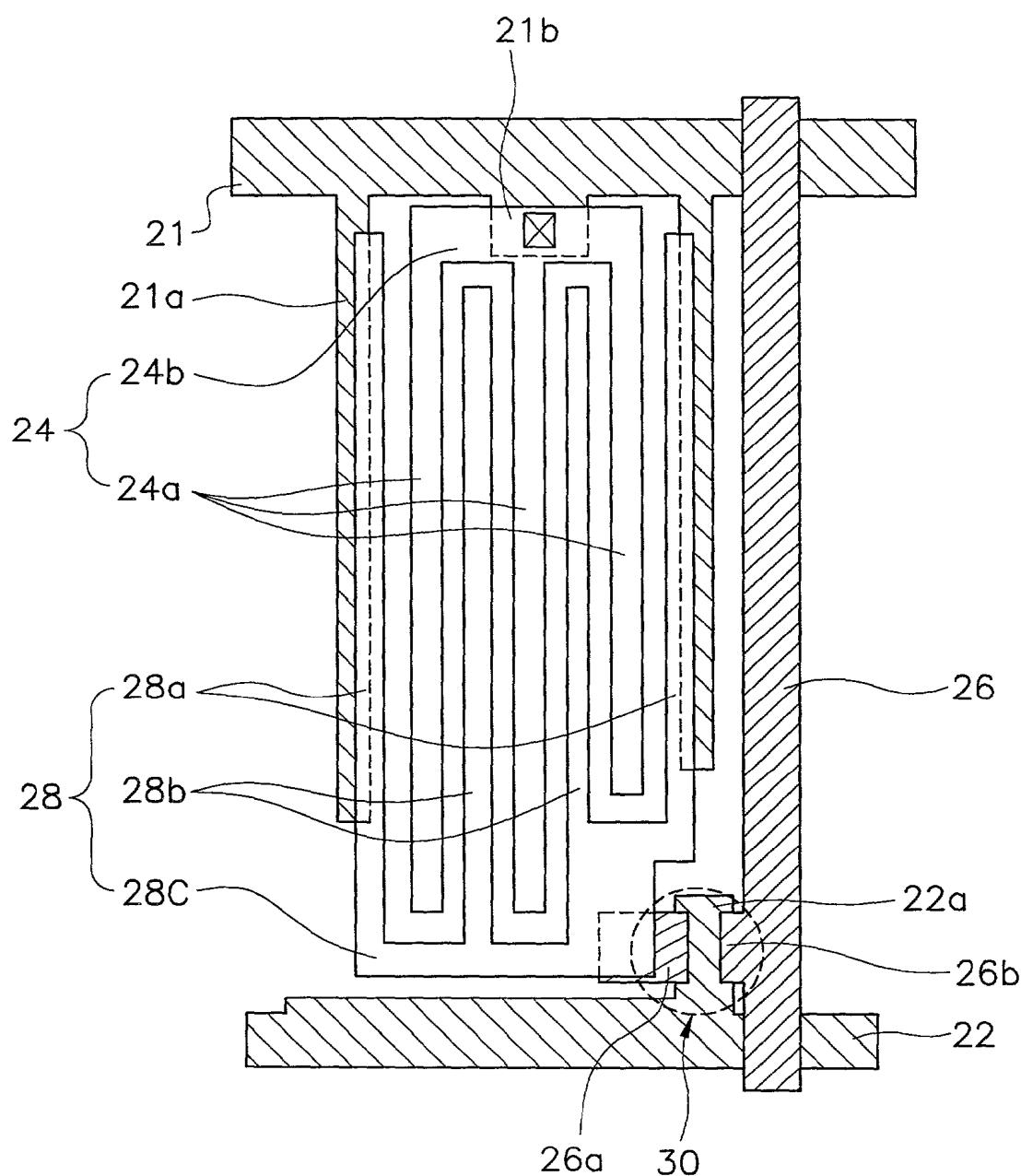

[0020] FIG. 3 is a plan view of an IPS mode LCD device according to an embodiment of the present invention;

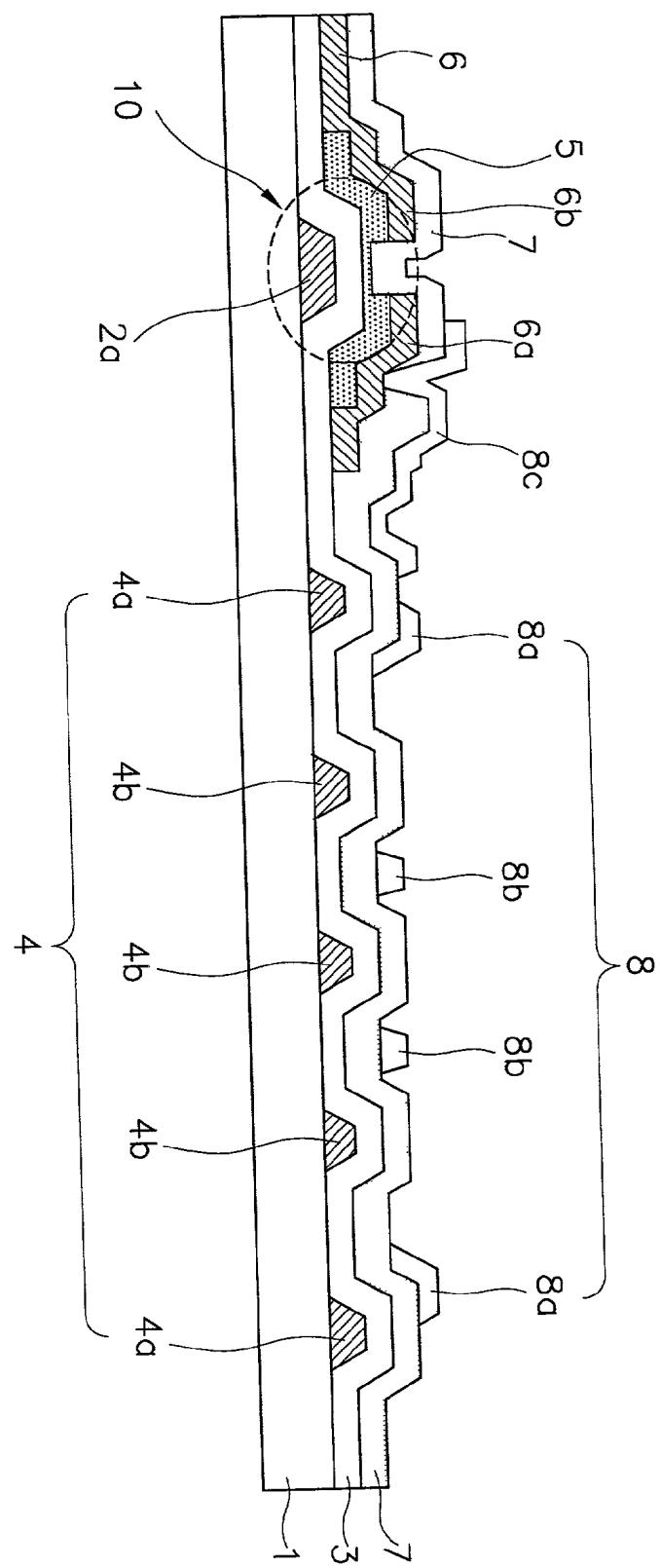

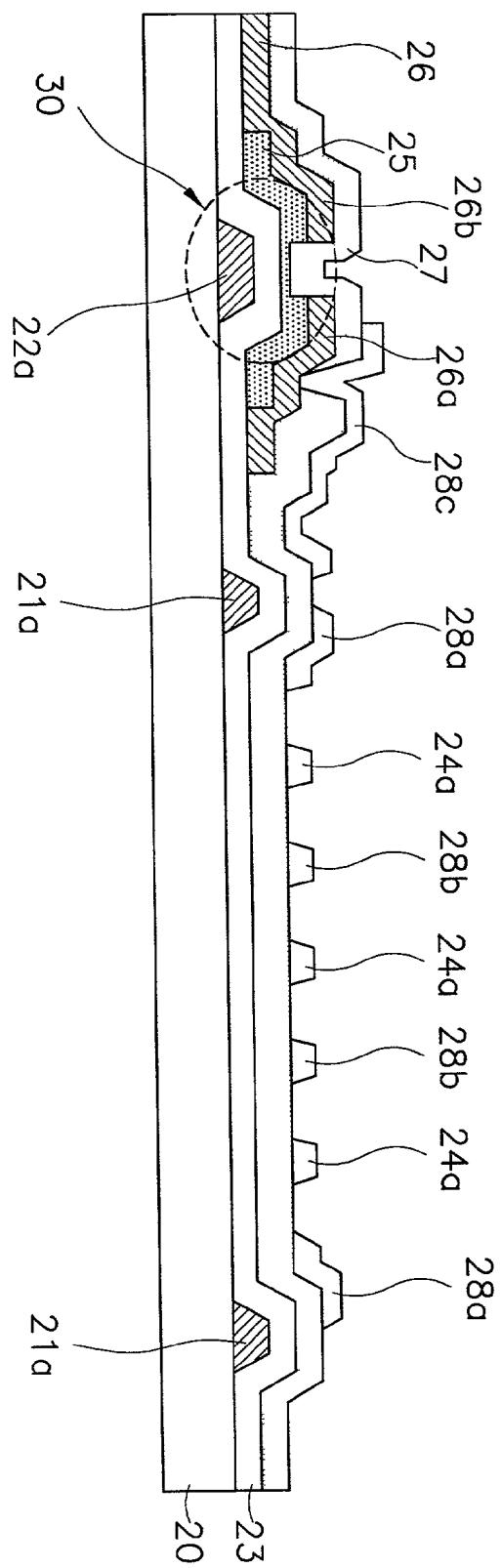

[0021] FIG. 4 is a cross-sectional view of the IPS mode LCD device according to the embodiment of the present invention; and

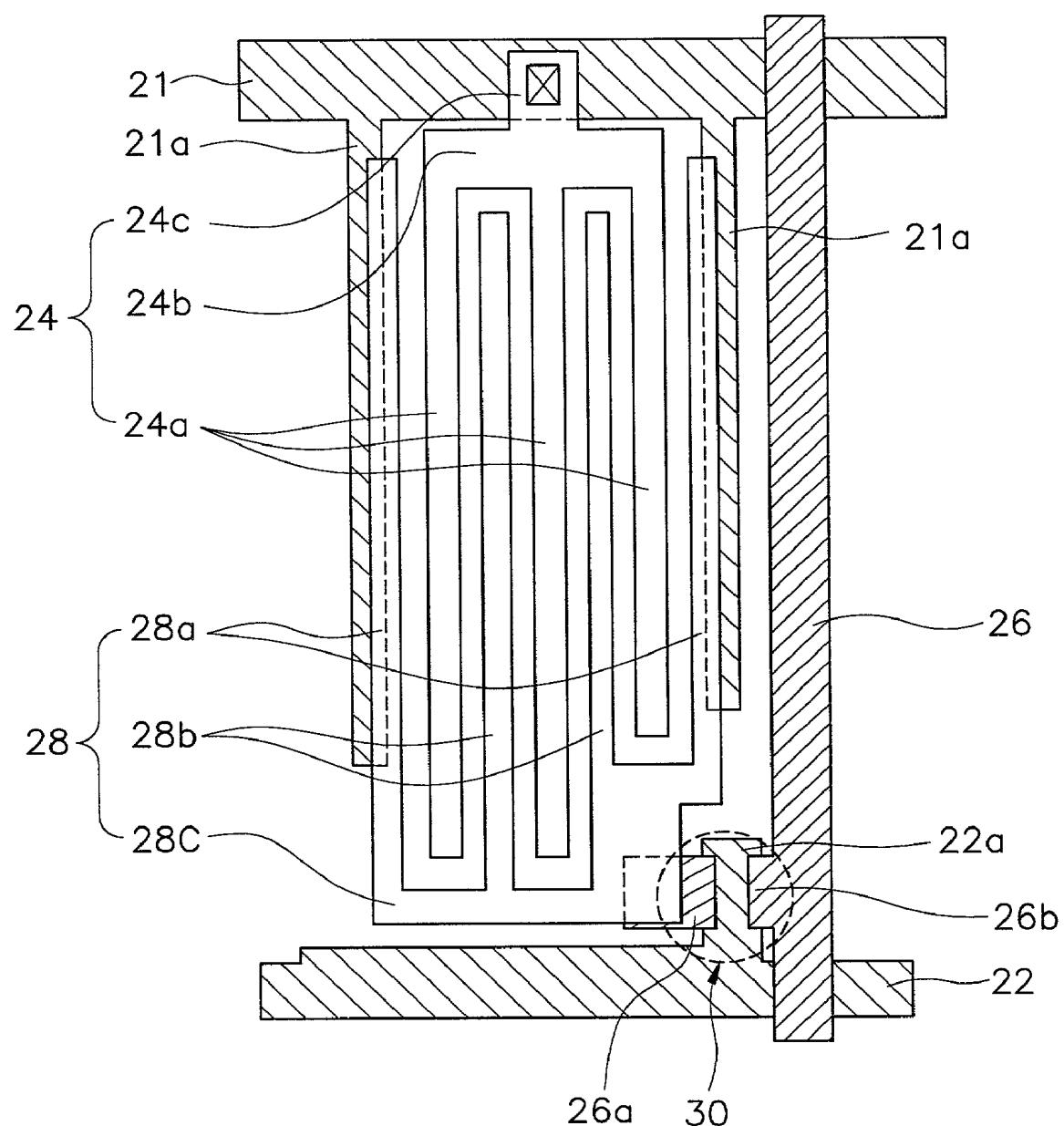

[0022] FIG. 5 is a plan view of an IPS mode LCD device according to another embodiment of the present invention.

#### DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0023] Now, an IPS mode LCD device and a fabrication method therefor according to a preferred embodiment of the present invention will be described in detail, with reference to the annexed drawings.

[0024] FIG. 3 is a plan view of an IPS mode LCD device according to an embodiment of the present invention. As shown, a gate bus line 22 and a data bus line 26 are arranged in such a fashion that they cross each other, to define a unit pixel.

[0025] A common electrode line 21 extends in parallel to the gate bus line 22 while being spaced apart from the gate bus line 22 by a maximum distance in the unit pixel. The common electrode line 21 is arranged on the same plane as the gate bus line 22. Also, the common electrode line 21 is made of the same material as the gate bus line 22. The common electrode line 21 is provided with a pair of shields 21a which are branched from the common electrode line 21 while extending in parallel to the data bus line 26. The shields 21a are disposed at both lateral edges of the unit pixel, respectively. The common electrode line 21 has a protrusion 21b slightly extending toward the inside of the pixel.

[0026] A TFT 30 as a switching element is disposed near the intersection of the gate bus line 22 and the data bus line 26. The TFT 30 includes a gate electrode 22a extending from the gate bus line 22, a channel layer (not shown) arranged over the gate electrode 22a, a drain electrode 26b extending from the data bus line 26 while overlapping with one lateral portion of the channel layer, and a source electrode 26a overlapping with the other lateral portion of the channel layer. A counter electrode 24 is also disposed in the unit pixel. The counter electrode 24 includes a plurality of first branches 24a disposed in parallel to the data bus line 26 within a pixel region defined between the shields 21a of the common electrode line 21, and a bar 24bc connecting respective one-side ends of the branches 24a together while contacting the protrusion 21b of the common electrode line 21. The counter electrode 24 is made of a transparent conductive material, for example, an ITO.

[0027] A pixel electrode 28 is also disposed in the unit pixel. The pixel electrode 28 includes a pair of first electrode parts 28a overlapping with respective shields 21a of the common electrode line 21 while extending in parallel to the data bus line 26, second electrode parts 28b each interposed between adjacent ones of the branches 24a of the counter electrode 24, and a third electrode part 28c connecting together respective ends of the first and second electrode parts 28a and 28b arranged near the gate bus line 22 while contacting the source electrode 26a of the TFT 30.

[0028] FIG. 4 shows a cross-sectional view of the IPS mode LCD device according to the embodiment of the

present invention. As shown, a first opaque metal film having a superior conductivity is deposited a transparent insulating substrate, for example a glass substrate **20**, and then patterned according to a known photo process to form a common electrode line having a pair of shields **21a** and a gate bus line having a gate electrode **22a**. Over the resultant structure, a gate insulating film **23** is then formed.

[0029] A channel layer **25** made of an undoped amorphous silicon is formed on a portion of the gate insulating film **23** over the gate electrode **22a** by a known method. A second opaque metal film for source/drain is deposited on the gate insulating film **23** including the channel layer, and then patterned according to the known photo process to form a data bus line having source/drain electrodes **26a** and **26b**. As such, a TFT **30** is constructed. Here, although not shown, an ohmic contact layer of a doped amorphous silicon is formed between the channel layer **25** and the source/drain electrodes **26a** and **26b**. A protection layer **27** such as a silicon nitride film is deposited over the resultant structure obtained after completion of the above process. Then, predetermined parts of the protection layer **27** are selectively subjected to an etching treatment so that the source electrode **26a** of the TFT and the common electrode line are partially exposed.

[0030] As a transparent conductor, a film selected from a group consisting of an ITO film, an IXO film made of a mixture of InO<sub>3</sub> and ZnO<sub>3</sub>, or an NiSi<sub>2</sub> film is deposited over the protection layer **27** to completely fill holes formed by the etching treatment. By patterning of the transparent conductor by the known photo process, a counter electrode is formed which has a plurality of branches **24a**, and a bar connecting respective one-side ends of the branches **24a** together. Simultaneously, a pixel electrode **28** is also formed which includes a pair of first electrode parts **28a** overlapping with respective shields **21a** of the common electrode line, second electrode parts **28b** each interposed between adjacent ones of the branches **24a** of the counter electrode, and a third electrode part **28c** connecting together respective ends of the first and second electrode parts **28a** and **28b** arranged near the gate bus line while contacting the source electrode **26a** of the TFT.

[0031] Here, the branches **24a** of the counter electrode and the first and second electrode parts **28a** and **28b** of the pixel electrode are formed to have a width of not more than 10  $\mu\text{m}$ , preferably 5 to 10  $\mu\text{m}$ . Also, the branches **24a** of the counter electrode and the first and second electrode parts **28a** and **28b** of the pixel electrode has a spacing of not more than 10  $\mu\text{m}$ , preferably 5 to 10  $\mu\text{m}$ .

[0032] The bar of the counter electrode is formed to contact the protrusion of the common electrode line through a hole formed on the protection layer **27**. When an NiSi<sub>2</sub> film is used as the transparent conductor, the NiSi<sub>2</sub> film will be deposited to a thickness of not more than 100 Å, preferably 50 to 100 Å.

[0033] The IPS mode LCD device according to the present invention has not only an enhanced viewing angle, as compared to TN mode LCD devices, but also an improved aperture ratio and enhanced transmittance, as compared to those of the conventional IPS mode LCD device.

[0034] In detail, aperture ratio and transmittance depend on an opening area, that is, a light transmission area defined in the pixel. Up to now, since the counter electrode is formed

of an opaque metal, the pixel area corresponding to the area of the counter electrode does not permit transmission of light. However, the counter electrode according to the present invention is formed of a transparent conductor, so that light can be transmitted through the counter electrode. Therefore, the IPS mode LCD device of the present invention has an aperture ratio and transmittance more improved than those of the prior art in that light is transmitted to the counter electrode part.

[0035] FIG. 5 shows a plan view of an IPS mode LCD device according to another embodiment according to the present invention. In this embodiment, the common electrode line **21** does not have the protrusion **21b**. In stead, the counter electrode **24** includes a protrusion **24c** for easiness of an electrical contact with the common electrode line **21**. Here, as the protrusion **24c** is made of a transparent conductor, this embodiment exhibits an aperture ratio and transmittance better than the above embodiment.

[0036] As apparent from the above description, according to the present invention, the counter electrode is made of a transparent conductor, whereby the opening area in the pixel area is increased. Accordingly, it is possible to obtain an IPS mode LCD device having an improved aperture ratio and transmittance.

[0037] Further, according to the present invention, since there is no surface topology resulting from the counter electrode, the deposition process for the protection layer and the following rubbing process can be stably carried out. Thus, an enhance production yield may be achieved.

[0038] Although the preferred embodiments of the invention have been disclosed for illustrative purposes, those skilled in the art will appreciate that various modifications, additions and substitutions are possible, without departing from the scope and spirit of the invention as disclosed in the accompanying claims.

#### What is claimed:

1. An in plane switching mode liquid crystal display device comprising:

- a transparent insulating substrate;

- a gate bus line and a data bus line arranged in a cross fashion on the transparent insulating substrate to define a unit pixel area;

- a common electrode line disposed in parallel to the gate bus line while being spaced at most apart from the gate bus line in the unit pixel area, the common electrode line having a pair of shields respectively disposed at both lateral edges of the unit pixel area;

- a thin film transistor disposed near an intersection of the gate bus line and the data bus line;

- a counter electrode arranged in the unit pixel area between the shield of the common electrode line and made of a transparent conductor, the counter electrode including a plurality of branches arranged in parallel to the data bus line, and a bar contacting the common electrode line and connecting respective one-side ends of the branches together; and

- a pixel electrode formed of a transparent conductor and including a pair of first electrode parts respectively overlapping with the shields of the common electrode

line while extending in parallel to the data bus line, second electrode parts interposed each between adjacent ones of the branches included in the counter electrode, and a third electrode part contacting a part of the thin film transistor while connecting together respective one-side ends of the first and second electrode parts.

**2.** The IPS mode LCD device according to claim 1, wherein the common electrode line further includes a protrusion contacting the bar of the counter electrode.

**3.** The IPS mode LCD device according to claim 1, wherein the bar of the counter electrode is provided with a protrusion contacting the common electrode line.

**4.** The IPS mode LCD device according to claim 1, wherein the branches of the counter electrode and the first and second electrode parts of the pixel electrode have a width of 5 to 10  $\mu\text{m}$ .

**5.** The IPS mode LCD device according to claim 1, wherein the branches of the counter electrode and the first and second electrode parts of the pixel electrode have a spacing of 5 to 10  $\mu\text{m}$ .

**6.** The IPS mode LCD device according to claim 1, wherein the transparent conductor is selected from a group consisting of an ITO film, an IXO film made of a mixture of  $\text{InO}_3$  and  $\text{ZnO}_3$ , and an  $\text{NiSi}_2$  film.

**7.** A method for manufacturing an in plane switching (IPS) mode LCD device comprising steps of:

depositing a first opaque metal film over a transparent insulating substrate;

patterning the first opaque metal film to form a gate bus line including a gate electrode and a common electrode line disposed in parallel to the gate bus line while being spaced at most apart from the gate bus line in a unit pixel and having a pair of shields disposed at both lateral edges of the unit pixel;

forming a gate insulating film on the transparent insulating substrate to cover the gate bus line and the common electrode line;

forming a channel layer on the gate insulating part over the gate electrode;

forming source/drain electrodes on the channel layer to form a thin film transistor (TFT) and to define a unit

pixel, and forming a data bus line to be arranged in a cross fashion with respect to the gate bus line;

forming, on a structure obtained after completion of the formation of the source/drain electrodes and the data bus line, a protection layer having contact holes, through which the common electrode line and the thin film transistor are partially exposed, respectively;

depositing a transparent conductor on the protection layer; and

patterning the transparent conductor to form a counter electrode including a plurality of branches arranged in parallel to the data bus line and a bar contacting the common electrode line and connecting respective one-side ends of the branches together, and a pixel electrode having a pair of first electrode parts overlapping the shields of the common electrode line while being parallel to the data bus line, second electrode parts each interposed between adjacent ones of the branches of the counter electrode, and a third electrode part connecting to respective one-side ends of the first and second electrode parts together and contacting a portion of the thin film transistor.

**8.** The method according to claim 7, wherein the common electrode line is formed to have a protrusion contacting the bar of the counter electrode.

**9.** The method according to claim 7, wherein the counter electrode is formed to have a protrusion contacting the common electrode line.

**10.** The method according to claim 7, wherein the transparent conductor is selected from a group consisting of an ITO film, an IXO film made of a mixture of  $\text{InO}_3$  and  $\text{ZnO}_3$ , and an  $\text{NiSi}_2$  film.

**11.** The method according to claim 10, wherein the  $\text{NiSi}_2$  film is deposited to a thickness of 50 to 100  $\text{\AA}$ .

**12.** The method according to claim 7, wherein the branches of the counter electrode and the first and second electrode parts of the pixel electrode are formed to have a width of 5 to 10  $\mu\text{m}$ .

**13.** The method according to claim 7, wherein the branches of the counter electrode and the first and second electrode parts of the pixel electrode have a spacing of 5 to 10  $\mu\text{m}$ .

\* \* \* \* \*

|                |                                                     |         |            |

|----------------|-----------------------------------------------------|---------|------------|

| 专利名称(译)        | 在平面切换模式中的液晶显示装置及其制造方法                               |         |            |

| 公开(公告)号        | <a href="#">US20010005252A1</a>                     | 公开(公告)日 | 2001-06-28 |

| 申请号            | US09/740558                                         | 申请日     | 2000-12-19 |

| [标]申请(专利权)人(译) | 李敬HA<br>金桢槿<br>朴升YIK                                |         |            |

| 申请(专利权)人(译)    | 李敬HA<br>金桢槿<br>朴升YIK                                |         |            |

| 当前申请(专利权)人(译)  | 李敬HA<br>金桢槿<br>朴升YIK                                |         |            |

| [标]发明人         | LEE KYUNG HA<br>KIM JEONG GEUN<br>PARK SEUNG YIK    |         |            |

| 发明人            | LEE, KYUNG HA<br>KIM, JEONG GEUN<br>PARK, SEUNG YIK |         |            |

| IPC分类号         | G02F1/136 G02F1/1343 G02F1/1368 G09F9/30            |         |            |

| CPC分类号         | G02F1/134363                                        |         |            |

| 优先权            | 1019990060328 1999-12-22 KR                         |         |            |

| 其他公开文献         | US6449027                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a>     |         |            |

### 摘要(译)

公开了一种面内切换(IPS)模式LCD装置及其制造方法。本发明的IPS模式LCD装置包括透明绝缘基板，栅极总线和数据总线，交叉排列在透明绝缘基板上以限定单位像素区域，公共电极线平行设置在透明绝缘基板上。栅极总线与单位像素区域中的栅极总线最多间隔开，公共电极线具有分别设置在单位像素区域的两个横向边缘处的一对屏蔽，薄膜晶体管设置在单元像素区域的交叉点附近。栅极总线和数据总线，一个反电极排列在屏蔽之间的单位像素区域公共电极线由透明导体制成，对电极包括与数据总线平行布置的多个分支，以及与公共电极线接触并将分支的各个一侧端连接在一起的条，以及像素电极由透明导体形成，并包括一对第一电极部分，分别与公共电极线的屏蔽层重叠，同时平行于数据总线延伸，第二电极部分插入在对电极中包括的相邻分支之间第三电极部分接触薄膜晶体管的一部分，同时将第一和第二电极的各个一侧端连接在一起部分。