US006590553B1

(12) **United States Patent**

Kimura et al.

(10) **Patent No.:** US 6,590,553 B1

(45) **Date of Patent:** Jul. 8, 2003

(54) **LIQUID CRYSTAL DISPLAY DEVICE AND METHOD FOR DRIVING THE SAME**

(75) Inventors: **Kazunori Kimura**, Tokyo (JP); **Hideki Asada**, Tokyo (JP)

(73) Assignee: **NEC Corporation**, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 41 days.

(21) Appl. No.: **09/621,534**

(22) Filed: **Jul. 21, 2000**

(30) **Foreign Application Priority Data**

Jul. 23, 1999 (JP) ..... 11-208329

Apr. 26, 2000 (JP) ..... 2000-125055

Jun. 8, 2000 (JP) ..... 2000-172582

(51) **Int. Cl.<sup>7</sup>** ..... **G09G 3/36**

(52) **U.S. Cl.** ..... **345/92; 345/98; 345/204**

(58) **Field of Search** ..... **345/87, 90-92, 345/97-100, 204-206, 690**

(56) **References Cited**

U.S. PATENT DOCUMENTS

4,781,437 A \* 11/1988 Shields et al. ..... 327/91

5,111,195 A \* 5/1992 Fukuoka et al. ..... 345/204

5,977,940 A \* 11/1999 Akiyama et al. ..... 345/205

6,107,980 A \* 8/2000 Hermanns et al. ..... 345/205

6,331,844 B1 \* 12/2001 Okumura et al. ..... 345/100

FOREIGN PATENT DOCUMENTS

|    |             |         |

|----|-------------|---------|

| JP | S59-170888  | 9/1984  |

| JP | 62-94828 A  | 5/1987  |

| JP | 63-41078 B2 | 8/1988  |

| JP | H1-158417   | 6/1989  |

| JP | 1-292979    | 11/1989 |

| JP | 02-116823 A | 5/1990  |

| JP | 2-272521    | 11/1990 |

| JP | 04-44092 A  | 2/1992  |

|    |             |         |

|----|-------------|---------|

| JP | H5-80716    | 4/1993  |

| JP | 5-173175    | 7/1993  |

| JP | 05-265403 A | 10/1993 |

| JP | 05-303078 A | 11/1993 |

| JP | 6-42130     | 6/1994  |

| JP | 7-20820     | 1/1995  |

| JP | 7-114043    | 5/1995  |

| JP | 07-261145 A | 10/1995 |

| JP | 61-243429 A | 10/1996 |

| JP | 09-9180 A   | 1/1997  |

| JP | 09-113879 A | 5/1997  |

| JP | 09-258163 A | 10/1997 |

| JP | 09-297564 A | 11/1997 |

| JP | 9-329806    | 12/1997 |

| JP | 10-62811 A  | 3/1998  |

| JP | 10-148848   | 6/1998  |

| JP | 11-119240   | 4/1999  |

| JP | 11-259016   | 9/1999  |

| JP | 11-326946   | 11/1999 |

\* cited by examiner

*Primary Examiner*—Bipin Shalwala

*Assistant Examiner*—Ricardo Osorio

(74) *Attorney, Agent, or Firm*—Sughrue Mion, PLLC

(57) **ABSTRACT**

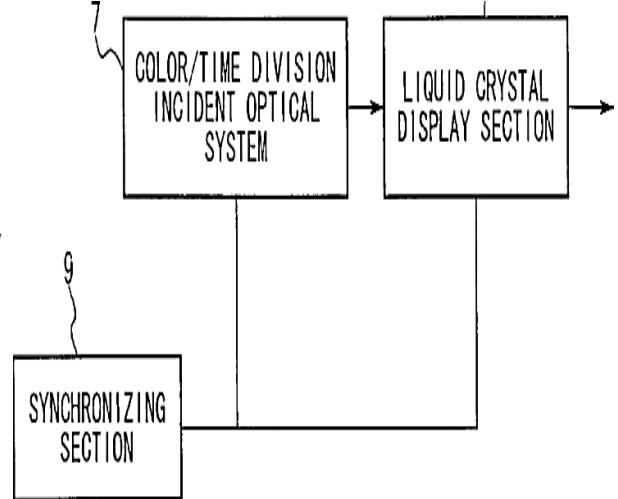

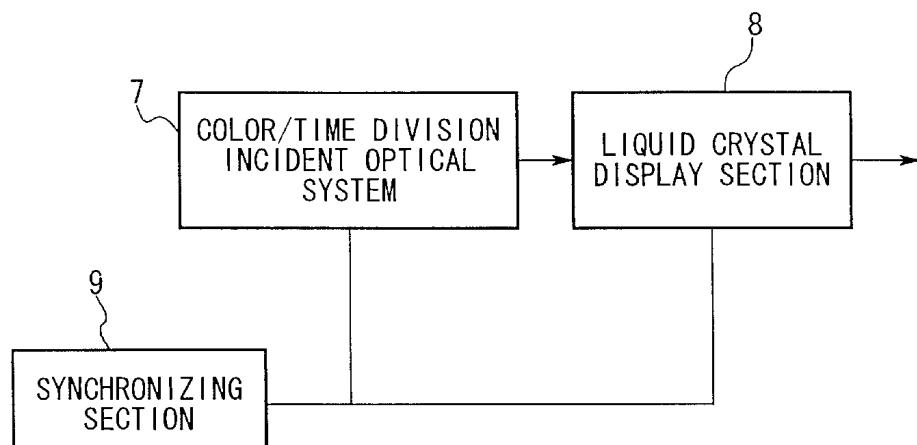

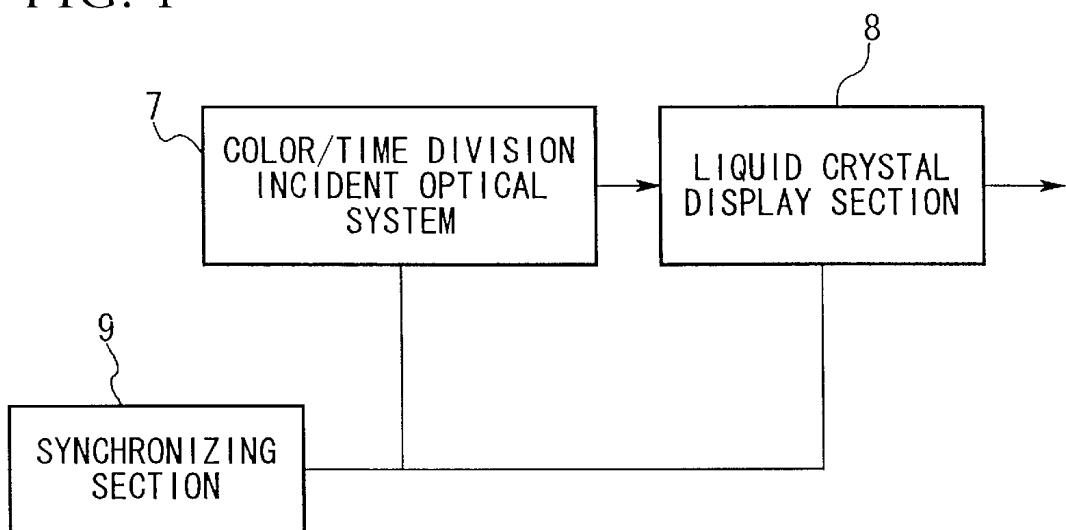

A liquid crystal display device of the invention has data drive circuits provided along both of two opposite sides of a rectangular display region, and gate drive circuits provided along the other two opposite sides. With the liquid crystal display section, the gate drive circuits are formed severally divided, and each data line group respectively extending from each of the data drive circuits is electrically separated respectively by the severally divided gate drive circuits. Moreover, the liquid crystal display section comprises a color/time division incident optical system arranged so as to sequentially shine light with different chromaticity onto the display region, and a synchronizing section for synchronizing the liquid crystal display section and the color/time division incident optical system under predetermined conditions.

**9 Claims, 58 Drawing Sheets**

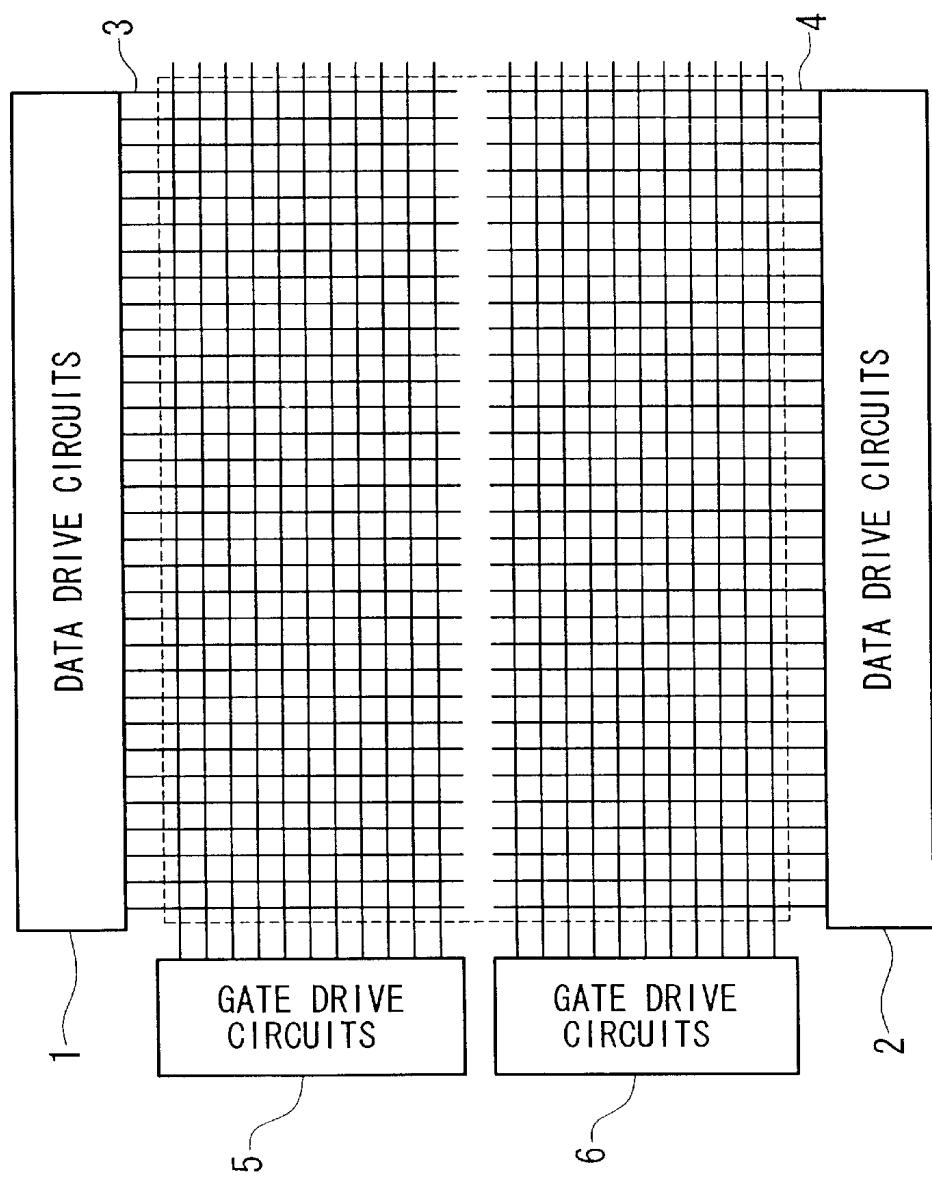

FIG. 1

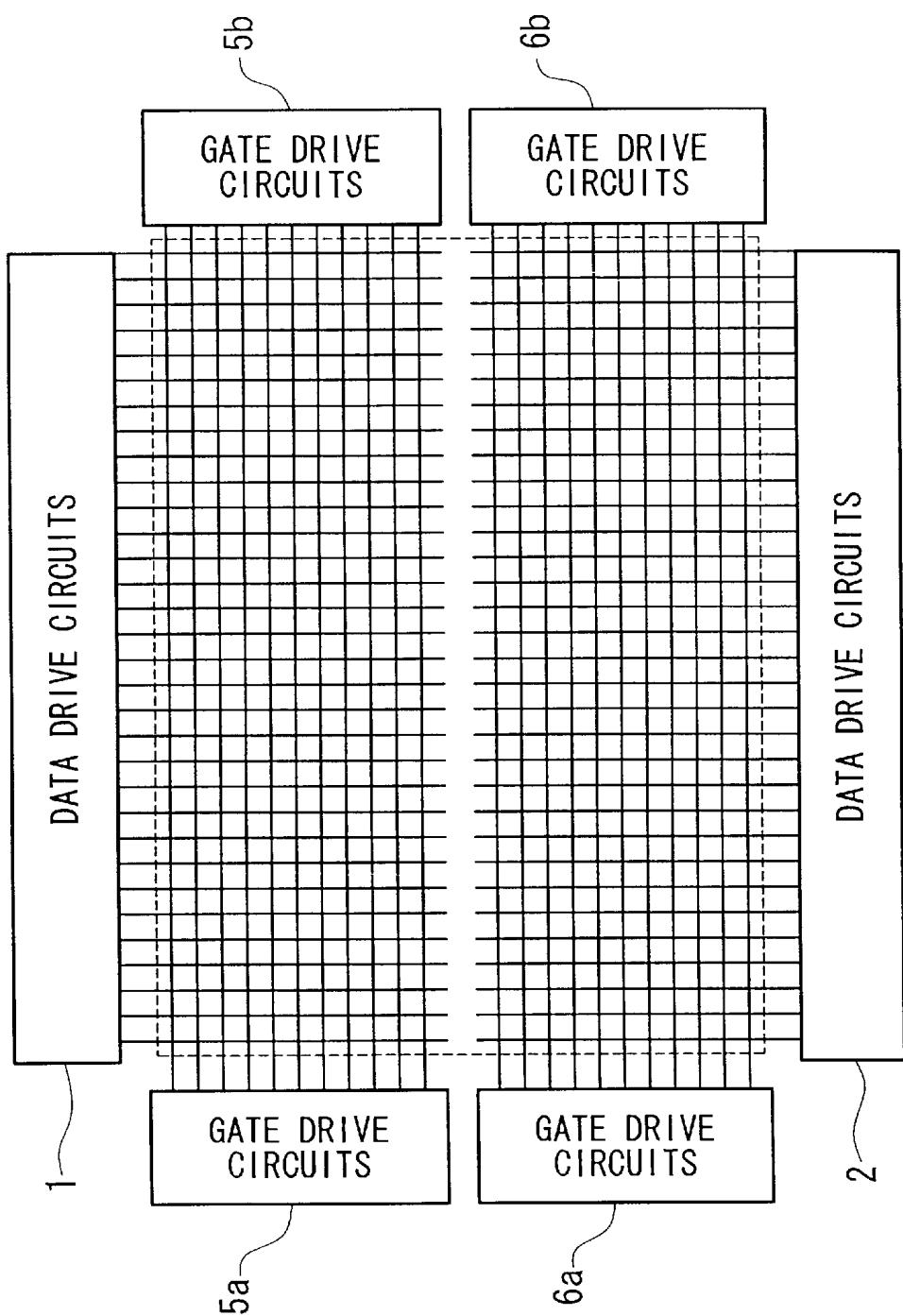

FIG. 2

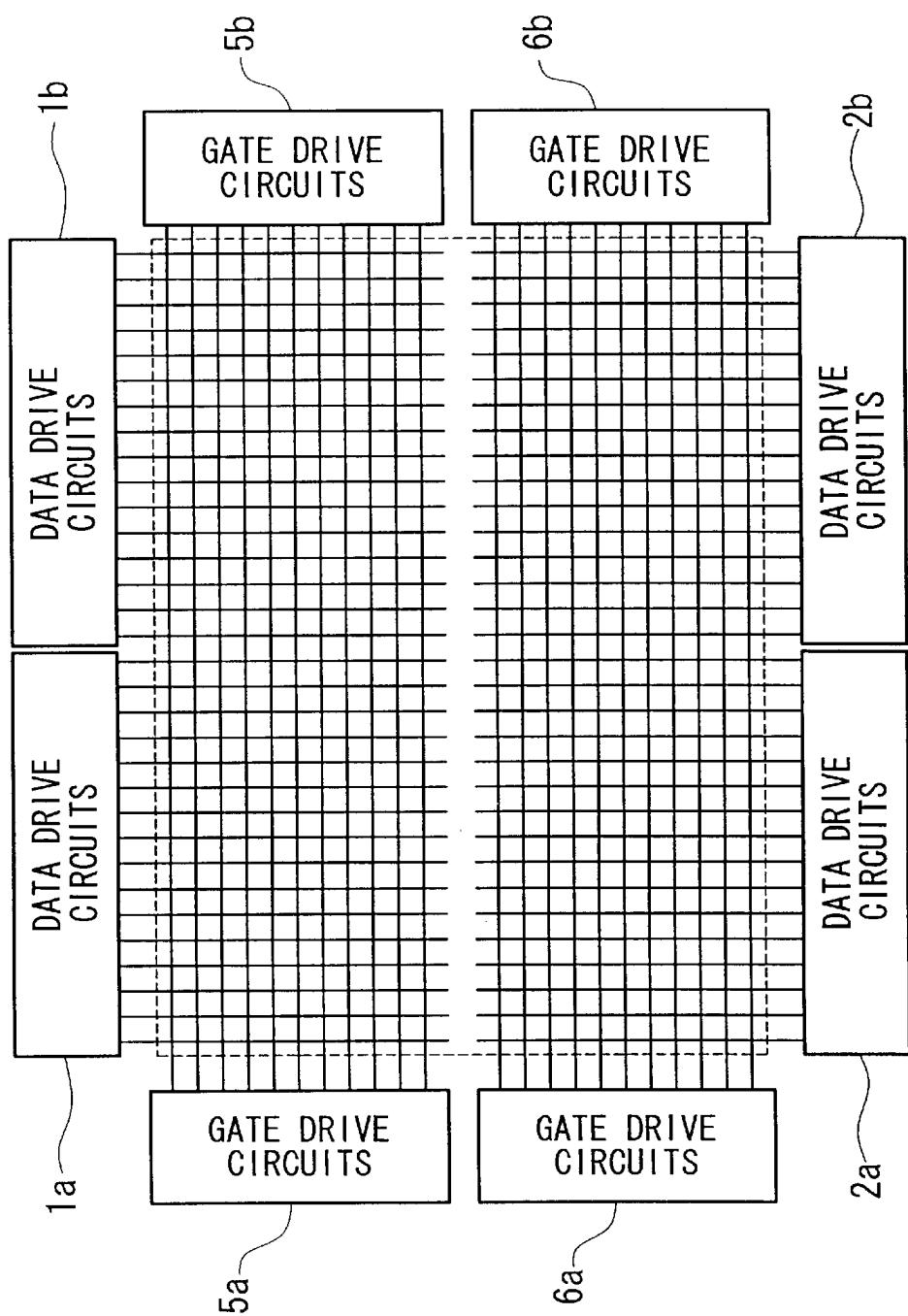

FIG. 3

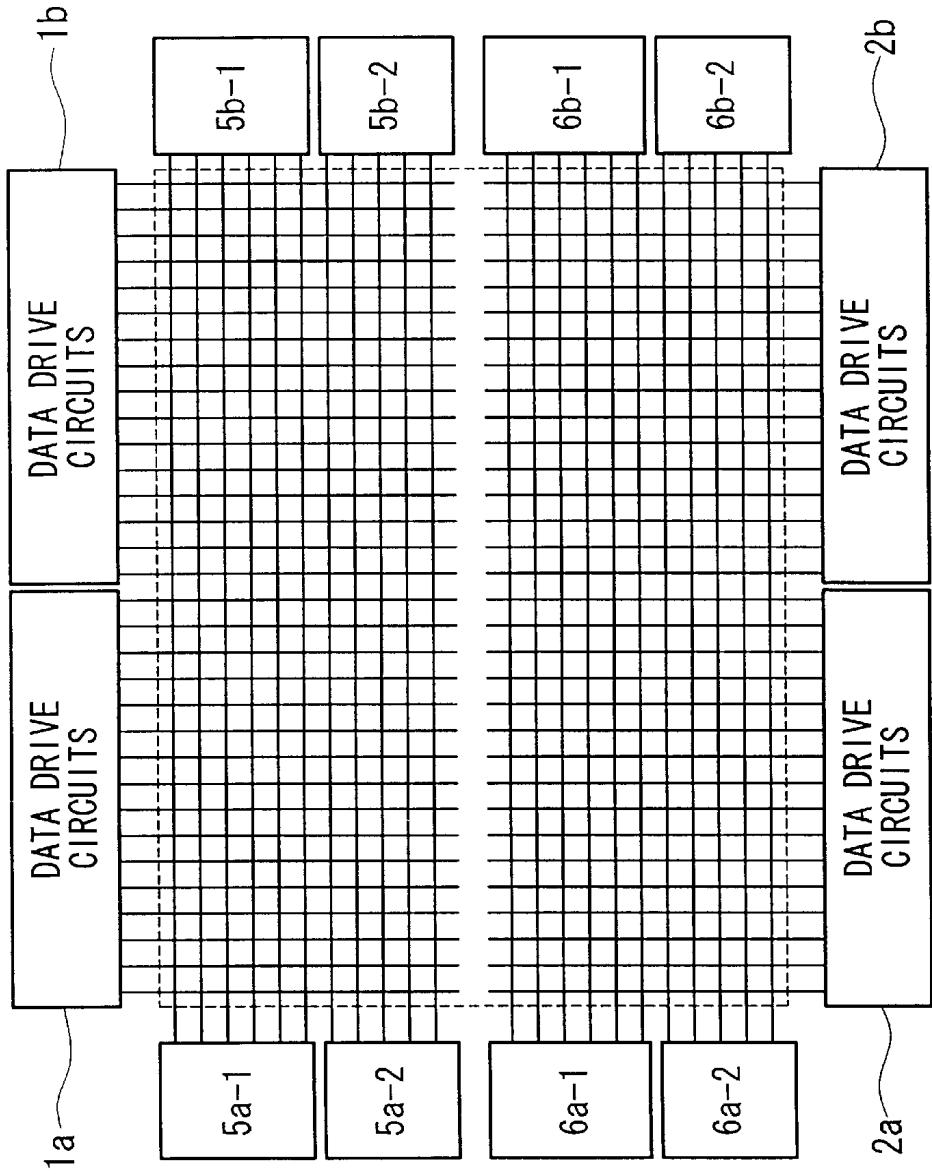

FIG. 4

FIG. 5

FIG. 6

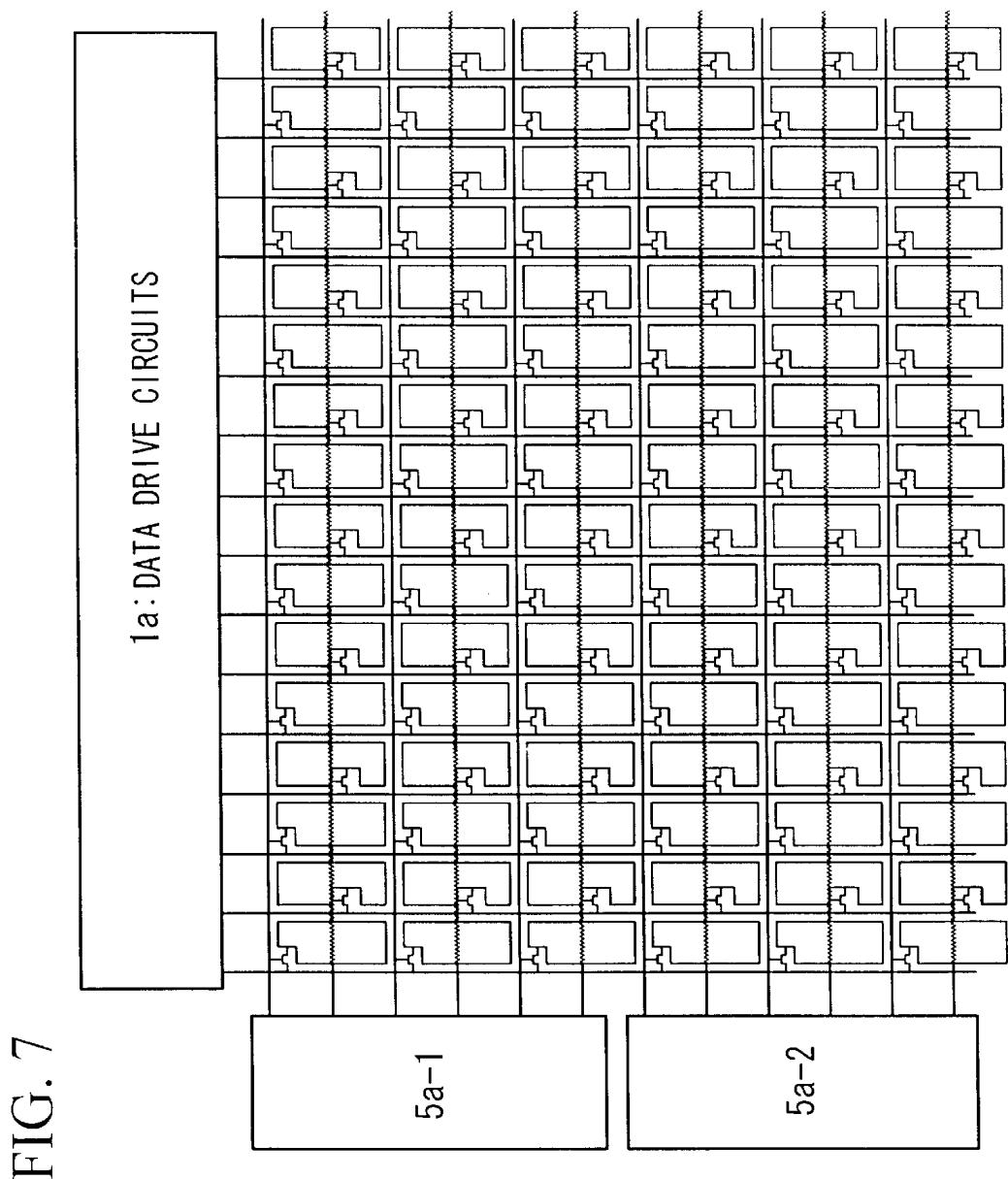

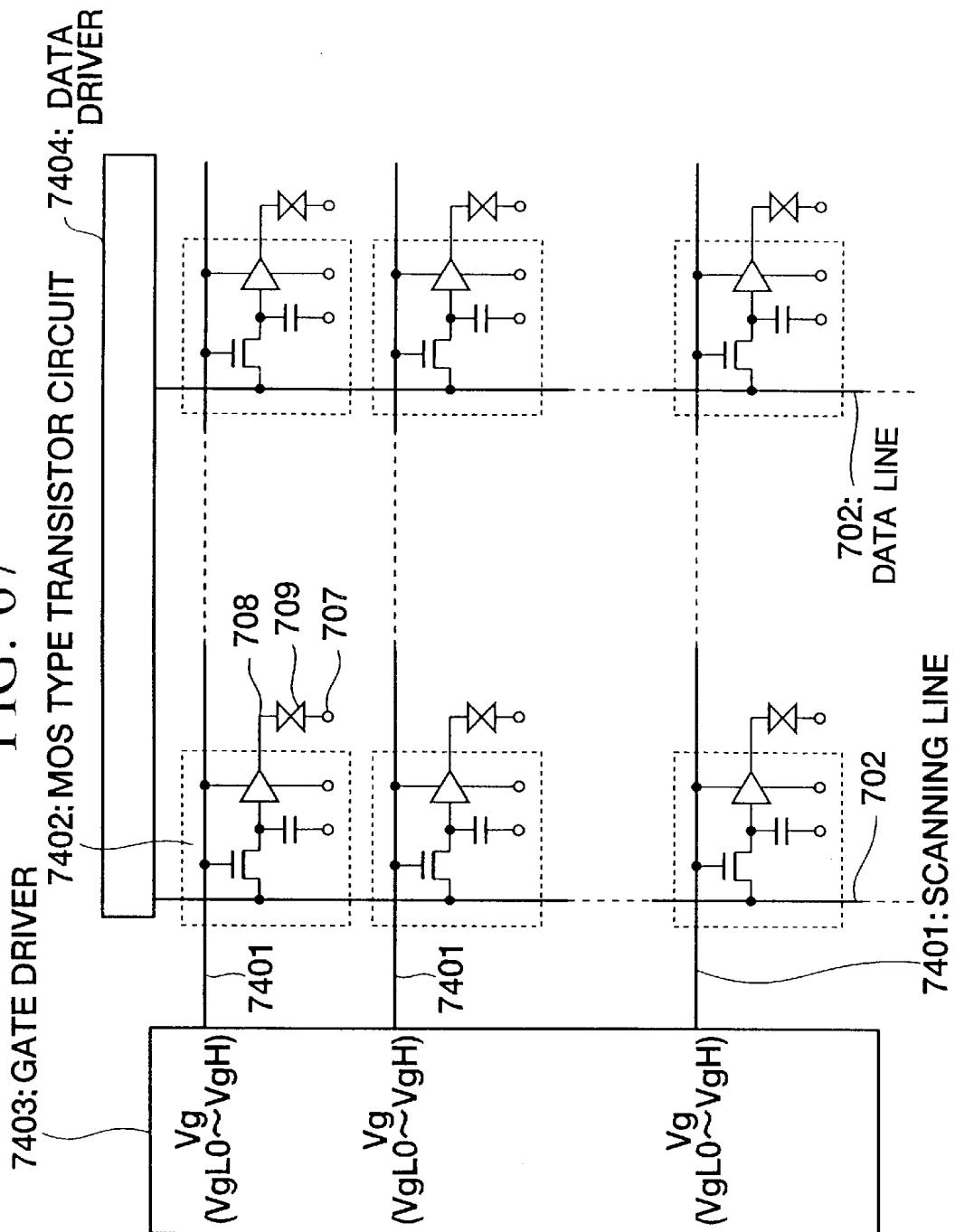

FIG. 7

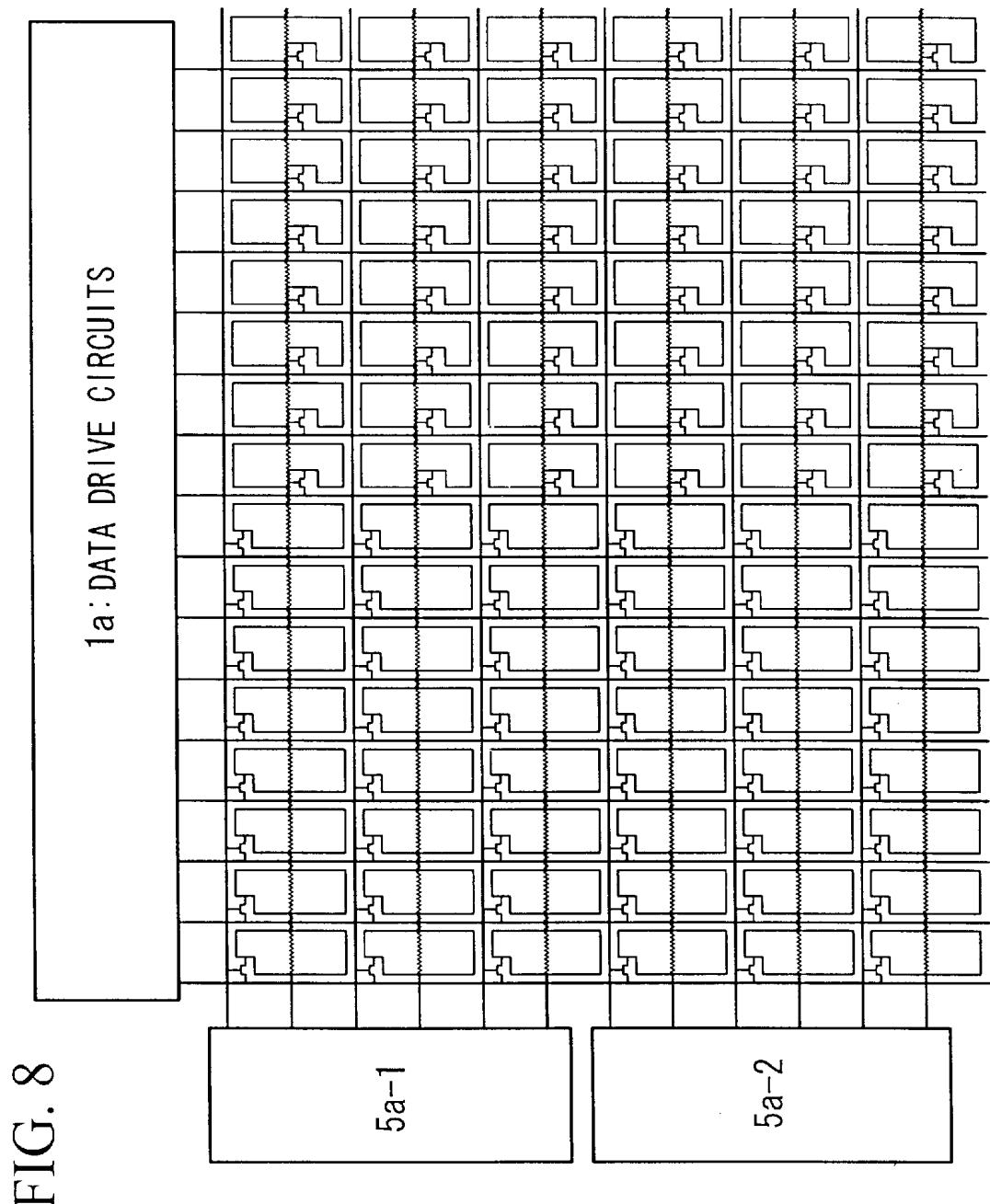

FIG. 8

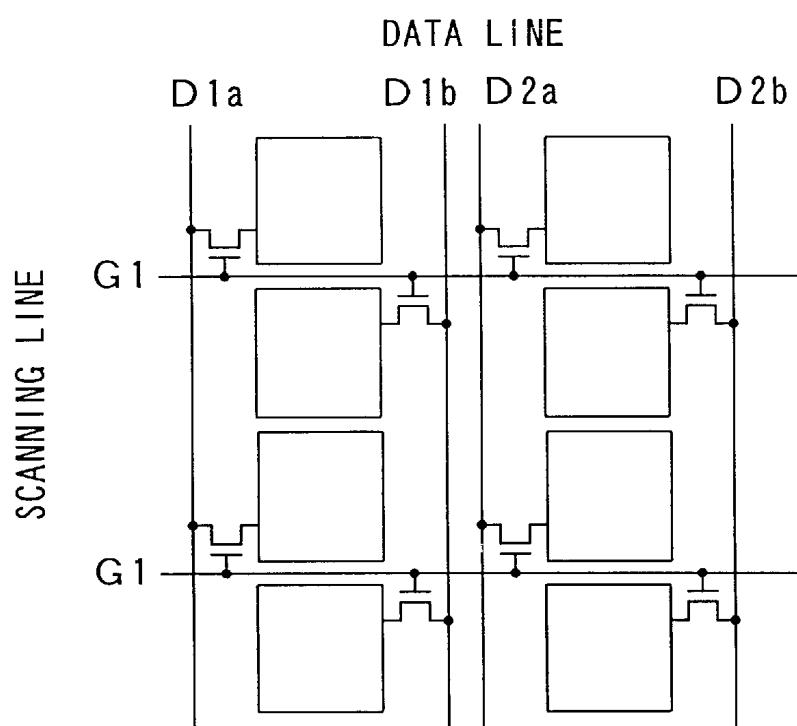

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 22

FIG. 23

FIG. 24 PRIOR ART

FIG. 25 PRIOR ART

FIG. 26 PRIOR ART

FIG. 27 PRIOR ART

FIG. 28 PRIOR ART

FIG. 29 PRIOR ART

FIG. 30 PRIOR ART

FIG. 31 PRIOR ART

FIG. 32 PRIOR ART

FIG. 33

FIG. 35

FIG. 36

FIG. 37

FIG. 38

FIG. 39

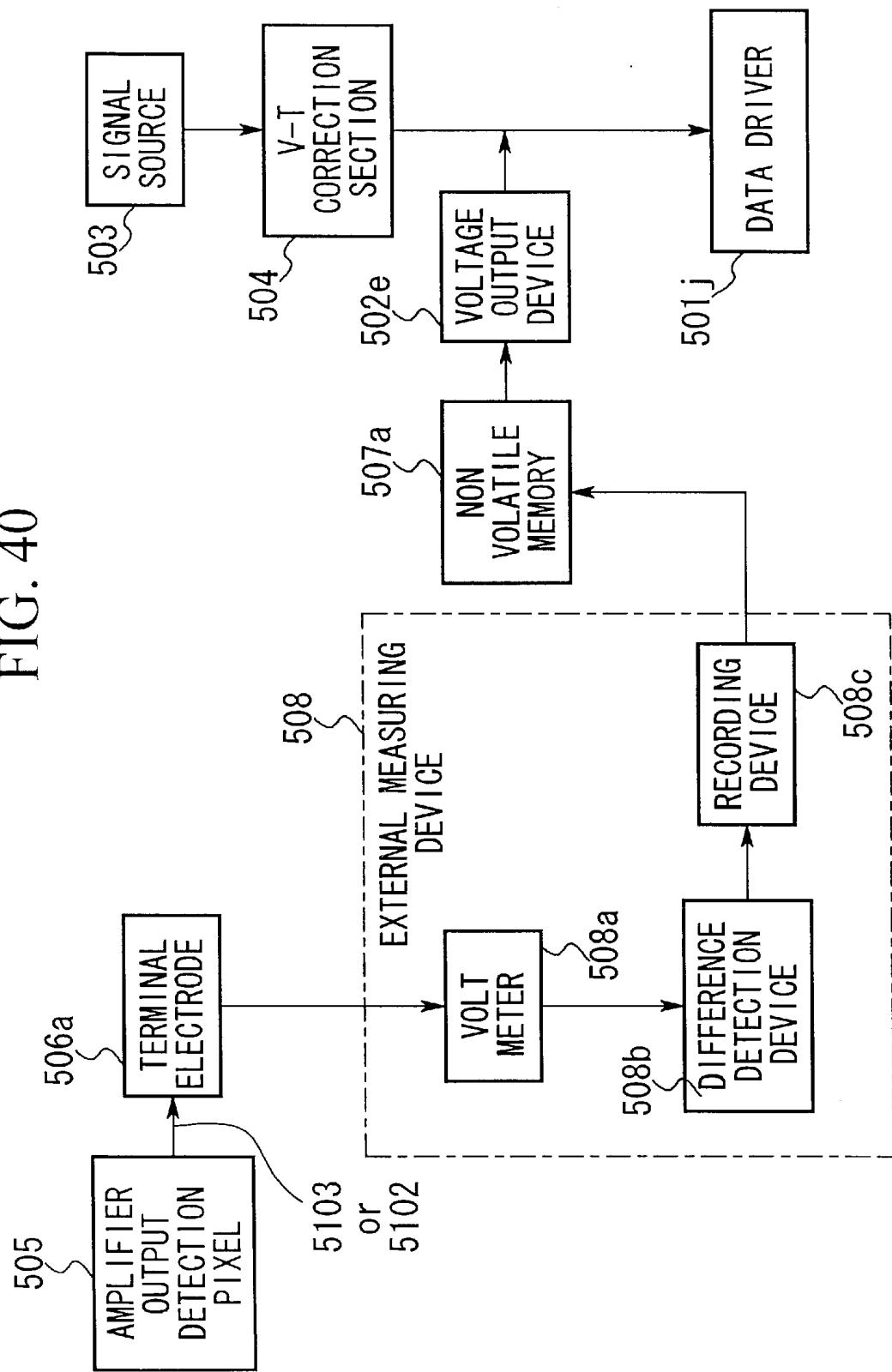

FIG. 40

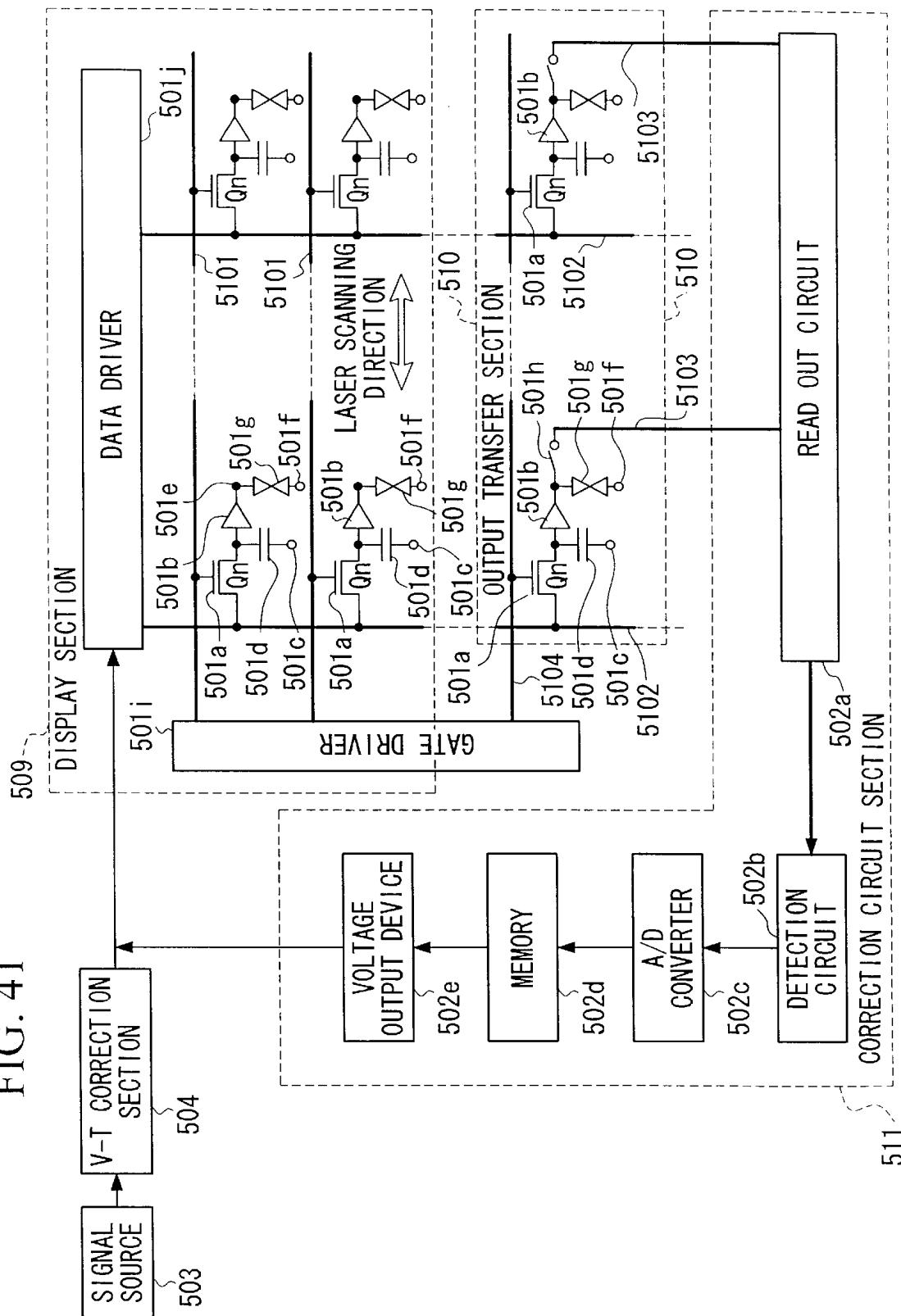

FIG. 41

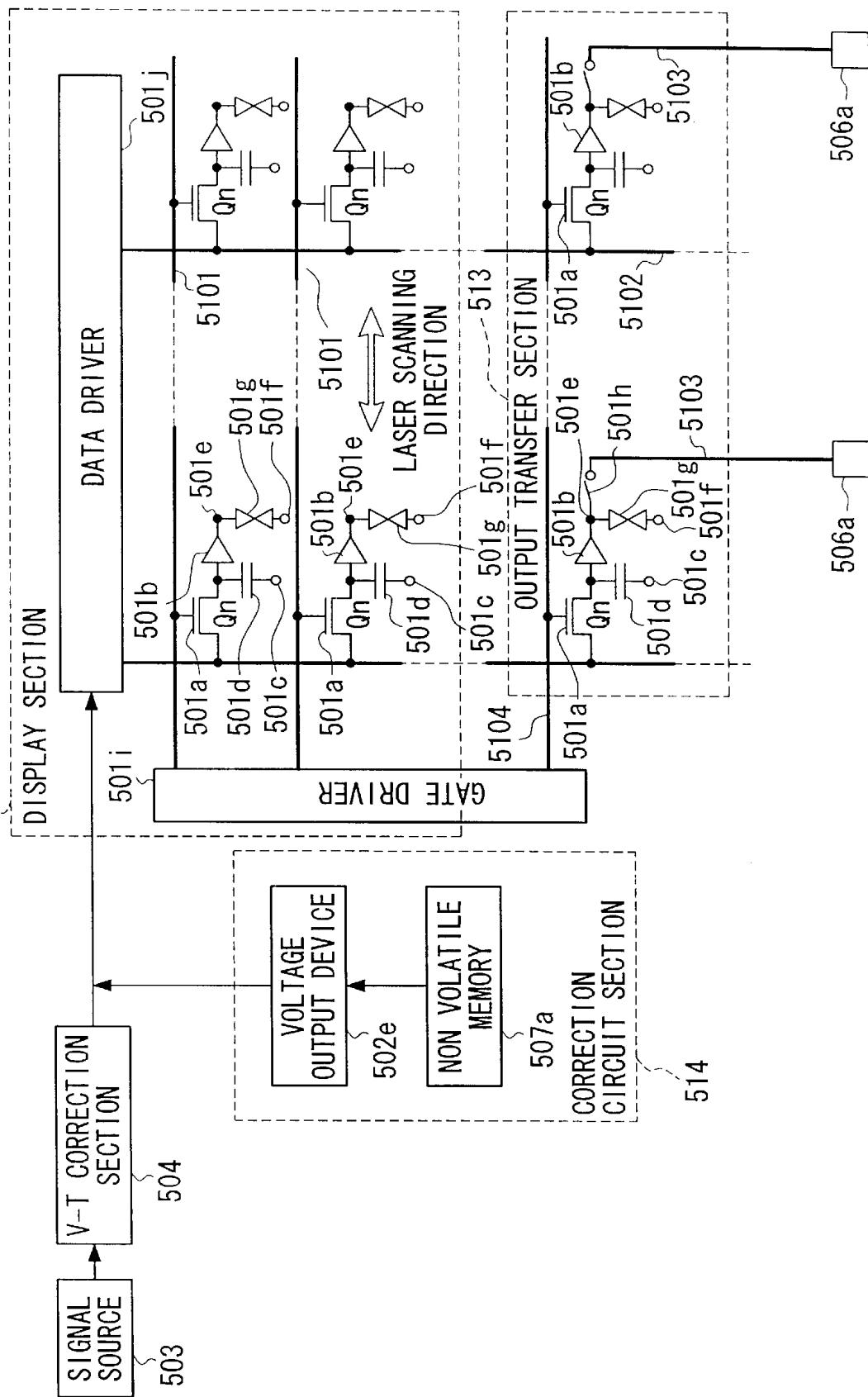

FIG. 42

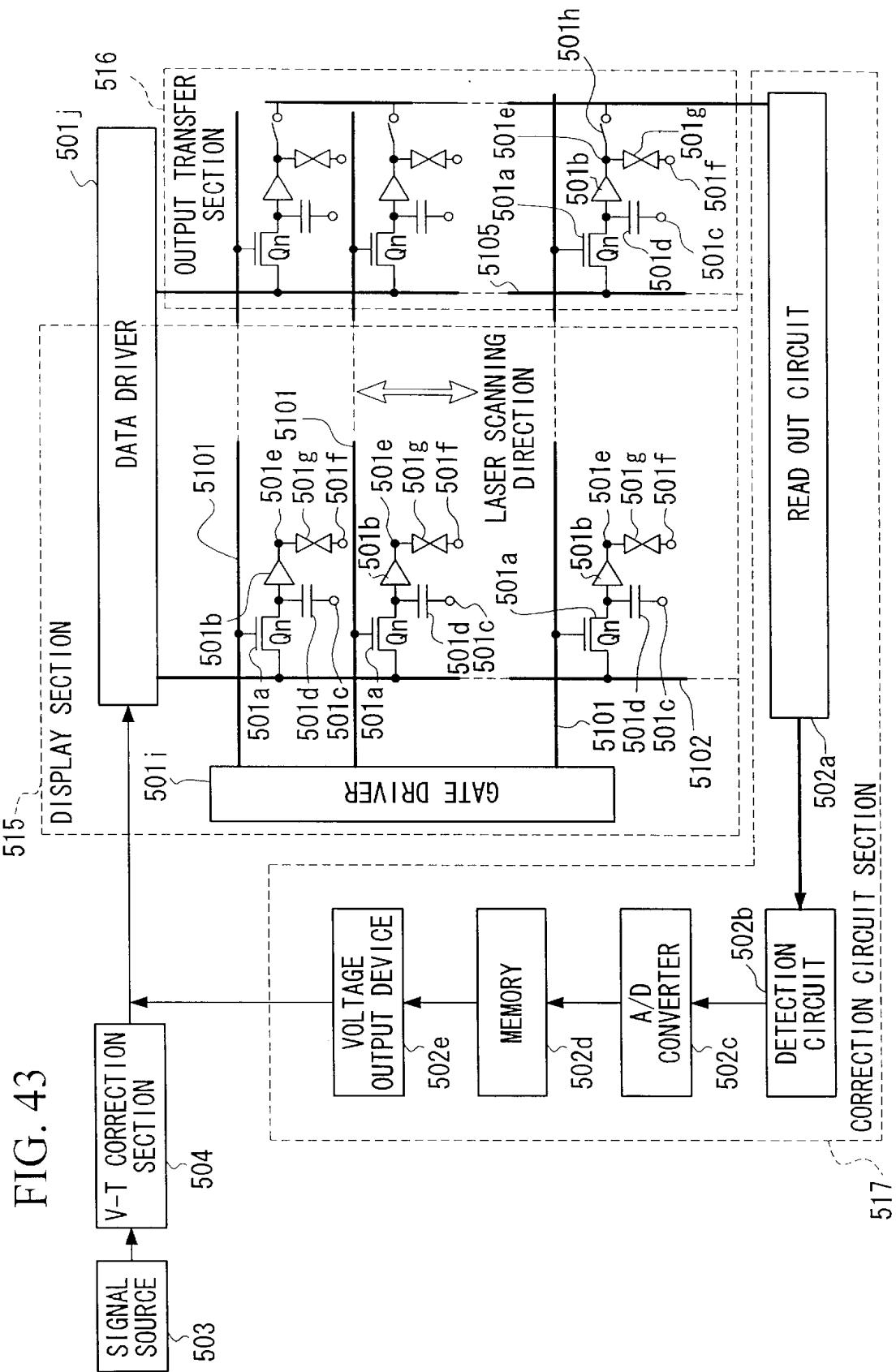

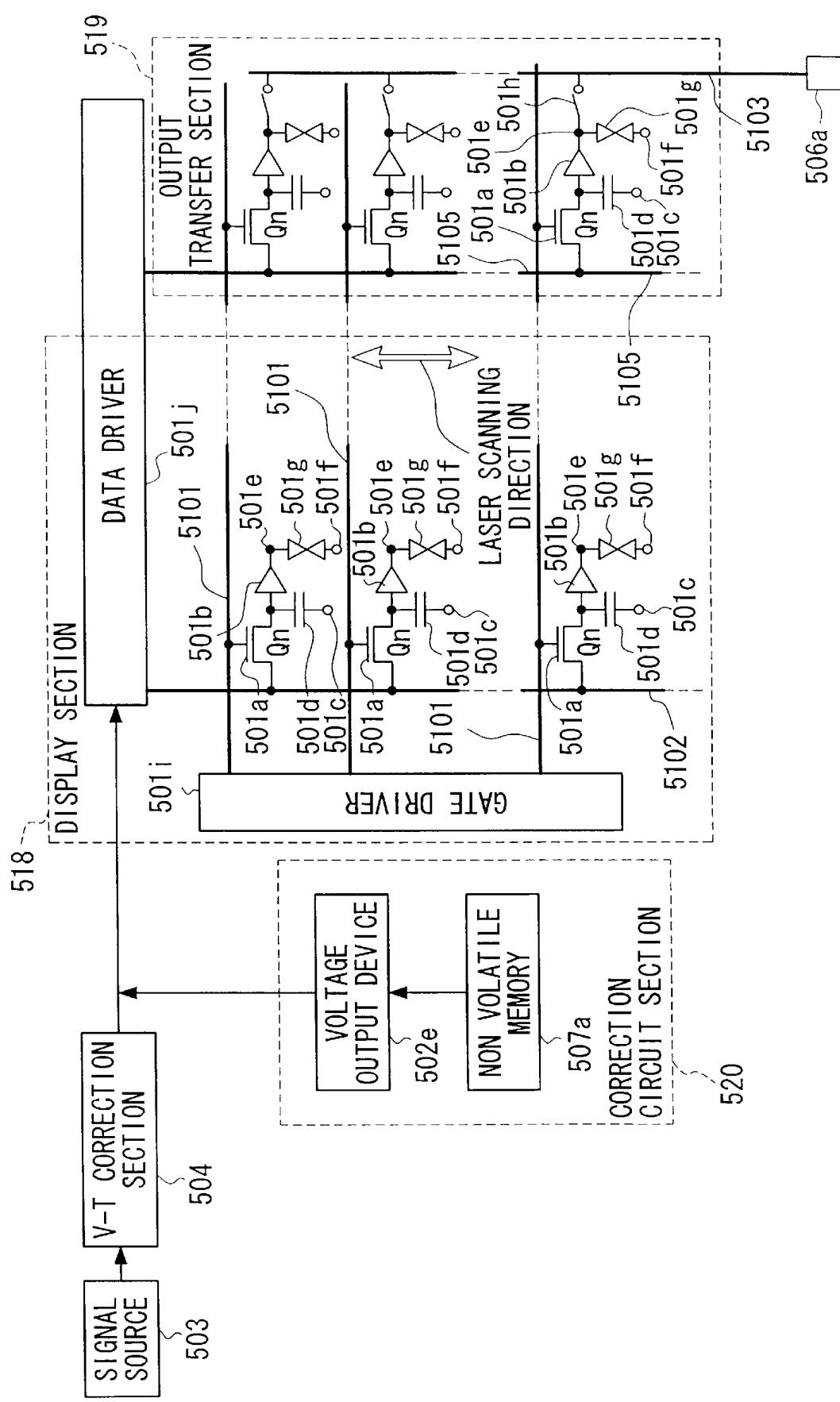

FIG. 44

FIG. 46

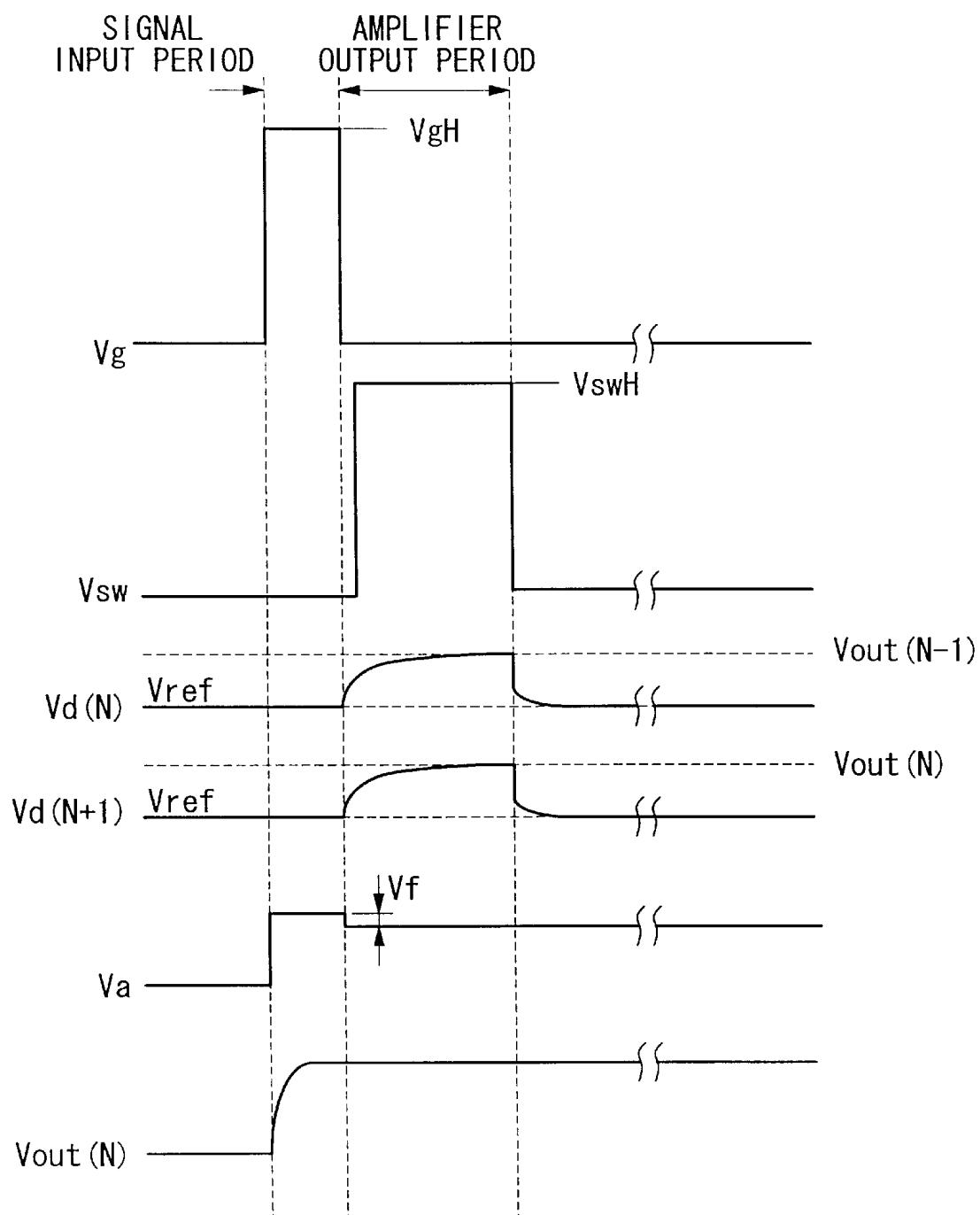

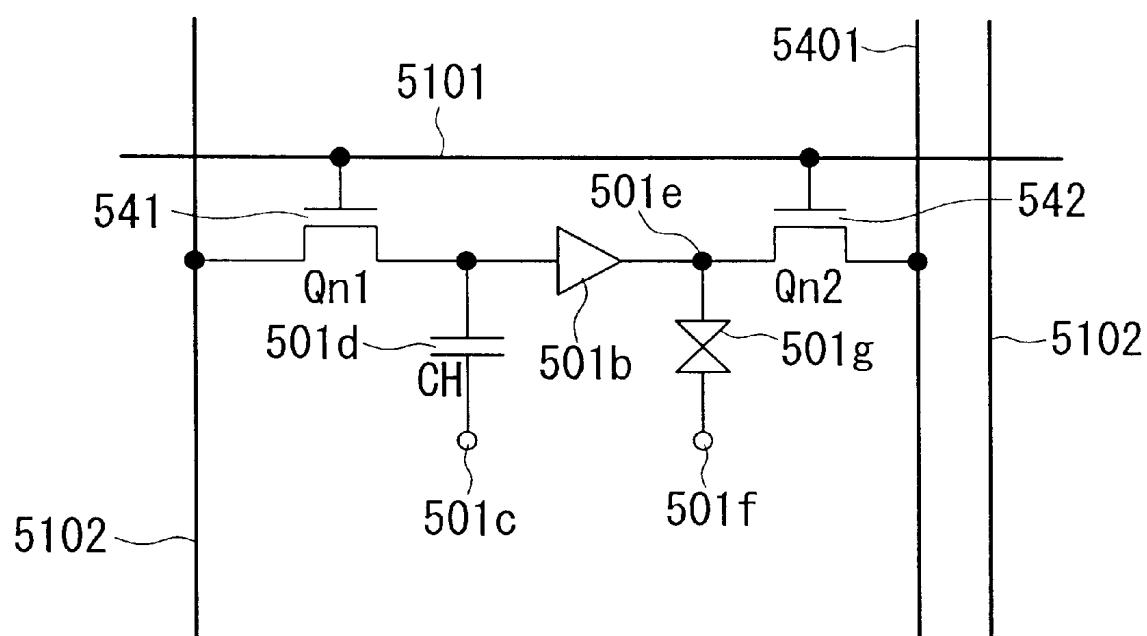

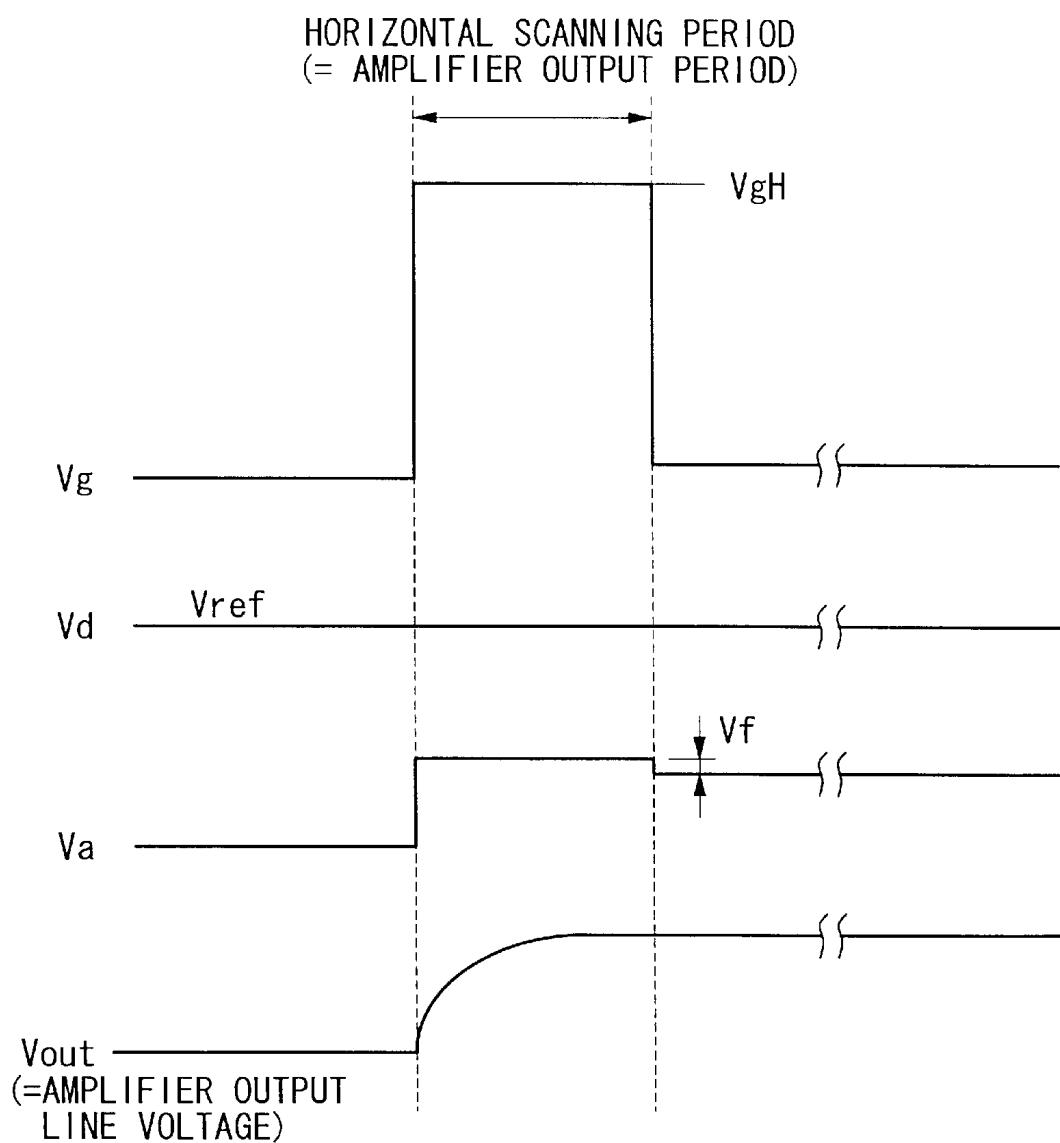

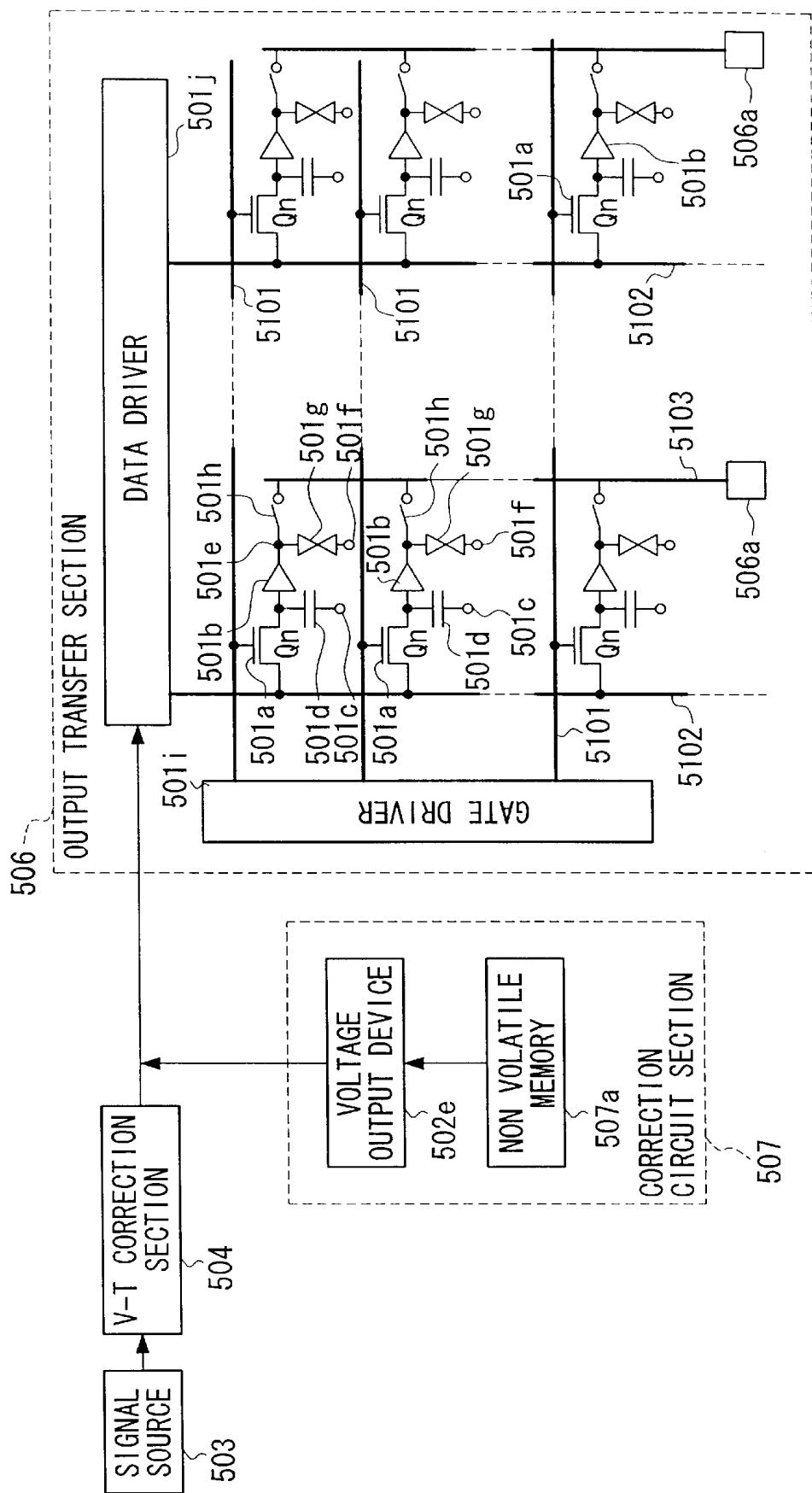

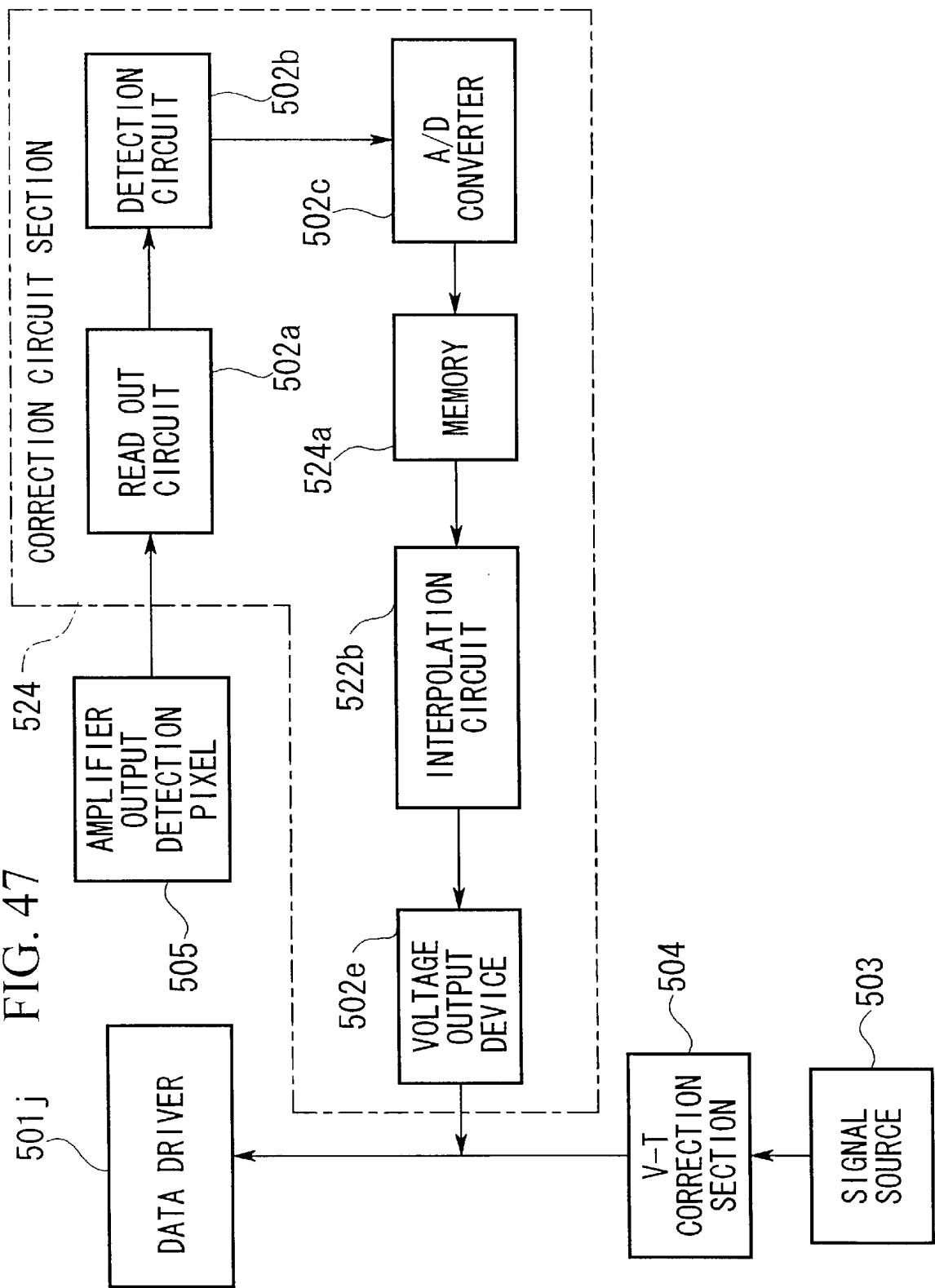

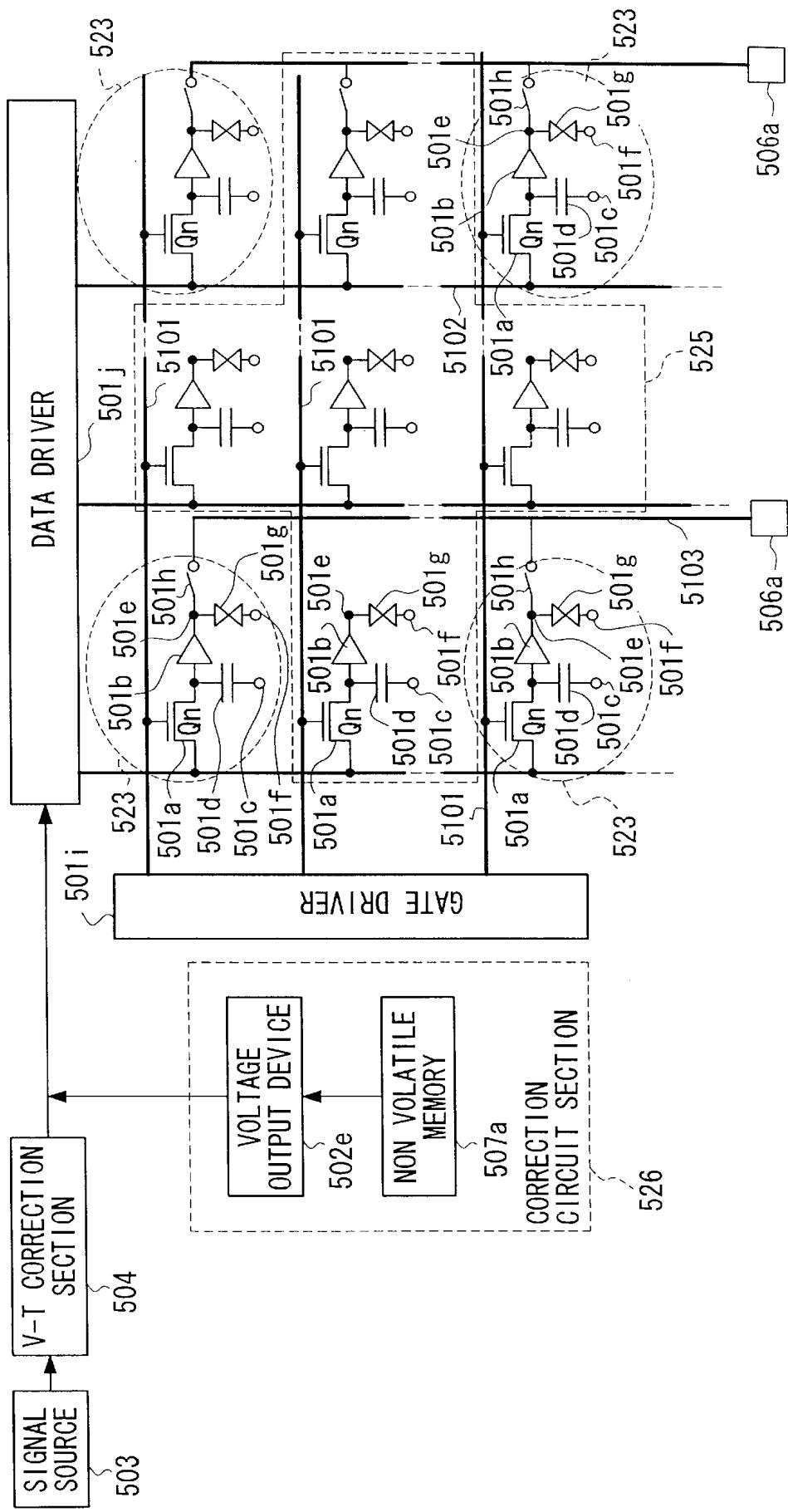

501 i FIG. 47

FIG. 48

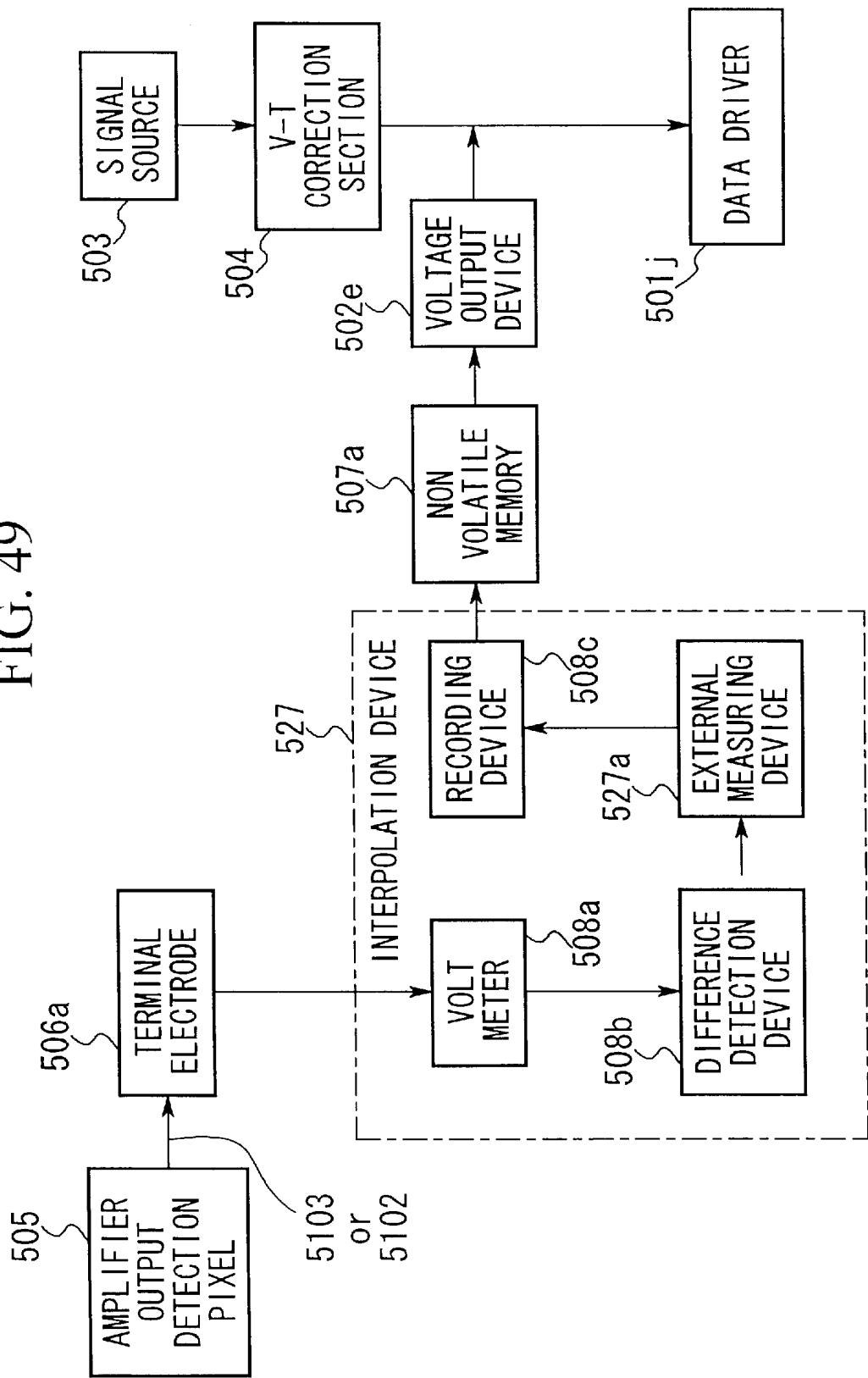

FIG. 49

FIG. 50

PRIOR ART

FIG. 51

PRIOR ART

FIG. 52 PRIOR ART

FIG. 53 PRIOR ART

FIG. 54

FIG. 55

FIG. 56

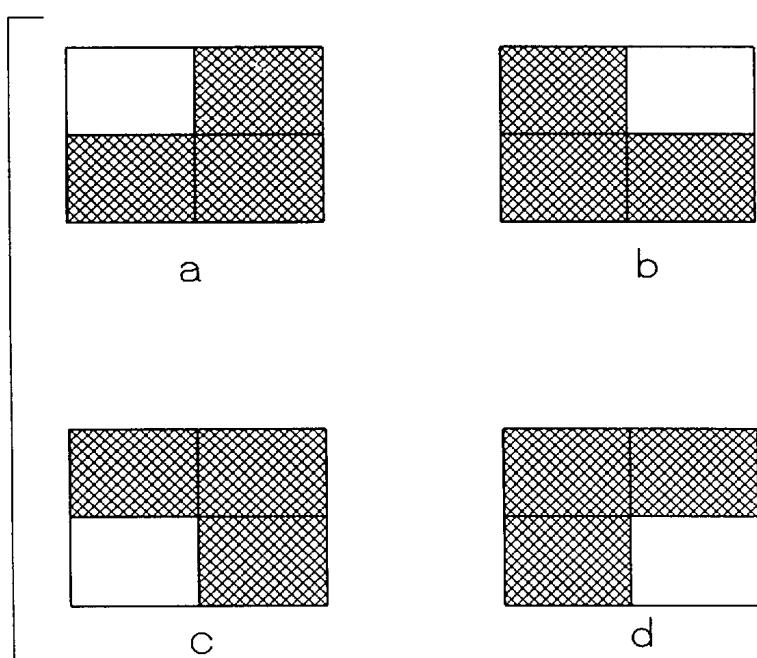

a

b

FIG. 57

FIG. 58

FIG. 59

FIG. 60

FIG. 61

FIG. 62

FIG. 63

FIG. 64

FIG. 65

FIG. 66

FIG. 67

FIG. 68

FIG. 69

FIG. 70

FIG. 71

FIG. 72

FIG. 73

FIG. 74 PRIOR ART

## LIQUID CRYSTAL DISPLAY DEVICE AND METHOD FOR DRIVING THE SAME

### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a liquid crystal display device and a method for driving the same, and in particular relates to a liquid crystal display device and a drive method, for increasing the performance of a display.

#### 2. Background Art

At present, practically all liquid crystal display elements are of the twisted nematic (TN) type display form. Liquid crystal display elements of this TN type display form use a nematic liquid crystal composition, and are largely divided into two.

One of these is an active matrix form where a switching element is provided for each pixel. For example, one (a TN-TFT form) is known which uses a thin film transistor (TFT: Thin Film Transistor) for a TN type display form. The other one is an STN (Super Twisted Nematic) form.

With this STN form, contrast and visual angle dependency are improved compared to the simple matrix form which uses the conventional TN type, but since the response speed is low, this is not suitable for moving picture display. Furthermore, this has the defect in that, compared to the active matrix form which uses the TFT, the display quality is low. This result means that at present, the TN-TFT form has become the market standard.

On the other hand, due to the requirement for further high image quality, research has started into methods of improving the angle of visibility, and practical use has been reached. As a result, with the main stream of current high performance liquid crystals displays, there are three types of TFT form active matrix liquid crystal display devices, namely a form which uses a compensating film in the TN mode, or an in plane switching (IPS) mode, or a multi domain vertical aligned (MVA) mode. With these active matrix liquid crystal display devices, normally, since the image signal involves positive and negative writing at 30 Hz, this is rewritten at 60 Hz, and the time for one field is approximately 16.7 ms (milliseconds) (the total time for both the positive and negative fields is referred to as one frame, and is approximately 33.3 ms). On the other hand, the response speed of current liquid crystals, even in the fastest state, is only about this frame time. Therefore, in the case where a projection signal comprising a moving picture is displayed, or in the case where a high-speed computer image is displayed, or in the case where a high-speed game image is displayed, a response speed higher than the current frame time is required.

On the other hand, in order to target even higher resolution, a field sequential (time sharing) color liquid crystal display where a back light serving as the illumination light for the liquid crystal display, switches time-wise between red green and blue, is also being investigated. With this form, since it is not necessary to arrange color filters spatially, high resolution three times higher than heretofore is possible. With the field sequential liquid crystal display, since it is necessary to display one color in one third of the time for one field, then the time which can be used for the display is approximately 5 ms. Consequently, for the liquid crystal itself, a response faster than 5 ms is required. As a liquid crystal which can realize this high-speed response, liquid crystals having spontaneous polarization such as

ferroelectric liquid crystals or antiferroelectric liquid crystal are being studied. Furthermore, with the nematic liquid crystals also, studies are being conducted for example to increase the dielectric anisotropy, to reduce the viscosity, to make the film thinner, and to change the liquid crystal molecular orientation to a  $\pi$  type orientation, or to increase speed by devising drive voltage wave forms.

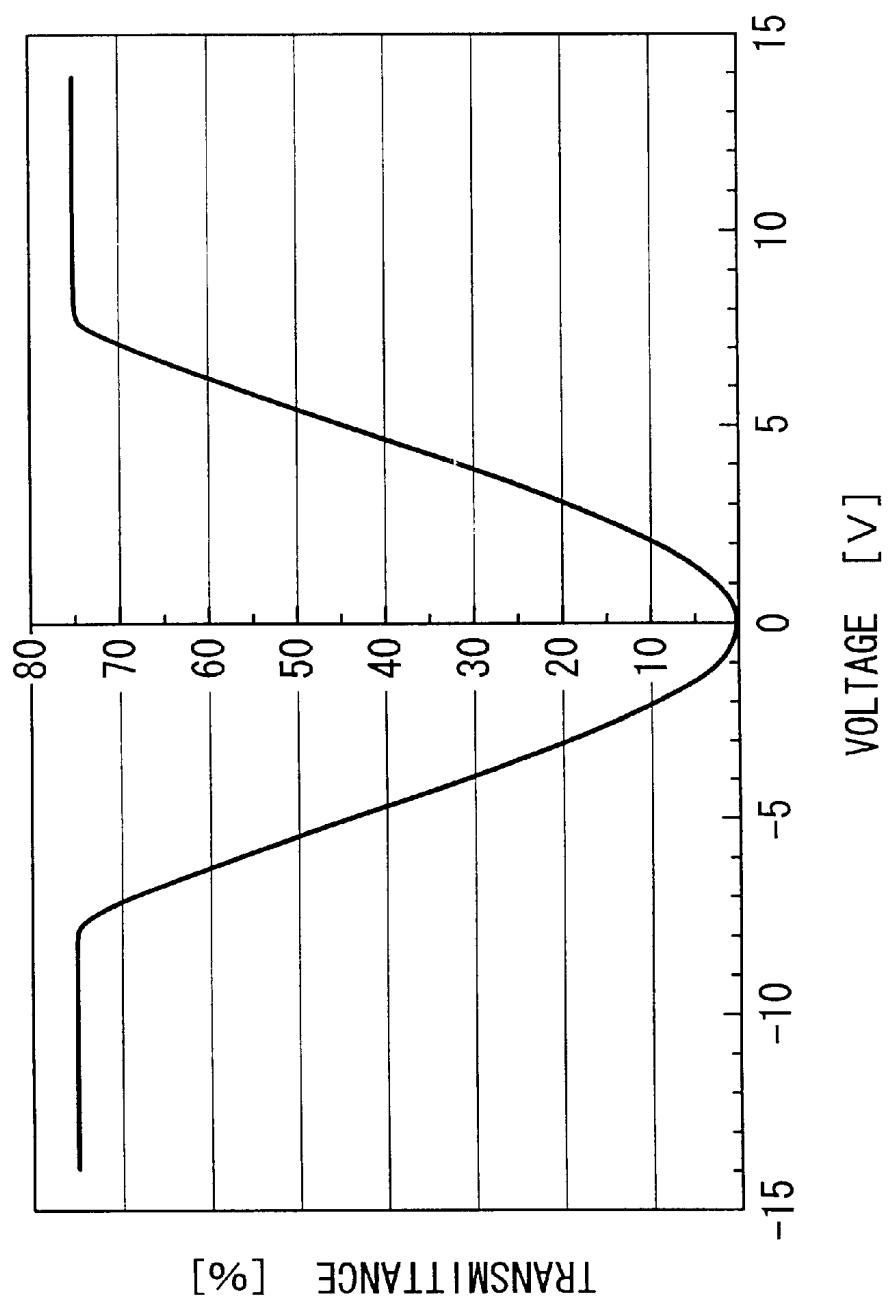

Here, with an active matrix liquid crystal display element, the time where voltage or electric charge is actually written to the liquid crystal, is only the selection time (writing time) of each scanning line. This time, in the case of having 1000 lines with writing normally in one field time is 16.7  $\mu$ s (microseconds), and in particular in the case where field sequential drive is performed, is approximately 5  $\mu$ s. At present, a liquid crystal or a liquid crystal operation mode which completes the response within this time, is practically non-existent. Even with a liquid crystal having the above-mentioned spontaneous polarization, or a high-speed nematic liquid crystal, an element which can give this fast response is not known. As a result, the liquid crystal responds after completion of writing of the signal, causing the following problems. At first, with a liquid crystal having spontaneous polarization, a depolarization field is produced due to the rotation of the spontaneous polarization, so that the voltage at both ends of the liquid crystal layer suddenly drops. Therefore, the voltage which has been written to both ends of the liquid crystal changes markedly. On the other hand, also with the high-speed nematic liquid crystal, due to the anisotropy of the dielectric constant, the change in the capacity of the liquid crystal layer becomes very large. Hence a change occurs in the holding voltage for holding the writing in the liquid crystal layer. Such a drop in the holding voltage, that is to say a drop in the effective applied voltage, lowers the contrast due to insufficient write in. Furthermore, in the case where the same signal is written in repeatedly, luminance continues to change until the holding voltage ceases to drop. Hence in order to obtain stabilized luminance, several frames are required.

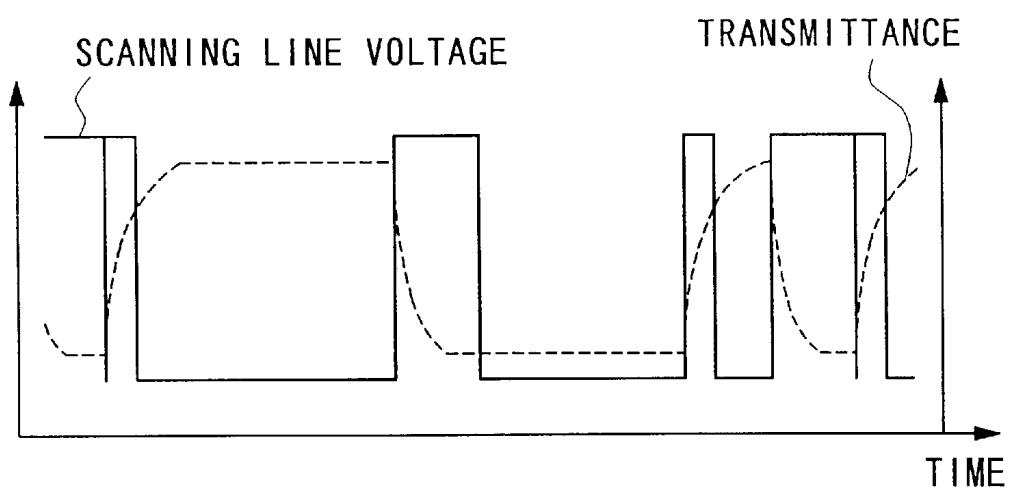

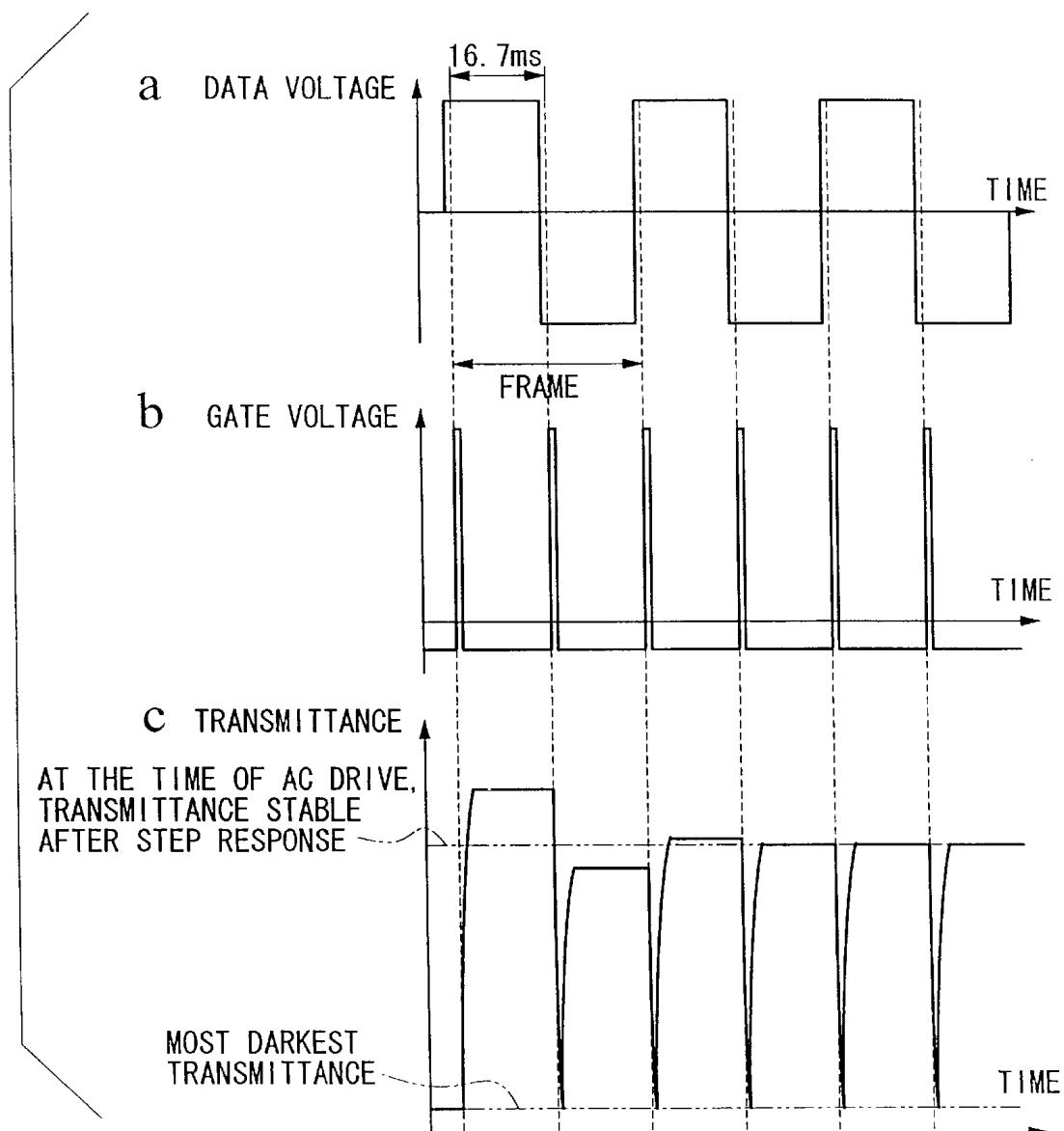

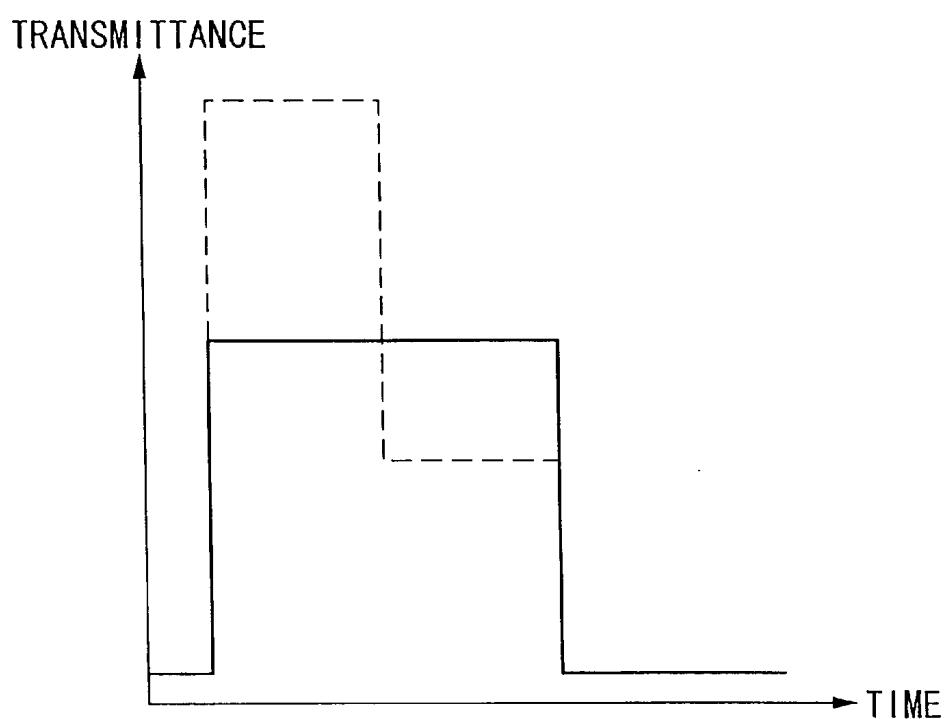

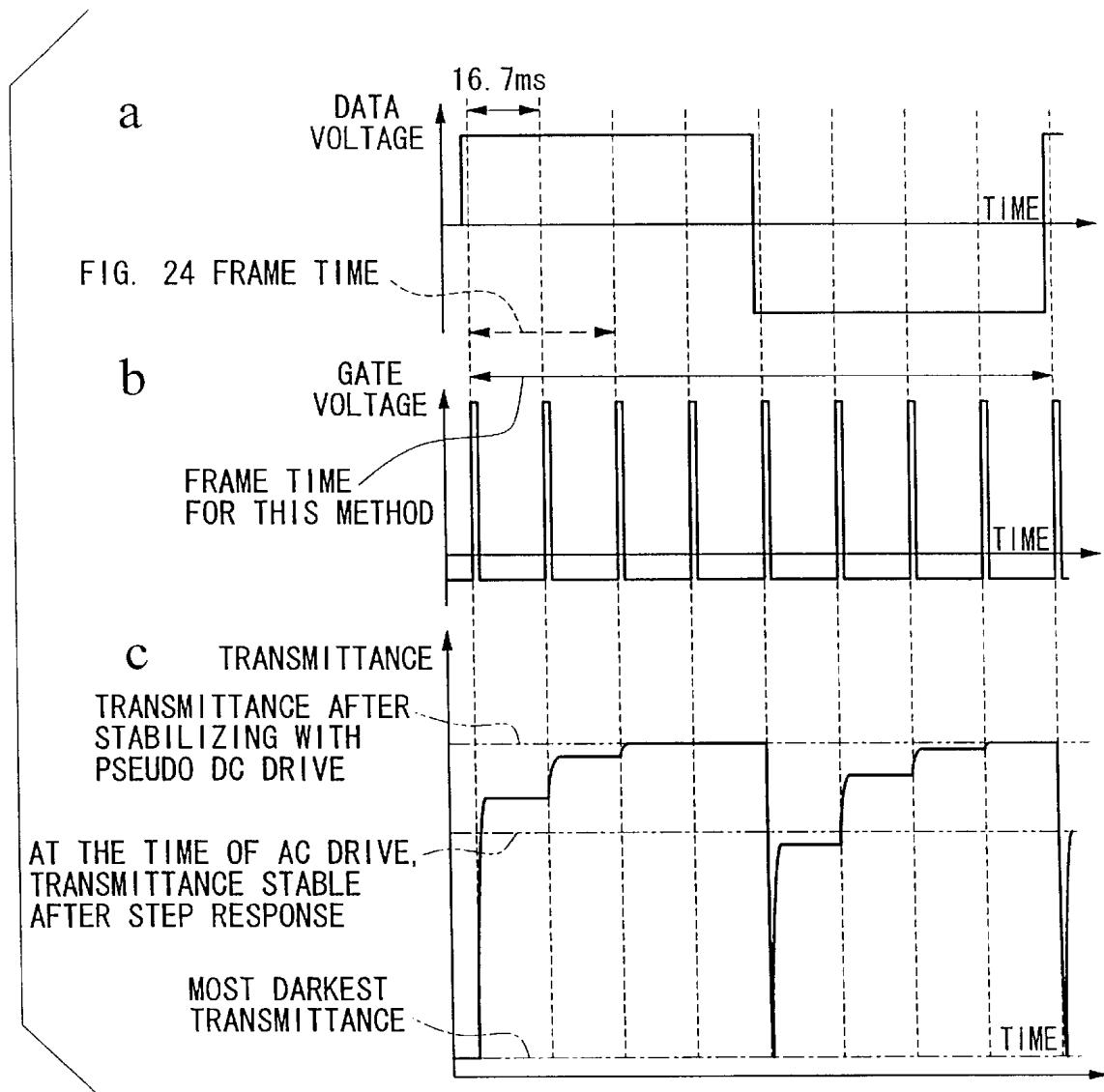

Furthermore, as shown in Japanese Applied Physics, chapter 36, part 1, number 2, pages 720 to 729, in the case where the same image signal continues to be written across several frames from the frame where there has been a change in the absolute value of the signal voltage for which the image signal has changed, a phenomena called a "step response" appears. This phenomena is a phenomena where the transmittance across several frames oscillates between light and dark with respect to the signal voltage of the AC drive at the same amplitude. Subsequently, this stabilizes to a constant transmitted light quantity. An example of this phenomena is shown by the schema in FIG. 24. Part (a) shown in FIG. 24 is a wave form diagram for data voltage, part (b) shown in FIG. 24 is a wave form diagram for gate voltage, and part (c) shown in FIG. 24 is a wave form diagram for transmittance at the time. At the time of AC drive, transmittance is stable after a step response. The transmittance when stabilized is shown by a two dot chain line, and the transmittance at the time of maximum darkness is shown by a single dot chain line.

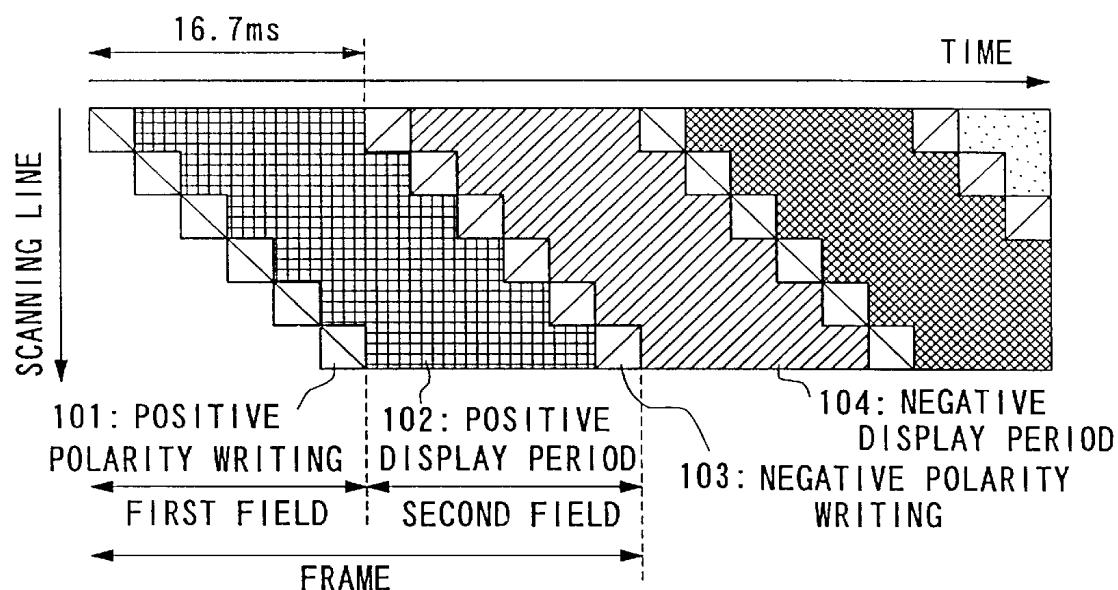

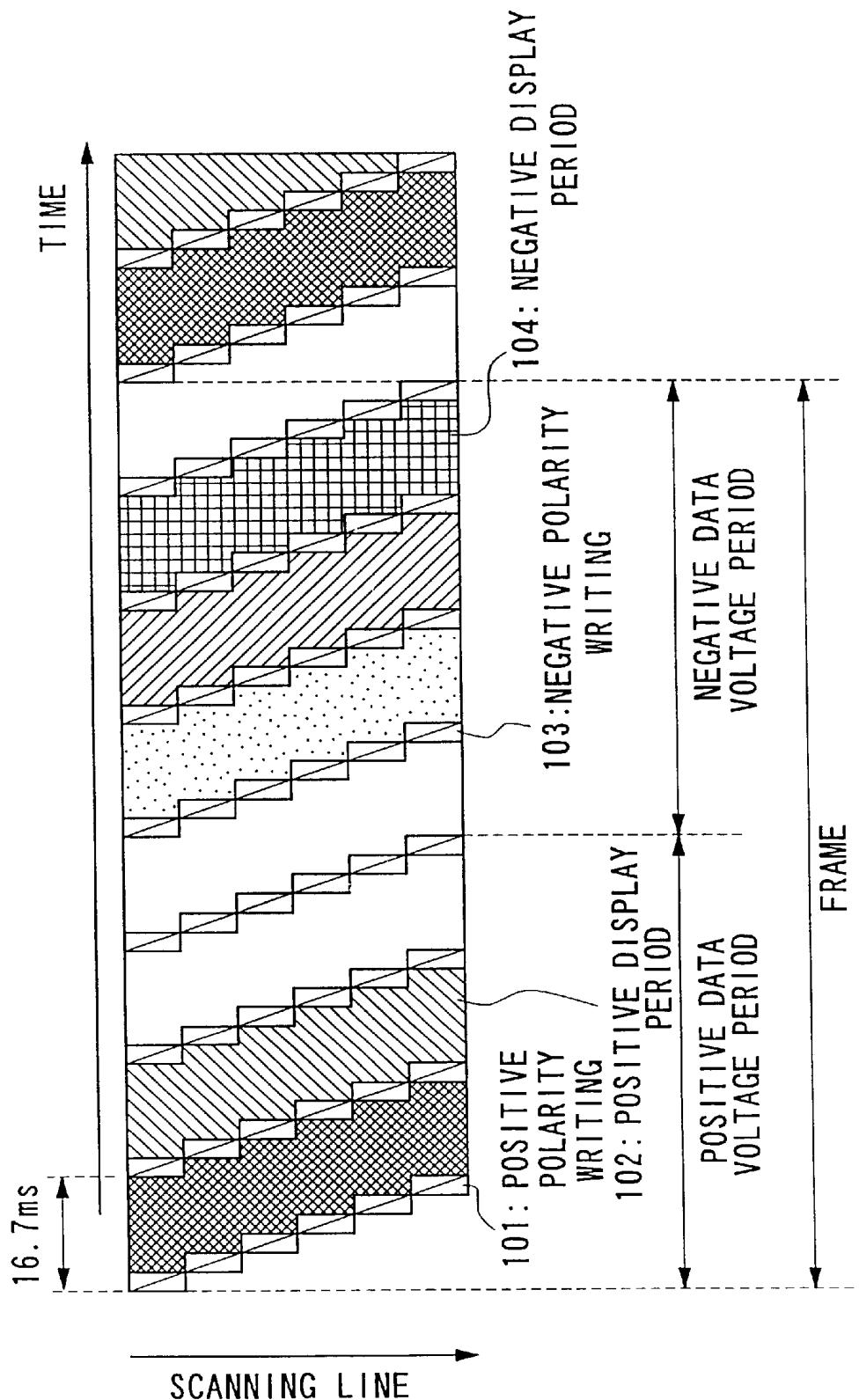

Furthermore, FIG. 25 is a timing chart for each scanning line, under drive of FIG. 24, schematically showing the luminance for the light and dark of a positive display period 102 and a negative display period 104, based on the transmittance of part (c) shown in FIG. 24. Moreover, in the figure, a time of 16.7  $\mu$ s being the time for one field, is shown by the arrow. In this figure, six scanning lines are assumed. From the top scanning line in sequence, positive polarity writing 101 is performed, and after obtaining the

positive display 102, then again from the top scanning line in sequence, negative polarity writing 103 is performed to obtain the negative display 104. For each scanning line, the field where the period of the positive polarity writing 101 and the positive display 102 are added, is the first field, and the field where the period of the negative polarity writing 103 and the negative display 104 are added for each scanning line, is the second field, and the total of the two fields becomes one frame. Therefore, when the data voltage of part (a) shown in FIG. 24 is applied and the TFT switch comes on with the gate voltage of part (b) shown in FIG. 24, then as in part (c) shown in FIG. 24, the transmittance oscillates between light and dark for each field. Such oscillation of the transmittance is observed as a flicker, causing deterioration in the quality of the display. Furthermore, in these figures, at two frames (four fields) after signal voltage application, the transmittance drops to a constant transmittance. As a result, the luminance change also oscillates as in FIG. 25. In this way, even if a high-speed response liquid crystal is used, since several frames are required for an actual stable luminance, the rapidity for the display image is lost.

On the other hand, with the active matrix drive, the transmittance after liquid crystal response is determined not by the applied signal voltage, but rather by the electric charge amount stored by the liquid crystal capacitance after liquid crystal response. This is because with the active drive, there is a fixed charge drive for responding to the liquid crystal due to the held charge. The charge amount supplied from the active element, ignoring slight leaks etc., is determined by the accumulation charge before predetermined signal writing, and a writing charge which is newly written. Furthermore, the accumulation charge after the liquid crystal responds also changes with pixel design values for the liquid crystal property constant, the electrical parameters, the accumulation capacity and the like. Therefore, to obtain a correspondence between the signal voltage and the transmittance, there is required for example (1) correspondence of the signal voltage to the writing charge, (2) accumulation charge prior to writing, (3) information for performing calculation of the accumulation charge after response, and actual calculation. As a result, a frame memory for storing (2) over the whole screen or a calculation part for (1) or (3) is necessary. This invites an increase in the number of parts for the system, and is thus undesirable.

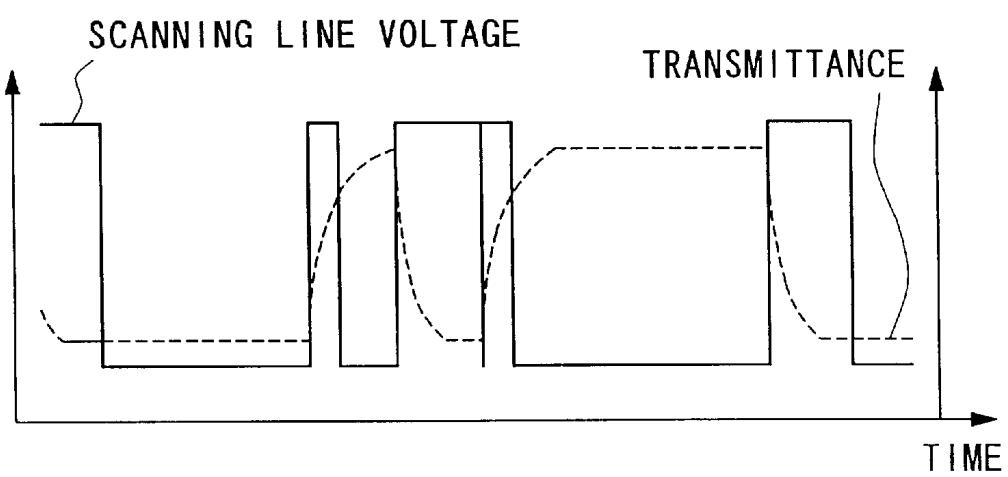

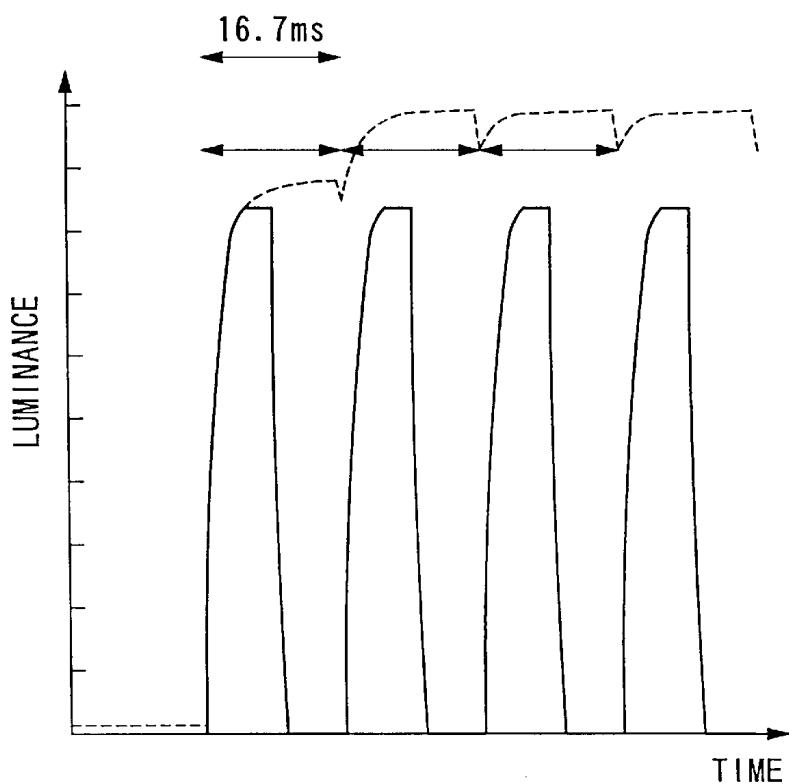

As a method of solving these problems, a reset pulse method involving applying a reset pulse arranged in a predetermined liquid crystal state before new data writing, is often used. As an example, the technology disclosed in IDRC 1997, L-66 to L-69 is reported. In this document, an OCB (Optical Compensated Birefringence) mode with an attached compensation film where the orientation of a nematic liquid crystal is in a  $\pi$  type orientation, is used. The response speed of this liquid crystal mode is approximately from two milliseconds to five milliseconds, which is much faster than the conventional TN mode. As a result, it can be expected that response is essentially completed inside the one frame. However as mentioned before, several frames are required until the large drop in the holding voltage due to the change in the transmittance due to the response of the liquid crystal occurs and a stable transmittance is obtained. Accordingly, a writing method which always shows black after writing a white display within one frame is shown in FIG. 26 (FIG. 5 in the above mentioned document). The X axis is time and the Y axis is luminance. The dotted lines are the luminance change in the case of normal drive, with stable luminance being reached in the third frame. Accord-

ing to this reset pulse method, a predetermined state always results at the time of new data writing, and hence a one to one correspondence referred to as a constant transmittance is seen with respect to a written constant signal voltage. Due to this one to one correspondence, generation of a drive signal becomes extremely simple, and at the same time the information written at the previous time is stored. Hence means such as the frame memory become unnecessary.

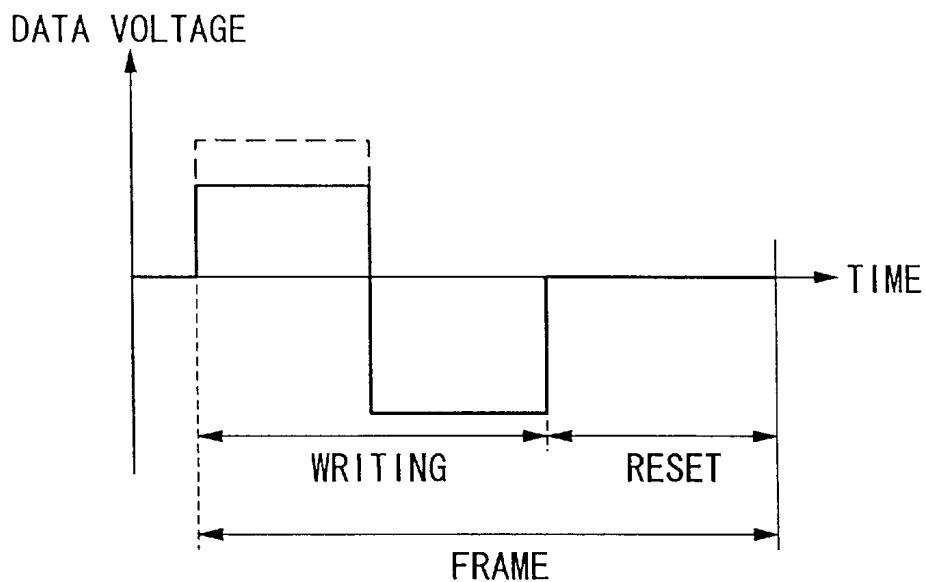

Furthermore, as another means of applying a reset voltage, a method is used where a positive and negative data signal voltage is generated with respect to a constant image signal, and after applying the positive (negative), a negative (positive) is applied and after that a reset voltage is applied. In this case, when positive and negative data signal voltages with equal amplitudes are simply applied, the aforementioned "step response" occurs. Therefore, application of the data signal voltage as in FIG. 27 and FIG. 28 is performed.

FIG. 27 is a waveform diagram for the data voltage, while FIG. 28 is a waveform diagram for the transmittance at that time. The waveforms shown by the dotted lines in the figures are the wave form of the data voltage with equal amplitude, and the waveform of the data voltage with equal amplitude, and the waveform of the transmittance when this is applied. In order to simplify these figures, the data voltage is shown with a common voltage subtracted (actually the common voltage corresponds to the position for zero hold voltage in the figure). In order to prevent "step response", the amplitude of the data voltage at the frame beginning (here a positive data voltage) is set low, and the amplitude of the data voltage for the frame latter half (here a negative data voltage) is made the same as the wave form of the dotted line. In this way the step response is stopped, and as shown in FIG. 28, the former half and latter half of the frame both obtain the same transmittance. After this, when the frame is completed, then by performing a reset, this is always arranged in a predetermined reset liquid crystal state. By newly applying the same wave form in the next frame, a one to one correspondence referred to as a constant transmittance is seen with respect to a constant signal voltage. Furthermore, here the reset voltage is made zero volts with respect to the common voltage. However this differs depending on the liquid crystal display mode, or the predetermined state realized with reset.

Moreover, these methods involving reset drive can be generally divided into two kinds by conditions related to the timing under which the reset of each scanning line is performed within a field. That is to say, there is the method where all of the scanning lines of the overall panel are reset at once (hereunder, whole screen en bloc reset), and the method of resetting as with scanning writing, while scanning each scanning line or scanning line block where scanning lines are multiply gathered together (hereunder, scanning reset). With the whole screen en bloc reset, at the time of reset, this can be thought of as scanning reset for all of the scanning lines in the same block (however with this way of thinking, reset scanning does not occur, and hence scanning reset and whole screen en bloc reset are different types).

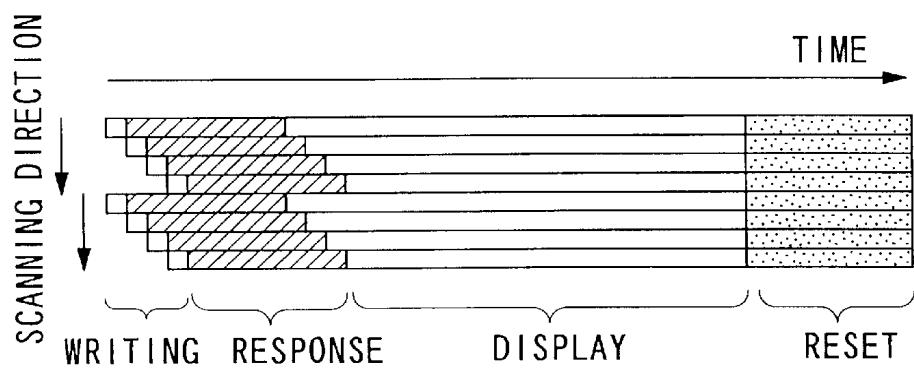

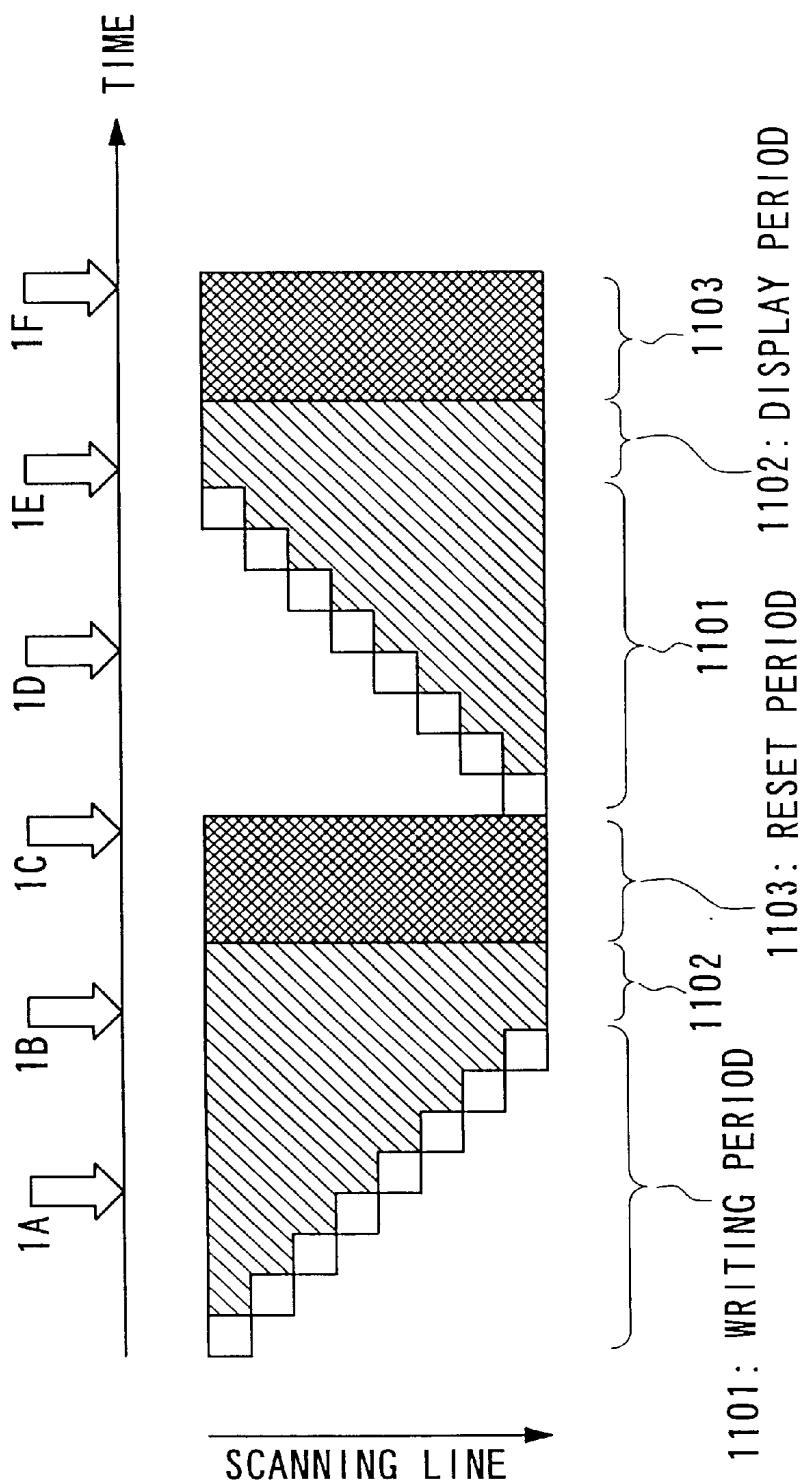

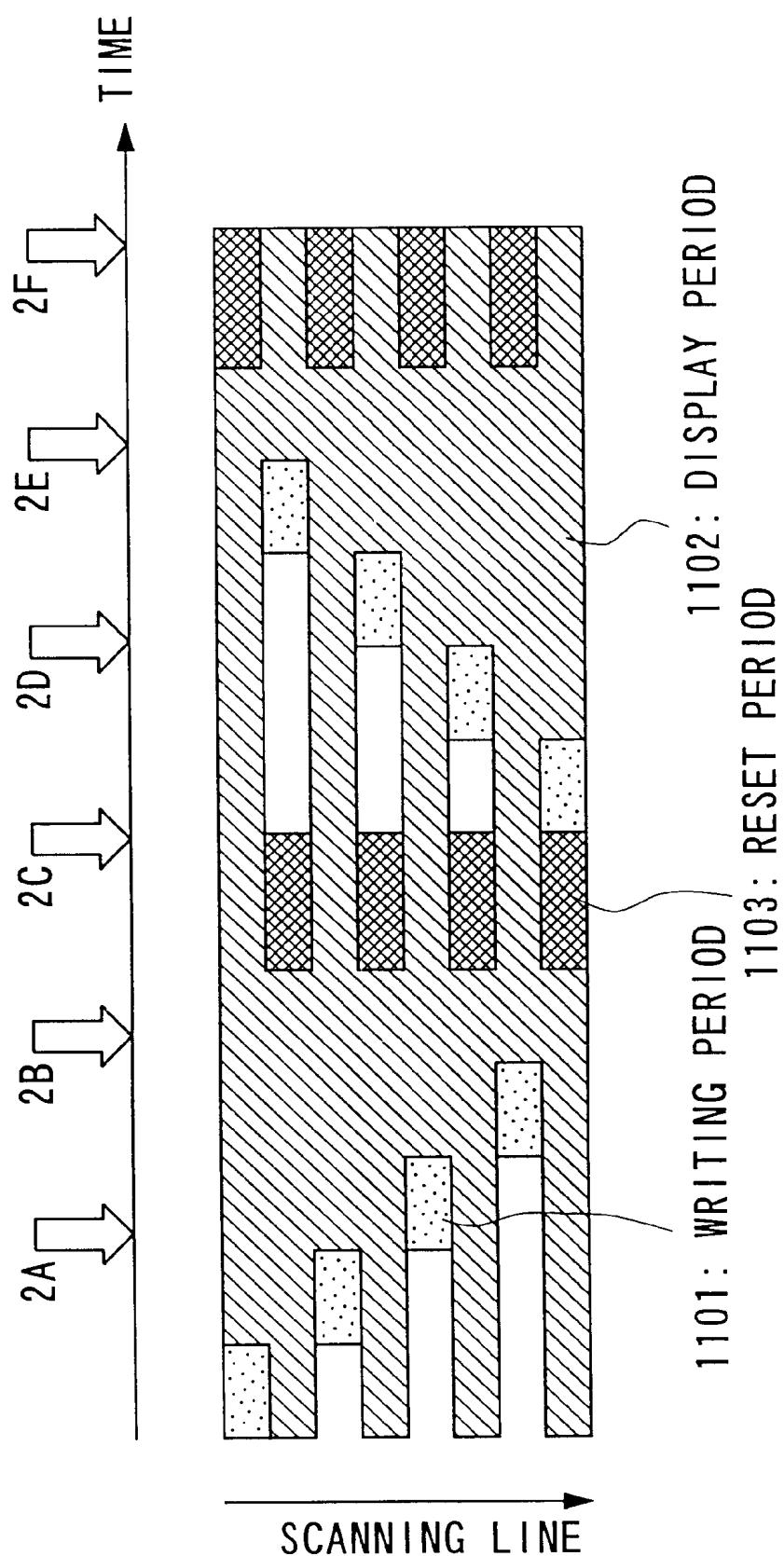

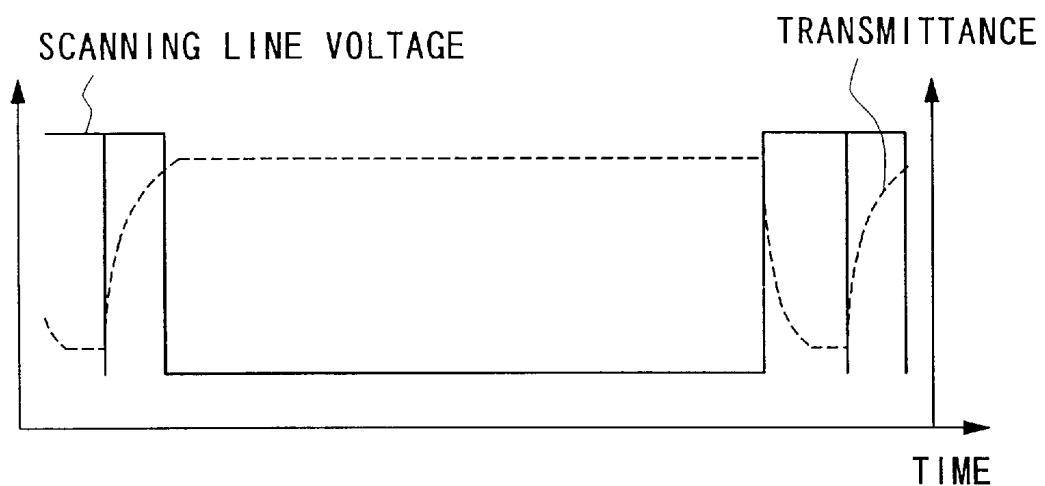

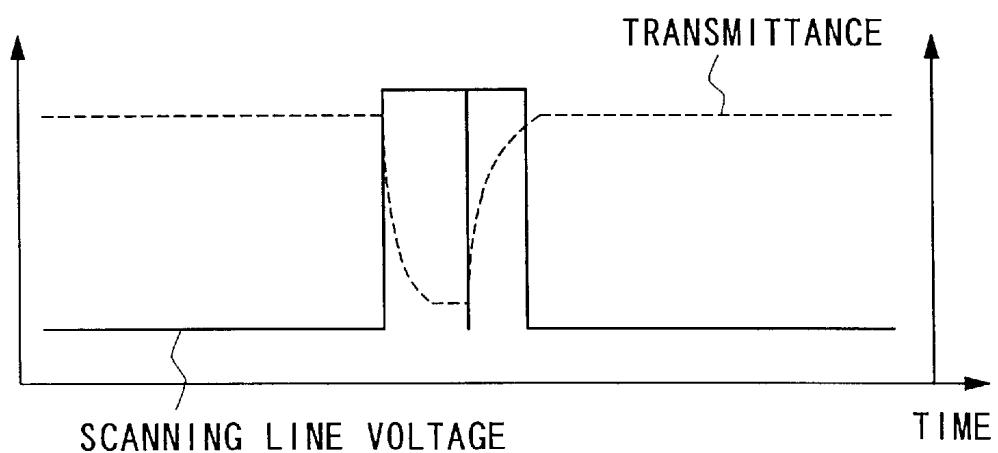

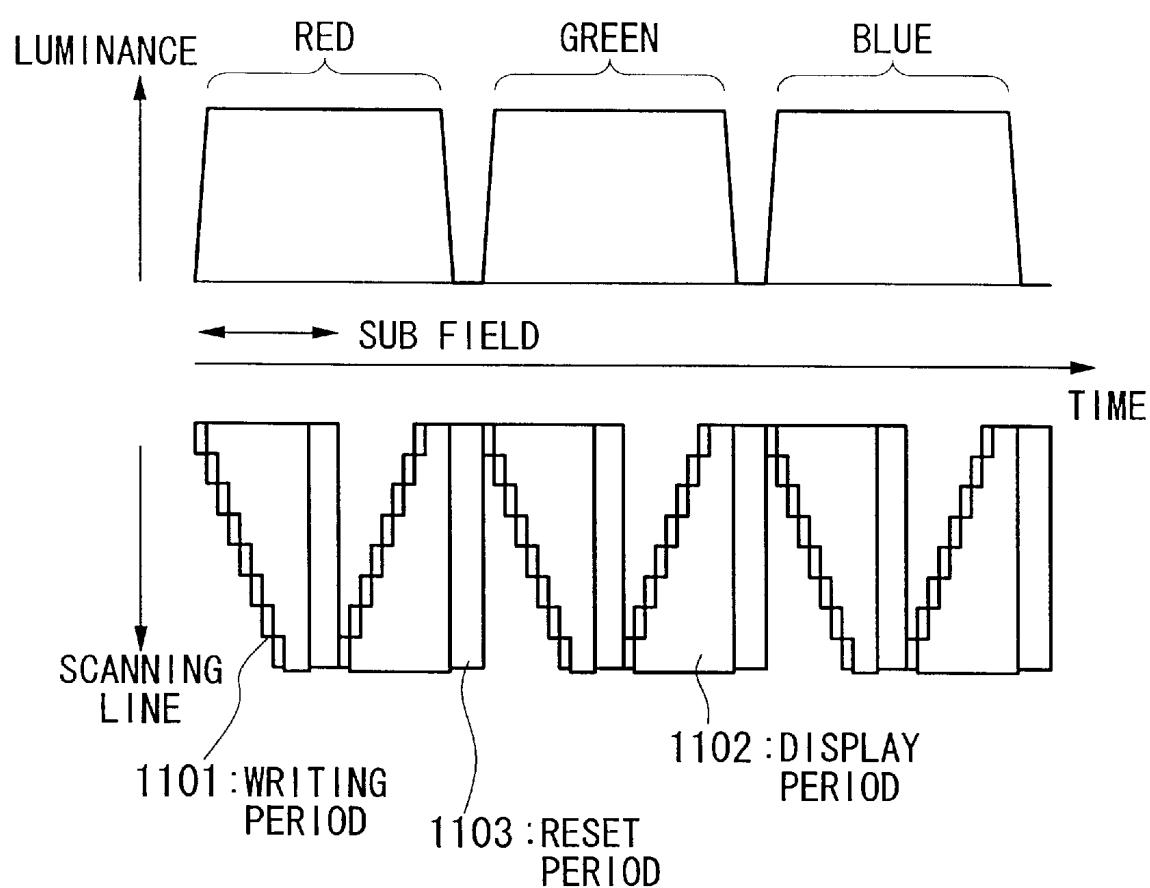

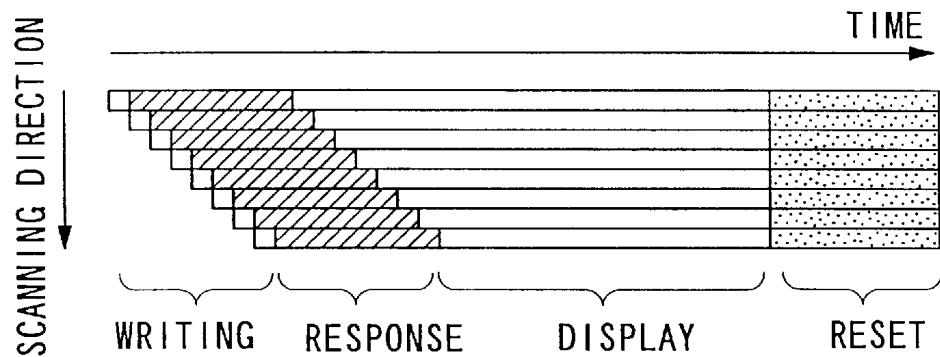

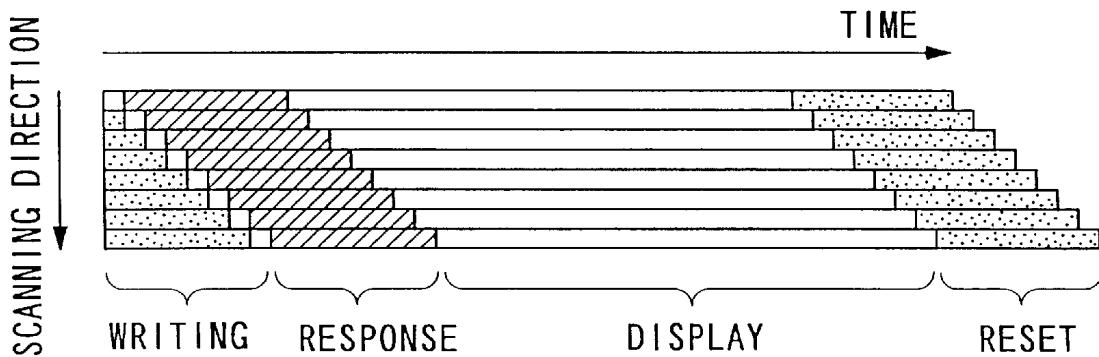

FIG. 29 and FIG. 30 show timing charts for each scanning line in the respective reset methods. FIG. 29 is a timing chart for each scanning line in the whole screen en bloc reset. FIG. 30 is a timing chart for each scanning line in the scanning reset. The X axis is time and the Y axis shows the scanning line direction. Each period, namely the writing period, the response period, the display period, and the reset period is shown. In both FIG. 29 and FIG. 30, writing is performed while scanning the scanning line in sequence (here from top to bottom) in the writing period. The writing period

(abbreviated to  $T_w$  as required) is shown by the necessary time  $T_w$  for writing of each of the scanning lines multiplied by the number  $n$  of scanning lines ( $T_w = n \times t_w$ ). After this, a response period (abbreviated to  $T_m$  as required) exists until the response of the liquid crystal becomes substantially stable. Then, a display only period (abbreviated to  $T_d$  as required) continues until the response of the liquid crystal becomes stable and reset starts. When reset starts, a large difference occurs between FIG. 29 and FIG. 30. That is to say, with the whole screen en bloc reset of FIG. 29, all of the scanning lines are reset simultaneously. The reset period (abbreviated to  $T_r$  as required) is the sum of the time required for reset writing and the time until the liquid crystal becomes substantially steady in a predetermined state. On the other hand, with the scanning reset of FIG. 30 the scanning lines are sequentially scanned and reset. As a result, with the scanning reset method of FIG. 30, the reset period  $T_r$  and the writing period  $T_w$  are quite overlapped at parts. In this way, with the scanning reset method, there is no wastage in time distribution.

Furthermore, as a different means for solving the problems such as step response, there is proposed a drive method called a "pseudo DC drive" shown in AMLCD '97 Digest from pages 119 to 122. This technique will be explained with reference to FIG. 31. With FIG. 31, as with FIG. 24, part (a) shown in FIG. 31 is a waveform diagram for data voltage, part (b) shown in FIG. 31 is a waveform diagram for gate voltage, and part (c) shown in FIG. 31 is a waveform diagram for transmittance at the time. Furthermore, FIG. 32 is a timing chart for each scanning line, showing the luminance for the light and dark of positive and negative display periods 102 and 104, based on the transmittance of part (c) shown in FIG. 31.

Moreover, in FIG. 32, a time of 16.7 ms is shown by the arrow. With the disclosure in the document, 16.7 ms is defined as the one frame time. However since this definition is not common, this is changed in the figures of the present specification (the one frame time of the disclosure in the literature, with the present invention corresponds to the normal one field time for the conventional technology). The "pseudo DC drive" differs from the normal AC drive shown in FIG. 24, in that the data voltage for the same signal continues to be applied during a plurality of fields. After the plurality of fields, the sign of the data voltage inverts, and the electrical bias disappears. In FIG. 31, after positive writing for four fields, negative writing for four fields is performed, and display of one image signal is finished. The writing timing for each scanning line is as shown in FIG. 32. Positive data is written sequentially from the top, and after repeating four times, the writing of negative data sequentially from the top is repeated four times. With this method, a state is obtained where the applied constant DC voltage and the holding voltage for both ends of the liquid crystal are the same. As a result, the drop in the holding voltage due to response of the liquid crystal disappears. Furthermore, compared to the method as with the AC drive of FIG. 24, where the holding voltage drops due to the response of the liquid crystal, the final transmittance increases. However, the one frame time with this method becomes the total of the plurality of frames for each sign. That is to say, with the example of FIG. 31, the one frame time of this method takes four times the time for the frame of FIG. 24.

Furthermore, a technique for flashing the light source, for a different purpose to field sequencing is known. This is aimed at moving picture correspondence. This is based on the analysis results of display characteristics for two cases. The case where a display method as with a CRT where due

to the properties of a fluorescent substance the luminance is reduced suddenly after high luminance is classified as an impulse type, and the case as with a liquid crystal display, where the luminance is held within one field period is classified as a hold type. This analysis is shown in the proceedings of a seminar sponsored by the LCD forum of the Japanese Liquid Crystal Society "LCDs Encroaching into the Market for CRT Monitors—from the Perspective of Moving-Image Quality" on pages 1 to 6. The results of this analysis indicate that in performing satisfactory moving picture display with the hold type, merely improving the response speed of the liquid crystal is insufficient. Moreover, it was indicated that there are problems attributable to the operating method of the hold type where the display light is held. In order to improve this, two methods have been considered, namely (1) to shorten the hold period of the display light, and (2) to arrange the display light as much as possible in the screen position along the movement of the image. With (1), as a method of shortening the hold period, on pages 21 to 23 of the same proceedings a technique is disclosed where a  $\pi$  cell construction which employs a compensating plate is used, and with a high-speed LCD the back light source is flashed to give display. Furthermore, there has also been discussion relating to a technique for shortening the hold period, by continually lighting the back light source and inserting a reset condition.

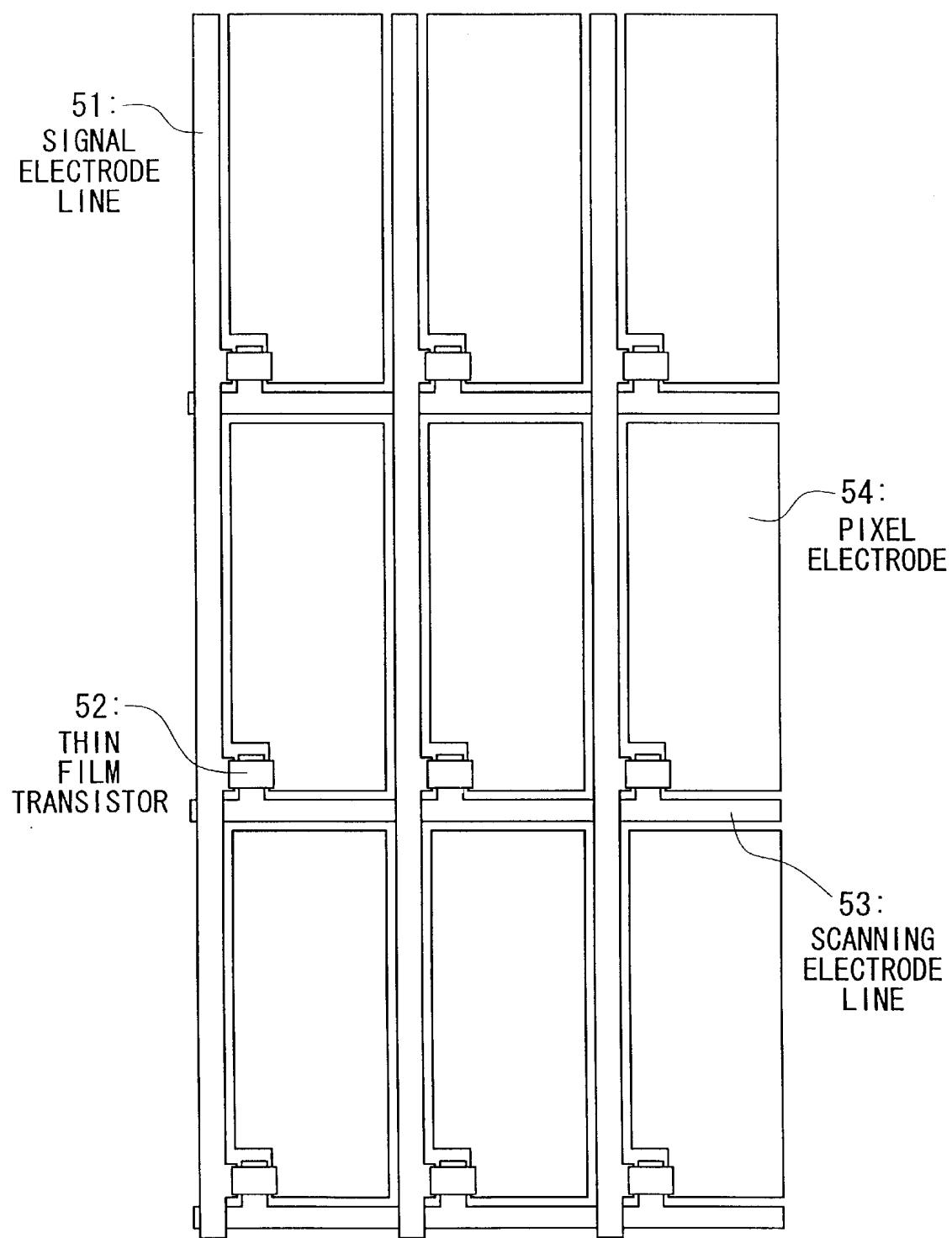

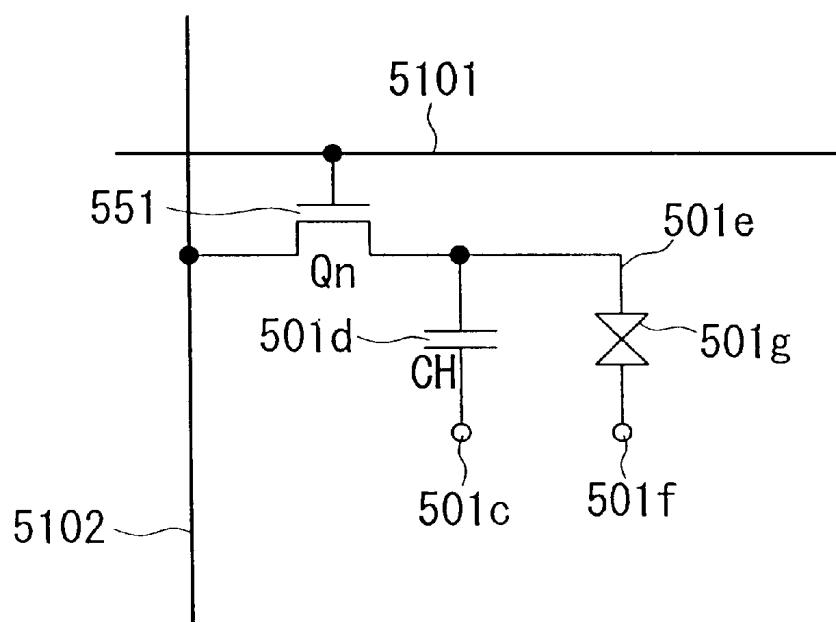

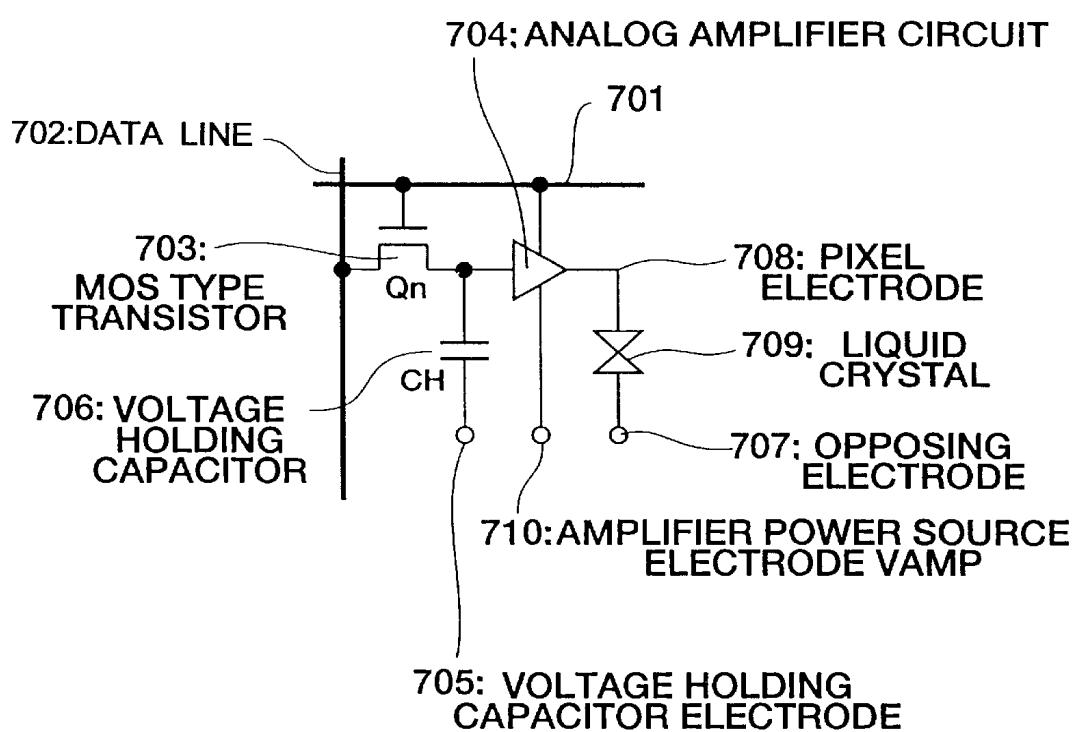

Furthermore, FIG. 50 shows an example of an equivalent circuit of a single pixel section of an active matrix liquid crystal display, for the case where a twisted nematic liquid crystal (TN liquid crystal) is used.

As shown in FIG. 50, a gate scanning line 5101 is connected to a gate electrode of a switching MOS type transistor (Qn) 551, a data line 5102 is connected to a source electrode, and a pixel electrode 501e of a liquid crystal element 501g is connected to a drain electrode, with the construction being such that a voltage is applied to the liquid crystal across the opposing electrode 501f for drive thereof.

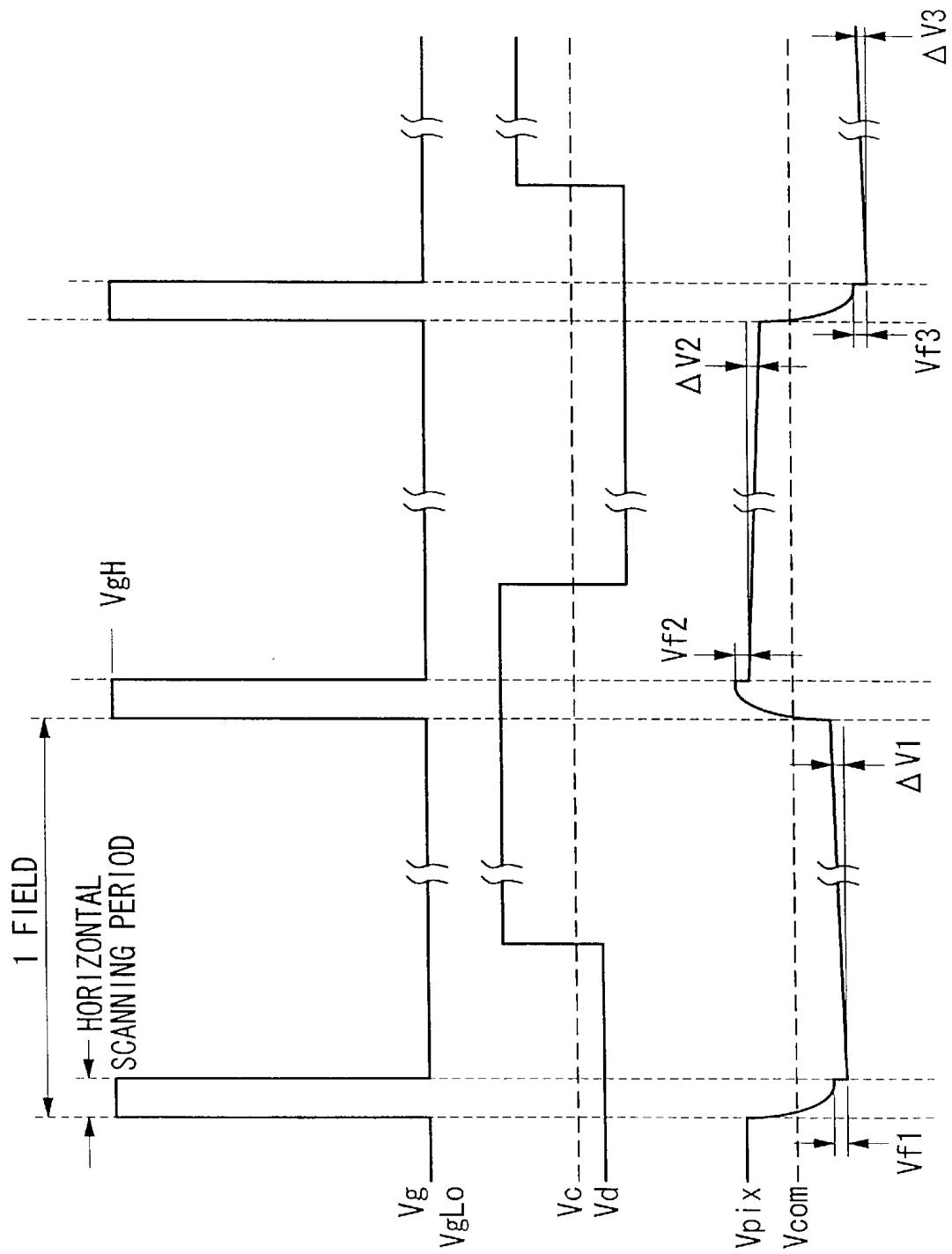

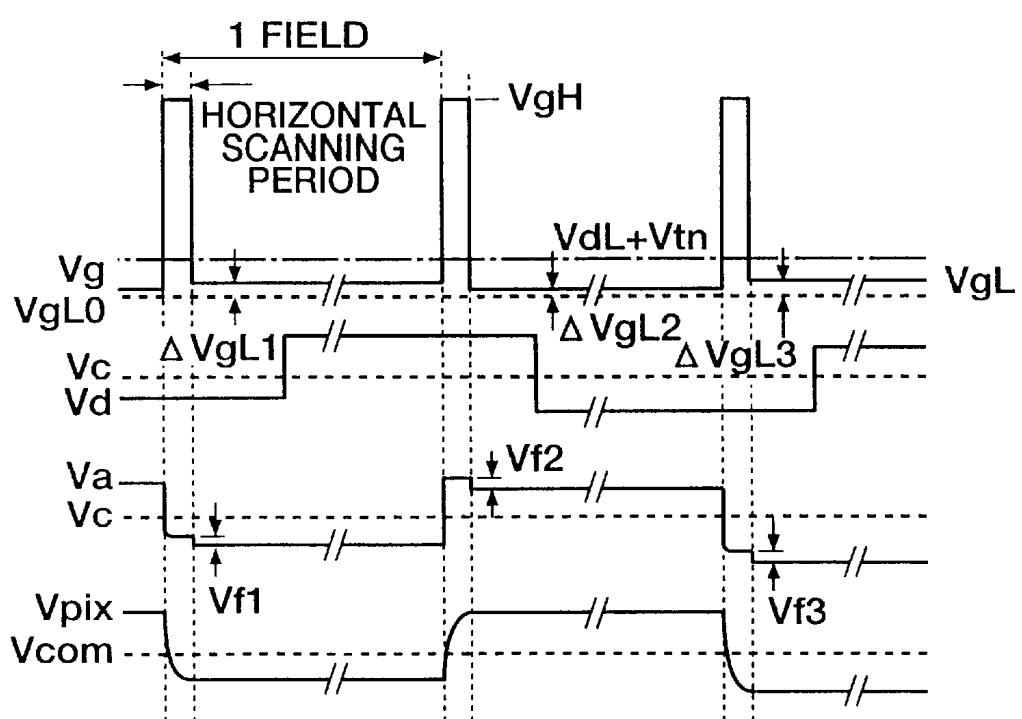

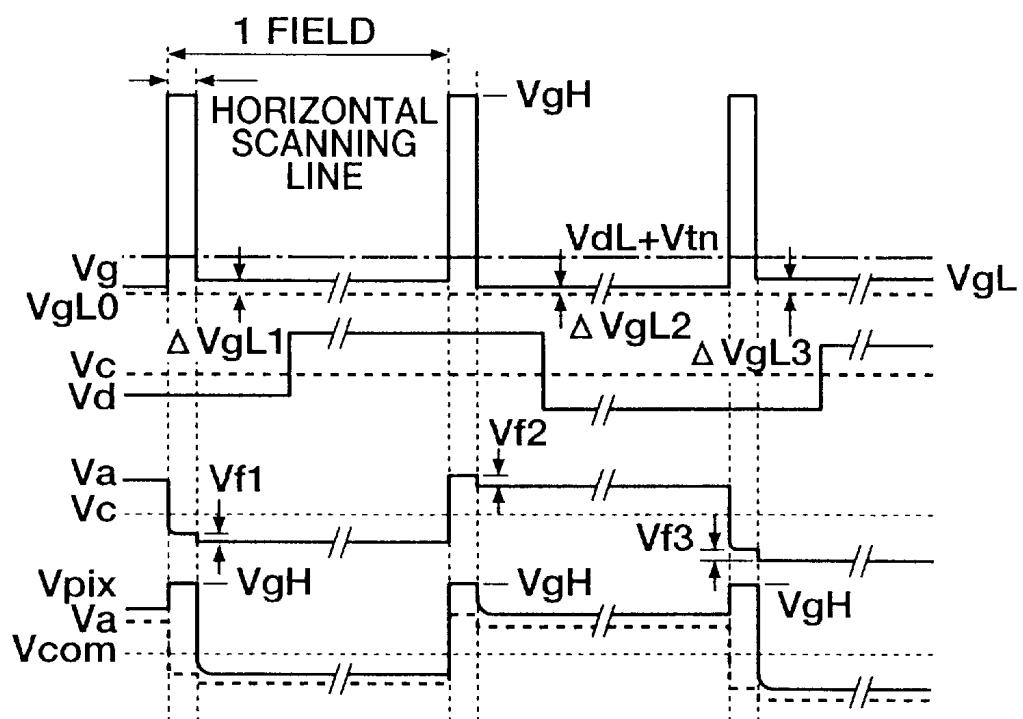

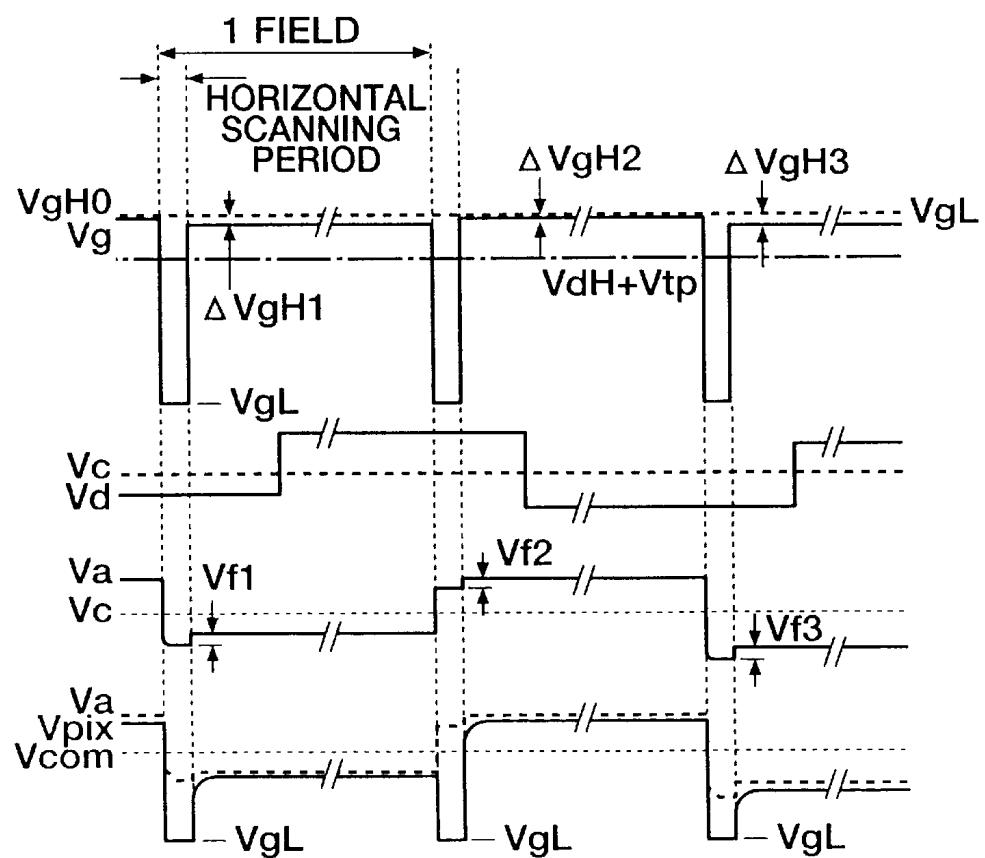

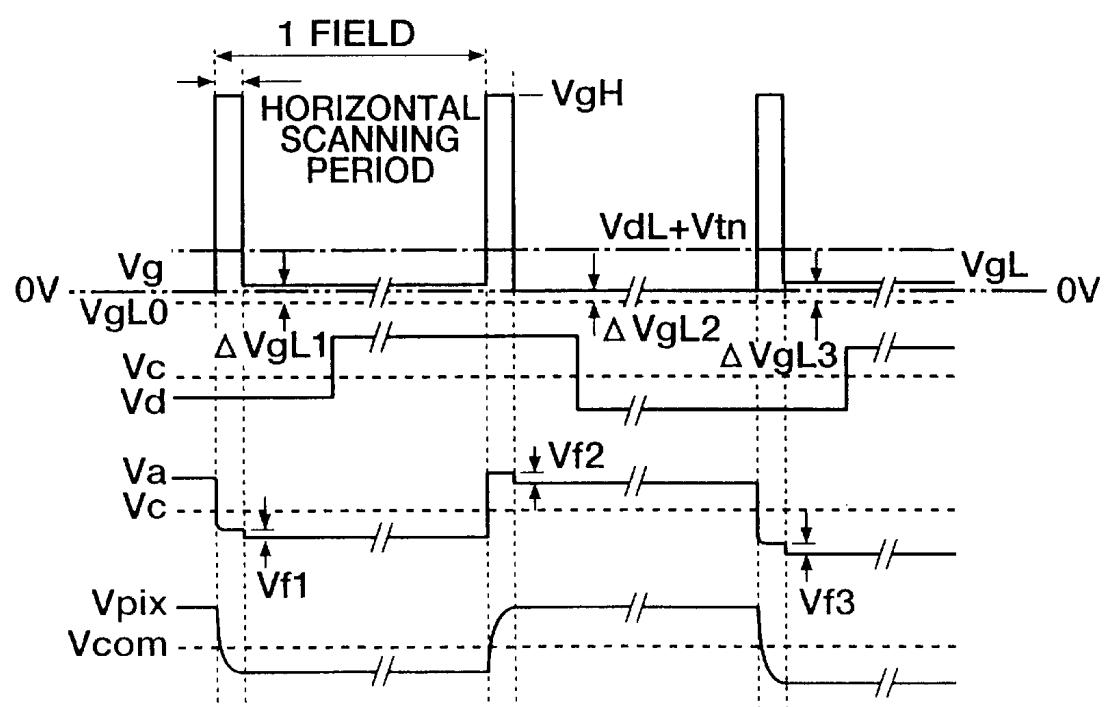

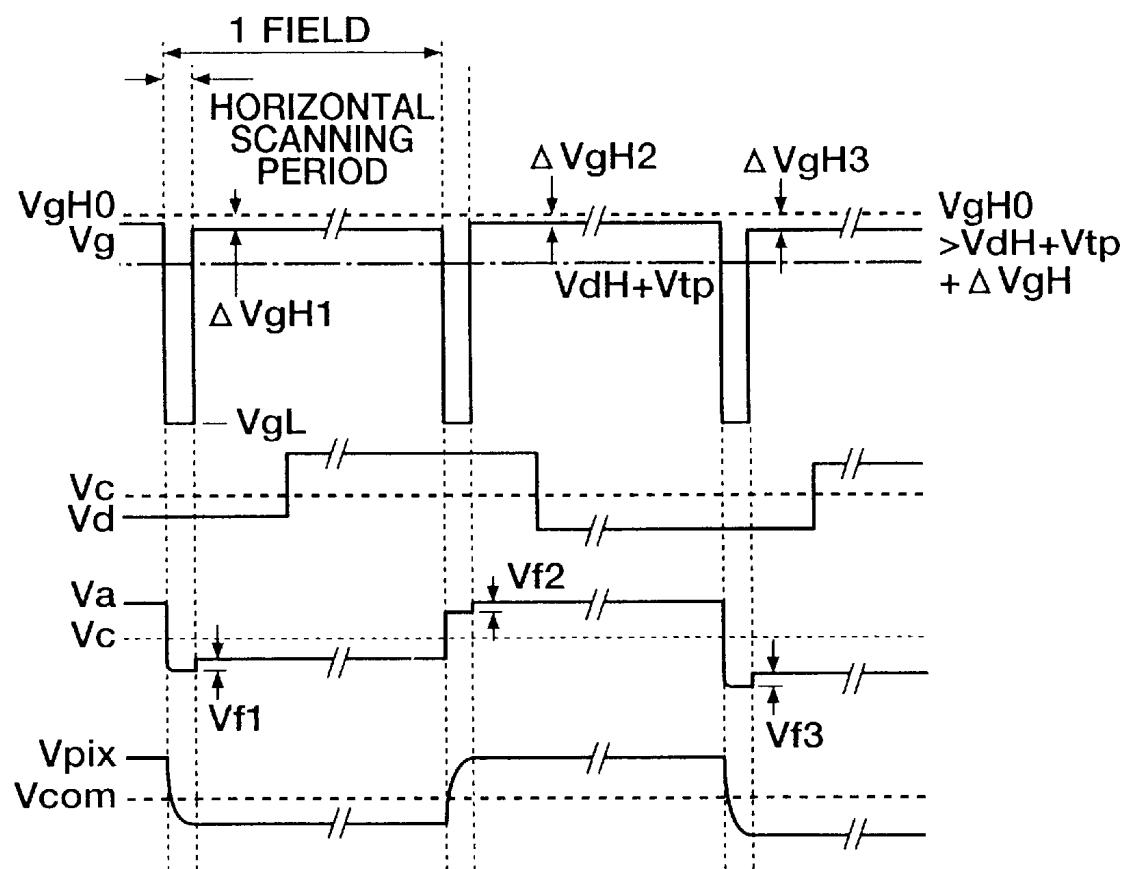

Furthermore, normally a voltage holding capacitor 501d is created between the pixel electrode 501e and a voltage holding capacitor electrode 501c. A typical timing chart for the gate scanning voltage  $V_g$ , the data signal voltage  $V_d$ , and the pixel electrode voltage  $V_{pix}$  at this time, is shown in FIG. 51.

By having a high level  $V_{gH}$  while the gate scanning voltage  $V_g$  is in the horizontal scanning period, the MOS type transistor 551 comes on, and the data signal  $V_d$  input to the data line is transferred to the pixel electrode 501e via the MOS type transistor 551.

When the horizontal scanning period is completed and the gate scanning voltage  $V_g$  becomes a low level, the MOS type transistor 551 goes off, and the data signal transferred to the pixel electrode 501e is held by the voltage holding capacitor 501d and the capacitance of the liquid crystal. At this time, with the pixel voltage  $V_{pix}$ , at the time when the MOS type transistor 551 goes off, a voltage shift referred to as a feed-through voltage occurs via the capacitance between the gate and source of the MOS type transistor 551. In FIG. 51, this voltage shift is shown by  $V_{f1}$ ,  $V_{f2}$  and  $V_{f3}$ . The amount of this voltage shift can be made smaller by increasing the value of the voltage holding capacitor 501d.

The pixel voltage  $V_{pix}$ , is held until the gate scanning voltage  $V_g$  again becomes a high level in the subsequent horizontal scanning period and the MOS type transistor 551 comes on. At this time, in the holding periods, the pixel voltage  $V_{pix}$  fluctuates slightly in each of the fields by respective amounts  $\Delta V_1$ ,  $\Delta V_2$ , and  $\Delta V_3$ . This is in accor-

dance with the liquid crystal response, and is attributable to the change in the capacitance of the liquid crystal. Normally, in order to make this change as small as possible, the voltage holding capacitor **501d** is set to a value two to three times larger than the pixel capacitance  $C_{pix}$ . As described above, the TN liquid crystal can be driven by the pixel circuit configuration shown in FIG. 50.

However, even if such an accumulation capacitance is used, theoretically there is a limit to the prevention of a drop in the charge holding function. Furthermore, in a highly integrated matrix display device, the provision of a capacitor with a large surface area so as to suppress voltage fluctuations for each pixel, causes a problem in that the load increases with respect to the data signal driver, or the switching MOS type transistor **551**, and there is a decrease in the pixel aperture ratio.

Furthermore, although research and development is being made into various liquid crystal materials for achieving high performance of liquid crystal displays. However with these, since a polarizer is not used, the materials are high polymer liquid crystal materials with increased light transmittance, liquid crystal materials having polarization such as ferroelectric liquid crystals and antiferroelectric liquid crystals with a high-speed response and wide viewing angle, and OCB mode liquid crystal material and the like.

However, since for example with the high polymer liquid crystal material, the resistivity is low, and the leakage current is large compared to the TN liquid crystal, the pixel voltage fluctuations during the holding period are large. Also with the liquid crystal material having polarization, similarly due to the redistribution etc. of the charge occurring due to spontaneous polarization, the pixel voltage fluctuations during the holding period are larger than for the case of the TN liquid crystal. Hence with conventional pixel construction, the practical use of a display device which uses such a liquid crystal materials is difficult.

As a method of solving such a problem, a construction, which uses a source-follower type amplifier where the pixel voltage  $V_{pix}$  is kept constant during the holding period, is disclosed for example in Japanese Patent Application, First Publication No. Hei 2-272521, No. Hei 7-20820, No. Hei 10-148848, No. Hei 1-292979, No. Hei 5-173175 and No. Hei 11-326946. According to these methods, the pixel voltage  $V_{pix}$  during the holding period can be kept constant.

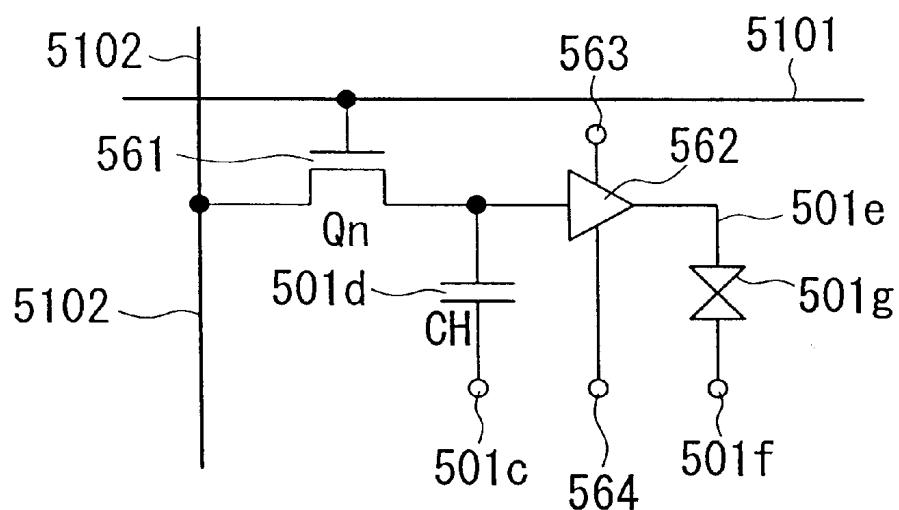

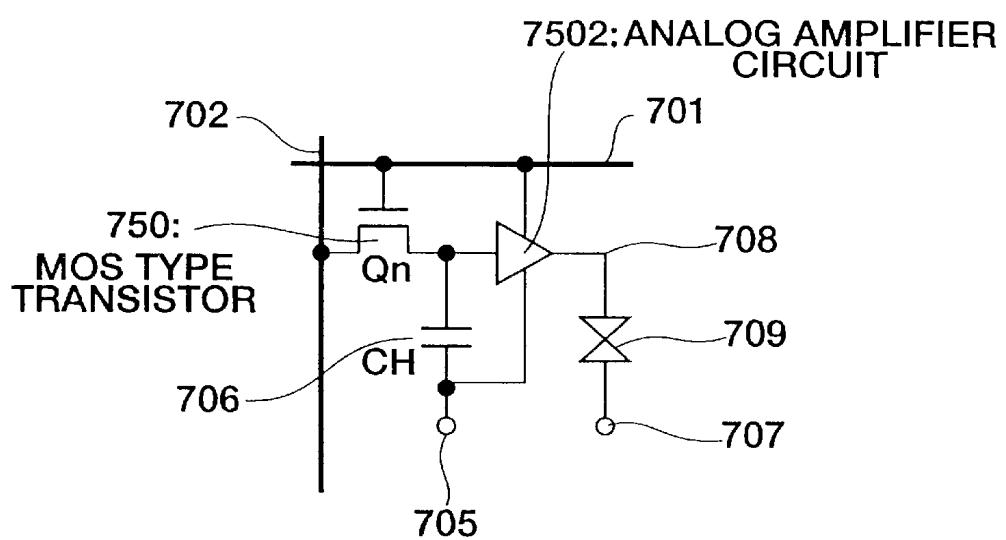

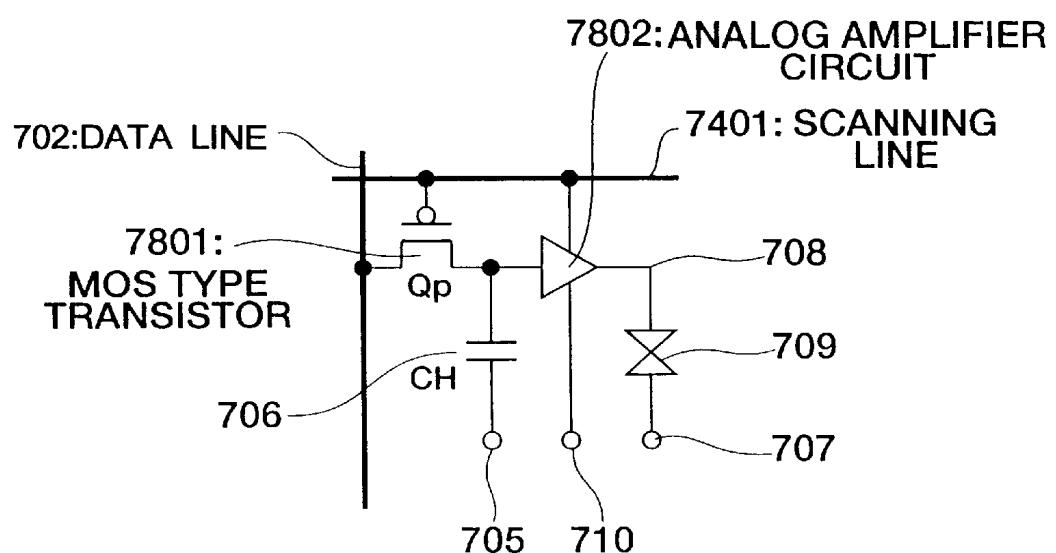

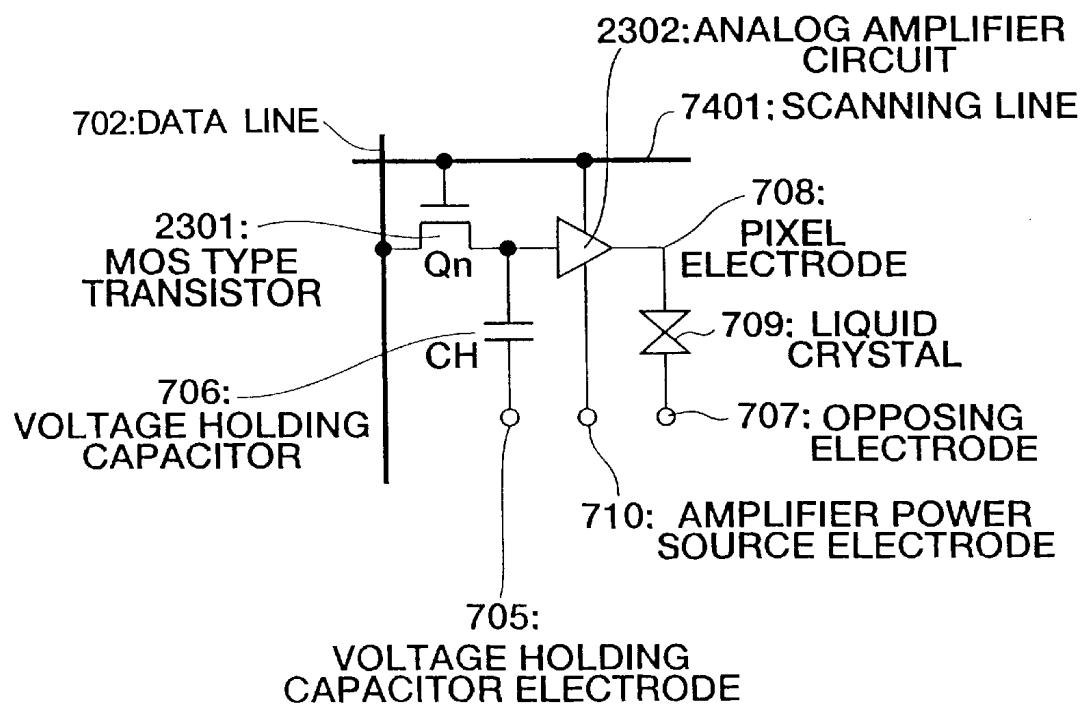

FIG. 52 is a diagram showing an example of such an analog amplifier circuit attached pixel. As shown in FIG. 52, a scanning line **5101** is connected to a gate electrode of a switching MOS type transistor (Qn) **561**, a data line **5102** is connected to a source electrode, a drain electrode of the MOS type transistor **561** is connected to the input electrode of an analog amplifier circuit **562**, and a pixel electrode **501e** of a liquid crystal element **501g** is connected to an output electrode, with the construction being such that a voltage is applied to the liquid crystal across the opposing electrode **501f** for drive thereof.

Normally, the voltage holding capacitor **501d** is created between the pixel electrode **501e** and the voltage holding capacitor electrode **501c**. The power source line of the analog amplifier circuit **562** is connected to a separately provided amplifier positive power source electrode **564** and amplifier negative power source electrode **563**. Alternatively, in order to simplify the circuit construction, the configuration may be such that one is connected to the scanning line and one is connected to an existing electrode such as the voltage holding capacitor electrode **501c**.

FIG. 52 shows the case where the positive power source electrode **564** and the amplifier negative power source

electrode **563** are provided. The operation of this circuit is basically the same as for the case described for the circuit shown in FIG. 50 and FIG. 51. However when the switching transistor is off, a predetermined voltage continues to be applied to the liquid crystal element **501g** by the analog amplifier circuit **562**. Hence the voltage fluctuations  $\Delta V1$ ,  $\Delta V2$  and  $\Delta V3$  produced in FIG. 51 can be suppressed.

Furthermore, in Japanese Patent Application, First Publication No. Hei 2-272521, No. Hei 7-20820 and No. Hei 10-148848 is disclosed a construction where the positive power source (VDD) line and the negative power source (VSS) line of the source-follower type amplifier circuit are provided separate to the normal bus line.

However, with this construction, the circuit construction becomes complicated, and the aperture ratio also is reduced.

In the aforesaid Japanese Patent Application, First Publication No. Hei 10-148848, increase in the size can be avoided by common use of the power source line in a plurality of lines. However the necessity arises for an increase in the amount of wiring. On the other hand, in Japanese Patent Application, First Publication No. Hei 1-292979, No. Hei 5-173175 and No. Hei 11-326946 a construction is proposed where either one of the negative power source lines and the positive power source lines of the amplifier circuit are connected to the gate scanning line, making a special bus line unnecessary. With this method, the pixel voltage  $V_{pix}$  during the holding period can be kept constant, with a simple construction where the aperture ratio is lowered only slightly.

With the aforementioned pseudo DC drive, compared to the AC drive, a long frame period (in FIG. 31 and FIG. 32, this is four times that of the AC drive) is necessary, high-speed response is not activated. Furthermore, as a result a long period flicker occurs oscillating at several times the normal frame time (16.7 ms) as shown by the luminance in light and dark in FIG. 32. Due to these results there is a problem in that display coordination with a moving picture is difficult.

Furthermore, with the method which compares the accumulation charge before and after writing, as mentioned before, there is the problem in that a comparison operation section etc. in addition to the frame memory is necessary, thus causing an enlargement of the system.

Moreover, with the reset method, within one field period there exists for example a writing period, a response period (the time after writing until the response becomes stable), and a reset period (the time until becoming stable in a constant state for reset writing and resetting). The period in which the display can be actually used becomes the time from the first field time excluding these periods. As a result, with the reset pulse method, there is a problem in that the reset period part, and the time which can be used for display becomes short.

Furthermore, a problem arises in that the reset period part and the scanning period becomes short. Normally the scanning period (writing time) is approximately equal to the field time, being half of the time of the frame time, divided by the scanning line number. However, if a reset period is provided during the field time, the scanning period shown in FIG. 29 becomes that where the reset time subtracted from the field time is divided by the number of scanning lines. As a result due to reset, the scanning period is shortened. A means for combining the interlace drive and the reset so that the reset period does not impose an influence on the scanning period, is disclosed for example in Japanese Patent Application, First Publication No. 4-186217. With this method, the FLC

(ferroelectric liquid crystal) panel is driven in the interlace mode, and some scanning lines are reset in the non display period. In this way, the reduction in the scanning period due to the provision of the reset period is somewhat protected. Furthermore, it is considered that since the periods for reset of the adjacent lines are shifted, the flicker is decreased due to averaging. However, with this method also, there is still a problem in that the time which can be used for the reset period part and the display, is shortened.

Such a decrease in the display period is particularly serious with the field sequential display, making it extremely difficult to ensure luminance.

Furthermore, due to the reset there is the occurrence of luminance unevenness inside the panel. As a countermeasure for this point, a slight improvement is possible with the technique disclosed in Japanese Patent Application No. 10-041689.

Moreover, if as shown in FIG. 52, the pixel construction is such that the analog amplifier circuit is used in addition to the conventional pixel construction, then not only with the TN liquid crystal, but also in low resistivity materials such as a high polymer liquid crystal, or liquid crystal materials having polarization such as ferroelectric liquid crystals or antiferroelectric liquid crystals, it is possible to suppress the voltage fluctuations in the liquid crystal pixel potential. However in the case where display is performed with this pixel construction, output deviations of the amplifier directly become display deviations of the pixels. Hence the requirement arises for making the amplifier output constant for each pixel, or for correcting the input voltage in response to the deviations in the amplifier output.

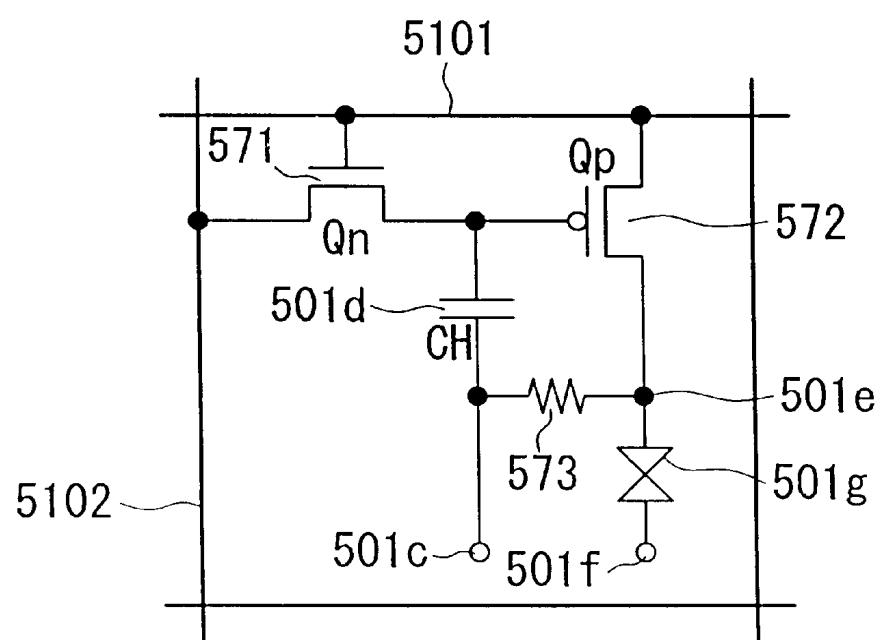

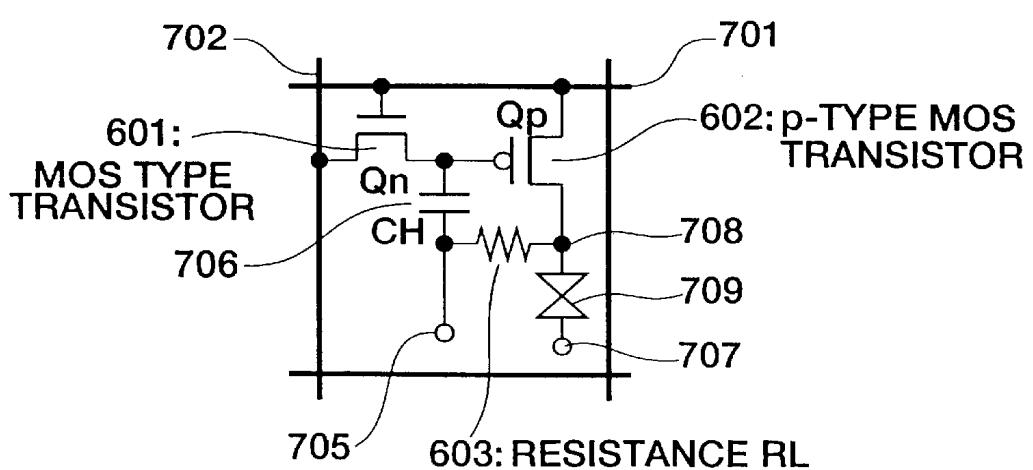

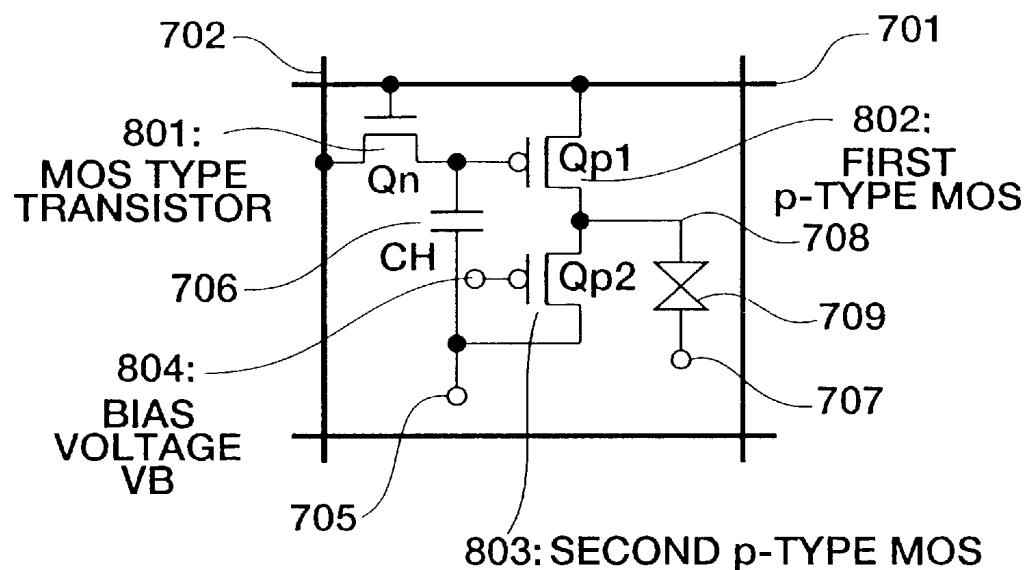

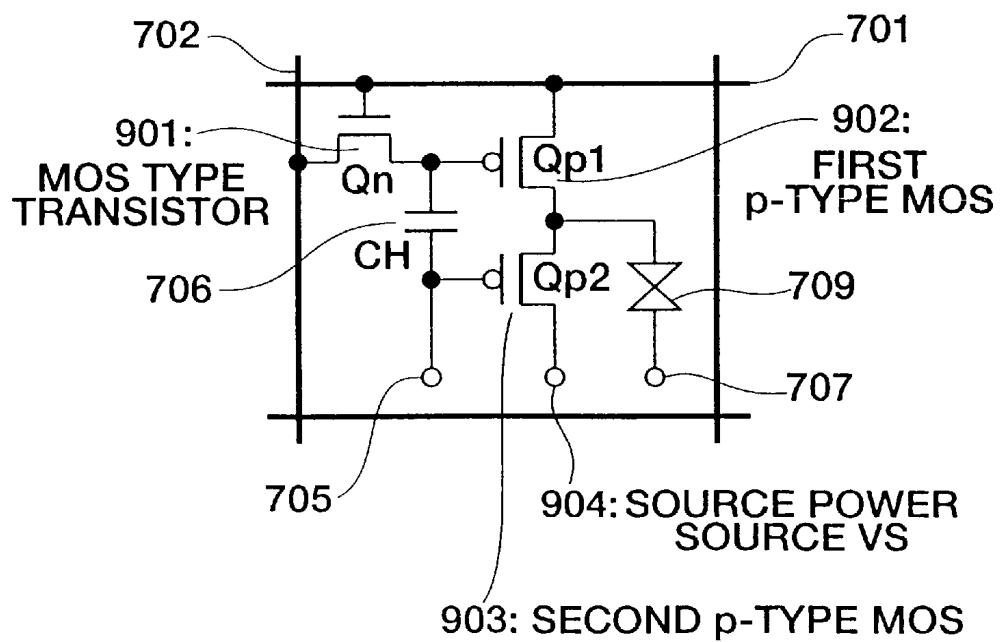

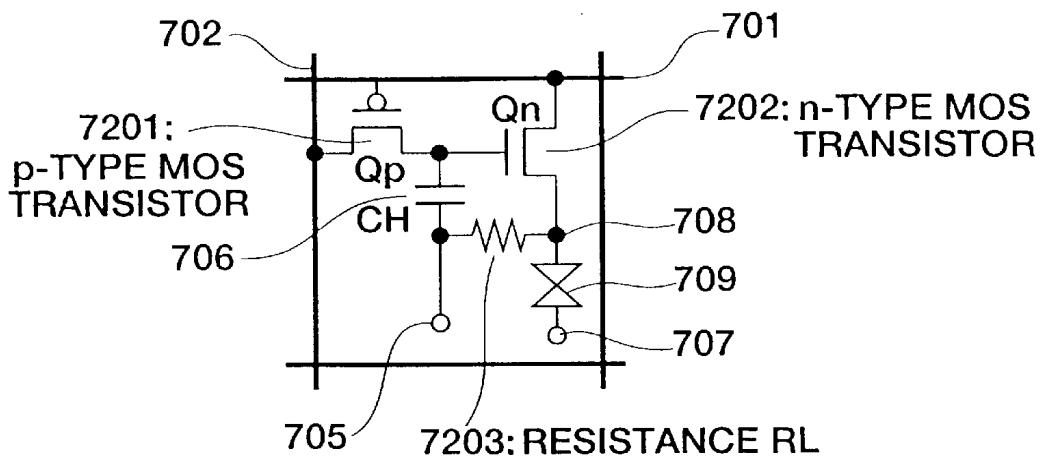

With these output deviations of the amplifier, the characteristic differences etc. of the transistors which constitute the analog amplifier circuit are the principal factor. FIG. 53 shows an equivalent circuit for one pixel to which an analog amplifier circuit is attached, showing a specific construction which uses thin film transistors. As shown in FIG. 53, the construction comprises: an n-type MOS transistor (Qn) 571 with the gate electrode connected to a scanning line 5101 and one of the source electrode and the drain electrode connected to a data line 5102, a p-type MOS transistor 572 with the gate electrode connected to the other of the source electrode and the drain electrode of the n-type MOS transistor 571, and one of the source electrode and the drain electrode connected to the scanning line 5101, and the other of the source electrode and the drain electrode connected to the pixel electrode 501e, a voltage holding capacitor 501d formed between the gate electrode of the p-type MOS transistor 572 and a voltage holding capacitor electrode 501c, a resistance (RL) 573 connected between the pixel electrode 501e and the voltage holding capacitor electrode 501c, and a liquid crystal 501g, the orientation of which is to be changed, disposed between the pixel electrode 501e and an opposing electrode 501f.

With the construction shown in FIG. 53, the pixel electrode 501e is driven by the analog amplifier circuit even after the horizontal scanning period is completed. Therefore, the fluctuations in the pixel voltage  $V_{pix}$  (=amplifier output voltage  $V_{out}$ ) accompanying the response of the liquid crystal as described for the conventional technology, can be suppressed.

At this time, the amplifier output voltage changes due to the value of the transconductance  $g_{mp}$  of the p-type MOS transistor, and the resistance  $RL$ . This is represented by an equation using the amplifier input voltage  $V_a$ , and the threshold value  $V_t$  of the MOS type transistor used in the amplifier, that is to say:

$$V_{out}=V_a-V_t$$

(1)

Therefore, in the conventional technology where only the analog amplifier circuit is fitted, the deviation of the threshold values for each of the pixels directly becomes the deviation of the pixel voltage, so that a decrease in image quality such as with irregular coloring occurs. This decrease in image quality is greater in the case of a large screen where the characteristic differences of the transistors is increased. However under present conditions where the demand for high detail and multiple gray scale is severe, there are also problems with small size screens.

Furthermore, if the pixel construction, where either one of the negative power source lines and the positive power source lines of the amplifier circuit are connected to the gate scanning line, is used, with a simple construction, the fluctuations in the liquid crystal pixel potential can be suppressed without much decrease in the aperture ratio. However in the case where display is performed with this pixel construction, the following problems arise.

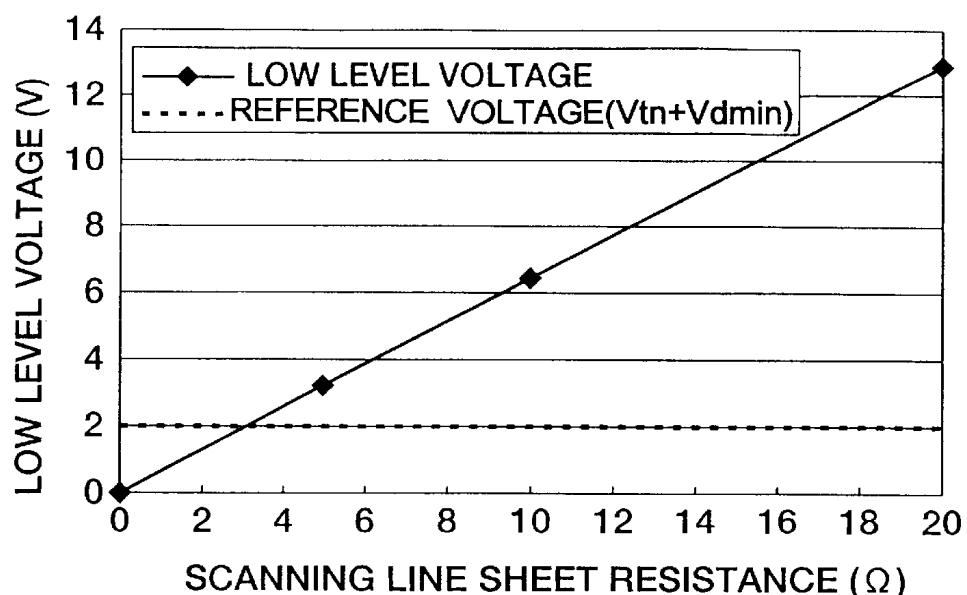

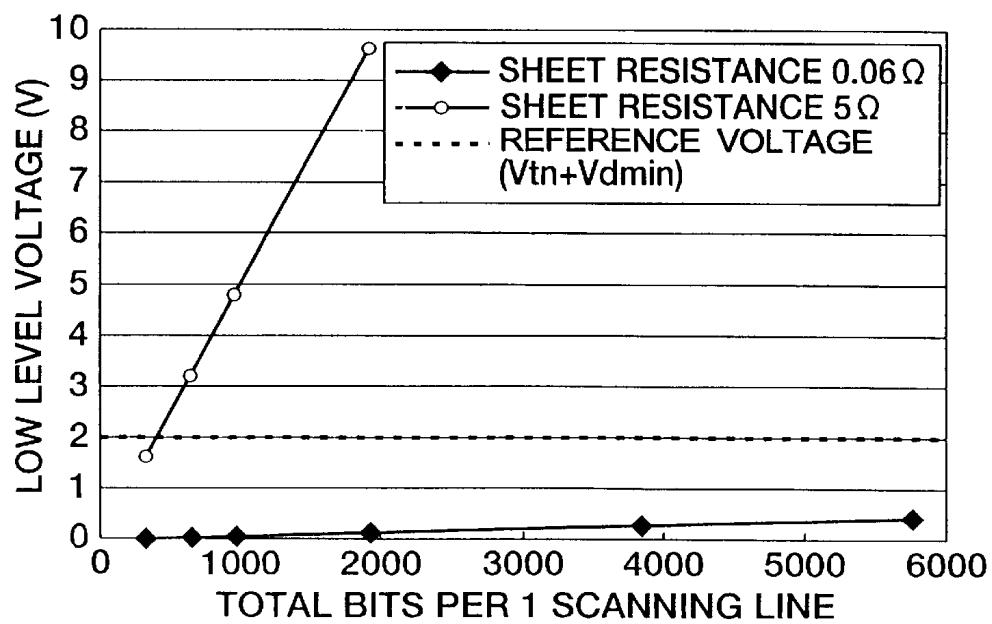

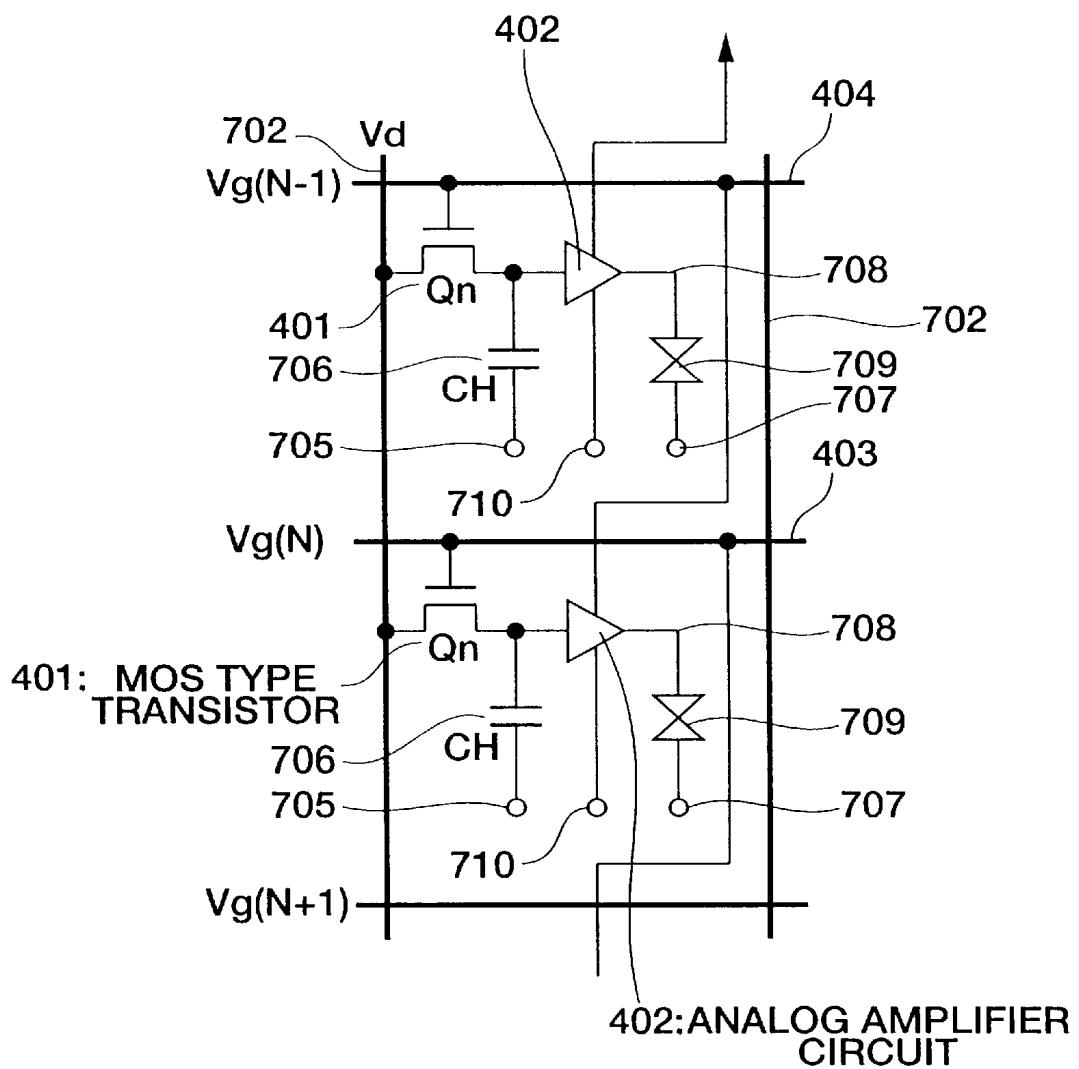

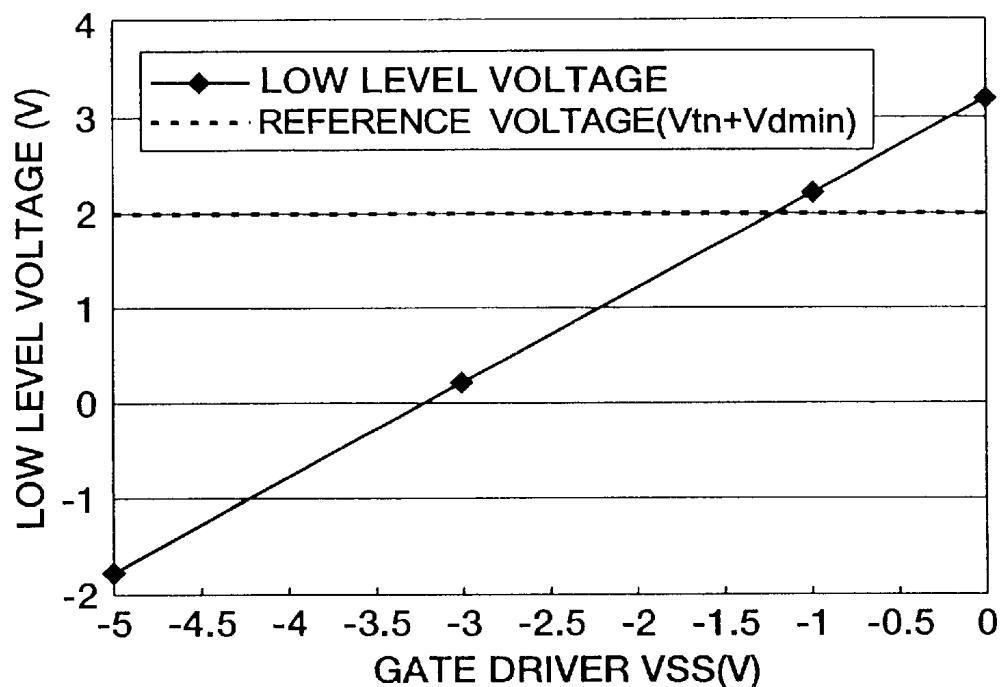

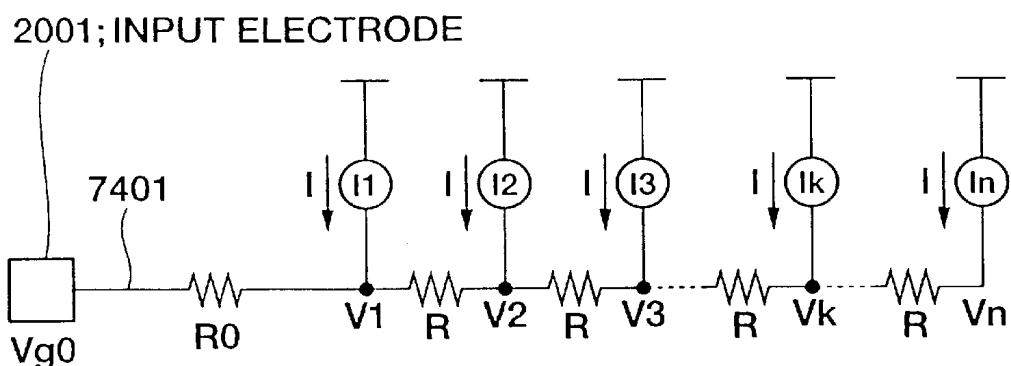

In the conventional pixel construction shown in FIG. 50, all that is connected to the gate scanning line is the gate electrode of the switching transistor (Qn) 551. However, in the construction shown in FIG. 74, a current is continually supplied from the positive power source side of the amplifier to the negative power source side through the analog amplifier circuit 2302. Therefore, when the switching transistor is in the off condition, the potential of the gate scanning line shifts either to positive, for the n-type MOS, with respect to the low level side power source voltage of the gate driver, or to negative, for the p-type MOS, with respect to the high level side power source voltage of the gate driver. Since this potential shift amount increases monotonously with respect to the pixel number, then in a high resolution panel, a problem arises in that the low level of the gate scanning potential exceeds the threshold value of the switching transistor, and pixel selection is no longer normally performed.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide a liquid crystal display device with a long period which can be actually used in the display, and a method for driving the same.

Furthermore, it is another object of the present invention to provide a liquid crystal display device with a high light utilization factor, and a method for driving the same.

Moreover, it is another object of the present invention to provide a liquid crystal display device with simplified linking with a light source, and a method for driving the same.

In addition, it is another object of the present invention to provide a liquid crystal display device where a drive method for the liquid crystal display section and the lighting method for the optical system are synchronized, and a method for driving the same.

Moreover, it is another object of the present invention to provide a liquid crystal display device where, in a pixel constructed with an analog amplifier circuit for suppressing pixel voltage fluctuations during a holding period added thereto, display fluctuations for each of the pixels which are attributable to fluctuations in the amplifier output can be suppressed.

Furthermore, it is another object of the present invention to provide a liquid crystal display device where, in a pixel circuit constructed with an analog amplifier circuit for suppressing pixel voltage fluctuations during a holding

period added thereto, and a power source line of this analog amplifier circuit connected to a gate scanning line, fluctuations in the gate scanning voltage arising as mentioned above can be reduced. Moreover, it is an object to appropriately perform on and off switching of a switching transistor, to suppress fluctuations in the pixel voltage while simplifying the circuit and maintaining a high aperture ratio for the display section. Furthermore, it is an object to be able to use liquid crystal materials having polarization or liquid crystal materials with a low resistivity.

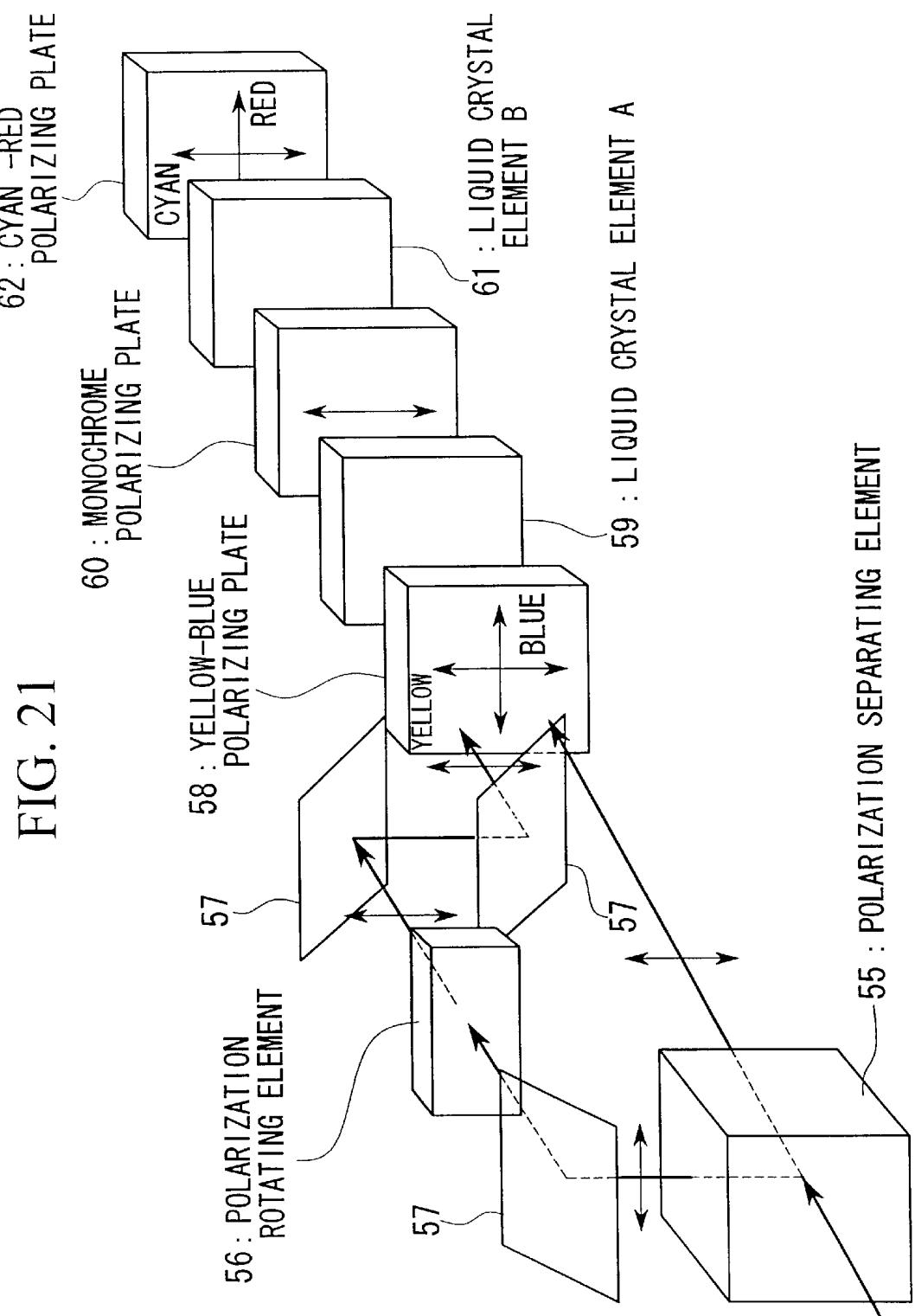

According to the present invention, the above objects are achieved by a liquid crystal display device incorporating a liquid crystal display section having data drive circuits provided along both of two opposite sides of a rectangular display region, and gate drive circuits provided along the other two opposite sides, wherein with the liquid crystal display section, the gate drive circuits are formed severally divided, and each data line group respectively extending from each of the data drive circuits is electrically separated respectively by the severally divided gate drive circuits, and there is provided a color/time division incident optical system arranged so as to sequentially shine light with different chromaticity onto the display region, and a synchronizing section for synchronizing the liquid crystal display section and the color/time division incident optical system under predetermined conditions.

To explain in more detail, the liquid crystal display device has a liquid crystal display section with data drive circuits at both the top and bottom (or the left and right) of the display region, and gate drive circuits at the left or right (or the top and bottom) of the display region. In the liquid crystal display section, each data line group respectively extending from each data drive circuit, is electrically separated at the top and bottom (or the left and right) of the display region. Furthermore, the gate drive circuits are formed divided into top and bottom (or left and right). Moreover, the color/time division incident optical system is arranged so as to sequentially shine light with different chromaticity onto the display region. The liquid crystal display section and the color/time division incident optical system are synchronized by the synchronizing section under predetermined conditions.

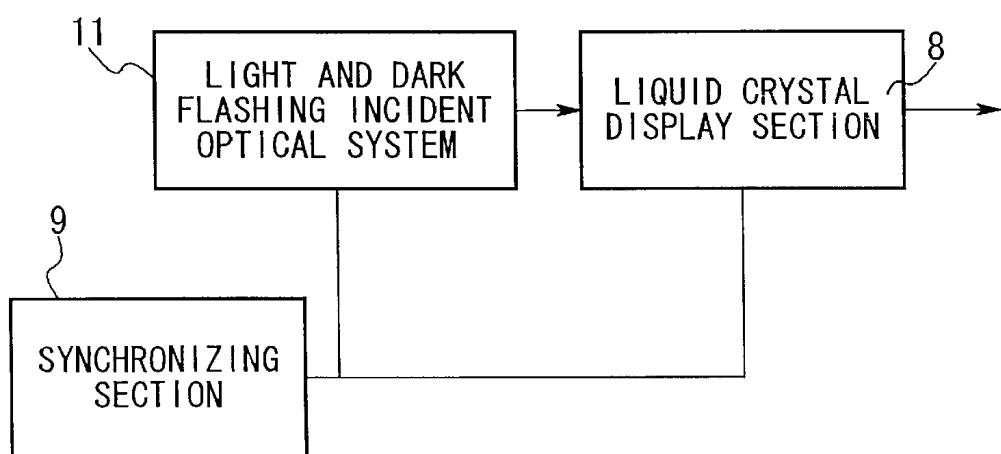

Moreover, with the present invention, the above objects are achieved by a liquid crystal display device incorporating a liquid crystal display section having data drive circuits provided along both of two opposite sides of a rectangular display region, and gate drive circuits provided along the other two opposite sides of the rectangular display region, wherein with the liquid crystal display section, the gate drive circuits are formed severally divided, and each data line group respectively extending from each of the data drive circuits is electrically separated respectively by the severally divided gate drive circuits, and there is provided a light and dark flashing incident optical system arranged so that flashing light (light and dark light) between dark states of a fixed period is shone onto the display region, and a synchronizing section for synchronizing the liquid crystal display section and the light and dark flashing incident optical system under predetermined conditions.

To explain in more detail, the liquid crystal display device has a liquid crystal display section with data drive circuits at both the top and bottom (or the left and right) of the display region, and gate drive circuits at the left or right (or the top and bottom) of the display region. In the liquid crystal display section, each data line group respectively extending from each data drive circuit, is electrically separated at the top and bottom (or the left and right) of the display region. Furthermore, the gate drive circuits are formed divided into

top and bottom (or left and right). Moreover, the light and dark flashing incident optical system is arranged so that flashing light (light and dark light) between dark states of a fixed period is shone onto the display region. The liquid crystal display section and the light and dark flashing incident optical system are synchronized by the synchronizing section under predetermined conditions.

Moreover, with the present invention, the above objects are achieved by a drive method for a liquid crystal display device for driving the liquid crystal display device mentioned above, wherein reset is performed en bloc in each of the gate drive circuits. That is, the feature is that reset is performed en bloc in each of the gate drive circuits.

In the above manner, in the case where the power source is an en bloc lighting type, the scanning of each gate drive circuit block is started at approximately the same time. Consequently, the result is obtained in that a liquid crystal display device with a long period which can be used in the display is realized.

Furthermore, since the display period can be lengthened, and the liquid crystal display device and the light source can be linked by devising the drive method, there is the result that a liquid crystal display device is obtained with a high light utilization factor.

Moreover, with the invention, since the drive circuit is divided and the respective drive circuit units are miniaturized, this gives the result that a low cost simple construction drive circuit can be used.

Furthermore, with the invention, since the synchronization of the drive method for the light source is optimized, there is the result that an extremely high resolution picture display is obtained.

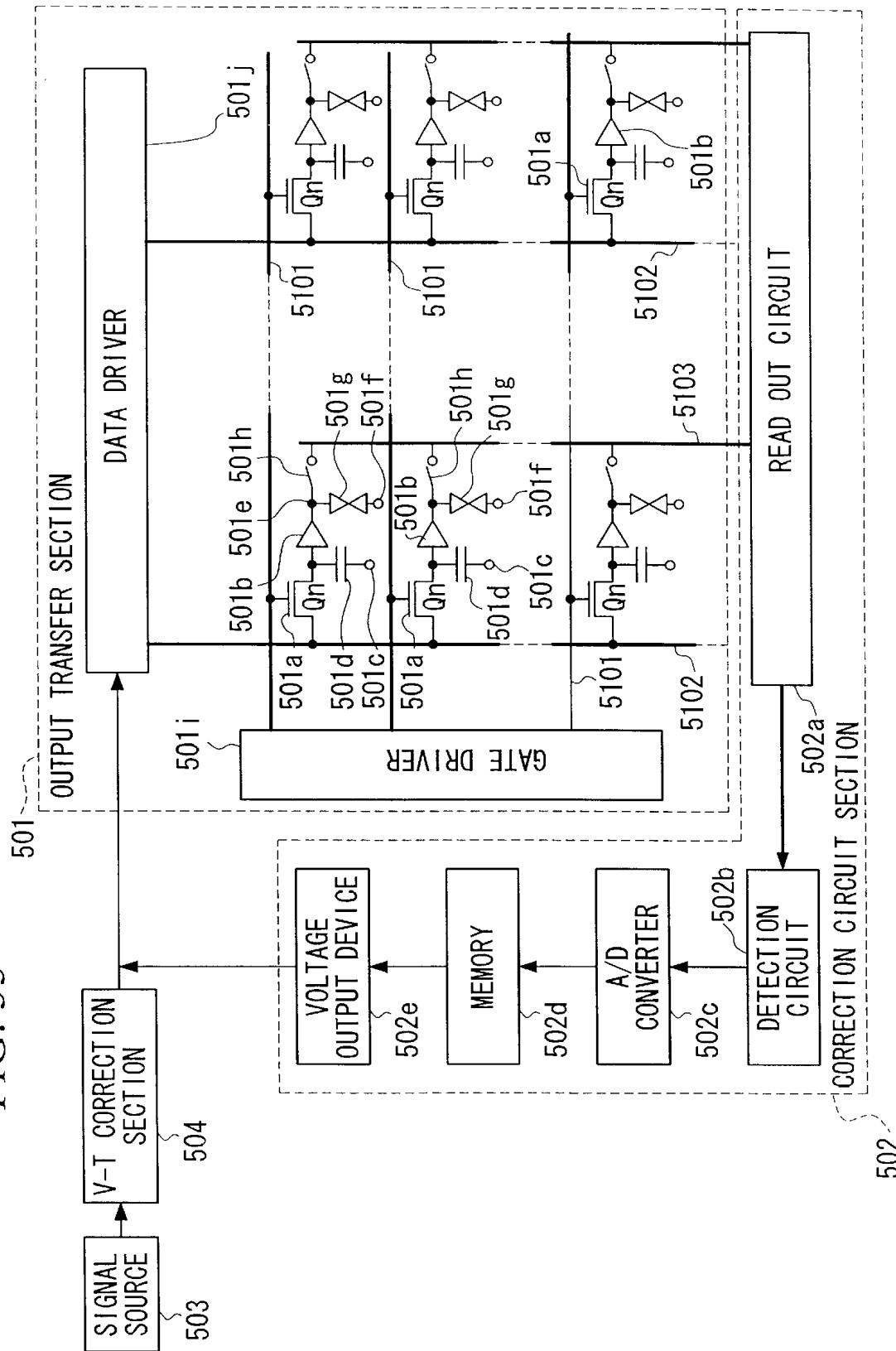

Moreover, with the invention, the above objects are achieved by a liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, the device incorporating; a detection device for detecting the output of the amplifier output transfer function for all bits, and a compensation device for performing output compensation on the amplifier output transfer function for each pixel, based on the detection results of the detection device.

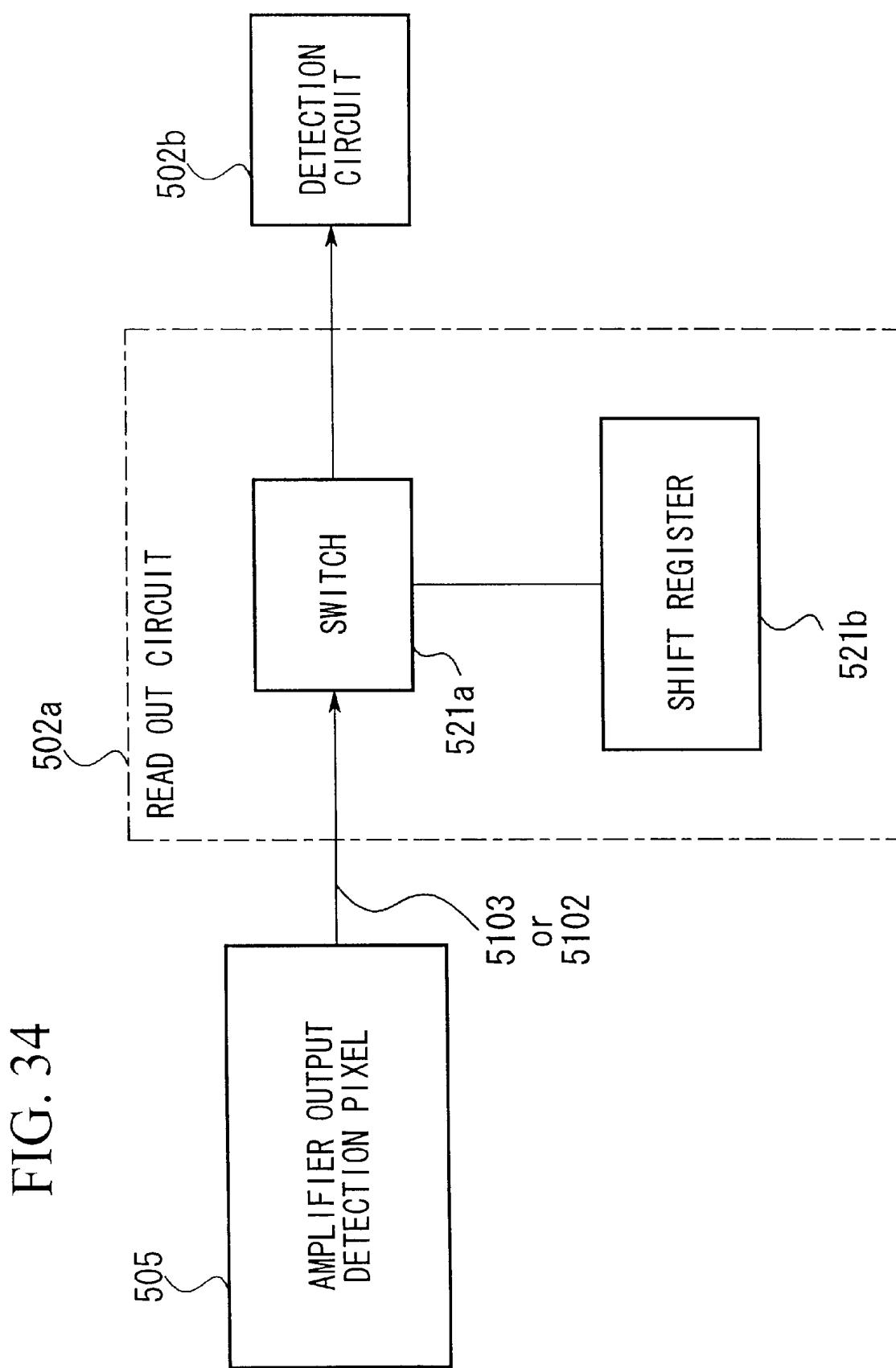

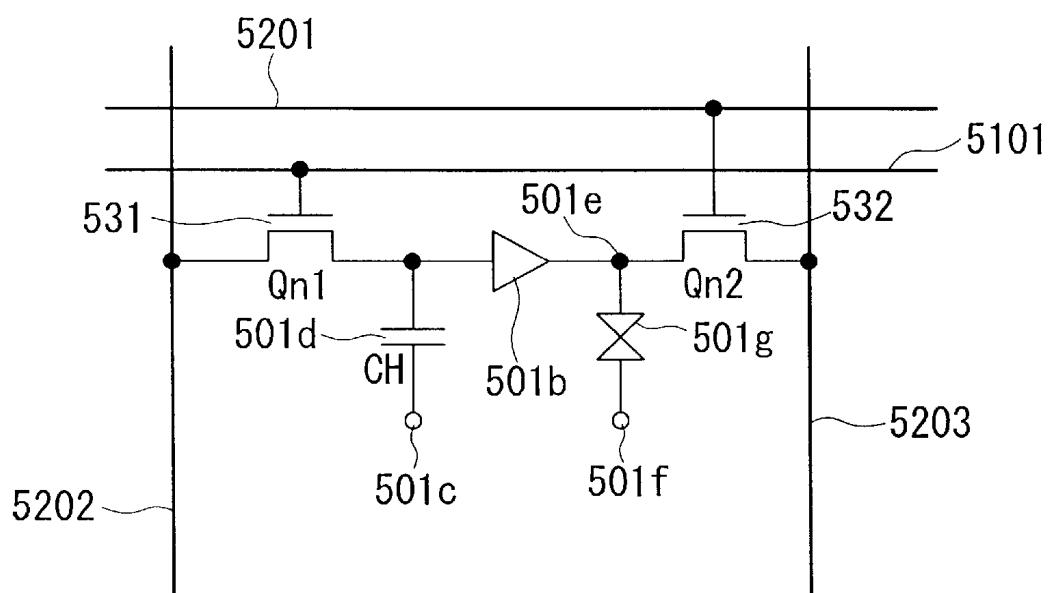

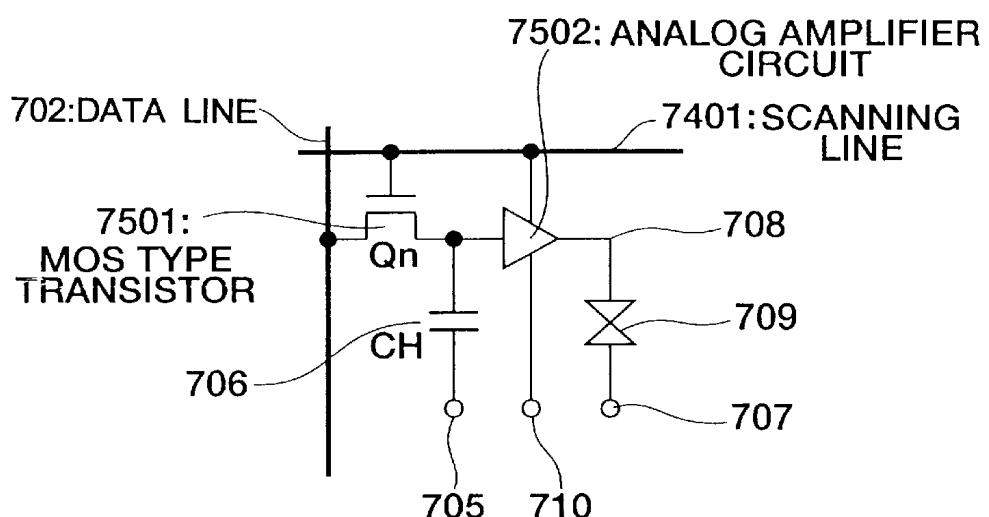

That is to say, with the liquid crystal display device described above, in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, a MOS type transistor circuit is formed from: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; and a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line.

Moreover, with the liquid crystal display device described above, in the above construction there is provided; a detection device for detecting a difference of a reference voltage with respect to an amplifier output voltage which has been

## 13

transferred in a predetermined sequence by the read out circuit through an amplifier monitor line or a data line, a memory for storing the difference voltage, and a voltage generating device for applying a compensation voltage based on the memory data, to an input image signal.

Furthermore, with the invention, the above objects are achieved by a liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, wherein the MOS type transistor circuits comprise: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; and a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to one of an amplifier monitor line and the data line, and has: a read out circuit for reading out an output voltage of the analog amplifier circuit through one of the amplifier monitor line and data line, a detection circuit for detecting a difference between an output voltage from the analog amplifier circuit which has been transferred in a predetermined sequence by the read out circuit, and a previously set reference voltage; a conversion device for converting the difference voltage from the detection circuit into digital data; a memory for storing the difference voltage which had been digitized; and a voltage generating device for applying a compensation voltage corresponding to the storage data of the memory, to an input image signal.

That is to say, with the liquid crystal display device described above, in the aforementioned construction, in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, a MOS type transistor circuit is formed from: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; and a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line.

Moreover, with the liquid crystal display device described above, in the above construction a feature is that one end of the amplifier monitor line constitutes a terminal electrode whereby measurement is possible by an external measuring device. Furthermore, with a second liquid crystal display device of the present invention, in the above construction, there is provided a non volatile memory for storing difference voltages detected by the external measuring device, and a voltage generating device for applying a compensation voltage based on data of the non volatile memory, to the input image signal.

With the aforementioned liquid crystal display device, the output from the analog amplifier circuit which is actually

## 14

used in the pixel is detected for all bits, and based on this output value, output compensation for the analog amplifier circuit for each pixel is performed. Therefore, a decrease in image quality attributable to characteristic differences in the analog amplifier circuit does not arise.

Furthermore, with the invention, the above objects are achieved by an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, wherein the MOS type transistor circuits comprise: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; and a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to one of an amplifier monitor line and the data line, and incorporate: a terminal electrode connected to the end of one of the amplifier monitor line and the data line, for outputting an output from the MOS type analog amplifier circuit to the outside; a memory for storing the output voltage data from the MOS type analog amplifier circuit which has been measured outside; and a voltage generating device for applying a compensation voltage corresponding to the storage data of the memory, to an input image signal.

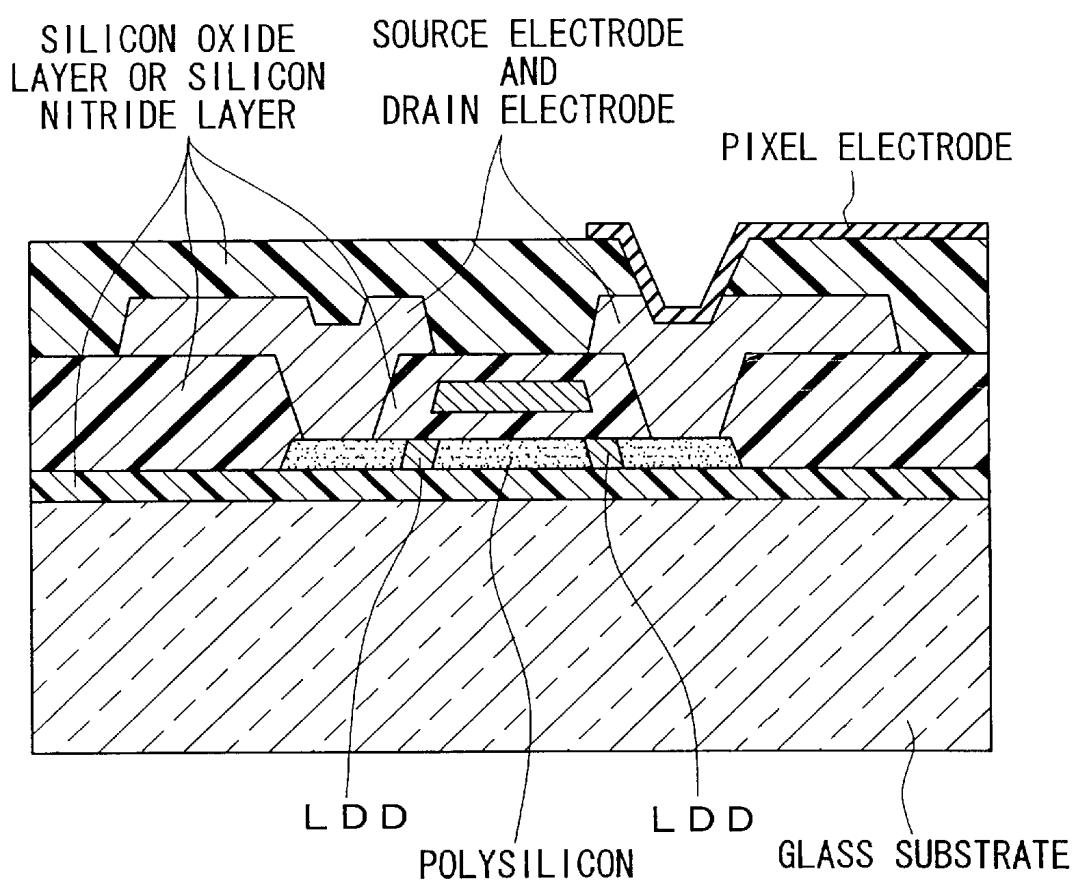

That is to say, the above described liquid crystal display device is characterized in that in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been crystallized or recrystallized by laser annealing, and at the time of the laser annealing the scanning direction of the laser is parallel to or at an angle substantially the same as the scanning line, apart from display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; there are amplifier output detection pixels formed on a scanning line of a screen edge portion.

With the amplifier output detection pixel, in the construction of the display pixel, a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line, is added.

Moreover, with the liquid crystal display device described above, in the above construction there is provided; a detection device for detecting a difference of a reference voltage with respect to an amplifier output voltage which has been transferred in a predetermined sequence by the read out circuit through an amplifier monitor line or a data line, a memory for storing the difference voltage, and a voltage generating device for applying a compensation voltage based on the memory data, to an input image signal.

15

Furthermore, according to the invention, the object is achieved by a liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been subjected to either of crystallizing and recrystallizing by laser annealing, and at the time of the laser annealing the laser is scanned substantially parallel with the scanning line, the device incorporating: a detection device for detecting the output of the amplifier output transfer function, and a compensation device for performing output compensation on the amplifier output transfer function only with respect to the laser scanning direction at the time of the laser annealing, based on the detection results of the detection device; and a voltage generating device for applying a compensation voltage based on data of the non volatile memory, to the input image signal.

That is to say, with the described liquid crystal display device, the object is achieved with a liquid crystal display device where, in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been crystallized or recrystallized by laser annealing, and at the time of the laser annealing the scanning direction of the laser is parallel to or at an angle substantially the same as the scanning line, apart from display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; there are amplifier output detection pixels formed on a scanning line of a screen edge portion.

With the amplifier output detection pixel, in the construction of the display pixel, a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line, is added. Moreover one end of the amplifier monitor line becomes a terminal electrode whereby measurement is possible by an external measuring device.

Moreover, with the liquid crystal display device described above, in the above construction there is provided a non volatile memory for storing difference voltages detected by the external measuring device, and a voltage generating device for applying a compensation voltage based on data of the non volatile memory, to the input image signal.

Moreover, according to the invention the objects are achieved by a liquid crystal display device being a liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been subjected to either of crystallizing and recrystallizing by laser annealing,

16

and at the time of the laser annealing the laser is scanned substantially parallel with the scanning line, and the device incorporates: display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; amplifier output detection pixels where a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to one of an amplifier monitor line and the data line is added to the construction of the display pixels; a read out circuit for reading out an output voltage of the MOS type analog amplifier circuit of the amplifier output detection pixels through one of the amplifier monitor line and data line; a detection circuit for detecting a difference between an output voltage from the MOS type analog amplifier circuit which has been transferred in a predetermined sequence by the read out circuit, and a reference voltage; a conversion device for converting the difference voltage from the detection circuit into digital data; a memory for storing the difference voltage which had been digitized by the conversion device; and a voltage generating device for applying a compensation voltage corresponding to the storage data of the memory, to an input image signal.

That is to say, the above described liquid crystal display device is characterized in that, in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been crystallized or recrystallized by laser annealing, and at the time of the laser annealing the scanning direction of the laser is parallel to or at an angle substantially the same as the data line, apart from display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; there are amplifier output detection pixels formed on a data line of a screen edge portion.

With the amplifier output detection pixel, in the construction of the display pixel, a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line, is added.

Moreover, with the liquid crystal display device described above, in the above construction there is provided; a detection device for detecting a difference of a reference voltage with respect to an amplifier output voltage which has been transferred in a predetermined sequence by the read out circuit through an amplifier monitor line or a data line, a memory for storing the difference voltage, and a voltage generating device for applying a compensation voltage based on the memory data, to an input image signal.

Furthermore, according to the invention, the object is achieved by a liquid crystal display device where with a

liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been subjected to either of crystallizing and recrystallizing by laser annealing, and at the time of the laser annealing the laser is scanned substantially parallel with the scanning line, the device incorporates: display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; amplifier output detection pixels where a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to one of an amplifier monitor line and the data line is added to the construction of the display pixels; a terminal electrode connected to the end of one of the amplifier monitor line and the data line, for outputting an output from the MOS type analog amplifier circuit of the amplifier output detection pixel to the outside; a memory for storing the output voltage data from the MOS type analog amplifier circuit which has been measured outside; and a voltage generating device for applying a compensation voltage corresponding to the storage data of the memory, to an input image signal.

That is to say, the above described liquid crystal display device is characterized in that in that, in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been crystallized or recrystallized by laser annealing, and at the time of the laser annealing the scanning direction of the laser is parallel to or at an angle substantially the same as the data line, apart from display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; there are amplifier output detection pixels formed on a data line of a screen edge portion.

With the amplifier output detection pixel, in the construction of the display pixel, a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line, is added. Moreover one end of the amplifier monitor line becomes a terminal electrode whereby measurement is possible by an external measuring device.

Moreover, with the liquid crystal display device described above, in the above construction there is provided a non volatile memory for storing difference voltages detected by the external measuring device, and a voltage generating

device for applying a compensation voltage based on data of the non volatile memory, to the input image signal.

Furthermore, according to the above described liquid crystal display device, when a p-Si transistor comprising a thin film semiconductor layer which has been crystallized or re-crystallized by laser annealing is used, then by performing compensation of the amplifier output only with respect to the laser scanning direction for which difference in transistor characteristic are likely to occur, effective compensation can be made with a small scale compensation circuit.

Moreover, according to the invention, the object is achieved by a liquid crystal display device where with a liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and where a semiconductor layer of the MOS type transistor circuits is a thin film semiconductor layer which has been subjected to either of crystallizing and recrystallizing by laser annealing, and at the time of the laser annealing the laser is scanned substantially parallel with the data line, the device incorporates: display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; amplifier output detection pixels where a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to one of an amplifier monitor line and the data line is added to the construction of the display pixels; a terminal electrode connected to the end of one of the amplifier monitor line and the data line, for outputting an output from the MOS type analog amplifier circuit of the amplifier output detection pixel to the outside; a memory for storing the output voltage data from the MOS type analog amplifier circuit which has been measured outside; and a voltage generating device for applying a compensation voltage corresponding to the storage data of the memory, to an input image signal.

That is to say, the liquid crystal display device described above is characterized in comprising, in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; and amplifier output detection pixels multiply provided at at least four points on an external edge portion of a screen.

With the amplifier output detection pixel, in the construction of the display pixel, a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line, is added.

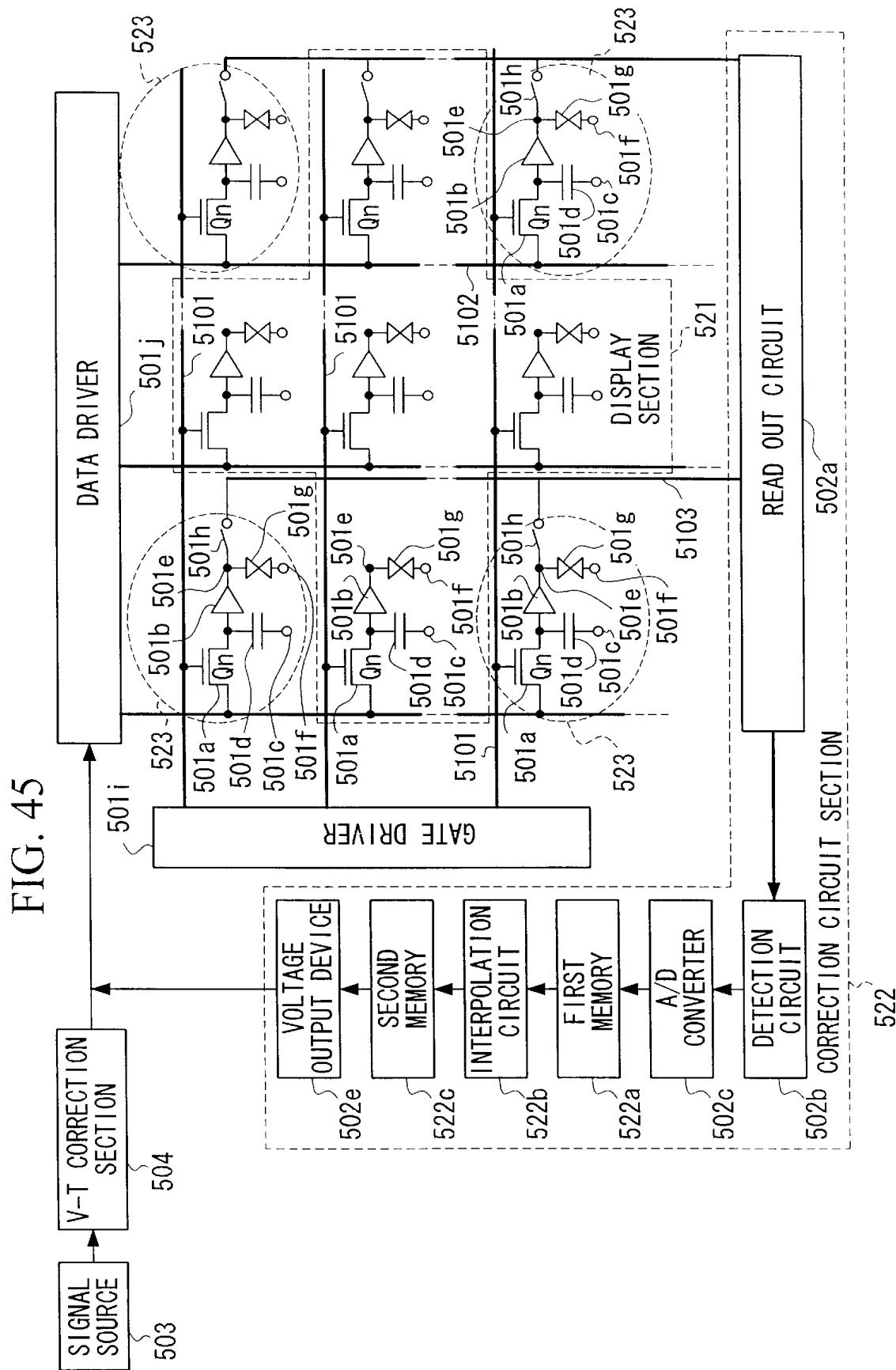

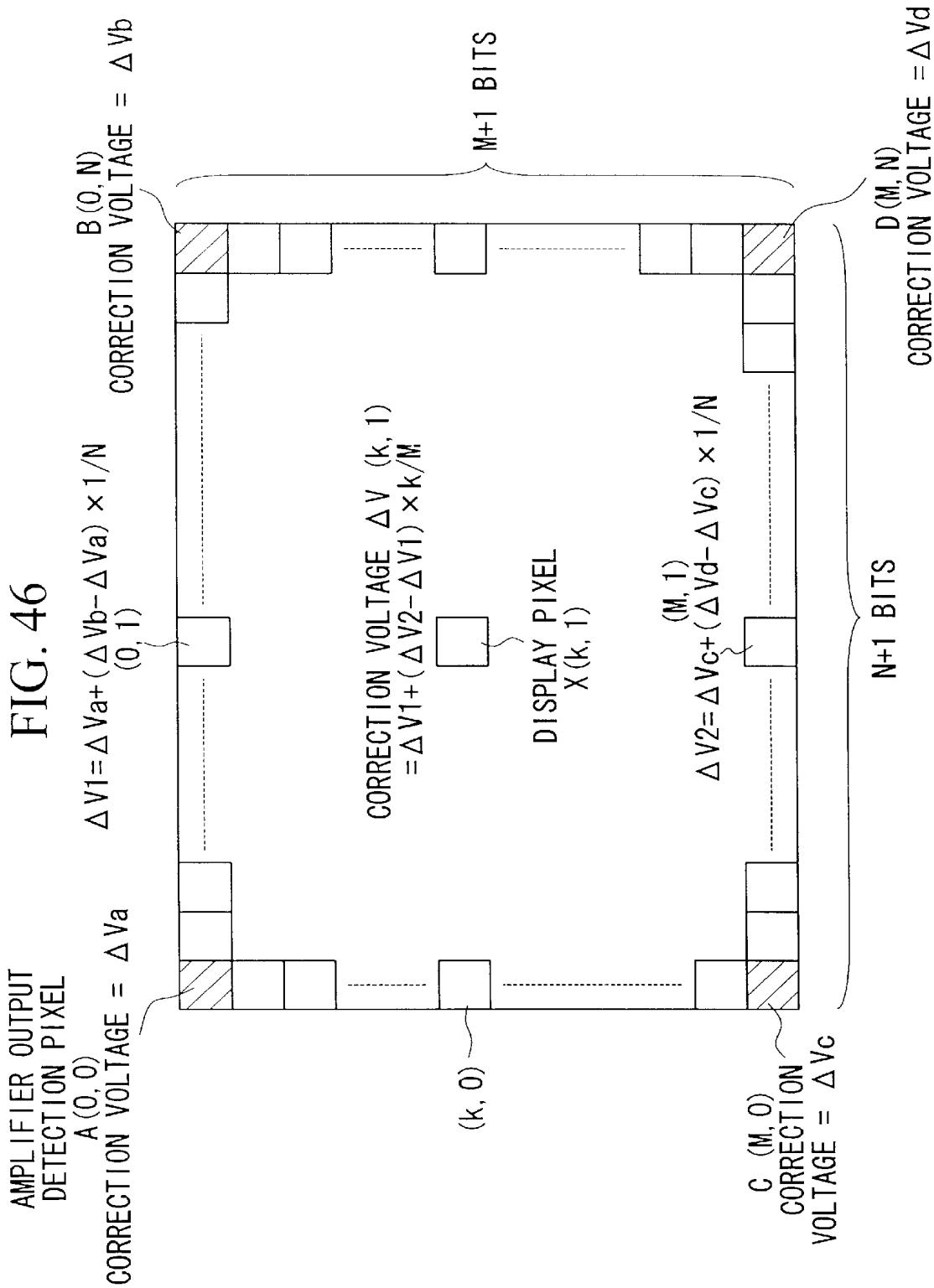

Moreover, with the liquid crystal display device described above, in the above construction there is provided; a detection device for detecting a difference of a reference voltage with respect to an amplifier output voltage which has been transferred in a predetermined sequence by the read out circuit through an amplifier monitor line or a data line; a first memory for storing the difference voltage; an interpolation circuit for computing compensation voltages for all bits from data of the first memory; a second memory for storing compensation voltages computed by the interpolation circuit; and a voltage generating device for applying a compensation voltage based on the second memory data, to an input image signal.

Furthermore according to the invention, the objects are achieved by a liquid crystal display device for driving pixel electrodes using MOS type transistor circuits incorporating an amplifier output transfer function and respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, and incorporating; a detection device for detecting the output of the amplifier output transfer function for a predetermined bit set beforehand, and a compensation device which performs linear interpolation processing between pixels for which detection of the output of the amplifier output transfer function has been performed, based on the detection results of the detection device.

That is to say, the liquid crystal display device described above is characterized in comprising, in an active matrix liquid crystal display device for driving pixel electrodes using MOS type transistor circuits respectively disposed in the vicinity of respective intersection points of a plurality of scanning lines and a plurality of data lines, display pixels each comprising: a MOS transistor with a gate electrode connected to the scanning line and one of a source electrode and a drain electrode connected to the data line; a MOS type analog amplifier circuit with an input electrode connected to the other of the source electrode and the drain electrode of the MOS type transistor, and an output electrode connected to a pixel electrode; and a voltage holding capacitor formed between the input electrode of the MOS type analog amplifier circuit and a voltage holding capacitor electrode; amplifier output detection pixels multiply provided at at least four points on an external edge portion of a screen.

With the amplifier output detection pixel, in the construction of the display pixel, a switch with an input electrode connected to an output electrode of the MOS type analog amplifier circuit and an output electrode connected to an amplifier monitor line or the data line, is added. Moreover one end of the amplifier monitor line becomes a terminal electrode whereby measurement is possible by an external measuring device.

Moreover, with the liquid crystal display device described above, in the above construction there is provided a non volatile memory for storing amplifier output compensation voltages for all bits, which have been obtained by interpolation of difference voltages detected by the external measuring device and the aforementioned difference voltage, and a voltage generating device for applying a compensation voltage based on data of the non volatile memory, to an input image signal. In this case, linear interpolation is performed by selecting the four points of the amplifier output detection pixels closest to the bit for which the compensation voltage is computed.

Furthermore, according to the above described liquid crystal display device, in the case where amplifier output detection is not performed for all of the bits, by performing

linear interpolation processing between pixels for which amplifier output detection has been performed, the compensation accuracy is improved, thus still enabling effective compensation to be made with a small scale circuit construction.

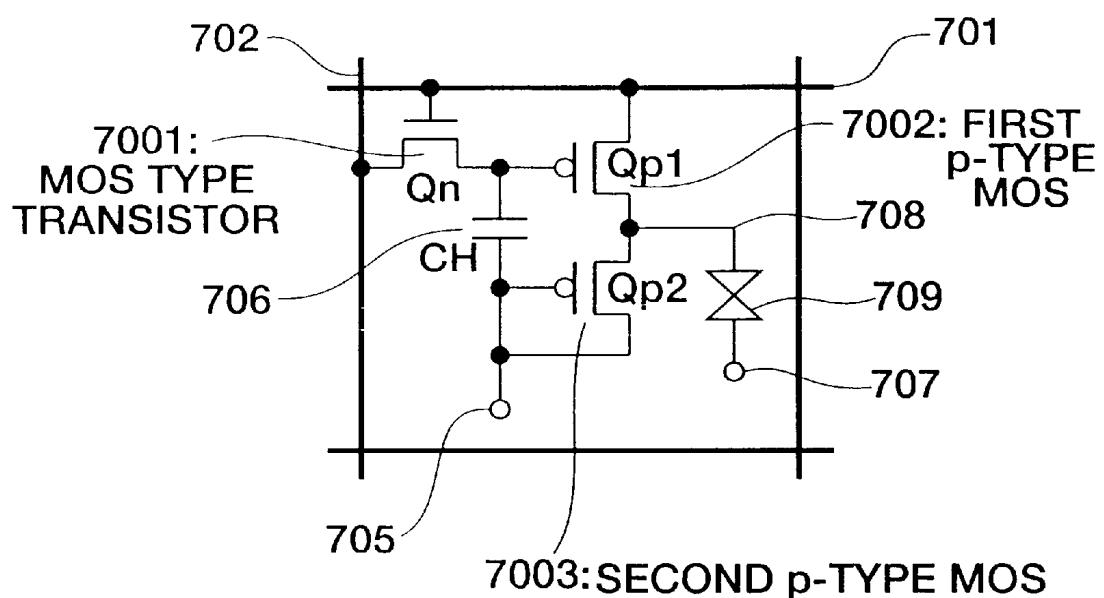

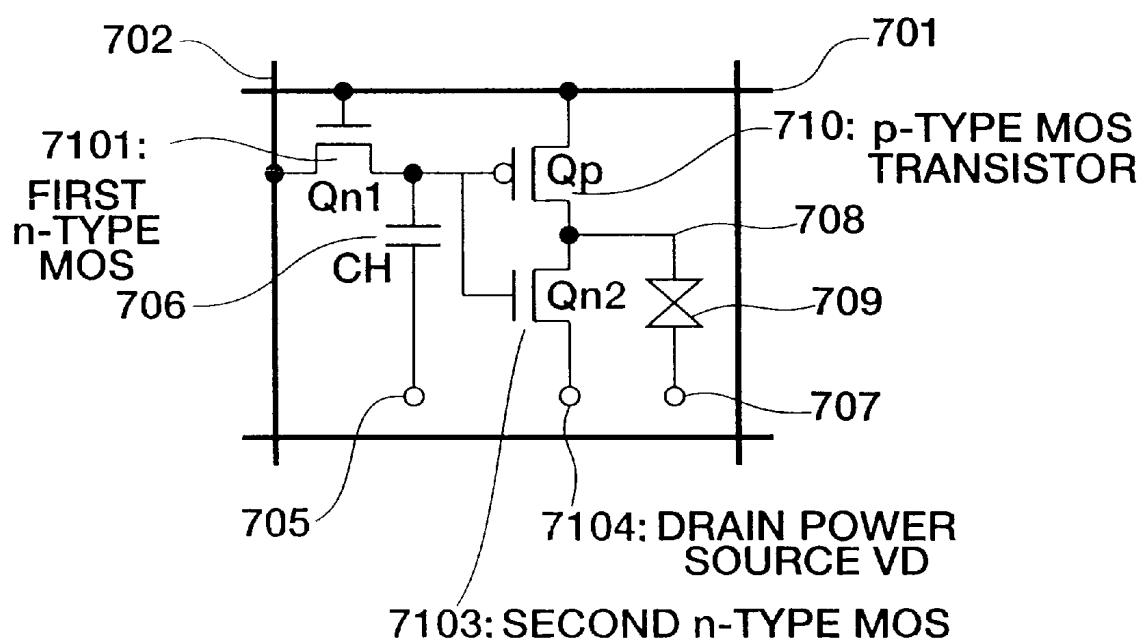

In addition, by making the memory for storing compensation voltages a non volatile memory, and using an external measuring device for one part of the detection process, then the circuit construction for the compensation from detection of the amplifier output can be simplified.