US 20050175792A1

(19) **United States**

(12) **Patent Application Publication**

Maeda et al.

(10) **Pub. No.: US 2005/0175792 A1**

(43) **Pub. Date: Aug. 11, 2005**

(54) **LIQUID CRYSTAL DISPLAY PANEL HAVING REFLECTION ELECTRODES IMPROVED IN SMOOTH SURFACE MORPHOLOGY AND PROCESS FOR FABRICATION THEREOF**

(76) Inventors: **Akitoshi Maeda, Tokyo (JP); Atsushi Yamamoto, Akita (JP); Tomohide Shindoh, Akita (JP)**

Correspondence Address:

**DICKSTEIN SHAPIRO MORIN & OSHINSKY LLP

1177 AVENUE OF THE AMERICAS (6TH AVENUE)

41 ST FL.

NEW YORK, NY 10036-2714 (US)**

(21) Appl. No.: **11/105,418**

(22) Filed: **Apr. 14, 2005**

#### **Related U.S. Application Data**

(63) Continuation of application No. 10/106,378, filed on Mar. 27, 2002.

#### **(30) Foreign Application Priority Data**

Mar. 29, 2001 (JP) ..... 2001-95824

Feb. 7, 2002 (JP) ..... 2002-30472

#### **Publication Classification**

(51) **Int. Cl. 7 ..... C09K 19/00**

(52) **U.S. Cl. ..... 428/1.3**

#### **(57) ABSTRACT**

A liquid crystal display panel of the type having reflection electrodes tends to have an image-forming plane undesirably yellowed due to the wavelength dependency of transparency observed in an orientation layer on the reflection electrodes; aluminum-neodymium alloy, which has neodymium content between 5 weight % to 10 weight %, is deposited on an inter-layered insulating layer at the substrate temperature equal to or less than 170 degrees in centigrade for the reflection electrodes so that the surface morphology is represented by average pitches equal to or less than 1 micron; even though the orientation layer has the wavelength dependency of transparency, the reflection electrodes make the optical path in the orientation layer equalized so that the image-forming plane is not yellowed.

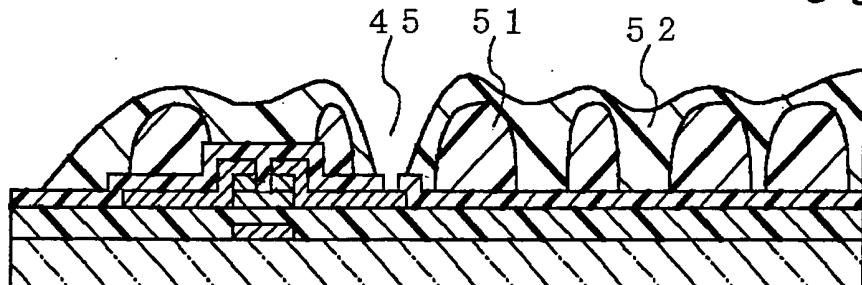

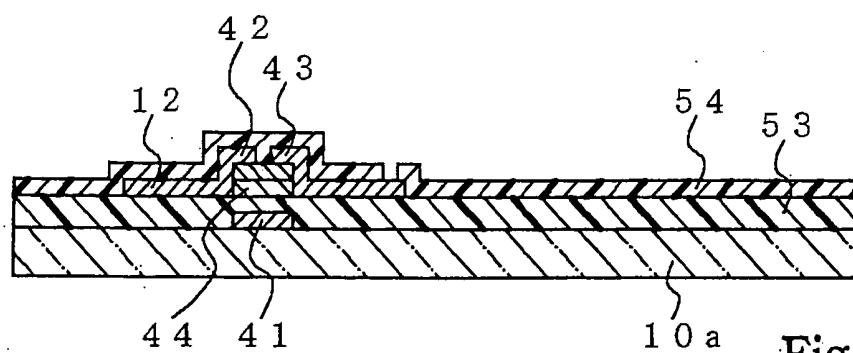

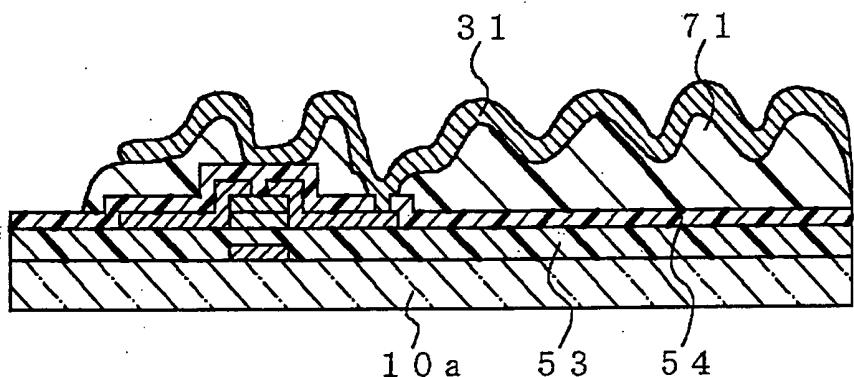

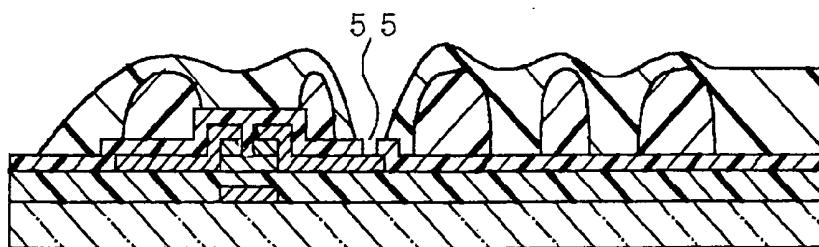

Fig. 1

PRIOR ART

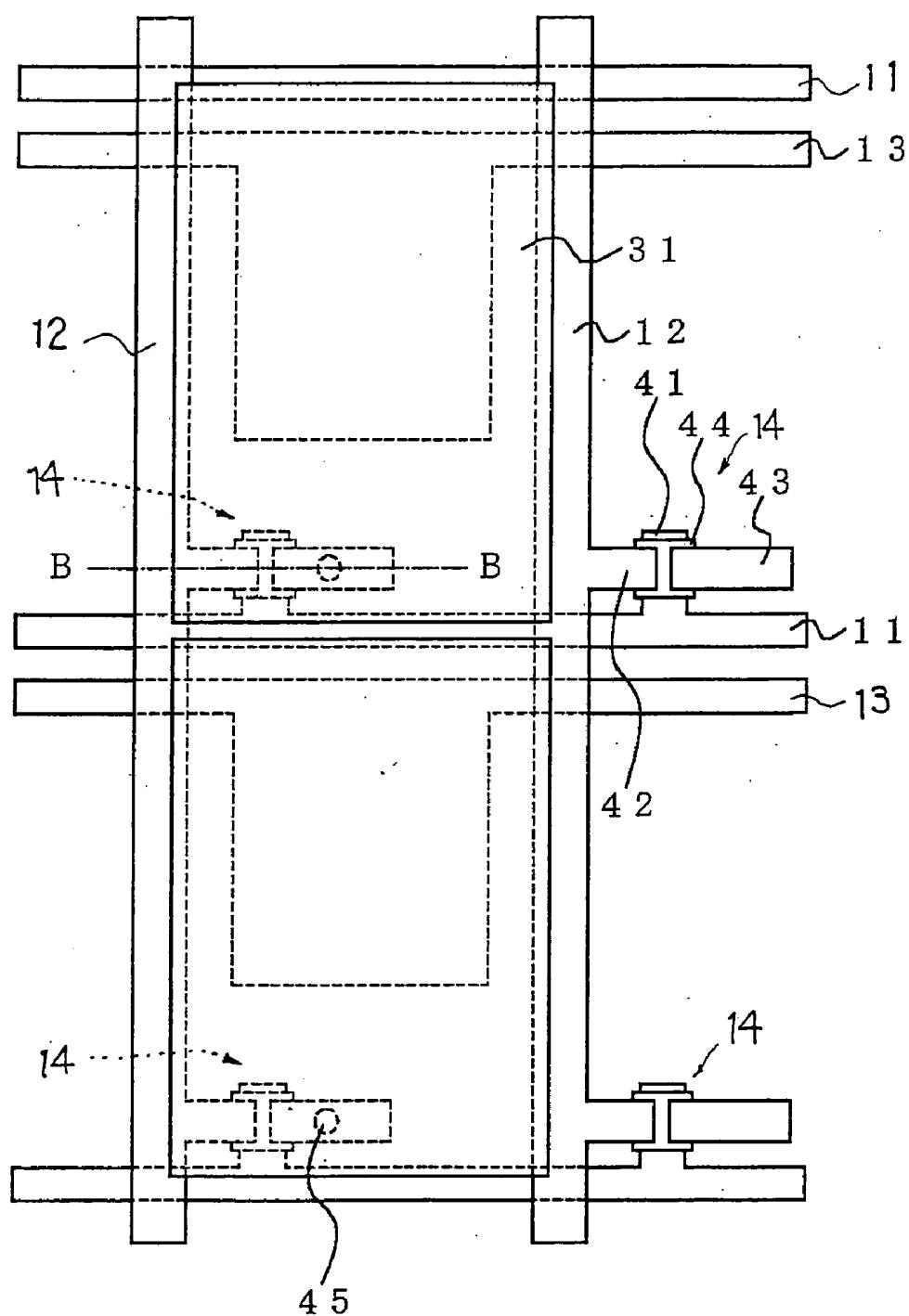

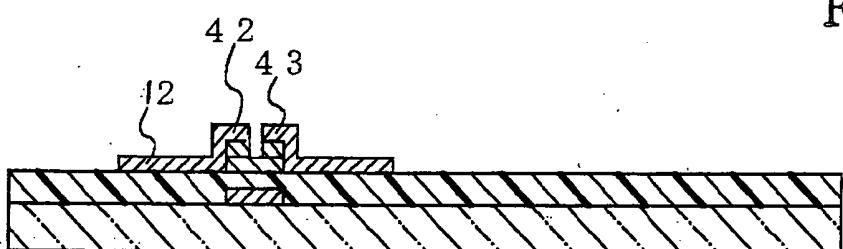

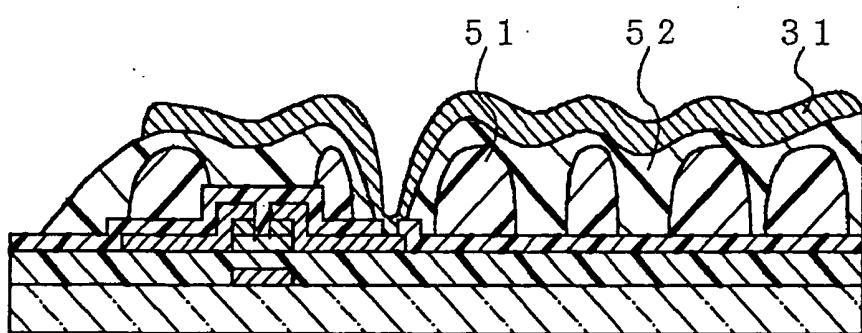

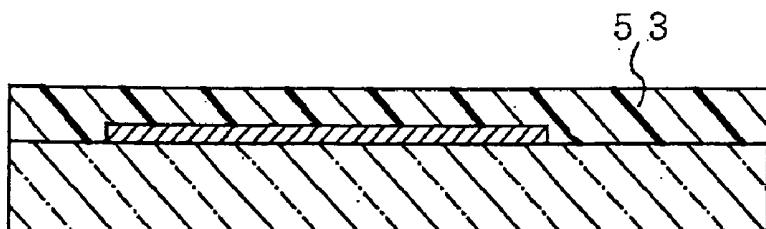

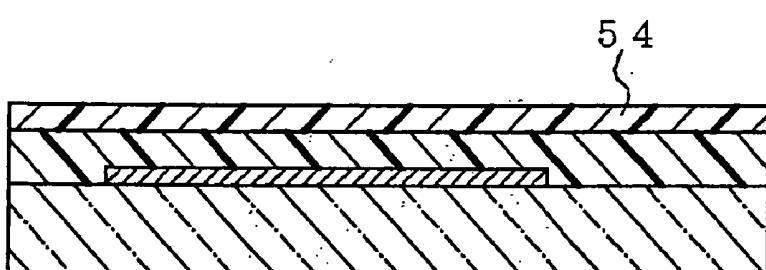

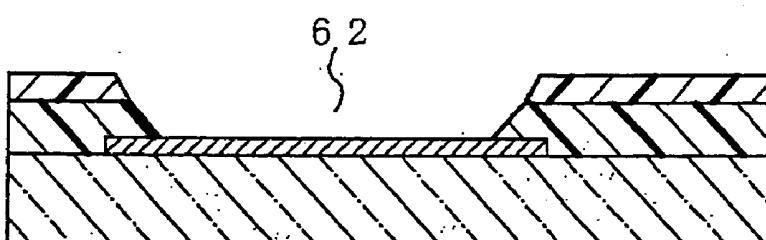

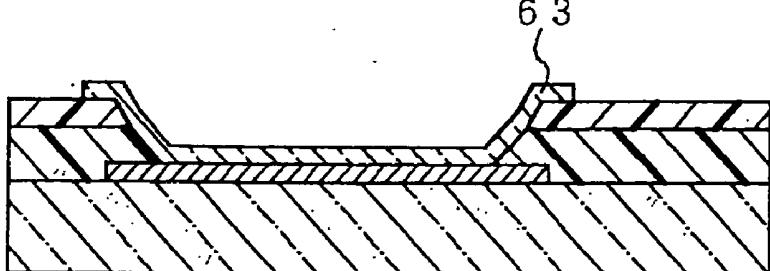

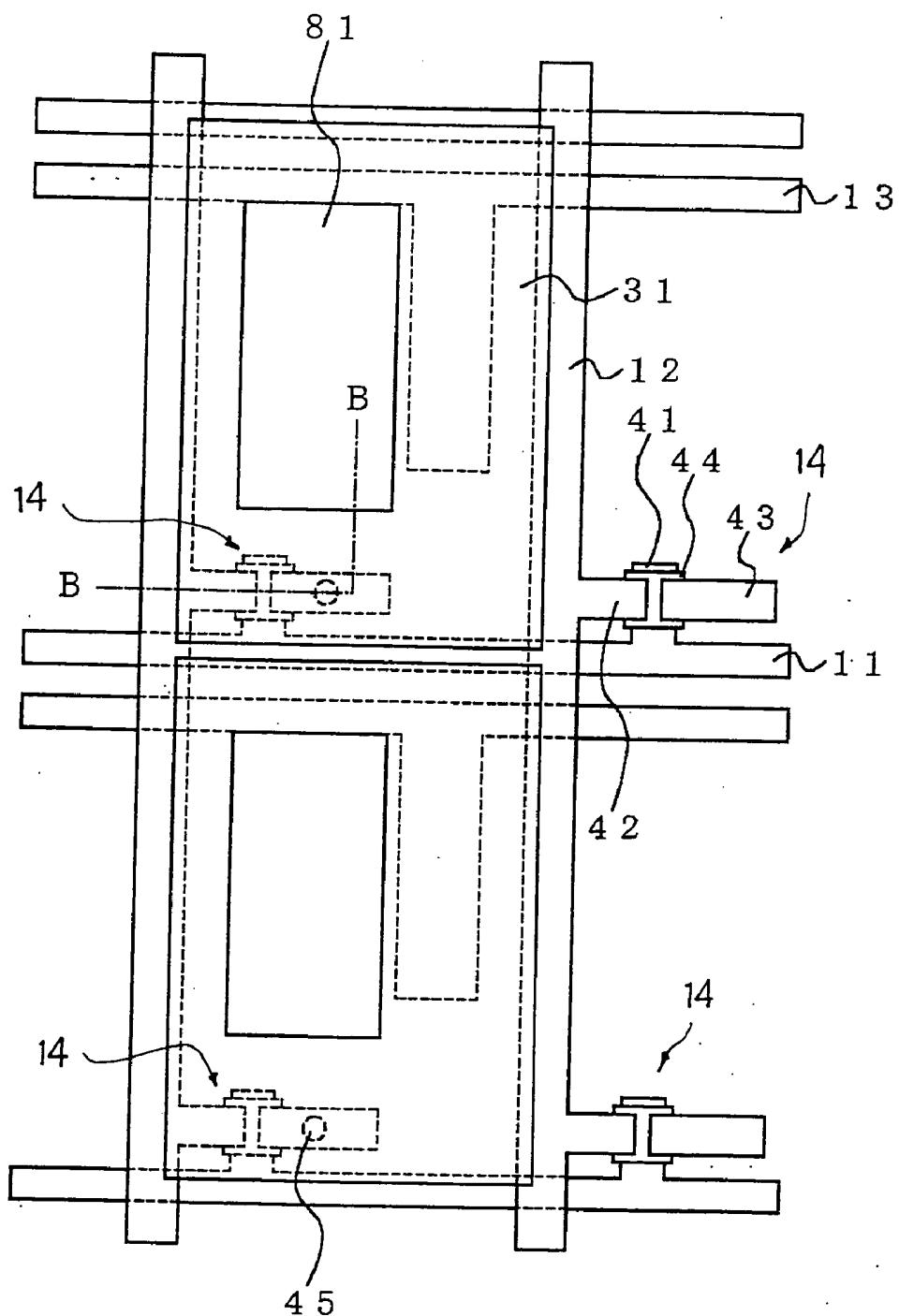

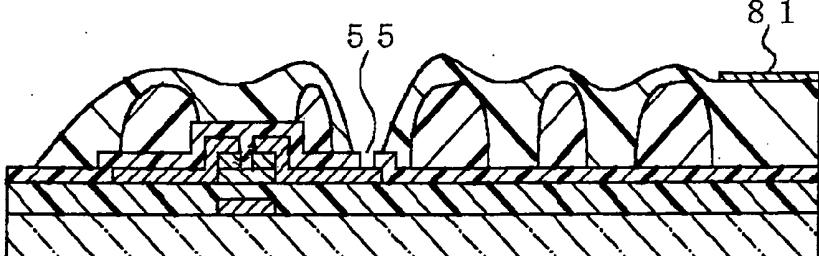

Fig. 2

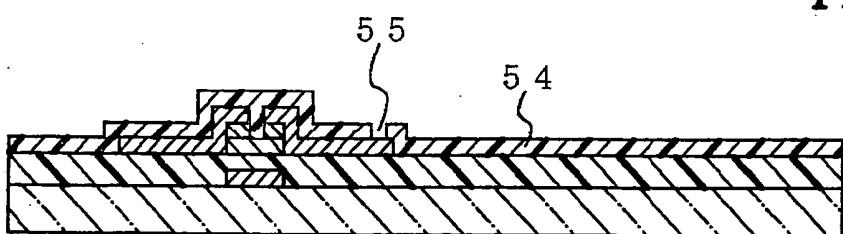

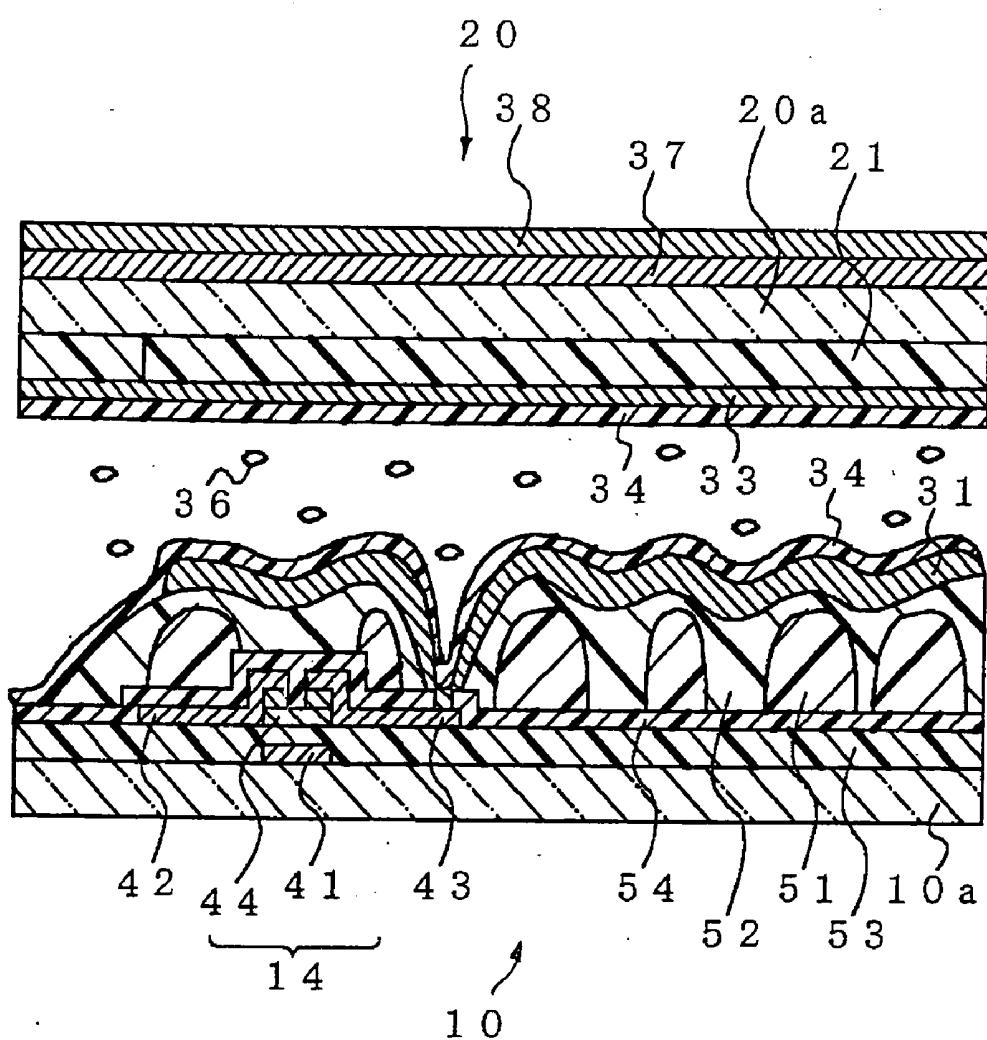

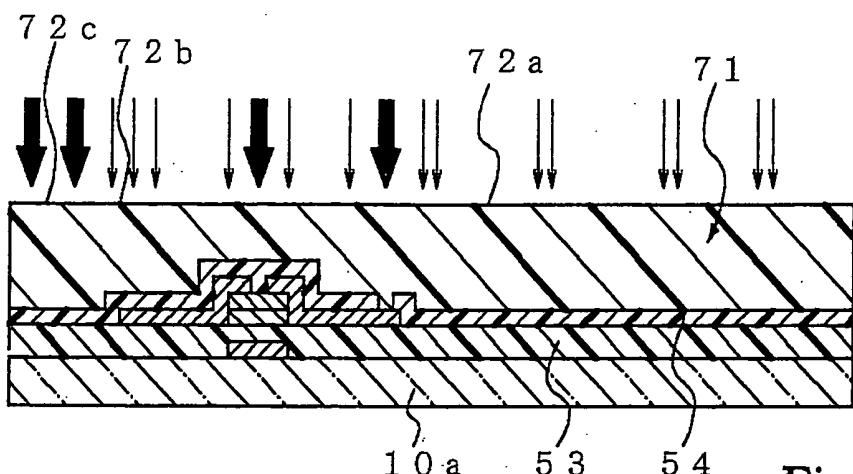

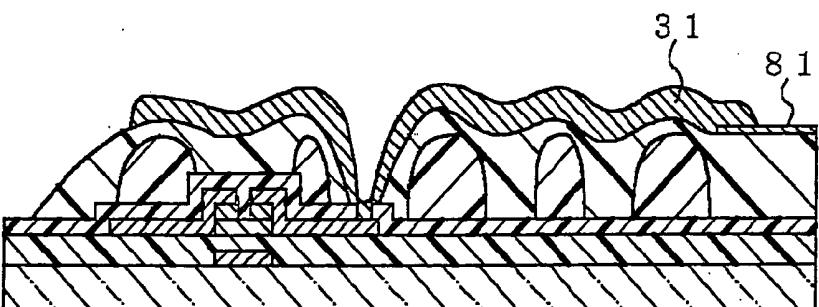

Fig. 3

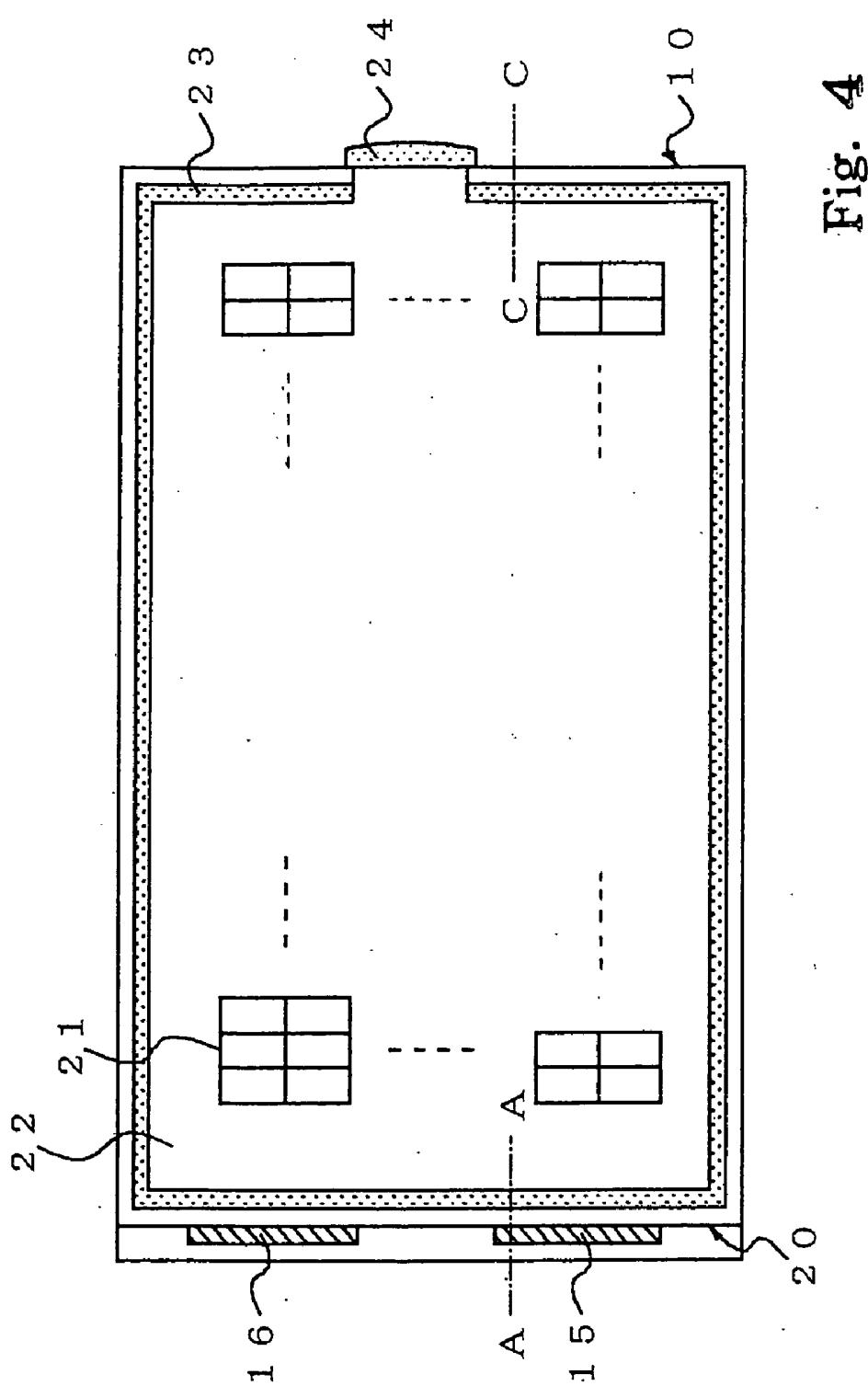

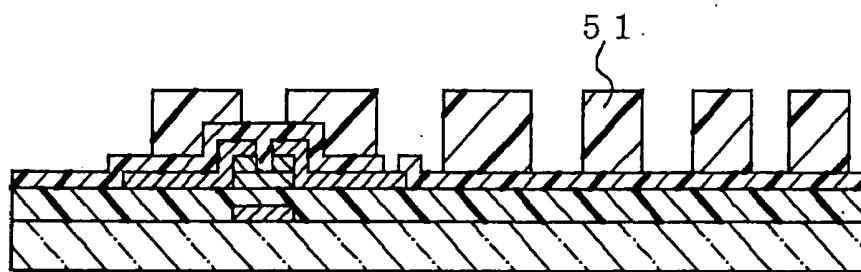

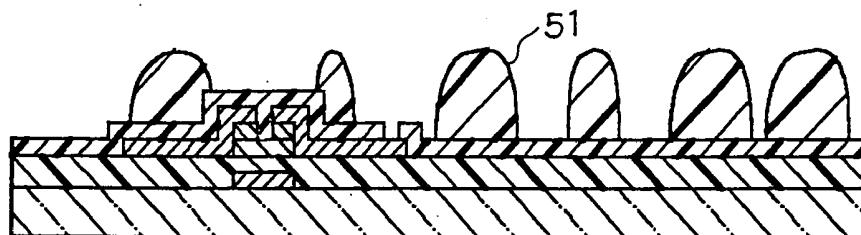

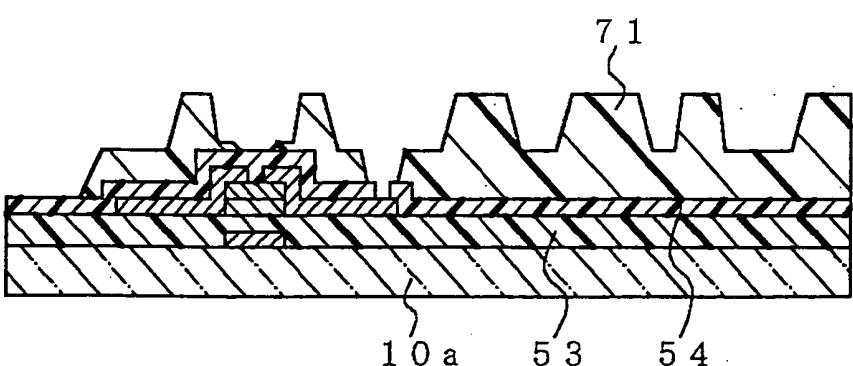

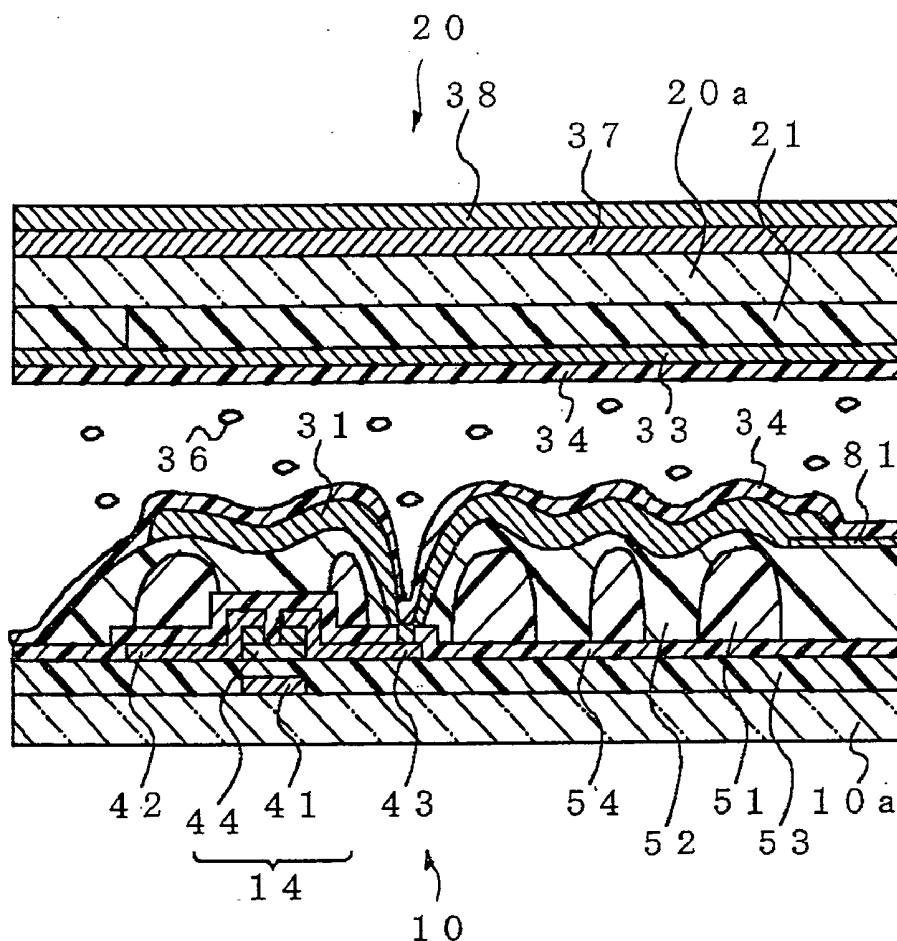

Fig. 4

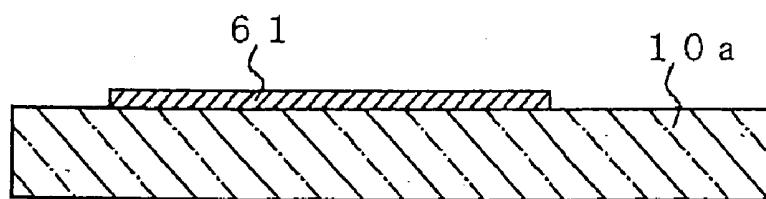

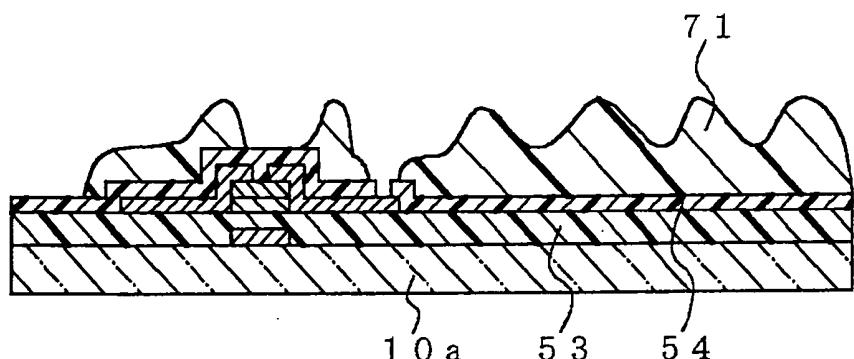

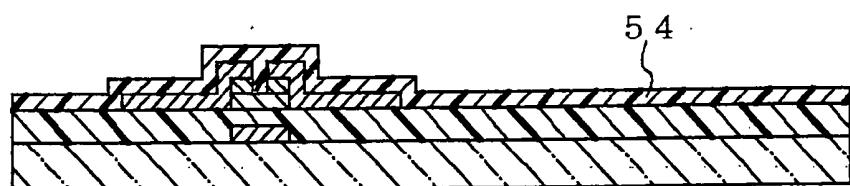

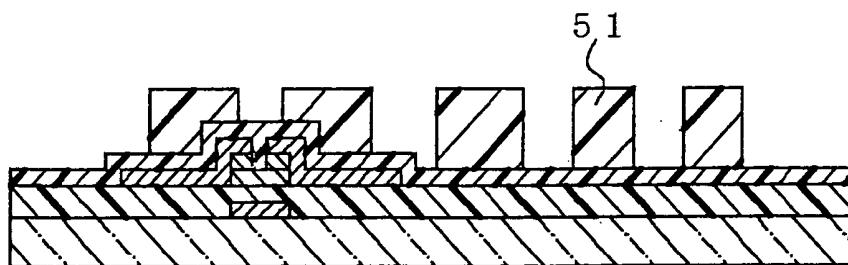

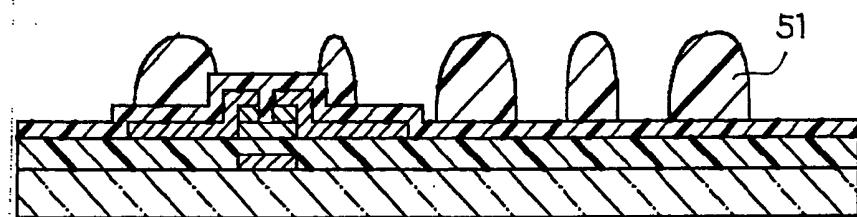

Fig. 5

Fig. 6 A

Fig. 6 B

Fig. 6 C

Fig. 6 D

Fig. 6 E

Fig. 6 F

Fig. 6 G

Fig. 6 H

Fig. 6 I

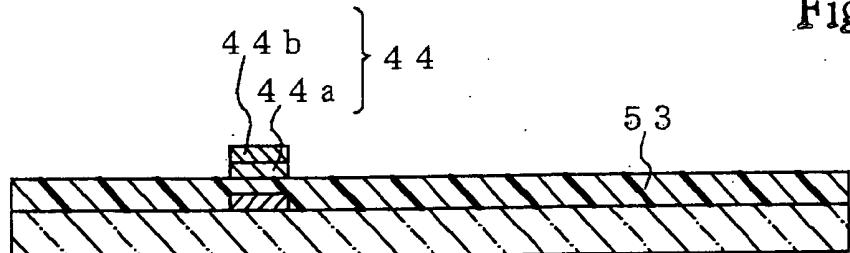

Fig. 7 A

Fig. 7 B

Fig. 7 C

Fig. 7 D

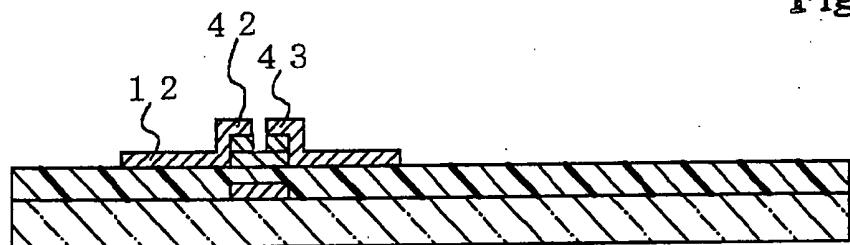

Fig. 7 E

Fig. 8A

Fig. 8B

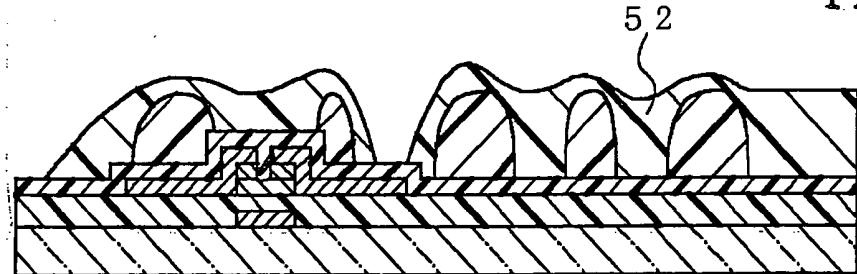

Fig. 8C

Fig. 8D

Fig. 8E

Fig. 9

Fig. 10 A

Fig. 10 B

Fig. 10 C

Fig. 10 D

Fig. 10 E

Fig. 10 F

Fig. 10 G

Fig. 10 H

Fig. 10 I

Fig. 10 J

Fig. 10 K

Fig. 11

Fig. 1 2

Fig. 1 3

Fig. 1 4

Fig. 1 5

Fig. 1 6

| NEODYMIUM<br>CONTENT (WT%) | 0.1 | 0.5 | 2 | 5 | 10 | 20 |

|----------------------------|-----|-----|---|---|----|----|

| HILLOCKS<br>(230°C, 1h)    | ×   | ○   | ○ | ○ | ○  | ○  |

| REFLECTIVITY               | ○   | ○   | ○ | ○ | △  | ×  |

Fig. 1 7

| SUBSTRATE<br>TEMP. (°C)               | 20 | 70 | 100 | 150 | 170 | 200 |

|---------------------------------------|----|----|-----|-----|-----|-----|

| COLOR                                 | ○  | ○  | ○   | ○   | ○   | ×   |

| REFLECTIVITY<br>(ON ORGANIC COMPOUND) | △  | ○  | ○   | ○   | △   | △   |

| CONTACT RESISTANCE                    | ×  | ○  | ○   | ○   | ○   | ○   |

Fig. 1 8

## LIQUID CRYSTAL DISPLAY PANEL HAVING REFLECTION ELECTRODES IMPROVED IN SMOOTH SURFACE MORPHOLOGY AND PROCESS FOR FABRICATION THEREOF

### FIELD OF THE INVENTION

[0001] This invention relates to a liquid crystal display panel and, more particularly, to a liquid crystal display panel of the type having a reflection electrode, which is hereinbelow referred to as "reflective liquid crystal panel, or a reflective-transparent liquid crystal display panel and a process for fabrication thereof.

### DESCRIPTION OF THE RELATED ART

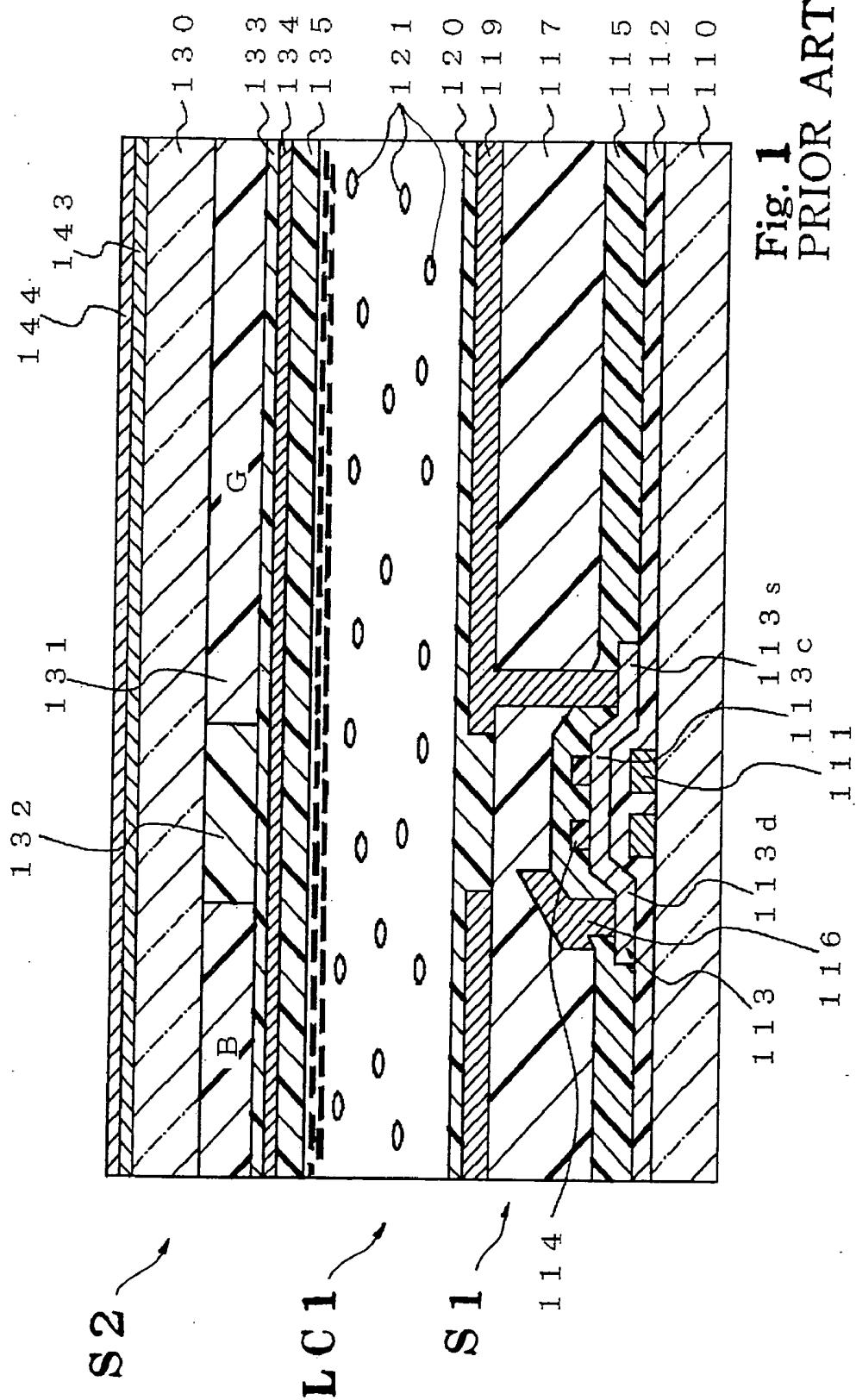

[0002] FIG. 1 shows a typical example of the reflective liquid crystal display panel disclosed in Japanese Patent Application laid-open No. 2000-258787. The prior art reflective liquid crystal display panel is broken down into a pair of substrate structures S1/S2, liquid crystal LC1, sealing layer (not shown) and spacers (not shown). The substrate structures S1 and S2 are spaced from each other by means of the spacers, and form an inner space together with the sealing layer. The inner space is filled with the liquid crystal LC1. In this instance, the twisted nematic liquid crystal is sealed in the inner space between the substrate structures S1 and S2. Ellipses stand for liquid crystal molecules, and are labeled with reference numeral 121.

[0003] The substrate structure S1 is fabricated on an insulating substrate 110. The insulating substrate 110 is formed of quartz or no-alkali glass. An array of switching transistors is fabricated on the insulating substrate 110. The switching transistors are thin film transistors, and only one thin film transistor is shown in FIG. 1. Other thin film transistors are fabricated concurrently with the thin film transistor. The thin film transistor is fabricated as follows. First, a gate electrode 111 of refractory metal such as chromium (Cr) or molybdenum (Mo) is formed on the insulating substrate 110. The gate electrode 111 is covered with a gate insulating layer 112, and an active layer 113 is patterned on the gate insulating layer 112. The active layer 113 is formed of polysilicon. An insulating stopper 114 is formed on the active layer 113. A part of the active layer 113 over the gate electrode 111 serves as a channel region 113c of the thin film transistor. Using the insulating stopper 114 as an ion-implantation mask, dopant impurity is ion implanted into the active layer 113, and forms a drain region 113d and a source region 113s on both sides of the channel region 113c.

[0004] On the entire surface of the resultant structure are successively deposited silicon dioxide ( $\text{SiO}_2$ ), silicon nitride ( $\text{SiN}_x$ ) and silicon dioxide ( $\text{SiO}_2$ ) which form in combination an inter-layered insulating layer 115. A contact hole is formed in the inter-layered insulating layer 115, and reaches the drain region 113d. A metal layer such as an aluminum layer is patterned into a drain electrode 116. The drain electrode 116 penetrates through the contact hole formed in the inter-layered insulating layer 115, and is held in contact with the drain region 113d.

[0005] Organic compound resin is, by way of example, deposited over the entire surface of the resultant structure, and forms a planarization layer 117. A contact hole is formed in the planarization layer 117 and the inter-layered insulating

layer 115. The source region 113s is exposed to the contact hole. A reflection electrode 119 is patterned on the planarization layer 117. The reflection electrode 119 penetrates through the contact hole, and is held in contact with the source region 113s. Thus, the reflection electrode 119 further serves as a source electrode. The reflection electrode 119 and the exposed surface of the planarization layer 117 are covered with an orientation layer 120, which is formed of organic compound resin such as polyimide.

[0006] The other substrate structure S2 is opposed to the above-described substrate structure S1, and is also fabricated on an insulating substrate 130. The insulating substrate 130 has two major surfaces. One of the major surfaces is opposed to the substrate structure S1, and is hereinbelow referred to as "inner surface". The other major surface is reverse to the inner surface, and is hereinbelow referred to as "outer surface".

[0007] Color filters 131 and a black matrix 132 are patterned on the inner surface of the insulating substrate 130. The color filters 131 are selectively in the primary three colors, i.e., red, green G and blue B, and are aligned with the reflection electrodes 119, respectively. The black matrix 132 is not transparent, and is aligned with the thin film transistors. The color filters 131 and the black matrix 132 are covered with a protective layer 133 of synthetic resin, and the protective layer is covered with a counter electrode 134. The counter electrode 134 is laminated with an orientation layer 135. On the other hand, a phase difference plate 143 is formed on the outer surface of the insulating substrate 130, and is covered with a polarizing plate 144.

[0008] In the above-described prior art reflective liquid crystal display panel, the reflection electrodes 119 are formed of aluminum-neodymium alloy, i.e., Al—Nd alloy. The Japanese Patent Application laid-open teaches that the alloy contains neodymium equal to or greater than 1 weight %. The Japanese Patent Application laid-open insists that the neodymium equal to or greater than 1 weight % is effective against hillocks. The Japanese Patent Application laid-open further insists that the aluminum-neodymium alloy, which was grown at the substrate temperature of the order of 200 degrees in centigrade, achieves reflectivity as high as an aluminum layer grown at room temperature.

[0009] Another prior art technology relating to the reflection plate is disclosed in Japanese Patent Application laid-open No. 5-80327. The Japanese Patent Application laid-open teaches a process for forming a diffuse reflection plate. The process starts with preparation of an organic compound layer. A reflection layer of aluminum or platinum is grown on the organic compound layer at 100 degrees to 250 degrees in centigrade. While the reflective substance, i.e., aluminum or platinum is growing on the organic compound layer, wrinkles take place in the organic compound layer due to the difference in thermal expansion coefficient between the organic compound and the reflective substance, and the reflective substance forms grains on the organic compound layer. Thus, the reflection plate is rugged. This results in improvement in irregular reflection property of the reflection plate.

[0010] Yet another prior art technology relating to the reflection plate is disclosed in Japanese Patent Application laid-open No. 2000-111906. The Japanese Patent Application laid-open teaches another process for fabricating an

electrooptical device with a rough reflection layer. The electrooptical device contains "liquid crystal display panel", and the prior art process includes the following steps. Bumps are firstly formed in a lower layer by using a honing or etching, and metal is grown over the bumps at 100 degrees to 300 degrees in centigrade at 80-250 angstroms/min. The bumps are transferred from the lower layer to the metal layer. The metal layer serves as a reflection layer. As to the metal, the Japanese Patent Application laid-open say, "The material for the reflection layer is aluminum or arbitrary kind of (metal)." However, the Japanese Patent Application laid-open is silent to concrete examples of "arbitrary kind of (metal)". After the growth of the metal, the reflection plate is treated with heat so as to form miniature bumps on the surface of the reflection plate at average pitches of 1-2 microns. The miniature bumps are of the order of 0.2 micron in depth. The reflection plate is improved in irregular reflection property by virtue of the miniature bumps. However, the Japanese Patent Application laid-open is silent to another purpose.

[0011] Japanese Patent Application laid-open No. 2000-111906 further teaches an orientation layer, which makes the liquid crystal molecules uniformly oriented in a certain direction. The Japanese Patent Application laid-open teaches that the orientation layer is formed of "high-molecular organic compound". Two kinds of high-molecular organic compound, i.e., polyimide and polyvinyl alcohol are exemplified in the Japanese Patent Application laid-open. However, the Japanese Patent Application laid-open is silent to a phenomenon in which the image-forming plane is made yellowish, and does not contain any description on a relation between the average pitch and the reflectivity to a certain wavelength light component.

[0012] The present inventors investigated the prior art technologies. The inventors fabricated samples of the prior art liquid crystal display panel with the reflection electrodes formed of the aluminum-neodymium alloy as taught in Japanese Patent Application laid-open No. 2000-258787.

[0013] Certain samples had the orientation layers 120 different in substance. In those samples, the aluminum-neodymium was grown at the substrate temperature around 200 degrees in centigrade, and, thereafter, the orientation layers 120 were formed over the reflection electrodes 119. The inventors assembled the substrate structures S1/S2 and the other components into the certain samples. The inventors found some samples to have yellowish image-forming planes.

[0014] Other samples had the reflection electrodes grown at the substrate temperature of the order of 70 degrees in centigrade and without heat application to the substrate. In detail, the inventors fabricated the thin film transistors on the insulating substrate of each sample, and spread the organic compound over the thin film transistors for forming the inter-layered insulating layer 117. The contact holes for the source regions 113s were formed in the inter-layered insulating layer 117, and the aluminum-neodymium alloy was deposited over the inter-layered insulating layer 117 at certain substrate temperature in the range from room temperature to 70 degrees in centigrade. The aluminum-neodymium alloy was patterned into the reflection electrodes 119. After the formation of the orientation layer 120, the substrate structure S1 was assembled with the other substrate structure

S2 so as to complete each sample. The samples were categorized into the reflective liquid crystal display panel and the reflective-transparent liquid crystal display panel. The inventors drove the samples, and found that the image-carrying signal was not completely written into the pixel electrodes. This was because of the fact that the contact resistance between the reflection electrodes 119 and the source regions 113s was too high. Furthermore, in case where the aluminum-neodymium alloy was grown without heat application to the substrate, the temperature of the inter-layered insulating layer 117 was raised due to the heat of condensation in the deposition of the aluminum-neodymium alloy, and out-gassing took place in the organic compound. The gas gave rise to change in quality of the aluminum-neodymium, and made the reflection electrodes 119 cloudy. This resulted in reduction in reflectivity.

[0015] The present inventors further fabricated samples of the electrooptical device disclosed in Japanese Patent Application laid-open No. 2000-111906. The samples have the miniature bumps transferred from the lower layer thereto. However, the miniature bumps were not effective against the yellowish image-forming plane.

[0016] These problems are encountered in the prior art liquid crystal display panel disclosed in Japanese Patent Application laid-open No. 2000-258787.

## SUMMARY OF THE INVENTION

[0017] It is therefore an important object of the present invention to provide a liquid crystal display panel, which is free from yellowish image-forming plane in spite of an orientation layer having a transparency to ultraviolet light smaller than a transparency to visible light.

[0018] It is also an important object of the present invention to provide a process for fabricating the liquid crystal display panel.

[0019] In accordance with one aspect of the present invention, there is provided a liquid crystal display panel comprising a first substrate structure including reflection plates having a surface morphology represented by average pitches equal to or less than 1 micron and an orientation layer formed over the reflection plates and having a first transparency to light components with wavelengths equal to or less than 400 nanometers and a second transparency to visible light components larger than the first transparency, a second substrate structure having an inner surface opposed to the orientation layer, and liquid crystal sealed in a space between the orientation layer and the inner surface and forming plural pixels together with the reflection plates so as to selectively change a transparency of the plural pixels depending upon the strength of local electric fields created in the vicinity of the reflection plates.

[0020] In accordance with another aspect of the present invention, there is provided a process for fabricating a liquid crystal display panel, comprising the steps of a) fabricating an intermediate structure of a first substrate structure, b) growing a highly reflective substance over the intermediate structure under the condition that the intermediate structure is heated to a certain temperature equal to or less than 170 degrees in centigrade for forming a highly reflective substance layer, c) patterning the highly reflective substance layer into reflection plates, d) covering an array of reflection

plates with an orientation layer having a first transparency to light components with wavelengths equal to or less than 400 nanometers and a second transparency to visible light components larger than the first transparency so as to complete the first substrate structure, e) assembling the first substrate structure with a second substrate structure in such a manner that the orientation layer is opposed to an inner surface of the second substrate structure and f) sealing liquid crystal in a space between the orientation layer and the inner surface.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0021] The features and advantages of the liquid crystal display panel and the process for fabrication thereof will be more clearly understood from the following description taken in conjunction with the accompanying drawings, in which

[0022] **FIG. 1** is a cross sectional view showing the structure of the prior art reflective liquid crystal display panel disclosed in Japanese Patent Application laid-open No. 2000-258787,

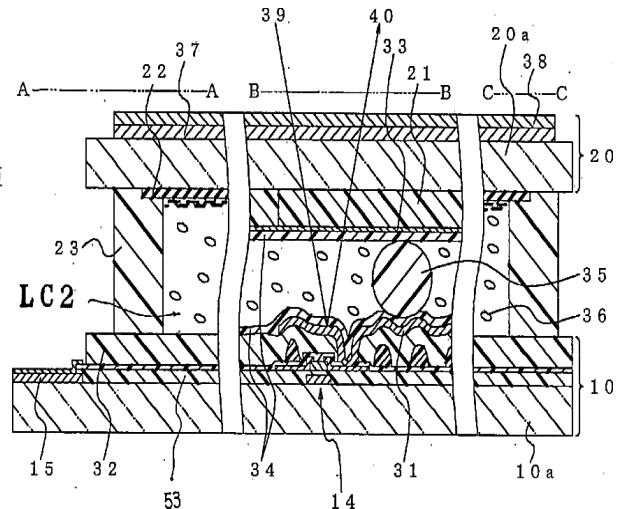

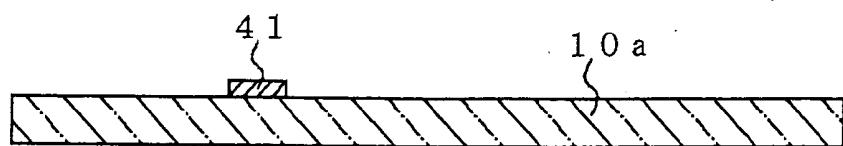

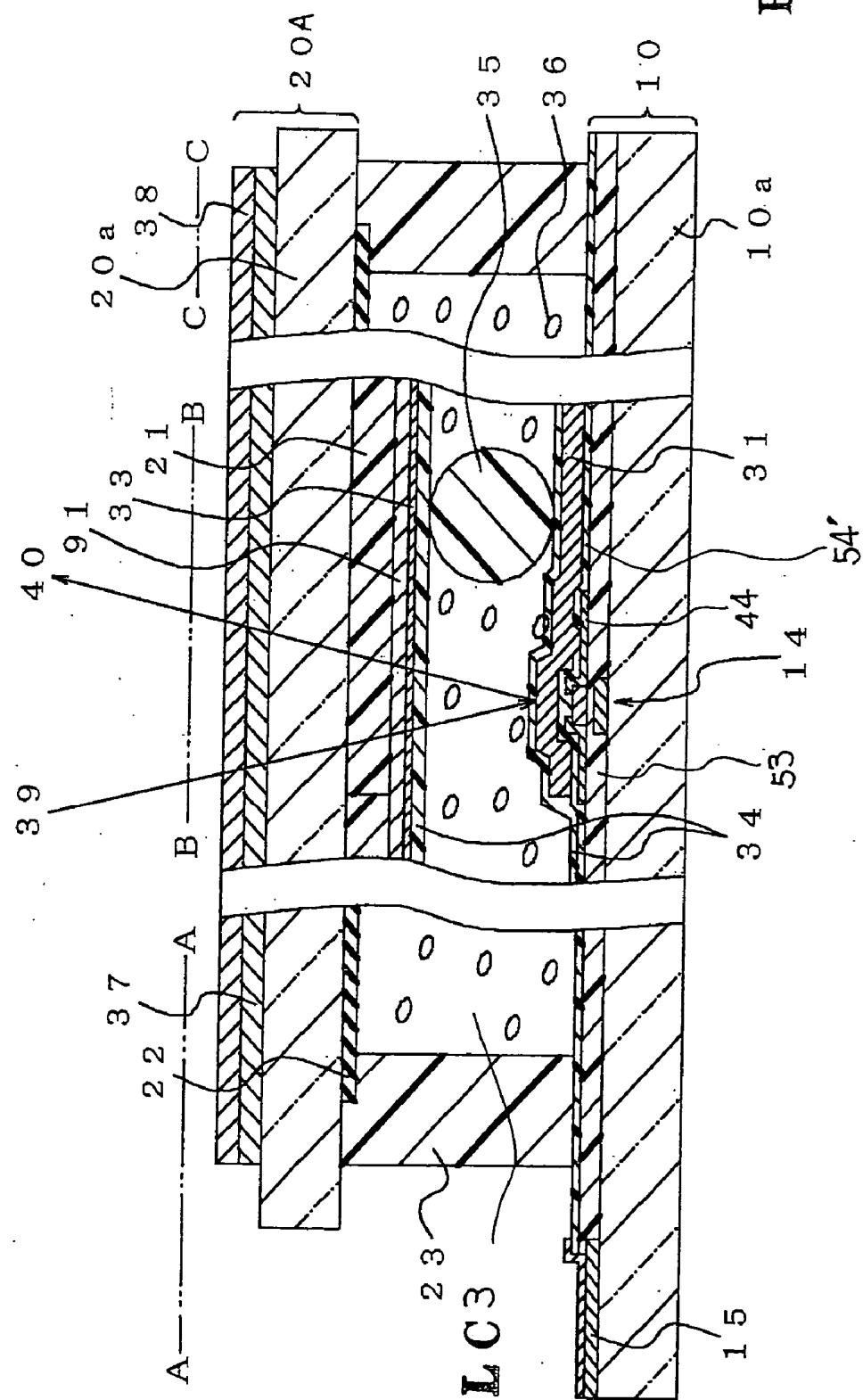

[0023] **FIG. 2** is a cross sectional view showing the structure of a reflective liquid crystal display panel according to the present invention,

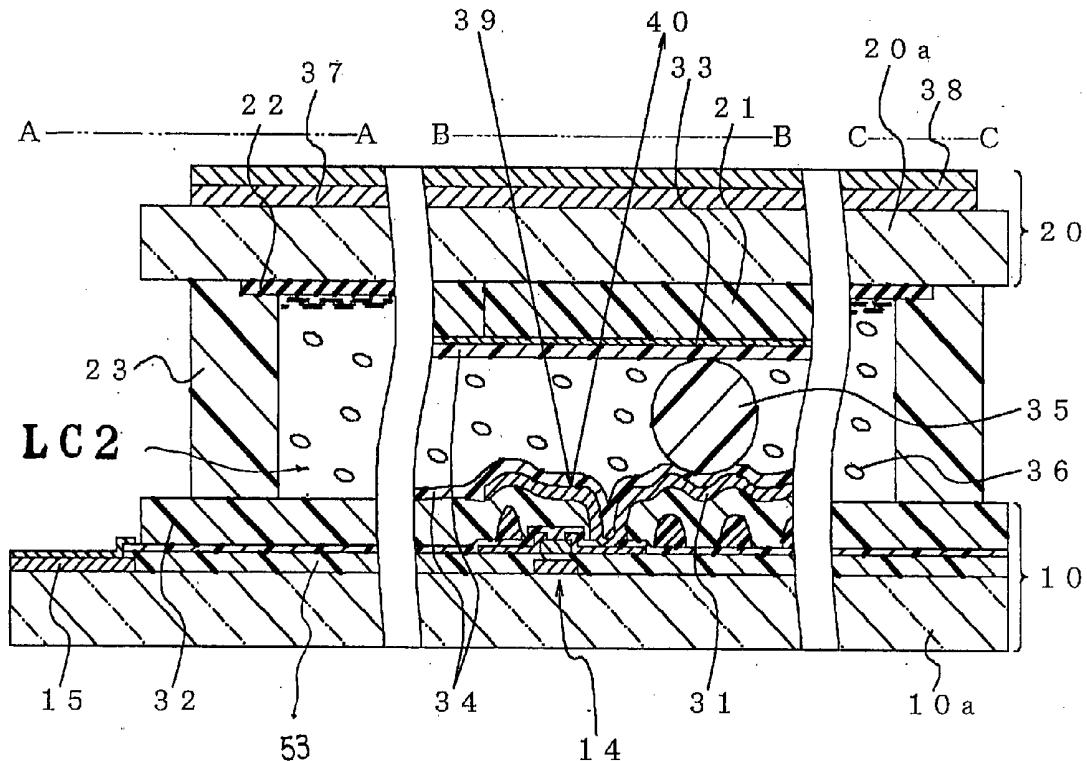

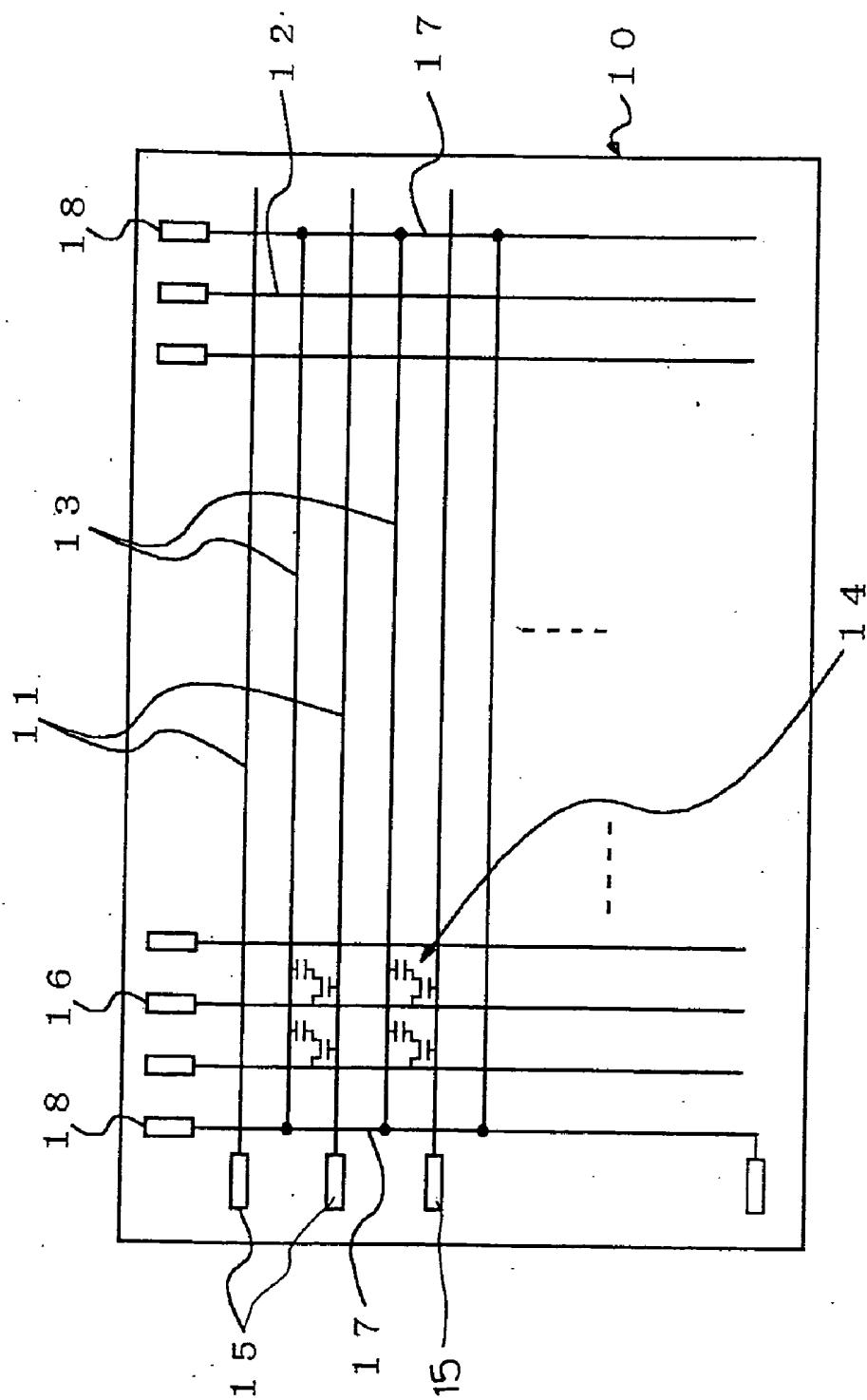

[0024] **FIG. 3** is a schematic plane view showing the arrangement of components in a substrate structure incorporated in the reflective liquid crystal display panel,

[0025] **FIG. 4** is a schematic plane view showing the arrangement of components in another substrate structure incorporated in the reflective liquid crystal display panel,

[0026] **FIG. 5** is a plane view showing the layout of thin film transistors and reflection electrodes on the substrate structure shown in **FIG. 3**,

[0027] **FIGS. 6A to 6I** are cross sectional views taken along line B-B of **FIG. 5** and showing a process sequence for fabricating the liquid crystal display panel,

[0028] **FIGS. 7A to 7E** are cross sectional views showing the process sequence on another cross section,

[0029] **FIGS. 8A to 8E** are cross sectional views showing essential steps of another process sequence for fabricating another liquid crystal display panel according to the present invention,

[0030] **FIG. 9** is a plane view showing the arrangement of components of pixels incorporated in yet another liquid crystal display panel according to the present invention,

[0031] **FIGS. 10A to 10K** are cross sectional views showing a process sequence for fabricating the liquid crystal display panel,

[0032] **FIG. 11** is a cross sectional view showing the structure of still another liquid crystal display panel according to the present invention,

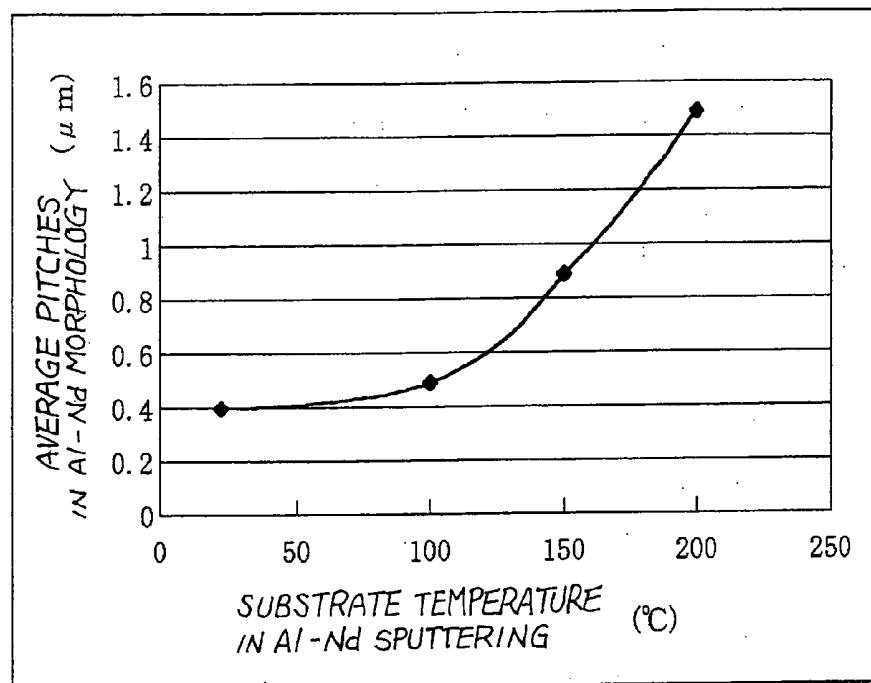

[0033] **FIG. 12** is a graph showing a relation between the substrate temperature in a sputtering and average pitches,

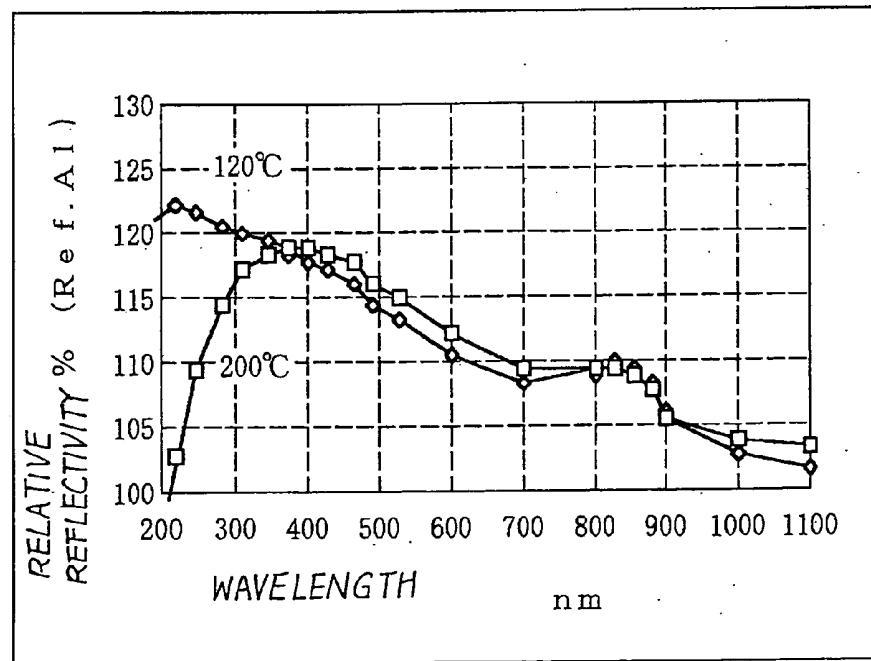

[0034] **FIG. 13** is a graph showing a relative reflectivity to light components,

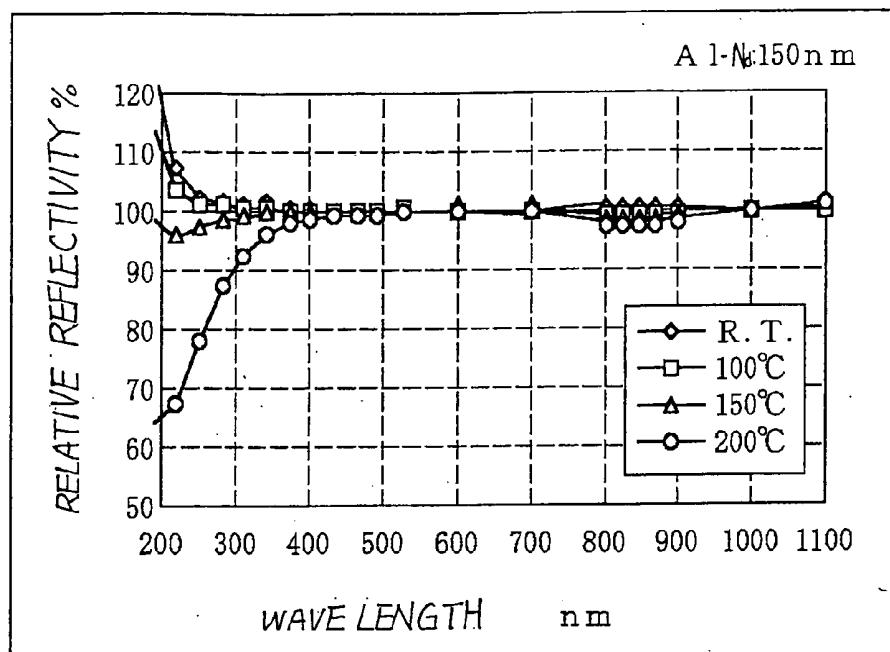

[0035] **FIG. 14** is a graph showing a relative reflectivity on aluminum-neodymium alloy layers of 150 nanometers thick to light components,

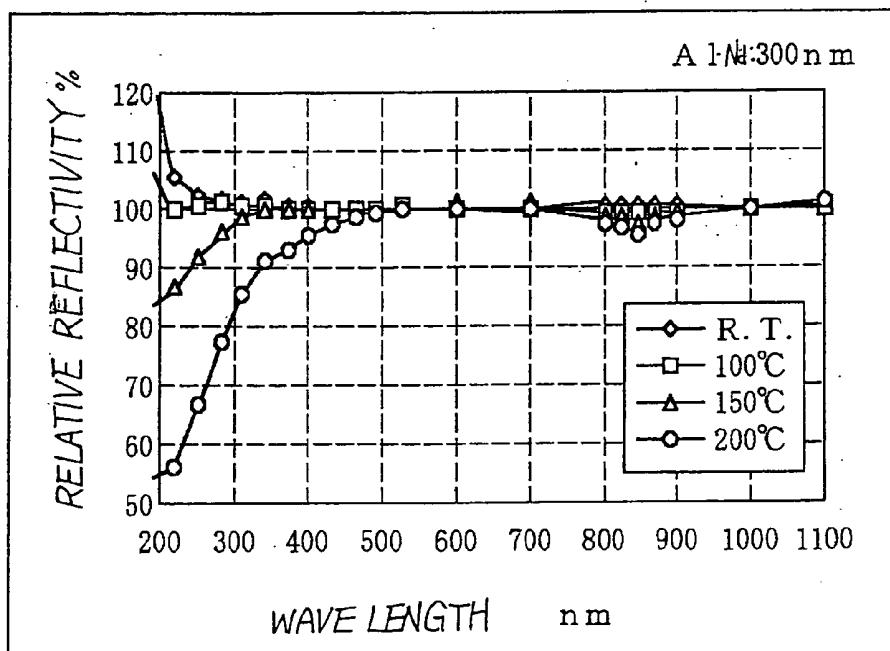

[0036] **FIG. 15** is a graph showing a relative reflectivity on aluminum-neodymium alloy layers of 300 nanometers thick to light components,

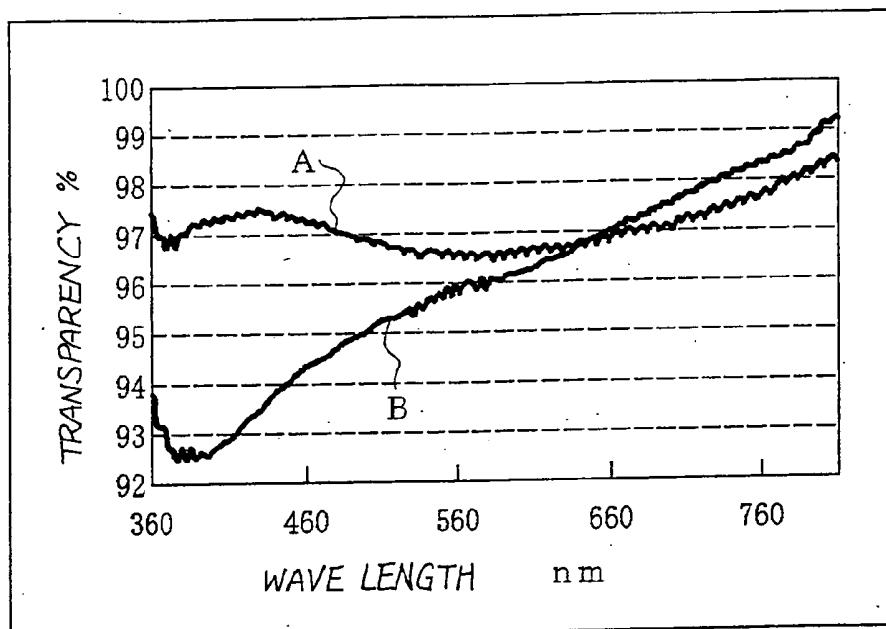

[0037] **FIG. 16** is a graph showing a relation between transparency and light components measured in different organic compounds,

[0038] **FIG. 17** is a view showing a relation between neodymium content and hillocks/reflectivity, and

[0039] **FIG. 18** is a view showing a relation between the substrate temperature, color on an image-forming plane, reflectivity and contact resistance.

#### DESCRIPTION OF THE PREFERRED EMBODIMENTS

##### First Embodiment

[0040] Referring to **FIG. 2** of the drawings, a liquid crystal display panel embodying the present invention largely a pair of substrate structures **10/20**, liquid crystal LC2, a sealing layer **23** and spherical spacers **35**. The substrate structures **10** and **20** are opposed to each other, and the sealing layer **23** and the spherical spacers **35** keep the substrate structures **10** and **20** spaced from each other. In detail, the sealing layer **23** extends along the peripheries of the substrate structures **10/20**, and the spherical spacers **35** are scattered inside of the sealing layer **23**. The sealing layer **23** and the spherical spacers **35** are sandwiched between the substrate structures **10** and **20**, and the liquid crystal LC2 fills the space defined by the substrate structures **10/20** and the sealing layer **23**. Ellipses stand for the liquid crystal molecules, and are labeled with reference numeral **36**.

[0041] Description is made on the substrate structure **10** with concurrent reference to **FIGS. 2 and 3**. The substrate structure **10** is fabricated on a transparent insulating substrate **10a**, and includes conductive strips **11** for a scanning signal, conductive strips **12** for a data signal, conductive strips **13** for a constant voltage, an array of thin film transistors **14** and reflection electrodes **31**. The conductive lines **11** for the scanning signal extend in parallel on the transparent insulating substrate **10a**, and are connected to the gate electrodes of the rows of thin film transistors **14**. The scanning signal is supplied through signal terminals **15** to the conductive strips **11** so as sequentially to cause the rows of thin film transistors **14** to turn on.

[0042] The conductive strips **12** for the data signal extend in the perpendicular direction to the conductive strips **11** for the scanning signal, and are connected to the drain regions of the columns of thin film transistors **14**. The data signal is supplied through signal terminals **16** to the conductive strips **12** so as to distribute pieces of data information representative of an image to be produced to the columns of thin film transistors **14**. Although the conductive strips **12** for the data signal cross the conductive strips **11** for the scanning signal, the conductive strips **12** for the data signal are electrically isolated from the conductive strips **11** for the scanning signal by means of a gate insulating layer **53**. Thus, the conductive strips **11** for the scanning signal and the conductive strips **12** for the data signal define plural crossing points over the central area of the transparent insulating layer **10a**, and the plural crossing points are assigned to the thin film transistors **14**, respectively.

[0043] Although the terminals 15 assigned to the scanning signal and the terminals 16 assigned to the data signal are arranged along the side line and along the end line of the substrate structure 10 in FIG. 3, both terminals 15/16 may be arranged along the side line of the substrate structure of a reflective liquid crystal display panel for a portable use (see FIG. 4).

[0044] The conductive strips 13 for the constant voltage extend in parallel to the conductive strips 11 for the scanning signal, and are widened at intervals. The wide portions of the conductive strips 13 are respectively associated with the thin film transistors 14, and serve as counter electrodes of holding capacitors. Terminals 18 are connected through distributing strips 17, which extend on both sides of the conductive strips 12, to the conductive strips 13, and the common voltage is applied through terminals 18 and the distributing strips 17 to the conductive strips 13. The common voltage finally reaches the counter electrodes.

[0045] The reflection electrodes 31 are arranged in matrix, and are respectively connected to the source regions of the thin film transistors 14. Thus, the reflection electrodes 31 serve as pixel electrodes, respectively. An inter-layered insulating layer 32 of organic compound is inserted between the array of thin film transistors 14 and the reflection electrodes 31, and the reflection electrodes 31 are respectively opposed to the counter electrodes thereunder. The array of reflection electrodes 31 is covered with an orientation layer 34. The orientation layer 34 is formed of organic compound, which makes an image-forming plane yellowish.

[0046] The inter-layered insulating layer 32 is formed with relatively large bumps, and the relatively large bumps make the reflection electrodes 31 rugged. The reflection electrode 31 has the upper surfaces with smooth surface morphology. The ruggedness on the upper surfaces is equal to or less than 1 micron in average pitches. It is more preferable that the average pitches are equal to or less than 0.6 micron. The smooth surface morphology prevents the image-forming plane from being yellowed. This is because of the fact that the smooth surface morphology reduces the light absorption to ultraviolet light component from 200 nanometer wavelength to 400 nanometer wavelength. The ruggedness in the upper surfaces of the reflection electrodes 31 is different from the relatively large bump. In this specification, words "surface morphology" means the ruggedness on the surfaces of the crystal structure.

[0047] The other substrate structure 20 is fabricated on a transparent insulating substrate 20a. As will be seen in FIG. 4, color filters 21 are patterned in a central area of the transparent insulating substrate 20a, and are surrounded by a black matrix 22. In this instance, the black matrix 22 is formed in the peripheral area, and does not occupy the central area. The black matrix makes the contrast of image fine. The color filters 21, i.e., red filters, green filters and blue filters are respectively aligned with the reflection electrodes 31, and are covered with a counter electrode 33. The counter electrode 33 in turn is covered with an orientation layer 34. The common voltage is applied to the counter electrode 33. In other words, the counter electrode 33 is equal in potential level to the counter electrodes of the holding capacitors. The orientation layer 34 of the substrate structure 10 is spaced from the orientation layer 34 of the other substrate structure 20 by means of the sealing layer 23 and the spherical spacers

35, and the liquid crystal LC2 fills the gap between the orientation layers 34. The liquid crystal LC2 is injected through an opening formed in the sealing layer 23, and the opening is closed with a plug 24. Dot-and-dash lines A-A and C-C are indicative of the cross sections under dots-and-dash lines A-A and C-C shown in FIG. 2.

[0048] Each of the thin film transistors 14, reflection electrode 31 connected to the thin film transistor, the color filter 21 aligned with the reflection electrode, the counter electrode 33 and a piece of liquid crystal LC2 therebetween constitute a pixel. A set of red, green and blue filters, the reflection electrodes 31 aligned therewith, the thin film transistors 14 connected to the reflection electrodes 31 and pieces of liquid crystal LC2 therebetween form in combination a color pixel. Namely, a pixel with the red filter, pixel with the green filter and the pixel with the blue filter as a whole constitute each color pixel, and plural color pixels form the image forming plane.

[0049] The substrate structure 20 further has a quarter wavelength plate 37 and a polarizing plate 38. The quarter wavelength plate 37 is fixed to the surface of the transparent insulating substrate 20a reverse to the surface where the color filters 21 and the black matrix 22 are patterned, and is covered with the polarizing plate 38.

[0050] Though not shown in FIG. 4, a semiconductor chip is mounted on the terminals 16, and a driving circuit on the semiconductor chip is connected to the liquid crystal display panel. The liquid crystal display panel and the COG (Chip-On-Glass) integrated circuit as a whole constitute a liquid crystal display unit.

[0051] The liquid crystal display unit behaves as follows. The scanning signal causes the rows of thin film transistors 14 sequentially to turn on, and the data signal carries pieces of data information representative of a part of image to the reflection electrodes 31 associated with the selected row of thin film transistors. The data signal reaches the selected reflection electrodes 31, and creates local electric fields between the selected reflection electrodes 31 and the common electrode 33. The liquid crystal molecules 36 are selectively raised in the local electric fields. When the data signal reaches the reflection electrodes 31 associated with the final row of thin film transistors 14, the liquid crystal LC2 becomes partially transparent, and incident light 39 is reflected on the reflection electrodes 31. The reflection 40 passes through the transparent liquid crystal LC2, and forms the image on the image-forming plane.

[0052] The incident light passes through each orientation layer 34 twice. If the reflection electrodes have surface rough morphology represented by the average pitches greater than 1 micron, the orientation layer is widely varied in thickness, and the optical path in the orientation layer 34 is different between rays of the incident light depending upon the incident points. In the reflective liquid crystal display panel, the difference is increased twice. The orientation layer 34 is formed of the organic compound which has the transparency to the ultraviolet light components much smaller than the transparency to the visible light components. While the light 39 is traveling in the orientation layer 34, the ultraviolet light components are absorbed more than the visible light components. This results in that the yellowish image-forming plane.

[0053] On the contrary, the reflection electrodes 31 according to the present invention have the smooth surface

morphology represented by the average pitches equal to or less than 1 micron. The orientation layer 34 is substantially uniform in thickness, and the light path of a ray of the incident light 39 is nearly equal to that of another ray of the incident light 39. Even though the rays pass the orientation layer 34 twice, the difference is not serious, and the ultra-violet light components are not absorbed in the orientation layer. Thus, the reflection electrodes 31 with the smooth surface morphology are effective against the yellowish image-forming plane.

[0054] Description is hereinbelow made on a process for fabricating the liquid crystal display panel with reference to FIGS. 5, 6A to 6I and 7A to 7E. FIG. 5 shows the thin film transistors 14, which are respectively connected to the reflection electrodes 31. The thin film transistors 14 shown in FIG. 5 are located at the outermost position of the array. The thin film transistors 14 have an inverted staggered structure, and dot-and-dash line B-B is indicative of the cross section shown in FIGS. 6A to 6I. FIGS. 7A to 7E show a cross section of a peripheral region of the substrate structure 10. The cross section is taken along a line parallel to the short sides of the terminals 15/16/18.

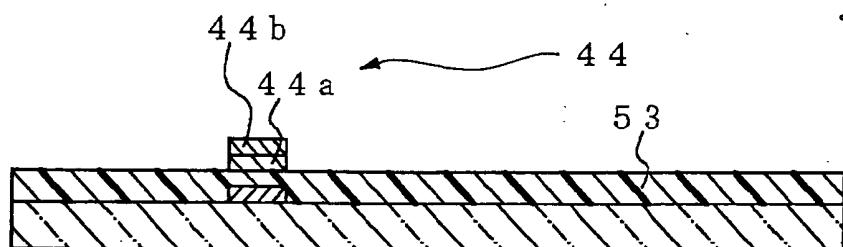

[0055] In order to make the process clearly understandable, the layout of the color pixels and the structure thereof are described with reference to FIG. 5. As shown in FIG. 5, the conductive strips 11 for the scanning signals extend in parallel to one another, and the conductive strips 12 for the data signal extend perpendicularly to the conductive strips 11. The conductive strips 13 for the common voltage alternately extend in parallel to the conductive strips 11, and are close to the associated conductive strips 11. The conductive strips 11 and 12 define plural rectangular regions, and the thin film transistors 14 occupy the rectangular regions, respectively. The wide portions of the conductive strips 13 project into the rectangular regions, and are opposed to the associated reflection electrodes 31, respectively. The inter-layered insulating layer 32 is sandwiched between the wide portions and the reflecting electrodes 31 so that the holding capacitors are produced over the rectangular regions, respectively. The thin film transistors 14 are similar in structure to one another. Each of the thin film transistors 14 has a gate electrode 41, a gate insulating layer 53 (see FIG. 6B), a drain electrode 42, a source electrode 43 and an active layer 44. A non-doped amorphous silicon layer 44a and heavily doped n-type amorphous silicon layer 44b form the active layer (see FIG. 6B).

[0056] The gate electrodes 41 of the thin film transistors 14 and the conductive strips 11 for the scanning signal are patterned on the major surface of the transparent insulating substrate 10a, and the gate electrodes 41 are merged with the associated conductive strips 11 for the scanning signal. Each gate electrode 41 is covered with the gate insulating layer 53, and the active layer 44 is patterned on the gate insulating layer 53 in such a manner as to be located over the associated gate electrode 41. Each of the active layers 44 serves as a drain region and a source region of the thin film transistor 14.

[0057] The drain electrodes 42, source electrodes 43 and the conductive strips 12 for the data signal are patterned on the gate insulating layer 53. The drain electrodes 42 are merged with the associated conductive strips 12, and are held in contact with the drain region in the active layer 14.

On the other hand, the source electrode 43 is held in contact with the source region in the active layer 14. The drain electrodes 42, source electrodes 43 and the conductive strips 12 for the data signal are covered with a passivation layer 54 (see FIG. 6D). The passivation layer 54 prevents the thin film transistors 14 from damages, and two insulating layers 51 and 52 are laminated on the passivation layer 54. The insulating layer 51 forms steep bumps, and the other insulating layer 52 makes the steep bumps mild. Thus, the insulating layers 51 and 52 create proto-bumps, which are transferred to the reflection electrodes 31 for forming the large bumps. The large bumps aim at uniform reflection characteristics over the image-forming plane. For this reason, the insulating layer 51 is irregularly formed on the central area of the substrate structure 10 which is assigned to the color pixels. However, the insulating layer 51 does not extend into the peripheral area which is assigned to the terminals. On the other hand, the insulating layer 52 extends over the central area, and penetrates into the peripheral area so that the proto-bumps are perfectly covered with the insulating layer 52. The passivation layer 53 and the insulating layers 51/52 as a whole constitute the inter-layered insulating layer 32.

[0058] Source contact holes 45 are formed in the insulating layers 51/52 as well as the passivation layer 54. The source contact holes 45 reach the source electrodes 43, respectively. The reflection electrodes 31 are formed on the insulating layer 52, and occupy the rectangular regions, respectively. The reflection electrodes 31 pass through the source contact holes 45, and are held in contact with the source electrodes 43, respectively.

[0059] The proto-bumps are transferred from the insulating layer 51 to the reflection electrodes 31, and the large bumps impart predetermined optical characteristics to the reflection 40. Thus, the large bumps deeply concern the quality of image formed on the image-forming plane. For this reason, the large bumps are designed to achieve the optical characteristics. In the design work, the pitches of the bumps, pitches of valleys, the height of the bumps and the depth of the valleys are taken into account. The large bumps are designed in such a manner that one of the pitches, height and depth has more than one value, i.e., two values or more than two values.

[0060] The insulating layer 51 further has an influence on electric characteristics of the pixels. As shown in FIG. 5, the conductive strips 11 for the scanning signal and the conductive strips 12 for the data signal are partially overlapped with the reflection electrodes 31, and the inter-layered insulating layer 31, i.e., the passivation layer 54 and the insulating layers 51/52 are inserted between the conductive strips 11/12 and the reflection electrodes 31. The conductive strips 11/12, the inter-layered insulating layer 32 and the reflection electrodes 31 undesirably form parasitic capacitors. If the insulating layer 51 is too thin, the incident light 39 is not widely changed in direction, and the parasitic capacitors have large capacitance. The large capacitance makes the signal propagation through the conductive strips 11/12 slow, and the pieces of data information are hardly written into the reflection electrodes 31. Moreover, the local electric fields are undesirably made strong, and the strong local electric fields give rise to serious turbulence in the orientation of the liquid crystal molecules in the vicinity of the pixels. This results in poor contrast in the image produced on the image-forming

plane. In order to prevent the pixels from those problems, it is necessary that the insulating layer **51** be fallen within the range between 1 micron thick to 3 microns thick.

[0061] The other insulating layer **52** is designed to make the steep bumps mild. If the insulating layer **52** is too thin, the proto-bumps become too steep, and the manufacturer suffers from the poor step-coverage. On the other hand, if the insulating layer **52** is too thick, the large bumps are not formed in the reflection electrodes **31**. In this instance, the insulating layer **52** ranges from 0.3 micron thick to 1.5 microns thick.

[0062] FIGS. 6A to 6I and 7A to 7E show a process sequence including the steps of (1) patterning a metal layer into the gate electrodes **41**, terminals **15/16/18** and the conductive strips **11/13**, (2) patterning amorphous silicon layers on the gate insulating layer into the active layers **44**, (3) patterning a metal layer into the conductive strips **12** and the source/drain electrodes **43/42**, (4) forming the contact holes in the passivation layer **54**, (5) patterning a transparent conductive layer into terminal connecting electrodes, (6) patterning an insulating layer into the proto-bumps, (7) forming contact holes in the insulating layer **52** deposited over the proto-bumps and (8) patterning a metal layer into the reflection electrodes **31**.

[0063] The process starts with preparation of the transparent insulating substrate **10a**. The transparent insulating substrate **10a** is formed of no-alkali glass, and is 0.5 millimeter thick. A chromium target is sputtered so as to deposit a chromium layer to 100 nanometers thick to 300 nanometers thick over the entire surface of the transparent insulating substrate **10a**. A photo-resist etching mask (not shown) is prepared on the chromium layer, and the chromium layer is partially etched away. The gate electrodes **41**, conductive strips **11** for the scanning signal, conductive strips **13** for the common voltage, metal layers **61** for the terminals **15/16/18** are left on the major surface of the transparent insulating substrate **10a**. Although the conductive strips **11** for the scanning signal and the conductive strips **13** for the common voltage are not seen, the resultant structure is shown in FIGS. 6A and 7A.

[0064] The gate electrodes **41**, conductive strips **11/13** and the metal layers **61** may be formed of another kind of metal or alloy in so far as the metal/alloy is formed in a thin film and patterned. The another kind of metal/alloy is Mo, Al or aluminum alloy, by way of example. The gate electrodes **41**, conductive strips **11/13** and the metal layers **61** may have a multi-layered structure such as, for example, an aluminum, aluminum alloy or molybdenum layer overlaid by a barrier metal layer of chromium, molybdenum or titanium.

[0065] Subsequently, silicon nitride, i.e., SiNx is deposited to 300 nanometers thick to 500 nanometers thick over the entire surface of the resultant structure by using a plasma-assisted chemical vapor deposition technique, and forms the gate insulating layer **53**. The gate electrodes **41** and the metal layers **61** are covered with the gate insulating layer **53**. FIG. 7B shows the metal layer **61** covered with the gate insulating layer **53**.

[0066] Undoped amorphous silicon is deposited to 150 nanometers thick to 300 nanometers thick over the gate insulating layer **53** also by using the plasma-assisted chemical vapor deposition, and heavily-doped n-type amorphous

silicon is further deposited to 30 nanometers thick to 50 nanometers thick. The undoped amorphous silicon forms the undoped amorphous silicon layer, and the heavily-doped n-type amorphous silicon forms the n+ amorphous silicon layer on the undoped amorphous silicon layer. A photo resist etching mask is prepared by using the photo-lithographic techniques, and the undoped amorphous silicon layer and the n+ amorphous silicon layer are patterned into the undoped amorphous silicon strips **44a** and the n+ amorphous silicon strips **44b** as shown in FIG. 7B. The undoped amorphous silicon strips **44a** and the n+ amorphous silicon strips **44b** form in combination the active layers **44**, and the active layers **44** are arranged over the gate electrodes **41** at intervals. The n+ amorphous silicon strips **44b** form ohmic contacts together with the source/drain electrodes **43/42**.

[0067] Subsequently, chromium is deposited to 100 nanometers thick to 300 nanometers thick over the entire surface of the resultant structure by using the sputtering technique. A photo resist mask is prepared by using the photolithographic techniques. Using the photo resist etching mask, the chromium layer is patterned into the drain electrodes **42**, source electrodes **43** and the conductive strips **12** for the data signal by using a dry etching technique.

[0068] The drain/source electrodes **42/43** and the conductive strips **12** may be formed of another kind of metal or alloy in so far as the metal/alloy is formed in a thin film and patterned. The another kind of metal/alloy is Mo, Al or aluminum alloy, by way of example. The conductive strips **12** and the source/drain electrodes **42/43** may have a multi-layered structure such as, for example, an aluminum, aluminum alloy or molybdenum layer overlaid by a barrier metal layer of chromium, molybdenum or titanium.

[0069] Using the drain/source electrodes **42/43** as an etching mask, the n+ amorphous silicon strips **44b** are partially etched by using a dry etching technique, and the ohmic contact portions are separate from each other. Thus, the channel region is only formed in the undoped amorphous silicon strip **44a**, and the conductivity of the channel region is controlled by the gate potential at the associated gate electrode **41**. In other words, the current does not flow directly between the ohmic contact portions. The resultant structure is shown in FIG. 6C.

[0070] Subsequently, silicon nitride is deposited to 100 nanometers thick to 300 nanometers thick over the entire surface of the resultant structure by using the plasma-assisted chemical vapor deposition, and forms the passivation layer **54**. The drain electrodes **42** and the source electrodes **43** are covered with the passivation layer **54**, and the gate insulating layer **53** is overlaid by the passivation layer **54** (see FIG. 7C). The passivation layer **54** prevents the undoped amorphous silicon strips **44a** from undesirable ions so that malfunction does not take place in the thin film transistors **14**.

[0071] A photo resist etching mask is prepared on the passivation layer **54** by using the photo-lithographic techniques. Using the photo resist etching mask, the gate insulating layer **53** and/or the passivation layer **54** are partially etched away for forming the contact holes **55/62**, and the source electrodes **43** and the metal layers **61** are exposed to the contact holes **55/62** as shown in FIGS. 6D and 7D. Though not shown in the drawings, contact holes are concurrently formed in the passivation layer **54** and/or the gate

insulating layer 53 so that the conductive strips 13 for the common voltage, metal layers 61 for the data signal and the conductive strips 12 adjacent to the metal layers 61 are exposed to the contact holes.

[0072] Subsequently, transparent material such as, for example, ITO (Indium-Tin-Oxide) is deposited to 40 nanometers thick to 100 nanometers thick by using a sputtering technique, and the indium-tin-oxide layer is patterned into connecting electrodes 63 held in contact with the metal layers 61 for the terminals 15/16/18, the interconnecting strips 17 and interconnections between the conductive strips 12 and the terminals 16. However, the indium-tin-oxide layer is not left in the central area assigned to the image forming plane. For this reason, if the source electrodes 43 are formed of molybdenum or aluminum sandwiched between molybdenum or aluminum alloy sandwiched between molybdenum, the indium-tin-oxide layer is to be etched by using a sort of etchant inactive to the molybdenum. Oxalic acid-containing etchant may be used in the etching. On the other hand, if the source electrodes 43 are formed of chromium, aluminum or aluminum sandwiched between chromium or titanium, the etchant may be an aqua regia series or a ferric chloride series. The reason why the indium-tin-oxide is removed from the central area assigned to the image-forming plane is that the indium-tin-oxide forms a battery together with aluminum. Even if the indium-tin-oxide is laminated on the source electrodes 43, the indium-tin-oxide layers are liable to peel off due to the battery phenomenon. The indium-tin-oxide layers 63 on the metal layers 61 enhances the reliability of the COG (Chip-On-Glass) mounting. FIG. 7E shows one of the terminal 15/16/18 implemented by the lamination of the metal layer 61 and the indium-tin-oxide layer 63.

[0073] Subsequently, solution of photo-sensitive novolak resin is spread over the resultant structure, and forms a photo-sensitive novolak resin layer of 1 micron thick to 3 microns thick. A pattern image for the proto-bumps is transferred to the photo-sensitive novolak resin layer, and the latent image is developed in alkaline developing solution. Then, bumps are irregularly formed in the insulating layer 51 of the photo-sensitive novolak in the central area assigned to the image-forming plane (see FIG. 6E). The bumps are defined by steep walls. In case where photo-sensitive substance is used for the insulating layer 51, the proto-bumps are produced through the process sequence including the steps of (1) spreading the photo-sensitive substance, (2) pattern transfer to the photo-sensitive substance layer and (3) developing the latent image produced in the photo-sensitive substance layer.

[0074] The insulating layer 51 is formed of either photo-sensitive or photo-insensitive substance. If the photo-insensitive substance is used for the insulating layer 51, the proto-bumps are produced through a process sequence including (1) spreading the photo-insensitive substance, (2) coating the photo-insensitive substance layer with a photo resist layer, (3) pattern transfer to the photo resist layer, (4) developing the latent image, (5) etching the photo-insensitive substance layer by using the patterned photo resist layer and (6) removing the patterned photo resist layer from the upper surface of the photo-insensitive layer. Thus, the usage of photo-sensitive substance makes the process sequence simple.

[0075] Subsequently, the steep walls are made mild. The resultant structure shown in FIG. 6E is placed in a furnace chamber, and the bumps are treated with heat at 80 degrees to 200 degrees in centigrade. The surface portions of the bumps are reflowed in the high temperature ambience, and the steep walls are varied to gentle walls. Thus, the insulating layer 51 is formed with the proto-bumps through the reflow. The proto-bumps may be formed by melting the surface portions in chemicals such as, for example, N-methyl-2-pyrrolidone. The resin is baked at 200 degrees to 250 degrees in centigrade, and the insulating layer 51 with the proto-bumps is obtained as shown in FIG. 6F.

[0076] Subsequently, solution of photo-sensitive novolak is spread over the entire surface of the resultant structure, and forms the photo-sensitive novolak layer of 0.3 micron thick to 1.5 microns thick. A pattern image is transferred to the photo-sensitive novolak layer, and the latent image is developed in the alkaline developing solution. Then, the contact holes 45 are formed in the photo-sensitive novolak layer. The photo-sensitive novolak layer is baked at 200 degrees to 250 degrees in centigrade, and the insulating layer 51 is covered with the insulating layer 52. The contact holes 55 are nested in the contact holes 45, respectively, and the source electrodes 43 are exposed to the contact holes 45, respectively, as shown in FIG. 6G.

[0077] In this instance, the insulating layers 51/52 are formed of the organic compound in the novolak series. Another substance available for the insulating layers 51/52 is PC403 manufactured by JSR. The insulating layers 51 and 52 may be different in substance. For example, acrylic resin and polyimide are selectively used for the insulating layers 51 and 52. A combination of organic substance and inorganic substance may be selectively used for the insulating layers 51 and 52. The combination of silicon nitride and acrylic resin and the combination of silicon oxide and polyimide are examples of the combination of organic compound and inorganic compound. The proto-bumps are formed in the insulating layer 51 of any one of the organic/inorganic substance layer.

[0078] In the first embodiment, the photo-lithographic techniques are used for the insulating layers 51/52. The insulating layers 51/52 may be formed through a printing technique. The printing technique makes the process simple. Other technologies available for the insulating layers 51/52 are a wet process such as, for example, liquid-phase growing techniques and a dry process such as, for example, plasma polymerization techniques. Thus, various insulating substance layers, in which the out-gassing are observed, are referred to as "insulating layers 51/52".

[0079] Subsequently, molybdenum and, thereafter, aluminum-neodymium alloy are deposited to 50 nanometers thick to 200 nanometers thick and 100 nanometers thick to 300 nanometers thick over the resultant structure by using sputtering techniques, and a molybdenum layer and an aluminum-neodymium layer are laminated over the inter-layered insulating layer 32. The molybdenum layer passes through the contact holes 45/55, and is held in contact with the source electrodes 43.

[0080] A photo resist etching mask is prepared on the aluminum-neodymium layer by using the photo-lithographic techniques, and the aluminum-neodymium layer and the molybdenum layer are selectively etched away through a

wet etching at 40 degrees to 60 degrees in centigrade for forming the reflection electrodes **31** as shown in **FIG. 6H**. The wet etchant contains phosphoric acid, acetic acid and nitric acid. Since the reflection electrodes **31** further serve as pixel electrodes, the reflection electrodes **31** are separated at intervals along the conductive strips **11** and conductive strips **12**. The molybdenum layer and the aluminum-neodymium layer are removed from the peripheral area. Thus, the molybdenum layer and the aluminum-neodymium layer are never left on the terminals **15/16/18**. The molybdenum layer serves as a barrier metal between the indium-tin-oxide layer **63** and the aluminum-neodymium layer. While the aluminum-neodymium layer is being patterned, the barrier metal prevents the indium-tin-oxide layer **63** from the wet etchant. If the wet etchant reaches the indium-tin-oxide layer **63**, a battery is undesirably produced between the indium-tin-oxide layer **63** and the aluminum-neodymium layer, and the indium-tin-oxide layer **63** tends to peel off. Thus, the molybdenum layer is to be thick enough to prevent the indium-tin-oxide layers **63** from the wet etchant.

**[0081]** The sputtering conditions are hereinbelow described in detail. First, the resultant substrate structure shown in **FIG. 6G** is inserted into a heating chamber, and the substrate structure is heated in vacuum at 70 degrees to 170 degrees in centigrade for 1-2 minutes. The water is vaporized in the high temperature ambience, and is eliminated from the insulating layers **51/52**. When the water is eliminated from the insulating layers **51/52**, the substrate structure is conveyed from the heating chamber to a sputtering chamber. Vacuum is developed in the sputtering chamber, and the molybdenum and aluminum-neodymium alloy are successively deposited over the substrate structure in the sputtering chamber.

**[0082]** It is preferable that the vacuum is developed in the sputtering chamber independently of the heating chamber. If the heat application and the sputtering are carried out in a single chamber, the vapor out-gassing from the insulating layers **51/52** changes the quality of the sputtered metal/alloy, and the contact resistance between the reflection electrodes and the source electrodes is undesirably increased. If the heating and sputtering are carried out in the same chamber, the heating is prolonged to 2-5 minutes, and the gaseous components are to be perfectly evacuated from the chamber during the sputtering.

**[0083]** The aluminum-neodymium alloy thus deposited under the above-described conditions is free from the cloudy surface, and, accordingly, achieves a high reflectivity. Moreover, the contact resistance between the source electrodes **43** and the reflection electrodes **31** is low and stable.

**[0084]** The substrate temperature may be different between the deposition of molybdenum and the deposition of aluminum-neodymium. It is preferable that the substrate temperature in the deposition of molybdenum is higher than the substrate temperature in the deposition of aluminum-neodymium. For example, the deposition of molybdenum is carried out at substrate temperature of 150 degrees in centigrade, and the substrate temperature in the deposition of aluminum-neodymium is, by way of example, 120 degrees in centigrade. This is because of the fact that the deposition at a relatively low substrate temperature makes the crystal of molybdenum poor. The poor crystal is influential in the crystal of aluminum-neodymium alloy, and the

poor crystals do not permit the wet etchant to form a fine profile in the reflection electrodes **31**. Of course, the substrate temperature may be equal between the deposition of molybdenum and the deposition of aluminum-neodymium alloy.

**[0085]** It is preferable that the aluminum-neodymium alloy contains the neodymium at least 0.5 weight %. The neodymium content equal to or greater than 0.5 weight % is effective against hillock during the firing on the orientation layer **34**, and keeps the reflectivity high. It is further preferable that the substrate structure is maintained at 170 degrees in centigrade or less during the deposition of the aluminum-neodymium alloy. The deposition at 170 degrees in centigrade or less makes the surface morphology on the reflection electrodes **31** equal to or less than 1 micron in average pitches, and the resultant aluminum-neodymium electrodes achieve the reflectivity equal to or greater than 90% to 200 nanometer wavelength to 400 nanometer wavelength light components with respect to the reflectivity to the visible light components at 400 nanometer wavelength. The high reflectivity to the 200 nm to 400 nm wavelength light components is effective against the yellowish image-forming plane regardless of the substance for the orientation layer **34**. However, the neodymium content greater than 10 weight % is not preferable. If the neodymium content exceeds 10 weight %, the reflection electrodes **31** become cloudy, and can not achieve a high reflectivity to the visible light components. Thus, the preferable range of the neodymium content is from 0.5 weight % to 10 weight %.

**[0086]** In this instance, the aluminum-neodymium alloy is desirable from the viewpoint of the high reflectivity and good alignment with the process for fabricating the thin film transistors **14**. However, any metal or alloy is available for the reflection electrodes **31** in so far as the metal/alloy exhibits high reflectivity. Another sort of aluminum alloy such as, for example, aluminum-titanium alloy or aluminum-molybdenum alloy is available for the reflection electrodes **31**. Otherwise, the reflection electrodes **31** may be formed of high-reflective metal such as, for example, silver.

**[0087]** Finally, the orientation layer **34** is formed on the array of reflection electrodes **31**. In detail, organic compound is printed on the resultant structure by using a printing technique. The organic compound layer is 50 nanometers thick to 100 nanometers thick. The organic compound layer is baked at 200 degrees to 230 degrees in centigrade, and is oriented. As a result, the substrate structure **10** is obtained.

**[0088]** The other substrate structure **20** is fabricated on the transparent insulating substrate **20** independently of the above-described process sequence. The color filters **21** are patterned on the transparent insulating substrate **20a**, and the indium-tin-oxide is deposited over the color filters **21** for forming the counter electrode **33**. The black matrix **22** is formed in the peripheral area around the color filters **21**. The organic compound of 50 nanometers thick to 100 nanometers thick is printed on the counter electrode **33**, and the organic compound layer is baked at 200 degrees to 230 degrees in centigrade. The orientation layer **34** is completed through the orientation process. It is preferable that the organic compound makes the orientation layer achieve transparency equal to or greater than 95% to the light components from 300 nanometer wavelength to 600 nanometer wavelength.

[0089] The spherical spacers 35 of synthetic resin are scattered in the central area of the substrate structure 10, and sealing agent of epoxy resin series is provided on the peripheral area along the edges of the substrate structure. The substrate structures 10 and 20 are opposed to each other as shown in FIG. 6I, and are assembled. The spherical spacers 35 keep the substrate structures 10 and 20 spaced by a predetermined gap. The sealing layer has an opening (see FIG. 4), and the liquid crystal LC2 is injected through the opening into the gap. The opening is closed with a piece of ultra-violet curable resin 24 in the acylate series, and the piece of ultra-violet curable resin 24 is solidified. Thus, the liquid crystal LC2 is confined in the space between the substrate structures 10 and 20.

[0090] The quarter wavelength plate 37 and the polarization plate 38 are successively adhered to the transparent insulating substrate 20a. Though not shown in the drawings, the semiconductor chip is mounted on the peripheral area of the resultant structure, and the conductive pads of the semiconductor chip is connected to the terminals 15/16/18 for the scanning signal, data signal and the common voltage.

[0091] As will be understood from the foregoing description, the liquid crystal display panel according to the present invention includes the reflection electrodes with the smooth surface morphology at average pitches equal to or less than 1 micron. The smooth surface morphology reduces the light absorption in the light ranging from 200 nanometer wavelength to 400 nanometer wavelength, and prevents the image-forming plane from being yellowed.

[0092] Moreover, while the aluminum-neodymium alloy is growing at the substrate temperature equal to or less than 170 degrees in centigrade, the surface morphology of the aluminum-neodymium alloy layer is equal to or less than 1.0 micron in average pitches.

#### Second Embodiment

[0093] Another liquid crystal display panel embodying the present invention is similar to the first embodiment except an inter-layered insulating layer between the array of thin film transistors 14 and the reflection electrodes 31. For this reason, the other layers, strips and substrates are labeled with the references same as those designating corresponding layers, strips and substrates incorporated in the first embodiment. Description is hereinbelow made on a process for fabricating the liquid crystal display panel implementing the second embodiment with reference to FIGS. 5, 6A-6D, 7A-7E and 8A-8E. FIGS. 8A-8E shows the cross section taken along line B-B of FIG. 5.

[0094] The process comprises the steps of (1) patterning a metal layer into the gate electrodes 41 and the conductive strips 11 for the scanning signal, (2) patterning the undoped/n+ amorphous silicon layers on the gate insulating layer 53 into the active layers 41, (3) patterning a metal layer into the drain/source electrodes 42/43 and the conductive strips 12 for the data signal, (4) forming the passivation layer 54, (5) patterning the transparent conductive layer into the terminal connecting electrodes 63, (6) forming bumps in an inter-layered insulating layer 71 and (7) patterning the alloy layer into the reflection electrodes 31.

[0095] The process starts with preparation of the transparent insulating substrate 10a, and the steps (1) to (5) are

similar to those of the first embodiment. The array of thin film transistors 14, passivation layer 54, terminals 15 for the scanning signal, terminals 16 for the data signal and the terminals 18 for the common voltage are patterned on or over the transparent insulating substrate 10a as shown in FIGS. 7E and 8A.

[0096] Subsequently, photo-sensitive novolak resin is spread over the resultant structure, and forms a photo-sensitive novolak resin layer 71 of 2.0 to 4.5 microns thick. A half-tone mask is aligned with the resultant structure, and a pattern image is transferred from the half-tone mask to the photo-sensitive novolak resin layer 71 as shown in FIG. 8B. The half-tone mask has a transparent pattern, a semi-transparent pattern and a non-transparent pattern. The transparent pattern is transparent to the exposure light, and the non-transparent pattern does not pass the exposure light. The exposure light is partially absorbed in the semi-transparent pattern. The non-transparent pattern is assigned to a region 72a not to be etched, i.e., high land portions of the inter-layered insulating layer 71, and the semi-transparent pattern is assigned to the region 72b partially to be etched, i.e., valleys in the inter-layered insulating layer 71. The transparent pattern is assigned to the other portion 72c to be completely etched. The half-tone mask is designed in such a manner that the semi-transparent pattern is adjacent to the transparent pattern. The half-tone mask is radiated with light, and image-carrying light is fallen onto the photo-sensitive novolak resin layer 71. The image-carrying light forms a latent image in the photo-sensitive novolak resin layer 71.

[0097] The latent image is developed. The region aligned with the non-transparent pattern is left on the structure, and the region aligned with the transparent pattern is removed from the structure. The region aligned with the semi-transparent pattern is partially etched so that the valleys are formed in the inter-layered insulating layer 71. The semi-transparent pattern is adjacent to the transparent pattern. In other words, the non-transparent pattern is not contiguous to the transparent pattern. Although bumps are formed in the inter-layered insulating layer 71, the inter-layered insulating layer 71 has a gentle contour as shown in FIG. 8C.

[0098] The half-tone mask varies the intensity of the exposure light, and the latent image has dispersion in depth corresponding to the dispersion in the light intensity. The latent image may be formed by varying the exposure time. Thus, the bumps are formed in the single inter-layered insulating layer 71. The inter-layered insulating layer 71 is corresponding to the two insulating layers 51 and 52. Thus, the bumps are formed through a relatively simple sequence.

[0099] Subsequently, the resultant structure is treated with heat at 80 degrees to 200 degrees in centigrade, and the inter-layered insulating layer 71 is reflowed. The surface of the inter-layered insulating layer 71 becomes gentle. The gentle surface may be created by using chemicals. The inter-layered insulating layer is baked at 200 degrees to 250 degrees in centigrade, and proto-bumps are formed in the inter-layered insulating layer 71 as shown in FIG. 8D.

[0100] The remaining process sequence is similar to that of the first embodiment. Molybdenum and aluminum-neodymium are successively deposited to 50 nanometers thick to 200 nanometers thick and 100 nanometers thick to 300 nanometers thick over the entire surface of the resultant

structure by using the sputtering. The preliminary heating and the sputtering conditions are similar to those of the first embodiment. The aluminum-neodymium layer and the molybdenum layer are patterned into the reflection electrodes 31 through the photo-lithography and etching as shown in **FIG. 8E**. The reflection electrodes 31 have the smooth surface morphology with the average pitches equal to or less than 1.0 micron.

**[0101]** The array of reflection electrodes 31 and the exposed surface of the inter-layered insulating layer 71 are covered with the orientation layer 34. The other substrate structure 20 is fabricated as similar to that of the first embodiment. The substrate structures 10 and 20 are assembled together, and liquid crystal is sealed in the gap between the substrate structures 10 and 20.

**[0102]** The reflection electrodes 31 has the smooth surface morphology with the average pitches equal to or less than 1.0 micron, and achieve the large reflectivity to 200 nanometer wavelength light component to 400 nanometer wavelength component. The large reflectivity to these light components is effective against the yellowish image-forming plane.

**[0103]** Since the reflective material is grown under the conditions same as those in the first embodiment, the smooth surface morphology is achieved. Moreover, the proto-bumps are formed in the inter-layered insulating layer 71 through the simple sequence, and the production cost is reduced.

**[0104]** The half-tone mask may be replaced with a set of photo masks. In this instance, the latent image for the region 72b to be partially etched is produced by using one of the photo masks, and the latent image for the region 72c to be completely etched is produced by using the other photo mask. Otherwise, the patent image may be produced by using another kind of half-tone mask, which has an extremely fine pattern, which exceeds the resolution limit of the exposure light, and the light passing through the extremely fine pattern produces the latent image for the region to be partially etched.

### Third Embodiment

**[0105]** Turning to **FIG. 9** of the drawings, some pixels occupy the periphery of the central area assigned to an array of color pixels incorporated in yet another liquid crystal display panel embodying the present invention. The liquid crystal display panel implementing the third embodiment is categorized in the reflective-transparent liquid crystal display panel. An inverted staggered type thin film transistor 14, a reflection electrode 31, a counter electrode 33 (see **FIG. 10K**), a transparent pixel electrode 81, a color filter 21 (see **FIG. 10K**) and a piece of liquid crystal form in combination a pixel, and a pixel with the red filter, pixel with the green filter and a pixel with the blue filter as a whole constitute a color pixel as similar to that of the first embodiment.

**[0106]** Conductive strips 11 for a scanning signal are arranged in parallel on a transparent insulating substrate 10a, and are respectively connected to the gate electrodes 41 of the thin film transistors 14 in the associated rows. Conductive strips 13 for the common voltage are arranged in parallel to the conductive strips 11, and are alternated with the conductive strips 11. The conductive strips 13 have wide

portions at intervals. Conductive strips 12 for a data signal extend in a direction perpendicular to the conductive strips 11/13, and are connected to the drain electrodes 42 of the thin film transistors 14 in the associated columns. Thus, the conductive strips 11 and the conductive strips 12 are arranged over the transparent insulating substrate 10a like a lattice, and define rectangular regions, which are respectively assigned to the pixels. The thin film transistor 14 and the wide portion occupy the associated rectangular region, and are overlapped with the associated reflection electrode 31 and the transparent pixel electrode 81. The reflection electrode 31 is connected to the source electrode 43 of the associated thin film transistor 14, and is electrically connected to the transparent pixel electrode 81. The transparent pixel electrode 81 is surrounded by the associated reflection electrode 31, and the outer periphery of the transparent pixel electrode 81 is held in contact with the inner periphery of the reflection electrode 31. Thus, the conductive strip 12 for the data signal is electrically connectable through the thin film transistor 14, i.e., the drain electrode 42, active layer 44 and the source electrode 43 to the reflection/transparent pixel electrodes 31/81, and a piece of data information representative of a part of image to be produced is written into the reflection/transparent pixel electrodes 31/81.

**[0107]** An inter-layered insulating layer 54/51/52 intervenes between the array of thin film transistors 14 and the reflection/transparent pixel electrodes 31/81 so that holding capacitors are provided in associated with the thin film transistors 14, respectively. Proto-bumps are formed in the inter-layered insulating layer 54/51/52, and are transferred to the reflection electrodes 31. The reflective substance is deposited under predetermined conditions so that the reflection electrodes 31 have smooth surface-morphology. The surface morphology is featured by the ruggedness at average intervals equal to or less than 1.0 micron.

**[0108]** Description is hereinbelow made on a process for fabricating the liquid crystal display panel with reference to **FIGS. 10A to 10K** and **FIGS. 7A to 7E**. **FIGS. 10A to 10K** shows the cross section taken along line B-B of **FIG. 9**. The process sequence of the third embodiment is similar to that of the first embodiment except the step for forming the transparent pixel electrode 81. The process sequence implementing the third embodiment comprises the steps of (1) patterning a metal layer into the gate electrodes 41, metal layers 61 and the conductive strips 11/13, (2) patterning undoped/n+ amorphous silicon layers on the gate insulating layer 53 into the active strips 44, (3) patterning a metal layer into the source/drain electrodes 42/43 and the conductive strips 12, (4) patterning an insulating layer on the passivation layer 54 into proto-bumps, (5) covering the proto-bumps with another insulating layer, (6) forming source contact holes 45 in the passivation layer 54, (7) patterning a transparent conductive layer into the terminal connecting electrodes 63 and the transparent pixel electrode 81 and (8) patterning a reflective metal layer into the reflection electrodes 31.

**[0109]** The transparent insulating substrate 10a is prepared, and a chromium layer is patterned into the gate electrodes 41, conductive strips 11 for the scanning signal and the conductive strips 13 for the common voltage as shown in **FIG. 10A**. The gate electrodes 41 and the conductive strips 11/13 are covered with the gate insulating layer 53, and the undoped amorphous silicon layer 44a and

the heavily doped n-type amorphous silicon layer **44b** are deposited over the gate insulating layer **53**. The undoped/n+ amorphous silicon layers **44a/44b** are patterned into the active layer **44** as shown in **FIG. 10B**. A chromium layer is deposited over the entire surface of the resultant structure, and is patterned into the drain/source electrodes **42/43** and the conductive strips **12**. Both end portions of each active layer **44** is covered with the source and drain electrodes **43** and **42**, and the n+ amorphous silicon layer **44b** is partially etched away by using the drain/source electrodes **42/43** as an etching mask as shown in **FIG. 10C**. Thus, the array of thin film transistors **14** are formed on the transparent insulating substrate **10a**. The array of thin film transistors **14** is covered with the passivation layer **54**. However, the source contact holes **45** are not formed in the passivation layer **54**. Thus, the process sequence is similar to that of the first embodiment until the formation of the source contact holes **45** in the passivation layer **54**.

**[0110]** The insulating layer **51** is patterned into bumps (see **FIG. 10E**), and the surface portions of the bumps are reflowed so as to be made gentle. The proto-bumps are formed in the insulating layer **51** as shown in **FIG. 10F**. The proto-bumps are covered with the insulating layer **52** as shown in **FIG. 10G**. Thus, the steps (4) and (5) are corresponding to the steps (6) and (7) of the process implementing the first embodiment. A difference is exposure to light without any mask after the latent images in the insulating layers **51/52** are developed. The exposure to light is effective against coloring. Since the liquid crystal display panel is of the reflective-transparent type, the anti-coloring treatment is preferable.

**[0111]** The gate insulating layer **53** and/or passivation layer **54** are selectively etched away so as to form the source contact holes **55** and the terminal contact holes **62** (see **FIGS. 10H and 7D**), and the source electrodes **43** and the metal layers **61** are exposed to the source contact holes **55** and the terminal contact holes **62**. Contact holes are concurrently formed in the gate insulating layer **53** and the passivation layer **54**, and end portions of the conductive strips **13**, the metal layers **61** for the terminals **16** and end portions of the conductive strips **12** close to the terminals **12** are exposed to the contact holes, respectively.

**[0112]** Subsequently, indium-tin-oxide is deposited to 40 nanometers thick to 100 nanometers thick over the resultant structure by using the sputtering. The indium-tin-oxide layer is patterned into the transparent pixel electrodes **81**, connecting electrodes **63** for the terminals **15/16/18**, the common connecting strips **17** and interconnection between the terminals **16** and the conductive strips **12**. The growth of the indium-tin-oxide is carried out as similar to the growth of the reflecting substance for the reflection electrodes **31** so as to prevent the transparent pixel electrodes **81** from the outgassing. Since, the indium-tin-oxide layer is removed from the contact holes **55**, the source electrodes **43** are still exposed to the source contact holes **55**. The resultant structure is shown in **FIGS. 10I and 7E**.

**[0113]** Subsequently, molybdenum and aluminum-neodymium are successively deposited to 50 nanometers thick to 200 nanometers thick and 100 nanometers thick to 300 nanometers thick over the entire surface of the resultant structure by using the sputtering, and the molybdenum layer and the aluminum-neodymium layer are patterned into the

reflection electrodes **31** as shown in **FIG. 10J**. Namely, the molybdenum layer and the aluminum-neodymium layer are removed from narrow areas along the conductive strips **11** and **12** and from the peripheral area assigned to the terminals. Thus, the reflection electrodes **31** are electrically isolated from one another. The reflection electrodes **31** are held in contact with the source electrodes **43** of the associated thin film transistors **14** through the source contact holes **55**, respectively. The inner periphery of each of the reflection electrodes **31** is held in contact with the outer periphery of the associated transparent pixel electrode **81**. The molybdenum layer intervenes between the transparent pixel electrodes **81** and the aluminum-neodymium layer, and the photo resist etching mask is left over the outer peripheries of the transparent pixel electrodes **81**. Although the aluminum-neodymium layer and the molybdenum layer are patterned by using etchant, the photo resist etching mask does not allow the etchant to penetrate into the gap between the transparent pixel electrodes **81** and the molybdenum layer. Any battery is not produced between the transparent pixel electrodes **81** and the aluminum-neodymium layer. The transparent pixel electrodes **81** are not damaged, and never peels off from the insulating layer **52**.

**[0114]** The orientation layer **34** is formed on the array of the reflection electrodes **31** and the exposed surface of the insulating layer **52**, and the substrate structure **10** is completed. The other substrate structure **20** is prepared separately from the substrate structure **10**. The substrate structures **10** is aligned with the other substrate structure **20** as shown in **FIG. 10K**, and the liquid crystal is sealed in the gap between the substrate structures **10** and **20**.