US 20030231735A1

(19) **United States**

(12) **Patent Application Publication**

**Moon et al.**

(10) **Pub. No.: US 2003/0231735 A1**

(43) **Pub. Date: Dec. 18, 2003**

(54) **METHOD OF DRIVING A SHIFT REGISTER, A SHIFT REGISTER, A LIQUID CRYSTAL DISPLAY DEVICE HAVING THE SHIFT REGISTER**

**Publication Classification**

(51) **Int. Cl. 7** ..... **G11C 19/00**

(52) **U.S. Cl.** ..... **377/64**

(76) Inventors: **Seung-Hwan Moon**, Yongin-si (KR);

**Back-Won Lee**, Seoul (KR)

(57) **ABSTRACT**

Correspondence Address:

**CANTOR COLBURN LLP**

**55 Griffin Road South**

**Bloomfield, CT 06002 (US)**

(21) Appl. No.: **10/460,856**

(22) Filed: **Jun. 13, 2003**

(30) **Foreign Application Priority Data**

Jun. 15, 2002 (KR) ..... 2002-33455

Jul. 2, 2002 (KR) ..... 2002-37946

Jul. 6, 2002 (KR) ..... 2002-39129

Feb. 4, 2003 (KR) ..... 2003-6683

In a shift register and LCD device having the shift register that may be employed in the liquid crystal display device having a large screen size and a large resolution, the shift register includes stages cascade-connected with each other and each of the stages have a carry buffer for generating a carry signal. The pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. A power voltage  $V_{ON}$  applied to a clock generator is applied to the shift register. A signal delay due to the RC delay of the gate lines may be minimized, the shift register is independent of the variation of the threshold voltage of the TFTs, and image display quality may not be deteriorated.

**FIG.1**

**(PRIOR ART)**

FIG. 2

(PRIOR ART)

FIG. 3

FIG. 4

FIG. 5

164

FIG. 6

FIG. 7

FIG. 8

FIG. 9

## FIG. 10

FIG.11

FIG. 12

FIG. 13

FIG. 14

FIG. 15A

FIG. 15B

FIG. 15C

FIG. 16A

FIG. 16B

FIG. 16C

FIG. 17

174

FIG. 18

FIG. 19A

FIG. 19B

FIG. 20

FIG. 21

174

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG.27

FIG. 28

FIG. 29

FIG. 30

FIG. 31

FIG. 32

**METHOD OF DRIVING A SHIFT REGISTER, A SHIFT REGISTER, A LIQUID CRYSTAL DISPLAY DEVICE HAVING THE SHIFT REGISTER**

**CROSS-REFERENCE TO RELATED APPLICATIONS**

[0001] This application relies for priority upon Korean Patent Application No. 2002-33455 filed on Jun. 15, 2002, Korean Patent Application No. 2002-37946 filed on Jul. 2, 2002, Korean Patent Application No. 2002-39129 filed on Jul. 6, 2002 and Korean Patent Application No. 2003-6683 filed on Feb. 4, 2003, the contents of which are herein incorporated by reference in their entirety.

**BACKGROUND OF THE INVENTION**

[0002] 1. Field of the Invention

[0003] The present invention relates to a method of driving a shift register, a shift register, and a liquid crystal display (LCD) device having the shift register. More particularly, the present invention relates to a method of driving a shift register that may be used in an a-Si thin film transistor liquid crystal display device (a-Si TFT LCD) having a large display screen, a shift register, and a liquid crystal display (LCD) device having the shift register.

[0004] 2. Description of the Related Art

[0005] The TFT LCD device is classified into amorphous-Si TFT LCD (or a-Si TFT LCD) device and a poly-Si TFT LCD device. The poly-silicon TFT LCD (or poly-Si TFT LCD) device has lower power consumption and a low price, but is manufactured through complex processes compared with the a-Si TFT LCD device. Accordingly, the poly-Si TFT LCD is used in a display device having a small display screen such as a mobile phone.

[0006] The a-Si TFT LCD device may provide a large display screen and a high yield (or high productivity), and is used in a display device having a large display screen such as a laptop computer, an LCD monitor or a high definition television (HDTV).

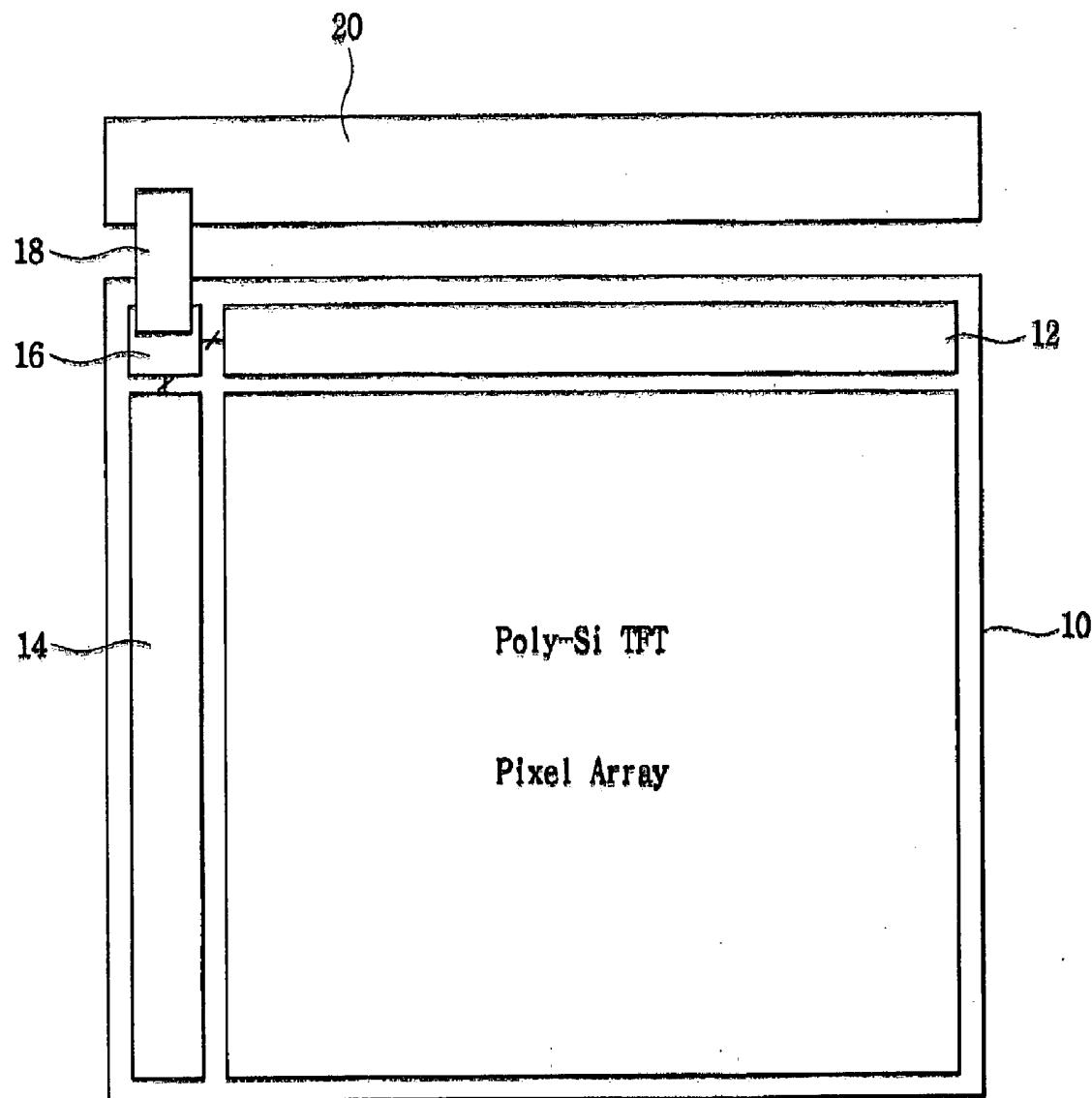

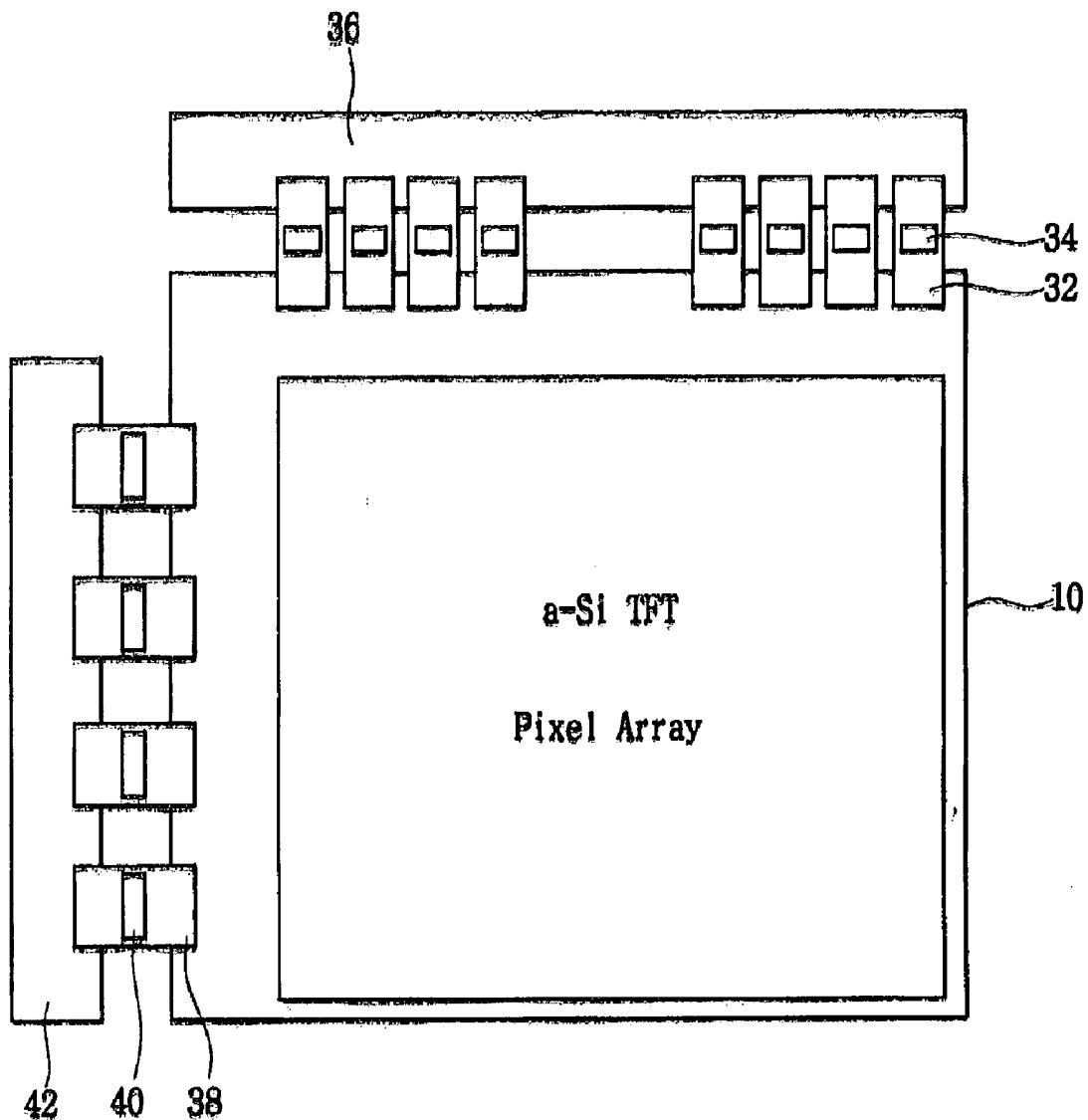

[0007] FIG. 1 is a schematic view showing a conventional poly-silicon thin film transistor LCD, and FIG. 2 is a schematic view showing a conventional a-Si thin film transistor LCD.

[0008] As shown in FIG. 1, the poly-Si TFT LCD device includes a poly-Si TFT pixel array formed on a glass substrate 10. A data driver circuit 12 and a gate driver circuit 14 are formed on the glass substrate 10. An integrated printed circuit board 20 is connected to a terminal part 16 by means of a film cable 18, so that the cost for manufacturing the poly-Si TFT LCD device may be reduced, the thickness of the poly-Si TFT LCD device may be reduced, and power consumption may be minimized because the data driver circuit 12 and the gate driver circuit 14 are integrated on the glass substrate 10.

[0009] However, as shown in FIG. 2, in the a-Si TFT LCD device, a data driver chip 34 is mounted on a flexible printed circuit board 32 via a chip on film (COF), and a data printed circuit board 36 is connected to a data line terminal on the a-Si TFT pixel array through the flexible printed circuit board 32. A gate driver chip 40 is mounted on the flexible printed circuit board 32 via the chip on film (COF), and a

gate printed circuit board 42 is connected to a gate line terminal on the a-Si TFT pixel array through a flexible printed circuit board 40.

[0010] The a-Si TFT LCD device has an advantage in aspect of yield (or productivity), but has disadvantage in aspect of manufacturing cost and thickness.

[0011] In addition, in an a-Si TFT LCD device used for displaying an image on a large display screen having a high resolution, the gate driver circuit need to rapidly discharge electric charges accumulated (or charged) at the gate lines connected to pixels. The gate lines have a capacitive load.

[0012] However, deterioration of display quality may occur when the conventional gate driver circuit is used in the a-Si TFT LCD device having a large display screen.

**SUMMARY OF THE INVENTION**

[0013] Accordingly, the present invention is provided to substantially obviate one or more problems due to limitations and disadvantages of the related art.

[0014] It is an aspect of the present invention to provide a shift register, which may drive an a-Si TFT LCD device used for displaying an image on a large display screen having a high resolution.

[0015] It is another aspect of the present invention to provide a liquid crystal display device having above shift register.

[0016] It is still another aspect of the present invention to provide a method of driving above the shift register.

[0017] In one aspect of the present invention, there is provided a shift register including a plurality of cascade-connected stages. The stages receive a first clock signal and a second clock signal to sequentially produce a plurality of scan line driving signals for selecting a plurality of scan lines. Each of the stages includes a carry buffer, a pull-up part, a pull-down part, a pull-up driver part and a pull-down driver part. The carry buffer provides a next stage with a carry signal corresponding to the first clock signal or the second clock signal, and the second clock signal has an inverted phase with respect to the first clock signal. The pull-up part provides an output terminal with a first scan line driving signal corresponding to the first clock signal or the second clock signal. The pull-down part provides the output terminal with a first power voltage. The pull-up driver part turns on the pull-up part in response to the carry signal provided from a previous stage and turns off the pull-up part in response to a second scan line driving signal of the next stage. The pull-down driver part turns off the pull-down part in response to the carry signal provided from the previous stage and turns on the pull-up part in response to the second scan line driving signal of the next stage.

[0018] In another aspect of the present invention, there is provided a liquid crystal display device including a display cell array, a data driver circuit and a gate driver circuit. The display cell array is formed on a transparent substrate and includes a plurality of gate lines, a plurality of data lines and a plurality of switching elements. The switching elements are coupled to the gate lines and the data lines. The data driver circuit provides each of the data lines with an image signal. The gate driver circuit includes a shift register, and the shift register includes a plurality of cascade-connected

stages. The stages receive a first clock signal and a second clock signal to sequentially produce a plurality of gate line driving signals for selecting the gate lines. Each of the stages includes a carry buffer, a pull-up part, a pull-down part, a pull-up driver part and a pull-down driver part. The carry buffer provides a next stage with a carry signal corresponding to the first clock signal or the second clock signal, and the second clock signal has an inverted phase with respect to the first clock signal. The pull-up part provides an output terminal with a first gate driving signal corresponding to the first clock signal or the second clock signal. The pull-down part provides the output terminal with a first power voltage. The pull-up driver part turns on the pull-up part in response to the carry signal provided from a previous stage and turns off the pull-up part in response to a second gate line driving signal of the next stage. The pull-down driver part turns off the pull-down part in response to the carry signal provided from the previous stage and turns on the pull-up part in response to the second gate line driving signal of the next stage.

[0019] In further another aspect of the present invention, there is provided a method of driving a shift register. The shift register includes a plurality of cascade-connected stages. The stages receive a first clock signal and a second clock signal to sequentially produce a plurality of scan line driving signals for selecting a plurality of scan lines. A next stage is provided with a carry signal corresponding to the first clock signal or the second clock signal, and the second clock signal has an inverted phase with respect to the first clock signal. Then, a first scan line driving signal corresponding to the first clock signal or the second clock signal is produced in response to the carry signal outputted from a previous stage. A first voltage level of the first scan line driving signal outputted from a present stage is lowered in response to a second scan line driving signal outputted from the next stage.

[0020] In still another aspect of the present invention, there is provided a shift register including a plurality of cascade-connected stages. A first stage receive a scan start signal, and the stages receive a first clock signal and a second clock signal to sequentially produce a plurality of scan line driving signals for selecting a plurality of scan lines. Each of the stages includes a first carry buffer, a pull-up part, a pull-down part, a pull-up driver part, and a pull-down driver part and a second carry buffer. The first carry buffer provides a next stage with a first carry signal corresponding to the first clock signal or the second clock signal, and the second clock signal has an inverted phase with respect to the first clock signal. The pull-up part provides a first output terminal with a first scan line driving signal corresponding to the first clock signal or the second clock signal. The pull-down part provides the first output terminal with a first power voltage. The pull-up driver part turns on the pull-up part in response to a second carry signal outputted from the first carry buffer of a previous stage and turns off the pull-up part in response to a second scan line driving signal of the next stage. The pull-down driver part turns off the pull-down part in response to the first carry signal provided from the first carry buffer of the previous stage and turns on the pull-up part in response to the second scan line driving signal of the next stage. The second carry buffer lowers a first voltage level of the second carry signal, and the first carry signal is outputted from the first carry buffer of the previous stage to be applied to the pull-up part.

[0021] In still another aspect of the present invention, there is provided a liquid crystal display device including a display cell array, a data driver circuit and a gate driver circuit. The display cell array is formed on a transparent substrate and includes a plurality of gate lines, a plurality of data lines and a plurality of switching elements. The switching elements are coupled to the gate lines and the data lines. The data driver circuit provides each of the data lines with an image signal. The gate driver circuit includes a shift register, and the shift register includes a plurality of cascade-connected stages. The stages receive a first clock signal and a second clock signal to sequentially produce a plurality of gate line driving signals for selecting the gate lines. Each of the stages includes a first carry buffer, a pull-up part, a pull-down part, a pull-up driver part, and a second carry buffer. The first carry buffer provides a next stage with a first carry signal corresponding to the first clock signal or the second clock signal, and the second clock signal has an inverted phase with respect to the first clock signal. The pull-up part provides a first output terminal with a first scan line driving signal corresponding to the first clock signal or the second clock signal. The pull-down part provides the first output terminal with a first power voltage. The pull-up driver part turns on the pull-up part in response to a second carry signal outputted from the first carry buffer of a previous stage and turns off the pull-up part in response to a second scan line driving signal of the next stage. The pull-down driver part turns off the pull-down part in response to the first carry signal provided from the first carry buffer of the previous stage and turns on the pull-up part in response to the second scan line driving signal of the next stage. The second carry buffer lowers a first voltage level of the second carry signal, and the first carry signal is outputted from the first carry buffer of the previous stage to be applied to the pull-up part.

[0022] In still another aspect of the present invention, there is provided a shift register including a plurality of cascade-connected stages. The stages receive a first clock signal and a second clock signal to sequentially produce a plurality of scan line driving signals for selecting a plurality of scan lines. Each of the stages includes a pull-up switching device, a first pull-up driver switching device, a second pull-up driver switching device, a first pull-down driver switching device, a pull-down driver switching device and a second pull-down driver switching device. The pull-up switching device provides an output terminal of each of the stages with a first scan line driving signal corresponding to the first clock signal or the second clock signal. The first pull-up driver switching device turns on the pull-up switching device in response to a scan start signal or a second scan line driving signal outputted from a previous stage. The second pull-up driver switching device turns off the pull-up switching device in response to a third scan line driving signal outputted from a next stage. The first pull-down driver switching device provides the output terminal with a first power voltage. The pull-down driver switching device turns off the pull-down switching device in response to the scan start signal or the second scan line driving signal outputted from the previous stage. The second pull-down driver switching device is turned on in response to the third scan line driving signal to provide the output terminal with the first power voltage.

[0023] In still another aspect of the present invention, there is provided a liquid crystal display device including a display cell array, a data driver circuit and a gate driver

circuit. The display cell array is formed on a transparent substrate and includes a plurality of gate lines, a plurality of data lines and a plurality of switching elements. The switching elements are coupled to the gate lines and the data lines. The data driver circuit provides each of the data lines with an image signal. The gate driver circuit includes a shift register, and the shift register includes a plurality of cascade-connected stages. The stages receive a first clock signal and a second clock signal to sequentially produce a plurality of gate line driving signals for selecting the gate lines. Each of the stages includes a pull-up switching device, a first pull-up driver switching device, a second pull-up driver switching device, a first pull-down switching device, a pull-down driver switching device and a second pull-down switching device. The pull-up switching device provides an output terminal of each of the stages with a first gate line driving signal corresponding to the first clock signal or the second clock signal. The first pull-up driver switching device turns on the pull-up switching device in response to a scan start signal or a second gate line driving signal outputted from a previous stage. The second pull-up driver switching device turns off the pull-up switching device in response to a third gate line driving signal outputted from a next stage. The first pull-down switching device provides the output terminal with a first power voltage. The pull-down driver switching device turns off the pull-down switching device in response to the scan start signal or the second gate line driving signal outputted from the previous stage. The second pull-down switching device is turned on in response to the third gate line driving signal to provide the output terminal with the first power voltage.

[0024] In still another aspect of the present invention, there is provided a shift register including a plurality of cascade-connected stages. The stages receive a first clock signal and a second clock signal to sequentially produce a plurality of scan line driving signals for selecting a plurality of scan lines. Each of the stages includes a first pull-up driver switching device, a pull-up switching device, a first pull-down switching device, a second pull-down switching device, a capacitor, a second pull-up driver switching device, a third pull-up driver switching device, a first pull-up driver switching device and a second pull-down driver switching device. A first electrode of the first pull-up driver switching device receives a second power voltage, a second electrode of the first pull-up driver switching device receives a scan start signal or a first scan line driving signal outputted from a previous stage, and a third electrode of the first pull-up driver switching device is coupled to a first node. A fourth electrode of the pull-up switching device receives the first clock signal or the second clock signal, a fifth electrode of the pull-up switching device is coupled to the first node, and a sixth electrode of the pull-up switching device is coupled to an output terminal. A seventh electrode of the first pull-down switching device is coupled to the output terminal, an eighth electrode of the first pull-down switching device is coupled to a second node, and a ninth electrode of the first pull-down switching device receives a first power voltage. A tenth electrode of the second pull-down switching device is coupled to the output terminal, an eleventh electrode of the second pull-down switching device receives a second gate line driving signal outputted from a next stage, and a twelfth electrode of the second pull-down switching device receives the first power voltage. The capacitor is coupled between the first node and the output terminal. A

thirteenth electrode of the second pull-up driver switching device is coupled to the first node, a fourteenth electrode of the second pull-up driver switching device receives the second gate line driving signal outputted from the next stage, and a fifteenth electrode of the second pull-up driver switching device receives the first power voltage. A sixteenth electrode of the third pull-up driver switching device is coupled to the first node, a seventeenth electrode of the third pull-up driver switching device is coupled to the second node, and an eighteenth electrode of the third pull-up driver switching device receives the first power voltage. A nineteenth electrode of the first pull-up driver switching device and a twentieth electrode of the first pull-up driver switching device are commonly coupled with each other to receive the second power voltage, and a twenty first electrode of the first pull-up driver switching device is coupled to the second node. A twenty second electrode of the second pull-down driver switching device is coupled to the second node, a twenty third electrode of the second pull-down driver switching device is coupled to the first node, and a twenty fourth electrode of the second pull-down driver switching device receives the first power voltage.

[0025] In still another aspect of the present invention, there is provided a method of driving a shift register. The shift register includes a plurality of cascade-connected stages, and the stages receive a first clock signal and a second clock signal to sequentially produce a plurality of scan line driving signals for selecting a plurality of scan lines. The first clock signal or the second clock signal is received, and each of the stages is provided with the first clock signal or the second clock signal. The first clock signal and the second clock signal have substantially a first voltage level corresponding to the first voltage level of a first power voltage. A second power voltage is generated, and each of the stages is provided with the second power voltage. The second power voltage has a second voltage level higher than the first voltage level by a predetermined voltage level. A first scan line driving signal for selecting a first scan line coupled to a present stage is generated. A third voltage level of the first scan line driving signal is lowered to a fourth voltage level lower than the third voltage level in response to a second scan line driving signal outputted from a next stage. The first scan line is provided with the first scan line driving signal having the fourth voltage level. The fourth voltage level of the first scan line driving signal is maintained for a predetermined period when a voltage level of an output signal of a pull-down switching device is changed from a fifth voltage level to a sixth voltage level higher than the fifth voltage level after lowering the third voltage level of the first scan line driving signal.

[0026] In still another aspect of the present invention, there is provided a method of driving a shift register. The shift register includes a plurality of cascade-connected stages, and the stages alternately receive a first clock signal and a second clock signal generated from a clock generator to sequentially generate a plurality of scan line driving signals for selecting a plurality of scan lines. The first and second clock signal have substantially a first voltage level corresponding to the first voltage level of a first power voltage. Each of the stages includes a pull-up switching device, a first pull-up driver switching device, a second pull-up driver switching device, a pull-down switching device and a pull-down driver switching device. The pull-up switching device provides an output terminal of each of the

stages with a first scan line driving signal corresponding to the first clock signal or the second clock signal. The first pull-up driver switching device turns on the pull-up switching device in response to a scan start signal or a second scan line driving signal outputted from a previous stage. The second pull-up driver switching device turns off the pull-up switching device in response to a third scan line driving signal outputted from a next stage. The pull-down switching device provides the output terminal with a third power voltage. The pull-down driver switching device turns off the pull-down switching device in response to the scan start signal or the second scan line driving signal outputted from the previous stage. The first clock signal or the second clock signal is received, and each of the stages is provided with the first clock signal or the second clock signal. A second power voltage is generated, and each of the stages is provided with the second power voltage. The second power voltage has a second voltage level higher than the first voltage level by a predetermined voltage level. A first scan line driving signal for selecting a first scan line coupled to a present stage is generated during a high level period of the first clock signal or the second clock signal. A third voltage level of the first scan line driving signal is lowered to a fourth voltage level lower than the third voltage level in response to the third scan line driving signal outputted from the next stage. The first scan line is provided with the first scan line driving signal having the fourth voltage level. The fourth voltage level of the first scan line driving signal for a predetermined period is maintained when a voltage level of an output signal of the pull-down switching device is changed from a fifth voltage level to a sixth voltage level higher than the fifth voltage level after lowering the third voltage level of the first scan line driving signal.

[0027] As described above, according to the shift register of this invention, the shift register includes a plurality of stages and a carry buffer transistor for generating a carry signal. A signal delay due to the RC delay of the gate lines may be minimized in the liquid crystal display device having a large screen size and a large resolution.

[0028] The carry signal is independent of the output signal that is outputted from the output terminal of a present stage and is transferred to the gate lines by the carry buffer transistor disposed in the present stage. Therefore, the effect of the RC loads due to the gate lines may be prevented.

[0029] In addition, since the next stage is not reset by the gate line driving signal but is reset by the clock signal, image display quality may not be deteriorated.

[0030] In addition, in the liquid crystal display device having a large screen size and a large resolution, the shift register is independent of the variation of the threshold voltage of the thin film transistors, and thus the shift register may output normal gate line driving signals even when the threshold voltage of the thin film transistor varies due to the variation of the peripheral temperature and an abnormal operation of the shift register due to the variation of the threshold voltage of the thin film transistors may be prevented.

[0031] In addition, since the shift register is independent of the variation of the threshold voltage of the thin film transistors in the liquid crystal display device having a large screen size and a large resolution may be enhanced.

[0032] In addition, the reliability of the shift register may be enhanced throughout a wide range of peripheral temperature.

[0033] In addition the yield for manufacturing the shift register may be increased because the tolerance of the variation of the threshold voltage may be increased.

[0034] In addition, the pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. Therefore, the transistor size of the pull-down transistor that contributes to the capacitive loads of an inverter of the shift register may be reduced, the operation speed of the inverter may be increased, and thus image display quality may not be deteriorated.

[0035] In addition, a power voltage  $V_{ona}$  larger than the power voltage  $V_{on}$  applied to a clock generator is applied to the shift register, and thus image display quality may not be deteriorated even in the liquid crystal display device having a large screen size and a large resolution.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0036] The above and other advantages of the present invention will become more apparent by describing in detail the preferred embodiments thereof with reference to the accompanying drawings, in which:

[0037] FIG. 1 is a schematic view showing a conventional poly-silicon thin film transistor LCD;

[0038] FIG. 2 is a schematic view showing a conventional a-Si thin film transistor LCD;

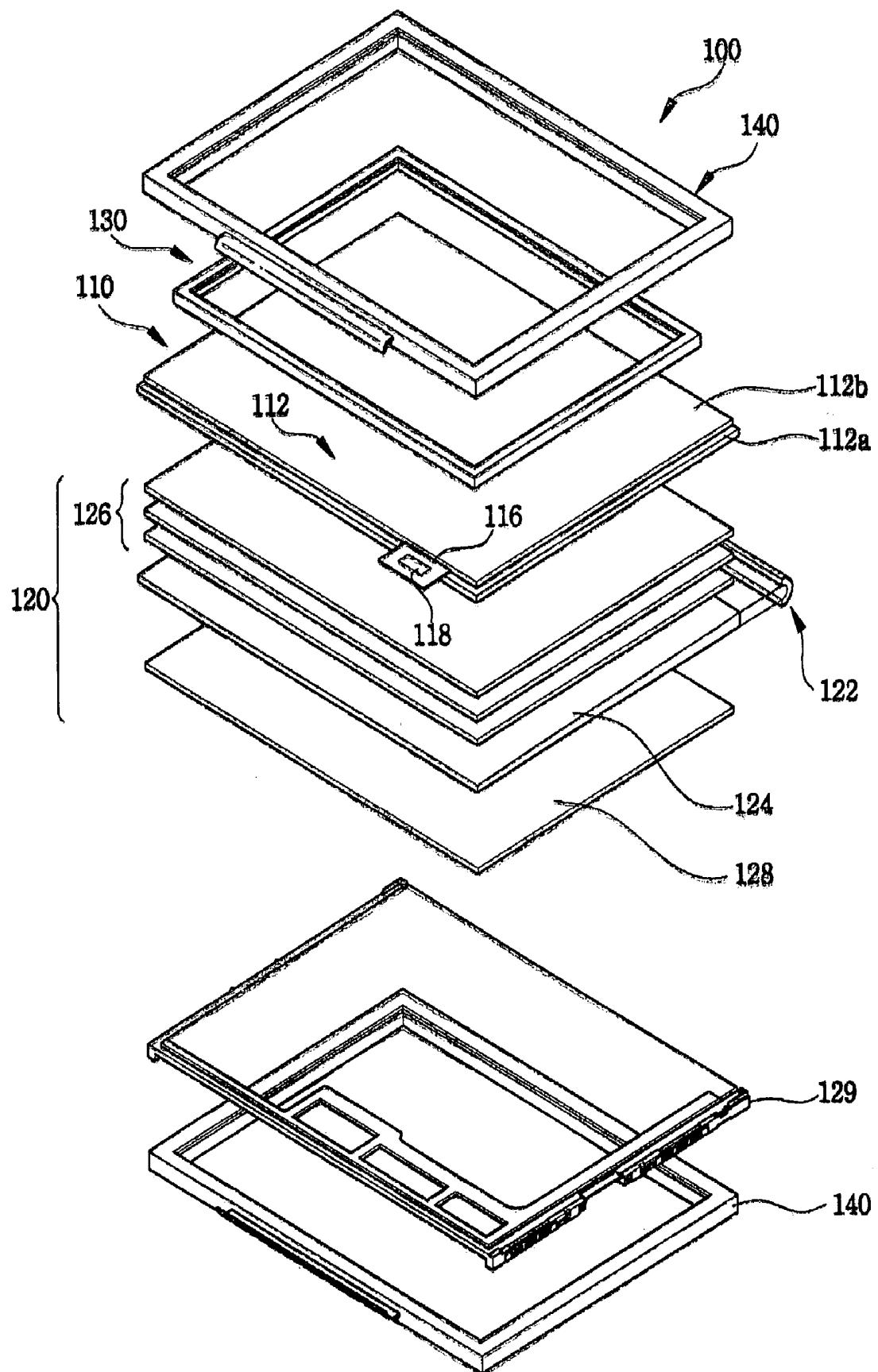

[0039] FIG. 3 is an exploded perspective view showing an a-Si thin film transistor LCD according to one exemplary embodiment of the present invention;

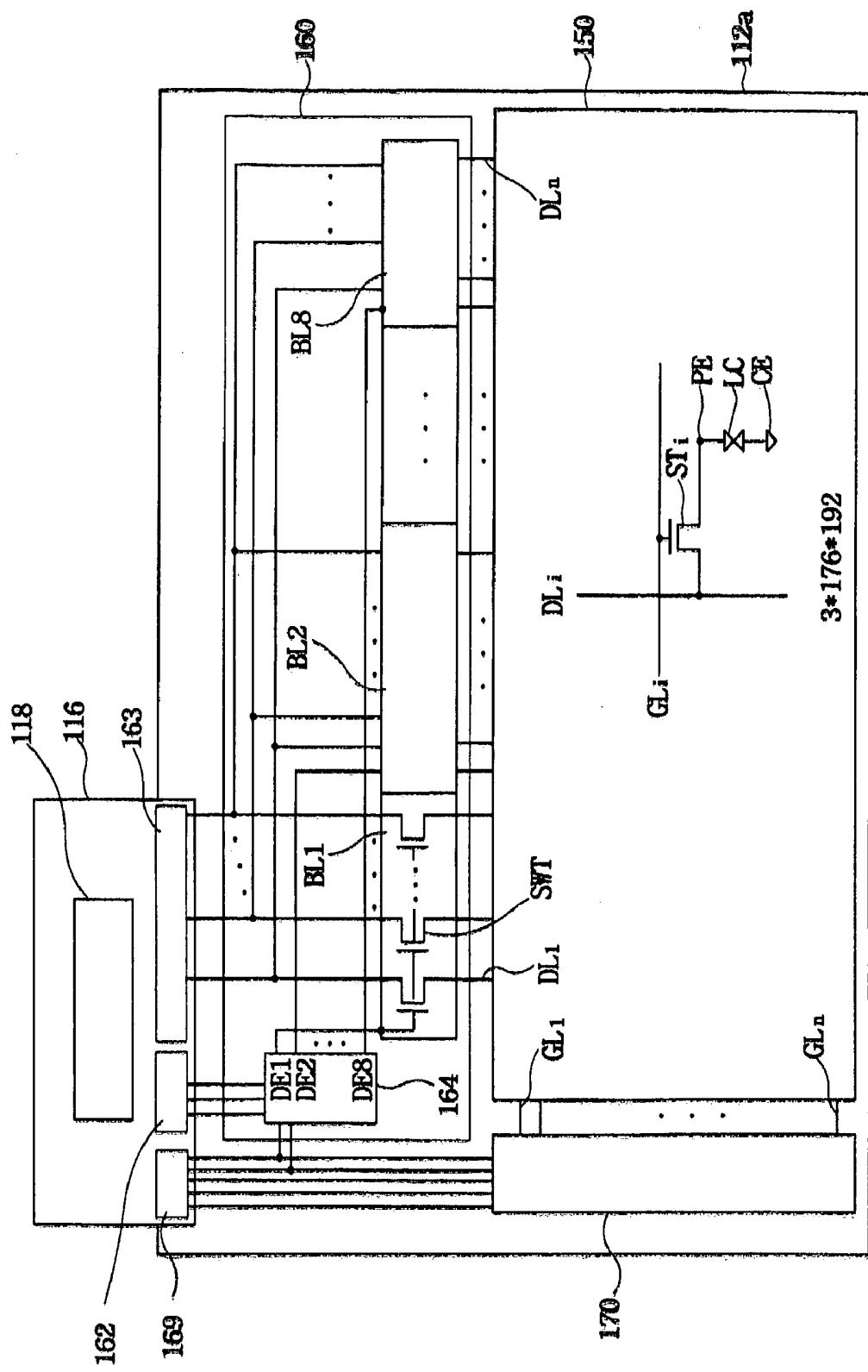

[0040] FIG. 4 is a schematic view showing an a-Si thin film transistor substrate of FIG. 3;

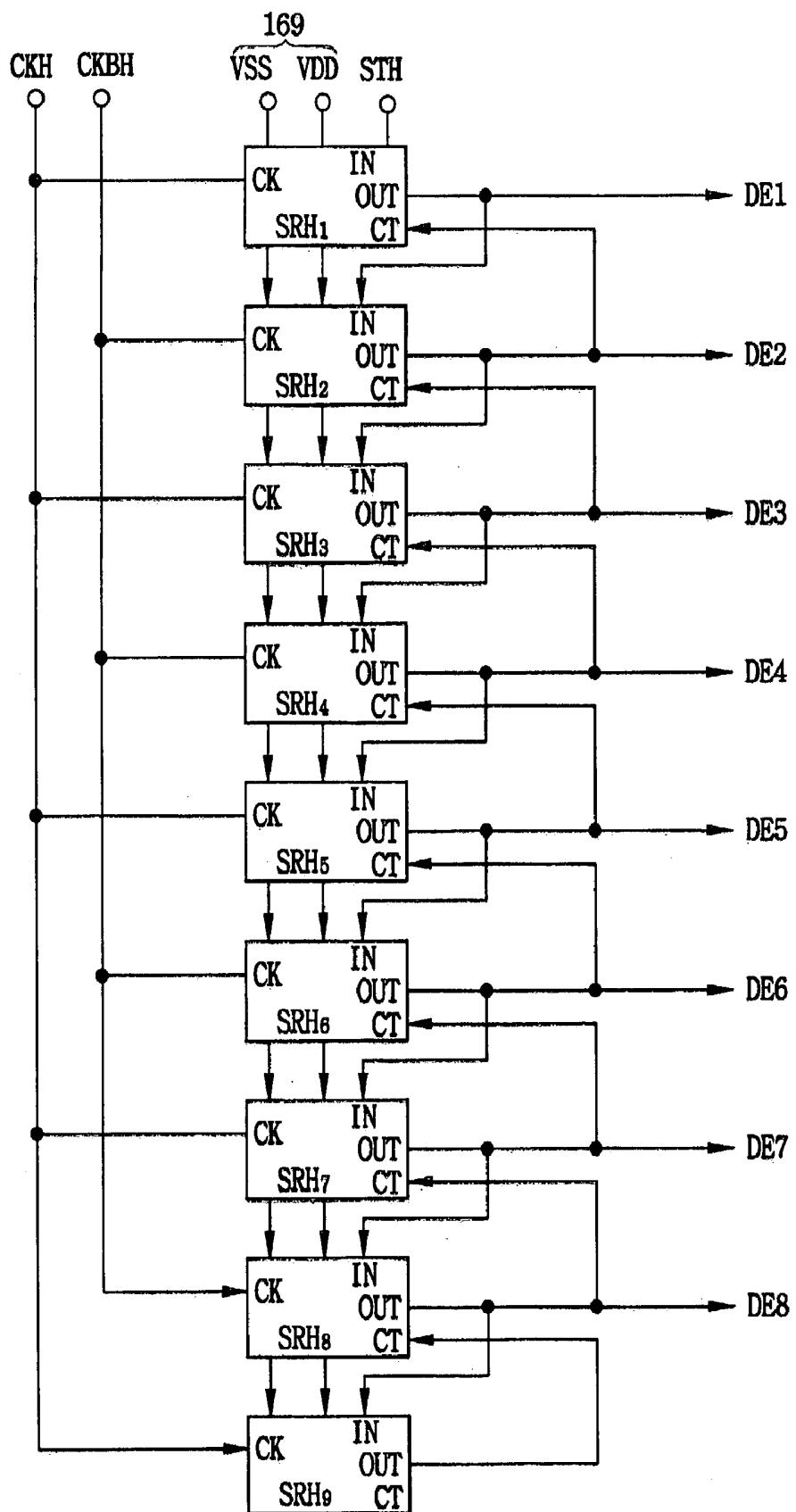

[0041] FIG. 5 is a block diagram showing a data driver circuit of FIG. 4;

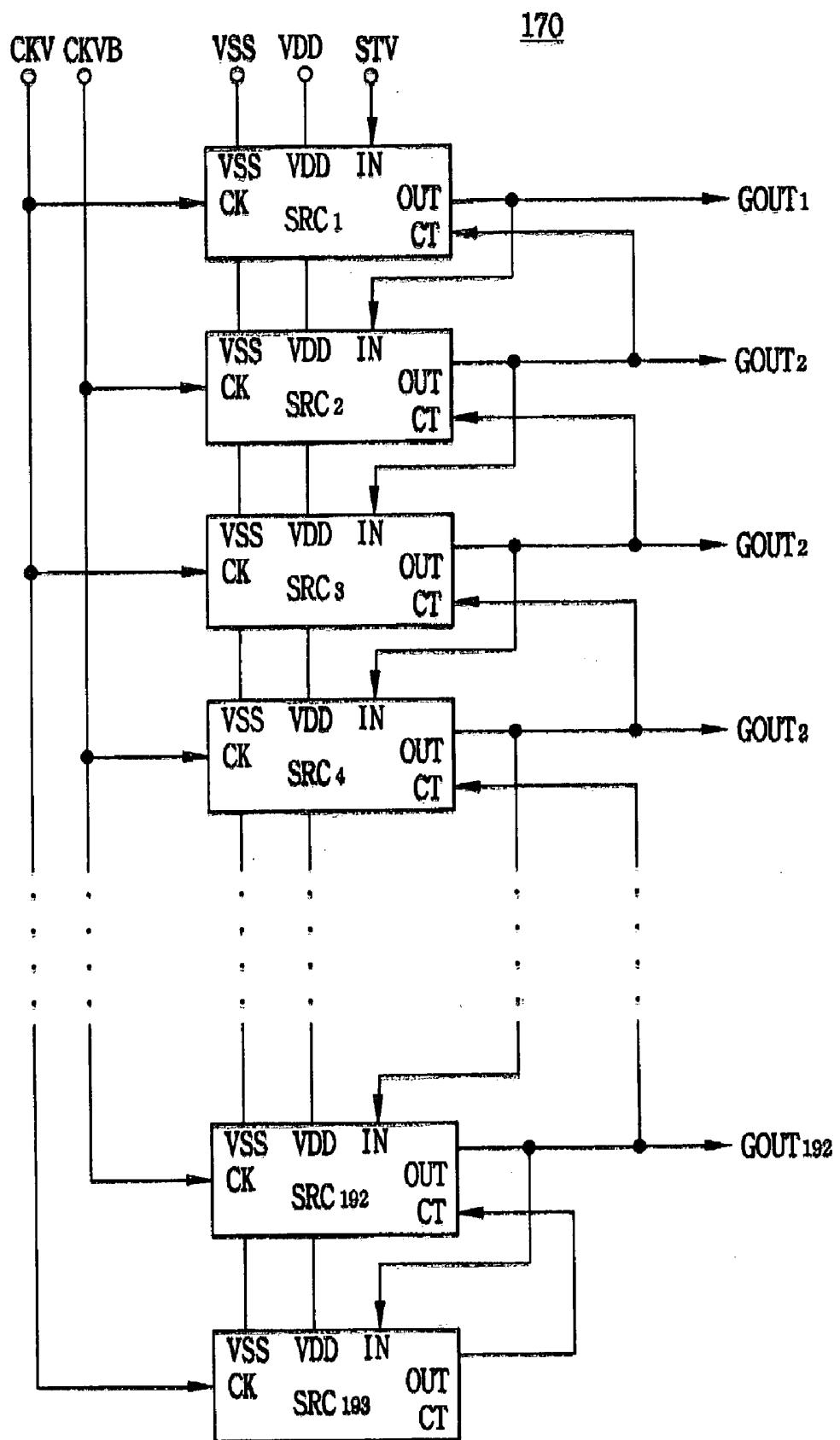

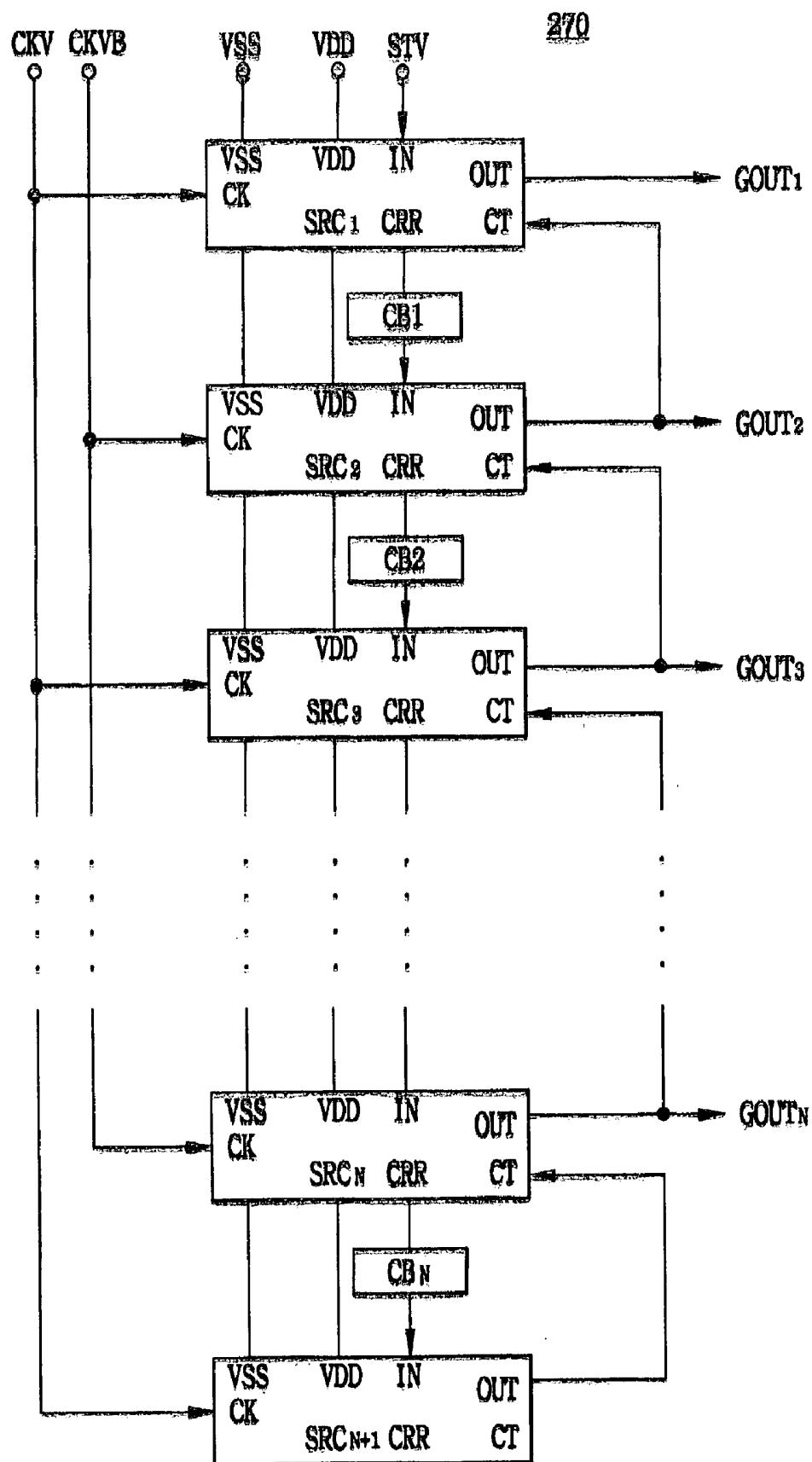

[0042] FIG. 6 is a block diagram showing a shift register used in a gate driver circuit of FIG. 4;

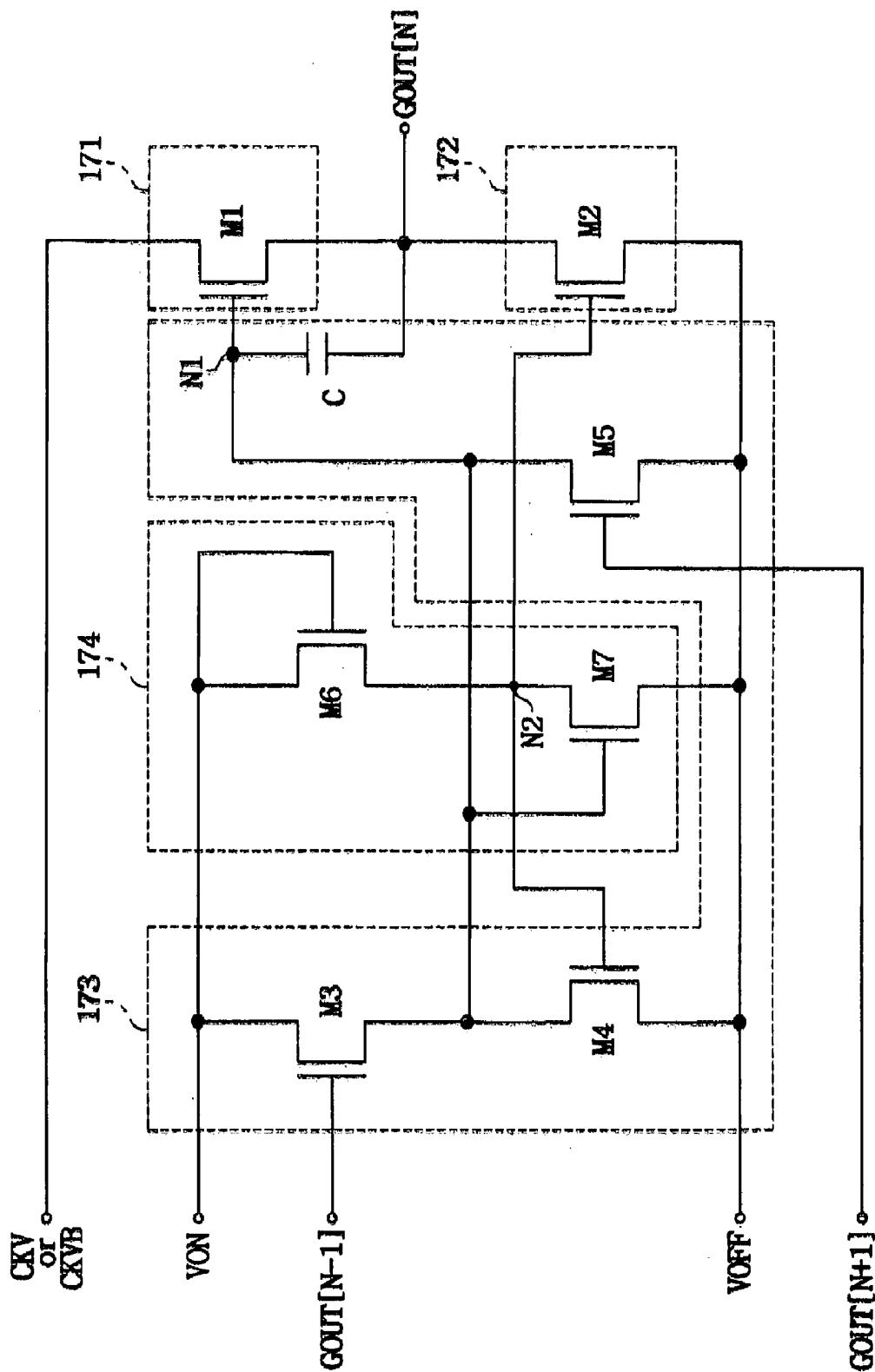

[0043] FIG. 7 is a circuit diagram showing a stage of the shift register of FIG. 6;

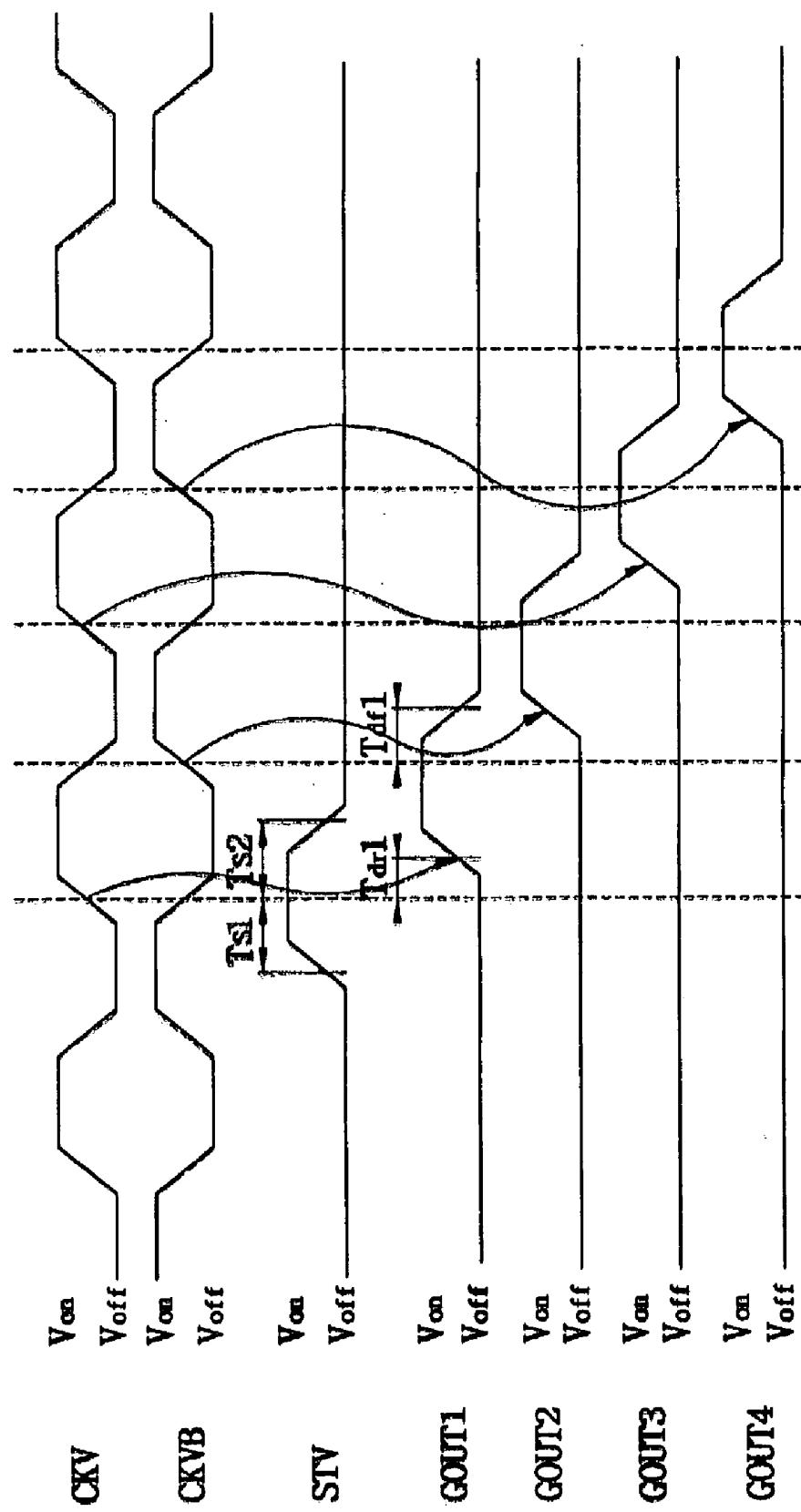

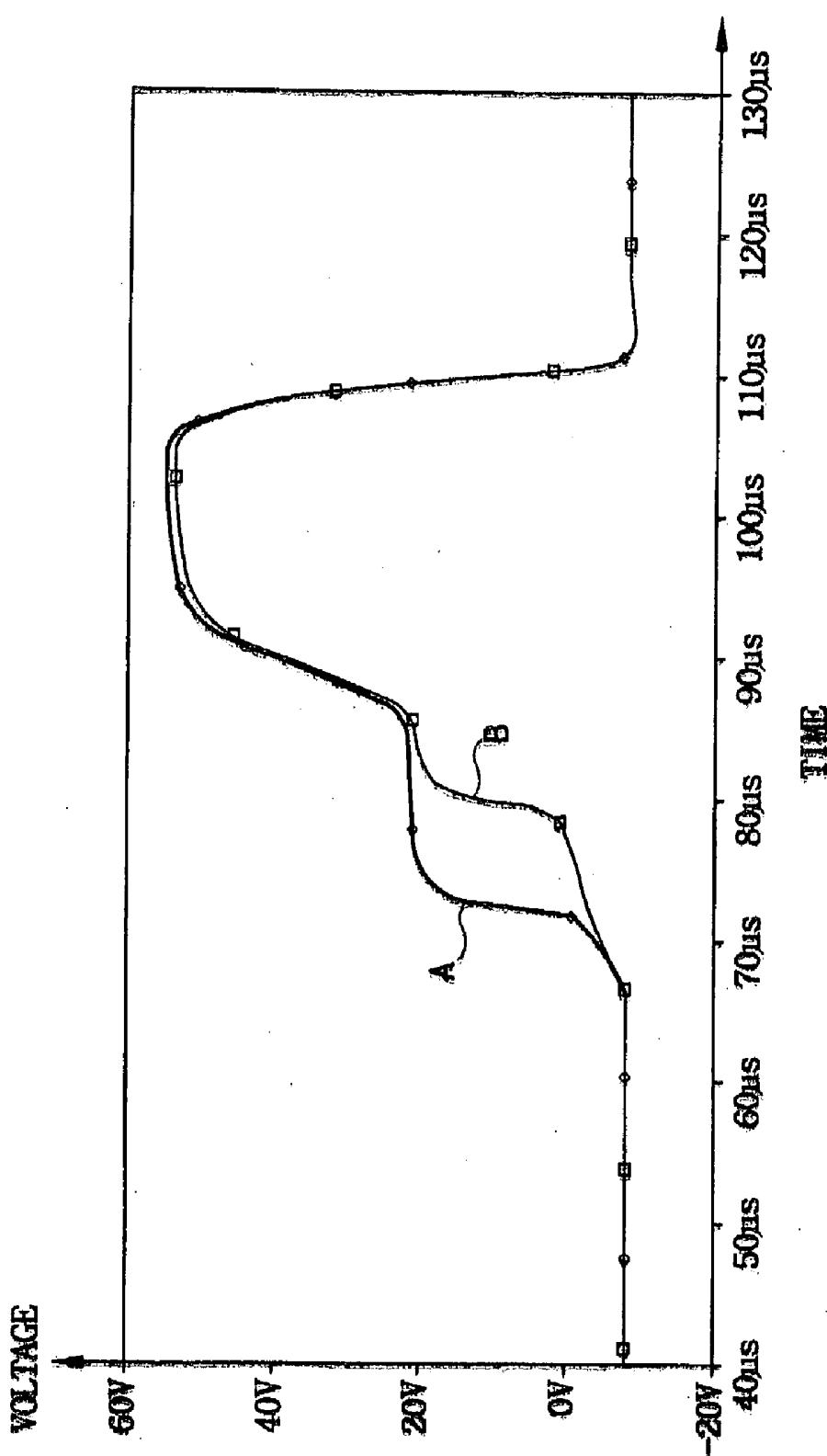

[0044] FIG. 8 is a graph showing scan line driving signals outputted from the stage of FIG. 7;

[0045] FIG. 9 is a graph showing the scan line driving signals outputted from the shift register of FIG. 6;

[0046] FIG. 10 is a schematic view showing the shift register of FIG. 6 and the gate lines.

[0047] FIG. 11 is a block diagram showing a shift register used in a gate driver circuit according to a first exemplary embodiment of the present invention;

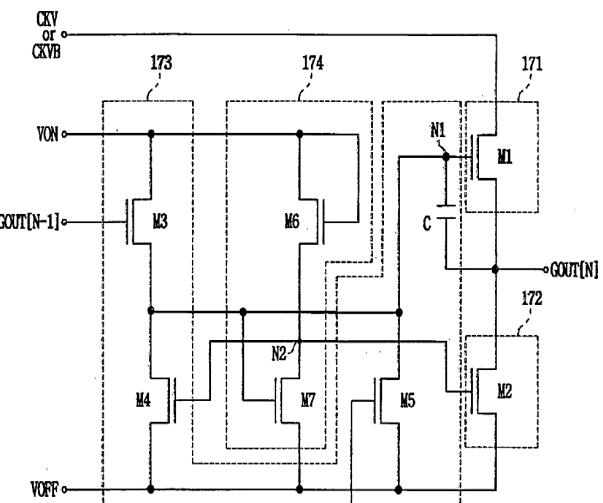

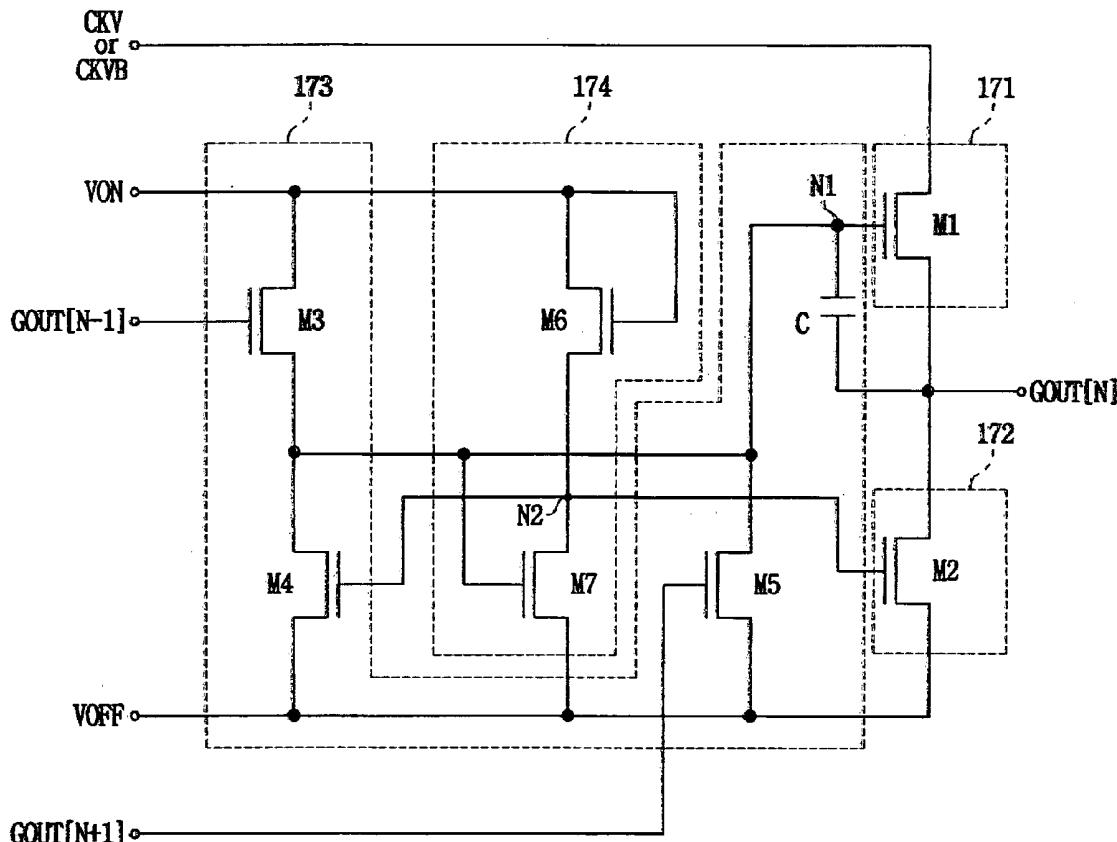

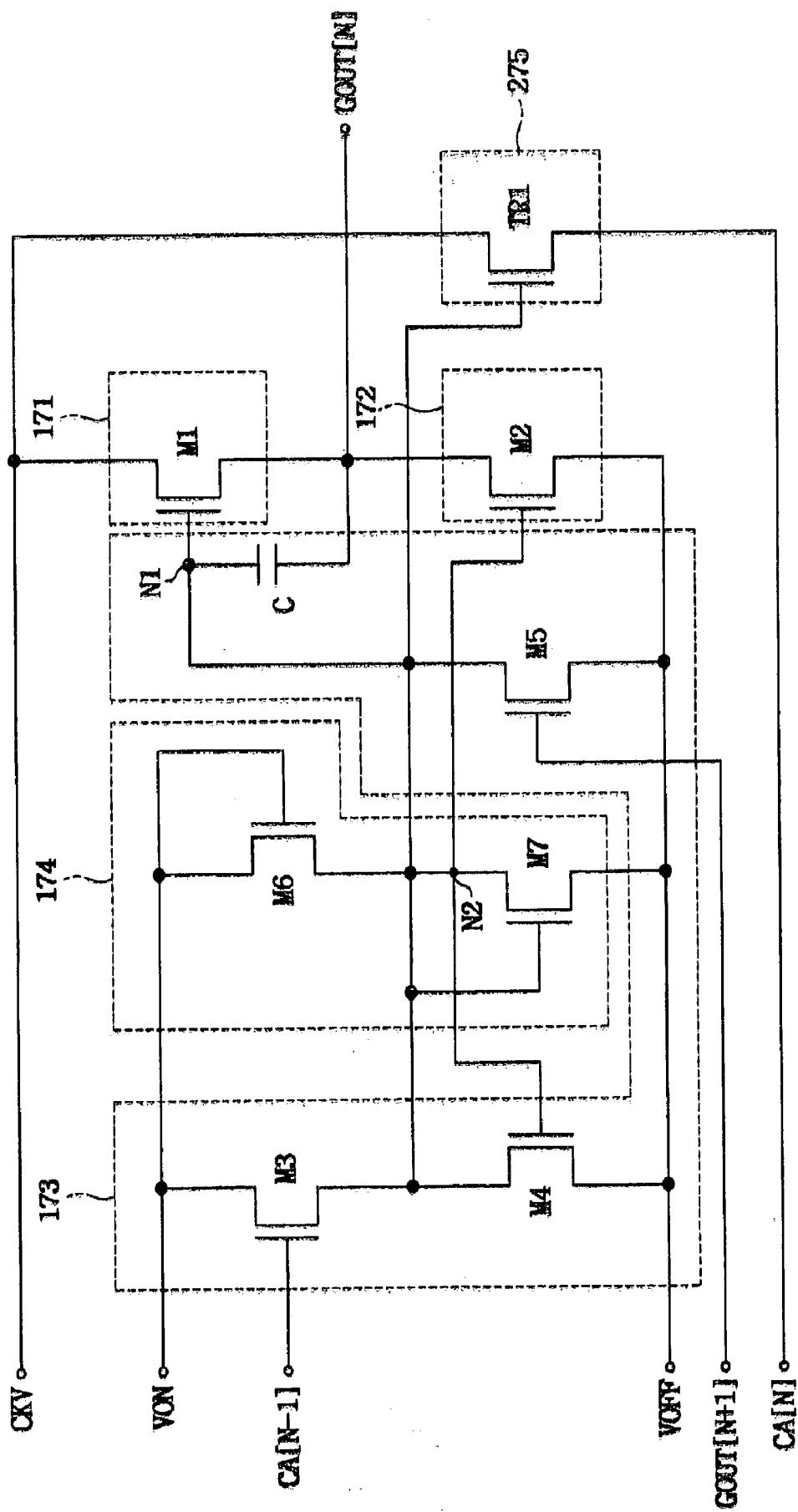

[0048] FIG. 12 is a circuit diagram showing an Nth stage in the shift register of FIG. 11;

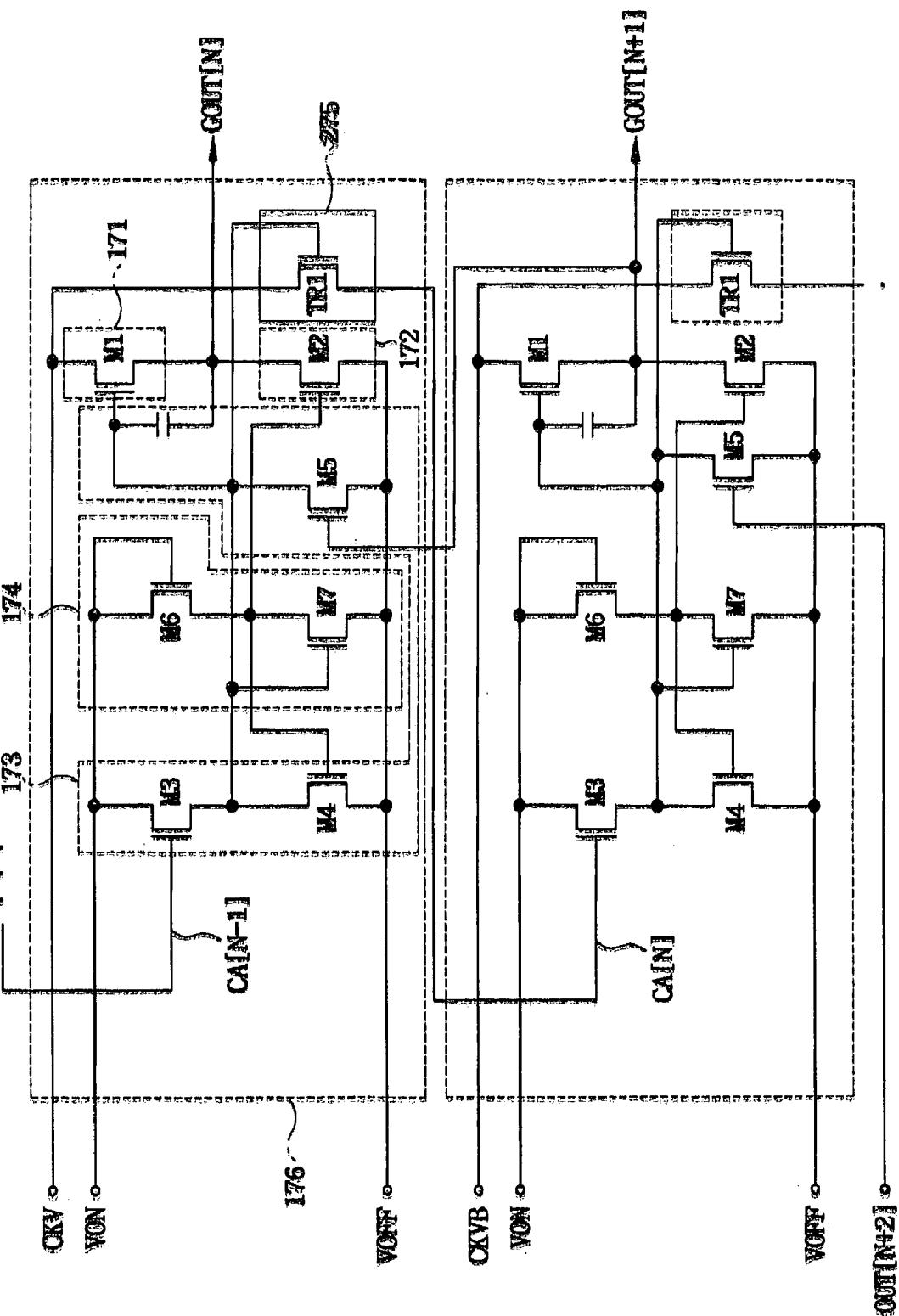

[0049] FIG. 13 is a circuit diagram showing a last stage and a dummy stage in the shift register of FIG. 11;

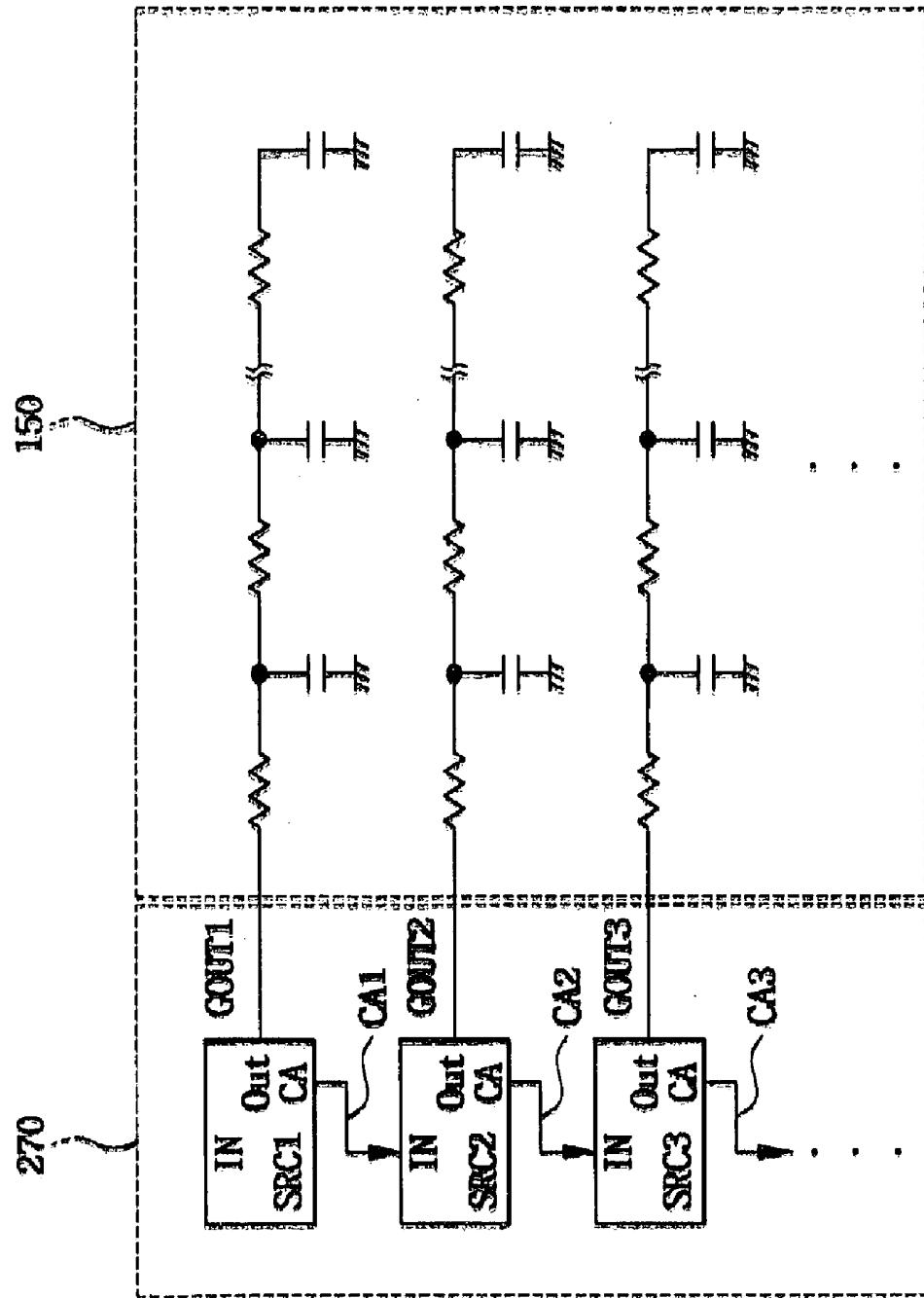

[0050] FIG. 14 is a schematic view showing the shift register of FIG. 11 and the gate lines.

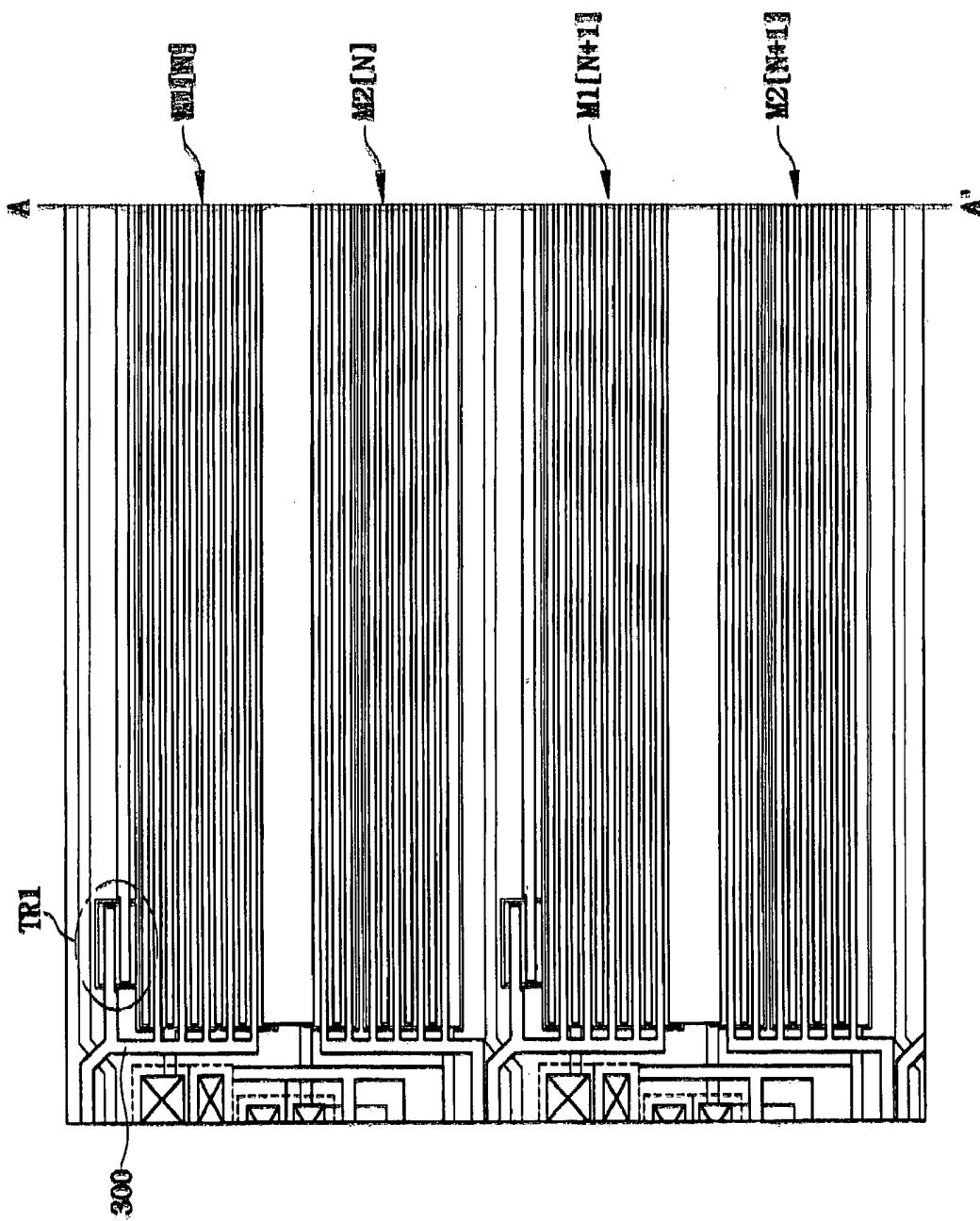

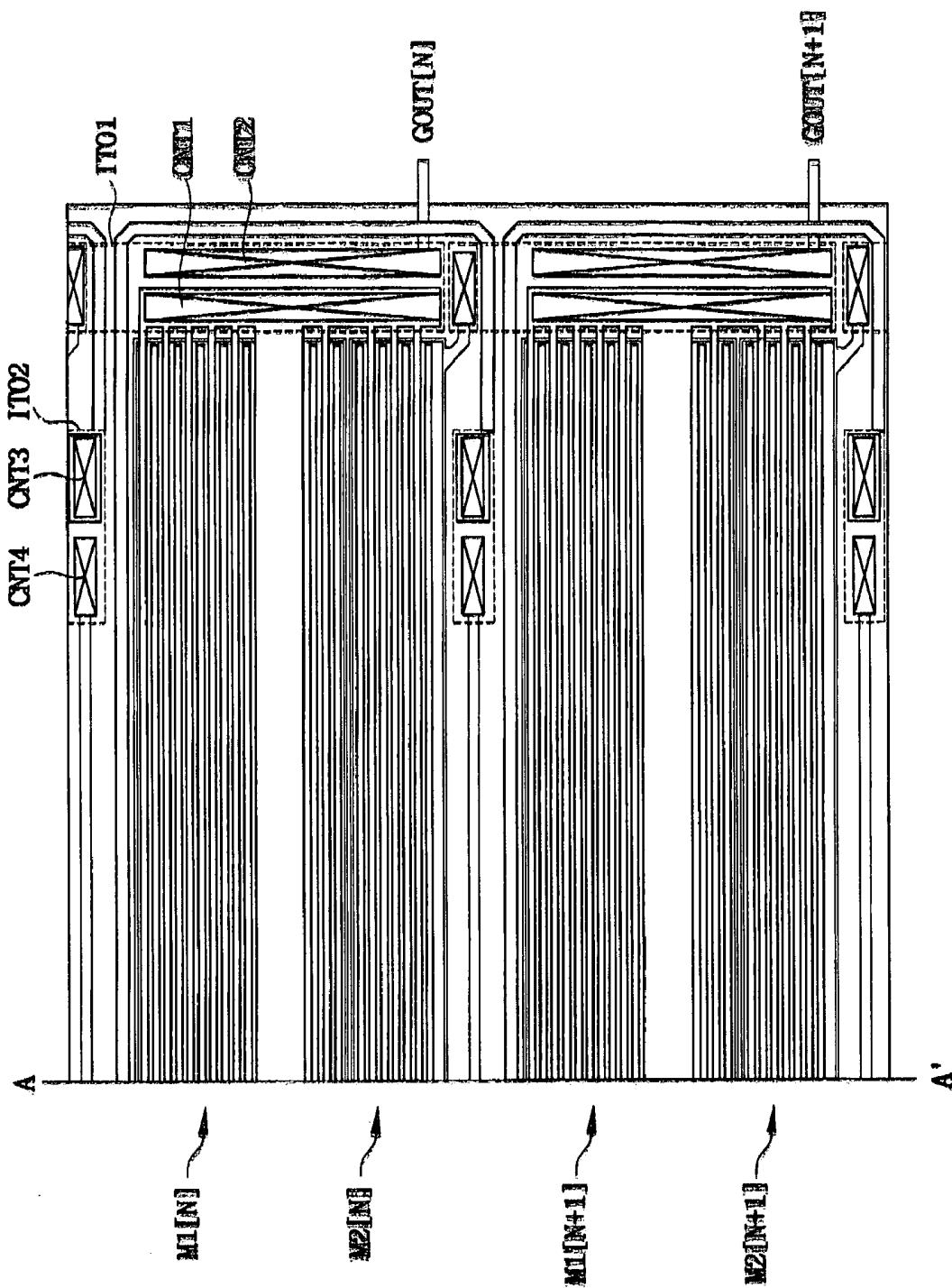

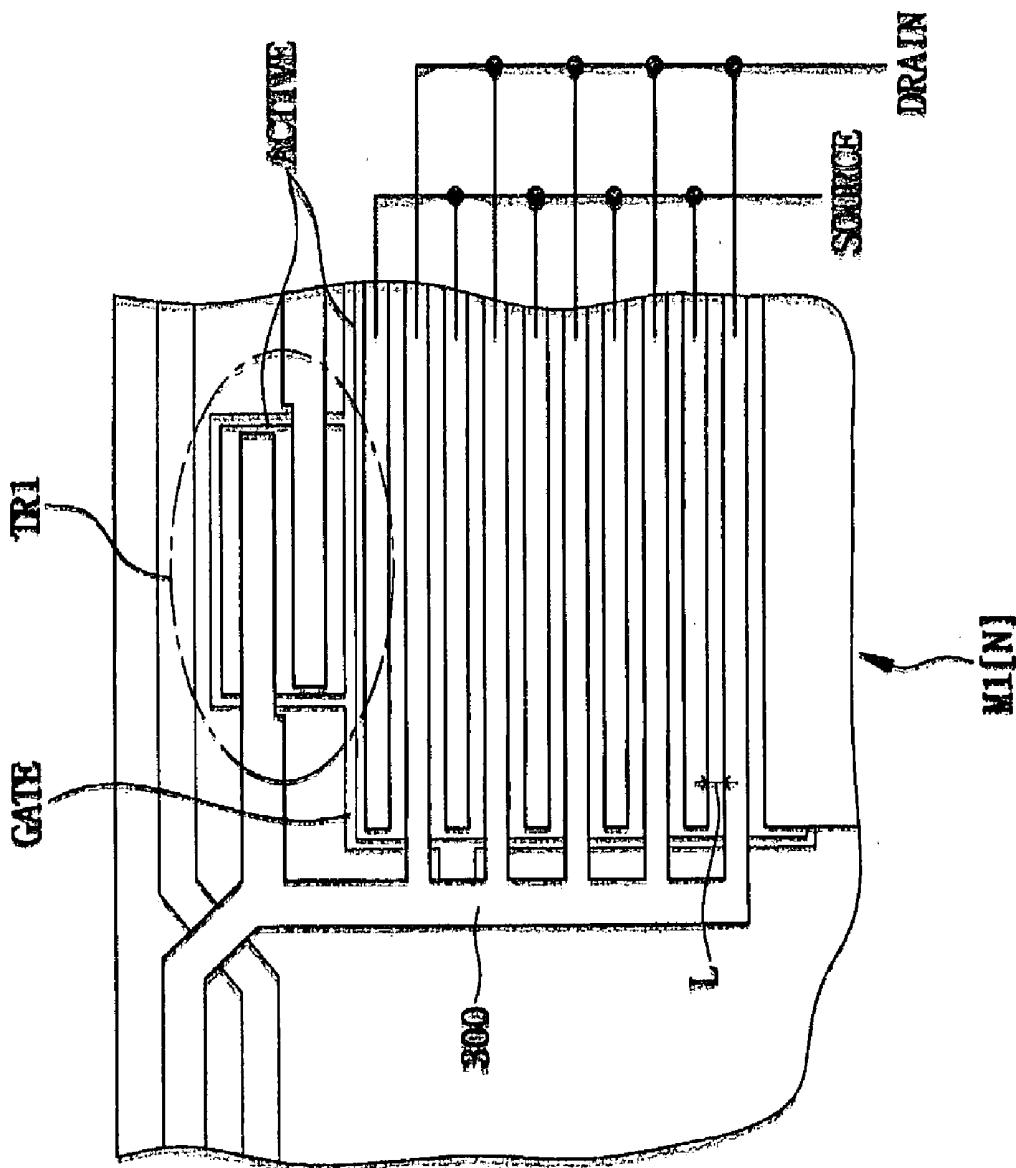

[0051] FIGS. 15A and 15B are layouts showing a pull-up part, a pull-down part and a carry buffer in a stage of the shift register of FIG. 11;

[0052] FIGS. 15C is an enlarged view showing the carry buffer in the shift register of FIG. 15A;

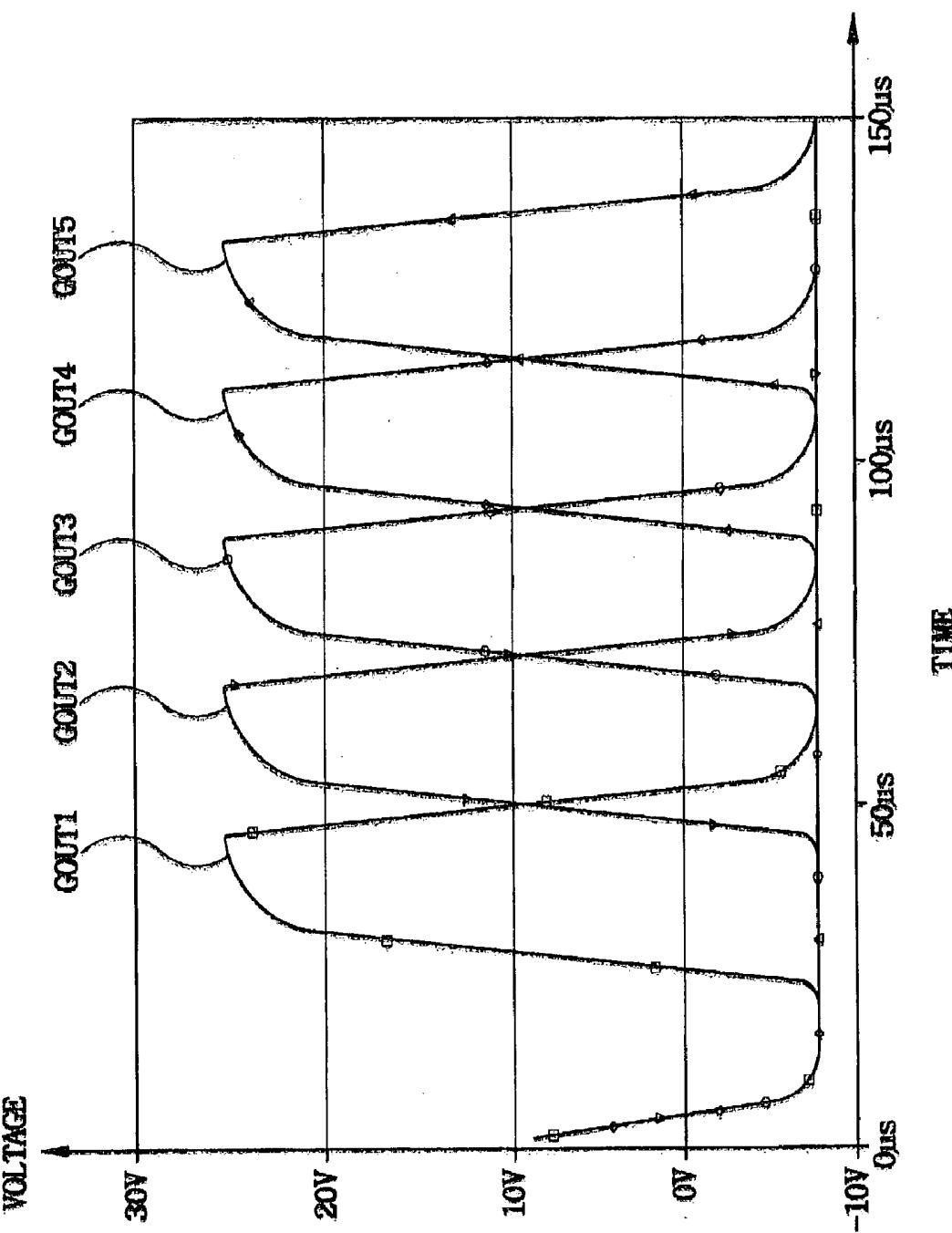

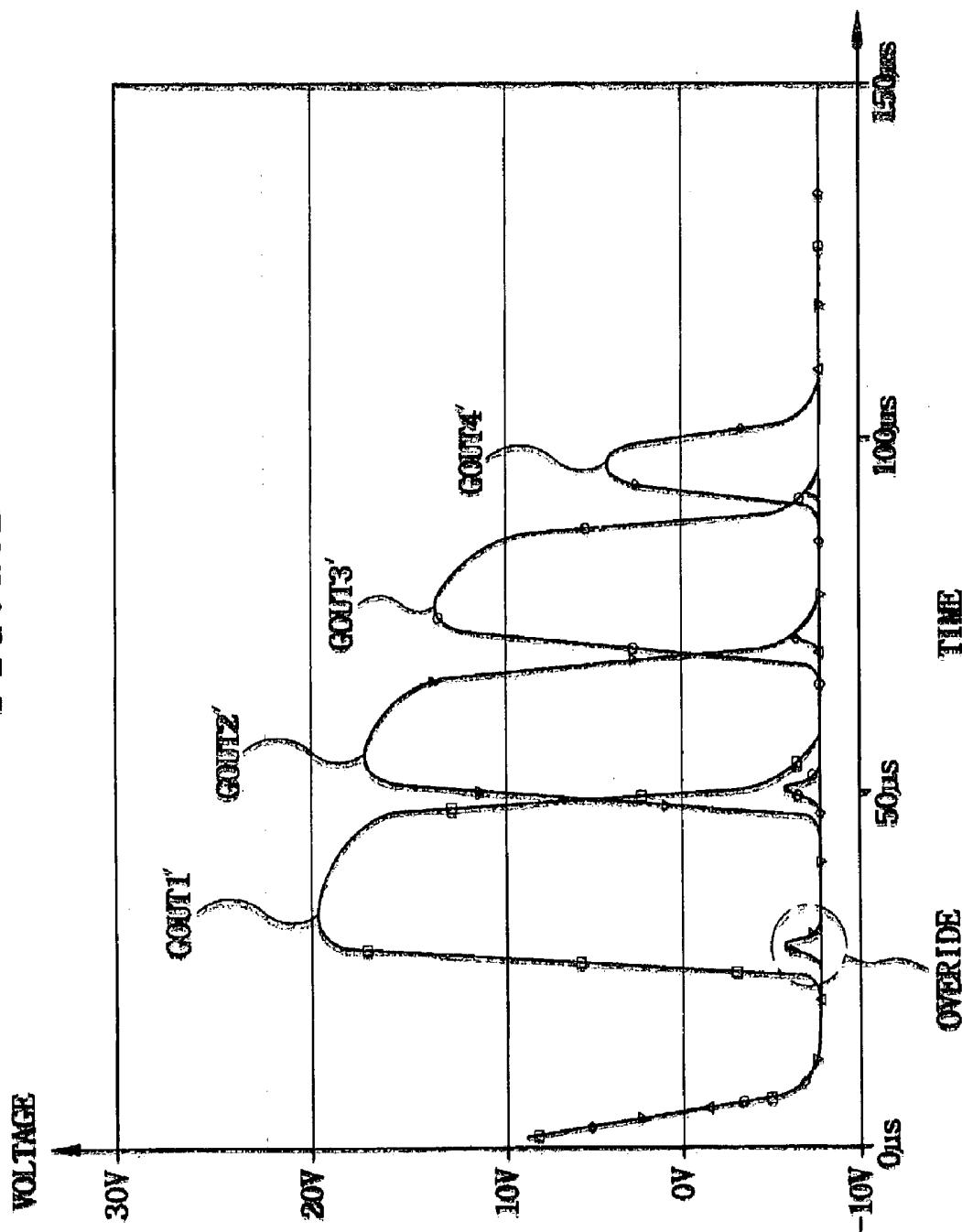

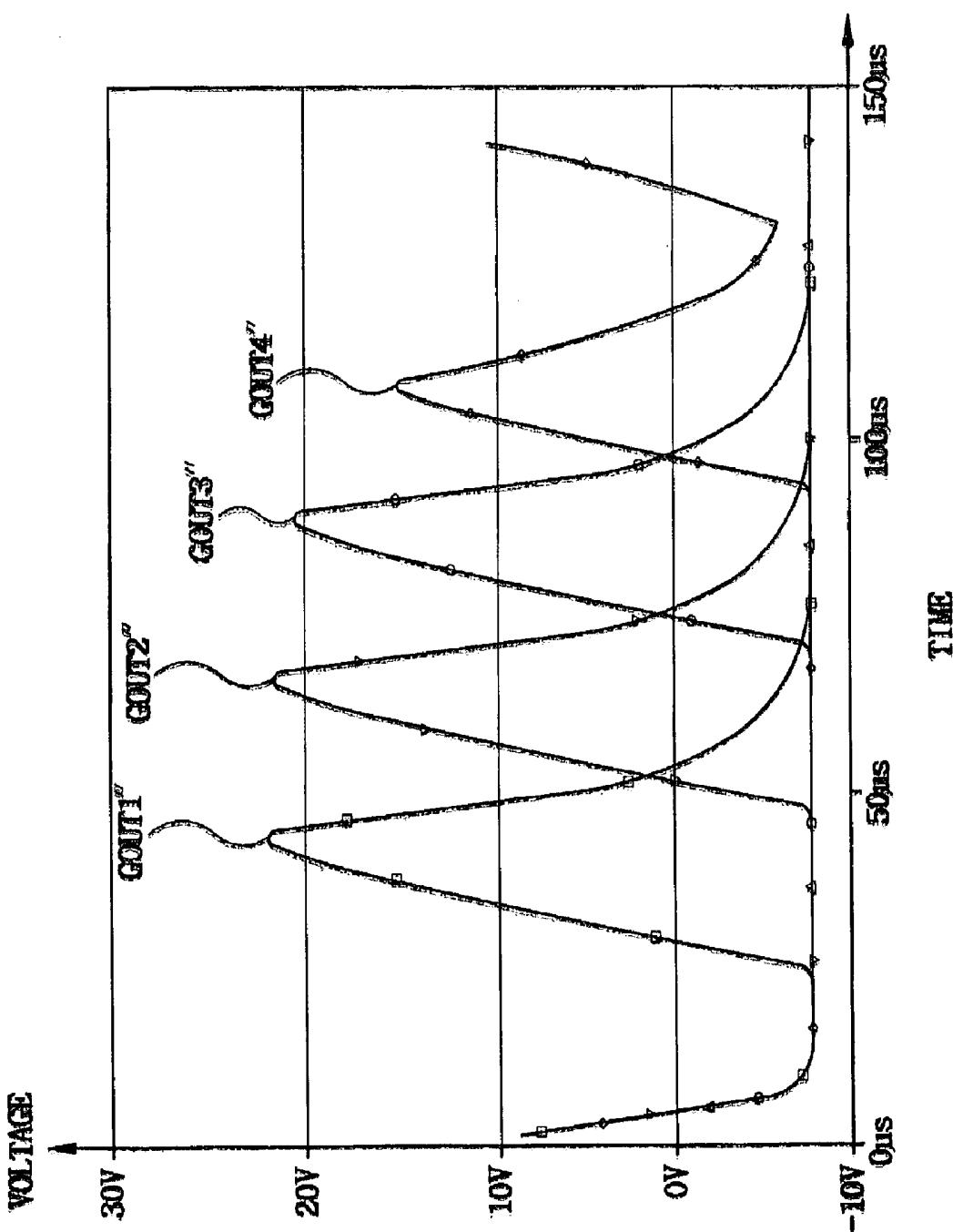

[0053] FIGS. 16A, 16B and 16C are graphs showing the gate line driving signal outputted from the shift register of FIG. 7;

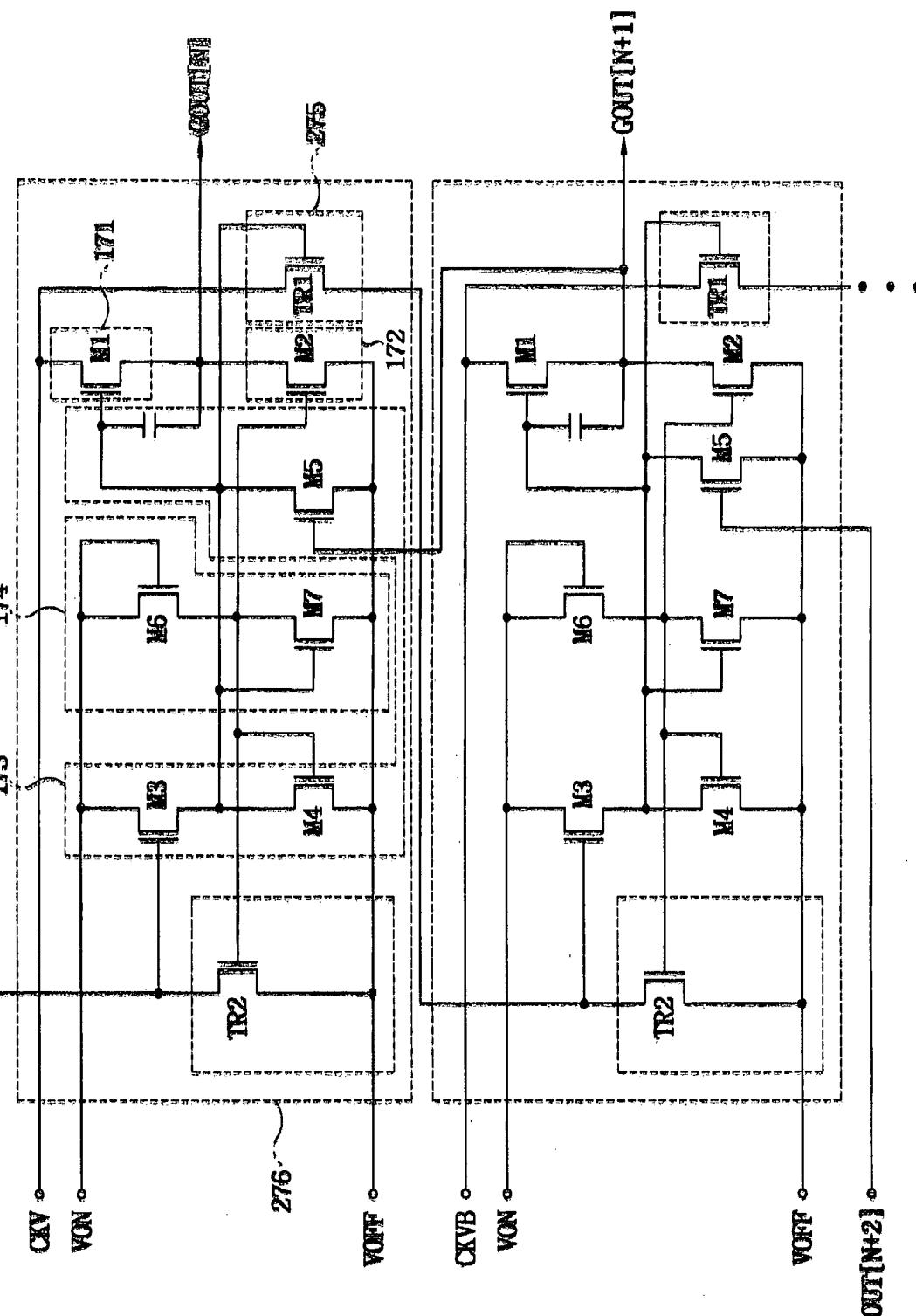

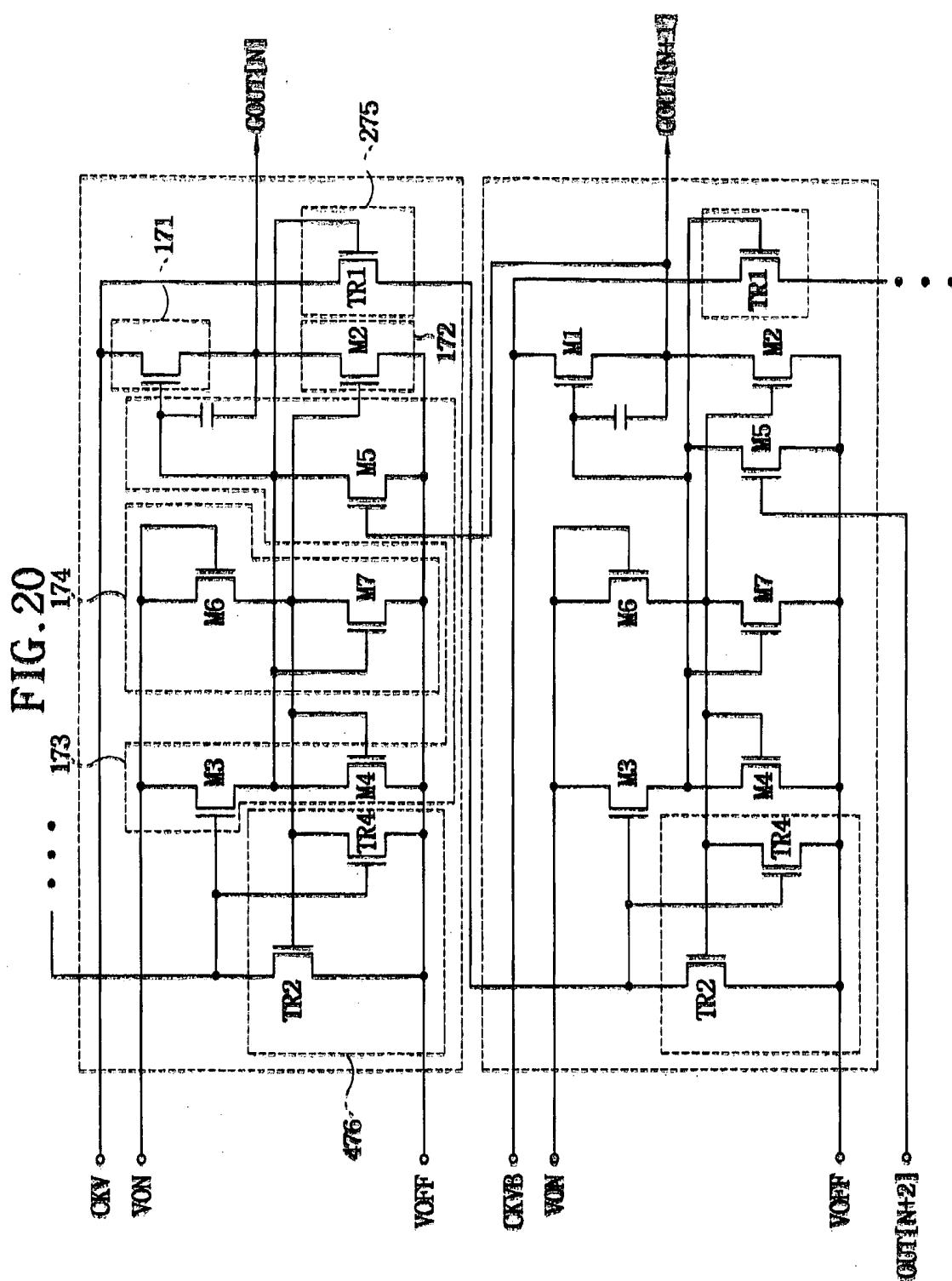

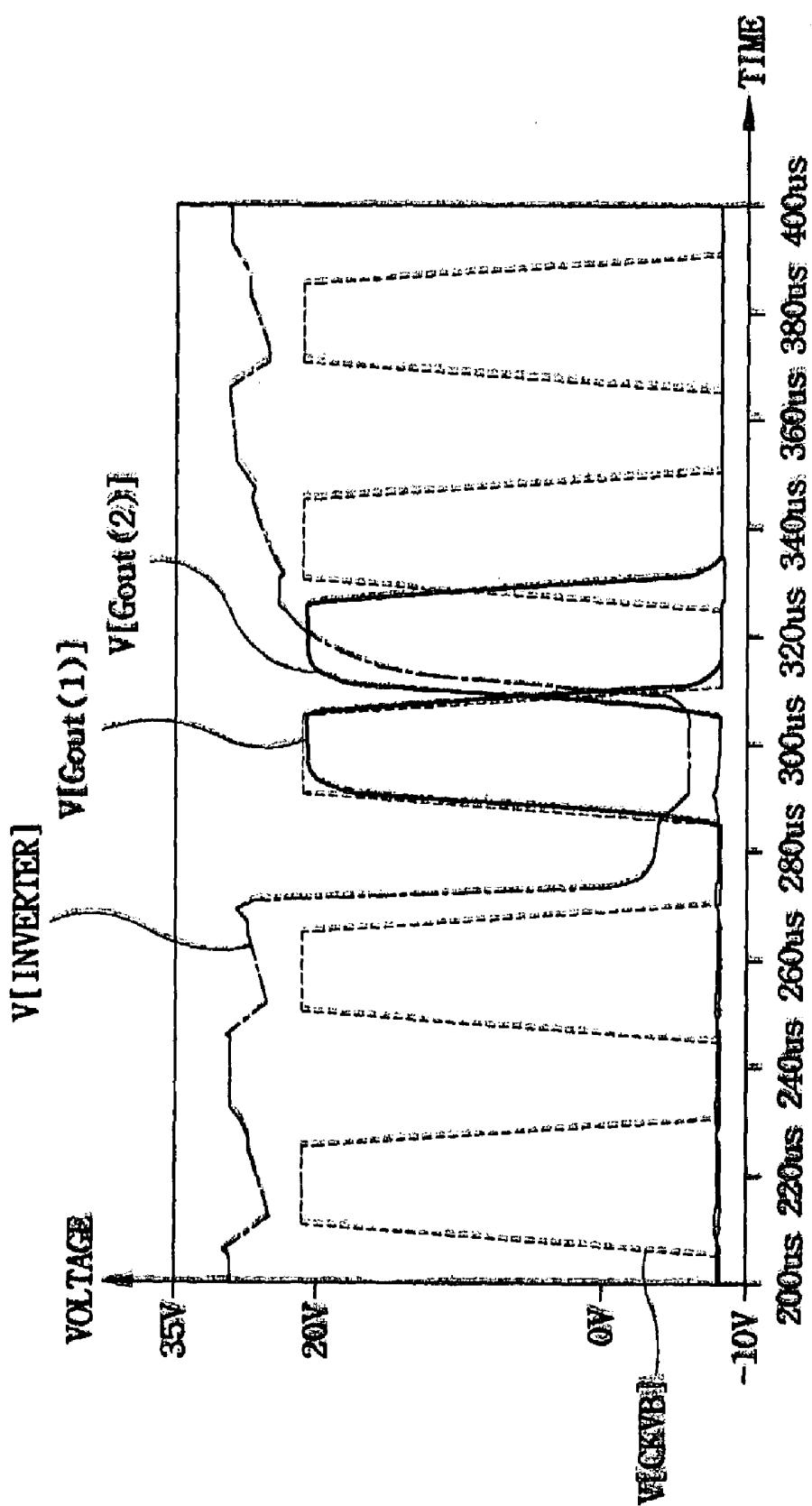

[0054] FIG. 17 is a block diagram showing a shift register used in a gate driver circuit according to a second exemplary embodiment of the present invention;

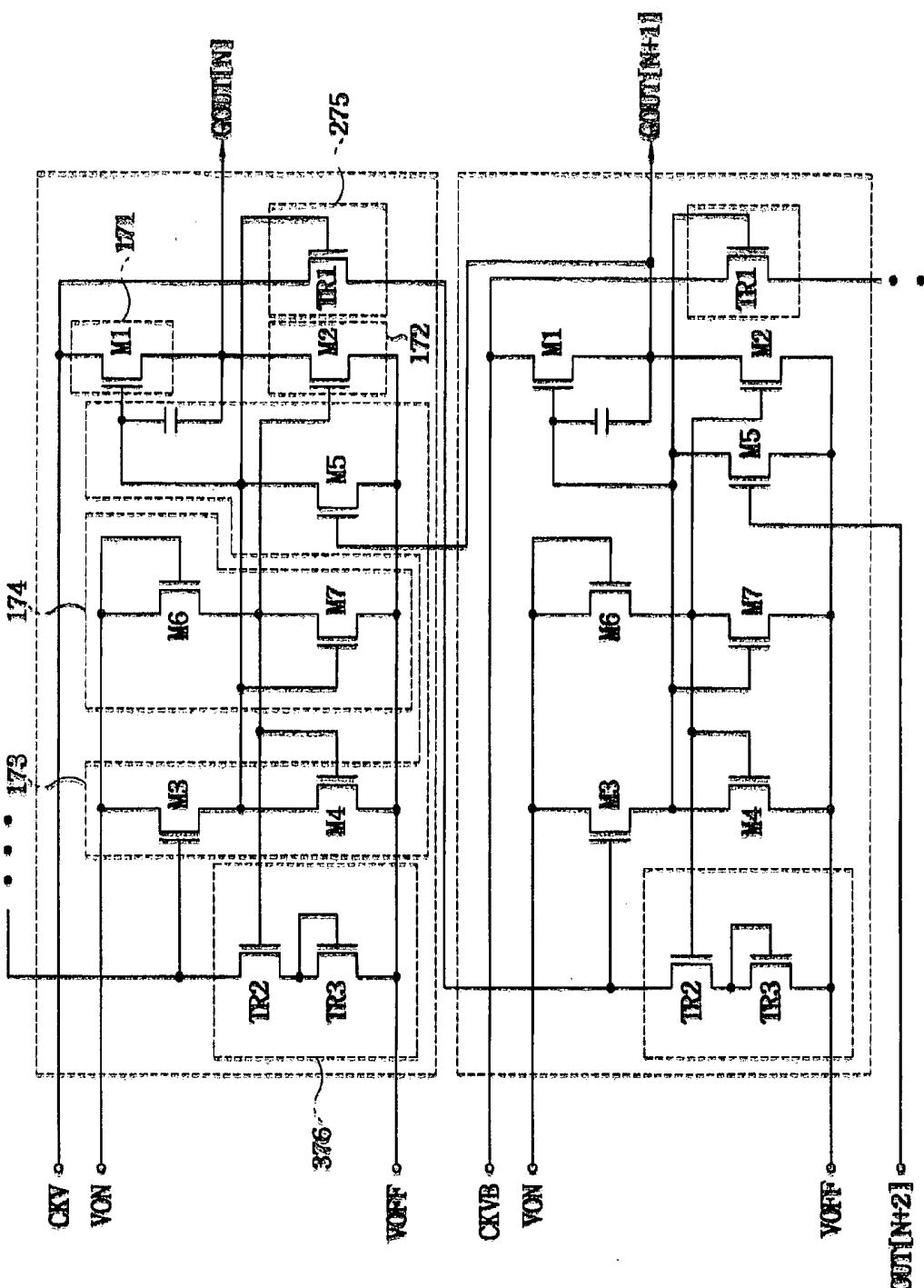

[0055] FIG. 18 is a block diagram showing a shift register used in a gate driver circuit according to a third exemplary embodiment of the present invention;

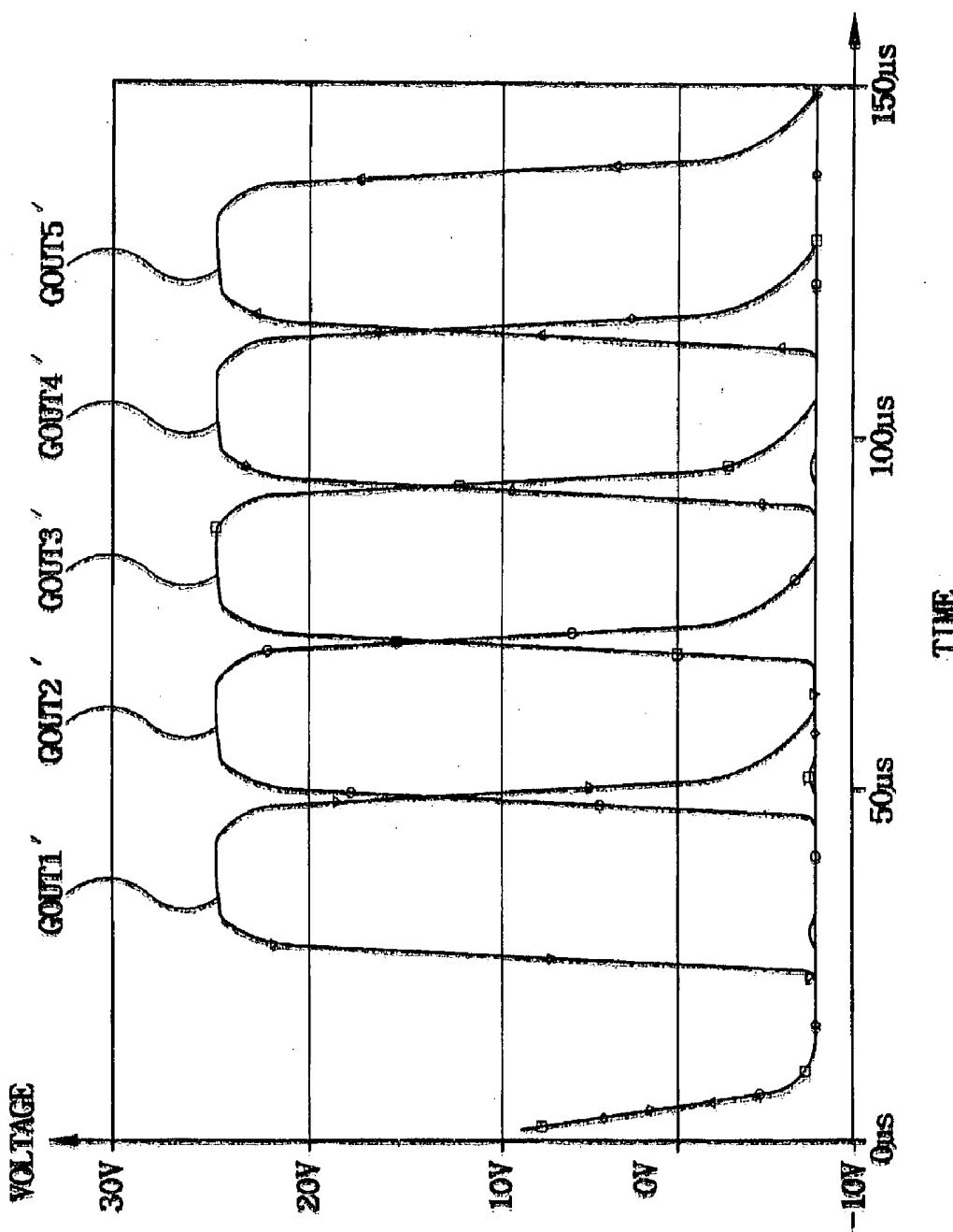

[0056] FIGS. 19A and 19B are graphs showing the output of the shift register of FIG. 18;

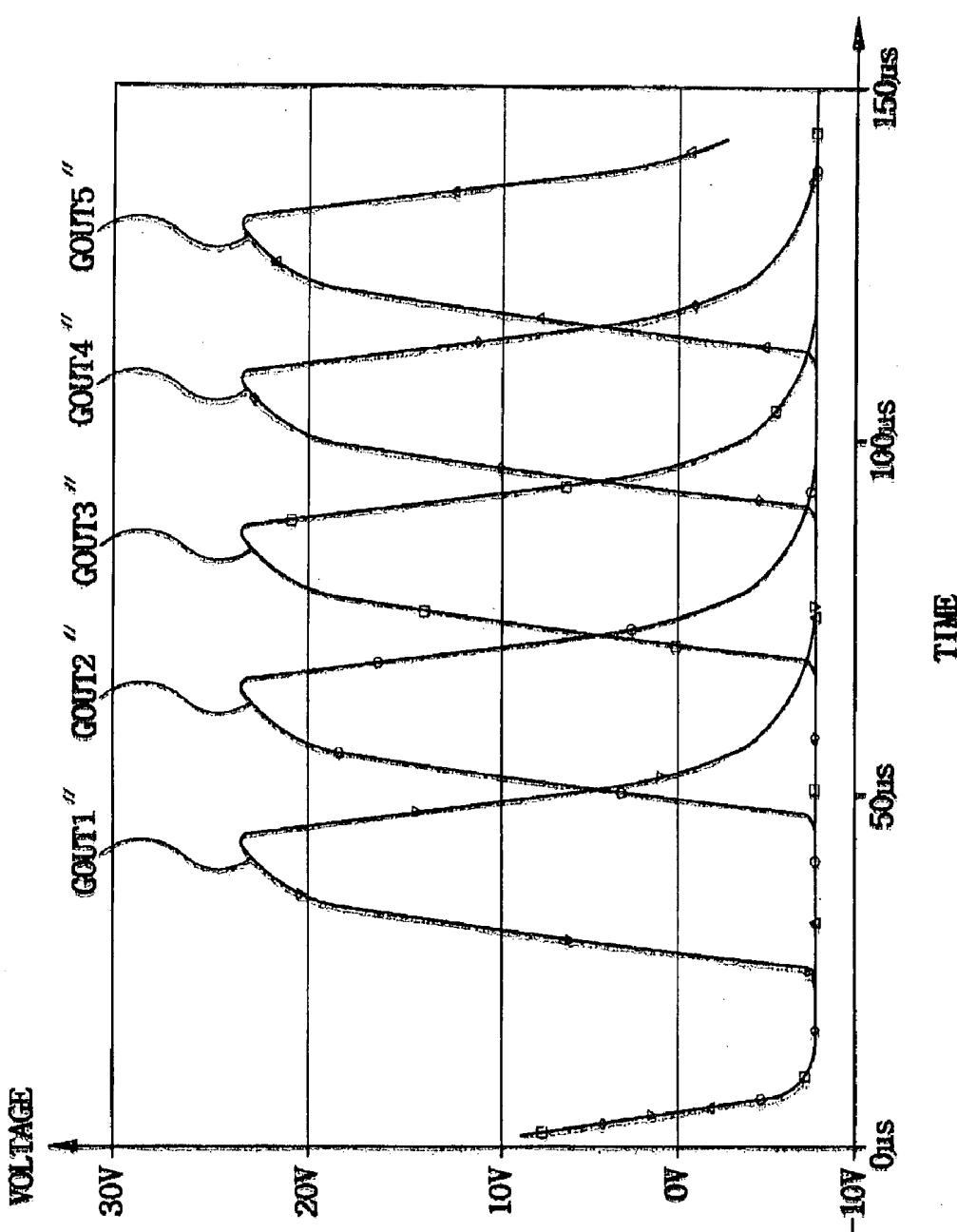

[0057] FIG. 20 is a block diagram showing a shift register used in a gate driver circuit according to a fourth exemplary embodiment of the present invention;

[0058] FIG. 21 is a block diagram showing a shift register used in a gate driver circuit according to a fifth exemplary embodiment of the present invention;

[0059] FIG. 22 is a graph showing the voltage measured at the capacitor of FIG. 21;

[0060] FIG. 23 is a graph showing the gate line driving signal outputted from the shift register of FIG. 7;

[0061] FIG. 24 is a block diagram showing a unit stage of a shift register used in a gate driver circuit according to a sixth exemplary embodiment of the present invention;

[0062] FIG. 25 is a graph showing the gate line driving signal outputted from the shift register of FIG. 24;

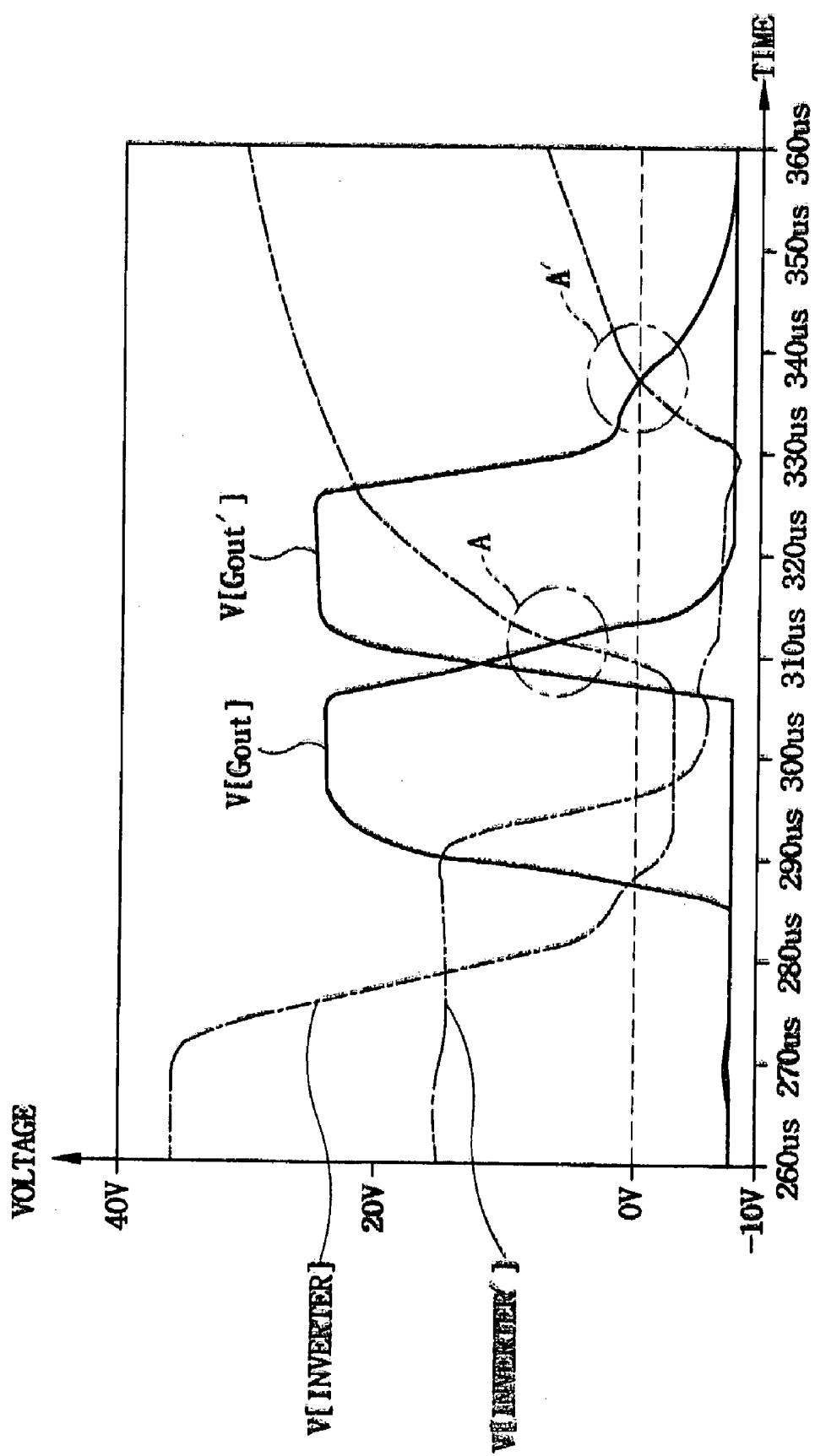

[0063] FIG. 26 is a graph showing the gate line driving signal outputted from the shift register of FIG. 7 and the gate line driving signal outputted from the shift register of FIG. 24;

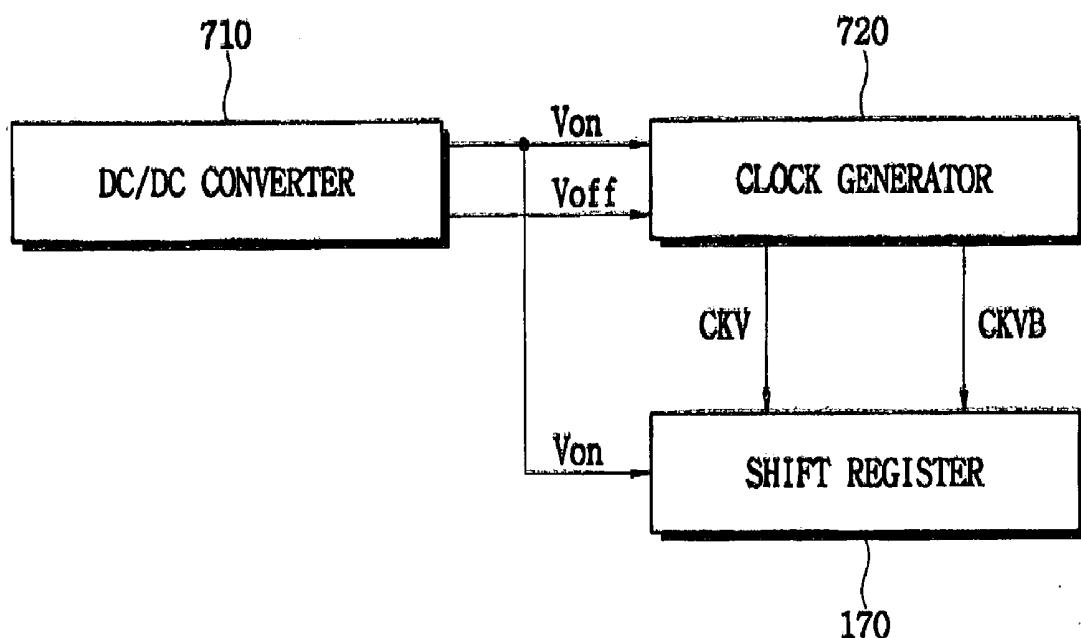

[0064] FIG. 27 is a block diagram showing a power supply and a clock generator according to a seventh exemplary embodiment of the present invention;

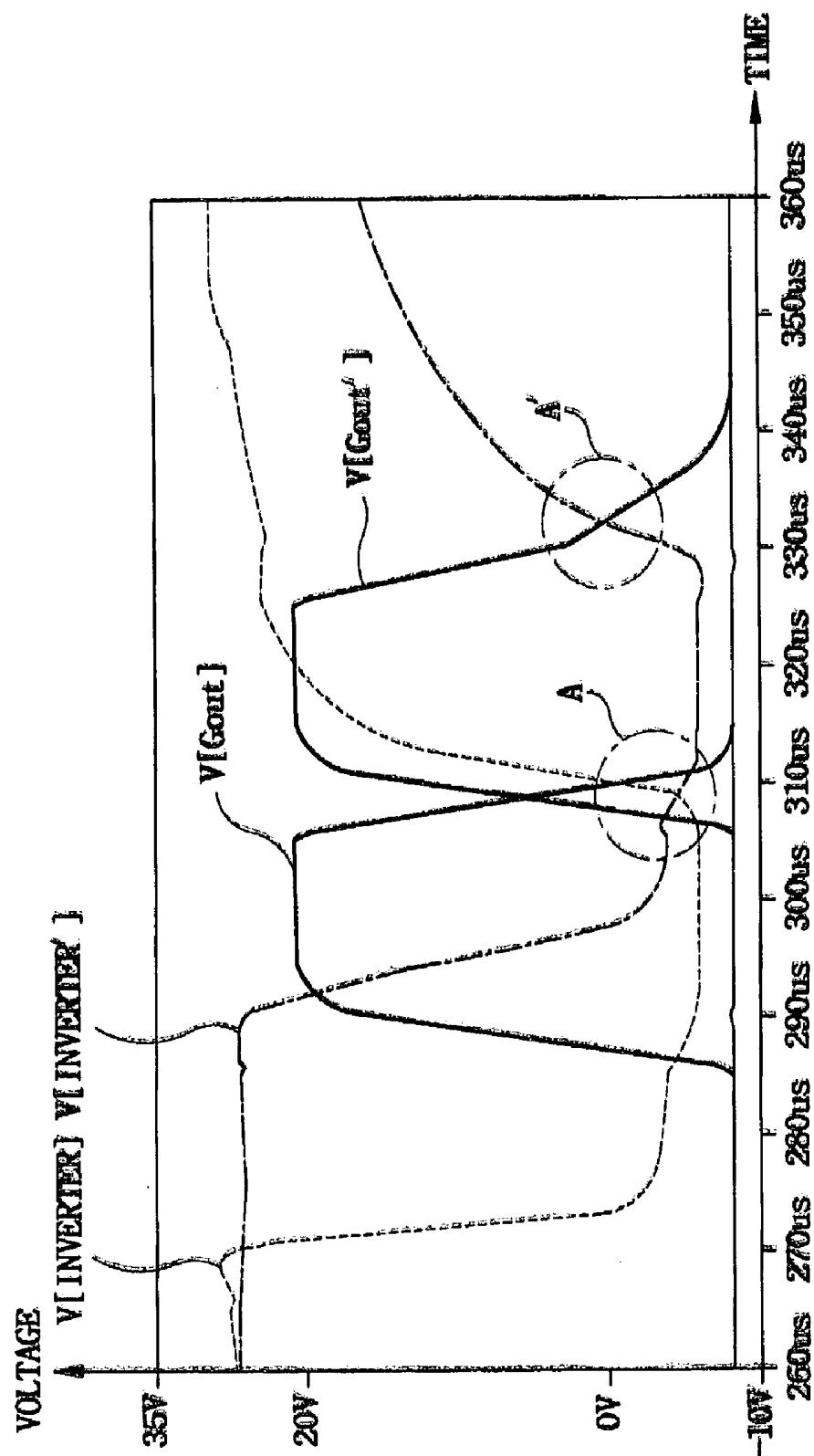

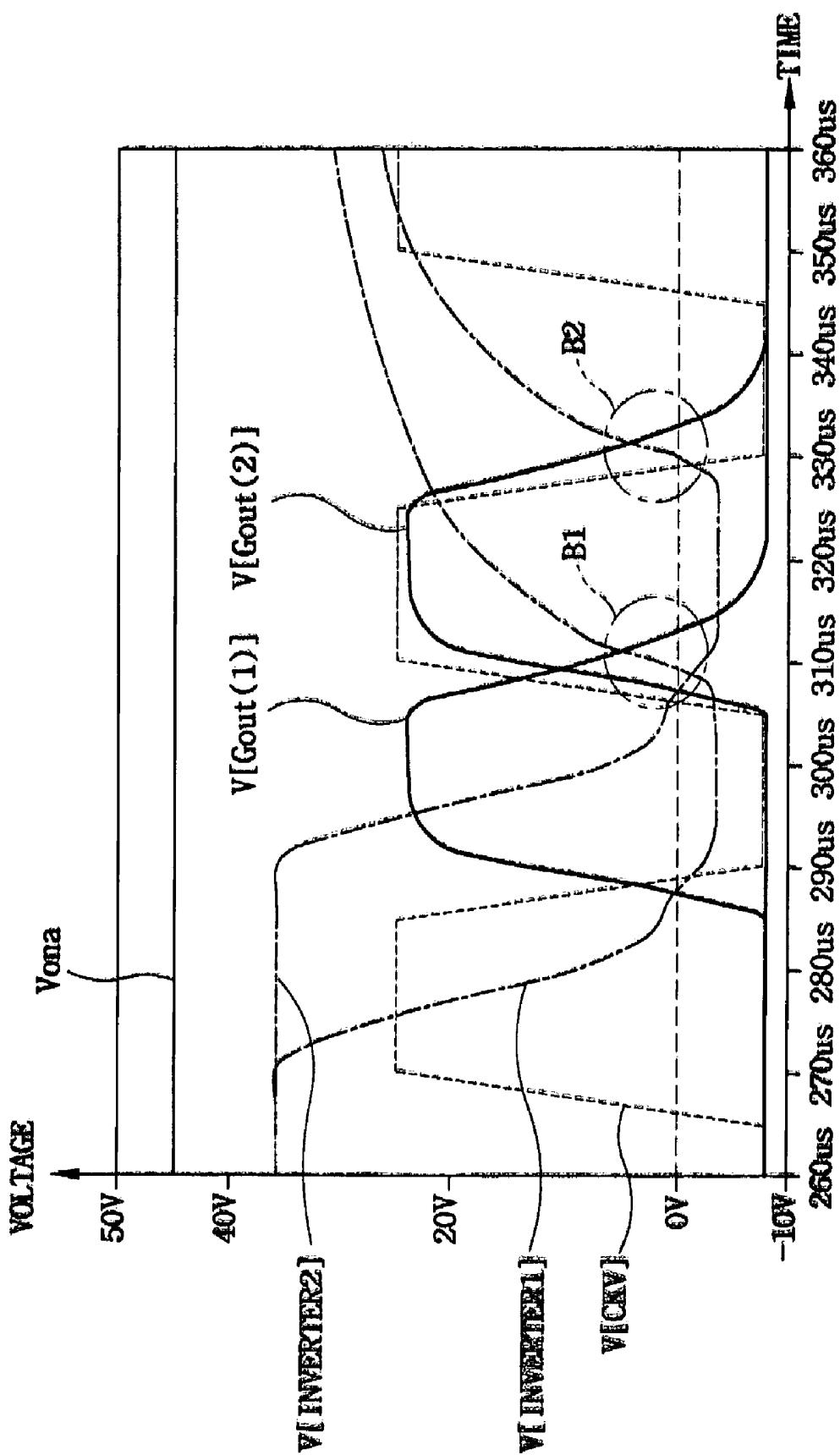

[0065] FIG. 28 is a graph showing the gate line driving signal outputted from the shift register when the same power voltage as that of the power voltage applied to the clock generator of FIG. 27 is applied to the shift register;

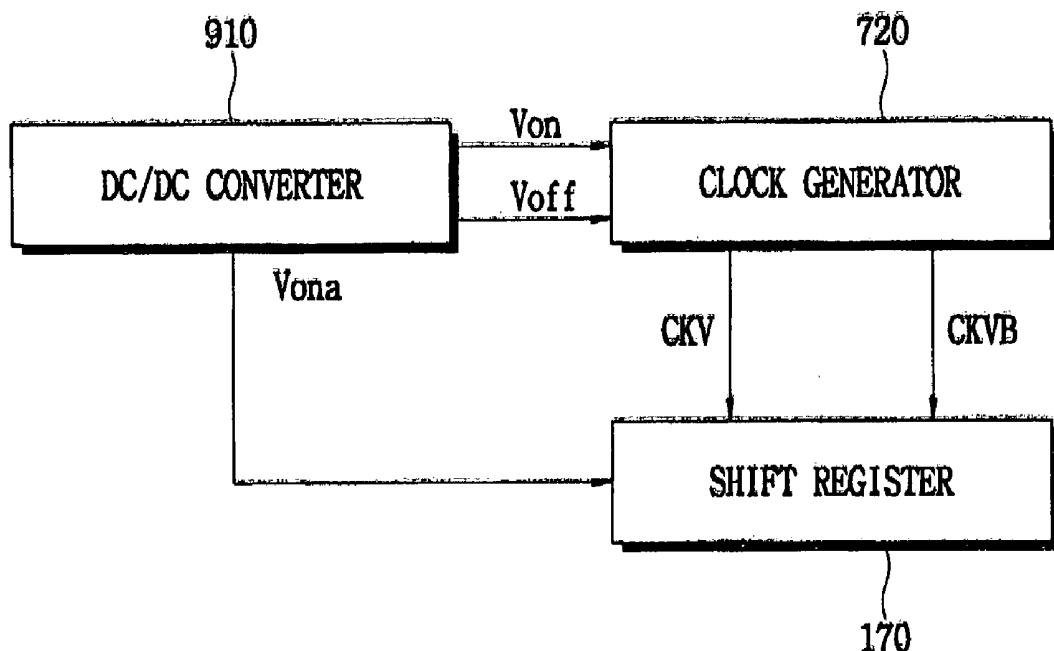

[0066] FIG. 29 is a block diagram showing a power supply and a clock generator according to a seventh exemplary embodiment of the present invention;

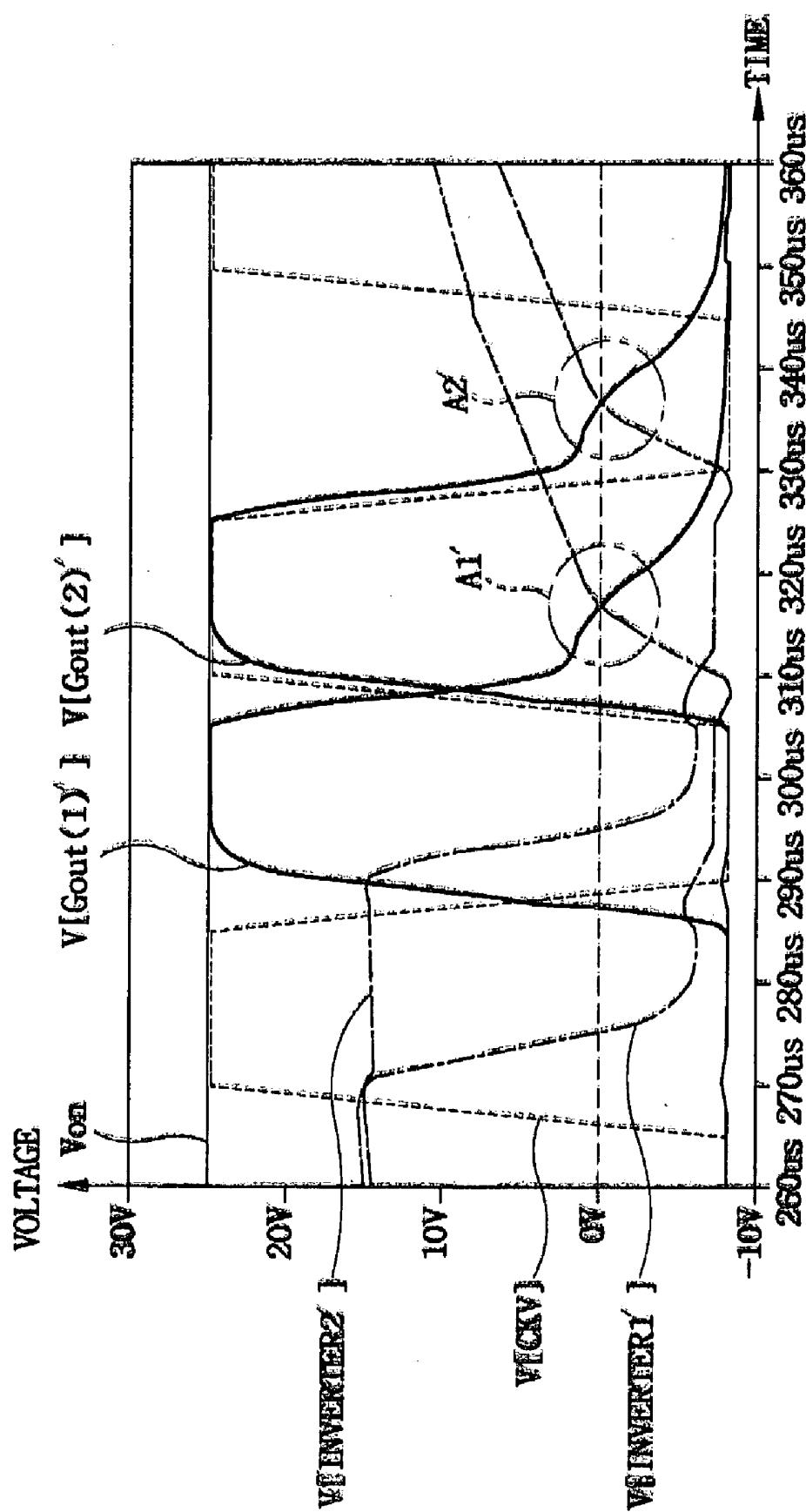

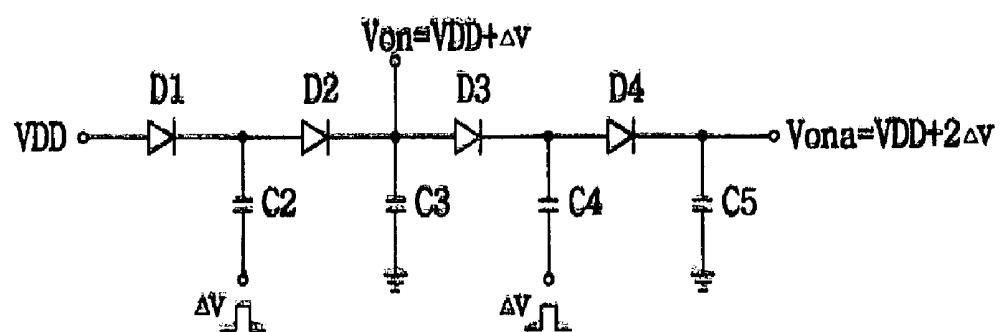

[0067] FIG. 30 is a circuit diagram showing an example of a DC-to-DC converter of FIG. 29;

[0068] FIG. 31 is a graph showing the gate line driving signal outputted from the shift register when the power supply and the clock generator of FIG. 29 drive the shift register; and

[0069] FIG. 32 is a graph showing the gate line driving signals outputted from the shift register when the power supply and the clock generator of FIGS. 29 and 28 drive the shift register.

## DESCRIPTION OF EMBODIMENTS

[0070] Hereinafter the preferred embodiment of the present invention will be described in detail with reference to the accompanying drawings.

[0071] FIG. 3 is an exploded perspective view showing an a-Si thin film transistor LCD according to one exemplary embodiment of the present invention.

[0072] Referring to FIG. 3, the liquid crystal display device 100 includes a liquid crystal display panel assembly 110, a backlight assembly 120, a chassis 130 and a cover case 140.

[0073] The liquid crystal display panel assembly 110 includes a liquid crystal display panel 112, a flexible printed circuit board 116 and an integrated control chip 118. The liquid crystal display panel 112 includes a TFT substrate 112a and a color filter substrate 112b.

[0074] A display cell array, a data driver circuit, a gate driver circuit and external connection terminals are formed on the TFT substrate 112a. Color filters and transparent common electrodes are formed on the color filter substrate 112b. The color filter substrate 112b faces the TFT substrate 112a, and liquid crystal is filled between the color filter substrate 112b and the TFT substrate 112a.

[0075] The integrated control chip 118 is electrically connected to the thin film transistors formed on display cell array of the TFT substrate 112a through the flexible printed circuit 116. Data signal, data timing signal, gate timing signal and power voltage for driving the gate driver circuit is supplied to the data driver circuit and the gate driver circuit formed on the TFT substrate 112a. The display cell array includes a plurality of gate lines, a plurality of data lines and a plurality of switching elements, and the switching elements respectively is connected to each of the data lines and each of the gate lines. The gate driver circuit is connected with the gate lines, and drives the switching elements. The data driver circuit is connected with the data lines, and provides the data lines with image signals.

[0076] The backlight assembly 120 includes a lamp assembly 122, a light-guide plate 124, optical sheets 126, a reflection plate 128 and a mold frame 129.

[0077] FIG. 4 is a schematic view showing an a-Si thin film transistor substrate of FIG. 3.

[0078] Referring to FIG. 4, a display cell array 150, a data driver circuit 160, a gate driver circuit 170 and an external connection terminals 162 and 163 for connecting the data driver circuit 160 to the integrated control chip 118 and another external connection terminal 169 for connecting the gate driver circuit 170 to the integrated control chip 118 are formed on the TFT substrate 112a in the same process in which the TFTs are formed on the TFT substrate 112a.

[0079] The display cell array 150 includes m data lines DL1, DL2, . . . , DLm and n gate lines GL1, GL2, . . . , GLn. The data lines DL1, DL2, . . . , DLm are extended in a column direction, and the gate lines GL1, GL2, . . . , GLn are extended in a row direction. For example, a liquid crystal display panel having 2-inch screen size is disclosed. The liquid crystal display panel has 176 data lines and 192 gate lines, to thereby provide a dot resolution 525 (176×3)×192.

[0080] Switching transistors (ST; or switching elements) are formed on an intersection between the data lines and the gate lines. A drain of the switching transistor ST<sub>i</sub> is connected to a data line DL<sub>i</sub>, a gate of the switching transistor ST<sub>i</sub> is connected to a gate line GL<sub>i</sub>, and a source of the switching transistor ST<sub>i</sub> is connected to a pixel electrode PE. Liquid crystal LC is disposed between the pixel electrode PE and the common electrode CE. The common electrode CE is formed on the color filter substrate 112b.

[0081] Therefore, the voltage applied to the pixel electrode PE and the common electrode CE changes the alignment angle of the liquid crystal molecules, the amount of the light that passing through the liquid crystal molecules are regulated, and an image may be displayed.

[0082] The data driver circuit 160 includes a shift register 164 and 528 switching transistors (SWTs). Each of 8 data line blocks BL1, BL2, . . . , BL8 includes 66 switching transistors (SWTs).

[0083] 66 input terminals of each of the data line blocks are commonly connected to the external connection terminal 163, and 66 output terminals are connected to the 66 corresponding data lines, respectively. The external connection terminal 163 has 66 data input terminals. A block selection terminal is connected to an output terminal of the shift register 164.

[0084] Sources of the 528 switching transistors (SWTs) are connected to the corresponding data lines, drains of the 528 switching transistors (SWTs) are connected to the corresponding data input terminals, respectively, and the gates of the 528 switching transistors (SWTs) are connected to the block selection terminal. Each of the 528 switching transistors (SWTs) is a-Si TFT MOS transistor.

[0085] Accordingly, 66 data lines of the 528 data lines are divided into 8 blocks, and 8 block selection signals may sequentially select each of the blocks.

[0086] The shift register 164 receives a first clock CKH, a second clock CKHB and a block selection start signal STH through the external connection terminal 162 having three terminals. Each of the output terminals of the shift register 164 is connected to the block selection terminal of the corresponding data line block.

[0087] FIG. 5 is a block diagram showing a data driver circuit of FIG. 4.

[0088] Referring to FIG. 5, the shift register 164 according to the present invention includes, for example, 9 stages SRH<sub>1</sub>, SRH<sub>2</sub>, . . . , SRH<sub>9</sub> that are cascade-connected with each other. An output terminal OUT of each of the stages is connected to the input terminal IN of a next stage. The stages includes 8 stages SRH<sub>1</sub>, SRH<sub>2</sub>, . . . , SRH<sub>8</sub> and a dummy stage (SRC<sub>9</sub>). The 8 stages SRH<sub>1</sub>, SRH<sub>2</sub>, . . . , SRH<sub>8</sub> correspond to the 8 data line blocks. Each of the stages includes an input terminal IN, an output terminal OUT, a control terminal CT, a clock terminal CK, a first power voltage terminal VSS and a second power voltage terminal VDD. The 8 stages SRH<sub>1</sub>, SRH<sub>2</sub>, . . . , SRH<sub>8</sub> provide the block selection terminal of each of the data line blocks BL1, BL2, . . . , BL8 with the block selection start signals DE1, DE2, . . . , DE8, respectively. The block selection start signals DE1, DE2, . . . , DE8 is an enable signal for selecting each of the data line blocks.

[0089] The first clock CKH is applied to odd numbered stages SRH<sub>1</sub>, SRH<sub>3</sub>, SRH<sub>5</sub>, SRH<sub>7</sub>, and SRH<sub>9</sub>, and the second clock CKHB is applied to even numbered stages SRH<sub>2</sub>, SRH<sub>4</sub>, SRH<sub>6</sub>, SRH<sub>8</sub>. The first clock CKH has an inverted phase with respect to the second clock CKHB. For example, the duty period of the first clock CKH and the second clock CKHB is lower than 1/66 ms.

[0090] An output signal (or gate line driving signal) of the next stage is applied to a control terminal CT as a control signal.

[0091] The output signals of each of the stages have sequentially an active period (or a high level period), the data line block corresponding to the active period is selected.

[0092] The dummy stage SRH<sub>9</sub> provides the control terminal CT of a previous stage (SRH<sub>8</sub>) with a control signal.

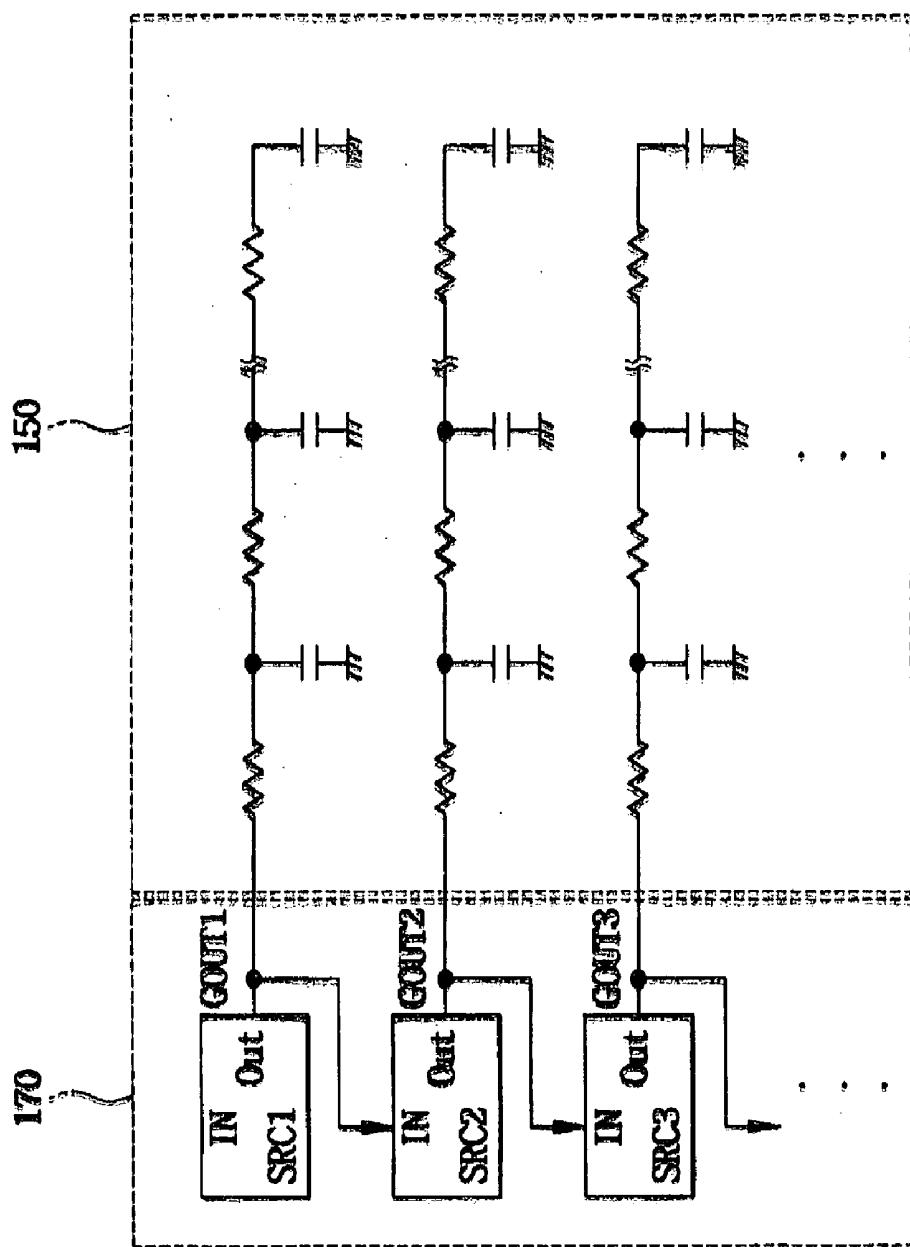

[0093] FIG. 6 is a block diagram showing a shift register used in a gate driver circuit of FIG. 4.

[0094] Referring to FIG. 6, the gate driver circuit 170 includes a shift register, and the shift register, a plurality of stages SRC<sub>1</sub>, SRC<sub>2</sub>, . . . , SRC<sub>192</sub> and a dummy stage SRC<sub>193</sub> that are cascade-connected with each other. An output terminal OUT of each of the stages is connected to an input terminal IN of a next stage. The stages includes 192 stages SRC<sub>1</sub>, SRC<sub>2</sub>, . . . , SRC<sub>192</sub> and a dummy stage SRC<sub>193</sub>.

[0095] Each of the stages includes an input terminal IN, an output terminal OUT, a control terminal CT, a clock signal input terminal CK, a first power voltage terminal VSS and a second power voltage terminal VDD.

[0096] The first stage SRC<sub>1</sub> receives a scan start signal STV through the input terminal IN. The scan start signal STV is a pulse synchronized with a vertical synchronization signal Vsync. Each of the stages SRC<sub>1</sub>, SRC<sub>2</sub>, . . . , SRC<sub>192</sub> generates gate line driving signals GOUT<sub>1</sub>, GOUT<sub>2</sub>, . . . , GOUT<sub>192</sub>, respectively, and the gate line driving signals GOUT<sub>1</sub>, GOUT<sub>2</sub>, . . . , GOUT<sub>192</sub> are connected to the gate lines, respectively, so as to select the gate lines.

[0097] A first clock signal ckv is applied to odd numbered stages (SRC<sub>1</sub>, SRC<sub>3</sub>, SRC<sub>5</sub>, . . . ), and the second clock signal ckvb is applied to even numbered stages (SRH<sub>2</sub>, SRH<sub>4</sub>, SRH<sub>6</sub>, . . . ). The first clock ckv has an inverted phase with respect to the second clock ckvb. For example, the duty period of the first clock ckv and the second clock ckvb is about 16.6/192 ms.

[0098] The duty period of the clock used in the shift register 164 of the data driver circuit is about 8 times larger than that of the clock used in the shift register 170 of the gate driver circuit.

[0099] Output signals GOUT<sub>1</sub>, GOUT<sub>2</sub>, . . . , GOUT<sub>192</sub> of the next stage SRC<sub>2</sub>, SRC<sub>3</sub>, SRC<sub>4</sub> is applied to control terminals CT of the stages SRC<sub>1</sub>, SRC<sub>2</sub>, SRC<sub>3</sub>, respectively, as a control signal.

[0100] The output signals of each of the stages have sequentially an active period (or a high level period), and the gate line corresponding to the active period is selected.

[0101] The dummy stage SRC<sub>193</sub> resets (or inactivates) the last stage (SRH<sub>192</sub>). Specifically, the dummy stage SRC<sub>193</sub> lowers a voltage level of the output signal of the last stage (SRH<sub>192</sub>) from a high voltage level (HIGH) to a low voltage level (LOW).

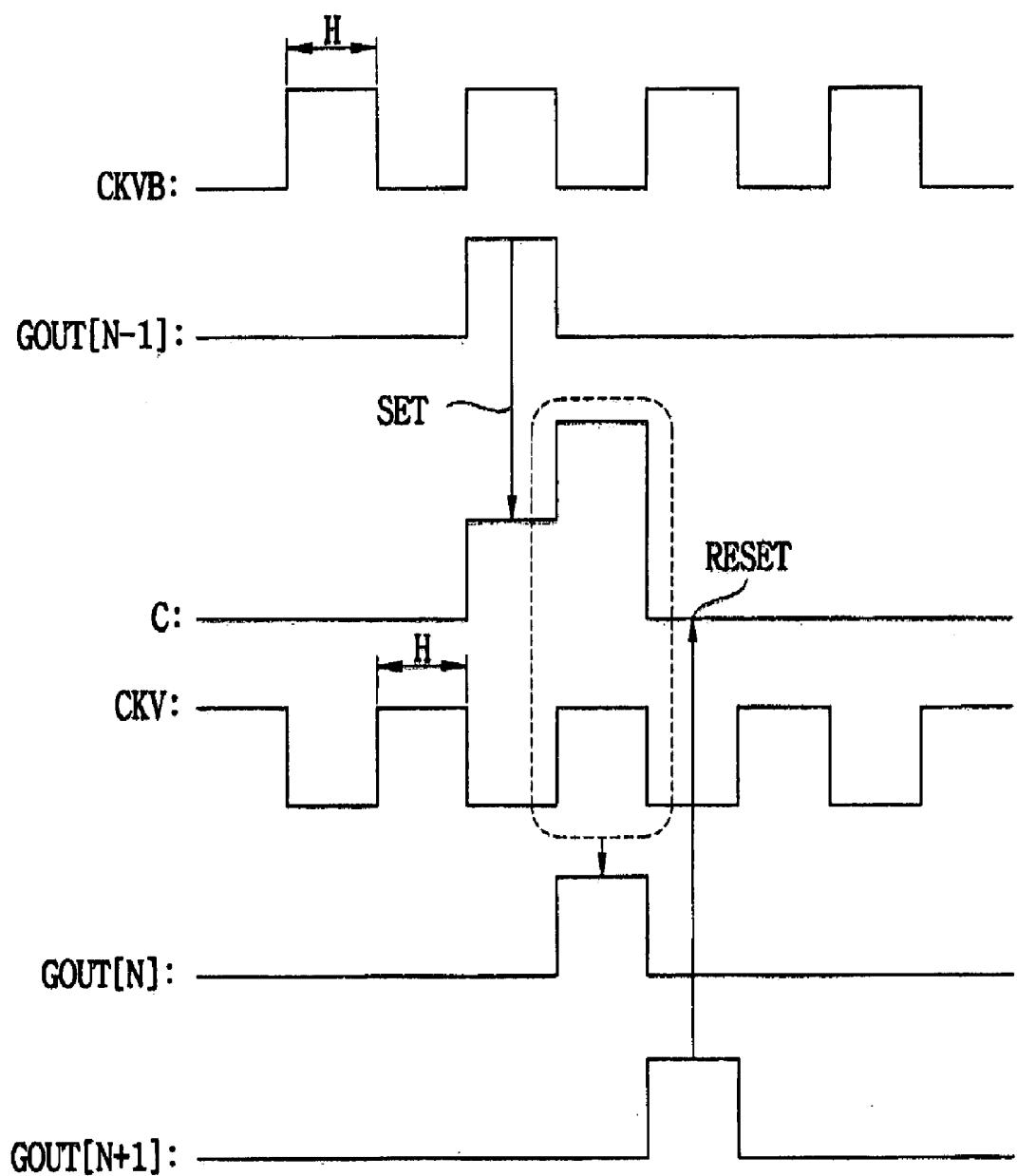

[0102] FIG. 7 is a circuit diagram showing a stage of the shift register of FIG. 6, and FIG. 8 is a graph showing scan line driving signals outputted from the stage of FIG. 7.

[0103] Referring to FIG. 7, each of the stages of the shift register 170 includes a pull-up part 171, a pull-down part 172, a pull-up driver part 173 and a pull-down driver part 174.

[0104] The pull-up part 171 includes a first NMOS transistor M1 of which a drain is connected to a clock signal input terminal CK, a gate is connected to a first node N1 and a source is connected to an output terminal GOUT[N].

[0105] The pull-down part 172 includes a second NMOS transistor M2 of which a drain is connected to an output terminal OUT, a gate is connected to a second node N2 and a source is connected to a first power voltage terminal VSS.

[0106] The pull-up driver part 173 includes a capacitor C and NMOS transistors M3, M4 and M5. The capacitor C is connected between the first node N1 and the output terminal GOUT[N]. The third NMOS Transistor M3 has a drain connected to a second power voltage VON, a gate connected to an output terminal GOUT[N-1] of a previous stage, and a source connected to the first node N1. Transistor M4 has a drain connected to the first node N1, a gate connected to the second node N2 and a source connected to the first power voltage VOFF. Transistor M5 has a drain connected to the first node N1, a gate connected to the second node N2 and a source connected to the first power voltage VOFF. Transistor M3 has a transistor size about two times larger than that of transistor M5.

[0107] The pull-down driver part 174 includes two NMOS transistors M6 and M7. Transistor M6 has a drain and a gate commonly connected with each other to be connected to the second power voltage VON, a source connected to the second node N2. Transistor M7 has a drain connected to the second node N2, a gate connected to the first node N1 and a source connected to the first power voltage VOFF. Transistor M6 has a transistor size about sixteen times larger than that of transistor M7.

[0108] As shown in FIG. 8, when first and second clock signals ckv and ckvb and In scan start signal STV are supplied to the shift register 170, the first stage SRC1 delays a high level period of the first clock signal ckv in response to the front (leading) edge of the scan start signal STV for a predetermined time of Tdr1, to thereby output a delayed output signal GOUT1.

[0109] As described above, the shift register formed on the glass substrate receives the scan start signal STV, the first clock ckv and the second clock ckvb, and drives the gates of the TFTs formed on the TFT substrate.

[0110] Hereinafter, the operation of each of the stages of the shift register is described.

[0111] FIG. 9 is a graph showing the scan line driving signals outputted from the shift register of FIG. 6.

[0112] Referring to FIG. 9, the shift register receives a first clock signal ckv or a second clock signal ckvb and sequentially provides a plurality of gate lines with a plurality of gate line driving signal (GOUT<sub>1</sub>, GOUT<sub>2</sub>, GOUT<sub>3</sub>, . . . ). The second clock ckvb has an inverted phase with respect to the first clock ckv. The first and second clock signals swings

in a period of 2H, as shown in FIG. 9. A signal outputted from a timing controller (not shown) has a voltage in a range from 0 volt to 3 volts and is amplified to have a voltage in a range from -8 volts to 24 volts, so that the first and second clock signals is acquired.

[0113] Referring again to FIG. 7, the output signal (or gate line driving signal) GOUT<sub>N-1</sub> of the previous stage charges the capacitor C and set (or activate) the present stage. The output signal (or gate line driving signal) GOUT<sub>N+1</sub> of the next stage discharges the capacitor C and reset (or inactivate) the present stage.

[0114] When the first clock signal ckv, the second clock signals ckvb and the scan start signal STV are applied to the first stage, a high level period of the first clock signal ckv is delayed by a predetermined period in response to an rising edge of the scan start signal STV to be outputted at the output terminal as an output signal GOUT[1].

[0115] The capacitor C begins to be charged in response to the rising edge of the scan start signal STV that is inputted into the gate of the transistor M1 through the input terminal IN. When the voltage Vc1 charged at the capacitor C is larger than the threshold voltage of the transistor M1, the pull-up transistor M1 is turned on, and the high level period of the first clock signal ckv is outputted at the output terminal OUT.

[0116] When the high level period of the first clock signal CKV is outputted at the output terminal OUT, this output voltage, or the high level period of the first clock signal ckv, is bootstrapped at the capacitor C and thereby the gate voltage of the pull-up transistor M1 rises over the turn-on voltage Von. Accordingly, the NMOS pull-up transistor M1 maintains a full turn-on state. The transistor M2 is turned on even when the transistor M4 is turned on by the scan start signal STV since a transistor size of the transistor M3 is about 2 times larger than that of the transistor M4.

[0117] Meanwhile, the voltage of the first node N1 rises to the second power voltage Von by the transistor M6 before the scan start signal STV is inputted into the pull-down driver part 174, and the transistor M2 is turned on. Accordingly, the output signal of the output terminal OUT has substantially the first power voltage Voff. When the scan start signal STV is inputted to the pull-down driver part 174, the transistor is turned on, and the voltage of the second node N2 is dropped to substantially the first power voltage Voff. Since the transistor size of the transistor M7 is about 16 times larger than that of the transistor M6, the second node N2 maintains substantially the first power voltage Voff even though the transistor M6 is turned on. Accordingly, the pull-down transistor M2 is turned off.

[0118] When the scan start signal STV is applied to the pull-down driver part 74, the pull-down transistor M2 is turned off, and the first clock signal ckv is delayed by a duty period of the first clock signal ckv to be outputted at the output terminal.

[0119] When the voltage of the output signal outputted from the output terminal OUT is dropped to a turn-off voltage Voff (or Vss), the transistor M7 is turned off. Since only the second power voltage Von is provided to the second node N2 through the transistor M6, the voltage of the second node N2 begins to rise from a first power voltage Voff to a second power voltage Von. When the voltage of the fourth node

begins to rise, the transistor M4 is turned on, and the charges at the capacitor are discharged through the transistor M4. Therefore, the pull-up transistor M1 begins to be turned off.

[0120] Then, since the output signal GOUT[N+1] outputted from the next stage rises to the turn-on voltage Von, the transistor M5 is turned on. Since the transistor size of the transistor M5 is about 2 times larger than that of the transistor M4, the voltage of the first node N1 is dropped to the first power voltage Voff more rapidly compared with the case in which only the transistor M4 is turned on.

[0121] In addition, when the voltage of the second node N2 rises to the second power voltage Von, the pull-down transistor M2 is turned on, and the output voltage outputted from the output terminal OUT is changed from the turn-on voltage Von to the turn-off voltage Voff.

[0122] Since the second node N2 is connected to the transistor M6, the second node N2 maintains the second power voltage Von even though the output signal GOUT[N+1] of the next stage that is applied to the control terminal CT is dropped to a low voltage level and the transistor M5 is turned off. Accordingly, the malfunction due to the turn-off of the pull-down transistor M2 is prevented.

[0123] As shown in FIG. 8, the output signals GOUT[1], GOUT[2], GOUT[3], GOUT[4], . . . are sequentially generated.

[0124] As described above, the capacitor C is charged in response to the output signal of the previous stage, the clock signal applied to the pull-up part or pull-down part is outputted as an output signal of the present stage. When the output signal of the next stage is generated at the gate line connected to the output terminal of the next stage, the output signal of the next stage turns on the discharge transistor M5 and discharges the capacitor C, to thereby terminate an operation cycle of the shift register.

[0125] Above described shift register is used as a gate driver circuit in a liquid crystal display device having a small or medium display size, but may not be used as a gate driver circuit in a liquid crystal display device having a large display screen because of an RC delay due to the resistance and capacitance existing in the gate lines.

[0126] As shown in FIG. 6, each of the stages receives a first clock ckv or a second clock ckvb having a period of 2H and applies the first clock ckv or a second clock ckvb to the gate lines.

[0127] Particularly, an Nth stage receives a (N-1)th gate turn-on voltage (or a (N-1)th gate line driving signal) through an input terminal and generates an Nth gate turn-on voltage (or a Nth gate line driving signal) in response to the (N-1)th gate turn-on voltage. The Nth stage receives a (N+1)th gate line driving signal through a control terminal and provides the gate lines with a gate turn-off voltage in response to a (N+1)th gate line driving signal.

[0128] Since the (N-1)th gate turn-on voltage is electrically coupled with a (N-1)th gate line, the load of the (N-1)th gate line electrically affects the input terminal of the Nth stage. Therefore, a signal delay is generated and each of the stage is affected by the loads of the gate lines.

[0129] As shown in FIG. 10, each of the gate lines have a plurality of resistive elements and a plurality of capacitive

elements, and the input terminal of the Nth stage receives the (N-1)th output signal of the (N-1)th stage. Since the input terminal of the Nth stage is connected to the (N-1)th gate line, the signal delay (for example an RC delay) may occurs due to an RC load of the gate lines.

[0130] In addition, since each of the stages is cascade-connected with each other, the signal delay may increase according as N increases because of the RC loads of the previous gate lines (first gate line, second gate line, . . . , (N-1)th gate line) connected to previous stages (first stage, second stage, . . . , (N-1)th stage). Therefore, display quality may be seriously deteriorated. In a liquid crystal display device having small or medium screen sizes, the signal delay may not cause above seriously deteriorated display quality since the RC load of the gate lines are small and the period during which the gate turn-on voltage is shown is long. However, in a liquid crystal display device having a large display screen size, the signal delay may cause above seriously deteriorated display quality.

[0131] An external signal instead of the gate line driving signal outputted from the previous stage may be used so as to activate (or set) the next stage.

[0132] FIG. 11 is a block diagram showing a shift register used in a gate driver circuit according to a first exemplary embodiment of the present invention.

[0133] Referring to FIG. 11, the gate driver circuit according to the first exemplary embodiment of the present invention includes a plurality of stages SRC<sub>1</sub>, SRC<sub>2</sub>, SRC<sub>3</sub>, . . . , SRC<sub>N</sub>, SRC<sub>N+1</sub> that are cascade-connected with each other and a plurality of carry buffers CB<sub>1</sub>, CB<sub>2</sub>, . . . , CB<sub>N</sub>. The carry buffers CB<sub>1</sub>, CB<sub>2</sub>, . . . , CB<sub>N</sub> are interposed between two adjacent stages. An output terminal OUT of each of the stages is connected to an input terminal IN of a next stage. The stages includes N stages SRC<sub>1</sub>, SRC<sub>2</sub>, . . . , SRC<sub>N</sub> and a dummy stage SRC<sub>N+1</sub>.

[0134] Each of the stages includes an input terminal IN, an output terminal OUT, a control terminal CT, a clock signal input terminal CK, a first power voltage terminal VSS, a second power voltage terminal VDD and a carry output terminal CRR.

[0135] The first stage SRC<sub>1</sub> receives a scan start signal STV through the input terminal IN. The scan start signal STV is a pulse signal synchronized with a vertical synchronization signal Vsync supplied from an external graphic controller (not shown).

[0136] The stages SRC<sub>2</sub>, . . . , SRC<sub>N</sub> receives a carry voltage supplied from the carry output terminal CRR of a previous stage through a carry buffer.

[0137] Each of the stages SRC<sub>1</sub>, SRC<sub>2</sub>, . . . , SRC<sub>192</sub> generates gate line driving signals GOUT<sub>1</sub>, GOUT<sub>2</sub>, . . . , GOUT<sub>192</sub>, respectively, and the gate line driving signals GOUT<sub>1</sub>, GOUT<sub>2</sub>, . . . , GOUT<sub>192</sub> are connected to the gate lines, respectively, so as to select the gate lines.

[0138] A first clock signal ckv is applied to odd numbered stages (SRC<sub>1</sub>, SRC<sub>3</sub>, SRC<sub>5</sub>, . . . ), and the second clock signal ckvb is applied to even numbered stages (SRC<sub>2</sub>, SRC<sub>4</sub>, SRC<sub>6</sub>, . . . ). The first clock ckv has an inverted phase with respect to the second clock ckvb. For example, the duty period of the first clock ckv and the second clock ckvb is about 16.6/192 ms.

[0139] The duty period of the clock used in the shift register 164 of the data driver circuit is about 8 times larger than that of the clock used in the shift register 170 of the gate driver circuit.

[0140] Output signals  $GOUT_2, \dots, GOUT_{192}$  of the next stage  $SRC_2, SRC_3, SRC_4$  is applied to control terminals CT of the stages  $SRC_1, SRC_2, SRC_3$ , respectively, as a control signal.

[0141] The carry buffers  $CB_1, CB_2, \dots, CB_N$  uses the clock signals supplied from an external power source as a carry signal instead of the gate line driving signal outputted from the previous stage so as to activate (or set) the next stage. The carry buffers  $CB_1, CB_2, \dots, CB_N$  may be installed inside each of the stages.

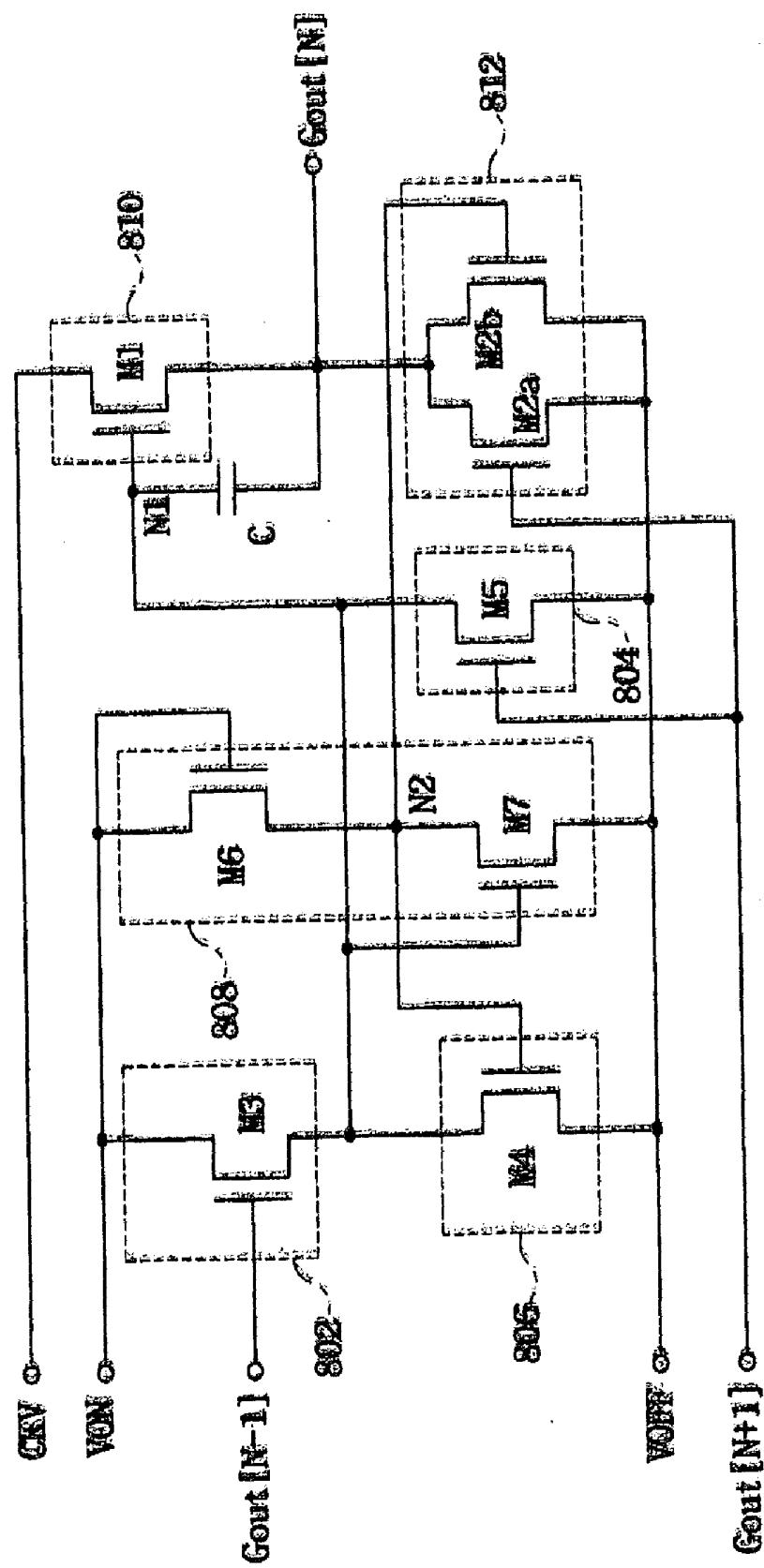

[0142] FIG. 12 is a circuit diagram showing an Nth stage in the shift register of FIG. 11.

[0143] Referring to FIG. 12, each of the stages of the shift register includes a pull-up part 171, a pull-down part 172, a pull-up driver part 173, a pull-down driver part 174 and a carry buffer 275.

[0144] The pull-up part 171 includes a first NMOS transistor M1 of which a drain is connected to a clock signal input terminal CK, a gate is connected to a first node N1 and a source is connected to an output terminal  $GOUT[N]$ .

[0145] The pull-down part 172 includes a second NMOS transistor M2 of which a drain is connected to the output terminal  $GOUT[N]$ , a gate is connected to a second node N2 and a source is connected to a first power voltage terminal VSS.

[0146] The pull-up driver part 173 includes a capacitor C and NMOS transistors M3, M4 and M5. The capacitor C is connected between the first node N1 and the output terminal  $GOUT[N]$ . The third NMOS Transistor M3 has a drain connected to a second power voltage VON, a gate connected to an output terminal  $GOUT[N-1]$  of a previous stage, and a source connected to the first node N1. Transistor M4 has a drain connected to the first node N1, a gate connected to the second node N2 and a source connected to the first power voltage VOFF. Transistor M5 has a drain 10 connected to the first node N1, a gate connected to the second node N2 and a source connected to the first power voltage VOFF. Transistor M3 has a transistor size about two times larger than that of transistor M5.

[0147] The pull-down driver part 174 includes two NMOS transistors M6 and M7. Transistor M6 has a drain and a gate commonly connected with each other to be connected to the second power voltage VON, a source connected to the second node N2. Transistor M7 has a drain connected to the second node N2, a gate connected to the first node N1 and a source connected to the first power voltage VOFF. Transistor M6 has a transistor size about sixteen times larger than that of transistor M7.

[0148] The carry buffer 275 includes a carry buffer transistor TR1 and outputs the first clock ckv or the second clock ckvb to the next stage. Particularly, a gate of the carry buffer transistor TR1 is connected to an input terminal of the pull-down driver part 174, a drain of the carry buffer transistor TR1 is connected to a clock terminal CKV or CKVB, and a source of the carry buffer transistor TR1 is connected to a gate of a third transistor M3 of pull-up part 173 of the next stage.

[0149] The carry buffer transistor TR1 of a previous stage receives the first clock ckv or the second clock ckvb and transfers the first clock ckv or the second clock ckvb to the present stage as a carry signal. Since the clock signals having substantially a uniform voltage level is used as the carry signal, the RC delay due to the RC load of the gate lines may not occur.

[0150] FIG. 13 is a circuit diagram showing a last stage and a dummy stage in the shift register of FIG. 11.

[0151] Referring to FIG. 13, each of the stages of the shift register includes a pull-up part 171, a pull-down part 172, a pull-up driver part 173, a pull-down driver part 174 and a carry buffer 275. In FIG. 13, the same reference numerals denote the same elements in FIG. 12, and thus the detailed descriptions of the same elements will be omitted.

[0152] As shown in FIG. 13, since an output signal of the previous stage is affected by the RC load of the gate lines, the output signal of the previous stage is not applied to the input terminal of each of the stages, the clock signals is applied to the input terminal of each of the stages as a carry signal. Therefore, since the clock signals used as the carry signal is independent of the output signal of the previous stage, the RC delay due to the RC load of the gate lines may not occur.

[0153] Hereinafter, an upper stage of FIG. 13 is referred to as a previous stage  $SRC_N$ , a lower stage of FIG. 13 is referred to as a present stage  $SRC_{N+1}$  in order to describe the operation of the shift register of the present invention.

[0154] The carry buffer transistor TR1 of a previous stage  $SRC_N$  receives the first clock ckv (or a control signal of the pull-up transistor M1) for activating (or setting) the present stage  $SRC_{N+1}$ , and transfers substantially the first clock ckv to the present stage  $SRC_{N+1}$  as a carry signal. Since the clock signal ckv having substantially a uniform voltage level is used as the carry signal, the RC delay due to the RC load of the gate lines may not occur.

[0155] The third transistor M3 remains in a turn-off state before the carry signal CA[N] is applied to a gate of the third transistor M3. When the carry signal CA[N] is applied to the gate of the third transistor M3, after a predetermined period, the third transistor M3 is turned on to form a current path through which the second power voltage Von is charged at the capacitor C.

[0156] When the clock ckv having a low level, or the voltage level of the first power voltage Voff, is applied to the gate of the third transistor M3, the third transistor M3 is turned off.

[0157] FIG. 14 is a schematic view showing the shift register of FIG. 11 and the gate lines.

[0158] Referring to FIG. 14, each of the stages ( $SRC_1, SRC_2, SRC_3, \dots$ ) sequentially applies a plurality of gate line driving signals ( $GOUT_1, GOUT_2, GOUT_3, \dots$ ), respectively, through the output terminal of each of the stages in order to select the gate lines of a liquid crystal display panel 150.

[0159] In addition, each of the stages ( $SRC_1, SRC_2, SRC_3, \dots$ ) sequentially applies a carry signal to an input terminal of the next stage through a carry output terminal CA. The carry signal is a first clock ckv or a second clock ckvb. The

first clock ckv or the second clock ckvb is supplied from an external power source and is independent of each of the stages. The second clock ckvb has an inverted phase with respect to the first clock ckv.

[0160] Since, instead of a gate line driving signal outputted from an output terminal OUT of a previous stage, the carry signal outputted from the carry output terminal of the previous stage is applied to the input terminal of the present stage in order to activate the present stage, the deterioration of the display quality due to RC load of the gate lines may be prevented.

[0161] FIGS. 15A and 15B are layouts showing a pull-up part, a pull-down part and a carry buffer in a stage of the shift register of FIG. 11, and FIGS. 15C is an enlarged view showing the carry buffer in the shift register of FIG. 15A.

[0162] The pull-up NMOS transistor M1 and the pull-down NMOS transistor M2 of FIG. 12 has a transistor size larger than that of the pull-up driver NMOS transistors M3, M4, M5 and the pull-down driver NMOS transistor M6, M7 in order to drive the gate line connected to the pull-up transistor M1 and the pull-down transistor M2.

[0163] As shown in FIGS. 15A, 15B and 15C, a gate wiring and an active pattern is sequentially formed in a predetermined region on an insulation substrate, and a plurality of drain electrodes and a plurality of source electrodes are formed in a 'branch' type shape (or 'finger' type shape) on the gate wiring, so that pull-up transistors (M1[N] and M1[N+1]) and pull-down transistors (M2[N] and M2[N+1]) is formed. The gate wiring includes a gate electrode (or gate electrodes) and a gate line (or gate lines). M1[N] is a pull-up transistor M1 of the Nth stage, and M1[N+1] is a pull-up transistor M1 of the (N+1)th stage. M2[N] is a pull-down transistor M2 of the Nth stage, and M2[N+1] is a pull-down transistor M2 of the (N+1)th stage. In the 'branch' type shape of the present invention, the drain electrodes are branched from a main drain wiring and each of the drain electrodes is inserted into the branches of the drain electrodes. For example, the active pattern is composed of amorphous silicon. Hereinafter, the Nth stage is referred to as a present stage, and the (N+1)th stage is referred to as a next stage.

[0164] Particularly, the gate wiring of the pull-up transistors (M1[N] and M1[N+1]) is formed in a first predetermined region by which a first predetermined area is defined. For example, the first predetermined region may have a rectangular shape. The active pattern of the pull-up transistors (M1[N] and M1[N+1]) is formed on the gate wiring of the pull-up transistors (M1[N] and M1[N+1]). The drain electrodes of the pull-up transistors (M1[N] and M1[N+1]) are branched from the main drain wiring 300 extended in a downward direction and are formed on the active pattern of the pull-up transistors (M1[N] and M1[N+1]). Each of the source electrodes of the pull-up transistors (M1[N] and M1[N+1]) is formed between the branches (or drain lines) of the drain electrodes. Namely, each of the branches (or source lines) of the source electrodes is formed between the branches (or drain lines) of the drain electrodes. The source electrode of the pull-up transistors (M1[N] and M1[N+1]) may be further formed at the exterior of the drain electrodes of the pull-up transistors (M1[N] and M1[N+1]). Each of the source electrodes of the pull-up transistors (M1[N] and M1[N+1]) is electrically connected to gate lines through

contact holes (CNT1, CNT2). For example, the width of each of the drain lines may be about 5  $\mu\text{m}$ , and the width of each of the gate lines may be about 5  $\mu\text{m}$ . For example, the width of the main drain line may be greater than about 5  $\mu\text{m}$ . The less the distance (L) between a drain line and a source line is, the better is the property of the thin film transistor (TFT). For example, the less the distance (L) between a drain line and a source line is, the larger is the transistor size (W/L).

[0165] Particularly, the gate wiring of the pull-down transistors (M2[N] and M2[N+1]) is formed in a second predetermined region by which a second predetermined area is defined. For example, the second predetermined region may have a rectangular shape. The active pattern of the pull-down transistors (M2[N] and M2[N+1]) is formed on the gate wiring of the pull-down transistors (M2[N] and M2[N+1]). The drain electrodes of the pull-down transistors (M2[N] and M2[N+1]) are branched from the main drain wiring 300 extended in a upward direction and are formed on the active pattern of the pull-down transistors (M2[N] and M2[N+1]). Each of the drain electrodes of the pull-down transistors (M2[N] and M2[N+1]) is electrically connected to the gate lines through contact holes (CNT1, CNT2). Each of the source electrodes of the pull-down transistors (M2[N] and M2[N+1]) is formed between the branches (or drain lines) of the drain electrodes. Namely, each of the branches (or source lines) of the source electrodes is formed between the branches (or drain lines) of the drain electrodes. The source electrode of the pull-down transistors (M2[N] and M2[N+1]) may be further formed at the exterior of the drain electrodes of the pull-down transistors (M2[N] and M2[N+1]).

[0166] Particularly, the plurality of source electrodes of the pull-up transistors (M1[N] and M1[N+1]) and the plurality of drain electrodes of the pull-down transistors (M2[N] and M2[N+1]) are commonly connected to the first contact hole CNT1 in order that the source electrodes of the pull-up transistors (M1[N] and M1[N+1]) and the plurality of drain electrodes of the pull-down transistors (M2[N] and M2[N+1]) may be commonly connected to gate lines. Since the height of the source electrodes of the pull-up transistors (M1[N] and M1[N+1]) or the height of the source electrodes of the pull-down transistors (M2[N] and M2[N+1]) is different from the height of gate lines, the source electrodes of the pull-up transistors (M1[N] and M1[N+1]) or the pull-down transistors (M2[N] and M2[N+1]) is connected to the gate lines by means of a bridge that is formed between a first indium tin oxide (ITO1) layer and a second contact hole CNT2. The first indium tin oxide (ITO1) layer comprises a conductive material. The first indium tin oxide (ITO1) layer is connected to a first contact hole CNT1.

[0167] The carry buffer transistor TR1 is formed at a position adjacent to the pull-up transistor M1 in order to supply the first clock ckv or the second clock ckvb applied to the drain electrode of the pull-up transistor M1 of the present stage to the gate electrode of the third transistor M3 of the next stage.

[0168] Particularly, the gate electrode of the carry buffer transistor TR1 is commonly connected to the gate electrode of the pull-up transistors (M1[N] and M1[N+1]). The drain electrode of the carry buffer transistor TR1 may be branched from the main drain wiring of the pull-up transistors (M1[N] and M1[N+1]). The source electrode of the carry buffer

transistor TR1 detours (or bypasses) the pull-up transistors (M1[N] and M1[N+1]) and the pull-down transistors (M2[N] and M2[N+1]) to be extended to a gate electrode of the third transistor M3 of the next stage.

[0169] Since the height of the branches (or source line) of the source electrodes of the carry buffer transistor TR1 is different from the height of gate wiring connected to the gate electrode of the third transistor M3 of the next stage, the source electrode of the carry buffer transistor TR1 is connected to the gate wiring connected to the gate electrode of the third transistor M3 by means of a bridge that is formed between a second indium tin oxide (ITO2) layer and a fourth contact hole CNT4. The second indium tin oxide (ITO2) layer comprises a conductive material. The second indium tin oxide (ITO2) layer is connected to the source line of the carry buffer transistor TR1 through a third contact hole CNT3.

[0170] The shift register of **FIGS. 7 and 8** is used in the liquid crystal display panel having a small or a medium screen size such as 525 (176×3)×192, but the shift register of **FIGS. 7 and 8** may not be used in the liquid crystal display panel having a large screen size because of the signal delay problem.

[0171] The transistor size of the pull-up or the pull-down transistor (M1 or M2) needs to be increased in order that the shift register of **FIGS. 7 and 8** may be used in the liquid crystal display panel having the large screen size. However, there is a limit in the increase of the transistor size of the pull-up or the pull-down transistor (M1 or M2) because of the limit of a chip area for the shift register.

[0172] Therefore, the reliability and the yield for manufacturing the liquid crystal display device may not be guaranteed because the threshold voltage of the thin film transistor varies due to the limit of the transistor size of the pull-up or the pull-down transistor (M1 or M2) and the property of the amorphous silicon thin film transistor.

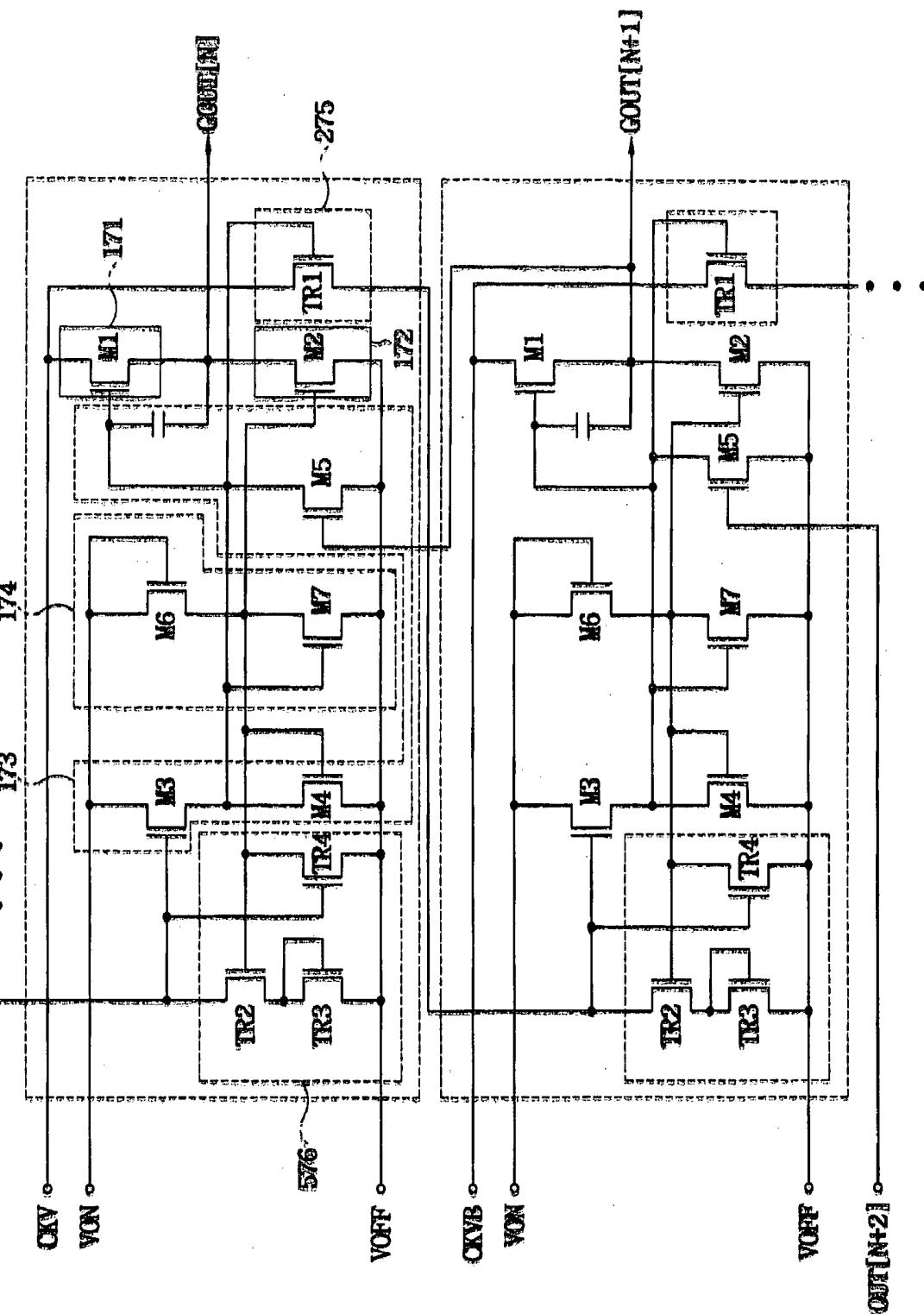

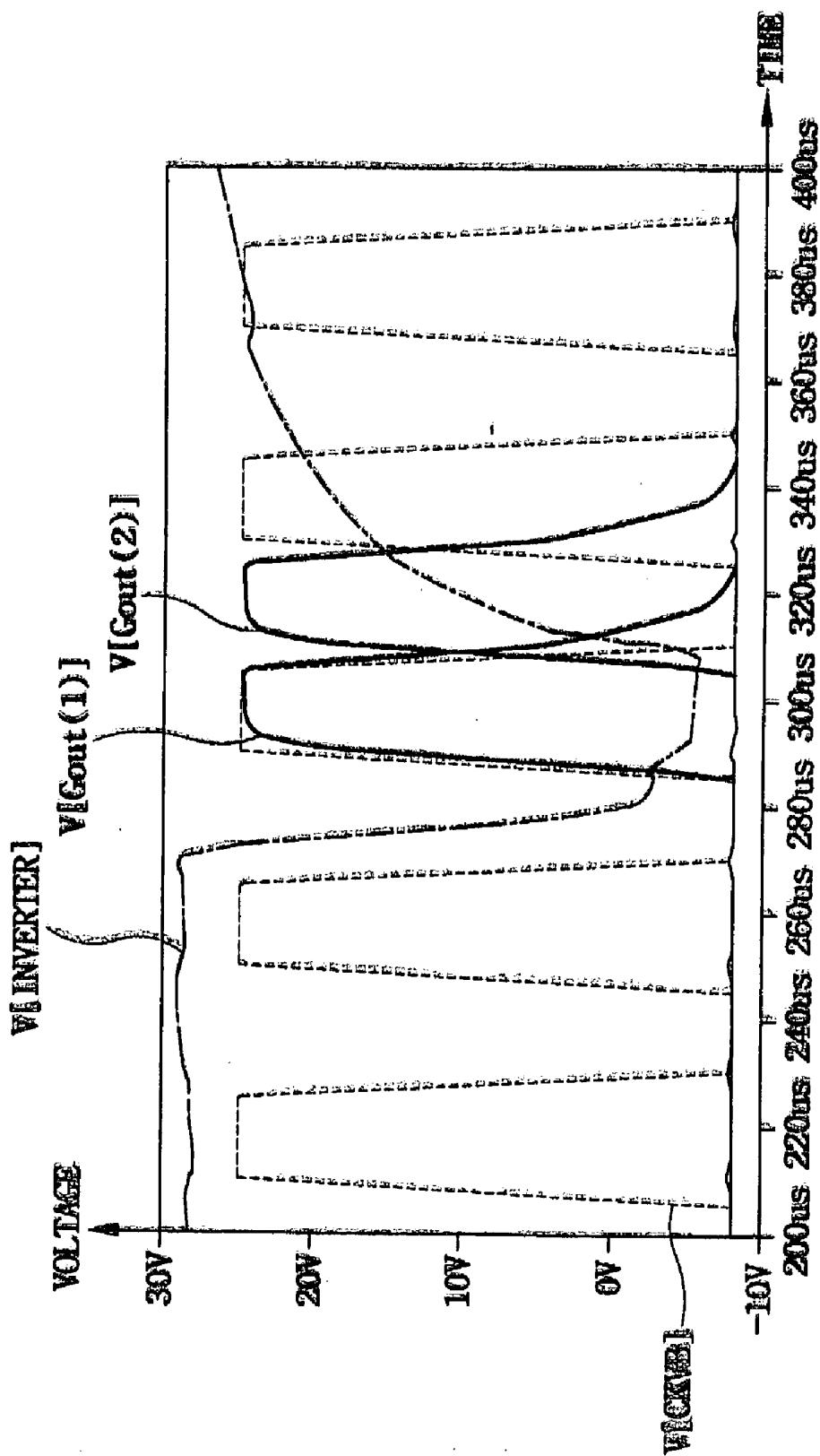

[0173] **FIGS. 16A, 16B and 16C** are graphs showing the gate line driving signal outputted from the shift register of **FIG. 7**.

[0174] Referring to **FIG. 16A**, when the thin film transistors of the shift register have normal threshold voltages in a room temperature, the gate line driving signals (GOUT<sub>1</sub>, GOUT<sub>2</sub>, GOUT<sub>3</sub>, ...) are similar to a square wave and have a uniform peak voltage level of about 25 volts.

[0175] Referring to **FIG. 16B**, the threshold voltage of the thin film transistors of the shift register decreases according as the temperature increases, the gate line driving signals (GOUT<sub>1</sub>, GOUT<sub>2</sub>, GOUT<sub>3</sub>, ...) are similar to a square wave, but the gate line driving signals (GOUT<sub>1</sub>, GOUT<sub>2</sub>, GOUT<sub>3</sub>, ...) have a decreasing peak voltage level. Namely, the peak voltage level of the first gate line driving signal GOUT<sub>1</sub> has about 20 volts, and the peak voltage level of the second gate line driving signal GOUT<sub>2</sub> is lower than 20 volts.

[0176] As shown in **FIG. 16B**, an override signal of which waveform is like a spark is applied to specific gate lines. The gate line driving signals (GOUT<sub>1</sub>, GOUT<sub>2</sub>, GOUT<sub>3</sub>, ...) have a decreasing peak voltage level due to the override signal, so that gate line driving signals having abnormal waveform are generated.

[0177] Referring to **FIG. 16C**, the threshold voltage of the thin film transistors of the shift register increases according as the temperature decreases, the gate line driving signals (GOUT<sub>1</sub>, GOUT<sub>2</sub>, GOUT<sub>3</sub>, ...) is not similar to a square wave, and the gate line driving signals (GOUT<sub>1</sub>, GOUT<sub>2</sub>, GOUT<sub>3</sub>, ...) have a decreasing peak voltage level. Namely, the peak voltage level of the first gate line driving signal GOUT<sub>1</sub> has about 22 volts, and the peak voltage level of the second gate line driving signal GOUT<sub>2</sub> is lower than 22 volts.

[0178] When the thin film transistors of the shift register have normal threshold voltages in a room temperature, the shift register operates normally, and the gate line driving signals outputted from the shift register are similar to a square wave and have a uniform peak voltage level.

[0179] However, when the threshold voltage of the thin film transistors of the shift register varies according as the temperature decreases (or increases), the gate line driving signals outputted from the shift register has an abnormal waveform, or a uniform peak voltage level. Therefore, the gate line driving signals having an abnormal waveform does not normally turn on the switching devices (switching elements) disposed on the liquid crystal display panel, and the display quality of the liquid crystal display device is deteriorated.

[0180] As shown in **FIG. 6**, the shift register has a circuit structure in which the gate line driving signal outputted from the previous stage affects the gate line driving signal outputted from the present stage, certain stages may not output a gate line driving signal when the threshold voltage of the thin film transistors of the shift register varies and each of the stages are driven sequentially by the shift register, especially in the liquid crystal display device having a large display screen size.

[0181] **FIG. 17** is a block diagram showing a shift register used in a gate driver circuit according to a second exemplary embodiment of the present invention.

[0182] Referring to **FIG. 17**, each of the stages of the shift register includes a pull-up part 171, a pull-down part 172, a pull-up driver part 173, a pull-down driver part 174, a first carry buffer 275 and a second carry buffer 276. In **FIG. 17**, the same reference numerals denote the same elements in **FIG. 7**, and thus the detailed descriptions of the same elements will be omitted.

[0183] The first carry buffer 275 includes a first carry buffer transistor TR1 and outputs the first clock ckv or the second clock ckvb to the next stage.

[0184] Particularly, a gate of the first carry buffer transistor TR1 is connected to an input terminal of the pull-down driver part 174, a drain of the first carry buffer transistor TR1 is connected to a clock terminal CKV or CKVB, and a source of the carry buffer transistor TR1 is connected to the second carry buffer 276 of the next stage.

[0185] The second carry buffer 276 includes a second carry buffer transistor TR2 that is controlled by the pull-down driver part 174, or an inverter. Particularly, the buffer transistor M3 is turned on by the first clock ckv or the second clock ckvb that is supplied from the first carry buffer 275 to be applied to the pull-up part 171, then the output voltage of the second carry buffer 276 (or the inverter) has a low

voltage level, and the second carry buffer 276 is turned off. Therefore, the voltage level of the carry signal may not be lowered when the carry signal is transferred to the second carry buffer transistor TR2.

[0186] A drain of the second carry buffer transistor TR2 is connected to an input terminal of the pull-up driver part 173 of the present stage and is also connected to the source of the first carry buffer transistor TR1. A gate of the second carry buffer transistor TR2 is connected to a gate of the second transistor M2, or the pull-down part 172, and a source of the second carry buffer transistor TR2 receives the first power voltage through the first power voltage terminal VOFF.

[0187] In addition, after a 1H period, the second carry buffer transistor TR2 maintains a turn-on state while the pull-down driver part 174 is turned on, and applies the first power voltage Voff to the buffer transistor M3 so as to turn off the buffer transistor M3. The first power voltage terminal VOFF is the same as the power voltage terminal VSS of FIG. 5.

[0188] Since the clock signals instead of the gate line driving signal outputted from the previous stage are used as the carry signal, the gate line driving signal outputted from each of the stages are independent of the gate line driving signal of the previous stage.

[0189] Hereinafter, an upper stage of FIG. 17 is referred to as a previous stage SRC<sub>N</sub>, a lower stage of FIG. 17 is referred to as a present stage SRC<sub>N+1</sub> in order to describe the operation of the shift register of the present invention.