# (11) **EP 2 924 498 A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication: 30.09.2015 Bulletin 2015/40

(51) Int Cl.: **5/40 G02F 1/1343** (2006.01) G02F 1/1362 (2006.01)

H01L 27/00 (2006.01)

(21) Application number: 10010225.0

(22) Date of filing: 20.03.2007

(84) Designated Contracting States: **DE FI FR GB NL**

(30) Priority: 06.04.2006 JP 2006105618

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC: 07005724.5 / 1 843 194

(71) Applicant: Semiconductor Energy Laboratory Co, Ltd.

Atsugi-shi, Kanagawa-ken 243-0036 (JP)

(72) Inventor: Kimura, Hajime Atsugi-shi Kanagawa-ken 243-0036 (JP)

(74) Representative: Grünecker Patent- und Rechtsanwälte

PartG mbB

Leopoldstraße 4

80802 München (DE)

## Remarks:

This application was filed on 22-09-2010 as a divisional application to the application mentioned under INID code 62.

## (54) Liquid crystal desplay device, semiconductor device, and electronic appliance

(57) The liquid crystal display device includes an island-shaped first semiconductor film 102 which is formed over a base insulating film 101 and in which a source 102d, a channel forming region 102a, and a drain 102b are formed; a first electrode 102c which is formed of a material same as the first semiconductor film 102 to be the source 102d or the drain 102b and formed over the base insulating film 101; a second electrode 108 which

is formed over the first electrode 102c and includes a first opening pattern 112; and a liquid crystal 110 which is provided over the second electrode 108. The electrical contact between the drain electrode (102b) and the second electrode is provided by a conductive film (107b) which is on and in contact with the second electrode (108).

EP 2 924 498 A1

30

35

40

## Description

#### **BACKGROUND OF THE INVENTION**

#### 1. Field of the Invention

**[0001]** The present invention relates to a semiconductor device, a liquid crystal display device, and an electronic appliance including them. In particular, the present invention relates to a semiconductor device and a liquid crystal display device in which an electric field generally parallel to a substrate is generated to control liquid crystal molecules, and an electronic appliance including the semiconductor device or the liquid crystal display device.

## 2. Description of the Related Art

[0002] As one of plans for technical development of a liquid crystal display device, to widen a viewing angle can be given. As a technique for realizing a wide viewing angle, a mode in which an electric field generally parallel to a substrate is generated and liquid crystal molecules are moved in a plane parallel to the substrate to control grayscale is employed. As such a mode, IPS (In-Plane Switching) and FFS (Fringe-Field Switching) are given. In these modes, a first electrode (such as a pixel electrode with which voltage is controlled for each pixel) having a slit (an opening pattern) is located under a liquid crystal and a second electrode (such as a common electrode with which common voltage is applied to all pixels) is located under the first electrode. An electric field is applied between the pixel electrode and the common electrode, so that the liquid crystal is controlled. With such layout, an electric field in a direction parallel to a substrate is applied to the liquid crystal. Therefore, the liquid crystal molecules can be controlled with the electric field. That is, the liquid crystal molecules which are aligned parallel to the substrate (so called homogeneous alignment) can be controlled in a direction parallel to the substrate; therefore, viewing angle is increased.

**[0003]** Conventionally, both common electrode and pixel electrode are formed of ITO (indium tin oxide) (Patent Document 1: Japanese Published Patent Application No. 2000-89255 (FIG 5 and 14th paragraph)).

## SUMMARY OF THE INVENTION

[0004] As described above, in the case of employing a structure in which the second electrode (such as the common electrode) is located under the first electrode (such as the pixel electrode), both the common electrode and the pixel electrode are formed of ITO conventionally. Accordingly, the numbers of manufacturing steps and masks, and manufacturing cost have been increased. The present invention is made in view of the foregoing, and an object of the present invention is to provide a liquid crystal display device and an electronic appliance with wide viewing angle, having less numbers of manu-

facturing steps and masks and low manufacturing cost compared with a conventional device; and to provide a manufacturing method of the liquid crystal display device. [0005] To solve the aforementioned problems, a liquid crystal display device according to the present invention includes a first electrode formed over a substrate, an insulating film formed over the first electrode, a second electrode formed over the insulating film, and a liquid crystal provided over the second electrode; in which the second electrode has an opening pattern and the first electrode has a semiconductor film containing silicon.

**[0006]** A semiconductor device according to the present invention includes a first electrode formed over a substrate, an insulating film formed over the first electrode, and a second electrode formed over the insulating film; in which the second electrode has an opening pattern and the first electrode has a semiconductor film containing silicon

[0007] A liquid crystal display device according to the present invention includes a first electrode formed over a substrate, an insulating film formed over the first electrode, a second electrode formed over the insulating film, a liquid crystal provided over the second electrode, and a transistor formed over the substrate; in which the second electrode has an opening pattern, the first electrode has a semiconductor film containing silicon, and the semiconductor film included in the first electrode is formed at the same time as the semiconductor film included in the transistor.

**[0008]** A semiconductor device according to the present invention includes a first electrode formed over a substrate, an insulating film formed over the first electrode, a second electrode formed over the insulating film, and a transistor formed over the substrate; in which the second electrode has an opening pattern, the first electrode has a semiconductor film containing silicon, the transistor has a semiconductor film containing silicon, and the semiconductor film included in the first electrode is formed at the same time as the semiconductor film included in the transistor.

[0009] In the liquid crystal display device and the semiconductor device, the first electrode and the semiconductor film included in the transistor are formed at the same time, and then, etched and patterned at the same time. Accordingly, the first electrode and the semiconductor film included in the transistor contain the same material. In addition, an n-type impurity or a p-type impurity is introduced thereto at the same time in some cases. In such a case, they have a portion with approximately the same concentration of the impurity. Note that the transistor includes a portion to which the impurity is introduced, a portion to which the impurity is slightly introduced, a portion to which the impurity is hardly introduced, and the like. The first electrode is generally in the same states as the portion in the semiconductor film included in the transistor, to which the impurity is introduced in many cases. Thus, the first electrode can be formed

at the same time as the transistor. Therefore, an additional step is not required to form the first electrode. In addition, a liquid crystal display device with wide viewing angle and low manufacturing cost compared with a conventional device can be provided.

**[0010]** Note that the opening pattern includes not only a closed opening pattern such as a slit, but also a space which is located between the conductive patterns and in which the conductive pattern is not formed, such as a space between the comb-teeth of a comb-shaped electrode. The same can be applied to description hereinafter

[0011] Note that in the aforementioned liquid crystal display device and the semiconductor device, a portion in which first and second interlayer insulating films are provided between the first electrode and the second electrode, and the second electrode and the first electrode except for the opening pattern are overlapped each other the first electrode; the first interlayer insulating film, and the second electrode can function as a capacitor. In this case, storage capacitance can be increased. Therefore, when a thin film transistor is turned off, the potential of the pixel electrode can be easily kept.

[0012] A liquid crystal display device according to the present invention includes a first electrode formed over a substrate, an insulating film formed over the first electrode, a second electrode formed over the insulating film, a liquid crystal provided over the second electrode, and a transistor formed over the substrate; in which the second electrode includes an opening pattern, the first electrode includes a semiconductor film containing silicon, the semiconductor film included in the first electrode is formed at the same time as the semiconductor film included in the transistor, and the semiconductor film included in the first electrode and the semiconductor film included in the transistor contain an impurity having the same conductivity type.

[0013] A semiconductor device according to the present invention includes a first electrode formed over a substrate, an insulating film formed over the first electrode, a second electrode formed over the insulating film, and a transistor formed over the substrate; in which the second electrode includes opening pattern, the first electrode includes a semiconductor film containing silicon, the semiconductor film included in the first electrode is formed at the same time as the semiconductor film included in the first electrode and the semiconductor film included in the first electrode and the semiconductor film included in the transistor contain an impurity having the same conductivity type.

**[0014]** When the first electrode and the transistor contain the impurity having the same conductivity type (such as an n-type or a p-type), the layout can be efficient. Accordingly, the aperture ratio can be improved.

**[0015]** A liquid crystal display device according to the present invention includes a transistor formed over a substrate, a semiconductor film formed in the transistor, a first electrode formed by a part of the semiconductor film,

an insulating film formed over the first electrode, a second electrode formed over the insulating film, and a liquid crystal provided over the second electrode; in which the second electrode includes an opening pattern.

**[0016]** A semiconductor device according to the present invention includes a transistor formed over a substrate, a semiconductor film formed in the transistor, a first electrode formed by a part of the semiconductor film, an insulating film formed over the first electrode, and a second electrode formed over the insulating film; in which the second electrode includes an opening pattern.

**[0017]** When the first electrode and the semiconductor film included in the transistor are formed in one island as described above, the layout can be efficient. Accordingly, the aperture ratio can be improved.

**[0018]** In the aforementioned structure of the liquid crystal display device according to the present invention, the first electrode is a pixel electrode and the second electrode is a common electrode.

**[0019]** In the aforementioned structure of the semiconductor device according to the present invention, the first electrode is a pixel electrode and the second electrode is a common electrode.

**[0020]** In the aforementioned structure of the liquid crystal display device according to the present invention, the first electrode is a common electrode and the second electrode is a pixel electrode.

**[0021]** In the aforementioned structure of the semiconductor device according to the present invention, the first electrode is a common electrode and the second electrode is a pixel electrode.

**[0022]** In the aforementioned structure of the liquid crystal display device according to the present invention, orientaion of the liquid crystal is controlled by an electric field between the first electrode and the second electrode.

[0023] Note that a switch shown in the present invention may be any switch such as an electrical switch or a mechanical switch. That is, as long as current flow can be controlled, any type of switch can be used without being limited to a particular type. For example, a transistor, a diode (such as a PN diode, a PIN diode, a Schottky diode, or a diode-connected transistor), or a logic circuit that is a combination thereof may be used. In the case of using a transistor as a switch, a polarity (conductivity) type of the transistor is not particularly limited because it operates as a mere switch. However, when off current is preferred to be small, a transistor of a polarity with smaller off current is desirably used. As a transistor with small off current, a transistor having an LDD region, a transistor having a multigate structure, and the like are given. Further, an N-channel transistor is desirably used when a potential of a source terminal of the transistor functioning as a switch is close to a low potential side power source (Vss, GND, 0V, or the like). On the other hand, a P-channel transistor is desirably used when the potential of the source terminal is close to a high potential side power source (Vdd or the like). This is because it is

35

45

40

45

50

easy for a transistor to function as a switch when an absolute value of a gate-source voltage is increased. Note that a CMOS switch can also be applied by using both N-channel and P-channel transistors. With a CMOS switch, an operation can be appropriately performed even when the situation changes such that a voltage outputted through the switch (that is, an input voltage) is higher or lower than an output voltage. Although as a switch in the present invention, a TFT controlling a pixel electrode, a switch element used in a driver circuit portion, and the like are given; a switch can be employed in another part, if current flow is required to be controlled. [0024] In the present invention, "being connected" includes "being electrically connected" and "being directly connected". Here, "being electrically connected" refers to a state in which an element capable of electric connection (such as a switch, a transistor, a capacitor, an inductor a resistor, or a diode) may be interposed in the predetermined connection. In addition, "being directly connected" refers to only a specific case of "being electrically connected", where no element capable of electric connection is interposed and direct connection is achieved. That is, "being directly connected" specifically refers to "being electrically connected" without another element interposed in the predetermined connection. Note that the description "being directly connected" means the same as "being connected in a direct manner" is also used.

[0025] Note that a display element, a display device, and a light emitting device can employ various modes or can include various elements. For example, a display medium whose contrast varies by an electromagnetic action can be used, such as an EL element (an organic EL element, an inorganic EL element, or an EL element including organic and inorganic substances), an electron emitting element, a liquid crystal element, electron ink, a grating light valve (GLV), a plasma display panel (PDP), a digital micromirror device (DMD), a piezoceramic display, or a carbon nanotube. Note that a display device using an EL element includes an EL display; a display device using an electron emitting element includes a field emission display (FED), an SED flat panel display (SED: Surface-conduction Electron-emitter Display), and the like; a display device using a liquid crystal element includes a liquid crystal display, a transmissive liquid crystal display, a transflective liquid crystal display, and a reflective liquid crystal display; and a display device using electronic ink includes electronic paper. As an application of the present invention other than a liquid crystal element, for example, an electrode containing silicon is used for an electrode in an EL element and the like. Therefore, an element such as an EL element can be manufactured at low cost. In this case, an electrode may have an opening pattern, but not necessarily. When an electrode containing silicon of the present invention is used in an organic EL element, a structure in which a layer containing an organic compound is interposed between electrodes is favorably employed, but not necessarily. On the other

hand, when the electrode containing silicon of the present invention is used in an inorganic EL element, a structure in which a layer containing an inorganic compound is interposed between electrodes may be employed, or a structure in which a layer containing an inorganic compound is formed over the electrode may be employed; since AC drive is possible in the inorganic EL element. In the latter structure, light emission can be carried out with use of a lateral electric field formed by a first electrode and a second electrode. With such a structure, a component which attenuates light from the electrode or the like is not necessarily provided on a light emitting side, accordingly, luminance of the EL display device is improved and deterioration of the EL display device is suppressed.

[0026] Note that various types of transistors can be applied to the present invention and an applicable type of the transistor is not limited. Accordingly, the present invention can employ a thin film transistor (TFT) using a non-single crystalline semiconductor film typified by amorphous silicon or polycrystalline silicon, a transistor using a semiconductor substrate or an SOI substrate, a MOS transistor, a junction transistor, a bipolar transistor, a transistor using a compound semiconductor such as ZnO or a-InGaZnO, a transistor using an organic semiconductor or a carbon nanotube, and the like. In addition, a type of substrate on which a transistor is provided is not particularly limited. The transistor can be formed on a single crystalline substrate, an SOI substrate, a glass substrate, a plastic substrate, a paper substrate, a cellophane substrate, a stone substrate, or the like. In addition, after forming a transistor over a substrate, the transistors may be transposed to another substrate to be located thereon.

[0027] Note that as described above, in the present invention, various types of transistor can be used and can be formed over any substrate. Therefore, all circuits may be formed over a glass substrate, a plastic substrate, a single crystalline substrate, an SOI circuit, or any other circuit. When all circuits are formed on one substrate, the cost can be reduced by reducing the number of components and the reliability can be improved by reducing the number of connection to components in the circuits. Alternatively, it is possible that some circuits are formed on a substrate and some other circuits are formed on another substrate. That is, all of the circuits are not necessarily formed over one substrate. For example, some circuits are formed over a glass substrate with a use of a transistor while some other circuits are formed over a single crystalline substrate, and the IC chip may be connected to the glass substrate by COG (Chip On Glass) to be located thereover. Alternatively, the IC chip may be connected to the glass substrate by TAB (Tape Auto Bonding) or by using a printed board. In this manner, when some circuits are formed over one substrate, the cost can be reduced by reducing the number of components and the reliability can be improved by reducing the number of connection to components in the circuits. Fur-

20

25

40

45

50

ther, when portions with high drive voltage or high drive frequency, which consume more power, are not formed on one substrate, increase in power consumption can be prevented.

[0028] It is to be noted that a transistor can have various structures and modes, and is not limited to a specific structure. For example, a multigate structure which has two or more gates may be employed as well. With a multigate structure, off current can be reduced and reliability can be improved by improving the pressure resistance of a transistor, and flat characteristics can be obtained such that a drain-source current hardly changes even when a drain-source voltage changes in operation in a saturation region. Alternatively, a structure in which gate electrodes may be provided over and under a channel may be employed. With such a structure in which gate electrodes are provided over and under a channel, a current value can be easily increased since a channel forming region increases, an S value (sub-threshold coefficient) can be reduced since a depletion layer is easily formed. Further alternatively, a structure in which a gate electrode is provided over a channel or under the channel may be employed. Also, a forward staggered structure or an inversed staggered structure may be employed. A channel forming region may be divided into a plurality of regions, connected in parallel, or connected in series. Further, a source electrode or a drain electrode may overlap with a channel (or a part thereof). Accordingly, with such a structure in which a source electrode or a drain electrode overlaps with a channel (or a part of thereof), charges are accumulated in a part of the channel and an unstable operation can be prevented. Further, an LDD region may be provided. By providing an LDD region, off current can be reduced and reliability can be improved by improving the withstand voltage of a transistor, and flat characteristics can be obtained such that a drainsource current hardly changes even when a drain-source voltage changes in operation in a saturation region.

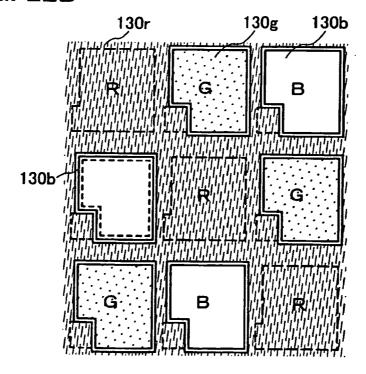

[0029] Note that in the present invention, one pixel corresponds to one element which can control brightness. Therefore, for example, one pixel shows one color element by which brightness is expressed. Accordingly, in the case of a color display device formed of color elements of R (red), G (green), and B (blue), the smallest unit of an image includes three pixels of an R pixel, a G pixel, and a B pixel. Note that color elements are not limited to three colors and may be more colors, and RG-BW (W is white) or RGB to which another color such as yellow, cyan, or magenta is introduced may be used, for example. Further, when one color element is controlled by using a plurality of regions, one of the regions corresponds to one pixel. For example, in the case of performing an area gray scale display, a plurality of regions are provided for one color element to control the brightness, which express gray scale as a whole. One of the regions to control the brightness corresponds to one pixel. Therefore, in that case, one color element includes a plurality of pixels. In that case, a region which contributes to display an image may differ in size depending on the pixels. Further, in a plurality of regions controlling the brightness which are provided for one color element, that is, in a plurality of pixels included in one color element, signals provided to each pixel may slightly differ from one another so that the viewing angle is expanded. Note that the description "one pixel (for three colors)" corresponds to three pixels of R, G, and B which are considered as one pixel; while "one pixel (for one color)" corresponds to a plurality of pixels provided for one color element which are collectively considered as one pixel.

[0030] Note that in the present invention, there is a case where pixels are arranged in matrix. The case where pixels are arranged in matrix includes not only to a case where the pixels are arranged in a stripe pattern, which is a so-called grid configuration where longitudinal stripes and lateral stripes cross each other, but also to a case where three color elements are arranged in a so-called delta pattern when a full color display is performed using three color elements (for example, RGB). Further, a Bayer arrangement is also included. Note that the color element is not limited to three colors and may have more colors, for example, RGBW (W is white) or RGB to which yellow, cyan, or magenta is added. The size of a light emission area may be different depending on color elements.

**[0031]** A transistor is an element including at least three terminals of a gate, a drain, and a source. A channel forming region is provided between a drain region and a source region. Here, it is difficult to determine which of two terminals is a source or a drain since it depends on a structure, operating condition, and the like of the transistor. Therefore, in the present invention, regions which function as a source and a drain are referred to as a first terminal and a second terminal, respectively.

**[0032]** Note that a gate includes a gate electrode and a gate wiring (also referred to as a gate line, a gate signal line, or the like) or a part thereof. A gate electrode corresponds to a conductive film a part of which overlaps with a semiconductor forming a channel forming region, an LDD (Lightly Doped Drain) region, or the like, with a gate insulating film interposed therebetween. A gate wiring corresponds to a wiring for connecting gate electrodes of each pixel and a wiring for connecting a gate electrode and another wiring.

[0033] However, there is a part which functions as a gate electrode and also as a gate wiring. Such a region may be referred to as a gate electrode or a gate wiring. That is, there is a region which cannot be distinguished as a gate electrode or a gate wiring. For example, in a case where a channel forming region overlaps with a gate wiring which is extended, the overlapped region functions both as a gate wiring and as a gate electrode. Therefore, such a region may be referred to as a gate electrode or a gate wiring.

**[0034]** Further, a region which is formed of the same material as a gate electrode and connected to the gate electrode may be referred to as a gate electrode as well.

40

45

Similarly, a region which is formed of the same material as a gate wiring and connected to the gate wiring may be referred to as a gate wiring. In a strict sense, such a region does not overlap with a channel forming region or does not have a function to connect to another gate electrode in some cases. However, there is a region which is formed of the same material as a gate electrode or a gate wiring and connected to the gate electrode or the gate wiring due to manufacturing cost, reduction of steps, layout, and the like. Therefore, such a region may also be referred to as a gate electrode or a gate wiring.

[0035] For example, in a multigate transistor, gate electrodes of one transistor and another transistor are often connected through a conductive film formed of the same material as the gate electrode. Such a region for connecting the gate electrodes may be referred to as a gate wiring, or may be referred to as a gate electrode when a multigate transistor is considered as one transistor. That is, a component which is formed of the same material as a gate electrode or a gate wiring and connected to the gate electrode or the gate wiring may be referred to as a gate electrode or a gate wiring. Moreover, for example, a portion of a conductive film which connects a gate electrode and a gate wiring may also be referred to as a gate electrode or a gate wiring.

**[0036]** Note that a gate terminal corresponds to a part of a region of a gate electrode or a region electrically connected to the gate electrode.

[0037] Note that a source includes a source region, a source electrode, and a source wiring (also referred to as a source line, a source signal line, or the like) or a part thereof. A source region corresponds to a semiconductor region which contains a large amount of p-type impurities (boron, gallium, or the like) or n-type impurities (phosphorus, arsenic, or the like). Therefore, a region containing a small amount of p-type impurities or n-type impurities, that is, an LDD (Lightly Doped Drain) region is not included in a source region. A source electrode corresponds to a conductive layer a part of which is formed of a different material from a source region and electrically connected to the source region. Note that a source electrode including a source region is sometimes referred to as a source electrode. A source wiring corresponds to a wiring for connecting source electrodes of each pixel and a wiring for connecting a source electrode and another wiring.

[0038] However, there is a part which functions as a source electrode and also as a source wiring. Such a region may be referred to as a source electrode or a source wiring. That is, there is a region which cannot be distinguished as a source electrode or a source wiring. For example, when there is a source region overlapping with a source wiring which is extended, the region functions as a source wiring and also as a source electrode. Therefore, such a region may be referred to as a source electrode or a source wiring.

[0039] Further, a region which is formed of the same material as a source electrode and connected to the

source electrode; or a part which connects one source electrode and another source electrode may also be referred to as a source electrode. Further, a part overlapping with a source region may be referred to as a source electrode. Similarly, a region which is formed of the same material as a source wiring and connected to the source wiring may be referred to as a source wiring. In a strict sense, there is a case where such a region does not have a function to connect one source electrode to another source electrode. However, there is a region which is formed of the same material as a source electrode or a source wiring and connected to the source electrode or the source wiring due to manufacturing cost, reduction of steps, layout, and the like. Therefore, such a region may also be referred to as a source electrode or a source wiring.

**[0040]** For example, a conductive film a part of which connects a source electrode and a source wiring may be referred to as a source electrode or a source wiring.

**[0041]** Note that a source terminal corresponds to a part of a source region, a source electrode, or a region electrically connected to a source electrode.

[0042] Note that a drain is similar to a source.

[0043] Note that in the present invention, a semiconductor device corresponds to a device including a circuit having a semiconductor element (a transistor, a diode, or the like). Further, a semiconductor device may correspond to a general device which functions by utilizing semiconductor characteristics. A display device corresponds to a device including a display element (a liquid crystal element, a light emitting element, or the like). Note that a display device may correspond to a display panel itself in which a plurality of pixels including display elements such as a liquid crystal element or an EL element and a peripheral driver circuit for driving the pixels are formed over a substrate. Moreover, a display device may include a device provided with a flexible printed circuit (FPC) or a printed wiring board (PWB). Further, a light emitting device corresponds to a display device including a self-luminous light emitting element such as an EL element or an element used for an FED, in particular. A liquid crystal display device corresponds to a display device including a liquid crystal element.

[0044] In the present invention, an expression that an object is formed on or formed over a different object does not necessarily mean that the object is in direct contact with the different object. The expression may include a case where two objects are not in direct contact with each other, that is, a case where another object is interposed therebetween. Accordingly, for example, when it is described that a layer B is formed on (or over) a layer A, it means either case where the layer B is formed on and in direct contact with the layer A, or where another layer (for example, a layer C or a layer D) is formed on and in direct contact with the layer A and the layer B is formed on and in direct contact with the layer C or D. Similarly, when it is described that an object is formed above a different object, it does not necessarily mean that the

20

25

object is in direct contact with the different object, and another object may be interposed therebetween. Accordingly, for example, when it is described that a layer B is formed above a layer A, it means either case where the layer B is formed in direct contact with the layer A, or where another layer (for example, a layer C or a layer D) is formed in direct contact with the layer A and the layer B is formed in direct contact with the layer C or D. Similarly, when it is described that an object is formed below or formed under a different object, it means either case where the objects are in direct contact with each other or not in contact with each other. In addition, if not specifically limited, one surface of a substrate is referred to as an upper direction, and the other surface of the substrate is referred to as a lower direction. That is, in a case where a layer B is formed over a layer A in manufacturing steps, its structure can be considered as a structure where the layer B is formed over the layer A, even when a completed product is turned upside down. That is, an expression over or under only refers to a side of an object to which another object is formed, and does not have a general meaning of over or under, which is "a direction with respect to gravity". Needless to say, similar description can be applied to other directions such as left or light. Note that it is not limited thereto when it is particularly specified, and the direction of gravity or the like may be employed as a standard.

**[0045]** With the present invention, a semiconductor film in a transistor and a first electrode for driving a liquid crystal can be formed in the same step. As a result, the first electrode can be manufactured without increasing the numbers of masks (reticles) and manufacturing steps.

**[0046]** Accordingly, a liquid crystal display device with wide viewing angle and low manufacturing cost compared with a conventional device can be provided.

#### BRIEF DESCRIPTION OF DRAWINGS

[0047] 40

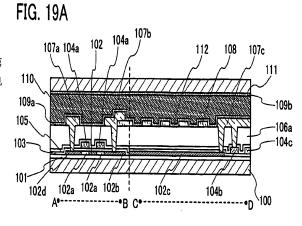

FIG. 1A is a plan view for illustrating a structure of a liquid crystal display device according to the present invention, and FIG. 1B is a cross-sectional view along a line A-B of FIG. 1A;

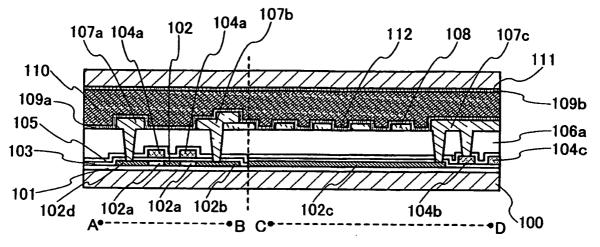

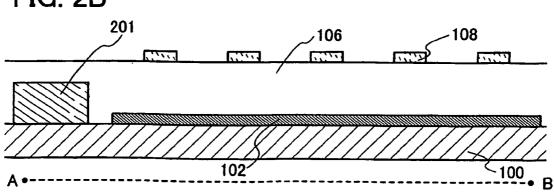

FIG 2A is a plan view for illustrating a structure of a liquid crystal display device according to the present invention, and FIG. 2B is a cross-sectional view along a line A-B of FIG 2A;

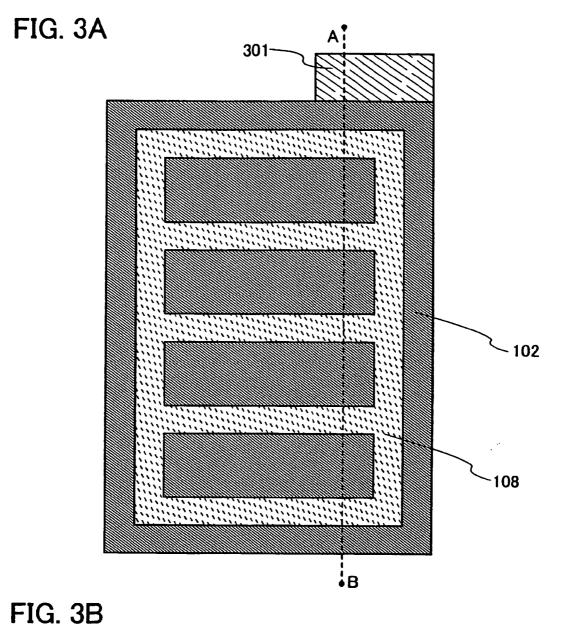

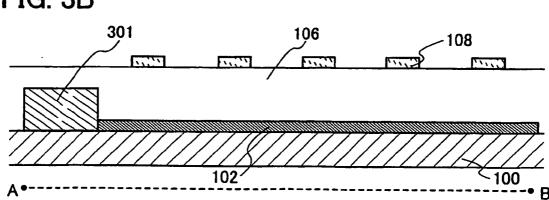

FIG 3A is a plan view for illustrating a structure of a liquid crystal display device according to the present invention, and FIG. 3B is a cross-sectional view along a line A-B of FIG. 3A;

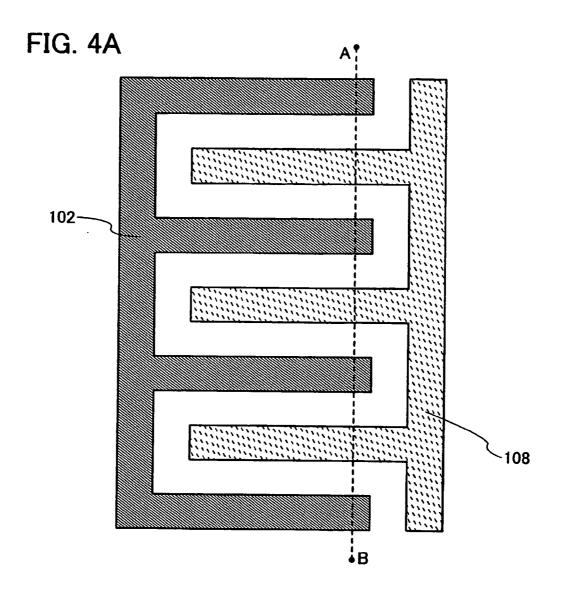

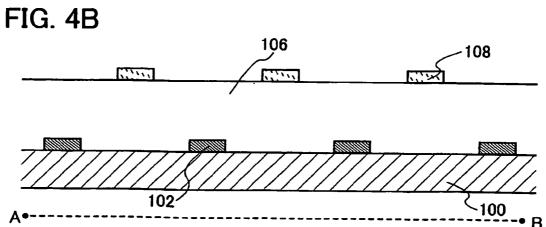

FIG 4A is a plan view for illustrating a structure of a liquid crystal display device according to the present invention, and FIG. 4B is a cross-sectional view along a line A-B of FIG 4A;

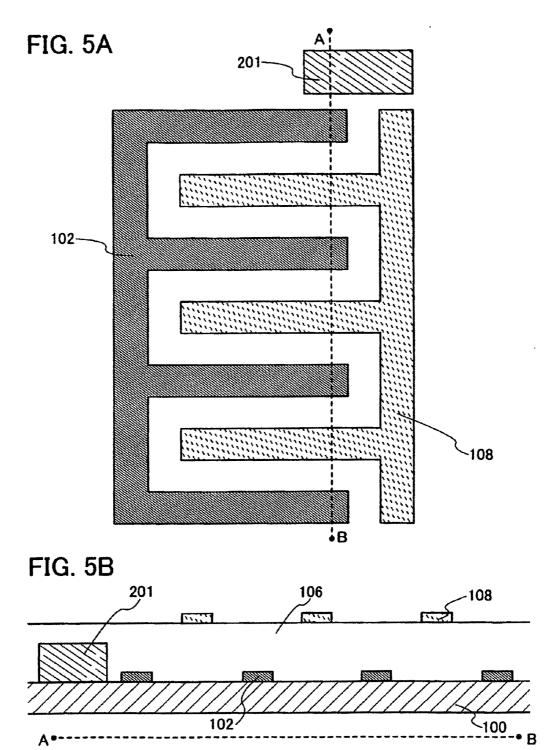

FIG 5A is a plan view for illustrating a structure of a

liquid crystal display device according to the present invention, and FIG. 5B is a cross-sectional view along a line A-B of FIG 5A;

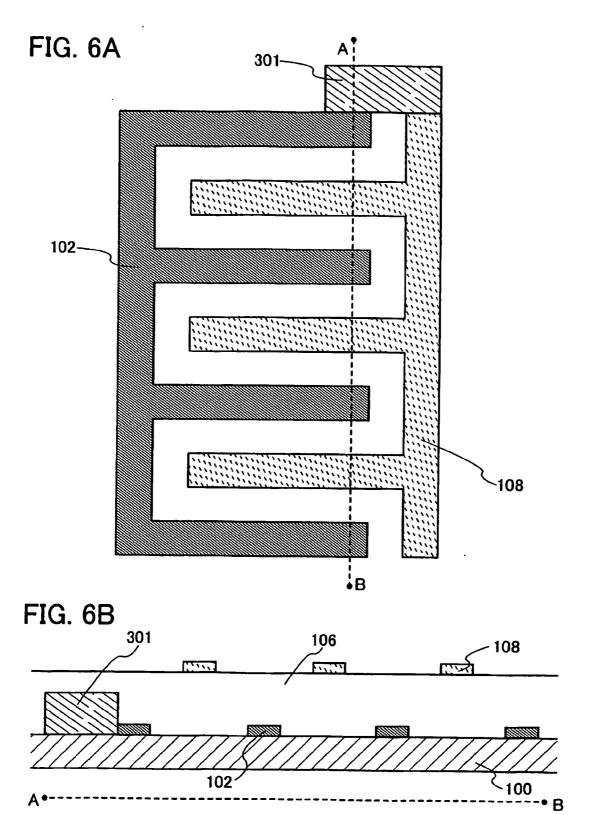

FIG 6A is a plan view for illustrating a structure of a liquid crystal display device according to the present invention, and FIG 6B is a cross-sectional view along a line A-B of FIG. 6A;

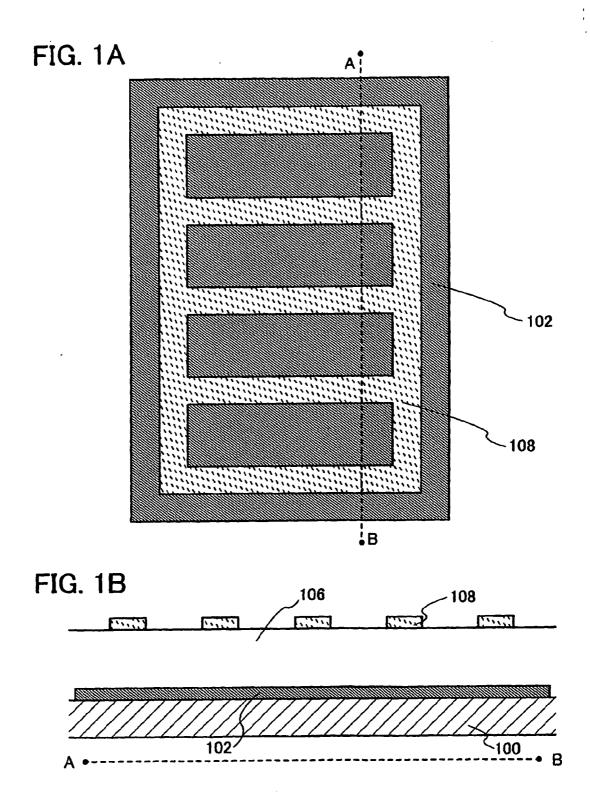

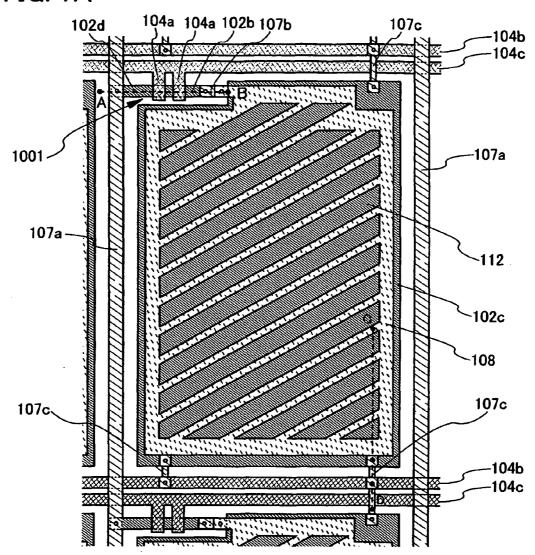

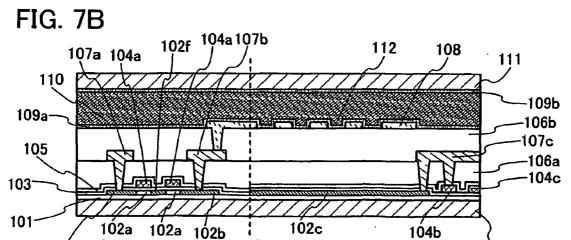

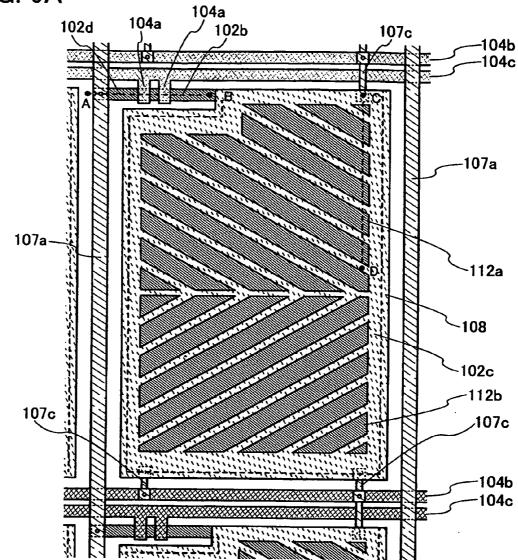

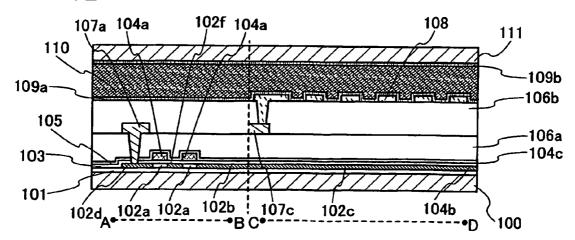

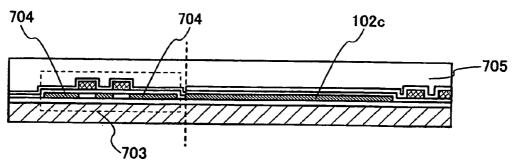

FIG. 7A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 1, and FIG. 7B is a cross-sectional view along lines A-B and C-D of FIG 7A;

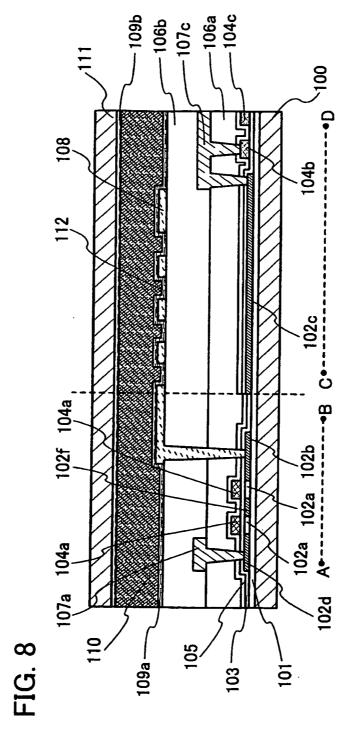

FIG 8 illustrates another structure of FIG 7B;

FIGS. 9A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 2, and FIG 9B is a cross-sectional view along lines A-B and C-D of FIG. 9A;

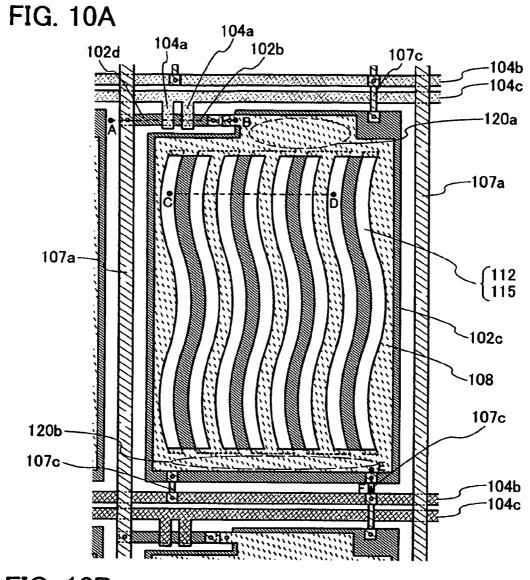

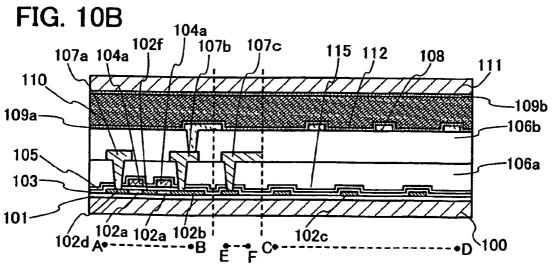

FIG 10A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 3, and FIG 10B is a cross-sectional view along lines A-B, C-D, and E-F of FIG 10A;

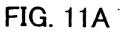

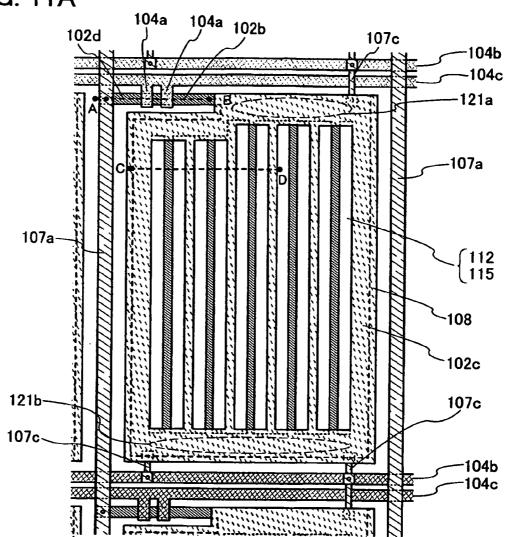

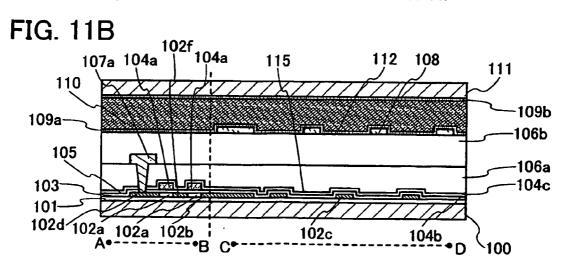

FIG 11A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 4, and FIG 11B is a cross-sectional view along lines A-B and C-D of FIG 11A;

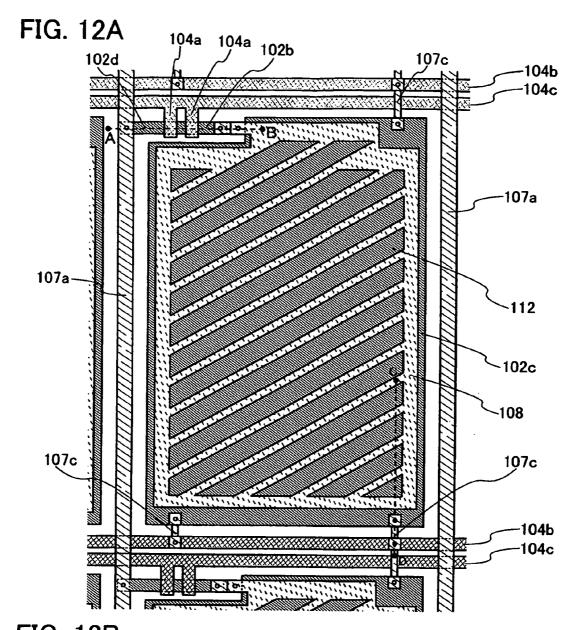

FIG. 12A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 5, and FIG 12B is a cross-sectional view along lines A-B and C-D of FIG 12A;

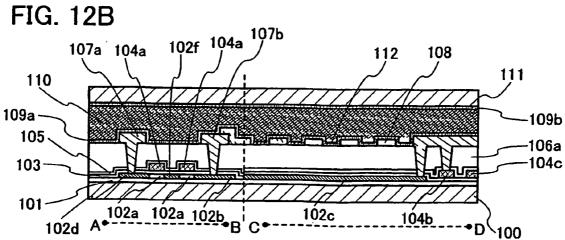

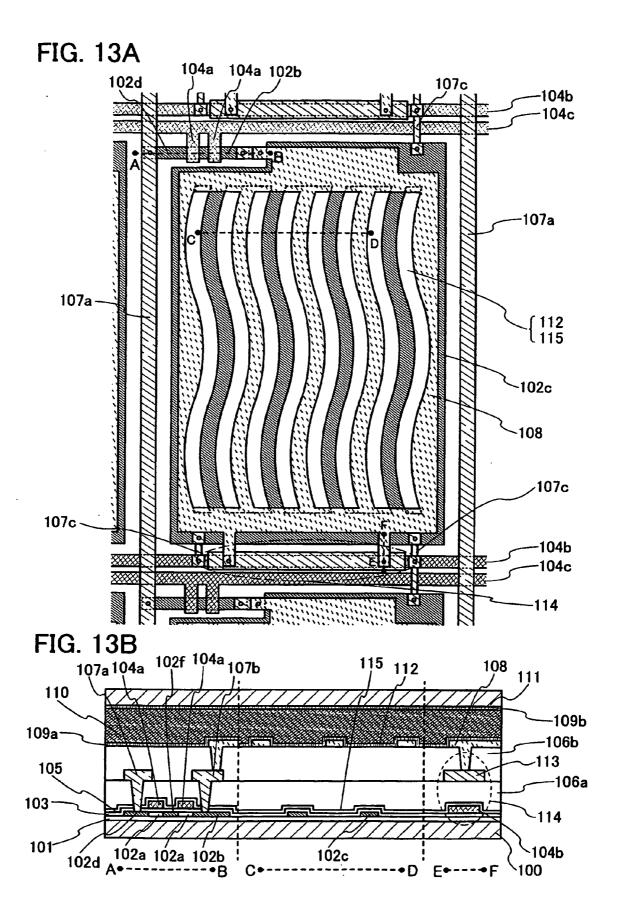

FIG 13A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 6, and FIG 13B is a cross-sectional view along lines A-B,C-D, and E-F of FIG 13A;

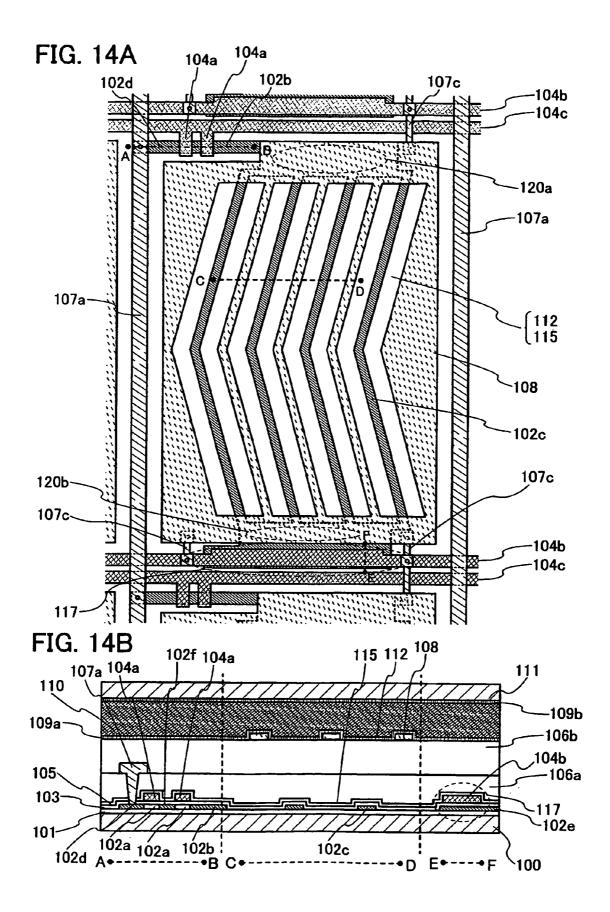

FIG 14A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 7, and FIG 14B is a cross-sectional view along lines A-B,C-D, and E-F of FIG 14A;

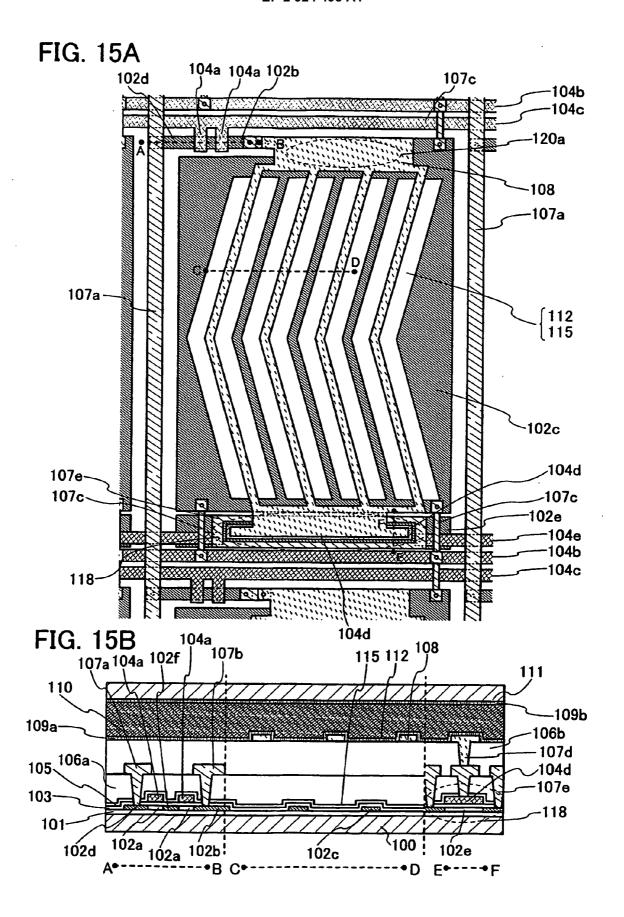

FIG 15A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 8, and FIG 15B is a cross-sectional view along lines A-B,C-D, and E-F of FIG 15A;

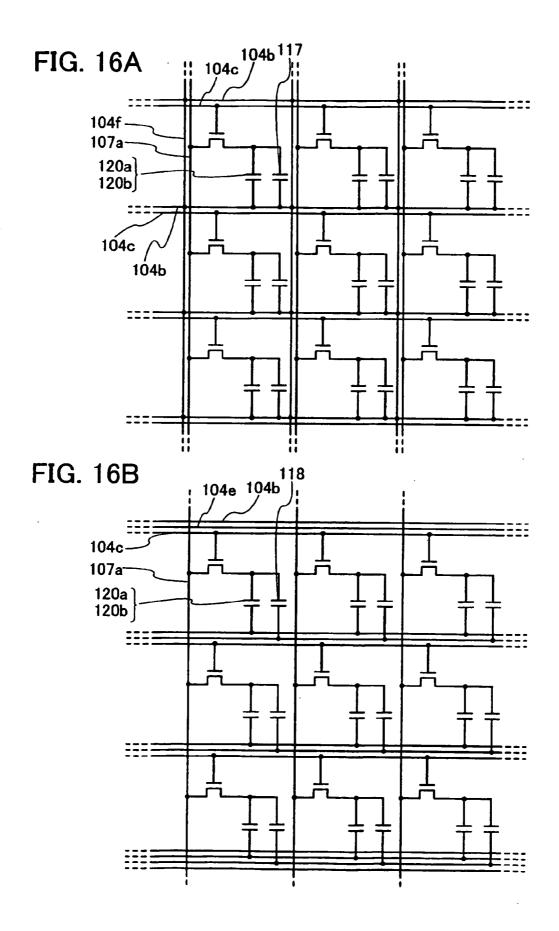

FIG 16A is a circuit diagram of a liquid crystal display device according to Embodiment Mode 9 and FIG 16B is a circuit diagram of a liquid crystal display device according to Embodiment Mode 10;

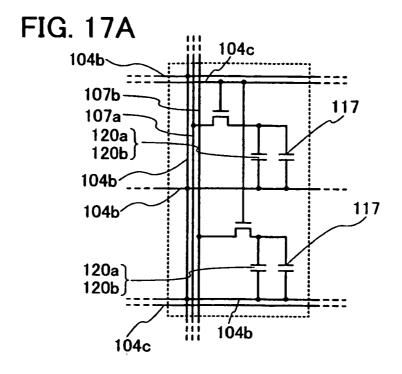

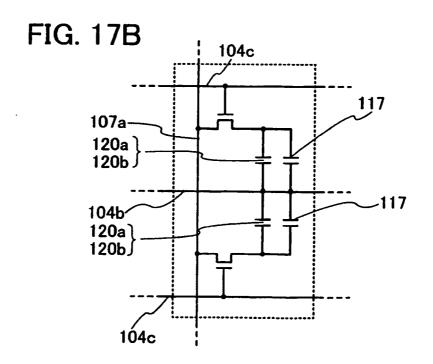

FIG 17A is a circuit diagram of a liquid crystal display device according to Embodiment Mode 11 and FIG 17B is a circuit diagram of a liquid crystal display device according to Embodiment Mode 12;

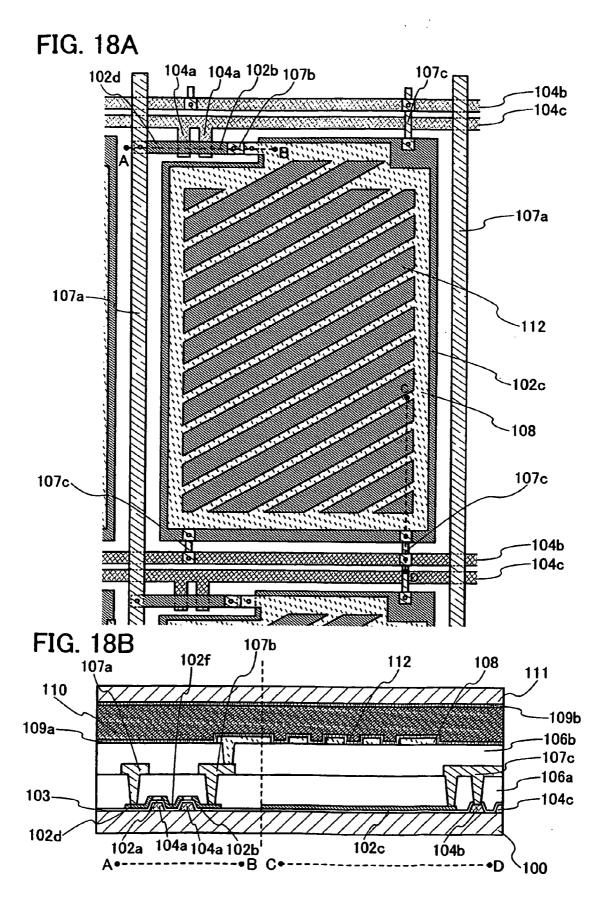

FIG 18A is a plan view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 13, and FIG 18B is a cross-sectional view along lines A-B and C-D of FIG 18A;

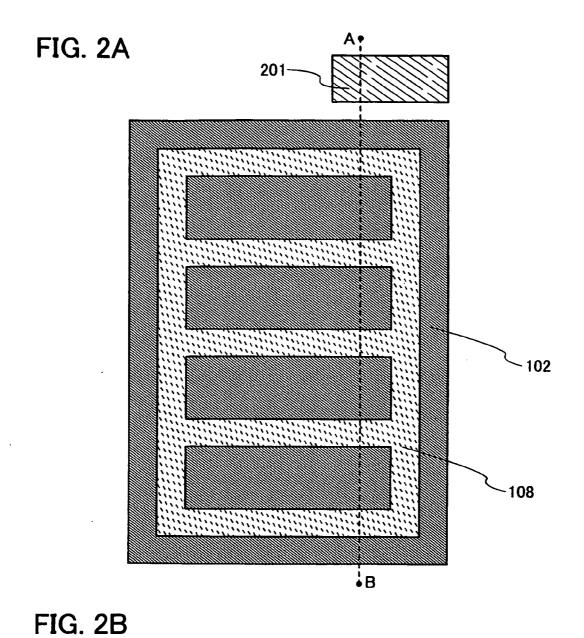

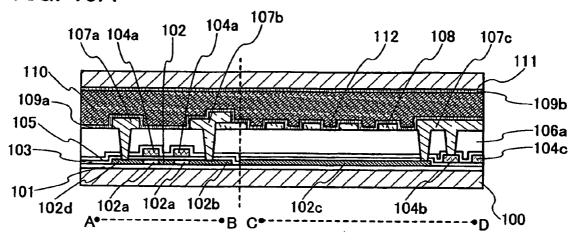

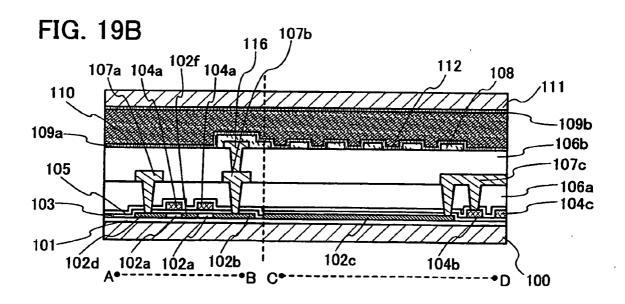

FIG 19A is a cross-sectional view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 14, and FIG 19B is a cross-sectional view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 15;

45

50

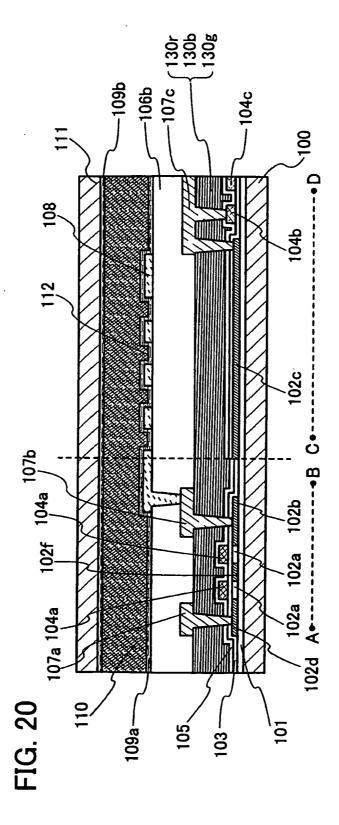

FIG 20 is a cross-sectional view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 16;

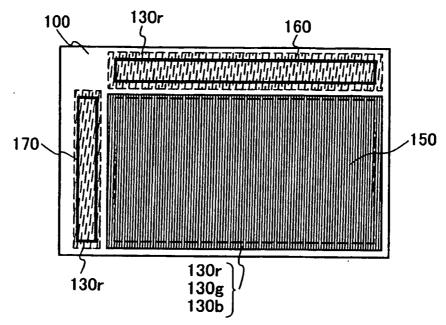

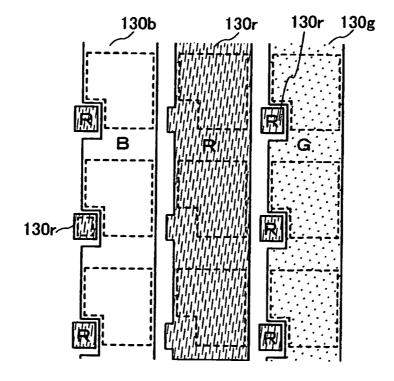

FIG 21A is a plan view of a liquid crystal display device shown in FIG 20 and FIG 21B is an enlarged view of a pixel portion of FIG 21A;

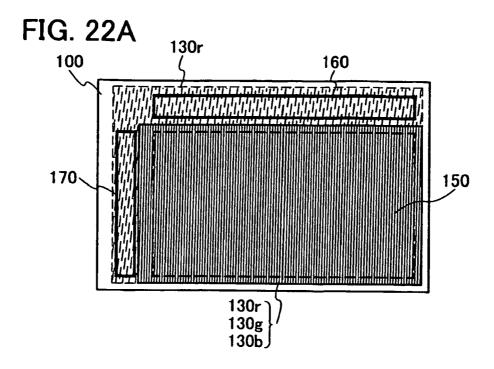

FIG 22A is a plan view of a liquid crystal display device according to Embodiment Mode 17 and FIG 22B is an enlarged view of a pixel portion of FIG 22A;

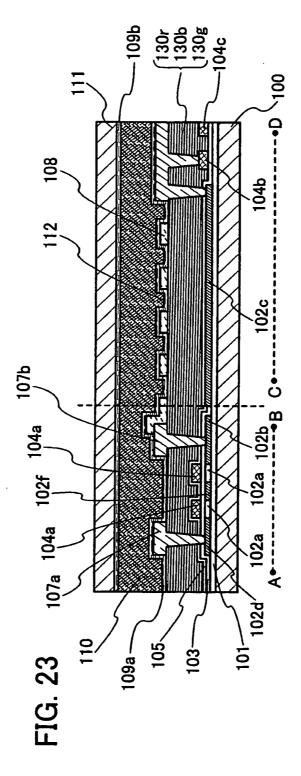

FIG 23 is a cross-sectional view for illustrating a structure of a liquid crystal display device according to Embodiment Mode 18;

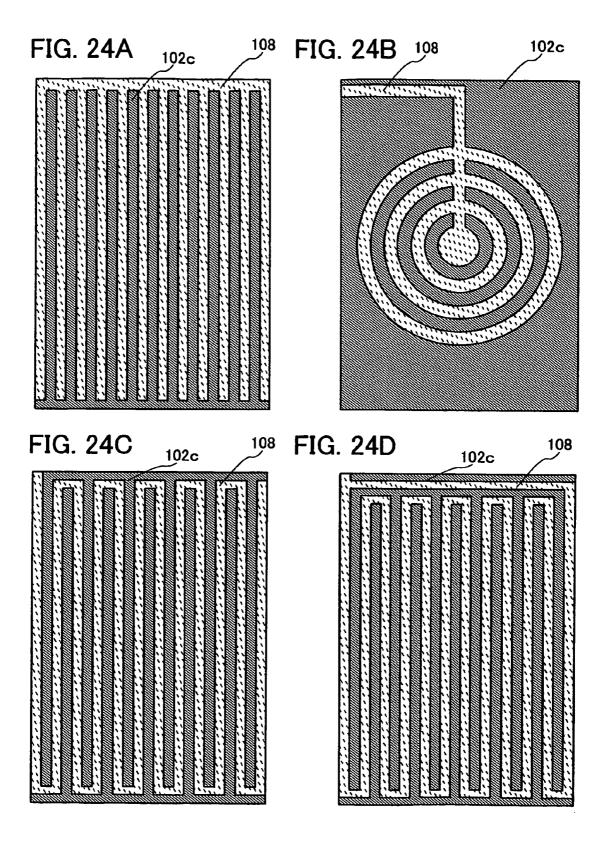

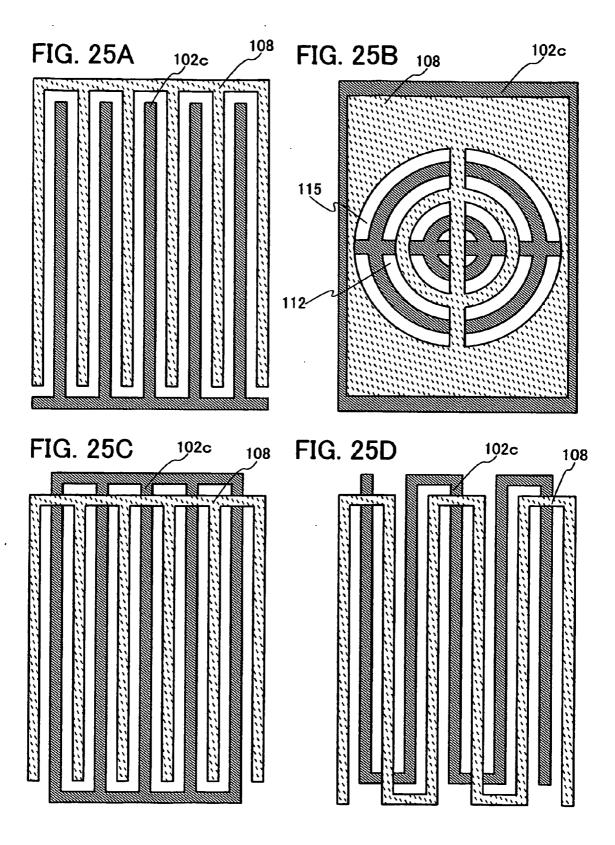

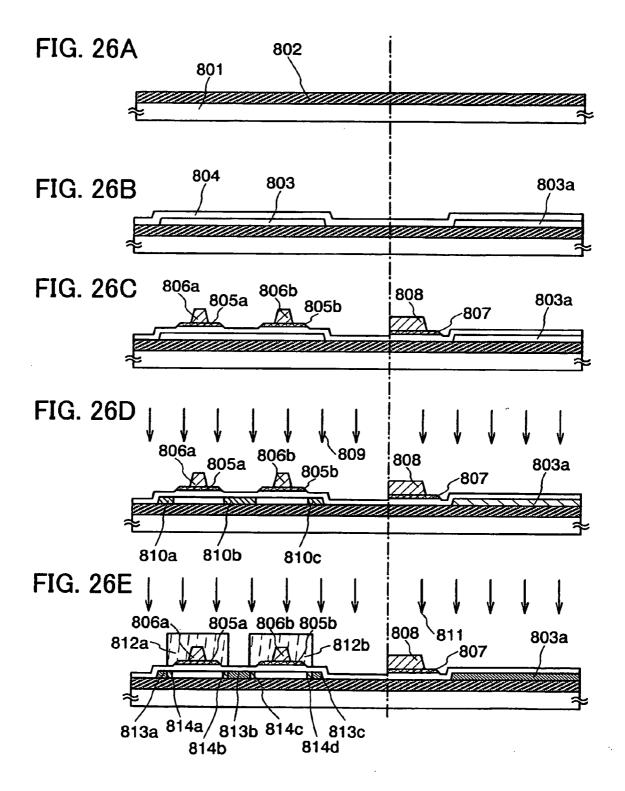

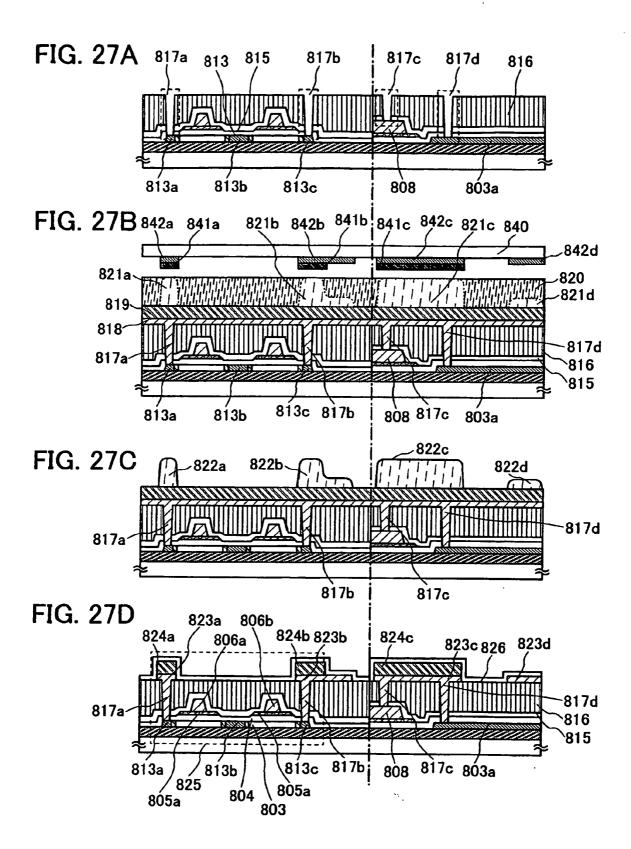

FIGS. 24A to 24D are plan views for illustrating shapes of an electrode of an FFS mode liquid crystal display device according to Embodiment Mode 19; FIGS. 25A to 25D are plan views for illustrating shapes of an electrode of an IPS mode liquid crystal display device according to Embodiment Mode 20; FIGS. 26A to 26E are cross-sectional views illustrating a manufacturing method of a liquid crystal display module of Embodiment 1;

FIGS. 27A to 27D are cross-sectional views illustrating a manufacturing method of a liquid crystal display module of Embodiment 1;

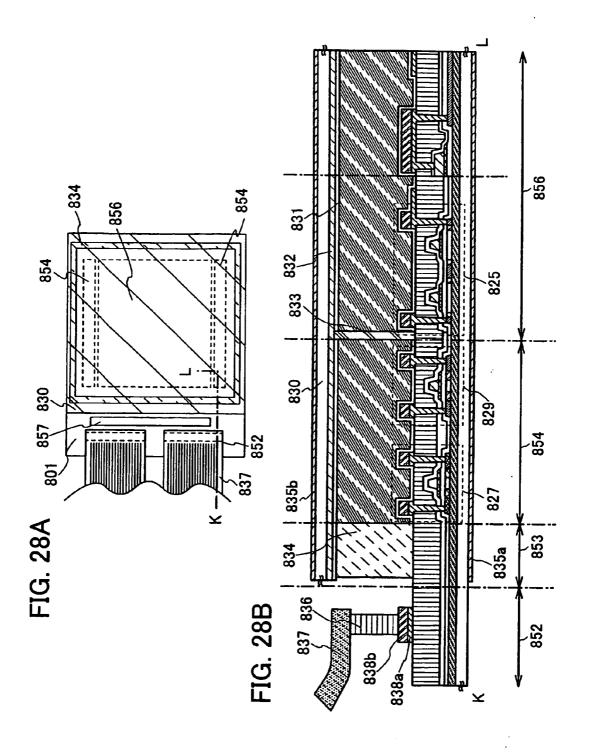

FIG. 28A is a plan view of a liquid crystal display module of Embodiment 1 and FIG 28B is a cross-sectional view along a line K-L of FIG 28A;

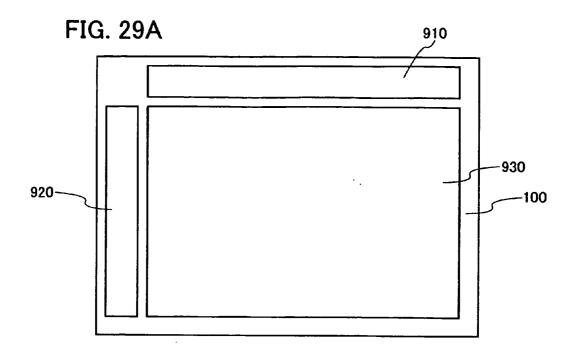

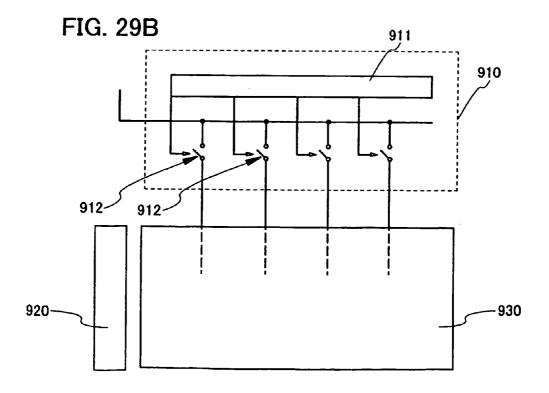

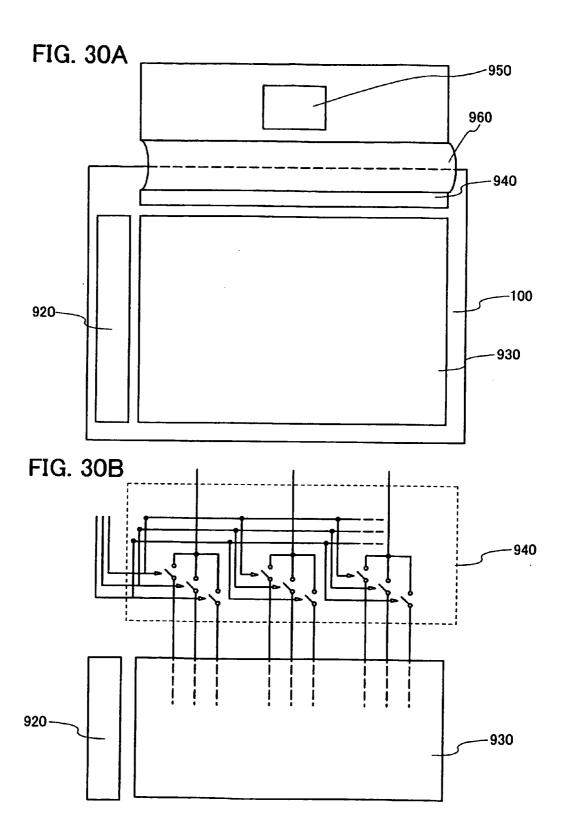

FIGS. 29A and 29B are diagrams for illustrating a liquid crystal display module according to Embodiment 2;

FIGS. 30A and 30B are diagrams for illustrating a liquid crystal display module according to Embodiment 2;

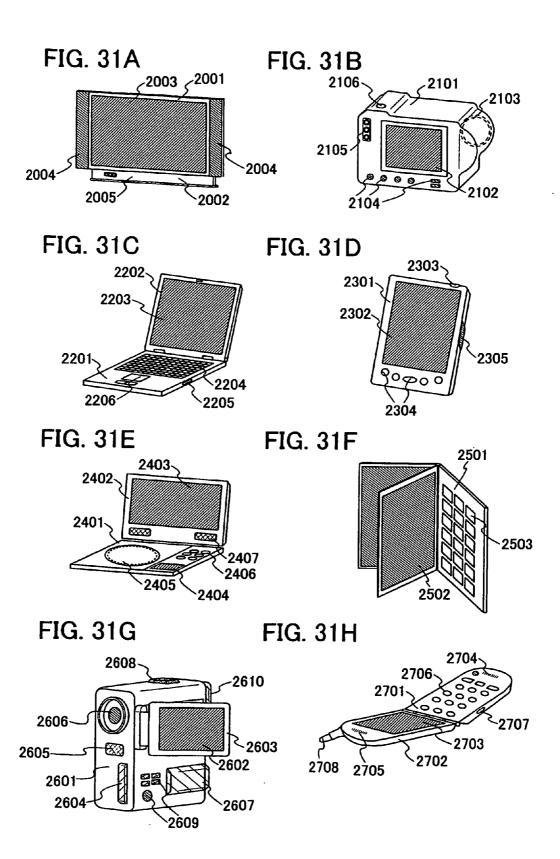

FIGS. 31A to 31H are perspective views illustrating electronic appliances of Embodiment 3;

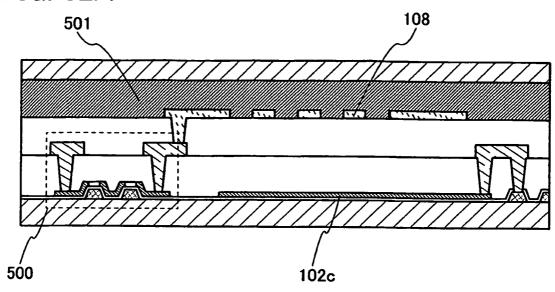

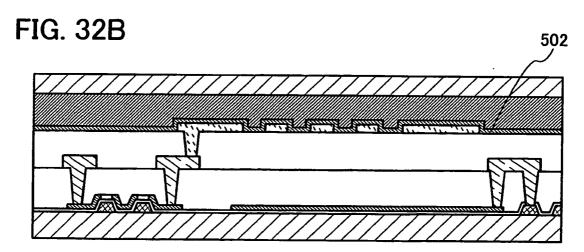

FIGS. 32A and 32B are cross-sectional views for illustrating a structure of an inorganic EL element according to Embodiment Mode 21;

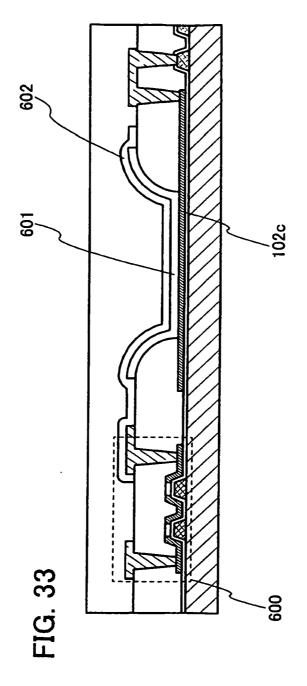

FIG 33 is a cross-sectional view for illustrating a structure of an organic EL element according to Embodiment Mode 22; and

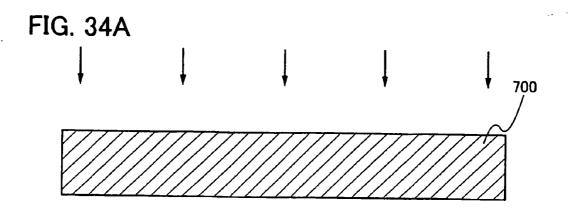

FIGS. 34A to 34D are cross-sectional views for illustrating a structure and manufacturing steps of a reflective liquid crystal display device according to Embodiment Mode 23.

## **DETAILED DESCRIPTION OF THE INVENTION**

**[0048]** Hereinafter, embodiment modes and embodiments in the present invention are described with reference to the accompanying drawings. However, the present invention can be carried out with many different modes and it is easily understood by those skilled in the art that modes and details can be modified in various ways without departing from the purpose and the scope of the present invention. Accordingly, the present invention should not be interpreted as being limited to the description of the embodiment modes and embodiments.

[Embodiment Mode 1]

**[0049]** FIGS. 1A and 1B illustrate a basic example of the present invention. FIG. 1A is a plan view and FIG 1B is a cross-sectional view.

**[0050]** A first electrode 102 is formed over a substrate 100. The first electrode 102 is formed with use of ITO (indium tin oxide) conventionally.

[0051] In the present invention, the first electrode 102 is formed of, for example, a semiconductor material containing silicon, although not limited thereto. Alternatively, amorphous silicon may be used but in order to enhance conductivity, polysilicon (polycrystalline silicon), single crystalline silicon, and the like may be used. Further, in many cases, the first electrode contains an impurity (a p-type impurity or an n-type impurity) such as phosphorus, boron, gallium, or arsenic to further enhance the conductivity.

**[0052]** The reason of using a semiconductor material containing silicon for the first electrode 102 is that silicon has high transmittance. In addition, since the first electrode 102 is thin, it can transmit light. The transmittance is preferably 50% or more, more preferably, 80% or more, so that higher visibility can be achieved.

**[0053]** Note that an insulating layer or a conductive layer may be provided between the substrate 100 and the first electrode 102. For example, an insulating layer for blocking an impurity intruding from the substrate 100, a gate electrode, a gate wiring, a gate insulating film, and the like may be provided.

**[0054]** An insulating film 106 is formed over the first electrode 102. Note that the insulating film 106 may have a single-layer structure or a stacked-layer structure.

**[0055]** An inorganic material or an organic material can be used for the insulating film 106. As an organic material, polyimide, acrylic, polyamide, polyimide amide, resist, siloxane, polysilazane, or the like can be used. As an inorganic material, an insulating substance containing oxygen or nitrogen, such as silicon oxide ( $SiO_x$ ), silicon nitride ( $SiN_x$ ), silicon oxynitride ( $SiO_xN_y$ : x > y), or silicon nitride oxide ( $SiN_xO_y$ : x > y) can be used. Alternatively, a stacked-layer film in which a plurality of these films are stacked may be used. Further alternatively, a stacked-layer film in which an organic material and an inorganic material are combined may be used.

**[0056]** Note that when an inorganic material is used for the insulating film, intrusion of moisture or an impurity can be prevented. In particular, a layer containing nitrogen can block moisture or an impurity efficiently.

**[0057]** Note that when an organic material is used for the insulating film, a surface thereof can be planarized. Accordingly, the insulating film can have a good effect on a layer provided thereover. For example, the layer formed over the organic material can be planarized, so that disturbance of orientation of the liquid crystal can be prevented, cutting of a wiring can be prevented, and a resist can be formed with accuracy.

[0058] A second electrode 108 is formed overt the in-

sulating film 106. The second electrode 108 may be formed of a material with a high light-transmitting property. For example, one or more elements selected from indium (In), tin (Sn), and oxygen (O); or a compound or an alloy material containing one or more of the aforementioned elements as a component (such as indium tin oxide (ITO), indium zinc oxide (IZO), or indium tin oxide doped with silicon oxide (ITSO)) are desirable. In particular, IZO is preferable since it is easy to be patterned and formed into a minute shape with accuracy, although it is not limited thereto.

**[0059]** Note that the second electrode 108 has an opening pattern (slit). The opening pattern is for generating an electric field in a direction generally parallel to the substrate, between the first electrode 102 and the second electrode 108. Accordingly, as long as an electric field having a part which is generally parallel to the substrate can be generated, the opening pattern can have various shapes. Here, "generally parallel" refers to a parallel direction with small deviation. Therefore, the direction may be deviated from the parallel direction as long as the display is not disturbed. The direction may have a deviation of, for example, approximately  $\pm$  10°, or desirably, approximately  $\pm$  5°.

**[0060]** The opening pattern includes not only a closed opening pattern such as a slit, but also a space which is located between conductive patterns and in which the conductive pattern is not formed, such as a space between comb-teeth of a comb-shaped electrode. In other words, a gap or an interspace is needed between portions functioning as an electrode.

**[0061]** As described above, the electric field is generated between the second electrode 108 and the first electrode 102, so that an alignment state of liquid crystal molecules can be controlled.

**[0062]** Note that in a case where electrodes are provided in each pixel, an electrode to which a signal different among pixels depending on an image signal is provided, that is, a pixel electrode can be either the second electrode 108 or the first electrode 102. Accordingly, it is possible to set the second electrode 108 to be the pixel electrode. Alternatively, it is possible to set the second electrode 108 to be the common electrode 108 to be the common electrode and the first electrode 102 to be the pixel electrode.

**[0063]** Since the pixel electrode is connected to a source or drain of a transistor in many cases, when the first electrode 102 or the second electrode 108 functions as the pixel electrode, the structure can be simplified. Further, since the common electrodes in all pixels are connected to one another in many cases, when the first electrode 102 or the second electrode 108 functions as the common electrode, the structure can be simplified.

**[0064]** FIG 2A is a plan view and FIG 2B is a cross-sectional view of a case where a transistor 201 is provided. The transistor 201 is located near the first electrode 102 and the second electrode 108.

[0065] In this case, a film in the transistor 201 and the

first electrode 102 can be formed at the same time. As a result, the first electrode can be manufactured without increasing the numbers of masks (reticles) and manufacturing steps.

[0066] For example, a semiconductor layer in the transistor 201 and the first electrode 102 can be formed at the same time. The semiconductor layer in the transistor 201 and the first electrode 102 can be formed at the same time and etched at the same time, whereby patterning can be carried out at the same time. Further, in the case where the semiconductor layer is formed of polysilicon, the semiconductor layer and the first electrode 102 are crystallized at the same time.

[0067] Accordingly, the semiconductor layer in the transistor 201 and the first electrode 102 contain the same material.

[0068] Note that in a case of adding an impurity (a ptype impurity or an n-type impurity) such as phosphorus, boron, gallium, or arsenic to a part of the semiconductor layer in the transistor 201, it is desirable that the impurity is also introduced to the first electrode 102 at the same time. In a case of adding the impurity at the same time to portions, the concentration thereof is influenced by a thickness and a quality of a material of a film over the portions. When being formed under the similar layer structures, the semiconductor layer in the transistor 201 and the first electrode 102 have the impurity (a p-type impurity or an n-type impurity) at approximately the same concentration, at least partially. For example, a layer forming a source region or a drain region in the semiconductor layer in the transistor 201 and a semiconductor layer forming the first electrode 102 have impurity regions at approximately the same concentration.

[0069] Note that the semiconductor layer in the transistor 201 has a channel forming region in many cases. A gate electrode is located over the channel forming region with a gate insulating film therebetween. An impurity (a p-type impurity or an n-type impurity) is not introduced to the channel forming region to form a high-concentration impurity region, normally. However, there is a case where an impurity (a p-type impurity or an n-type impurity) is introduced to the channel forming region to form an extremely low-impurity region in order to adjust a value of a threshold voltage. Further, an impurity (a p-type impurity or an n-type impurity) is introduced to the semiconductor layer in the transistor 201 to form a low-concentration impurity region (LDD: Lightly Doped Drain) in some cases. Accordingly, in many cases, the semiconductor layer in the transistor 201 has a plurality of regions where impurities (p-type impurities or n-type impurities) are contained at various concentrations.

**[0070]** Note that in a case where an impurity (a p-type impurity or an n-type impurity) is introduces to the semiconductor layer in the transistor 201 and the first electrode 102 at the same time, the semiconductor layer in the transistor 201 and the first electrode 102 may be located extremely close to each other. It is because the same impurity (a p-type impurity or an n-type impurity)

40

is introduced thereto in many cases. Thus, the layout of the transistor 201 and the first electrode 102 can be significantly effective, which leads to improvement in aperture ratio.

[0071] Note that the conductivity of a part of the semiconductor layer in the transistor 201 and that of the first electrode 102 may differ from each other. In such a case, an impurity (a p-type impurity or an n-type impurity) is introduced to the first electrode 102 at the same as a transistor other than the transistor 201. Accordingly, in that case, the semiconductor layer in the transistor other than the transistor 201 and the first electrode 102 have the impurity (a p-type impurity or an n-type impurity) at approximately the same concentration, at least partially. For example, the transistor other than the transistor 201 is provided as a part of a source signal line driver circuit or a gate signal line driver circuit.

[0072] The transistor 201 and one of the first electrode 102 and the second electrode 108 are electrically connected in many cases. In addition, the electrode which is electrically connected to the transistor 201 functions as the pixel electrode in many cases. The transistor 201 and one of the first electrode 102 and the second electrode 108 are electrically connected through a contact hole, a wiring, or the like.

**[0073]** Note that in FIGS. 2A and 2B, a case in which the first electrode 102 is formed at the same time as the film in the transistor 201 is described; however, it is not limited thereto. The first electrode 102 may be formed at the same time as another film, such as a film in a wiring, a resistor, or a capacitor.

[0074] FIGS. 3A and 3B illustrate a case in which a transistor 301 is provided and a part of the transistor 301 and the first electrode 102 are contiguous with each other to form one island. FIG. 3A shows a plan view and FIG. 3B shows a cross-sectional view. Note that in this specification, "contiguous" refers to a case in which elements are formed continuously.

**[0075]** At this time, a film in the transistor 301 and the first electrode 102 are connected to each other as one film; therefore, they can be formed at the same time. As a result, the first electrode can be manufactured without increasing the numbers of masks (reticles) and manufacturing steps.

[0076] For example, a semiconductor layer in the transistor 301 and the first electrode 102 are connected to each other and can be formed at the same time. The semiconductor layer in the transistor 301 and the first electrode 102 can be formed at the same time and etched at the same time, whereby patterning can be carried out at the same time. Further, if the semiconductor layer is formed of polysilicon, the semiconductor layer and the first electrode 102 are crystallized at the same time. In this case, a crystal grain boundary of the semiconductor layer in the transistor 301 and that of the semiconductor layer forming the first electrode 102 extend in substantially the same direction. Here, the description "crystal grain boundaries extend in substantially the same direc-

tion" refers to a case in which, for example, grain boundaries with a longitudinal direction and a direction perpendicular to the longitudinal direction (also referred to as a short direction) have uniform longitudinal direction alignment.

**[0077]** Accordingly, the semiconductor layer in the transistor 301 and the first electrode 102 contain the same material.

**[0078]** Note that since the semiconductor layer in the transistor 301 and the first electrode 102 are contiguous and connected to each other; therefore, in some cases, it is difficult to clearly distinguish where the semiconductor layer in the transistor 301 ends and where the first electrode 102 begins.

**[0079]** Note that in a case where an impurity (a p-type impurity or an n-type impurity) such as phosphorus, boron, gallium, or arsenic is introduced to a part of the semiconductor layer in the transistor 301, it is desirable that the impurity is also introduced to the first electrode 102 at the same time. When the impurity is introduced to the semiconductor layer in the transistor 301 and the first electrode 102 at the same time, since they are contiguous with each other, they can be electrically connected to each other.

**[0080]** In that case, it is not necessary to provide a contact hole and to use another wiring in order to connect the semiconductor layer in the transistor 301 and the first electrode 102. Therefore, the layout can be significantly effective, which leads to improvement in aperture ratio.

**[0081]** Note that since the transistor 301 and the first electrode 102 are contiguous, they are electrically connected to each other in many cases. The electrode which is electrically connected to the transistor 301 functions as the pixel electrode in many cases.

[0082] Note that in a case of adding the impurity at the same time to portions, the concentration thereof is influenced by a thickness or a quality of a material of a film over the portions. When being formed under the similar layer structures, the semiconductor layer in the transistor 301 and the first electrode 102 have the impurity (a ptype impurity or an n-type impurity) at approximately the same concentration, at least partially.

[0083] Note that the semiconductor layer in the transistor 301 has a channel forming region in many cases. A gate electrode is located over the channel forming region with a gate insulating film therebetween. An impurity (a p-type impurity or an n-type impurity) is not introduced to the channel forming region to form a high-concentration impurity region, normally. However, there is a case where an impurity (a p-type impurity or an n-type impurity) is introduced to the channel forming region to form an extremely low-impurity region in order to adjust a value of a threshold voltage. Further, an impurity (a p-type impurity or an n-type impurity) is introduced to the semiconductor layer in the transistor 301 to form a low-concentration impurity region (LDD: Lightly Doped Drain) in some cases. Accordingly, in many cases, the semiconductor layer in the transistor 301 has a plurality of regions

40

20

25

40

45

50

where impurities (p-type impurities or n-type impurities) are contained at various concentrations.

[0084] Note that the conductivity of a part of the semiconductor layer in the transistor 301 and that of the first electrode 102 may differ from each other. In such a case, an impurity (a p-type impurity or an n-type impurity) is introduced to the first electrode 102 at the same as a transistor other than the transistor 301. Accordingly, in that case, the semiconductor layer in the transistor other than the transistor 301 and the first electrode 102 have the impurity (a p-type impurity or an n-type impurity) at approximately the same concentration, at least partially. For example, the transistor other than the transistor 301 is provided as a part of a source signal line driver circuit or a gate signal line driver circuit.

**[0085]** The transistor 301 and the first electrode 102 are electrically connected in many cases. In addition, the electrode which is electrically connected to the transistor 301, that is, the first electrode 102 functions as the pixel electrode in many cases. Accordingly, the electrode and the transistor can be efficiently located, which is favorable.

**[0086]** Note that in FIGS. 3A and 3B, a case in which the first electrode 102 is formed at the same time as the film in the transistor 301 is described; however, it is not limited thereto. The first electrode 102 may be formed at the same time as another film, such as a film in a wiring, a resistor, a capacitor, or the like.

[0087] Note that in FIGS. 1A to 3B, a case in which only the second electrode 108 has an opening pattern is described, but it is not limited thereto. The first electrode 102 may also have an opening pattern. Accordingly, an electric field generally parallel to the substrate is generated, and orientation of the liquid crystal molecules can be controlled. FIGS. 4A to 6B show such cases. FIGS. 4A and 4B correspond to a case shown in FIGS. 1A and 1B, in which the first electrode 102 also has an opening pattern. FIGS. 5A and 5B correspond to a case shown in FIGS. 2A and 2B, in which the first electrode 102 also has an opening pattern. FIGS. 3A and 3B, in which the first electrode 102 also has an opening pattern.

[0088] When the first electrode 102 has an opening pattern as shown in FIGS. 4A to 6B, the amount of light transmitting through a portion of the opening pattern is increased. This is because the first electrode 102 and the second electrode 108 are not overlapped with each other. When the first electrode 102 and the second electrode 108 are overlapped, the amount of light transmitted therethrough is decreased unless the light transmittance is 100%. On the other hand, in a portion where the first electrode 102 and the second electrode 108 are not overlapped, light does not attenuate, which leads to increase in amount of light transmitted therethrough. As a result, it is possible to increase luminance and to reduce power consumption.

[0089] FIG 7A is a plan view for illustrating a structure of a liquid crystal display device according to Embodi-

ment Mode 1 in the present invention. In FIG 7A, one of a plurality of pixels provided in the liquid crystal display device is illustrated. This liquid crystal display device is a device in which an orientation of a liquid crystal is controlled by an FFS mode. In FIG 7A, a plurality of source wirings 107a are located parallel to one another (extending up and down in FIG 7A) and separately from one another, whereas a plurality of gate wirings 104c are located extending in a direction generally perpendicular to the source wirings 107a (from side to side in FIG. 7A) and are separated from one another. Auxiliary wirings 104b are located adjacent to each of the plurality of gate wirings 104c and extended to a direction generally parallel to the gate wirings 104c, that is, in a direction generally perpendicular (from side to side in FIG 7A) to the source wirings 107a. A space which is substantially rectangle is surrounded by the source wiring 107a, the auxiliary wiring 104b, and the gate wiring 104c. The pixel electrode of the liquid crystal display device is located in the space. A thin film transistor for driving the pixel electrode is located on the upper-left corner of FIG 7A.

[0090] As a material to be used for the gate wiring 104c, the auxiliary wiring 104b, and the source wiring 107a, one or more elements selected from aluminum (AI), tantalum (Ta), titanium (Ti), molybdenum (Mo), tungsten (W), neodymium (Nd), chromium (Cr), nickel (Ni), platinum (Pt), gold (Au), silver (Ag), copper (Cu), magnesium (Mg), scandium (Sc), cobalt (Co), zinc (Zn), niobium (Nb), silicon (Si), phosphorus (P), boron (B), arsenic (As), gallium (Ga), indium (In), tin (Sn), and oxygen (O); a compound or an alloy material containing one or more of the aforementioned elements (for example, indium tin oxide (ITO), indium zinc oxide (IZO), indium tin oxide doped with silicon oxide (ITSO), zinc oxide (ZnO), aluminum neodymium (Al-Nd), or magnesium silver (Mg-Ag)); a substance obtained by combining such compounds; or the like can be given. Alternatively, a compound (silicide) of silicon and the aforementioned material (such as aluminum silicon, molybdenum silicon, or nickel silicide) or a compound of nitride and the aforementioned material (such as titanium nitride, tantalum nitride, or molybdenum nitride) can be used. Note that silicon (Si) may contain a large amount of n-type impurities (phosphorus or the like) or p-type impurities (boron or the like). When such an impurity is contained, conductivity of silicon is improved and silicon functions similarly to normal conductor, so that it becomes easy to use silicon as a wiring or an electrode. Silicon may be single crystalline silicon, polycrystalline silicon (polysilicon), or amorphous silicon. When single crystalline silicon or polycrystalline silicon is used, resistance can be reduced. When amorphous silicon is used, a manufacturing process can be simplified. Aluminum and silver have high conductivity, so that signal delay can be reduced, and minute processing is possible since they are easy to be etched and patterned. Copper has high conductivity, so that signal delay can be reduced. Molybdenum is desirable because it can be manufactured without a problem such as a defect of a mate-

rial, even if molybdenum is in contact with an oxide semiconductor such as ITO or IZO, or silicon; and because it is easily patterned and etched, and has high heat resistance. Titanium is desirable because it can be manufactured without a problem such as a defect of a material, even if titanium is in contact with an oxide semiconductor such as ITO or IZO, or silicon; and it is easily patterned and etched, and has high heat resistance. Tungsten is desirable because it has high heat resistance. Neodymium is desirable because it has high heat resistance. In particular, an alloy of neodymium and aluminum is desirable because heat resistance is improved and hillocks of aluminum are hardly generated. Silicon is desirable because it can be manufactured at the same time as the semiconductor layer in the transistor and has high heat resistance. Indium tin oxide (ITO), indium zinc oxide (IZO), indium tin oxide doped with silicon oxide (ITSO), zinc oxide (ZnO), and silicon (Si) are desirable because they have a light-transmitting property and can be used for a portion which is required to transmit light, such as the pixel electrode and the common electrode.

[0091] Note that a wiring or an electrode may have a single layer or a multilayer structure of these materials. If a single-layer structure is employed, the manufacturing process can be simplified and the number of steps can be reduced; which leads to reduction in cost. If a multilayer structure is employed, advantage of a material can be derived and disadvantage of the material can be reduced, so that a wiring and an electrode with favorable characteristics can be formed. For example, when a material with low resistance (such as aluminum) is included in the multilayer structure, the resistance of the wiring can be reduced. In addition, if a material with high heat resistance is used, for example, to be interposed between a material with low heat resistance and another advantage in a stacked-layer structure, the heat resistance of wiring or electrode as a whole can be improved. For example, a stacked-layer structure in which a layer containing aluminum is interposed between layers containing molybdenum or titanium is desirable. In addition, there is a case in which a material is directly in contact with another wiring or another electrode of another material, so that the materials are adversely affected. For example, a material may enter another material and change its characteristics; therefore, the material cannot serve its original purpose or a problem occurs in manufacturing and the material cannot be manufactured normally. In such a case, a problem can be solved when the layer is interposed between or covered with another layer. For example, if indium tin oxide (ITO) and aluminum are required to be in contact with each other, it is desirable that titanium or molybdenum is interposed therebetween. Also, if silicon and aluminum are required to be in contact with each other, it is desirable that titanium or molybdenum is interposed therebetween.

**[0092]** Note that it is desirable that the material of the gate wiring 104c and the auxiliary wiring 104b have heat resistance higher than that of the source wiring 107a. It

is because the gate wiring 104c and the auxiliary wiring 104b are located in a higher temperature in their manufacturing steps.

[0093] Note that it is desirable that the material of the source wiring 107a has resistance lower than that of the gate wiring 104c. It is because only signals of two values, that is, High-signal and Low-signal are given to the gate wiring 104c, whereas an analog signal which contributes display is introduced to the source wiring 107a. Accordingly, it is desirable that a material with low resistance is used for the source wiring 107a so that a signal can be applied with accuracy thereto.

[0094] Note that the auxiliary wiring 104b is not necessarily provided but a potential of the common electrode in each pixel can be stabilized when the auxiliary wiring 104b is provided. Note that in FIGS. 7A and 7B, the auxiliary wiring 104b and the gate wiring 104c are located to be generally parallel to each other, but it is not limited thereto. The auxiliary wiring 104b and the source wiring 107a may be located to be generally parallel to each other. In this case, the auxiliary wiring 104b is desirably formed of a material with the same quality as the source wiring 107a.

**[0095]** However, it is favorable that the auxiliary wiring 104b is located generally parallel to the gate wiring 104c because an aperture ratio can be increased and the layout can be efficient.

**[0096]** FIG. 7B is a cross-sectional view along a line A-B and a line C-D in FIG 7A. As shown in the drawing, a base insulating film 101 is formed over the substrate 100 so as to prevent diffusion of an impurity from the substrate 100. The base insulating film 101 is formed of, for example, an insulating substance containing oxygen or nitrogen, such as silicon oxide (SiO<sub>x</sub>), silicon nitride (SiN<sub>x</sub>), silicon oxynitride (SiO<sub>x</sub>N<sub>y</sub>: x > y), or silicon nitride oxide (SiN<sub>x</sub>O<sub>y</sub>: x > y). Alternatively, a stacked-layer film including a plurality of films thereof may be used.

**[0097]** Note that the substrate 100 is a glass substrate, a quartz substrate, a substrate formed of an insulator such as alumina, a plastic substrate with enough heat resistance to withstand a processing temperature of subsequent steps, a silicon substrate, or a metal substrate. Alternatively, polysilicon may be used.

[0098] Note that when the liquid crystal display device functions as a transmissive display device, it is desirable that the substrate 100 has a light-transmitting property. [0099] A semiconductor film 102f and a first electrode 102c controlling the orientation of the liquid crystal are formed over the base insulating film 101. The semiconductor film 102f and the first electrode 102c are, for example, polysilicon films, which are formed by selectively etching a film in the same step. In other words, the semiconductor film 102f and the first electrode 102c are formed over the baser film 101 and in the same layer. However, the present invention is not limited to film formation at the same time and etching in one step. In the semiconductor film 102f, an impurity region 102d to be a source region or a drain region and an impurity region

35

45

50

102b to be a drain region or a source region of the thin film transistor are formed. The impurity regions 102d and 102b are n-type impurity regions to which, for example, phosphorus or arsenic is introduced, but the impurity regions may be p-type impurity regions. An impurity for imparting n-type conductivity, phosphorus (P) and arsenic (As) are given as an example; and as an impurity for imparting p-type conductivity, boron (B) and gallium (Ga) are given as an example. However, it is desirable that the impurity regions 102d and 102b are n-type impurity regions having high conductivity. On the other hand, when a driver circuit only includes p-type transistors, it is desirable that the impurity regions 102d and 102b also have p-type conductivity type so that the manufacturing cost can be reduced.

[0100] The first electrode 102c functions as the common electrode to which common voltage which is same as other pixels is applied and is formed of, for example, a polysilicon film to which an impurity is introduced. The resistance of the first electrode 102 is lowered since an impurity is introduced thereto, and functions as an electrode. As shown in a dotted line in FIG 7A, the first electrode 102c has a rectangular shape with a portion 1001 in which one corner (the upper-left corner of the drawing) is lacked, and is formed over almost the whole surface of the pixel. Note that in the portion 102e of which one corner is lacked, a thin film transistor is located. When a thin film transistor is located in the portion 102e in which one corner is lacked, a region which can be used to display can be formed more efficiently, which leads to improvement in aperture ratio. The first electrode 102c has a thickness of, for example, 45 nm to 60 nm, and has sufficiently high light transmittance. In order to further improve the light transmittance, it is desirable to set the thickness of the first electrode 102 to be 40 nm or less. **[0101]** The first electrode 102c is formed of polysilicon, for example, but may be another semiconductor material such as amorphous silicon, single crystalline silicon, organic semiconductor, or a carbon nanotube. In this case, an amorphous silicon film, an organic semiconductor film, or the like is used in the thin film transistor instead of the semiconductor film 102f. Note that the semiconductor film 102f and the first electrode 102c forming the transistor are desirably formed by selectively etching one film in the same step. In this case, the numbers of masks (reticles) and steps can be reduced, so that the manufacturing cost can be reduced. In addition, it is desirable that impurity elements of the same type are introduced to the impurity regions 102b and 102d at the same time. This is because when the impurity elements of the same type are introduced, the impurity elements can be introduced without a problem even if the impurity regions 102b and 102d are located close to each other, so that dense layout becomes possible. It is desirable to add impurity elements of either p-type or n-type because the manufacturing cost can be low compared with a case in which impurity elements of different types are introduced.

[0102] A gate insulating film 103 in the transistor is

formed over the whole surface including over the semiconductor film 102f.

[0103] However, there is a case in which the gate insulating film 103 is located only in the vicinity of the channel forming region and is not located in other parts. In addition, a thickness or a stacked-layer structure of the gate insulating film 103 may differ according to location. For example, the gate insulating film 103 may be thicker or include more layers in the vicinity of the channel forming region and may be thinner or include less layers in another location. Therefore, it becomes easy to control the addition of an impurity to the source region or the drain region. Further, when the thickness or the number of layers of the gate insulating film 103 in the vicinity of the channel forming region differs, the amount of impurity introduced to the semiconductor layer can be different by location, so that an LDD region or the like can be formed. When the LDD region is formed, leak current and generation of hot carriers can be suppressed, which can improve the reliability.

[0104] The gate insulating film 103 is formed of, for example, an insulating substance containing oxygen or nitrogen, such as silicon oxide (SiOx), silicon nitride  $(SiN_x)$ , silicon oxynitride  $(SiO_xN_y: x > y)$ , or silicon nitride oxide ( $SiN_xO_v$ : x > y). Alternatively, a stacked-layer film including a plurality of these films may be used. A gate electrode 104a is formed over the gate insulating film 103 and is located above the channel forming region 102a. As shown in FIGS. 7A and 7B, the gate electrode 104a is in the same wiring layer as the auxiliary wiring 104b and the gate wiring 104c, and is connected to the gate wiring 104c. In the semiconductor film 102f, a region 102a located under the gate electrode 104a functions as a channel forming region. Note that, to a semiconductor region between the two channel forming regions 102a, an impurity which is the same as that in the impurity regions 102b and 102d is introduced. Note that in this embodiment mode, a multigate structure having two gate electrodes is employed, but the present invention is not limited to this structure.

**[0105]** An insulating film 105 and a first interlayer insulting film 106a are sequentially formed over the gate insulating film 103 and the gate electrode 104a.

**[0106]** Note that only one of the insulating film 105 and the first interlayer insulating film 106a may be formed, alternatively, each of the insulating films has a multilayer structure. An inorganic material or an organic material can be used for the insulating films. As an organic material, polyimide, acrylic, polyamide, polyimide amide, resist, siloxane, polysilazane, or the like can be used. As an inorganic material, an insulating substance containing oxygen or nitrogen, such as silicon oxide  $(SiO_x)$ , silicon nitride  $(SiN_x)$ , silicon oxynitride  $(SiO_xN_y$ : x > y), or silicon nitride oxide  $(SiN_xO_y$ : x > y) can be used. Alternatively, a stacked-layer film in which a plurality of these films are stacked may be used. Further alternatively, a stacked-layer film in which an organic material and an inorganic material are combined may be used.

15

25

35

45

50

**[0107]** In the gate insulating film 103, the insulating film 105, and the first interlayer insulating film 106a, a contact hole located over the impurity region 102b, a contact hole located over the impurity region 102d, a contact hole located over the first electrode 102c, and a contact hole located over the auxiliary wiring 104b are formed. Over the first interlayer insulating film 106a, the source wiring 107a, a drain wiring 107b, and a connection wiring 107c are formed. When an organic material is used for the insulating film, intrusion of moisture or an impurity can be prevented. In particular, a layer containing nitrogen can block moisture or an impurity efficiently.

**[0108]** Note that when an organic material is used for the insulating film, a surface thereof can be planarized. Accordingly, the insulating film can have a good effect on a layer provided thereover. For example, the layer formed over the organic material can be planarized, so that disturbance of orientation of the liquid crystal can be prevented.

**[0109]** The source wiring 107a is located above a source, that is, the impurity region 102d, and has a part embedded in the contact hole; therefore, the source wiring 107a and the impurity region 102d are electrically connected. Accordingly, the source electrode functions as a part of the source wiring 107a. The drain wiring 107b is located above a drain, that is, the impurity region 102b, and has a part embedded in the contact hole; therefore, the drain wiring 107b and the impurity region 102b are connected.

**[0110]** The connection wiring 107c is extended from above the first electrode 102c to above the auxiliary wiring 104b. The connection wiring 107c has a part embedded in the contact hole; therefore, the connection wiring 107c is electrically connected to both the first electrode 102c and the auxiliary wiring 104b. When the connection wiring 107c is provided in such a manner, the contact hole can be formed with accuracy since it is not required to be deep.

[0111] In the example shown in FIG 7B, the drain wiring 107b is formed at the same time as the source wiring 107a and the connection wiring 107c. In this case, the contact hole in which a part of the drain wiring 107b is embedded and the contact hole in which a part of the second electrode 108 is embedded is not overlapped with each other. Thus, even if the drain wiring 107b and the second electrode 108 have depressions over the contact holes, the depressions are not overlapped with each other. Therefore, a deep depressed portion is not formed in the second electrode 108, so that generation of a defect in shape of the resist pattern formed thereover can be suppressed.