Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

EP 1 335 347 B1

(12)

## EUROPEAN PATENT SPECIFICATION

(45) Date of publication and mention

of the grant of the patent:

**29.04.2009 Bulletin 2009/18**

(51) Int Cl.:

**G09G 3/36 (2006.01)**

(21) Application number: **03002553.0**

(22) Date of filing: **06.02.2003**

(54) **Reference voltage generation circuit and method, display driver circuit and liquid crystal display device**

Referenzspannungserzeugungsschaltung, Verfahren dafür und Flüssigkristallanzeigevorrichtung

Circuit de génération d'une tension de référence, sa méthode de commande et circuit de commande pour panneau d'affichage à cristaux liquides

(84) Designated Contracting States:

**AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HU IE IT LI LU MC NL PT SE SI SK TR**

(30) Priority: **08.02.2002 JP 2002032677**

(43) Date of publication of application:

**13.08.2003 Bulletin 2003/33**

(73) Proprietor: **Seiko Epson Corporation

Shinjuku-ku

Tokyo 163-0811 (JP)**

(72) Inventor: **Morita, Akira

Suwa-shi,

Nagano-ken 392-8502 (JP)**

(74) Representative: **Hoffmann, Eckart

Patentanwalt,

Bahnhofstrasse 103

82166 Gräfelfing (DE)**

(56) References cited:

**EP-A- 1 014 333 EP-A- 1 094 440

US-A- 5 745 092 US-A- 5 867 057

US-B1- 6 275 207**

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

## Description

### BACKGROUND OF THE INVENTION

**[0001]** The present invention relates to a reference voltage generation circuit, a display driver circuit, a display device, and a method of generating a reference voltage.

**[0002]** A decrease in size and an increase in resolution have been demanded for a display device represented by an electro-optical device such as a liquid crystal device. In particular, a liquid crystal device realizes a decrease in power consumption and has been generally used for portable electronic equipment. In the case where a liquid crystal device is used as a display section of a portable telephone, image display with a rich color tone due to an increase in the number of grayscale levels is required.

**[0003]** Generally, an image signal for image display is gamma-corrected according to display characteristics of the display device. The gamma correction is performed by a gamma correction circuit (or a reference voltage generation circuit in a broad sense). Taking a liquid crystal device as an example, the gamma correction circuit generates a voltage corresponding to the pixel transmittance, based on grayscale data for performing grayscale display.

**[0004]** The gamma correction circuit is included in a display driver circuit which drives a display device. Therefore, a display driver circuit used in electronic equipment for which downsizing is demanded is preferably small. So that the gamma correction circuit is adjusted to perform gamma correction specified for display characteristics of the display device to be driven, and a multi-purpose display driver circuit which is widely used irrespective of the type of display device cannot be provided.

**[0005]** US-A-6,275,207 discloses a reference voltage generation circuit for generating a plurality of reference voltages comprising: one resistance ladder circuit having a plurality of variable resistance circuits in which the resistance value between both ends is variable and which are connected in series between a first and a second power supply line. The resistance values of the variable resistance circuits are variably controlled according to a given command setting. A reference voltage generation circuit of the same structure is also disclosed in US-A-5,867,057.

**[0006]** In one embodiment, US-A-5,867,057 discloses a reference voltage generation circuit according to the pre-characterizing portion of claim 1. In this known circuit a resistance ladder circuit is composed of a series connection of a plurality of pairs of series-connected resistors, a first one of a higher resistance value and a second one of a lower resistance value. A respective switch is connected in parallel to each first resistor so that these first resistors can be selectively short-circuited whereas no such short-circuiting is provided for the second resistors.

**[0007]** EP-A-1 094 440 discloses a signal driver for a liquid crystal display device which supplies a voltage to a load capacitance to finish charging the load capacitance with a predetermined voltage within a predetermined charging period. The driver comprises a digital-analogue converter (DAC) and a voltage follower circuit for performing the impedance conversion for a voltage from the DAC and outputting the converted voltage. A first switching element is provided between the output of

5 the voltage follower circuit and the load capacitance. A bypass line is provided for supplying a voltage from the DAC to the load capacitance bypassing the impedance conversion circuit and the first switching element, and a second switching element is provided in the bypass line.

10 In a first period of the charging period, the first switching element is turned on, and the second switching element is turned off, whereby the output of the voltage follower circuit is supplied to the load capacitance. In a second period of the charging period, the first switching element is turned off, and the second switching element is turned on, whereby the output of the DAC is supplied to the load capacitance instead of the output of the voltage follower circuit. This structure is provided to overcome the problem of an offset voltage introduced by the voltage follower circuit.

15 **[0008]** US-A-5,745,092 discloses a reference voltage generation circuit for generating a plurality of reference voltages for generating a gamma-corrected grayscale value based on grayscale data. This known reference voltage generation circuit comprises a first resistance ladder circuit having at least one variable resistance circuit in which the resistance value between both ends is variable; and a second resistance ladder circuit in which a plurality of resistance circuits each having a fixed resistance value are connected in series. The first and the second resistance ladder circuits are connected in series between a first and a second power supply line to which a first and a second power supply voltage are respectively supplied. The resistance value of the variable resistance 20 circuit in the first resistance ladder circuit is variably controlled according to a given command setting or a given variable control signal. A respective buffer amplifier is connected between each node of the second resistance ladder circuit and the corresponding reference voltage output. This prior art aims at providing a power supply technique for a LCD device which is optimum when the source voltage range of a signal driver is different from that of a scan driver.

### 50 BRIEF SUMMARY OF THE INVENTION

**[0009]** It is an object of the present invention to provide a reference voltage generation circuit, a display driver circuit, and a display device which can be multi-purposely used without increasing the circuit size, irrespective of the type of display device.

**[0010]** This object is achieved by a reference voltage generation circuit as claimed in claim 1, a display driver

circuit as claimed in claim 3, and a display device as claimed in claim 5. Preferred embodiments of the invention are subject-matter of the dependent claims.

**[0011]** In this configuration, the first to third resistance ladder circuits are connected in series between the first and second power supply lines, and the multi-valued reference voltages are output from each of the resistance ladder circuits. Each of the first and third resistance ladder circuits includes at least one variable resistance circuit in which the resistance value between both ends is variable, and the second resistance ladder circuit is formed by connecting the resistance circuits having a fixed resistance value in series. The first and third resistance ladder circuits are variably controlled by a given command from a user or a given variable control signal, for example. The resistance value of the second resistance ladder circuit is not changed by the command or the variable control signal.

**[0012]** The first and third resistance ladder circuits may be variably controlled by the same command or the same variable control signal, or by different commands or different variable control signals.

**[0013]** In a display panel, in particular a liquid crystal panel, the reference voltage for performing optimum grayscale display depends on a liquid crystal material or the like. Therefore, the resistance ratio of the resistance ladder must be optimized according to the type of display panel. However, the resistance ratio of the resistance ladder is substantially constant in a halftone region irrespective of the type of display panel. According to this configuration of the invention, the resistance ratio can be changed according to the type of display panel by variably controlling only the resistance values of the first and third resistance ladder circuits using a command or a variable control signal. So that the reference voltages which are gamma-corrected for performing optimum grayscale display can be generated irrespective of the type of display panel, while minimizing an increase in circuit size due to variable control.

**[0014]** The embodiment according to claim 2 makes it possible to control the resistance ratio with higher accuracy to provide a general-purpose reference voltage generation circuit.

#### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

##### **[0015]**

FIG. 1 is a block diagram showing a display device to which a display driver circuit including a reference voltage generation circuit according to one embodiment of the present invention is applied.

FIG. 2 is a block diagram showing a signal driver IC to which the display driver circuit including the reference voltage generation circuit is applied.

FIG. 3 is a graph illustrating the principle of gamma correction.

FIG. 4 is a circuit diagram schematically showing a voltage follower circuit.

FIG. 5 is a timing chart showing an example of the operation timing of the voltage follower circuit.

FIG. 6 is a circuit diagram schematically showing the reference voltage generation circuit according to one comparative example.

FIG. 7 is a graph illustrating grayscale characteristics.

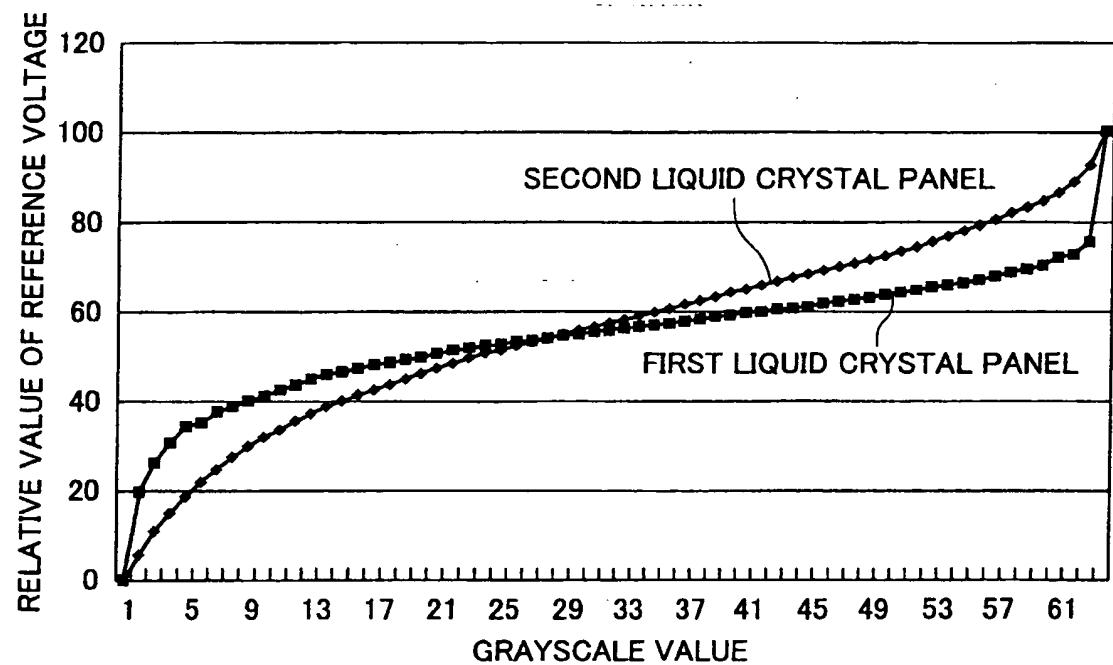

FIG. 8 is a graph illustrating reference voltages optimized for grayscale values in the first and second liquid crystal panels.

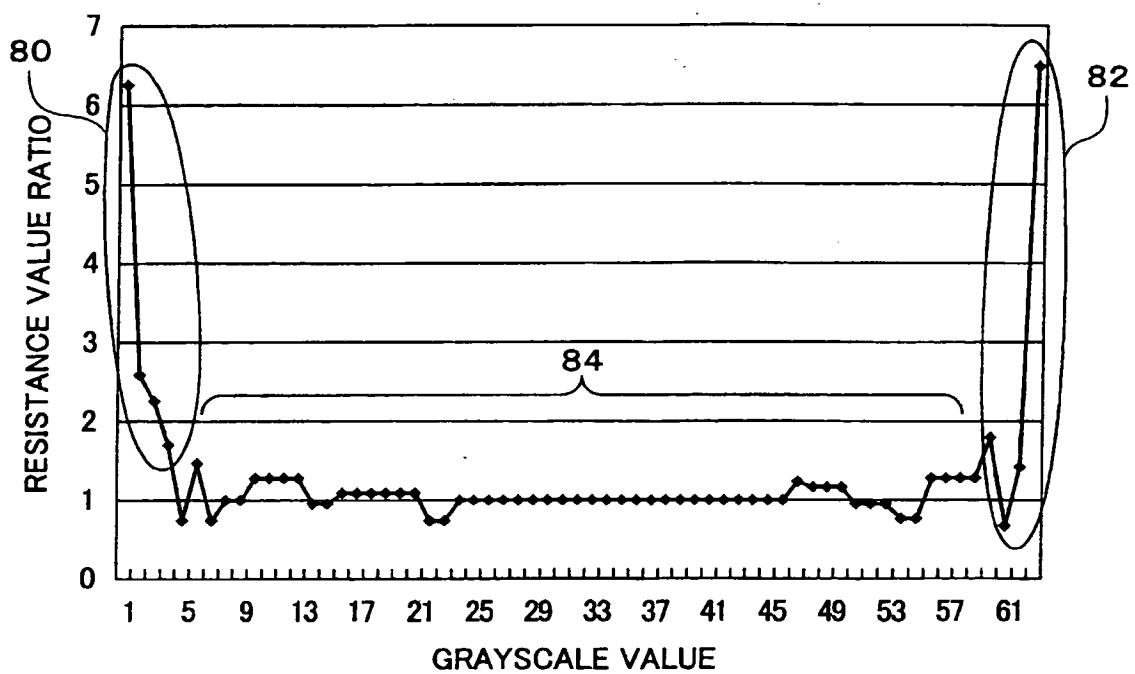

FIG. 9 is a graph showing the relationship between a grayscale value and a resistance value ratio of the first and second liquid crystal panels.

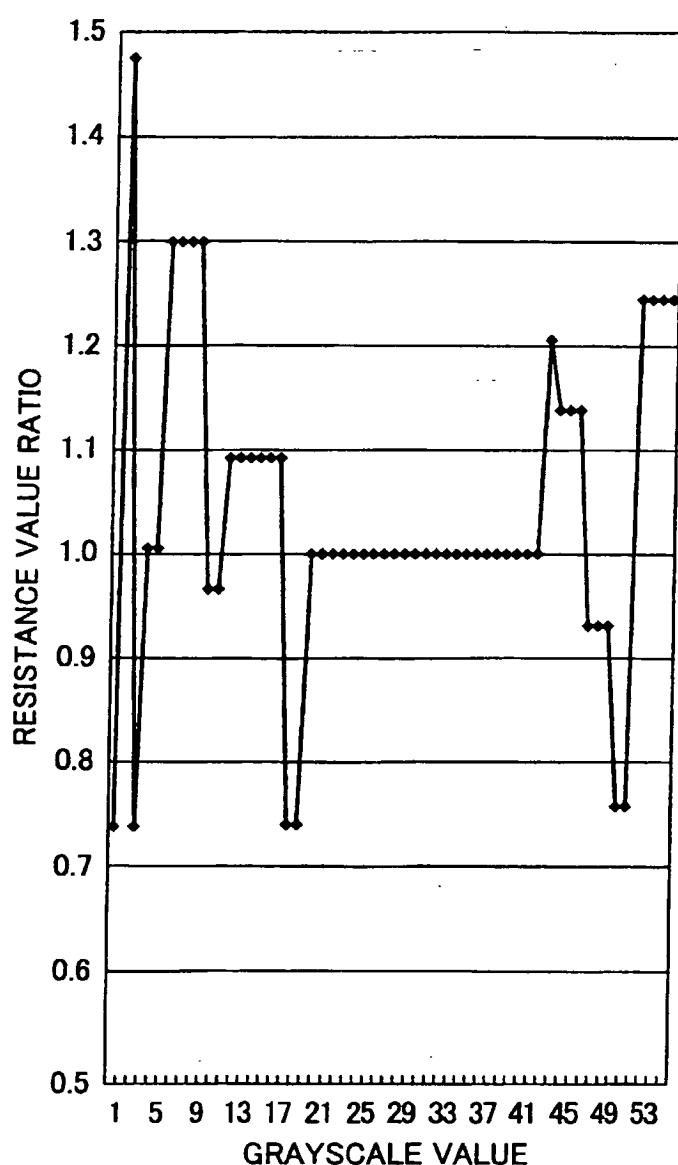

FIG. 10 is a graph showing the relationship between a grayscale value and a resistance value ratio of the first and second liquid crystal panels when four grayscales on each end are removed.

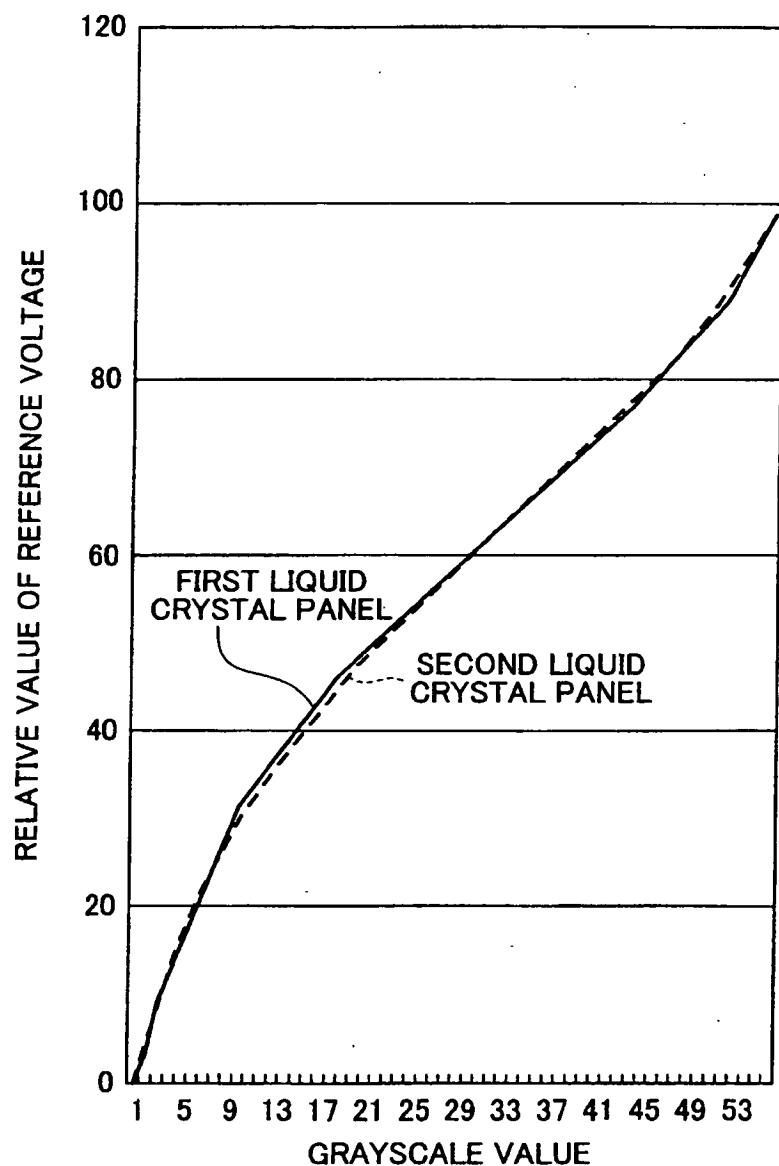

FIG. 11 is a graph showing a reference voltage optimized for grayscale values when four grayscales on each end are removed.

FIG. 12 is a circuit diagram showing an example of the reference voltage generation circuit according to another example.

FIGS. 13A to 13C are circuit diagrams showing a first resistance ladder circuit in the first example.

FIG. 14 is a circuit diagram showing the first resistance ladder circuit in the second example.

FIG. 15 is a circuit diagram showing the first resistance ladder circuit in the third example.

FIG. 16 is a circuit diagram showing the first resistance ladder circuit in the fourth example.

FIG. 17 is a timing chart showing the operation timing of the first resistance ladder circuit in the fourth example.

FIG. 18 is a circuit diagram showing an example of the operational amplifier circuit.

FIG. 19 is a timing chart showing the operation control timing of the operational amplifier circuit.

FIG. 20 is a circuit diagram showing an example of a two-transistor pixel circuit in an organic EL panel.

FIG. 21A is a circuit diagram showing an example of a four-transistor pixel circuit in an organic EL panel; and FIG. 21B is a timing chart showing an example of the display control timing of the pixel circuit.

#### DETAILED DESCRIPTION OF THE EMBODIMENT

**[0016]** Examples of the present invention are described below in detail with reference to the drawings. Note that the embodiments described below do not in any way limit the scope of the invention defined by the claims laid out herein. Similarly, all the elements of the examples described below should not be taken as essential requirements of the present invention.

**[0017]** A reference voltage generation circuit in one embodiment of the present invention may be used as a

gamma correction circuit. The gamma correction circuit is included in a display driver circuit. The display driver circuit may be used to drive an electro-optical device such as a liquid crystal device having optical characteristics which can be changed by application of voltages.

**[0018]** Although embodiments of the reference voltage generation circuit of the present invention applied to a liquid crystal device will be described below, the present invention is not limited thereto, and it can equally well be applied to other display devices.

### 1. Display device

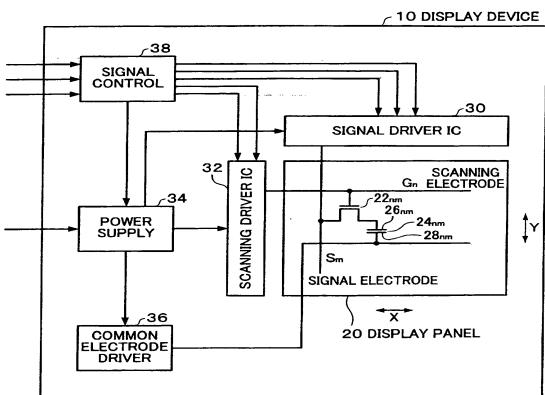

**[0019]** FIG. 1 schematically shows a display device to which a display driver circuit including a reference voltage generation circuit according to one comparative example is applied.

**[0020]** A display device (electro-optical device or liquid crystal device in a narrow sense) 10 may include a display panel (liquid crystal panel in a narrow sense) 20.

**[0021]** The display panel 20 is formed on a glass substrate, for example. A plurality of scanning electrodes (gate lines)  $G_1$  to  $G_N$  ( $N$  is an integer equal to or larger than 2) which are arranged in the Y direction and extend in the X direction, and a plurality of signal electrodes (source lines)  $S_1$  to  $S_M$  ( $M$  is an integer equal to or larger than 2) which are arranged in the X direction and extend in the Y direction are disposed on the glass substrate. A pixel region (pixel) is provided corresponding to the intersection point between the scanning electrode  $G_n$  ( $1 \leq n \leq N$ ,  $n$  is an integer) and the signal electrode  $S_m$  ( $1 \leq m \leq M$ ,  $m$  is an integer). A thin film transistor (TFT)  $22_{nm}$  is disposed in the pixel region.

**[0022]** A gate electrode of the TFT  $22_{nm}$  is connected with the scanning electrode  $G_n$ . A source electrode of the TFT  $22_{nm}$  is connected with the signal electrode  $S_m$ . A drain electrode of the TFT  $22_{nm}$  is connected with a pixel electrode  $26_{nm}$  of a liquid crystal capacitance (liquid crystal element in a broad sense)  $24_{nm}$ .

**[0023]** The liquid crystal capacitance  $24_{nm}$  is formed by sealing a liquid crystal between the pixel electrode  $26_{nm}$  and a common electrode  $28_{nm}$  opposite thereto. The transmittance of the pixel is changed corresponding to voltage applied between these electrodes. A common electrode voltage  $V_{com}$  is supplied to the common electrode  $28_{nm}$ .

**[0024]** The display device 10 may include a signal driver IC 30. The display driver circuit in this example may be used as the signal driver IC 30. The signal driver IC 30 drives the signal electrodes  $S_1$  to  $S_M$  of the display panel 20 based on image data.

**[0025]** The display device 10 may include a scanning driver IC 32. The scanning driver IC 32 sequentially drives the scanning electrodes  $G_1$  to  $G_N$  of the display panel 20 in one vertical scanning period.

**[0026]** The display device 10 may include a power supply circuit 34. The power supply circuit 34 generates voltage necessary for driving the signal electrode and sup-

plies the voltage to the signal driver IC 30. The power supply circuit 34 generates voltage necessary for driving the scanning electrode and supplies the voltage to the scanning driver IC 32. The power supply circuit 34 generates the common electrode voltage  $V_{com}$ .

**[0027]** The display device 10 may include a common electrode driver circuit 36. The common electrode voltage  $V_{com}$  generated by the power supply circuit 34 is supplied to the common electrode driver circuit 36. The common electrode driver circuit 36 outputs the common electrode voltage  $V_{com}$  to the common electrode of the display panel 20.

**[0028]** The display device 10 may include a signal control circuit 38. The signal control circuit 38 controls the signal driver IC 30, the scanning driver IC 32, and the power supply circuit 34 according to the contents set by a host such as a central processing unit (or CPU, not shown). For example, the signal control circuit 38 sets the operation mode, or supplies a vertical synchronization signal or a horizontal synchronization signal generated therein to the signal driver IC 30 and the scanning driver IC 32. The signal control circuit 38 controls a polarity inversion timing of the power supply circuit 34.

**[0029]** In FIG. 1, the display device 10 includes the power supply circuit 34, the common electrode driver circuit 36, and the signal control circuit 38. However, at least one of these circuits may be provided outside the display device 10. The display device 10 may include the host.

**[0030]** In FIG. 1, at least either the display driver circuit having a function of the signal driver IC 30 or the scanning electrode driver circuit having a function of the scanning driver IC 32 may be formed on the glass substrate on which the display panel 20 is formed.

**[0031]** In the display device 10 having the above-described configuration, the signal driver IC 30 outputs voltage corresponding to grayscale data to the signal electrode for performing grayscale display based on the grayscale data. The signal driver IC 30 gamma-corrects the voltage to be output to the signal electrode based on the grayscale data. Therefore, the signal driver IC 30 includes a reference voltage generation circuit (or a gamma correction circuit, in a narrow sense) for performing gamma correction.

**[0032]** Generally, grayscale characteristics of the display panel 20 differ depending on the structure of the display panel 20 or a liquid crystal material used therefor. Specifically, the relationship between the voltage which should be applied to the liquid crystal and the transmittance of the pixel does not become uniform. Therefore, gamma correction is performed by the reference voltage generation circuit in order to generate an optimum voltage which should be applied to the liquid crystal corresponding to the grayscale data.

**[0033]** In gamma correction, multi-valued voltages generated by a resistance ladder are corrected in order to optimize the voltage which is selected and output based on the grayscale data. The resistance ratio of the resistance circuits of the resistance ladder is determined

so that the voltage specified by the manufacturer or the like of the display panel 20 is generated.

**[0034]** Gamma correction enables the display panel to be driven by using voltage optimum for the display panel to be driven. However, it is necessary to change the voltage generated by the reference voltage generation circuit for each display panel to be driven by changing the resistance ratio of each resistance circuit of the resistance ladder. Therefore, the display driver circuit including the reference voltage generation circuit must be changed depending on the type of display panel to be driven. As a result, the display driver circuit cannot be used irrespective of the type of display panel, whereby a further decrease in cost cannot be achieved.

**[0035]** In one comparative example, a reference voltage generation circuit which can be widely used irrespective of the type of display panel to be driven, and a display driver circuit using the same are provided.

**[0036]** The signal driver IC 30 to which the display driver circuit including the above reference voltage generation circuit is applied is described below.

## 2. Signal driver IC

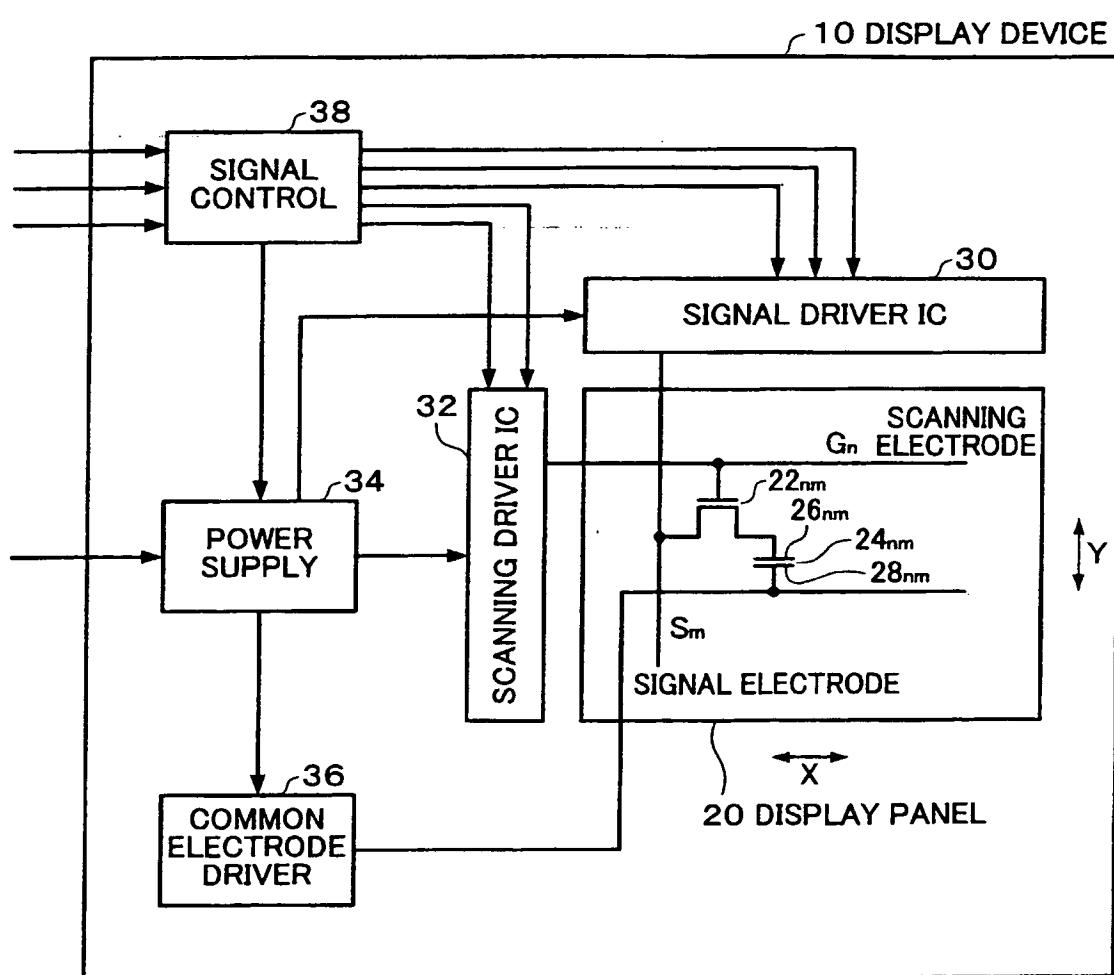

**[0037]** FIG. 2 is a block diagram showing the signal driver IC 30 to which the display driver circuit including the reference voltage generation circuit according to one comparative example is applied.

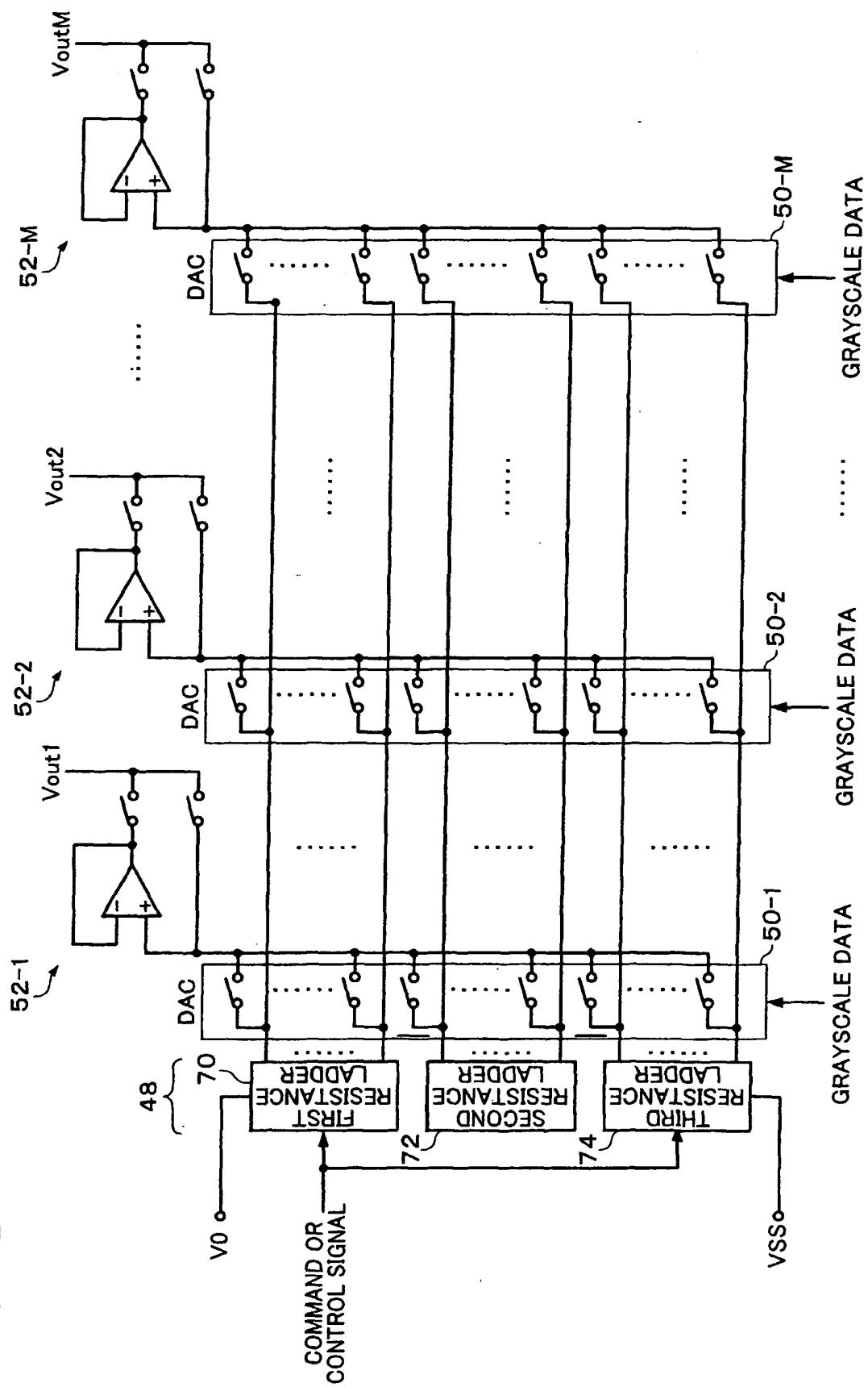

**[0038]** The signal driver IC 30 includes an input latch circuit 40, a shift register 42, a line latch circuit 44, a latch circuit 46, a reference voltage generation circuit (or a gamma correction circuit, in a narrow sense) 48, a digital/analog converter (DAC, or a voltage select circuit, in a broad sense) 50, and a voltage follower circuit (or a signal electrode driver circuit, in a broad sense) 52.

**[0039]** The input latch circuit 40 latches the grayscale data consisting of each six bits of RGB signals supplied from the signal control circuit 38 shown in FIG. 1 based on a clock signal CLK, for example. The clock signal CLK is supplied from the signal control circuit 38.

**[0040]** The grayscale data latched by the input latch circuit 40 is sequentially shifted in the shift register 42 based on the clock signal CLK. The grayscale data sequentially shifted in the shift register 42 is captured in the line latch circuit 44.

**[0041]** The grayscale data captured in the line latch circuit 44 is latched by the latch circuit 46 at a timing of a latch pulse signal LP. The latch pulse signal LP is input in a horizontal scanning cycle.

**[0042]** The reference voltage generation circuit 48 outputs multi-valued reference voltages V0 to VY (Y is a positive integer) generated at the divided nodes which are divided by resistance between the power supply voltage (first power supply voltage) V0 on the high potential side and the power supply voltage (second power supply voltage) VSS on the low potential side by using the resistance ratio of the resistance ladder determined so that the grayscale display of the display panel to be driven is

optimized.

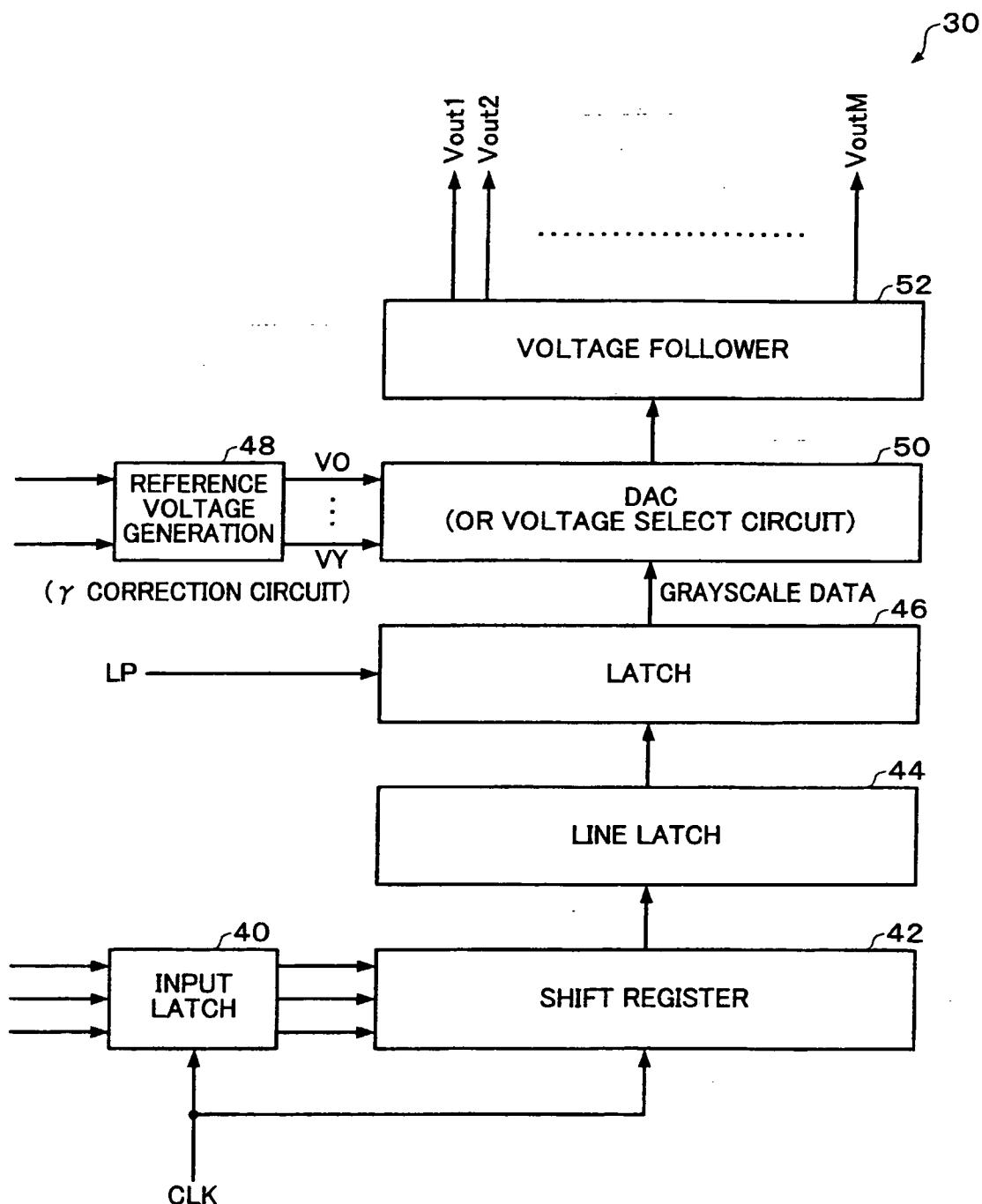

**[0043]** FIG. 3 is a graph illustrating the principle of gamma correction.

**[0044]** Grayscale characteristics showing a change in transmittance of the pixel with respect to the voltage applied to the liquid crystal is shown in this figure. If the transmittance of the pixel is indicated by 0% to 100% (or 100% to 0%), the change in transmittance is generally decreased as the voltage applied to the liquid crystal is decreased or increased. The change in transmittance is increased in a region near the middle of the voltage applied to the liquid crystal.

**[0045]** Therefore, transmittance which is gamma-corrected so as to be linearly changed corresponding to the applied voltage can be realized by performing gamma ( $\gamma$ ) correction so that the change in transmittance is the reverse of the above-described change in transmittance. Therefore, a reference voltage Vy which realizes an optimized transmittance can be generated based on the grayscale data as digital data. Specifically, the resistance ratio of the resistance ladder is determined so that such a reference voltage is generated.

**[0046]** The multi-valued reference voltages V0 to VY generated by the reference voltage generation circuit 48 shown in FIG. 2 are supplied to the DAC 50.

**[0047]** The DAC 50 selects one of the multi-valued reference voltages V0 to VY based on the grayscale data supplied from the latch circuit 46, and outputs the selected reference voltage to the voltage follower circuit 52.

**[0048]** The voltage follower circuit 52 performs impedance transformation and drives the signal electrode based on the voltage supplied from the DAC 50.

**[0049]** As described above, the signal driver IC 30 performs impedance transformation by using the voltage selected from the multi-valued reference voltages based on the grayscale data, and outputs the voltage to each signal electrode.

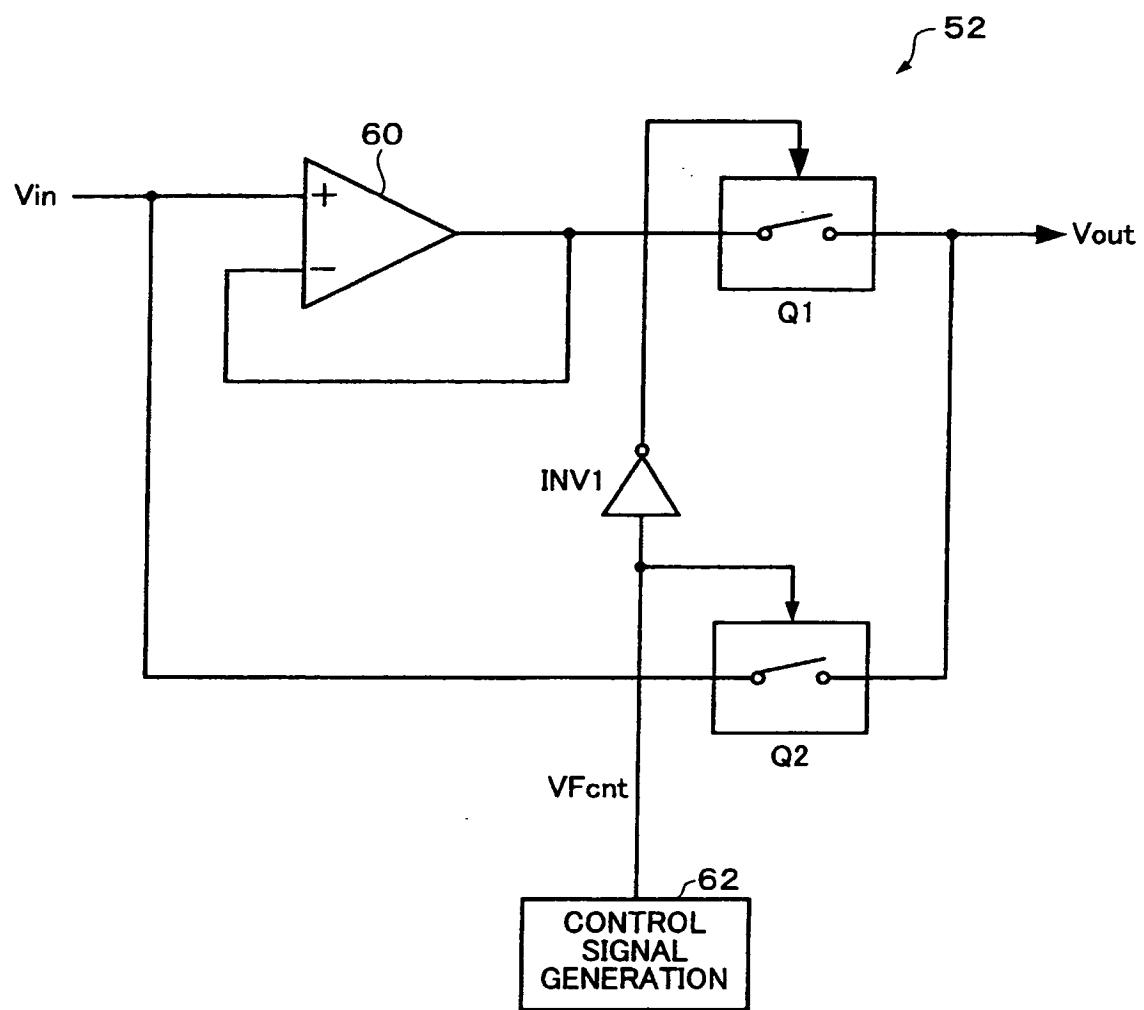

**[0050]** FIG. 4 schematically shows the voltage follower circuit 52.

**[0051]** Only the configuration for one output is shown in this figure.

**[0052]** The voltage follower circuit 52 includes an operational amplifier 60 and first and second switch elements Q1 and Q2.

**[0053]** The operational amplifier 60 is voltage follower connected. Specifically, an output terminal of the operational amplifier 60 is connected with an inverting input terminal of the operational amplifier 60, whereby negative feedback is formed.

**[0054]** A reference voltage Vin selected by the DAC 50 shown in FIG. 2 is input to a noninverting input terminal of the operational amplifier 60. The output terminal of the operational amplifier 60 is connected with the signal electrode to which a drive voltage Vout is output through the first switch element Q1. The signal electrode is also connected with the noninverting input terminal of the operational amplifier 60 through the second switch element Q2.

**[0055]** A control signal generation circuit 62 generates

a control signal VFcnt for ON-OFF controlling the first and second switch elements Q1 and Q2. The control signal generation circuit 62 may be provided for each unit of one or more signal electrodes.

**[0056]** The second switch element Q2 is ON-OFF controlled by the control signal VFcnt. The first switch element Q1 is ON-OFF controlled by an output signal of an inverter circuit INV1 to which the control signal VFcnt is input.

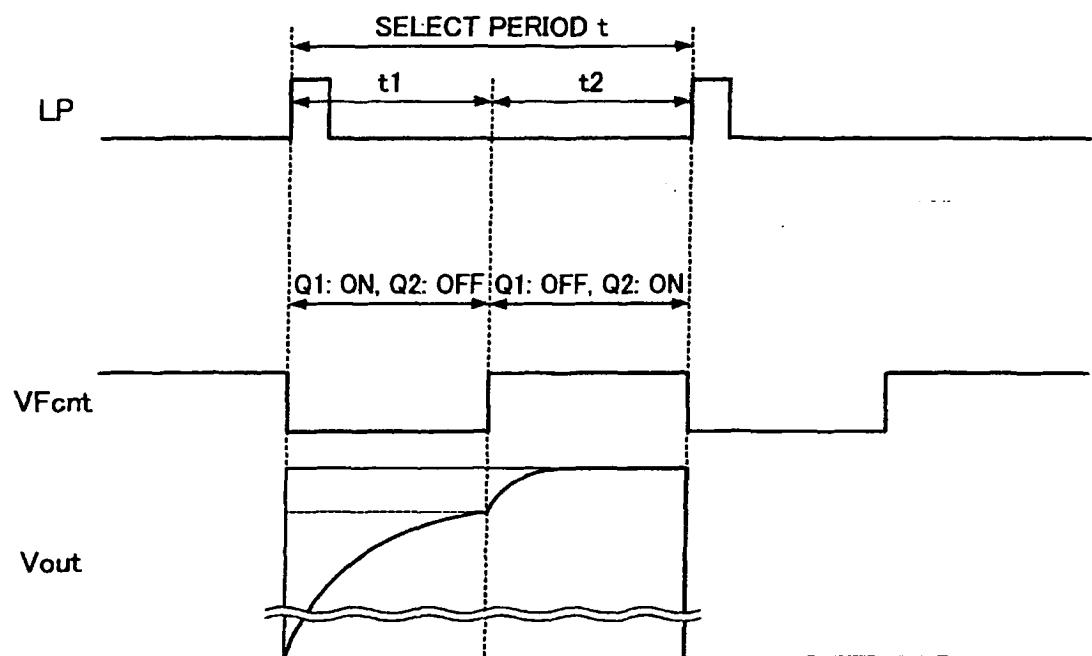

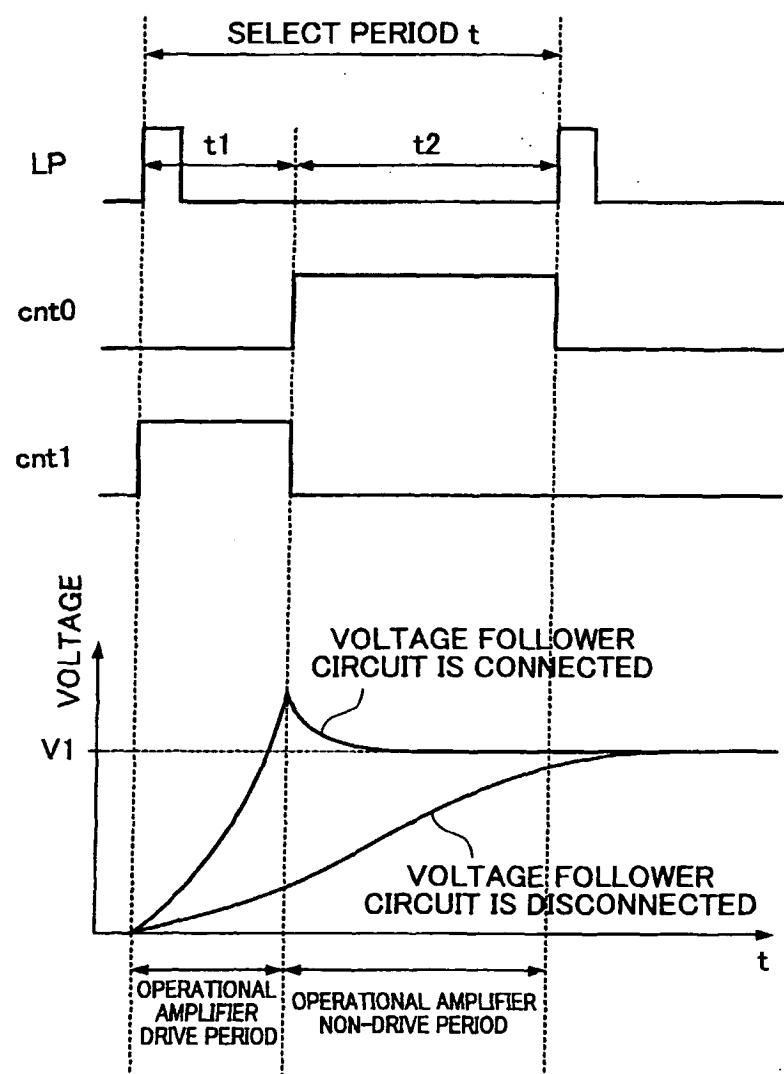

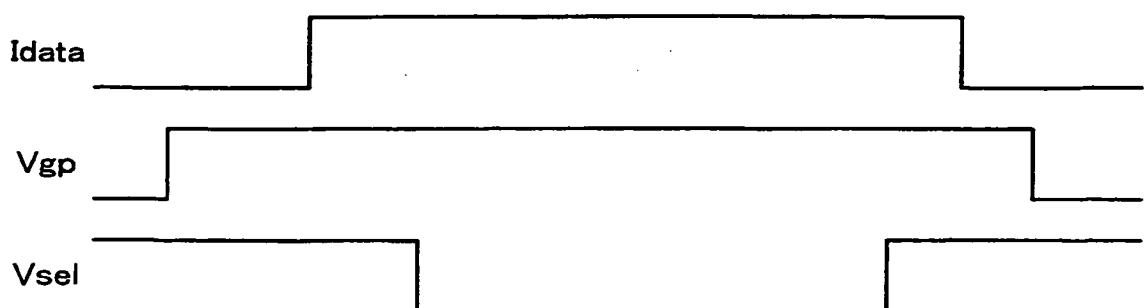

**[0057]** FIG. 5 shows an example of the operation timing of the voltage follower circuit 52.

**[0058]** The logic level of the control signal VFcnt generated by the control signal generation circuit 62 is changed between a former period (a given first period of a drive period) t1 and a latter period t2 of a select period (or a drive period) t specified by the latch pulse signal LP. Specifically, when the logic level of the control signal VFcnt becomes "L" in the former period t1, the first switch element Q1 is turned ON and the second switch element Q2 is turned OFF. When the logic level of the control signal VFcnt becomes "H" in the latter period t2, the first switch element Q1 is turned OFF and the second switch element Q2 is turned ON. Therefore, in the former period t1 of the select period t, the signal electrode is driven after impedance transformation by the voltage follower connected operational amplifier 60. In the latter period t2, the signal electrode is driven by using the reference voltage output from the DAC 50.

**[0059]** This enables the drive voltage Vout to be raised at high speed by the voltage follower connected operational amplifier 60 having high drive capability in the former period t1 necessary for charging the liquid crystal capacitance, interconnect capacitance, and the like, and the drive voltage to be output by the DAC 50 in the latter period t2 in which high drive capability is unnecessary. Therefore, the operation period of the operational amplifier 60 which consumes a large amount of current can be minimized, whereby power consumption can be decreased. Moreover, occurrence of a problem in which the charge period becomes insufficient due to a decrease in the select period t accompanied by an increase in the number of lines can be prevented.

**[0060]** The reference voltage generation circuit 48 shown in FIG. 2 is formed so that only some of the resistance circuits can be variably controlled without making all the resistance circuits of the resistance ladder variable, taking grayscale characteristics of a display panel to be driven into consideration. This enables the circuit scale of the resistance ladder, interconnection of control lines, and the control of the resistance ladder to be simplified. In particular, since an increase in the number of grayscale levels involves expectation of an increase in the number of reference voltages to be generated, it is preferable that the reference voltage generation circuit can be multi-purposely used without increasing the circuit size of the resistance ladder circuit as much as possible and irrespective of the type of display panel.

**[0061]** The reference voltage generation circuit 48 var-

iably controls the resistance ladder based on a given command from the user or a variable control signal input through an external input terminal instead of switching interconnects by changing a mask pattern or the like.

**5** This enables the signal driver IC 30 to be widely used irrespective of the type of display panel.

**[0062]** The reference voltage generation circuit 48 is described below in detail.

**10** 3. Reference voltage generation circuit

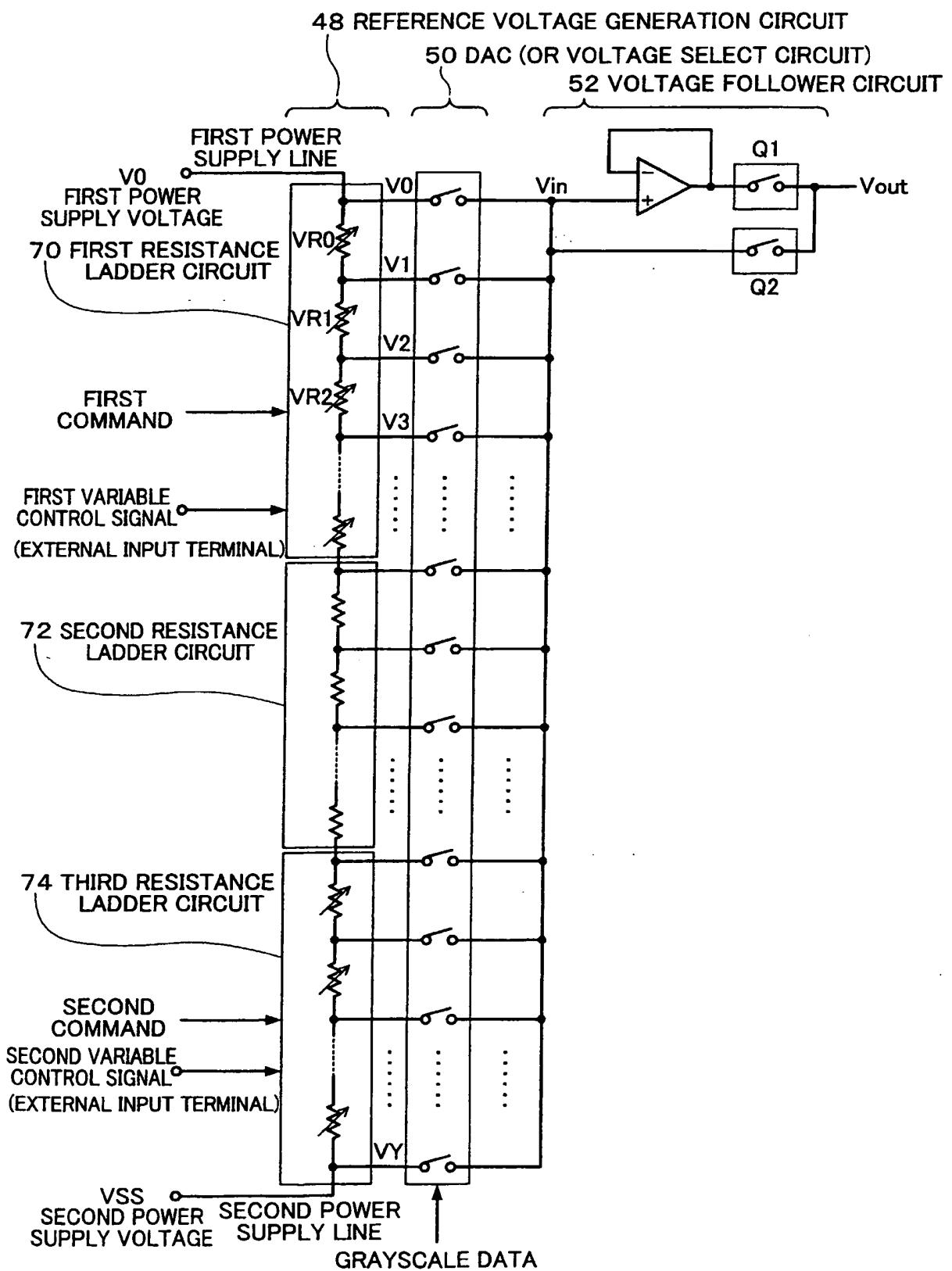

**[0063]** FIG. 6 schematically shows the reference voltage generation circuit 48 according to one comparative example.

**15** **[0064]** In addition to the reference voltage generation circuit 48, the DAC 50 and the voltage follower circuit 52 are also illustrated in this figure.

**[0065]** The reference voltage generation circuit 48 outputs the multi-valued reference voltages V0 to VY by the

**20** resistance ladder connected between the first power supply line to which the power supply voltage (first power supply voltage) V0 on the high potential side is supplied and the second power supply line to which the power supply voltage (second power supply voltage) VSS on

**25** the low potential side is supplied. In more detail, the reference voltage generation circuit 48 includes first to third resistance ladder circuits 70, 72, and 74. The first resistance ladder circuit 70 includes at least one variable resistance circuit in which the resistance value between

**30** both ends is variable, and outputs multi-valued voltages. The second resistance ladder circuit 72 has a plurality of series-connected resistance circuits each having a fixed resistance value, and outputs a plurality of voltages. The third resistance ladder circuit 74 includes at least one

**35** variable resistance circuit in which the resistance value between both ends is variable, and outputs multi-valued voltages.

**[0066]** The first to third resistance ladder circuits 70, 72, and 74 are connected in series between the first and

**40** second power supply lines. In more detail, one end of the first resistance ladder circuit 70 is connected with the first power supply line. The other end of the first resistance ladder circuit 70 is connected with one end of the second resistance ladder circuit 72. The other end of the

**45** second resistance ladder circuit 72 is connected with one end of the third resistance ladder circuit 74. The other end of the third resistance ladder circuit 74 is connected with the second power supply line. The first resistance ladder circuit 70 outputs voltages generated between

**50** both ends of each resistance circuit in the resistance ladder as the multi-valued reference voltages. The second resistance ladder circuit 72 outputs voltages across the resistance circuits of the resistance ladder as the multi-valued reference voltages. The third resistance ladder

**55** circuit 74 outputs voltages across the resistance circuits of the resistance ladder as the multi-valued reference voltages.

**[0067]** The resistance value of the variable resistance

circuit of the first resistance ladder circuit 70 is variably controlled based on a first command specified by the user or a first variable control signal input through a given external input terminal, for example. The resistance value of the variable resistance circuit of the third resistance ladder circuit 74 is variably controlled based on a second command specified by the user or a second variable control signal input through a given external input terminal, for example. The first and third resistance ladder circuits 70 and 74 may include a resistance circuit having a fixed resistance value, or may be formed only of the variable resistance circuits. The first and third resistance ladder circuits 70 and 74 include at least one variable resistance circuit. The variable resistance circuit may be realized by a resistance element or a resistance element and a switch element, for example.

**[0068]** The first and second commands may be the same command or separately specified. The first and second variable control signals may be the same signal or separately input.

**[0069]** As described above, the reference voltage generation circuit 48 has a configuration in which only the resistance circuits for generating the reference voltages close to the first and the second power supply voltages are variably controlled in the resistance ladder connected between the first and second power supply lines. This eliminates the need to variably control all the resistance circuits of the resistance ladder, whereby the control is facilitated and an increase in circuit scale can be prevented.

**[0070]** The multi-valued reference voltages  $V_0$  to  $V_Y$  generated by the reference voltage generation circuit 48 are supplied to the DAC 50. The DAC 50 includes switch circuits provided for each reference voltage output node. Each switch circuit is alternatively turned ON based on the grayscale data supplied from the latch circuit 46 shown in FIG. 2. The DAC 50 outputs the select voltage to the voltage follower circuit 52 as the output voltage  $V_{in}$ .

### 3.1 Grayscale characteristics

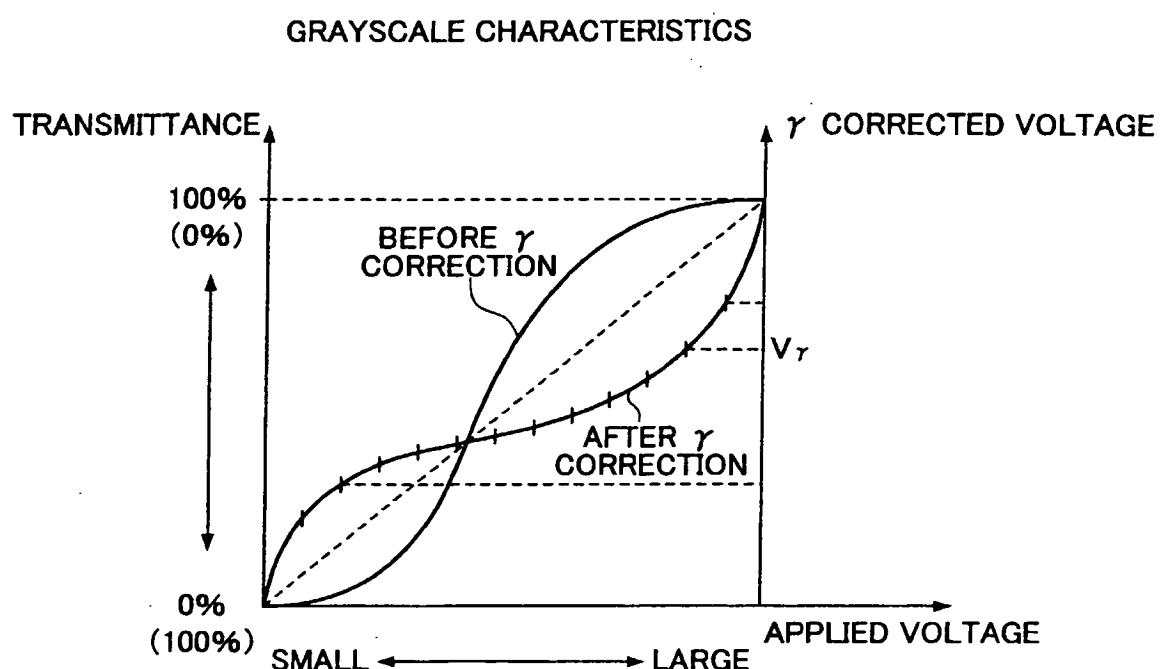

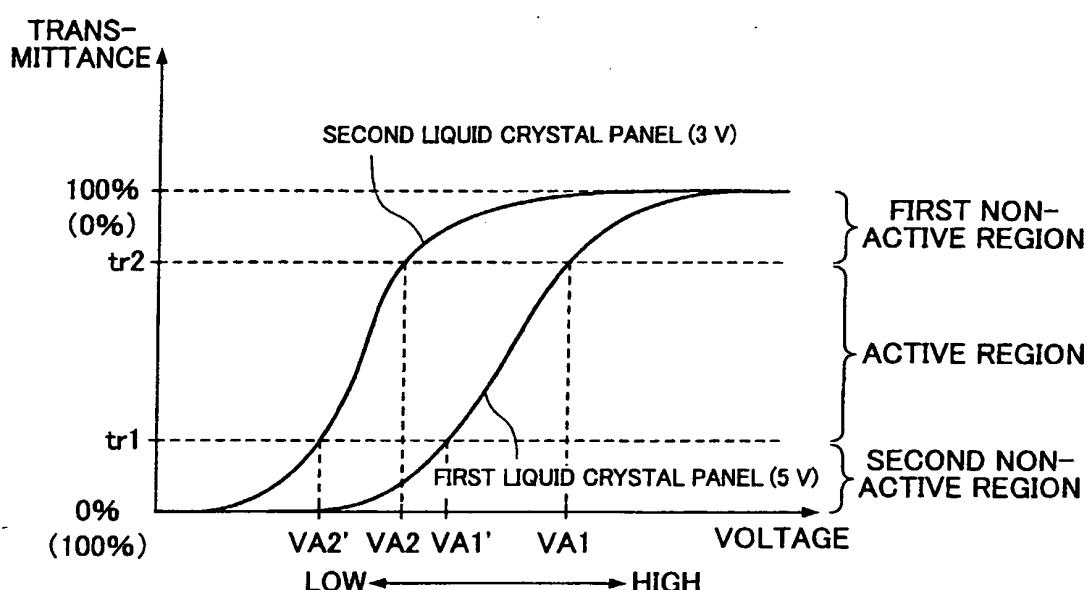

**[0071]** FIG. 7 is a graph illustrating grayscale characteristics.

**[0072]** Generally, grayscale characteristics of a display panel, in particular a liquid crystal panel, differ depending on the structure of the display panel or a liquid crystal material used therefor. Therefore, it is known that the relationship between the voltage which should be applied to the liquid crystal and the transmittance of the pixel does not become constant. Taking a first liquid crystal panel designed for a power supply voltage of 5 V and a second liquid crystal panel designed for a power supply voltage of 3 V as examples, the range of the applied voltage at which the liquid crystal panel is operated in an active region in which the change in transmittance of the pixel is large differs between the first and second liquid crystal panels, as shown in FIG. 7. Therefore, it is necessary to determine the resistance ratio of the resistance

ladder separately for the first and second liquid crystal panels in order to correct the voltage so that optimum grayscale display is realized. The resistance ratio of the resistance ladder used herein refers to a ratio of the resistance value of each resistance circuit of the resistance ladder to the total resistance value of the resistance ladder connected in series between the first and second power supply lines.

**[0073]** FIG. 8 shows reference voltages optimized for grayscale values in the first and second liquid crystal panels.

**[0074]** Reference voltages optimized for 64 grayscale values are indicated by relative value ratios based on the power supply voltage. The relative value of the reference voltage is "100" when the grayscale value is maximum. As shown in FIG. 8, the corrected reference voltages differs depending on the type of liquid crystal panel.

**[0075]** The inventor of the present invention has analyzed the resistance value ratio and obtained the following results. The meaning of the resistance value ratio is as follows. In the case where the resistance ladder is formed by first to P-th (P is a positive integer) resistance circuits connected in series, provided that the resistance value of the L-th ( $1 \leq L \leq P$ , L is a positive integer) resistance circuit which generates the reference voltage optimized for the first liquid crystal panel is a first resistance value, and the resistance value of the L-th resistance circuit which generates the reference voltage optimized for the second liquid crystal panel is a second resistance value, the resistance value ratio refers to the ratio of the first resistance value to the second resistance value.

**[0076]** FIG. 9 shows the relationship between a grayscale value and a resistance value ratio of the first and second liquid crystal panels.

**[0077]** 63 resistance value ratios necessary for generating the reference voltages for 64 grayscale levels are shown in this graph. The resistance value ratios are increased in sections 80 and 82 in which the reference voltages close to the power supply voltage on the high potential side and the power supply voltage on the low potential side are generated. However, the resistance value ratios in a half tone section 84 are approximately "1". In the case where the resistance value ratio is approximately "1", the resistance values for generating the reference voltages corresponding to the grayscale value are equal.

**[0078]** In the case of removing each four grayscales in the sections 80 and 82 in which the reference voltages close to the power supply voltage on the high potential side and the power supply voltage on the low potential side are generated, the resistance values for generating the reference voltages in the half tone become substantially "1", as shown in FIG. 10. Therefore, the resistance circuits for generating the reference voltages in the half tone can be shared.

**[0079]** In the case of removing each four grayscales in the sections 80 and 82 in which the reference voltages

close to the power supply voltage on the high potential side and the power supply voltage on the low potential side are generated, the grayscale characteristics of the first and second liquid crystal panels shown in FIG. 8 are almost the same in the half tone, as shown in FIG. 11.

**[0080]** Therefore, a reference voltage generation circuit capable of performing gamma correction optimum for different types of liquid crystal panels can be provided by adjusting only the resistance values of several (four, for example) resistance circuits disposed close to the power supply voltages on the high and low potential sides of the resistance ladder. Specifically, it is unnecessary to variably control all the resistance circuits of the resistance ladder.

**[0081]** As shown in FIG. 6, in the reference voltage generation circuit 48, only the first and third resistance ladder circuits 70 and 74 are variably controlled, and the second resistance ladder circuit 72 for generating the reference voltages in the half tone is formed only of the resistance circuits having a fixed resistance value.

**[0082]** If the resistance value ratio of each resistance circuit of the second resistance ladder circuit 72 is two or less, a general-purpose reference voltage generation circuit can be provided without impairing the grayscale characteristics.

**[0083]** FIG. 12 shows an example of the signal driver IC 30 to which the reference voltage generation circuit 48 is applied.

**[0084]** The reference voltage generation circuit 48 is shared to drive M signal electrodes in this figure. Specifically, the DACs 50-1 to 50-M and the voltage follower circuits 52-1 to 52-M are respectively provided for the M signal electrodes  $S_1$  to  $S_M$ .

**[0085]** The DACs 50-1 to 50-M select one of the multi-valued reference voltages based on the grayscale data corresponding to each signal electrode. The multi-valued reference voltages supplied to the DACs 50-1 to 50-M are generated by the reference voltage generation circuit 48. The reference voltage generation circuit 48 includes the first to third resistance ladder circuits 70, 72, and 74. In the first and third resistance ladder circuits 70 and 74, the resistance values of the resistance circuits of the resistance ladder are variably controlled by the command from the user or the variable control signal input through the external input terminal. This configuration makes the effect of preventing an increase in circuit scale by the reference voltage generation circuit 48 significant, even if the number of signal electrodes is increased.

### 3.2 Variable control of resistance ladder

**[0086]** In the grayscale characteristics shown in FIG. 7, a region between given transmittances  $tr_1$  and  $tr_2$  in which the change in transmittance is large is referred to as an active region, and regions other than the active region are referred to as first and second non-active regions. The active region is a region in which the voltage corresponding to the grayscale value in the half tone is

applied. The first non-active region is a region in which the transmittance is changed when a higher voltage is applied to the liquid crystal, and the second non-active region is a region in which the transmittance is changed when a lower voltage is applied to the liquid crystal.

**[0087]** Assuming that an applied voltage for obtaining the transmittance  $tr_2$  is  $VA$ , an applied voltage for obtaining the transmittance  $tr_1$  is  $VA'$  in a given liquid crystal panel ( $VA = VA_1$ , and  $VA' = VA_1'$  in the first liquid crystal panel,  $VA = VA_2$ , and  $VA' = VA_2'$  in the second liquid crystal panel), and the difference in voltage between the first and the second power supply voltages is  $VDIF$ , the resistance values of the variable resistance circuits which are variably controlled in the first and third resistance ladder circuits 70 and 74 are increased as  $(VDIF-VA)/VDIF$  becomes larger, and the resistance values of the variable resistance circuits which are variably controlled in the first and third resistance ladder circuits 70 and 74 are decreased as  $(VDIF-VA)/VDIF$  becomes smaller.

**[0088]** For example, the resistance values of the variable resistance circuits which are variably controlled in the first and third resistance ladder circuits 70 and 74 in the first liquid crystal panel shown in FIG. 8 are set larger than the resistance values of the variable resistance circuits which are variably controlled in the first and third resistance ladder circuits 70 and 74 in the second liquid crystal panel.

**[0089]** It is preferable that the resistance value ratio shown in FIG. 9 be two or less in the active region. Specifically, it is preferable that the second resistance ladder circuit 72 be formed so that the resistance circuits having a resistance value ratio of two or less are connected in series. The variable resistance circuits of the first and third resistance ladder circuits 70 and 74 which generate the reference voltages corresponding to grayscale values on both ends are variably controlled as described above.

**[0090]** For example, the signal driver IC 30 including the reference voltage generation circuit 48 shown in FIG. 6 can be widely used irrespective of the display panel to be driven by variably controlling the variable resistance circuits as described above.

### 3.3 Configuration of resistance ladder

**[0091]** The first and third resistance ladder circuits 70 and 74 which are variably controlled in the reference voltage generation circuit 48 as described above may have the following configuration. The following description illustrates the first resistance ladder circuit 70, but the third resistance ladder circuit 74 may have the same configuration as the first resistance ladder circuit 70.

#### 3.3.1 First example

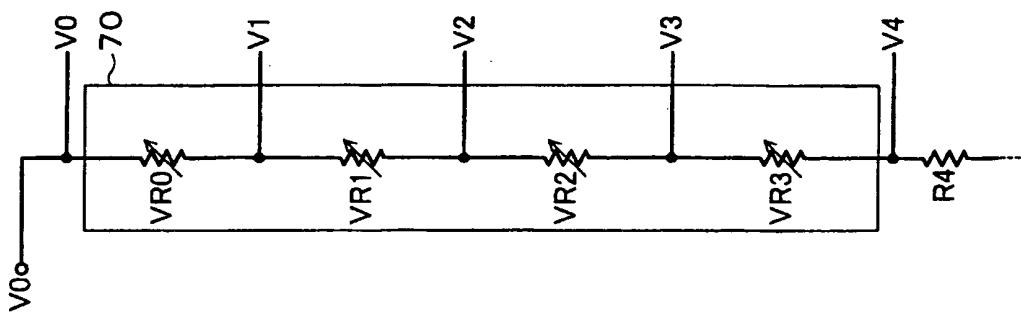

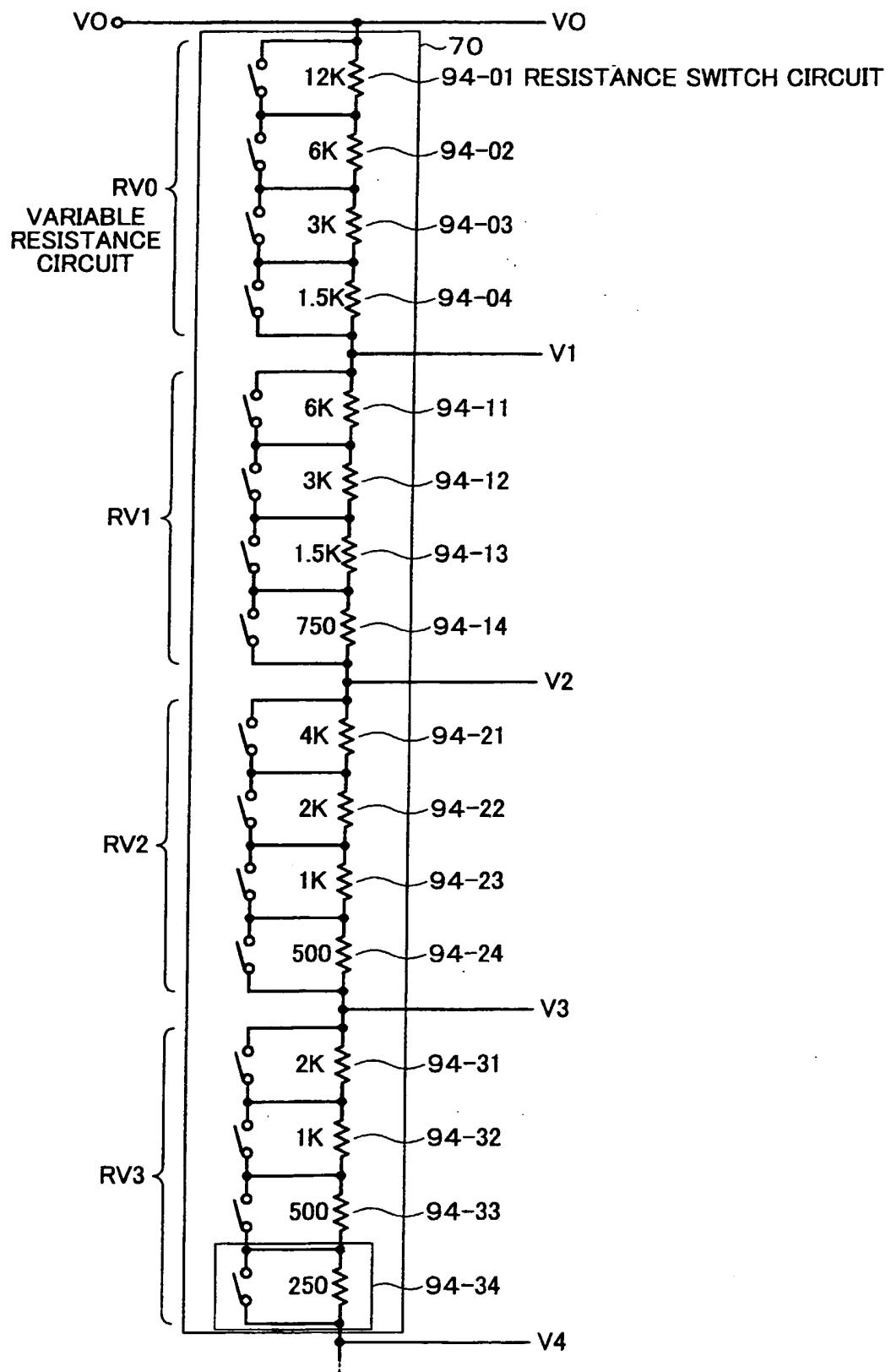

**[0092]** A first example of the first resistance ladder circuit 70 is shown in FIGS. 13A to 13C.

**[0093]** In this example, the first resistance ladder circuit

70 includes variable resistance circuits VR0 to VR3 connected in series, as shown in FIG. 13A.

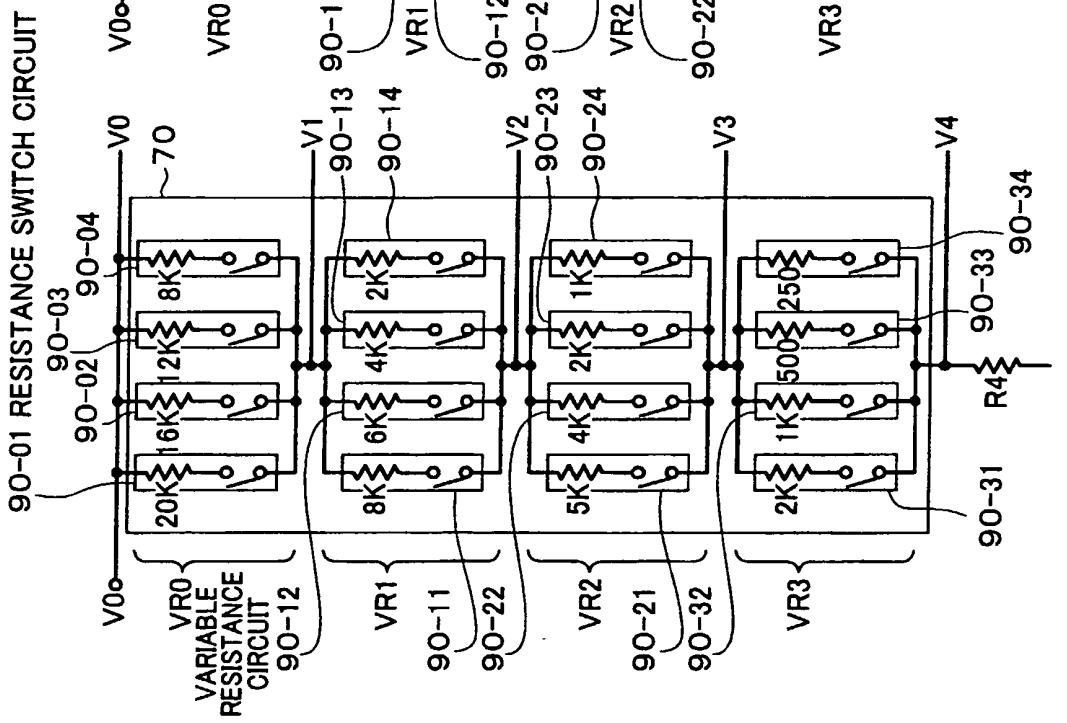

**[0094]** As shown in FIG. 13B, the variable resistance circuit may be formed by parallelly connecting resistance switch circuits in which a switch circuit (switch element) and a resistance circuit (resistance element) are connected in series. In this case, the resistance switch circuits connected in parallel are controlled so that at least one of the switch circuits is turned ON based on the command or the variable control signal input through the external input terminal.

**[0095]** For example, the variable resistance circuit VR0 may be formed by connecting resistance switch circuits 90-01 to 90-04 in parallel. The variable resistance circuit VR1 may be formed by connecting resistance switch circuits 90-11 to 90-14 in parallel. The variable resistance circuit VR2 may be formed by connecting resistance switch circuits 90-21 to 90-24 in parallel. The variable resistance circuit VR3 may be formed by connecting resistance switch circuits 90-31 to 90-34 in parallel.

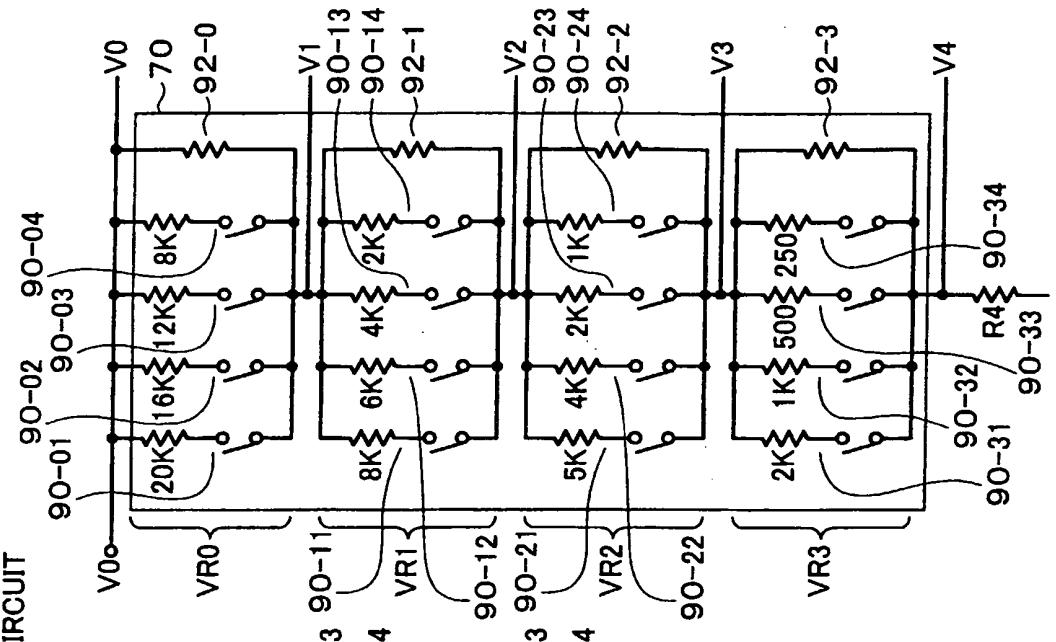

**[0096]** As shown in FIG. 13C, a resistance circuit may be further connected in parallel with the resistance switch circuits which are connected in parallel in the variable resistance circuit.

**[0097]** For example, the variable resistance circuit VR0 may be formed by connecting a resistance circuit 92-0 in parallel with the resistance switch circuits 90-01 to 90-04. The variable resistance circuit VR1 may be formed by connecting a resistance circuit 92-1 in parallel with the resistance switch circuits 90-11 to 90-14. The variable resistance circuit VR2 may be formed by connecting a resistance circuit 92-2 in parallel with the resistance switch circuits 90-21 to 90-24. The variable resistance circuit VR3 may be formed by connecting a resistance circuit 92-3 in parallel with the resistance switch circuits 90-31 to 90-34.

**[0098]** In this case, it is unnecessary to control the resistance switch circuits connected in parallel so that at least one of the switch circuits is turned ON. This eliminates the need to avoid a state in which the switch circuits are erroneously set in an open state, or to provide a circuit for avoiding such a state, whereby the configuration or control is simplified.

**[0099]** In this configuration, the switch circuit of each resistance switch circuit is ON-OFF controlled based on the command or the variable control signal input through the external input terminal.

### 3.3.2 Second example

**[0100]** A second example of the first resistance ladder circuit 70 is shown in FIG. 14.

**[0101]** In this example, the first resistance ladder circuit 70 includes the variable resistance circuits VR0 to VR3 connected in series similarly to FIG. 13A.

**[0102]** The variable resistance circuit may be formed by connecting resistance switch circuits in series in which

a resistance circuit and a switch circuit are connected in parallel, as shown in FIG. 14. In this case, the switch element of the resistance switch circuit is ON-OFF controlled based on the command or the variable control signal input through the external input terminal.

**[0103]** For example, the variable resistance circuit VR0 may be formed by connecting resistance switch circuits 94-01 to 94-04 in series. The variable resistance circuit VR1 may be formed by connecting resistance switch circuits 94-11 to 94-14 in series. The variable resistance circuit VR2 may be formed by connecting resistance switch circuits 94-21 to 94-24 in series. The variable resistance circuit VR3 may be formed by connecting resistance switch circuits 94-31 to 94-34 in series.

**[0104]** In this configuration, the switch circuit of each resistance switch circuit is ON-OFF controlled based on the command or the variable control signal input through the external input terminal.

### 3.3.3 Third example

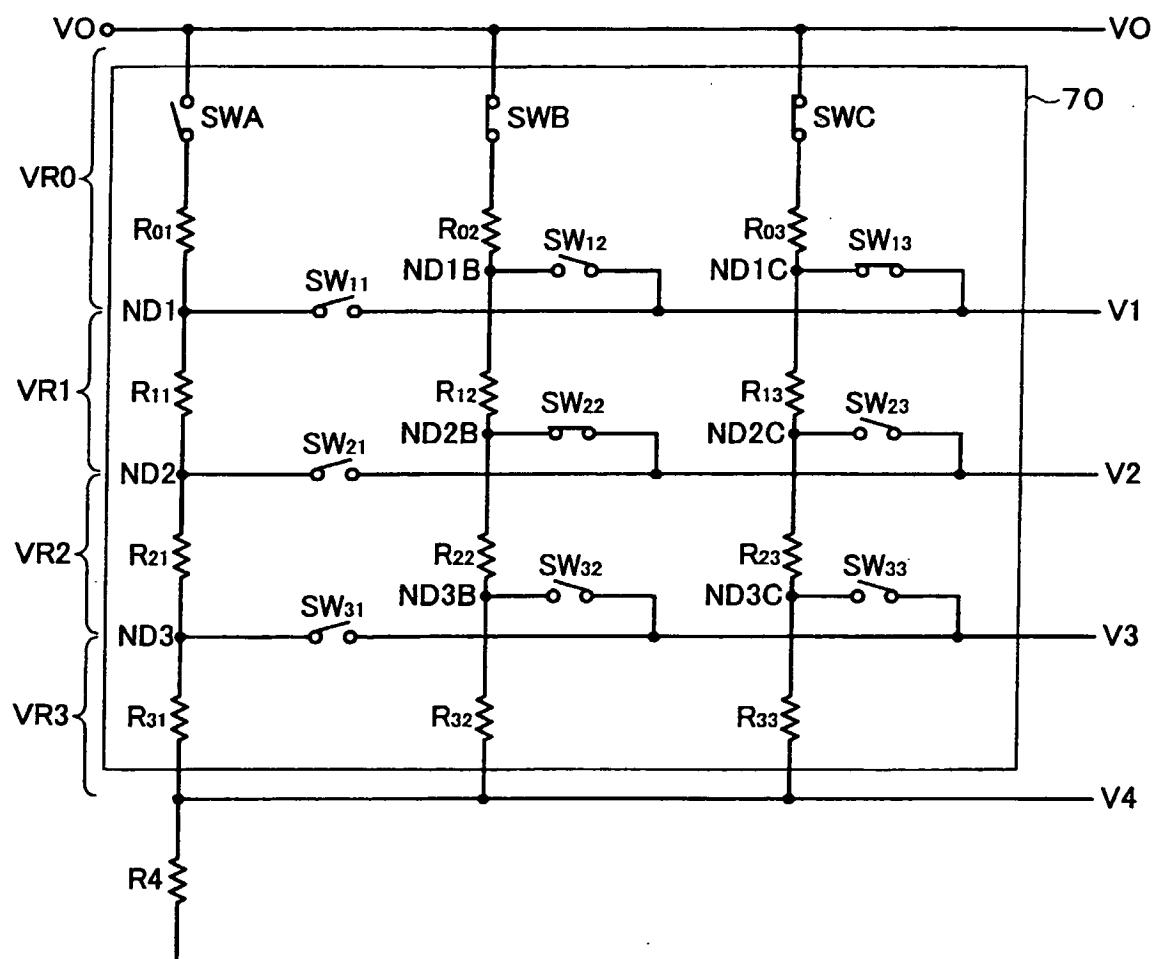

**[0105]** A third example of the first resistance ladder circuit 70 is shown in FIG. 15.

**[0106]** In this example, the first resistance ladder circuit 70 includes the variable resistance circuits VR0 to VR3 connected in series similarly to FIG. 13A.

**[0107]** In the variable resistance circuit VR0, a switch circuit (switch element) SWA and a resistance circuit  $R_{01}$  connected in series are inserted between the first power supply line and the divided node ND1. A switch circuit  $SW_{11}$  is inserted between the divided node ND1 and the output node of the reference voltage V1. In the variable resistance circuit VR0, a switch circuit SWB and a resistance circuit  $R_{02}$  connected in series are inserted between the first power supply line and a node ND1B. A switch circuit  $SW_{12}$  is inserted between the node ND1B and the output node of the reference voltage V1. In the variable resistance circuit VR0, a switch circuit SWC and a resistance circuit  $R_{03}$  connected in series are inserted between the first power supply line and a node ND1C. A switch circuit  $SW_{13}$  is inserted between the node ND1C and the output node of the reference voltage V1.

**[0108]** In the variable resistance circuit VR1, a resistance circuit  $R_{11}$  is inserted between the divided node ND1 and the divided node ND2. A switch circuit  $SW_{21}$  is inserted between the divided node ND2 and the output node of the reference voltage V2. In the variable resistance circuit VR1, a resistance circuit  $R_{12}$  is inserted between the node ND1B and a node ND2B. A switch circuit  $SW_{22}$  is inserted between the node ND2B and the output node of the reference voltage V2. In the variable resistance circuit VR1, a resistance circuit  $R_{13}$  is inserted between the node ND1C and a node ND2C. A switch circuit  $SW_{23}$  is inserted between the node ND2C and the output node of the reference voltage V2.

**[0109]** In the variable resistance circuit VR2, a resistance circuit  $R_{21}$  is inserted between the divided node ND2 and the divided node ND3. A switch circuit  $SW_{31}$  is

inserted between the divided node ND3 and the output node of the reference voltage V3. In the variable resistance circuit VR2, a resistance circuit  $R_{22}$  is inserted between the node ND2B and a node ND3B. A switch circuit  $SW_{32}$  is inserted between the node ND3B and the output node of the reference voltage V3. In the variable resistance circuit VR2, a resistance circuit  $R_{23}$  is inserted between the node ND2C and a node ND3C. A switch circuit  $SW_{33}$  is inserted between the node ND3C and the output node of the reference voltage V3.

**[0110]** In the variable resistance circuit VR3, a resistance circuit  $R_{31}$  is inserted between the divided node ND3 and the output node of the reference voltage V4. In the variable resistance circuit VR3, a resistance circuit  $R_{32}$  is inserted between the node ND3B and the output node of the reference voltage V4. In the variable resistance circuit VR3, a resistance circuit  $R_{33}$  is inserted between the node ND3C and the output node of the reference voltage V4.

**[0111]** In this configuration, the switch circuits SWA, SWB, SWC,  $SW_{11}$  to  $SW_{13}$ ,  $SW_{21}$  to  $SW_{23}$ , and  $SW_{31}$  to  $SW_{33}$  are ON-OFF controlled based on the command or the variable control signal input through the external input terminal.

**[0112]** In the case where the switch circuits SWB, SWC,  $SW_{13}$ , and  $SW_{22}$  are turned ON and the switch circuits SWA,  $SW_{11}$ ,  $SW_{12}$ ,  $SW_{21}$ , and  $SW_{23}$  are turned OFF, a voltage obtained by dropping the power supply voltage V0 through the resistance circuit  $R_{03}$  is output as the reference voltage V1, and a voltage obtained by dropping the power supply voltage V0 through the resistance circuit  $R_{03}$  and the resistance circuit  $R_{12}$  is output as the reference voltage V2.

**[0113]** As described above, since the settable resistance value of the variable resistance circuit of the resistance ladder can be further diversified, a signal driver IC including a reference voltage generation circuit which can be optimized for various display panels can be provided.

### 3.3.4 Fourth example

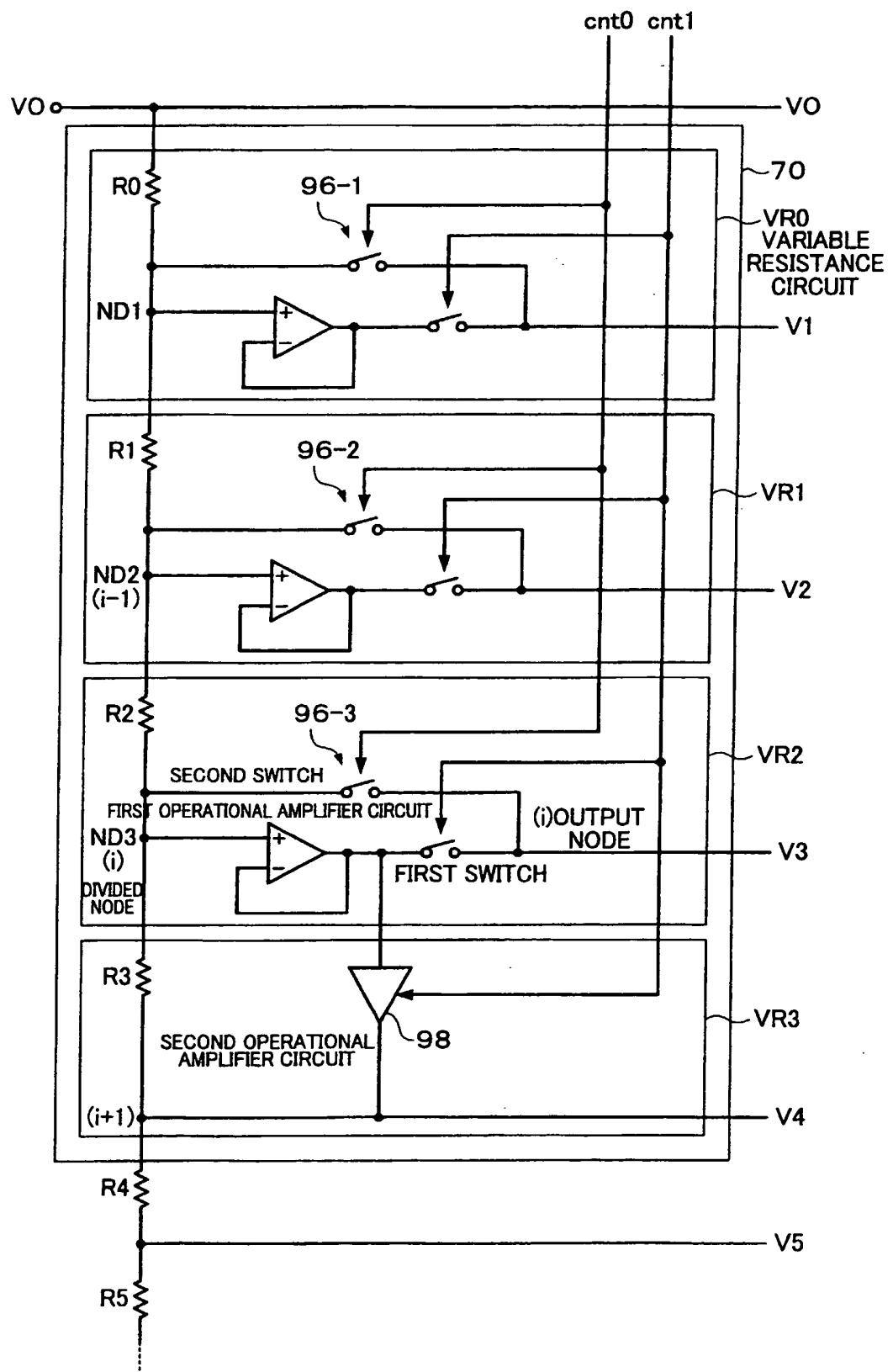

**[0114]** A fourth example of the first resistance ladder circuit 70 according to one embodiment of the present invention is shown in FIG. 16.

**[0115]** In this example, the first resistance ladder circuit 70 includes the variable resistance circuits VR0 to VR3 connected in series similarly to FIG. 13A.

**[0116]** In the variable resistance circuit VR0, a resistance circuit R0 is inserted between the first power supply line and the divided node ND1. In the variable resistance circuit VR0, a voltage follower circuit 96-1 is inserted between the divided node ND1 and the output node of the reference voltage V1. The voltage follower circuit 96-1 has the same configuration as the voltage follower circuit shown in FIG. 4. Each switch circuit of the voltage follower circuit 96-1 is ON-OFF controlled by control signals cnt0 and cnt1.

**[0117]** In the variable resistance circuit VR1, a resist-

ance circuit R1 is inserted between the divided node ND1 and the divided node ND2. In the variable resistance circuit VR1, a voltage follower circuit 96-2 is inserted between the divided node ND2 and the output node of the reference voltage V2. The voltage follower circuit 96-2 has the same configuration as the voltage follower circuit shown in FIG. 4. Each switch circuit of the voltage follower circuit 96-2 is ON-OFF controlled by the control signals cnt0 and cnt1.

**[0118]** In the variable resistance circuit VR2, a resistance circuit R2 is inserted between the divided node ND2 and the divided node ND3. In the variable resistance circuit VR2, a voltage follower circuit 96-3 is inserted between the divided node ND3 and the output node of the reference voltage V3. The voltage follower circuit 96-3 has the same configuration as the voltage follower circuit shown in FIG. 4. Each switch circuit of the voltage follower circuit 96-3 is ON-OFF controlled by the control signals cnt0 and cnt1.

**[0119]** In the variable resistance circuit VR3, a resistance circuit R3 is inserted between the divided node ND3 and the output node of the reference voltage V4. In the variable resistance circuit VR3, an operational amplifier circuit 98 with an offset is inserted between an output terminal of a voltage follower connected operational amplifier of the voltage follower circuit 96-3 and the output node of the reference voltage V4. The operation of the operational amplifier circuit 98 is controlled by the control signal cnt1 (operating current is controlled by the control signal cnt1).

**[0120]** Specifically, a resistance element (resistance circuit R2, for example) is inserted between the i-th ( $1 \leq i \leq R$ , i is an integer) divided node (divided node ND3, for example) for generating the i-th reference voltage (reference voltage V3, for example) and the (i-1)th divided node (divided node ND2, for example) for generating the (i-1)th reference voltage, among the first to R-th reference voltages (R is an integer equal to or larger than 2). The first resistance ladder circuit 70 includes a first voltage follower connected operational amplifier (operational amplifier of the voltage follower circuit 96-3, for example) of which an input terminal is connected with the i-th divided node, a first switch element (first switch element of the voltage follower circuit 96-3, for example) inserted

between the output node of the i-th reference voltage and the output of the first operational amplifier circuit, and a second switch element (second switch element of the voltage follower circuit 96-3, for example) inserted between the output node of the i-th reference voltage and the i-th divided node.

**[0121]** In the case where the resistance value of the resistance circuit inserted between the (i+1)th divided node and the (i+2)th divided node is fixed, a second operational amplifier circuit (operational amplifier circuit 98, for example) is inserted between the output of the first operational amplifier (operational amplifier of the voltage follower circuit 96-3, for example) and the output node of the (i+1)th reference voltage.

**[0122]** FIG. 17 shows an example of the control timing of the first resistance ladder circuit 70 shown in FIG. 16. **[0123]** In the resistance circuit VR0, the logic levels of the control signals cnt0 and cnt1 are changed between the former period (first given period of drive period) t1 and the latter period t2 of the select period (drive period) specified by the latch pulse signal LP, for example. Specifically, when the logic level of the control signal cnt0 becomes "L" and the logic level of the control signal cnt1 becomes "H" in the former period t1, the voltage follower connected operational amplifier drives the output node of the reference voltage V1. When the logic level of the control signal cnt0 becomes "H" and the logic level of the control signal cnt1 becomes "L" in the latter period t2, the divided node ND1 is short-circuited with the output node of the reference voltage V4. Therefore, impedance transformation is performed by the voltage follower connected operational amplifier and the output node of the reference voltage V1 is driven in the former period t1 of the select period t. In the latter period t2, the voltage of the output node of the reference voltage V1 is determined through the resistance circuit R0.

**[0124]** Specifically, the drive voltage Vout can be raised at high speed by the voltage follower connected operational amplifier having high drive capability in the former period t1 necessary for charging the liquid crystal capacitance, interconnect capacitance, and the like, and the drive voltage can be output by the resistance circuit R0 in the latter period t2 in which high drive capability is unnecessary, as shown in FIG. 17. Therefore, since the impedance transformation can be performed by the voltage follower circuit, effects the same as in the first to third examples can be obtained.

**[0125]** Since the operating current steadily flows through the operational amplifiers of the voltage follower circuits 96-1 to 96-3 during operation, it is preferable to limit or terminate the operating current in the latter period t2 of the select period t.

**[0126]** In the variable resistance circuit VR3, the reference voltage V3 to which an offset voltage is added by the operational amplifier circuit 98 is output as the reference voltage V4 in the former period t1 of the select period t.

**[0127]** It is preferable to limit or terminate the operating current of the operational amplifier circuit 98 in the latter period t2 of the select period t.

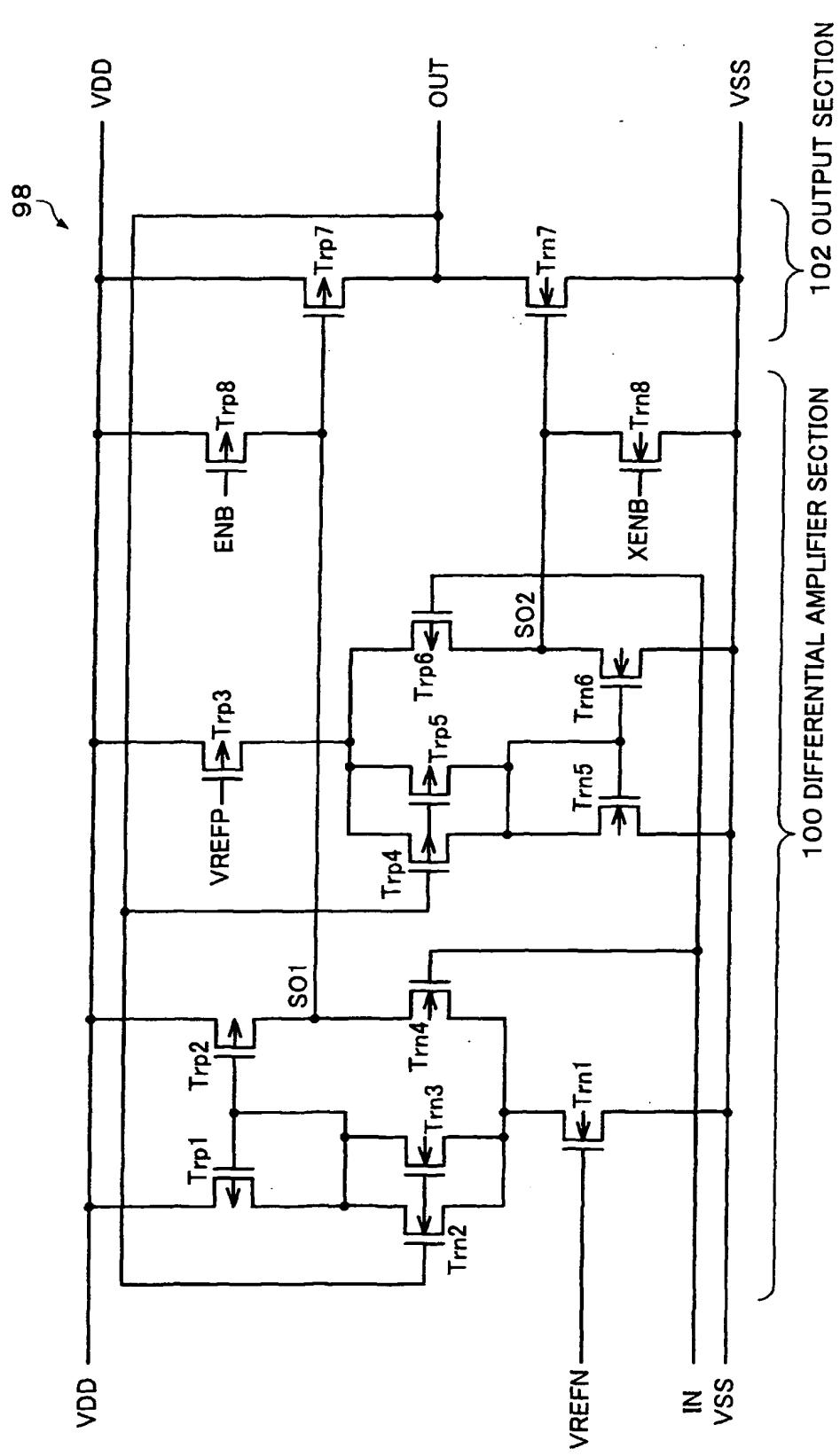

**[0128]** FIG. 18 is a detailed circuit diagram showing an example of the operational amplifier circuit 98.

**[0129]** The operational amplifier circuit 98 includes a differential amplifier section 100 and an output section 102.

**[0130]** The differential amplifier section 100 includes first and second differential amplifier sections 104 and 106.

**[0131]** The first differential amplifier section 104 utilizes current flowing between a drain and a source of an n-type MOS transistor Trn1 (n-type MOS transistor Trnx (x is an integer) is hereinafter abbreviated as "transistor

Trnx") to which a reference signal VREFN is applied at a gate electrode as a current source. The current source is connected with source terminals of transistors Trn2 to Trn4. An output signal OUT of the operational amplifier circuit 98 is applied to gate electrodes of the transistors Trn2 and Trn3. An input signal IN is applied to a gate electrode of the transistor Trn4.

**[0132]** The drain terminals of the transistors Trn2 to Trn4 are connected with drain terminals of p-type MOS transistors Trp1 (p-type MOS transistor Trpy (y is an integer) is hereinafter abbreviated as "transistor Trpy") and Trp2 having a current mirror structure. Gate electrodes of the transistors Trp1 and Trp2 are connected with drain terminals of the transistors Trn2 and Trn3.

**[0133]** A differential output signal SO1 is output from the drain terminal of the transistor Trp2.

**[0134]** The second differential amplifier section 106 utilizes current flowing between a drain and a source of a transistor Trp3 to which a reference signal VREFP is applied at a gate electrode as a current source. The current source is connected with source terminals of transistors Trp4 to Trp6. The output signal OUT of the operational amplifier circuit 98 is applied to gate electrodes of the transistors Trp4 and Trp5. The input signal IN is applied to a gate electrode of the transistor Trp6.

**[0135]** The drain terminals of the transistors Trp4 to Trp6 are connected with drain terminals of transistors Trn5 and Trn6 having a current mirror structure. Gate electrodes of the transistors Trn5 and Trn6 are connected with the drain terminals of the transistors Trp4 and Trp5.

**[0136]** A differential output signal SO2 is output from the drain terminal of the transistor Trn6.

**[0137]** The output section 102 includes transistors Trp7 and Trn7 connected in series between the power supply voltage VDD and the ground power supply voltage VSS. The differential output signal SO1 is applied to a gate electrode of the transistor Trp7. The differential output signal SO2 is applied to a gate electrode of the transistor Trn7. The output signal OUT is output from drain terminals of the transistors Trp7 and Trn7.

**[0138]** The gate electrode of the transistor Trp7 is connected with a drain terminal of a transistor Trp8. A source terminal of the transistor Trp8 is connected with the power supply voltage VDD. An enable signal ENB is applied to a gate electrode of the transistor Trp8. The gate electrode of the transistor Trn7 is connected with a drain terminal of a transistor Trn8. A source terminal of the transistor Trn8 is connected with the ground power supply voltage VSS. An inverted enable signal XENB is applied to a gate electrode of the transistor Trn8.

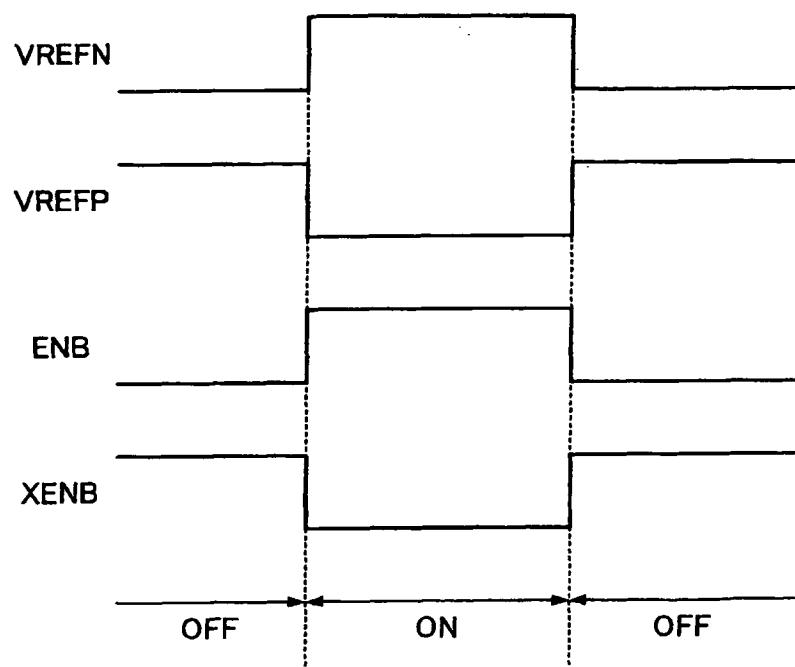

**[0139]** The operational amplifier circuit 98 having the above-described configuration makes the reference signals VREFN and VREFP, the enable signal ENB, and the inverted enable signal XENB operate, and outputs the output signal OUT which is a voltage obtained by adding an offset voltage to the input signal IN, as shown in FIG. 19. The control signal cnt1 shown in FIGS. 16 and 17 may be used as the reference signal VREFN and

the enable signal ENB. A signal obtained by inverting the control signal cnt1 may be used as the reference signal VREFP and the inverted enable signal XENB.

**[0140]** In the first differential amplifier section 104, when the logic level of the reference signal VREFN becomes "H" and the transistor Trn1 starts to be operated as the current source, voltage corresponding to the difference in drive capability between the transistors Trn2 and Trn3 and the transistor Trn4 which make a differential pair is output as the differential output signal SO1 based on the output signal OUT and the input signal IN. At this time, since the transistor Trp8 is turned OFF, the differential output signal SO1 is applied to the gate electrode of the transistor Trp7. In the second differential amplifier section 106, the differential output signal SO2 is applied to the gate electrode of the transistor Trn7. As a result, the output section 102 outputs the output signal OUT which is the input signal IN to which an offset corresponding to the drive capability of the transistors which make up the differential pair is added.

**[0141]** In the first differential amplifier section 104, since the amplification operation cannot be performed when the logic level of the reference signal VREFN becomes "L" and the transistor Trn1 is turned OFF, the power supply voltage VDD is applied to the gate electrode of the transistor Trp7 through the transistor Trp8. In the second differential amplifier section 106, the ground power supply voltage VSS is applied to the gate electrode of the transistor Trn7 through the transistor Trn8. As a result, the output section 102 puts its output in a high impedance state. Since the current flowing through the current source can be limited or terminated by the reference signals VREFN and VREFP, the operating current can be prevented from flowing in a period in which the operation is unnecessary.

**[0142]** This enables the operational amplifier circuit 98 to add an offset with high accuracy. Therefore, in the fourth example, the resistance value of the variable resistance circuit can be variably controlled by using impedance transformation by the voltage follower circuit, whereby a general-purpose reference voltage generation circuit irrespective of the type of display panel can be formed.

**[0143]** In the fourth example, the variable resistance circuits VR0 to VR3 are variably controlled by the control signals cnt0 and cnt1. However, the present invention is not limited thereto. The variable resistance circuits VR0 to VR3 may be variably controlled by different control signals.

#### 4. Others

**[0144]** The above embodiments are described taking the liquid crystal device including a liquid crystal panel using TFTs as an example, but the present invention is not limited thereto. The reference voltage generated by the reference voltage generation circuit 48 may be changed into current by a given current conversion circuit

and supplied to a current driven type element. This enables the present invention to be applied to a signal driver IC which drives an organic EL panel including organic EL elements provided corresponding to pixels specified by signal electrodes and scanning electrodes, for example.

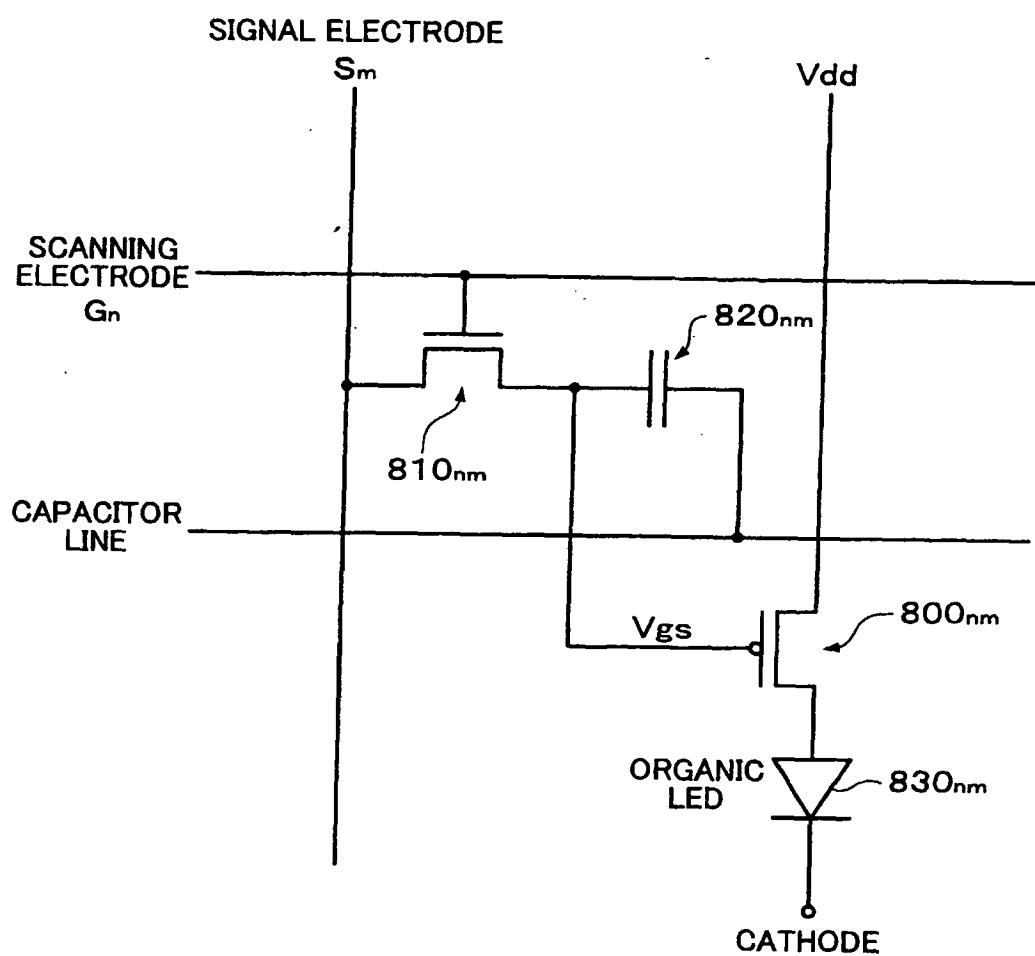

**[0145]** FIG. 20 is a circuit diagram showing an example of a two-transistor pixel circuit in an organic EL panel driven by such a signal driver IC.

**[0146]** The organic EL panel includes a drive TFT 800<sub>nm</sub>, a switch TFT 810<sub>nm</sub>, a storage capacitor 820<sub>nm</sub>, and an organic LED 830<sub>nm</sub> at an intersection point between a signal electrode S<sub>m</sub> and a scanning electrode G<sub>n</sub>. The drive TFT 800<sub>nm</sub> is formed by a p-type transistor.

**[0147]** The drive TFT 800<sub>nm</sub> and the organic LED 830<sub>nm</sub> are connected in series with a power supply line.

**[0148]** The switch TFT 810<sub>nm</sub> is inserted between a gate electrode of the drive TFT 800<sub>nm</sub> and the signal electrode S<sub>m</sub>. A gate electrode of the switch TFT 810<sub>nm</sub> is connected with the scanning electrode G<sub>n</sub>.

**[0149]** The storage capacitor 820<sub>nm</sub> is inserted between the gate electrode of the drive TFT 800<sub>nm</sub> and a capacitor line.

**[0150]** In this organic EL element, when the scanning electrode G<sub>n</sub> is driven and the switch TFT 810<sub>nm</sub> is turned ON, voltage of the signal electrode S<sub>m</sub> is written into the storage capacitor 820<sub>nm</sub> and applied to the gate electrode of the drive TFT 800<sub>nm</sub>. A gate voltage V<sub>gs</sub> of the drive TFT 800<sub>nm</sub> is determined depending on the voltage of the signal electrode S<sub>m</sub>, whereby current flowing through the drive TFT 800<sub>nm</sub> is determined. Since the drive TFT 800<sub>nm</sub> and the organic LED 830<sub>nm</sub> are connected in series, the current flowing through the drive TFT 800<sub>nm</sub> flows through the organic LED 830<sub>nm</sub>.

**[0151]** Therefore, if the gate voltage V<sub>gs</sub> corresponding to the voltage of the signal electrode S<sub>m</sub> is held by the storage capacitor 820<sub>nm</sub>, for example, in the case where current corresponding to the gate voltage V<sub>gs</sub> is caused to flow through the organic LED 830<sub>nm</sub> in one frame period, a pixel which continues to shine during the frame can be realized.

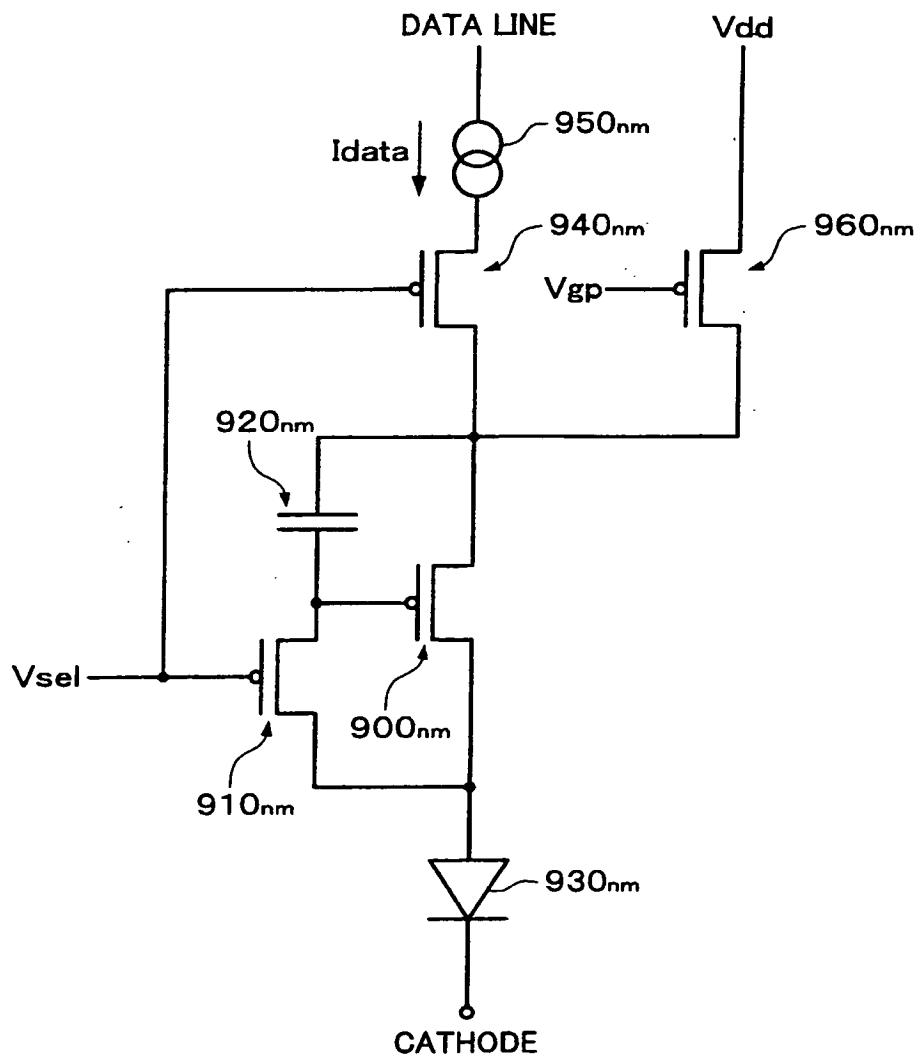

**[0152]** FIG. 21A shows an example of a four-transistor pixel circuit in an organic EL panel driven by the signal driver IC. FIG. 21B shows an example of the display control timing of the pixel circuit.

**[0153]** The organic EL panel includes a drive TFT 900<sub>nm</sub>, a switch TFT 910<sub>nm</sub>, a storage capacitor 920<sub>nm</sub>, and an organic LED 930<sub>nm</sub>.

**[0154]** The features differing from the two-transistor pixel circuit shown in FIG. 20 are that a constant current I<sub>data</sub> from a constant current source 950<sub>nm</sub> is supplied to the pixel through a p-type TFT 940<sub>nm</sub> as a switch element instead of a constant voltage, and the storage capacitor 920<sub>nm</sub> and the drive TFT 900<sub>nm</sub> are connected with the power supply line through a p-type TFT 960<sub>nm</sub> as a switch element.

**[0155]** In this organic EL element, the power supply line is disconnected by allowing the p-type TFT 960<sub>nm</sub> to

be turned OFF by a gate voltage  $V_{gp}$ , and the constant current  $I_{data}$  from the constant current source  $950_{nm}$  is caused to flow through the drive TFT  $900_{nm}$  by allowing the p-type TFT  $940_{nm}$  and the switch TFT  $910_{nm}$  to be turned ON by a gate voltage  $V_{sel}$ . 5

**[0156]** Voltage corresponding to the constant current  $I_{data}$  is held by the storage capacitor  $920_{nm}$  until the current flowing through the drive TFT  $900_{nm}$  becomes stable.

**[0157]** The p-type TFT  $940_{nm}$  and the switch TFT  $910_{nm}$  are turned OFF by the gate voltage  $V_{sel}$  and the p-type TFT  $960_{nm}$  is turned ON by the gate voltage  $V_{gp}$ , whereby the power supply line is electrically connected with the drive TFT  $900_{nm}$  and the organic LED  $930_{nm}$ . Current almost equal to or in an amount corresponding to the constant current  $I_{data}$  is supplied to the organic LED  $930_{nm}$  by the voltage held by the storage capacitor  $920_{nm}$ . 10

**[0158]** In this organic EL element, the scanning electrode may be used as an electrode to which the gate voltage  $V_{sel}$  is applied, and the signal electrode may be used as a data line. 20

**[0159]** The organic LED may have a structure in which a light-emitting layer is provided on a transparent anode (ITO) and a metal cathode is provided on the light-emitting layer, or a structure in which a light-emitting layer, a light-transmitting cathode, and a transparent seal are provided on a metal anode. The element structure of the organic LED is not limited. 25

**[0160]** A signal driver IC which is widely used for organic EL panels can be provided by forming a signal driver IC which drives an organic EL panel including organic EL elements as described above. 30

**[0161]** The present invention is not limited to the above-described embodiments. Various modifications can be made within the scope of the invention as defined by the appended claims. 35

#### Claims 40

1. A reference voltage generation circuit (48) for generating a plurality of reference voltages for generating a gamma-corrected grayscale value based on grayscale data, the reference voltage generation circuit comprising: 45

a first resistance ladder circuit (70) having at least one variable resistance circuit in which the resistance value between its both ends is variable; and 50

a second resistance ladder circuit (72) in which a plurality of resistance circuits each having a fixed resistance value are connected in series; wherein 55

the first and second resistance ladder circuits are connected in series between a first and a second power supply line to which a first and a

second power supply voltage are respectively supplied;

a third resistance ladder circuit (74) having at least one variable resistance circuit, in which the resistance value between its both ends is variable, is connected in series with said first and second resistance ladder circuits between said first and second power supply lines such that the second resistance ladder circuit is connected between the first and the third one, the resistance values of the variable resistance circuits (VR0 - VR3) in the first and the third resistance ladder circuit are arranged to be variably controlled according to a given command setting or a given variable control signal (cnt0, cnt1), and

the variable resistance circuit in at least one of the first and third resistance ladder circuits includes a resistance element (R0-R3) inserted between the i-th divided node for generating the i-th reference voltage and the (i-1)th divided node for outputting the (i-1)th reference voltage among first to R-th reference voltages, where i is a positive integer, R is an integer equal to or larger than 2 and  $1 \leq i \leq R$ ;

#### characterized in that

said variable resistance circuit in at least one of the first and third resistance ladder circuits further includes a first operational amplifier circuit, which is voltage-follower connected and an input of which is connected to the i-th divided node; a first switch element inserted between an output node of the i-th reference voltage and the output of the first operational amplifier circuit; and

a second switch element (96-1 - 96-3) inserted between the output node of the i-th reference voltage and the i-th divided node, wherein the first switch element is in the ON state and the second switch element is in the OFF state during a first period (t1) in a given drive period (select period t) and the first switch element is in the OFF state and the second switch element is in the ON state during a second period (t2) in the drive period (select period t).

the second driving period immediately following the first driving period; and wherein in the case where the resistance value of the resistance circuit inserted between the (i+1)th divided node and the (i+2)th divided node is fixed, the first resistance circuit (70) further comprises a second operational amplifier circuit (98) inserted between the output of the first operational amplifier circuit and an output node of the (i+1)th reference voltage, the second operational amplifier circuit being adapted to output a voltage obtained by applying a given offset voltage to the i-th reference voltage in the first period; and

wherein the operating current of the first operational amplifier circuit and that of the second operational amplifier circuit are limited or terminated in the second period of the drive period.

5

2. The circuit as defined in claim 1, wherein at least one of the first and third resistance ladder circuits (70,74) has at least two of the variable resistance circuits which are connected to each other in series.

10

3. A display driver circuit (30) comprising:

the circuits as defined in claim 1;

a voltage select circuit (50) which selects a voltage from among multi-valued reference voltages generated by the circuit, based on grayscale data; and

a signal electrode driver circuit (52) which drives a signal electrode by using the voltage selected by the voltage select circuit.

15

20

4. The display driver circuit as defined in claim 3, further comprising an external input terminal through which the variable control signal is input.

25

5. A display device (10) comprising:

a plurality of signal electrodes (Sm);

a plurality of scanning electrodes (Gn) which intersect the signal electrodes;

pixels specified by the signal electrodes and the scanning electrodes;

the display driver circuit (30) as defined in claim 3 or 4 which drives the signal electrodes; and

a scanning electrode driver circuit (32) which drives the scanning electrodes.

30

35

### Patentansprüche

40

1. Referenzspannungs-Erzeugungsschaltung (48) zum Erzeugen einer Mehrzahl Referenzspannungen, um einen Gamma-korrigierten Grauskalenwert auf Basis von Grauskalendaten zu erzeugen, wobei die Referenzspannungs-Erzeugungsschaltung aufweist:

45

eine erste Widerstandsleiterschaltung (70), die mindestens eine variable Widerstandsschaltung enthält, bei der der Widerstandswert zwischen ihren beiden Enden variabel ist; und

eine zweite Widerstandsleiterschaltung (72), bei der eine Mehrzahl Widerstandsschaltungen mit jeweils einem festen Widerstandswert in Reihe geschaltet sind; wobei

die erste und die zweite Widerstandsleiterschaltung zwischen einer ersten und einer zweiten Spannungsversorgungsleitung, an die jeweils

50

55

eine erste und eine zweite Versorgungsspannung gelegt wird, in Reihe geschaltet sind; eine dritte Widerstandsleiterschaltung (74), die mindestens eine variable Widerstandsschaltung enthält, bei der der Widerstandswert zwischen ihren beiden Enden variabel ist, mit der ersten und der zweiten Widerstandsleiterschaltung zwischen der ersten und der zweiten Spannungsversorgungsleitung so in Reihe geschaltet ist, dass die zweite Widerstandsleiterschaltung zwischen die erste und die dritte geschaltet ist;

die Widerstandswerte der variablen Widerstandsschaltungen (VR0 bis VR3) der ersten und der dritten Widerstandsleiterschaltung gemäß einer gegebenen Befehlseinstellung oder einem gegebenen variablen Steuersignal (cnt0, cnt1) variabel steuerbar sind; und

die variable Widerstandsschaltung in mindestens einer der ersten und der dritten Widerstandsleiterschaltungen ein Widerstandselement (R0 bis R3) enthält, das zwischen dem i-ten Teilungsknoten zum Erzeugen der i-ten Referenzspannung und dem (i-1)-ten Teilungsknoten zum Ausgeben der (i-1)-ten Referenzspannung aus einer ersten bis R-ten Referenzspannung eingefügt ist, wobei i eine positive ganze Zahl, R eine ganze Zahl gleich oder größer als 2 ist und  $1 \leq i \leq R$ ;

**dadurch gekennzeichnet, dass**

die variable Widerstandsschaltung in mindestens einer der ersten und der dritten Widerstandsleiterschaltungen ferner eine erste Operationsverstärkerschaltung enthält, die als Spannungsfolger geschaltet ist, und die einen mit dem i-ten Teilungsknoten verbundenen Eingang aufweist;

ein erstes Schaltelement zwischen einem Ausgangsknoten der i-ten Referenzspannung und dem Ausgang der ersten Operationsverstärkerschaltung eingefügt ist; und

ein zweites Schaltelement (96-1 bis 96-3) zwischen dem Ausgangsknoten der i-ten Referenzspannung und dem i-ten Teilungsknoten eingefügt ist; wobei