(19)

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 1 274 068 A2

(12)

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

08.01.2003 Bulletin 2003/02

(51) Int Cl. 7: G09G 3/36

(21) Application number: 02014807.8

(22) Date of filing: 02.07.2002

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

IE IT LI LU MC NL PT SE SK TR

Designated Extension States:

AL LT LV MK RO SI

(30) Priority: 06.07.2001 JP 2001206987

(71) Applicant: NEC CORPORATION

Tokyo (JP)

(72) Inventors:

- Tsuchi, Hiroshi

Minato-ku, Tokyo (JP)

- Uchiyama, Yoshinori

Nakahara-ku, Kawasaki-shi, Kanagawa (JP)

(74) Representative: Glawe, Delfs, Moll & Partner

Patentanwälte

Postfach 26 01 62

80058 München (DE)

### (54) Driver circuit and liquid crystal display device

(57) Disclosed is a driver circuit, as well as a LCD device having the driver circuit, in which changeover between first and second buffer circuits the operating ranges of which extend to high- and low-potential power supply voltages can be performed reliably within the drive changeover range. The driver circuit includes first and second buffer circuits(13 and 14) having their input terminals connected in common with one input terminal(1) to which an input signal voltage(Vin) is input and having their output terminals connected in common with an output terminal(2), the first and second buffer circuits having operating ranges that extend to high- and low-potential power supply voltages, respectively; first and second storage units(3a and 3b) for storing respectively

positive- and negative-polarity reference data, which correspond to voltages within a range in which both of the first and second buffer circuits(13 and 14) are operable, with regard to each of a standard state and modulated state of a gamma characteristic; a selector(4) for selecting either of the storage units based upon a polarity signal, and selectively outputting reference data corresponding to the standard or modulated state based upon modulation information that specifies modulation; and a comparator(5) for comparing entered data and the reference data output from the selector. Activation and deactivation of the first and second buffer circuits(13 and 14) is controlled based upon an output signal from the comparator(5) and a control signal.

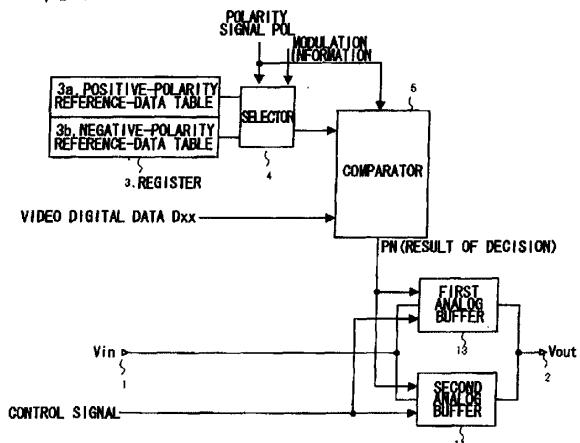

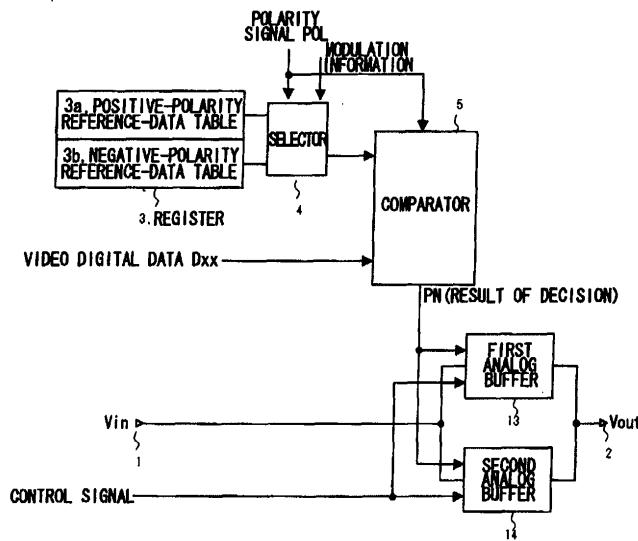

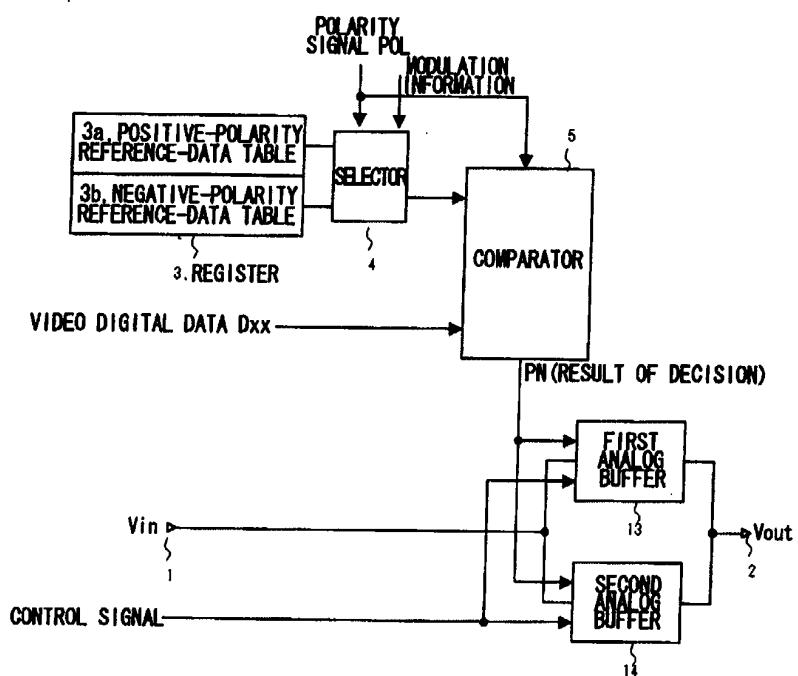

FIG. 1

**Description****FIELD OF THE INVENTION**

**[0001]** This invention relates to a driver circuit and, more particularly, to a driver circuit suited for driving a capacitative load.

**BACKGROUND OF THE INVENTION**

**[0002]** For technical publications related to the present invention, see

- (1) the reference "A New Low-Power Driver for Portable Devices," by H. Tsuchi, N. Ikeda and H. Hayama, SID 00 DIGEST pp. 146 - 149, and

- (2) the specification of Japanese Patent Kokai Publication JP-A-2000-33846.

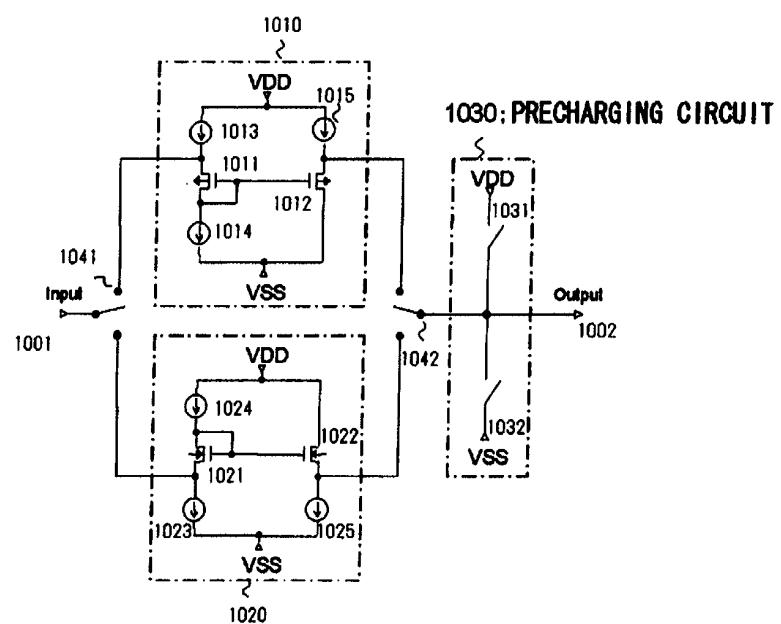

**[0003]** Fig. 24 is a diagram illustrating one example of a driver circuit for driving video digital data in a liquid crystal display device [see Figure 1 in reference (1)].

**[0004]** The buffer shown in Fig. 24 is such that even if a full-range output cannot be produced with an analog buffer alone, a full-range output is made possible by switching between two analog buffer circuits (referred to simply as "buffer circuits" below). The term "full-range output" refers to substantially the entire area of the range of power supply voltage of the driver circuit. As shown in Fig. 24, a first buffer circuit 1010 comprises a first changeover switch 1041 having a stationary end, which is connected to an input terminal 1001, and first and second switching terminals; a first constant-current source 1013 connected serially between the first switching terminal of the first changeover switch 1041 and a high-potential power supply VDD; a P-channel MOS transistor 1011 having a source, which is connected to the first terminal of the first changeover switch 1041, and a gate and drain that are tied together; a second constant-current source 1014 connected between the drain of the P-channel MOS transistor 1011 and a low-potential power supply VSS; a second changeover switch 1042 having a stationary end, which is connected to an output terminal 1002, and first and second switching terminals; a third constant-current source 1015 connected serially between the first switching terminal of the second changeover switch 1042 and the high-potential power supply VDD; and a P-channel MOS transistor 1012 having a source connected to the first terminal of the second changeover switch 1042, a gate connected to the gate of the P-channel MOS transistor 1011, and a drain connected to the low-potential power supply VSS.

**[0005]** A second buffer circuit 1020 comprises a fourth constant-current source 1023 connected between the low-potential power supply VSS and the second switching terminal of the first changeover switch 1041 whose fixed end is connected to the input terminal 1001; an N-

channel MOS transistor 1021 having a source, which is connected to the second terminal of the first changeover switch 1041, and a gate and drain that are tied together; a fifth constant-current source 1024 connected between the drain of the N-channel MOS transistor 1021 and the high-potential power supply VDD; a sixth constant-current source 1025 connected serially between the low-potential power supply VSS and the second switching terminal of the second changeover switch 1042 whose stationary end is connected to the output terminal 1002; and an N-channel MOS transistor 1022 having a source connected to the second terminal of the second changeover switch 1042, a gate connected to the gate of the N-channel MOS transistor 1021, and a drain connected to the high-potential power supply VDD.

**[0006]** The buffer further includes a precharging circuit 1030, which comprises a switch 1031 between the output terminal 1002 and the high-potential power supply VDD, and a switch 1032 between the output terminal

20 1002 and the low-potential power supply VSS, for pre-discharging and precharging the output terminal 1002.

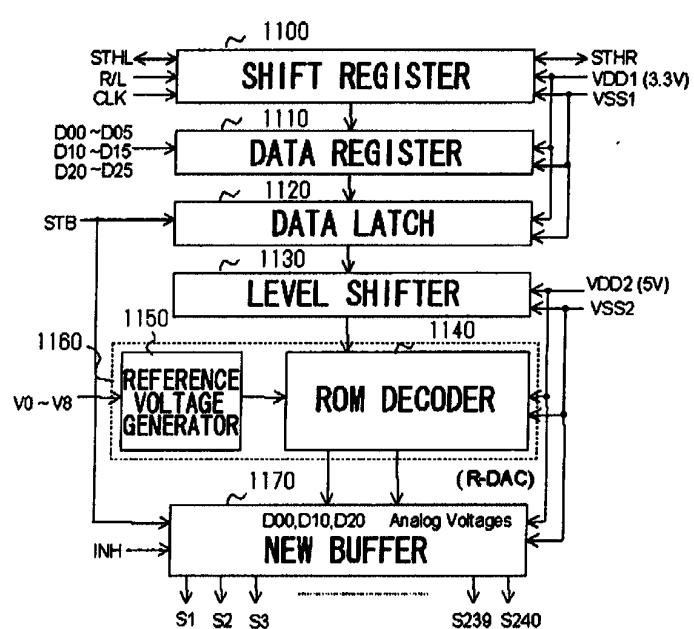

**[0007]** Fig. 25 illustrates the structure of a 6-bit digital-data driver [see Figure 3 in reference (1)]. The driver comprises a shift register 1100, a data register 1110, a latch 1120, a level shifter circuit 1130, an R-DAC 1160 (a reference-voltage generator 1150 and ROM decoder 1140), and the new buffer 1170. Analog voltage is supplied from the ROM decoder 1140 to the new buffer 1170, 1-bit data (D00, D10 and D20) of each 6-bit data set of R, G, B is supplied from the ROM decoder 1140 to the new buffer 1170, the precharging circuit 1030 supplies the data line with a suitable power supply voltage (VDD, VSS) based upon the single bit of data, and the switches 1041 and 1042 are selected to select the buffer circuit 1010 or 1020.

**[0008]** If the driver circuit shown in Fig. 24 is applied to a common-inversion drive liquid crystal display circuit (drive in which opposing-electrode voltage Vcom is inverted), little power is consumed. Such a driver circuit is ideal for driving the liquid crystal display device of a mobile terminal such as a cellular telephone terminal. Further, by using a driver circuit that produces a full-range output, power consumption can be reduced further by lowering the power supply voltage. The driver circuit of Fig. 24 is one which can produce a full-range output by switching between the first buffer circuit 1010 and second buffer circuit 1020.

**[0009]** The first buffer circuit 1010 and second buffer circuit 1020 have a limitation imposed upon their operating ranges owing to the threshold voltage Vth of their transistors. The changeover between the first buffer circuit 1010 and second buffer circuit 1020 must be performed in a voltage range (Vlim1 to Vlim2) in which both of these buffer circuits operate.

**[0010]** If conditions such as ambient temperature are fixed, switching between the first buffer circuit 1010 and second buffer circuit 1020 in accordance with video digital data can perform driving.

**[0011]** In order to facilitate an understanding of the present invention, changeover between the buffer circuits 1010 and 1020 in a case where the driver circuit shown in Fig. 24 is used to drive the data line of a liquid crystal display panel will be described with reference to Fig. 6.

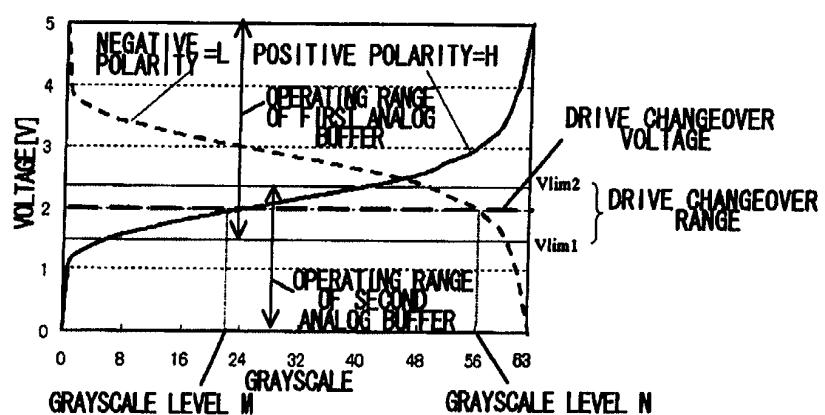

**[0012]** Fig. 6A is a diagram useful in describing a liquid crystal gamma characteristic (grayscale and signal voltage) and driver-circuit operating range (in the standard state) in common inversion drive (where potential  $V_{com}$  of opposing electrodes of a liquid crystal display device is switched between a high-potential voltage source and a low-potential voltage source). In Fig. 6A and in similar diagrams below, it will be assumed that the grayscale level has one-to-one correspondence with video digital data and that each grayscale is associated with two analog voltages corresponding to polarity. Fig. 6B is a diagram useful in describing a liquid crystal gamma characteristic and driver-circuit operating range (at the time of gamma modulation) in common inversion drive.

**[0013]** The operating range of a first analog buffer (which corresponds to the first buffer circuit 1010 of Fig. 24) is a voltage of 2 to 5V (which corresponds to grayscale 24 to 63 in positive polarity and grayscale 0 to 56 in negative polarity), the operating range of a second analog buffer (which corresponds to the second buffer circuit 1020 of Fig. 24) is a voltage of 0 to 3V (which corresponds to grayscale 0 to 56 in positive polarity and grayscale 24 to 63 in negative polarity), and the range in which drive changeover is possible is a voltage of 2 to 3V. Even if operation of the first and second analog buffers is changed over at level 32 using one higher-order bit of video digital data, for example, the voltage at changeover (the input voltage corresponding to the video digital data) for each of the positive and negative polarities is within the range in which the first and second analog buffers are capable of operating. As a result, an analog voltage corresponding to the grayscale level can be output.

**[0014]** Accordingly, in the case of the liquid crystal gamma characteristic (grayscale and voltage characteristic) of the kind shown in Fig. 6A, the first and second analog buffers can be changed over at grayscale level 32 by one higher-order bit of video digital data.

**[0015]** However, in the case of a gamma characteristic of the kind shown in Fig. 6B, the voltage of grayscale level 32 in the characteristic (solid line) of positive polarity is outside the operating range of the first analog buffer (which corresponds to the first buffer circuit 1010 of Fig. 24), and the voltage of grayscale level 32 in the characteristic (dashed line) of negative polarity is outside the operating range of the second analog buffer (which corresponds to the second buffer circuit 1020 of Fig. 24). This means that a changeover can no longer be performed at level 32. In other words, if the operating range of a first analog buffer is a voltage of 2 to 5V (grayscale levels 24 to 63), the operating range of a second

analog buffer is a voltage of 0 to 3V (grayscale levels 24 to 63) and the first and second buffers are changed over at level 32, then the output of the first analog buffer will be fixed to voltage  $V_{lim1}$  between levels 32 to 48 with regard to positive polarity and the output of the second analog buffer will be fixed to voltage  $V_{lim2}$  between levels 32 to 48 with regard to negative polarity. That is, even if a video digital signal corresponding to grayscale levels 32 to 48 is input between grayscale levels 32 to 48, an analog voltage corresponding to these levels will not be output and so-called a skip in grayscale levels occurs. It should be noted that Fig. 6B illustrates an example of a case where modulation of the gamma characteristic is approximately the same for both the positive and negative polarities. However, it is readily understood that modulation that differs depending upon polarity also may occur.

**[0016]** In order to support operation under a wide range of temperatures as in the case of a mobile terminal or the like, various types of modulation are required. For example, display quality is maintained by modulating the gamma characteristic with respect to temperature, and power consumption is suppressed by modulating power supply voltage. A problem that arises in such cases is that a fixed changeover between buffers conforming to some specific video digital data (some specific grayscale level) cannot be carried out.

#### SUMMARY OF THE DISCLOSURE

**[0017]** Accordingly, it is an object of the present invention to provide a driver circuit so adapted that a first buffer circuit, which has an operating range at least on the side of a high potential, and a second buffer circuit, which has an operating range at least on the side of a low potential, can be switched between reliably in a drive changeover range, as well as a liquid crystal display device having this driver circuit.

**[0018]** In accordance with one aspect of the present invention, the above and other objects are attained by providing a driver circuit for driving an output load, comprising: first and second buffer circuits having respective ones of input terminals connected in common with one input terminal provided for receiving an input signal voltage and respective ones of output terminals connected in common with an output terminal, said first buffer circuit having an operating range at least on the side of a high potential and said second buffer circuit having an operating range at least on the side of a low potential; a storage unit for storing reference data, which is for selecting changeover between operation of said first buffer circuit and operation of said second buffer circuit, the reference data corresponding to a voltage that is in a changeover range in which both the first and second buffer circuits are capable of operating; a comparator for comparing an entered data signal and the reference data; and means for controlling switching of said first buffer circuit and said second buffer circuit between ac-

tivation and deactivation thereof within a range in which both of said buffer circuits are capable of operating, based upon an output signal of said comparator, which indicates result of the comparison, and a control signal. [0019] A driver circuit, in accordance with another aspect of the present invention, comprises: first and second buffer circuits having respective ones of input terminals connected commonly to one input terminal provided for receiving an input signal voltage and respective ones of output terminals connected commonly to an output terminal, the first buffer circuit having an operating range that extends to a high-potential power supply voltage and the second buffer circuit having an operating range that extends to a low-potential power supply voltage; a storage unit for storing, in association with a relationship between entered digital data and signal voltage, reference data, which is for determining changeover between the first buffer circuit and the second buffer circuit, with regard to positive polarity defining a characteristic from the low-potential power supply voltage and negative polarity defining a characteristic from the high-potential power supply voltage, the reference data being of positive and negative polarity and corresponding to a voltage within a drive changeover range in which both the first and second buffer circuits are capable of operating; a selector, to which a polarity signal specifying polarity is input, for selecting the reference data of the positive or negative polarity based upon the value of the polarity signal; and a comparator for comparing entered digital data and the reference data output from the selector; wherein the first buffer circuit and the second buffer circuit have their activation and deactivation controlled based upon an output signal of the comparator, which indicates result of the comparison, and a control signal.

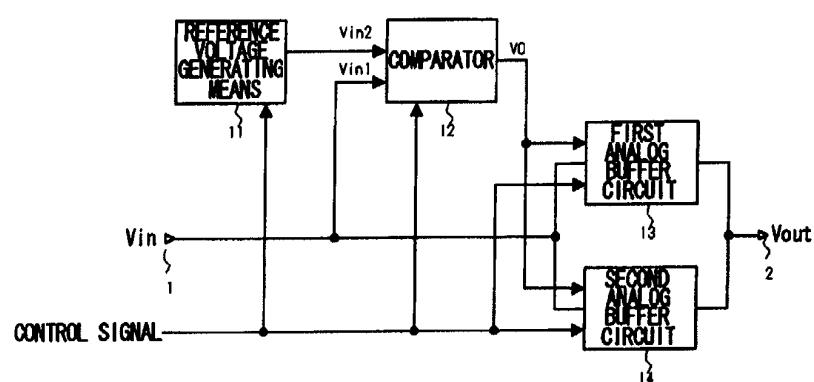

[0020] A driver circuit, in accordance with further aspect of the present invention, comprises: first and second buffer circuits having respective ones of input terminals connected commonly to one input terminal provided for receiving an input signal voltage and respective ones of output terminals connected commonly to an output terminal, the first buffer circuit having an operating range at least on the side of a high potential and the second buffer circuit having an operating range at least on the side of a low potential; reference voltage generating means for generating a reference voltage corresponding to a voltage range in which both the first and second buffer circuits are capable of operating; and a comparator for comparing the reference voltage, which is output from the reference voltage generating means, and the input signal voltage; wherein the first buffer circuit and the second buffer circuit have their activation and deactivation controlled based upon an output signal of the comparator, which indicates result of the comparison, and a control signal.

[0021] In a case where the control signal specifies activation, the first buffer circuit is placed in an operating state and the second buffer circuit is shut down if the

output signal of the comparator is a value indicating that the input signal voltage is equal to or greater than the reference voltage, and the second buffer circuit is placed in the operating state and the first buffer circuit is shut down if the output signal of the comparator is a value indicating that the input signal voltage is less than the reference voltage.

[0022] In accordance with a further aspect of the present invention, there is provided a liquid crystal display device, comprising: grayscale-level voltage generating means, which has a plurality of resistors connected serially between first and second reference voltages, for generating grayscale voltages from taps thereof; and a decoder circuit, to which a digital data signal is input, for selectively outputting a corresponding voltage from output voltages of the grayscale-level voltage generating means. The above-described driver circuit according to the present invention, which receives the outputs of the decoder circuit, drives a data line that constitutes an output load.

Still other objects and advantages of the present invention will become readily apparent to those skilled in this art from the following detailed description in conjunction with the accompanying drawings wherein only the preferred embodiments of the invention are shown and described, simply by way of illustration of the best mode contemplated of carrying out this invention. As will be realized, the invention is capable of other and different embodiments, and its several details are capable of modifications in various obvious respects, all without departing from the invention. Accordingly, the drawing and description are to be regarded as illustrative in nature, and not as restrictive.

### 35 BRIEF DESCRIPTION OF THE DRAWINGS

#### [0023]

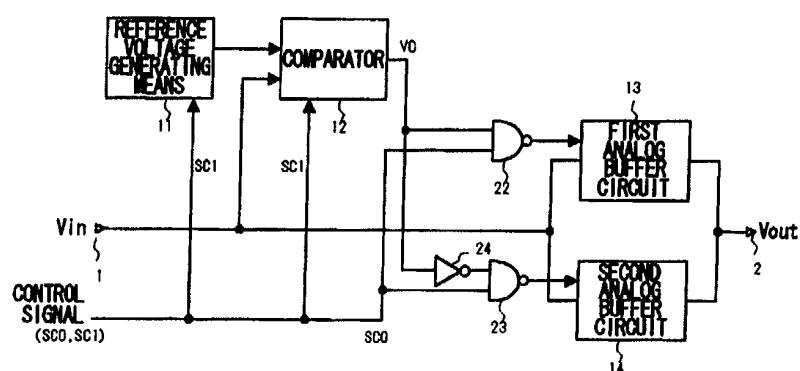

Fig. 1 is a block diagram illustrating the structure of a driver circuit according to an embodiment of the present invention;

Fig. 2 is a diagram useful in describing operation of the driver circuit according to the embodiment shown in Fig. 1;

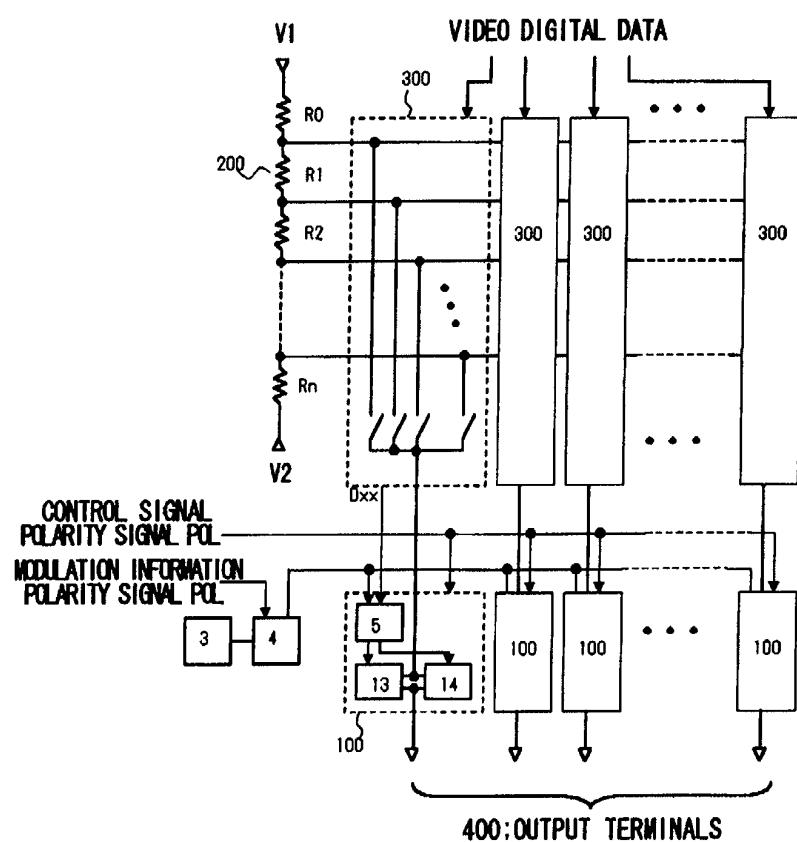

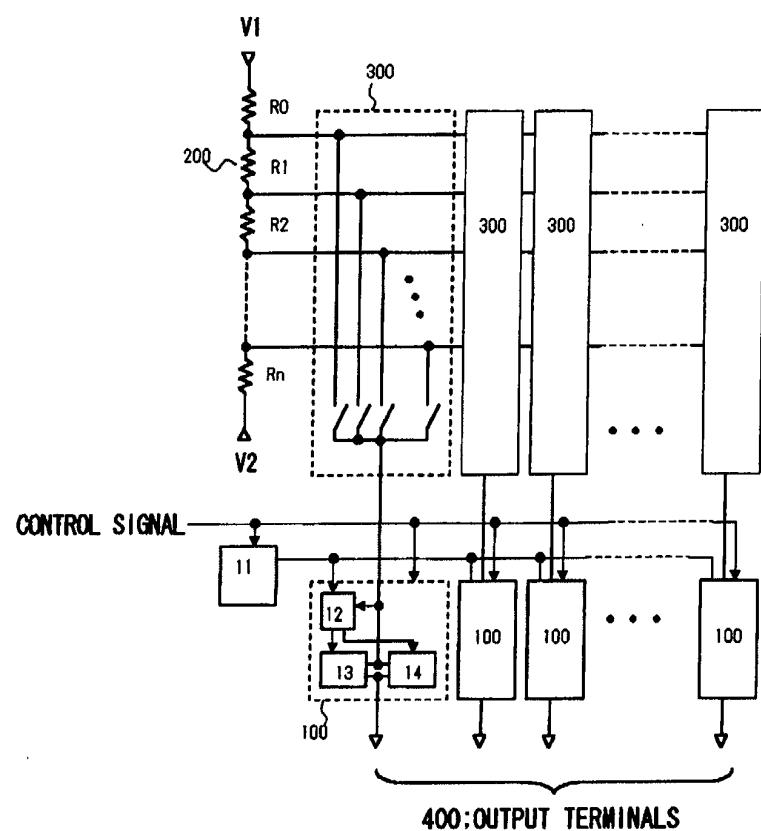

Fig. 3 is a diagram showing the structure of a multiple-output driver circuit having a plurality of the driver circuits according to the embodiment shown in Fig. 1;

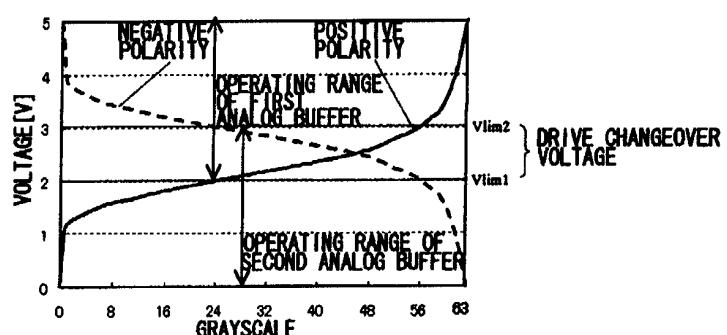

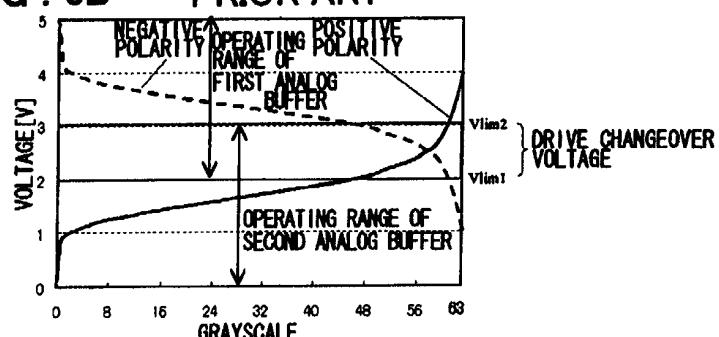

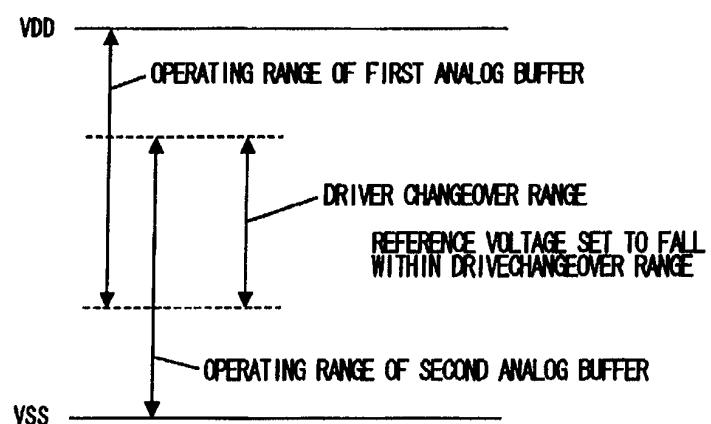

Fig. 4 is a diagram for describing drive changeover voltage in a driver circuit according to the present invention;

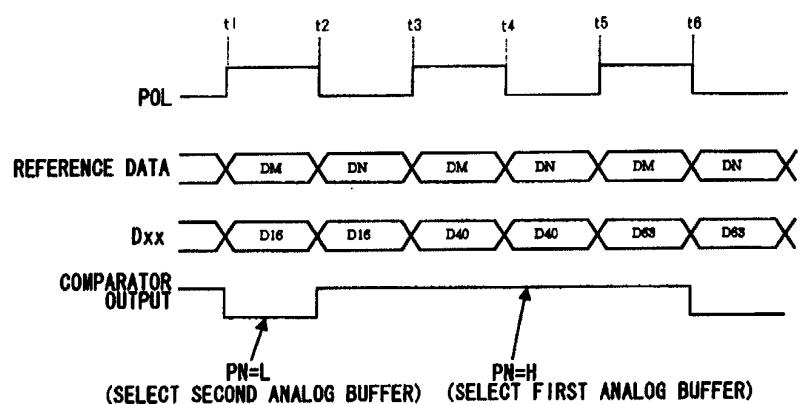

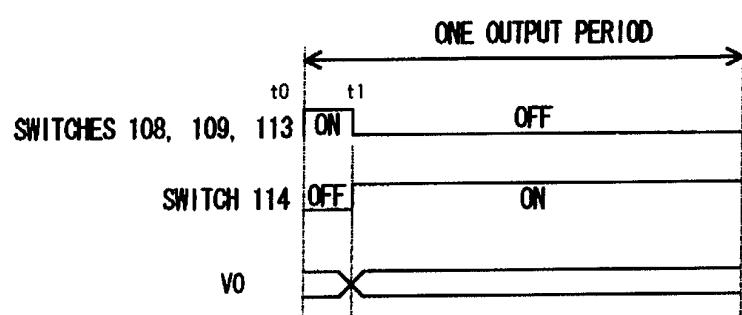

Fig. 5 is a timing chart for describing operation of the driver circuit according to the embodiment shown in Fig. 1;

Figs. 6A and 6B are diagrams useful in describing drive changeover voltage in a driver circuit according to the prior art serving as an example for comparative purposes, in which Fig. 6A is a diagram il-

lustrating a liquid crystal gamma characteristic and operating range (standard state) of a driver circuit in common inversion drive, and Fig. 6B is a diagram illustrating a liquid crystal gamma characteristic and operating range (modulated) of a driver circuit in common inversion drive;

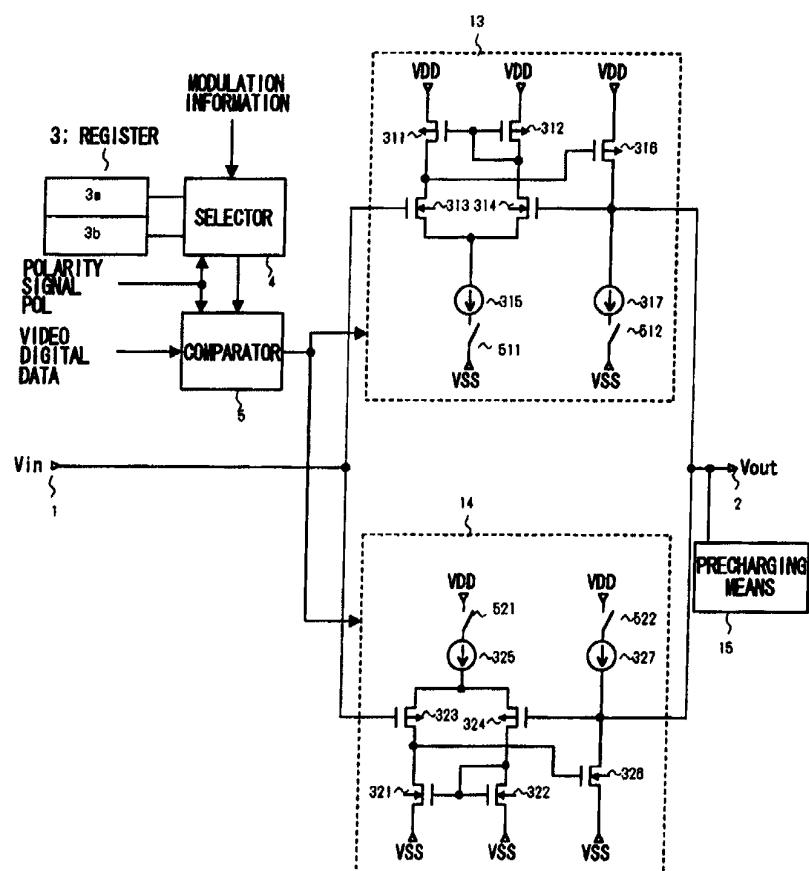

Fig. 7 is a block diagram illustrating the structure of a driver circuit according to another embodiment of the present invention;

Fig. 8 is a diagram useful in describing operation of the driver circuit according to the embodiment shown in Fig. 7;

Fig. 9 is a diagram showing the structure of a multiple-output driver circuit having a plurality of the driver circuits according to the embodiment shown in Fig. 7;

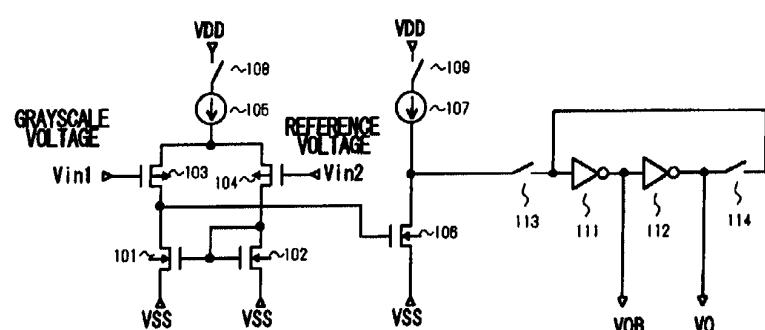

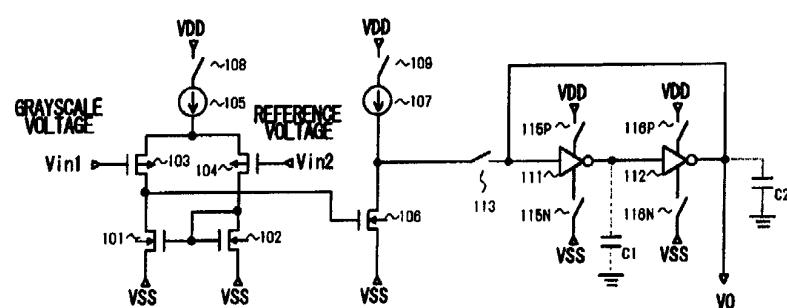

Fig. 10 is a diagram showing an example of the structure of a comparator in the driver circuit according to the embodiment shown in Fig. 7;

Fig. 11 is a diagram useful in describing operation of the comparator shown in Fig. 10;

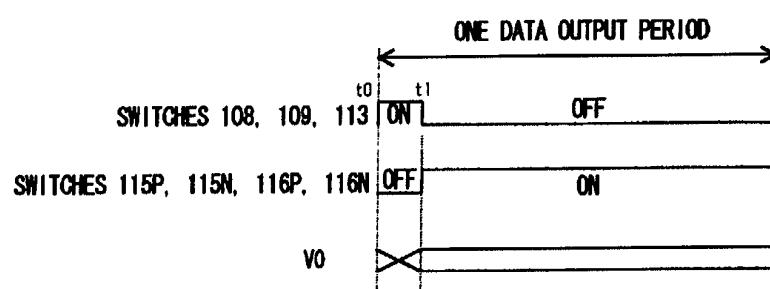

Fig. 12 is a diagram showing another example of the structure of a comparator in the driver circuit according to the embodiment shown in Fig. 7;

Fig. 13 is a diagram useful in describing operation of the comparator shown in Fig. 12;

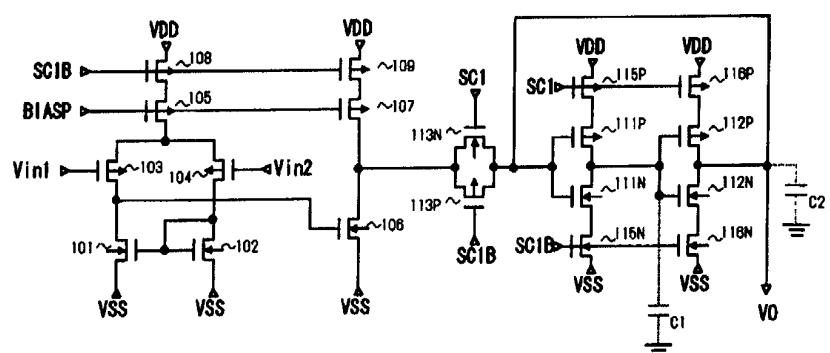

Fig. 14 is a diagram showing another example of the structure of a comparator in the driver circuit according to the embodiment shown in Fig. 12;

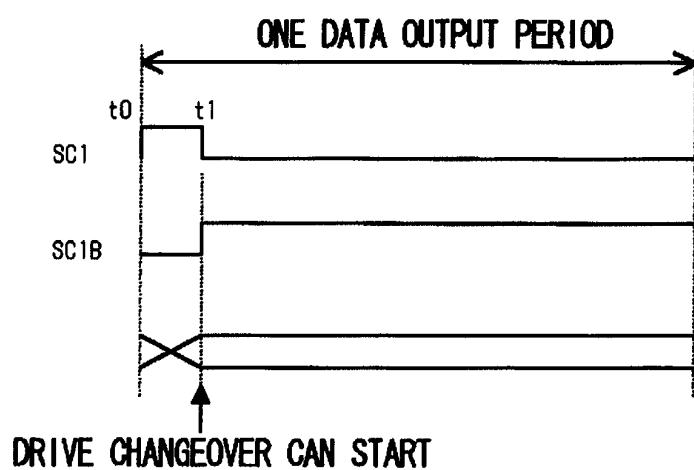

Fig. 15 is a diagram useful in describing operation of the comparator shown in Fig. 14;

Fig. 16A is a diagram showing another example of the structure of the driver circuit according to the embodiment shown in Fig. 7, and Fig. 16B is a diagram useful in describing the operation thereof;

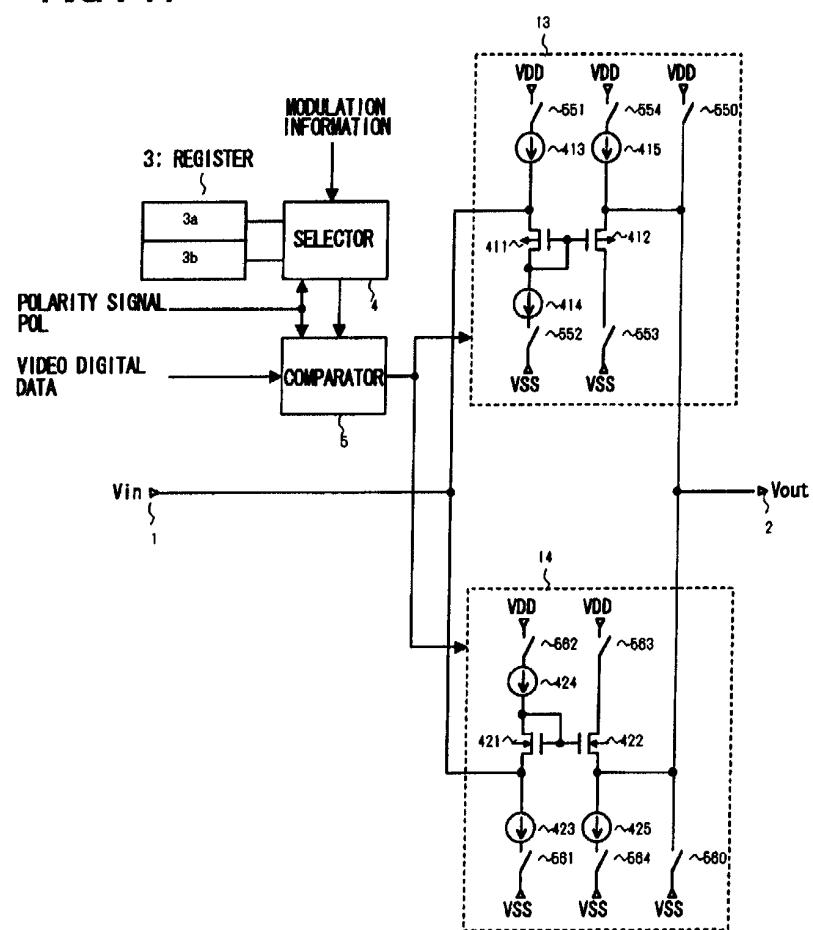

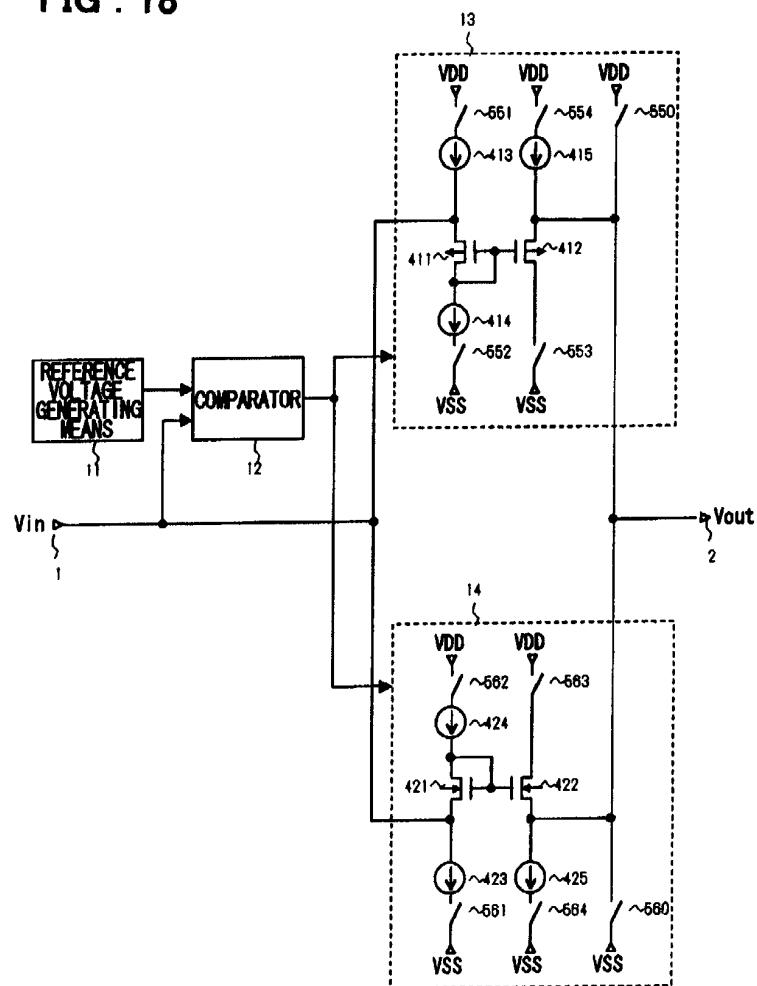

Fig. 17 is a diagram showing an example of the structure of an analog buffer circuit in the driver circuit according to the embodiment shown in Fig. 1; Fig. 18 is a diagram showing an example of the structure of an analog buffer circuit in the driver circuit according to the other embodiment shown in Fig. 7;

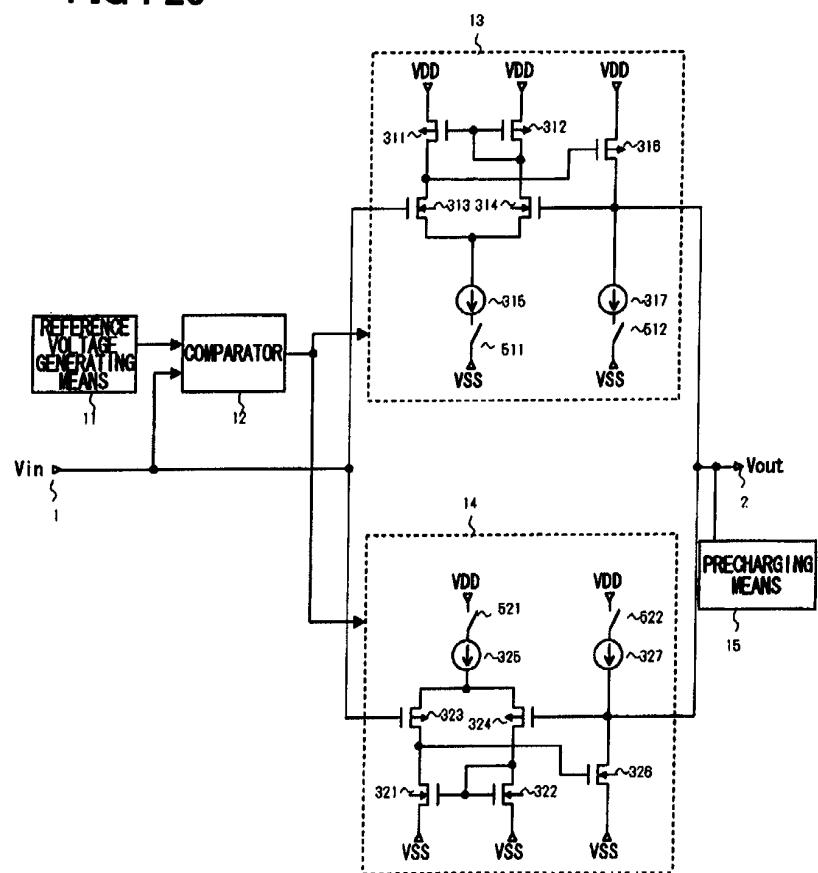

Fig. 19 is a diagram showing another example of the structure of an analog buffer circuit in the driver circuit according to the embodiment shown in Fig. 1; Fig. 20 is a diagram showing another example of the structure of an analog buffer circuit in the driver circuit according to the other embodiment shown in Fig. 7;

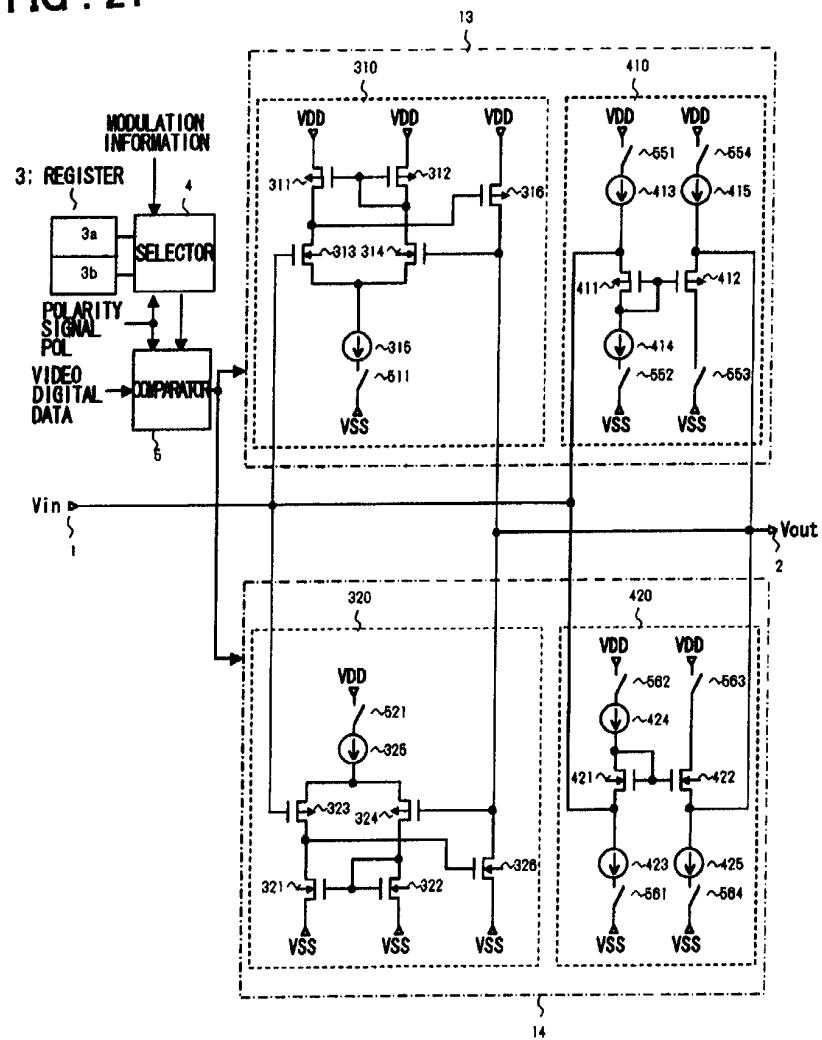

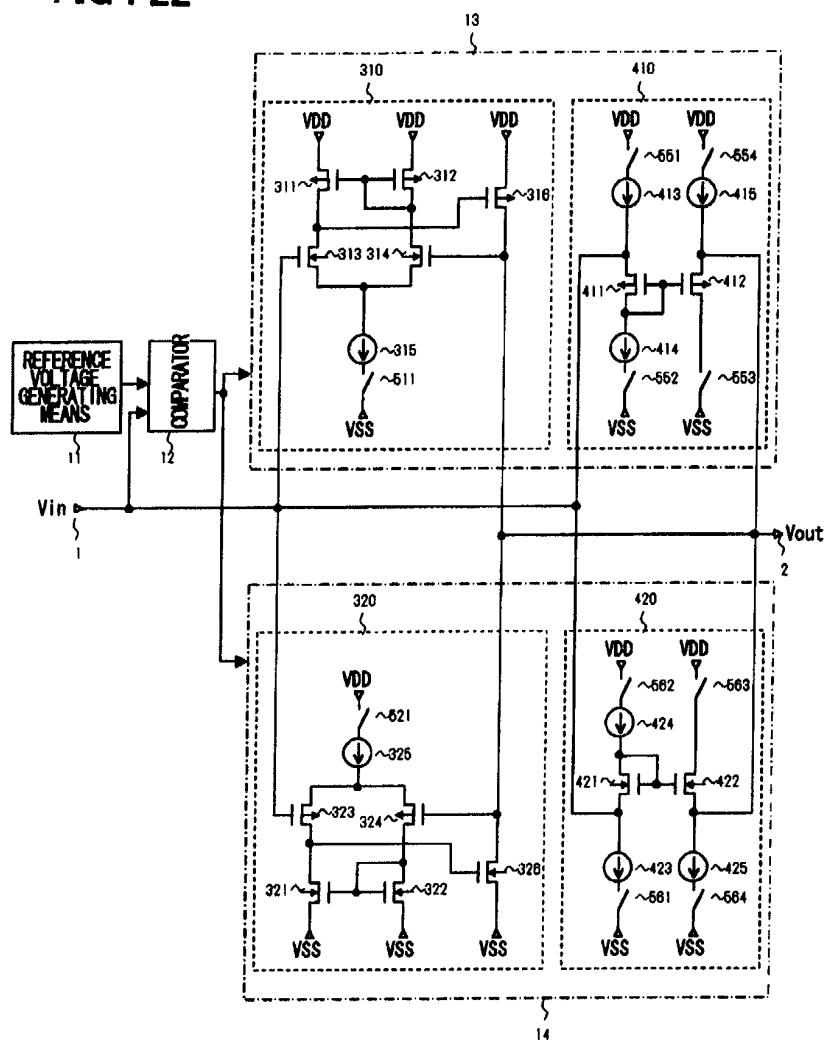

Fig. 21 is a diagram showing another example of the structure of an analog buffer circuit in the driver circuit according to the embodiment shown in Fig. 1; Fig. 22 is a diagram showing another example of the structure of an analog buffer circuit in the driver circuit according to the other embodiment shown in Fig. 7;

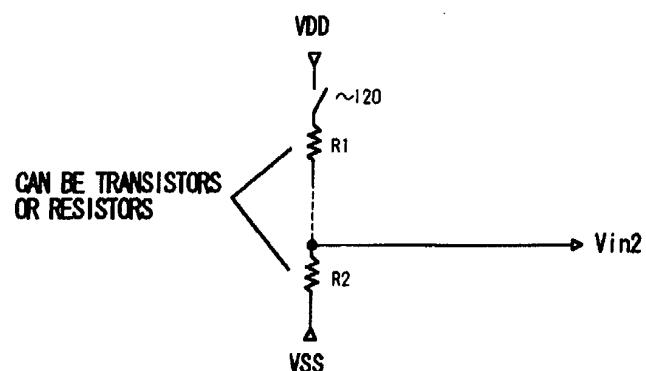

Figs. 23A and 23B are diagrams illustrating an example of the structure of reference voltage gener-

ating means in the driver circuit according to the embodiment shown in Fig. 7;

Fig. 24 is a diagram showing the structure of a buffer described in the reference "A New Low-Power Driver for Portable Devices," by H. Tsuchi, N. Ikeda and H. Hayama, SID 00 DIGEST pp. 146 - 149; and

Fig. 25 is a diagram showing the structure of a digital-data line driver described in the reference mentioned in Fig. 24.

## PREFERRED EMBODIMENTS OF THE INVENTION

**[0024]** Preferred embodiments of the present invention will be described below.

The present invention provides a driver circuit which, even if individual analog buffers thereof cannot produce a full-range output, is capable of providing a full-range output by switching between the two buffers. The optimum one of the two buffers is selected to make possible normal drive at all times even when various types of modulation are applied. Specifically, modulation of a variety of conditions is divided into a plurality of steps, and a table is provided for storing digital data, which corresponds to a grayscale level at which the two buffers are changed over, on a per-modulation-step basis. The data in the table is adopted as reference data and is compared with video digital data, and the optimum buffer is selected based upon the result of the comparison.

**[0025]** A voltage that resides in a range in which the two buffers are capable of being changed over is adopted as a reference voltage with regard to modulation of various conditions, a selected grayscale-level voltage is compared with the reference voltage, and the optimum one of the two buffers is selected in accordance with the result of the comparison.

**[0026]** In accordance with one embodiment of the present invention, there is provided a driver circuit for driving an output load such as a capacitative load, comprising: a first buffer circuit (13) and a second buffer circuit (14) having their input terminals connected commonly to one input terminal (1) to which an input signal voltage (Vin) is input and their output terminals connected commonly to an output terminal (2), the first buffer circuit (13) having an operating range at least on the side of a high potential and the second buffer circuit (14) having an operating range at least on the side of a low potential; a storage unit (3) for storing reference data, which is for determining changeover between the first and second buffer circuits (13 and 14), the reference data corresponding to a voltage within a range in which both the first and second buffer circuits (13 and 14) are capable of operating; and a comparator (5) for comparing an entered data signal and the reference data. The first and second buffer circuits (13 and 14) have their activation and deactivation controlled based upon an output signal (PN) of the comparator (5), which indicates result of the comparison, and a control signal.

**[0027]** Alternatively, in accordance with one preferred embodiment of the present invention, there is provided a driver circuit comprising: a first buffer circuit (13) and a second buffer circuit (14) having their input terminals connected commonly to one input terminal to which an input signal voltage is input and respective ones of output terminals connected commonly to an output terminal, the first buffer circuit (13) having an operating range that extends to a high-potential power supply voltage and the second buffer circuit (14) having an operating range that extends to a low-potential power supply voltage; a storage unit (3) for storing reference data, which corresponds to an input signal voltage within a range in which both the first and second buffer circuits are capable of operating, with regard to each of a standard state and modulation state of a characteristic relating to grayscale level and signal voltage; a selector (4) for selectively outputting reference data corresponding to the standard state or modulated state based upon modulation information that specifies modulation; and a comparator (5) for comparing entered data and the reference data output from the selector; and means for controlling activation and deactivation of the first buffer circuit and the second buffer circuit based upon an output signal of the comparator, which indicates result of the comparison, and a control signal.

**[0028]** The storage unit (3) stores reference data, which is for determining changeover between the first and second buffer circuits, with regard to positive polarity defining a characteristic from the low-potential power supply voltage and negative polarity defining a characteristic from the high-potential power supply voltage, the reference data being of positive and negative polarity and corresponding to a voltage within a drive changeover range (see Fig. 4) in which both the first and second buffer circuits are capable of operating.

**[0029]** The selector (4), to which a polarity signal (POL) specifying polarity is input, selects reference data of the positive or negative polarity based upon the value of the polarity signal.

**[0030]** Preferably, a storage unit (3a) stores reference data of the positive polarity, which corresponds to an input signal voltage within a range in which both the first and second buffer circuits are capable of operating, with regard to each of a standard state and modulated state of a gamma characteristic relating to grayscale level and signal voltage.

**[0031]** Preferably, a storage unit (3b) stores reference data of the negative polarity, which corresponds to a voltage within a drive changeover range in which both the first and second buffer circuits are capable of operating, with regard to each of a standard state and modulated state of a gamma characteristic relating to grayscale level and signal voltage.

**[0032]** The selector (4) selects one of the storage units (3a, 3b) on the basis of a polarity signal (POL) specifying polarity and selectively outputs the reference data corresponding to the standard state or modulated

state based upon modulation information specifying modulation.

**[0033]** A plurality of items of reference data of positive polarity, which are defined in accordance with type of modulation of the gamma characteristic, are stored in the storage unit (3a), a plurality of items of reference data of negative polarity, which are defined in accordance with type of modulation of the gamma characteristic, are stored in the storage unit (3b), and the selector (4) selects one of the storage units (3a, 3b) based upon the polarity signal and selectively outputs the reference data conforming to the type of modulation based upon the modulation information.

**[0034]** In a case where the control signal specifies activation, the first buffer circuit (13) is placed in the operating state and the second buffer circuit (14) is shut down if the output signal of the comparator (5) is a value indicating that the entered data is equal to or greater than the reference data, and the second buffer circuit (14) is placed in the operating state and the first buffer circuit (13) is shut down if the output signal of the comparator (5) is a value indicating that the entered data is less than the reference data.

**[0035]** In accordance with one embodiment of the present invention, the polarity signal (POL) is a logic value indicating polarity, in inversion drive, of a common potential (Vcom) of opposing electrodes in a liquid crystal display device.

**[0036]** In accordance with the embodiment of the present invention, the storage unit (3) and selector (4) may be provided externally of the driver circuit and may be electrically connected to the driver circuit. Furthermore, the storage unit (3) may be a register, a ROM or a non-volatile semiconductor memory device such as a writable EEPROM.

**[0037]** As shown in Fig. 3, in the embodiment, there are provided grayscale-level voltage generating means (200), which has a plurality of resistors (R0, R1, ..., Rn) connected serially between first and second reference voltages, for generating grayscale-level voltages from taps thereof; and a decoder circuit (300), to which a digital data signal is input, for selectively outputting a corresponding voltage from output voltages of the grayscale-level voltage generating means (200). The driver circuit according to the present invention, which receives the output of the decoder circuit (300), drives an output load. The storage unit (3) and selector (4) are provided in common for a plurality of the driver circuits, and the driver circuit preferably incorporates the comparator (5).

**[0038]** In accordance with another embodiment of the present invention, as shown in Fig. 7, a driver circuit comprises: a first buffer circuit (13) and a second buffer circuit (14) having their input terminals connected commonly to one input terminal (1) to which an input signal voltage (Vin) is input and their output terminals connected commonly to an output terminal (2), the first buffer circuit (13) having an operating range at least on the

side of a high potential and the second buffer circuit (14) having an operating range at least on the side of a low potential; reference voltage generating means (11) for generating a reference voltage Vin2 corresponding to a voltage range in which both the first and second buffer circuits are capable of operating; and a comparator (12) for comparing the reference voltage Vin2, which is output from the reference voltage generating means (11), and the input signal voltage Vin (= Vin1); wherein the first buffer circuit and the second buffer circuit have their activation and deactivation controlled based upon an output signal of the comparator (12), which indicates result of the comparison, and a control signal. In a case where the control signal specifies activation, the first buffer circuit (13) is placed in the operating state and the second buffer circuit (14) is shut down if the output signal (VO) of the comparator (12) is a value indicating that the input signal voltage Vin is equal to or greater than the reference voltage Vin2, and the second buffer circuit (14) is placed in the operating state and the first buffer circuit (13) is shut down if the output signal of the comparator is a value indicating that the input signal voltage Vin is less than the reference voltage Vin2.

**[0039]** In this embodiment, the driver circuit may further comprise a first logic circuit (22 in Fig. 16), to which the output signal (VO) of the comparator (12) and the control signal are input, for outputting the result of a logical operation upon the comparator output signal (VO) to the first buffer circuit when the control signal is active, and a second logic circuit (23 in Fig. 16), to which a signal that is the inverse of the output signal (VO) of the comparator (12) and the control signal are input, for outputting the result of a logical operation upon the signal that is the inverse of the comparator output signal (VO) to the second buffer circuit when the control signal is active.

**[0040]** In accordance with this embodiment of the invention, as shown in Fig. 9, a liquid crystal display device comprises grayscale-level voltage generating means (200), which has a plurality of resistors (R0, R1, ..., Rn) connected serially between first and second reference voltages, for generating grayscale-level voltages from taps thereof; and a decoder circuit (300), to which a digital data signal is input, for selectively outputting a corresponding voltage from output voltages of the grayscale-level voltage generating means (200). The driver circuit according to the present invention, which receives the output of the decoder circuit (300), drives an output load. The reference voltage generating means (11) is provided in common for a plurality of the driver circuits, and the driver circuit preferably incorporates the comparator (12).

**[0041]** In accordance with this embodiment of the invention, the comparator (12), as shown in Fig. 10, includes a differential amplifier circuit the differential inputs to which are the input signal Vin (= Vin1) and the reference voltage Vin2, and a holding circuit connected to the output of the differential amplifier circuit via a

switch. The holding circuit comprises a flip-flop circuit connected to one output terminal of the differential amplifier circuit via a switch (113). The flip-flop includes a first inverter (111) having an input terminal connected to the switch (113), a second inverter (112) having an input terminal connected to an output terminal of the first inverter, and a switch (114) connected between the output terminal of the second inverter and the input terminal of the first inverter. The signal from the second inverter (112) is output as the comparator output signal (VO). When the differential amplifier circuit operates, the switch (113) is turned on and the output of the differential amplifier circuit is received and latched. When this occurs, the switch (113) is turned off and the switch (114) is turned on.

**[0042]** The differential amplifier circuit includes a switch (108) provided between a current source (105) driving the differential pair and a power supply, and a switch (109) provided in a path for feeding power to an output stage transistor (106) which receives the output of the differential pair. These switches are turned on only when the comparator operates, as a result of which consumption of power is reduced.

**[0043]** When the differential amplifier circuit operates, the switches (108, 109 and 113) are turned on and the output of the differential amplifier circuit is received and latched. When this occurs, the switches (108, 109 and 113) are turned off and the switch (114) is turned on.

**[0044]** In accordance with this embodiment of the invention, as shown in Fig. 12, the flip-flop of the comparator includes a first clocked inverter (111) connected to the output terminal of the output transistor of the differential amplifier circuit via the switch (113), and a second clocked inverter (112) having its input terminal connected to the output terminal of the first clocked inverter. The second clocked inverter (112) has an output terminal connected to the input terminal of the first clocked inverter (111), and the signal (VO) at the output terminal of the second clocked inverter and/or the signal at the output terminal of the first clocked inverter is output as the signal representing the result of the comparison. When the differential amplifier circuit operates, the switches (108, 109 and 113) are all turned on and the output of the differential amplifier circuit is received and latched. When this occurs, the switches (108, 109 and 113) are turned off. The capacitance value of a load capacitance (C2) at the output terminal of the second clocked inverter (112) is made larger than that of the load capacitance (C1) at the output terminal of the first clocked inverter (111).

**[0045]** In accordance with the embodiment of the invention, as shown in Figs. 17 and 18, the first buffer circuit (13) includes a source-follower transistor (412) connected to the low-potential power supply (VSS) and the output terminal (2), first gate-bias control means (transistor 411, current sources 414 and 413, and switches 551 and 552), to which the input signal voltage is input, for supplying the source-follower transistor (412) with a

gate bias voltage, and means (550) for charging the output terminal (2).

**[0046]** The second buffer circuit (14) includes a source-follower transistor (422) connected to the high-potential power supply (VDD) and the output terminal (2), second gate-bias control means (transistor 421, current sources 424 and 423, and switches 561 and 562), to which the input signal voltage is input, for supplying the source-follower transistor with a gate bias voltage, and means (560) for discharging the output terminal (2).

**[0047]** In accordance with the embodiment of the invention, as shown in Figs. 19 and 20, the first buffer circuit (13) is constituted by a first voltage follower circuit comprising a differential amplifier circuit, which has a differential pair comprising a pair of N-channel MOS transistors (313 and 314), in which the input terminal (1) is connected to a non-inverting input terminal and the output terminal (2) is connected to an inverting input terminal. The second buffer circuit (14) is constituted by a second voltage follower circuit comprising a differential amplifier circuit, which has a differential pair comprising P-channel MOS transistors (323 and 324), in which the input terminal (1) is connected to a non-inverting input terminal and the output terminal (2) is connected to an inverting input terminal. Means (15) is provided for charging and discharging the output terminal (2).

**[0048]** More specifically, the first buffer circuit (13) comprises: a differential stage having a differential pair comprising a pair of N-channel MOS transistors (313 and 314), a load circuit (311 and 312) connected between the output of the differential pair and the high-potential power supply, a current source (315) for driving the differential pair, and a first switch (511) for controlling the opening and closing of the current path between the current source and the low-potential power supply; and an output stage having a MOS transistor (316), to which the output of the differential pair is input, whose output is connected to the output terminal, a current source (317) connected between the output terminal (2) and the low-potential power supply, and a switch (512). The input terminal (1) and output terminal (2) are connected to the gates of the MOS transistor pair (313 and 314) constituting the differential pair. The second buffer circuit (14) comprises: a differential stage having a differential pair (323 and 324) comprising the pair of P-channel MOS transistors, a load circuit (321 and 322) connected between the output of the differential pair and the low-potential power supply, a current source (325) for driving the differential pair, and a switch (521) for controlling the opening and closing of the current path between the current source and the high-potential power supply; and an output stage having a MOS transistor (326), to which the output of the differential pair is input, whose output is connected to the output terminal, a current source (327) connected between the output terminal (2) and the low-potential power supply, and a switch (522). The input terminal (1) and output terminal (2) are connected to the gates of the MOS transistor pair (323

and 324) constituting the differential pair.

**[0049]** In accordance with the embodiment of the invention, as shown in Figs. 21 and 22, the first buffer circuit (13) is constituted by a first voltage follower circuit comprising a differential amplifier circuit, which has a differential pair comprising the pair of N-channel MOS transistors (313 and 314), in which the input terminal (1) is connected to a non-inverting input terminal and the output terminal (2) is connected to an inverting input terminal; a source-follower transistor (412) connected to the low-potential power supply and the output terminal; and first gate-bias control means (transistor 411, current sources 414 and 413 and switches 551 and 552), to which the input signal voltage is input, for supplying the source-follower transistor with a gate bias voltage. The second buffer circuit (14) is constituted by a second voltage follower circuit comprising a differential amplifier circuit, which has a differential pair comprising the pair of P-channel MOS transistors (323 and 324), in which the input terminal (1) is connected to a non-inverting input terminal and the output terminal (2) is connected to an inverting input terminal; a source-follower transistor (422) connected to the high-potential power supply and the output terminal; and second gate-bias control means (transistor 421, current sources 424 and 423 and switches 561 and 562), to which the input signal voltage is input, for supplying the source-follower transistor with a gate bias voltage.

**[0050]** In accordance with the embodiment of the invention, the reference voltage generating means (11) has a plurality of resistors (R1 and R2) and a switch (120) connected between first and second references voltages. When the switch (120) is in the ON state, a voltage within the drive changeover range, which is defined by the overlap between the operating ranges of the first and second buffers, is output as a reference voltage from the point at which the resistors are connected. It should be noted that diode-connected transistors or the like might be used as the plurality of resistors (R1 and R2).

**[0051]** Embodiments of the present invention will now be described in greater detail with reference to the drawings.

Fig. 1 is a block diagram illustrating the structure of a driver circuit according to an embodiment of the present invention.

As shown in Fig. 1, the driver circuit according to this embodiment comprises a register 3 having a positive-polarity reference-data table 3a and a negative-polarity reference-data table 3b for storing, for every type of modulation of a characteristic of the relation between grayscale level and voltage (inclusive also of the characteristic in the standard state thereof as a matter of course), reference data (positive-polarity reference data and negative-polarity reference data, respectively) corresponding to a grayscale level at which first and second analog buffer circuits 13, 14 are changed over; a selector 4, to which outputs of the positive-polarity reference-

data table 3a and negative-polarity reference-data table 3b are input, for selecting one of the tables based upon a polarity signal POL and for selectively outputting reference data, which conforms to the modulation, based upon modulation information; comparator 5 for comparing entered video digital data and the output of the selector 4; and first and second analog buffer circuits 13 and 14, to which an output PN of the comparator, which represents the result of the comparison, and a control signal are input, for having their activation and deactivation controlled, wherein the input terminals of these buffer circuits are connected in common to an input terminal 1 and their output terminals are connected in common to an output terminal 2. The data in the positive-polarity reference-data table 3a and negative-polarity reference-data table 3b has the same bit width and the same binary expression format as those of video digital data. The comparator 5 comprises a well-known digital comparator for comparing magnitudes of two digital data. An analog voltage, which corresponds to video digital data input to the comparator 5, is applied to the input terminal 1.

**[0052]** At any modulation step, reference data (positive polarity and negative polarity) corresponding to the modulation step is selected by the selector 4 in accordance with the polarity signal POL, the comparator 5 compares the selected reference data and the video digital data to determine whether the grayscale level corresponding to the video digital data is lower or higher with regard to an electric potential than a changeover grayscale level, and outputs the discrimination signal PN. One of the first and second analog buffers circuits 13 and 14 is selected by the discrimination signal PN and is driven. The control signal controls the operation of the first and second analog buffer circuits 13 and 14. In Vcom inversion drive control, the polarity signal POL is placed at the high or low level depending upon whether the Vcom voltage is a low potential (positive drive) or a high potential (negative drive).

**[0053]** At any modulation step, reference data (positive polarity and negative polarity) corresponding to the modulation step is selected by the selector 4 in accordance with the polarity signal POL, the comparator 5 compares the selected reference data and the video digital data to determine whether the grayscale level corresponding to the video digital data is lower or higher than a changeover grayscale level, and outputs the discrimination signal PN. One of the first and second analog buffers circuits 13 and 14 is selected by the discrimination signal PN and is driven. The control signal controls the operation of the first and second analog buffer circuits 13 and 14. In Vcom inversion drive control, the polarity signal POL is placed at the high or low level depending upon whether the Vcom voltage is a low potential (positive drive) or a high potential (negative drive).

**[0054]** Fig. 2 is a diagram illustrating the control operation of the circuit shown in Fig. 1. When the control signal is at the low level, the first and second analog

buffer circuits 13 and 14 cease operating (become inactive) irrespective of the output PN of comparator 5. When the control signal is at the high level and the output PN of the comparator 5 is at the high level, the first analog buffer circuit 13 operates and the second analog buffer circuit 14 ceases operating (becomes inactive).

**[0055]** When the control signal is at the high level and the output PN of the comparator 5 is at the low level, the second analog buffer circuit 14 operates and the first analog buffer circuit 13 ceases operating (becomes inactive).

**[0056]** Fig. 3 is a diagram showing an arrangement in which the driver circuit according to this embodiment of the invention is applied to a multiple-output driver circuit.

**[0057]** This multiple-output driver circuit is used to drive the data line of a liquid crystal display device, by way of example. As shown in Fig. 3, the multiple-output driver circuit has grayscale-level voltage generating means 200, which is composed of a resistor string obtained by serially connecting a plurality of resistance elements R0 to Rn between a power supply V1 and a power supply V2 serving as reference voltages, for outputting analog voltages, which conform to polarity, from the taps of the resistor string. The grayscale-level voltages (analog voltages) from the grayscale-level voltage generating means 200 are input to a decoder 300, to which the video digital signal is also applied. The decoder 300 selectively outputs a grayscale-level voltage corresponding to the video digital signal and inputs the voltage to a driver circuit 100. It should be noted that the grayscale-level voltage generating means 200 may be so constructed that the power supplies V1 and V2 are made fixed voltages and analog voltages conforming to polarity are output from resistor-string taps the number of which is twice the number of grayscale levels. Alternatively, an arrangement may be adopted in which the potential levels of the power supplies V1 and V2 are inverted in sync with a reversal of polarity and analog voltages conforming to polarity are output from resistor-string taps the number of which is the same as that of the number of grayscale levels.

**[0058]** The driver circuit 100 has the construction of the above embodiment described with reference to Fig. 1. Each driver circuit 100 includes the first and second analog buffer circuits 13 and 14 and the comparator 5. The register 3 and selector 4 are shared by each of the driver circuits 100.

**[0059]** Fig. 4 is a diagram illustrating an example of the gamma characteristic of liquid crystal and the operating range of a driver circuit in common inversion drive. The gamma characteristic at the time of operation with positive polarity is represented by a solid line (polarity signal POL = H), and the gamma characteristic at the time of operation with negative polarity is represented by a broken line (polarity signal POL = L). Positive-polarity reference data and negative-polarity reference data has been stored in the register 3 in such a manner that drive changeover voltage Vc falls within a drive

changeover range defined by limits  $V_{lim1}$ ,  $V_{lim2}$ . Specifically, in accordance with this embodiment, the changeover between the first analog buffer circuit 13 and second analog buffer circuit 14 is performed by providing reference data, which corresponds to voltage  $V_c$  within the drive changeover range  $V_{lim1}$  to  $V_{lim2}$ , for every type of modulation. In the example of Fig. 4 (which represents the standard state), the drive changeover voltage  $V_c$  is common to both the positive and negative polarities and digital data corresponding to grayscale levels M and N (positive polarity: grayscale level M; negative polarity: grayscale level N) nearest to the voltage  $V_c$  are set beforehand as standard-state reference data for each polarity. The first analog buffer circuit 13 is activated when the entered video digital data takes on a value which corresponds to a voltage equal to or greater than that of the reference data, and the second analog buffer circuit 14 is activated when the entered video digital data takes on a value of voltage less than that of the reference data.

**[0059]** Reference will now be had to Figs. 6A, and 6B for the purpose of comparison. In a case where the changeover between a first analog buffer (which corresponds to the first analog buffer circuit 13 of Fig. 1) and a second analog buffer (which corresponds to the second analog buffer circuit 14 of Fig. 1) is performed at grayscale level 32 among grayscale levels 0 to 63 in response to one higher order bit of video digital data, the changeover is possible if the signal voltage (the entered grayscale-level voltage) corresponding to grayscale level 32 falls within the drive changeover range ( $V_{lim1}$  to  $V_{lim2}$ ) of the first and second analog buffers, as shown in Fig 6A. In Fig. 6B, however, in which modulation has been applied, the signal voltage corresponding to grayscale level 32 falls outside the drive changeover range ( $V_{lim1}$  to  $V_{lim2}$ ). In the case of positive polarity, the output of the first analog buffer is fixed at  $V_{lim1}$  between grayscale levels 32 to 48 and, in the case of negative polarity, the output of the second analog buffer is fixed at  $V_{lim2}$  between grayscale levels 32 to 48. In other words, even if a video digital signal corresponding to levels 32 to 48 is input, an analog voltage corresponding to these levels will not be output and so-called "tone jump" occurs. By contrast, in accordance with the present invention, the changeover in operation between the first analog buffer and second analog buffer is performed at a voltage within the drive changeover range ( $V_{lim1}$  to  $V_{lim2}$ ). That is, control through which the modulation data prevailing at the time of changeover is varied for each type of modulation is carried out. As a result, tone jump does not occur.

**[0060]** Fig. 5 is a timing chart in the case of a modulation step having the gamma characteristic shown in Fig. 4. At timing  $t_1$  in Fig. 5, the polarity signal  $POL$  is at the high level and the reference data is positive-polarity data  $DM$  (data corresponding to grayscale level M). The reference data is compared with video digital data  $D16$  corresponding to grayscale level 16, the comparator

output  $PN$  changes from the high to the low level, the first analog buffer circuit 13 is changed over to the second analog buffer circuit 14 and the second analog buffer circuit 14 operates.

5 **[0061]** At time  $t_2$ , the polarity signal  $POL$  assumes the low level and the reference data becomes negative-polarity data  $DN$  (data corresponding to grayscale level N). The reference data is compared with video digital data  $D16$  corresponding to grayscale level 16, the comparator output  $PN$  changes to the high level and the first analog buffer circuit 13 is selected.

10 **[0062]** At time  $t_3$ , the polarity signal  $POL$  assumes the high level and the reference data becomes positive-polarity data  $DM$ . The reference data is compared with video digital data  $D40$  corresponding to grayscale level 40, the comparator output  $PN$  is at the high level and the first analog buffer circuit 13 is selected and activated.

15 **[0063]** At time  $t_4$ , the polarity signal  $POL$  assumes the low level and the reference data becomes negative-polarity data  $DN$ . The reference data is compared with video digital data  $D40$  corresponding to grayscale level 40, the comparator output  $PN$  is at the high level and the first analog buffer circuit 13 is selected.

20 **[0064]** At time  $t_5$ , the polarity signal  $POL$  assumes the high level and the reference data becomes positive-polarity data  $DM$ . The reference data is compared with video digital data  $D63$  corresponding to grayscale level 63, the comparator output  $PN$  is at the high level and the first analog buffer circuit 13 is selected and activated.

25 **[0065]** At time  $t_6$ , the polarity signal  $POL$  assumes the low level and the reference data becomes negative-polarity data  $DN$ . The reference data is compared with video digital data  $D63$  corresponding to grayscale level 63, the comparator output  $PN$  falls to the low level and the second analog buffer circuit 14 is selected.

30 **[0066]** Fig. 7 is a block diagram illustrating the structure of another embodiment of the present invention. As shown in Fig. 7, the driver circuit according to this embodiment comprises reference voltage generating means 11, a comparator 12 for comparing the output of the reference voltage generating means 11 and input signal voltage  $V_{in}$  ( $= V_{in1}$ ), and first and second analog buffer circuits 13 and 14, to which an output  $VO$  of the comparator and a control signal are input, for having their activation and deactivation controlled, wherein the input terminals of these buffer circuits are connected in common to the input terminal 1 and their output terminals are connected in common to the output terminal 2.

35 **[0067]** The reference voltage generating means 11 generates reference voltage  $V_c$ , at which the first and second analog buffers 13 and 14 are capable of being changed over, for each of a variety of modulation steps. That is, the reference voltage  $V_c$  is provided within a voltage range in which both the first and second analog buffers 13 and 14 are capable of operating.

40 **[0068]** The comparator 12 compares the grayscale-level voltage  $V_{in}$ , which has been selected by the video digital data, with the reference voltage  $V_c$ , and selects

one of the first and second analog buffers 13, 14 in accordance with the sizes of the compared voltages, whereby the selected buffer is driven. The control signal controls the operation of the reference voltage generating means 11, comparator 12 and the first and second analog buffer circuits 13 and 14. Operation is halted except when necessary. Of course, an arrangement may be adopted in which the input signal voltage  $V_{in}$  is supplied to the first and second analog buffer circuits 13 and 14 upon being delayed by a delay circuit (not shown) for a length of time needed for the comparator 12 to execute comparison processing.

**[0069]** Fig. 8 is a diagram illustrating the control operation of the arrangement shown in Fig. 1. When the control signal is at the low level, the first and second analog buffer circuits 13 and 14 cease operating (become inactive). When the control signal is at the high level and the output PN of the comparator 12 is at the high level, the first analog buffer circuit 13 operates and the second analog buffer circuit 14 ceases operating (becomes inactive).

**[0070]** When the control signal is at the high level and the output of the comparator 12 is at the low level, the second analog buffer circuit 14 operates and the first analog buffer circuit 13 ceases operating (becomes inactive).

**[0071]** Fig. 9 is a diagram in which the driver circuit shown in Fig. 7 is applied to a multiple-output driver circuit. This multiple-output driver circuit is used to drive the data line of a liquid crystal display device, by way of example. As shown in Fig. 9, the multiple-output driver circuit has the grayscale-level voltage generating means 200, which is composed of a resistor string obtained by serially connecting a plurality of resistance elements  $R_0$  to  $R_n$  between a power supply  $V_1$  and a power supply  $V_2$  serving as reference voltages, for outputting analog voltages, which conform to polarity, from the taps of the resistor string. The grayscale-level voltages (analog voltages) from the grayscale-level voltage generating means 200 are input to a decoder 300, to which the video digital signal is also applied. The decoder 300 selectively outputs a grayscale-level voltage corresponding to the video digital signal and inputs the voltage to the driver circuit 100. It should be noted that the grayscale-level voltage generating means 200 may be so constructed that the power supplies  $V_1$  and  $V_2$  are made fixed voltages and analog voltages conforming to polarity are output from resistor-string taps the number of which is twice the number of gray levels. Alternatively, an arrangement may be adopted in which the potential levels of the power supplies  $V_1$  and  $V_2$  are inverted in sync with a reversal of polarity and analog voltages conforming to polarity are output from resistor-string taps the number of which is the same as that of the number of grayscale levels.

The driver circuit 100 has the construction of the above embodiment described with reference to Fig. 7. Each driver circuit 100 includes the first and second an-

alog buffer circuits 13 and 14 and the comparator 12. The reference voltage generating means 11 is shared by each of the driver circuits 100.

**[0072]** Fig. 10 is a diagram showing an example of the structure of the comparator 12 in the driver circuit according to the embodiment shown in Fig. 7.

As shown in Fig. 10, the comparator 12 includes P-channel MOS transistors 103 and 104 constituting a differential pair and having their sources tied together and connected to one end of a constant-current source 105. The grayscale-level voltage (input signal voltage  $V_{in}$ ) and the reference voltage are input to the gates of the P-channel MOS transistors 103 and 104, respectively, and the drains of the P-channel MOS transistors 103 and 104 are connected respectively to N-channel MOS transistors 101 and 102 (transistor 102 is on the input side and transistor 101 is on the output side), which construct a current mirror circuit. The other end of the constant-current source 105 is connected to the high-potential power supply  $VDD$  via a switch 108.

**[0073]** The drain of the P-channel MOS transistor 103 is connected to the gate of an N-channel MOS transistor 106 whose source is connected to the low-potential power supply  $VSS$  and whose drain is connected to one end of a constant-current source 107. The other end of the constant-current source 107 is connected to the high-potential power supply  $VDD$  via a switch 109.

**[0074]** The drain of the N-channel MOS transistor 106 is connected to one end of a switch (transfer switch) 113, and the other end of the switch 113 is connected to a flip-flop comprising two inverters 111 and 112. The output of the inverter 111 is connected to the input of the inverter 112, and the output of the inverter 112 is connected to the input of the inverter 111. More specifically, one end of the switch (transfer switch) 113 is connected to the input terminal of the inverter 111, the output terminal of the inverter 111 is connected to the input terminal of the inverter 112, and the output terminal of the inverter 112 is connected to the input terminal of the inverter 111 via the switch 114. The outputs of the inverters 111 and 112 are extracted as the outputs  $VO_B$  and  $VO$ , respectively.

**[0075]** Fig. 11 is a timing chart useful in describing the operation of the comparator 12 having the circuit structure shown in Fig. 10. When the switches 108, 109, 113 are turned on and the switch 114 turned off by the control signal, the differential amplifier circuit is activated and the result of the comparison is transmitted to the flip-flop.

**[0076]** The operation of the comparator 12 shown in Fig. 10 will now be described. First, assume that the switches 108, 109, 113 are on and that the switch 114 is off, so that the differential amplifier circuit is operating and the grayscale-level voltage and reference voltage is compared. When the grayscale-level voltage  $V_{in1}$  is lower than the reference voltage  $V_{in2}$ , the transistor 103 has a larger drain current than that of the transistor 104, the gate voltage of the N-channel MOS transistor 106

increases and the potential at the connection between the drain of transistor 106 and the constant-current source 107 takes on the low-potential level. When the grayscale-level voltage  $V_{in1}$  is higher than the reference voltage  $V_{in2}$ , a larger drain current flows into the transistor 104, the gate voltage of the N-channel MOS transistor 106 decreases and the potential at the connection between the drain of transistor 106 and the constant-current source 107 takes on the high-potential level. The output of the differential circuit is input to the inverter 111 via the switch 113 (this switch 114 is off at this time).

**[0077]** The switch 113 is turned off (and so are the switches 108, 109), the switch 114 is turned on, the flip-flop is constructed by the two inverter stages, and the input data (result of the comparison) of inverter 111 is latched and output as  $VO$ .

**[0078]** Fig. 12 is a diagram showing another structure of the comparator 12 according to this embodiment of the invention. The power consumption of the comparator shown in Fig. 12 is lower than that of a circuit shown in Fig. 10.

**[0079]** As shown in Fig. 12, the structure of the differential circuit is similar to that shown in Fig. 11. With regard to the flip-flop, a switch 115P is provided in a power feeding path between the high-potential power supply VDD and the high-potential power supply terminal of the inverter 111, and a switch 115N is provided in a power feeding path between the low-potential power supply VSS and the low-potential power supply terminal of the inverter 111. Further, a switch 116P is provided between the high-potential power supply VDD and the power supply path of the inverter 112, and a switch 115N is provided between the low-potential power supply VSS and the power supply path of the inverter 112. The switch 114 in Fig. 11 is eliminated. A storage operation is performed utilizing stored charge in a parasitic capacitance C1 at the output of the inverter 111 and a parasitic capacitance C2 at the output of the inverter 112. The capacitance C2 is made larger than the capacitance C1. The duration of charge/discharge of capacitance C1 by the inverter 111 is made shorter than that of charge/discharge of capacitance C2 by the inverter 112. As a result, operation of the flip-flop is stabilized.

**[0080]** Fig. 13 is a timing chart illustrating the operation of the circuit shown in Fig. 12. Over the initial part of the length of one output period, the switches 108, 109 and 113 are turned on, the result of the comparison from the differential circuit is transmitted to the input terminal of the inverter 111 of the flip-flop and the switches 115P, 115N, 116P and 116N are turned off. Next, the switches 108, 109 and 113 are turned off, the switches 115P, 115N, 116P and 116N are turned on and the flip-flop stores data.

**[0081]** It should be noted that by establishing the relation  $C2 > C1$  with regard to the load capacitance C2 of inverter 112 and the load capacitance C1 of inverter 111, malfunction could be prevented. That is, the rise time and decay time of the signal resulting from the charging

and discharging of the output load of inverter 111 is set to be shorter than in the case of the inverter 112. Operation of the flip-flop is stabilized as a result.

**[0082]** When the switch 113 is ON, the output of the differential circuit charges or discharges the capacitance C2 and the output  $VO$  of the comparator is caused to change before time  $t1$  at which the switch 113 is turned off.

It should be noted that if the current controlled by the constant-current sources 105 and 107 is kept sufficiently small in the comparator of Fig. 12, the change in input potential of the inverter 111 while the switches 108, 109 and 113 are ON will become more gentle. However, since the switches 115P, 115N, 116P and 116N are OFF, feedthrough current does not occur in the inverters 111 and 112. If the switches 108, 109 and 113 are turned off and the switches 115P, 115N, 116P and 116N are turned on after the input potential of the inverter 111 stabilizes at the high or low level, then the inverters 111 and 112 will operate immediately and the comparator can be operated without loss due to power consumption ascribable to feedthrough current. Further, though not shown in Fig. 12, a switch is provided in the power supply path of the circuit to which the output  $VO$  of the comparator is input, and good effects can be obtained if the switch is controlled in sync with the switches 115P, 115N, 116P and 116N. On the other hand, if current controlled by the constant-current sources 105 and 107 is kept sufficiently small in the comparator of Fig. 10, loss due to power consumption ascribable to feedthrough current of the inverters 111 and 112 increases and, as a result, a sufficiently low power consumption cannot be achieved.

**[0083]** Fig. 14 is a diagram illustrating transistor levels in the circuit arrangement shown in Fig. 12. As shown in Fig. 14, the constant-current sources 105, 107 of Fig. 12 are constructed by P-channel MOS transistors having a bias voltage BIASp supplied to the gates thereof, and the switches 108 and 109 of Fig. 12 are constructed by P-channel MOS transistors having a gate signal SC1B (a signal that is the inverse of SC1) supplied to the gates thereof.

**[0084]** Further, as shown in Fig. 14, the switch 113 of Fig. 12 comprises a CMOS transfer gate, the control signal SC1B is supplied to the gate of P-channel MOS transistor 113P, and the control signal SC1 is supplied to the gate of N-channel MOS transistor 113N. The switch 113 turns on when the control signal SC1 is high.

**[0085]** The inverter 111, which is a clocked inverter, comprises a P-channel MOS transistor 111P and an N-channel MOS transistor 111N having their gates tied together, their drains tied together and constructing a CMOS (complementary MOS) inverter; a P-channel MOS transistor 115P having a source connected to the power supply VDD, a gate connected to the control signal SC1 and a drain connected to the source of the P-channel MOS transistor 111P; and an N-channel MOS transistor 115N having a gate connected to the control signal SC1B and a drain connected to the source of the

N-channel MOS transistor 111N.

**[0086]** The inverter 112, which is a clocked inverter, comprises a P-channel MOS transistor 112P and an N-channel MOS transistor 112N having their gates tied together, their drains tied together and constructing a CMOS inverter; a P-channel MOS transistor 116P having a source connected to the power supply VDD, a gate connected to the control signal SC1 and a drain connected to the source of the P-channel MOS transistor 112P; and an N-channel MOS transistor 116N having a gate connected to the control signal SC1B and a drain connected to the source of the N-channel MOS transistor 112N.

**[0087]** Fig. 15 is a timing chart illustrating the operation of the comparator shown in Fig. 14. Over the initial part (t0 to t1) of the length of one output period, the control signal SC1 is placed at the high level (ON) (SC1B is at the low level). On a succeeding period, the control signal SC1 is then placed at the low level (SC1B is placed at the high level). With the control signal SC1 at the high level, the differential circuit is activated, switch 13 turns on and the inverters 11 and 12 are deactivated. With the control signal SC1 at the low level, switch 13 turns off and inverters 11 and 12 are activated.

**[0088]** Fig. 16A is a diagram showing the structure of another embodiment of the present invention. As shown in Fig. 16A, this circuit includes the reference voltage generating means 11, the comparator 12, the first analog buffer circuit 13 and the second analog buffer circuit 14. The circuit further includes a NAND gate 22 the inputs to which are the output VO of the comparator 12 and a control signal SC0, and a NAND gate 23 the inputs to which are a signal, which is obtained by inverting the output VO of the comparator 12 by an inverter 24, and the control signal SC0. The outputs of the NAND gates 22 and 23 are supplied to the first analog buffer circuit 13 and second analog buffer circuit 14 as control signals.

**[0089]** It should be noted that the control signal SC1 controls the operation of the reference voltage generating means 11 and the comparator 12 shown in Fig. 14.

**[0090]** Fig. 16B is a timing chart useful in describing the operation of the circuit shown in Fig. 16A. Here SC0 represents the control signal and VO the output of comparator 12. When SC0 is at the low level, the outputs of NAND gates 22 and 23 are at the high level. When SC0 is at the high level, NAND gate 22 outputs a signal that is the inverse of VO and NAND gate 23 outputs VO.

**[0091]** Fig. 17 is a diagram showing an example of the structure of the analog buffer circuits 13 and 14 in the driver circuit shown in Fig. 1.

As shown in Fig. 17, the first analog buffer circuit 13 includes a constant-current source 413 and a switch 551 connected in series between the input terminal 1 and high-potential power supply VDD; a P-channel MOS transistor 411 having a source connected to the input terminal 1 and a gate and drain that are connected together; a constant-current source 414 and a switch

552 connected in series between the drain of the P-channel MOS transistor 411 and low-potential power supply VSS; a constant-current source 415 and a switch 554 connected in series between the output terminal 2 and high-potential power supply VDD; and a P-channel MOS transistor 412 having a source connected to the output terminal 2, a gate connected in common with the gate of the P-channel MOS transistor 411, and a drain connected to the low-potential power supply VSS via a switch 553. A switch 550 is connected between the output terminal 2 and high-potential power supply VDD and in parallel with the series circuit composed of the constant-current source 415 and switch 554.

**[0092]** The second analog buffer circuit 14 includes a constant-current source 423 and a switch 561 connected in series between the input terminal 1 and low-potential power supply VSS; an N-channel MOS transistor 421 having a source connected to the input terminal 1 and a gate and drain that are connected together; a constant-current source 424 and a switch 562 connected in series between the drain of the N-channel MOS transistor 421 and high-potential power supply VDD; a constant-current source 425 and a switch 564 connected in series between the output terminal 2 and low-potential power supply VSS; and an N-channel MOS transistor 422 having a source connected to the output terminal 2, a gate connected in common with the gate of the N-channel MOS transistor 421, and a drain connected to the high-potential power supply VDD via a switch 563. A switch 560 is connected between the output terminal 2 and low-potential power supply VSS and in parallel with the series circuit composed of the constant-current source 425 and switch 564.

**[0093]** An example of operation of the first analog buffer circuit 13 will now be described. Control is performed in response to control signals in such a manner that switch 550 is turned on and switches 551, 552, 553 and 554 turned off, switches 551 and 552 are then turned on, after which switch 550 is turned off and switches 553 and 554 turned on.

**[0094]** When switches 551 and 552 are turned on, a common-gate potential VG1 of the transistors 411 and 412 becomes a voltage shifted from the input signal voltage Vin by a gate-source voltage Vgs1 of the transistor 411 owing to the action of transistor 411. Specifically, we have

$$VG1 = Vin + Vgs1 \quad (1)$$

50 It should be noted that the gate-source voltage Vgs is represented by the potential of the gate with respect to the source.

**[0095]** The transistor has a unique VI characteristic between drain-source current Ids and gate-source voltage Vgs, and the gate-source voltage Vgs1 of transistor 411 is uniquely decided by the Ids-Vgs characteristic of the transistor 411 and current I1 controlled by the con-

stant-current source 414.

**[0096]** Let the gate-source voltage that prevails when the drain-source current of the transistor 411 becomes  $I_1$  (the current value of the constant-current source 414) be represented by  $V_{gs1}(I_1)$ . In such case the gate voltage  $VG_1$  of the transistor 411 stabilizes at

$$VG_1 = Vin + V_{gs1}(I_1) \quad (2)$$

**[0097]** When the voltage  $VG_1$  is applied to the gate of the transistor 412, the output voltage  $V_{out}$  becomes a voltage shifted from the voltage  $VG_1$  by a gate-source voltage  $V_{gs2}$  of the transistor 412. Specifically, we have

$$V_{out} = VG_1 - V_{gs2} \quad (3)$$

The output voltage  $V_{out}$  stabilizes when the drain-source current of transistor 412 becomes equal to  $I_3$  (the current value of constant-current source 415). The gate-source voltage  $V_{gs2}$  of transistor 412 at this time becomes  $V_{gs2}(I_3)$  owing to the  $Ids$ - $Vgs$  characteristic of transistor 412 and the current  $I_3$ . The output voltage  $V_{out}$  stabilizes at

$$V_{out} = VG_1 - V_{gs2}(I_3) \quad (4)$$

**[0098]** From Equations (2) and (4), the output voltage  $V_{out}$  that prevails when the input signal voltage  $Vin$  is constant becomes

$$V_{out} = Vin + V_{gs1}(I_1) - V_{gs2}(I_3) \quad (5)$$

**[0099]** The output-voltage range at this time becomes narrower than the voltage range between power supply voltage  $VDD$  and power supply voltage  $VSS$  by a voltage difference equivalent to at least the gate-source voltage  $V_{gs2}(I_3)$  of transistor 412. If currents  $I_1$  and  $I_3$  of constant-current sources 414 and 415, respectively, are controlled in such a manner that gate-source voltages  $V_{gs1}(I_1)$  and  $V_{gs2}(I_3)$  of transistors 411 and 412, respectively, become equal, then the output voltage  $V_{out}$  becomes a voltage equal to the input signal voltage  $Vin$  on the basis of Equation (5). Further, even if the transistor characteristic fluctuates, a highly precise voltage output can be produced, irrespective of this fluctuation, by setting the element sizes and currents  $I_1$  and  $I_3$  of the transistors 411 and 412 in such a manner that

$$V_{gs1}(I_1) - V_{gs2}(I_3)$$

will not change.

**[0100]** More specifically, a voltage output that is independent of threshold-voltage fluctuation of the transis-

tors can be produced by setting the element sizes of the transistors 411 and 412 and currents  $I_1$  and  $I_3$  so as to be equal, or by uniformizing the channel lengths of the transistors 411 and 412 and setting the currents  $I_1$  and  $I_3$  in accordance with the channel-width ratio. Further, if the current  $I_2$  of constant-current source 413 is controlled so as to become equal to the current  $I_1$  of constant-current source 414, the buffer circuits can be operated with ease even in case of a low current supplying capability for the external circuit that supplies the input signal voltage  $Vin$ . It should be noted that the buffer circuits can operate even in the absence of the constant-current source 413. In such case, however, it is required that the external circuit that supplies the input signals voltage  $Vin$  has a satisfactory current supply capability.