(11)

EP 2 207 060 A1

(12)

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

14.07.2010 Bulletin 2010/28

(51) Int Cl.:

**G02F 1/1343** (2006.01)      **G02F 1/1339** (2006.01)

**G02F 1/1362** (2006.01)      **G03F 7/20** (2006.01)

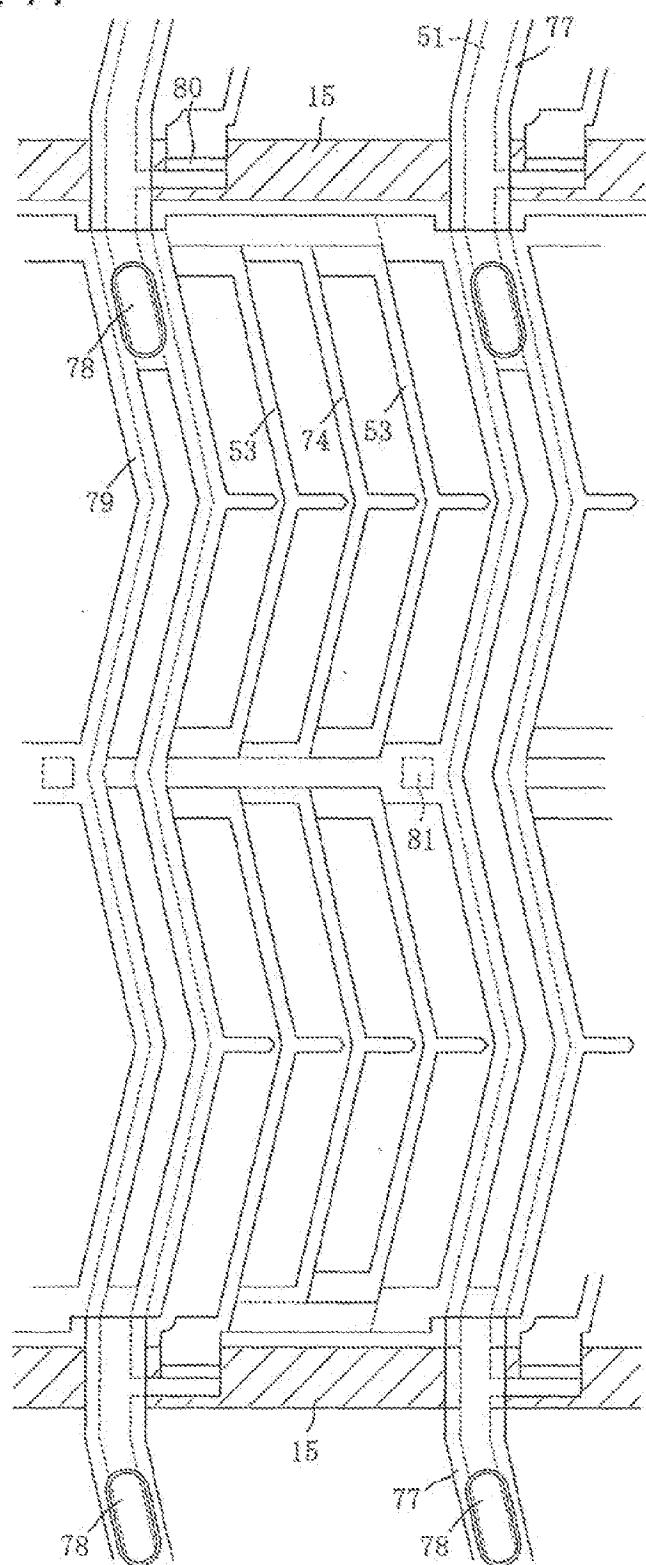

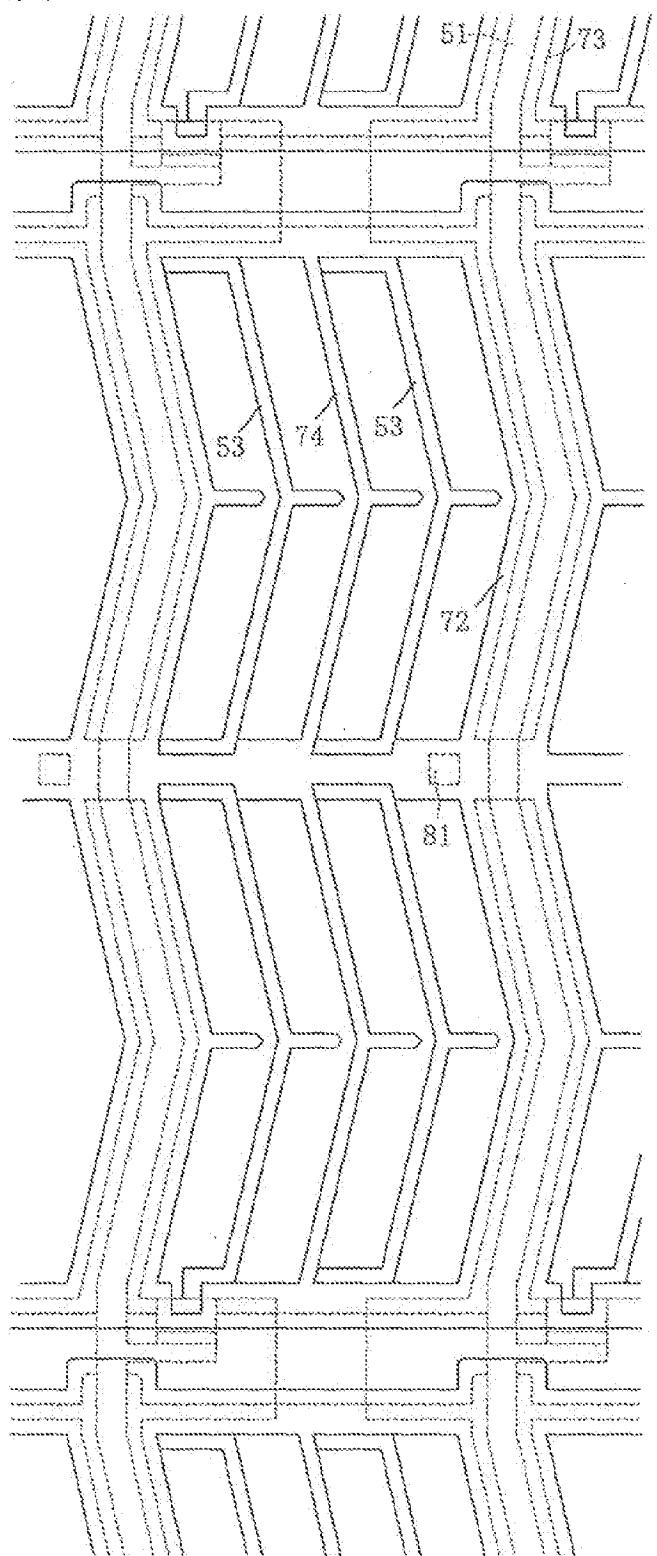

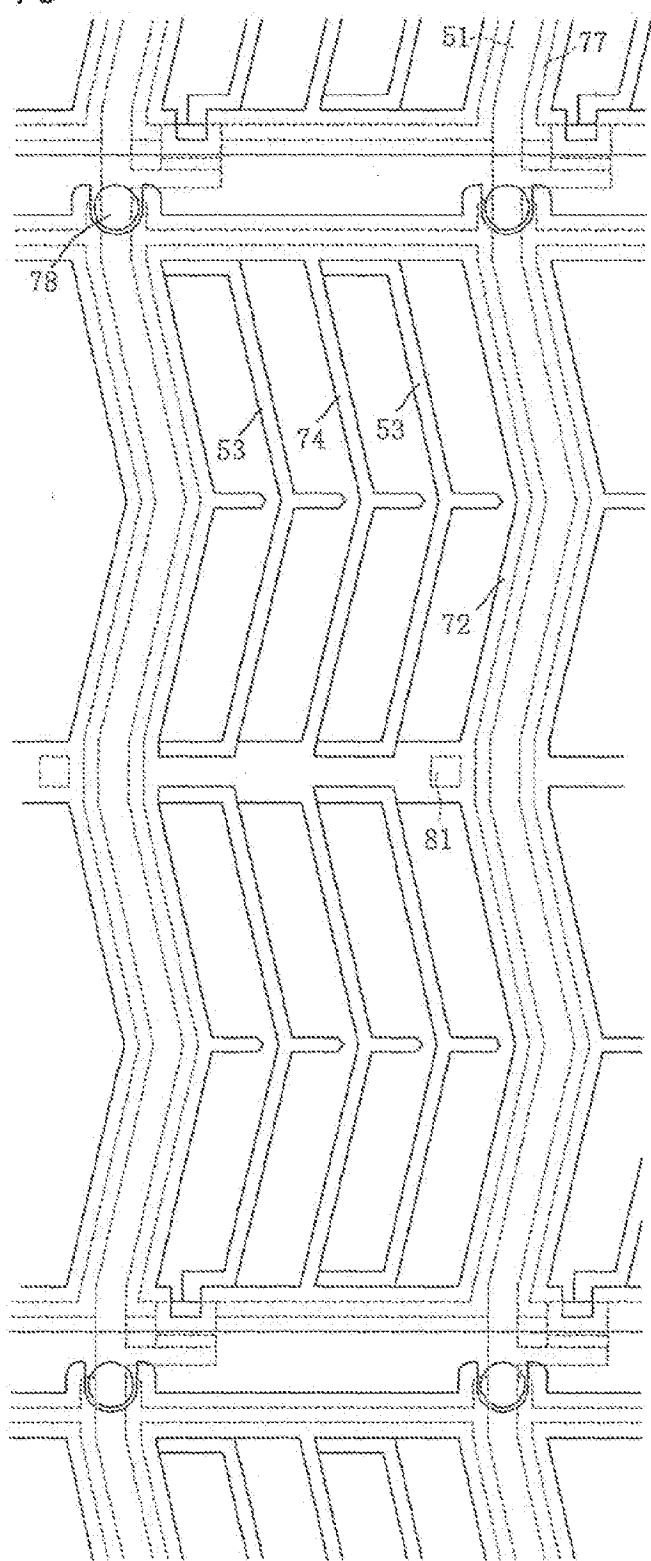

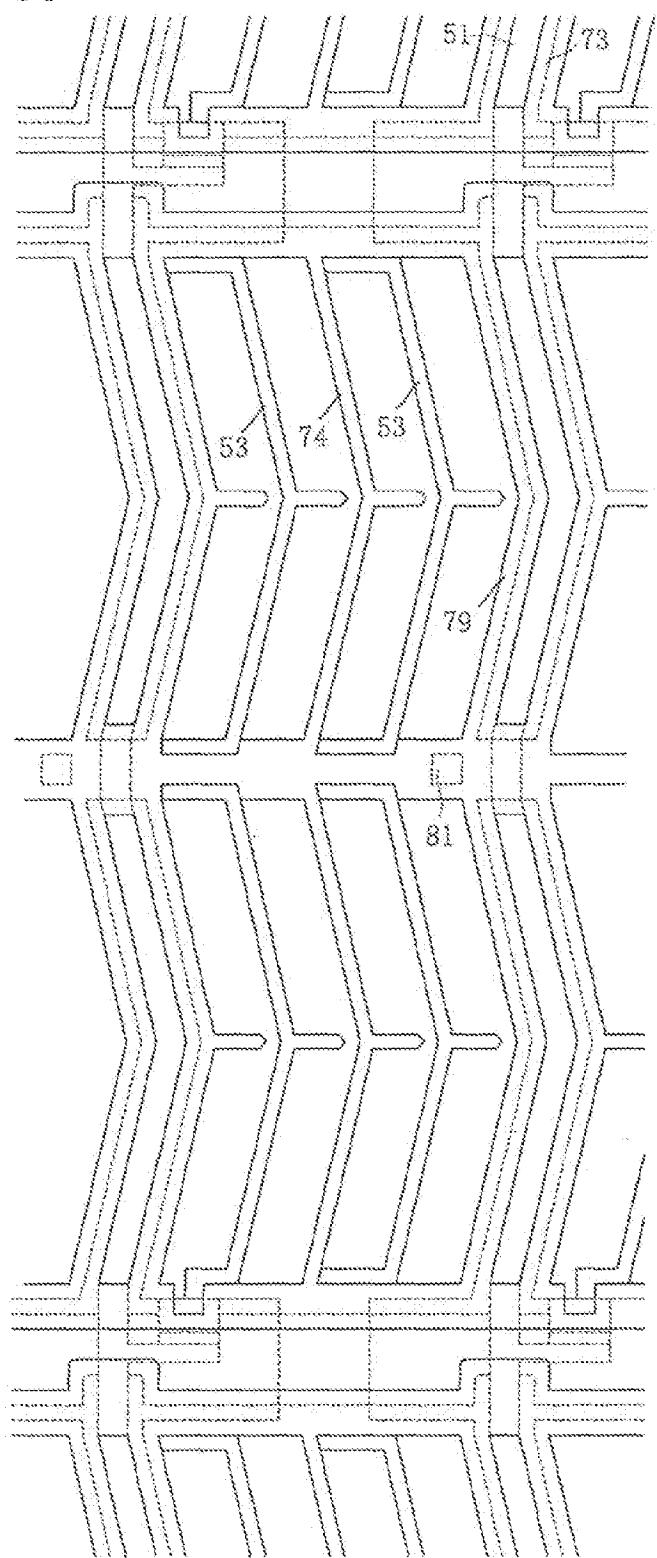

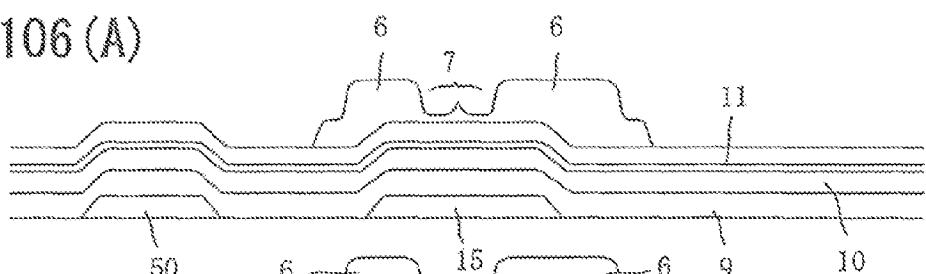

(21) Application number: 10161534.2

(22) Date of filing: 30.04.2004

(84) Designated Contracting States:

**GB**

(30) Priority: 14.05.2003 JP 2003185823

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC:

**06025254.1 / 1 760 518**

**04010322.8 / 1 480 072**

(71) Applicant: **Obayashiseikou Co., Ltd.**

**Toyokawa-City,**

**Aichi-Pref. 442-0068 (JP)**

(72) Inventor: **Hirota, Naoto**

**Toyokawa-City**

**Aichi 442-0068 (JP)**

(74) Representative: **Prüfer & Partner GbR**

**European Patent Attorneys**

**Sohnckestraße 12**

**81479 München (DE)**

### Remarks:

This application was filed on 29-04-2010 as a divisional application to the application mentioned under INID code 62.

### (54) High quality and ultra large screen liquid crystal display device and production method thereof

(57) A large screen liquid crystal display device using a transverse electric field system which is capable of dramatically improving an aperture ratio, a transmittance ratio, brightness, and contrast with low cost and high production yield. For example, the width of the common electrodes that shield the electric fields of the video signal lines can be decreased dramatically and the aperture

ratio can be improved dramatically. Especially, the bumps covering the video signal lines can be used along with the spacers, and with the use of halftone exposure method, the bumps covering the video signal lines and the spacers can be constructed at the same time, which dramatically shortens the time required for the production process.

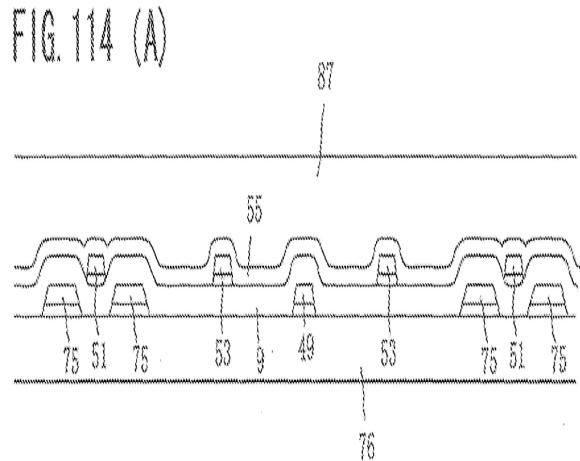

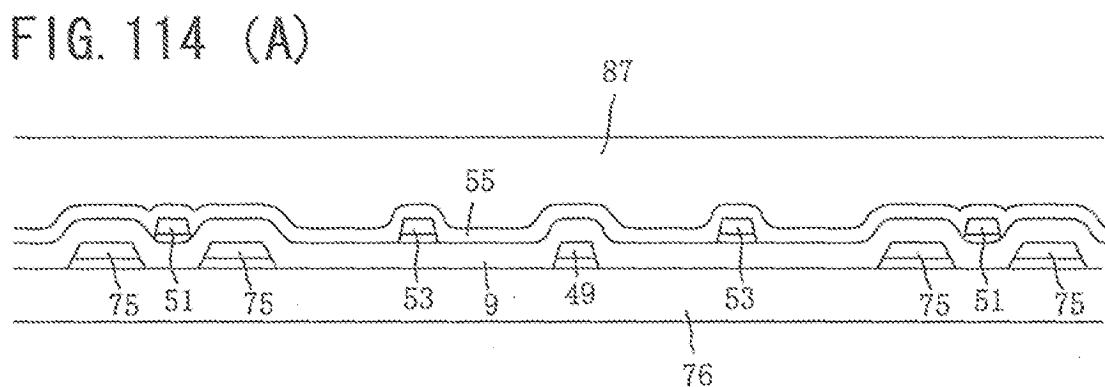

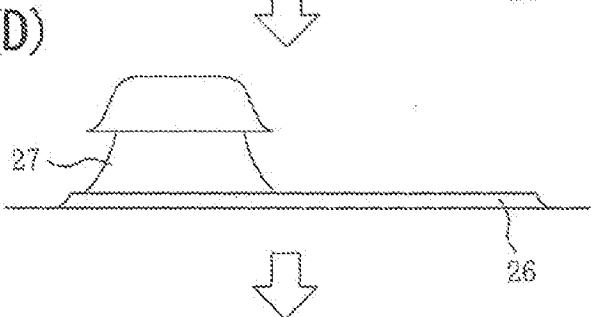

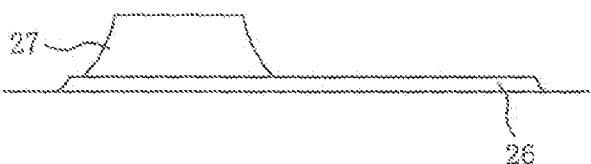

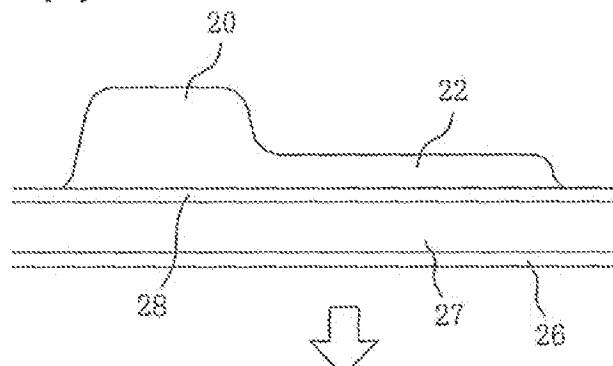

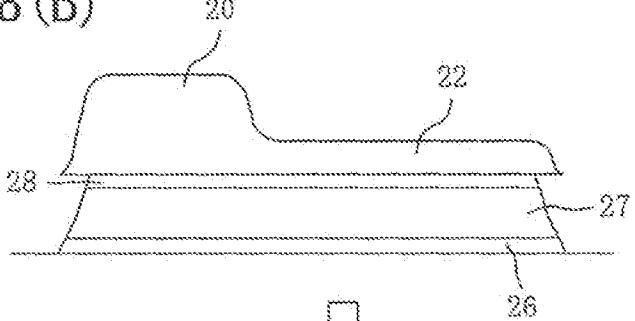

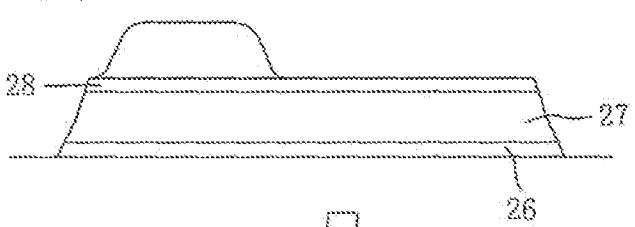

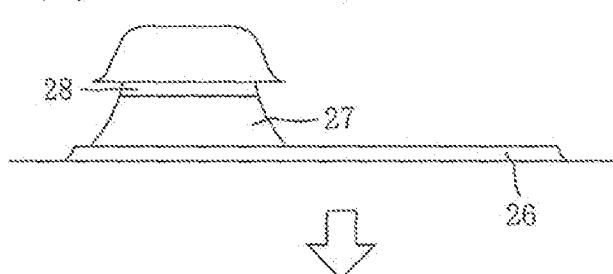

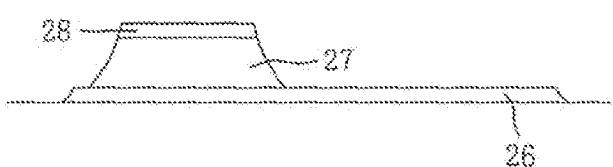

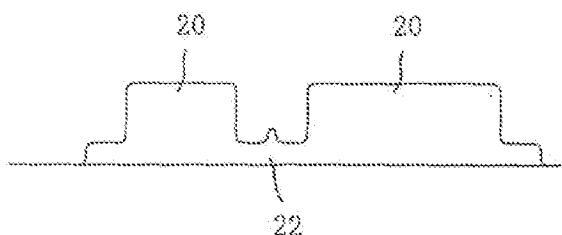

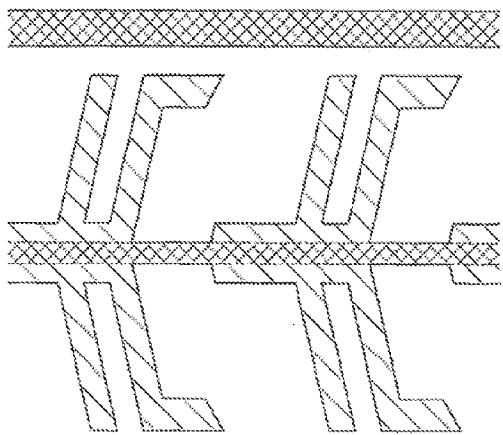

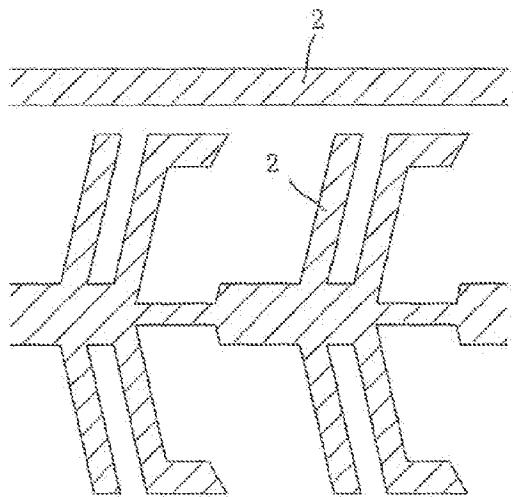

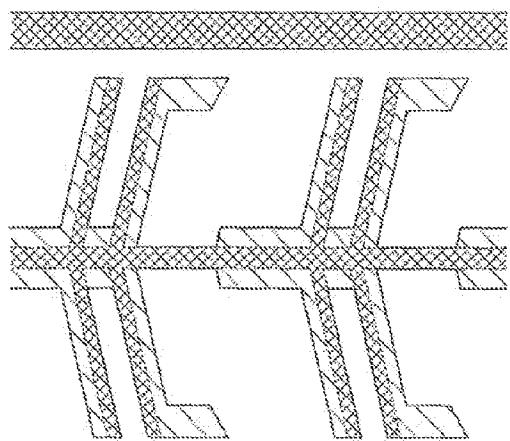

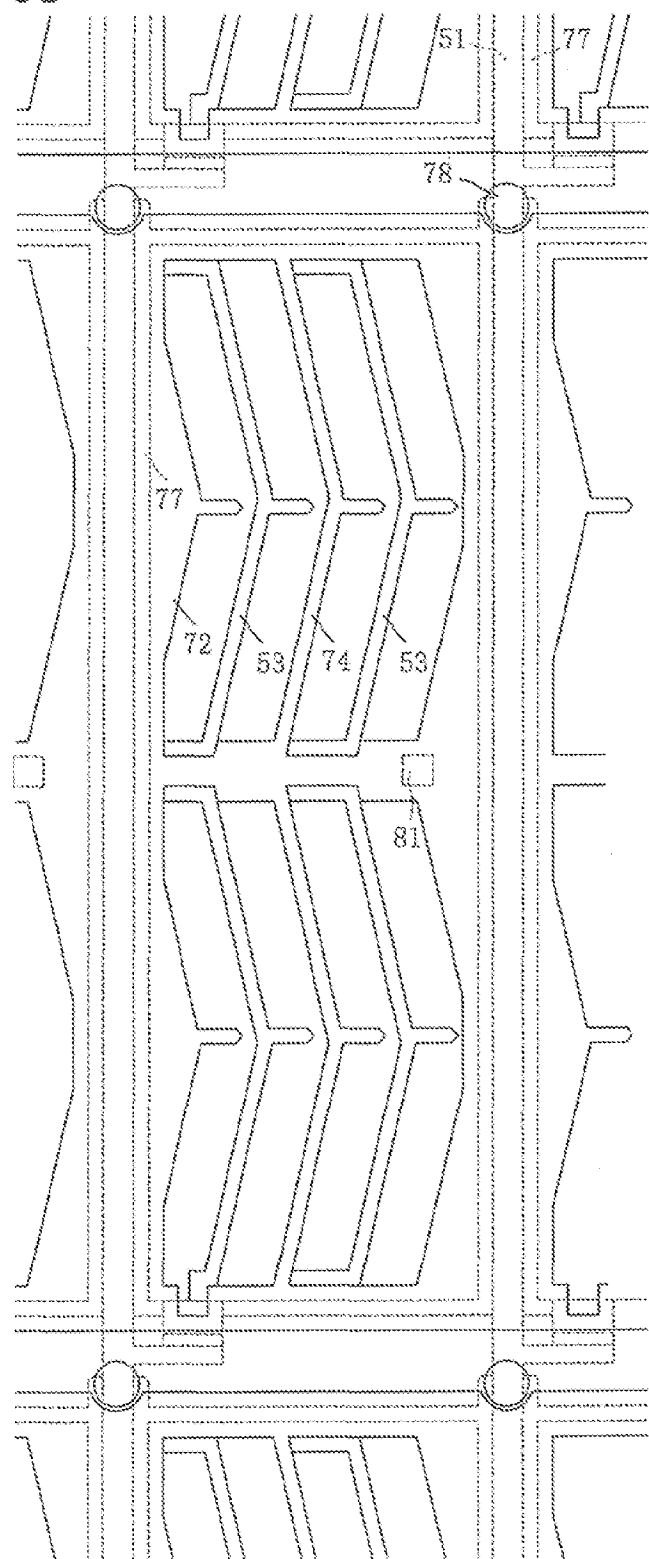

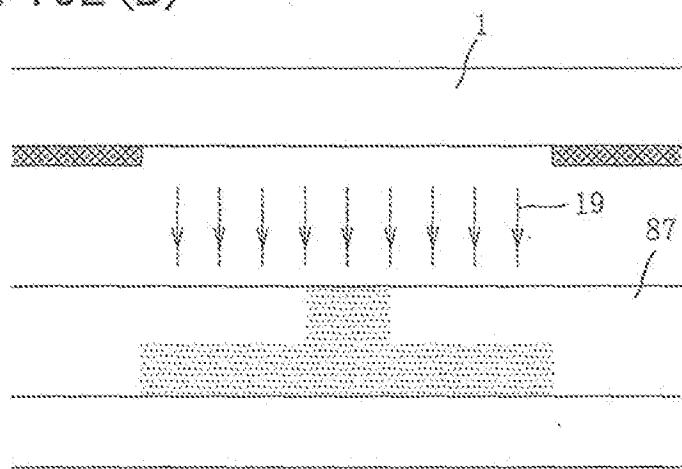

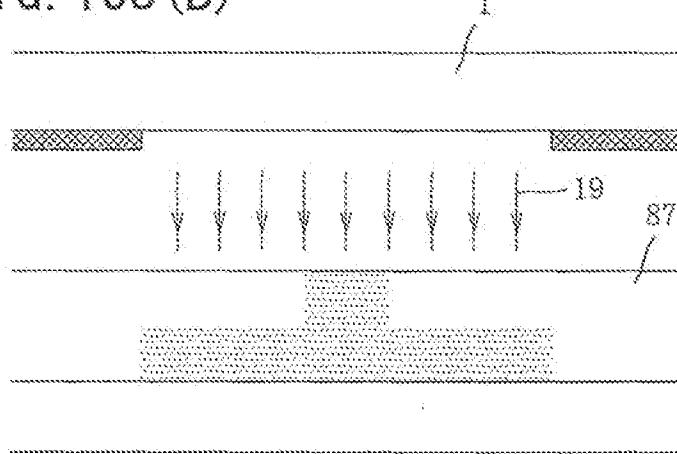

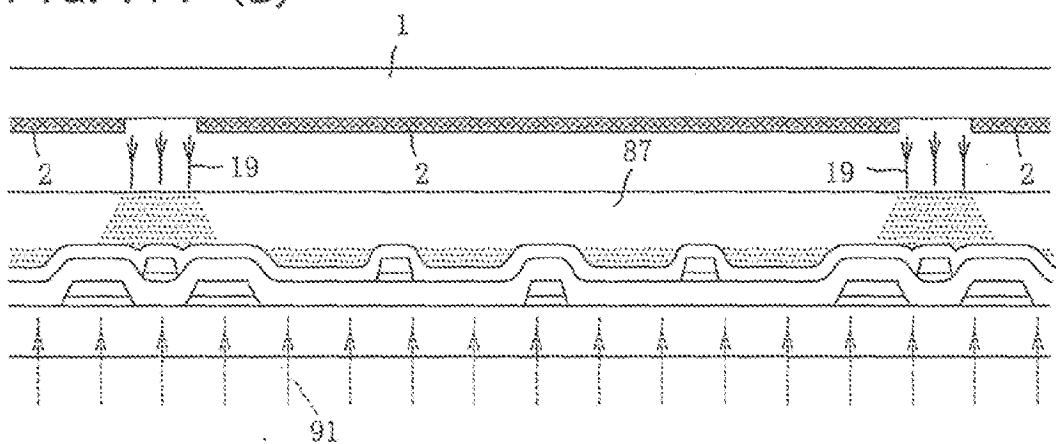

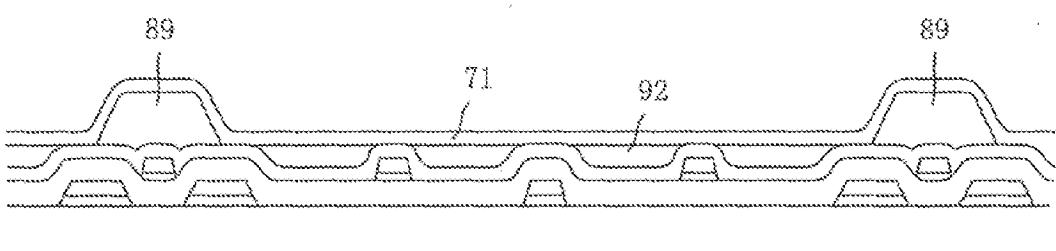

FIG. 114 (B)

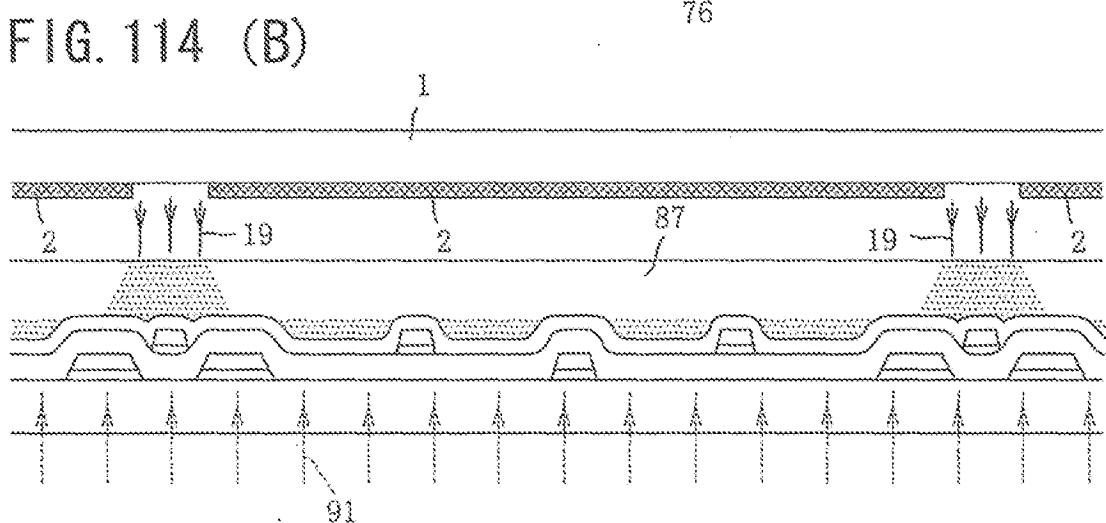

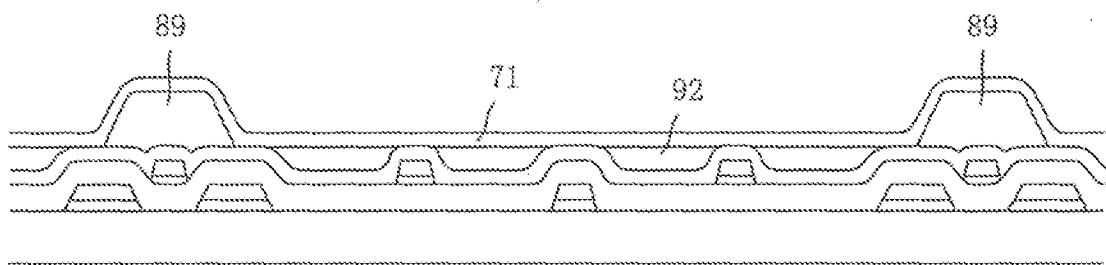

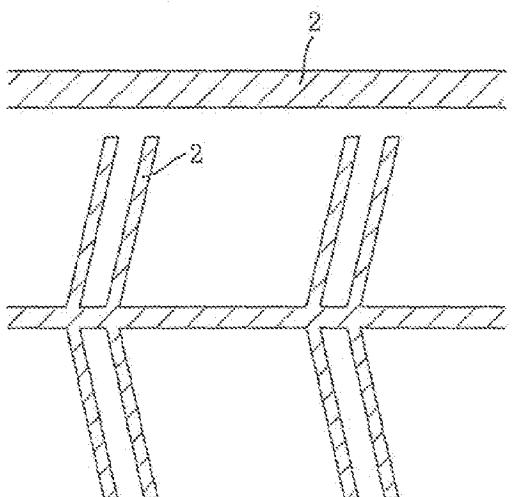

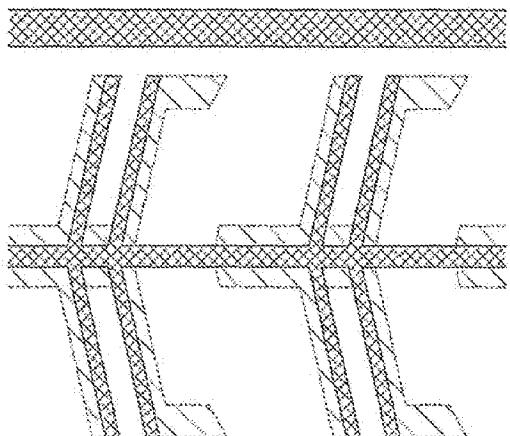

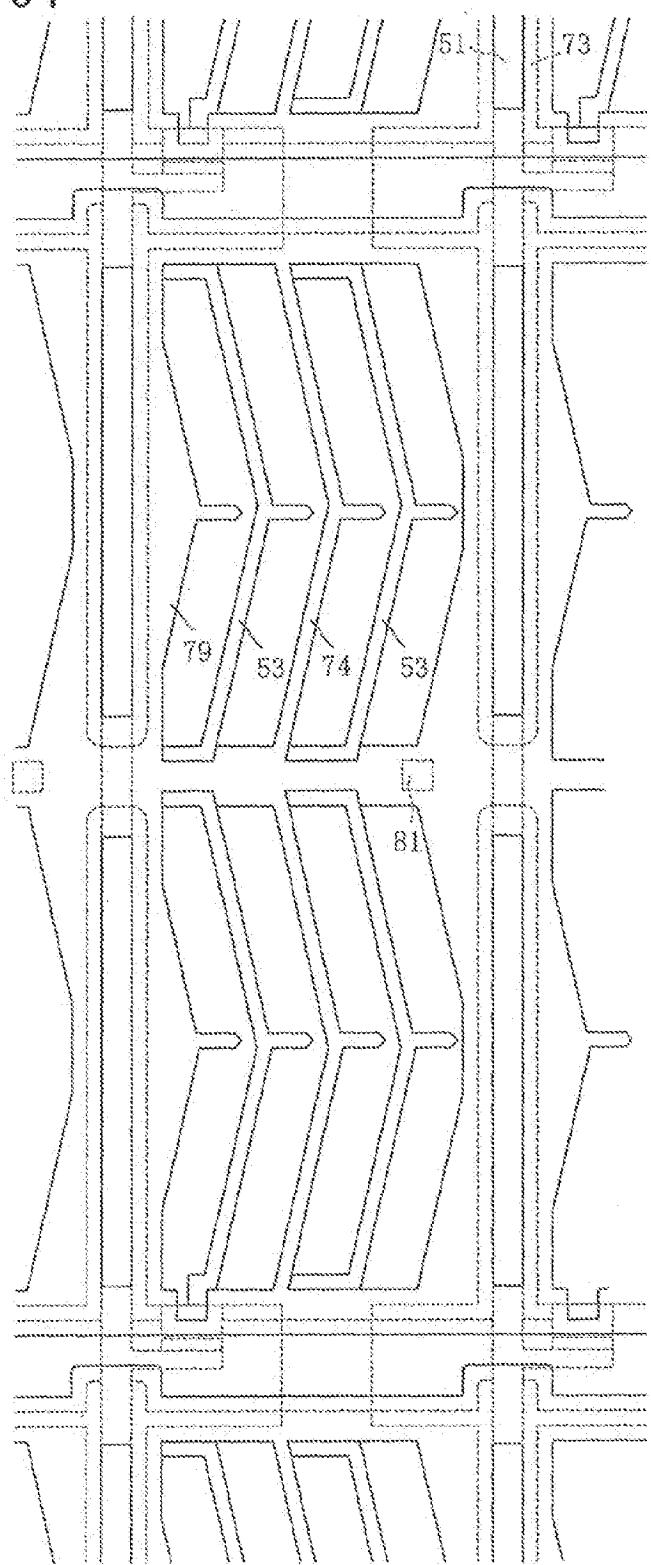

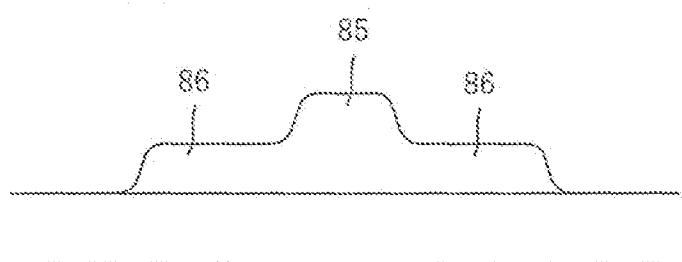

FIG. 114 (C)

## Description

### FIELD OF THE INVENTION

**[0001]** This invention relates to a liquid crystal display device using a transverse electric field system, and more particularly, to an ultra large screen liquid crystal display device which is capable of dramatically improving an aperture ratio, a transmittance ratio, brightness, and contrast with low cost and high production yield.

### BACKGROUND OF THE INVENTION

**[0002]** A liquid crystal display device utilizing a transverse electric field system which applies an electric field to a liquid crystal in a parallel direction with a substrate has a wide viewing angle and is the standard for a large screen liquid crystal display. Such technologies have been proposed, for example, by Japanese patent laid-open publication Nos. 10-55000, 10-325961, 11-24104, 10-55001, 10-170939, and 11-52420, and have been improved to solve problems such as vertical crosstalk.

**[0003]** Numerous technologies have been proposed by liquid crystal makers including a technology in which a photolithography spacer is utilized to improve the contrast of a transverse electric field type liquid crystal display system. For example, such a technology has been proposed by Japanese patent laid-open publication Nos. 2000-199904 and 2000-19527. The majority of them utilize a photolithography technology to establish a spacer on a color filter substrate.

**[0004]** The Japanese patent laid-open publication Nos. 2000-19527 and 2000-199904 show an idea of producing an electric field of a video signal line in a vertical direction of a substrate rather than a horizontal direction in order to suppress the vertical crosstalk. This requires the dielectric constant of the photolithography spacer to be larger than the dielectric constant of the liquid crystal. The Japanese patent laid-open publication No. 2000-19526 also proposed a photolithography spacer in which the dielectric constant is larger than that of the liquid crystal.

**[0005]** The Japanese patent laid-open publication No. 2001-209053 proposes a photolithography spacer in a vertical electric field system utilising dielectric material with a smaller dielectric constant than that of the liquid crystal along a video signal line to cover the video signal line in order to lower the waveform distortion. According to this patent publication, the liquid crystal cell is constructed by creating a vacuum space inside the liquid crystal cell, then injecting the liquid crystal in the space through an injection opening using the atmospheric pressure. In this liquid crystal injection method, a batch process is used in which several hundred cells are processed at the same time to produce a large liquid crystal panel.

**[0006]** Japanese patent laid-open publication Nos. 2002-258321 and 2002-323706 teach a structure using a dielectric material of a smaller dielectric constant than

that of the liquid crystal along the video signal line to cover the video signal line and placing a transparent conductive material along the video signal line to improve the pixel aperture ratio as well as to prevent signal delay.

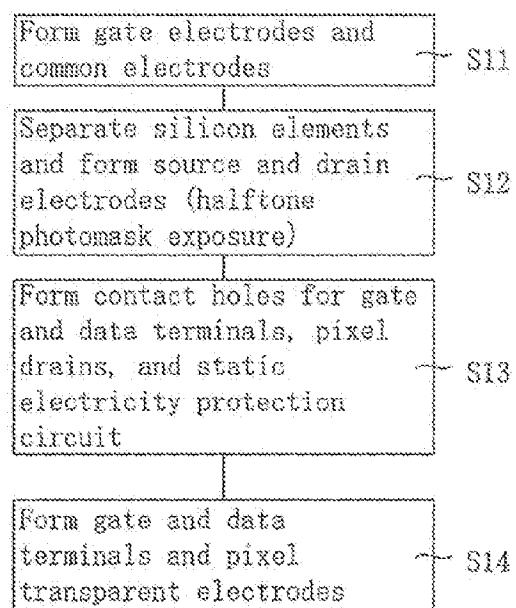

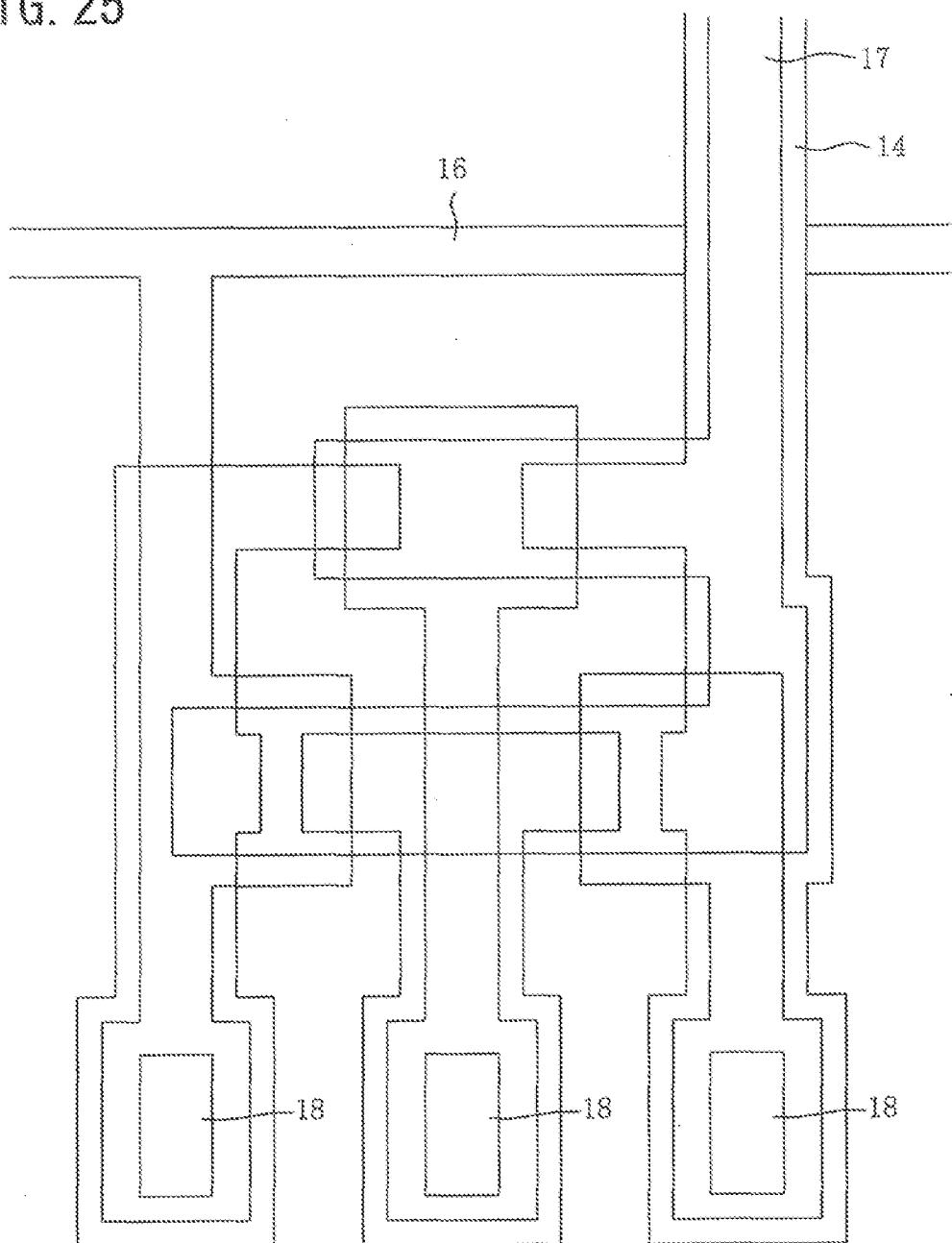

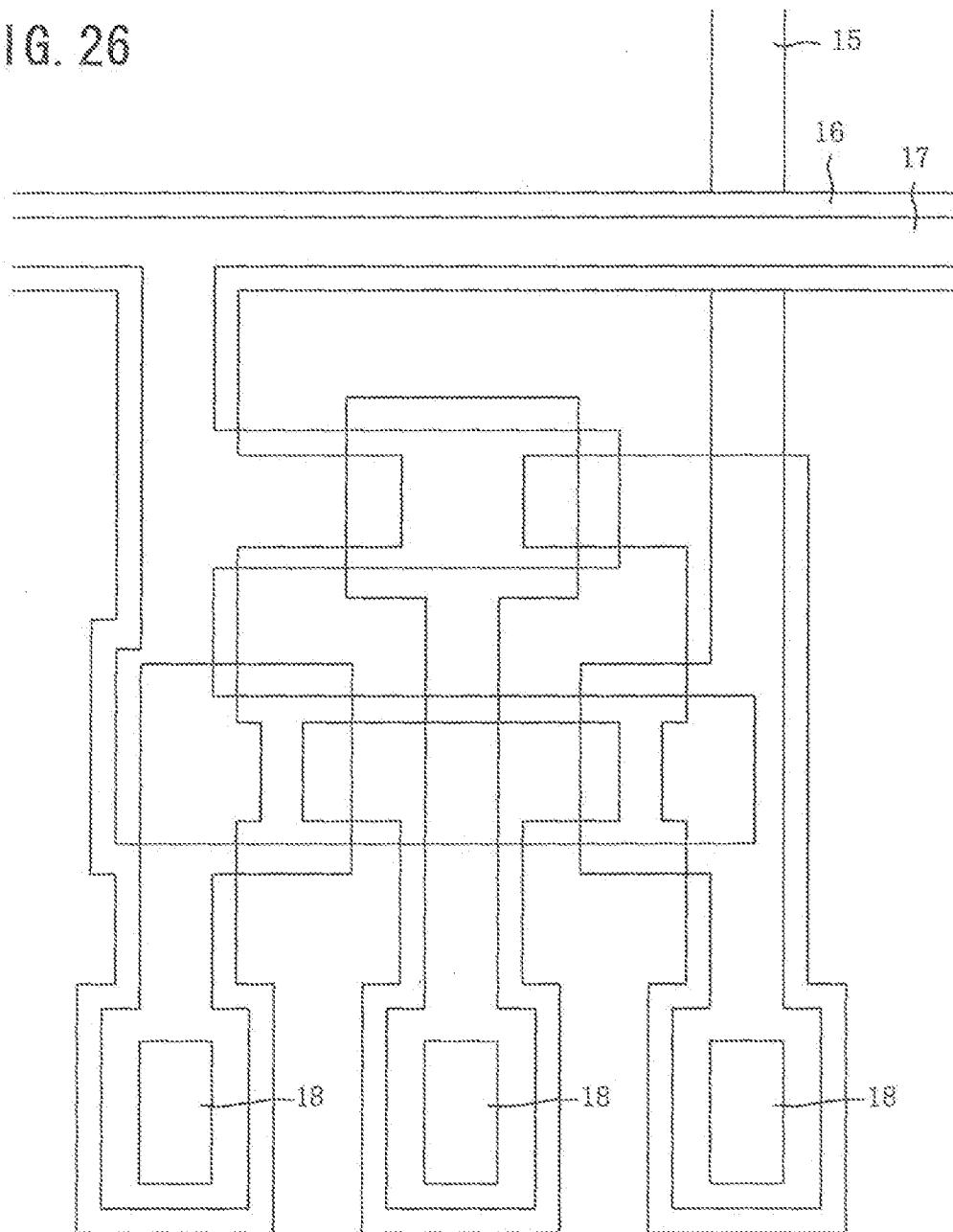

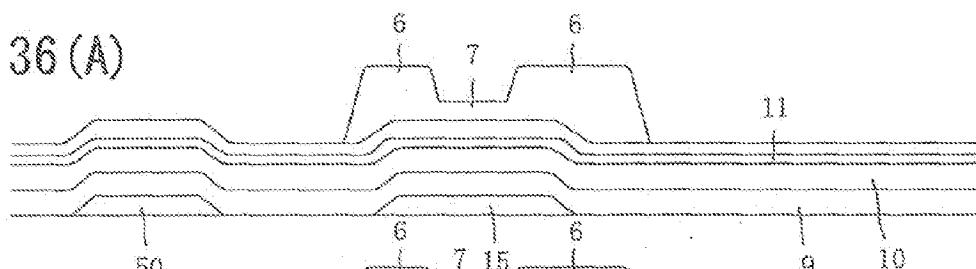

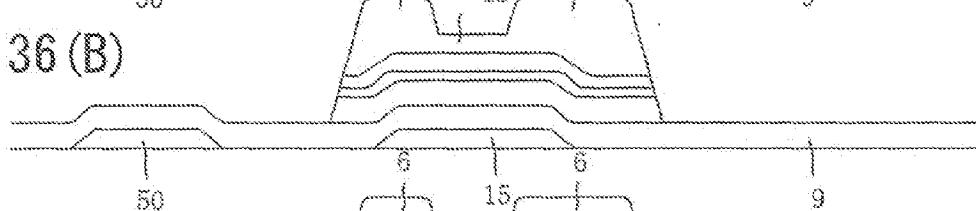

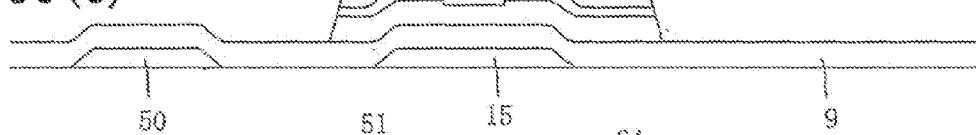

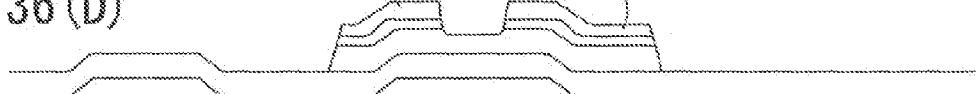

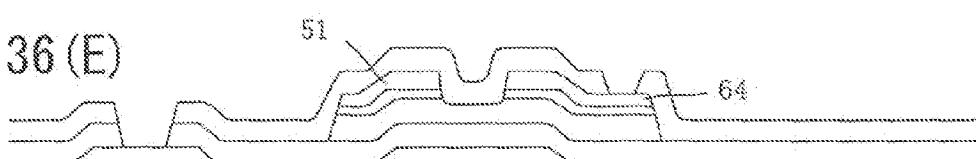

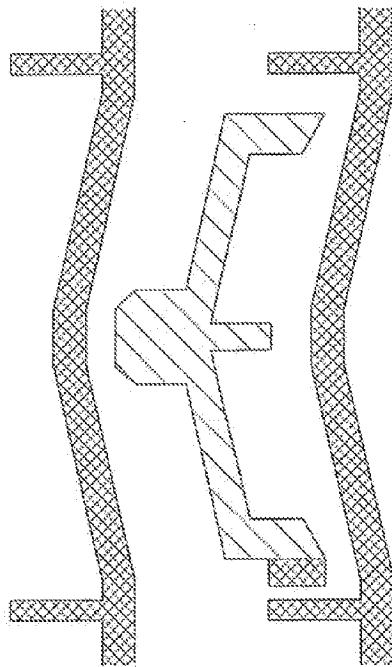

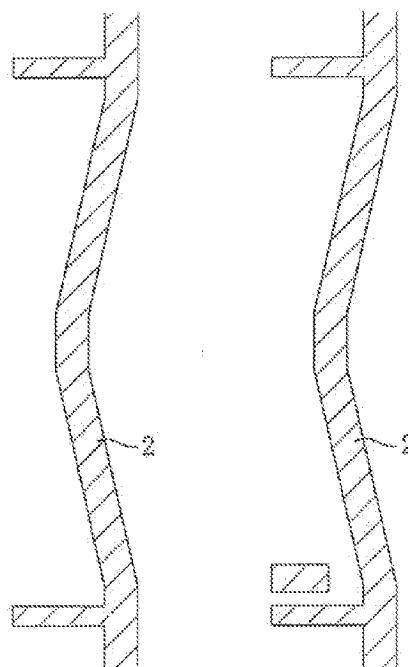

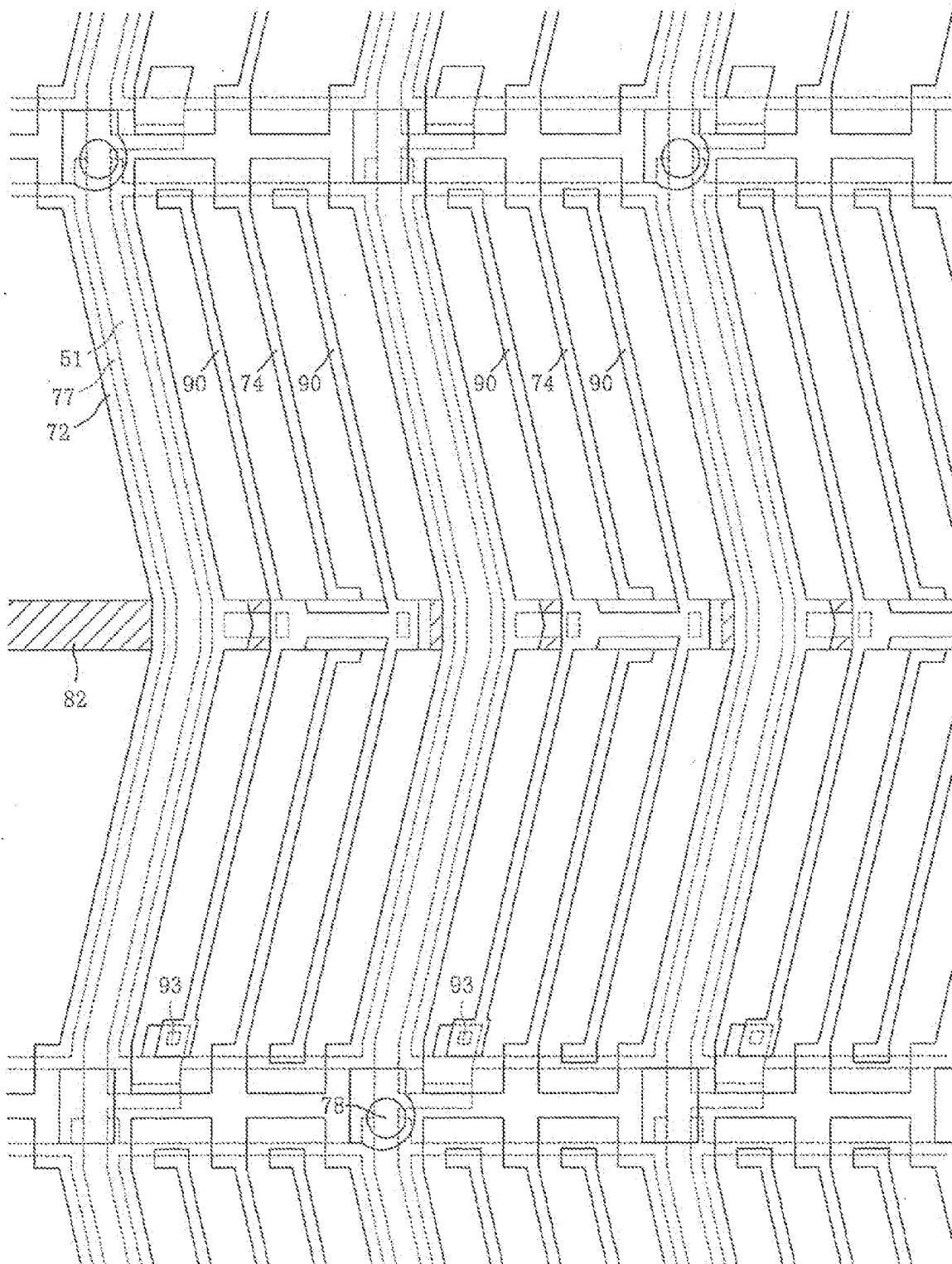

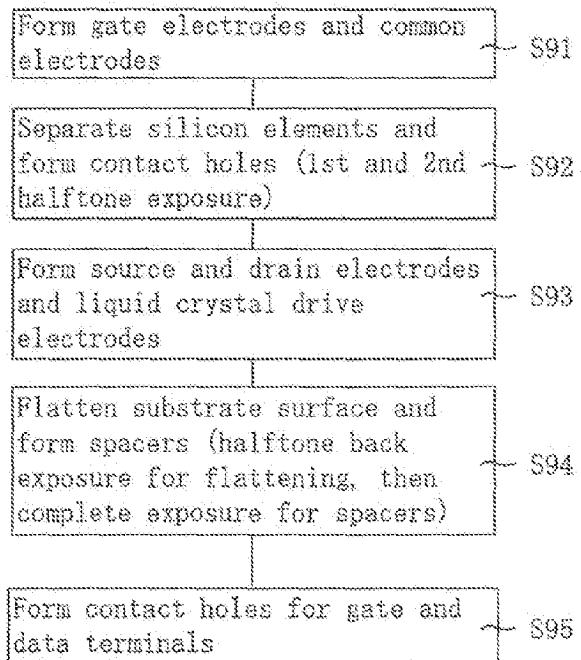

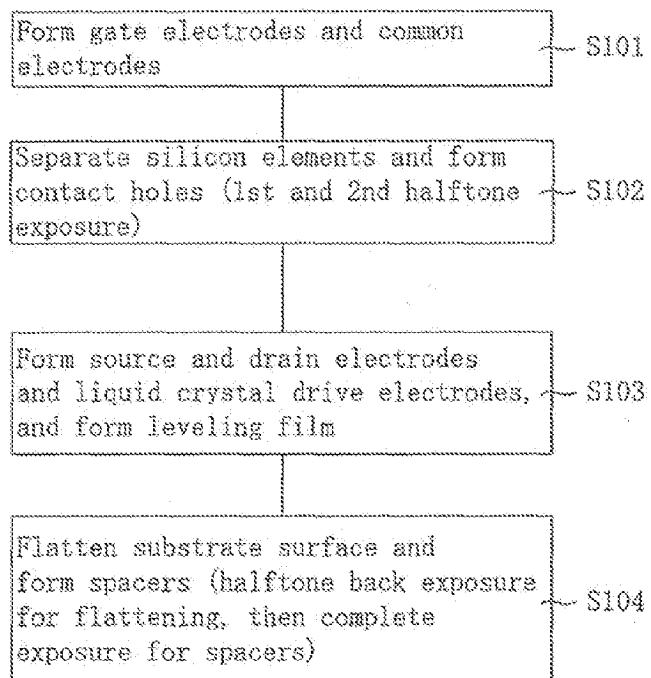

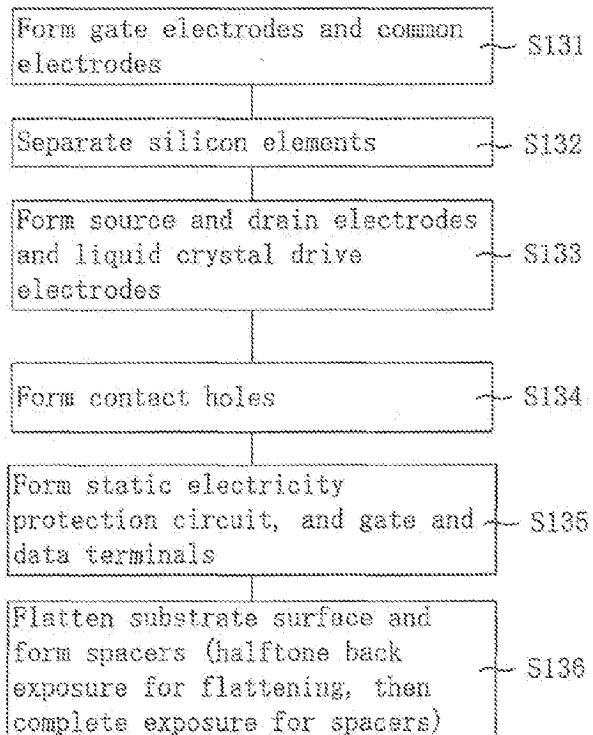

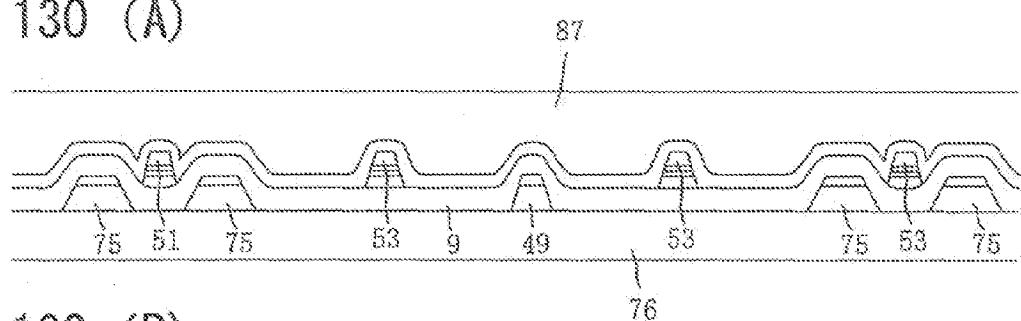

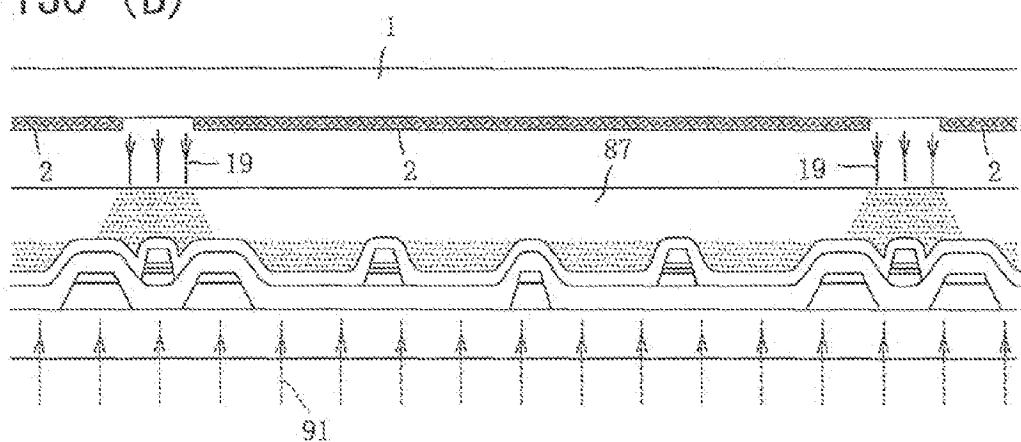

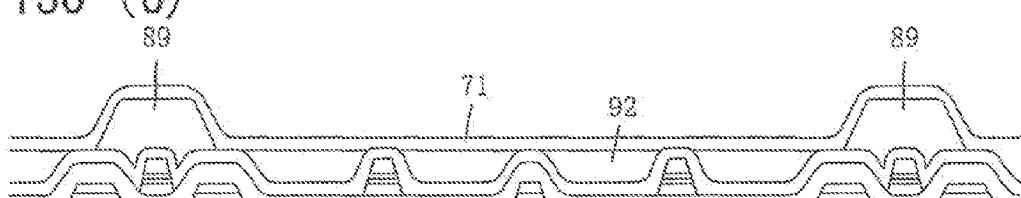

**[0007]** Figure 3 is a flow chart showing a typical production process in the conventional technology for producing a TFT (thin film transistor) array substrate (active matrix substrate) of the transverse electric field type liquid crystal panel. This production process includes four-step photomasking processes using the conventional halftone exposure technology. Figures 36A-36F are cross sectional views showing the structural developments in accordance with the production flow of Figure 3 using the four-step photomasking technology.

**[0008]** In the conventional production process of Figure 3, gate electrodes of thin film transistors and common electrodes are formed at the same time in step S11. Then, at step S12, thin film transistors are separated from a semiconductor layer and source electrodes and drain electrodes of the thin film transistors are formed using the halftone photomask exposure. In step S13, contact holes for gate terminals, data terminals, pixel drain portions, and transistor circuits for electrostatic protection are created. Then, at step S14, gate terminals, data terminals, transparent conductive pixel electrodes are formed.

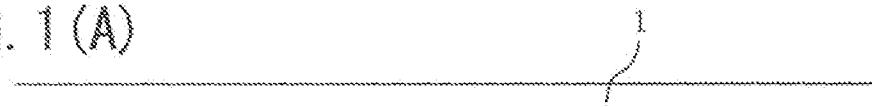

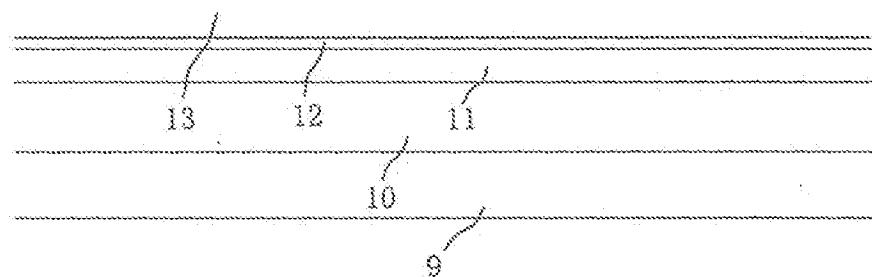

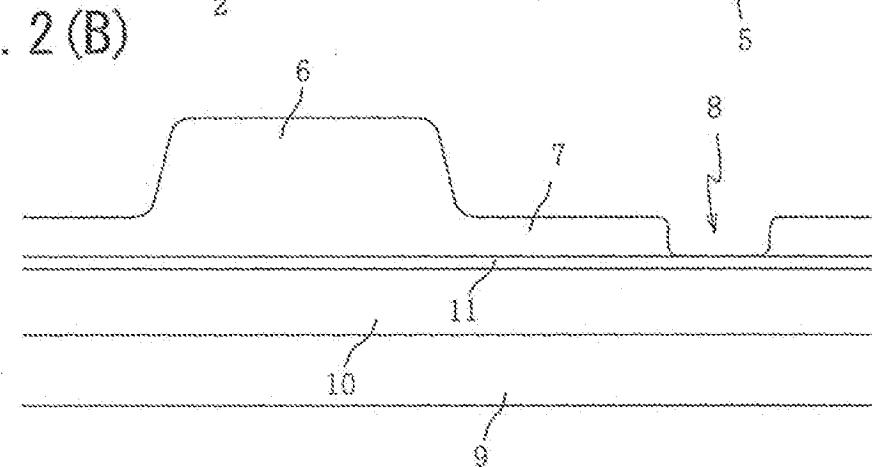

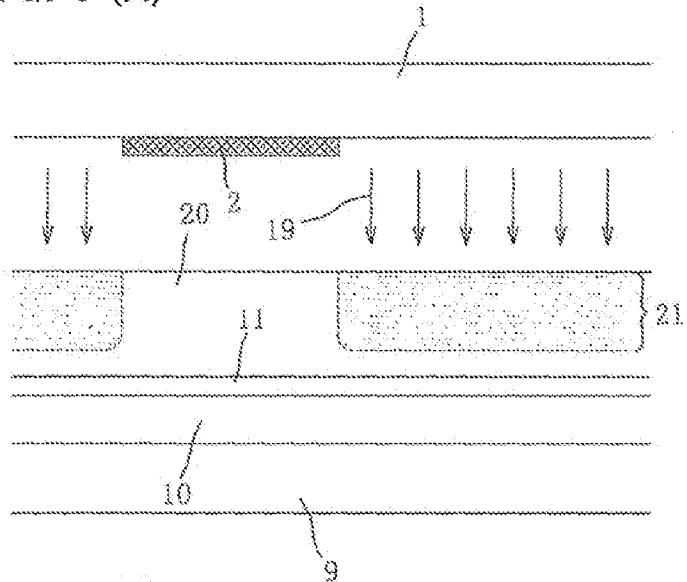

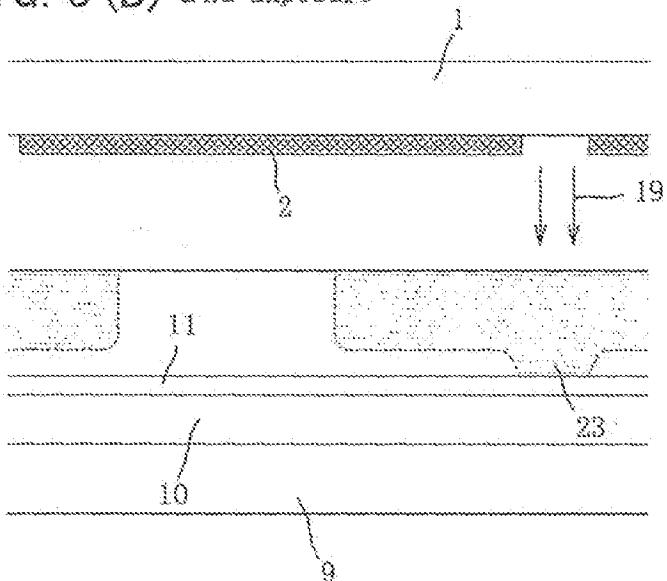

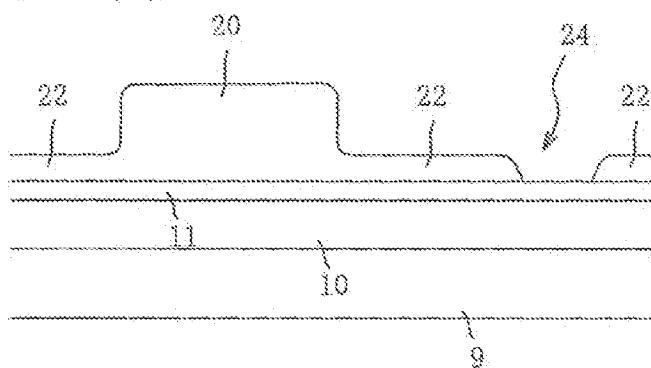

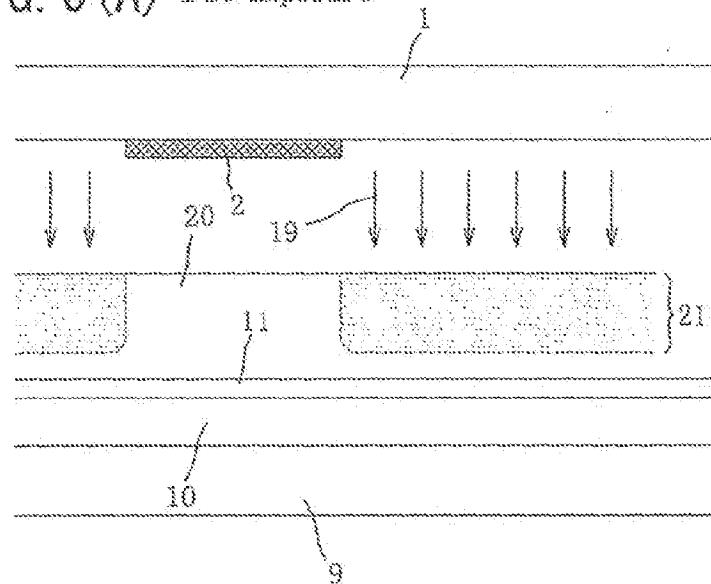

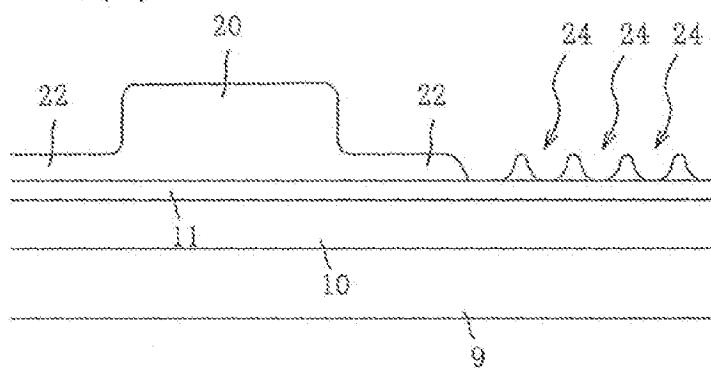

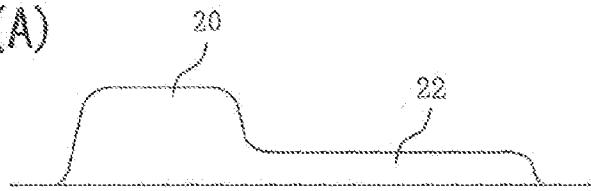

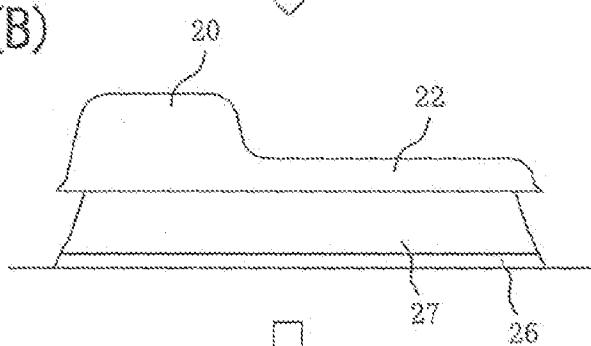

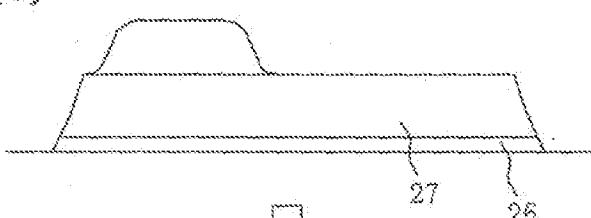

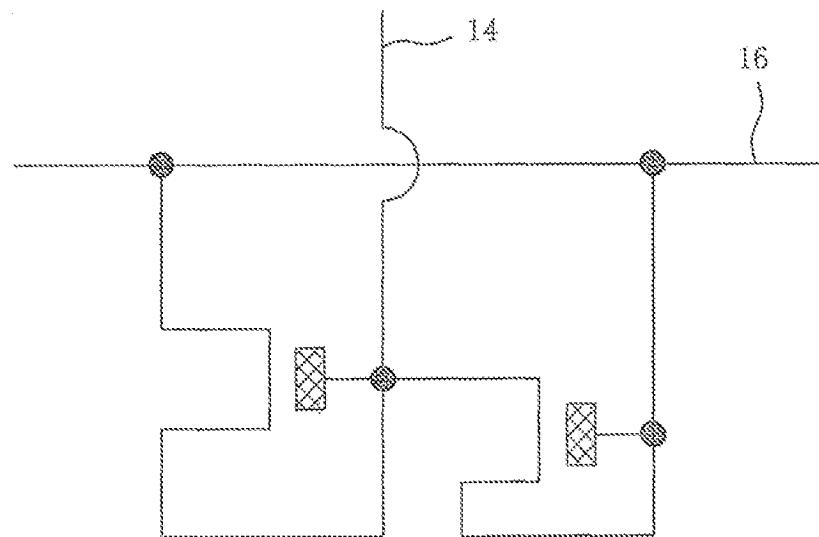

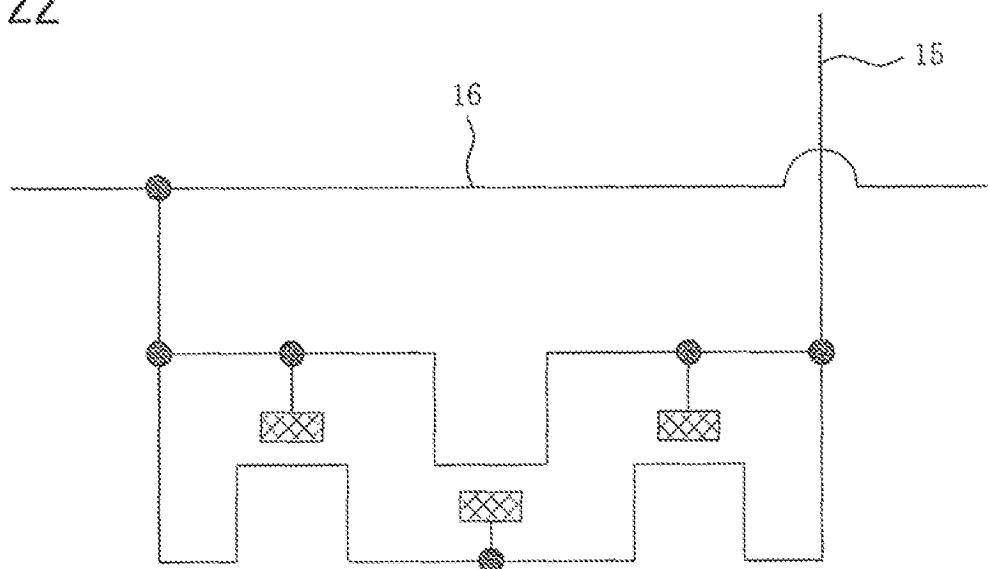

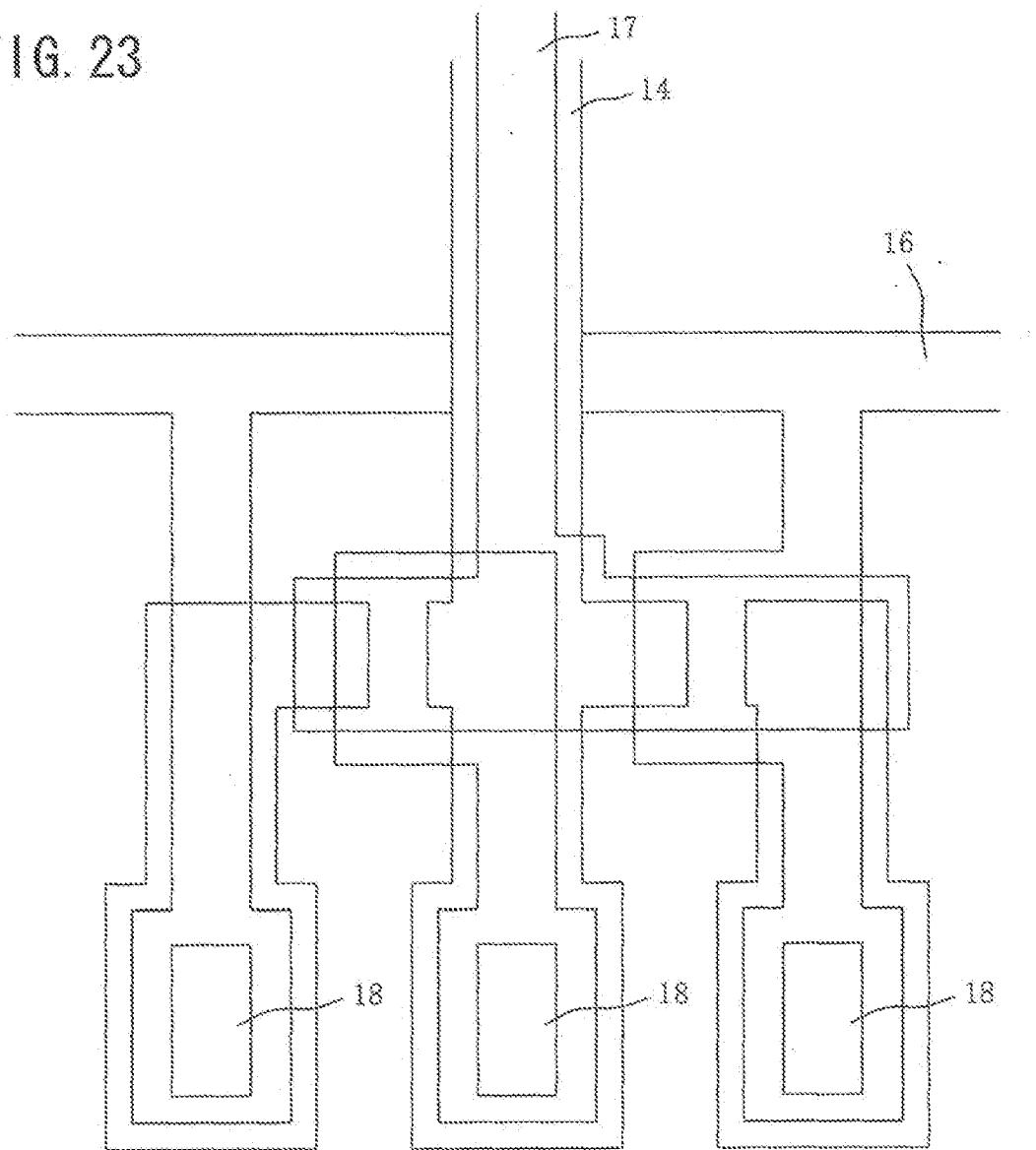

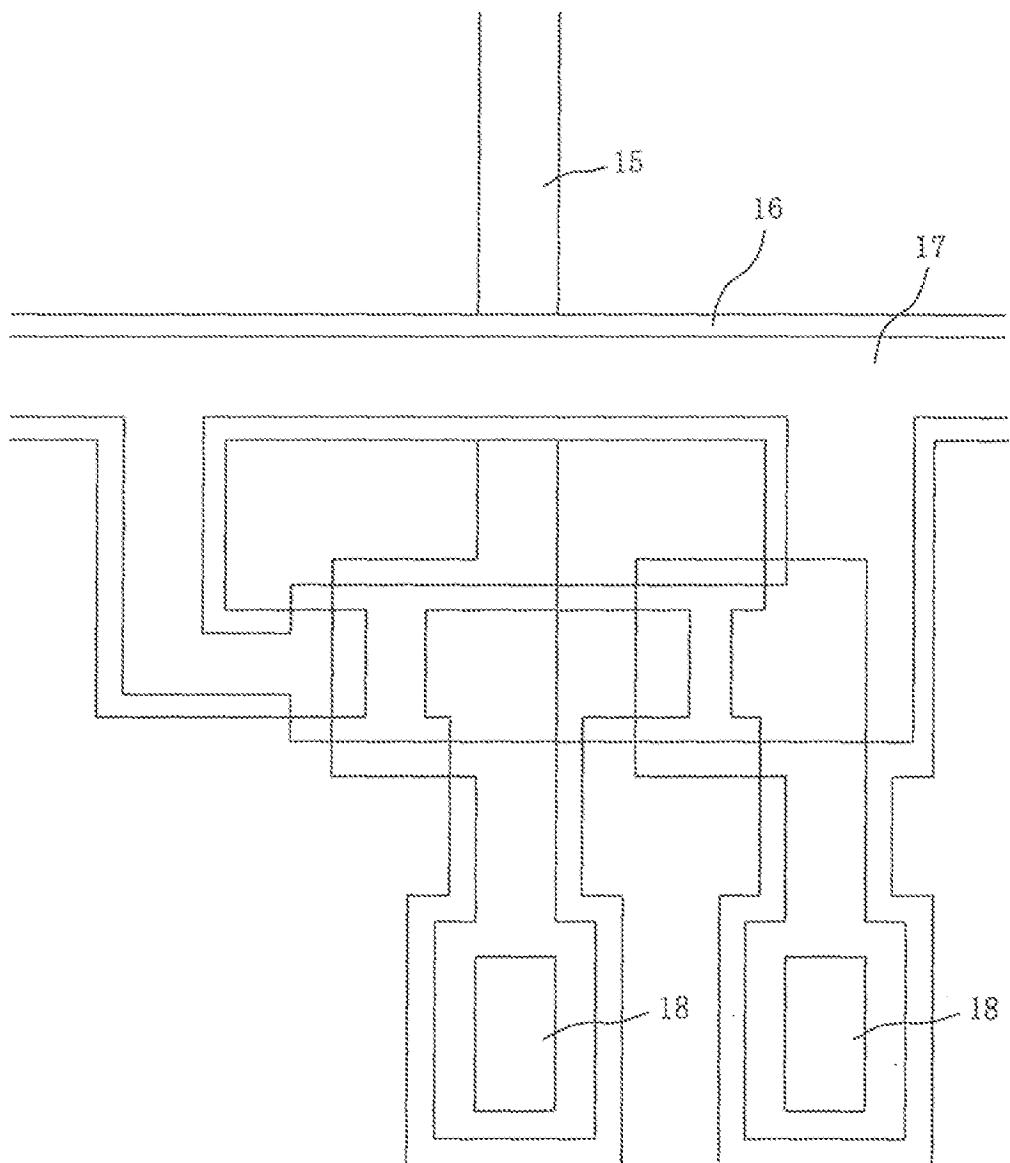

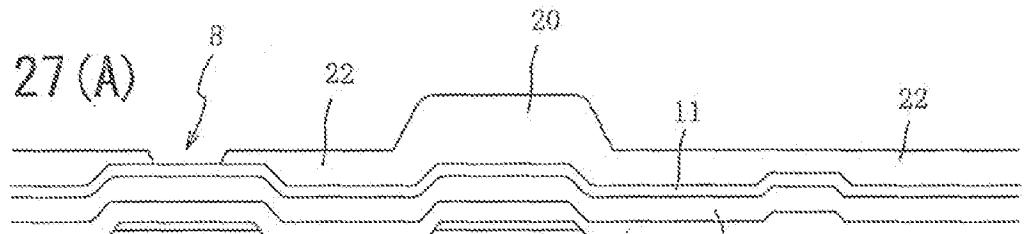

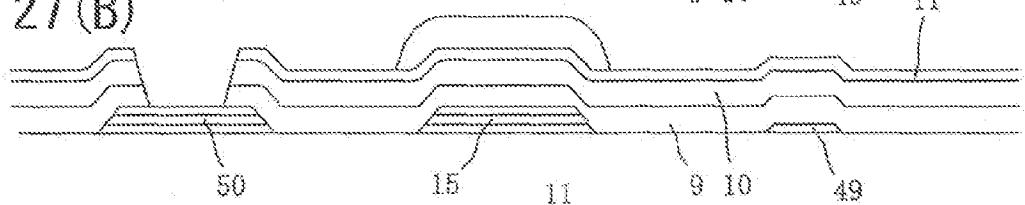

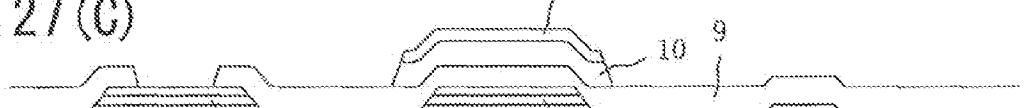

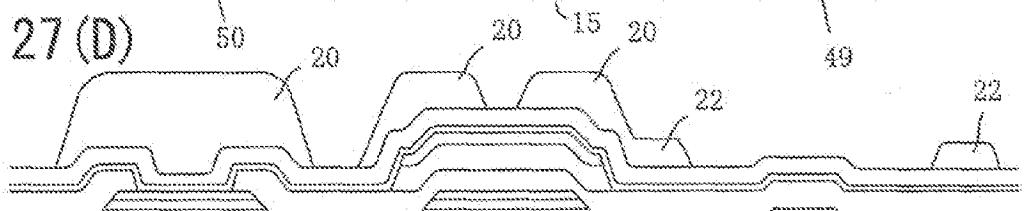

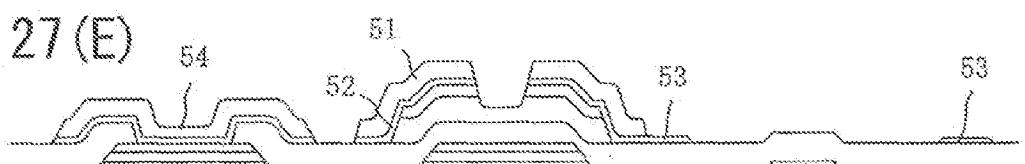

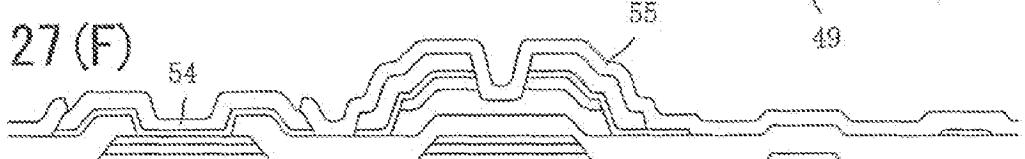

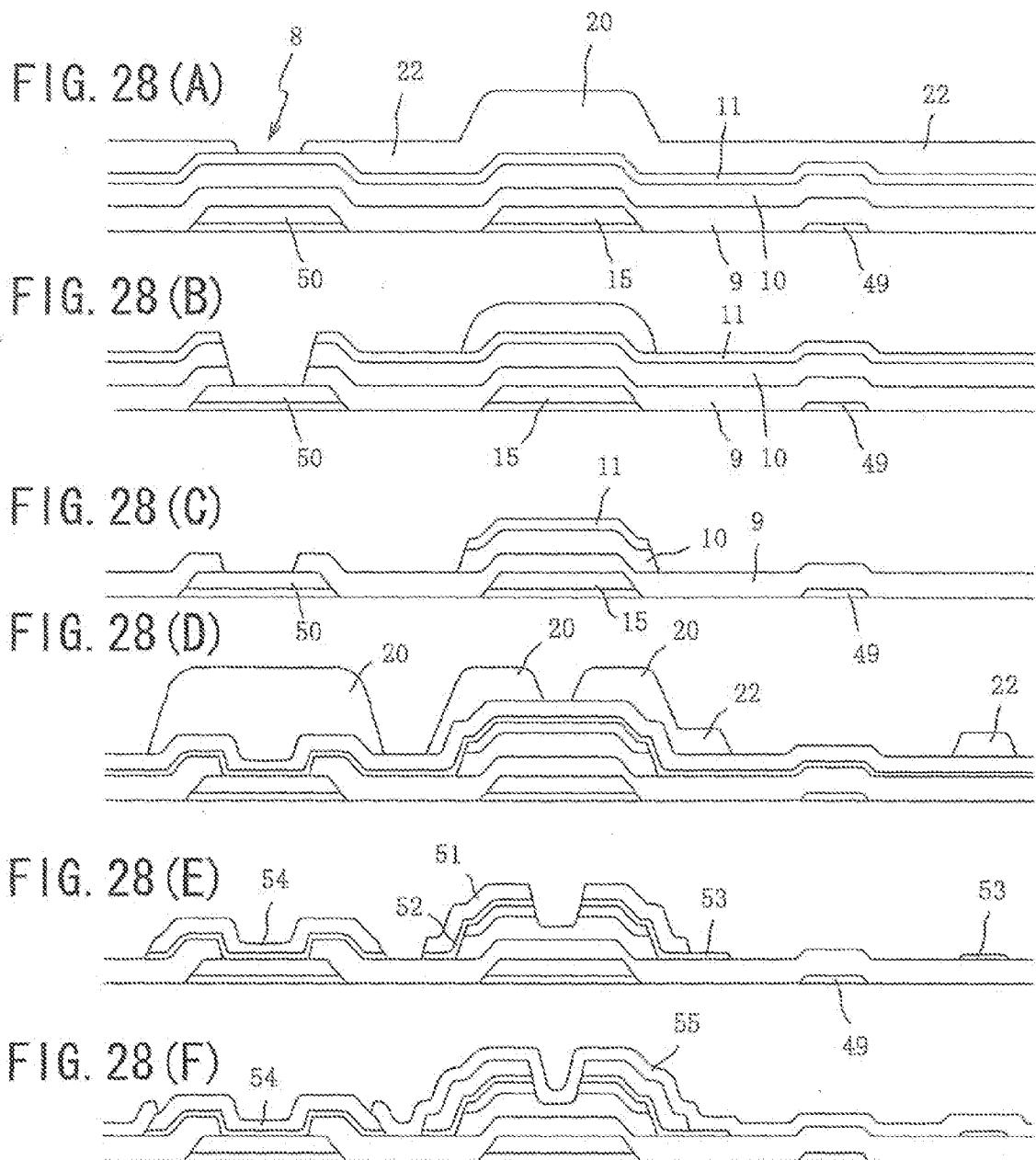

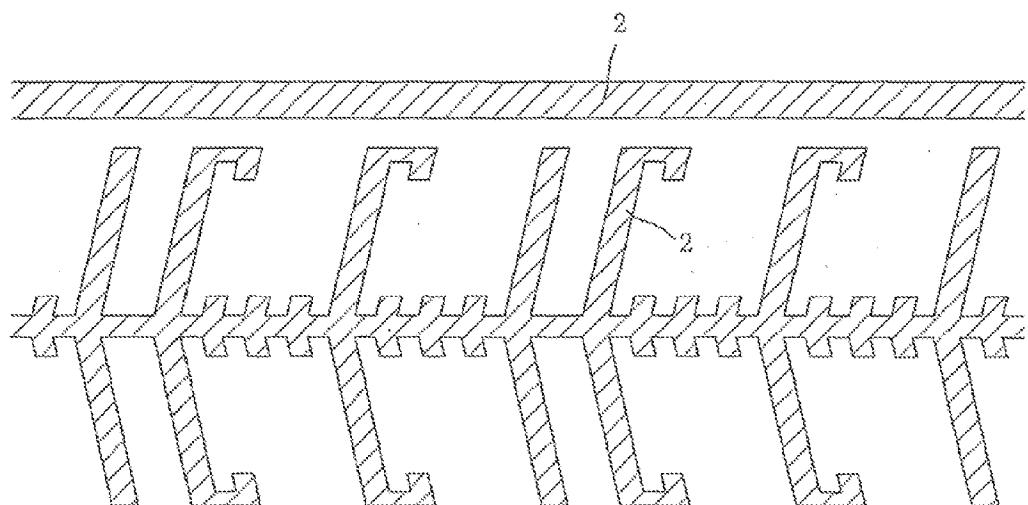

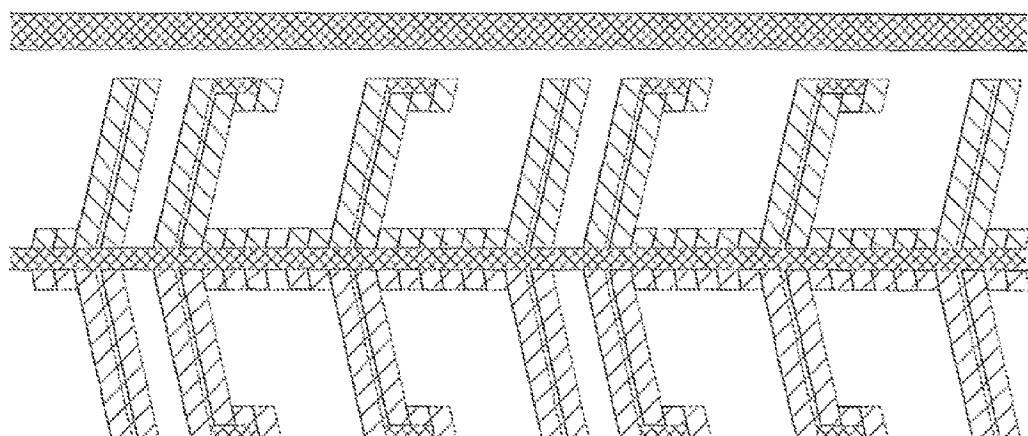

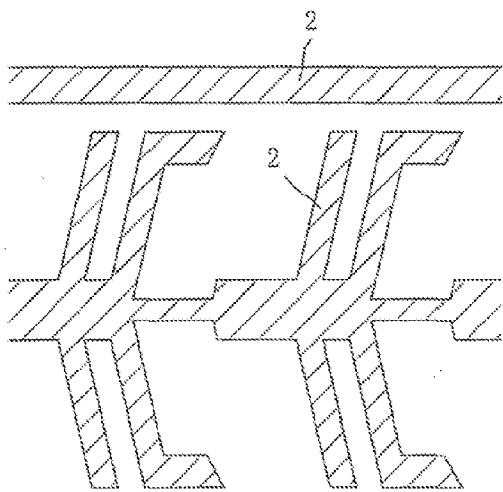

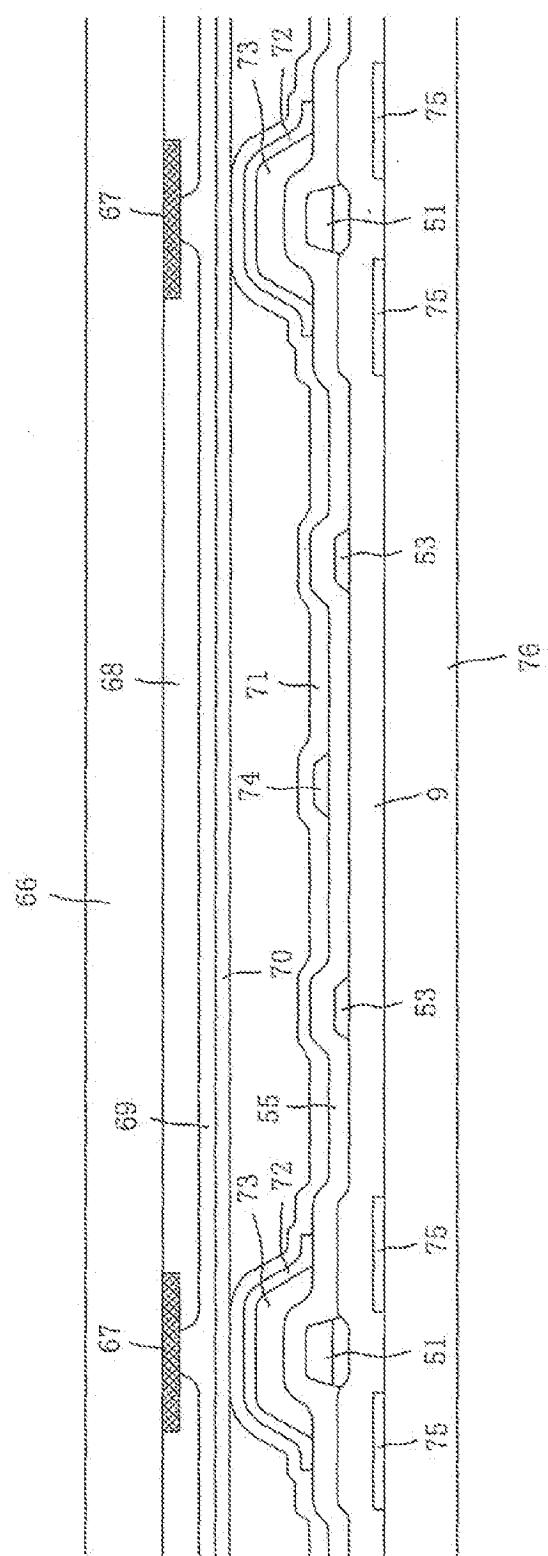

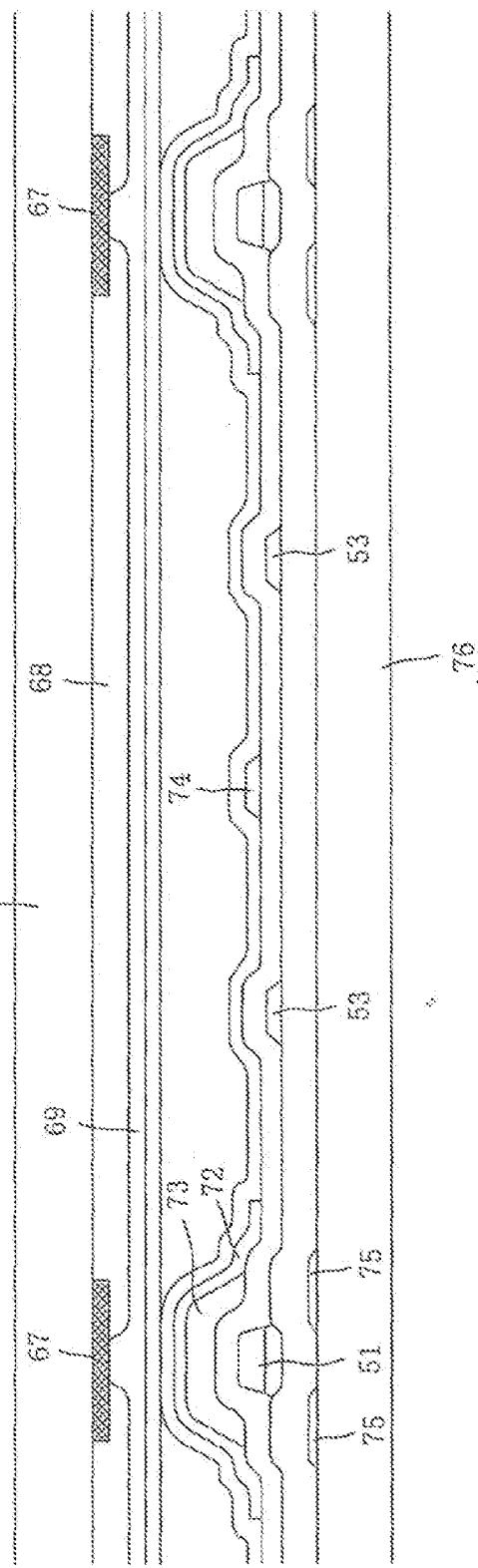

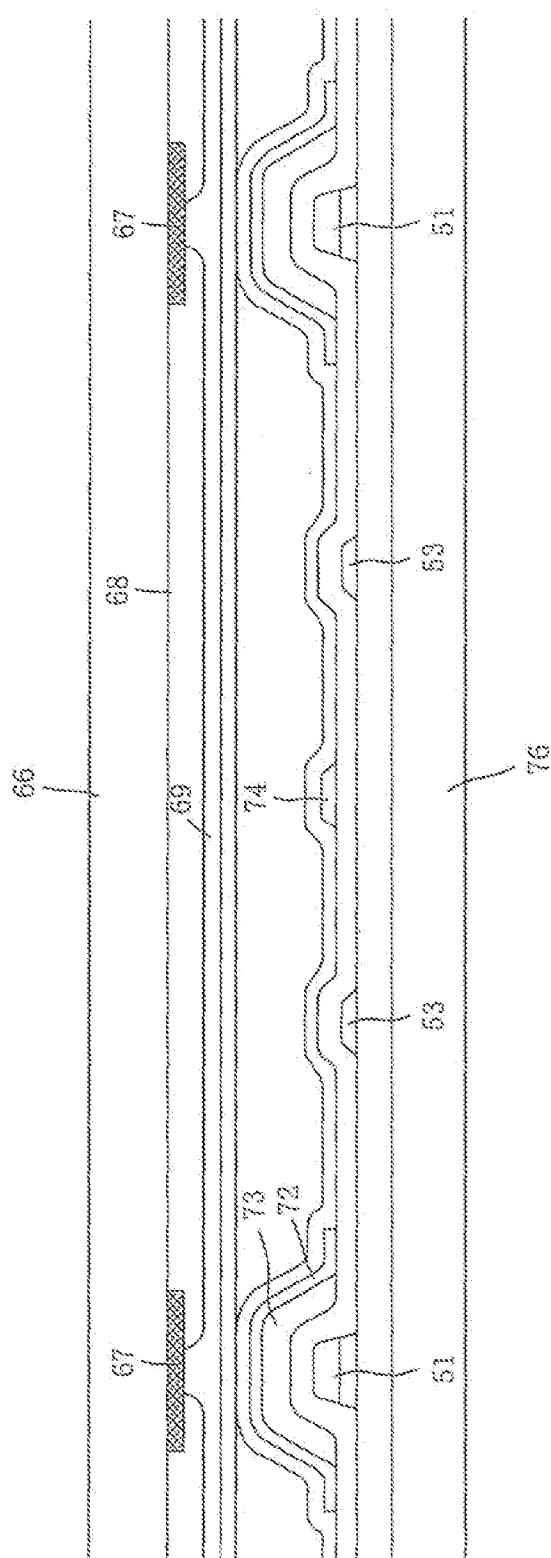

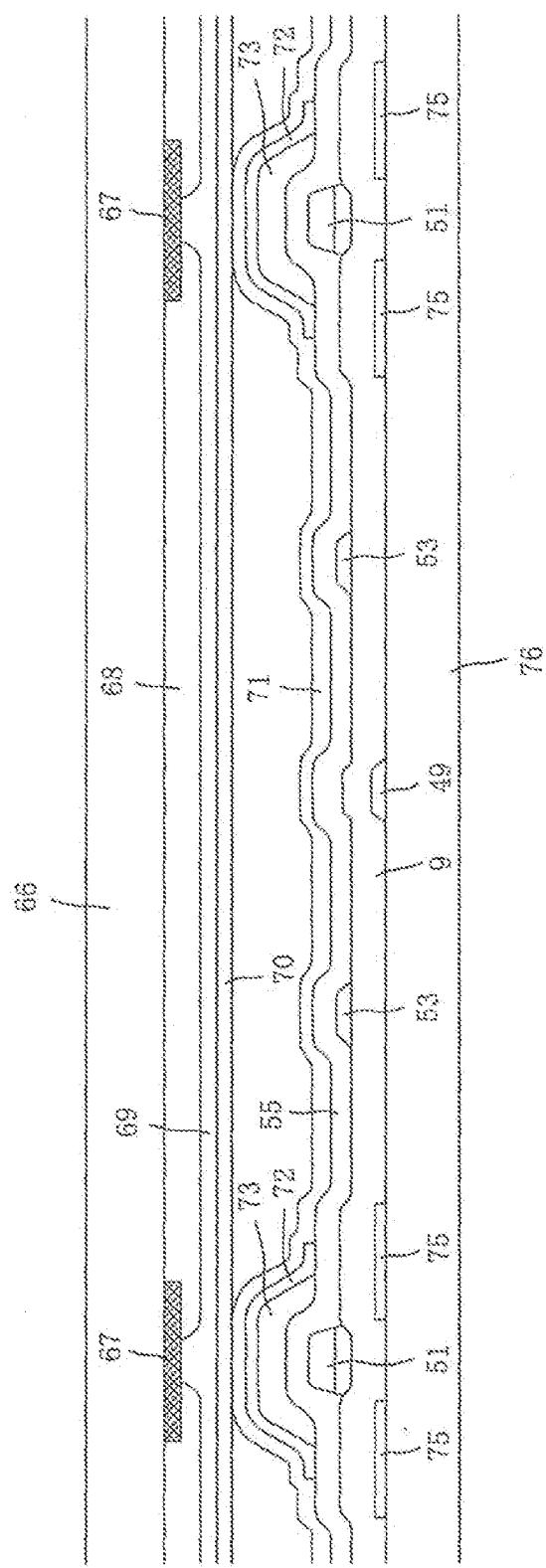

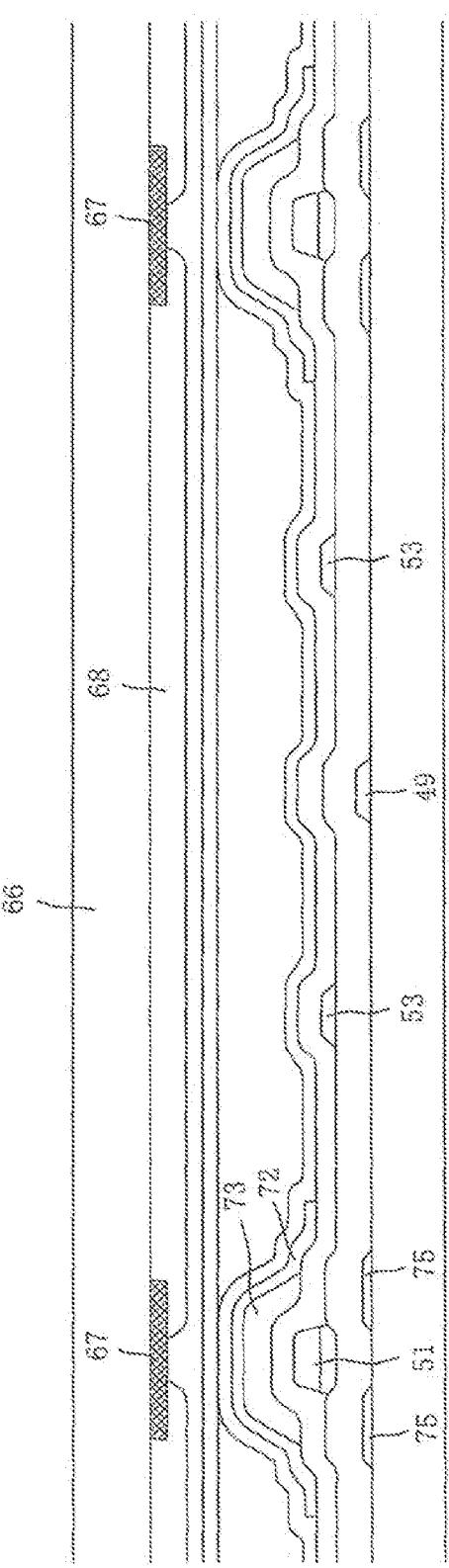

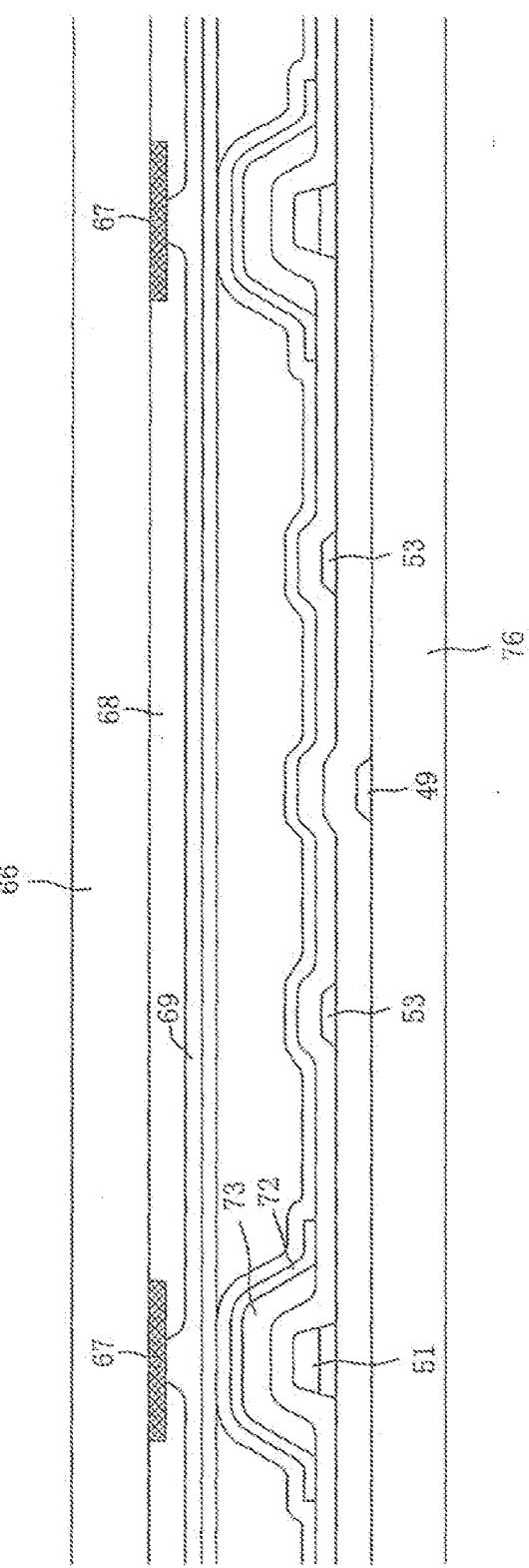

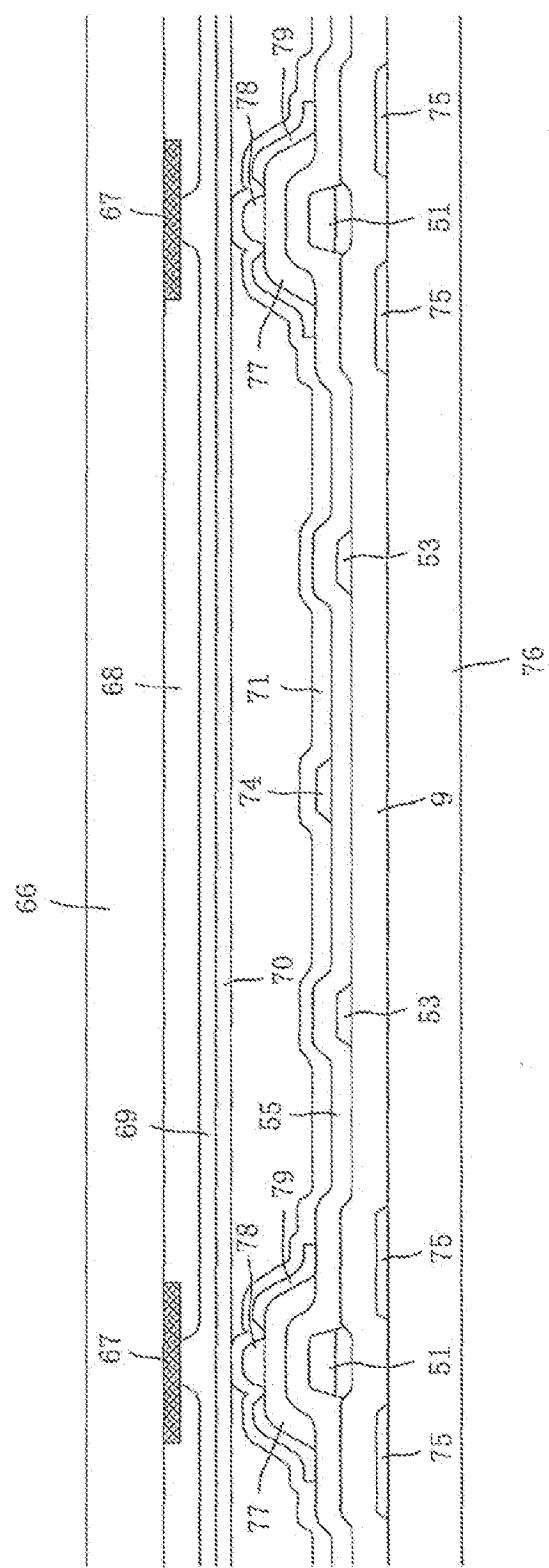

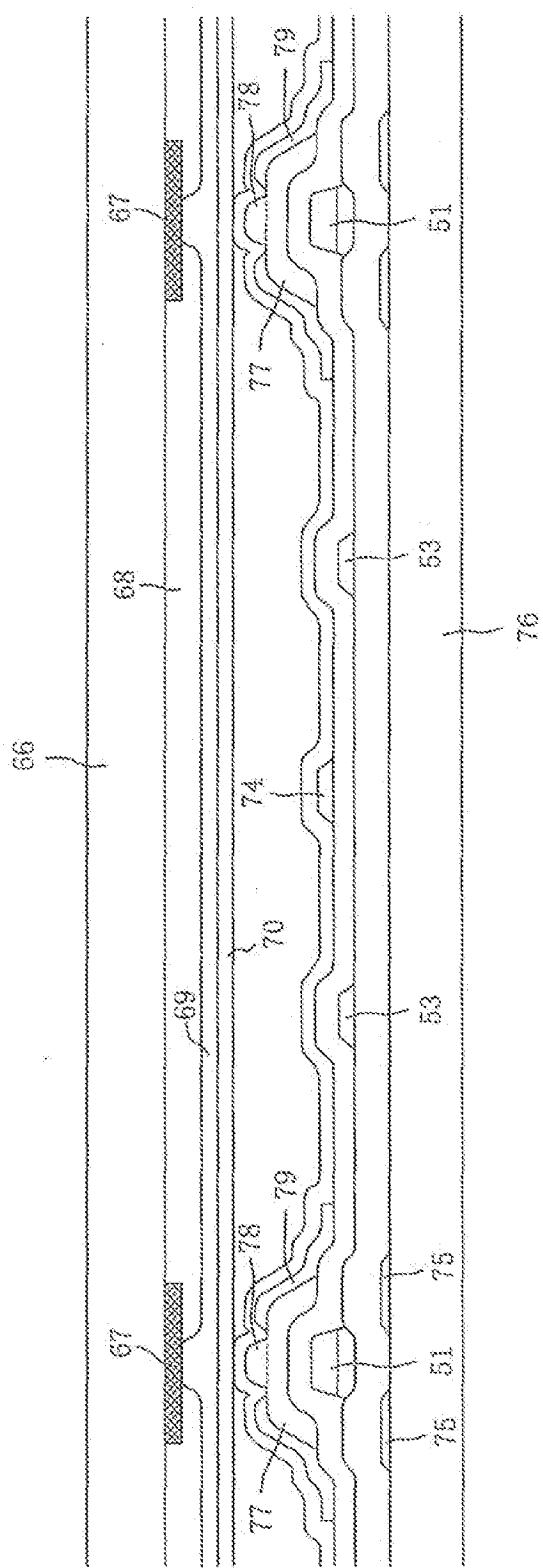

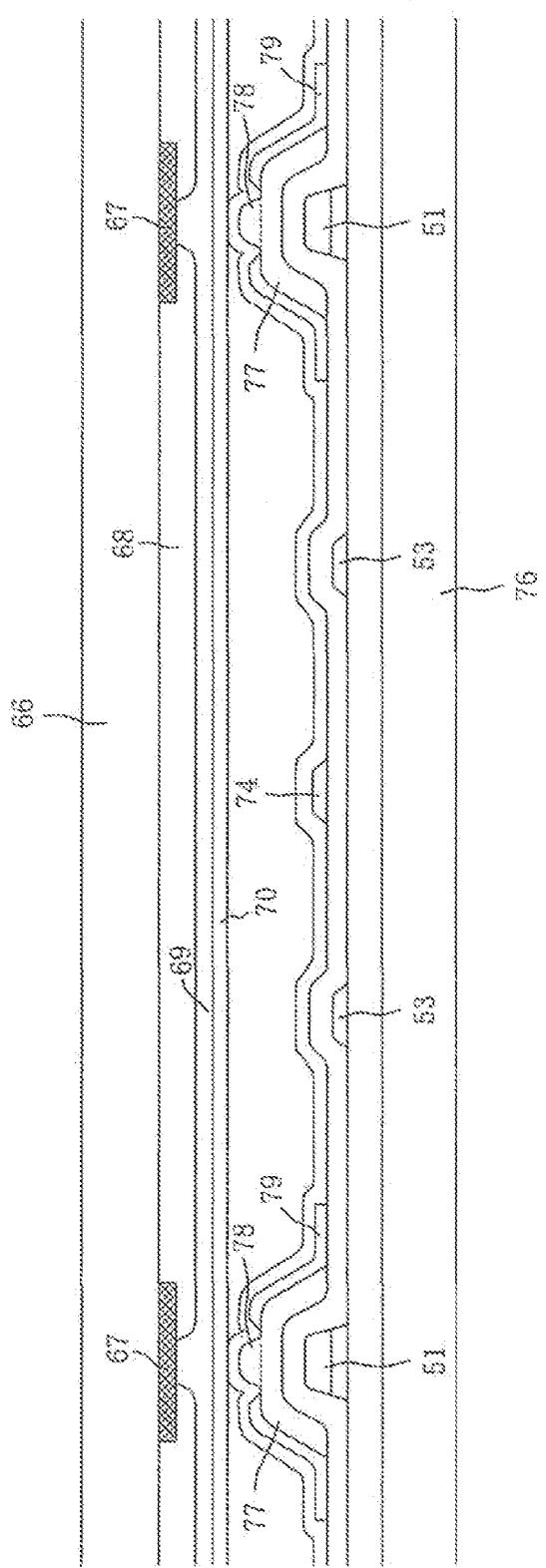

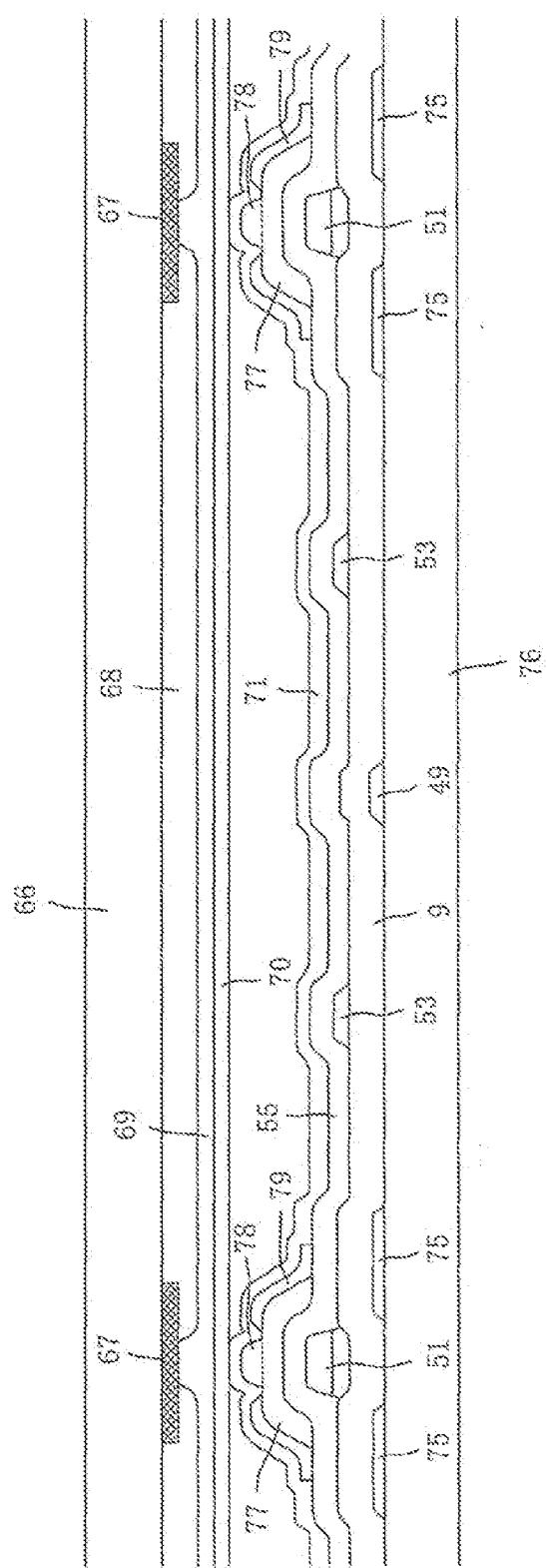

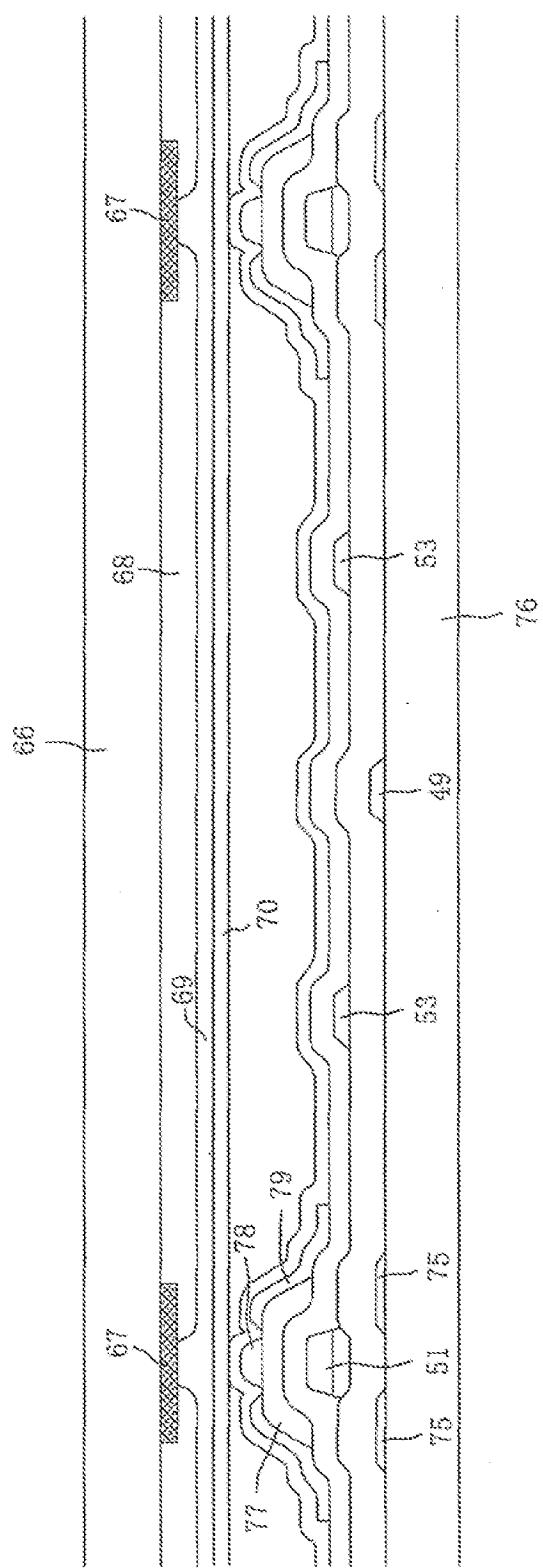

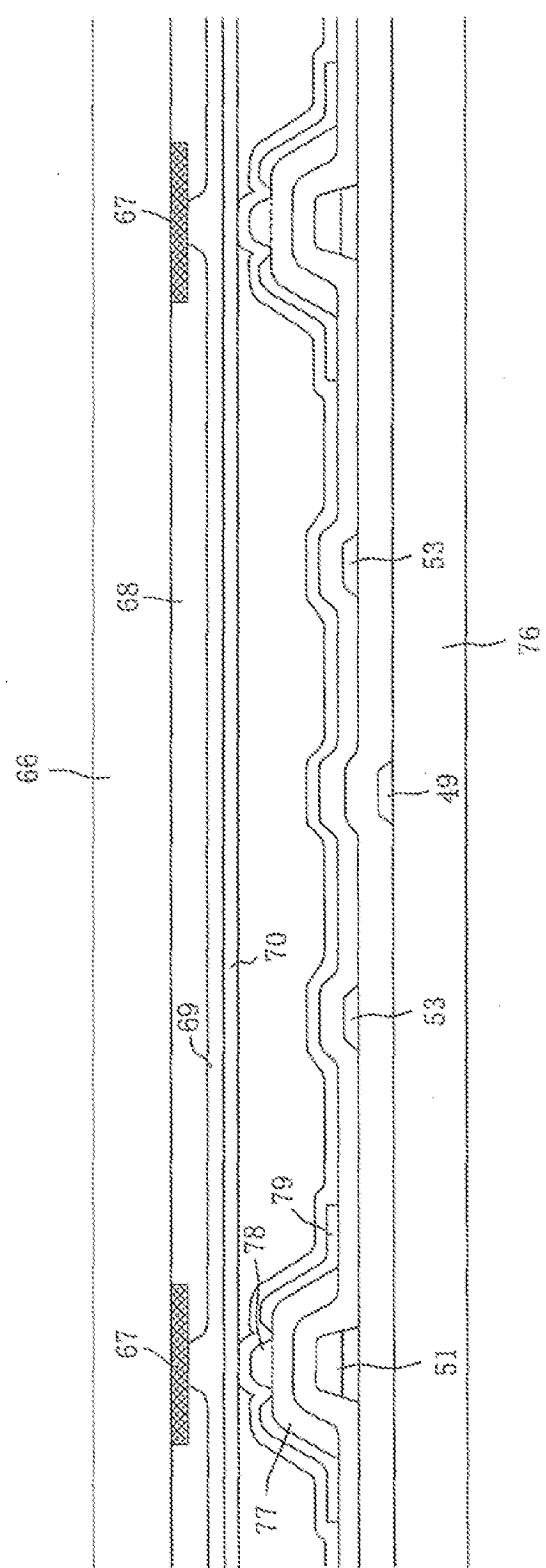

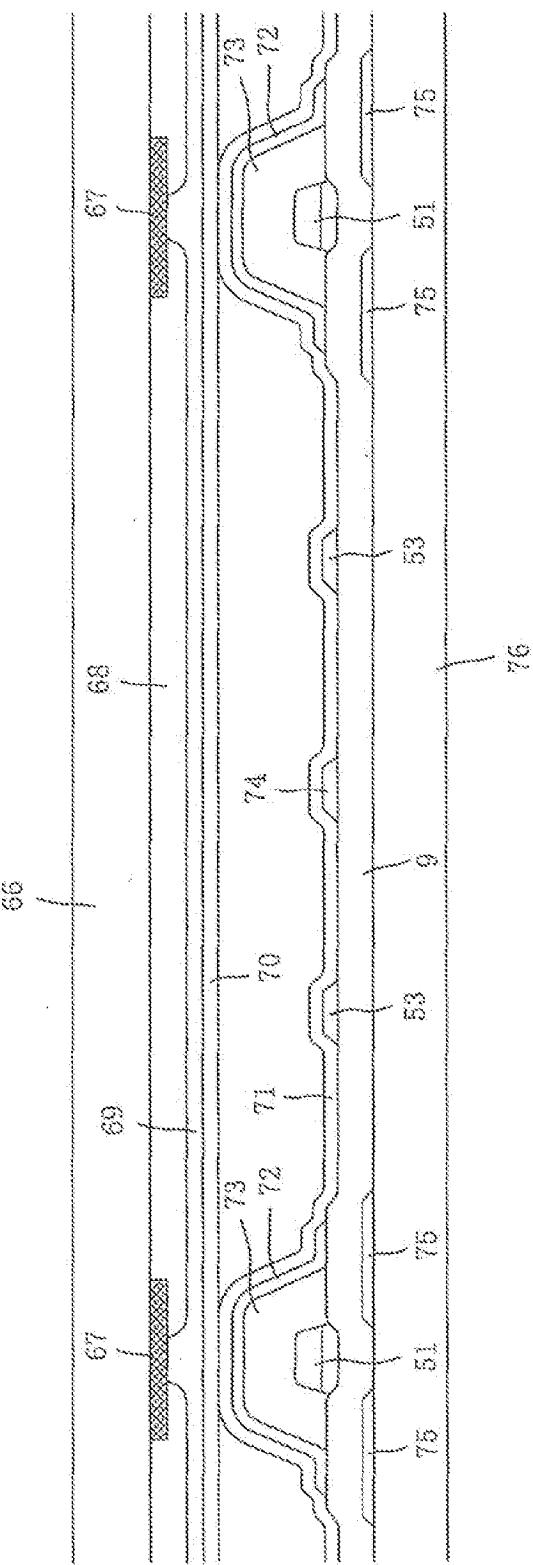

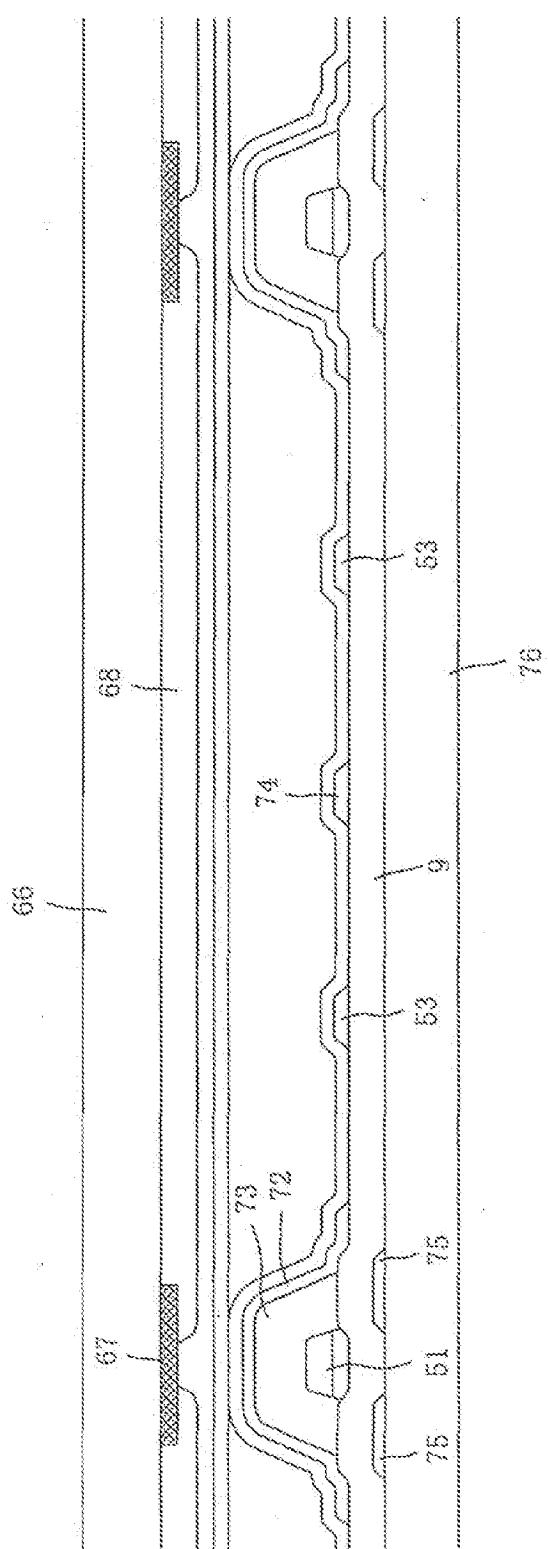

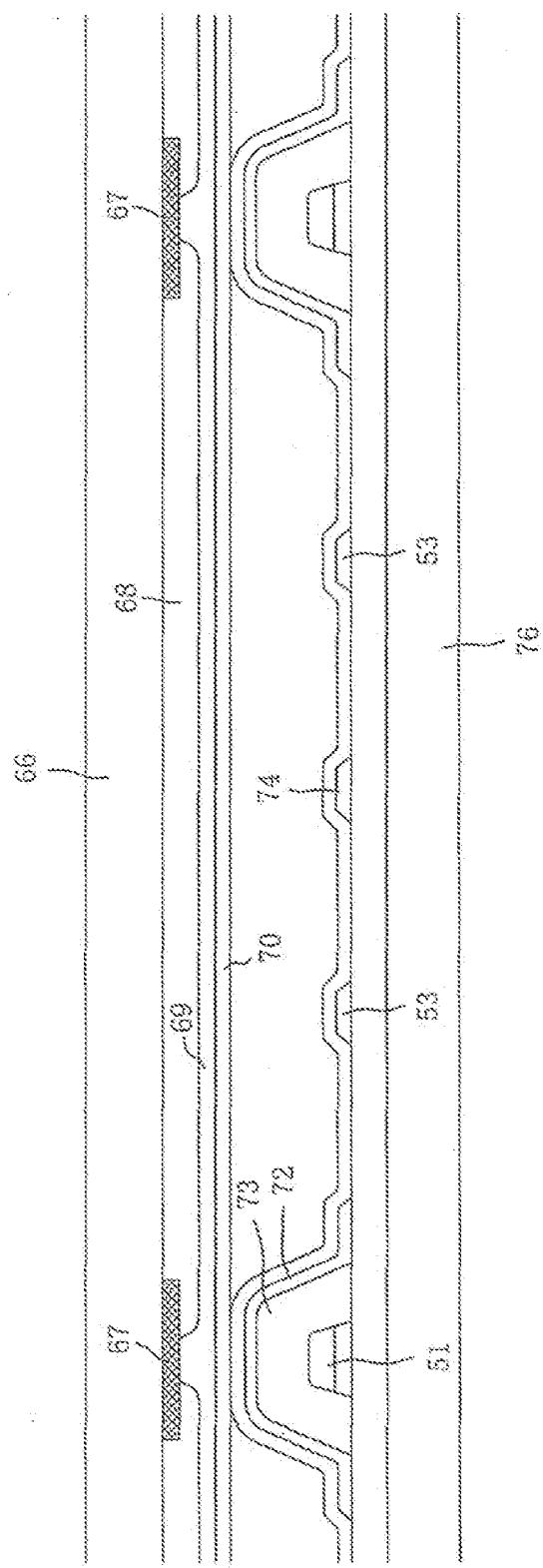

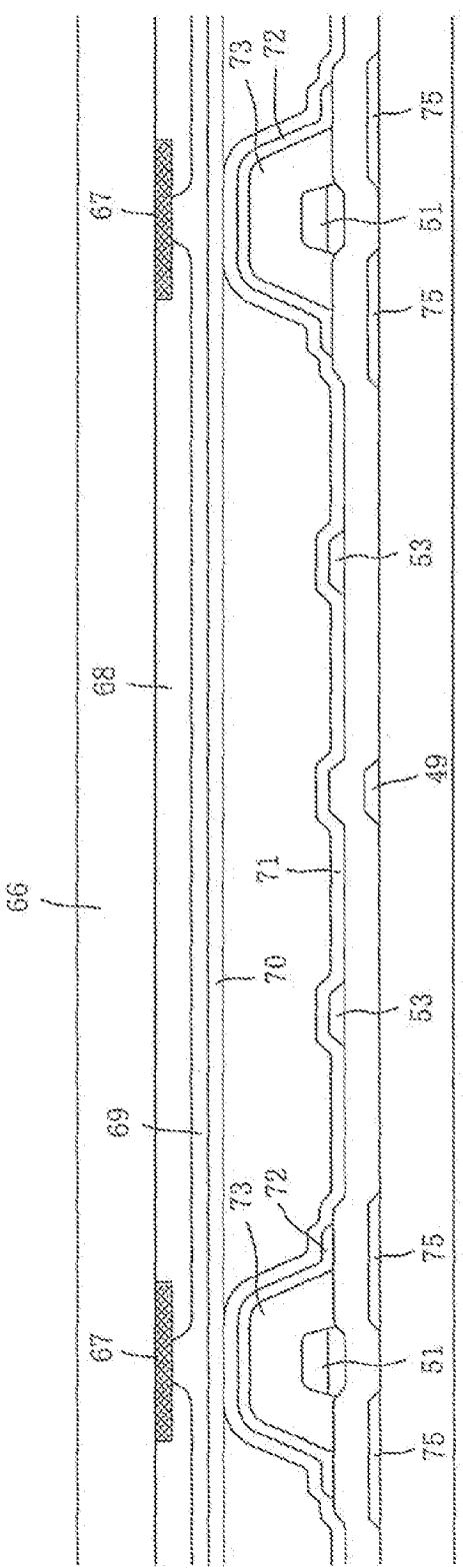

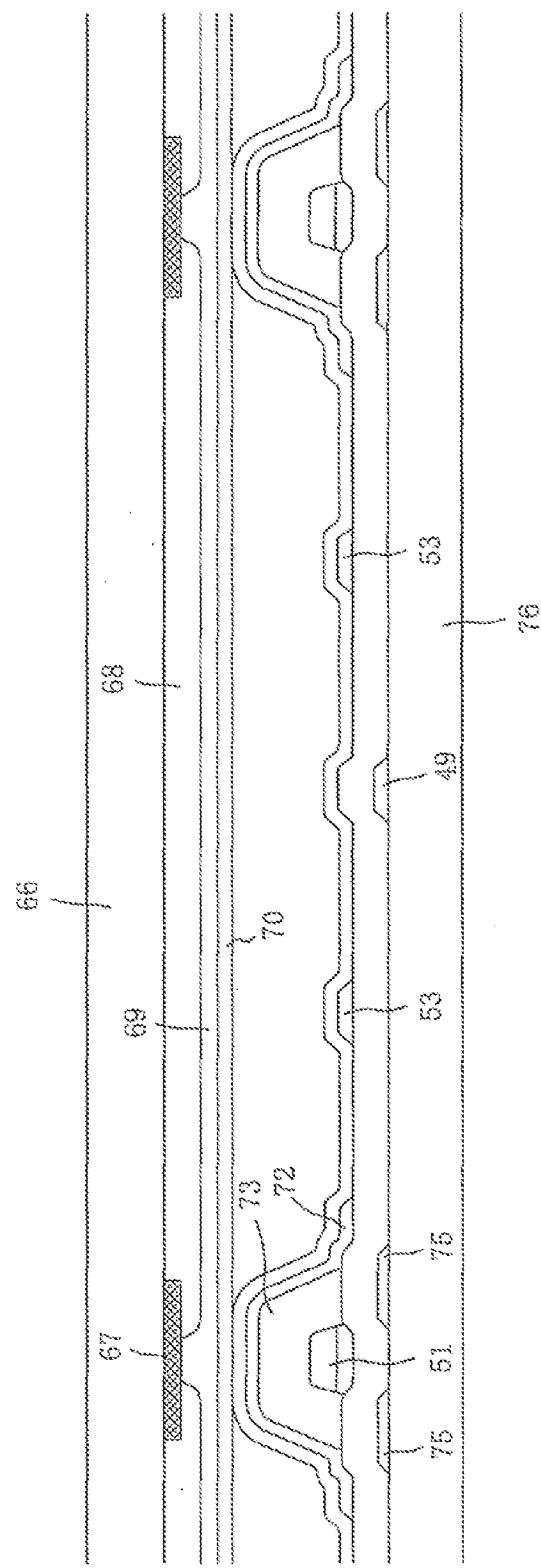

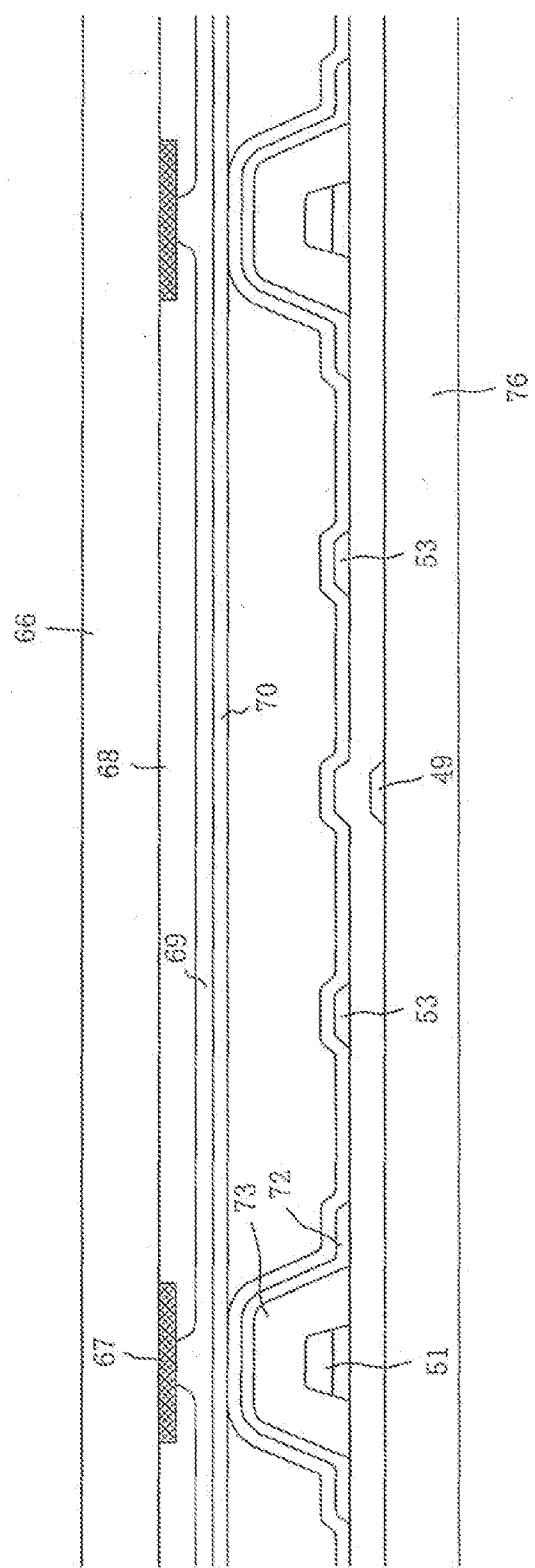

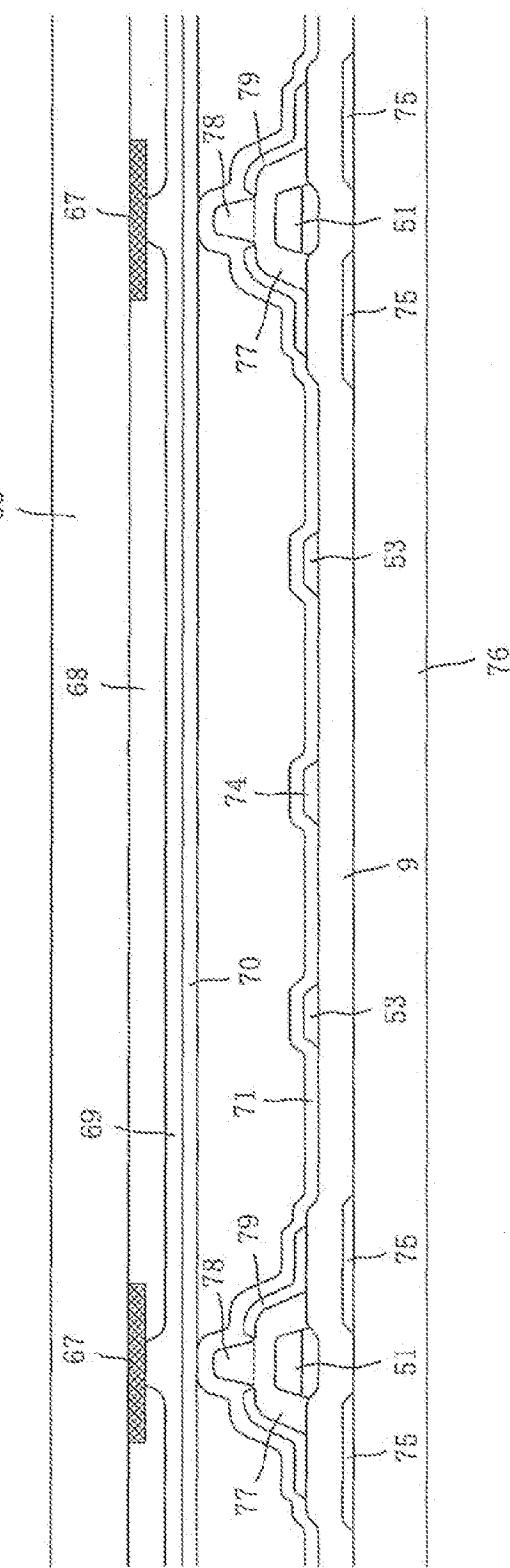

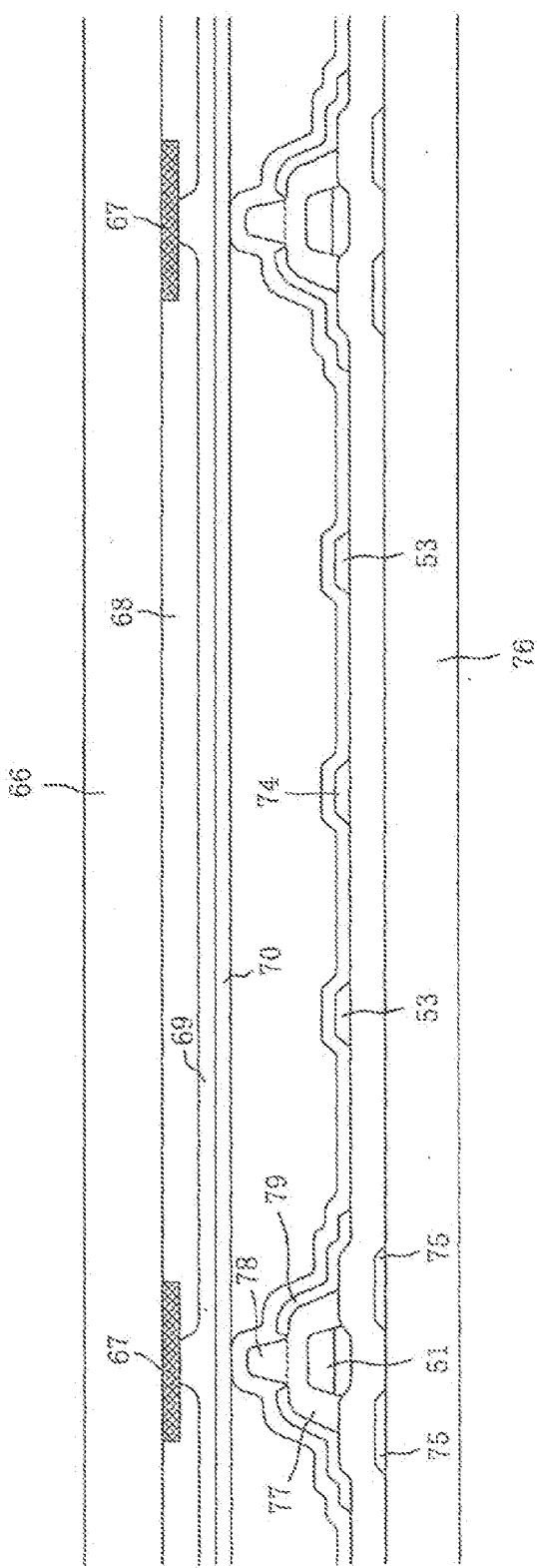

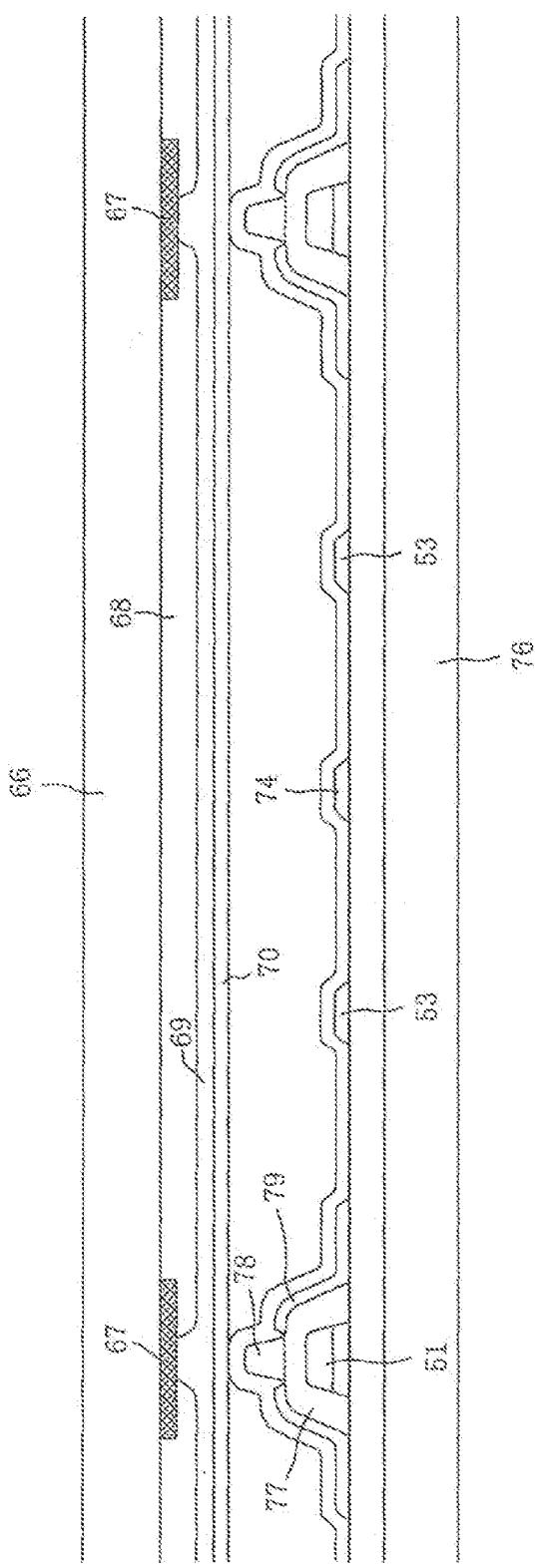

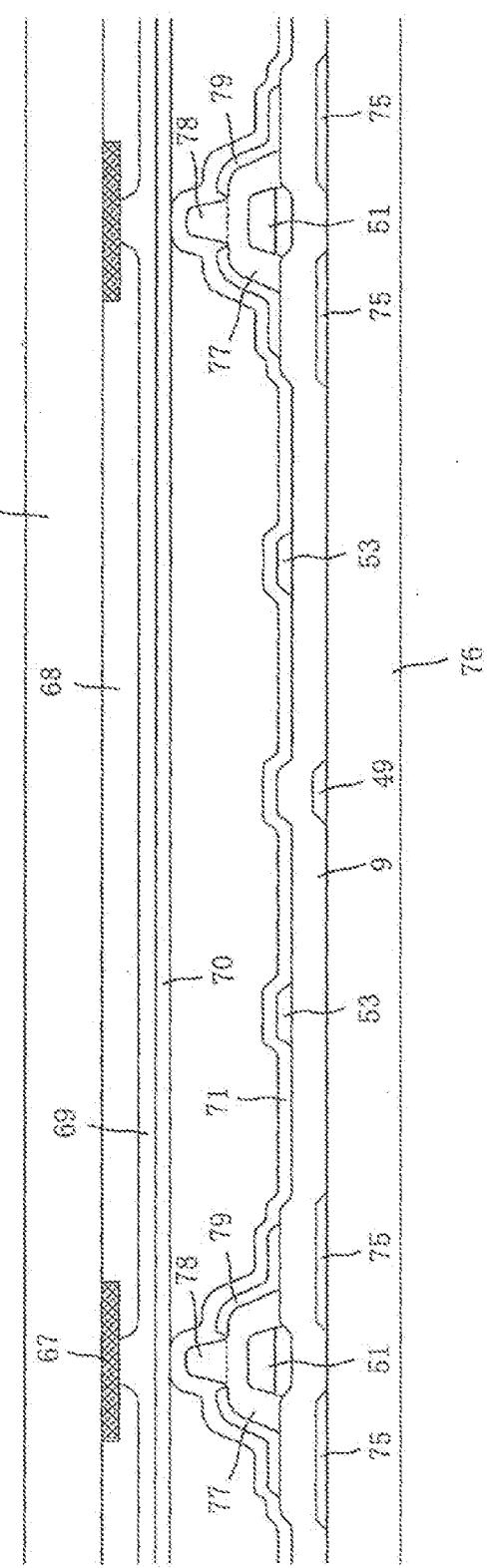

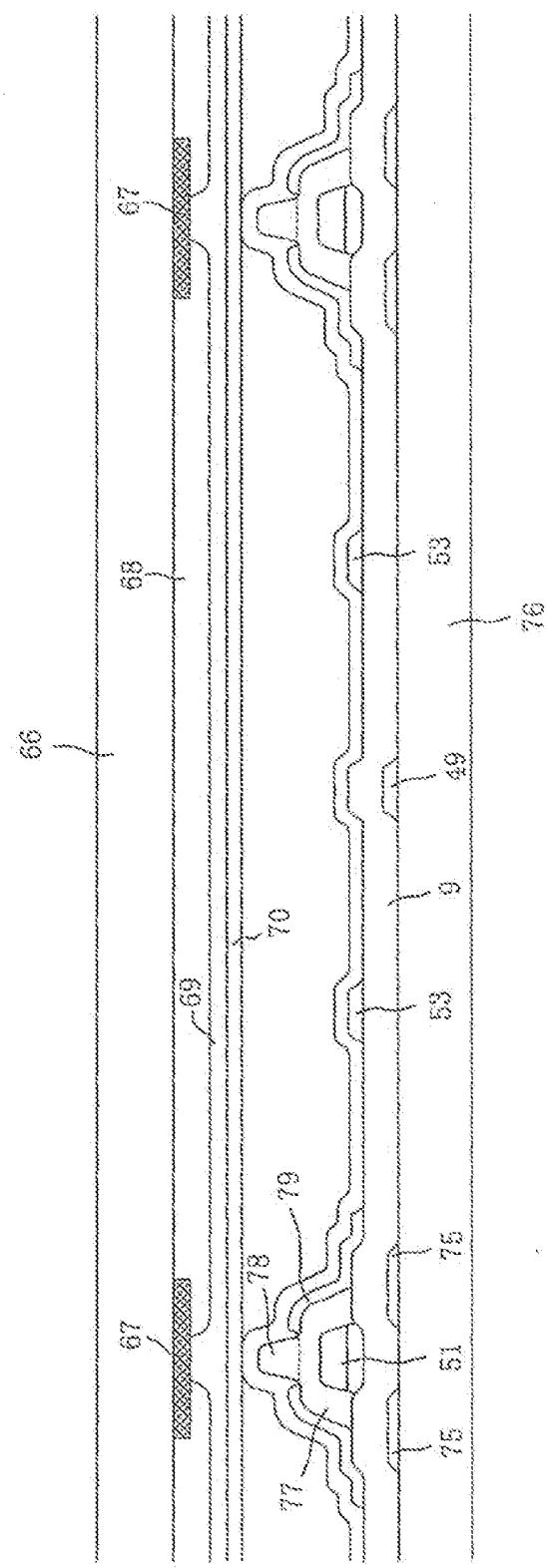

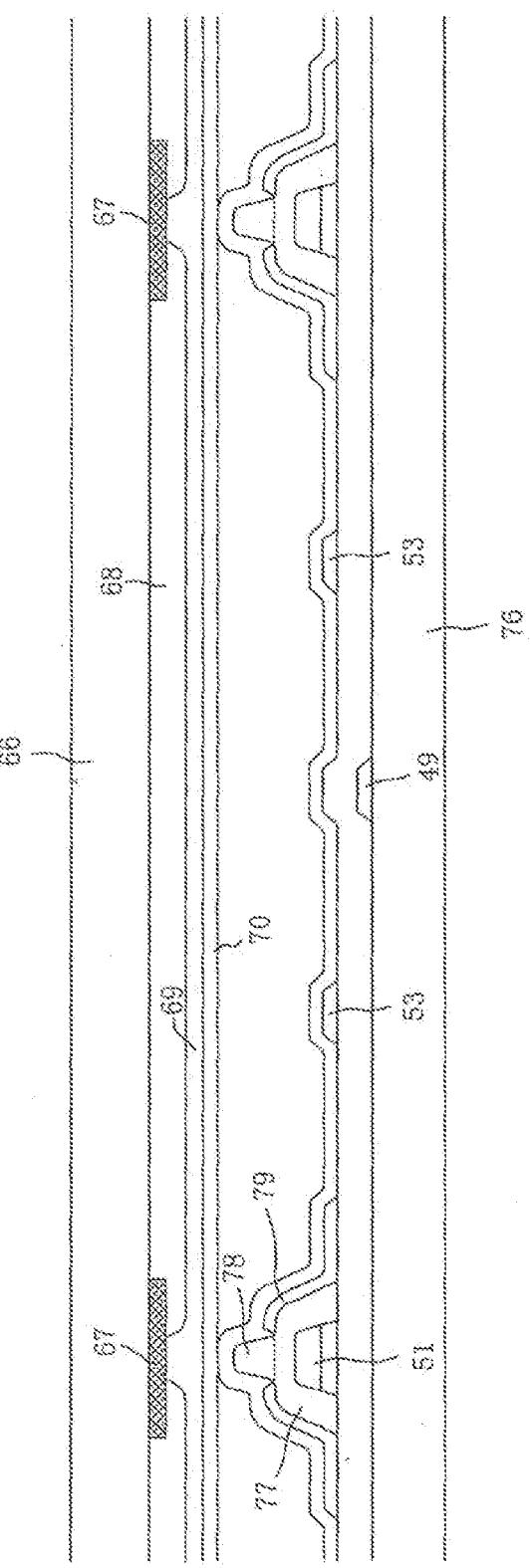

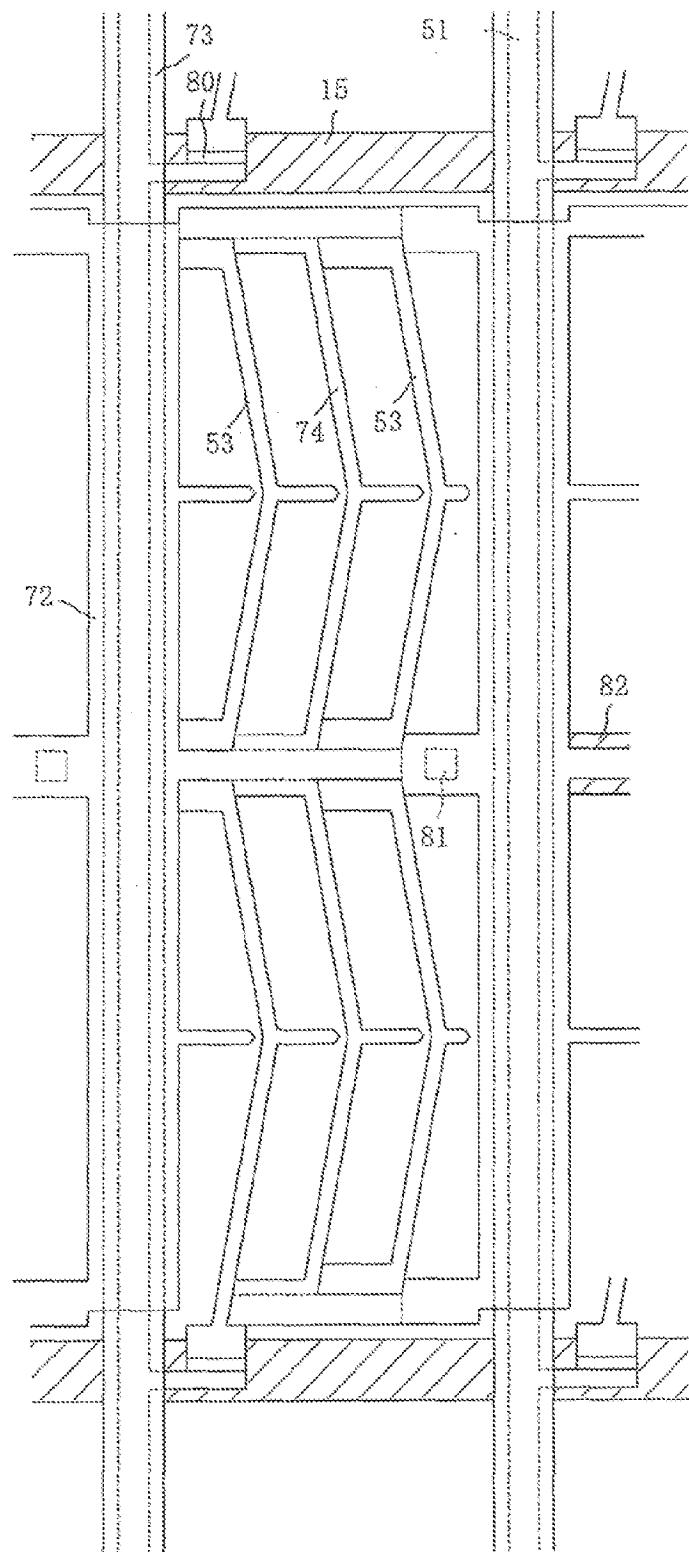

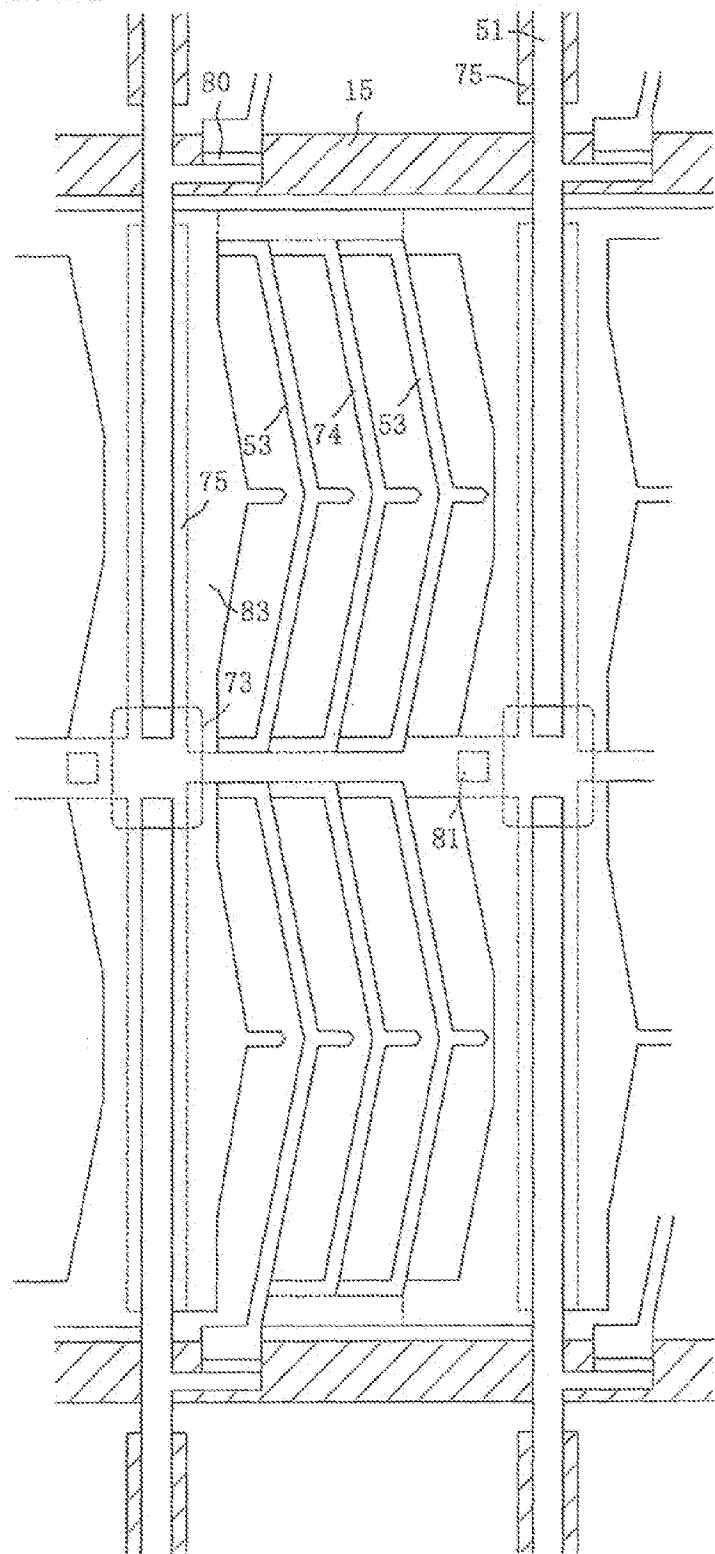

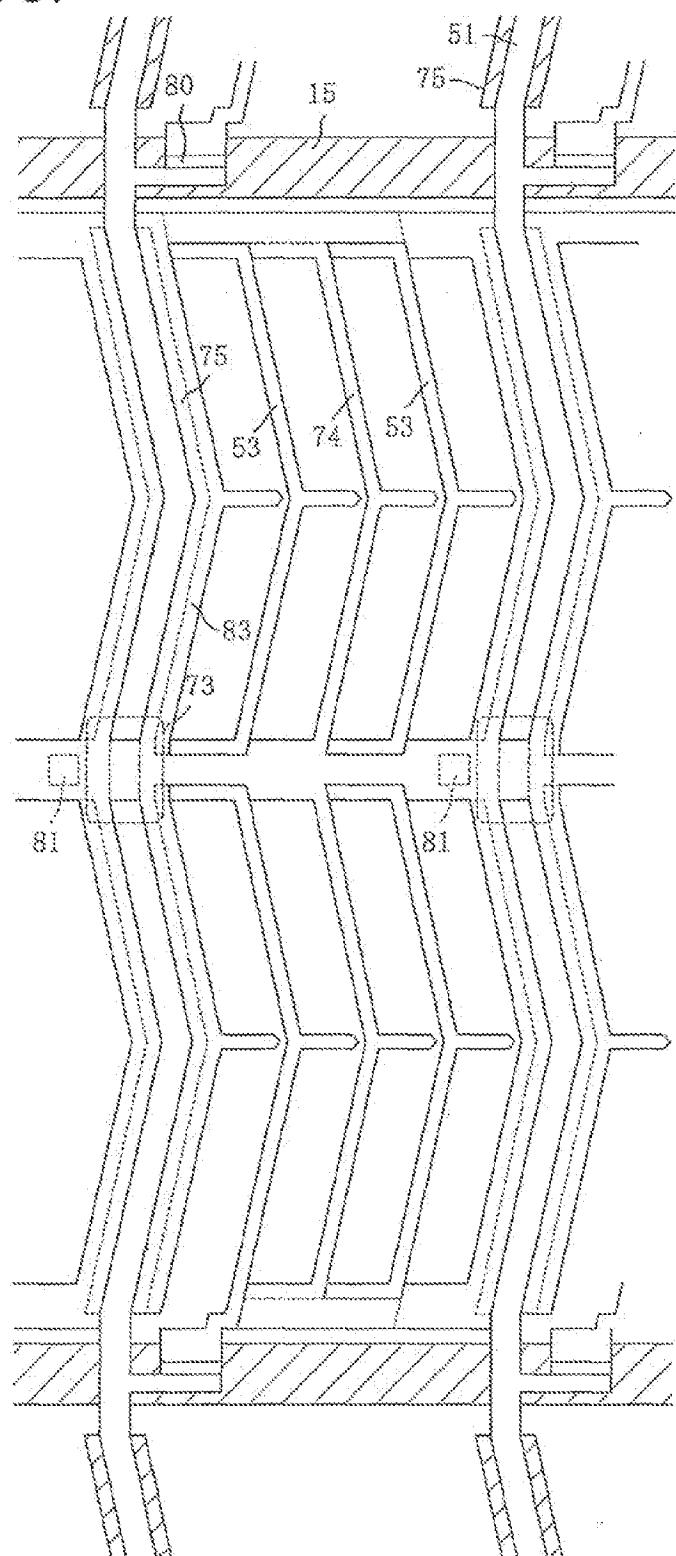

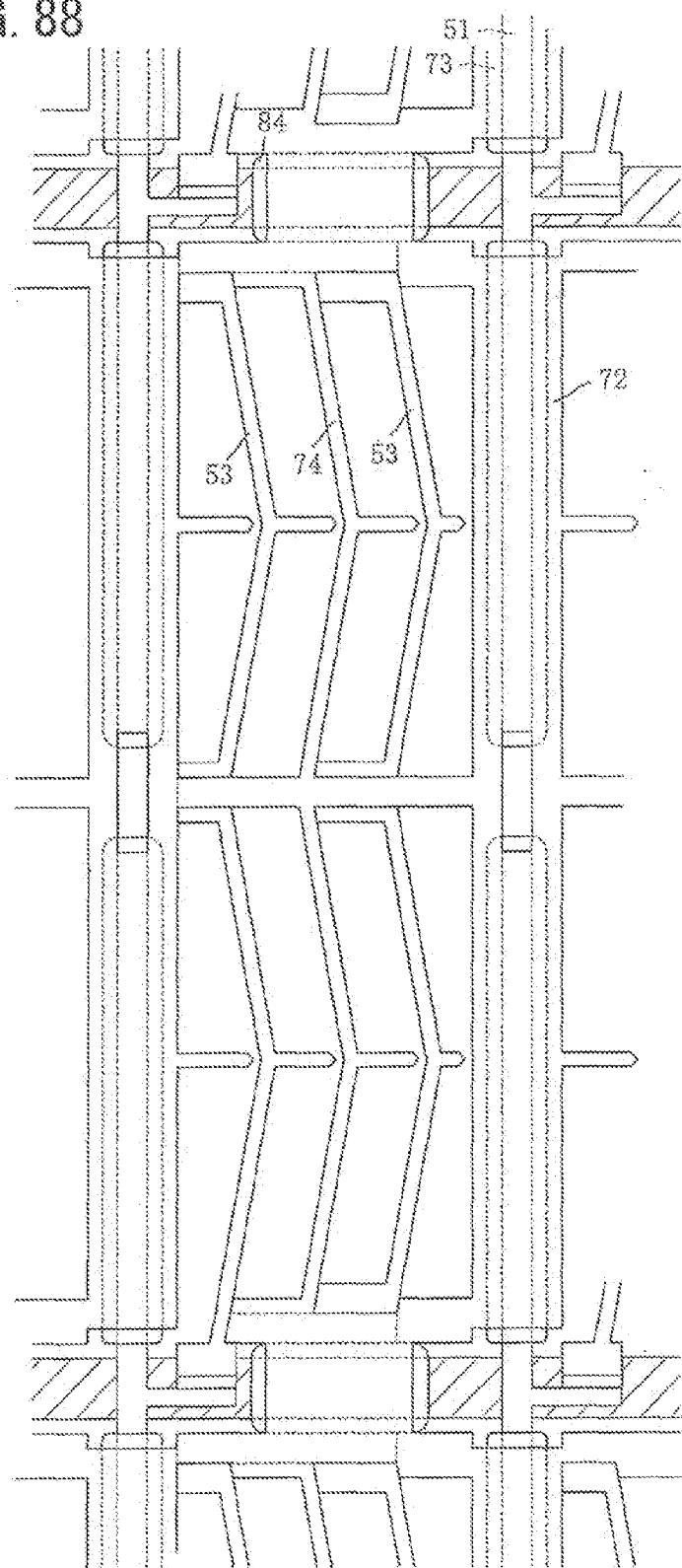

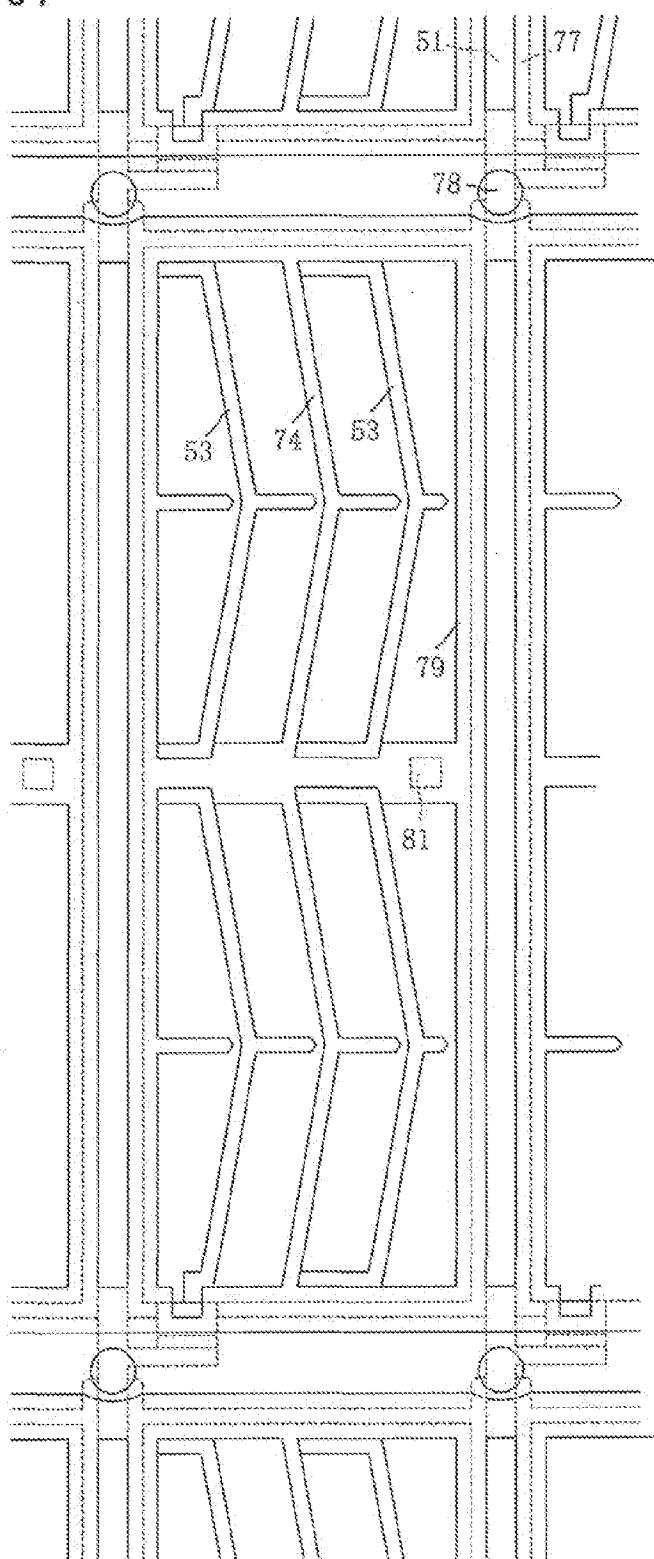

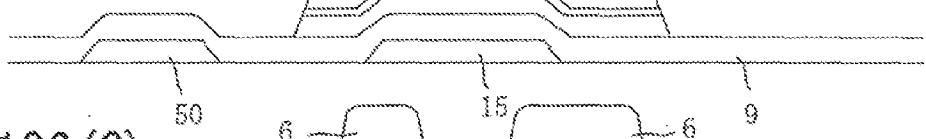

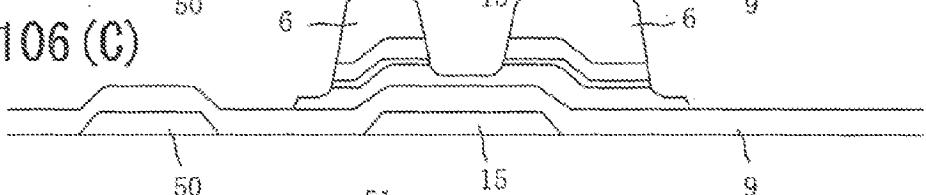

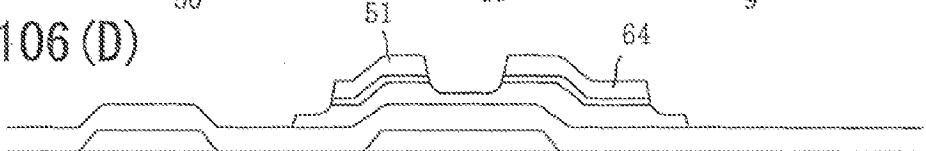

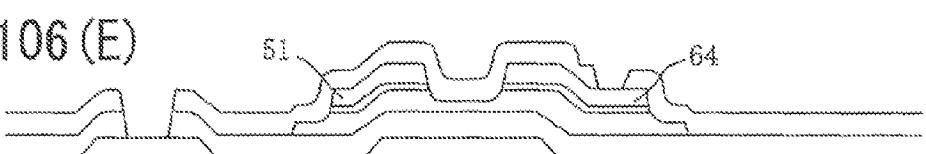

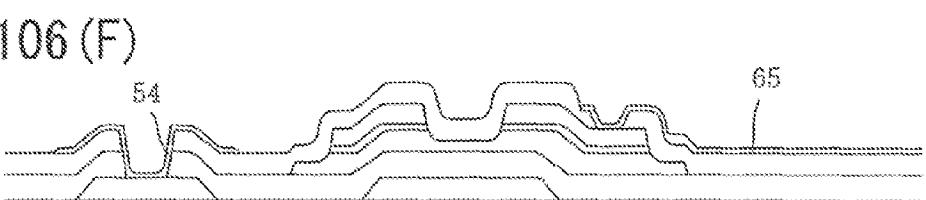

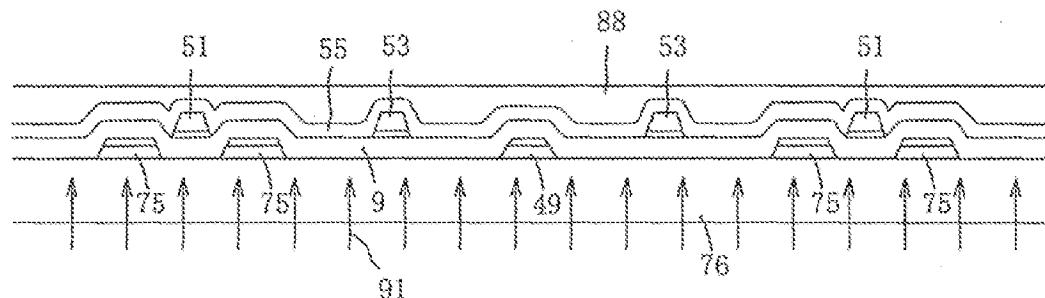

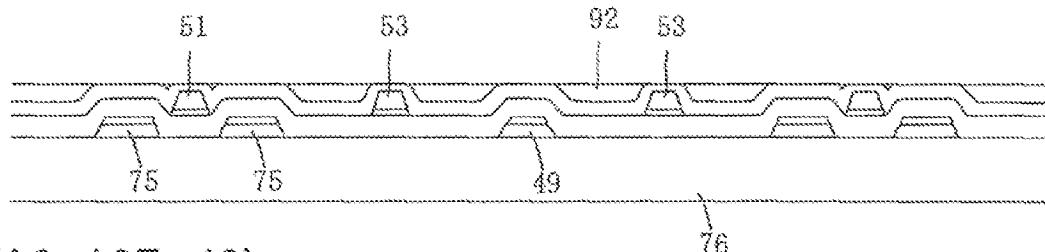

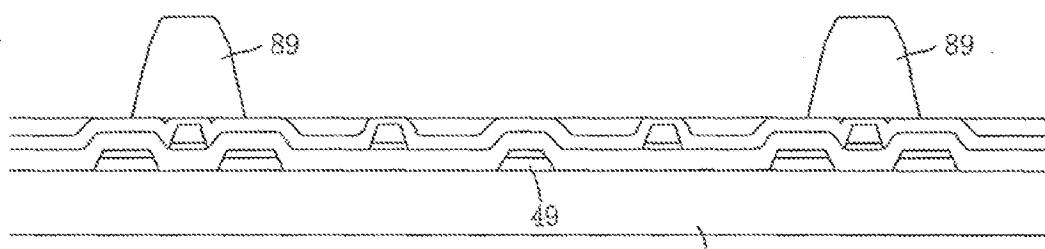

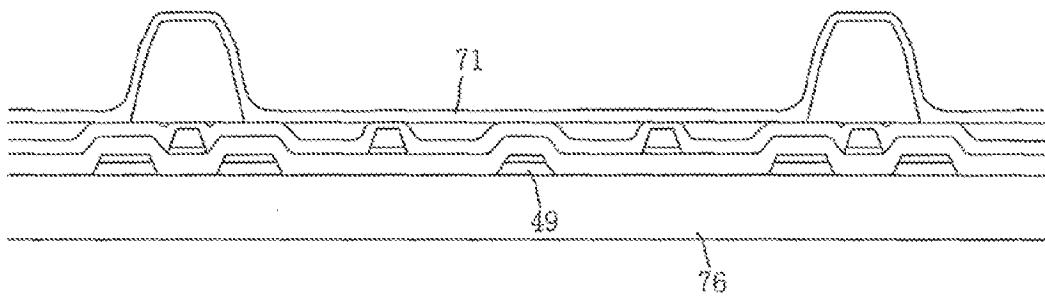

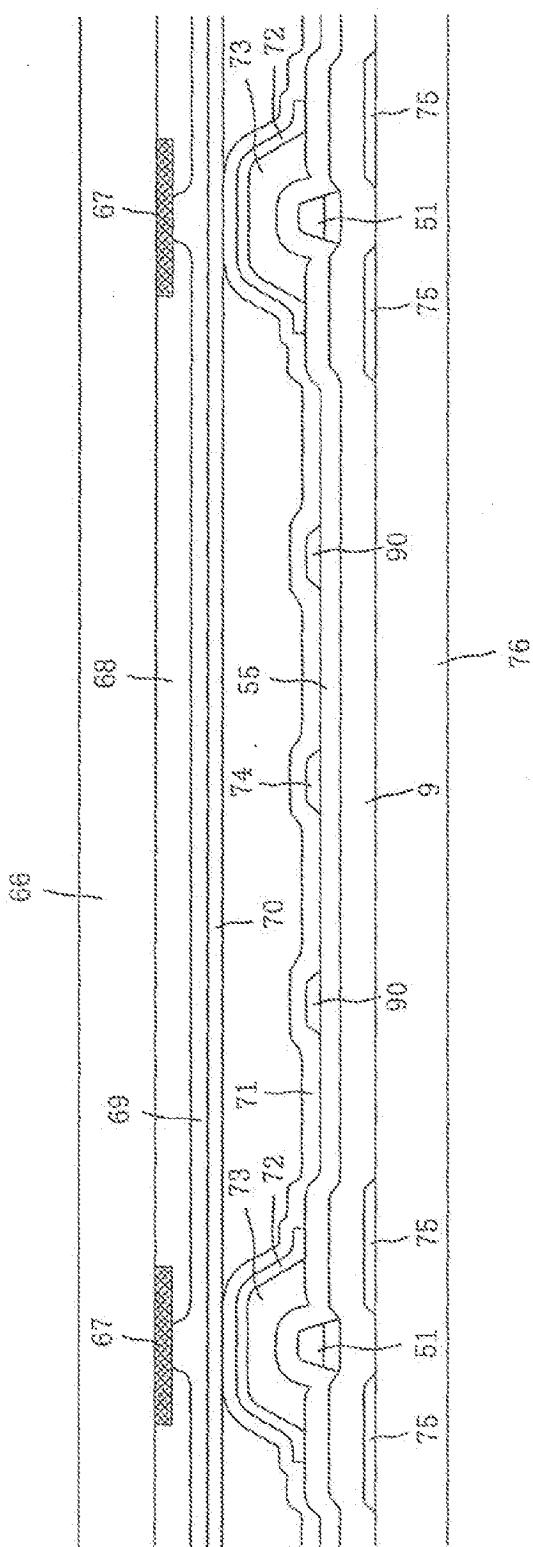

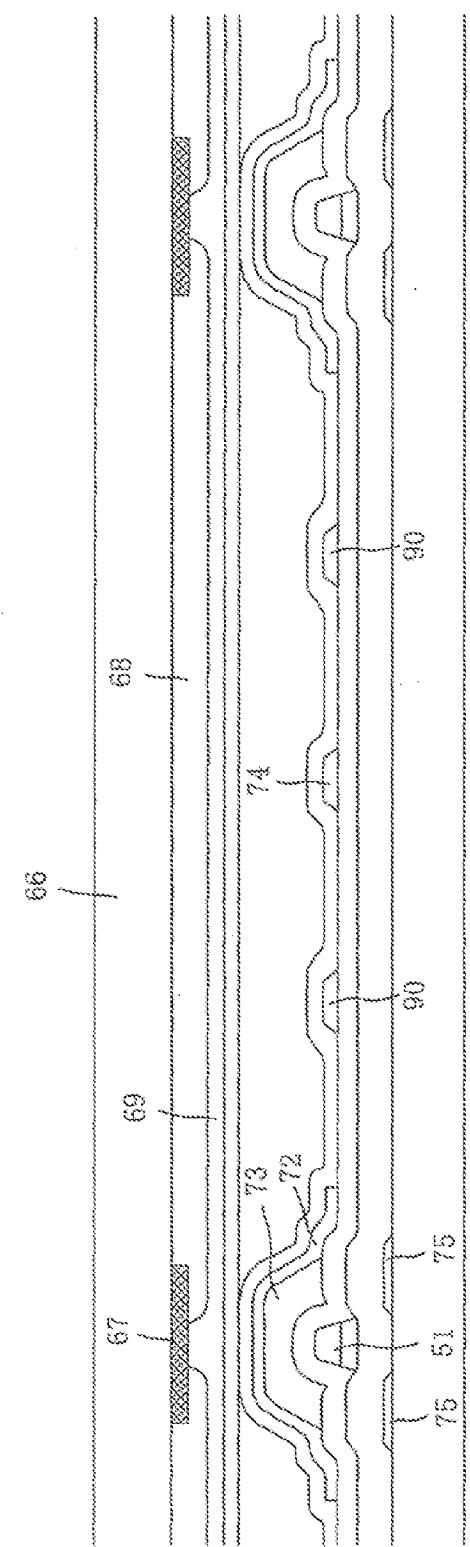

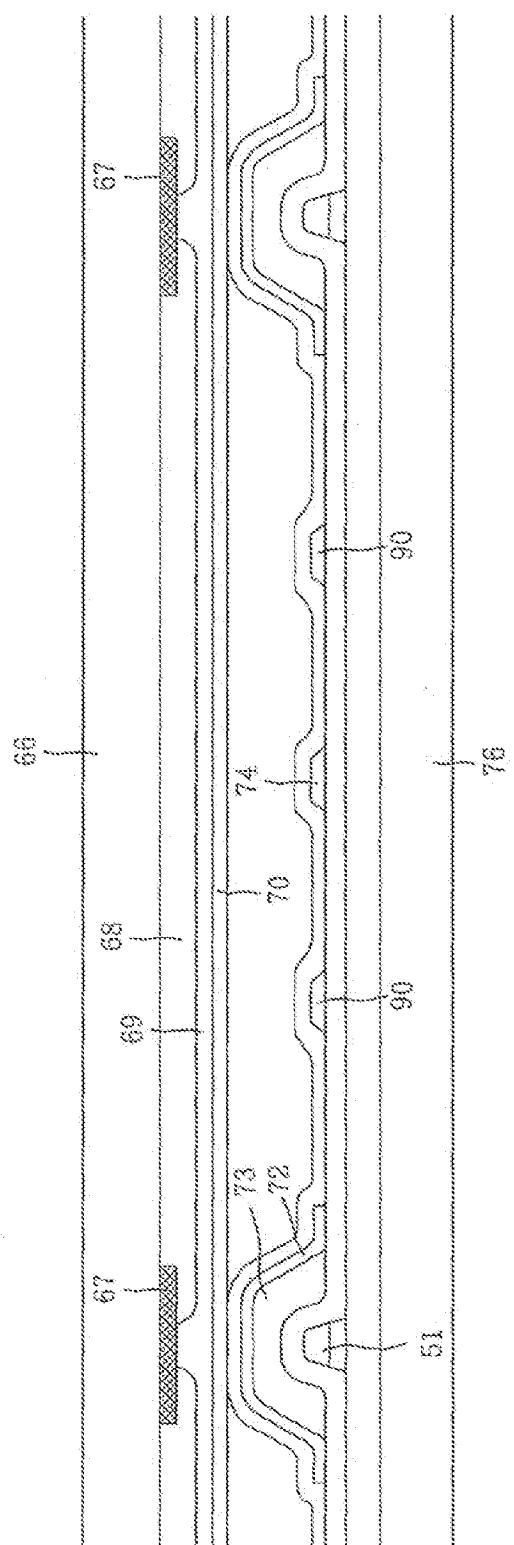

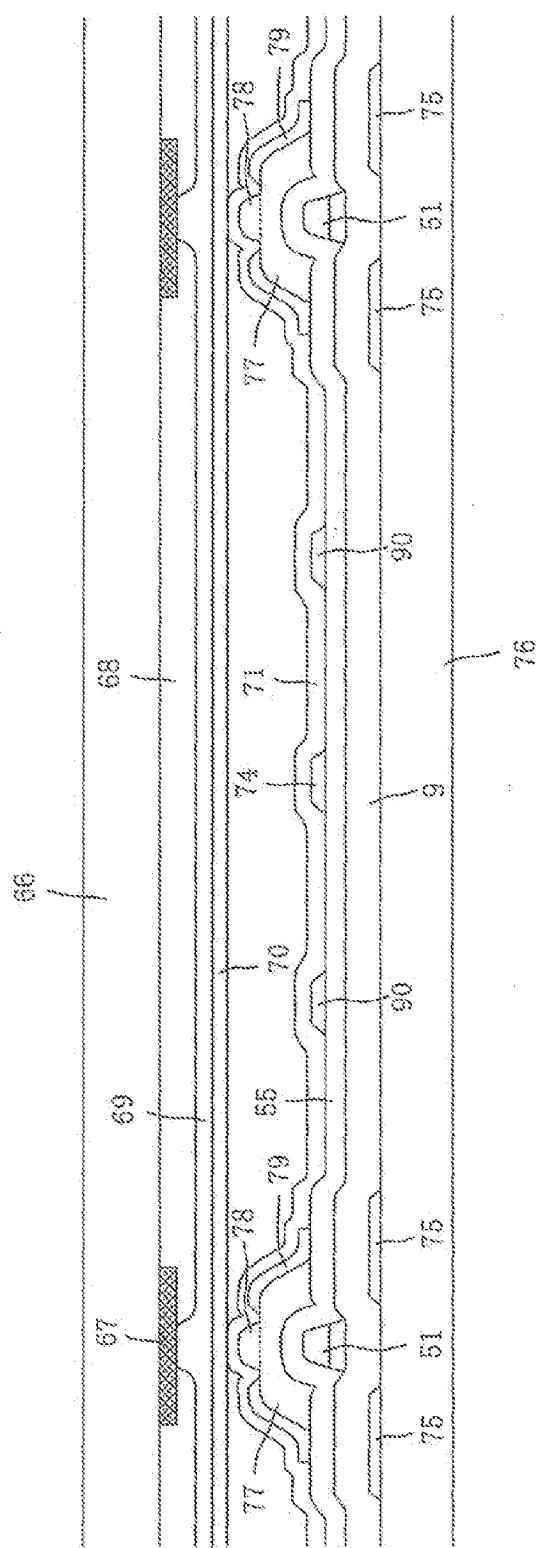

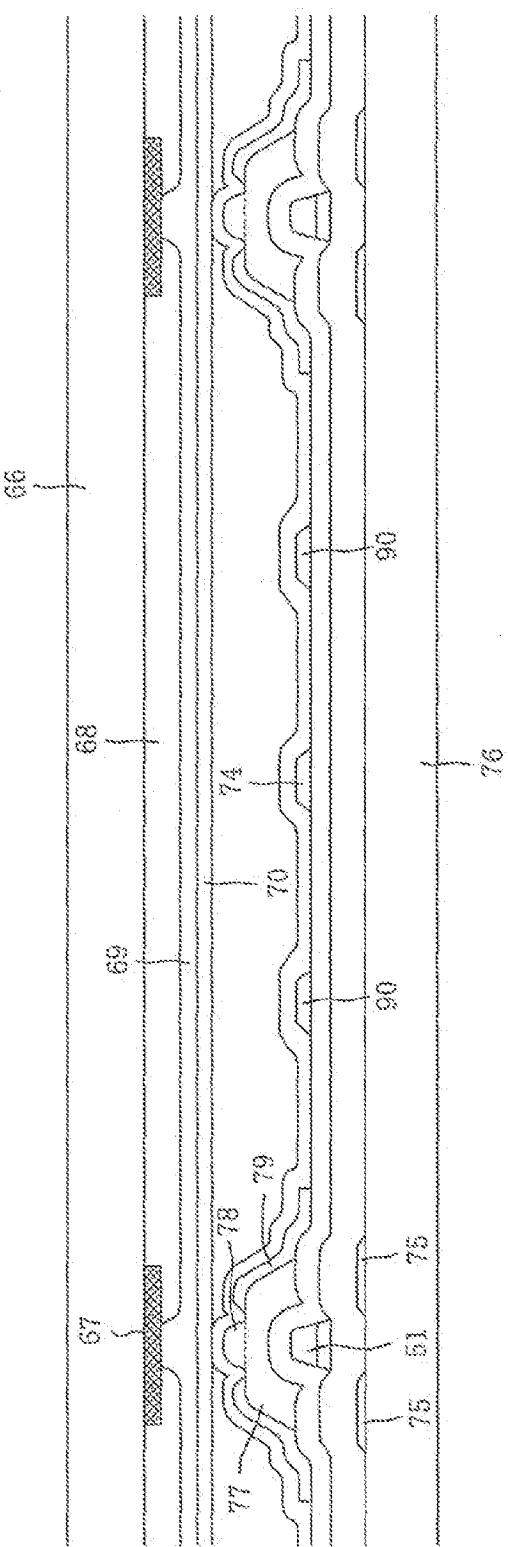

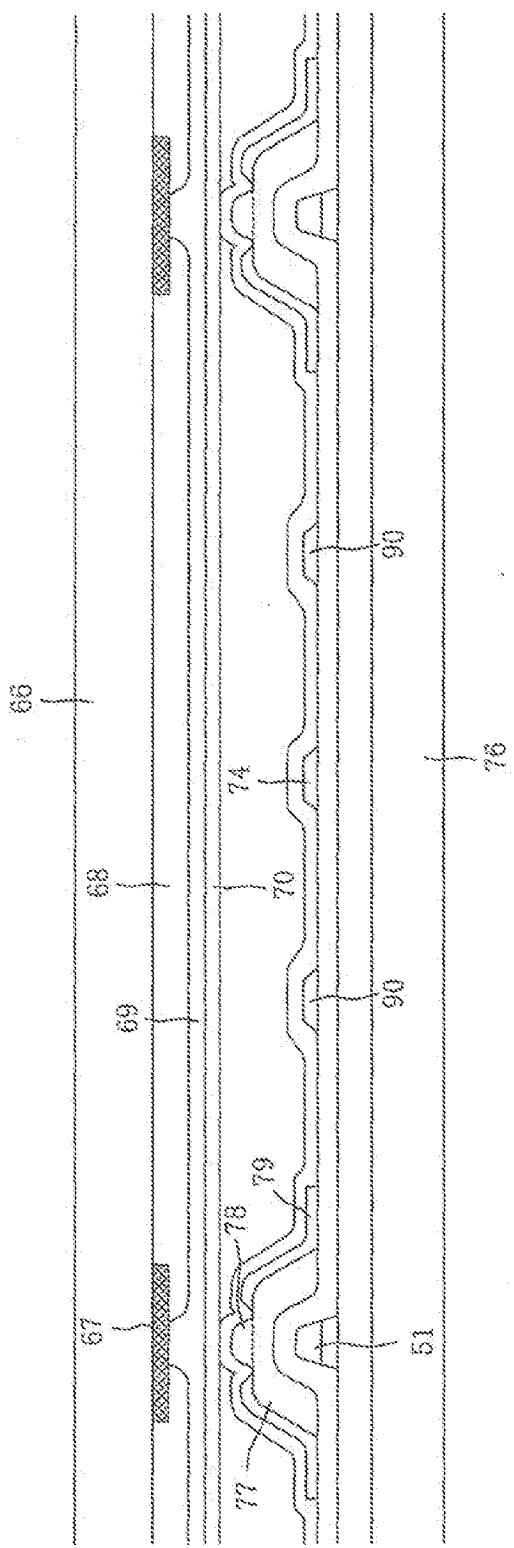

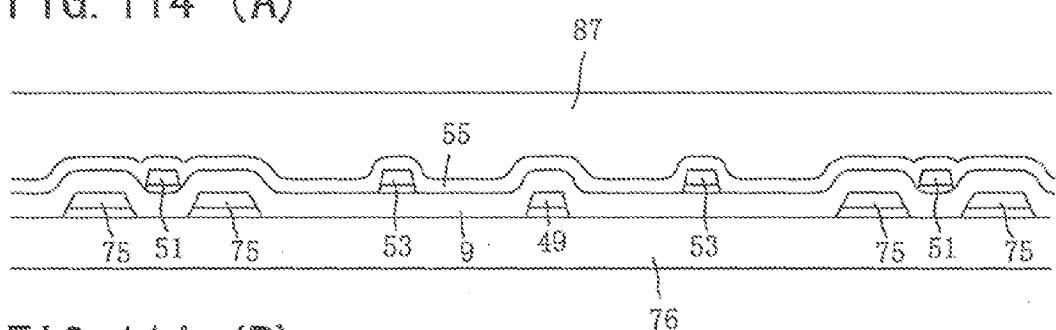

**[0009]** In the cross sectional views of Figures 36A-36F, a numeral 6 denotes an area on a positive photoresist layer after development where UV exposure is blocked, a numeral 7 denotes an area on the positive photoresist layer after development where the UV exposure is made through the halftone (translucent) photomask, a numeral 9 denotes a gate insulation film, a numeral 10 denotes a thin film semiconductor layer (non-doped layer), a numeral 11 denotes a thin film semiconductor layer (doped layer, i.e., ohmic contact layer), a numeral 15 denotes a scanning line, a numeral 50 denotes a scanning line terminal, a numeral 51 denotes a video signal line, a numeral 54 denotes a scanning line drive circuit contact electrode, a numeral 64 denotes a drain electrode of the thin film transistor, and a numeral 65 denotes a transparent pixel electrode.

**[0010]** Prior to the start of the processes of Figures 36A-36F, the scanning lines 15 and the scanning terminals 50 are formed on a glass substrate (not shown). In Figure 36A, the gate insulation film 9, the thin film semiconductor layer (non-doped layer) 10 and the thin film transistor ohmic contact layer 11 are respectively deposited by, for example, a CVD plasma device. The positive photoresist 6 is coated and the halftone exposure is conducted so that the thicker positive photoresist 6 and the thinner positive photoresist 7 are created. In Figures 36B and 36C, through a dry etching process, the thin film transistors are separated from the semiconductor layer. In Figure 36D, the drain electrode 64 of the thin film transistor and the video signal line 51 are formed by further conducting the etching process. In Figure 36E, through the dry etching, contact holes are created over the scan-

ning line terminals 50. In Figure 36F, the scanning line drive circuit electrodes 54 and the transparent pixel electrodes 65 are formed.

**[0011]** The conventional transverse electric field type liquid crystal panel utilises common electrodes placed at both sides of the video signal line to shield the electric field caused by the signal video line. In order for this construction to completely solve the problem involved with the vertical crosstalk, it is necessary to design the width of the common electrodes to be at least 1.5 times larger than that of the video signal line, hence resulted in a reduction of the pixel aperture ratio.

**[0012]** It is possible to reduce the vertical crosstalk by collecting the electric force lines of the electric field produced by the video signal line to the photolithography spacer. This can be done by placing a black mask made of thin film conductive material (chromium oxide layer and chromium metal thin film layer) at the side of color filter and setting the electric potential of the black mask to that of the common electrodes, and creating a photolithography spacer that is placed in an elongated fashion at the same direction as the video signal line by an insulation material that has a dielectric constant larger than that of the liquid crystal. However, in this method, because the material of large dielectric constant is used, the capacitance between the black mask and the video signal line is increased, hence the video signal waveform is delayed and distorted, which is not appropriate for a large screen liquid crystal panel.

**[0013]** As disclosed in Japanese patent laid-open publication No. 11-24104, it is possible to almost completely shield the video signal line by constructing a passivation layer on the video signal line and placing a shielding electrode thereon along the video signal line. However, because this construction utilizes a very thin passivation layer with a thickness in the range between 0.3 micrometer and 1 micrometer, and the passivation layer made of silicon oxide or silicon nitride has a relatively large dielectric constant of 4-6, the capacitance between the shielding electrode and the video signal line increases. This causes the signal waveform to be delayed and distorted and is not appropriate for a large screen liquid crystal display panel.

**[0014]** Japanese patent laid-open publication No. 2001-209053 discloses a photolithography spacer constructed in a very thin manner that surround the video signal line using a dielectric material of a small dielectric constant so that the capacitance between the common electrodes on the side of the color filter and the video signal line can be decreased.

**[0015]** This technology, however, utilises a conventional method of injecting the liquid crystal through an injection opening. Thus, the thin and long photolithography spacers cause the liquid crystal to be injected at a very slow speed, which severely decreases the production efficiency.

**[0016]** Japanese patent laid-open publication Nos. 2002-258321 and 2002-323706 disclose a structure

which, utilises a dielectric material that has a smaller dielectric constant than that of the liquid crystal to cover the video signal line and places a transparent conductive material along the video signal line so that the pixel aperture ratio can be improved and the video signal line delay can be prevented. However, with this construction, it is not possible to produce the liquid crystal cell and the spacer at the same time. Therefore, an additional photolithography process has to be performed to produce

5 the photolithography spacers. This causes the production processes to be more complicated and costly.

**[0017]** The implementation of the technology disclosed in Japanese patent laid-open publication No. 2002-258321 is not enough to produce a transverse electric field type liquid crystal panel with high contrast and low light leakage. When an angle of the bumps of the dielectric material with a small dielectric constant that cover the video signal lines along the video signal lines is larger than 40 degrees, the conventional technology

10 of rubbing treatment using rubbing cloth causes areas with alignment defects due to the sideways slip caused at the tapered portions of the bumps in the direction of the movement at the tips of hairs of the rubbing cloth or areas on the inclined surfaces of the bumps where the 15 hair tips of the rubbing cloth cannot reach.

## SUMMARY OF THE INVENTION

**[0018]** The present invention has: been made to solve 30 the above mentioned problems involved in the conventional technology, and it is an object of the present invention to provide a large screen color liquid crystal display device which is capable of achieving an improved aperture ratio, a transmittance ratio, high brightness and high 35 contrast while promoting low cost and high production yield.

**[0019]** In order to achieve the above objectives, in the 40 first aspect of the present invention, a thin and long bump made of insulation material is placed on a video signal line formed on a transverse electric field type active matrix substrate in a manner to cover the video signal line. Then, a common electrode is formed along the video signal line in a manner to cover the thin and long insulation bump and the video signal line, thereby shielding an 45 electric field generated by the video signal line.

**[0020]** In the second aspect of the present invention, a thin and long bump made of insulation material is placed on a video signal line formed on a transverse electric field type active matrix substrate in a manner to cover the video signal line. Then, a common electrode is formed on both side walls of the thin and long insulation bump in a manner to sandwich the video signal line, thereby shielding an electric field generated by the video signal line.

**[0021]** In the third aspect of the present invention, the thin and long insulation bump formed in the manner to cover the video signal line, in the first and the second aspects of the present invention noted above, is used as

a spacer to define a liquid crystal cell gap when assembling the liquid crystal cells.

**[0022]** In the fourth aspect of the present invention, a thin and long bump made of insulation material for covering the video signal line on the transverse electric field type active matrix substrate and a spacer to define a liquid crystal cell gap are formed at the same time through a halftone exposure process. Then, a common electrode is formed on the thin and long insulation bump in a manner to cover the video signal line, thereby shielding an electric field generated by the video signal line.

**[0023]** In the fifth aspect of the present invention, a thin and long bump made of insulation material for covering the video signal line on the transverse electric field type active matrix substrate and a spacer to define a liquid crystal cell gap are formed at the same time through a halftone exposure process. Then, a common electrode is formed on both side walls of the thin and long insulation bump in a manner to sandwich the video signal line, thereby shielding an electric field generated by the video signal.

**[0024]** In the sixth aspect of the present invention, the common electrode for shielding the video signal line, in the first, second, third, fourth and fifth aspects of the present invention noted above, is made of a thin-film transparent conductive material that allows the light to transmit in a degree greater than 20% such as titanium metal compound including titanium nitride (TiNx), titanium oxide nitride (TiOxNy), titanium silicide nitride (TiSixNy), and titanium silicide (TiSix), or a metal oxide transparent conductive material such as indium oxide (In2O3) or zinc oxide (ZnO).

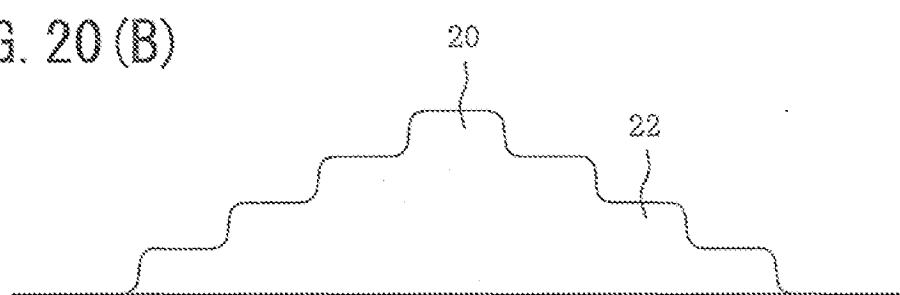

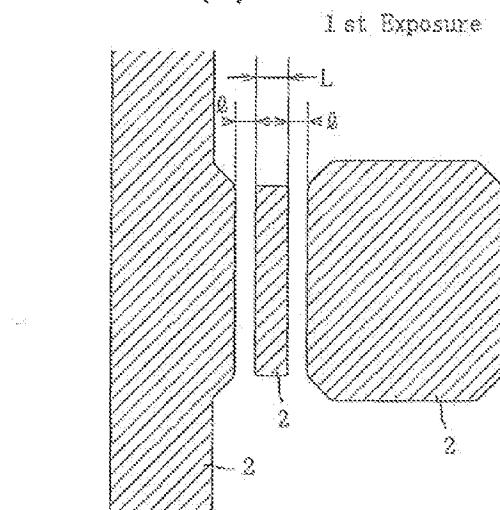

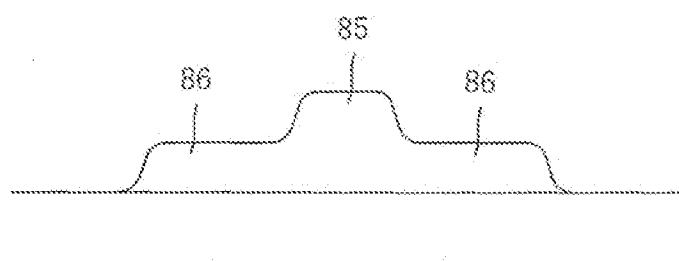

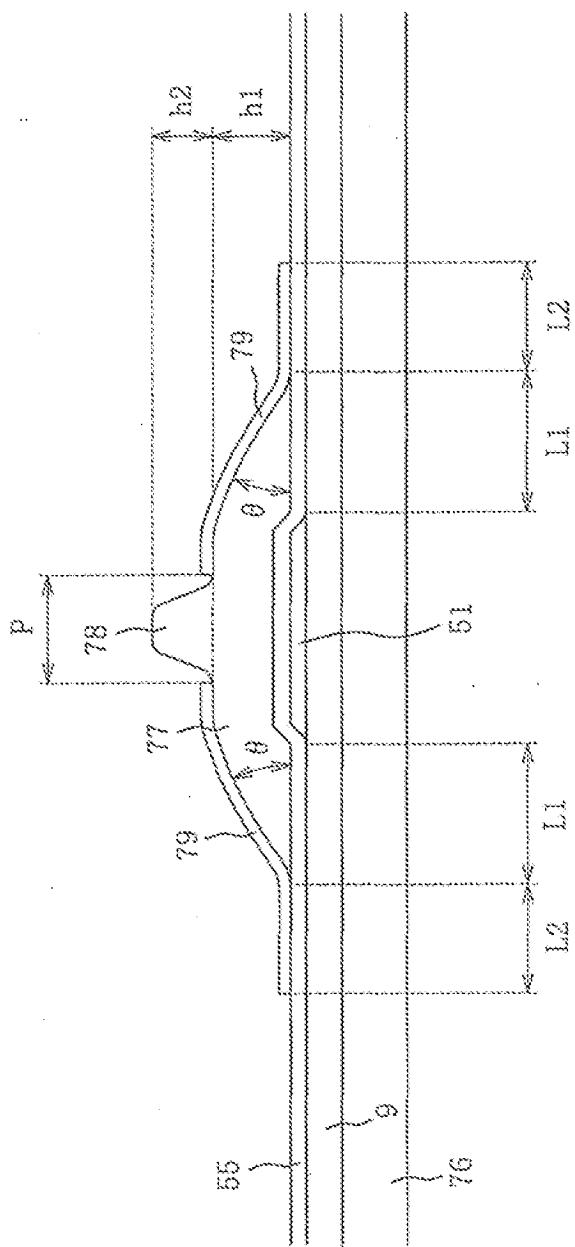

**[0025]** In the seventh aspect of the present invention, the thin and long insulation bump formed in the manner to cover the video signal line, in the first, second, third, fourth and fifth aspects of the present invention noted above, has a cross sectional shape of circular, semi-circular, hyperbolic, or parabolic shape and a taper angle  $\theta$  of the insulation bump is 30 degrees or less.

**[0026]** In the eighth aspect of the present invention, the thin and long insulation bump formed in the manner to cover the video signal line, in the first, second, third, fourth and fifth aspects of the present invention noted above, is not formed around an area at which the video signal line and the scanning line intersect with one another.

**[0027]** In the ninth aspect of the present invention, the spacer that is constructed at the same time as the thin and long insulation bump using the halftone exposure process, in the fourth and fifth aspects of the present invention noted above, is not covered by the common electrode at an area around the top thereof so as to expose the dielectric material that forming the spacer.

**[0028]** In the tenth aspect of the present invention, the spacer that defines a height of the thin and long insulation bump and the gap of the liquid crystal cell, in the fourth and fifth aspects of the present invention noted above, has a height difference  $h2$  within a range between 0.2

micrometers and 2.0 micrometers.

**[0029]** In the eleventh aspect of the present invention a density of the spacers that are constructed at the same time with the thin and long insulation bumps through the halftone exposure process, in the fourth and fifth aspects of the present invention noted above, is in a range between one (1) and seventy five (75) per square millimeter and the spacers are distributed evenly throughout the substrate.

**[0030]** In the twelfth aspect of the present invention, an area of the spacer that is constructed at the same time with the thin and long insulation bump through the halftone exposure process, in the fourth and fifth aspects of the present invention noted above, is in a range between 200 square micrometers and 2000 square micrometers per one square millimeter.

**[0031]** In the thirteenth aspect of the present invention, a thin and long bump made of insulation material is formed on a video signal line formed on a transverse electric field type active matrix substrate in a manner to cover the video signal line. Then, a common electrode is formed along the video signal line in a manner to cover the thin and long insulation bump and the video signal line, thereby shielding the electric field generated by the video signal line. Further, a thin and long insulation bump is similarly formed on a scanning line in a manner to cover the scanning line. Then, a common electrode is formed on side walls of the scanning line in a manner to sandwich the scanning line, thereby shielding the electric field generated by the scanning line.

**[0032]** In the fourteenth aspect of the present invention, a thin and long bump made of insulation material is formed on a video signal line formed on a transverse electric field type active matrix substrate in a manner to cover the video signal line. Then, a common electrode is formed on both side walls of the thin and long insulation bump in a manner to sandwich the video signal line, thereby shielding the electric field generated by the video signal line. Further, a thin and long insulation bump is similarly formed on a scanning line in a manner to cover the scanning line. Then, a common electrode is formed on both side walls of the scanning line in a manner to sandwich the scanning line, thereby shielding the electric field generated by the scanning line.

**[0033]** In the fifteenth aspect of the present invention, the thin and long insulation bumps formed in the manner to cover around the video signal line and the scanning line, in the thirteenth and fourteenth aspects of the present invention noted above, are used as a spacer to define a liquid crystal cell gap when assembling the liquid crystal cells.

**[0034]** In the sixteenth aspect of the present invention, a thin and long bump made of insulation material for covering the video signal line on the transverse electric field type active matrix substrate and a spacer to define a liquid crystal cell gap are formed at the same time through a halftone exposure process. Then, a common electrode is formed on the thin and long insulation bump in a man-

ner to cover the video signal line, thereby shielding the electric field generated by the video signal line. Further, a thin and long insulation bump is similarly formed on a scanning line through a halftone exposure process in a manner to cover the scanning line. Then, a common electrode is formed on both side walls of the scanning line in a manner to sandwich the scanning line, thereby shielding the electric field generated by the scanning line.

**[0035]** In the seventeenth aspect of the present invention, a thin and long bump made of insulation material for covering the video signal line on the transverse electric field type active matrix substrate and a spacer to define a liquid crystal cell gap are formed at the same time through a halftone exposure process. Then, a common electrode is formed on both side walls of the thin and long insulation bump in a manner to sandwich the video signal line, thereby shielding the electric field generated by the video signal. Farther, a thin and long insulation bump is similarly formed on a scanning line through a halftone exposure process in a manner to cover the scanning line. Then, a common electrode is formed on both side walls of the scanning line in a manner to sandwich the scanning line, thereby shielding the electric field generated by the scanning line.

**[0036]** In the eighteenth aspect the present invention, the common electrodes for shielding the video signal line and the scanning line, in the thirteenth, fourteenth, fifteenth, sixteenth and seventeenth, aspects of the present invention noted above, are made of thin-film transparent conductive material that allows the light transmit in a degree greater than 20 % such as titanium metal compound including titanium nitride (TiNx), titanium oxide nitride (Ti-OxNy), titanium silicide nitride (TiSixNy), and titanium silicide (TiSix), or a metal oxide transparent conductive material such as indium oxide (In2O3) or zinc oxide (ZnO).

**[0037]** In the nineteenth aspect of the present invention, the thin and long insulation bumps formed in the manner to cover the video signal line and the scanning line, in the thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above have, have a cross sectional shape of circular, semi-circular, hyperbolic, or parabolic shape and a taper angle  $\theta$  of the insulation bump is 30 degrees or less.

**[0038]** In the twentieth aspect of the present invention, the thin and long insulation bumps formed in the manner to cover the video signal line and the scanning line, in the thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are not formed around an area at which the video signal line and the scanning line intersect with one another,

**[0039]** In the twenty first aspect of the present invention, the spacer that is constructed at the same time as the thin and long insulation bump through the halftone exposure process, in the sixteenth and seventeenth aspects of the present invention noted above, is not covered by the common electrode at an area around the top thereof so as to expose the dielectric material that forming the spacer.

**[0040]** In the twenty second aspect of the present invention, the spacer that defines a height of the thin and long insulation bump and a gap of the liquid crystal cell, in the sixteenth and seventeenth aspects of the present invention noted above, has a height difference  $h2$  within a range between 0.2 micrometers and 2.0 micrometers,

**[0041]** In the twenty third aspect of the present invention, a density of the spacers that are constructed at the same time with the thin and long insulation bump through the halftone exposure process, in the sixteenth and seventeenth aspects of the present invention noted above, is in a range between one (1) and seventy five (75) per square millimeter and the spacers are distributed evenly throughout the substrate.

**[0042]** In the twenty fourth aspect of the present invention an area of the spacer that is constructed at the same time with the thin and long insulation bump through the halftone exposure process, in the sixteenth and seventeenth aspects of the present invention noted above, is in a range between 200 square micrometers and 2000 square micrometer per one square millimeter.

**[0043]** In the twenty fifth aspect of the present invention, the common electrodes, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are provided in an upper layer and a lower layer through a gate insulating film and a passivation film therebetween in a manner to sandwich the video signal line in up/down directions and right/left directions wherein the common electrode on the lower layer is made of a metal electrode which prohibits the light to pass there through whereas the common electrode in the upper layer is a transparent electrode that allows the light to pass there through. The common electrode at the upper layer has an electrode width wider than that of the common electrode in the lower layer and is projected towards the side of the liquid crystal drive electrode.

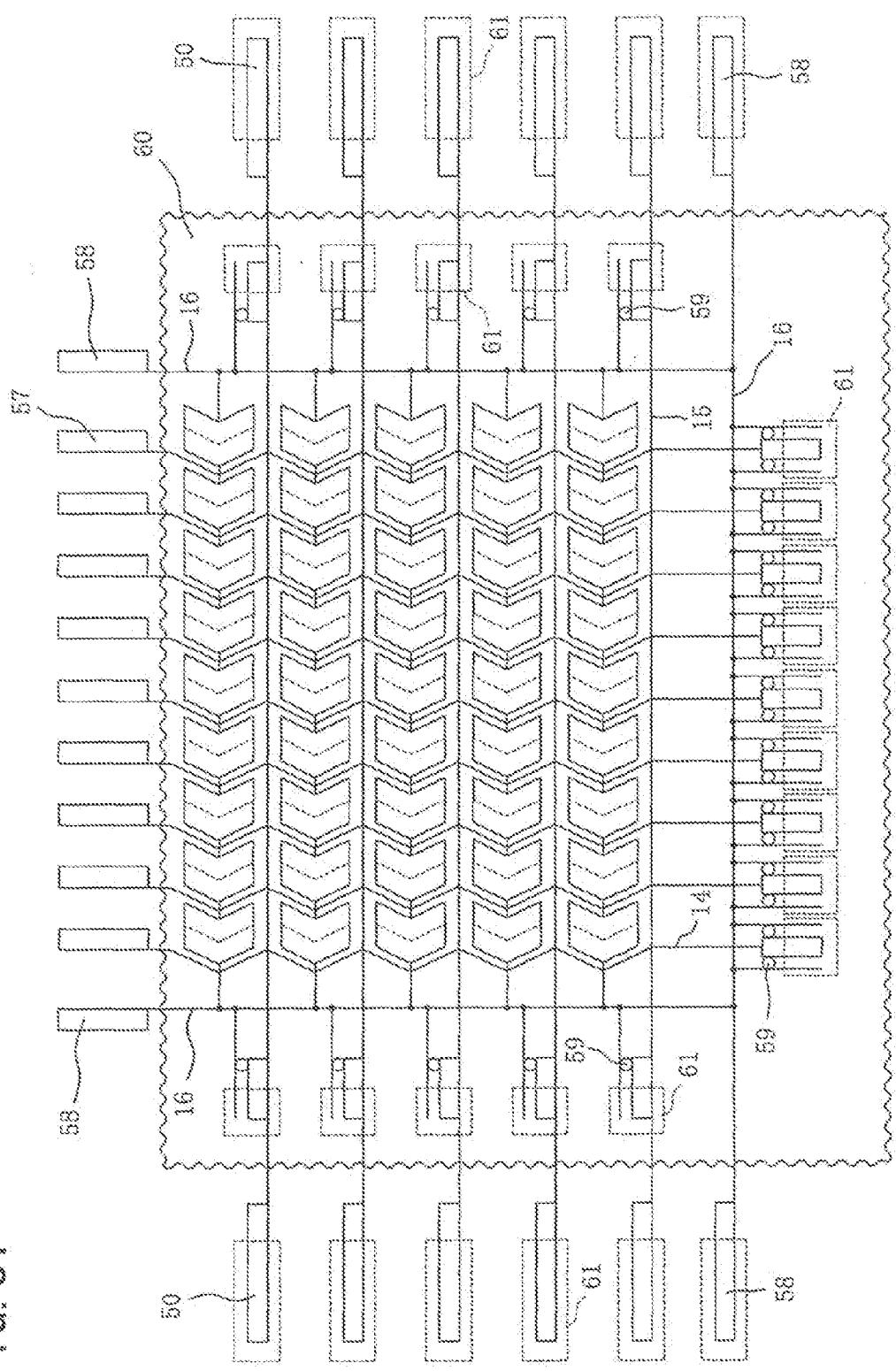

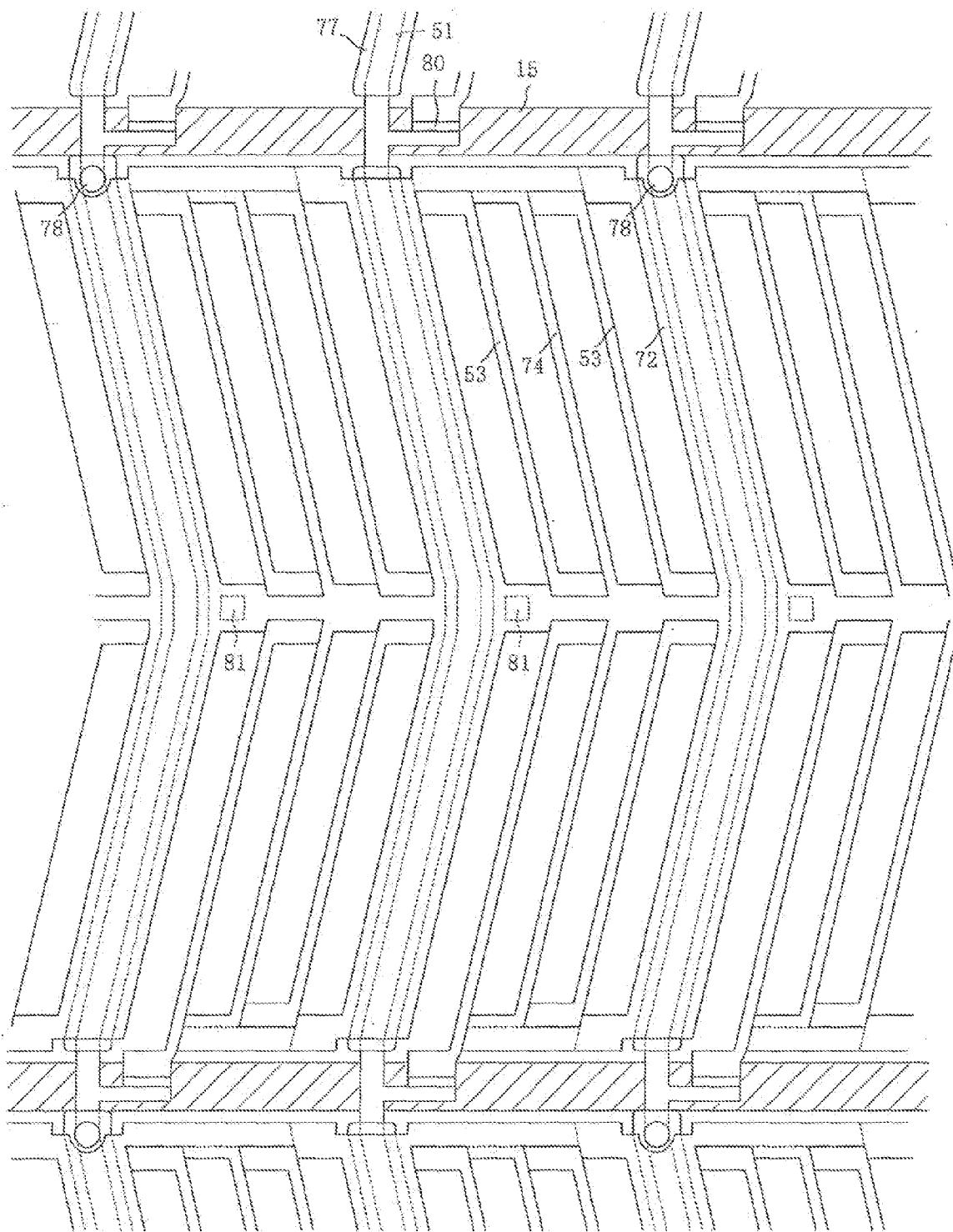

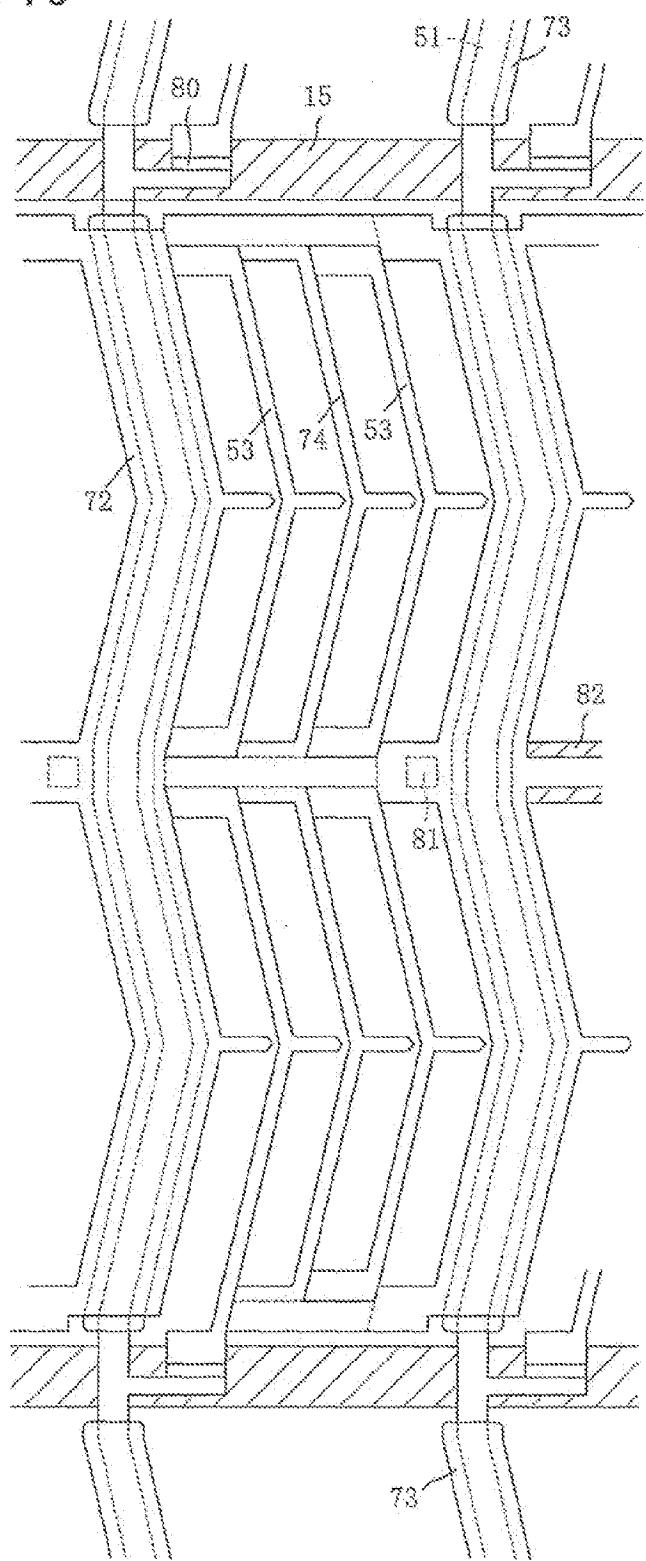

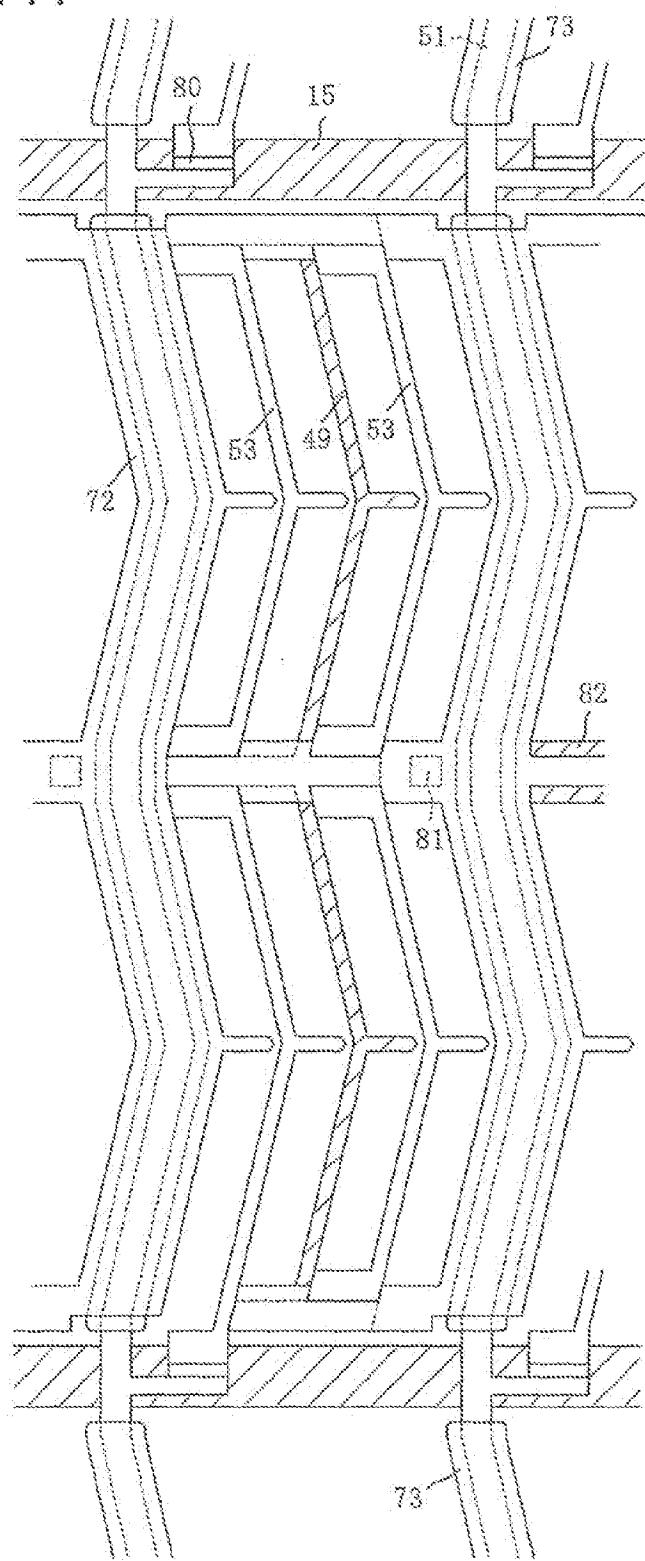

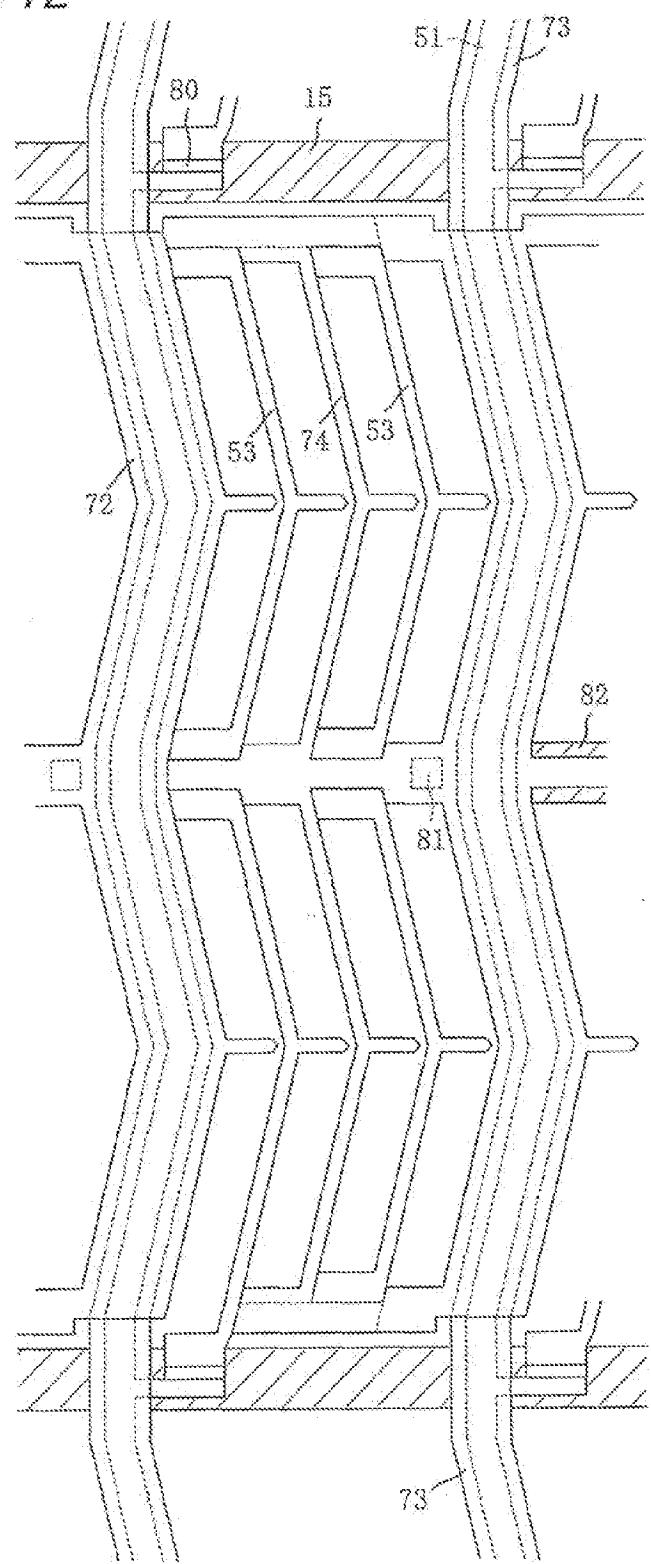

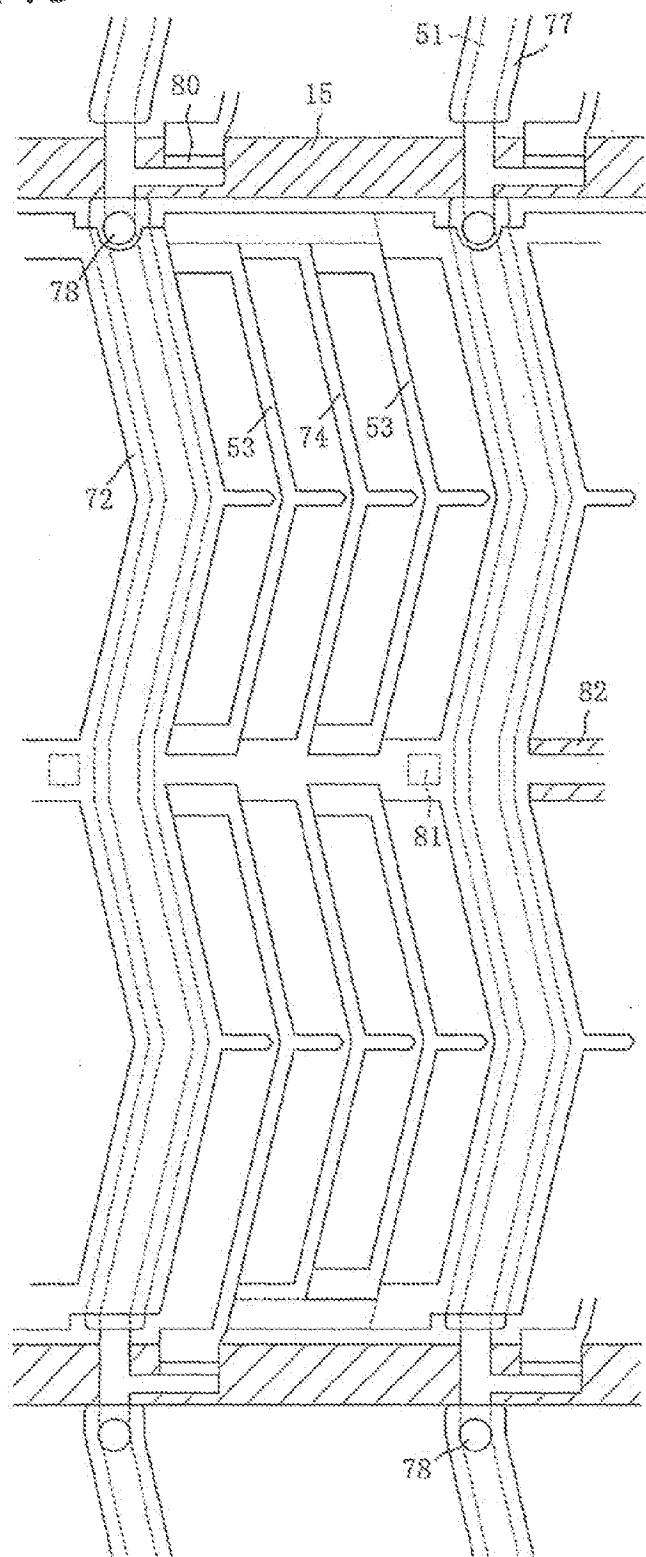

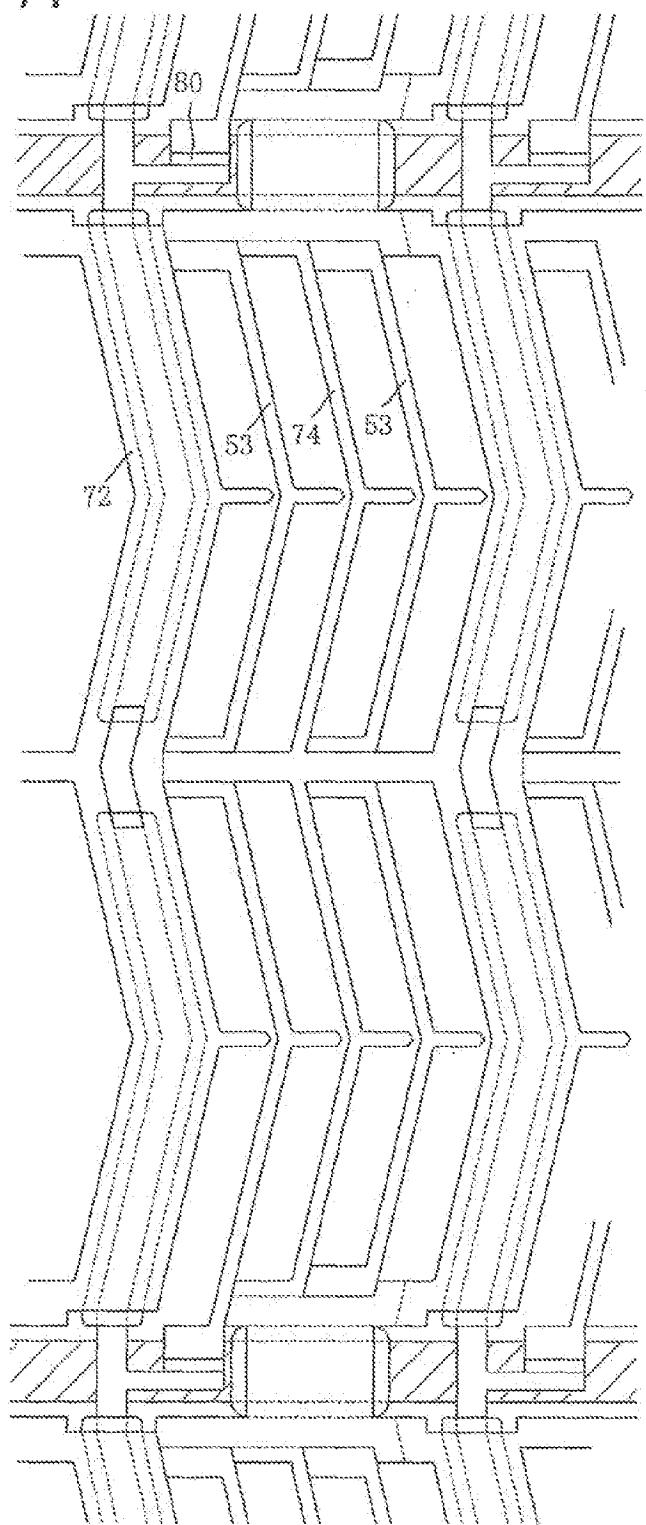

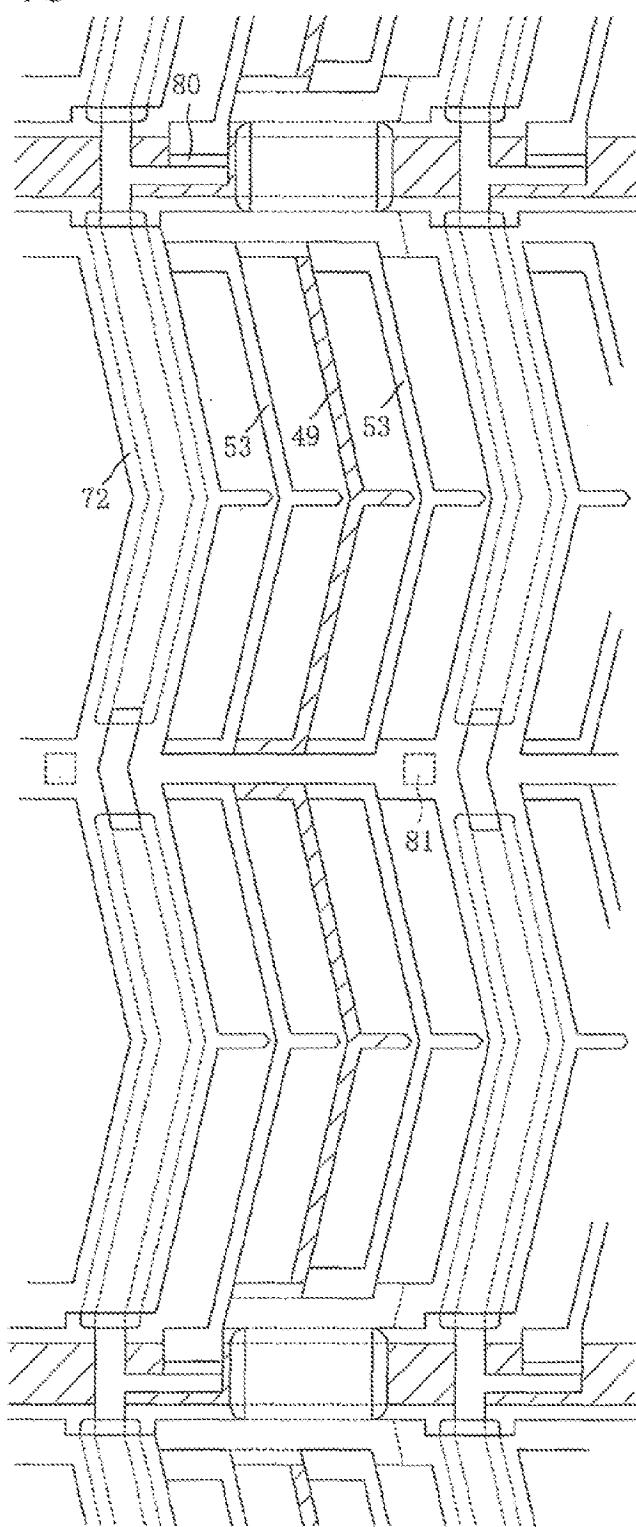

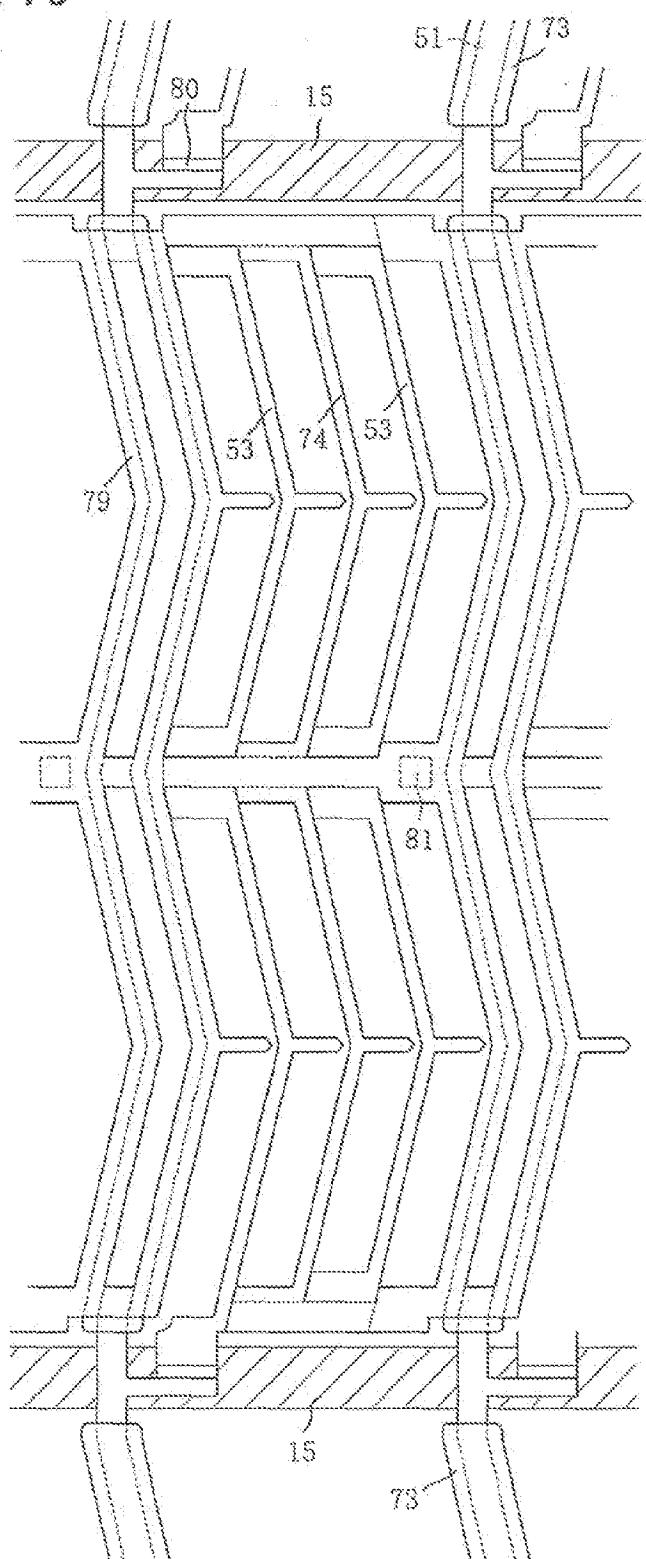

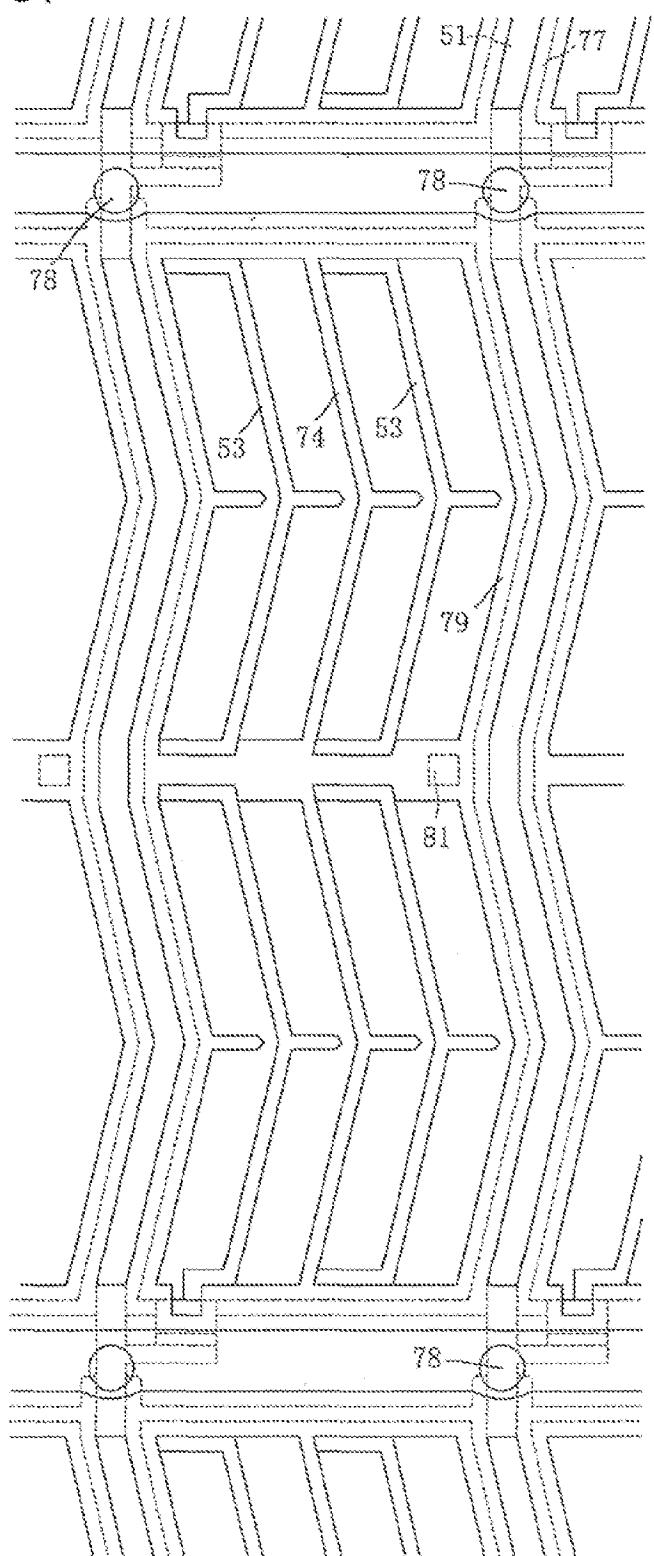

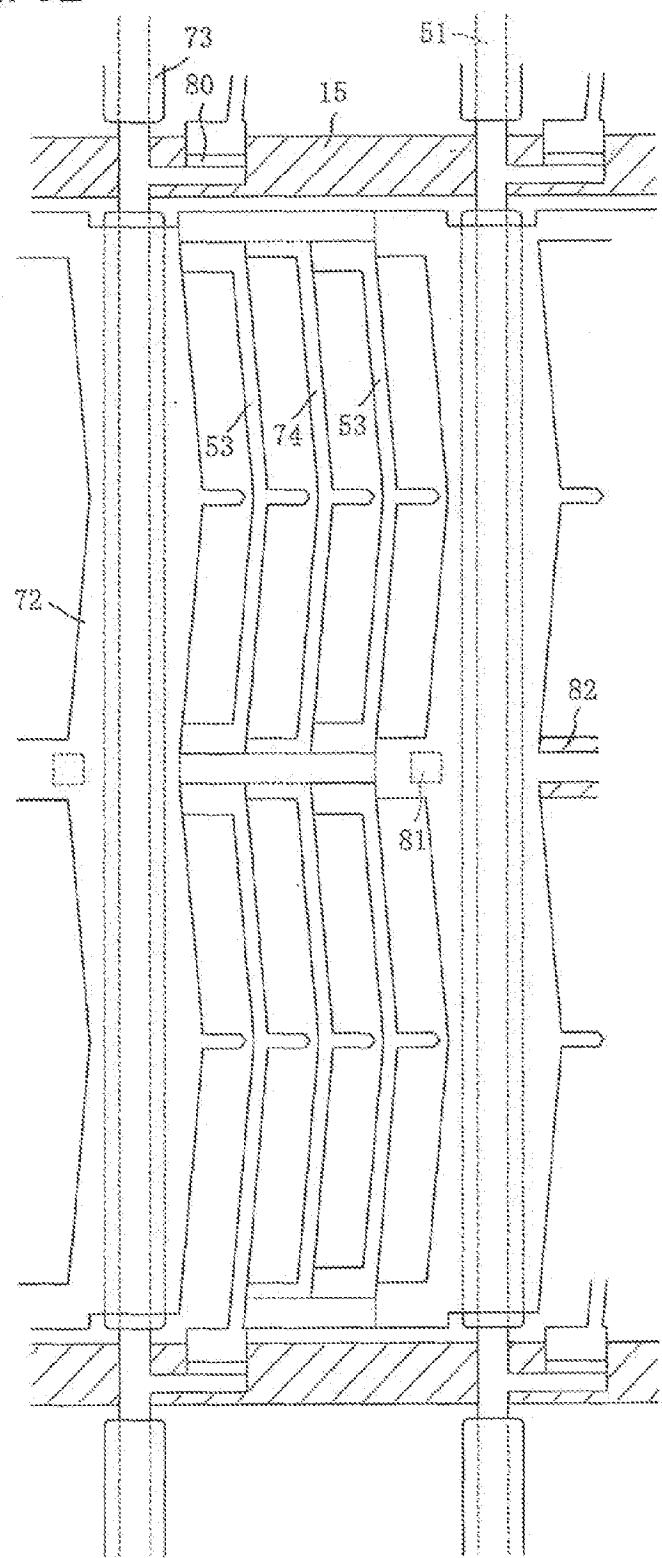

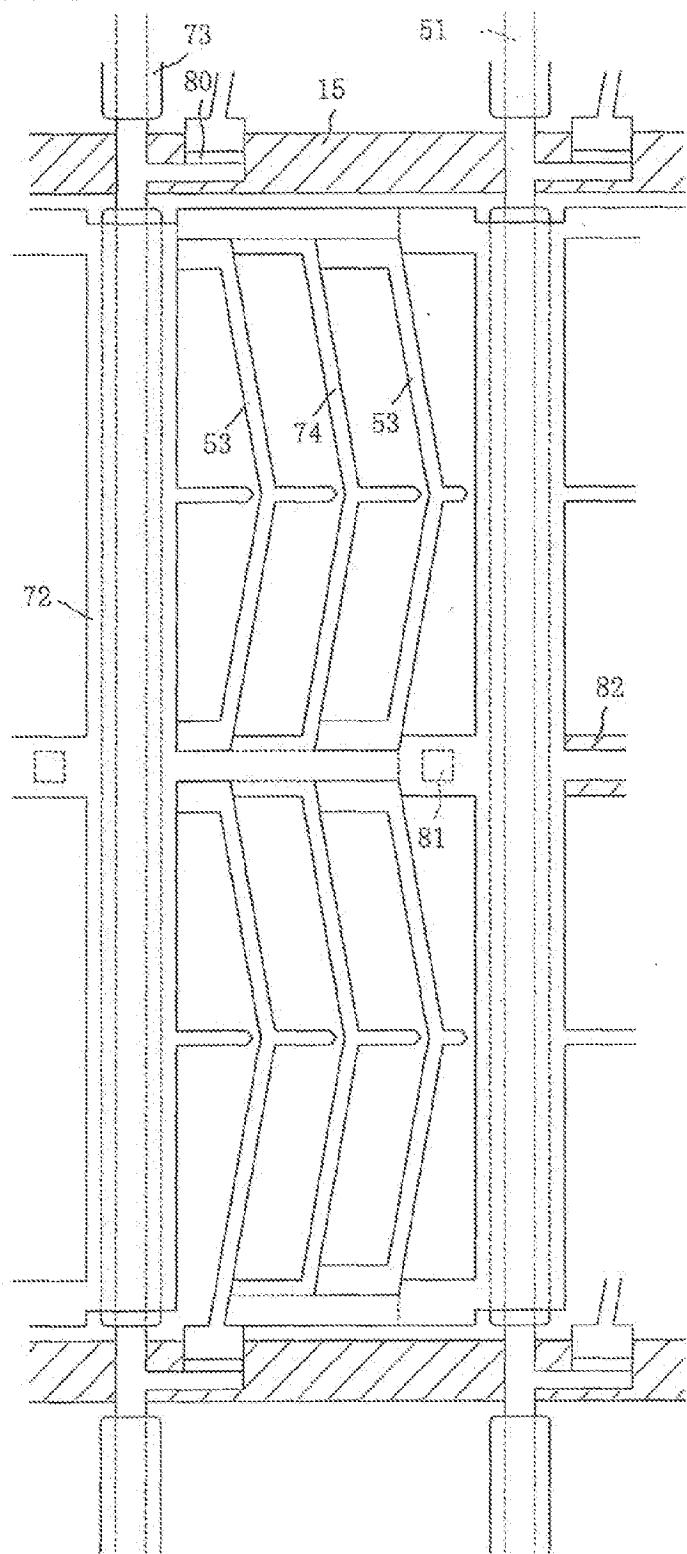

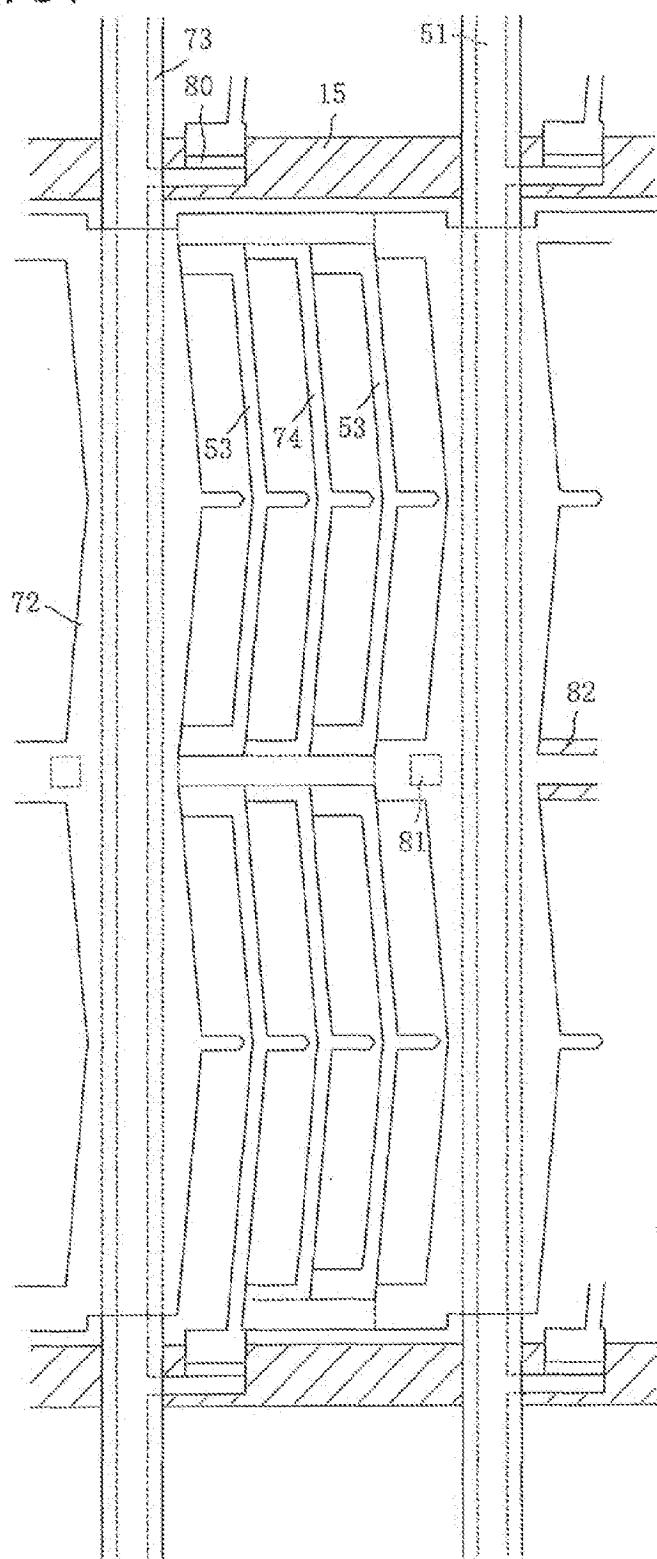

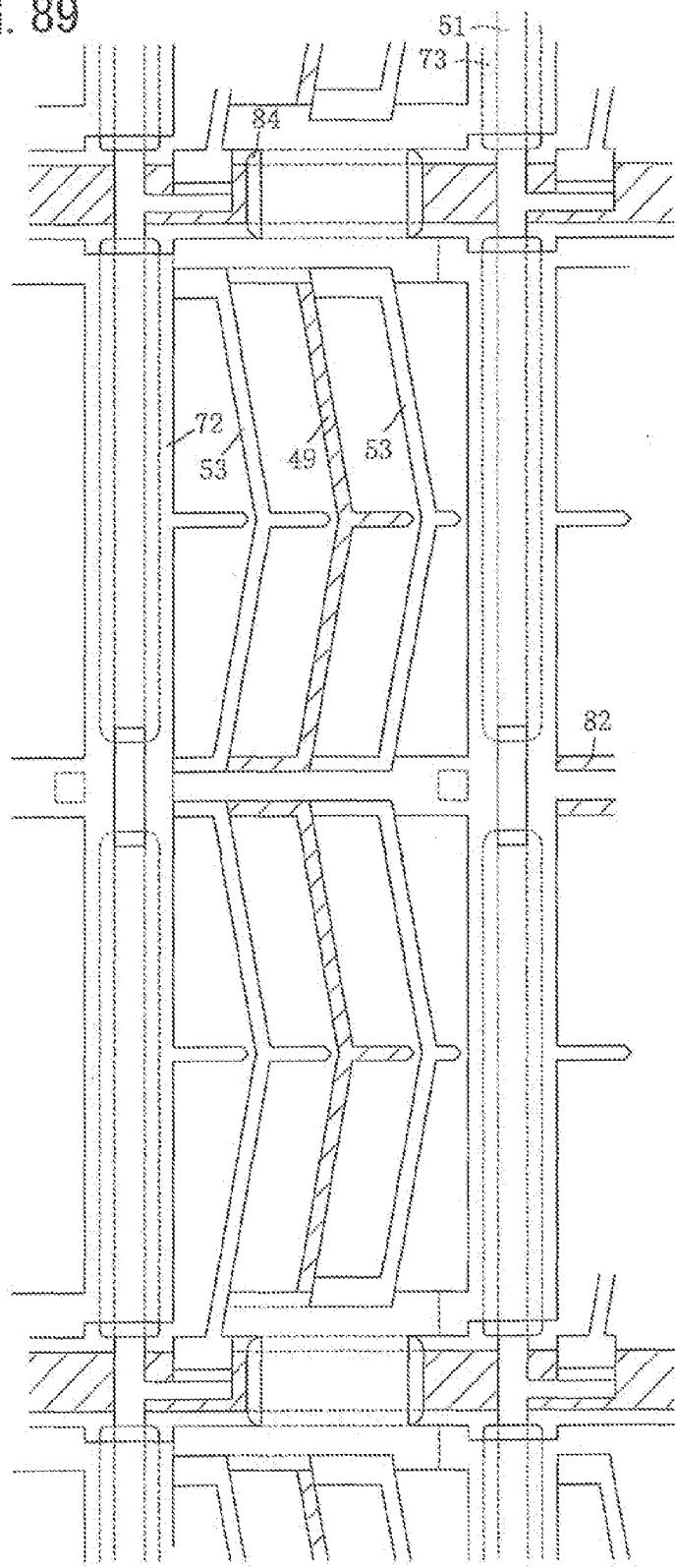

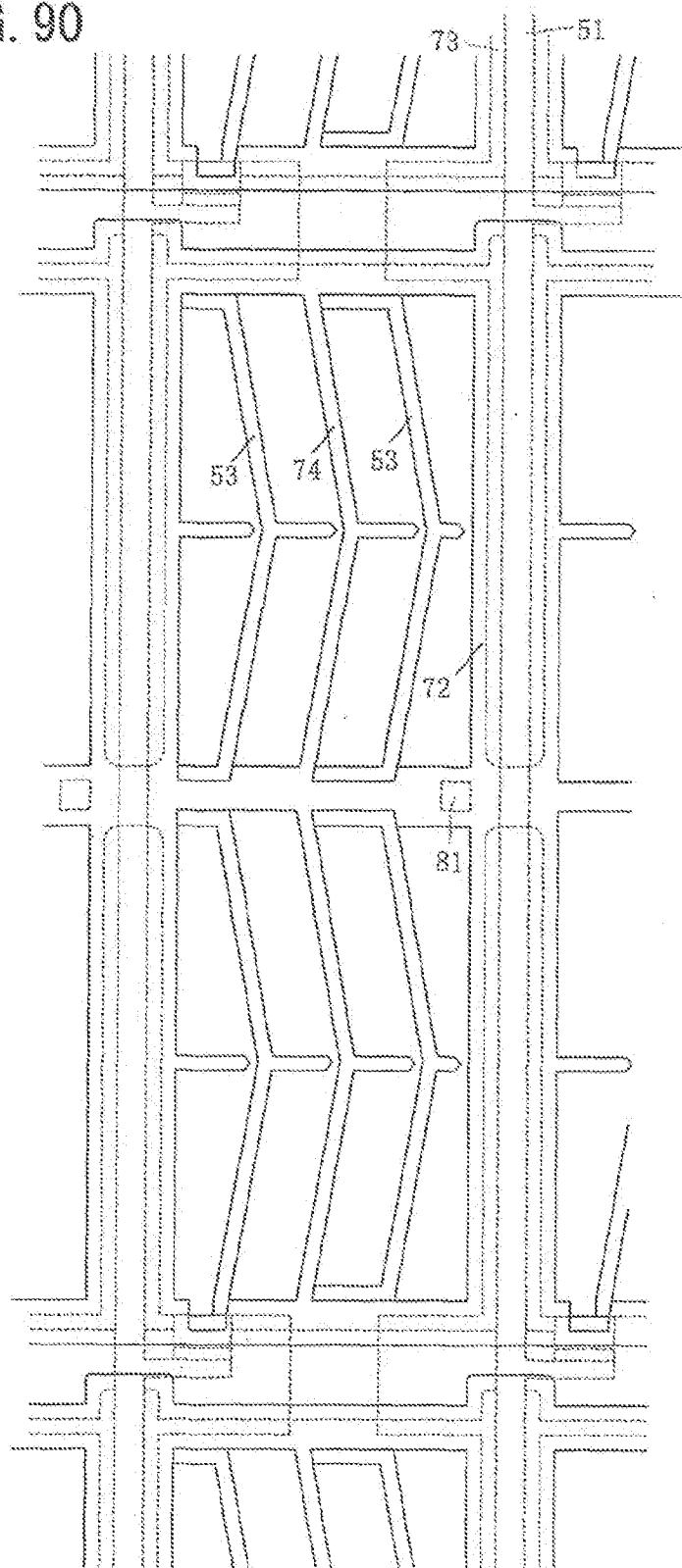

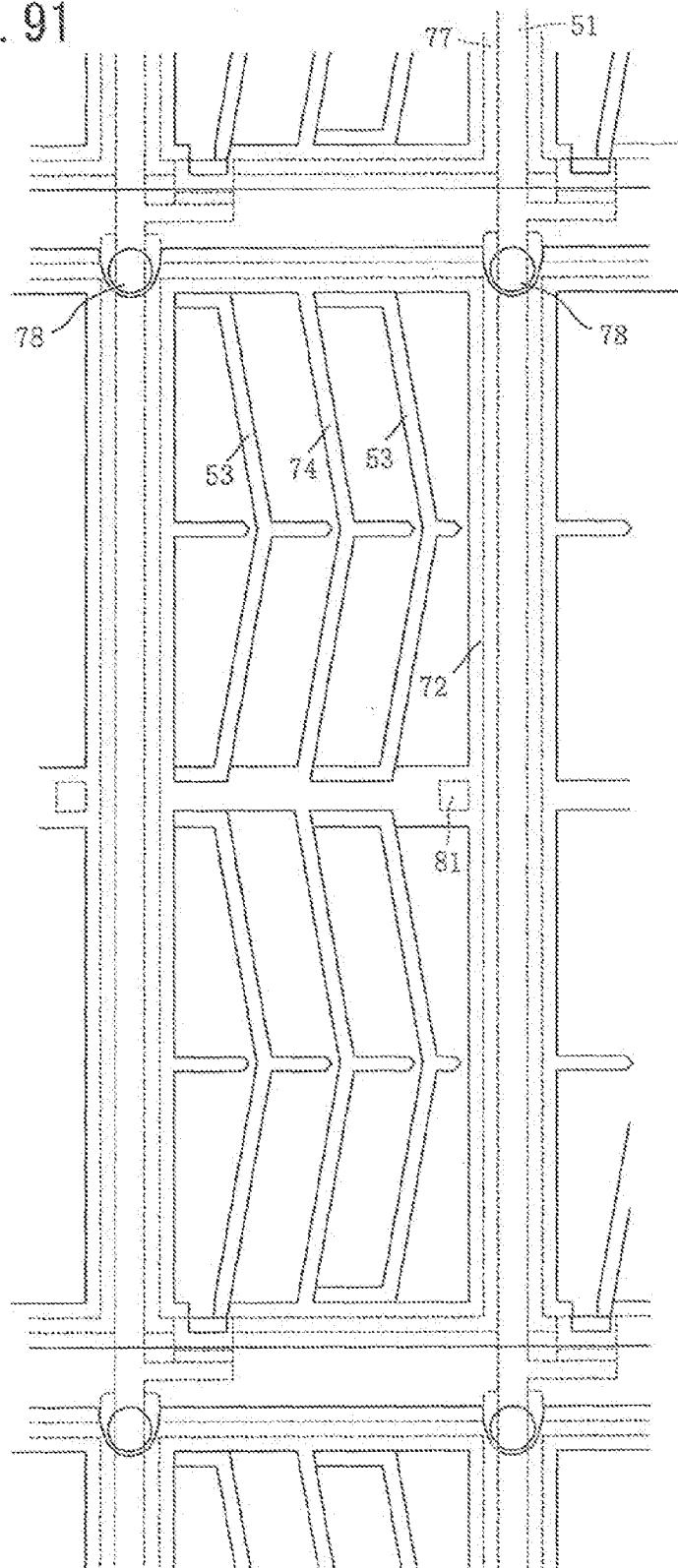

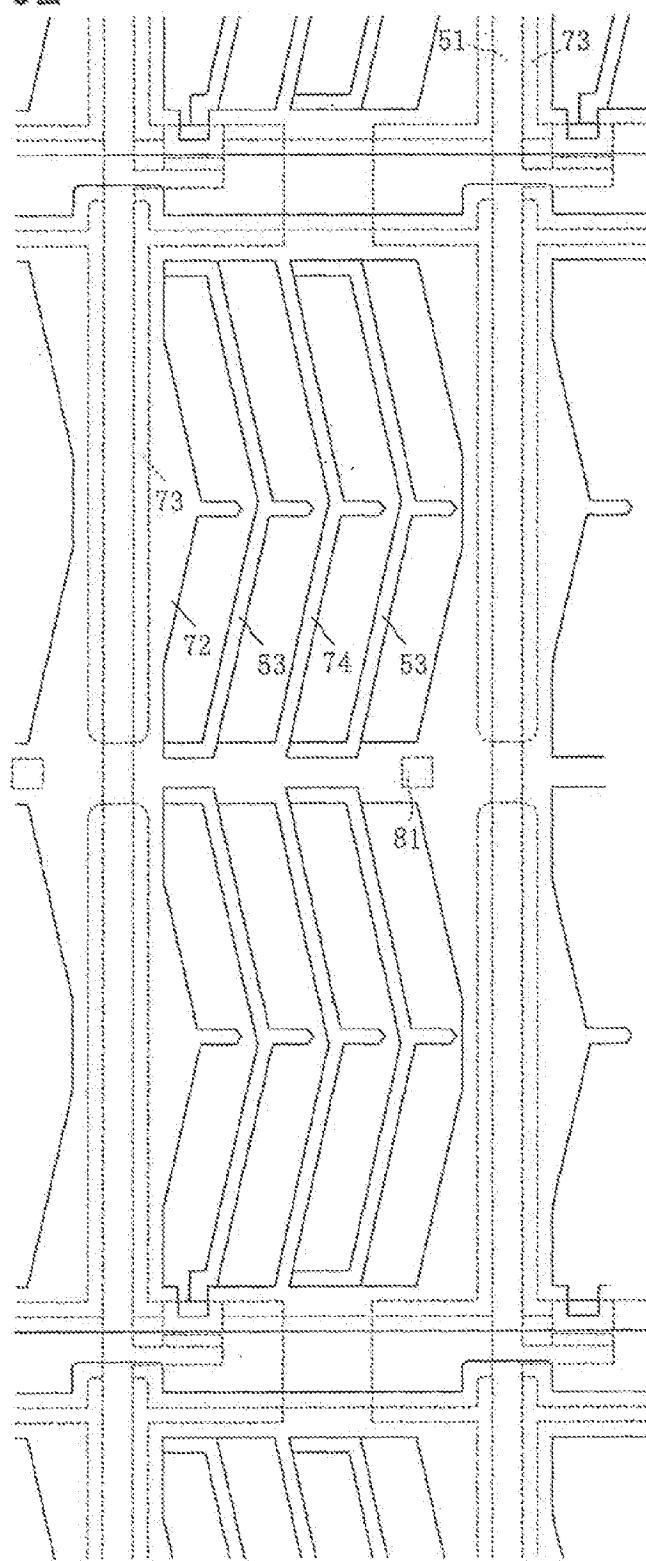

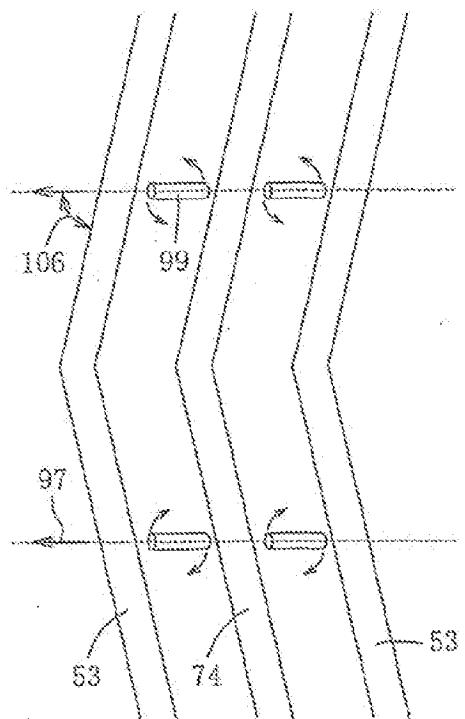

**[0044]** In the twenty sixth aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, and the common electrode formed along the video signal line for shielding the video signal line, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are aligned in a manner of straight line wherein the liquid crystal drive electrode within the pixel and the common electrode within the pixel are bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to an alignment direction of the liquid crystal molecule.

**[0045]** In the twenty seventh aspect of the present invention, the video signal line and the thin and long insulation bump formed in the manner to cover the video signal line, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are aligned in a manner of straight line wherein the common electrode formed along the video signal line for shielding the video

signal line, the liquid crystal drive electrode within the pixels and the common electrode within the pixel are bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to an alignment direction of the liquid crystal molecule.

**[0046]** In the twenty eighth aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, the common electrode formed along the video signal line for shielding the video signal line, and the common electrode within the pixel, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are aligned in a manner of straight line wherein only the liquid crystal drive electrode within the pixel is bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to an alignment direction of the liquid crystal molecule.

**[0047]** In the twenty ninth aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, the common electrode formed along the video signal line for shielding the video signal line, the common electrode within a pixel, and the liquid crystal drive electrode within the pixel, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to an alignment direction of the liquid crystal molecule.

**[0048]** In the thirtieth aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, the common electrode formed along the video signal line for shielding the video signal line, the common electrode within the pixel, and the liquid crystal drive electrode within the pixel, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to an alignment direction of the liquid crystal molecule, and similarly, the color filter layer and the light shielding film (black mask) on the side of the color filter substrate which is opposite to the active matrix substrate are bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to an alignment direction of the liquid crystal molecule.

**[0049]** In the thirty first aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, and the common electrode forced along the video signal line for shielding the video signal line, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are aligned in a manner of straight line wherein the liquid crystal drive electrode within the pixel and the common electrode within the pixel are bent within

the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to an alignment direction of the liquid crystal molecule.

**[0050]** In the thirty second aspect of the present invention, the video signal line and the thin and long insulation bump formed in the manner to cover the video signal line, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are aligned in a manner of straight line wherein the common electrode formed along the video signal line for shielding the video signal line, the liquid crystal drive electrode within the pixel, and the common electrode within the pixel are bent within the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to an alignment direction of the liquid crystal molecule.

**[0051]** In the thirty third aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, the common electrode formed along the video signal line for shielding the video signal line, and the common electrode within the pixel, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are aligned in a manner of straight line wherein only the liquid crystal drive electrode within the pixel is bent within the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to an alignment direction of the liquid crystal molecule.

**[0052]** In the thirty fourth aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, the common electrode formed along the video signal line for shielding the video signal line, the common electrode within the pixel, and the liquid crystal drive electrode within the pixel, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are bent within the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to an alignment direction of the liquid crystal molecule.

**[0053]** In the thirty fifth aspect of the present invention, the video signal line, the thin and long insulation bump formed in the manner to cover the video signal line, the common electrode formed along the video signal line for shielding the video signal line, the common electrode within the pixel, and the liquid crystal drive electrode within the pixel, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, are bent within the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to an alignment direction of the liquid crystal molecule, and similarly, the color filter layer and the light shielding film (black mask) on the side of the color filter substrate which is opposite to the active matrix substrate are bent within the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to an alignment direction of the liquid crystal molecule.

ment direction of the liquid crystal molecule.

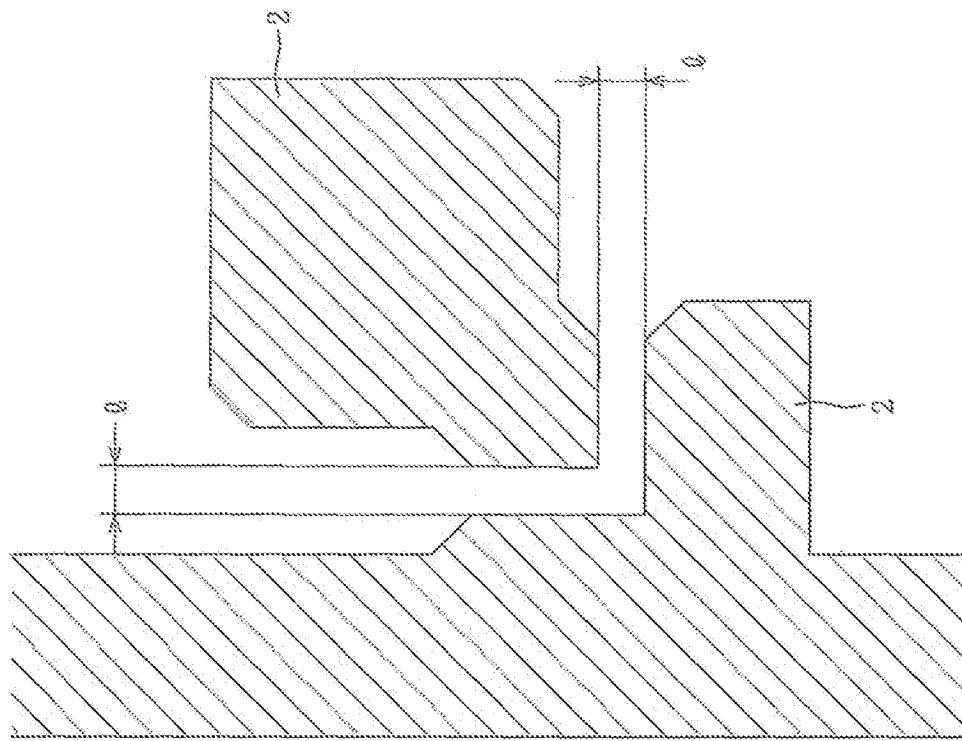

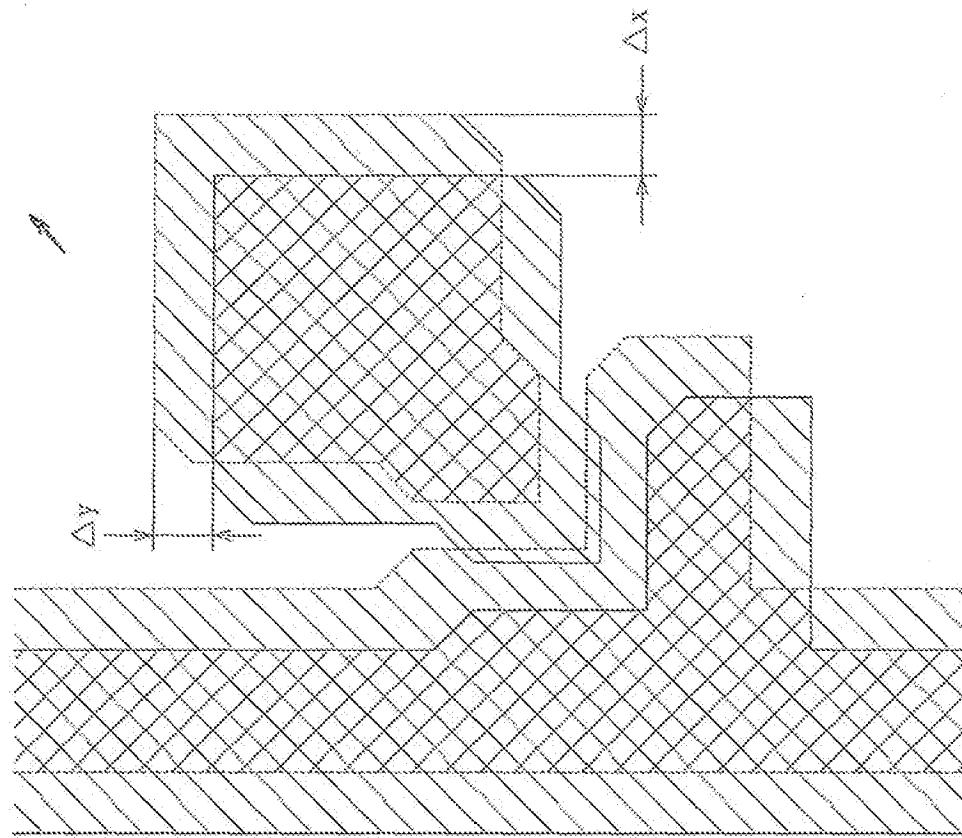

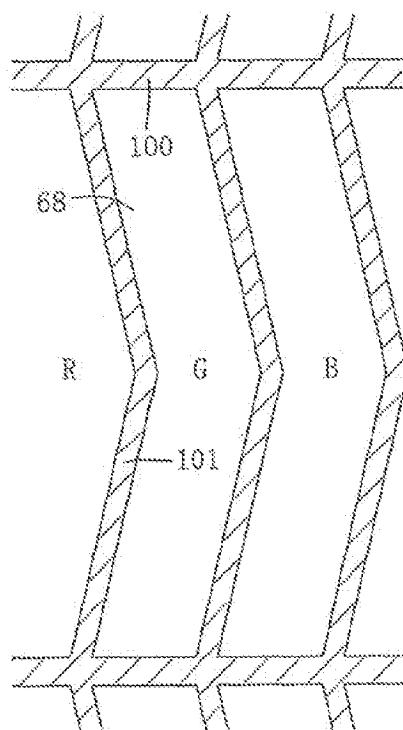

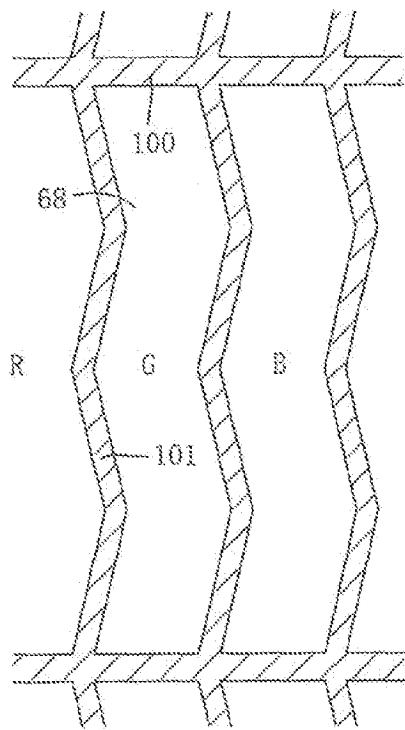

**[0054]** In the thirty' sixth aspect of the present invention, the thin and long insulation bump formed along the video signal line to cover the video signal line, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, has a dielectric constant of less than 3.3, and a height h1 is in a range between 1.5 micrometers and 5.0 micrometers. A distance L1 between an edge of the video signal line and an edge of the insulation bump is in a range between 3.0 micrometers and 6.0 micrometers.

**[0055]** In the thirty seventh aspect of the present invention, a distance L2 between an edge of the insulation bump covering the video signal line and an edge of the shielding common electrode covering the insulation bump, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, is in a range between 0.5 micrometers and 10.0 micrometers.

**[0056]** In the thirty eighth aspect of the present invention, monomer or oligomer used as a material for fabricating the insulation bump covering the video signal line, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present invention noted above, has at least one benzo-cyclobutene structure or its dielectric form or has at least one fluorene skeleton or its dielectric form.

**[0057]** In the thirty ninth aspect of the present invention, when forming the thin and long insulation bump covering the video signal line, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects of the present indentation noted above, at least one barrier bump spacer in a closed loop structure is formed at the same time for preventing the breakage of a main seal due to an atmospheric pressure or a pressure from liquid crystals at a location identical to an area on which the main seal of the liquid crystal cell that surrounds an entire effective pixel area is formed.

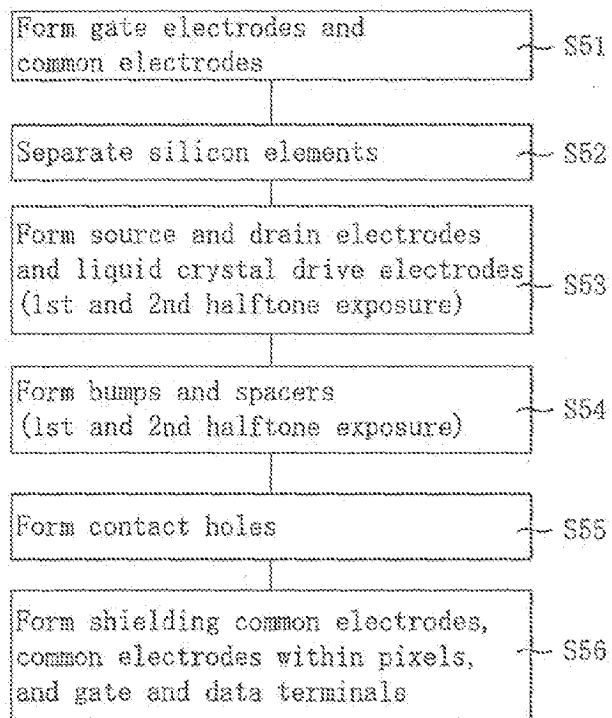

**[0058]** In the fortieth aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming patterns for scanning lines (scanning line patterning step);

- (2) separating the silicon elements for the thin film transistors from the semiconductor layer (silicon island step) ;

- (3) forming the video signal lines and the liquid crystal drive electrodes at the same time;

- (4) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the insulation bumps that cover the video signal lines at the same time (halftone exposure process);

- (5) forming the contact holes for terminal portions and for the static electricity protection circuits; and

- (6) forming the transparent common electrodes for

shielding the video signal line and the transparent common electrodes within the pixel at the same time.

**[0059]** In the forty first aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the scanning lines, common electrodes within the pixels, and lower layer common electrodes for shielding the video signal lines at the same time;

- (2) separating the silicon elements for the thin film transistors from the semiconductor layer (silicon island step);

- (3) forming the video signal lines and the liquid crystal drive electrodes at the same time;

- (4) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the insulation bumps that cover the video signal lines at the same time (halftone exposure process);

- (5) forming the contact holes for terminal portions and for the static electricity protection circuits; and

- (6) It forming the transparent common electrodes for shielding the video signal lines.

**[0060]** In the forty second aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming patterns for the scanning lines;

- (2) forming the patterns of etching stopper channels for the thin film transistors;

- (3) forming the video signal lines and the liquid crystal drive electrode at the same time;

- (4) forming the spacer bumps that cover the video signal line, or simultaneously forming the spacers and the insulation bumps that cover the video signal lines at the same time (halftone exposure process);

- (5) forming the contact holes for terminal portions and for the static electricity protection circuits; and

- (6) forming the transparent common electrodes for shielding the video signal lines and the transparent common electrodes within the pixels at the same time.

**[0061]** In the forty third aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the scanning lines, common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) forming the patterns of etching stopper channels for the thin film transistors;

- (3) forming the video signal lines and the liquid crystal

drive electrodes at the same time;

- (4) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the insulation bumps that cover the video signal lines at the same time (halftone exposure process);

- (5) forming the contact holes for terminal portions and for the static electricity protection circuits; and

- (6) forming the transparent common electrodes for shielding the video signal lines.

**[0062]** In the forty fourth aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the patterns for the scanning lines;

- (2) forming the video signal lines and the liquid crystal drive electrodes, and separating silicon elements for the thin film transistors from the semiconductor layer at the same time (halftone exposure process);

- (3) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the insulation bumps that cover the video signal lines at the same time (halftone exposure process);

- (4) forming the contact holes for terminal portions and for the static electricity protection circuits; and

- (5) forming the transparent common electrodes for shielding the video signal lines and the transparent common electrodes within the pixels at the same time.

**[0063]** In the forty fifth aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the scanning lines, the common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) forming the video signal lines and the liquid crystal drive electrodes, and separating silicon elements for the thin film transistors from the semiconductor layer at the same time (halftone exposure process);

- (3) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the insulation bumps that cover the video signal lines at the same time (halftone exposure process);

- (4) forming the contact holes for terminal portions and for the static electricity protection circuits; and

- (5) forming the transparent common electrodes for shielding the video signal lines.

**[0064]** In the forty sixth aspect of the present invention, the common electrodes formed along the thin and long insulation bumps in the manner to surround the video signal lines for shielding, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and sev-

enteenth aspects of the present invention noted above, are connected with each other throughout the entire effective pixel display area and are set to an electric potential close to a center voltage of the video signal voltage.

**[0065]** In the forty seventh aspect of the present invention, the electrode for one pixel for driving the liquid crystal molecule, in the first, second, third, fourth, fifth, thirteenth, fourteenth, fifteenth, sixteenth and seventeenth aspects

- 5 of the present invention noted above, is configured by three different electrodes including a single electrode connected to the thin film transistor for driving the liquid crystal, a lower layer common electrode formed both right and left sides to the pixel for shielding the video signal line, and an upper layer shielding common electrode formed along the thin and long insulation bump surrounding the video signal line, so that there exist no common electrodes within the pixel.

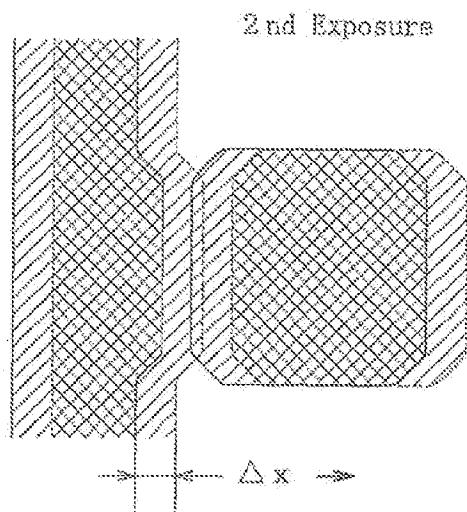

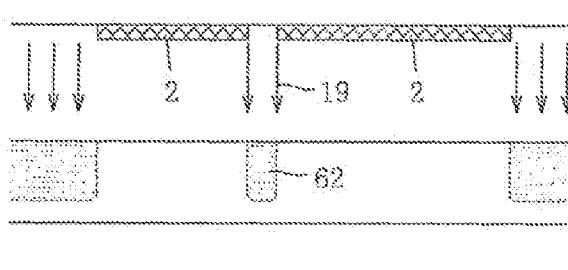

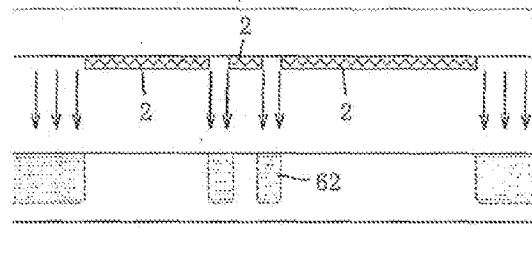

**[0066]** In the transverse electric field type active matrix

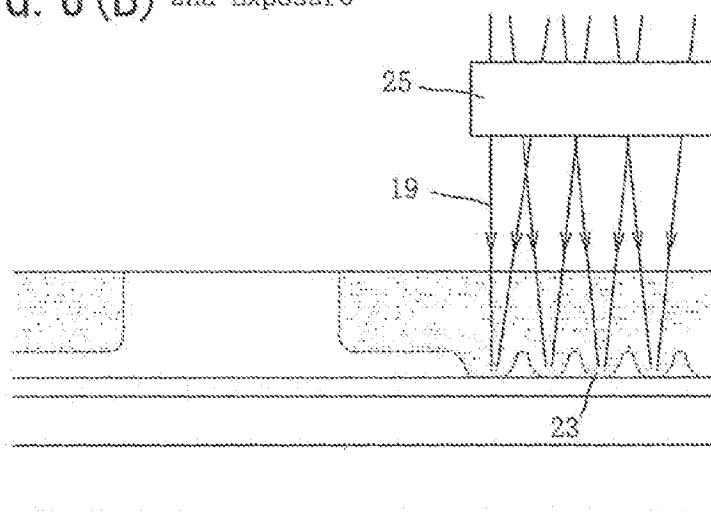

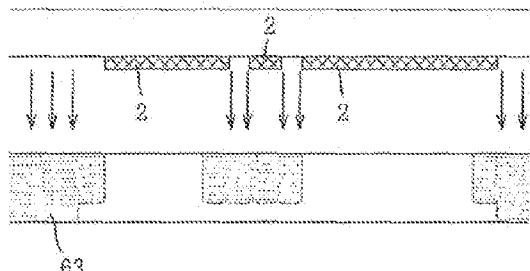

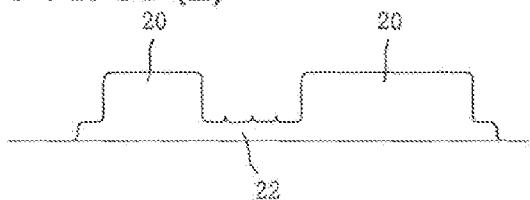

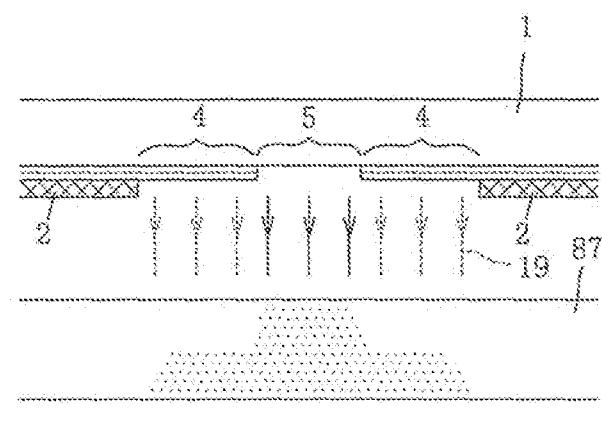

- 20 liquid crystal display device in the forty eighth aspect of the present invention, processes for planarizing (levelling) the active matrix substrate and construction of the photolithography spacers are conducted at the same time by first applying negative photoresist with a thickness which is a sum of a liquid crystal cell gap and the largest thickness among the common electrode within the pixel made of non-transparent metal material or metal silicide or metal nitride, the lower layer common electrode for shielding the video signal line, and the liquid crystal drive electrode, then exposing the ultraviolet light to the entire effective pixel area from the back surface of the active matrix substrate, and then completely exposing the ultraviolet light to the portions where the spacers are formed using the photomask for the photolithography spacers, and lastly developing the active matrix substrate.

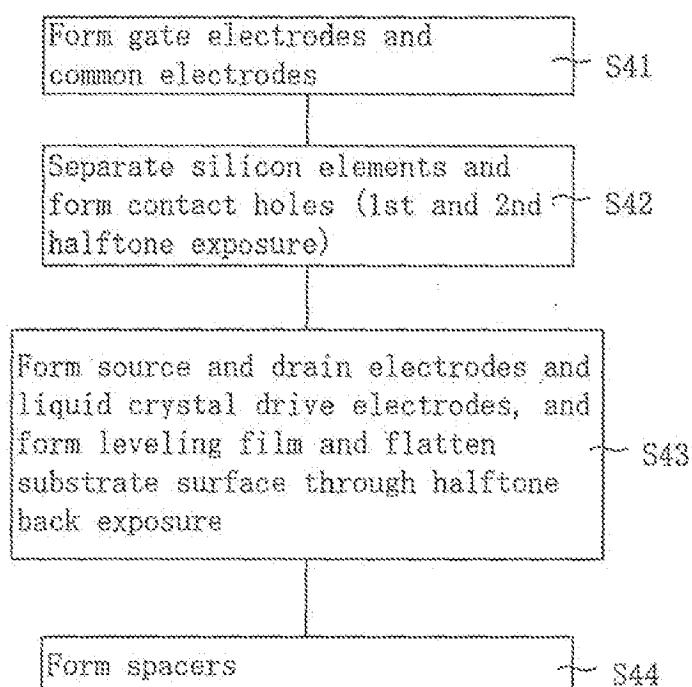

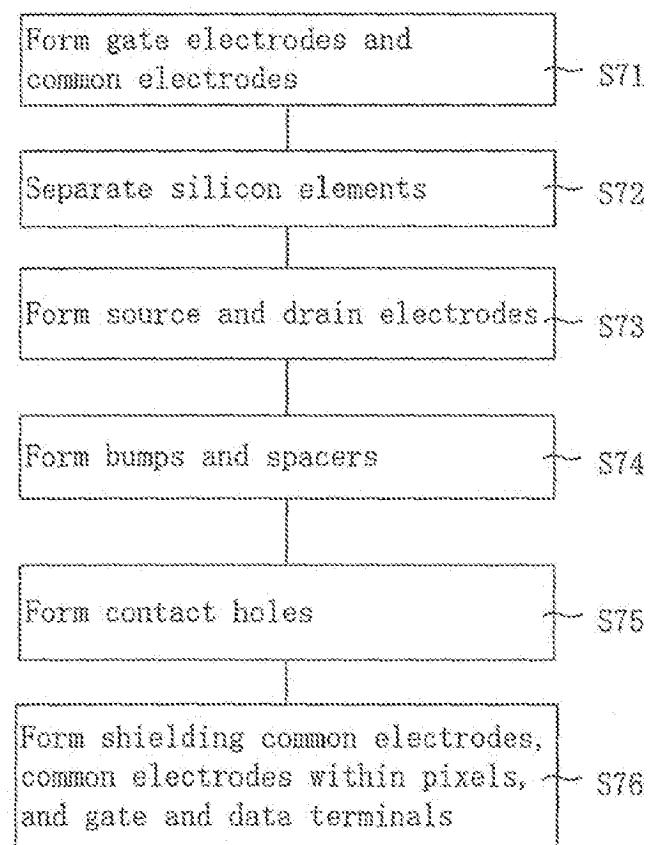

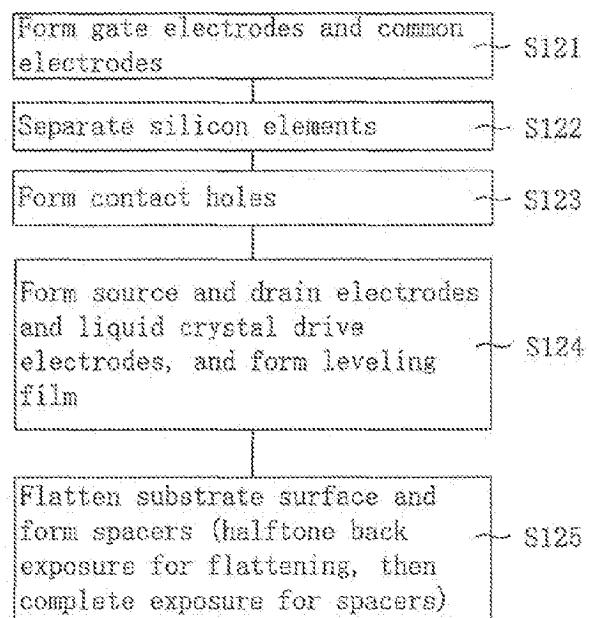

**[0067]** In the forty ninth aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- 30 (1) forming the scanning lines (gate electrodes of the thin film transistors), common electrodes within the pixels, and lower layer common electrodes for shielding the video signal lines at the same time;

- 35 (2) separating the silicon elements for the thin film transistors from the semiconductor layer (silicon island);

- 40 (3) forming the video signal lines and the liquid crystal drive electrodes at the same time;

- 45 (4) forming the contact holes for terminal portions and for the static electricity protection circuits;

- 50 (5) forming the scanning line terminal portions, the video signal line terminal portions, and the static electricity protection circuits at the same time; and

- 55 (6) forming the photolithography spacers and leveling the effective pixel area (halftone back surface exposure process).

**[0068]** In the fiftieth aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the scanning lines (gate electrodes of the thin film transistors), the common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) forming the patterns of etching stopper channels for the thin film transistors;

- (3) forming the video signal lines and the liquid crystal drive electrodes at the same time;

- (4) forming the contact holes for the terminal portions and for the static electricity protection circuits;

- (5) forming the scanning line terminal portions, the video signal line terminal portions, and the static electricity protection circuits at the same time; and

- (6) forming the photolithography spacers and leveling the effective pixel area (halftone back surface exposure process).

**[0069]** In the fifty first aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the scanning lines (gate electrodes of the thin film transistors), the common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) separating the silicon elements for the thin film transistors from the semiconductor layer (silicon island);

- (3) forming the contact holes for the terminal portions and for the static electricity protection circuits;

- (4) forming the video signal lines, the liquid crystal drive electrodes, the scanning line terminal portions, the video signal line terminal portions, and the static electricity protection circuits at the same time; and

- (5) forming the photolithography spacers and leveling the effective pixel area (halftone back surface exposure process).

**[0070]** In the fifty second aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the scanning lines (gate electrodes of the thin film transistors), the common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time; and

- (2) separating the silicon elements for the thin film transistors from the semiconductor layer (silicon island) and forming the contact holes for the terminal portions and for the static electricity protection cir-

cuits (first and second halftone exposure processes).

**[0071]** In the fifty third aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the scanning lines (gate electrodes of the thin film transistors), the common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) forming the video signal lines and the liquid crystal drive electrodes and separating the silicon elements for the thin film transistors from the semiconductor layer at the same time (halftone exposure process);

- (3) forming the contact holes for the terminal portions and for the static electricity protection circuits;

- (4) forming the scanning line terminal portions, the video signal line terminal portions, and the static electricity protection circuits at the same time; and

- (5) forming the photolithography spacers and leveling the effective pixel area (halftone back surface exposure process).

**[0072]** In the fifty fourth aspect of the present invention, a process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

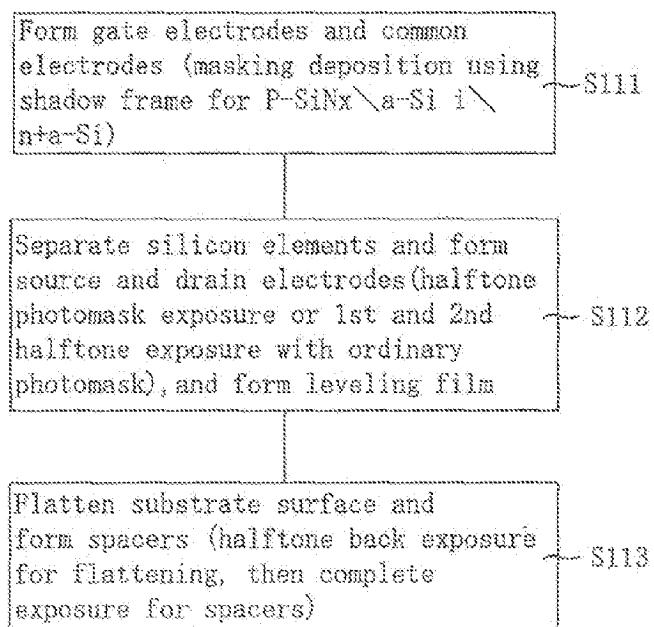

- (1) forming the scanning lines (gate electrodes of the thin film transistors), the common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time (using a masking deposition process incorporating a shadow frame for a structure of P-SiNx\i-Si i layer\n+a-Si layers);

- (2) forming the video signal lines, the liquid crystal drive electrodes, the static electricity protection circuits, and the scanning line terminal portions, and separating the silicon elements for the thin film transistors from a semiconductor layer at the same time (halftone exposure process); and

- (3) forming the photolithography spacers and leveling the effective pixel area (halftone back surface exposure process).

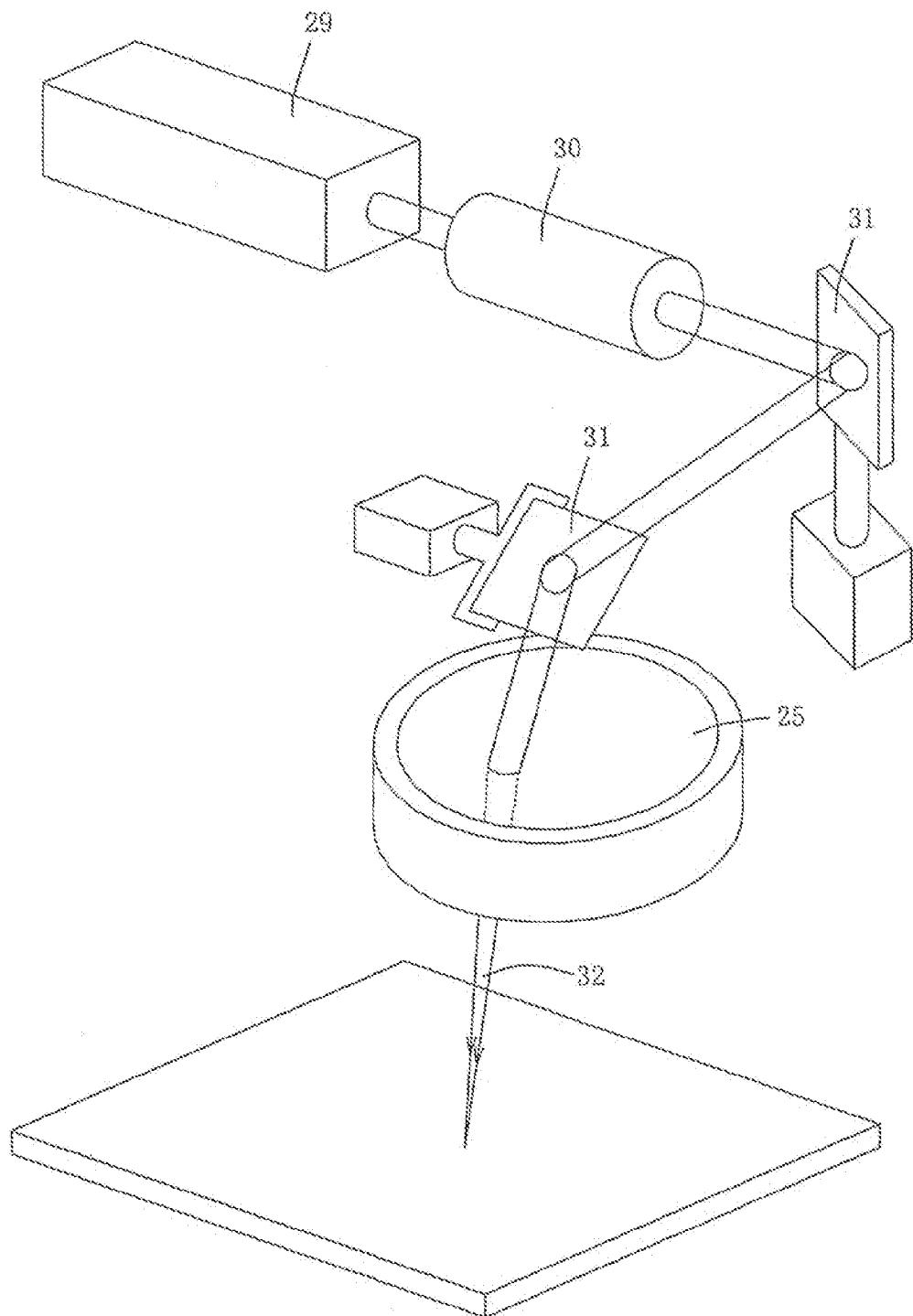

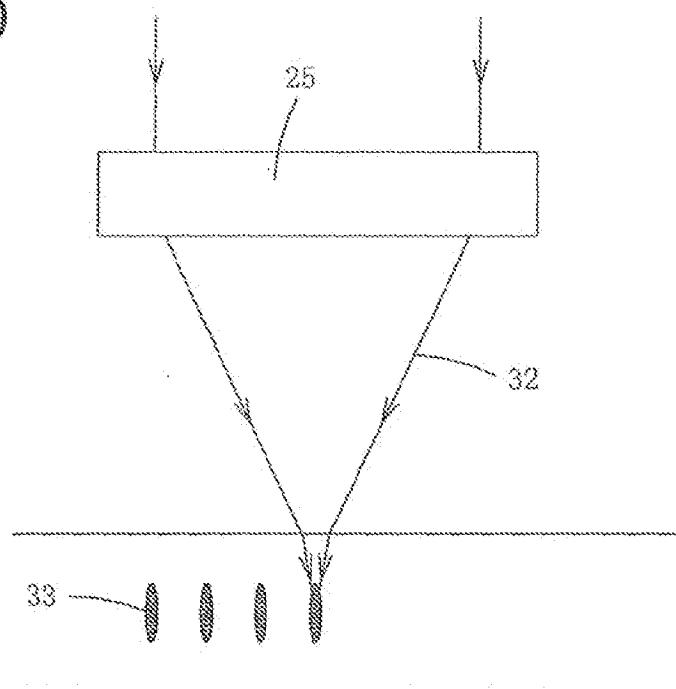

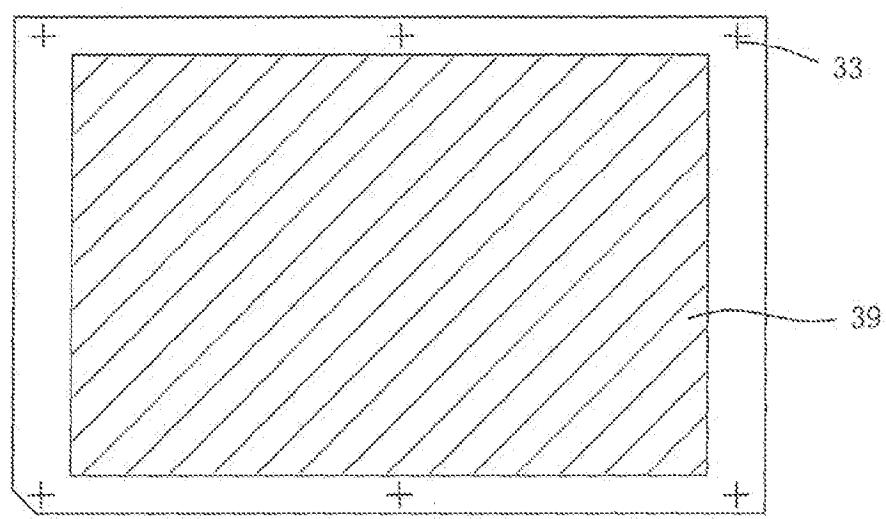

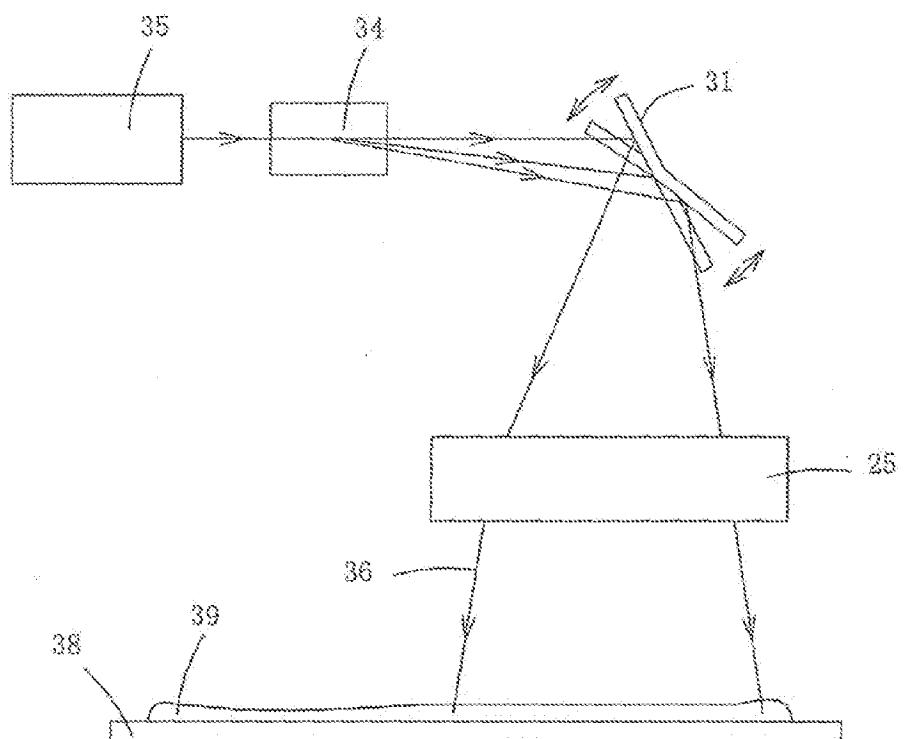

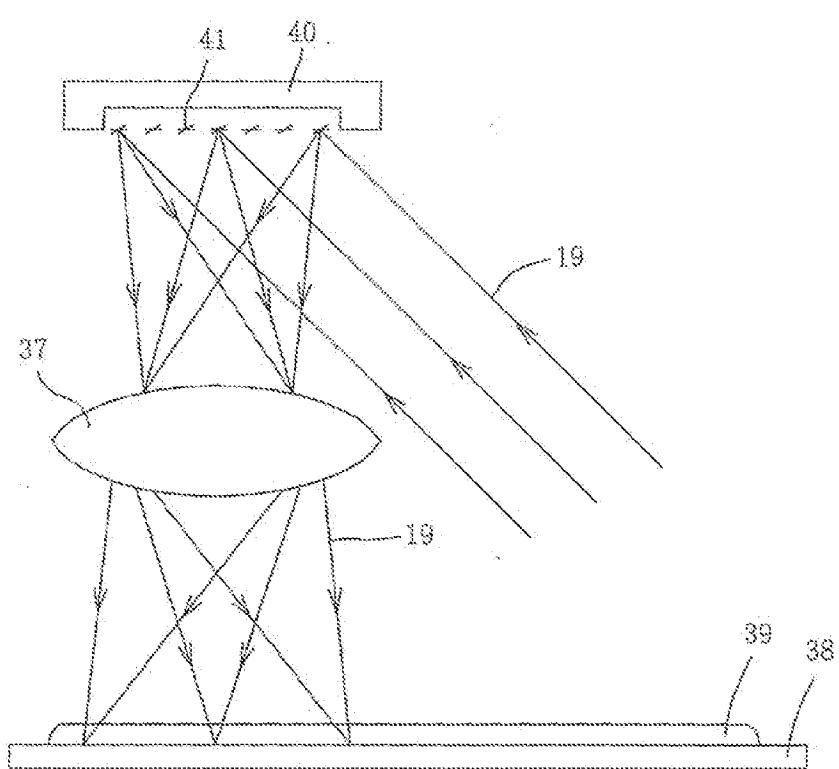

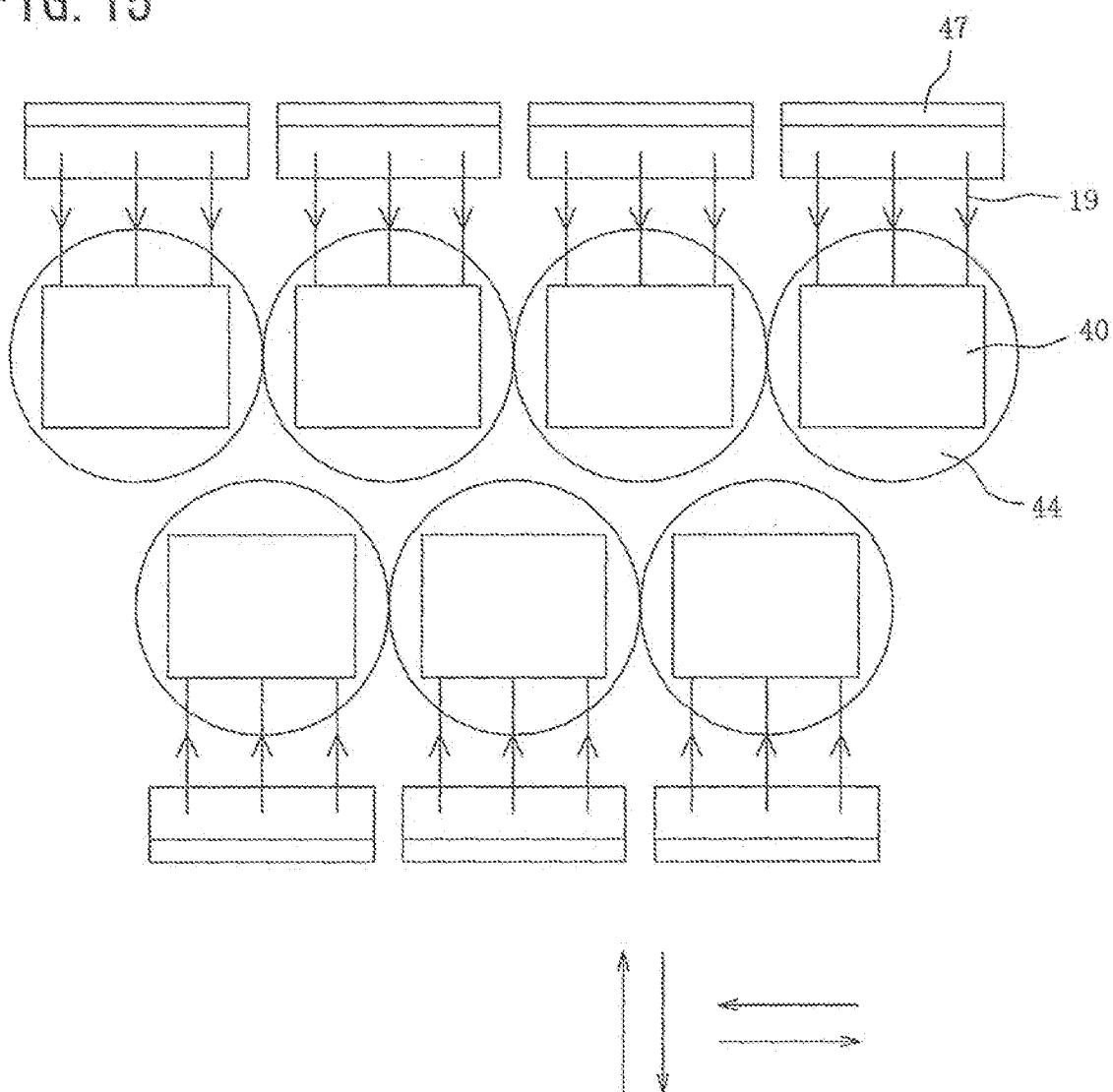

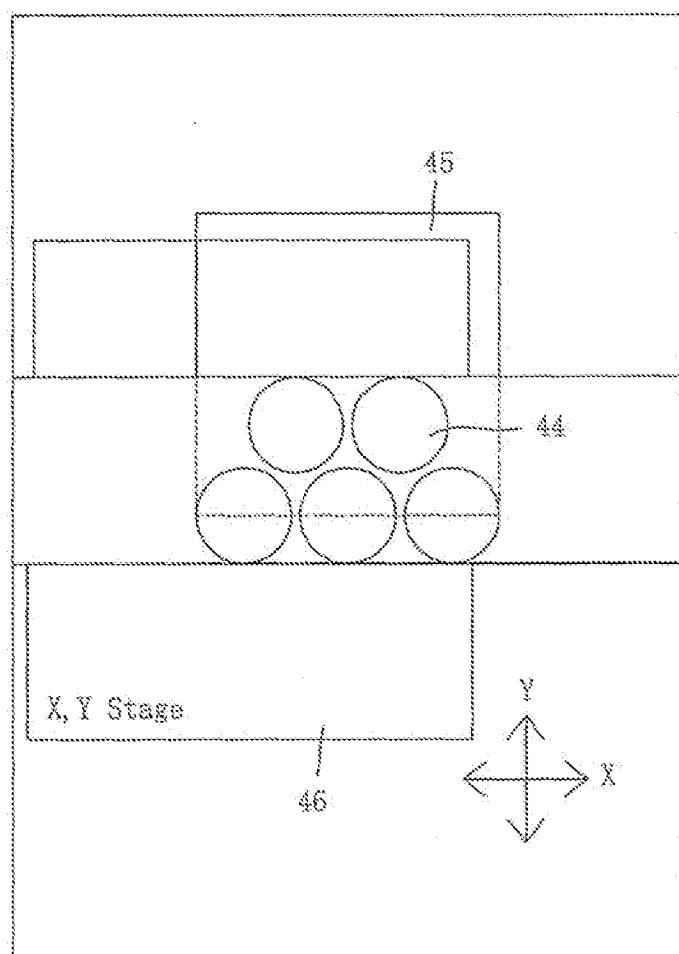

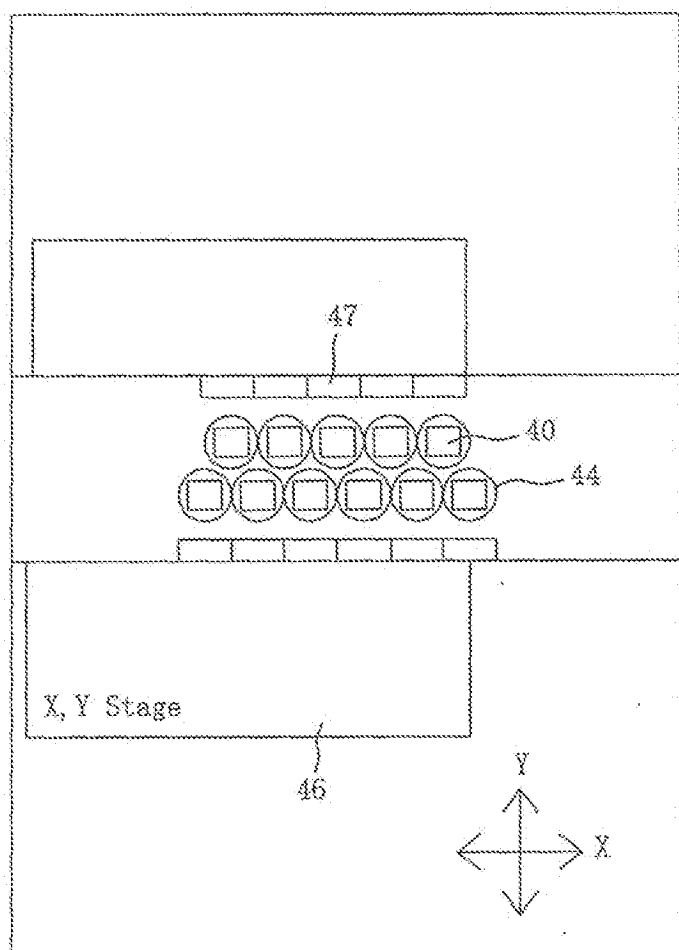

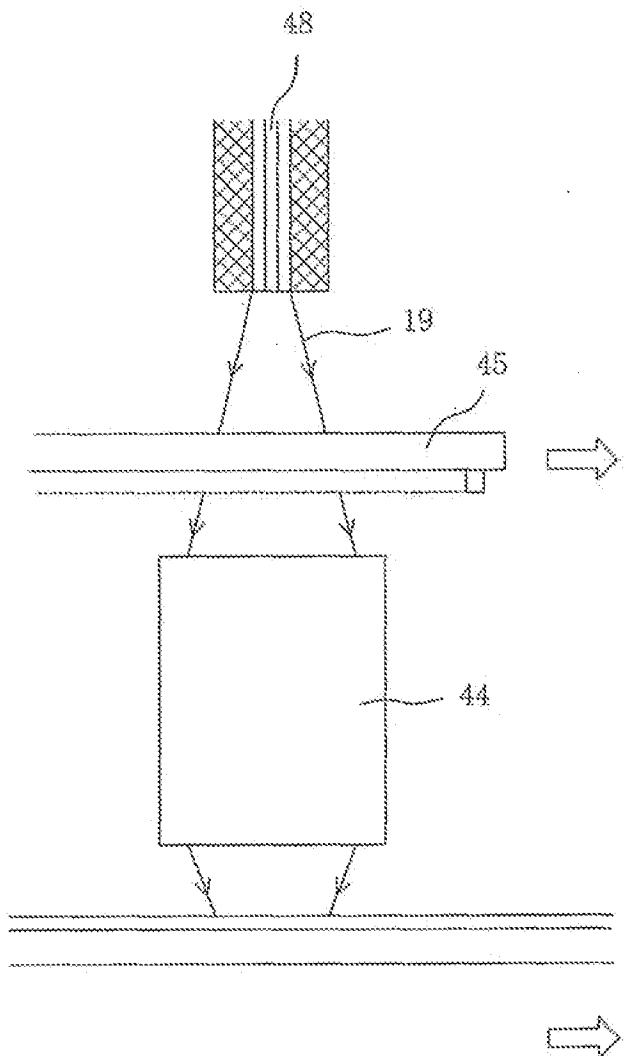

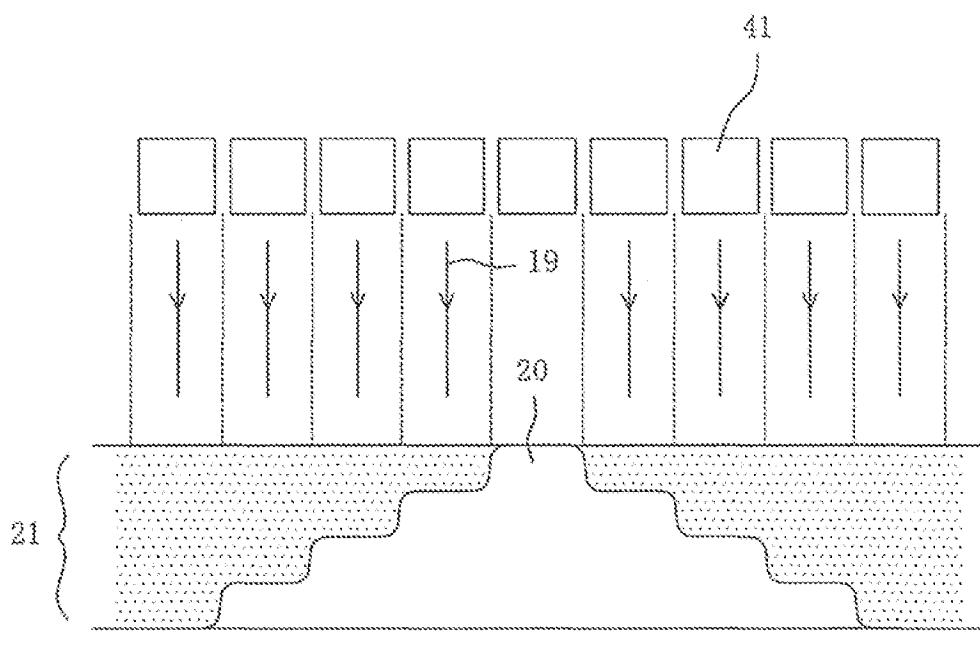

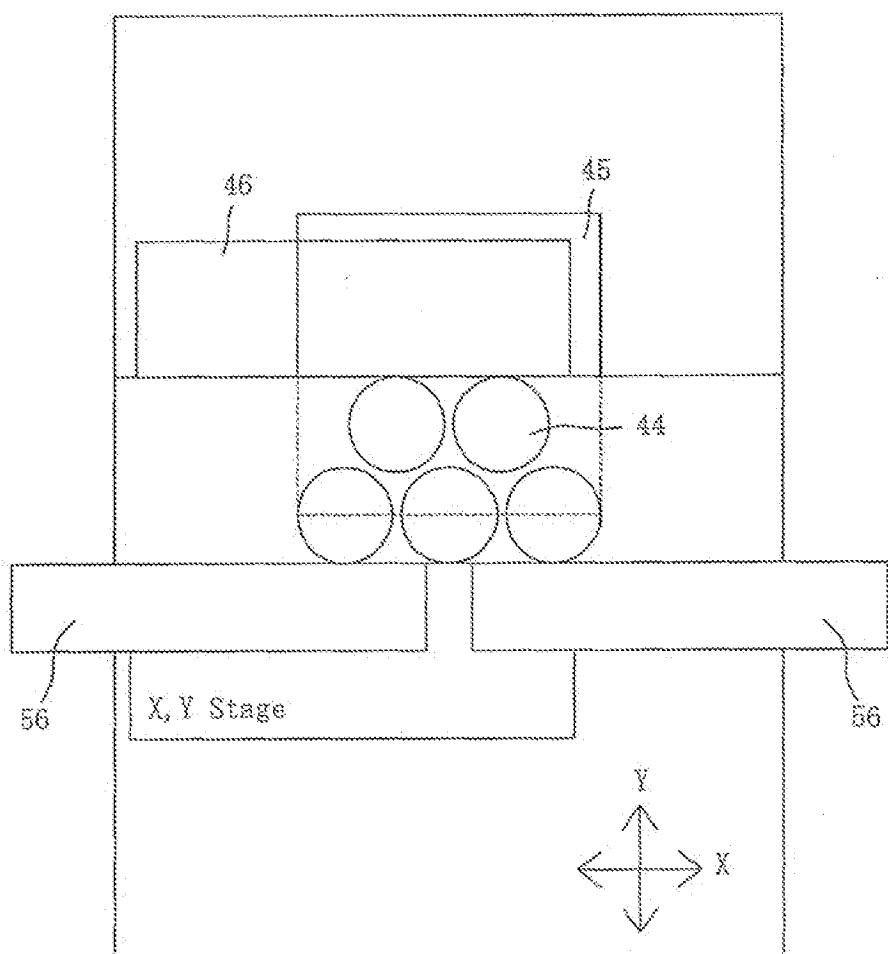

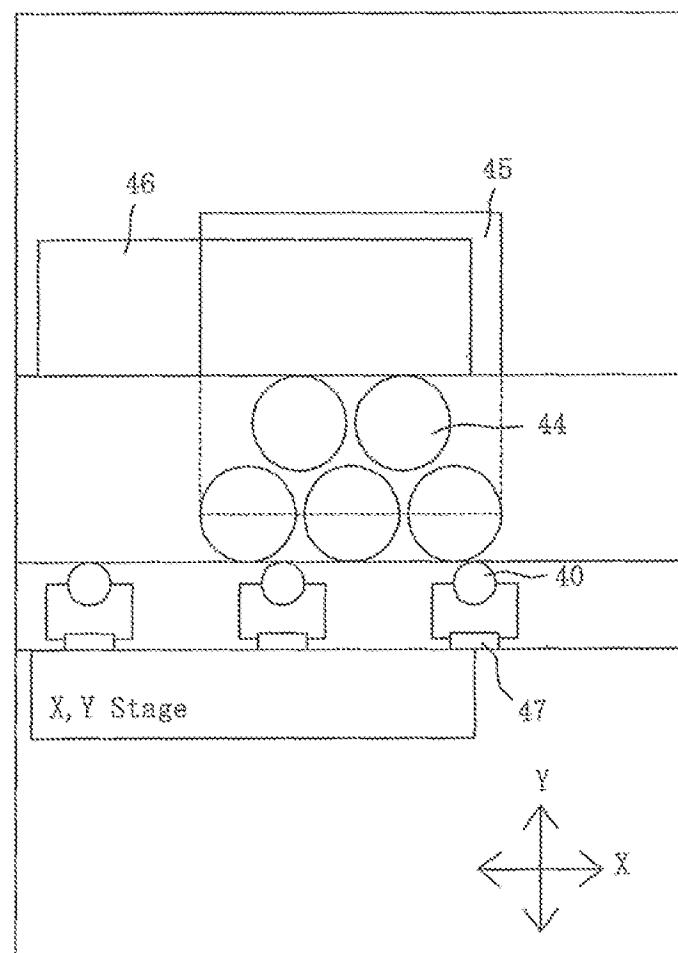

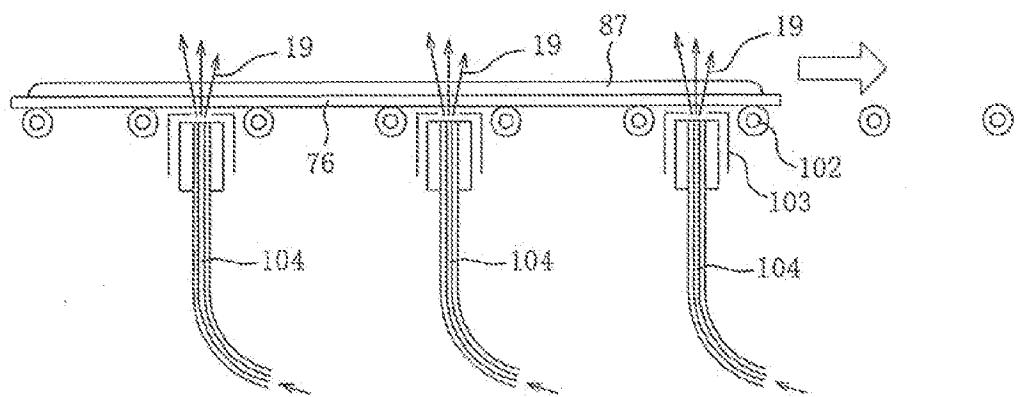

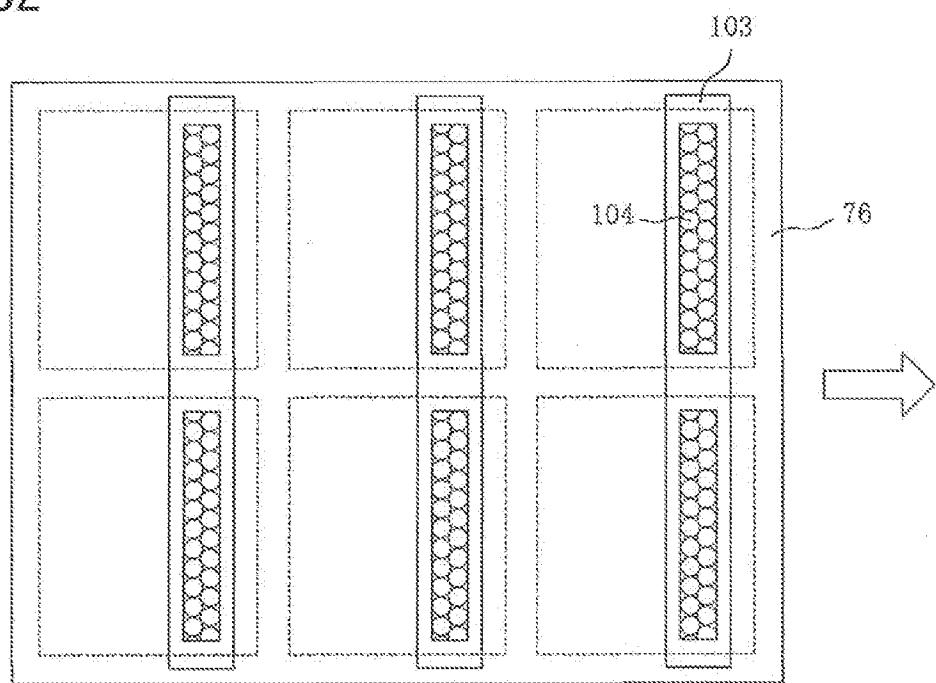

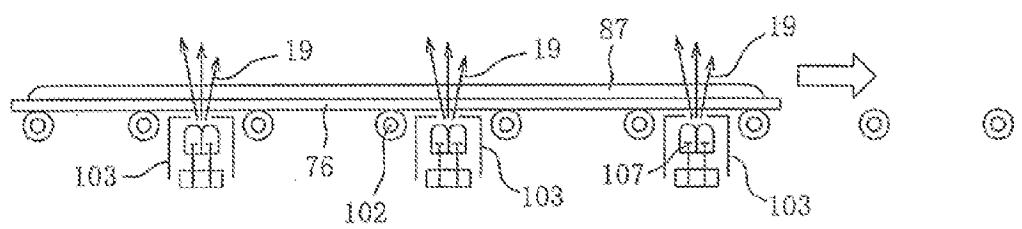

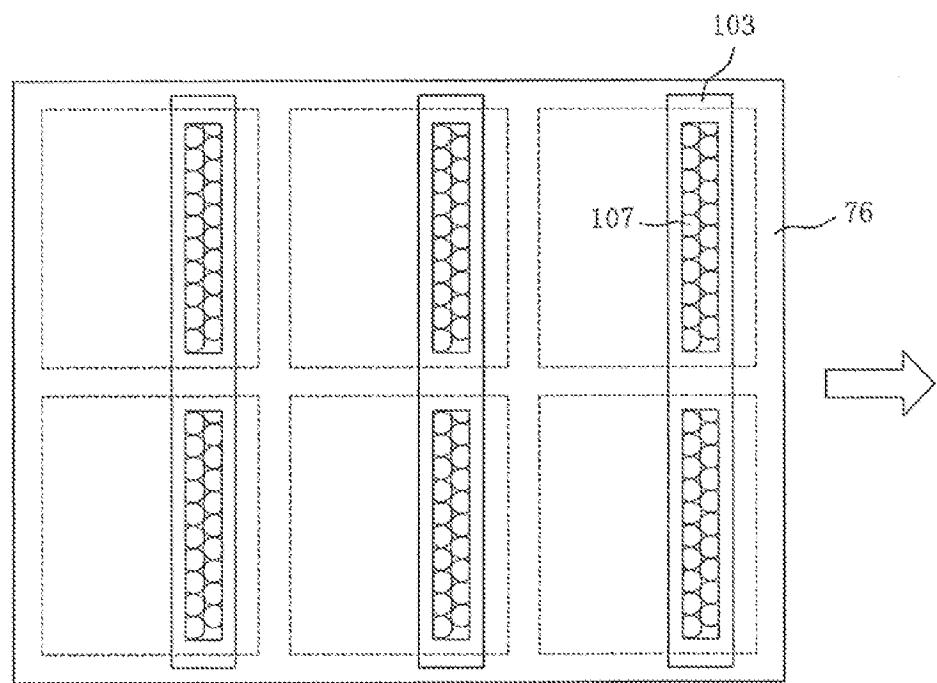

**[0073]** In the fifty fifth aspect of the present invention, with respect the halftone back surface exposure apparatus that is used in the leveling (planarization) process for the effective pixel area of the active matrix substrate of the transverse electric field type liquid crystal display device, silica optical fiber cables for ultraviolet light or ultraviolet light LED are bundled in an in-line form in such a way that the ultraviolet rays can expose only the effective pixel area of the active matrix substrate of the transverse electric field type liquid crystal display device from the back side of the substrate.

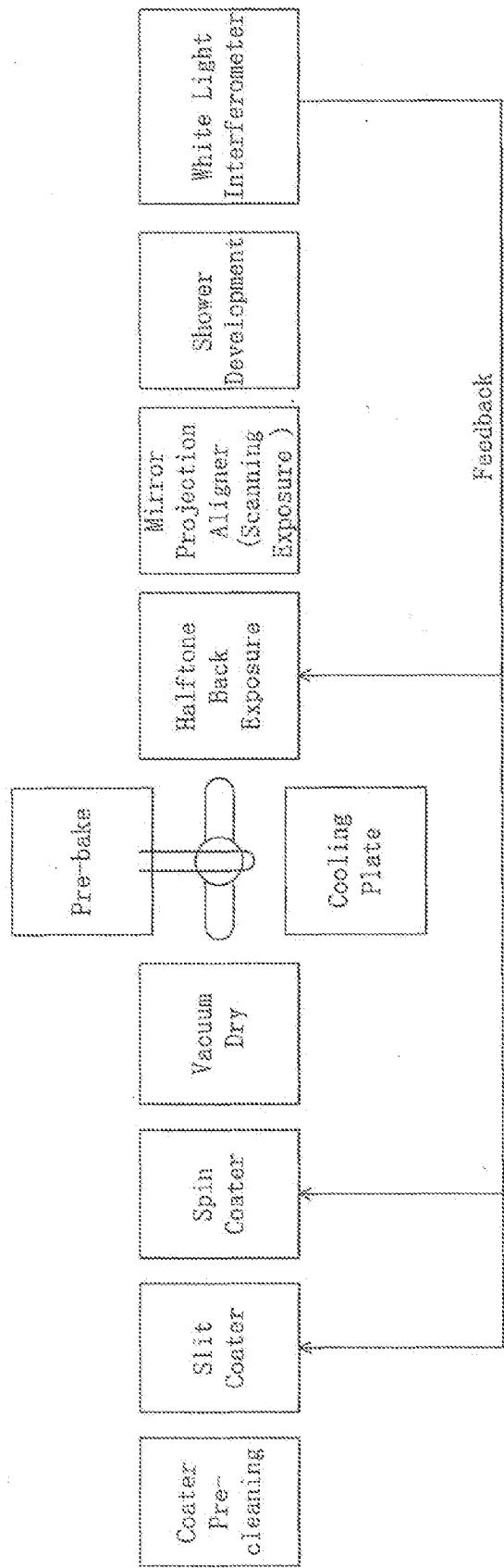

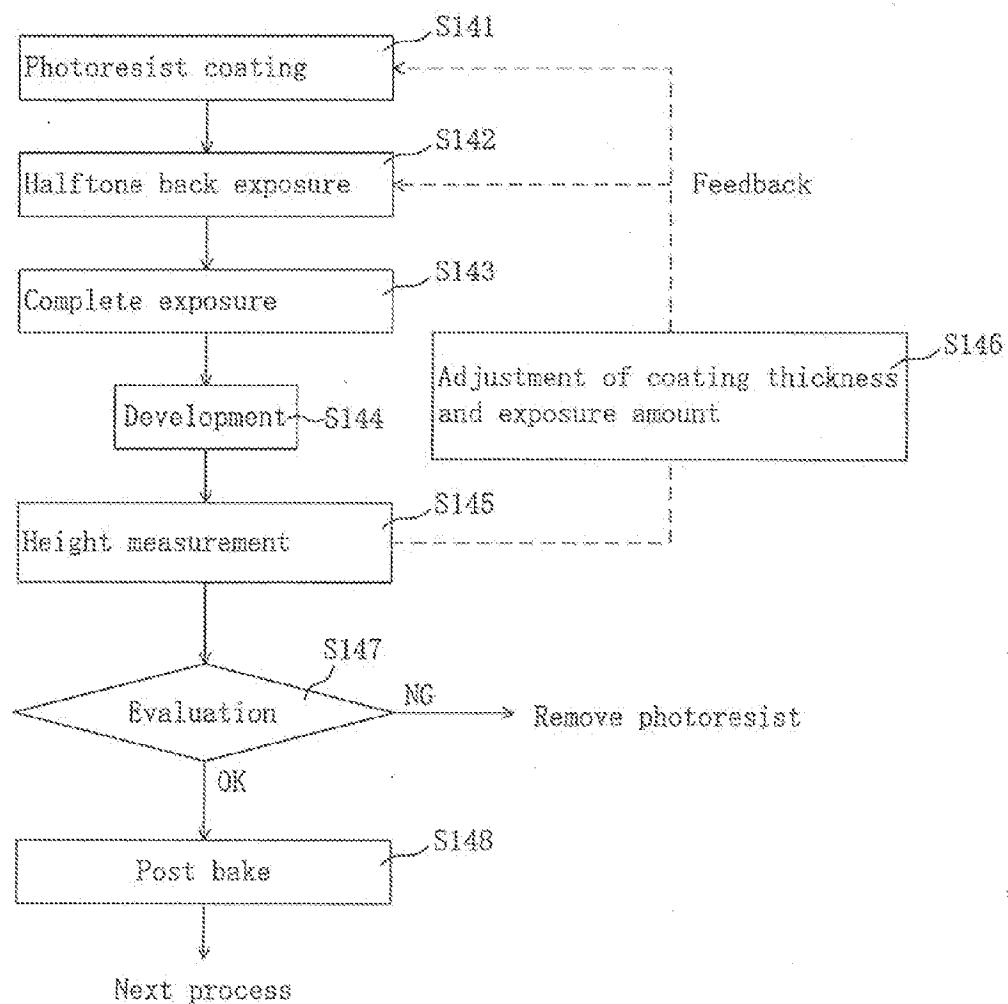

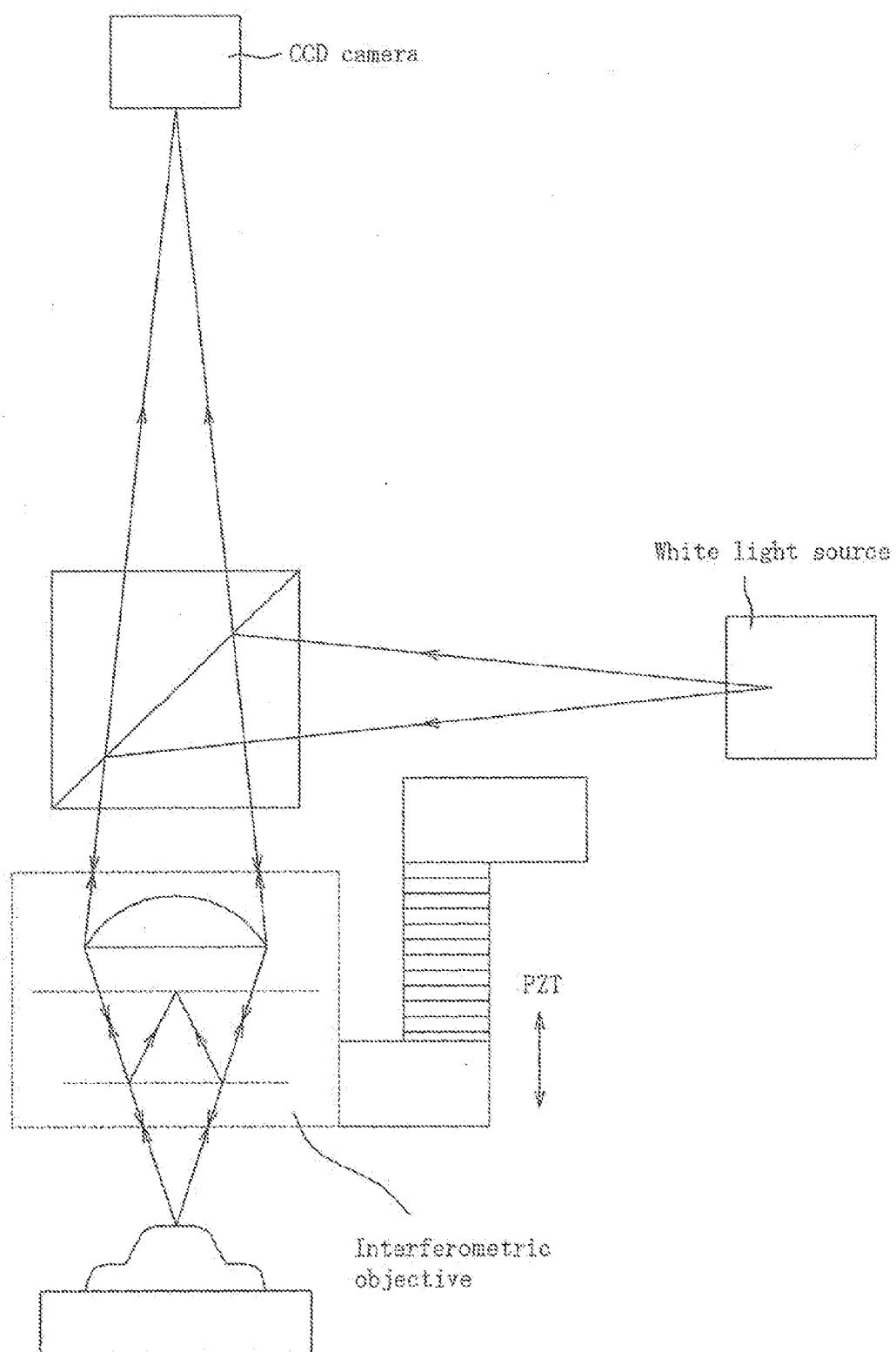

**[0074]** In the fifty sixth aspect of the present invention, with respect to the halftone back surface exposure process, in the forty eight, forty ninth, fiftieth, fifty first, fifty second, fifty third and fifty fourth aspects of the present invention noted above, the entire effective pixel area is exposed by the ultraviolet light from the back surface of the active matrix substrate before completely exposing the ultraviolet light on the portions where the spacers are to be constructed by using a photomask for photolithography spacer construction. Then, after the development of the substrate, degrees of irregularity of the substrate surface within the effective pixel area at side of the active matrix substrate and the heights of the spacers are measured with use of a white Light interferometer so that the coating thickness of the photoresist and the amount of light for the halftone back surface exposure are controlled in response to the measured data from the white light interferometer through a feedback control process.

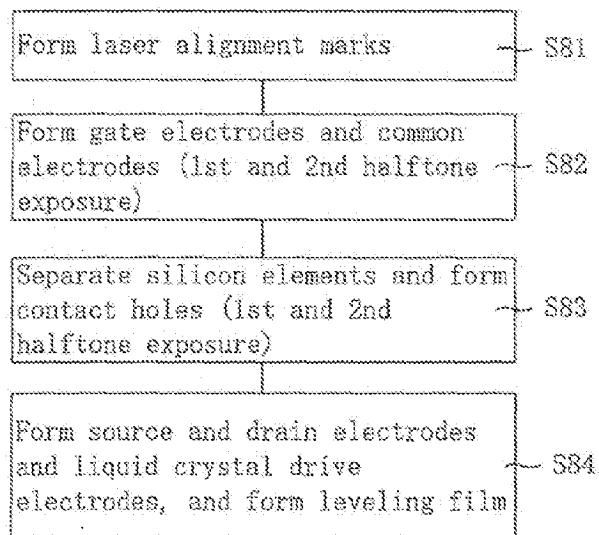

**[0075]** In the fifty seventh aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted in the following steps:

- (1) forming the alignment marks inside of a glass substrate with use of a laser beam;

- (2) depositing two or more layers of different kinds of metals or metal compounds or alloys (portions where the alignment marks are created by the laser beam are not deposited);

- (3) exposing the gate bus lines and the common bus lines after the application of positive photoresist through the first halftone exposure process of an under exposure method that utilizes an ordinary photomask, then, the gate bus line, the common bus line, the common electrodes for shielding the video signal lines, and the common electrodes within the pixels are exposed through the second exposure process;

- (4) after the development, the deposited metals are etched away with use of a first wet etching or dry etching process, then, removing the positive photoresist at the areas of the halftone exposure by an oxygen plasmas ashing method, and then removing the metal layers art the halftone exposed area that are unnecessary through a second dry etching or wet etching process, and forcing the gate bus, common bus, common electrodes for shielding the video signal lines, and the common electrodes within the pixels by using the first and second etching processes;

- (5) depositing the gate insulation film, a non-doped thin film semiconductor layer (a-Si layer), and a n+a-Si layer (ohmic contact layer) and coating the positive photoresist thereon, then exposing the a-Si silicon islands through a first halftone exposure process of an under exposure method with use of a normal photomask, and then exposing the contact holes for gate terminal connection portions and for the stat-

ic electricity protection circuits through a second exposure process;

(6) after the development, forming the contact holes for the gate terminal connection portions and the static electricity protection circuits by etching away the gate insulation film, non-doped thin film semiconductor layer (a-Si layer), and the n+a-Si layer (ohmic contact layer) through a first dry etching process, then, after removing the positive photoresist at the area of the halftone exposure with use of an oxygen plasma ashing method, removing the non-doped thin film semiconductor layer (a-Si layer) and the n+a-Si layer (ohmic contact layer) that are unnecessary at the halftone exposed area with use of a second dry etching process, and then, constructing the a-Si silicon islands, the gate terminal connection portions, and the static electricity protection circuit with use of the first and second etching processes; and

(7) constructing the video signal lines, the liquid crystal drive electrodes, the static electricity protection circuits, and the gate terminals at the same time (through the halftone exposure process using the normal photomask).

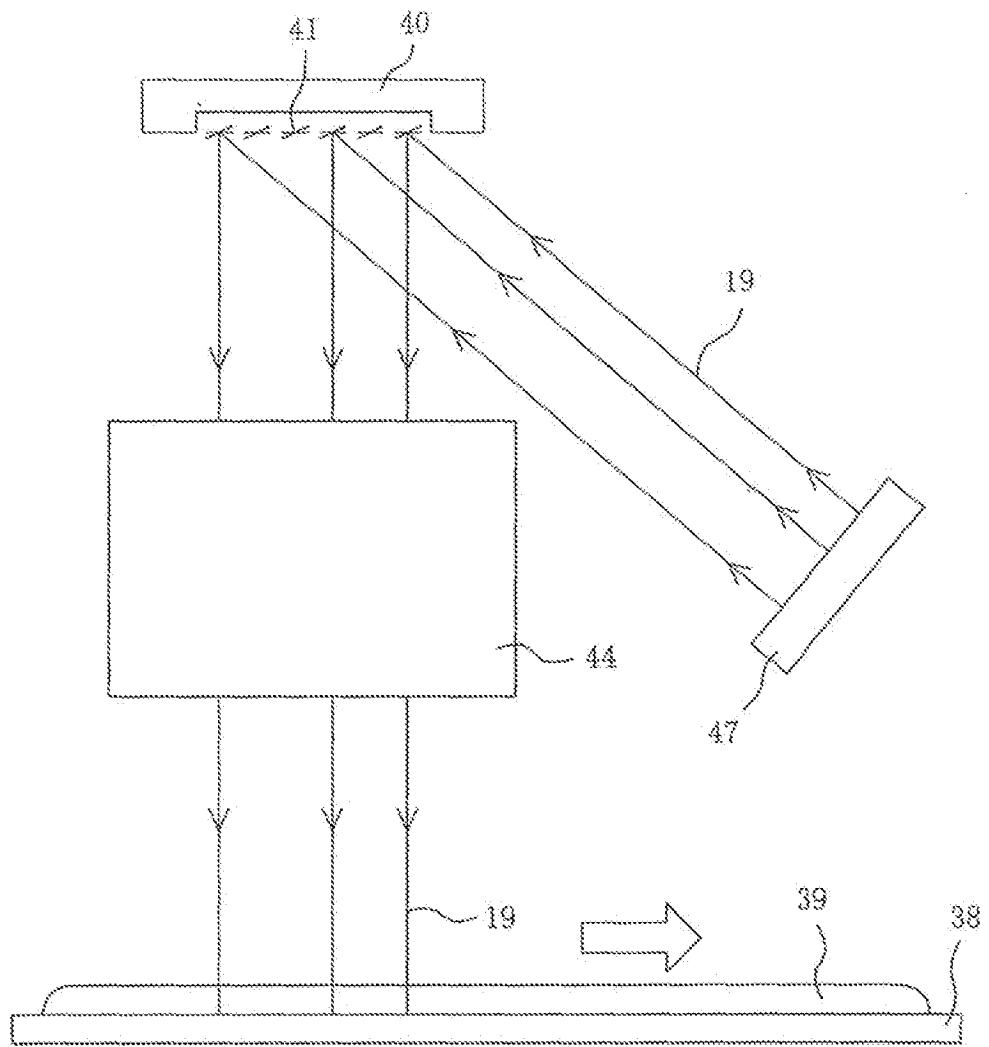

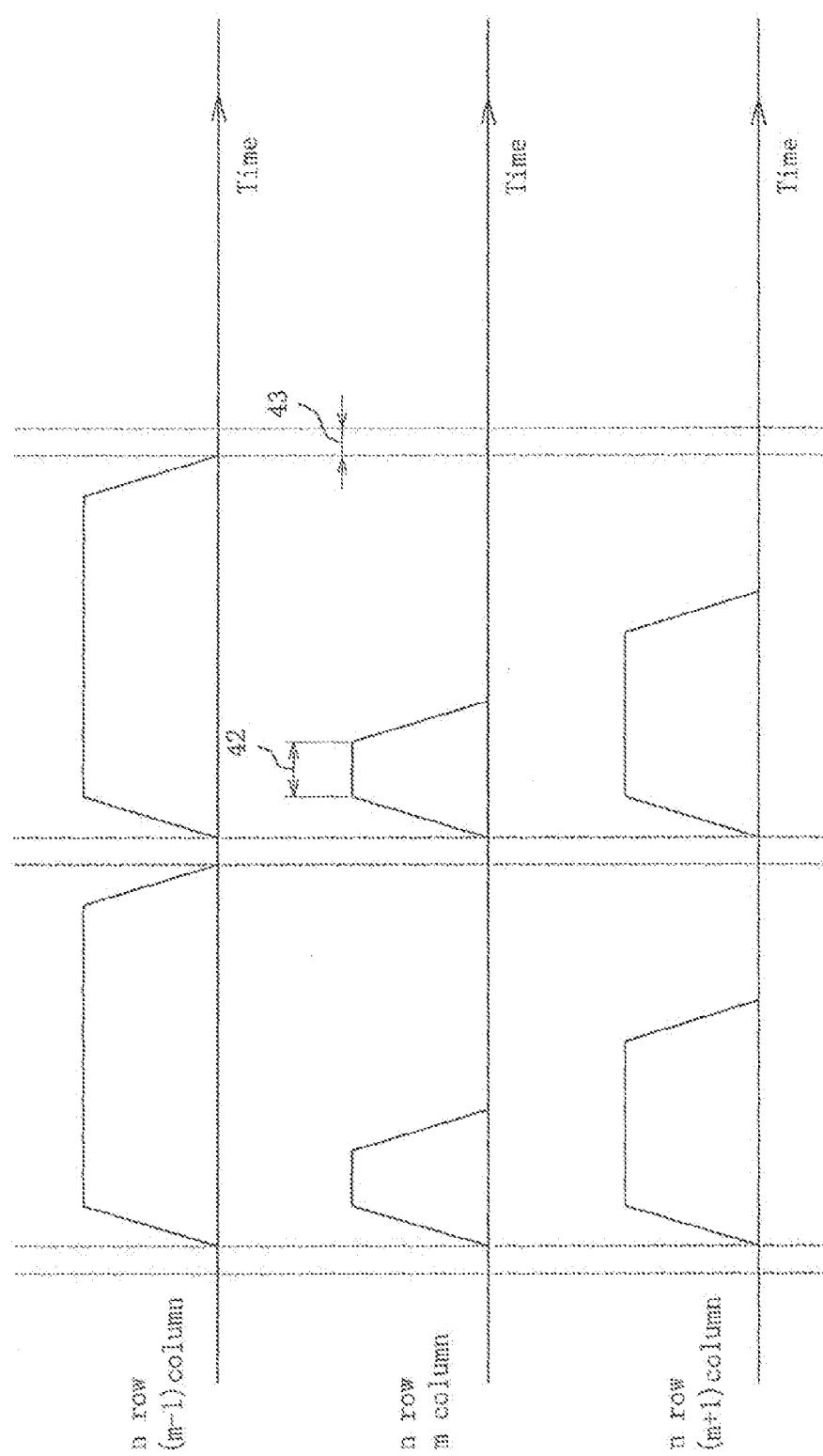

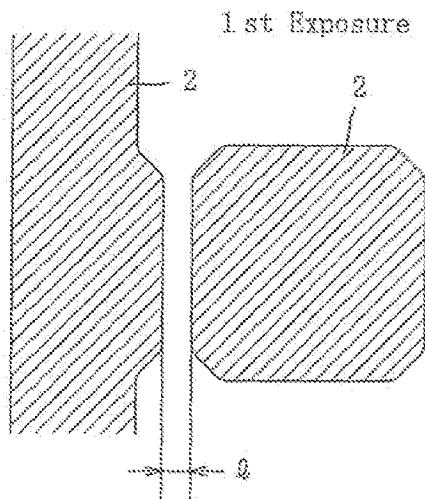

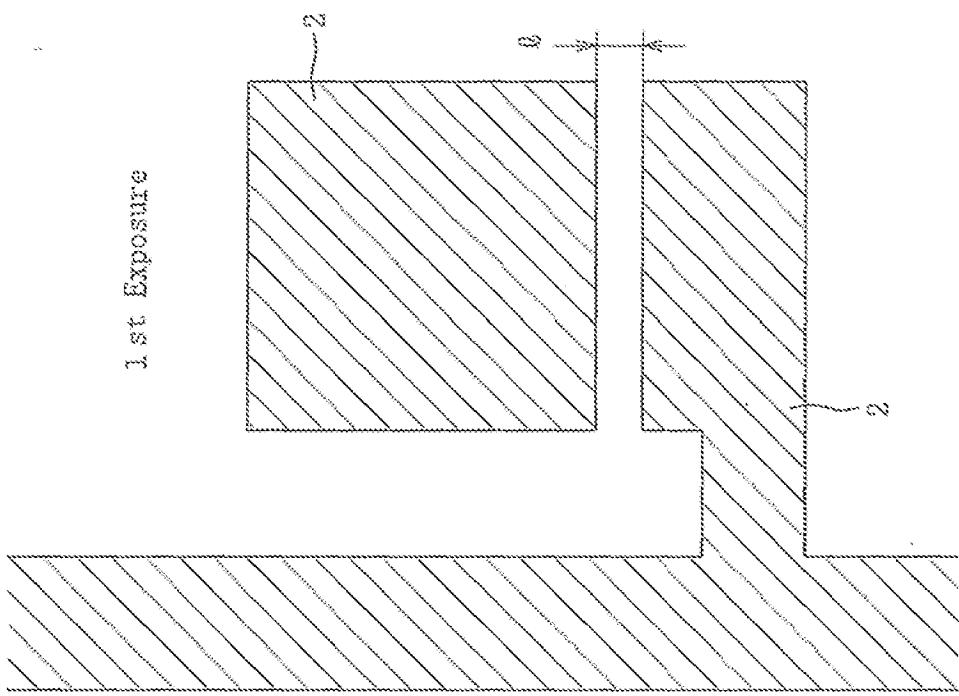

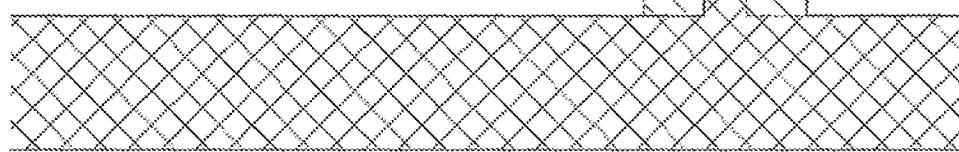

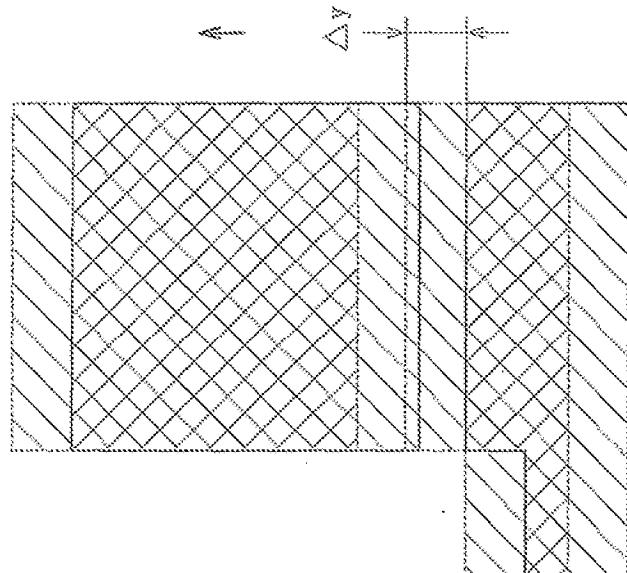

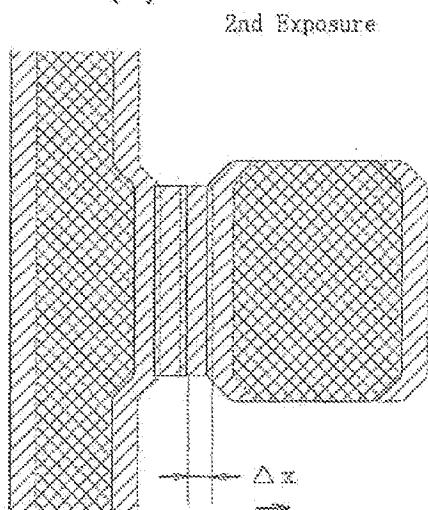

**[0076]** In the fifty eighth aspect of the present invention, an exposure device used in the production process for producing the thin film transistors of the active matrix display device of the present invention has a function of performing a second halftone exposure (complete exposure) process after shifting the active matrix substrate in a horizontal direction for the length of about a half of the channel length of the thin film transistor after performing a first halftone exposure (incomplete exposure) process using a normal photomask to construct the source electrodes and the drain electrodes of a channel length of about a half of the channel length of the thin film transistor.

**[0077]** In the fifty ninth aspect of the present invention, the process of producing the thin film transistors of the active matrix liquid crystal display device is conducted by, first performing the first halftone exposure (incomplete exposure; under exposure) with use of a normal photomask to construct the source electrodes and the drain electrodes of the thin film transistors with the channel length of, about a half of the channel length of the thin film transistor, then, shifting the active matrix substrate in a horizontal direction for the length of about a half of the target channel length of the thin film transistor, and then developing the positive photoresist after performing the second halftone exposure (incomplete exposure; under exposure), thereby reducing the thickness of the positive photoresist of the channel portion of the thin film transistor by an amount corresponding to the target channel length.

**[0078]** In the sixtieth aspect of the present invention, the halftone shift exposure technology in the fifty ninth aspect of the present invention noted above is used for performing the silicon element separation for the thin film transistors, and the formation of the video signal lines

(source electrodes and the drain electrodes (electrodes connected to the liquid crystal drive electrodes or the transparent pixel electrodes) at the same time.

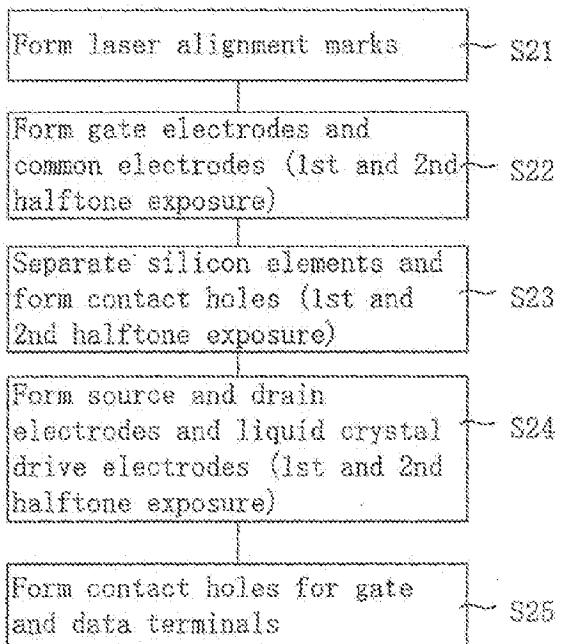

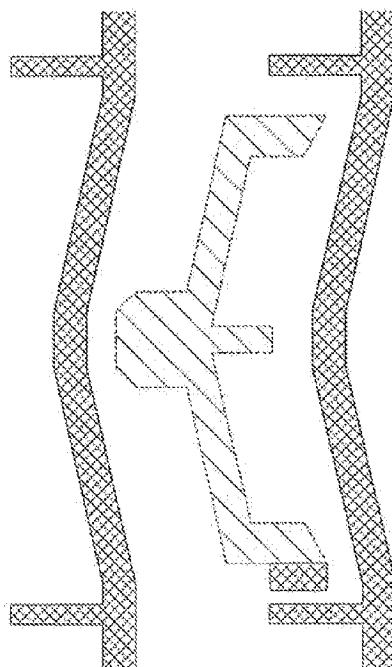

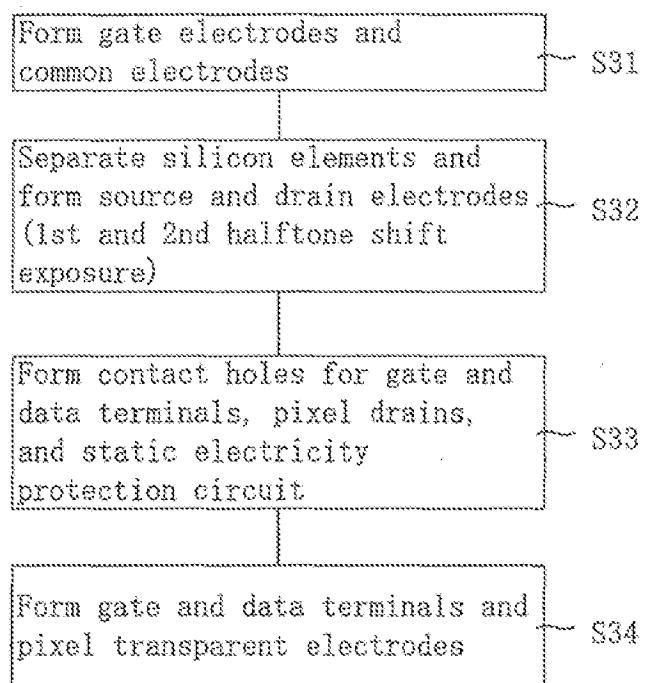

**[0079]** In the sixty first aspect of the present invention, the process of producing the active matrix substrate is conducted with use of the halftone shift exposure technology in the fifty ninth aspect of the present invention noted above by the following steps:

- (1) forming the scanning lines (gate electrodes of the thin film transistors) and the common electrodes at the same time;

- (2) forming the video signal lines (source electrodes of the thin film transistors) and the drain electrodes, and separating the silicon element for the thin film transistors from a semiconductor layer at the same time (halftone exposure process);

- (3) forming the contact holes for the scanning line terminal portions, the video signal line terminal portions, and for the static electricity protection circuits; and

- (4) forming the scanning line terminal portions, the video signal line terminal portions, the static electricity protection circuits, and transparent electrodes at the same time.

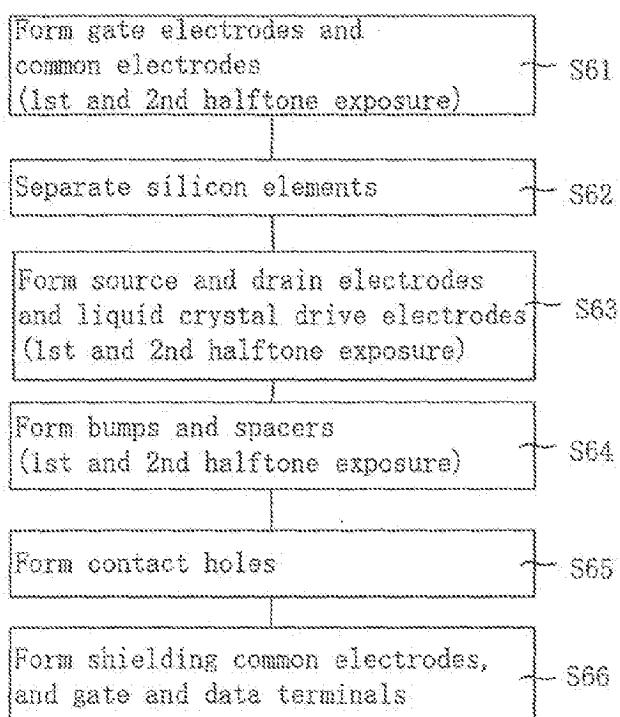

**[0080]** In the sixty second aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted with use of the halftone shift exposure technology in the fifty ninth aspect of the present invention noted above by the following steps:

- (1) forming the scanning lines (gate electrodes), the common electrodes within the pixels, and the lower layer common electrodes for shielding the video signal lines at the same time (using a masking deposition process incorporating a shadow frame in the case of using the structure of P-SiNx\|a-Si i layer\|n+a-Si layer);

- (2) forming the video signal lines, the liquid crystal drive electrodes, the static electricity protection circuits, and the scanning line terminal portions, and separating the silicon elements for the thin film transistors from the semiconductor layer at the same time (halftone exposure process); and

- (3) forming the photolithography spacers and leveling the effective pixel area (halftone back surface exposure process).

**[0081]** In the sixty third aspect of the present invention, the spacer bumps, in the third, fourth, fifth, fifteenth, sixteenth, and seventeenth aspects of the present invention noted above, have a characteristic of elastically and evenly deforming along the entire effective pixel area in a range between 0.1 micrometers and 0.5 micrometers in response to the atmospheric pressure during the construction of the liquid crystal cell by superposing the ac-

tive matrix substrate and the color filter substrate with one another under a vacuum atmosphere.

**[0082]** In the sixty fourth aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted by the following steps:

- (1) forming the scanning lines;

- (2) separating the silicon elements for the thin film transistors from the semiconductor layer (silicon island step);

- (3) forming the video signal lines (source electrodes) and the drain electrodes at the same time;

- (4) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the bumps that cover the video signal lines (halftone exposure process);

- (5) forming the contact holes for the terminal portions, the drain electrodes, and the static electricity protection circuits; and

- (6) forming the transparent common electrodes for shielding the video signal line, the transparent common electrodes within the pixels, and the liquid crystal drive electrodes at the same time.

**[0083]** In the sixty fifth aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted by the following steps:

- (1) forming the scanning lines and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) separating the silicon elements the thin film transistors from the semiconductor layer (silicon island step);

- (3) forming the video signal lines (source electrodes) and the drain electrodes at the same time;

- (4) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the bumps that cover the video signal lines (halftone exposure process);

- (5) forming the contact holes for the terminal portions, the drain electrodes, and the static electricity protection circuits; and

- (6) forming the transparent common electrodes for shielding the video signal lines, the transparent common electrodes within the pixels, and the liquid crystal drive electrodes at the same time.

**[0084]** In the sixty sixth aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted by the following steps:

- (1) forming the scanning lines;

- (2) forming the patterns of etching stopper channels for the thin film transistors;

- (3) forming the video signal lines (source electrodes) and the drain electrodes at the same time;

- (4) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the bumps that cover the video signal lines (halftone exposure process);

- (5) forming the contact holes for terminal portions, drain electrodes, and static electricity protection circuits; and

- (6) forming the transparent common electrodes for shielding the video signal lines, the transparent common electrodes within the pixels, and the liquid crystal drive electrodes at the same time.

**[0085]** In the sixty seventh aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted by the following steps:

- (1) forming the scanning lines and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) forming the patterns of etching stopper channels for the thin film transistors;

- (3) forming the video signal lines (source electrodes) and the drain electrodes at the same time;

- (4) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the bumps that cover the video signal lines (halftone exposure process);

- (5) forming the contact holes for the terminal portions, the drain electrodes, and the static electricity protection circuits; and

- (6) forming the transparent common electrodes for shielding the video signal lines, the transparent common electrodes within the pixels, and the liquid crystal drive electrodes at the same time.

**[0086]** In the sixty eighth aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted by the following steps;

- (1) forming the scanning lines;

- (2) forming the video signal lines source electrodes) and the drain electrodes, and separating the silicon elements for the thin film transistors from the semiconductor layer at the same time (halftone exposure process);

- (3) forming the spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the bumps that cover the video signal lines (halftone exposure process);

- (4) forming the contact holes for the terminal portions, the drain electrodes, and the static electricity protection circuits; and

- (5) forming the transparent common electrodes for shielding the video signal lines, the transparent com-

mon electrodes within the pixels, and the liquid crystal drive electrodes at the same time.

**[0087]** In the sixty ninth aspect of the present invention, the process of producing an active matrix substrate of a transverse electric field type active matrix liquid crystal display device is conducted by the following steps:

- (1) forming the scanning lines and the lower layer common electrodes for shielding the video signal lines at the same time;

- (2) forming the video signal lines (source electrodes) and the drain electrodes, and separating silicon elements for the thin film transistors from the semiconductor layer at the same time (halftone exposure process);

- (3) forming this spacer bumps that cover the video signal lines, or simultaneously forming the spacers and the bumps that cover the video signal lines (halftone exposure process);

- (4) forming the contact holes for the terminal portions, the drain electrodes, and the static electricity protection circuits; and

- (5) forming the transparent common, electrodes for shielding the video signal lines, the transparent common electrodes within the pixels, and the liquid crystal drive electrodes at the same time.

**[0088]** In the seventieth aspect of the present invention, the video signal like, the thin and long insulation bumps formed in the manner to cover the video signal lines, the upper layer common electrodes for shielding, the electric fields caused by the video signal lines, the lower layer common electrodes for shielding, and the liquid crystal drive electrodes within the pixels in the forty seventh aspect of the present invention noted above are bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to an alignment direction of the liquid crystal molecule, and similarly, the color filter layer and the light shielding film (black mask) on the side of the color filter substrate which, is opposite to the active matrix substrate are bent within the pixel at least once at an angle within a range between 0-30 degrees (except 0 degree) relative to the alignment direction of the liquid crystal molecule.

**[0089]** In the seventy first aspect of the present invention, the video signal line, the thin and long insulation bumps formed in the manner to cover the video signal lines, the upper layer common electrodes for shielding the electric fields caused by the video signal lines, the lower layer common electrodes for shielding, and the liquid crystal drive electrodes within the pixels in the forty seventh aspect of the present invention noted above are bent within the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to an alignment direction of the liquid crystal molecule, and similarly, the color filter layer and the light shielding film (black mask) on the side of the color filter

substrate which is opposite to the active matrix substrate are bent within the pixel at least once at an angle within a range between 60-120 degrees (except 90 degrees) relative to the alignment direction of the liquid crystal molecule.

**[0090]** According to the first, second, third, fourth and fifth aspects of the invention noted above, the width of the common electrodes that shield the electric fields of the video signal lines can be decreased dramatically and the aperture ratio can be improved dramatically. Especially, by utilising the third, fourth and fifth aspects of the present invention, the bumps covering the video signal lines can be used along with the spacers. Further with the use of halftone exposure method, the bumps covering the video signal lines and the spacers can be constructed at the same time, which dramatically shortens the time required for the production process. In the conventional technologies disclosed by Japanese patent laid-open publication NOS. 2002-258321 and 2002-323706 require to construct the photo spacers on the color filter substrate which requires an additional production process. The use of both the bumps surrounding the video signal lines and the spacers in the present invention can simplify the production process especially when the liquid crystal cell gap is smaller than 3 micrometers, thereby enabling to dramatically reduce the production cost.

**[0091]** According to the second and fifth aspects of the present invention noted above, the capacitance between the video signal line and the shielding common electrode can be minimized, thus, it is possible to maximize the aperture ratio while minimizing the distortion of the video signal waveforms even when the size of the liquid crystal display system is increased to forty (40) inches or more. Especially, the second and fifth aspects of the present invention are useful to decrease the distortion of the video signal waveforms especially when the liquid crystal cell gap is smaller than 2.5 micrometers.

**[0092]** According to the sixth and eighteenth aspects of the present invention noted above, the adhesion strength between the insulation bumps covering the video signal lines and the shielding common electrodes is improved and the problem of film peeling can be prevented, thereby improving the production yield. Furthermore, by using the transparent material for the shielding common electrodes, it is possible to allow the light to pass through the areas around the shielding common electrodes when the liquid crystal is driven so that the effective transmittance ratio can be improved, thereby achieving a liquid crystal display device with high brightness and high contrast.

**[0093]** According to the seventh and nineteenth aspects of the present invention noted above, the movement of the hair tips of the rubbing cloth during the rubbing alignment treatment can be done smoothly so that it can prevent the occurrence of alignment defects. The conventional technologies disclosed in Japanese patent laid-open Nos. 2002-258321 and 2002-323706 do not utilise the taper angle of less than 30 degrees at the edges of

the bumps on the active matrix substrate. As a result, the smooth movements of the hair tips of the rubbing cloth at edge portions of bumps of the conventional technology cannot be attained, which causes the poor alignment.

5 Therefore, it causes the light to leak during the black display at the portions with the poor alignment and thus significantly decreases the contrast. According to the present the taper angle of the bumps covering the video signal lines is controlled to be less than 30 degrees so that no light leak can occur during the black display, which makes it possible to attain a high picture quality with high contrast.

**[0094]** According to the fourth, fifth, eighth, tenth, eleventh, twelfth, sixteenth, seventeenth, twentieth, twenty 10 third and twenty fourth aspects of the present invention noted above, with use of the liquid crystal drop-feed vacuum attachment alignment device, the liquid crystals spread smoothly inside the liquid crystal cells during liquid crystal cell construction, therefore problems associated with residual air bubbles can be decreased. The conventional technology which creates the liquid crystal cells in the normal atmosphere, and then cuts them into the individual cell for injecting the liquid crystals in the vacuum atmosphere is not suitable for the liquid crystal cell construction of the present invention.

**[0095]** The conventional infection technology takes too much time, which significantly decreases the production efficiency. Since the liquid crystal drop-feed vacuum attachment alignment device is beginning to be used in the 15 mass production line today, the structure of the present invention can be easily implemented in the actual application.

**[0096]** According to the ninth and twenty first aspects of the present invention noted above the problem of film 20 peeling of the shielding common electrodes can be avoided when the active matrix substrate and the color filter substrate contact each other in the attachment alignment movement during the liquid crystal drop-feed vacuum attachment process, thereby enabling to minimize the damage to the alignment film.

**[0097]** According to the thirteenth, fourteenth, fifteenth, sixteenth, and seventeenth aspects of the present invention noted above, it is possible to reduce the capacitance created between the shielding common electrodes 25 and the scanning lines. Therefore, the aperture ratio can be maximized while the distortion of the scanning signal waveforms on the scanning lines can be minimised even for the liquid crystal display device of an ultra large size such as forty (40) inches or more. Especially, with use of the fourteenth and seventeenth aspects, it is possible to 30 maximize the aperture ratio while minimizing the distortion of the signal waveforms both on the video signal lines and the scanning lines.

**[0098]** According to the twenty fifth aspect of the 35 present invention noted above, the shielding effect can be improved because of the use of the upper layer and lower layer shielding common electrodes that cover the video signal lines through the insulation films. Accord-

ingly, the vertical crosstalk can be eliminated even when the width of the shielding common electrodes is decreased and the aperture ratio can be increased to the maximum level. Because the imper layer shielding common electrode has a shielding effect higher than that of the lower layer common electrode, the highest shielding effect and high aperture ratio can be achieved by forming the width of the upper layer shielding common electrodes larger than that of the lower layer shielding common electrodes.

**[0099]** According to the twenty sixth, twenty seventh, twenty eighth, twenty ninth and thirtieth aspects of the present invention noted above, it is possible to rotate the positive dielectric constant anisotropic liquid crystal molecules in two different directions (right rotation and left rotation) within a single pixel, thereby enabling to achieve a wider viewing angle. Furthermore, it is possible to significantly decrease the color shift phenomenon so that a picture quality suitable for a liquid crystal display television is achieved. With use of the structure of the present invention, the transverse electric field type liquid crystal display device is able to achieve the wider viewing angle, high aperture ratio, low cost, high contrast, and high response speed.

**[0100]** According to the thirty first, thirty second, thirty third, thirty fourth and thirty fifth aspects of the present invention noted above, it is possible to rotate the negative dielectric constant anisotropic liquid crystal molecules in two different directions (right rotation and left rotation) within a single pixel, thereby enabling to achieve a wider viewing angle.

**[0101]** According to the thirty sixths thirty seventh and thirty eighth aspects of the present invention noted above, it is possible to prevent the capacitance created between the shielding common electrodes and the video signal line from increasing even when the cell gap of the transverse electric field type liquid crystal display device becomes less than 3.0 micrometers, thereby decreasing the distortion of the signal waveforms on the video signal lines. Furthermore, it is possible to concentrate the electric fields created between the liquid crystal drive electrodes and the shielding common electrodes to the edge of each electrode so that it is possible to drive the liquid crystal molecules without increasing the liquid crystal drive voltage even when the cell gap is less than 3.0 micrometers.

**[0102]** According to the thirty ninth aspect of the present invention noted above, it is possible to prevent damage to the main seal that would typically arise during the liquid crystal drop-feed vacuum attachment alignment process. When the spacer bumps are located around the application area of the main seal, the spacer bumps function as a protection wall against the piercing of the liquid crystal. By increasing the width of the spacer bumps provided around the application area of the main seal in a closed loop fashion so that it is larger than the width of the spacer bumps of the effective pixel area, the affect of the protection wall will further increase. Further-

more, because the liquid crystal display device of the present invention does not need to mix the main seal material with glass fibers to determine the cell gaps, it completely eliminates the breakage of wiring due to the pressure of the glass fibers mixed in the main seal that would arise when aluminum or aluminum alloy are used as the scanning lines and the video signal lines.

**[0103]** According to the fortieth, forty first, forty second, forty third, forty fourth and forty fifth aspects of the present invention noted above, since it is possible to produce the insulation bump covering the video signal lines or to produce both the bumps covering the video signal lines and the spacer at the same time with use of the halftone exposure technique, thus it is possible to reduce the production steps and cost. According to the conventional technologies shown in Japanese patent laid-open publication Nos. 2002-258321 and 2002-323706, a separate process is required for producing the photolithography spacers, which inevitably increases the production cost.