(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6138310号

(P6138310)

(45) 発行日 平成29年5月31日(2017.5.31)

(24) 登録日 平成29年5月12日(2017.5.12)

(51) Int.Cl.

F 1

|             |              |                  |      |      |      |

|-------------|--------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36 |      |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 642K |

| <b>G09G</b> | <b>3/34</b>  | <b>(2006.01)</b> | G09G | 3/20 | 660V |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20 | 660U |

|             |              |                  | G09G | 3/20 | 621K |

請求項の数 4 (全 39 頁) 最終頁に続く

(21) 出願番号 特願2016-63113 (P2016-63113)

(22) 出願日 平成28年3月28日 (2016.3.28)

(62) 分割の表示 特願2015-78310 (P2015-78310)

原出願日 平成23年4月27日 (2011.4.27)

(65) 公開番号 特開2016-136276 (P2016-136276A)

(43) 公開日 平成28年7月28日 (2016.7.28)

審査請求日 平成28年3月29日 (2016.3.29)

(31) 優先権主張番号 特願2010-104032 (P2010-104032)

(32) 優先日 平成22年4月28日 (2010.4.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 中村 直行

最終頁に続く

(54) 【発明の名称】表示装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

液晶素子と、トランジスタと、赤の光源と、緑の光源と、青の光源と、白の光源と、制御回路と、を有し、

前記トランジスタは、前記液晶素子と電気的に接続され、

前記制御回路は、動画を表示する第1のモードにおいて、前記赤の光源、前記緑の光源、及び前記青の光源の輝度を制御する機能を有し、

前記制御回路は、静止画を表示する第2のモードにおいて、前記白の光源の輝度を制御する機能を有し、

前記トランジスタは、チャネル形成層としての機能を有する酸化物半導体層を有し、 10

前記酸化物半導体層は、二次イオン質量分析法で測定された水素濃度が  $5 \times 10^{-9}$  a

t o m s / c m<sup>3</sup> 以下である領域を有し、

前記第2のモードにおいて、前記液晶素子に印加された電圧の保持期間を1分以上とする機能を有することを特徴とする表示装置。

## 【請求項 2】

請求項1において、

前記トランジスタの単位チャネル幅あたりのオフ電流は、1 aA /  $\mu$ m未満であることを特徴とする表示装置。

## 【請求項 3】

請求項1又は2において、

前記赤の光源、前記緑の光源、前記青の光源、及び前記白の光源は、発光ダイオードであることを特徴とする表示装置。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一項に記載の表示装置を有する電子機器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、液晶表示装置に関する。または本発明は、液晶表示装置の駆動方法に関する。または、当該液晶表示装置を具備する電子機器に関する。

**【背景技術】**

10

**【0002】**

液晶表示装置は、テレビ受像機などの大型表示装置から携帯電話などの小型表示装置に至るまで、普及が進んでいる。今後は、より付加価値の高い製品が求められており開発が進められている。近年では、地球環境への関心の高まり、及びモバイル機器の利便性向上の点から、低消費電力型の液晶表示装置の開発が注目されている。

**【0003】**

非特許文献 1 では、液晶表示装置の低消費電力化を図るために、動画表示と静止画表示の際のリフレッシュレートを異ならせる構成について開示している。

**【先行技術文献】**

**【非特許文献】**

20

**【0004】**

**【非特許文献 1】 Kazuhiko Tsuda et al., IDW '02, pp 295 - 298**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

上記非特許文献 1 では、静止画を表示する際のリフレッシュレートを低減することで低消費電力化を図ることができる。しかしながら、さらに高品位の動画、及び静止画を表示できる改善の余地がある。

**【0006】**

30

そこで、本発明の一態様は、低消費電力化を図ると共に、動画及び静止画を表示する際の表示品位を向上した液晶表示装置を提供することを課題の一とする。

**【課題を解決するための手段】**

**【0007】**

本発明の一態様は、赤のカラーフィルタを有する副画素と、緑のカラーフィルタを有する副画素と、青のカラーフィルタを有する副画素と、白色の光の透過を制御するための副画素とを有する複数の画素が設けられた表示パネルと、赤、緑、青、及び白の光源を有するバックライト部と、表示パネルを動画モードで表示するか、または静止画モードで表示するかを切り替える画像切替回路と、動画モードでは画像信号に応じてバックライト部の赤、緑、及び青の光源の輝度の制御をし、静止画モードでは画像信号に応じてバックライト部の白の光源の輝度の制御をする表示制御回路と、を有する液晶表示装置である。

40

**【0008】**

本発明の一態様は、赤のカラーフィルタを有する副画素と、緑のカラーフィルタを有する副画素と、青のカラーフィルタを有する副画素と、白色の光の透過を制御するための副画素とを有する複数の画素が設けられた表示パネルと、赤、緑、青、及び白の光源を有するバックライト部と、表示パネルを動画モードで表示するか、または静止画モードで表示するかを切り替える画像切替回路と、第 1 の画像信号を副画素に供給するための第 2 の画像信号に変換するための画像信号変換回路と、動画モードで第 2 の画像信号に応じてバックライト部の赤、緑、及び青の光源の輝度の制御及び表示パネルの制御をする動画表示制御回路と、静止画モードで第 2 の画像信号に応じて白の光源の輝度の制御及び表示パネルの

50

制御をする静止画表示制御回路と、を含む表示制御回路と、を有する液晶表示装置である。

【0009】

本発明の一態様は、赤のカラーフィルタを有する副画素と、緑のカラーフィルタを有する副画素と、青のカラーフィルタを有する副画素と、白色の光の透過を制御するための副画素とを有する複数の画素が設けられた表示パネルと、赤、緑、青、及び白の光源を有するバックライト部と、表示パネルを動画モードで表示するか、または静止画モードで表示するかを切り替える画像切替回路と、第1の画像信号を副画素に供給する第2の画像信号に変換するための画像信号変換回路と、動画モードで第2の画像信号を複数の書き込み期間により表示するよう表示パネルの制御を行う動画タイミング信号生成回路と、動画モードで第2の画像信号に応じてバックライト部の赤、緑、及び青の光源の輝度の制御を行う動画バックライト制御回路と、静止画モードで第2の画像信号を複数の書き込み期間及び保持期間により表示するよう表示パネルの制御を行う静止画タイミング信号生成回路と、静止画モードで第2の画像信号に応じてバックライト部の白の光源の輝度の制御を行う静止画バックライト制御回路と、を含む表示制御回路と、を有する液晶表示装置である。

10

【0010】

本発明の一態様は、赤のカラーフィルタを有する副画素と、緑のカラーフィルタを有する副画素と、青のカラーフィルタを有する副画素と、黄のカラーフィルタを有する副画素とを有する複数の画素が設けられた表示パネルと、赤、緑、青、及び黄の光源を有するバックライト部と、表示パネルを動画モードで表示するか、または静止画モードで表示するかを切り替える画像切替回路と、第1の画像信号を副画素に供給する第2の画像信号に変換するための画像信号変換回路と、動画モードで第2の画像信号を複数の書き込み期間により表示するよう表示パネルの制御を行う動画タイミング信号生成回路と、動画モードで第2の画像信号に応じてバックライト部の赤、緑、及び青の光源の輝度の制御を行う動画バックライト制御回路と、静止画モードで第2の画像信号を複数の書き込み期間及び保持期間により表示するよう表示パネルの制御を行う静止画タイミング信号生成回路と、静止画モードで第2の画像信号に応じてバックライト部の青及び黄の光源の輝度の制御を行う静止画バックライト制御回路と、を含む表示制御回路と、を有する液晶表示装置である。

20

【0011】

本発明の一態様において、保持期間は1分以上である液晶表示装置でもよい。

30

【0012】

本発明の一態様において、副画素は、酸化物半導体でなる半導体層を有するトランジスタを具備する液晶表示装置でもよい。

【0013】

本発明の一態様において、バックライト部の光源は、発光ダイオードである液晶表示装置でもよい。

【発明の効果】

【0014】

本発明の一態様によれば、低消費電力化を図ると共に、動画及び静止画を表示する際の表示品位を向上することができる。

40

【図面の簡単な説明】

【0015】

【図1】本発明の一形態における模式図、及びブロック図。

【図2】本発明の一形態におけるブロック図。

【図3】本発明の一形態におけるブロック図。

【図4】本発明の一形態におけるブロック図。

【図5】本発明の一形態におけるタイミングチャート図。

【図6】本発明の一形態におけるタイミングチャート図。

【図7】本発明の一形態を説明するための模式図。

【図8】本発明の一形態を説明するための模式図。

50

- 【図9】本発明の一形態を説明するための模式図。

- 【図10】本発明の一形態を説明するための回路図。

- 【図11】本発明の一形態を説明するための上面図、及び断面図。

- 【図12】本発明の一形態を説明するための断面図。

- 【図13】本発明の一形態を説明するための断面図。

- 【図14】本発明の一形態における電子機器を説明する図。

- 【図15】本発明の一形態における電子書籍を説明する図。

- 【図16】実施例を説明するための回路図。

- 【図17】実施例を説明するためのタイミングチャート図。

- 【図18】実施例を説明するための関係図。

- 【図19】実施例を説明するための関係図。

- 【図20】実施例を説明するための関係図。

【発明を実施するための形態】

【0016】

以下、本発明の実施の形態及び実施例について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

【0017】

なお、各実施の形態及び実施例の図面等において示す各構成の、大きさ、層の厚さ、信号波形、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

【0018】

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0019】

（実施の形態1）

以下、静止画モードと動画モードとを切り替えて表示をする本実施の形態の液晶表示装置について説明する。なお、液晶表示装置が液晶表示装置に入力される画像信号を静止画として表示を行う動作を静止画モード、動画として表示を行う動作を動画モードとする。

【0020】

なお動画は、複数のフレームに時分割した複数の画像を高速に切り替えることで人間の目に動く画像として認識される画像をいう。具体的には、1秒間に60回（60フレーム）以上画像を切り替えることで、人間の目にはちらつきが少なく動画と認識される。一方、静止画は、動画と異なり、複数のフレーム期間に時分割した複数の画像を高速に切り替えて動作させた際に連続するフレーム期間で、例えばnフレーム目と、（n+1）フレーム目とで変化しない画像信号による画像、または写真や文書等の動きのない画像のことをいう。

【0021】

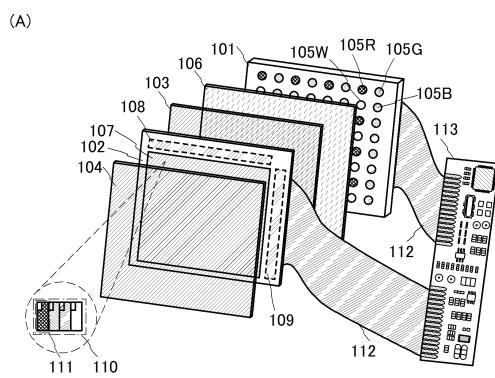

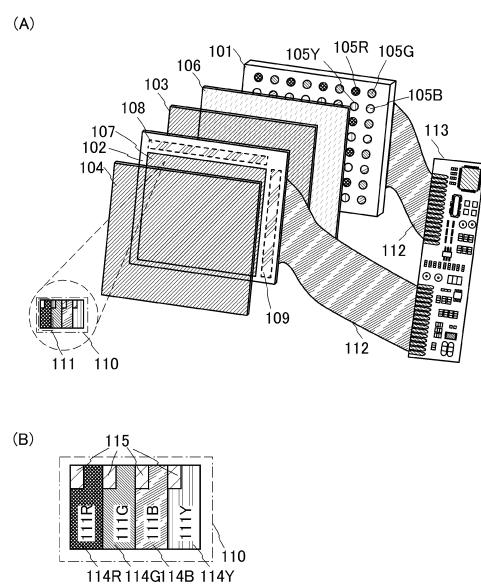

図1（A）は、液晶表示装置の内部の構成を一部示した模式図である。図1（A）の液晶表示装置はバックライト部101と、液晶素子がマトリクス状に設けられた表示パネル102と、表示パネル102を挟む偏光板103、及び偏光板104を有する。バックライト部101には赤、緑、青、及び白の4色の光源（以下光源105R、105G、105B及び105W）、具体的には赤、緑、青、及び白の4色の発光ダイオード（LED）をマトリクス状に配置している。また、表示パネル102とバックライト部101の間には、バックライト部101からの光の放射を一様にするため、拡散板106を配置している。

10

20

30

40

50

## 【0022】

バックライト部101の4色の光源は、静止画モードと動画モードとが切り替わることで、各光源の輝度が切り替えられる。なお図1(A)の模式図は、バックライト部101から放射される光が表示パネル102の液晶素子を通過して観察者側で視認される様子を表している。なお本実施の形態ではバックライトの光源を発光ダイオードとして説明するが、所望の色の光の放射が得られる光源であれば他の種類の光源であってもよい。なお白色の光源に用いる発光ダイオードとしては、発光ダイオードと蛍光体を組み合わせた、3波長白色発光ダイオードを用いればよい。

## 【0023】

図1(A)に示す表示パネル102は、画素部107、走査線駆動回路108(ゲート線駆動回路ともいう)、信号線駆動回路109(データ線駆動回路ともいう)を有する。なお、走査線駆動回路108、及び/または信号線駆動回路109は、表示パネル102の外に設けられる構成でもよい。表示パネル102の画素部107には、複数の画素が設けられる。図1(A)では、複数の画素の一つである画素110を示しており、画素110はカラー表示を行うための複数の副画素111(サブ画素ともいう)を有する。

## 【0024】

またバックライト部101及び表示パネル102は、表示切替回路及び表示制御回路等が設けられた外部基板113と、外部入力端子となるFPC112(フレキシブルプリントサーキット)により、電気的に接続されている。

## 【0025】

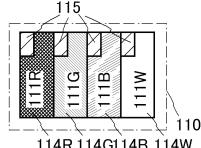

次いで図1(B)では、図1(A)で示した画素110の構成について、拡大して示している。画素110は、赤、緑、青、及び白の4色に対応した副画素111R、111G、111B、111Wを有する。副画素111Rは、カラーフィルタが設けられた光透過部114Rと、副画素111Rを選択するための回路が設けられる回路部115を有する。副画素111Gは、カラーフィルタが設けられた光透過部114Gと、副画素111Gを選択するための回路が設けられる回路部115を有する。副画素111Bは、カラーフィルタが設けられた光透過部114Bと、副画素111Bを選択するための回路が設けられる回路部115を有する。副画素111Wは、カラーフィルタのない光透過部114Wと、副画素111Wを選択するための回路が設けられる回路部115を有する。画素110は、副画素111R、111G、111B、111Wの光の透過を個別に制御することができ、複数の画素110での動画及び静止画のカラー表示を可能にする。

## 【0026】

なお副画素111Wでは、副画素111R、111G、111Bとは異なり、バックライト部101からの白色の光の透過を制御するために設けられており、光透過部114Wにカラーフィルタを必ずしも設ける必要はない。そのため、バックライト部101から放射される光が光透過部114Wを透過して白色を得る構成とする際、カラーフィルタを光が透過することによる光の減衰の影響を受けることなく、カラー表示のための白色とすることができます。一方、赤(R)、緑(G)、青(B)の加法混色により白色を得る構成では、赤(R)、緑(G)、青(B)のいずれの光透過部にもカラーフィルタを設けており、光の減衰を受けてしまう。そのため、カラーフィルタを設けない光透過部114Wを透過して白色を得る副画素を画素に加えた構成により、白色の表示を行う際にカラーフィルタによる光の減衰の影響を受けない分、バックライト部の輝度を低減することができるため、液晶表示装置の低消費電力化を図ることができる。

## 【0027】

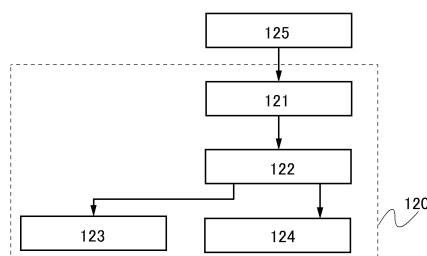

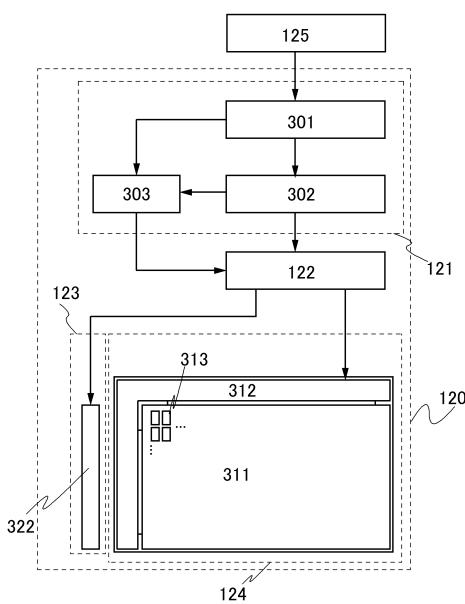

次いで液晶表示装置のブロック図について図1(C)に示す。図1(C)に示す液晶表示装置120は、表示切替回路121、表示制御回路122、バックライト部123、表示パネル124を有する。

## 【0028】

表示切替回路121は、画像信号供給源125からの画像信号(第1の画像信号ともいう)に基づく表示について、表示パネル124で動画として表示する(動画モード)か、ま

10

20

30

40

50

たは静止画として表示する（静止画モード）か、を切り替えるための回路である。例えば、連続するフレーム間での画像を比較することで、動画であるか静止画であるかの判定を行い、動画モードと静止画モードとを切り替える構成とすればよい。または表示切替回路 121 は、入力される画像信号の種類に応じて、静止画モードとするか、動画モードとするかを切り替える構成としてもよい。例えば、画像信号供給源 125 の画像信号のもとになる電子データのファイル形式等を参照することにより、動画モードとするかまたは静止画モードとするかを切り替える構成とすればよい。または表示切替回路 121 は、表示切替回路 121 の外部からの切替信号に応じて、動画モード、または静止画モードの切り替えを行う構成としてもよい。例えば、切り替えスイッチで動画モードまたは静止画モードを切り替える構成としてもよい。

10

#### 【0029】

なお、画像信号供給源 125 からの画像信号は、デジタル値の画像信号であることが望ましい。アナログ値の画像信号の場合には、画像信号供給源 125 と表示切替回路 121 との間に A/D 変換回路を設けて、アナログ値からデジタル値への変換を行う構成とすればよい。

#### 【0030】

表示制御回路 122 は、表示切替回路 121 での動画モードまたは静止画モードの切り替えに応じて、バックライト部 123 及び表示パネル 124 を制御するための信号を出力するための回路である。具体的に、表示制御回路 122 は、動画モードまたは静止画モードに応じて、バックライト部 123 の光源の輝度を制御するための信号の供給、及び動画モードまたは静止画モードに応じた表示パネル 124 での画像表示のための画像信号の供給、及び駆動回路を動作させるための信号（クロック信号、スタートパルス等）の供給、を制御するための回路である。

20

#### 【0031】

バックライト部 123 は、バックライトを制御するための回路及び赤（R）、緑（G）、青（B）、及び白（W）の光源を有する。バックライト部 123 の赤（R）、緑（G）、青（B）、及び白（W）の光源は、表示制御回路 122 により個別に輝度が制御される。

#### 【0032】

表示パネル 124 は、駆動回路、及び複数の画素を有する。画素は赤、緑、青、及び白の 4 色に対応した副画素を有する。副画素は、副画素を選択するための回路部となるトランジスタと、該トランジスタに接続された画素電極と、容量素子を有する。なお該画素電極とそれに対応する電極との間に液晶層を挟持して液晶素子が形成される。なお副画素に設けるトランジスタは、リーケ電流が極めて小さいことが好適であり、半導体層として酸化物半導体を用いることが望ましい。酸化物半導体は半導体中のキャリアを極めて少なくすることで、オフ電流を少なくすることができる。よって、画素においては画像信号等の電気信号の保持時間を長くすることができ、書き込み期間の間隔も長く設定できる。

30

#### 【0033】

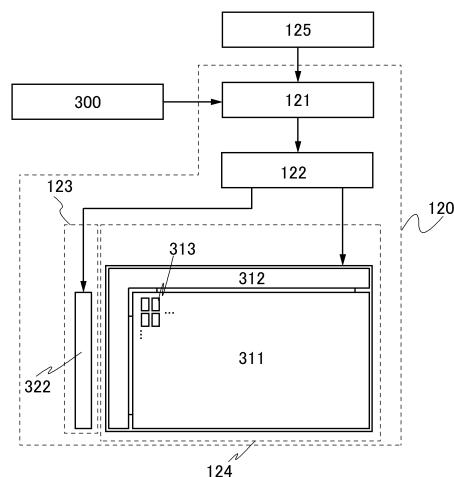

次いで、図 1 (C) に示すブロック図について、具体的な例として液晶表示装置のプロック図を図 2 に示す。図 2 では、表示切替回路 121 の具体的な例として、外部切替手段によって動画モード、又は静止画モードを切り替える構成について示している。加えて、図 2 では図 1 (C) で示したバックライト部 123 及び表示パネル 124 の構成について、より詳細に示している。

40

#### 【0034】

液晶表示装置の構成は、図 1 (C) と同様に、表示切替回路 121、表示制御回路 122、バックライト部 123、表示パネル 124 を有し、表示切替回路 121 には外部切替手段 300 より信号が供給される様子について示している。また図 2 では、表示切替回路 121 には、画像信号供給源 125 より画像信号が供給される様子について示している。なお外部切替手段 300 の具体的な例としては、切替スイッチのように機械的に切り替えて操作する手段を有する構成であればよく、タッチセンサやキーボード等により切り替える手段を有する構成でもよい。

50

## 【0035】

図2に示すバックライト部123はバックライト322を有する。バックライト322には赤、緑、青、及び白（RGBWと略記する）の各色の光源が配置される。なお図2に示すバックライト322は、表示パネル124と並んで設ける構成としているが、実際には表示パネル124と重畳して設けられる。

## 【0036】

表示パネル124は、画素部311、及び駆動回路312を有する。画素部311には、走査線と信号線に接続されたRGBWの各色に対応する副画素313がマトリクス状に複数配置されている。副画素313は、副画素を選択するための回路部となるトランジスタと、該トランジスタに接続された画素電極と、容量素子を有する。なお該画素電極とそれに対応する電極との間に液晶層を挟持して液晶素子が形成される。

10

## 【0037】

液晶素子の一例としては、液晶の光学的変調作用によって光の透過又は非透過を制御する素子がある。その素子は一対の電極と液晶層により構造されることが可能である。なお、液晶の光学的変調作用は、液晶にかかる電界によって制御される。

## 【0038】

なお図2に示す表示制御回路122は、表示切替回路121から供給される、表示パネル124を動画モードで表示するか、または静止画モードで表示するかに応じた信号、及び画像信号により、バックライト部123のバックライト322の光源を制御するための信号、及び表示パネル124の駆動回路312を制御するための信号を出力する回路となる。

20

## 【0039】

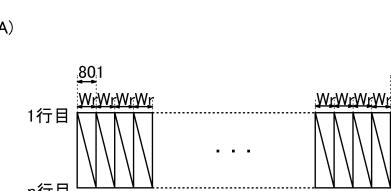

次いで、図2とは異なる表示切替回路121の構成について図3で説明する。図3に示す表示切替回路121は、連続するフレーム間での画像を比較することで動画であるか静止画であるかの判定を行い、動画モードと静止画モードとを切り替える構成である。

## 【0040】

図3に示す表示切替回路121は、記憶回路301、比較回路302、及び選択回路303を有する。

## 【0041】

ここで図3に示す表示切替回路121の動作について説明する。

30

## 【0042】

画像信号供給源125から、表示切替回路121の記憶回路301に画像信号が入力される。記憶回路301は、複数のフレームに関する画像信号を記憶するための複数のフレームメモリを有する。なお記憶回路301が有するフレームメモリの数は特に限定されるものではなく、複数のフレームに関する画像信号を記憶できる素子であればよい。なおフレームメモリは、例えばDRAM（Dynamic Random Access Memory）、SRAM（Static Random Access Memory）等の記憶素子を用いて構成すればよい。

## 【0043】

なおフレームメモリは、フレーム期間毎に画像信号を記憶する構成であればよく、フレームメモリの数について特に限定されるものではない。またフレームメモリの画像信号は、比較回路302及び選択回路303により選択的に読み出されるものである。

40

## 【0044】

比較回路302は、記憶回路301に記憶された連続するフレーム期間の画像信号を選択的に読み出して、当該画像信号の連続するフレーム間での比較を画素毎に行い、差分を検出するための回路である。

## 【0045】

なお、差分の検出の有無により、表示制御回路122及び選択回路303での動作が決定されることとなる。比較回路302での画像信号の比較により、いずれかの画素で差分が検出された際に当該差分を検出した連続するフレーム期間は、動画であると判断される。

50

一方、比較回路 302 での画像信号の比較により、全ての画素で差分が検出されない際に当該差分を検出しなかった連続するフレーム期間は、静止画であると判断する。すなわち比較回路 302 は、連続するフレーム期間の画像信号の差分を検出することによって、動画を表示するための画像信号であるか、または静止画を表示するための画像信号であるかの判断をする。

【0046】

なお、当該比較により得られる差分は、一定のレベルを超えたときに、差分を検出したと判断されるように設定してもよい。なお比較回路 302 は、差分の大きさにかかわらず、差分の絶対値によって、差分の検出の判断をする設定とすればよい。

【0047】

選択回路 303 は、複数のスイッチ、例えばトランジスタで形成される複数のスイッチを設ける構成とする。また、選択回路 303 は、比較回路 302 での差分の演算により差分が検出された際、すなわち連続するフレーム間で表示される画像が動画の際、当該画像信号が記憶された記憶回路 301 内のフレームメモリより画像信号を選択して表示制御回路 122 に出力するための回路である。

【0048】

なお選択回路 303 は、比較回路 302 での演算により画像信号の差分が検出されない際、すなわち連続するフレーム間で表示される画像は静止画の際、当該画像信号について表示制御回路 122 に出力しない回路となる。そのため静止画の際、選択回路 303 では、画像信号を記憶回路 301 のフレームメモリより表示制御回路 122 に出力する動作を停止することができ、その分の消費電力を削減することができる。

【0049】

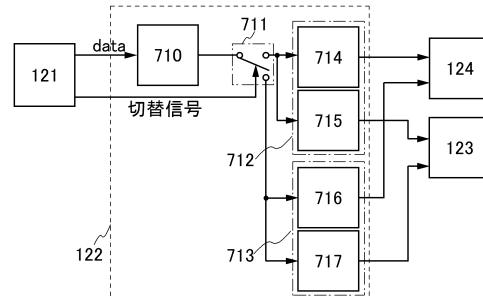

次いで、表示制御回路 122 の構成について図 4 で説明する。図 4 に示す表示制御回路 122 のブロック図は、表示切替回路 121 での動画モードまたは静止画モードの切り替えに応じて、バックライト部 123 及び表示パネル 124 を制御するための信号を切り替えて出力するための一例である。具体的には表示制御回路 122 は、画像信号変換回路 710、表示制御切替回路 711、動画表示制御回路 712、静止画表示制御回路 713 を有する。動画表示制御回路 712 は、動画タイミング信号生成回路 714、及び動画バックライト制御回路 715 を有する。静止画表示制御回路 713 は、静止画タイミング信号生成回路 716、及び静止画バックライト制御回路 717 を有する。

【0050】

画像信号変換回路 710 は、表示切替回路 121 からの画像信号 data が RGBW の副画素 111R、111G、111B、111W に対応していない第 1 の画像信号である場合、例えば R (赤)、G (緑)、B (青) の 3 色に対応したカラー画像の画像信号の場合に、演算処理により RGBW の副画素 111R、111G、111B、111W に対応する第 2 の画像信号に変換するための回路である。具体的な例を挙げて説明すると、R (赤)、G (緑)、B (青) の 3 色に対応したカラー画像の画像信号から副画素 111W に対応する白色の画像信号に相当する階調分を減算して新たに副画素 111W に対応する白色の画像信号を生成し、RGBW の副画素 111R、111G、111B、111W により R (赤)、G (緑)、B (青) の 3 色に対応したカラー画像の画像信号と同等のカラー画像の画像信号に変換するものである。

【0051】

表示制御切替回路 711 は、表示切替回路 121 での動画モードまたは静止画モードの切替の信号 (切替信号) に応じて、画像信号変換回路 710 で変換された RGBW の画像信号を動画表示制御回路 712 または静止画表示制御回路 713 に振り分けるかの切り替えを制御する回路である。具体的には、トランジスタ等でスイッチング素子を構成して設ければよい。

【0052】

動画タイミング信号生成回路 714 は、表示パネル 124 を動画モードで表示させる画像信号の供給、及び表示パネル 124 の駆動回路を動作させるための信号 (クロック信号、

10

20

30

40

50

スタートパルス等)の供給、を制御するための回路である。動画バックライト制御回路715は、表示パネル124を動画モードで表示させる画像信号に応じてバックライト部のR(赤)、G(緑)、B(青)の光源の輝度を制御するための回路である。

【0053】

静止画タイミング信号生成回路716は、表示パネル124を静止画モードで表示させる画像信号の供給、及び表示パネル124の駆動回路を動作させるための信号(クロック信号、スタートパルス等)の供給、を制御するための回路である。静止画バックライト制御回路717は、表示パネル124を静止画モードで表示させる画像信号に応じてバックライト部の白(W)の光源の輝度を制御するための回路である。

【0054】

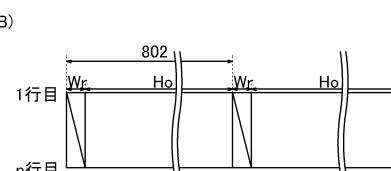

次いで、上述した動画モード及び静止画モードでの動画タイミング信号生成回路714及び静止画タイミング信号生成回路716による表示パネル124の制御について説明する。以下、動画モードでの表示を動画表示期間、静止画モードでの表示を静止画表示期間として説明する。なお動画表示期間は1つの画像を表示する1フレーム期間が複数連続して動画を表示する期間である。具体的には、1秒間に60回(60フレーム)以上画像を切り替えて動画を表示する期間である。また静止画表示期間は、1つの画像を表示する1フレーム期間が1つまたは複数連続して設けられ、静止画を表示する。静止画表示期間では、一定のリフレッシュレートにより画像信号が書き込まれる。なお1フレーム期間とは、表示パネルの複数の画素に画像信号を順次書き込んで表示される画像が更新される期間のことをいう。

【0055】

図5(A)に示す期間801を動画表示期間の1フレーム期間として説明する。期間801は書き込み期間(図5(A)中、「Wr」で表記)を有する。なお動画表示期間は書き込み期間の他に保持期間を有していてもよいが、フリッカが生じない程度に短い期間であることが望ましい。書き込み期間では、表示パネルにおける画素の1行目から順にn行目まで画像信号を書き込む。書き込み期間では、連続するフレーム期間で異なる画像信号を画素に書き込むことで、視認者に動画と知覚させるものである。具体的には、動画表示期間における画像信号の書き込み期間Wrは、フリッカ(ちらつき)が生じない程度の書き込み速度となる16.6m秒以下であることが好ましい。

【0056】

図5(B)に示す期間802を静止画表示期間の1フレーム期間として説明する。期間802は画像信号を画素に書き込む書き込み期間(図5(B)中「Wr」で表記)、及び画像信号を画素に保持する保持期間(図5(B)中「Ho」で表記)を有する。書き込み期間では、表示パネルにおける画素の1行目から順にn行目にかけて画像信号を書き込む。書き込まれた画像信号は、保持期間においてトランジスタをオフ状態とすることで液晶素子に印加された電圧を保持し続ける。すなわち保持期間では、トランジスタからのリーク電流による電圧降下が極端に小さいことを利用して画像信号を保持し続ける。静止画表示期間802における画像信号の保持期間は、累積時間の経過により液晶素子に印加した電圧の降下が表示品位の低下を招かない程度が望ましい。画像信号の保持期間を1分以上とすることで、人間の目の疲労を減らせるといった効果もある。なお、累積時間の経過により液晶素子に印加した電圧が降下した場合には、再度、前の期間と同じ画像信号の書き込み期間を設け、再び保持期間を設ける構成とすればよい。

【0057】

なお副画素に設けるトランジスタは、リーク電流が極めて小さいことが好適であり、半導体層として酸化物半導体を用いることが望ましい。酸化物半導体は半導体中のキャリアを極めて少なくすることで、オフ電流を少なくすることができる。よって、画素においては画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。またトランジスタの構造については逆スタガ型の構造でもよいし、順スタガ型の構造でもよい。または、チャネル領域が複数の領域に分かれて直列に接続された、ダブルゲート型の構造でもよい。または、ゲート電極がチャネル領域の上下に設けられたデュアルゲー

10

20

30

40

50

ト型の構造でもよい。また、トランジスタを構成する半導体層を複数の島状の半導体層にわけて形成し、スイッチング動作を実現しうるトランジスタ素子としてもよい。

#### 【0058】

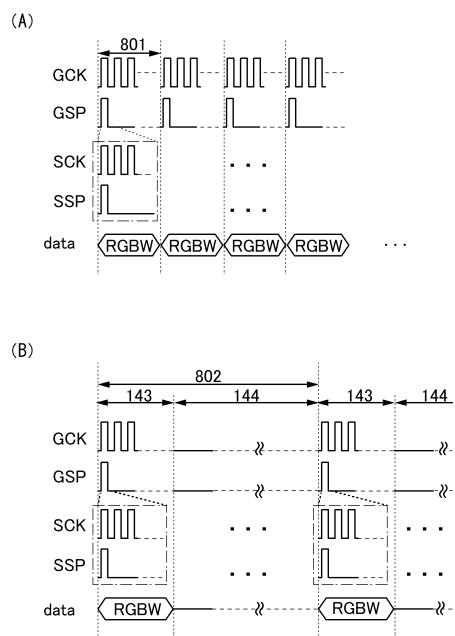

次いで、上述した動画モード及び静止画モードでの動画タイミング信号生成回路714及び静止画タイミング信号生成回路716による表示パネル124の駆動回路312の制御について、各信号のタイミングチャートについて示し、説明する。ここでは図5(A)で説明した期間801について図6(A)に、期間802について図6(B)に、それぞれのタイミングチャートを示す。

#### 【0059】

図6(A)では、期間801における走査線側駆動回路に供給するクロック信号GCK、及びスタートパルスGSP、信号線側駆動回路に供給するクロック信号SCK、及びスタートパルスSSP、画像信号dataについて示したものである。

10

#### 【0060】

期間801において、クロック信号GCKは常時供給されるクロック信号となる。またスタートパルスGSPは、垂直同期周波数に応じたパルスとなる。またクロック信号SCKは常時供給されるクロック信号となる。またスタートパルスSSPは、1ゲート選択期間に応じたパルスとなる。なお期間801では、各画素の副画素に応じたR(赤)、G(緑)、B(青)、W(白)の画像信号の書き込みが行われる。また画像信号の書き込みと共に、R(赤)、G(緑)、B(青)のバックライトの光源からの光により、カラー表示の画像を視認することができる。そして視認者は、複数の書き込みの期間801により、複数の画像が切り替わることで、動画でのカラー表示を視認することができる。

20

#### 【0061】

次いで図6(B)について説明する。図6(B)では、期間802について、書き込み期間143、保持期間144に分けて説明を行う。

#### 【0062】

書き込み期間143においては、クロック信号GCKは一画面書き込むためのクロック信号となる。またスタートパルスGSPは、一画面書き込むためのパルスとなる。またクロック信号SCKは一画面書き込むためのクロック信号となる。またスタートパルスSSPは、一画面書き込むためのパルスとなる。なお書き込み期間143では、各画素の副画素に応じたR(赤)、G(緑)、B(青)、W(白)の画像信号の書き込みが行われる。

30

#### 【0063】

保持期間144においては、クロック信号GCK、スタートパルスGSP、クロック信号SCK、スタートパルスSSPは、信号線側駆動回路及び走査線側駆動回路の動作を停止するために、供給が停止されることとなる。そのため保持期間144では電力消費を低減することができ、低消費電力化を図ることができる。なお保持期間144では、書き込み期間143に画素に書き込んだ画像信号が、オフ電流が極端に小さい画素トランジスタにより保持されるため、カラー表示の静止画を1分以上の期間保持することができる。なおこの間視認者は、W(白)のバックライトの光源からの光により、静止画のカラー表示を視認することができる。また、保持される画像信号に応じた電位が一定の期間の経過により低下する前に、新たに書き込み期間143を設けて先の期間の画像信号と同じ画像信号を書き込み(リフレッシュ動作)、再度保持期間144を設ければよい。

40

#### 【0064】

次いで、上述した動画モード及び静止画モードでの動画バックライト制御回路715及び静止画バックライト制御回路717によるバックライト部123の制御について説明する。本実施の形態の構成では、バックライト部の点灯状態を動画モード及び静止画モードで切り替えることで、動画及び静止画を表示する際の表示品位をさらに向上することができる。図7、図8では具体的な構成を説明し、その効果について述べる。

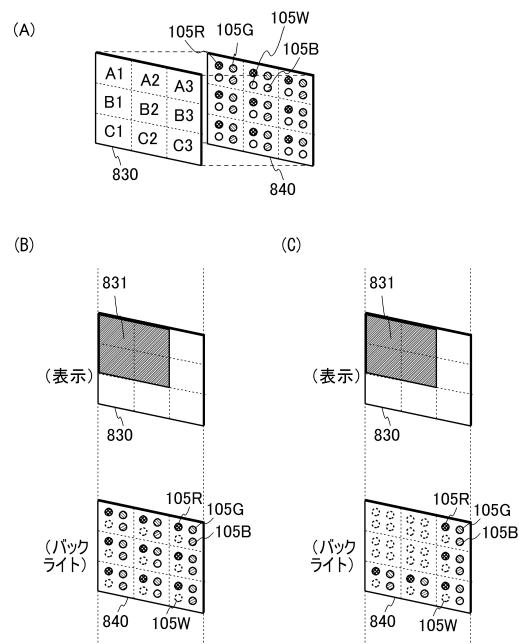

#### 【0065】

まず図7(A)では、説明のため、表示パネルの画素部830を複数の領域に分割した様子を示している。図7(A)では、画素部830を、領域A1、領域A2、領域A3、領

50

域 B 1、領域 B 2、領域 B 3、領域 C 1、領域 C 2、領域 C 3 に分割して、以下説明する。また図 7 ( A ) では画素部 830 に対応するバックライト 840 を併せて示し、前述の一つの領域に対し R (赤)、G (緑)、B (青)、W (白) の光源 105R、105G、105B、105W を有する構成を一例として示している。

【0066】

次いで図 7 ( B ) では、動画モードでの動画バックライト制御回路 715 の動作について説明するため、画素部での模式的な表示とそのときのバックライトの点灯状態について示し、動作について説明する。

【0067】

図 7 ( B ) では、画素部 830 での表示と、バックライト 840 の点灯状態を並べて示している。画素部 830 の表示において、表示の一例として、前述の領域 A 1、領域 A 2、領域 B 1、及び領域 B 2 に表示画像 831 を示している。

10

【0068】

動画バックライト制御回路 715 は、動画モードで RGBW の副画素に対応する画像信号 (第 2 の画像信号) に応じてバックライト 840 の輝度の制御を行う回路である。具体的に図 7 ( B ) に示す例でいえば、光源 105R、105G、及び 105B を点灯する制御、光源 105W を消灯する制御を行う。なお、バックライト 840 の各光源の点灯状態について図 7 ( B ) では、点灯状態を実線で図示し、消灯状態を点線で表している。

【0069】

図 7 ( B ) に示す動画モードでの表示は、バックライトの R (赤)、G (緑)、B (青) の光源を同時に点灯することで、白色の光を得る構成としている。そのためバックライトの R (赤)、G (緑)、B (青) の光源を用いることによる色再現範囲の良好な表示とすることで、動画を表示する際の表示品位を向上することができる。

20

【0070】

また図 7 ( C ) では、図 7 ( B ) と同様に、画素部 830 の表示において、表示の一例として、前述の領域 A 1、領域 A 2、領域 B 1、及び領域 B 2 に表示画像 831 を示している。図 7 ( C ) では、表示画像 831 に応じてバックライトの輝度を制御するローカルディミング (local dimming) の駆動方式を組み合わせた例について説明する。ここで、表示画像 831 に属する領域は、表示される画像の輝度が低輝度 (またはゼロ) の領域とし、その他の領域が画像の輝度が高輝度の領域、とする。

30

【0071】

動画バックライト制御回路 715 は、動画モードで RGBW の副画素に対応する画像信号 (第 2 の画像信号) に応じてバックライト 840 の輝度の制御を行う回路である。具体的には、動画バックライト制御回路 715 では、画素部 830 の領域毎に入力される画像信号の階調値の頻度に関するヒストグラムを演算及び記憶し、領域毎の輝度を演算する。なお、色要素として赤 (R)、G (緑)、B (青)、W (白) の 4 つの副画素で一つの色を表す画素とするため、動画バックライト制御回路 715 では、RGBW の各色で重み付けを行った上で 4 つの副画素を併せて領域毎の輝度を演算すればよい。そして動画バックライト制御回路 715 は、画素部 830 の領域毎の輝度に応じて、画素部 830 の領域に対応するバックライトの輝度を制御する信号をバックライト部 123 に出力する。

40

【0072】

図 7 ( C ) に示す例でいえば、表示画像 831 の領域に対応するバックライトが消灯するよう、光源 105R、105G、105B を制御する。また、表示画像 831 以外の領域に対応するバックライトが高輝度の光となるよう、光源 105R、105G、及び 105B を制御する。

【0073】

なお図 7 ( C ) では、画素部で表示する輝度を大小の 2 段階で説明したが、適宜複数の段階でバックライトの輝度を制御する構成とすればよい。

【0074】

図 7 ( C ) に示す動画モードでの表示は、図 7 ( B ) と同様に、バックライトの R (赤)

50

、 G ( 緑 ) 、 B ( 青 ) の光源を同時に点灯することで、白色の光を得る構成としている。そのため色再現範囲の良好な表示を行うことができ、動画を表示する際の表示品位を向上することができる。加えて、画素部の領域毎にバックライトの明るさを制御し、表示する画像のコントラストを向上させることができ、動画を表示する際の表示品位を向上することができる。

【 0 0 7 5 】

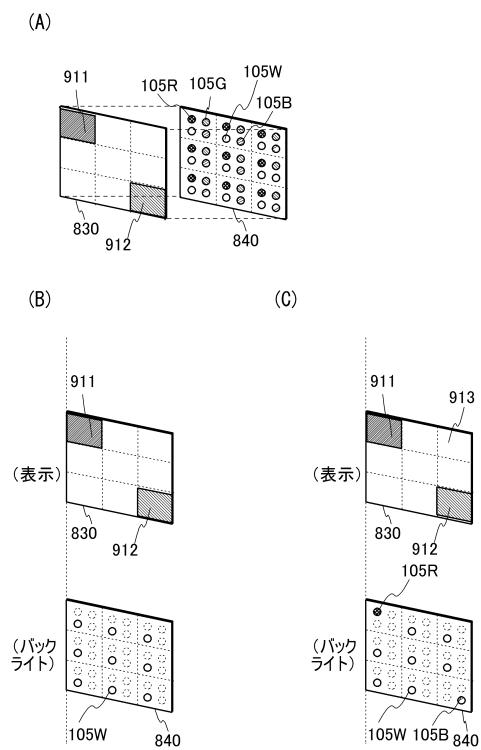

次いで、図 8 ( A ) 乃至 ( C ) では、静止画モードでの静止画バックライト制御回路 717 の動作について説明するため、画素部での模式的な表示とそのときのバックライトの点灯状態について示し、動作について説明する。なお図 8 ( A ) 乃至 ( C ) では、図 7 ( A ) と同様に画素部 830 の領域を複数の領域に区切って説明する。

10

【 0 0 7 6 】

図 8 ( B ) では、静止画モードでの静止画バックライト制御回路 717 の動作について説明するため、画素部での模式的な表示とそのときのバックライトの点灯状態について示し、動作について説明する。

【 0 0 7 7 】

図 8 ( B ) では、画素部 830 での表示と、バックライト 840 の点灯状態を並べて示している。画素部 830 の表示において、表示の一例として、前述の領域 A1 に表示画像 911 、前述の領域 C3 に表示画像 912 を示している。

【 0 0 7 8 】

静止画バックライト制御回路 717 は、静止画モードで R G B W の副画素に対応する画像信号 ( 第 2 の画像信号 ) に応じてバックライト 840 の輝度の制御を行う回路である。具体的に図 8 ( B ) に示す例でいえば、光源 105R 、 105G 、及び 105B を消灯する制御、光源 105W を点灯する制御を行う。なお、バックライト 840 の各光源の点灯状態について図 8 ( B ) では、点灯状態を実線で図示し、消灯状態を点線で表している。

20

【 0 0 7 9 】

図 8 ( B ) に示す静止画モードでの表示は、バックライトの W ( 白 ) の光源を点灯することで、白色の光を得る構成としている。そのため R ( 赤 ) 、 G ( 緑 ) 、 B ( 青 ) の光源を同時に点灯させて得られる白色でなく、白色の光源を用いることで点灯させる光源を減らすことができ、低消費電力化を図ることができる。

【 0 0 8 0 】

また図 8 ( C ) では、図 8 ( B ) と同様に、画素部 830 の表示において、表示の一例として、前述の領域 A1 に表示画像 911 、前述の領域 C3 に表示画像 912 を示している。図 8 ( C ) では、表示画像 911 、表示画像 912 に応じてバックライトの輝度を制御する駆動方式を組み合わせた例について説明する。ここで、画素部 830 の表示の例として、領域 A1 では赤色の表示画像 911 、領域 C3 では青色の表示画像 912 、その他の領域が白色の表示画像 913 として、図 8 ( C ) での動作の説明を行うものとする。

30

【 0 0 8 1 】

静止画バックライト制御回路 717 は、静止画モードで R G B W の副画素に対応する画像信号 ( 第 2 の画像信号 ) に応じてバックライト 840 の輝度の制御を行う回路である。具体的には、静止画バックライト制御回路 717 では、領域 A1 に対応する光源で赤色 ( R ) の光源 105R が点灯するよう制御し、領域 C3 に対応する光源で青色 ( B ) の光源 105B が点灯するよう制御し、その他の領域で白色 ( W ) の光源 105W が点灯するよう制御する。なお他の光源は消灯状態とする。従って本実施の形態の構成は、画素部の領域毎にバックライトの光源の輝度を R ( 赤 ) 、 G ( 緑 ) 、 B ( 青 ) 、または W ( 白 ) の各色で選択して制御することができ、色純度が良好な画像の表示を行うことができ、白色の光源または単色の光源を用いることで、低消費電力化を図ることができる。

40

【 0 0 8 2 】

なお図 8 ( C ) では、画素部で表示する輝度について説明を省略したが、適宜複数の段階でバックライトの各光源の輝度を制御する構成とすればよい。

【 0 0 8 3 】

50

図8(C)に示す静止画モードでの表示は、図8(B)と同様に、バックライトのW(白)の光源を点灯することで、白色の光を得る構成としている。そのためR(赤)、G(緑)、B(青)の光源を同時に点灯させて得られる白色でなく、白色の光源を用いることで点灯させる光源を減らすことができ、低消費電力化を図ることができる。また画素部での表示に応じてバックライトのR(赤)、G(緑)、B(青)の光源を点灯することで、色再現範囲の良好な表示を行うことができ、静止画を表示する際の表示品位を向上することができる。

#### 【0084】

以上説明したように、図8(C)に示す静止画モードでの表示は、動画モードでの表示に比べ、複数の階調値によって表示がなされることが多い。そのため画素部の領域毎にバックライトの光源の輝度をR(赤)、G(緑)、B(青)の各色で選択して制御することで、色純度が良好な画像の表示を行うことができる。そして白色のバックライトを点灯させる領域では、R(赤)、G(緑)、B(青)の光源105R、105G、105Bを同時に点灯させて得られる白色でなく、白色の光源105Wを用いて白色に対応する光源とすることで、低消費電力化を図ることができる。

10

#### 【0085】

本実施の形態において述べた液晶表示装置は、静止画表示を行う際、画像信号の書き込み回数を低減することにより、低消費電力化を図ることができる。加えて本実施の形態において述べた液晶表示装置は、動画を表示する際に、バックライトの光源の輝度をR(赤)、G(緑)、B(青)の光源で制御することで、色純度が良好な画像の表示とし、表示品位を向上することができる。また、本実施の形態において述べた液晶表示装置は、静止画を表示する際に、バックライトの光源の輝度をW(白)の光源で制御することで、白色を点灯する際の消費電力を低減することができる。

20

#### 【0086】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0087】

##### (実施の形態2)

本実施の形態では、上記実施の形態1で述べた画素110を構成する副画素の色要素の組み合わせとして、RGBWでなく、Wの代わりに黄色の副画素を追加した構成について説明する。なお上記実施の形態1と重複する説明については、本実施の形態での説明を省略するものとする。

30

#### 【0088】

図9(A)には、図1(A)と同様に、液晶表示装置の模式図について示している。図1(A)と異なる点は、バックライト部101の光源の組み合わせについて、赤、緑、青、及び黄の4色の光源(以下光源105R、105G、105B及び105Y)を用いる点にある。

#### 【0089】

本実施の形態の構成では、実施の形態1の構成と異なり、白色の光源を用いるのでなく、青、及び黄の発光ダイオードを同時に点灯することによる白色の光源とする構成である。なお青色と補色の関係にある黄色を用いて白色の光源とする構成により、R(赤)、G(緑)、B(青)を同時に点灯することにより得られる白色に比べ、低消費電力化が図れる等の利点がある。

40

#### 【0090】

本実施の形態における画素110はカラー表示を行うための複数の副画素111(サブ画素ともいう)を有する。図9(B)では、本実施の形態で示す画素が有する副画素の組み合わせとして、上記実施の形態1と異なり、赤、緑、青、及び黄の4色に対応した副画素111R、111G、111B、111Yを有する構成について示している。

#### 【0091】

なお副画素111Yでは、光透過部114Yを有する。光源105Yから放射される光を

50

副画素 111Y の光透過部 114Y を透過して黄色を得る構成とする際、色純度の良好な表示とすることができる。その結果、赤、緑、青、及び黄の 4 色に対応した副画素 111R、111G、111B、111Y による色再現範囲の良好な表示を行うことができる。加えて、青色の光源 105B 及び黄色の光源 105Y を同時に点灯すること白色の光源を得る構成とすることで、R(赤)、G(緑)、B(青)の光源 105R、105G、105B を同時に点灯させて白色を得る構成に比べ、低消費電力化を図ることができる。

#### 【0092】

なお本実施の形態においても、図 1(C) で説明した液晶表示装置のブロック図、図 2 及び図 3 で説明した表示切替回路 121 の構成、図 4 で説明した表示制御回路 122 の構成、並びに図 5 乃至図 8 の動画モード及び静止画モードでのバックライト部 123 及び表示パネル 124 の制御について、適宜同様の動作とすればよい。

10

#### 【0093】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0094】

##### (実施の形態 3)

本実施の形態では、上記実施の形態 1 で説明した表示パネルの構成、及び副画素の回路構成の一例について説明する。

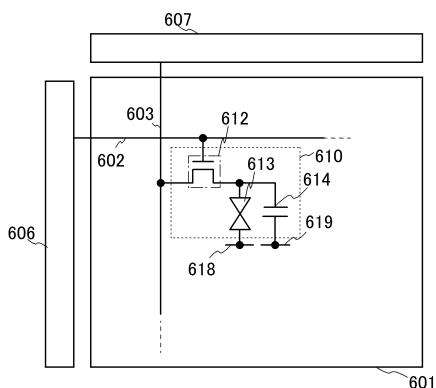

#### 【0095】

図 10 に示す表示パネルは、画素部 601、走査線 602(ゲート線ともいう)、信号線 603(データ線ともいう)、副画素 610、共通電極 618(コモン電極ともいう)、容量線 619、駆動回路である走査線側駆動回路 606、駆動回路である信号線側駆動回路 607 を有する。

20

#### 【0096】

副画素 610 は、画素トランジスタ 612、液晶素子 613、容量素子 614 を有する。画素トランジスタ 612 はゲートが走査線 602 に接続され、ソース又はドレインの一方となる第 1 端子が信号線 603 に接続され、ソース又はドレインの他方となる第 2 端子が、液晶素子 613 の一方の電極及び容量素子 614 の第 1 の電極に接続される。なお液晶素子 613 の他方の電極は、共通電極 618 に接続されている。なお容量素子 614 の第 2 の電極は、容量線 619 に接続される。なお画素トランジスタ 612 は、薄膜の酸化物半導体層を有する薄膜トランジスタ(TFT)で構成することが好ましい。

30

#### 【0097】

なお、薄膜トランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本書類(明細書、特許請求の範囲又は図面など)においては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第 1 端子、第 2 端子と表記する場合がある。

40

#### 【0098】

なお画素トランジスタ 612 の半導体層として酸化物半導体を用いると、トランジスタのオフ電流を少なくすることができます。よって、画素においては画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。よって 1 フレーム期間の周期を長くすることができ、静止画モードのリフレッシュ動作の頻度を少なくすることができるため、より消費電力を抑制する効果を高くできる。また、酸化物半導体を用いたトランジスタは、アモルファスシリコンを用いたトランジスタと比較して、高い電界効果移動度が得られるため、書き込み時間を短縮することができ、高速駆動が可能である。

#### 【0099】

なお走査線側駆動回路 606、信号線側駆動回路 607 は、画素部 601 と同じ基板上に

50

設ける構成とすることが好ましいが、必ずしも同じ基板上に設ける必要はない。画素部 601 と同じ基板上に走査線側駆動回路 606、信号線側駆動回路 607 を設けることで、外部との接続端子数を削減することができ、液晶表示装置の小型化を図ることができる。

【0100】

なお、副画素 610 は、マトリクス状に配置（配列）されている。ここで、画素がマトリクスに配置（配列）されているとは、縦方向もしくは横方向において、画素が直線上に並んで配置されている場合や、ギザギザな線上に配置されている場合を含む。

【0101】

なお、A と B とが接続されている、と明示的に記載する場合は、A と B とが電気的に接続されている場合と、A と B とが機能的に接続されている場合と、A と B とが直接接続されている場合とを含むものとする。

10

【0102】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0103】

（実施の形態 4）

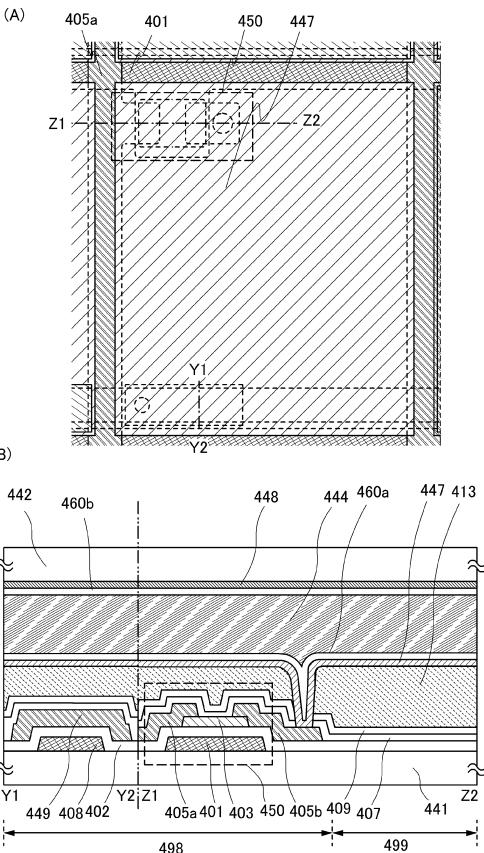

本実施の形態では、表示パネルの画素の平面図及び断面図の一例について図面を用いて説明する。なお本実施の形態でいう画素は、上記実施の形態 1 で説明した副画素に相当するものである。

【0104】

20

図 11 (A) は表示パネルにおける 1 画素分の画素の平面図を示している。図 11 (B) は図 11 (A) の線 Y1 - Y2、及び線 Z1 - Z2 における断面図である。

【0105】

図 11 (A) において、複数のソース配線層（ソース電極層 405a 又はドレイン電極層 405b を含む）が互いに平行（図中上下方向に延伸）かつ互いに離間した状態で配置されている。複数のゲート配線層（ゲート電極層 401 を含む）は、ソース配線層に概略直交する方向（図中左右方向）に延伸し、かつ互いに離間するように配置されている。容量配線層 408 は、複数のゲート配線層それぞれに隣接する位置に配置されており、ゲート配線層に概略平行な方向、つまり、ソース配線層に概略直交する方向（図中左右方向）に延伸している。

30

【0106】

図 11 (A)、図 11 (B) の液晶表示装置は、画素電極層として透明電極層 447 が形成されている。トランジスタ 450 上には絶縁膜 407、409、及び層間膜 413 が設けられ、絶縁膜 407、409、及び層間膜 413 に形成された開口（コンタクトホール）において、透明電極層 447 はトランジスタ 450 と電気的に接続されている。

【0107】

図 11 (B) に示すように、第 2 の基板 442 には共通電極層 448（対向電極層ともいう）が形成され、第 1 の基板 441 上の透明電極層 447 と、液晶層 444 を介して対向している。なお、図 11 (A)、図 11 (B) では、透明電極層 447 と液晶層 444 との間に配向膜 460a が設けられ、共通電極層 448 と液晶層 444 との間には配向膜 460b が設けられている。配向膜 460a、460b は、液晶の配向を制御する機能を有する絶縁層であり、液晶材料によっては設けなくてもよい。

40

【0108】

トランジスタ 450 は、ボトムゲート構造の逆スタガ型トランジスタの例であり、ゲート電極層 401、ゲート絶縁層 402、酸化物半導体層 403、ソース電極層 405a、及びドレイン電極層 405b を含む。また、ゲート電極層 401 と同工程で形成された容量配線層 408、ゲート絶縁層 402、及びソース電極層 405a 又はドレイン電極層 405b と同工程で形成された導電層 449 が積層し、容量を形成している。

【0109】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

50

である。

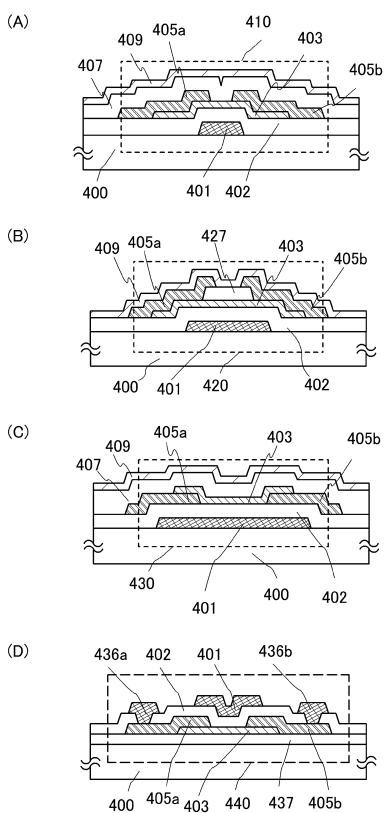

【0110】

(実施の形態5)

本実施の形態では、本明細書に開示する液晶表示装置に適用できるトランジスタの例を示す。本明細書に開示する液晶表示装置に適用できるトランジスタの構造は特に限定されず、例えばゲート電極が、ゲート絶縁層を介して、酸化物半導体層の上側に配置されるトップゲート構造、又はゲート電極が、ゲート絶縁層を介して、酸化物半導体層の下側に配置されるボトムゲート構造のスタガ型及びプレーナ型などを用いることができる。また、トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。また、チャネル領域の上下にゲート絶縁層を介して配置された2つのゲート電極層を有する、デュアルゲート型でもよい。なお、図12(A)乃至(D)にトランジスタの断面構造の一例を以下に示す。図12(A)乃至(D)に示すトランジスタは、半導体層として酸化物半導体を用いるものである。酸化物半導体を用いることのメリットは、トランジスタのオン状態において高い電界効果移動度(最大値で $5\text{ cm}^2/\text{V sec}$ 以上、好ましくは最大値で $10\text{ cm}^2/\text{V sec} \sim 150\text{ cm}^2/\text{V sec}$ )と、トランジスタのオフ状態において低い単位チャネル幅あたりのオフ電流(例えば単位チャネル幅あたりのオフ電流が $1\text{ aA}/\mu\text{m}$ 未満、さらに好ましくは $10\text{ zA}/\mu\text{m}$ 未満、且つ、85にて $100\text{ zA}/\mu\text{m}$ 未満)が得られることである。

10

【0111】

20

図12(A)に示すトランジスタ410は、ボトムゲート構造のトランジスタの一つであり、逆スタガ型トランジスタともいう。

【0112】

トランジスタ410は、絶縁表面を有する基板400上に、ゲート電極層401、ゲート絶縁層402、酸化物半導体層403、ソース電極層405a、及びドレイン電極層405bを含む。また、トランジスタ410を覆い、酸化物半導体層403に積層する絶縁膜407が設けられている。絶縁膜407上にはさらに保護絶縁層409が形成されている。

【0113】

30

図12(B)に示すトランジスタ420は、チャネル保護型(チャネルトップ型ともいう)と呼ばれるボトムゲート構造の一つであり逆スタガ型トランジスタともいう。

【0114】

トランジスタ420は、絶縁表面を有する基板400上に、ゲート電極層401、ゲート絶縁層402、酸化物半導体層403、酸化物半導体層403のチャネル形成領域を覆うチャネル保護層として機能する絶縁層427、ソース電極層405a、及びドレイン電極層405bを含む。また、トランジスタ420を覆い、保護絶縁層409が形成されている。

【0115】

図12(C)に示すトランジスタ430はボトムゲート型のトランジスタであり、絶縁表面を有する基板400上に、ゲート電極層401、ゲート絶縁層402、ソース電極層405a、ドレイン電極層405b、及び酸化物半導体層403を含む。また、トランジスタ430を覆い、酸化物半導体層403に接する絶縁膜407が設けられている。絶縁膜407上にはさらに保護絶縁層409が形成されている。

40

【0116】

トランジスタ430においては、ゲート絶縁層402は基板400及びゲート電極層401上に接して設けられ、ゲート絶縁層402上にソース電極層405a、ドレイン電極層405bが接して設けられている。そして、ゲート絶縁層402、及びソース電極層405a、ドレイン電極層405b上に酸化物半導体層403が設けられている。

【0117】

図12(D)に示すトランジスタ440は、トップゲート構造のトランジスタの一つであ

50

る。トランジスタ440は、絶縁表面を有する基板400上に、絶縁層437、酸化物半導体層403、ソース電極層405a、ドレイン電極層405b、ゲート絶縁層402、及びゲート電極層401を含み、ソース電極層405a、ドレイン電極層405bにそれぞれ配線層436a、配線層436bが接して設けられ電気的に接続している。

【0118】

本実施の形態では、上述のとおり、半導体層として酸化物半導体層403を用いる。酸化物半導体層403に用いる酸化物半導体としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O系酸化物半導体や、三元系金属酸化物であるIn-Ga-Zn-O系酸化物半導体、In-Sn-Zn-O系酸化物半導体、In-Al-Zn-O系酸化物半導体、Sn-Ga-Zn-O系酸化物半導体、Al-Ga-Zn-O系酸化物半導体、Sn-Al-Zn-O系酸化物半導体や、二元系金属酸化物であるIn-Zn-O系酸化物半導体、Sn-Zn-O系酸化物半導体、Al-Zn-O系酸化物半導体、Zn-Mg-O系酸化物半導体、Sn-Mg-O系酸化物半導体、In-Mg-O系酸化物半導体、In-Ga-O系酸化物半導体や、または単元系金属酸化物であるIn-O系酸化物半導体、Sn-O系酸化物半導体、Zn-O系酸化物半導体などを用いることができる。また、上記酸化物半導体にSiO<sub>2</sub>を含んでもよい。ここで、例えば、In-Ga-Zn-O系酸化物半導体とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物膜、という意味であり、その化学量論比はとくに問わない。また、InとGaとZn以外の元素を含んでもよい。

【0119】

また、酸化物半導体層403は、化学式InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。

【0120】

酸化物半導体層403を用いたトランジスタ410、420、430、440は、オフ状態における電流値(オフ電流値)を低くすることができる。よって画素において、画像信号等の電気信号を保持するための容量素子を小さく設計することができる。よって、画素の開口率の向上を図ることができると、その分の低消費電力化を図るといった効果を奏する。

【0121】

また、酸化物半導体層403を用いたトランジスタ410、420、430、440は、オフ電流を少なくすることができる。よって、画素においては画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。よって1フレーム期間の周期を長くすることができ、静止画表示期間でのリフレッシュ動作の頻度を少なくすることができるため、より消費電力を抑制する効果を高くできる。また、上記トランジスタは、同一基板上に駆動回路部または画素部に作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

【0122】

絶縁表面を有する基板400に使用することができる基板に大きな制限はないが、バリウムホウケイ酸ガラスやアルミニオホウケイ酸ガラスなどのガラス基板を用いる。

【0123】

ボトムゲート構造のトランジスタ410、420、430において、下地膜となる絶縁膜を基板とゲート電極層の間に設けてもよい。下地膜は、基板からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

【0124】

ゲート電極層401の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。

10

20

30

40

50

## 【0125】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。例えば、第1のゲート絶縁層としてプラズマCVD法により膜厚50nm以上200nm以下の窒化シリコン層( $\text{SiN}_y$  ( $y > 0$ ))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層( $\text{SiO}_x$  ( $x > 0$ ))を積層して、合計膜厚200nmのゲート絶縁層とする。

## 【0126】

10

ソース電極層405a、ドレイン電極層405bに用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜など)等を用いることができる。また、Al、Cuなどの金属膜の下側又は上側の一方または双方にTi、Mo、Wなどの高融点金属膜またはそれらの金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜)を積層させた構成としても良い。

## 【0127】

ソース電極層405a、ドレイン電極層405bに接続する配線層436a、配線層436bのような導電膜も、ソース電極層405a、ドレイン電極層405bと同様な材料を用いることができる。

20

## 【0128】

また、ソース電極層405a、ドレイン電極層405b(これと同じ層で形成される配線層を含む)となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $\text{In}_2\text{O}_3$ )、酸化スズ( $\text{SnO}_2$ )、酸化亜鉛( $\text{ZnO}$ )、酸化インジウム酸化スズ合金( $\text{In}_2\text{O}_3\text{--SnO}_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金( $\text{In}_2\text{O}_3\text{--ZnO}$ )またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

## 【0129】

酸化物半導体層の上方に設けられる絶縁膜407、427、下方に設けられる絶縁層437は、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの無機絶縁膜を用いることができる。

30

## 【0130】

また、酸化物半導体層の上方に設けられる保護絶縁層409は、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜を用いることができる。

## 【0131】

また、保護絶縁層409上にトランジスタ起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド、アクリル、ベンゾシクロブテン、等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(Low-k材料)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁膜を形成してもよい。

40

## 【0132】

このように、本実施の形態を用いて作製した酸化物半導体層を含むトランジスタは、オフ電流を少なくすることができる。よって、画素においては画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。よって1フレーム期間の周期を長くすることができ、静止画表示期間でのリフレッシュ動作の頻度を少なくすることができるため、より消費電力を抑制する効果を高くできる。また酸化物半導体層は、レーザ照射等の処理を経ることなく作製でき、大面積基板へのトランジスタの形成を可能にすることができるため、好適である。

## 【0133】

50

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0134】

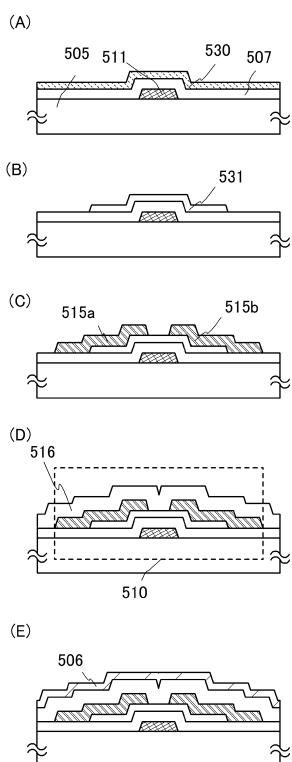

(実施の形態6)

本実施の形態は、酸化物半導体層を含むトランジスタ、及び作製方法の一例について、図13を用いて詳細に説明する。上記実施の形態と同一部分又は同様な機能を有する部分、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0135】

図13(A)乃至(E)にトランジスタの断面構造の一例を示す。図13(A)乃至(E)に示すトランジスタ510は、図12(A)に示すトランジスタ410と同様なボトムゲート構造の逆スタガ型トランジスタである。

10

【0136】

以下、図13(A)乃至(E)を用い、基板505上にトランジスタ510を作製する工程を説明する。

【0137】

まず、絶縁表面を有する基板505上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層511を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

20

【0138】

絶縁表面を有する基板505は、実施の形態4に示した基板400と同様な基板を用いることができる。本実施の形態では基板505としてガラス基板を用いる。

【0139】

下地膜となる絶縁膜を基板505とゲート電極層511との間に設けてもよい。下地膜は、基板505からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

30

【0140】

また、ゲート電極層511の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

【0141】

次いで、ゲート電極層511上にゲート絶縁層507を形成する。ゲート絶縁層507は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。

40

【0142】

本実施の形態の酸化物半導体は、不純物を除去され、I型化又は実質的にI型化された酸化物半導体を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、酸化物半導体層とゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。

【0143】

例えば、μ波(例えば周波数2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができますからである。

【0144】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理

50

によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であること、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

【0145】

また、ゲート絶縁層507、酸化物半導体膜530に水素、水酸基及び水分がなるべく含まれないようにするために、酸化物半導体膜530の成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層511が形成された基板505、又はゲート絶縁層507までが形成された基板505を予備加熱し、基板505に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、絶縁層516の成膜前に、ソース電極層515a及びドレイン電極層515bまで形成した基板505にも同様に行ってもよい。10

【0146】

次いで、ゲート絶縁層507上に、膜厚2nm以上200nm以下、好ましくは5nm以上30nm以下の酸化物半導体膜530を形成する(図13(A)参照。)。

【0147】

なお、酸化物半導体膜530をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層507の表面に付着している粉状物質(パーティクル、ごみともいう)を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。20

【0148】

酸化物半導体膜530に用いる酸化物半導体は、実施の形態5に示した酸化物半導体を用いることができる。また、上記酸化物半導体にSiO<sub>2</sub>を含んでもよい。本実施の形態では、酸化物半導体膜530をIn-Ga-Zn-O系酸化物ターゲットを用いてスパッタリング法により成膜する。この段階での断面図が図13(A)に相当する。また、酸化物半導体膜530は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下においてスパッタ法により形成することができる。

【0149】

酸化物半導体膜530をスパッタリング法で作製するためのターゲットとしては、例えば、組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol数比]の酸化物ターゲットを用い、In-Ga-Zn-O膜を成膜する。また、このターゲットの材料及び組成に限定されず、例えば、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 2 [mol数比]の酸化物ターゲットを用いてもよい。30

【0150】

また、酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とすることができます。

【0151】

酸化物半導体膜530を成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。40

【0152】

減圧状態に保持された成膜室内に基板を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板505上に酸化物半導体膜530を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好50

ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水( $H_2O$ )など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

【0153】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ごみともいう)が軽減でき、膜厚分布も均一となるために好ましい。

【0154】

次いで、酸化物半導体膜530を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

10

【0155】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体膜530の加工時に同時に行うことができる。

【0156】

なお、ここで酸化物半導体膜530のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。例えば、酸化物半導体膜530のウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N(関東化学社製)を用いてもよい。

20

【0157】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、または400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層531を得る(図13(B)参照。)。

【0158】

30

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

40

【0159】

例えば、第1の加熱処理として、650~700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。

【0160】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.9999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

50

## 【0161】

また、第1の加熱処理で酸化物半導体層を加熱した後、その温度を維持しながら又はその加熱温度から降温する過程で、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア（露点が-40以下、好ましくは-60以下）を導入してもよい。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N以上好ましくは7N以上（即ち、酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。酸素ガス又はN<sub>2</sub>Oガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型（真性）化する。

## 【0162】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜530に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

## 【0163】

なお、第1の加熱処理は、上記以外にも、酸化物半導体層成膜後であれば、酸化物半導体層上にソース電極層及びドレイン電極層を積層させた後、あるいは、ソース電極層及びドレイン電極層上に絶縁層を形成した後、のいずれで行っても良い。

## 【0164】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体膜530に第1の加熱処理を行う前でも行った後でもよい。

## 【0165】

また、酸化物半導体層を2回に分けて成膜し、2回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域（単結晶領域）、即ち、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3nm以上15nm以下の第1の酸化物半導体膜を成膜し、窒素、酸素、希ガス、または乾燥空気の雰囲気下で450以上850以下、好ましくは550以上750以下の第1の加熱処理を行い、表面を含む領域に結晶領域（板状結晶を含む）を有する第1の酸化物半導体膜を形成する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、450以上850以下、好ましくは600以上700以下の第2の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体膜の全体を結晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

## 【0166】

次いで、ゲート絶縁層507、及び酸化物半導体層531上に、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる導電膜を形成する。ソース電極層、及びドレイン電極層に用いる導電膜としては、実施の形態5に示したソース電極層405a、ドレイン電極層405bに用いる材料を用いることができる。

## 【0167】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層515a、ドレイン電極層515bを形成した後、レジストマスクを除去する（図13（C）参照。）。

## 【0168】

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いるとよい。酸化物半導体層531上で向かい合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet light）を用いて第3のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。

10

20

30

40

50

とよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化できる。

#### 【0169】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

10

#### 【0170】

なお、導電膜のエッチングの際に、酸化物半導体層531がエッチングされ、分断することのないようエッチング条件を最適化することが望まれる。しかしながら、導電膜のみをエッチングし、酸化物半導体層531を全くエッチングしないという条件を得ることは難しく、導電膜のエッチングの際に酸化物半導体層531は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。

#### 【0171】

次いで、N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理を行い、露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる絶縁層516を形成する。

20

#### 【0172】

絶縁層516は、少なくとも1nm以上の膜厚とし、スパッタ法など、絶縁層516に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。絶縁層516に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化(N型化)してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁層516はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

30

#### 【0173】

本実施の形態では、絶縁層516として膜厚200nmの酸化シリコン膜をスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化シリコン膜のスパッタ法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下において行うことができる。また、ターゲットとして酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素を含む雰囲気下でスパッタ法により酸化シリコン膜を形成することができる。酸化物半導体層に接して形成する絶縁層516は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

40

#### 【0174】

酸化物半導体膜530の成膜時と同様に、絶縁層516の成膜室内の残留水分を除去するためには、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて排気した成膜室で成膜した絶縁層516に含まれる不純物の濃度を低減できる。また、絶縁層516の成膜室内の残留水分を除去するための排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。

#### 【0175】

絶縁層516を成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの

50

不純物が除去された高純度ガスを用いることが好ましい。

【0176】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理（好ましくは200以上400以下、例えば250以上350以下）を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部（チャネル形成領域）が絶縁層516と接した状態で加熱される。

【0177】

以上の工程を経ることによって、酸化物半導体膜に対して第1の加熱処理を行って水素、水分、水酸基又は水素化物（水素化合物ともいう）などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料の一つである酸素を第2の加熱処理によって供給することができる。よって、酸化物半導体層は高純度化及び電気的にI型（真性）化する。なお高純度化された酸化物半導体膜中の水素濃度は $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、望ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より望ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下となる。なお、上述の酸化物半導体膜中の水素濃度は、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectroscopy）で測定されるものである。

10

【0178】

以上の工程でトランジスタ510が形成される（図13（D）参照。）。

【0179】

20

また、絶縁層516に欠陥を多く含む酸化シリコン層を用いると、酸化シリコン層形成後の加熱処理によって酸化物半導体層中に含まれる水素、水分、水酸基又は水素化物などの不純物を絶縁層516に拡散させ、酸化物半導体層中に含まれる該不純物をより低減させる効果を奏する。

【0180】

絶縁層516上にさらに保護絶縁層506を形成してもよい。例えば、RFスパッタ法を用いて窒化シリコン膜を形成する。RFスパッタ法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜などを用いる。本実施の形態では、保護絶縁層506を、窒化シリコン膜を用いて形成する（図13（E）参照。）。

30

【0181】

本実施の形態では、保護絶縁層506として、絶縁層516まで形成された基板505を100～400の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜する。この場合においても、絶縁層516と同様に、処理室内の残留水分を除去しつつ保護絶縁層506を成膜することが好ましい。

【0182】

保護絶縁層の形成後、さらに大気中、100以上200以下、1時間以上30時間以下での加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。

40

【0183】

このように、本実施の形態を用いて作製した高純度化された酸化物半導体層を含むトランジスタは、オフ電流を少なくすることができます。よって、画素においては画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。よって1フレーム期間の周期を長くすることができ、静止画表示期間でのリフレッシュ動作の頻度を少なくすることができるため、より消費電力を抑制する効果を高くできる。また、高純度化された酸化物半導体層は、レーザ照射等の処理を経ることなく作製でき、大面積基板へのトランジスタの形成を可能にすることができるため、好適である。

50

**【 0 1 8 4 】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

**【 0 1 8 5 】****( 実施の形態 7 )**

本明細書に開示する液晶表示装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態で説明した液晶表示装置を具備する電子機器の例について説明する。

10

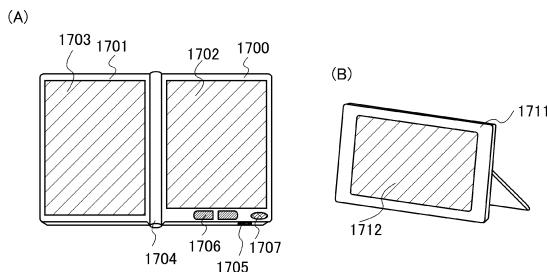

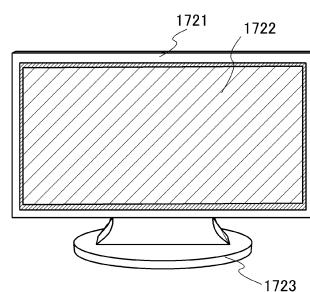

**【 0 1 8 6 】**

図14（A）は、電子書籍の一例を示している。図14（A）に示す電子書籍は、筐体1700及び筐体1701の2つの筐体で構成されている。筐体1700及び筐体1701は、蝶番1704により一体になっており、開閉動作を行うことができる。このような構成により、書籍のような動作を行うことが可能となる。

**【 0 1 8 7 】**

筐体1700には表示部1702が組み込まれ、筐体1701には表示部1703が組み込まれている。表示部1702及び表示部1703は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部（図14（A）では表示部1702）に文章を表示し、左側の表示部（図14（A）では表示部1703）に画像を表示することができる。

20

**【 0 1 8 8 】**

また、図14（A）では、筐体1700に操作部等を備えた例を示している。例えば、筐体1700は、電源入力端子1705、操作キー1706、スピーカ1707等を備えている。操作キー1706により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングディバイス等を備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB端子、及びUSBケーブル等の各種ケーブルと接続可能な端子等）、記録媒体挿入部等を備える構成としてもよい。さらに、図14（A）に示す電子書籍は、電子辞書としての機能を持たせた構成としてもよい。

30

**【 0 1 8 9 】**

図14（B）は、液晶表示装置を用いたデジタルフォトフレームの一例を示している。例えば、図14（B）に示すデジタルフォトフレームは、筐体1711に表示部1712が組み込まれている。表示部1712は、各種画像を表示することができる、例えば、デジタルカメラ等で撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

**【 0 1 9 0 】**

なお、図14（B）に示すデジタルフォトフレームは、操作部、外部接続用端子（USB端子、USBケーブル等の各種ケーブルと接続可能な端子等）、記録媒体挿入部等を備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部1712に表示させることができる。

40

**【 0 1 9 1 】**

図14（C）は、液晶表示装置を用いたテレビジョン装置の一例を示している。図14（C）に示すテレビジョン装置は、筐体1721に表示部1722が組み込まれている。表示部1722により、映像を表示することができる。また、ここでは、スタンド1723により筐体1721を支持した構成を示している。表示部1722は、上記実施の形態に示した液晶表示装置を適用することができる。

50

## 【0192】

図14(C)に示すテレビジョン装置の操作は、筐体1721が備える操作スイッチや、別体のリモコン操作機により行うことができる。リモコン操作機が備える操作キーにより、チャンネルや音量の操作を行うことができ、表示部1722に表示される映像を操作することができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

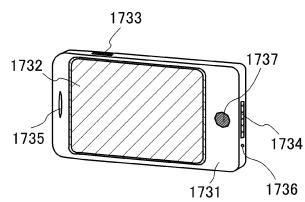

## 【0193】

図14(D)は、液晶表示装置を用いた携帯電話機の一例を示している。図14(D)に示す携帯電話機は、筐体1731に組み込まれた表示部1732の他、操作ボタン1733、操作ボタン1737、外部接続ポート1734、スピーカ1735、及びマイク1736等を備えている。

10

## 【0194】

図14(D)に示す携帯電話機は、表示部1732がタッチパネルになっており、指等の接触により、表示部1732の表示内容を操作することができる。また、電話の発信、或いはメールの作成等は、表示部1732を指等で接触することにより行うことができる。

## 【0195】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【0196】

## (実施の形態8)

20

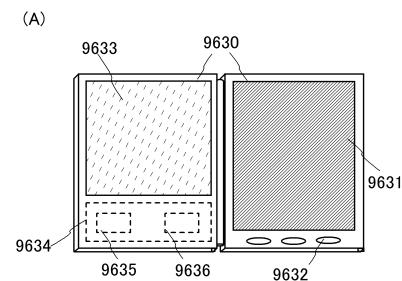

本実施の形態においては、上記実施の形態7で説明した電子書籍の構成について、具体例を示し説明する。

## 【0197】

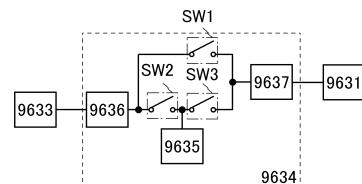

図15(A)に示す電子書籍(E-bookともいう)は、筐体9630、表示部9631、操作キー9632、太陽電池9633、充放電制御回路9634を有する。図15(A)に示した電子書籍は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。なお、図15(A)では充放電制御回路9634の一例としてバッテリー9635、DCDCコンバータ(以下、コンバータ9636と略記)を有する構成について示している。

30

## 【0198】

図15(A)に示す構成とすることにより、太陽電池9633による発電、及びバッテリー9635での充電を効率よく行うことができ、好適である。なお太陽電池9633を筐体9630の表面及び裏面に設けることで、より効率的にバッテリー9635の充電を行う構成とすることができる。なおバッテリー9635としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

## 【0199】

また図15(A)に示す充放電制御回路9634の構成、及び動作について図15(B)にブロック図を示し説明する。図15(B)には、太陽電池9633、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3、表示部9631について示しており、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3が充放電制御回路9634に対応する箇所となる。

40

## 【0200】

まず外光により太陽電池9633により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー9635を充電するための電圧となるようコンバータ9636で昇圧または降圧がなされる。そして、表示部9631の動作に太陽電池9633からの電力が用いられる際にはスイッチSW1をオンにし、コンバータ9637で表示部9631に必要な電圧に昇圧または降圧をすることとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2、3をオンにしてバッテリー96

50

35の充電を行う構成とすればよい。

【0201】

次いで外光により太陽電池9633により発電がされない場合の動作の例について説明する。バッテリー9635に蓄電された電力は、スイッチSW3をオンにすることでコンバータ9637により昇圧または降圧がなされる。そして、表示部9631の動作にバッテリー9635からの電力が用いられることとなる。

【0202】

なお太陽電池9633については、充電手段の一例として示したが、他の手段によるバッテリー9635の充電を行う構成であってもよい。また他の充電手段を組み合わせて行う構成としてもよい。

10

【0203】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【実施例1】

【0204】

本実施例では、特性評価用回路によるリーク電流測定を用いた、トランジスタの一例のオフ電流の値の算出例について以下に説明する。

【0205】

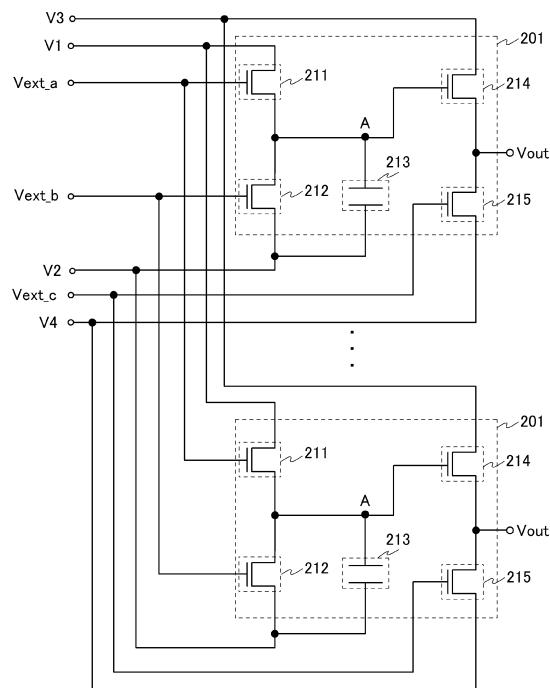

まず、特性評価用回路の構成について、図16を用いて説明する。図16は、特性評価用回路の構成を示す回路図である。

20

【0206】

図16に示す特性評価用回路は、複数の測定系201を備える。複数の測定系201は、互いに並列に接続される。ここでは、一例として8個の測定系201が並列に接続される構成とする。

【0207】

測定系201は、トランジスタ211と、トランジスタ212と、容量素子213と、トランジスタ214と、トランジスタ215と、を含む。

【0208】

トランジスタ211の第1端子には、電圧V1が入力され、トランジスタ211のゲートには、電圧Vext\_aが入力される。トランジスタ211は、電荷注入用のトランジスタである。

30

【0209】

トランジスタ212の第1端子は、トランジスタ211の第2端子に接続され、トランジスタ212の第2端子には、電圧V2が入力され、トランジスタ212のゲートには、電圧Vext\_bが入力される。トランジスタ212は、リーク電流評価用のトランジスタである。なお、ここでのリーク電流とは、トランジスタのオフ電流を含むリーク電流である。

【0210】

容量素子213の第1の電極は、トランジスタ211の第2端子に接続され、容量素子213の第2の電極には、電圧V2が入力される。ここでは、電圧V2として0Vが入力される。

40

【0211】

トランジスタ214の第1端子には、電圧V3が入力され、トランジスタ214のゲートは、トランジスタ211の第2端子に接続される。なお、トランジスタ214のゲートと、トランジスタ211の第2端子、トランジスタ212の第1端子、並びに容量素子213の第1の電極との接続箇所をノードAともいう。

【0212】

トランジスタ215の第1端子は、トランジスタ214の第2端子に接続され、トランジスタ215の第2端子には、電圧V4が入力され、トランジスタ215のゲートには、電圧Vext\_cが入力される。なお、ここでは、電圧Vext\_cとして0.5Vが入力

50

される。

【0213】

さらに、測定系201は、トランジスタ214の第2端子と、トランジスタ215の第1端子との接続箇所の電圧を出力電圧 $V_{out}$ として出力する。

【0214】

ここでは、トランジスタ211の一例として、酸化物半導体層を含み、チャネル長 $L = 10 \mu m$ 、チャネル幅 $W = 10 \mu m$ のトランジスタを用いる。また、トランジスタ214及びトランジスタ215の一例として、酸化物半導体層を含み、チャネル長 $L = 3 \mu m$ 、チャネル幅 $W = 100 \mu m$ のトランジスタを用いる。また、トランジスタ212の一例として、酸化物半導体層を含み、酸化物半導体層の上部にソース電極及びドレイン電極が接し、ソース電極及びドレイン電極と、ゲート電極とのオーバーラップ領域を設けず、幅1 $\mu m$ のオフセット領域を有するボトムゲート構造のトランジスタを用いる。オフセット領域を設けることにより、寄生容量を低減することができる。さらにトランジスタ212としては、チャネル長 $L$ 及びチャネル幅 $W$ の異なる6条件のトランジスタを用いる(表1参照)。

【0215】

【表1】

|     | チャネル長 $L[\mu m]$ | チャネル幅 $W[\mu m]$ |

|-----|------------------|------------------|

| 条件1 | 1.5              | $1 \times 10^5$  |

| 条件2 | 3                | $1 \times 10^5$  |

| 条件3 | 10               | $1 \times 10^5$  |

| 条件4 | 1.5              | $1 \times 10^6$  |

| 条件5 | 3                | $1 \times 10^6$  |

| 条件6 | 10               | $1 \times 10^6$  |

【0216】

図16に示すように、電荷注入用のトランジスタと、リーク電流評価用のトランジスタとを別々に設けることにより、電荷注入の際に、リーク電流評価用のトランジスタを常にオフ状態に保つことができる。電荷注入用のトランジスタを設けない場合には、電荷注入の際に、リーク電流評価用トランジスタを一度オン状態にする必要があるが、オン状態からオフ状態の定常状態に到るまでに時間を要するような素子では、測定に時間を要してしまう。

【0217】

また、電荷注入用のトランジスタと、リーク電流評価用のトランジスタとを別々に設けることにより、それぞれのトランジスタを適切なサイズとすることができる。また、リーク電流評価用トランジスタのチャネル幅 $W$ を、電荷注入用のトランジスタのチャネル幅 $W$ よりも大きくすることにより、リーク電流評価用トランジスタ以外の特性評価回路のリーク電流成分を相対的に小さくすることができる。その結果、リーク電流評価用トランジスタのリーク電流を高い精度で測定することができる。同時に、電荷注入の際に、リーク電流評価用トランジスタを一度オン状態とする必要がないため、チャネル形成領域の電荷の一部がノードAに流れ込むことによるノードAの電圧変動の影響もない。

【0218】

一方、電荷注入用トランジスタのチャネル幅 $W$ を、リーク電流評価用トランジスタのチャネル幅 $W$ よりも小さくすることにより、電荷注入用トランジスタのリーク電流を相対的に小さくすることができる。また、電荷注入の際に、チャネル形成領域の電荷の一部がノードAに流れ込むことによるノードAの電圧変動の影響も小さい。

【0219】

また、図16に示すように、複数の測定系を並列接続させた構造にすることにより、より正確に特性評価回路のリーク電流を算出することができる。

10

20

30

40

50

## 【0220】

次に、図16に示す特性評価回路を用いた、本実施例のトランジスタの一例のオフ電流の値の算出方法について説明する。

## 【0221】

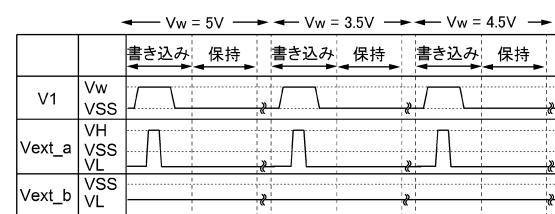

まず、図16に示す特性評価回路のリーク電流測定方法について、図17を用いて説明する。図17は、図16に示す特性評価回路を用いたリーク電流測定方法を説明するためのタイミングチャートである。

## 【0222】

図16に示す特性評価回路を用いたリーク電流測定方法は、書き込み期間及び保持期間に分けられる。それぞれの期間における動作について、以下に説明する。

10

## 【0223】

まず、書き込み期間において、電圧  $V_{ext\_b}$  として、トランジスタ212がオフ状態となるような電圧  $V_L$  (-3V) を入力する。また、電圧  $V_1$  として、書き込み電圧  $V_w$  を入力した後、電圧  $V_{ext\_a}$  として、一定期間トランジスタ211がオン状態となるような電圧  $V_H$  (5V) を入力する。これによって、ノードAに電荷が蓄積され、ノードAの電圧は、書き込み電圧  $V_w$  と同等の値になる。その後、電圧  $V_{ext\_a}$  として、トランジスタ211がオフ状態となるような電圧  $V_L$  を入力する。その後、電圧  $V_1$  として、電圧  $V_{SS}$  (0V) を入力する。

## 【0224】

その後、保持期間において、ノードAが保持する電荷量の変化に起因して生じるノードAの電圧の変化量の測定を行う。電圧の変化量から、トランジスタ212のソース電極とドレイン電極との間を流れる電流値を算出することができる。以上により、ノードAの電荷の蓄積とノードAの電圧の変化量の測定とを行うことができる。

20

## 【0225】

このとき、ノードAの電荷の蓄積及びノードAの電圧の変化量の測定（蓄積及び測定動作ともいう）を繰り返し行う。まず、第1の蓄積及び測定動作を15回繰り返し行う。第1の蓄積及び測定動作では、書き込み期間に書き込み電圧  $V_w$  として5Vの電圧を入力し、保持期間に1時間の保持を行う。次に、第2の蓄積及び測定動作を2回繰り返し行う。第2の蓄積及び測定動作では、書き込み期間に書き込み電圧  $V_w$  として3.5Vの電圧を入力し、保持期間に50時間の保持を行う。次に、第3の蓄積及び測定動作を1回行う。第3の蓄積及び測定動作では、書き込み期間に書き込み電圧  $V_w$  として4.5Vの電圧を入力し、保持期間に10時間の保持を行う。蓄積及び測定動作を繰り返し行うことにより、測定した電流値が、定常状態における値であることを確認することができる。言い換えると、ノードAを流れる電流  $I_A$  のうち、過渡電流（測定開始後から時間経過とともに減少していく電流成分）を除くことができる。その結果、より高い精度でリーク電流を測定することができる。

30

## 【0226】

一般に、ノードAの電圧  $V_A$  は、出力電圧  $V_{out}$  の関数として式(1)のように表すことができる。

## 【0227】

## 【数1】

40

$$V_A = F(V_{out}) \quad \cdots (1)$$

## 【0228】

また、ノードAの電荷  $Q_A$  は、ノードAの電圧  $V_A$  、ノードAに接続される容量  $C_A$  、定数 (const) を用いて、式(2)のように表される。ここで、ノードAに接続される容量  $C_A$  は、容量素子213の容量と容量素子213以外の容量成分の和である。

## 【0229】

## 【数2】

$$Q_A = C_A V_A + const \quad \dots(2)$$

## 【0230】

ノードAの電流  $I_A$  は、ノードAに流れ込む電荷（またはノードAから流れ出る電荷）の時間微分であるから、ノードAの電流  $I_A$  は式(3)のように表現される。

## 【0231】

## 【数3】

$$I_A \equiv \frac{\Delta Q_A}{\Delta t} = \frac{C_A \cdot \Delta F(V_{out})}{\Delta t} \quad \dots(3)$$

10

## 【0232】

なお、ここでは、一例として、 $t$ を約54000secとする。このように、ノードAに接続される容量  $C_A$  と、出力電圧  $V_{out}$  から、ノードAの電流  $I_A$  を求めることができたため、特性評価回路のリーク電流を求めることができる。

## 【0233】

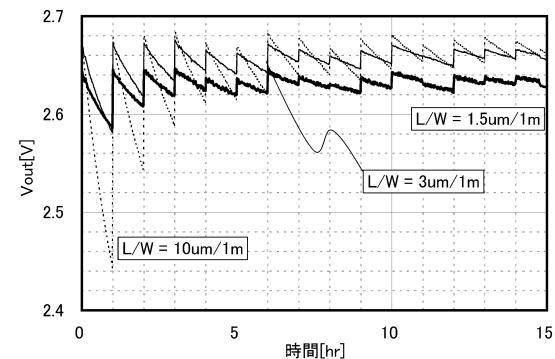

次に、上記特性評価回路を用いた測定方法による出力電圧の測定結果及び該測定結果より算出した特性評価回路のリーク電流の値を示す。

## 【0234】

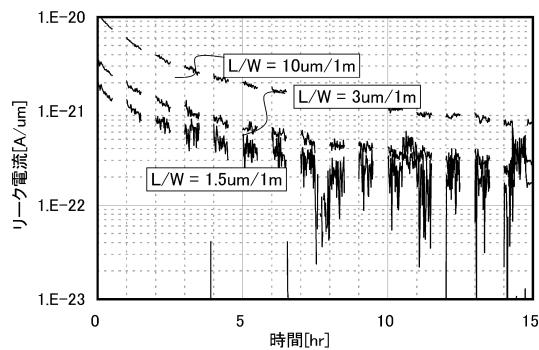

図18に、一例として、条件1、条件2及び条件3における上記測定（第1の蓄積及び測定動作）に係る経過時間  $Time$  と、出力電圧  $V_{out}$  との関係を示す。図19に、上記測定に係る経過時間  $Time$  と、該測定によって算出されたリーク電流との関係を示す。測定開始後から出力電圧  $V_{out}$  が変動しており、定常状態に到るためには10時間以上必要であることがわかる。

20

## 【0235】

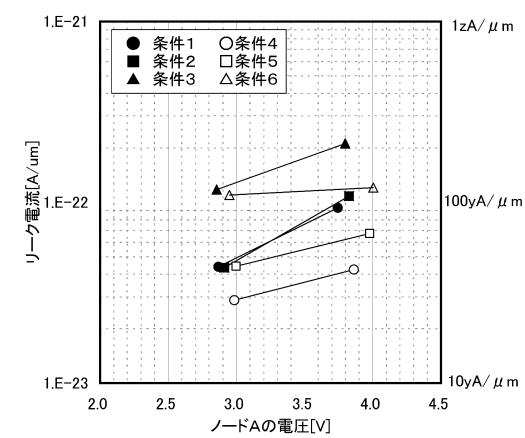

また、図20に、上記測定により見積もられた条件1乃至条件6におけるノードAの電圧とリーク電流の関係を示す。図20では、例えば条件4において、ノードAの電圧が3.0Vの場合、リーク電流は28yA/ $\mu$ mである。リーク電流にはトランジスタ212のオフ電流も含まれるため、トランジスタ212のオフ電流も28yA/ $\mu$ m以下とみなすことができる。

30

## 【0236】

以上のように、チャネル形成層としての機能を有し、高純度化された酸化物半導体層を含むトランジスタを用いた特性評価用回路において、リーク電流が十分に低いため、該トランジスタのオフ電流が十分に小さいことがわかる。

## 【符号の説明】

## 【0237】

|     |         |

|-----|---------|

| 101 | バックライト部 |

| 102 | 表示パネル   |

| 103 | 偏光板     |

| 104 | 偏光板     |

| 106 | 拡散板     |

| 107 | 画素部     |

| 108 | 走査線駆動回路 |

| 109 | 信号線駆動回路 |

| 110 | 画素      |

| 111 | 副画素     |

| 112 | FPC     |

| 113 | 外部基板    |

| 115 | 回路部     |

| 120 | 液晶表示装置  |

40

50

|       |         |    |

|-------|---------|----|

| 1 2 1 | 表示切替回路  |    |

| 1 2 2 | 表示制御回路  |    |

| 1 2 3 | バックライト部 |    |

| 1 2 4 | 表示パネル   |    |

| 1 2 5 | 画像信号供給源 |    |

| 1 4 3 | 書き込み期間  |    |

| 1 4 4 | 保持期間    |    |

| 2 0 1 | 測定系     |    |

| 2 1 1 | トランジスタ  | 10 |

| 2 1 2 | トランジスタ  |    |

| 2 1 3 | 容量素子    |    |

| 2 1 4 | トランジスタ  |    |

| 2 1 5 | トランジスタ  |    |

| 3 0 0 | 外部切替手段  |    |

| 3 0 1 | 記憶回路    |    |

| 3 0 2 | 比較回路    |    |

| 3 0 3 | 選択回路    |    |

| 3 1 1 | 画素部     |    |

| 3 1 2 | 駆動回路    |    |

| 3 1 3 | 副画素     | 20 |

| 3 2 2 | バックライト  |    |

| 4 0 0 | 基板      |    |

| 4 0 1 | ゲート電極層  |    |

| 4 0 2 | ゲート絶縁層  |    |

| 4 0 3 | 酸化物半導体層 |    |

| 4 0 7 | 絶縁膜     |    |

| 4 0 8 | 容量配線層   |    |

| 4 0 9 | 保護絶縁層   |    |

| 4 1 0 | トランジスタ  |    |

| 4 1 3 | 層間膜     | 30 |

| 4 2 0 | トランジスタ  |    |

| 4 2 7 | 絶縁層     |    |

| 4 3 0 | トランジスタ  |    |

| 4 3 7 | 絶縁層     |    |

| 4 4 0 | トランジスタ  |    |

| 4 4 1 | 基板      |    |

| 4 4 2 | 基板      |    |

| 4 4 4 | 液晶層     |    |

| 4 4 7 | 透明電極層   |    |

| 4 4 8 | 共通電極層   | 40 |

| 4 4 9 | 導電層     |    |

| 4 5 0 | トランジスタ  |    |

| 5 0 5 | 基板      |    |

| 5 0 6 | 保護絶縁層   |    |

| 5 0 7 | ゲート絶縁層  |    |

| 5 1 0 | トランジスタ  |    |

| 5 1 1 | ゲート電極層  |    |

| 5 1 6 | 絶縁層     |    |

| 5 3 0 | 酸化物半導体膜 |    |

| 5 3 1 | 酸化物半導体層 | 50 |

|         |                |    |

|---------|----------------|----|

| 6 0 1   | 画素部            |    |

| 6 0 2   | 走査線            |    |

| 6 0 3   | 信号線            |    |

| 6 0 6   | 走査線側駆動回路       |    |

| 6 0 7   | 信号線側駆動回路       |    |

| 6 1 0   | 副画素            |    |

| 6 1 2   | 画素トランジスタ       |    |

| 6 1 3   | 液晶素子           |    |

| 6 1 4   | 容量素子           |    |

| 6 1 8   | 共通電極           | 10 |

| 6 1 9   | 容量線            |    |

| 7 1 0   | 画像信号変換回路       |    |

| 7 1 1   | 表示制御切替回路       |    |

| 7 1 2   | 動画表示制御回路       |    |

| 7 1 3   | 静止画表示制御回路      |    |

| 7 1 4   | 動画タイミング信号生成回路  |    |

| 7 1 5   | 動画バックライト制御回路   |    |

| 7 1 6   | 静止画タイミング信号生成回路 |    |

| 7 1 7   | 静止画バックライト制御回路  |    |

| 8 0 1   | 期間             | 20 |

| 8 0 2   | 期間             |    |

| 8 3 0   | 画素部            |    |

| 8 3 1   | 表示画像           |    |

| 8 4 0   | バックライト         |    |

| 9 1 1   | 表示画像           |    |

| 9 1 2   | 表示画像           |    |

| 9 1 3   | 表示画像           |    |

| 1 0 5 B | 光源             |    |

| 1 0 5 R | 光源             |    |

| 1 0 5 G | 光源             | 30 |

| 1 0 5 W | 光源             |    |

| 1 0 5 Y | 光源             |    |

| 1 1 1 B | 副画素            |    |

| 1 1 1 G | 副画素            |    |

| 1 1 1 R | 副画素            |    |

| 1 1 1 W | 副画素            |    |

| 1 1 1 Y | 副画素            |    |

| 1 1 4 B | 光透過部           |    |

| 1 1 4 G | 光透過部           |    |

| 1 1 4 R | 光透過部           | 40 |

| 1 1 4 W | 光透過部           |    |

| 1 1 4 Y | 光透過部           |    |

| 1 7 0 0 | 筐体             |    |

| 1 7 0 1 | 筐体             |    |

| 1 7 0 2 | 表示部            |    |

| 1 7 0 3 | 表示部            |    |

| 1 7 0 4 | 蝶番             |    |

| 1 7 0 5 | 電源入力端子         |    |

| 1 7 0 6 | 操作キー           |    |

| 1 7 0 7 | スピーカ           | 50 |

|         |         |    |

|---------|---------|----|

| 1 7 1 1 | 筐体      |    |

| 1 7 1 2 | 表示部     |    |

| 1 7 2 1 | 筐体      |    |

| 1 7 2 2 | 表示部     |    |

| 1 7 2 3 | スタンド    |    |

| 1 7 3 1 | 筐体      |    |

| 1 7 3 2 | 表示部     |    |

| 1 7 3 3 | 操作ボタン   |    |

| 1 7 3 4 | 外部接続ポート |    |

| 1 7 3 5 | スピーカ    | 10 |

| 1 7 3 6 | マイク     |    |

| 1 7 3 7 | 操作ボタン   |    |

| 4 0 5 a | ソース電極層  |    |

| 4 0 5 b | ドレイン電極層 |    |

| 4 3 6 a | 配線層     |    |

| 4 3 6 b | 配線層     |    |

| 4 6 0 a | 配向膜     |    |

| 4 6 0 b | 配向膜     |    |

| 5 1 5 a | ソース電極層  |    |

| 5 1 5 b | ドレイン電極層 | 20 |

| 9 6 3 0 | 筐体      |    |

| 9 6 3 1 | 表示部     |    |

| 9 6 3 2 | 操作キー    |    |

| 9 6 3 3 | 太陽電池    |    |

| 9 6 3 4 | 充放電制御回路 |    |

| 9 6 3 5 | バッテリー   |    |

| 9 6 3 6 | コンバータ   |    |

| 9 6 3 7 | コンバータ   |    |

【図1】

(B)

(c)

【図2】

〔 3 〕

〔 4 〕

【 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

(C)

(D)

【図15】

(B)

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(51)Int.Cl.

| F I     |       |         |

|---------|-------|---------|

| G 0 9 G | 3/34  | J       |

| G 0 9 G | 3/20  | 6 4 2 E |

| G 0 9 G | 3/20  | 6 1 1 A |

| G 0 9 G | 3/20  | 6 1 1 G |

| G 0 9 G | 3/20  | 6 5 0 J |

| G 0 9 G | 3/20  | 6 1 2 U |

| G 0 2 F | 1/133 | 5 3 5   |

| G 0 2 F | 1/133 | 5 1 0   |

| G 0 2 F | 1/133 | 5 5 0   |

(56)参考文献 特開2010-021039(JP, A)

特開2007-114274(JP, A)

特開2003-271106(JP, A)

特開2001-312253(JP, A)

特開2008-209828(JP, A)

特開2003-044011(JP, A)

特開2009-141002(JP, A)

特開2007-194594(JP, A)

特開2002-207462(JP, A)

特開2009-135468(JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |           |   |         |

|---------|-----------|---|---------|

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8 |

| G 0 2 F | 1 / 1 3 3 |   |         |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示设备和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP6138310B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2017-05-31 |

| 申请号            | JP2016063113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2016-03-28 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 山崎舜平<br>小山潤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 山崎 舜平<br>小山 潤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G09G3/34 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G02F1/133603 G09G3/006 G09G3/3413 G09G3/3426 G09G3/3607 G09G2300/0452 G09G2320/0261<br>G09G2320/062 G09G2320/0646 G09G2320/066 G09G2320/0666 G09G2320/103 G09G2330/021<br>G09G2340/06 G09G2360/16 G09G2380/14 H01L27/12 H01L27/1225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/36 G09G3/20.642.K G09G3/20.660.V G09G3/20.660.U G09G3/20.621.K G09G3/34.J G09G3<br>/20.642.E G09G3/20.611.A G09G3/20.611.G G09G3/20.650.J G09G3/20.612.U G02F1/133.535 G02F1<br>/133.510 G02F1/133.550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZD17 2H193/ZF44 2H193/ZG03 2H193/ZG14 2H193/ZG28 2H193/ZG44 2H193<br>/ZG48 5C006/AA02 5C006/AA16 5C006/AA22 5C006/AF03 5C006/AF04 5C006/AF19 5C006/AF23<br>5C006/AF42 5C006/AF43 5C006/AF44 5C006/AF45 5C006/AF51 5C006/AF52 5C006/AF53 5C006<br>/AF68 5C006/AF69 5C006/AF72 5C006/AF81 5C006/AF84 5C006/AF85 5C006/BB16 5C006/BB29<br>5C006/BC20 5C006/BF02 5C006/BF14 5C006/BF15 5C006/BF22 5C006/BF24 5C006/BF28 5C006<br>/BF42 5C006/BF45 5C006/BF46 5C006/EA01 5C006/EC02 5C006/FA04 5C006/FA12 5C006/FA23<br>5C006/FA36 5C006/FA42 5C006/FA43 5C006/FA48 5C006/FA54 5C080/AA10 5C080/BB05 5C080<br>/CC03 5C080/DD03 5C080/DD06 5C080/DD08 5C080/DD23 5C080/DD25 5C080/DD26 5C080<br>/EE01 5C080/EE19 5C080/EE26 5C080/EE28 5C080/EE29 5C080/EE30 5C080/FF03 5C080/FF11 5C080<br>/GG02 5C080/GG05 5C080/GG07 5C080/GG08 5C080/GG11 5C080/GG13 5C080/GG15 5C080<br>/GG17 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C080/KK02 5C080/KK07 5C080<br>/KK43 5C080/KK50 |         |            |

| 审查员(译)         | 中村直之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 优先权            | 2010104032 2010-04-28 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 其他公开文献         | JP2016136276A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

**摘要(译)**

要解决的问题在显示动态图像和静止图像时，要降低功耗并提高显示质量 本发明的一个目的是提供一种液晶显示装置。 液晶显示装置包括具有红色，绿色和蓝色滤色器的子像素以及控制白光透射的子像素 一种显示面板，具有多个像素，包括用于红色，绿色，蓝色和白色的子像素 背光单元具有源，显示面板以运动图像模式或静止图像模式显示 根据运动图像模式中的图像信号和背光 在静止图像模式中，控制图像部分的红色，绿色和蓝色的亮度，并且根据图像信号，背光 以及用于控制另一部分的白色光源的亮度的显示控制电路。 点域1

(45)発行日 平成29年5月31日(2017.5.31)

(24)登録日 平成29年5月12日(2017.5.12)

| (51)Int.Cl. |              | F 1       |                |

|-------------|--------------|-----------|----------------|

| <b>G09G</b> | <b>3/36</b>  | (2006.01) | G09G 3/36      |

| <b>G09G</b> | <b>3/20</b>  | (2006.01) | G09G 3/20 642K |

| <b>G09G</b> | <b>3/34</b>  | (2006.01) | G09G 3/20 660V |

| <b>G02F</b> | <b>1/133</b> | (2006.01) | G09G 3/20 660U |

|             |              |           | G09G 3/20 621K |

請求項の数 4 (全 39 頁) 最終頁に続く

|                                          |                     |

|------------------------------------------|---------------------|

| (21)出願番号 特願2016-63113 (P2016-63113)      | (73)特許権者 000153878  |

| (22)出願日 平成28年3月28日 (2016.3.28)           | 株式会社半導体エネルギー研究所     |

| (23)分割の表示 特願2015-78310 (P2015-78310)     | 神奈川県厚木市長谷398番地      |

|                                          | の分割                 |

| 原出願日 平成23年4月27日 (2011.4.27)              | 山崎 雅平               |

| (63)公開番号 特開2016-136276 (P2016-136276A)   | 神奈川県厚木市長谷398番地 株式会社 |

| (43)公開日 平成28年7月28日 (2016.7.28)           | 半導体エネルギー研究所内        |

| 審査請求日 平成28年3月29日 (2016.3.29)             | 小山 潤                |

| (31)優先権主張番号 特願2010-104032 (P2010-104032) | 神奈川県厚木市長谷398番地 株式会社 |

| (32)優先日 平成22年4月28日 (2010.4.28)           | 半導体エネルギー研究所内        |

| (33)優先権主張国 日本国 (JP)                      |                     |

|                                          | 審査官 中村 直行           |

最終頁に続く

(54)【発明の名称】表示装置及び電子機器