(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5178941号

(P5178941)

(45) 発行日 平成25年4月10日(2013.4.10)

(24) 登録日 平成25年1月18日(2013.1.18)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G09G 3/20 (2006.01)

G09G 3/20 660U

G02F 1/133 (2006.01)

G09G 3/20 660V

G09G 3/20 621K

G09G 3/20 611A

請求項の数 2 (全 46 頁) 最終頁に続く

(21) 出願番号

特願2012-159234 (P2012-159234)

(22) 出願日

平成24年7月18日(2012.7.18)

(62) 分割の表示

特願2011-4551 (P2011-4551)

の分割

原出願日 平成23年1月13日(2011.1.13)

(65) 公開番号

特開2012-230413 (P2012-230413A)

(43) 公開日

平成24年11月22日(2012.11.22)

審査請求日 平成24年7月19日(2012.7.19)

(31) 優先権主張番号

特願2010-10419 (P2010-10419)

(32) 優先日

平成22年1月20日(2010.1.20)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 早川 昌彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 脇本 研一

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 中村 直行

早期審査対象出願

最終頁に続く

(54) 【発明の名称】 液晶表示装置

(57) 【特許請求の範囲】

## 【請求項 1】

画像信号が入力され、入力された前記画像信号をデータとして順次記憶する記憶回路と、

前記記憶回路に記憶された前記画像信号のデータが入力され、連続するフレーム期間の画像に対応する前記画像信号のデータを比較し、比較結果に応じた第1の信号を生成する比較回路と、

前記第1の信号に応じて、選択的に前記記憶回路に記憶された前記画像信号のデータを読み出し、読み出した前記画像信号のデータをデータ信号として出力する選択回路と、

前記液晶表示装置の温度を検出し、検出した温度に応じた第2の信号を生成する補正回路と、

スタート信号、クロック信号、前記第1の信号、前記第2の信号、及び電源電圧が入力され、前記選択回路から前記画像信号が入力され、前記第1の信号及び前記第2の信号に応じて、入力された前記画像信号、前記スタート信号、前記クロック信号、及び前記電源電圧の出力の開始又は停止を選択的に行う表示制御回路と、

前記表示制御回路から前記画像信号、前記スタート信号、前記クロック信号、及び前記電源電圧が選択的に順次入力されることにより動作の開始又は停止が制御される駆動回路部と、

前記駆動回路部から前記画像信号のデータが書き込まれることにより表示状態が制御される画素と、

10

20

前記補正回路は、前記液晶表示装置の温度を検出し、検出した温度に応じた温度データを生成する温度検出回路と、

連続して静止画となるフレーム期間の数を計数する計数回路と、

前記計数回路の計数値と、前記温度データに応じて設定された基準となる計数値を比較し、比較結果に応じて前記第2の信号を生成する計数値比較回路と、を有し、

前記第1の信号は、前記記憶回路に記憶された前記画像信号に応じて、前記表示制御回路の動作を制御することができる機能を有し、

前記第2の信号は、前記温度検出回路で検出した温度に応じて、前記表示制御回路の動作を制御することができる機能を有することを特徴とする液晶表示装置。

【請求項2】

10

画像信号が入力され、入力された前記画像信号をデータとして順次記憶する記憶回路と、

前記記憶回路に記憶された前記画像信号のデータが入力され、連続するフレーム期間の画像に対応する前記画像信号のデータを比較し、比較結果に応じた第1の信号を生成する比較回路と、

前記第1の信号に応じて、選択的に前記記憶回路に記憶された前記画像信号のデータを読み出し、読み出した前記画像信号のデータをデータ信号として出力する選択回路と、

前記液晶表示装置の温度を検出し、検出した温度に応じた第2の信号を生成する補正回路と、

スタート信号、クロック信号、前記第1の信号、前記第2の信号、及び電源電圧が入力され、前記選択回路から前記画像信号が入力され、前記第1の信号及び前記第2の信号に応じて、入力された前記画像信号、前記スタート信号、前記クロック信号、及び前記電源電圧の出力の開始又は停止を選択的に行う表示制御回路と、

前記表示制御回路から前記画像信号、前記スタート信号、前記クロック信号、及び前記電源電圧が選択的に順次入力されることにより動作の開始又は停止が制御される駆動回路部と、

前記駆動回路部から前記画像信号のデータが書き込まれることにより表示状態が制御される画素と、

前記補正回路は、前記液晶表示装置の温度を検出し、検出した温度に応じた温度データを生成する温度検出回路と、

30

連続して静止画となるフレーム期間の数を計数する計数回路と、

前記計数回路の計数値と前記温度データに応じて設定された基準となる計数値とを比較し、比較結果に応じて前記第2の信号を生成する計数値比較回路と、

前記画像信号を出力するか否かを制御するトランジスタと、を有し、

前記トランジスタは、チャネル形成領域において酸化物半導体を有し、

前記第1の信号は、前記記憶回路に記憶された前記画像信号に応じて、前記表示制御回路の動作を制御することができる機能を有し、

前記第2の信号は、前記温度検出回路で検出した温度に応じて、前記表示制御回路の動作を制御することができる機能を有することを特徴とする液晶表示装置。

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一態様は、表示装置の駆動方法に関する。また、液晶表示装置に関する。

【背景技術】

【0002】

液晶表示装置などの表示装置は、テレビ受像機などの大型表示装置から携帯電話などに用いられる小型表示装置に至るまでの広範囲にわたって普及が進んでおり、更に付加価値の高い製品の開発が進められている。近年では、例えばモバイル機器の利便性向上の点から、低消費電力型の表示装置の開発が注目されている。

50

**【0003】**

例えば、特許文献1では、全ての走査線及び信号線を非選択状態とする休止期間に各信号線の電圧を一定に保持するために、信号線駆動回路から全信号線を電気的に切り離してハイインピーダンス状態とすることにより、液晶表示装置における消費電力の低減を図る技術が開示されている。

**【0004】**

また、非特許文献1では、動画表示と静止画表示の際のリフレッシュレートを異ならせることにより、液晶表示装置における消費電力の低減を図る構成が開示されている。また、非特許文献1では、静止画表示のときの休止期間と走査期間の信号切り替えの際に、液晶素子に印加される電圧の変動によるフリッカの知覚を防ぐために、休止期間中にも信号線と共に通電極と共に同位相の交流信号を印加して液晶素子に印加される電圧の変動を防ぐ技術が開示されている。10

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2001-312253号公報

**【非特許文献】****【0006】**

【非特許文献1】Kazuhiko Tsuda et al., IDW'02, pp 2

95-298

20

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

しかしながら、上記駆動方式では、液晶表示装置の走査線や信号線に信号を供給する駆動回路の構成及びその動作が複雑になり、液晶表示装置の消費電力を十分低減することができない。

**【0008】**

また、特許文献1に示すように、全ての走査線及び信号線を非選択状態とする休止期間を設けると画素への書き込み動作の間隔が長くなるため、その分トランジスタのリーク電流や寄生容量により液晶素子に印加される電圧が大幅に低下することがある。液晶素子に印加される電圧が大幅に低下すると、所望の階調での表示が行えなくなるなど、表示品位が低下してしまう。30

**【0009】**

また、上記液晶表示装置は、自身の温度変化により輝度が変化してしまい、静止画を表示する場合であっても、時間が経過するに従って徐々に輝度の変化が大きくなり、表示品位が低下してしまう。

**【0010】**

そこで、本発明の一態様は、表示装置の駆動回路での複雑な動作を必要とせず、消費電力を低減することを課題の一つとする。また、本発明の一態様は、表示品位の低下を抑制することを課題の一つとする。40

**【課題を解決するための手段】****【0011】**

本発明の一態様は、動画表示モードと静止画表示モードを設け、静止画表示モードのとき、駆動回路を動作させるための信号及び電圧を駆動回路に供給する動作を停止させてもその直前に書き込まれた画像を静止画として維持し、その後、表示画像を静止画として維持させるために画像信号のデータを再度書き込むことにより画素の表示状態を静止画として維持するものであり、さらに表示装置の温度によって静止画像の保持期間を設定するものである。

**【0012】**

また、本発明の一態様は、相対的に高い周波数（例えば60Hz以上）で動画を表示する50

モードと、相対的に低い周波数（例えば1Hz以下）で画素へ向けた画像信号のデータの書き込み動作を行う静止画表示モード又は簡易動画再生モードを設け、表示装置の温度に応じて静止画表示モード又は簡易動画再生モードの画像信号のデータの書き込み間隔を設定するものである。

【0013】

本発明の一態様は、画像信号が入力される駆動回路部と、駆動回路部から画像信号のデータが書き込まれることにより表示状態が制御される画素と、を具備し、動画表示モードと静止画表示モードを有する表示装置の駆動方法であって、静止画表示モードは、第1の期間において、駆動回路部により画素に画像信号のデータを書き込み、その後第2の期間において、駆動回路部を動作させるための信号及び電圧を駆動回路部に供給するのを停止させ、その後第3の期間において、駆動回路部を動作させるための信号及び電圧を駆動回路部に供給するのを再開させ、駆動回路部により画素に画像信号のデータを書き込むことにより画素の表示状態を静止画として維持し、第2の期間及び第3の期間において、駆動回路部を動作させるための信号及び電圧の駆動回路部への供給を停止してから再開するまでの期間の長さを表示装置の温度に応じて設定する表示装置の駆動方法である。

10

【0014】

本発明の一態様は、液晶表示装置であって、画像信号、スタート信号、クロック信号、画像信号に応じた信号である第1の制御信号、液晶表示装置の温度に応じた信号である第2の制御信号、及び電源電圧が入力され、第1の制御信号及び第2の制御信号に応じて、入力された画像信号、スタート信号、クロック信号、及び電源電圧の出力の開始又は停止を選択的に行う表示制御回路と、表示制御回路から画像信号、スタート信号、クロック信号、及び電源電圧が順次入力されることにより動作の開始又は停止が制御される駆動回路部と、駆動回路部から画像信号のデータが書き込まれることにより表示状態が制御される画素と、を具備することを特徴とする液晶表示装置である。

20

【0015】

本発明の一態様は、液晶表示装置であって、画像信号が入力され、入力された画像信号の状態をデータとして順次記憶する記憶回路と、記憶回路に記憶された画像信号のデータの中から連続するフレーム期間の画像に対応する画像信号のデータを比較し、比較結果に応じた第1の制御信号を生成する比較回路と、第1の制御信号に応じて、記憶回路に記憶された画像信号のデータを読み出し、読み出した画像信号のデータをデータ信号として出力する選択回路と、液晶表示装置の温度を検出し、検出した温度に応じた第2の制御信号を生成する温度検出回路と、スタート信号、クロック信号、第1の制御信号、第2の制御信号、及び電源電圧が入力され、選択回路から画像信号が入力され、第1の制御信号及び第2の制御信号に応じて、入力された画像信号、スタート信号、クロック信号、及び電源電圧の出力の開始又は停止を選択的に行う表示制御回路と、表示制御回路から画像信号、スタート信号、クロック信号、及び電源電圧が選択的に入力されることにより動作の開始又は停止が制御される駆動回路部と、駆動回路部から画像信号のデータが書き込まれることにより表示状態が制御される画素と、を具備する液晶表示装置である。

30

【発明の効果】

【0016】

40

本発明の一態様により、静止画を表示する際の消費電力を低減することができる。また表示品位の低下を抑制することができる。

【図面の簡単な説明】

【0017】

【図1】実施の形態1における表示装置の構成の一例を示す図。

【図2】画像処理回路、補正回路、及び表示制御回路の構成を示す図。

【図3】図1に示す表示装置の動作の一例を示すタイミングチャート。

【図4】図1に示す表示装置の動作の一例を示すタイミングチャート。

【図5】図1に示す表示装置の動作の一例を示すタイミングチャート。

【図6】温度変化によるトランジスタの電気特性の変動を示す図。

50

【図7】温度変化による表示装置の画素における保持電圧の変動を示す図。

【図8】実施の形態2におけるシフトレジスタの構成の一例を示す図。

【図9】実施の形態2におけるシフトレジスタの動作の一例を示す図。

【図10】実施の形態3におけるトランジスタの構造の一例を示す図。

【図11】実施の形態3におけるトランジスタの作製方法の一例を示す図。

【図12】実施の形態4における液晶表示装置の構造の一例を示す図。

【図13】実施の形態5における液晶表示装置の構成の一例を示す図。

【図14】実施の形態6における液晶表示装置の構成の一例を示す図。

【図15】実施の形態7における液晶表示装置の構成の一例を示す図。

【発明を実施するための形態】

10

【0018】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではないとする。

【0019】

(実施の形態1)

本実施の形態では、表示装置の一例として、周囲の温度に応じて駆動回路の動作の開始又は停止のタイミングを制御する液晶表示装置について説明する。

【0020】

20

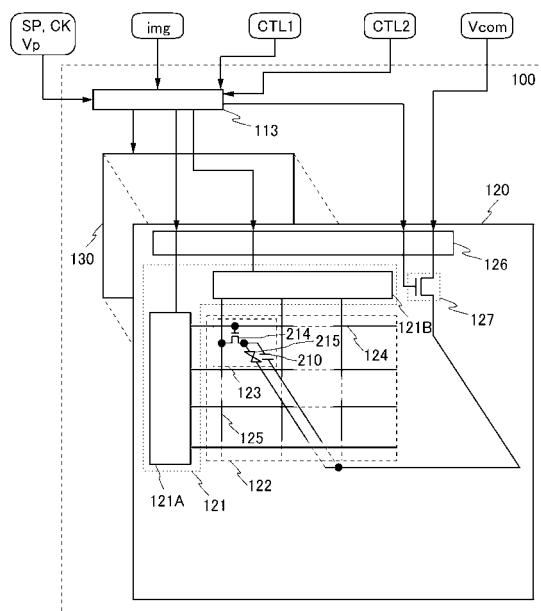

まず、本実施の形態における液晶表示装置の構成の一例について、図1を用いて説明する。図1は、液晶表示装置の構成の一例を示すブロック図である。

【0021】

図1に示す液晶表示装置100は、制御信号CTL1及び制御信号CTL2に基づいて、信号又は電圧の出力が制御される表示制御回路113と、表示制御回路113により表示動作が制御される表示パネル120と、を具備する。

【0022】

なお、一般的に電圧とは、ある二点間における電位の差（電位差ともいう）のことをいう。しかし、電圧及び電位の値は、回路図などにおいていずれもボルト（V）で表されることがあるため、区別が困難である。そこで、本明細書では、特に指定する場合を除き、ある一点の電位と基準となる電位（基準電位ともいう）との電位差を、該一点の電圧として用いる場合がある。

30

【0023】

さらに、表示パネル120は、駆動回路部121と、画素部122と、走査線124と、画像信号線125と、を具備し、駆動回路部121は、駆動回路121Aと、駆動回路121Bと、を有し、画素部122は、画素123を複数有する。

【0024】

表示制御回路113は、画像信号img、駆動回路部121を動作させるための信号又は電圧（例えばスタート信号SP、クロック信号CK、制御信号CTL1、制御信号CTL2、及び電源電圧Vp）が入力（供給ともいう）され、制御信号CTL1及び制御信号CTL2に応じて、入力された画像信号img、スタート信号SP、クロック信号CK、及び電源電圧Vpを選択的に出力する機能を有する回路である。電源電圧Vpは、例えば外部機器から入力される。

40

【0025】

なお、例えばドット反転駆動、ソースライン反転駆動、ゲートライン反転駆動、フレーム反転駆動などに応じてフレーム期間毎に極性を反転させた信号を画像信号imgとしてもよい。また、画像信号imgがアナログ信号の場合には、A/Dコンバータなどを介してアナログ信号をデジタル信号に変換し、変換したデジタル信号を画像信号imgとしてもよい。

【0026】

50

スタート信号 S P としては、例えば駆動回路 1 2 1 A に出力するためのスタート信号 G S P 及び駆動回路 1 2 1 B に出力するためのスタート信号 S S P などが挙げられる。なお、スタート信号 G S P 及びスタート信号 S S P に相当するスタート信号は、それぞれ複数であってもよい。スタート信号 S P は、例えば外部機器から入力される。

【 0 0 2 7 】

クロック信号 C K としては、駆動回路 1 2 1 A に出力するためのクロック信号 G C K 及び駆動回路 1 2 1 B に出力するためのクロック信号 S C K などが挙げられる。なお、クロック信号 G C K 及びクロック信号 S C K に相当するクロック信号は、それぞれ複数であってもよい。クロック信号 C K は、例えば外部機器から入力される。

【 0 0 2 8 】

制御信号 C T L 1 は、画像信号 i m g に応じて表示制御回路 1 1 3 の動作を制御するための信号である。制御信号 C T L 1 に含まれるデータとしては、例えば表示制御回路 1 1 3 から駆動回路部 1 2 1 に画像信号 i m g 、スタート信号 S P 、クロック信号 C K 、及び電源電圧 V p を出力するタイミング、又は回数などを指定する命令又は情報などが挙げられる。制御信号 C T L 1 は、例えば画像信号 i m g に応じて適宜生成される。また、生成した制御信号 C T L 1 のデータを予め記憶回路などに記憶しておき、記憶回路から適宜データを読み出して用いてもよい。

10

【 0 0 2 9 】

制御信号 C T L 2 は、液晶表示装置 1 0 0 の温度に応じて表示制御回路 1 1 3 の動作を制御するための信号であり、制御信号 C T L 2 に含まれるデータとしては、例えば液晶表示装置 1 0 0 の温度に応じて、最適な表示制御回路 1 1 3 から駆動回路部 1 2 1 に画像信号 i m g 、スタート信号 S P 、クロック信号 C K 、及び電源電圧 V p を出力するタイミング、又は回数などを指定する命令又は情報などが挙げられる。制御信号 C T L 2 は、例えば液晶表示装置の温度に応じて適宜生成される。ここでの温度としては、例えば液晶表示装置 1 0 0 に内部の温度又は液晶表示装置 1 0 0 が置かれる環境下の温度が挙げられる。

20

【 0 0 3 0 】

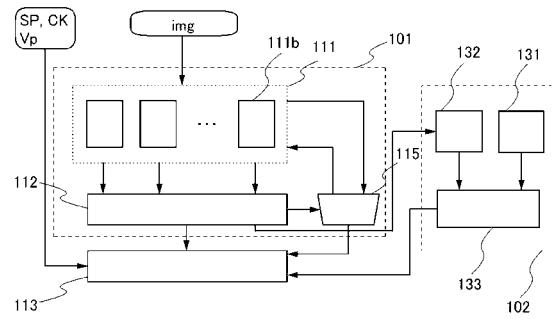

なお、図 1 に示す液晶表示装置に画像処理回路を設け、画像処理回路により制御信号 C T L 1 を生成することもでき、図 1 に示す液晶表示装置に補正回路を設け、補正回路により制御信号 C T L 2 を生成することもできる。画像処理回路及び補正回路を設ける場合の画像処理回路、補正回路、及び表示制御回路 1 1 3 の構成について図 2 を用いて説明する。

30

図 2 は、画像処理回路、補正回路、及び表示制御回路の構成の一例を示す図である。

【 0 0 3 1 】

図 2 に示す画像処理回路 1 0 1 は、画像信号 i m g のデータ（画像データともいう）を記憶する記憶回路 1 1 1 と、記憶回路 1 1 1 に記憶された複数の画像データを比較する比較回路 1 1 2 と、比較回路 1 1 2 により、記憶回路 1 1 1 からの画像データの読み出しが制御される選択回路 1 1 5 と、を有する。

【 0 0 3 2 】

記憶回路 1 1 1 は、画像信号 i m g が入力され、入力された画像信号 i m g をデータとして順次記憶する機能を有する回路である。記憶回路 1 1 1 は、複数のフレーム期間の画像に対応する画像信号 i m g のデータを記憶するための複数のフレームメモリを有する。なお、フレームメモリ 1 1 1 b は、1 フレーム期間分のメモリ領域を概念的に図示するものである。また、記憶回路 1 1 1 は、複数のフレーム期間の画像に対応する画像信号 i m g のデータを記憶することができればよく、記憶回路 1 1 1 が有するフレームメモリの数は、特に限定されるものではない。また、フレームメモリは、例えば D R A M ( D y n a m i c R a n d o m A c c e s s M e m o r y ) 、又は S R A M ( S t a t i c R a n d o m A c c e s s M e m o r y ) などの記憶素子を用いて構成される。

40

【 0 0 3 3 】

比較回路 1 1 2 は、連続するフレーム期間の画像に対応する画像信号 i m g のデータを記憶回路 1 1 1 から読み出し、読み出した画像信号 i m g のデータを比較し、比較結果に応じた信号である制御信号 C T L 1 を生成し、生成した制御信号 C T L 1 を表示制御回路 1

50

13及び選択回路115に出力する回路である。比較回路112では、画像データの比較を行うことにより、連続するフレーム期間の画像に対応する画像信号のデータが動画を表示するためのデータであるか又は静止画を表示するためのデータであるかが判断される。

【0034】

なお、動画とは、複数のフレーム期間に時分割した複数の画像を高速に切り替えることにより、動く画像として人間の目に認識される画像のことである。

【0035】

また、静止画とは、動画及び部分動画と異なり、複数のフレーム期間に時分割した複数の画像を高速に切り替えて動作させた場合であっても、連続するフレーム期間、例えば第nのフレーム期間(nは自然数)と、第(n+1)のフレーム期間とで変化がない画像として人間の目に認識される画像のことである。

10

【0036】

また、上記では、連続するフレーム期間の画像に対応する画像信号のデータを比較回路112が比較することにより、比較した画像が動画であるか又は静止画であるかを判断する構成について示したが、これに限定されず、本実施の形態の液晶表示装置は、予め動画であるか又は静止画であるかが決められている画像信号が外部から入力される構成としてもよい。

【0037】

選択回路115は、制御信号CTL1に応じて、記憶回路111に記憶された画像信号のデータを読み出し、読み出した画像信号のデータをデータ信号として選択的に出力する機能を有する回路である。なお、選択回路115は、比較回路112の検出基準により動作が設定されてもよい。

20

【0038】

選択回路115は、例えば複数のスイッチを含む回路により構成され、該スイッチとしては、例えばトランジスタを用いることができる。

【0039】

さらに、補正回路102は、温度検出回路131と、計数回路132と、計数値比較回路133と、を有する。

【0040】

温度検出回路131は、検出した温度に応じた温度データ信号TMLを生成し、さらに温度データ信号TMLを用いて基準となる計数値のデータ信号CNT1を生成する機能を有する。温度検出回路131は、例えば温度データ信号TMLを生成する温度センサを有する。温度センサとしては、例えば熱電対、抵抗温度センサ、サーミスタ、I C温度センサ、磁気温度センサ、又は赤外線温度センサなどを用いることができる。また、温度センサとしては、トランジスタの温度特性を利用したセンサなどを用いることもできる。

30

【0041】

計数回路132は、比較回路112で静止画と判断された連続するフレーム期間の数を計数し、計数した計数値のデータ信号CNT2を出力する機能を有する。

【0042】

計数値比較回路133は、計数回路132の計数値のデータ信号CNT2のデータと基準となる計数値のデータ信号CNT1のデータを比較し、比較結果に応じて制御信号CTL2を生成し、生成した制御信号CTL2を表示制御回路113に出力する機能を有する。

40

【0043】

基準となる計数値は、温度センサにより生成した温度データTMLに基づいて設定することができる。例えば、各温度に対してそれぞれ計数値を設定し、温度に対する計数値の補正データテーブルを作成し、温度検出回路131は、該データテーブルから温度センサにより生成した温度データTMLに対応する計数値のデータを読み出し、読み出した計数値のデータを基準となる計数値のデータ信号CNT1のデータとして用いることにより、温度に応じて駆動回路部121が動作するための信号又は電圧(画像信号、スタート

50

信号 S P、クロック信号 C K、及び電源電圧 V p ) の出力のタイミングを補正することができる。また、本実施の形態の液晶表示装置は、別途メモリなどに計数値の補正データテーブルをデータとして記憶しておき、記憶されている補正データテーブルを適宜読み出して用いる構成とすることもできる。

【 0 0 4 4 】

なお、補正回路 1 0 2 は、図 2 に示す構成に限定されず、温度検出回路 1 3 1 により温度を検出し、検出した温度のデータを用いて制御信号 C T L 2 を生成することができる構成であればよい。

【 0 0 4 5 】

さらに、画像処理回路 1 0 1 及び補正回路 1 0 2 の動作の一例について、以下に説明する 10

。

【 0 0 4 6 】

まず、画像信号 i m g が記憶回路 1 1 1 に入力される。

【 0 0 4 7 】

記憶回路 1 1 1 は、入力された画像信号 i m g のデータを順次記憶し、記憶した画像信号 i m g のデータを比較回路 1 1 2 に順次出力する。

【 0 0 4 8 】

さらに、比較回路 1 1 2 は、記憶回路 1 1 1 から入力された、連続するフレーム期間の画像に対応する画像信号 i m g のデータを比較し、比較した画像信号 i m g のデータの間に差分があるか否かを調べ、比較した画像信号 i m g のデータに対応する画像が動画であるか静止画であるかを判断する。 20

【 0 0 4 9 】

例えば、連続するフレーム期間の画像に対応する画像信号 i m g のデータの間で差分を検出した場合、比較回路 1 1 2 は、比較した画像信号 i m g のデータに対応する画像を動画と判断し、比較結果に応じた制御信号 C T L 1 を表示制御回路 1 1 3 及び選択回路 1 1 5 に出力する。

【 0 0 5 0 】

また、連続するフレーム期間の画像に対応する画像信号 i m g のデータの間で差分が無かった場合、比較回路 1 1 2 は、比較した画像信号 i m g のデータに対応する画像を静止画と判断し、比較結果に応じた制御信号 C T L 1 を表示制御回路 1 1 3 及び選択回路 1 1 5 30

に出力する。

【 0 0 5 1 】

なお、比較回路 1 1 2 における比較により検出される差分が一定の値を超えた場合に差分が検出されたと判断されるように、差分の検出基準を設定してもよい。

【 0 0 5 2 】

さらに、選択回路 1 1 5 は、比較回路 1 1 2 から入力された制御信号 C T L 1 に基づき、記憶回路 1 1 1 から画像信号 i m g のデータを読み出し、読み出した画像信号 i m g のデータをデータ信号として表示制御回路 1 1 3 に出力する。

【 0 0 5 3 】

例えば、比較回路 1 1 2 により比較した画像信号 i m g のデータに基づく画像が動画と判断された場合、選択回路 1 1 5 は、記憶回路 1 1 1 から画像信号 i m g のデータを読み出し、読み出した画像信号 i m g のデータをデータ信号として表示制御回路 1 1 3 に出力する。 40

【 0 0 5 4 】

また、比較回路 1 1 2 により比較した画像信号 i m g のデータに基づく画像が静止画と判断された場合、選択回路 1 1 5 は、表示制御回路 1 1 3 へ向けた画像信号 i m g の出力を停止する。

【 0 0 5 5 】

また、温度検出回路 1 3 1 は、液晶表示装置の温度を検出し、検出した温度に応じた温度データ信号 T M L を生成する。さらに、データテーブルから温度検出回路 1 3 1 により生 50

成した温度データ T M L に対応する計数値のデータを読み出し、読み出した計数値のデータを基準となる計数値のデータ信号 C N T 1 として計数値比較回路 1 3 3 に出力する。

【 0 0 5 6 】

また、計数回路 1 3 2 は、連続する静止画と判断されるフレーム期間の数を計数し、計数した値のデータを計数値のデータ信号 C N T 2 として計数値比較回路 1 3 3 に出力する。

【 0 0 5 7 】

計数値比較回路 1 3 3 は、計数回路 1 3 2 の計数値のデータ信号 C N T 2 のデータと基準となる計数値のデータ信号 C N T 1 のデータを比較し、比較結果に応じて制御信号 C T L 2 を生成し、生成した制御信号 C T L 2 を表示制御回路 1 1 3 に出力する。さらに、計数回路 1 3 2 の計数値が基準となる計数値になったとき、制御信号 C T L 2 に応じて表示制御回路 1 1 3 から駆動回路部 1 2 1 に画像信号 i m g 、スタート信号 S P 、クロック信号 C K 、及び電源電圧 V p を出力する。以上が画像処理回路 1 0 1 及び補正回路 1 0 2 の動作の一例である。

【 0 0 5 8 】

また、図 1 に示す液晶表示装置は、表示パネル 1 2 0 に光を供給する光源部 1 3 0 を具備する。

【 0 0 5 9 】

光源部 1 3 0 は、表示パネル 1 2 0 に光を供給する機能を有し、例えば光源制御回路及び光源を有する。光源は、液晶表示装置の用途に応じて構成要素を選択して組み合わせればよく、例えばフルカラーの画像を表示する場合は、光源として光の三原色を含む光源を用いることができる。また、光源としては、例えば白色の発光素子（例えば L E D ）を用いることができる。また、光源部 1 3 0 は、図 1 に示すように、表示制御回路 1 1 3 により点灯状態が制御される構成とすることもできる。光源部 1 3 0 は、必ずしも表示制御回路 1 1 3 により制御される構成とする必要はないが、表示制御回路 1 1 3 により光源部 1 3 0 を制御することにより、必要に応じて光源を消灯させることができるために、消費電力を低減することができる。光源としては、例えばバックライト又はサイドライトを用いることができる。

【 0 0 6 0 】

さらに、表示パネル 1 2 0 の構成について、以下に説明する。

【 0 0 6 1 】

駆動回路 1 2 1 A は、画像信号 i m g を出力する画素 1 2 3 を選択する走査線 1 2 4 を制御する走査線駆動回路としての機能を有する。駆動回路 1 2 1 A は、端子部 1 2 6 を介して電源電圧 V p 、スタート信号 G S P 、及びクロック信号 G C K が選択的に入力される。

【 0 0 6 2 】

駆動回路 1 2 1 B は、画素 1 2 3 に画像信号 i m g を出力するか否かを制御する信号線駆動回路としての機能を有する。駆動回路 1 2 1 B は、端子部 1 2 6 を介して画像信号 i m g 、電源電圧 V p 、スタート信号 S S P 、及びクロック信号 S C K が選択的に入力される。

【 0 0 6 3 】

駆動回路 1 2 1 A 及び駆動回路 1 2 1 B は、例えばシフトレジスタを有する構成とすることができる、該シフトレジスタは、例えばトランジスタを用いて構成される。

【 0 0 6 4 】

複数の画素 1 2 3 は、それぞれ走査線 1 2 4 及び画像信号線 1 2 5 に環囲されてマトリクス状に設けられている。なお、図 1 に示す液晶表示装置において、走査線 1 2 4 は、駆動回路 1 2 1 A から延在し、画像信号線 1 2 5 は、駆動回路 1 2 1 B から延在している。

【 0 0 6 5 】

さらに、画素 1 2 3 の回路構成の一例について、以下に説明する。

【 0 0 6 6 】

画素 1 2 3 は、トランジスタ 2 1 4 と、容量素子 2 1 0 と、液晶素子 2 1 5 と、を有する。

10

20

30

40

50

## 【0067】

なお、本明細書において、トランジスタは、電界効果トランジスタであり、ソース、ドレイン、及びゲートを少なくとも有する。

## 【0068】

ソースとは、ソース電極、及びソース配線の一部又は全部のことをいう。また、ソース電極とソース配線とを区別せずにソース電極及びソース配線の両方の機能を有する導電層をソースという場合がある。

## 【0069】

ドレインとは、ドレイン電極、及びドレイン配線の一部又は全部のことをいう。また、ドレイン電極とドレイン配線とを区別せずにドレイン電極及びドレイン配線の両方の機能を有する導電層をドレインという場合がある。

10

## 【0070】

ゲートとは、ゲート電極及びゲート配線の一部又は全部のことをいう。また、ゲート電極とゲート配線とを区別せずにゲート電極及びゲート配線の両方の機能を有する導電層をゲートという場合がある。

## 【0071】

また、トランジスタの構造や動作条件などによって、トランジスタのソースとドレインが互いに入れ替わるため、いずれがソース又はドレインであるかを限定することが困難である。そこで、本書類（明細書、特許請求の範囲又は図面など）では、トランジスタのソース及びドレインのいずれか一方をソース及びドレインの一方と表記し、他方をソース及びドレインの他方と表記することができる。

20

## 【0072】

トランジスタ214は、ソース及びドレインの一方が画像信号線125に電気的に接続され、ゲートが走査線124に電気的に接続される。

## 【0073】

液晶素子215は、第1端子及び第2端子を有し、第1端子がトランジスタ214のソース及びドレインの他方に電気的に接続される。液晶素子215は、第1端子の一部又は全部としての機能を有する画素電極と、第2端子の一部又は全部としての機能を有する共通電極と、画素電極及び共通電極の間に電圧が印加されることにより透過率が変化する液晶層と、を有する構成とすることができる。

30

## 【0074】

なお、画素電極は、可視光を透過する領域と、可視光を反射する領域と、を有する構成とすることもできる。画素電極の可視光を透過する領域は、光源部130から入射する光を透過し、画素電極の可視光を反射する領域は、液晶層を介して入射する光を反射する。

## 【0075】

また、画素電極は、第1の基板の上に設けられることが好ましく、共通電極は、第2の基板の上に設けられることが好ましい。このとき、共通電極が設けられた第2の基板は、共通接続部を介して第1の基板に電気的に接続される。例えば絶縁性球体に金属膜が被覆された導電粒子を用いて共通接続部を構成することができる。なお、第1の基板及び第2の基板の間に複数の共通接続部を設ける構成としてもよい。

40

## 【0076】

また、画素電極及び共通電極の形状は、多様な開口パターンを有する形状としてもよい。

## 【0077】

液晶層に適用可能な液晶の一例としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子分散型液晶（PDL C）、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、又はバナナ型液晶などが挙げられる。

## 【0078】

なお、液晶層に用いられる液晶材料の固有抵抗は、 $1 \times 10^{12} \text{ } \cdot \text{ cm}$ 以上であり、好ましくは $1 \times 10^{13} \text{ } \cdot \text{ cm}$ 以上であり、さらに好ましくは $1 \times 10^{14} \text{ } \cdot \text{ cm}$ 以上

50

である。なお、本明細書における固有抵抗の値は、20で測定した値とする。また、該液晶材料を用いて液晶表示装置を構成した場合、液晶素子となる部分の抵抗は、例えば配向膜又はシール材などにより液晶層に不純物が混入する可能性があるため、 $1 \times 10^{11} \cdot \text{cm}$ 以上さらには $1 \times 10^{12} \cdot \text{cm}$ 以上となる場合がある。

【0079】

液晶材料の固有抵抗が大きいほど液晶層のリーク電流が低減し、表示期間において液晶素子に印加される電圧が経時に低下する現象を抑制することができる。その結果、一回の画像データの書き込みに対応する画素123の表示期間を長くすることができるため、画素123に画像データを書き込む頻度を低減でき、液晶表示装置の消費電力を低減することができる。

10

【0080】

また、液晶素子に適用可能な液晶の駆動方法の一例としては、TN(Twisted Nematic)モード、STN(Super Twisted Nematic)モード、OCB(Optically Compensated Birefringence)モード、ECB(Electrically Controlled Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、PNLC(Polymer Network Liquid Crystal)モード、又はゲストホストモードなどが挙げられる。

20

【0081】

容量素子210は、第1端子及び第2端子を有し、第1端子がトランジスタ214のソース及びドレインの他方に電気的に接続される。容量素子210は、保持容量としての機能を有し、第1端子の一部又は全部としての機能を有する第1の電極と、第2端子の一部又は全部としての機能を有する第2の電極と、第1の電極及び第2の電極の間に電圧が印加されることにより電荷が蓄積される誘電体層と、を有する構成とすることができる。容量素子210の容量は、トランジスタ214のオフ電流などを考慮して設定すればよい。本実施の形態では、各画素における液晶素子215の容量(液晶容量ともいう)に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。また、必ずしも容量素子210を設ける必要はなく、容量素子210を設けない構成としてもよい。画素123に容量素子210を設けない構成とすることにより画素の開口率を向上させることができる。

30

【0082】

さらに、本実施の形態の液晶表示装置は、図1に示すように、トランジスタ127を有する構成とすることができます。

【0083】

トランジスタ127は、表示制御回路113により制御され、オン状態又はオフ状態になることにより、共通電位Vcomを液晶素子215の共通電極に供給するか否かを制御する制御トランジスタとしての機能を有する。トランジスタ127は、ソース及びドレインの一方に共通電位Vcomが入力され、ゲートに表示制御回路113から制御信号が入力され、ソース及びドレインの他方が液晶素子215の第2端子に電気的に接続される。なお、トランジスタ127は、駆動回路部121、又は画素部122と同じ基板に形成されるものでもよいし、別の基板に形成されるものであってもよい。また、トランジスタ127は、オン状態又はオフ状態になることにより、共通電位Vcomを容量素子210の第2端子に出力するか否かを制御する機能を有する。

40

【0084】

共通電位Vcomは、画像信号imgの電位に対して設定される電位であり、共通電位Vcomは、例えば接地電位であってもよい。共通電位Vcomは、例えば外部機器から入力される。

【0085】

50

ここで、本実施の形態の液晶表示装置を構成するトランジスタ（例えば表示パネルのトランジスタ）として適用可能なトランジスタについて、以下に説明する。

【0086】

本実施の形態の液晶表示装置を構成するトランジスタとして適用可能なトランジスタとしては、例えばチャネル形成層としての機能を有する酸化物半導体層を含むトランジスタを用いることができる。トランジスタのチャネル形成層としての機能を有する酸化物半導体層は、n型不純物である水素が除去され、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性（I型）、又は実質的に真性の半導体層である。すなわち、本実施の形態に示す、酸化物半導体層を含むトランジスタは、不純物を添加して該酸化物半導体層をI型化するのではなく、水素や水などの不純物を極力除去し、高純度化することにより、I型にすること又はI型に近づけることを特徴としている。

10

【0087】

なお、高純度化とは、酸化物半導体層中の水素を極力排除すること、及び酸化物半導体層に酸素を供給して、酸化物半導体層中の酸素欠乏に起因する欠陥を低減することの少なくとも一方を含む概念である。

【0088】

酸化物半導体としては、例えば四元系金属酸化物、三元系金属酸化物、又は二元系金属酸化物を用いることができる。四元系金属酸化物としては、例えばIn-Sn-Ga-Zn-O系金属酸化物などを用いることができる。三元系金属酸化物としては、例えばIn-Ga-Zn-O系金属酸化物、In-Sn-Zn-O系金属酸化物、In-Al-Zn-O系金属酸化物、Sn-Ga-Zn-O系金属酸化物、Al-Ga-Zn-O系金属酸化物、又はSn-Al-Zn-O系金属酸化物などを用いることができる。二元系金属酸化物としては、In-Zn-O系金属酸化物、Sn-Zn-O系金属酸化物、Al-Zn-O系金属酸化物、Zn-Mg-O系金属酸化物、Sn-Mg-O系金属酸化物、In-Mg-O系金属酸化物、又はIn-Sn-O系金属酸化物を用いることができる。また、酸化物半導体としては、In-O系金属酸化物、Sn-O系金属酸化物、又はZn-O系金属酸化物などを用いることができる。また、上記酸化物半導体として適用可能な金属酸化物にSiO<sub>2</sub>が含まれていてもよい。

20

【0089】

また、酸化物半導体として、InMO<sub>3</sub>(ZnO)<sub>m</sub>（mは0より大きい数）で表記される材料を用いることができる。ここで、Mは、Ga、Al、Mn及びCoから選ばれた一つ又は複数の金属元素を示す。例えばMとしては、Ga、Ga及びAl、Ga及びMn、又はGa及びCoなどが挙げられる。InMO<sub>3</sub>(ZnO)<sub>m</sub>で表記される構造の酸化物半導体のうち、MとしてGaを含む構造の酸化物半導体を、In-Ga-Zn-O酸化物半導体ともいう。

30

【0090】

さらに、酸化物半導体層として用いられる酸化物半導体のバンドギャップを2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上にする。これにより、熱励起によって生じるキャリアの数は無視できる程度となる。さらに、ドナーを形成する水素などの不純物を一定量以上低減することにより、キャリア濃度を1×10<sup>14</sup>/cm<sup>3</sup>未満、好ましくは1×10<sup>12</sup>/cm<sup>3</sup>以下にする。即ち、酸化物半導体層のキャリア濃度をゼロ又はゼロと実質的に同等の値にする。

40

【0091】

さらに、上記酸化物半導体層を有するトランジスタでは、チャネル幅1μmあたりのオフ電流密度を10aA/μm(1×10<sup>-17</sup>A/μm)以下、さらには1aA/μm(1×10<sup>-18</sup>A/μm)以下、さらには10zA/μm(1×10<sup>-20</sup>A/μm)以下、好ましくは、1zA/μm(1×10<sup>-21</sup>A/μm)以下と、非常に低くすることができる。

【0092】

例えば、トランジスタ214として、上記酸化物半導体層を有するトランジスタを用いる

50

ことにより、一回の画像データの書き込みに対応する画像の表示期間を長くすることができる。そのため、画像データの書き込みの間隔を長くすることができる。例えば、画像データの書き込みの間隔を10秒以上、好ましくは30秒以上、さらに好ましくは1分以上とすることもできる。また、画像データを書き込む間隔を長くすればするほど、より消費電力を低減することができる。

#### 【0093】

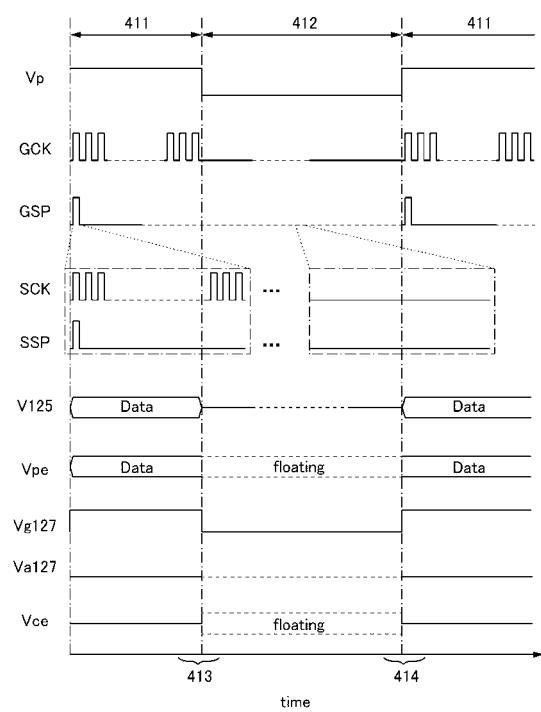

次に、図1に示す液晶表示装置の動作の一例について、図3を用いて説明する。図3は、本実施の形態における液晶表示装置の動作の一例を示すタイミングチャートであり、電源電圧V<sub>p</sub>、クロック信号GCK、スタート信号GSP、クロック信号SCK、スタート信号SSP、画像信号線125の電位(V125ともいう)、液晶素子215における画素電極の電位(V<sub>pe</sub>ともいう)、トランジスタ127のゲートの電位(V<sub>g127</sub>ともいう)、トランジスタ127のソース及びドレインの他方の電位(V<sub>a127</sub>ともいう)、及び液晶素子215における共通電極の電位(V<sub>ce</sub>ともいう)の波形を示している。なお、図3に示すタイミングチャートにおいて、スタート信号GSPは、垂直同期周波数に応じたパルス信号であり、スタート信号SSPは、1ゲート選択期間に応じたパルス信号である。また、図3に示すタイミングチャートにおいて、クロック信号GCK及びクロック信号SCKの波形は、便宜のため単純な矩形波とする。

10

#### 【0094】

図1に示す液晶表示装置の動作の一例は、期間411の動作及び期間412の動作に分けて考えることができる。期間411は、動画を表示するための画像信号を書き込むフレーム期間に相当し、また、期間412は、静止画を表示するフレーム期間に相当する。各期間の動作の一例について、以下に説明する。また、動画を表示するためのモードを動画表示モードといい、静止画を表示するためのモードを静止画モードという。また、静止画モードには動画の一部を静止画として表示するモード(簡易動画再生モードともいう)も含まれる。

20

#### 【0095】

期間411において、表示制御回路113は、画像信号img、電源電圧V<sub>p</sub>、スタート信号GSP、スタート信号SSP、クロック信号GCK、クロック信号SCK、制御信号CTL1、及び制御信号CTL2が入力され、制御信号CTL1及び制御信号CTL2に応じて、入力された電源電圧V<sub>p</sub>、スタート信号GSP、及びクロック信号GCKを駆動回路121Aに出力し、画像信号img、電源電圧V<sub>p</sub>、スタート信号SSP、及びクロック信号SCKを駆動回路121Bに出力する。また、期間411において、表示制御回路113は、トランジスタ127のゲートにトランジスタ127がオン状態になる制御信号CTL127を出力する。このとき、トランジスタ127がオン状態になり、共通電極の電位が共通電位V<sub>com</sub>の電位と同等の値になる。

30

#### 【0096】

さらに、駆動回路121Aは、入力されたスタート信号GSP及びクロック信号GCKにより動作を開始し、走査線124に走査信号を出力し、駆動回路121Bは、入力されたスタート信号SSP及びクロック信号SCKにより動作を開始し、画像信号線125に画像信号imgを出力する。

40

#### 【0097】

さらに、画素123において、トランジスタ214が走査線124の電位に応じてオン状態又はオフ状態になり、トランジスタ214がオン状態のとき、画素電極の電位が画像信号線125の電位と同等の値になり、液晶素子215は、画素電極及び共通電極の間に印加される電圧に応じて光の透過率を設定する。これにより、画素123に画像信号imgのデータが書き込まれ、画素123が表示状態になる。

#### 【0098】

さらに、期間412において、表示制御回路113は、制御信号CTL1及び制御信号CTL2に応じて駆動回路121Aへ向けた電源電圧V<sub>p</sub>、スタート信号GSP、及びクロック信号GCKの出力を順次停止し、駆動回路121Bへ向けた電源電圧V<sub>p</sub>、スタート

50

信号 S S P、及びクロック信号 S C K の出力を順次停止する。なお、期間 4 1 2 において、駆動回路 1 2 1 A に向けての電源電圧 V p、スタート信号 G S P、及びクロック信号 G C K の出力は、必ずしも停止する必要はない。また、期間 4 1 2 において、表示制御回路 1 1 3 は、トランジスタ 1 2 7 のゲートにトランジスタ 1 2 7 がオフ状態になる制御信号 C T L 1 2 7 を出力する。このとき、トランジスタ 1 2 7 がオフ状態になり、共通電極が浮遊状態になる。

【 0 0 9 9 】

さらに、駆動回路 1 2 1 B は、動作が停止し、画像信号 i m g も入力されないため、画素 1 2 3 へ向けた信号の出力が停止する。

【 0 1 0 0 】

さらに、画素 1 2 3 において、トランジスタ 2 1 4 が走査線 1 2 4 の電位に応じてオフ状態になり、画素電極が浮遊状態になる。これにより、画素 1 2 3 は、期間 4 1 1 の表示状態を静止画として維持する。

【 0 1 0 1 】

このように、図 1 に示す液晶表示装置は、期間 4 1 2 において、液晶素子 2 1 5 の画素電極及び共通電極を浮遊状態にすることにより、液晶素子 2 1 5 の画素電極及び共通電極の間に新たに電圧を印加することなく、連続する複数のフレーム期間において静止画の表示を維持することができる。

【 0 1 0 2 】

また、図 1 に示す液晶表示装置は、トランジスタとしてオフ電流の小さいトランジスタを用いる。これにより、液晶素子の画素電極及び共通電極の間に印加される電圧が経時的に低下する現象を抑制することできることため、静止画を表示する期間において、駆動回路へ向けた駆動回路が動作するための信号又は電圧の供給を停止することができ、消費電力を低減することができる。

【 0 1 0 3 】

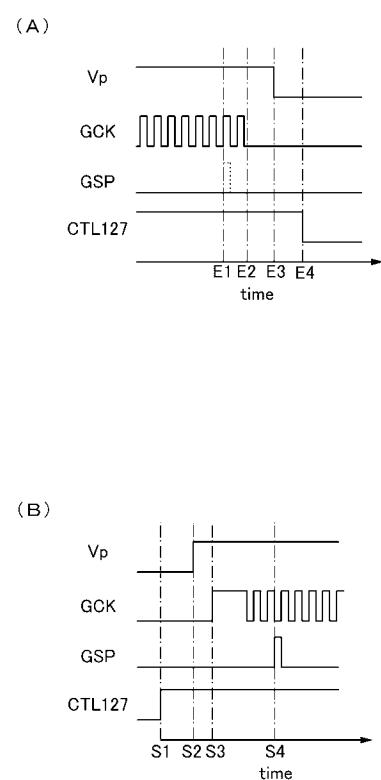

さらに、第 1 の画像切り替え期間（図 3 中の期間 4 1 3）、及び第 2 の画像切り替え期間（図 3 中の期間 4 1 4）における表示制御回路 1 1 3 の動作の一例について、図 4 ( A )、( B )を用いて説明する。図 4 ( A ) 及び図 4 ( B ) は、図 1 に示す液晶表示装置の動作の一例を示すタイミングチャートであり、電源電圧 V p、スタート信号 G S P、クロック信号 G C K、及びトランジスタ 1 2 7 を制御するための制御信号 C T L 1 2 7 の波形を一例として示している。

【 0 1 0 4 】

期間 4 1 3 において、表示制御回路 1 1 3 は、まずスタート信号 G S P の出力を停止する（図 4 ( A ) の E 1、第 1 のステップ）。次に、パルス出力がシフトレジスタの最終段まで達した後に、クロック信号 G C K の出力を停止する（図 4 ( A ) の E 2、第 2 のステップ）。次に、電源電圧 V p の出力を停止する（図 4 ( A ) の E 3、第 3 のステップ）。次に、制御信号 C T L 1 2 7 の電位を、トランジスタ 1 2 7 がオフ状態になる電位にする（図 4 ( A ) の E 4、第 4 のステップ）。

【 0 1 0 5 】

以上のように、駆動回路 1 2 1 A の誤動作を引き起こすことなく、駆動回路 1 2 1 A の動作、例えば駆動回路 1 2 1 A に向けての駆動回路 1 2 1 A を動作させるための信号又は電圧の出力を停止することができる。動画から静止画に切り替わる際の誤動作はノイズを発生させ、ノイズにより画像信号の波形が変動するため、駆動回路の誤動作を抑制することにより、画像の劣化が少ない静止画を表示することができる。

【 0 1 0 6 】

なお、これに限定されず、駆動回路 1 2 1 B へ向けた駆動回路 1 2 1 B を動作させるための信号又は電圧（電源電圧 V p、スタート信号 S S P、及びクロック信号 S C K ）の出力の停止も駆動回路 1 2 1 A と同様に行うことができる。

【 0 1 0 7 】

さらに、期間 4 1 4 において、表示制御回路 1 1 3 は、制御信号 C T L 1 2 7 の電位をト

10

20

30

40

50

ランジスタ 127 がオン状態になる電位にする（図 4（B）の S1、第 1 のステップ）。次に、電源電圧 Vp の出力を再開する（図 4（B）の S2、第 2 のステップ）。次に、クロック信号が入力される配線をクロック信号 GCK におけるハイレベルの電位と同等の値にした後、クロック信号 GCK の出力を再開する（図 4（B）の S3、第 3 のステップ）。次にスタート信号 GSP の出力を再開する（図 4（B）の S4、第 4 のステップ）。

【0108】

以上のように、誤動作を引き起こすことなく、駆動回路 121A の動作、例えば駆動回路 121A に向けての駆動回路 121A が動作するための信号又は電圧の出力を再開することができる。

【0109】

なお、これに限定されず、駆動回路 121B へ向けた駆動回路 121B を動作させるための信号又は電圧（電源電圧 Vp、スタート信号 SSP、及びクロック信号 SCK）の出力の再開も駆動回路 121A と同様に行うことができる。

【0110】

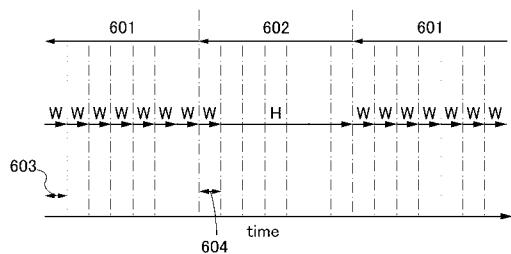

また、図 5 に動画を表示する期間 601、又は静止画を表示する期間 602 における、フレーム期間毎の画像信号の書き込み頻度を示す。図 5 は、フレーム期間毎の画像信号の書き込み頻度を示す模式図であり、「W」は画像信号を書き込む期間であり、「H」は画像信号を保持する期間であり、期間 603 は単位フレーム期間である。

【0111】

このように、本実施の形態の液晶表示装置の構成において、期間 602 で表示される静止画の画像信号は期間 604 に書き込まれ、期間 604 で書き込まれた画像信号は、期間 602 の他の期間で保持される。

【0112】

さらに、図 1 に示す液晶表示装置の温度が変動する場合について、以下に説明する。

【0113】

本実施の形態の液晶表示装置に用いられるトランジスタは、温度により電気特性の変動が生じる。該トランジスタにおける温度による電気特性の変動について以下に説明する。

【0114】

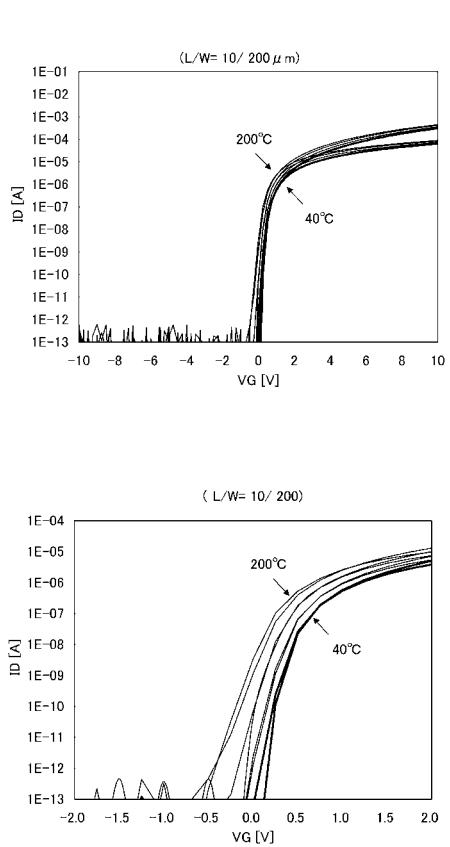

トランジスタを形成した基板を 40、85、150、及び 200 のそれぞれの温度で一定温度とし、ドレイン電圧を 1V 及び 10V の 2 つの条件とし、ゲート電位（VG ともいう）を -10V から 10V まで変化させて VG - ID 特性を取得した。なお、ID とは、ソース及びドレインの間に流れる電流である。また、測定したトランジスタは、チャネル長 L が 10 μm であり、チャネル幅が 200 μm であり、ゲート絶縁層の膜厚が 100 nm である。

【0115】

図 6（A）は、上記それぞれの温度で測定したトランジスタの VG - ID 特性を重ね書きした図であり、図 6（B）は、図 6（A）に示すゲート電位が -2V から 2V までの領域を拡大した図である。図中の矢印で示す右端の曲線が 40、左端が 200 で取得した曲線で、その他の温度で取得した曲線は、その間に位置する。図 6（A）及び図 6（B）に示すように、温度が上昇するに従って、カットオフ電流（VG = 0V のときのドレイン電流）が大きくなり、トランジスタがオフ状態であってもリーク電流が発生するなどの問題が生じる。

【0116】

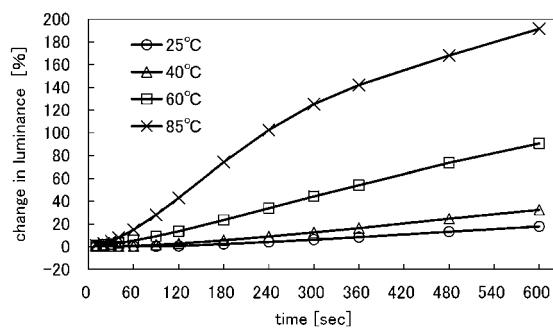

さらに、該トランジスタを用いた液晶表示装置の画像データの書き込み後の電圧保持特性について、図 7 に示す。図 7 は、液晶表示装置における画素に画像信号 img のデータを書き込み、その後駆動回路が停止した後の画素の輝度の経時変化を示す図であり、横軸が保持期間（例えば図 5 における期間 602）であり、縦軸が基準値に対する画素の輝度変化の割合である。図 7 では、輝度が上昇するほど、画像が白に近づく。

【0117】

図 7 に示すように、高温になるほど、また、保持期間が長くなるほど画素の輝度変化が大

10

20

30

40

50

きくなっていることがわかる。これは、温度上昇により、画像信号線と液晶素子の間に設けられたトランジスタのリーク電流が大きくなり、液晶素子の画素電極の電位が変化するためである。

【0118】

これに対し、本実施の形態の液晶表示装置では、液晶表示装置の温度に応じて駆動回路部121を動作させるための信号及び電圧を駆動回路部121に供給するのを停止してから再開するまでの期間の長さを設定する。これにより、トランジスタの電気特性が温度により変動した場合であっても、表示画像へ向けた影響を低減することができる。

【0119】

例えば、液晶表示装置の温度が上昇するにつれて、駆動回路部121への駆動回路部121を動作させるための信号及び電圧の供給を停止してから再開するまでの期間の長さを短くする。すると、画素123に画像信号のデータを書き込む間隔が短くなる。例えば、図7の結果では、輝度変化が20%以上変化すると表示される画像の変化が顕著になる。よって、例えば60では、保持時間が180秒となるように、駆動回路部121への駆動回路部121を動作させるための信号及び電圧の供給を停止してから再開するまでの期間の長さを設定することが好ましい。また、85では、保持時間が60秒となるように、駆動回路部121への駆動回路部121を動作させるための信号及び電圧の供給を停止してから再開するまでの期間の長さを設定することが好ましい。これにより、温度変化による画像の輝度変化の影響を低減することができる。

【0120】

本実施の形態の液晶表示装置は、画像信号の書き込み頻度を低減することができる。よって、消費電力を低減することができる。

【0121】

また、同一の画像を複数回書き換えて静止画を表示する場合、画像の切り替わりが視認できると、人間は目に疲労を感じことがある。本実施の形態の液晶表示装置は、画像信号の書き込み頻度が削減されているため、目の疲労を減らすといった効果もある。

【0122】

特に、本実施の形態の液晶表示装置は、オフ電流が低減されたトランジスタを各画素のトランジスタに適用することにより、液晶素子又は保持容量で電圧を保持する期間を長くすることができる。その結果、画像信号の書き込み頻度を低減することができるため、消費電力を低減することができ、また、目の疲労を低減することができる。

【0123】

(実施の形態2)

本実施の形態では、上記実施の形態に示す表示装置における走査線駆動回路及び信号線駆動回路に適用可能なシフトレジスタの一例について説明する。

【0124】

本実施の形態におけるシフトレジスタの構成の一例について、図8を用いて説明する。図8は、本実施の形態におけるシフトレジスタの構成の一例を示す図である。

【0125】

図8(A)に示すシフトレジスタは、第1のパルス出力回路10\_1乃至第Nのパルス出力回路10\_N(Nは3以上の自然数)を有する。

【0126】

第1のパルス出力回路10\_1乃至第Nのパルス出力回路10\_Nのそれぞれは、第1の入力端子21、第2の入力端子22、第3の入力端子23、第4の入力端子24、第5の入力端子25、第1の出力端子26、及び第2の出力端子27を有する(図8(B)参照)。各パルス出力回路において、第1の入力端子21、第2の入力端子22、及び第3の入力端子23のそれぞれは、第1の配線11乃至第4の配線14のうち、異なる一つの配線に電気的に接続される。

【0127】

図8(A)及び図8(B)において、第1のパルス出力回路10\_1は、第1の入力端子

10

20

30

40

50

2 1 が第 1 の配線 1 1 に電気的に接続され、第 2 の入力端子 2 2 が第 2 の配線 1 2 に電気的に接続され、第 3 の入力端子 2 3 が第 3 の配線 1 3 に電気的に接続される。

【 0 1 2 8 】

また、図 8 ( A ) 及び図 8 ( B ) において、第 2 のパルス出力回路 1 0 \_ 2 は、第 1 の入力端子 2 1 が第 2 の配線 1 2 に電気的に接続され、第 2 の入力端子 2 2 が第 3 の配線 1 3 に電気的に接続され、第 3 の入力端子 2 3 が第 4 の配線 1 4 に電気的に接続される。

【 0 1 2 9 】

図 8 ( A ) に示すシフトレジスタは、第 1 の配線 1 1 を介して第 1 のクロック信号 C K 1 が入力され、第 2 の配線 1 2 を介して第 2 のクロック信号 C K 2 が入力され、第 3 の配線 1 3 を介して第 3 のクロック信号 C K 3 が入力され、第 4 の配線 1 4 を介して第 4 のクロック信号 C K 4 が入力される。

【 0 1 3 0 】

なお、第 1 のクロック信号 C K 1 乃至第 4 のクロック信号 C K 4 は、ハイレベルとロー レベルを繰り返すデジタル信号である。また、第 1 のクロック信号 C K 1 乃至第 4 のクロック信号 C K 4 は、順に 1 / 4 周期分遅延している。本実施の形態のシフトレジスタは、第 1 のクロック信号 C K 1 乃至第 4 のクロック信号 C K 4 を用いてパルス出力回路の駆動を制御する。

【 0 1 3 1 】

また、第 1 のパルス出力回路 1 0 \_ 1 は、第 4 の入力端子 2 4 が第 5 の配線 1 5 に電気的に接続される。本実施の形態のシフトレジスタは、第 5 の配線 1 5 を介してスタート信号 S P 1 ( 第 1 のスタートパルス ) が入力される。

【 0 1 3 2 】

また、2 段目以降の第 n のパルス出力回路 1 0 \_ n ( n は、2 以上 N 以下の自然数 ) は、一段前段のパルス出力回路 1 0 \_ n - 1 から前段信号 O U T ( n - 1 ) が入力される。

【 0 1 3 3 】

また、第 1 のパルス出力回路 1 0 \_ 1 は、2 段後段の第 3 のパルス出力回路 1 0 \_ 3 から信号が入力され、2 段目以降の第 1 ( 1 は 2 以上 N - 2 以下の自然数 ) のパルス出力回路 1 0 \_ 1 は、2 段後段の第 1 + 2 のパルス出力回路 1 0 \_ 1 + 2 から後段信号 O U T ( 1 + 2 ) が入力される。

【 0 1 3 4 】

また、各段のパルス出力回路は、前段及び / 又は後段のパルス出力回路に第 1 の出力信号を出力し、電気的に接続された別の配線などに第 2 の出力信号を出力する。

【 0 1 3 5 】

例えば、図 8 ( A ) 及び図 8 ( B ) において、第 1 のパルス出力回路 1 0 \_ 1 は、第 4 の入力端子 2 4 を介してスタート信号が入力され、第 5 の入力端子 2 5 を介して後段信号 ( 第 3 のパルス出力回路 1 0 \_ 3 の第 2 の出力信号 ) が入力され、第 1 の出力端子 2 6 を介して第 1 の出力信号を出力し、第 2 の出力端子 2 7 を介して第 2 の出力信号を出力する。

【 0 1 3 6 】

なお、N - 1 段目のパルス出力回路 1 0 \_ N - 1 及び N 段目のパルス出力回路及び 1 0 \_ N は、後段信号 O U T ( 1 + 2 ) が入力されないため、図 8 ( A ) に示すシフトレジスタのように、該シフトレジスタを、別途第 6 の配線 1 7 を介して第 2 のスタート信号 S P 2 が N - 1 段目のパルス出力回路 1 0 \_ N - 1 に入力され、第 7 の配線 1 8 を介して第 3 のスタート信号 S P 3 が N 段目のパルス出力回路 1 0 \_ N に入力される構成としてもよい。また、第 2 のスタート信号 S P 2 及び第 3 のスタート信号 S P 3 に限定されず、第 2 のスタート信号 S P 2 及び第 3 のスタート信号 S P 3 の代わりに内部で生成された信号を用いてもよい。例えば、画素部へ向けたパルス出力に寄与しない第 N + 1 のパルス出力回路 1 0 \_ N + 1 及び第 N + 2 のパルス出力回路 1 0 \_ N + 2 ( ダミー段のパルス出力回路ともいう ) を設け、第 N + 1 のパルス出力回路 1 0 \_ N + 1 の第 1 の出力信号を第 N - 1 のパルス出力回路 1 0 \_ N - 1 の第 5 の入力端子 2 5 に入力し、第 N + 2 のパルス出力回路 1 0 \_ N + 2 の第 1 の出力信号を第 N のパルス出力回路 1 0 \_ N の第 5 の入力端子 2 5 に入

10

20

30

40

50

力する構成としてもよい。また、別途シフトレジスタの内部で生成された信号を用いる構成としてもよい。

【0137】

次に、図8(B)に示すパルス出力回路の回路構成の一例について、図8(C)を用いて説明する。図8(C)は、図8(B)に示すパルス出力回路の回路構成の一例を示す回路図である。

【0138】

図8(C)に示すパルス出力回路は、トランジスタ31と、トランジスタ32と、トランジスタ33と、トランジスタ34と、トランジスタ35と、トランジスタ36と、トランジスタ37と、トランジスタ38と、トランジスタ39と、トランジスタ40と、トランジスタ41と、を有する。

10

【0139】

トランジスタ31は、ソース及びドレインの一方が電源線51に電気的に接続され、ゲートが第4の入力端子24に電気的に接続される。

【0140】

トランジスタ32は、ソース及びドレインの一方が電源線52に電気的に接続され、ソース及びドレインの他方がトランジスタ31のソース及びドレインの他方に電気的に接続される。

【0141】

トランジスタ33は、ソース及びドレインの一方が第1の入力端子21に電気的に接続され、ソース及びドレインの他方が第1の出力端子26に電気的に接続される。

20

【0142】

トランジスタ34は、ソース及びドレインの一方が電源線52に電気的に接続され、ソース及びドレインの他方が第1の出力端子26に電気的に接続され、ゲートがトランジスタ32のゲートに電気的に接続される。

【0143】

トランジスタ35は、ソース及びドレインの一方が電源線52に電気的に接続され、ソース及びドレインの他方がトランジスタ32のゲートに電気的に接続され、ゲートが第4の入力端子24に電気的に接続される。

【0144】

トランジスタ36は、ソース及びドレインの一方が電源線51に電気的に接続され、ソース及びドレインの他方がトランジスタ32のゲートに電気的に接続され、ゲートが第5の入力端子25に電気的に接続される。

30

【0145】

トランジスタ37は、ソース及びドレインの一方が電源線51に電気的に接続され、ゲートが第3の入力端子23に電気的に接続される。

【0146】

トランジスタ38は、ソース及びドレインの一方がトランジスタ32のゲートに電気的に接続され、ソース及びドレインの他方がトランジスタ37のソース及びドレインの他方に電気的に接続され、ゲートが第2の入力端子22に電気的に接続される。

40

【0147】

トランジスタ39は、ソース及びドレインの一方がトランジスタ31のソース及びドレインの他方、並びにトランジスタ32のソース及びドレインの他方に電気的に接続され、ソース及びドレインの他方がトランジスタ33のゲートに電気的に接続され、ゲートが電源線51に電気的に接続される。

【0148】

トランジスタ40は、ソース及びドレインの一方が第1の入力端子21に電気的に接続され、ソース及びドレインの他方が第2の出力端子27に電気的に接続され、ゲートがトランジスタ39のソース及びドレインの他方に電気的に接続される。

【0149】

50

トランジスタ 4 1 は、ソース及びドレインの一方が電源線 5 2 に電気的に接続され、ソース及びドレインの他方が第 2 の出力端子 2 7 に電気的に接続され、ゲートがトランジスタ 3 2 のゲートに電気的に接続される。

【 0 1 5 0 】

なお、図 8 ( C ) において、トランジスタ 3 3 のゲートと、トランジスタ 4 0 のゲートと、トランジスタ 3 9 のソース及びドレインの他方との接続箇所をノード N A とする。また、トランジスタ 3 2 のゲートと、トランジスタ 3 4 のゲートと、トランジスタ 3 5 のソース及びドレインの他方と、トランジスタ 3 6 のソース及びドレインの他方と、トランジスタ 3 8 のソース及びドレインの一方と、トランジスタ 4 1 のゲートとの接続箇所をノード N B とする。

10

【 0 1 5 1 】

例えば、第 1 のパルス出力回路 1 0 \_ 1 の場合、第 1 のパルス出力回路 1 0 \_ 1 には、第 1 の入力端子 2 1 を介して第 1 のクロック信号 C K 1 が入力され、第 2 の入力端子 2 2 を介して第 2 のクロック信号 C K 2 が入力され、第 3 の入力端子 2 3 を介して第 3 のクロック信号 C K 3 が入力され、第 4 の入力端子 2 4 を介してスタート信号 S P が入力され、第 5 の入力端子 2 5 を介して第 3 のパルス出力回路 1 0 \_ 3 の第 1 の出力端子 2 6 を介して出力される信号が入力される。また、第 1 のパルス出力回路 1 0 \_ 1 は、第 1 の出力端子 2 6 を介して第 1 の出力信号を出力し、第 2 の出力端子 2 7 を介して第 2 の出力信号である信号 O U T ( 1 ) を出力する。

【 0 1 5 2 】

20

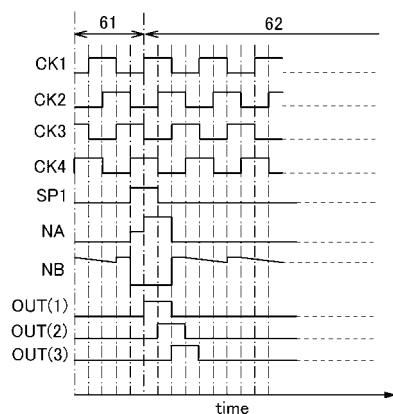

ここで、図 8 ( A ) 乃至図 8 ( C ) に示すシフトレジスタにおける動作例について、図 9 を用いて説明する。図 9 は、図 8 に示すシフトレジスタの動作の一例を示すタイミングチャートである。なお、走査線駆動回路に用いられるシフトレジスタの場合、図 9 に示す期間 6 1 は垂直帰線期間であり、期間 6 2 はゲート選択期間に相当する。

【 0 1 5 3 】

上記構成とすることにより、駆動回路部を常時動作することなく、静止画を表示することができる。

【 0 1 5 4 】

なお、本実施の形態は、他の実施の形態と適宜組み合わせ、又は置き換えを行うことができる。

30

【 0 1 5 5 】

( 実施の形態 3 )

本実施の形態では、上記実施の形態に示す表示装置に適用可能なトランジスタについて説明する。

【 0 1 5 6 】

上記実施の形態に示す表示装置に適用可能なトランジスタの構造としては、例えばトップゲート構造又はボトムゲート構造などが挙げられる。さらに、ボトムゲート構造としては、例えばスタガ型及びプレーナ型などを用いることができる。

【 0 1 5 7 】

また、上記実施の形態に示すトランジスタは、チャネル形成領域が一つ形成される構造 ( シングルゲート構造ともいう ) 、チャネル形成領域が複数形成される構造 ( マルチゲート構造ともいう ) であってもよい。また、上記実施の形態に示す表示装置に適用可能なトランジスタは、チャネル形成領域の上下にゲート絶縁層を介して配置された 2 つのゲート電極層を有する構造 ( デュアルゲート構造ともいう ) などであってもよい。

40

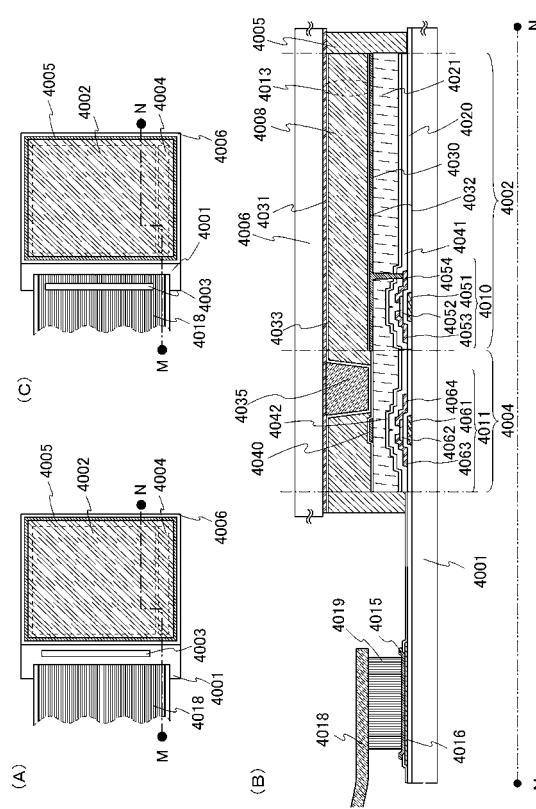

【 0 1 5 8 】

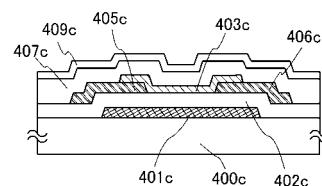

本実施の形態のトランジスタの構造例について、図 1 0 ( A ) 乃至図 1 0 ( D ) を用いて説明する。図 1 0 ( A ) 乃至図 1 0 ( D ) は、本実施の形態におけるトランジスタの構造例を示す断面模式図である。

【 0 1 5 9 】

図 1 0 ( A ) に示すトランジスタは、ボトムゲート構造のトランジスタの一つであり、逆

50

スタガ型トランジスタともいう。

【0160】

図10(A)に示すトランジスタは、ゲート電極層401aと、ゲート絶縁層402aと、酸化物半導体層403aと、ソース電極層405aと、ドレイン電極層406aと、を有する。

【0161】

ゲート電極層401aは、基板400aの上に設けられ、ゲート絶縁層402aは、ゲート電極層401aの上に設けられ、酸化物半導体層403aは、ゲート絶縁層402aを挟んでゲート電極層401aの上に設けられ、ソース電極層405a及びドレイン電極層406aは、酸化物半導体層403aの上にそれぞれ設けられる。

10

【0162】

さらに、図10(A)に示すトランジスタにおいて、酸化物半導体層403aは、上面の一部(上面にソース電極層405a及びドレイン電極層406aが設けられていない部分)に酸化物絶縁層407aが接する。また、酸化物絶縁層407aは、上部に保護絶縁層409aが設けられる。

【0163】

図10(B)に示すトランジスタは、ボトムゲート構造の一つであるチャネル保護型(チャネルトップ型ともいう)トランジスタであり、逆スタガ型トランジスタともいう。

20

【0164】

図10(B)に示すトランジスタは、ゲート電極層401bと、ゲート絶縁層402bと、酸化物半導体層403bと、絶縁層427と、ソース電極層405bと、ドレイン電極層406bと、を有する。

【0165】

ゲート電極層401bは、基板400bの上に設けられ、ゲート絶縁層402bは、ゲート電極層401bの上に設けられ、酸化物半導体層403bは、ゲート絶縁層402bを挟んでゲート電極層401bの上に設けられ、絶縁層427は、ゲート絶縁層402b及び酸化物半導体層403bを挟んでゲート電極層401bの上に設けられ、ソース電極層405b及びドレイン電極層406bは、絶縁層427を挟んで酸化物半導体層403bの上にそれぞれ設けられる。

30

【0166】

さらに、図10(B)に示すトランジスタは、上部に保護絶縁層409bが接する。

【0167】

図10(C)に示すトランジスタは、ボトムゲート構造のトランジスタの一つである。

【0168】

図10(C)に示すトランジスタは、ゲート電極層401cと、ゲート絶縁層402cと、酸化物半導体層403cと、ソース電極層405cと、ドレイン電極層406cと、を有する。

40

【0169】

ゲート電極層401cは、基板400cの上に設けられ、ゲート絶縁層402cは、ゲート電極層401cの上に設けられ、ソース電極層405c及びドレイン電極層406cは、ゲート絶縁層402cの上に設けられ、酸化物半導体層403cは、ゲート絶縁層402c、ソース電極層405c、及びドレイン電極層406cを挟んでゲート電極層401cの上に設けられる。

【0170】

さらに、図10(C)に示すトランジスタにおいて、酸化物半導体層403cは、上面及び側面に酸化物絶縁層407cが接する。また、酸化物絶縁層407cは、上部に保護絶縁層409cが設けられる。

【0171】

図10(D)に示すトランジスタは、トップゲート構造のトランジスタの一つである。

【0172】

50

図10(D)に示すトランジスタは、ゲート電極層401dと、ゲート絶縁層402dと、酸化物半導体層403dと、ソース電極層405dと、ドレイン電極層406dと、を有する。

【0173】

酸化物半導体層403dは、下地層447を挟んで基板400dの上に設けられ、ソース電極層405d及びドレイン電極層406dは、酸化物半導体層403dの一部の上にそれぞれ設けられ、ゲート絶縁層402dは、酸化物半導体層403d、ソース電極層405d、及びドレイン電極層406dの上に設けられ、ゲート電極層401dは、ゲート絶縁層402dを挟んで酸化物半導体層403dの上に設けられる。

【0174】

さらに、図10(D)に示すトランジスタにおいて、ソース電極層405dは、ゲート絶縁層402dに設けられた開口部を介して配線層436に接し、ドレイン電極層406dは、ゲート絶縁層402dに設けられた開口部を介して配線層437に接する。

【0175】

基板400a乃至基板400dとしては、例えばバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

【0176】

また、基板400a乃至基板400dとして、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いることもできる。また、基板400a乃至基板400dとして、結晶化ガラスを用いることもできる。また、基板400a乃至基板400dとして、プラスチック基板などを用いることもできる。また、基板400a乃至基板400dとして、シリコンなどの半導体基板を用いることもできる。

【0177】

下地層447は、基板400dからの不純物元素の拡散を防止する機能を有する。下地層447としては、例えば窒化シリコン層、酸化シリコン層、窒化酸化シリコン層、酸化窒化シリコン層、酸化アルミニウム層、又は酸化窒化アルミニウム層を用いることができる。また、下地層447に適用可能な材料の層の積層により下地層447を構成することもできる。

【0178】

なお、図10(A)、図10(B)、及び図10(C)に示すトランジスタにおいて、図10(D)に示すトランジスタと同様に、基板とゲート電極層の間に下地層を設けてもよい。

【0179】

ゲート電極層401a乃至ゲート電極層401dとしては、例えばモリブデン、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、ゲート電極層401a乃至ゲート電極層401dに適用可能な材料の層の積層により、ゲート電極層401a乃至ゲート電極層401dを構成することもできる。

【0180】

ゲート絶縁層402a乃至ゲート絶縁層402dとしては、例えば酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を用いることができる。また、ゲート絶縁層402a乃至ゲート絶縁層402dに適用可能な材料の層の積層によりゲート絶縁層402a乃至ゲート絶縁層402dを構成することもできる。ゲート絶縁層402a乃至ゲート絶縁層402dに適用可能な材料の層は、例えばプラズマCVD法又はスパッタリング法などを用いて形成することができる。例えば、プラズマCVD法により窒化シリコン層を形成し、プラズマCVD法により窒化シリコン層の上に酸化シリコン層を形成することによりゲート絶縁層402a乃至ゲート絶縁層402dを作製することができる。

【0181】

10

20

30

40

50

酸化物半導体層 4 0 3 a 乃至酸化物半導体層 4 0 3 d に適用可能な酸化物半導体としては、例えば四元系金属酸化物、三元系金属酸化物、又は二元系金属酸化物などが挙げられる。四元系金属酸化物としては、例えば In - Sn - Ga - Zn - O 系金属酸化物などが挙げられる。三元系金属酸化物としては、例えば In - Ga - Zn - O 系金属酸化物、In - Sn - Zn - O 系金属酸化物、In - Al - Zn - O 系金属酸化物、Sn - Ga - Zn - O 系金属酸化物、Al - Ga - Zn - O 系金属酸化物、又は Sn - Al - Zn - O 系金属酸化物などが挙げられる。二元系金属酸化物としては、In - Zn - O 系金属酸化物、Sn - Zn - O 系金属酸化物、Al - Zn - O 系金属酸化物、Zn - Mg - O 系金属酸化物、Sn - Mg - O 系金属酸化物、In - Mg - O 系金属酸化物、又は In - Sn - O 系金属酸化物などが挙げられる。また、酸化物半導体としては、In - O 系金属酸化物、Sn - O 系金属酸化物、又は Zn - O 系金属酸化物などが挙げられる。また、上記酸化物半導体として適用可能な金属酸化物に SiO<sub>2</sub> が含まれていてもよい。また、例えば In - Ga - Zn - O 系金属酸化物とは、少なくとも In と Ga と Zn を含む酸化物であり、その組成比に特に制限はない。また、In - Ga - Zn - O 系金属酸化物に In と Ga と Zn 以外の元素が含まれていてもよい。

#### 【 0 1 8 2 】

また、酸化物半導体層 4 0 3 a 乃至酸化物半導体層 4 0 3 d に適用可能な酸化物半導体としては、化学式 InMO<sub>3</sub> (ZnO)<sub>m</sub> (m は 0 より大きい数) で表記される金属酸化物も挙げられる。ここで、M は、Ga、Al、Mn 及び Co から選ばれた一つ又は複数の金属元素を示す。M としては、例えば Ga、Ga 及び Al、Ga 及び Mn、又は Ga 及び Co などがある。

#### 【 0 1 8 3 】

ソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d としては、例えばアルミニウム、クロム、銅、タンタル、チタン、モリブデン、若しくはタングステンなどの金属材料、又はこれらの金属材料を主成分とする合金材料の層を用いることができる。また、ソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d に適用可能な材料の層の積層によりソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d のそれぞれを構成することができる。

#### 【 0 1 8 4 】

例えば、アルミニウム又は銅の金属層と、チタン、モリブデン、タングステンなどの高融点金属層との積層によりソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d を構成することができる。また、複数の高融点金属層の間にアルミニウム又は銅の金属層が設けられた積層によりソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d を構成することもできる。また、ヒロックやウィスカーの発生を防止する元素 (Si、Nd、Sc など) が添加されているアルミニウム層を用いてソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d を構成することにより、耐熱性を向上させることができる。

#### 【 0 1 8 5 】

また、ソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d として、導電性の金属酸化物を含む層を用いることもできる。導電性の金属酸化物としては、例えば酸化インジウム (In<sub>2</sub>O<sub>3</sub>)、酸化スズ (SnO<sub>2</sub>)、酸化亜鉛 (ZnO)、酸化インジウム酸化スズ合金 (In<sub>2</sub>O<sub>3</sub> - SnO<sub>2</sub>、ITO と略記する)、若しくは酸化インジウム酸化亜鉛合金 (In<sub>2</sub>O<sub>3</sub> - ZnO)、又はこれらの金属酸化物に酸化シリコンを含ませたものを用いることができる。

#### 【 0 1 8 6 】

さらに、ソース電極層 4 0 5 a 乃至ソース電極層 4 0 5 d、及びドレイン電極層 4 0 6 a 乃至ドレイン電極層 4 0 6 d の形成に用いられる材料を用いて他の配線を形成してもよい。

10

20

30

40

50

## 【0187】

配線層436及び配線層437としては、ソース電極層405a乃至ソース電極層405d、及びドレイン電極層406a乃至ドレイン電極層406dに適用可能な材料の層を用いることができる。また、配線層436及び配線層437に適用可能な材料の層の積層により配線層436及び配線層437を構成することもできる。

## 【0188】

絶縁層427としては、例えば下地層447に適用可能な材料の層を用いることができる。また、絶縁層427に適用可能な材料の層の積層により絶縁層427を構成することもできる。

## 【0189】

酸化物絶縁層407a及び酸化物絶縁層407cとしては、酸化物絶縁層を用いることができ、例えば酸化シリコン層などを用いることができる。また、酸化物絶縁層407a及び酸化物絶縁層407cに適用可能な材料の層の積層により酸化物絶縁層407a及び酸化物絶縁層407cを構成することもできる。

## 【0190】

保護絶縁層409a乃至保護絶縁層409cとしては、無機絶縁層を用いることができ、例えば窒化シリコン層、窒化アルミニウム層、窒化酸化シリコン層、又は窒化酸化アルミニウム層などを用いることができる。また、保護絶縁層409a乃至保護絶縁層409cに適用可能な材料の層の積層により保護絶縁層409a乃至保護絶縁層409cを構成することもできる。

10

## 【0191】

なお、上記実施の形態の表示装置では、本実施の形態のトランジスタに起因する表面凹凸を低減するために、トランジスタの上（酸化物絶縁層又は保護絶縁層を有する場合には酸化物絶縁層又は保護絶縁層を挟んでトランジスタの上）に平坦化絶縁層を有する構成とすることもできる。平坦化絶縁層としては、ポリイミド、アクリル、ベンゾシクロブテン、などの有機材料の層を用いることができる。また平坦化絶縁層としては、低誘電率材料（low-k材料）の層を用いることもできる。また、平坦化絶縁層に適用可能な材料の層の積層により平坦化絶縁層を構成することもできる。

20

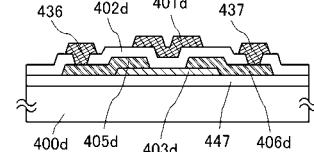

## 【0192】

さらに、本実施の形態のトランジスタの作製方法の一例として、図10(A)に示すトランジスタの作製方法の一例について、図11を用いて説明する。図11は、図10(A)に示すトランジスタの作製方法の一例を示す図である。なお、本実施の形態のトランジスタの作製方法の一例として、図10(A)に示すトランジスタの作製方法の一例を示すが、これに限定されず、例えば図10(B)乃至図10(D)に示す各構成要素において、符号を除く名称が図10(A)に示す各構成要素と同じであれば、図10(A)に示すトランジスタの作製方法の一例の説明を適宜援用することができる。

30

## 【0193】

まず、基板400aを準備し、基板400aの上に第1の導電膜を形成する。

## 【0194】

また、基板400aの一例としてガラス基板を用いる。

40

## 【0195】

また、第1の導電膜としては、例えばモリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の膜を用いることができる。また、第1の導電膜に適用可能な材料の膜の積層膜により、第1の導電膜を構成することもできる。

## 【0196】

次に、第1のフォトリソグラフィ工程により第1の導電膜の上に第1のレジストマスクを形成し、第1のレジストマスクを用いて選択的に第1の導電膜のエッチングを行うことによりゲート電極層401aを形成し、第1のレジストマスクを除去する。

## 【0197】

50

なお、本実施の形態において、インクジェット法を用いてレジストマスクを形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0198】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクは、透過した光が複数の強度となる露光マスクである。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、製造工程を簡略にすることができる。

10

【0199】

次に、ゲート電極層401aの上にゲート絶縁層402aを形成する。

【0200】

本実施の形態のトランジスタに用いられる酸化物半導体は、不純物を除去され、I型化又は実質的にI型化された酸化物半導体を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、酸化物半導体層とゲート絶縁層との界面は重要である。そのため、高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。よって、ゲート絶縁層402aは、膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できる絶縁層であることが好ましい。

20

【0201】

例えば、高密度プラズマCVD法を用いてゲート絶縁層402aを形成することができる。例えばμ波（例えば、周波数2.45GHzのμ波）を用いた高密度プラズマCVD法は、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるため、好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位が低減し、界面特性を良好にすることができる。

30

【0202】

また、スパッタリング法やプラズマCVD法など、他の成膜方法を用いてゲート絶縁層402aを形成することもできる。また、ゲート絶縁層402aを形成後に熱処理を行ってもよい。該熱処理を行うことによりゲート絶縁層402aの膜質、酸化物半導体との界面特性を改質させることができる。

【0203】

次に、ゲート絶縁層402aの上に膜厚2nm以上200nm以下、好ましくは5nm以上30nm以下の酸化物半導体膜530を形成する（図11（A）参照）。例えばスパッタリング法を用いて酸化物半導体膜530を形成することができる。

【0204】

なお、酸化物半導体膜530を形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層402aの表面に付着している粉状物質（パーティクル、ごみともいう）を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加することによりプラズマを形成して基板の表面を改質する方法である。なお、アルゴンに代えて窒素、ヘリウム、酸素などを用いてもよい。

40

【0205】

例えば、酸化物半導体層403aに適用可能な酸化物半導体材料を用いて酸化物半導体膜530を形成することができる。本実施の形態では、In-Ga-Zn-O系酸化物ターゲットを用いてスパッタリング法により酸化物半導体膜530を形成する。また、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下にお

50

いて、スパッタリング法により酸化物半導体膜 530 を形成することもできる。

【0206】

スパッタリング法を用いて酸化物半導体膜 530 を作製するためのターゲットとしては、例えば、 $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 1$  [mol 数比] の組成比である酸化物ターゲットを用いることができる。また、上記に示すターゲットに限定されず、例えば、 $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 2$  [mol 数比] の組成比である酸化物ターゲットを用いてもよい。また、作製される酸化物ターゲットのうち、全体の体積に対して全体の体積から空隙などが占める空間を除いた部分の体積の割合（充填率ともいう）は、90%以上100%以下、好ましくは95%以上99.9%である。充填率の高い金属酸化物ターゲットを用いることにより形成した酸化物半導体膜は、緻密な膜となる。

10

【0207】

なお、酸化物半導体膜 530 を形成する際に用いるスパッタガスとしては、例えば水素、水、水酸基、又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0208】

また、酸化物半導体膜 530 を形成する前に、スパッタリング装置の予備加熱室でゲート電極層 401a が形成された基板 400a、又はゲート電極層 401a 及びゲート絶縁層 402a が形成された基板 400a を予備加熱し、基板 400a に吸着した水素、水分などの不純物を脱離し、排気することができる。上記予備加熱により、ゲート絶縁層 402a 及び酸化物半導体膜 530 に水素、水酸基、及び水分への侵入を抑制することができる。なお、予備加熱室に設ける排気手段として、クライオポンプを用いることが好ましい。また、上記予備加熱の処理を省略することもできる。また、上記予備加熱は、酸化物絶縁層 407a の成膜前に、ソース電極層 405a 及びドレイン電極層 406a まで形成した基板 400a にも同様に行つてもよい。

20

【0209】

また、スパッタリング法を用いて酸化物半導体膜 530 を形成する場合、減圧状態に保持された成膜室内に基板 400a を保持し、基板温度を 100 以上 600 以下好ましくは 200 以上 400 以下とする。基板 400a を加熱することにより、形成する酸化物半導体膜 530 に含まれる不純物濃度を低減することができる。また、基板 400a を加熱することにより、スパッタリング法による損傷が軽減する。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板 400a の上に酸化物半導体膜 530 を成膜する。

30

【0210】

成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを設けたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水素原子を含む化合物（水など）、より好ましくは水素原子及び炭素原子を含む化合物などが排気されるため、クライオポンプを用いることにより、当該成膜室で形成した酸化物半導体膜 530 に含まれる不純物の濃度を低減することができる。

40

【0211】

成膜条件の一例としては、基板 400a とターゲットの間との距離を 100 mm、圧力 0.6 Pa、直流 (DC) 電源 0.5 kW、酸素（酸素流量比率 100%）雰囲気下の条件が適用される。なお、パルス直流電源を用いたスパッタリング法は、成膜時に発生する粉状物質が軽減でき、膜厚分布も均一となるために好ましい。

【0212】

次に、第 2 のフォトリソグラフィ工程により酸化物半導体膜 530 の上に第 2 のレジストマスクを形成し、第 2 のレジストマスクを用いて選択的に酸化物半導体膜 530 のエッチングを行うことにより、酸化物半導体膜 530 を島状の酸化物半導体層に加工し、第 2 のレジストマスクを除去する。

50

## 【0213】

なお、ゲート絶縁層402aにコンタクトホールを形成する場合、酸化物半導体膜530を島状の酸化物半導体層に加工する際に該コンタクトホールを形成することもできる。

## 【0214】

例えば、ドライエッチング、ウェットエッチング、又はドライエッチング及びウェットエッチングの両方を用いて酸化物半導体膜530のエッチングを行うことができる。例えば、酸化物半導体膜530のウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N（関東化学社製）を用いてもよい。

## 【0215】

次に、酸化物半導体層に第1の加熱処理を行う。第1の加熱処理によって酸化物半導体層の脱水化又は脱水素化を行うことができる。第1の加熱処理の温度は、350以上750以下、又は350以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層403aを得る（図11（B）参照）。

## 【0216】

なお、加熱処理装置は、電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置などのRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

## 【0217】

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。

## 【0218】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴンなどの希ガスに、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴンなどの希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.99999%）以上、（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。

## 【0219】

また、第1の加熱処理で酸化物半導体層を加熱した後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥工ア（露点が-40以下、好ましくは-60以下）を導入してもよい。酸素ガス又はN<sub>2</sub>Oガスには、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する酸素ガス又はN<sub>2</sub>Oガスの純度を、6N以上、好ましくは7N以上、（即ち、酸素ガス又はN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。酸素ガス又はN<sub>2</sub>Oガスの作用により、脱水化又は脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層403aを高純度化させる。

## 【0220】

また、島状の酸化物半導体層に加工する前の酸化物半導体膜530に第1の加熱処理を行うこともできる。その場合には、第1の加熱処理後に加熱装置から基板を取り出し、島状

10

20

30

40

50

の酸化物半導体層への加工を行う。

【0221】

また、上記以外にも、酸化物半導体層成膜後であれば、酸化物半導体層403a上にソース電極層405a及びドレイン電極層406aを形成した後、又はソース電極層405a及びドレイン電極層406aの上に酸化物絶縁層407aを形成した後に第1の加熱処理を行ってもよい。

【0222】

また、ゲート絶縁層402aにコンタクトホールを形成する場合、酸化物半導体膜530に第1の加熱処理を行う前にコンタクトホールを形成してもよい。

【0223】

また、酸化物半導体膜を2回に分けて成膜し、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域（単結晶領域）、即ち、膜表面に垂直にc軸配向した結晶領域を有する膜を形成し、該膜を用いて酸化物半導体層を形成してもよい。例えば、3nm以上15nm以下の第1の酸化物半導体膜を成膜し、窒素、酸素、希ガス、又は乾燥空気の雰囲気下で450以上850以下、好ましくは550以上750以下の第1の加熱処理を行い、表面を含む領域に結晶領域（板状結晶を含む）を有する第1の酸化物半導体膜を形成する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、450以上850以下、好ましくは600以上700以下の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体膜の全体を結晶化させ、結果として膜厚の厚い結晶領域を有する膜を用いて酸化物半導体層を形成してもよい。

10

【0224】

次に、ゲート絶縁層402a及び酸化物半導体層403aの上に第2の導電膜を形成する。

【0225】

第2の導電膜としては、例えばアルミニウム、クロム、銅、タンタル、チタン、モリブデン、若しくはタンクスチタンなどの金属材料、又はこれらの金属材料を主成分とする合金材料の膜を用いることができる。また、第2の導電膜に適用可能な膜の積層膜により第2の導電膜を形成することができる。

20

【0226】

次に、第3のフォトリソグラフィ工程により第2の導電膜の上に第3のレジストマスクを形成し、第3のレジストマスクを用いて選択的にエッチングを行ってソース電極層405a及びドレイン電極層406aを形成した後、第3のレジストマスクを除去する（図11（C）参照）。

【0227】

なお、ソース電極層405a及びドレイン電極層406aを形成する際に、第2の導電膜を用いて他の配線を形成することもできる。

【0228】

また、第3のレジストマスク形成時の露光として、紫外線やKrFレーザ光やArFレーザ光を用いることが好ましい。酸化物半導体層403aの上で隣り合うソース電極層405aの下端部とドレイン電極層406aの下端部との間隔幅により、後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて第3のレジストマスク形成の際に露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることもでき、該露光を用いて形成されたトランジスタを用いることにより、回路の動作速度を速くすることできる。また、該トランジスタのオフ電流値は、極めて小さいため、該トランジスタを用いた回路の消費電力を低減することもできる。

40

【0229】

50

なお、第2の導電膜のエッチングを行う場合、エッチングによる酸化物半導体層403aの分断を抑制するために、エッチング条件を最適化することが好ましい。しかしながら、第2の導電膜のみエッチングが行われ、酸化物半導体層403aは、全くエッチングが行われないという条件を得ることは難しく、第2の導電膜のエッチングの際に酸化物半導体層403aは一部のみエッチングが行われ、溝部(凹部)を有する酸化物半導体層403aとなることもある。

【0230】

本実施の形態では、第2の導電膜の一例としてチタン膜を用い、酸化物半導体層403aの一例としてIn-Ga-Zn-O系酸化物半導体を用いるため、エッチャントとしてアンモニア過水(アンモニア、水、過酸化水素水の混合液)を用いる。

10

【0231】

次に、酸化物半導体層403a、ソース電極層405a、及びドレイン電極層406aの上に酸化物絶縁層407aを形成する。このとき、酸化物絶縁層407aは、酸化物半導体層403aの上面の一部に接する。

【0232】

酸化物絶縁層407aは、少なくとも1nm以上の膜厚とし、スパッタリング法など、酸化物絶縁層407aに水、水素などの不純物を混入させない方法を適宜用いて形成することができる。酸化物絶縁層407aに水素が含まれると、その水素の酸化物半導体層への侵入、又は水素が酸化物半導体層中の酸素を引き抜き、酸化物半導体層のバックチャネルが低抵抗化(N型化)してしまい、寄生チャネルが形成されるおそれがある。よって、酸化物絶縁層516は、できるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

20

【0233】

本実施の形態では、酸化物絶縁層407aとして、スパッタリング法を用いて膜厚200nmの酸化シリコン膜を形成する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では一例として100とする。酸化シリコン膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下において行うことができる。

【0234】

また、酸化物絶縁層407aを形成するためのターゲットとしては、酸化シリコンターゲット又はシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素を含む雰囲気下でスパッタリング法により酸化シリコン膜を形成することができる。

30

【0235】

また、酸化物絶縁層407aの形成に用いられる成膜室内の残留水分を除去するためには、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて成膜室内の残留水分を除去することにより、酸化物絶縁層407aに含まれる不純物の濃度を低減できる。また、酸化物絶縁層407aの形成に用いられる成膜室内の残留水分を除去するための排気手段としては、ターボポンプにコールドトラップを加えたものを用いることもできる。

40

【0236】

また、酸化物絶縁層407aを成膜する際に用いるスパッタガスは、水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0237】

また、酸化物絶縁層407aを形成する前にN<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行い、露出している酸化物半導体層403aの表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層403aの上面の一部に接する酸化物絶縁層407aを形成することが好ましい。

【0238】

さらに、不活性ガス雰囲気下、又は酸素ガス雰囲気下で第2の加熱処理(好ましくは20

50

0 以上 400 以下、例えば 250 以上 350 以下) を行うこともできる。例えば、窒素雰囲気下で 250 、1 時間の第 2 の加熱処理を行う。第 2 の加熱処理を行うと、酸化物半導体層 403a の上面の一部が酸化物絶縁層 407a と接した状態で加熱される。

【0239】

以上の工程を経ることによって、酸化物半導体膜に対して第 1 の加熱処理を行って水素、水分、水酸基又は水素化物(水素化合物ともいう)などの不純物を酸化物半導体層から意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料の一つである酸素を供給することができる。よって、酸化物半導体層は高純度化及び電気的に I 型(真性)化する。

10

【0240】

以上の工程でトランジスタが形成される(図 11 (D) 参照)。

【0241】

また、酸化物絶縁層に欠陥を多く含む酸化シリコン層を用いると、酸化シリコン層形成後の加熱処理によって酸化物半導体層中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁層に拡散させ、酸化物半導体層中に含まれる該不純物をより低減させる効果を奏する。

【0242】

酸化物絶縁層 407a の上にさらに保護絶縁層 409a を形成してもよい。例えば、RFスパッタリング法を用いて窒化シリコン膜を形成する。RFスパッタリング法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜などを用いる。本実施の形態では、保護絶縁層として保護絶縁層 409a を、窒化シリコン膜を用いて形成する(図 11 (E) 参照)。

20

【0243】

本実施の形態では、酸化物絶縁層 407a まで形成された基板 400a を 100 ~ 400 の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜することで保護絶縁層 409a を形成する。この場合においても、酸化物絶縁層 407a と同様に、処理室内の残留水分を除去しつつ保護絶縁層 409a を成膜することが好ましい。

30

【0244】

保護絶縁層 409a の形成後、さらに大気中、100 以上 200 以下、1 時間以上 30 時間以下の加熱処理を行ってもよい。加熱処理は、一定の加熱温度を保持して加熱してもよいし、室温から、100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。

【0245】

以上のように、本実施の形態に示すトランジスタは、チャネル形成層として酸化物半導体層を有するトランジスタである。本実施の形態のトランジスタに用いられる酸化物半導体層は、熱処理により高純度化することにより I 型又は実質的に I 型にさせた酸化物半導体層である。

40

【0246】

また、高純度化された酸化物半導体層は、キャリアが極めて少なく(ゼロに近い)、キャリア濃度は  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満である。このように酸化物半導体層のキャリアが極めて少ないため、本実施の形態のトランジスタは、オフ電流を少なくすることができる。オフ電流は、少なければ少ないほど好ましい。本実施の形態のトランジスタでは、チャネル幅 1  $\mu\text{m}$ あたりのオフ電流密度を  $10 \text{ aA} / \mu\text{m}$  ( $1 \times 10^{-17} \text{ A} / \mu\text{m}$ ) 以下にすること、さらには、 $1 \text{ aA} / \mu\text{m}$  ( $1 \times 10^{-18} \text{ A} / \mu\text{m}$ ) 以下、さらには  $10 \text{ zA} / \mu\text{m}$  ( $1 \times 10^{-20} \text{ A} / \mu\text{m}$ ) 以下、 $1 \text{ zA} / \mu\text{m}$  ( $1 \times 10^{-21} \text{ A} / \mu\text{m}$ ) 以下にすることが可能である。

50

## 【0247】

オフ電流値が極めて小さいトランジスタを例えば実施の形態1の液晶表示装置における画素のトランジスタとして用いることにより、静止画を表示する際の画像データの再書き込み(リフレッシュともいう)の回数を少なくすることができる。

## 【0248】

また、本実施の形態のトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、例えば本実施の形態のトランジスタを上記実施の形態1の表示装置のトランジスタに用いることにより、画像の画質を向上させることができる。また、本実施の形態のトランジスタを上記実施の形態1の表示装置に用いることにより、同一基板上に駆動回路部及び画素部を作製することができるため、表示装置の部品点数を削減することができ、例えば表示装置を湾曲させた場合であっても駆動回路部と画素部との接続不良の発生を防止することができる。10

## 【0249】

なお、本実施の形態は、他の実施の形態と適宜組み合わせ、又は置き換えを行うことが可能である。

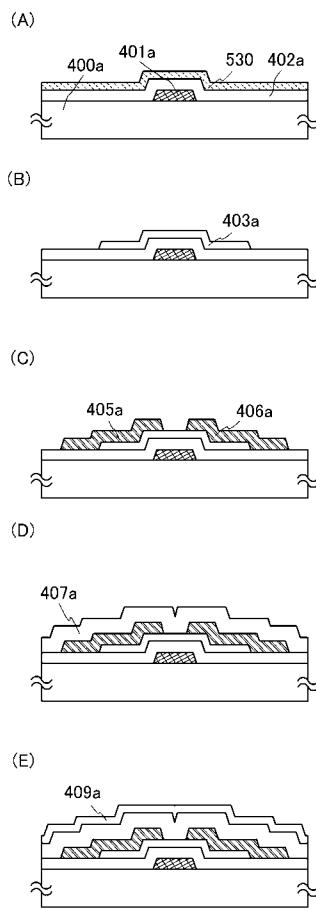

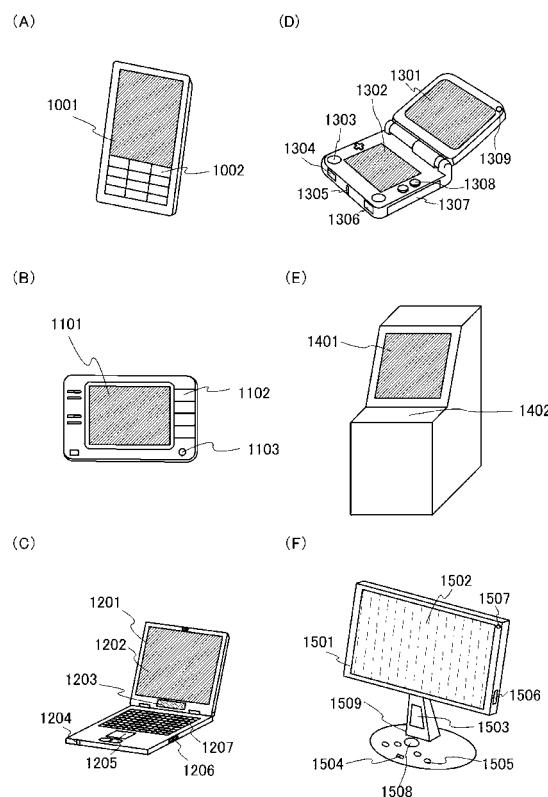

## 【0250】

## (実施の形態4)

本実施の形態では、上記実施の形態に示す液晶表示装置の一例の外観及び断面について、図12を用いて説明する。図12は、本実施の形態における液晶表示装置の一例を説明するための図であり、図12(A)及び図12(C)は、平面図であり、図12(B)は、図12(A)又は図12(C)のM-Nにおける断面図に相当する。20

## 【0251】

図12(A)乃至図12(C)に示す液晶表示装置は、第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また、画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって、画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。また、図12(A)乃至図12(C)に示す液晶表示装置は、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、単結晶半導体膜又は多結晶半導体膜を用いて別途用意された基板上に形成された信号線駆動回路4003が実装されている。30

## 【0252】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG法、ワイヤボンディング法、或いはTAB法などを用いることができる。図12(A)は、COG法により信号線駆動回路4003を実装する例であり、図12(C)は、TAB法により信号線駆動回路4003を実装する例である。

## 【0253】

また、第1の基板4001上に設けられた画素部4002及び走査線駆動回路4004のそれぞれは、トランジスタを複数有しており、図12(B)では、画素部4002に含まれるトランジスタ4010と、走査線駆動回路4004に含まれるトランジスタ4011とを例示している。トランジスタ4010及びトランジスタ4011上には絶縁層4041、4042、4021が設けられている。40

## 【0254】

トランジスタ4010及びトランジスタ4011としては、上記実施の形態1の液晶表示装置と同様に、チャネル形成層としての機能を有する酸化物半導体層を有するトランジスタを用いることができ、例えば上記実施の形態3に示すトランジスタを用いることができる。

## 【0255】

トランジスタ4010は、ゲート電極層4051と、ゲート電極層4051の上に設けられたゲート絶縁層4020と、ゲート絶縁層4020を挟んでゲート電極層4051の上50

に設けられた酸化物半導体層 4052 と、酸化物半導体層 4052 の上にそれぞれ設けられたソース電極層 4053 及びドレイン電極層 4054 と、を有する。

【0256】

トランジスタ 4011 は、ゲート電極層 4061 と、ゲート電極層 4061 の上に設けられたゲート絶縁層 4020 と、ゲート絶縁層 4020 を挟んでゲート電極層 4061 の上に設けられた酸化物半導体層 4062 と、酸化物半導体層 4062 の上にそれぞれ設けられたソース電極層 4063 及びドレイン電極層 4064 と、を有する。

【0257】

さらに、絶縁層 4021 上において、トランジスタ 4011 の酸化物半導体層 4062 のチャネル形成領域と重なる位置に導電層 4040 が設けられている。導電層 4040 を酸化物半導体層 4062 のチャネル形成領域と重なる位置に設けることによって、BT 試験前後におけるトランジスタ 4011 のしきい値電圧の変化量を低減することができる。また、導電層 4040 は、電圧がトランジスタ 4011 のゲート電極層 4061 と同じでもよいし、異なっていても良く、第 2 のゲート電極層として機能させることもできる。また、導電層 4040 の電位が接地電位、0V、或いは導電層 4040 が浮遊状態であってもよい。なお、導電層 4040 は、必ずしも設ける必要はない。

10

【0258】

また、絶縁層 4041、絶縁層 4042、及び絶縁層 4021 を貫通する開口部を介してトランジスタ 4010 のソース電極層 4053 又はドレイン電極層 4054 と電気的に接続されるように画素電極層 4030 が設けられる。そして、第 2 の基板 4006 上に対向電極層 4031 が設けられる。画素電極層 4030 と対向電極層 4031 と液晶層 4008 とが重なっている部分が、液晶素子 4013 に相当する。なお、画素電極層 4030、対向電極層 4031 は、それぞれ配向膜として機能する絶縁層 4032、4033 を介して液晶層 4008 を挟持している。

20

【0259】

なお、第 1 の基板 4001、第 2 の基板 4006 としては、透光性基板を用いることができ、ガラス、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP (Fiberglass-Reinforced Plastics) 板、PVF (ポリビニルフルオライド) フィルム、ポリエスチルフィルム、又はアクリル樹脂フィルムを用いることができる。

30

【0260】

また、絶縁層 4032 及び絶縁層 4033 の間にスペーサ 4035 が設けられる。スペーサ 4035 は、絶縁膜を選択的にエッチングすることで得られる隔壁であり、画素電極層 4030 と対向電極層 4031 との間の距離 (セルギャップ) を制御するために設けられている。また、スペーサ 4035 として球状のスペーサを用いてもよい。

【0261】

また、対向電極層 4031 は、トランジスタ 4010 と同一基板上に設けられる共通電圧線と電気的に接続される。また、共通電圧線との接続部 (共通接続部ともいう) を用いて、一対の基板間に配置される導電性粒子を介して対向電極層 4031 と共通電圧線とを電気的に接続することができる。

40

【0262】

また、シール材 4005 は、導電性粒子を含む。

【0263】

また、本実施の形態の液晶表示装置では、液晶層 4008 における液晶材料として配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は、液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は、狭い温度範囲でしか発現しないため、温度範囲を改善するために 5 重量 % 以上のカイラル剤を混合させた液晶組成物を液晶材料として用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が 1 msec 以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。また、配向膜を設け

50

なくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって、液晶表示装置の生産性を向上させることができるとなる。特に、酸化物半導体層を有するトランジスタは、静電気の影響によりトランジスタの電気的な特性が著しく変動して設計範囲を逸脱する恐れがある。よって、酸化物半導体層を有するトランジスタを有する液晶表示装置にブルー相の液晶材料を用いることにより、静電気によるトランジスタの電気的変動を抑制することができる。

【0264】

また、本実施の形態における液晶表示装置では、基板の外側（視認側）に偏光板を設け、内側に着色層、表示素子に用いる電極層という順に設けてもよいし、偏光板を基板の内側に設けてもよい。また、偏光板と着色層の積層構造は、偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。また、表示部以外にブラックマトリクスとして機能する遮光層を設けてもよい。

10

【0265】

また、絶縁層4041は、酸化物半導体層4052及び酸化物半導体層4062に接する。絶縁層4041としては、例えば酸化シリコン層を用いることができる。

【0266】

また、絶縁層4042は、絶縁層4041上に接して設けられる。絶縁層4042としては、例えば窒化シリコン層を用いることができる。

【0267】

また、絶縁層4021は、絶縁層4042の上に設けられる。絶縁層4021は、トランジスタの表面の凹凸を低減するための平坦化絶縁層としての機能を有する。絶縁層4021としては、例えばポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシなどの、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）などを用いることもできる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層4021を形成してもよい。

20

【0268】

絶縁層4021の形成法は、特に限定されず、絶縁層4021の形成法としては、その材料に応じて、スパッタリング法、SOG法、スピンドルコート法、ディップ法、スプレー塗布法、液滴吐出法（インクジェット法、スクリーン印刷法、オフセット印刷法など）、ドクターナイフを用いる形成法、ロールコーテーを用いる形成法、カーテンコーテーを用いる形成法、ナイフコーテーを用いる形成法などを用いることができる。

30

【0269】

画素電極層4030及び対向電極層4031としては、例えばインジウム錫酸化物、酸化インジウムに酸化亜鉛を混合した金属酸化物（IZO：indium zinc oxideともいう）、酸化インジウムに酸化珪素（SiO<sub>2</sub>）を混合した導電材料、有機インジウム、有機スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、又は酸化チタンを含むインジウム錫酸化物などの透光性を有する導電性材料の層を用いることができる。なお、本実施の形態の液晶表示装置を反射型とする場合、画素電極層4030及び対向電極層4031としては、タンゲステン、モリブデン、ジルコニア、ハフニウム、バナジウム、ニオブ、タンタル、クロム、コバルト、ニッケル、チタン、白金、アルミニウム、銅、若しくは銀などの金属、又はその合金の層を用いることができる。また、画素電極層4030及び対向電極層4031に適用可能な材料の層を積層して画素電極層4030及び対向電極層4031を構成してもよい。

40

【0270】

また、画素電極層4030及び対向電極層4031は、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した電極層は、シート抵抗が10000 / 以下、波長550nmにおける透光率が7

50

0 %以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率は、0.1 cm以下であることが好ましい。

【0271】

導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、またはアニリン、ピロールおよびチオフェンの2種以上からなる共重合体若しくはその誘導体などがあげられる。

【0272】

また、別途形成された信号線駆動回路4003、走査線駆動回路4004、又は画素部4002に与えられる各種信号及び電圧は、FPC4018から供給される。さらに、FPC4018は、接続端子電極4015及び異方性導電膜4019を介して端子電極4016に電気的に接続される。

10

【0273】

接続端子電極4015は、液晶素子4013が有する画素電極層4030と同じ導電膜を用いて形成され、端子電極4016は、トランジスタ4010のソース電極層4053及びドレイン電極層4054と同じ導電膜を用いて形成される。

【0274】

接続端子電極4015は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

20

【0275】

また、図12においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装してもよいし、信号線駆動回路の一部又は走査線駆動回路の一部のみを別途形成して実装してもよい。

【0276】

また、図12に示す液晶表示装置では、ブラックマトリクス(遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材(光学基板)などを適宜設けることができる。例えば、光学部材としては、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライトなどを用いてもよい。

30

【0277】

アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。より詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

【0278】

また、液晶表示装置の動画特性を改善するため、バックライトとして複数のLED(発光ダイオード)光源又は複数のEL光源などを用いて面光源を構成し、面光源を構成している各光源を独立して1フレーム期間内で間欠点灯駆動する駆動技術もある。面光源として、3種類以上のLEDを用いてもよいし、白色発光のLEDを用いてもよい。独立して複数のLEDを制御できるため、液晶層の光学変調の切り替えタイミングに合わせてLEDの発光タイミングを同期させることもできる。この駆動技術は、LEDを部分的に消灯することができるため、特に一画面を占める黒い表示領域の割合が多い映像表示の場合には、消費電力を低減することができる。

40

【0279】

これらの駆動技術を組み合わせることによって、上記実施の形態に示す液晶表示装置の表示特性を向上させることができる。

【0280】

また、トランジスタは静電気などにより破壊されやすいため、さらに画素部又は駆動回路と同一基板上に保護回路を設けることが好ましい。保護回路は、酸化物半導体層を用いた

50

非線形素子を用いて構成することができる。例えば、保護回路は、画素部と、走査線入力端子及び信号線入力端子との間に配設されている。本実施の形態では、複数の保護回路を配設して、走査線、信号線及び容量バス線に静電気などによりサージ電圧が印加され、画素におけるトランジスタなどが破壊されないように構成されている。そのため、保護回路は、サージ電圧が印加されたときに、共通配線に電荷を逃がすように構成する。また、保護回路は、走査線に対して並列に配置された非線形素子によって構成されている。非線形素子は、ダイオードのような二端子素子又はトランジスタのような三端子素子で構成される。例えば、画素部のトランジスタと同じ工程で形成することも可能であり、例えばゲートとドレインを接続することによりダイオードと同様の特性を持たせることができる。

【0281】

10

また、本実施の形態の液晶表示装置の表示モードとしては、TN (Twisted Nematic) モード、IPS (In-Plane-Switching) モード、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optically Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、又はAFLC (AntiFerroelectric Liquid Crystal) モードなどを用いることができる。また、これに限定されず、FFS (Fringing Field Switching) モードなど用いてもよい。

【0282】

20

また、本実施の形態の液晶表示装置としては、TN液晶、OCB液晶、STN液晶、VA液晶、ECB型液晶、GH液晶、高分子分散型液晶、ディスコチック液晶などを用いることができるが、中でもノーマリーブラック型の液晶表示装置、例えば垂直配向(VA)モードを採用した透過型の液晶表示装置とすることが好ましい。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ASV モードなどを用いることができる。

【0283】

以上のように、本実施の形態の液晶表示装置を構成することができる。また、本実施の形態の液晶表示装置の構成にすることにより消費電力を低減することができる。

【0284】

30

なお、本実施の形態は、他の実施の形態と適宜組み合わせ、又は置き換えを行うことができる。

【0285】

(実施の形態5)

本実施の形態では、上記実施の形態に示す液晶表示装置の一例として、タッチパネル機能を付加した液晶表示装置について説明する。

【0286】

本実施の形態における液晶表示装置の構成について図13を用いて説明する。図13は、本実施の形態における液晶表示装置の一例を示す図である。

【0287】

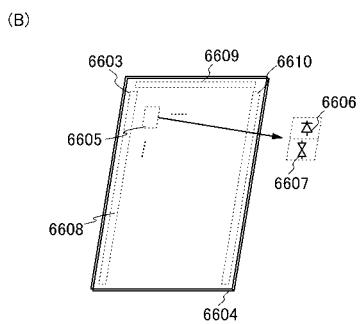

40

図13(A)に示す液晶表示装置は、液晶表示ユニット6601と、液晶表示ユニット6601に重畳して設けられたタッチパネルユニット6602と、を有し、液晶表示ユニット6601及びタッチパネルユニット6602が筐体(ケース)6603により合着された構造である。

【0288】

液晶表示ユニット6601としては、上記実施の形態に示す液晶表示装置を適用することができる。

【0289】

タッチパネルユニット6602としては、例えば抵抗膜方式、表面型静電容量方式、又は投影型静電容量方式のタッチパネルを用いることができる。

50

## 【0290】

図13(A)に示すように、本実施の形態の液晶表示装置の一例は、互いに別々に作製した液晶表示ユニットとタッチパネルユニットとを重畳させた構造である。該構造により、タッチパネル機能を付加した液晶表示装置の製造コストを削減することができる。

## 【0291】

また、図13(B)に示す液晶表示装置6604は、表示部に複数の画素6605を有し、画素6605は、光センサ6606及び液晶素子6607を有する構造である。図13(B)に示す液晶表示装置6604は、画素6605に設けられた光センサ6606に被読み取り物(指やペンなど)を接触又は近付け、被読み取り物からの反射光に応じて光センサにおいて光電流を生成させることにより読み取りを行うものである。図13(B)に示す液晶表示装置6604は、図13(A)とは異なり、タッチパネルユニット6602を重畳させる必要がないため、液晶表示装置の薄型化を図ることができる。なお、画素6605とともに走査線駆動回路6608、信号線駆動回路6609、及び光センサ用駆動回路6610を画素6605と同じ基板上に作製することで、液晶表示装置の小型化を図ることができる。なお、光センサ6606は、アモルファスシリコンなどで形成し、酸化物半導体を用いたトランジスタと重畳して形成する構成としてもよい。

10

## 【0292】

本実施の形態のタッチパネルの機能を付加した液晶表示装置は、チャネル形成層としての機能を有する酸化物半導体層を含むトランジスタを用いることで、表示時間の長い静止画像の表示が可能な表示装置を提供することができる。また、静止画像の表示時に駆動回路部の動作を停止することにより消費電力を低減することもできる。

20

## 【0293】

なお、本実施の形態は、他の実施の形態と適宜組み合わせ、又は置き換えを行うことができる。

## 【0294】

## (実施の形態6)

本実施の形態では、上記実施の形態に示す液晶表示装置の一例として電子書籍について説明する。

## 【0295】

30

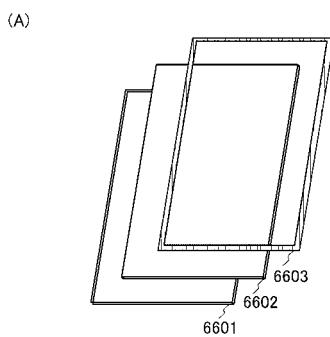

本実施の形態における電子書籍について図14を用いて説明する。図14は、本実施の形態における電子書籍の一例を示す図である。

## 【0296】

図14に示す電子書籍は、筐体2701及び筐体2703の2つの筐体で構成されている。筐体2701及び筐体2703は、軸部2711により接続され、軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

## 【0297】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705及び表示部2707は、互いに異なる画像を表示する構成としてもよく、例えば両方の表示部で一続きの画像を表示する構成としてもよい。異なる画面を表示する構成とすることにより、例えば右側の表示部(図14では表示部2705)に文章を表示し、左側の表示部(図14では表示部2707)に画像を表示することができる。

40

## 【0298】

また、図14に示す電子書籍は、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。また、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、又はACアダプタ及び

50

U S B ケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、図 14 に示す電子書籍は、電子辞書としての機能を持たせた構成としてもよい。

【 0 2 9 9 】

なお、本実施の形態の電子書籍は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【 0 3 0 0 】

また、本実施の形態の電子書籍は、太陽電池セルと、太陽電池セルから出力される電圧を充電する蓄電装置と、該蓄電装置に充電された電圧を各回路に必要な電圧に変換する直流変換回路と、を用いて構成される電源回路を有する構成にしてもよい。これにより、外部電源が不要となるため、外部電源が無い場所であっても、該電子書籍を長時間使用することができ、利便性を向上させることができる。蓄電装置としては、リチウムイオン二次電池、リチウムイオンキャパシタ、電気二重層キャパシタ、及びレドックスキャパシタのいずれか一つ又は複数などを用いることができる。例えばリチウムイオン二次電池及びリチウムイオンキャパシタを併用することにより、高速充放電が可能であり、且つ長時間電源を供給することができる蓄電装置にすることができる。なお、リチウムイオン二次電池に限定されず、蓄電装置として、他のアルカリ金属イオン又はアルカリ土類金属イオンなどを可動イオンとして用いた二次電池を用いてもよい。また、リチウムイオンキャパシタに限定されず、蓄電装置として、他のアルカリ金属イオン又はアルカリ土類金属イオンなどを可動イオンとして用いたキャパシタを用いてもよい。

10

【 0 3 0 1 】

以上のように、本実施の形態の電子書籍は、チャネル形成層としての機能を有する酸化物半導体層を含むトランジスタを用いることで、静止画像の表示時間の長い表示装置を提供することができるため、電子書籍において一定の静止画像を長時間閲覧する場合には特に有効である。また、静止画像の表示時に駆動回路部の動作を停止することにより消費電力を低減することもできる。

20

【 0 3 0 2 】

なお、本実施の形態は、他の実施の形態と適宜組み合わせ、又は置き換えを行うことができる。

30

【 0 3 0 3 】

(実施の形態 7 )

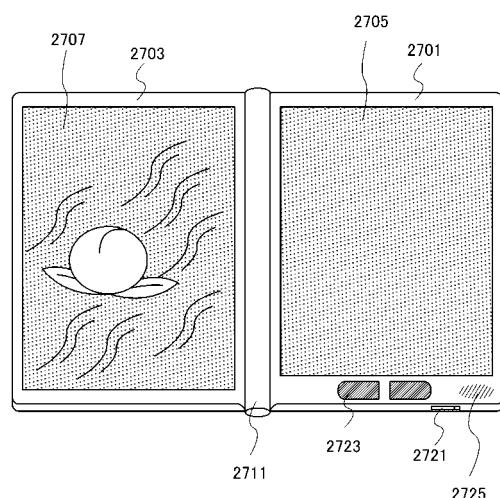

本実施の形態では、上記実施の形態に示す液晶表示装置を表示部に有する電子機器について説明する。

【 0 3 0 4 】

上記実施の形態に示す液晶表示装置を様々な電子機器の表示部に適用することにより、表示機能に加えて様々な機能を持たせた電子機器を提供することができる。上記実施の形態に示す液晶表示装置を表示部に適用した電子機器の具体例について図 15 を用いて説明する。図 15 は、本実施の形態の電子機器の構成の一例を示す図である。

【 0 3 0 5 】

図 15 ( A ) は、携帯型情報通信端末を示す図である。図 15 ( A ) に示す携帯型情報通信端末は少なくとも表示部 1001 を有する。また、図 15 ( A ) に示す携帯型情報通信端末は、例えばタッチパネルと組み合わせることにより、様々な携帯品の代わりとして利用することができる。例えば表示部 1001 に操作部 1002 を設けることで携帯電話として利用することができる。なお、操作部 1002 は必ずしも表示部 1001 に設ける必要はなく、別途操作ボタンを設けた構成とすることもできる。またメモ帳の代わりとしての利用や原稿入出力機能を利用してハンディスキャナーとして利用することもできる。また、上記実施の形態に示す液晶表示装置は、1 回の画像データの書き込みに対する表示時間が長いため、書き込み動作の間隔を長くすることができる。そのため、上記実施の形態に示す液晶表示装置を図 15 ( A ) に示す携帯型情報通信端末に用いることにより、例え

40

50

ば表示部において長時間画像を閲覧する場合であっても、眼精疲労を抑制することができる。

【0306】

図15(B)は、例えばカーナビゲーションを含む情報案内端末を示す図である。図15(B)に示す情報案内端末は、少なくとも表示部1101を有し、さらに操作ボタン1102や外部入力端子1103などを有する構成とすることもできる。自動車の車内は、気温と共に温度が大きく変動し、温度が50℃を超えることもある。しかし上記実施の形態に示す液晶表示装置は、温度による特性変化の影響が少ないため、自動車の車内のような温度が大きく変動する環境下において特に有効である。

【0307】

図15(C)は、ノート型パーソナルコンピュータを示す図である。図15(C)に示すノート型パーソナルコンピュータは、筐体1201、表示部1202、スピーカ1203、LEDランプ1204、ポインティングデバイス1205、接続端子1206、及びキー・ボード1207を有する。上記実施の形態に示す液晶表示装置は、1回の画像データの書き込みに対する表示時間が長いため、書き込み動作の間隔を長くすることができる。そのため、上記実施の形態に示す液晶表示装置を図15(C)に示すノート型パーソナルコンピュータに用いることにより、例えば表示部において長時間画像を閲覧する場合であっても、眼精疲労を抑制することができる。

【0308】

図15(D)は、携帯型遊技機を示す図である。図15(D)に示す携帯型遊技機は、第1の表示部1301と第2の表示部1302と、スピーカ1303と、接続端子1304と、LEDランプ1305、マイクロフォン1306、記録媒体読込部1307と、操作ボタン1308と、センサ1309と、を有する。また、上記実施の形態に示す液晶表示装置は、1回の画像データの書き込みに対する表示時間が長いため、書き込み動作の間隔を長くすることができる。そのため、上記実施の形態に示す液晶表示装置を図15(D)に示す携帯型遊技機に用いることにより、例えば表示部において長時間画像を閲覧する場合であっても、眼精疲労を抑制することができる。また、第1の表示部1301と第2の表示部1302のいずれか一方を動画像表示とし、他方を静止画像表示と互いに異なる表示にすることもできる。これにより、静止画像を表示している表示部において駆動回路部への信号又は電圧の供給を停止させることができるために、消費電力を低減することができる。

【0309】

図15(E)は、設置型情報通信端末を示す図である。図15(E)に示す設置型情報通信端末は、少なくとも表示部1401を有する。なお、表示部1401は、平面部1402上に設けることができる。また、平面部1402に別途操作ボタンなどを設けることができる。図15(E)に示す設置型情報通信端末は、例えば現金自動預け払い機、又はチケット(乗車券を含む)などの券の注文をするための情報通信端末(マルチメディアステーションともいう)などとして利用することができる。上記実施の形態に示す液晶表示装置は、1回の画像データの書き込みに対する表示時間が長いため、書き込み動作の間隔を長くすることができる。そのため、上記実施の形態に示す液晶表示装置を図15(E)に示す設置型情報通信端末に用いることにより、例えば表示部において長時間画像を閲覧する場合であっても、眼精疲労を抑制することができる。

【0310】

図15(F)は、ディスプレイを示す図である。図15(F)に示すディスプレイは、筐体1501と、表示部1502と、スピーカ1503と、LEDランプ1504と、操作ボタン1505と、接続端子1506と、センサ1507と、マイクロフォン1508と、支持台1509と、を有する。上記実施の形態に示す液晶表示装置は、1回の画像データの書き込みに対する表示時間が長いため、書き込み動作の間隔を長くすることができる。そのため、上記実施の形態に示す液晶表示装置を図15(F)に示すディスプレイに用いることにより、例えば表示部において長時間画像を閲覧する場合であっても、眼精疲労

10

20

30

40

50

を抑制することができる。

【0311】

上記実施の形態に示す液晶表示装置を電子機器の表示部に搭載することにより多機能型の電子機器を提供することができる。

【0312】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

【符号の説明】

【0313】

|         |         |    |

|---------|---------|----|

| 1 0     | パルス出力回路 |    |

| 1 1     | 配線      | 10 |

| 1 2     | 配線      |    |

| 1 3     | 配線      |    |

| 1 4     | 配線      |    |

| 1 5     | 配線      |    |

| 1 7     | 配線      |    |

| 1 8     | 配線      |    |

| 2 1     | 入力端子    |    |

| 2 2     | 入力端子    |    |

| 2 3     | 入力端子    |    |

| 2 4     | 入力端子    | 20 |

| 2 5     | 入力端子    |    |

| 2 6     | 出力端子    |    |

| 2 7     | 出力端子    |    |

| 3 1     | トランジスタ  |    |

| 3 2     | トランジスタ  |    |

| 3 3     | トランジスタ  |    |

| 3 4     | トランジスタ  |    |

| 3 5     | トランジスタ  |    |

| 3 6     | トランジスタ  |    |

| 3 7     | トランジスタ  | 30 |

| 3 8     | トランジスタ  |    |

| 3 9     | トランジスタ  |    |

| 4 0     | トランジスタ  |    |

| 4 1     | トランジスタ  |    |

| 5 1     | 電源線     |    |

| 5 2     | 電源線     |    |

| 6 1     | 期間      |    |

| 6 2     | 期間      |    |

| 1 0 0   | 液晶表示装置  |    |

| 1 0 1   | 画像処理回路  | 40 |

| 1 0 2   | 補正回路    |    |

| 1 1 1   | 記憶回路    |    |

| 1 1 1 b | フレームメモリ |    |

| 1 1 2   | 比較回路    |    |

| 1 1 3   | 表示制御回路  |    |

| 1 1 5   | 選択回路    |    |

| 1 2 0   | 表示パネル   |    |

| 1 2 1   | 駆動回路部   |    |

| 1 2 2   | 画素部     |    |

| 1 2 3   | 画素      | 50 |

|         |         |    |

|---------|---------|----|

| 1 2 4   | 走査線     |    |

| 1 2 5   | 画像信号線   |    |

| 1 2 6   | 端子部     |    |

| 1 2 7   | トランジスタ  |    |

| 1 3 0   | 光源部     |    |

| 1 3 1   | 温度検出回路  |    |

| 1 3 2   | 計数回路    |    |

| 1 3 3   | 計数値比較回路 |    |

| 2 1 0   | 容量素子    |    |

| 2 1 4   | トランジスタ  | 10 |

| 2 1 5   | 液晶素子    |    |

| 4 0 0 a | 基板      |    |

| 4 0 0 b | 基板      |    |

| 4 0 0 c | 基板      |    |

| 4 0 0 d | 基板      |    |

| 4 0 1 a | ゲート電極層  |    |

| 4 0 1 b | ゲート電極層  |    |

| 4 0 1 c | ゲート電極層  |    |

| 4 0 1 d | ゲート電極層  |    |

| 4 0 2 a | ゲート絶縁層  | 20 |

| 4 0 2 b | ゲート絶縁層  |    |

| 4 0 2 c | ゲート絶縁層  |    |

| 4 0 2 d | ゲート絶縁層  |    |

| 4 0 3 a | 酸化物半導体層 |    |

| 4 0 3 b | 酸化物半導体層 |    |

| 4 0 3 c | 酸化物半導体層 |    |

| 4 0 3 d | 酸化物半導体層 |    |

| 4 0 5 a | ソース電極層  |    |

| 4 0 5 b | ソース電極層  |    |

| 4 0 5 c | ソース電極層  | 30 |

| 4 0 5 d | ソース電極層  |    |

| 4 0 6 a | ドレイン電極層 |    |

| 4 0 6 b | ドレイン電極層 |    |

| 4 0 6 c | ドレイン電極層 |    |

| 4 0 6 d | ドレイン電極層 |    |

| 4 0 7 a | 酸化物絶縁層  |    |

| 4 0 7 c | 酸化物絶縁層  |    |

| 4 0 9 a | 保護絶縁層   |    |

| 4 0 9 b | 保護絶縁層   |    |

| 4 0 9 c | 保護絶縁層   | 40 |

| 4 1 1   | 期間      |    |

| 4 1 2   | 期間      |    |

| 4 1 3   | 期間      |    |

| 4 1 4   | 期間      |    |

| 4 2 7   | 絶縁層     |    |

| 4 3 6   | 配線層     |    |

| 4 3 7   | 配線層     |    |

| 4 4 7   | 下地層     |    |

| 5 1 6   | 酸化物絶縁層  |    |

| 5 3 0   | 酸化物半導体膜 | 50 |

|         |             |    |

|---------|-------------|----|

| 6 0 1   | 期間          |    |

| 6 0 2   | 期間          |    |

| 6 0 3   | 期間          |    |

| 6 0 4   | 期間          |    |

| 1 0 0 1 | 表示部         |    |

| 1 0 0 2 | 操作部         |    |

| 1 1 0 1 | 表示部         |    |

| 1 1 0 2 | 操作ボタン       |    |

| 1 1 0 3 | 外部入力端子      |    |

| 1 2 0 1 | 筐体          | 10 |

| 1 2 0 2 | 表示部         |    |

| 1 2 0 3 | スピーカ        |    |

| 1 2 0 4 | L E D ランプ   |    |

| 1 2 0 5 | ポインティングデバイス |    |

| 1 2 0 6 | 接続端子        |    |

| 1 2 0 7 | キーボード       |    |

| 1 2 1 A | 駆動回路        |    |

| 1 2 1 B | 駆動回路        |    |

| 1 3 0 1 | 表示部         |    |

| 1 3 0 2 | 表示部         | 20 |

| 1 3 0 3 | スピーカ        |    |

| 1 3 0 4 | 接続端子        |    |

| 1 3 0 5 | L E D ランプ   |    |

| 1 3 0 6 | マイクロフォン     |    |

| 1 3 0 7 | 記録媒体読込部     |    |

| 1 3 0 8 | 操作ボタン       |    |

| 1 3 0 9 | センサ         |    |

| 1 4 0 1 | 表示部         |    |

| 1 4 0 2 | 平面部         |    |

| 1 5 0 1 | 筐体          | 30 |

| 1 5 0 2 | 表示部         |    |

| 1 5 0 3 | スピーカ        |    |

| 1 5 0 4 | L E D ランプ   |    |

| 1 5 0 5 | 操作ボタン       |    |

| 1 5 0 6 | 接続端子        |    |

| 1 5 0 7 | センサ         |    |

| 1 5 0 8 | マイクロフォン     |    |

| 1 5 0 9 | 支持台         |    |

| 2 7 0 1 | 筐体          |    |

| 2 7 0 3 | 筐体          | 40 |

| 2 7 0 5 | 表示部         |    |

| 2 7 0 7 | 表示部         |    |

| 2 7 1 1 | 軸部          |    |

| 2 7 2 1 | 電源          |    |

| 2 7 2 3 | 操作キー        |    |

| 2 7 2 5 | スピーカ        |    |

| 4 0 0 1 | 基板          |    |

| 4 0 0 2 | 画素部         |    |

| 4 0 0 3 | 信号線駆動回路     |    |

| 4 0 0 4 | 走査線駆動回路     | 50 |

|         |            |    |

|---------|------------|----|

| 4 0 0 5 | シール材       |    |

| 4 0 0 6 | 基板         |    |

| 4 0 0 8 | 液晶層        |    |

| 4 0 1 0 | トランジスタ     |    |

| 4 0 1 1 | トランジスタ     |    |

| 4 0 1 3 | 液晶素子       |    |

| 4 0 1 5 | 接続端子電極     |    |

| 4 0 1 6 | 端子電極       |    |

| 4 0 1 8 | F P C      |    |

| 4 0 1 9 | 異方性導電膜     | 10 |

| 4 0 2 0 | ゲート絶縁層     |    |

| 4 0 2 1 | 絶縁層        |    |

| 4 0 3 0 | 画素電極層      |    |

| 4 0 3 1 | 対向電極層      |    |

| 4 0 3 2 | 絶縁層        |    |

| 4 0 3 3 | 絶縁層        |    |

| 4 0 3 5 | スペーサ       |    |

| 4 0 4 0 | 導電層        |    |

| 4 0 4 1 | 絶縁層        |    |

| 4 0 4 2 | 絶縁層        | 20 |

| 4 0 5 1 | ゲート電極層     |    |

| 4 0 5 2 | 酸化物半導体層    |    |

| 4 0 5 3 | ソース電極層     |    |

| 4 0 5 4 | ドレイン電極層    |    |

| 4 0 6 1 | ゲート電極層     |    |

| 4 0 6 2 | 酸化物半導体層    |    |

| 4 0 6 3 | ソース電極層     |    |

| 4 0 6 4 | ドレイン電極層    |    |

| 6 5 0 5 | 画素         |    |

| 6 6 0 1 | 液晶表示ユニット   | 30 |

| 6 6 0 2 | タッチパネルユニット |    |

| 6 6 0 3 | 筐体         |    |

| 6 6 0 4 | 液晶表示装置     |    |

| 6 6 0 5 | 画素         |    |

| 6 6 0 6 | 光センサ       |    |

| 6 6 0 7 | 液晶素子       |    |

| 6 6 0 8 | 走査線駆動回路    |    |

| 6 6 0 9 | 信号線駆動回路    |    |

| 6 6 1 0 | 光センサ用駆動回路  |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

(A)

(B)

(C)

(D)

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 1 1 B |

| G 0 9 G | 3/20  | 6 1 2 J |

| G 0 2 F | 1/133 | 5 8 0   |

| G 0 2 F | 1/133 | 5 5 0   |

(56)参考文献 特開2000-132135 (JP, A)

特開2009-075500 (JP, A)

特開2009-300722 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |           |   |         |

|---------|-----------|---|---------|

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8 |

| G 0 2 F | 1 / 1 3 3 |   |         |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP5178941B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2013-04-10 |