(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5509281号

(P5509281)

(45) 発行日 平成26年6月4日(2014.6.4)

(24) 登録日 平成26年3月28日(2014.3.28)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G09G 3/20 (2006.01)

G09G 3/20 624B

G02F 1/133 (2006.01)

G09G 3/20 623G

G09G 3/20 623F

G09G 3/20 623R

請求項の数 1 (全 41 頁) 最終頁に続く

(21) 出願番号 特願2012-194858 (P2012-194858)

(22) 出願日 平成24年9月5日 (2012.9.5)

(62) 分割の表示 特願2007-75173 (P2007-75173)

原出願日 平成13年8月9日 (2001.8.9)

(65) 公開番号 特開2013-11901 (P2013-11901A)

(43) 公開日 平成25年1月17日 (2013.1.17)

審査請求日 平成24年9月26日 (2012.9.26)

(31) 優先権主張番号 特願2000-249090 (P2000-249090)

(32) 優先日 平成12年8月18日 (2000.8.18)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2000-253196 (P2000-253196)

(32) 優先日 平成12年8月23日 (2000.8.23)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】 液晶表示装置

(57) 【特許請求の範囲】

【請求項 1】

画素を有し、前記画素は、

第1のトランジスタと、

第2のトランジスタと、

第3のトランジスタと、

第4のトランジスタと、

第5のトランジスタと、

第6のトランジスタと、

第7のトランジスタと、

第8のトランジスタと、

第9のトランジスタと、

第10のトランジスタと、

第11のトランジスタと、

第1の配線と、

第2の配線と、

第3の配線と、

第4の配線と、

第5の配線と、

10

20

第 6 の配線と、

第 7 の配線と、

第 8 の配線と、

第 1 の容量と、

第 2 の容量と、

液晶素子と、

第 1 の記憶回路と、

第 2 の記憶回路と、を有し、

前記第 1 の記憶回路は、第 1 の入力端子と、第 1 の出力端子と、第 2 の出力端子と、を

有し、

前記第 2 の記憶回路は、第 2 の入力端子と、第 3 の出力端子と、第 4 の出力端子と、を

有し、

前記液晶素子は、前記第 1 の容量の一方の電極と接続されており、

前記液晶素子は、前記第 2 の容量の一方の電極と接続されており、

前記液晶素子は、前記第 1 のトランジスタのソース又はドレインの一方と接続されてお

り、

前記第 1 の容量の他方の電極は、前記第 2 のトランジスタのソース又はドレインの一方

と接続されており、

前記第 1 の容量の他方の電極は、前記第 3 のトランジスタのソース又はドレインの一方

と接続されており、

前記第 2 の容量の他方の電極は、前記第 4 のトランジスタのソース又はドレインの一方

と接続されており、

前記第 2 の容量の他方の電極は、前記第 5 のトランジスタのソース又はドレインの一方

と接続されており、

前記第 2 のトランジスタのソース又はドレインの他方は、前記第 6 のトランジスタのソ

ース又はドレインの一方と接続されており、

前記第 2 のトランジスタのソース又はドレインの他方は、前記第 7 のトランジスタのソ

ース又はドレインの一方と接続されており、

前記第 4 のトランジスタのソース又はドレインの他方は、前記第 8 のトランジスタのソ

ース又はドレインの一方と接続されており、

前記第 4 のトランジスタのソース又はドレインの他方は、前記第 9 のトランジスタのソ

ース又はドレインの一方と接続されており、

前記第 10 のトランジスタのソース又はドレインの一方は、前記第 1 の入力端子と接続

されており、

前記第 11 のトランジスタのソース又はドレインの一方は、前記第 2 の入力端子と接続

されており、

前記第 1 の出力端子は、前記第 2 のトランジスタのゲートと接続されており、

前記第 2 の出力端子は、前記第 3 のトランジスタのゲートと接続されており、

前記第 3 の出力端子は、前記第 4 のトランジスタのゲートと接続されており、

前記第 4 の出力端子は、前記第 5 のトランジスタのゲートと接続されており、

前記第 1 の配線は、前記第 1 のトランジスタのソース又はドレインの他方と接続されて

おり、

前記第 2 の配線は、前記第 1 のトランジスタのゲートと接続されており、

前記第 2 の配線は、前記第 6 のトランジスタのゲートと接続されており、

前記第 2 の配線は、前記第 8 のトランジスタのゲートと接続されており、

前記第 3 の配線は、前記第 7 のトランジスタのゲートと接続されており、

前記第 3 の配線は、前記第 9 のトランジスタのゲートと接続されており、

前記第 4 の配線は、前記第 7 のトランジスタのソース又はドレインの他方と接続されて

おり、

前記第 4 の配線は、前記第 9 のトランジスタのソース又はドレインの他方と接続されて

おり、

10

20

30

40

50

おり、

前記第5の配線は、前記第3のトランジスタのソース又はドレインの他方と接続されており、

前記第5の配線は、前記第5のトランジスタのソース又はドレインの他方と接続されており、

前記第5の配線は、前記第6のトランジスタのソース又はドレインの他方と接続されており、

前記第5の配線は、前記第8のトランジスタのソース又はドレインの他方と接続されており、

前記第6の配線は、前記第10のトランジスタのゲートと接続されており、

10

前記第7の配線は、前記第11のトランジスタのゲートと接続されており、

前記第8の配線は、前記第10のトランジスタのソース又はドレインの他方と接続されており、

前記第8の配線は、前記第11のトランジスタのソース又はドレインの他方と接続されており、

前記第1の出力端子は、第1の信号を供給することができる機能を有し、

前記第2の出力端子は、第2の信号を供給することができる機能を有し、

前記第3の出力端子は、第3の信号を供給することができる機能を有し、

前記第4の出力端子は、第4の信号を供給することができる機能を有し、

前記第1の信号又は前記第2の信号の一方は、前記第1の信号又は前記第2の信号の他方の反転信号であり、

20

前記第3の信号又は前記第4の信号の一方は、前記第3の信号又は前記第4の信号の他方の反転信号であり、

前記第1の配線は、第1の電位を供給することができる機能を有し、

前記第2の配線は、第5の信号を供給することができる機能を有し、

前記第3の配線は、第6の信号を供給することができる機能を有し、

前記第4の配線は、第2の電位を供給することができる機能を有し、

前記第5の配線は、第3の電位を供給することができる機能を有し、

前記第6の配線は、第7の信号を供給することができる機能を有し、

前記第7の配線は、第8の信号を供給することができる機能を有し、

30

前記第8の配線は、映像信号を供給することができる機能を有し、

前記第2の電位は、前記第3の電位よりも高く、

前記第1の電位は、前記第3の電位よりも高く、

前記第2の電位は、前記第1の電位よりも高く、

前記第6の信号は、前記第5の信号の反転信号であり、

前記第7の信号によって、前記第10のトランジスタの導通状態又は非導通状態が選択され、

前記第8の信号によって、前記第11のトランジスタの導通状態又は非導通状態が選択され、

前記第7の信号と前記第8の信号とは、異なる信号であることを特徴とする液晶表示装置。

40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体表示装置（以下、表示装置と表記する）に関し、特に、絶縁体上に作製される薄膜トランジスタを有するアクティブマトリクス型表示装置に関する。その中で特に、映像信号としてデジタル信号を用いるアクティブマトリクス型液晶表示装置に関する。また、この表示装置を用いた携帯情報装置に関する。特に、アクティブマトリクス型液晶表示装置を用いた携帯電話、PDA、携帯パーソナルコンピュータ、携帯ナビゲーションシステム、電子書籍などの携帯情報装置に関する。

50

**【背景技術】****【0002】**

近年、絶縁体上、特にガラス基板上に半導体薄膜を形成した表示装置、特に薄膜トランジスタ（以下、TFTと表記する）を用いたアクティブマトリクス型表示装置の普及が顕著となっている。TFTを使用したアクティブマトリクス型表示装置は、マトリクス状に配置された数十万から数百万個のTFTを有し、各画素の電荷を制御することによって画像の表示を行っている。

**【0003】**

さらに最近の技術として、画素を構成する画素TFTの他に、画素部の周辺部に、TFTを用いて駆動回路を同時形成するポリシリコンTFTに関する技術が発展してきており、装置の小型化、低消費電力化に大いに貢献している。それに伴って、近年その応用分野の拡大が著しいモバイル機器の表示部等に、液晶表示装置は不可欠なデバイスとなってきた。

10

**【0004】**

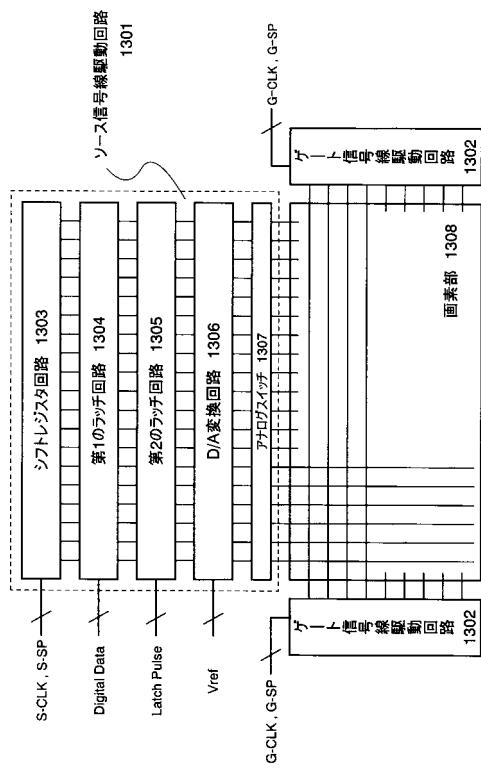

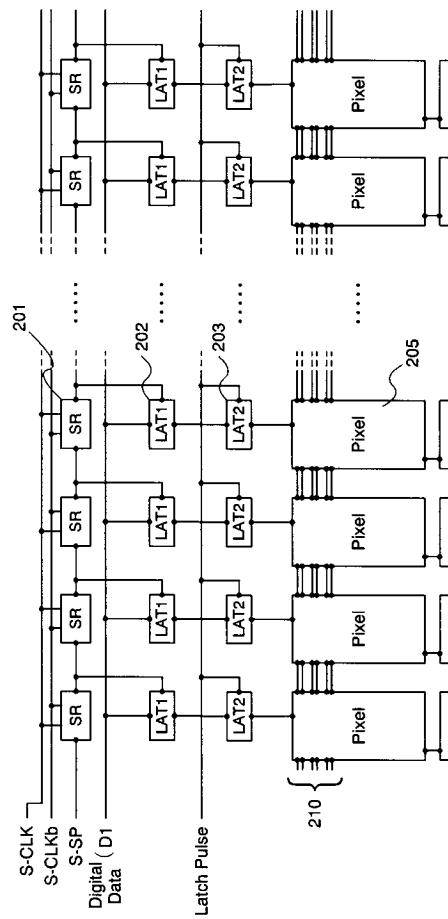

通常のデジタル方式の液晶表示装置の概略図を、図13に示す。中央に画素部1308が配置されている。画素部の上側には、ソース信号線を制御するための、ソース信号線駆動回路1301が配置されている。ソース信号線駆動回路1301は、シフトレジスタ回路1303、第1のラッチ回路1304、第2のラッチ回路1305、D/A変換回路（D/Aコンバータ）1306、アナログスイッチ1307等を有する。画素部の左右には、ゲート信号線を制御するための、ゲート信号線駆動回路1302が配置されている。なお、図13においては、ゲート信号線駆動回路1302は、画素部の左右両側に配置されているが、片側配置でも構わない。ただし、両側配置としたほうが、駆動効率、駆動信頼性の面から見て望ましい。

20

**【0005】**

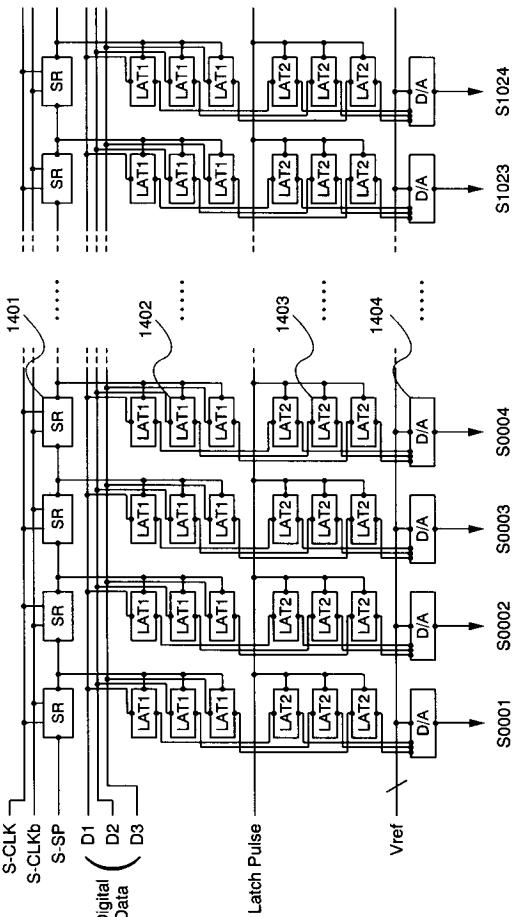

ソース信号線駆動回路1301に関しては、図14に示すような構成を有している。図14に例として示す駆動回路は、水平方向解像度1024画素、3ビットデジタル階調信号に対応したソース信号線駆動回路であり、シフトレジスタ回路（SR）1401、第1のラッチ回路（LAT1）1402、第2のラッチ回路（LAT2）1403、D/A変換回路（D/A）1404等を有する。なお、図14では図示していないが、必要に応じてバッファ回路、レベルシフタ回路等を配置しても良い。

30

**【0006】**

図13および図14を用いて動作について簡単に説明する。まず、シフトレジスタ回路1303（図14中、SRと表記）にクロック信号（S-CLK、S-CLKb）およびスタートパルス（S-SP）が入力され、順次パルスが出力される。続いて、それらのパルスは第1のラッチ回路1304（図14中、LAT1と表記）に入力され、同じく第1のラッチ回路1304に入力されたデジタル信号（Digital Data）をそれぞれ保持していく。ここで、D1が最上位ビット（MSB：Most Significant Bit）、D3が最下位ビット（LSB：Least Significant Bit）である。第1のラッチ回路1304において、1水平周期分のデジタル信号の保持が完了すると、帰線期間中に、第1のラッチ回路1304で保持されているデジタル信号は、ラッチ信号（Latch Pulse）の入力に従い、一斉に第2のラッチ回路1305（図14中、LAT2と表記）へと転送される。

40

**【0007】**

その後、再びシフトレジスタ回路1303が動作し、次の水平周期分のデジタル信号の保持が開始される。同時に、第2のラッチ回路1305で保持されているデジタル信号は、D/Aコンバータ1306（図14中、D/Aと表記）にてアナログ信号へと変換される。このアナログ信号は、ソース信号線を経由して画素に書き込まれる。この動作を繰り返すことによって、画像の表示が行われる。

**【0008】**

また、上述の従来の液晶表示装置を用いた携帯情報端装置について説明する。

**【0009】**

50

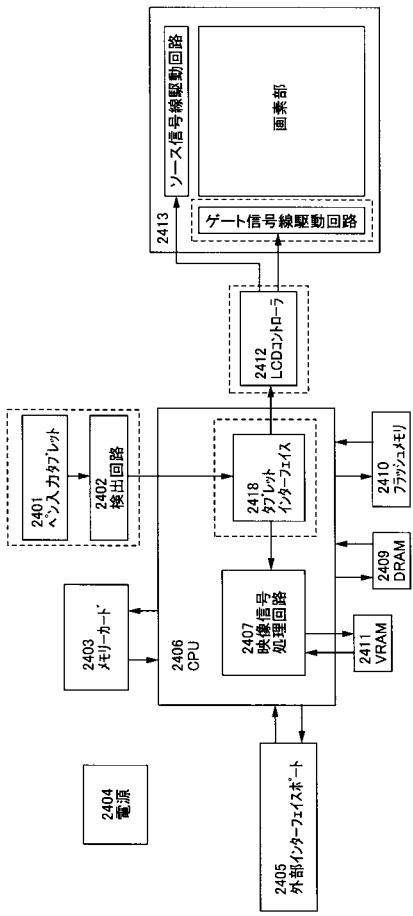

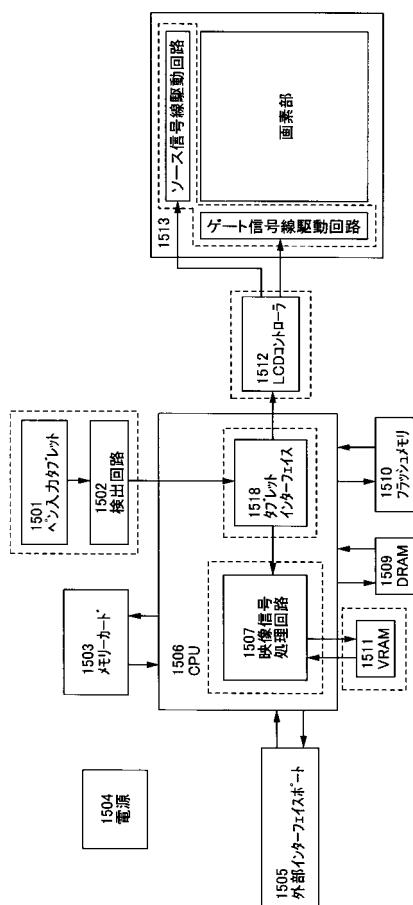

携帯情報装置として、携帯情報端末を例に説明する。図34に、従来の携帯情報端末のブロック図を示す。携帯情報端末ではユーザーが必要に応じて、求める情報を引き出すことが要求される。その情報は、まず、その携帯情報端末内の記憶装置(DRAM1509、フラッシュメモリ1510など)に記憶されているもの、または携帯情報端末に差し込まれるメモリーカード1503に記憶されているもの、外部インターフェイスポート1505を介して外部機器と接続して情報を得る物などがある。これらの情報はペン入力タブレット1501より入力されるユーザーの指示に基づいて、CPU1506により処理され、液晶表示装置1513は表示を行う。

#### 【0010】

具体的には、ペン入力タブレット1501より入力された信号は、検出回路1502により検出され、タブレットインターフェイス1518に入力される。この入力信号は、タブレットインターフェイス1518により処理され、映像信号入力回路1507等に入力される。必要なデータをCPU1506が処理し、それをVRAM1511に格納してある画像フォーマットに基づき、画像データに変換し、LCDコントローラ1512に送付する。ここでLCDコントローラ1512は液晶表示装置1513を駆動する信号を生成し、表示装置を駆動し、表示を行う。

#### 【0011】

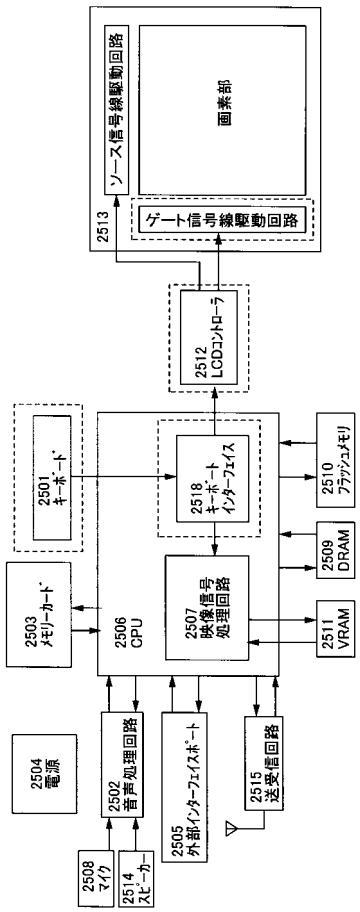

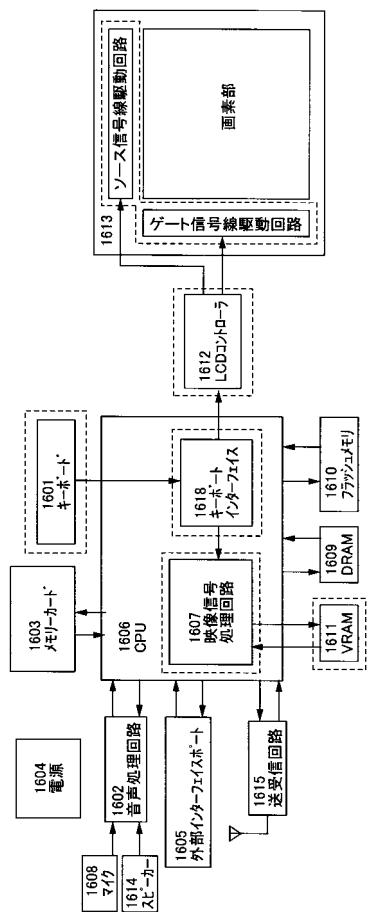

携帯情報装置として、携帯電話を例に説明する。図35に、従来の携帯電話のブロック図を示す。携帯電話は電波を送受信する送受信回路1615と、受信した信号を音声処理する音声処理回路1602、スピーカ1614、マイク1608、またデータを入力するキーボード1601、キーボード1601より入力された信号を処理する、キーボードインターフェイス1618などを有している。

#### 【0012】

キーボードより入力されるユーザーの指示に基づいて、記憶装置(DRAM1609、フラッシュメモリ1610など)に記憶されているもの、または携帯電話に差し込まれるメモリーカード1603に記憶されているもの、外部インターフェイスポート1605を介して外部機器と接続して得る情報等がCPU1606により処理され、液晶表示装置1613は表示を行う。

#### 【0013】

具体的には、キーボード1601より入力された信号は、キーボードインターフェイス1618により処理され、映像信号処理回路1607等に入力される。必要なデータをCPU1606が処理し、それをVRAM1611に格納してある画像フォーマットに基づき、画像データに変換し、LCDコントローラ1612に送付する。ここでLCDコントローラ1612は液晶表示装置1613を駆動する信号を生成し、表示装置を駆動し、表示を行う。

#### 【0014】

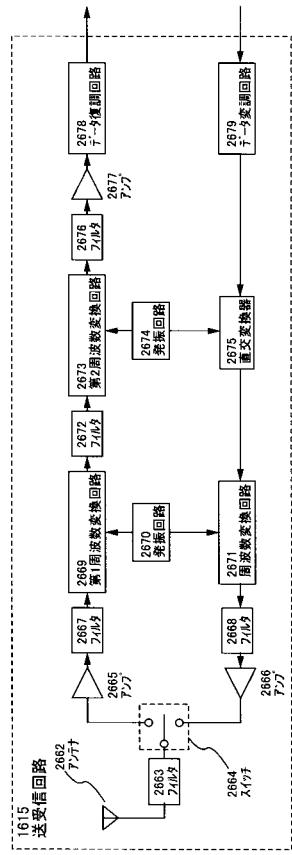

なお、送受信回路1615の構造の例として、図26を示す。

#### 【0015】

送受信回路1615は、アンテナ2662、フィルタ2663、2667、2668、2672、2676、スイッチ2664、アンプ2665、2666、2677、第1周波数変換回路2669、第2周波数変換回路2673、周波数変換回路2671、発振回路2670、2674、直交変換器2675、データ復調回路2678、データ変調回路2679を含む。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0016】

一般的なアクティブマトリクス型液晶表示装置においては、動画の表示をスムーズに行うため、1秒間に60回前後、画面表示の更新が行われる。すなわち、1フレーム毎にデジタル信号を供給し、その都度画素への書き込みを行わなければならない。たとえ、映像が静止画であったとしても、1フレーム毎に同一の信号を供給しつづけなければならないため、

10

20

30

40

50

外部回路、駆動回路などが連続して同じデジタル信号の繰り返し処理を行う必要がある。

【0017】

静止画のデジタル信号を一旦、外部の記憶回路に書き込み、以後は1フレーム毎に外部の記憶回路から液晶表示装置にデジタル信号を供給する方法もあるが、いずれの場合にも外部の記憶回路と駆動回路とは動作し続ける必要があることに変わりはない。

【0018】

また、従来の携帯情報装置では、組み込まれた表示装置が画像を表示する場合、たとえその画像が静止画像であっても、同一の映像のデータを1秒間に60回づつ、表示装置に送り続けていた。即ち、図34中、破線で囲った部分（CPU1506にある映像信号処理回路1507、VRAM1511、LCDコントローラ1512、液晶表示装置1513のソース信号線駆動回路及びゲート信号線駆動回路、ペン入力ダブレット1501、検出回路1502、ダブルエットインターフェイス1518）は画像の表示を行っている限り、動作を行い続けていた。

また、図35中、破線で囲った部分（CPU1606にある映像信号処理回路1607、VRAM1611、LCDコントローラ1612、液晶表示装置1613のソース信号線駆動回路及びゲート信号線駆動回路、キーボード1601、キーボードインターフェイス1618）は画像の表示を行っている限り、動作を行い続けていた。

【0019】

ここで、画素数の少ないパッシブマトリクス型表示装置においては、記憶回路を表示装置のドライバICもしくはコントローラの中に内蔵し、VRAMを停止するものも存在するが、アクティブマトリクス型表示装置のような多数の画素を用いる表示装置では、ドライバ内もしくはコントローラ内に記憶回路を有するのはチップサイズの観点から、非現実的である。よって、従来の携帯情報装置では、静止画を表示する場合においても、多くの回路は動作を続けねばならず、消費電力の低減に対して、妨げとなっていた。

【0020】

また、モバイル機器においては、低消費電力化が大きく望まれている。さらに、このモバイル機器においては、静止画モードで使用されることが大部分を占めているにもかかわらず、前述のように駆動回路は静止画表示の際にも動作し続けているため、低消費電力化への足かせとなっている。

【0021】

本発明は前述のような問題点を鑑みて、静止画の表示時における駆動回路などの消費電力を低減することを課題とする。

【課題を解決するための手段】

【0022】

前述の課題を解決するために、本発明では次のような手段を用いた。

【0023】

画素内に複数の記憶回路と、画素毎にデジタル信号を記憶させる。静止画の場合、一度書き込みを行えば、それ以降、画素に書き込まれる情報は同様であるので、フレーム毎に信号の入力を行わなくとも、記憶回路に記憶されている信号を読み出すことによって静止画を継続的に表示することができる。すなわち、静止画を表示する際は、最低1フレーム分の信号の処理動作を行って以降は、ソース信号線駆動回路や画像信号処理回路等を停止させておくことが可能となり、それに伴って電力消費を大きく低減することが可能となる。

【0024】

以下に、本発明の液晶表示装置及びそれを用いた携帯情報装置の構成について記載する。

【0025】

本発明によって、画素を有する液晶表示装置において、前記画素は、複数の記憶回路と、D/Aコンバータとを有することを特徴とする液晶表示装置が提供される。

【0026】

10

20

30

40

50

本発明によって、画素を有する液晶表示装置において、前記画素は、 $n$  ( $n$  は、2以上の自然数) 個の記憶回路と、前記  $n$  個の記憶回路に記憶されたデジタル信号をアナログ信号に変換する D / A コンバータとを有することを特徴とする液晶表示装置が提供される。

#### 【 0 0 2 7 】

本発明によって、画素を有し、前記画素は、液晶素子を有し、アナログ信号が前記液晶素子に入力される液晶表示装置において、前記画素は、 $n$  ( $n$  は 2 以上の自然数) 個の記憶回路と、前記  $n$  個の記憶回路に記憶されたデジタル信号を前記アナログ信号に変換する D / A コンバータとを有することを特徴とする液晶表示装置が提供される。

#### 【 0 0 2 8 】

本発明によって、画素を有する液晶表示装置において、前記画素は、 $n \times m$  ( $n$  及び  $m$  は、2 以上の自然数) 個の記憶回路と、前記  $n \times m$  個の記憶回路に記憶された  $n$  ビット分のデジタル信号をアナログ信号に変換する D / A コンバータとを有することを特徴とする液晶表示装置が提供される。

#### 【 0 0 2 9 】

本発明によって、画素を有する液晶表示装置の駆動方法において、前記画素は、 $n \times m$  ( $n$  及び  $m$  は、2 以上の自然数) 個の記憶回路と、前記  $n \times m$  個の記憶回路に記憶された  $n$  ビット分のデジタル信号をアナログ信号に変換する D / A コンバータとを有し、前記画素が、 $m$  フレーム分のデジタル信号を記憶することを特徴とする液晶表示装置が提供される。

#### 【 0 0 3 0 】

ソース信号線を有し、前記記憶回路及び前記 D / A コンバータは、前記ソース信号線と重なって配置されていることを特徴とした液晶表示装置であってもよい。

#### 【 0 0 3 1 】

ゲート信号線を有し、前記記憶回路及び前記 D / A コンバータは、前記ゲート信号線と重なって配置されていることを特徴とした液晶表示装置であってもよい。

#### 【 0 0 3 2 】

本発明によって、画素を有し、前記画素は、液晶素子を有する液晶表示装置において、前記画素は、ソース信号線と、 $n$  ( $n$  は 2 以上の自然数) 本のゲート信号線と、 $n$  個の TFT と、 $n$  個の記憶回路と、D / A コンバータとを有し、前記  $n$  個の TFT のゲート電極はそれぞれ、前記  $n$  本のゲート信号線のうちのそれぞれ 1 本に接続され、ソース領域とドレイン領域の一方は、前記ソース信号線に接続され、もう一方はそれぞれ、前記  $n$  個の記憶回路のうちのそれぞれ 1 つの入力端子に接続され、前記  $n$  個の記憶回路の出力端子はそれぞれ、前記 D / A コンバータの入力端子に接続され、前記 D / A コンバータの出力端子は、液晶素子に接続されていることを特徴とする液晶表示装置が提供される。

#### 【 0 0 3 3 】

本発明によって、画素を有し、前記画素は、液晶素子を有する液晶表示装置において、前記画素は、 $n$  ( $n$  は 2 以上の自然数) 本のソース信号線と、ゲート信号線と、 $n$  個の TFT と、 $n$  個の記憶回路と、D / A コンバータとを有し、前記  $n$  個の TFT のゲート電極は、前記ゲート信号線に接続され、ソース領域とドレイン領域の一方はそれぞれ、前記  $n$  本のソース信号線のうちのそれぞれ 1 つに接続され、もう一方はそれぞれ、前記  $n$  個の記憶回路のうちのそれぞれ 1 つの入力端子に接続され、前記  $n$  個の記憶回路の出力端子はそれぞれ、前記 D / A コンバータの入力端子に接続され、前記 D / A コンバータの出力端子は、前記液晶素子に接続されていることを特徴とする液晶表示装置が提供される。

#### 【 0 0 3 4 】

ソース信号線駆動回路を有し、前記ソース信号線駆動回路は、シフトレジスタと、前記シフトレジスタからのサンプリングパルスによって  $n$  ビットのデジタル信号を保持する第 1 のラッチ回路と、前記第 1 のラッチ回路に保持された前記  $n$  ビットのデジタル信号が

10

20

30

40

50

転送される第2のラッチ回路と、前記第2のラッチ回路に転送された前記nビットのデジタル信号を1ビットずつ順に選択し前記ソース信号線に入力するスイッチとを有することを特徴とする液晶表示装置であってもよい。

**【0035】**

ソース信号線駆動回路を有し、前記ソース信号線駆動回路は、シフトレジスタと、前記シフトレジスタからのサンプリングパルスによって1ビットのデジタル信号を保持する第1のラッチ回路と、前記第1のラッチ回路に保持された前記1ビットのデジタル信号が転送される第2のラッチ回路とを有することを特徴とする液晶表示装置であってもよい。

**【0036】**

ソース信号線駆動回路を有し、前記ソース信号線駆動回路は、シフトレジスタと、前記シフトレジスタからのサンプリングパルスによってnビットのデジタル信号を保持する第1のラッチ回路とを有することを特徴とする液晶表示装置であってもよい。 10

**【0037】**

ソース信号線駆動回路を有し、前記ソース信号線駆動回路は、シフトレジスタと、前記シフトレジスタからのサンプリングパルスによってnビットのデジタル信号を保持する第1のラッチ回路と、前記第1のラッチ回路に保持されたnビットのデジタル信号を前記n本のソース信号線に入力するn個のスイッチとを有することを特徴とする液晶表示装置であってもよい。

**【0038】**

前記記憶回路はスタティック型メモリ(SRAM)、強誘電体メモリ(FRAM)またはダイナミック型メモリ(DRAM)であることを特徴とする液晶表示装置であってもよい。 20

**【0039】**

前記記憶回路は、ガラス基板上、プラスチック基板上、ステンレス基板上または単結晶ウェハ上に形成されていることを特徴とする液晶表示装置であってもよい。

**【0040】**

前記液晶表示装置を用いることを特徴とするテレビ、パソコンコンピュータ、携帯端末、ビデオカメラまたはヘッドマウントディスプレイであってもよい。

**【0041】**

本発明によって、マトリクス状に配置された複数の画素を有する液晶表示装置の駆動方法において、前記複数の画素はそれぞれ、複数の記憶回路と、D/Aコンバータとを有し、前記複数の画素のうち、特定の行の画素または特定の列の画素が有する前記複数の記憶回路のデータを書き換えることを特徴とする液晶表示装置の駆動方法が提供される。 30

**【0042】**

本発明によって、複数の画素と、前記複数の画素に映像信号を入力するソース信号線駆動回路とを有する液晶表示装置の駆動方法において、前記複数の画素はそれぞれ、複数の記憶回路と、D/Aコンバータとを有し、静止画を表示するとき、前記ソース信号線駆動回路の動作を停止することを特徴とする液晶表示装置の駆動方法が提供される。

**【0043】**

前記記憶回路はスタティック型メモリ(SRAM)、強誘電体メモリ(FRAM)またはダイナミック型メモリ(DRAM)であることを特徴とする液晶表示装置の駆動方法であってもよい。 40

**【0044】**

前記記憶回路は、ガラス基板上、プラスチック基板上、ステンレス基板上または単結晶ウェハ上に形成されていることを特徴とする液晶表示装置の駆動方法であってもよい。

**【0045】**

前記駆動方法の前記液晶表示装置を用いることを特徴とするテレビ、パソコンコンピュータ、携帯端末、ビデオカメラまたはヘッドマウントディスプレイであってもよい。

**【0046】**

本発明によって、液晶表示装置と、C P Uとを有する携帯情報装置の駆動方法において、前記液晶表示装置は、画素中に、複数の記憶回路と、D / A コンバータと、前記複数の記憶回路に信号を出力する駆動回路とを有し、前記C P Uは、前記駆動回路を制御する第1の回路と、前記携帯情報装置に入力される信号を制御する第2の回路とを有し、

前記液晶表示装置が静止画を表示するとき、前記第1の回路を停止することを特徴とする携帯情報装置の駆動方法が提供される。

#### 【0047】

本発明によって、液晶表示装置と、V R A Mとを有する携帯情報装置の駆動方法において、前記液晶表示装置は、画素中に、複数の記憶回路と、D / A コンバータとを有し、前記液晶表示装置が静止画を表示するとき、前記V R A Mのデータの読み出し操作を停止することを特徴とする携帯情報装置の駆動方法が提供される。 10

#### 【0048】

本発明によって、液晶表示装置を有する携帯情報装置の駆動方法において、前記液晶表示装置は、画素中に、複数の記憶回路と、D / A コンバータとを有し、前記液晶表示装置が静止画を表示するとき、前記液晶表示装置のソース信号線駆動回路を停止することを特徴とする携帯情報装置の駆動方法が提供される。

#### 【0049】

前記複数の記憶回路は、1フレーム期間に1度読み出し操作が行われることを特徴とする携帯情報装置の駆動方法であってもよい。

#### 【0050】

本発明によって、液晶表示装置を有する携帯情報装置の駆動方法において、前記液晶表示装置はマトリクス状に配置された複数の画素を有し、前記複数の画素はそれぞれ、複数の記憶回路と、D / A コンバータとを有し、前記液晶表示装置は、前記複数の画素のうち、特定の行の画素または特定の列の画素が有する前記複数の記憶回路のデータを書き換えることを特徴とする携帯情報装置の駆動方法が提供される。 20

#### 【0051】

前記携帯情報装置は、携帯電話、パーソナルコンピュータ、ナビゲーションシステム、P D Aまたは電子書籍であることを特徴とする携帯情報装置の駆動方法であってもよい。

#### 【発明の効果】

#### 【0052】

各画素の内部に配置された複数の記憶回路を用いてデジタル信号の記憶を行うことにより、静止画を表示する際に各フレーム期間で記憶回路に記憶されたデジタル信号を反復して用いる。これによって、継続的に静止画表示を行う際に、ソース信号線駆動回路を停止させておくことが可能となる。よって、液晶表示装置全体の低消費電力化に大きく貢献することが出来る。 30

#### 【0053】

また、液晶表示装置を組み込んだ携帯情報装置において、液晶表示装置に入力する信号を処理する、映像信号処理回路等の回路も、継続的に静止画表示を行う際は、停止させておくことが可能になるため、携帯情報装置の低消費電力化に大きく貢献する。

#### 【図面の簡単な説明】

#### 【0054】

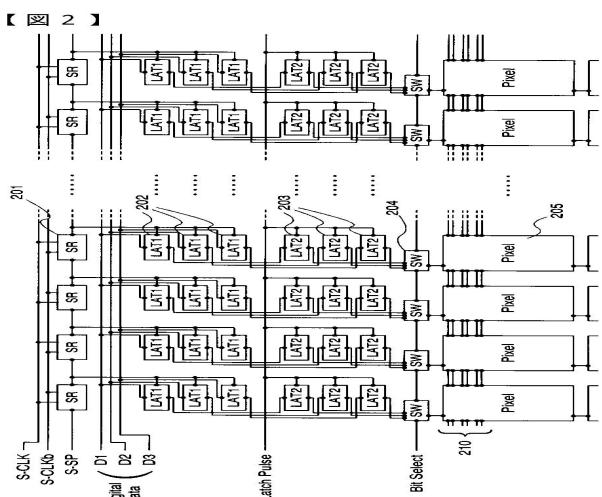

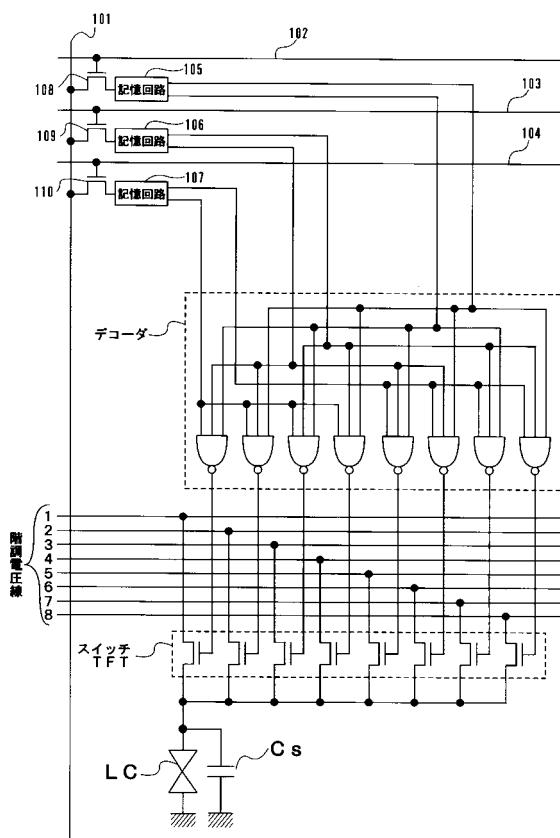

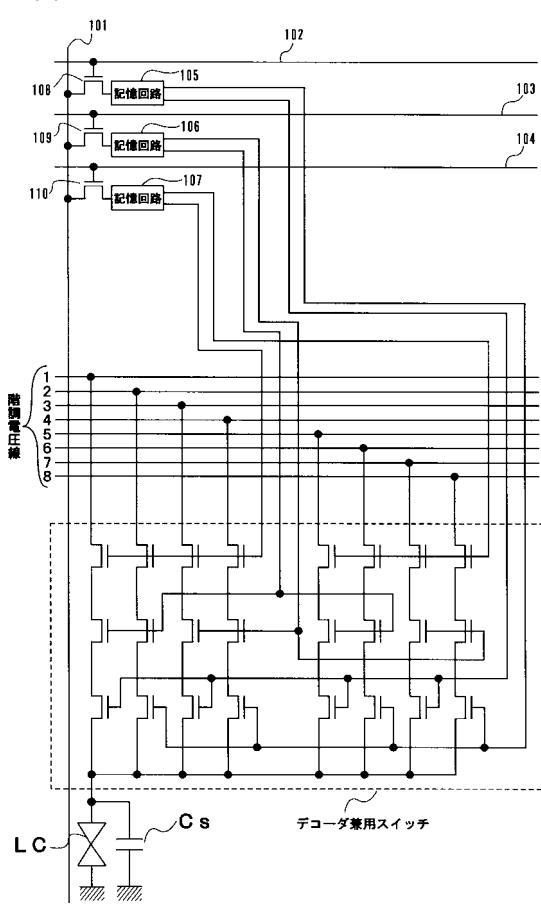

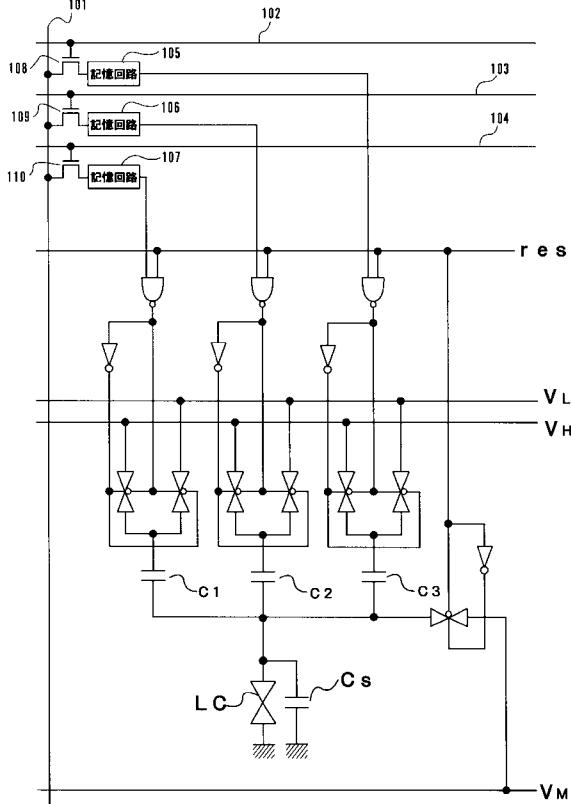

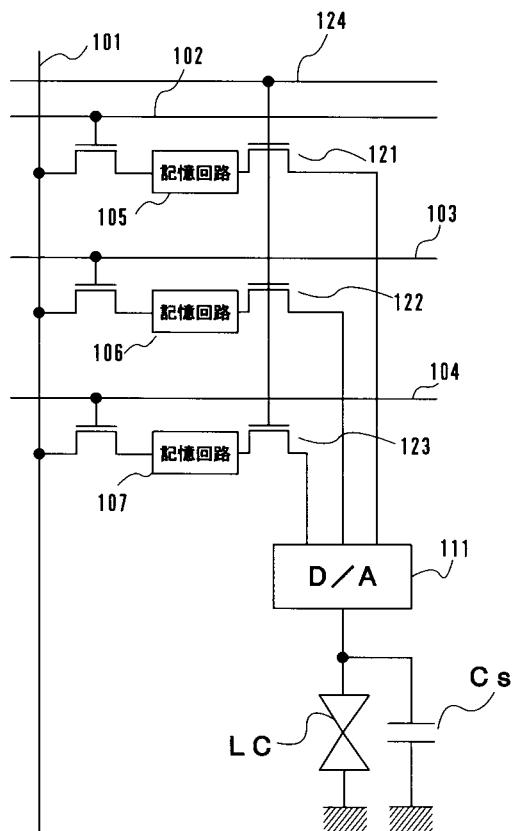

【図1】複数の記憶回路を内部に有する本発明の画素の回路図。

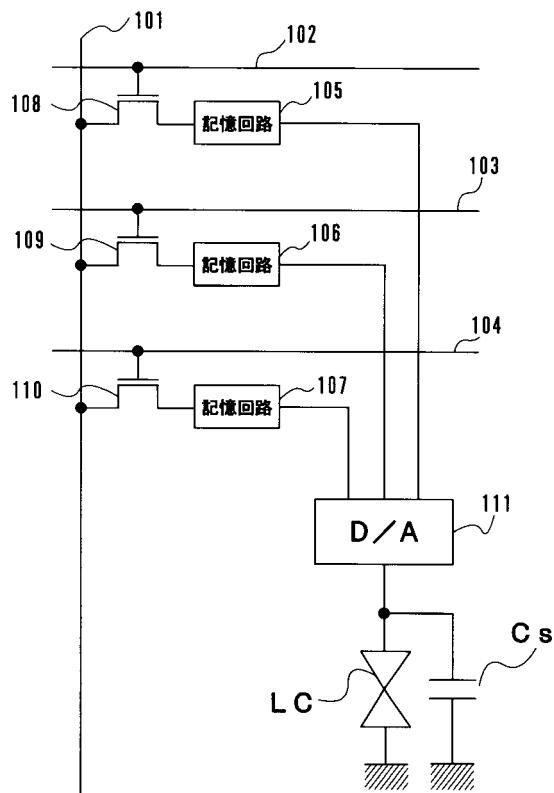

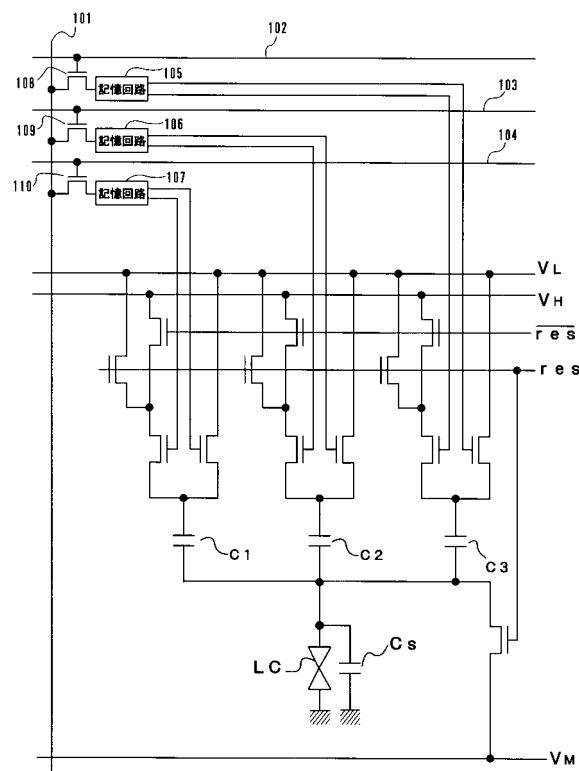

【図2】本発明の画素を用いて表示を行うためのソース信号線駆動回路の回路構成を示す図。

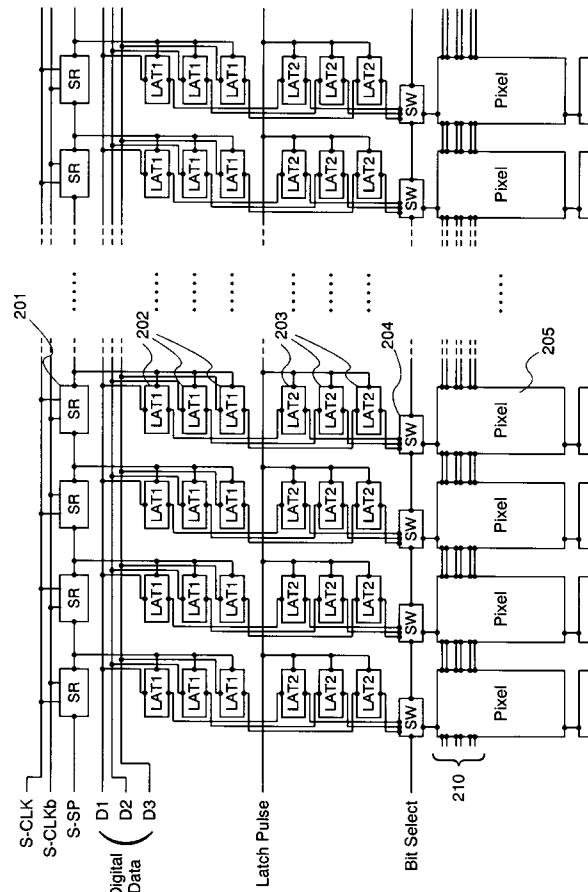

【図3】本発明の画素を用いて表示を行うためのタイミングチャートを示す図。

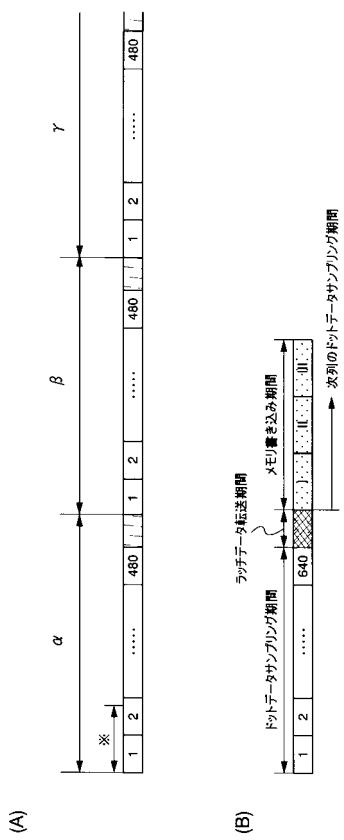

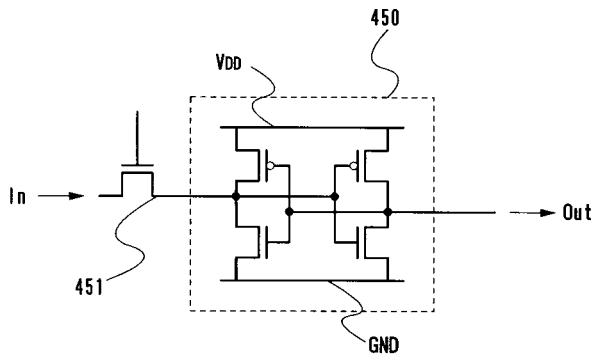

【図4】記憶回路の詳細な回路図。

【図5】第2のラッチ回路を持たないソース信号線駆動回路の回路構成を示す図。

【図6】図5のソース信号線駆動回路によって駆動される本発明の画素の回路図。

【図7】図5及び図6に記載の回路を用いて表示を行うためのタイミングチャートを示す図。 40

- 【図 8】本発明の液晶表示装置の D / A コンバータの構成を示す図。

- 【図 9】本発明の液晶表示装置の D / A コンバータの構成を示す図。

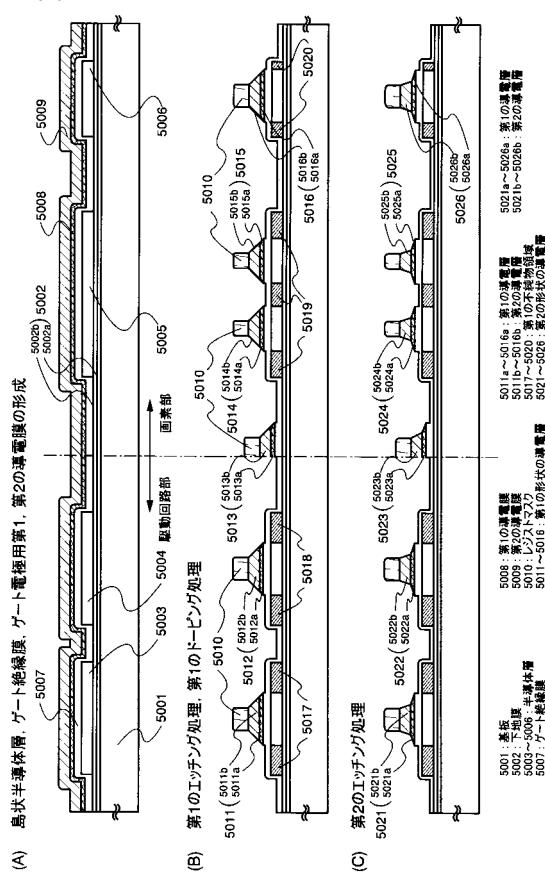

- 【図 10】本発明の画素を有する液晶表示装置の作製工程例を示す図。

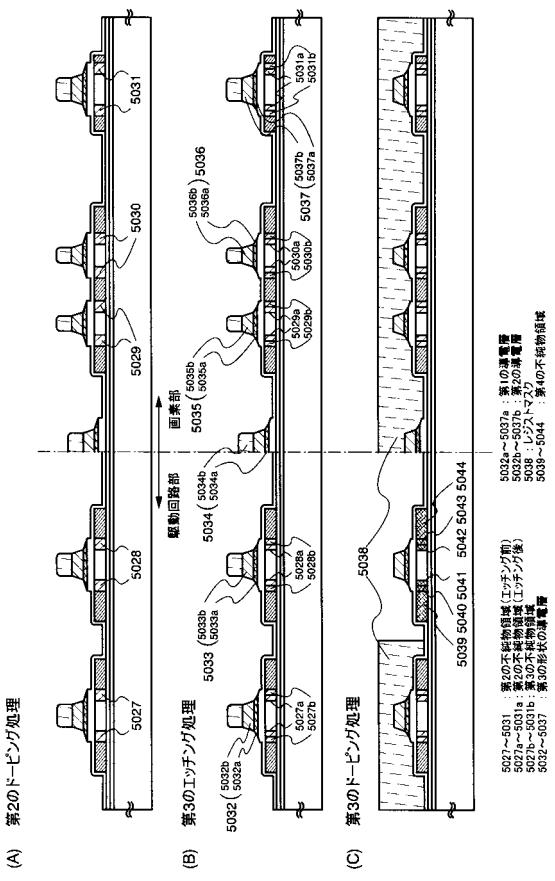

- 【図 11】本発明の画素を有する液晶表示装置の作製工程例を示す図。

- 【図 12】本発明の画素を有する液晶表示装置の作製工程例を示す図。

- 【図 13】従来の液晶表示装置の全体の回路構成を簡略に示す図。

- 【図 14】従来の液晶表示装置のソース信号線駆動回路の回路構成を示す図。

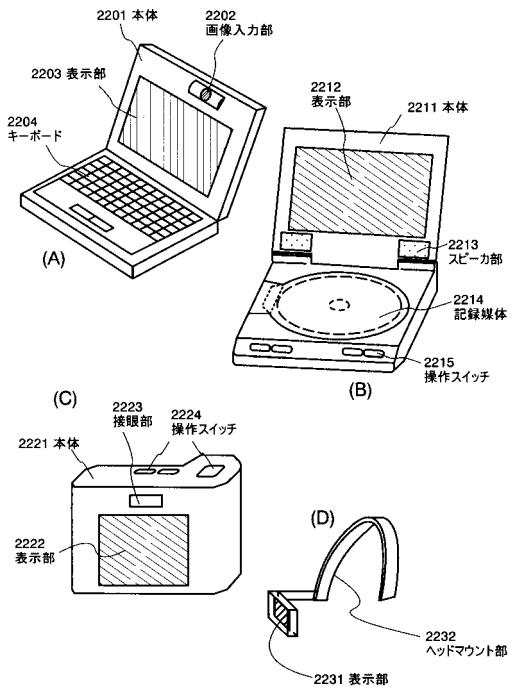

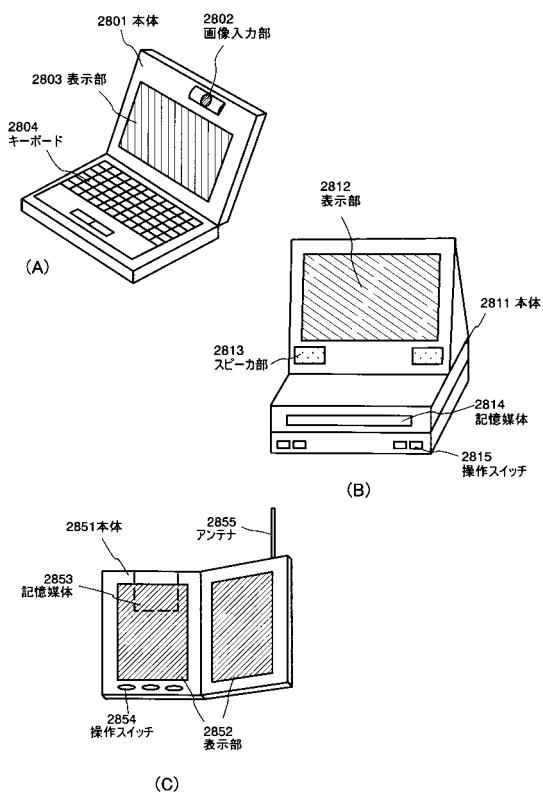

- 【図 15】本発明の画素を有する表示装置の適用が可能な電子装置を示す図。

- 【図 16】本発明の画素を有する表示装置の適用が可能な電子装置を示す図。

- 【図 17】第 2 のラッチ回路を持たないソース信号線駆動回路の回路構成を示す図。 10

- 【図 18】図 17 に記載の回路を用いて表示を行うためのタイミングチャートを示す図。

- 【図 19】反射型液晶表示装置の作製工程例を示す図。

- 【図 20】本発明の液晶表示装置の D / A コンバータの構成を示す図。

- 【図 21】本発明の液晶表示装置の D / A コンバータの構成を示す図。

- 【図 22】1 ビット処理分のラッチ回路を有するソース信号線駆動回路の回路構成を示す図。

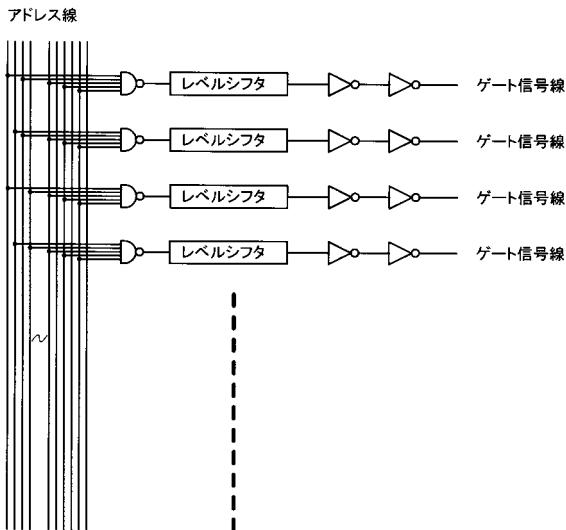

- 【図 23】デコーダを用いたゲート信号線駆動回路を示す図。

- 【図 24】本発明を用いた携帯情報端末のブロック図。

- 【図 25】本発明を用いた携帯電話のブロック図。

- 【図 26】携帯電話の送受信部のブロック図。 20

- 【図 27】本発明の携帯情報装置の液晶表示装置の上面図及び断面図。

- 【図 28】本発明の携帯情報装置の応用例を示す図。

- 【図 29】本発明の携帯情報装置の応用例を示す図。

- 【図 30】本発明の携帯情報装置の液晶表示装置の画素の上面図。

- 【図 31】本発明の携帯情報端末の例を示す図。

- 【図 32】本発明の携帯情報端末の例を示す図。

- 【図 33】本発明の携帯情報端末の例を示す図。

- 【図 34】従来の携帯情報端末のブロック図。

- 【図 35】従来の携帯電話のブロック図。

- 【図 36】本発明の液晶表示装置の画素の構成を示す図。 30

- 【図 37】本発明の液晶表示装置の画素の構成を示す図。

- 【図 38】本発明の液晶表示装置の画素の構成を示す図。

**【発明を実施するための形態】**

**【0055】**

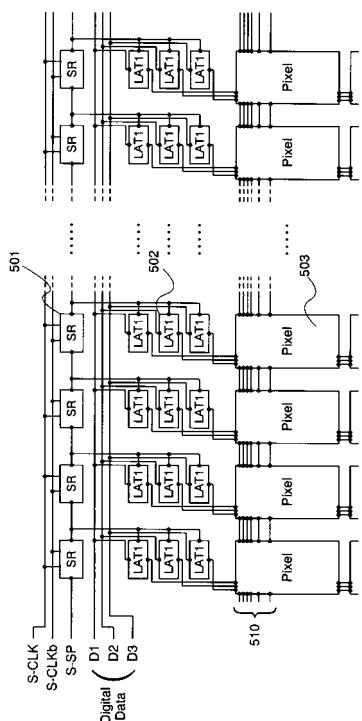

図 2 は、記憶回路を有する画素を用いた表示装置における、ソース信号線駆動回路および一部の画素の構成を示したものである。この回路は、3 ビットデジタル階調信号に対応したものであり、シフトレジスタ回路 (S R) 201、第 1 のラッチ回路 (L A T 1) 202、第 2 のラッチ回路 (L A T 2) 203、ビット信号選択スイッチ (S W) 204、画素 (P i x e l) 205 を有する。210 は、ゲート信号線駆動回路あるいは外部から直接供給される信号であり、画素の説明とともに後述する。 40

**【0056】**

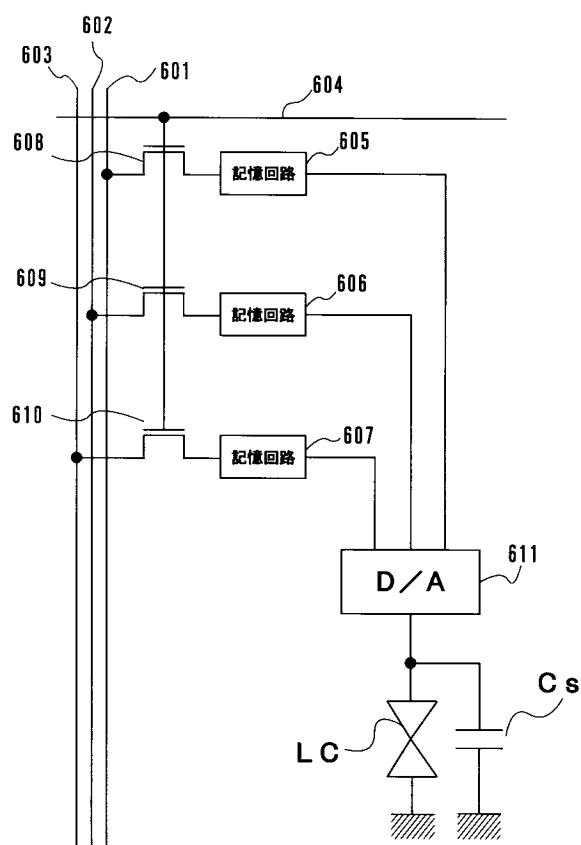

図 1 は、図 2 における画素 205 における回路構成を詳細に示したものである。この画素は、3 ビットデジタル階調信号に対応したものであり、液晶素子 (L C)、保持容量 (C s)、記憶回路 (105 ~ 107) 及び D / A (D / A コンバータ : 111) 等を有している。101 はソース信号線、102 ~ 104 は書き込み用ゲート信号線、108 ~ 110 は書き込み用 T F T である。

**【0057】**

D / A コンバータ 111 の具体例は実施例にて記述するが、実施例に記述された以外の方式を用いて D / A コンバータを構成してもかまわない。

**【0058】**

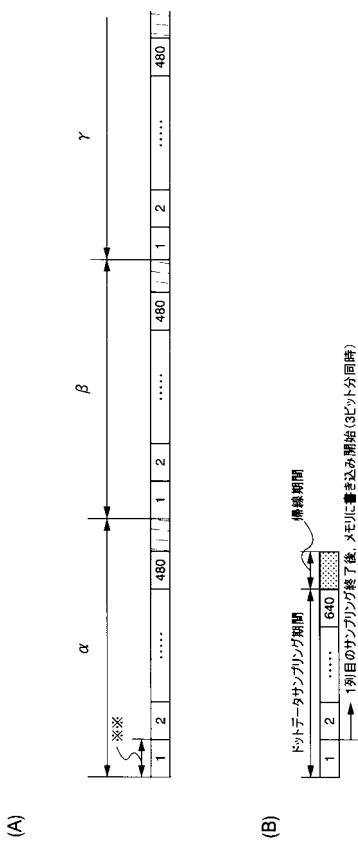

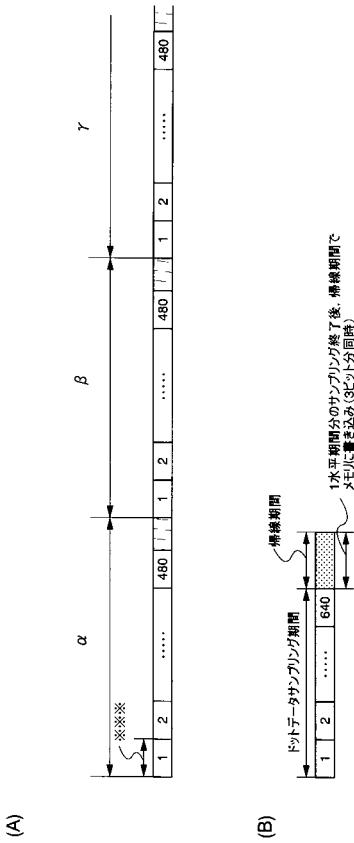

図3は、図1に示した本発明の表示装置におけるタイミングチャートである。表示装置は3ビットデジタル階調信号、VGAのものを対象としている。図1～図3を用いて、駆動方法について説明する。なお、各番号は、図1～図3のものをそのまま用いる（図番は省略する）。

#### 【0059】

図2および図3(A)(B)を参照する。図3(A)において、各フレーム期間を、と表記して説明する。まず、区間ににおける回路動作について説明する。

#### 【0060】

従来のデジタル方式の駆動回路の場合と同様に、シフトレジスタ回路201にクロック信号(S-CLK, S-CLKb)およびスタートパルス(S-SP)が入力され、順次サンプリングパルスが出力される。続いて、サンプリングパルスは第1のラッチ回路202(LAT1)に入力され、同じく第1のラッチ回路202に入力されたデジタル信号(Digital Data)をそれぞれ保持していく。この期間を、本明細書においてはドットデータサンプリング期間と表記する。1水平期間分のドットデータサンプリング期間は、図3(A)において1～480で示す各期間である。デジタル信号は3ビットであり、D1がMSB(Most Significant Bit)、D3がLSB(Least Significant Bit)である。第1のラッチ回路202において、1水平周期分のデジタル信号の保持が完了すると、帰線期間中に、第1のラッチ回路202で保持されているデジタル信号は、ラッチ信号(Latch Pulse)の入力に従い、一斉に第2のラッチ回路203(LAT2)へと転送される。

10

#### 【0061】

続いて、再びシフトレジスタ回路201から出力されるサンプリングパルスに従い、次の水平周期分のデジタル信号の保持動作が行われる。

#### 【0062】

一方、第2のラッチ回路203に転送されたデジタル信号は、画素内に配置された記憶回路に書き込まれる。図3(B)に示すように、次列のドットデータサンプリング期間をI、IIおよびIIIと3分割し、第2のラッチ回路に保持されているデジタル信号をソース信号線に出力する。このとき、ビット信号選択スイッチ204によって、各ビットの信号が順番にソース信号線に出力されるようとする。

20

#### 【0063】

期間Iでは、書き込み用ゲート信号線102にパルスが入力されてTFT108が導通し、記憶回路105にデジタル信号が書き込まれる。続いて、期間IIでは、書き込み用ゲート信号線103にパルスが入力されてTFT109が導通し、記憶回路106にデジタル信号が書き込まれる。最後に、期間IIIでは、書き込み用ゲート信号線104にパルスが入力されてTFT110が導通し、記憶回路107にデジタル信号が書き込まれる。

30

#### 【0064】

以上で、1水平期間分のデジタル信号の処理が終了する。図3(B)の期間は、図3(A)において印で示された期間である。以上の動作を最終段まで行うことにより、1フレーム分のデジタル信号が記憶回路105に書き込まれる。

40

#### 【0065】

書き込まれたデジタル信号は、D/A111によってアナログ信号に変換され、液晶素子に入力される。このアナログ信号に応じて液晶素子の透過率が変化し、階調を表現する。ここでは、3ビットであるから、輝度は0～7までの8段階が得られる。

#### 【0066】

以上の動作を繰り返して、映像の表示が継続的に行われる。ここで、静止画を表示する場合には、最初の動作で記憶回路105～107に、いったんデジタル信号が記憶されてからは、各フレーム期間で記憶回路105～107に記憶されたデジタル信号を反復して読み出せば良い。

#### 【0067】

フレーム期間毎に、記憶回路にそれぞれ記憶されたデジタル信号を反復して読み出し、

50

D / A 1 1 1においてアナログ信号に変換する操作は、D A Cコントローラを用いて制御すればよい。

**【0068】**

もしくは、記憶回路の出力をそれぞれ、読み出し用TFT（図示せず）を介してD / A 1 1 1に入力するようにする。この読み出し用TFTのオン・オフを操作することによって、各フレーム期間毎に、記憶回路に記憶されたデジタル信号を反復して読み出してもよい。

**【0069】**

このとき、読み出し用TFTのゲート電極が接続された読み出し用ゲート信号線（図示せず）に信号を入力する動作は、読み出し用のゲート信号線駆動回路（図示せず）を用いて行う。

10

**【0070】**

したがって、静止画が表示されている期間中は、ソース信号線駆動回路の駆動を停止させることが出来る。

**【0071】**

さらに、記憶回路へのデジタル信号の書き込み、あるいは記憶回路からのデジタル信号の読み出しは、ゲート信号線1本単位で行うことが可能である。すなわち、ソース信号線駆動回路を短期間のみ動作させ、画面の一部のみを書き換えるなどといった表示方法をとることも出来る。

**【0072】**

この場合は、ゲート信号線駆動回路として、デコーダを使うのが望ましい。デコーダを使用する場合には、特開平8-101669に開示された回路を用いればよく、図23に一例を示す。また、ソース信号線駆動回路にもデコーダを用いて部分書き換えを行うことも可能である。

20

**【0073】**

また、本実施形態においては、1画素内に3つの記憶回路を有し、3ビットのデジタル信号を1フレーム分だけ記憶する機能を有しているが、本発明は、記憶回路をこの数に限定しない。例えば、n（nは、2以上の自然数）ビットのデジタル信号をm（mは、2以上の自然数）フレーム分だけ記憶するには、1画素内にn×m個の記憶回路を有していれば良い。

30

**【0074】**

以上のように、画素内に実装された記憶回路を用いてデジタル信号の記憶を行うことにより、静止画を表示する際に各フレーム期間で記憶回路に記憶されたデジタル信号を反復して用いる。これによって、外部回路、ソース信号線駆動回路などを駆動することなく、継続的に静止画表示が可能となる。よって、液晶表示装置の低消費電力化に大きく貢献することが出来る。

**【0075】**

また、ソース信号線駆動回路に関しては、ビット数に応じて増加するラッチ回路等の配置の問題から、必ずしも絶縁体上に一体形成する必要はなく、その一部あるいは全部を外付けで構成しても良い。

40

**【0076】**

さらに、本実施形態にて示したソース信号線駆動回路においては、ビット数に応じたラッチ回路を配置しているが、1ビット分のみ配置して動作させることも可能である。この場合、上位ビットから下位ビットのデジタル信号を直列にラッチ回路に入力すれば良い。

**【0077】**

図24は、上述した構成の液晶表示装置を用いた本発明の携帯情報装置の構成をしたものである。静止画を表示する場合、表示装置2413の画素の内部にある、記憶回路に映像信号を記憶させ、記憶した映像信号を呼び出すことによって、表示をおこなう。よって、従来、動作させていたCPU2406の内部回路のうち、映像信号処理回路2407、VRAM(Video RAM)2411、表示装置2413の中のソース信号線駆動回路を停

50

止することが可能となる。

#### 【0078】

以下その内容について、具体的に説明をおこなう。ペン入力タブレット2401からの入力が一定時間の間行われない、もしくは外部インターフェイスポート2405から、映像表示を変えなければならないような信号入力が一定時間されない場合、CPU2406は静止画モードであると判断をおこなう。CPU2406がそのような判断を行った場合、CPU2406は以下のようない動作をおこなう。LCDコントローラ2412を介して、表示装置2413のソース信号線駆動回路を停止させる。具体的には、ソース信号線駆動回路へのスタートパルス、クロック信号、映像データ信号の供給を停止することによって、ソース信号線駆動回路の動作を停止させることができる。このときゲート信号線駆動回路は停止させずに、信号の供給をうけ、記憶回路のデータを反復して読み出す操作をおこなう。10

#### 【0079】

ゲート信号線駆動回路はソース信号線駆動回路に比べて、一般的には、1/100以下の周波数で駆動されるため、動作を停止しなくとも、消費電力上は問題にならない。もちろん、液晶の画質上の問題、例えば、焼きつき現象が発生しないような液晶材料を使用する場合には、ゲート信号線駆動回路を停止してもよい。このような動作によって、表示装置2413はゲート信号線駆動回路のみ、または、ソース信号線駆動回路とゲート信号線駆動回路の両方の信号線駆動回路を停止させて、表示をおこなう。

#### 【0080】

次に、CPU2406は、CPU2406内部の映像信号処理回路2407および、VRAM2411を停止する。前述したように、表示装置2413は、その内部の記憶回路に蓄えられた映像データで表示を行っているので、新たに映像データを表示装置に入力する必要性がない。よって、映像データを発生、加工する映像信号処理回路2407、VRAM2411などは動作していないてもかまわない。以上により、CPU2406内部の電力削減、VRAM2411の電力削減、ソース信号線駆動回路の電力削減が達成される。20

#### 【0081】

また、ペン入力タブレット2401に入力がされ、映像信号が入力された場合は、ペン入力タブレットの検出回路2402からダブルエットインターフェイス2418を介して、CPU2406に表示内容を変えるような指示がだされ、CPU2406は停止していたVRAM2411、映像信号処理回路2407を動作させる。そして、LCDコントローラ2412を介して、表示装置2413のソース線信号駆動回路にスタートパルス、クロック信号、映像データを供給し、新たな映像信号を画素に書き込むことができる。30

#### 【0082】

この様に、図24中、破線で囲った部分（ゲート信号線駆動回路、LCDコントローラ2412、ペン入力タブレット2401、検出回路2402、ダブルエットインターフェイス2418）が動作していれば、この携帯情報端末は静止画を表示し続けることができる。40

#### 【0083】

図25は本発明を使用した携帯電話の例である。動作は図24の携帯情報端末とおおよそ同じである。携帯情報端末と異なるのは、携帯電話では、入力は、キーボード2501によって行われ、キーボードインターフェイス2518を介してCPU2506で制御されることと、外部からのデータは、電話会社の通信系を介して、アンテナに入力され、送受信回路2515で増幅されたのち、CPU2506で制御されることである。静止画を表示する場合は、携帯情報端末と同様に、映像信号処理回路2507、VRAM2511、ソース信号線駆動回路などは停止させることができる。

#### 【0084】

この様に、図25中、破線で囲った部分（ゲート信号線駆動回路、LCDコントローラ2512、キーボード2501、キーボードインターフェイス2518）が動作していれ50

ば、この携帯電話は静止画を表示し続けることができる。

**【0085】**

以下に本発明の実施例について記述する。

**【実施例1】**

**【0086】**

本実施例においては、実施形態において示した回路における画素を、具体的にトランジスタ等を用いて構成し、その動作について説明する。

**【0087】**

図8は、図1に示した画素と同様のもので、D/A111を実際に回路で構成した例である。図中、各部に付した番号において、図1と同じ部位については、図1と同じ番号を付している。記憶回路105～107の各々に、書き込み用TFT108～110を設け、記憶回路選択信号線（書き込み用ゲート信号線）102～104をもって制御する。

10

**【0088】**

図4は、記憶回路の一例を示したものである。点線枠450で示される部分が記憶回路（図8中、105～107で示す部分）であり、451は書き込み用TFT（図8中、108～110で示す部分）である。ここで示した記憶回路450には、フリップフロップを利用したスタティック型メモリ（Static RAM：SRAM）を用いているが、記憶回路に関してはこの構成に限定しない。

**【0089】**

本実施例にて図8で示した回路の駆動は、実施形態にて図3を用いて示したタイミングチャートに従って駆動することが出来る。図3、図8を用いて、記憶回路選択部の実際の駆動方法を加えて、回路動作について説明する。なお、各番号は、図3、図8のものをそのまま用いる（図番は省略する）。

**【0090】**

図3（A）（B）を参照する。図3（A）において、各フレーム期間を、と表記して説明する。まず、区間ににおける回路動作について説明する。

**【0091】**

シフトレジスタ回路から第2のラッチ回路までの駆動方法に関しては実施形態にて示したものと同様であるのでそれに従う。

**【0092】**

期間Iでは、書き込み用ゲート信号線102にパルスが入力されてTFT108が導通し、記憶回路105にデジタル信号が書き込まれる。続いて、期間IIでは、書き込み用ゲート信号線103にパルスが入力されてTFT109が導通し、記憶回路106にデジタル信号が書き込まれる。最後に、期間IIIでは、書き込み用ゲート信号線104にパルスが入力されてTFT110が導通し、記憶回路107にデジタル信号が書き込まれる。

30

**【0093】**

以上で、1水平期間分のデジタル信号の処理が終了する。図3（B）の期間は、図3（A）において印で示された期間である。以上の動作を最終段まで行うことにより、1フレーム分のデジタル信号が記憶回路105～107に書き込まれる。

**【0094】**

書き込まれたデジタル信号は、D/A111によってアナログ信号に変換され、液晶素子に入力される。このアナログ信号に応じて液晶素子の透過率は変化し、階調を表現する。ここでは、3ビットであるから、輝度は0～7までの8段階が得られる。

40

**【0095】**

以上のようにして、1フレーム期間分の表示が行われる。一方、駆動回路側では、同時に次のフレーム期間のデジタル信号の処理が行われている。

**【0096】**

以上の手順を繰り返すことにより、映像の表示を行う。

**【0097】**

なお、静止画の表示を行う場合には、あるフレームのデジタル信号の、記憶回路への書

50

き込みが終了したら、ソース信号線駆動回路を停止させ、同じ記憶回路に書き込まれている信号を、毎フレームで読み込んで表示を行う。

#### 【0098】

この際、図8において図示していないが、各画素の各記憶回路の出力が、読み出し用TFTを介してD/Aに入力されるようにし、この読み出し用TFTを、操作することによって、フレーム期間毎に記憶回路の信号を反復して読み出すことができる。この読み出し用TFTを操作する回路は、公知の構成の回路を自由に用いることができる。

#### 【0099】

また、記憶回路に入力された信号を、常にD/A回路に入力し、対応するアナログ信号を液晶素子に出力して、静止画の表示を行うこともできる。この場合は、書き込み用TFTが選択され、新たに記憶回路に情報が書き込まれるまで、画素は、同じ輝度の表示を続ける。この駆動方法では、前述の読み出し用TFT等は必要ない。10

#### 【0100】

このような方法により、静止画の表示中における消費電力を大きく低減することが出来る。

#### 【実施例2】

#### 【0101】

本実施例においては、画素部の記憶回路への書き込みを点順次で行うことにより、ソース信号線駆動回路の第2のラッチ回路を省略した例について記す。

#### 【0102】

図5は、記憶回路を有する画素を用いた液晶表示装置における、ソース信号線駆動回路および一部の画素の構成を示したものである。この回路は、3ビットデジタル階調信号に対応したものであり、シフトレジスタ回路(SR)501、ラッチ回路(LAT1)502、画素(Pixel)503を有する。510は、ゲート信号線駆動回路等から直接供給される信号であり、画素の説明とともに後述する。20

#### 【0103】

図6は、図5に示した画素503の回路構成の詳細図である。実施例1と同様、3ビットデジタル階調信号に対応したものであり、液晶素子(LC)、保持容量(CS)、記憶回路(605～607)及びD/A(D/Aコンバータ:611)等を有している。601は第1ビット(MSB)信号用ソース信号線、602は第2ビット信号用ソース信号線、603は第3ビット(LSB)信号用ソース信号線、604は書き込み用ゲート信号線、608～610は書き込み用TFTである。30

#### 【0104】

図7は、本実施例にて示した回路の駆動に関するタイミングチャートである。

図6および図7を用いて説明する。

#### 【0105】

シフトレジスタ回路501からラッチ回路(LAT1)502までの動作は実施形態および実施例1と同様に行われる。図7(B)に示すように、第1段目でのラッチ動作が終了すると、直ちに画素の記憶回路への書き込みを開始する。書き込み用ゲート信号線604にパルスが入力され、書き込み用TFT608～610が導通し、記憶回路への書き込みが可能な状態となる。ラッチ回路502に保持されたビット毎のデジタル信号は、3本のソース信号線601～603を経由して、同時に書き込まれる。40

#### 【0106】

第1段目でラッチ回路に保持されたデジタル信号が、記憶回路へ書き込まれているとき、次段では続くサンプリングパルスに従って、ラッチ回路においてデジタル信号の保持が行われている。このようにして、順次記憶回路への書き込みが行われていく。

#### 【0107】

最終段まで上記動作を繰り返し、1水平期間が終了する。

#### 【0108】

なお、図7(B)で示す期間は、図7(A)において、50で示す期間に相当する。

**【0109】**

全ての水平期間 1 ~ 480 に対して同様の操作を行う。

**【0110】**

以上で、1 フレーム目の表示期間が完了する。区間 では、次のフレームにおけるデジタル信号の処理が行われる。

**【0111】**

以上の手順を繰り返すことにより、映像の表示を行う。なお、静止画の表示を行う場合には、あるフレームのデジタル信号の、記憶回路への書き込みが終了したら、ソース信号線駆動回路を停止させ、同じ記憶回路に書き込まれている信号を毎フレームで読み込んで表示を行う。このような方法により、静止画の表示中における消費電力を大きく低減することが出来る。さらに、実施形態にて示した回路と比較すると、ラッチ回路の数を 1 / 2 とすることが出来、回路配置の省スペース化による装置全体の小型化に貢献出来る。10

**【実施例 3】****【0112】**

本実施例においては、実施例 2 にて示した、第 2 のラッチ回路を省略した液晶表示装置の回路構成を応用し、線順次駆動により画素内の記憶回路への書き込みを行う方法を用いた液晶表示装置の例について記す。

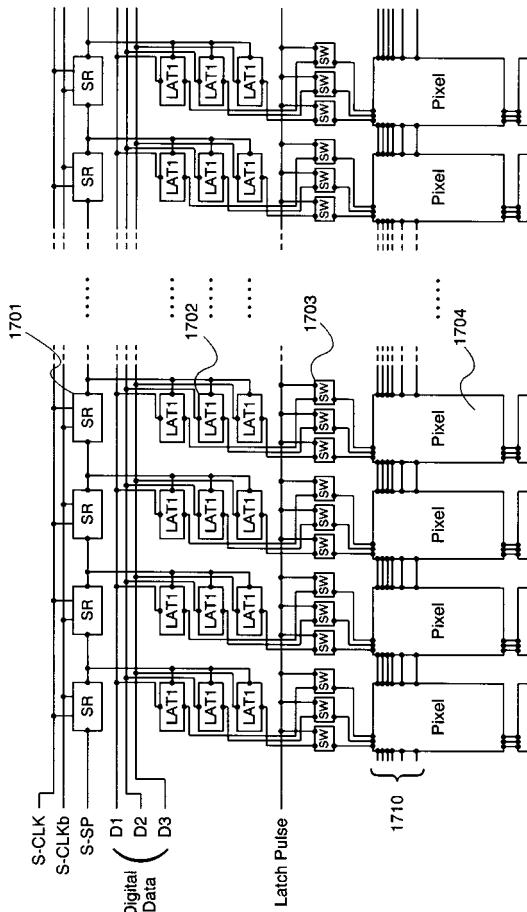

**【0113】**

図 17 は、本実施例にて示す液晶表示装置のソース信号線駆動回路の回路構成例を示している。この回路は、3 ビットデジタル階調信号に対応したものであり、シフトレジスタ回路 1701、ラッチ回路 1702、スイッチ回路 1703、画素 1704 を有する。20 1710 は、ゲート信号線駆動回路あるいは外部から直接供給される信号である。画素の回路構成に関しては、実施例 2 のものと同様で良いので、図 6 をそのまま参照する。

**【0114】**

図 18 は、本実施例にて示した回路の駆動に関するタイミングチャートである。図 6、図 17 および図 18 を用いて説明する。

**【0115】**

シフトレジスタ回路 1701 からサンプリングパルスが出力され、ラッチ回路 1702 で、サンプリングパルスに従ってデジタル信号を保持するまでの動作は、実施例 1 および実施例 2 と同様である。本実施例では、ラッチ回路 1702 と画素 1704 内の記憶回路との間に、スイッチ回路 1703 を有しているため、ラッチ回路でのデジタル信号の保持が完了しても、直ちに記憶回路への書き込みが開始されない。ドットデータサンプリング期間が終了するまでの間は、スイッチ回路 1703 は閉じたままであり、その間、ラッチ回路ではデジタル信号が保持され続ける。30

**【0116】**

図 18 (B) に示すように、1 水平期間分のデジタル信号の保持が完了すると、その後の帰線期間中にラッチ信号 (Latch Pulse) が入力されてスイッチ回路 1703 が一斉に開き、ラッチ回路 1702 で保持されていたデジタル信号は一斉に画素 1704 内の記憶回路に書き込まれる。このときの書き込み動作に関わる、画素 1704 内の動作、さらには次のフレーム期間における表示の際の読み出し動作に関わる、画素 1704 内の動作については、実施例 2 と同様で良いので、ここでは説明を省略する。40

**【0117】**

図 18 (B) で示す期間は、図 18 (A) において、で示す期間である。

**【0118】**

以上のことによつて、第 2 のラッチ回路を省略したソース信号線駆動回路においても、線順次の書き込み駆動を容易に行うことが出来る。

**【実施例 4】****【0119】**

本実施例では、D/A コンバータとして、複数の階調電圧線を選択する方式のものを用いた例を示す。図 8 に、その回路図を示す。50

**【0120】**

3ビットのデジタル信号を処理する場合、8本の階調電圧線があり、それぞれにスイッチTFTが接続されている。記憶回路の出力は、デコーダを介して、それらのスイッチTFTを選択的に駆動する。スイッチはトランスマッショングートを用いても良い。

**【0121】**

なお、図8において、記憶回路105～107のそれからの出力は、記憶回路に記憶された信号及びその信号の反転信号によって構成される。

**【0122】**

本実施例は、実施例1～実施例3と自由に組み合わせて実施することが可能である。

**【実施例5】**

10

**【0123】**

本実施例では、実施例4において図8で示したD/Aコンバータとは異なる構造のものを用いた例を示す。図9に、その回路図を示す。

**【0124】**

実施例4において図8で示したものと同様に階調電圧線を選択する方式であるが、図8では、素子の数が多く、画素内で素子の占める面積が大きくなる。そのため、図9では、スイッチを直列接続し、デコーダとスイッチを兼ねて素子数を減らしている。スイッチはトランスマッショングートを用いても良い。

**【0125】**

なお、図9において、記憶回路105～107のそれからの出力は、記憶回路に記憶された信号及びその信号の反転信号によって構成される。

20

**【実施例6】**

本実施例は、実施例1～実施例3と自由に組み合わせて実施することが可能である。

**【0126】**

本実施例では、実施例4や実施例5において図8や図9で示したD/Aコンバータとは異なる構造のものを用いた例を示す。図20に、その回路図を示す。

**【0127】**

図8や図9で示したD/Aコンバータでは、階調電圧線を用いるため、階調数の分だけ配線が必要となり、多階調化には適さない。そのため、図20では、容量C1～C3の組み合わせによって、基準電圧を分圧し、階調電圧を作っている。この様な容量分割方式では、容量C1～C3の比で階調が作られるため、多様な階調が表現可能である。

30

**【0128】**

この様な容量分割方式のD/Aコンバータは、AMLCD99 Digest of Technical Papers p29～32に記載してある。

**【0129】**

本実施例は、実施例1～実施例3と自由に組み合わせて実施することが可能である。

**【実施例7】****【0130】**

本実施例では、実施例4や実施例5及び実施例6において図8や図9及び図20で示したD/Aコンバータとは異なる構造のものを用いた例を示す。図21に、その回路図を示す。

40

**【0131】**

図21に示したものは、実施例6で示した図20のD/Aコンバータをさらに簡略化したものである。容量C1～C3それぞれの2つの電極のうち液晶素子と接続されていない方の電極は、リセット時には $V_L$ に接続され、非リセット時には、 $V_H$ または $V_L$ のいずれかに接続されるが、その接続をスイッチのみで構成できる。スイッチはトランスマッショングートを用いても良い。

**【0132】**

なお、図21において、記憶回路105～107のそれからの出力は、記憶回路に

50

記憶された信号及びその信号の反転信号によって構成される。

**【0134】**

本実施例は、実施例1～実施例3と自由に組み合わせて実施することが可能である。

**【実施例8】**

**【0135】**

図22に示す様に、ソース信号線駆動回路のラッチ回路を1ビット分のみ有し、代わりにソース信号線駆動回路を3倍の速度で動作させ、1ライン期間中に、第1ビットデータ、第2ビットデータ、第3ビットデータの順にデータをソース信号線駆動回路に入力し、実施例1のソース信号線駆動回路と同様の効果を得られる。

**【0136】**

10

この方式では、外部にデータを順に入れ替えるための回路が必要であるが、ソース信号線駆動回路は小さくすることが可能である。

**【実施例9】**

**【0137】**

本実施例では、本発明の表示装置の画素部とその周辺に設けられる駆動回路部（ソース信号線側駆動回路、ゲート信号線側駆動回路、画素選択信号線側駆動回路）のTFTを同時に作製する方法について説明する。但し、説明を簡単にするために、駆動回路部に関しては基本単位であるCMOS回路を図示することとする。

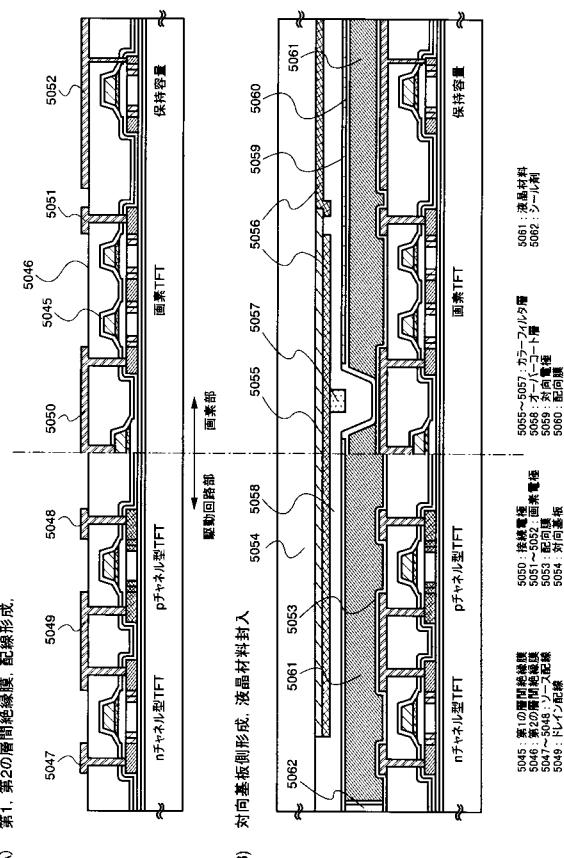

**【0138】**

20

まず、図10(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスから成る基板5001上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜5002を形成する。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜5002aを10～200[nm]（好ましくは50～100[nm]）形成し、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化シリコン膜5002bを50～200[nm]（好ましくは100～150[nm]）の厚さに積層形成する。

本実施例では下地膜5002を2層構造として示したが、前記絶縁膜の单層膜または2層以上積層させた構造として形成しても良い。

**【0139】**

30

島状半導体層5003～5006は、非晶質構造を有する半導体膜をレーザー結晶化法や公知の熱結晶化法を用いて作製した結晶質半導体膜で形成する。この島状半導体層5003～5006の厚さは25～80[nm]（好ましくは30～60[nm]）の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコングルマニウム(SiGe)合金などで形成すると良い。

**【0140】**

40

レーザー結晶化法で結晶質半導体膜を作製するには、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宜選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数30[Hz]とし、レーザーエネルギー密度を100～400[mJ/cm<sup>2</sup>]（代表的には200～300[mJ/cm<sup>2</sup>]）とする。また、YAGレーザーを用いる場合にはその第2高調波を用いパルス発振周波数1～10[kHz]とし、レーザーエネルギー密度を300～600[mJ/cm<sup>2</sup>]（代表的には350～500[mJ/cm<sup>2</sup>]）とすると良い。そして幅100～1000[μm]、例えば400[μm]で線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率（オーバーラップ率）を80～98[%]として行う。

**【0141】**

次いで、島状半導体層5003～5006を覆うゲート絶縁膜5007を形成する。ゲート絶縁膜5007はプラズマCVD法またはスパッタ法を用い、厚さを40～150[n

50

m]としてシリコンを含む絶縁膜で形成する。本実施例では、120 [nm]の厚さで酸化窒化シリコン膜で形成する。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。例えば、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS (Tetraethyl Orthosilicate)とO<sub>2</sub>とを混合し、反応圧力40 [Pa]、基板温度300～400[°C]とし、高周波(13.56 [MHz])、電力密度0.5～0.8 [W/cm<sup>2</sup>]で放電させて形成することが出来る。このようにして作製される酸化シリコン膜は、その後400～500[°C]の熱アニールによりゲート絶縁膜として良好な特性を得ることが出来る。

#### 【0142】

そして、ゲート絶縁膜5007上にゲート電極を形成するための第1の導電膜5008と第2の導電膜5009とを形成する。本実施例では、第1の導電膜5008をTaで50～100 [nm]の厚さに形成し、第2の導電膜5009をWで100～300 [nm]の厚さに形成する。

#### 【0143】

Ta膜はスパッタ法で、TaのターゲットをArでスパッタすることにより形成する。この場合、Arに適量のXeやKrを加えると、Ta膜の内部応力を緩和して膜の剥離を防止することが出来る。また、Ta相のTa膜の抵抗率は20 [μΩ cm]程度でありゲート電極に使用することが出来るが、Ta相のTa膜の抵抗率は180 [μΩ cm]程度でありゲート電極とするには不向きである。Ta相のTa膜を形成するために、TaのTa相に近い結晶構造をもつ窒化タンタルを10～50 [nm]程度の厚さでTaの下地に形成しておくとTa相のTa膜を容易に得ることが出来る。

#### 【0144】

W膜を形成する場合には、Wをターゲットとしたスパッタ法で形成する。その他に6フッ化タンゲステン(WF<sub>6</sub>)を用いる熱CVD法で形成することも出来る。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20 [μΩ cm]以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることが出来るが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999 [%]のWターゲットを行い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9～20 [μΩ cm]を実現することが出来る。

#### 【0145】

なお、本実施例では、第1の導電膜5008をTa、第2の導電膜5009をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cuなどから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。本実施例以外の組み合わせの一例で望ましいものとしては、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をWとする組み合わせ、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をAlとする組み合わせ、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をCuとする組み合わせ等が挙げられる。

#### 【0146】

次に、レジストによるマスク5010を形成し、電極及び配線を形成するための第1のエッチング処理を行う。本実施例ではICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング法を行い、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>を混合し、1 [Pa]の圧力でコイル型の電極に500 [W]のRF(13.56 [MHz])電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100 [W]のRF(13.56 [MHz])電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した場合にはW膜及びTa膜とも同程度にエッチングされる。

#### 【0147】

上記エッチング条件では、レジストによるマスクの形状を適したものとすることにより

10

20

30

40

50

、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテー<sup>10</sup>パー形状となる。テー<sup>10</sup>パー部の角度は15～45°となる。

ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10～20[%]程度の割合でエッティング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2～4（代表的には3）であるので、オーバーエッティング処理により、酸化窒化シリコン膜が露出した面は20～50[nm]程度エッティングされることになる。こうして、第1のエッティング処理により第1の導電層と第2の導電層から成る第1の形状の導電層5011～5016（第1の導電層5011a～5016aと第2の導電層5011b～5016b）を形成する。このとき、ゲート絶縁膜5007においては、第1の形状の導電層5011～5016で覆われない領域は20～50[nm]程度エッティングされ薄くなった領域が形成される。<sup>10</sup>

（図10（B））

#### 【0148】

そして、第1のドーピング処理を行いn型を付与する不純物元素を添加する。

ドーピングの方法はイオンドープ法もしくはイオン注入法で行えれば良い。イオンドープ法の条件はドーズ量を $1 \times 10^{13} \sim 5 \times 10^{14} [\text{atoms/cm}^2]$ とし、加速電圧を60～100[keV]として行う。N型を付与する不純物元素として15族に属する元素、典型的にはリン（P）または砒素（As）を用いるが、ここではリン（P）を用いる。この場合、導電層5011～5016がn型を付与する不純物元素に対するマスクとなり、自己整合的に第1の不純物領域5017～5020が形成される。第1の不純物領域5017～5020には $1 \times 10^{20} \sim 1 \times 10^{21} [\text{atoms/cm}^3]$ の濃度範囲でn型を付与する不純物元素を添加する。（図10（B））<sup>20</sup>

#### 【0149】

次に、図10（C）に示すように、レジストマスクは除去しないまま、第2のエッティング処理を行う。エッティングガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、W膜を選択的にエッティングする。この時、第2のエッティング処理により第2の形状の導電層5021～5026（第1の導電層5021a～5026aと第2の導電層5021b～5026b）を形成する。このとき、ゲート絶縁膜5007においては、第2の形状の導電層5021～5026で覆われない領域はさらに20～50[nm]程度エッティングされ薄くなった領域が形成される。<sup>30</sup>

#### 【0150】

W膜やTa膜の、CF<sub>4</sub>とCl<sub>2</sub>の混合ガスによるエッティング反応は、生成されるラジカルまたはイオン種と反応生成物の蒸気圧から推測することが出来る。WとTaのフッ化物と塩化物の蒸気圧を比較すると、Wのフッ化物であるWF<sub>6</sub>が極端に高く、その他のWC<sub>1.5</sub>、TaF<sub>5</sub>、TaCl<sub>5</sub>は同程度である。従って、CF<sub>4</sub>とCl<sub>2</sub>の混合ガスではW膜及びTa膜共にエッティングされる。しかし、この混合ガスに適量のO<sub>2</sub>を添加するとCF<sub>4</sub>とO<sub>2</sub>が反応してCOとFになり、FラジカルまたはFイオンが多量に発生する。その結果、フッ化物の蒸気圧が高いW膜のエッティング速度が増大する。一方、TaはFが増大しても相対的にエッティング速度の増加は少ない。また、TaはWに比較して酸化されやすいので、O<sub>2</sub>を添加することでTaの表面が酸化される。Taの酸化物はフッ素や塩素と反応しないため、さらにTa膜のエッティング速度は低下する。従って、W膜とTa膜とのエッティング速度に差を作ることが可能となりW膜のエッティング速度をTa膜よりも大きくすることが可能となる。<sup>40</sup>

#### 【0151】

そして、図11（A）に示すように第2のドーピング処理を行う。この場合、第1のドーピング処理よりもドーズ量を下げる高い加速電圧の条件としてn型を付与する不純物元素をドーピングする。例えば、加速電圧を70～120[keV]とし、 $1 \times 10^{13} [\text{atoms/cm}^2]$ のドーズ量で行い、図10（B）で島状半導体層に形成された第1の不純物領域の内側に新たな不純物領域を形成する。ドーピングは、第2の形状の導電層5021～5026を不純物元素に対するマスクとして用い、第1の導電層5021a～5026aの下側の<sup>50</sup>

領域の半導体層にも不純物元素が添加されるようにドーピングする。こうして、第2の不純物領域 5027～5031が形成される。この第2の不純物領域 5027～5031に添加されたリン(P)の濃度は、第1の導電層 5021a～5026aのテーパー部の膜厚に従って緩やかな濃度勾配を有している。なお、第1の導電層 5021a～5026aのテーパー部と重なる半導体層において、第1の導電層 5021a～5026aのテーパー部の端部から内側に向かって若干、不純物濃度が低くなっているものの、ほぼ同程度の濃度である。

#### 【0152】

続いて、図11(B)に示すように第3のエッチング処理を行う。エッチングガスにCF<sub>6</sub>を用い、反応性イオンエッチング法(RIE法)を用いて行う。

10

第3のエッチング処理により、第1の導電層 5021a～5026aのテーパー部を部分的にエッチングして、第1の導電層が半導体層と重なる領域が縮小される。第3のエッチング処理によって、第3の形状の導電層 5032～5037(第1の導電層 5032a～5037aと第2の導電層 5032b～5037b)

を形成する。このとき、ゲート絶縁膜 5007においては、第3の形状の導電層 5032～5037で覆われない領域はさらに20～50[nm]程度エッチングされ薄くなった領域が形成される。

#### 【0153】

第3のエッチング処理によって、第2の不純物領域 5027～5031においては、第1の導電層 5032a～5037aと重なる第2の不純物領域 5027a～5031aと、第1の不純物領域と第2の不純物領域との間の第3の不純物領域 5027b～5031bとが形成される。

20

#### 【0154】

そして、図11(C)に示すように、pチャネル型TFTを形成する島状半導体層 5004に、第1の導電型とは逆の導電型の第4の不純物領域 5039～5044を形成する。第3の形状の導電層 5033bを不純物元素に対するマスクとして用い、自己整合的に不純物領域を形成する。このとき、nチャネル型TFTを形成する島状半導体層 5003、5005、保持容量部 5006および配線部 5034はレジストマスク 5038で全面を被覆しておく。不純物領域 5039～5044にはそれぞれ異なる濃度でリンが添加されているが、ジボラン(B<sub>2</sub>H<sub>6</sub>)を用いたイオンドープ法で形成し、そのいずれの領域においても不純物濃度が2×10<sup>20</sup>～2×10<sup>21</sup>[atoms/cm<sup>3</sup>]となるようにする。

30

#### 【0155】

以上までの工程でそれぞれの島状半導体層に不純物領域が形成される。島状半導体層と重なる第3の形状の導電層 5032、5033、5035、5036がゲート電極として機能する。また、5034は島状のソース信号線として機能する。5037は容量配線として機能する。

#### 【0156】

レジストマスク 5038を除去した後、導電型の制御を目的として、それぞれの島状半導体層に添加された不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することが出来る。

40

熱アニール法では酸素濃度が1[ppm]以下、好ましくは0.1[ppm]以下の窒素雰囲気中で400～700[ ]、代表的には500～600[ ]で行うものであり、本実施例では500[ ]で4時間の熱処理を行う。ただし、第3の形状の導電層 5032～5037に用いた配線材料が熱に弱い場合には、配線等を保護するため層間絶縁膜(シリコンを主成分とする)を形成した後で活性化を行うことが好ましい。

#### 【0157】

さらに、3～100[%]の水素を含む雰囲気中で、300～450[ ]で1～12時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダンギリングボンドを終端する工程である。水素化の他の手段として

50

、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

**【0158】**

次いで、第1の層間絶縁膜5045は酸化窒化シリコン膜を100～200[nm]の厚さで形成する。その上に有機絶縁物材料から成る第2の層間絶縁膜5046を形成する。次いで、コンタクトホールを形成するためのエッティング工程を行う。

**【0159】**

そして、駆動回路部において島状半導体層のソース領域とコンタクトを形成するソース配線5047、5048、ドレイン領域とコンタクトを形成するドレイン配線5049を形成する。また、画素部においては、接続電極5050、画素電極5051、5052を形成する（図12（A））。この接続電極5050により、ソース信号線5034は、画素TFTと電気的に接続される。なお、画素電極5052及び保持容量は隣り合う画素のものである。

**【0160】**

以上のようにして、nチャネル型TFT、pチャネル型TFTを有する駆動回路部と、画素TFT、保持容量を有する画素部とを同一基板上に形成することができる。本明細書中ではこのような基板をアクティブマトリクス基板と呼ぶ。

**【0161】**

ブラックマトリクスを用いることなく、画素電極間の隙間を遮光することができるように、画素電極の端部をソース信号線やゲート信号線と重なるように配置されている。

**【0162】**

また、本実施例で示す工程に従えば、アクティブマトリクス基板の作製に必要なフォトマスクの数を5枚（島状半導体層パターン、第1配線パターン（ソース信号線、ゲート信号線、容量配線）、pチャネル領域のマスクパターン、コンタクトホールパターン、第2配線パターン（画素電極、接続電極含む））とすることができる。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与することができる。

**【0163】**

続いて、図12（A）の状態のアクティブマトリクス基板を得た後、図12（B）において、アクティブマトリクス基板上に配向膜5053を形成しラビング処理を行う。

**【0164】**

一方、対向基板5054を用意する。対向基板5054にはカラーフィルター層5055～5057、オーバーコート層5058を形成する。カラーフィルター層はTFTの上方で赤色のカラーフィルター層5055と青色のカラーフィルター層5056とを重ねて形成し遮光膜を兼ねる構成とする。少なくともTFTと、接続電極と画素電極との間を遮光する必要があるため、それらの位置を遮光するように赤色のカラーフィルターと青色のカラーフィルターを重ねて配置することが好ましい。

**【0165】**

また、接続電極5050に合わせて赤色のカラーフィルター層5055、青色のカラーフィルター層5056、緑色のカラーフィルター層5057とを重ね合わせてスペーサを形成する。各色のカラーフィルターはアクリル樹脂に顔料を混合したもので1～3[μm]の厚さで形成する。これは感光性材料を用い、マスクを用いて所定のパターンに形成することができる。スペーサの高さはオーバーコート層5058の厚さ1～4[μm]を考慮することにより2～7[μm]、好ましくは4～6[μm]とすることができます、この高さによりアクティブマトリクス基板と対向基板とを貼り合わせた時のギャップを形成する。オーバーコート層5058は光硬化型または熱硬化型の有機樹脂材料で形成し、例えば、ポリイミドやアクリル樹脂などを用いる。

**【0166】**

スペーサの配置は任意に決定すれば良いが、例えば図12（B）で示すように接続電極上に位置が合うように対向基板5054上に配置すると良い。また、駆動回路部のTFT上にその位置を合わせてスペーサを対向基板5054上に配置してもよい。このスペーサは駆動回路部の全面に渡って配置しても良いし、ソース配線およびドレイン配線を覆うよ

10

20

30

40

50

うにして配置しても良い。

【0167】

オーバーコート層5058を形成した後、対向電極5059をパターニング形成し、配向膜5060を形成した後ラビング処理を行う。

【0168】

そして、画素部と駆動回路部が形成されたアクティブマトリクス基板と対向基板とをシール剤5062で貼り合わせる。シール剤5062にはフィラーが混入されていて、このフィラーとスペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料5061を注入し、封止剤(図示せず)によって完全に封止する。液晶材料5061には公知の液晶材料を用いれば良い。このようにして図12(B)に示すアクティブマトリクス型液晶表示装置が完成する。

10

【0169】

なお、上記の行程により作製されるアクティブマトリクス型液晶表示装置におけるTFTはトップゲート構造をとっているが、ボトムゲート構造のTFTやその他の構造のTFTに対しても本実施例は容易に適用され得る。

【0170】

また、本実施例においては、ガラス基板上を使用しているが、ガラス基板に限らず、プラスチック基板、ステンレス基板、単結晶ウェハ等、ガラス基板以外のものを使用することによっても実施が可能である。

【0171】

本実施例は、実施例1～実施例8と自由に組み合わせて実施することが可能である。

20

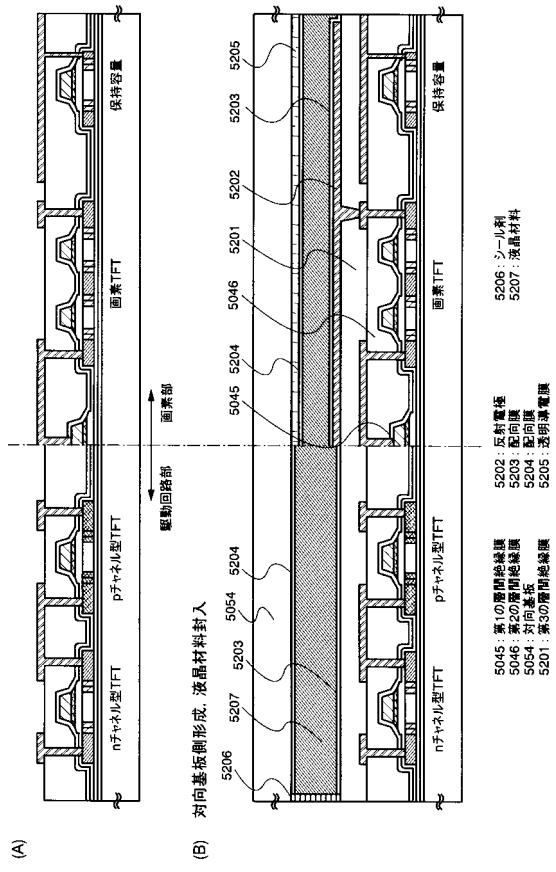

【実施例10】

【0172】

本発明の液晶表示装置は、その画素部に記憶回路を複数有するため、1つの画素を構成する素子の数が通常の画素よりも多くなる。よって、透過型の液晶表示装置の場合、開口率の低下による輝度不足が考えられることから、本発明は、反射型の液晶表示装置に適用されるのが望ましい。本実施例において、作製工程の一例を示す。

【0173】

実施例9に従い、図19(A)に示すアクティブマトリクス基板(図12(A)と同様)を作製する。続いて、第3の層間絶縁膜5201として、樹脂膜を形成した後、画素電極部にコンタクトホールを開口し、反射電極5202を形成する。反射電極5202としては、Al、Agを主成分とする膜、あるいはそれらの積層膜等の、反射性に優れた材料を用いることが望ましい。

30

【0174】

一方、対向基板5054を用意する。対向基板5054には、本実施例においては対向電極5205をパターニングして形成している。対向電極5205は、透明導電膜として形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物(ITOと呼ばれる)または酸化インジウムと酸化亜鉛との化合物からなる材料を用いることが出来る。

【0175】

特に図示していないが、カラー液晶表示装置の作製の際には、カラーフィルタ層を形成する。このとき、隣接した色の異なるカラーフィルタ層を重ねて形成し、TFT部分の遮光膜を兼ねる構成とすると良い。

40

【0176】

その後、アクティブマトリクス基板および対向基板に、配向膜5203および5204を形成し、ラビング処理を行う。

【0177】

そして、画素部と駆動回路部が形成されたアクティブマトリクス基板と対向基板とをシール剤5206で貼り合わせる。シール剤5206にはフィラーが混入されていて、このフィラーとスペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料5207を注入し、封止剤(図示せず)によって完全に封止する

50

。液晶材料 5207 には公知の液晶材料を用いれば良い。このようにして図 19 (B) に示す反射型の液晶表示装置が完成する。

#### 【0178】

なお、本実施例においては、ガラス基板に限らず、プラスチック基板、ステンレス基板、単結晶ウェハ等、ガラス基板以外のものを使用することも可能である。

#### 【0179】

また、画素の半分を反射電極、残る半分を透明電極とした、半透過型の表示装置として作製する場合にも、本発明は容易に適用することが出来る。

#### 【0180】

本実施例は、実施例 1 ~ 実施例 8 と自由に組み合わせて実施することが可能である。

10

#### 【実施例 11】

#### 【0181】

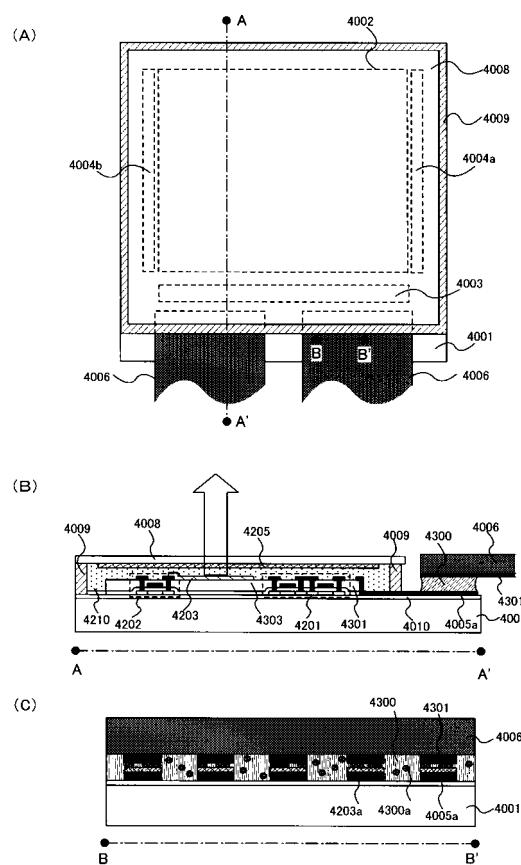

本実施例では、本発明の液晶表示装置を作製した例について、図 27 を用いて説明する。

#### 【0182】

図 27 (A) は、TFT 基板と対向基板との間に液晶を封止することによって形成された液晶表示装置の上面図であり、図 27 (B) は、図 27 (A) の A - A' における断面図、図 27 (C) は図 27 (A) の B - B' における断面図である。

#### 【0183】

TFT 基板 4001 上に設けられた画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b とを囲むようにして、シール材 4009 が設けられている。また画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b の上に対向基板 4008 が設けられている。TFT 基板 4001 とシール材 4009 と対向基板 4008 とで囲まれた空間に液晶 4210 が充填されている。

20

#### 【0184】

また TFT 基板 4001 上に設けられた画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b とは、複数の TFT を有している。図 27 (B) では代表的に、下地膜 4010 上に形成された、ソース信号線駆動回路 4003 に含まれる駆動 TFT ( 但し、ここでは n チャネル型 TFT と p チャネル型 TFT を図示する ) 4201 及び画素部 4002 に含まれる画素 TFT ( 画素電極にかかる電圧を制御する TFT ) 4202 を図示した。

30

#### 【0185】

本実施例では、駆動 TFT 4201 には公知の方法で作製された p チャネル型 TFT 及び n チャネル型 TFT が用いられ、画素 TFT 4202 には公知の方法で作製された p チャネル型 TFT が用いられる。また、画素部 4002 には画素 TFT 4202 のゲート電極に電気的に接続された保持容量 ( 図示せず ) が設けられる。

#### 【0186】

駆動 TFT 4201 及び画素 TFT 4202 上には層間絶縁膜 ( 平坦化膜 ) 4301 が形成され、その上に画素 TFT 4202 のドレインと電気的に接続する画素電極 4203 が形成される。

40

#### 【0187】

対向基板 4008 上には対向電極 4205 が形成されている。なお図 27 (B) では図示していないが、カラーフィルターや偏光板を適宜設ける。そして対向電極 4205 には所定の電圧が与えられている。

#### 【0188】

以上のようにして、画素電極 4203、液晶 4210 及び対向電極 4205 からなる液晶セルが形成される。

#### 【0189】

4005 は引き回し配線であり、画素部 4002、ソース信号線駆動回路 4003、第

50

1 のゲート信号線駆動回路 4004a、第2のゲート信号線駆動回路 4004b と外部の電源とを接続している。引き回し配線 4005a はシール材 4009 と TFT 基板 4001との間を通り、異方導電性フィルム 4300 を介して FPC 4006 が有する FPC 用配線 4301 に電気的に接続される。

#### 【0190】

対向基板 4008 としては、ガラス材、金属材（代表的にはステンレス材）、セラミック材、プラスチック材（プラスチックフィルムも含む）を用いることができる。プラスチック材としては、FRP（Fiberglass-Reinforced Plastic）板、PVF（ポリビニルフルオライド）フィルム、マイラーフィルム、ポリエスチルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルを PVF フィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。10

#### 【0191】

但し、画素電極からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエスチルフィルムまたはアクリルフィルムのような透明物質を用いる。

#### 【0192】

図 27(C) に示すように、画素電極 4203 が形成されると同時に、引き回し配線 4005a 上に接するように導電性膜 4203a が形成される。

#### 【0193】

また、異方導電性フィルム 4300 は導電性フィラー 4300a を有している。TFT 基板 4001 と FPC 4006 とを熱圧着することで、TFT 基板 4001 上の導電性膜 4203a と FPC 4006 上の FPC 用配線 4301 とが、導電性フィラー 4300a によって電気的に接続される。20

#### 【0194】

本実施例は、実施例 1 ~ 実施例 10 と自由に組み合わせて実施することが可能である。

#### 【実施例 12】

#### 【0195】

本実施例では、本発明の液晶表示装置として、透過型の液晶表示装置を使用した場合の例を示す。

#### 【0196】

デサインルールを  $1 \mu m$  ルール、画素ピッチを  $100 \mu m$  程度とすれば、画素内部の記憶回路及び D/A コンバータ等は、ソース信号線の下に配置することが可能となり、開口率の低下の問題を解決することができる。これにより、本発明を反射型の液晶表示装置だけでなく透過型の液晶表示装置にも適用できる。30

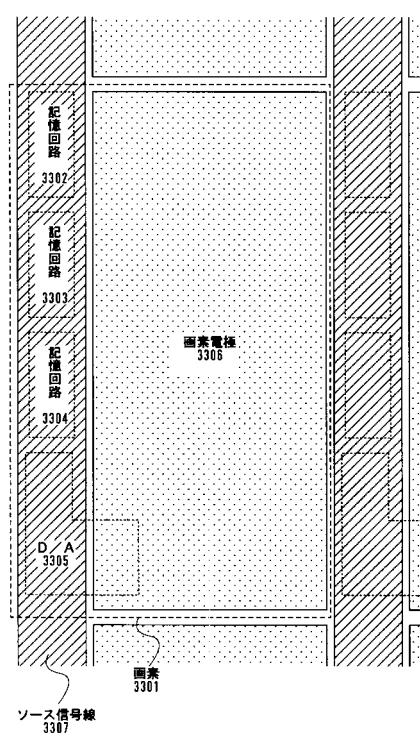

#### 【0197】

図 30 に、上記構成の透過型液晶表示装置の画素の上面図を模式的に示す。

#### 【0198】

3301 は画素、3302 ~ 3304 は記憶回路、3305 は D/A コンバータ（図中 D/A と記載）、3306 は画素電極、3307 はソース信号線である。なお、対向電極やカラーフィルタ及び保持容量等は図示していない。ここで、記憶回路 3302 ~ 3304 及び D/A コンバータ 3305 は、ソース信号線 3307 と重ねて形成されている。40

#### 【0199】

なお図示していないが、ソース信号線 3307 の下ではなくゲート信号線と重ねて、これらの記憶回路 3302 ~ 3304 及び D/A コンバータ 3305 等を配置することも可能である。

#### 【実施例 13】

#### 【0200】

実施例 1 ~ 実施例 12 にて示した、本発明の液晶表示装置の画素部においては、記憶回路は、スタティック型メモリ（Static RAM : SRAM）を用いて構成していたが、記憶回路は SRAM のみに限定されない。本発明の液晶表示装置の画素部に適用可能な記憶回路に50

は、他にダイナミック型メモリ（Dynamic RAM：DRAM）等があげられる。

#### 【0201】

さらに、特に図示しないが、他の形式の記憶回路として、強誘電体メモリ（Ferroelectric RAM：FRAM）を利用して本発明の液晶表示装置の画素部を構成することも可能である。FRAMは、SRAMやDRAMと同等の書き込み速度を有する不揮発性メモリであり、その書き込み電圧が低い等の特徴を利用して、本発明の液晶表示装置のさらなる低消費電力化が可能である。またその他、フラッシュメモリ等によつても、構成は可能である。

#### 【0202】

本実施例は、実施例1～実施例12と自由に組み合わせて実施することが可能である。

#### 【実施例14】

10

#### 【0203】

本発明を適用して作製した駆動回路を用いたアクティブマトリクス型液晶表示装置には様々な用途がある。本実施例では、本発明を適用して作製した駆動回路を用いた表示装置を組み込んだ半導体装置について説明する。

#### 【0204】

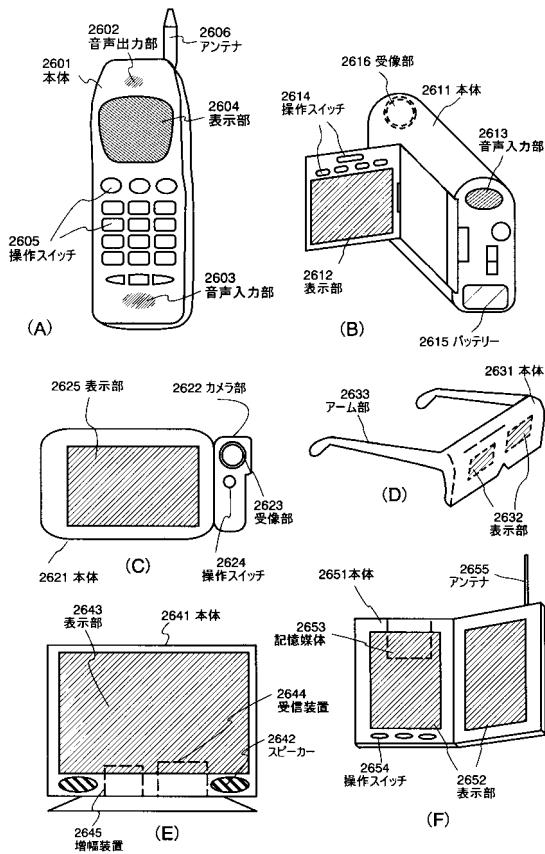

このような表示装置には、携帯情報端末（電子手帳、モバイルコンピュータ、携帯電話等）、ビデオカメラ、デジタルカメラ、パソコンコンピュータ、テレビ等が挙げられる。それらの一例を図15および図16に示す。

#### 【0205】

図15（A）は携帯電話であり、本体2601、音声出力部2602、音声入力部2603、表示部2604、操作スイッチ2605、アンテナ2606から構成されている。本発明は表示部2604に適用することができる。

20

#### 【0206】

図15（B）はビデオカメラであり、本体2611、表示部2612、音声入力部2613、操作スイッチ2614、バッテリー2615、受像部2616から成っている。本発明は表示部2612に適用することができる。

#### 【0207】

図15（C）はモバイルコンピュータあるいは携帯情報端末であり、本体2621、カメラ部2622、受像部2623、操作スイッチ2624、表示部2625で構成されている。本発明は表示部2625に適用することができる。

30

#### 【0208】

図15（D）はヘッドマウントディスプレイであり、本体2631、表示部2632、アーム部2633で構成される。本発明は表示部2632に適用することができる。

#### 【0209】

図15（E）はテレビであり、本体2641、スピーカー2642、表示部2643、受信装置2644、増幅装置2645等で構成される。本発明は表示部2643に適用することができる。

#### 【0210】

図15（F）は携帯書籍であり、本体2651、表示部2652、記憶媒体2653、操作スイッチ2654、アンテナ2655から構成されており、ミニディスク（MD）やDVD（Digital Versatile Disc）に記憶されたデータや、アンテナで受信したデータを表示するものである。本発明は表示部2652に適用することができる。

40

#### 【0211】

図16（A）はパソコンコンピュータであり、本体2201、画像入力部2202、表示部2203、キーボード2204で構成される。本発明は表示部2203に適用することができる。

#### 【0212】

図16（B）はプログラムを記録した記録媒体を用いるプレーヤーであり、本体2211、表示部2212、スピーカー部2213、記録媒体2214、操作スイッチ2215

50

で構成される。なお、この装置は記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部2212に適用することができる。

**【0213】**

図16(C)はデジタルカメラであり、本体2221、表示部2222、接眼部2223、操作スイッチ2224、受像部(図示しない)で構成される。本発明は表示部2222に適用することができる。

**【0214】**

図16(D)は片眼のヘッドマウントディスプレイであり、表示部2231、バンド部2232で構成される。本発明は表示部2231に適用することができる。

10

**【実施例15】**

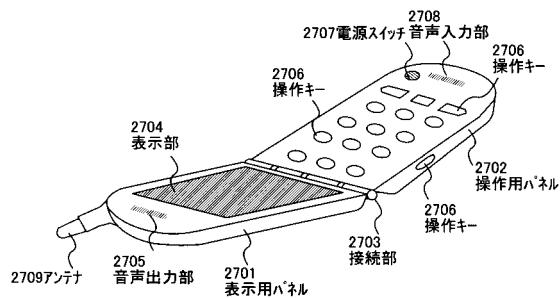

**【0215】**

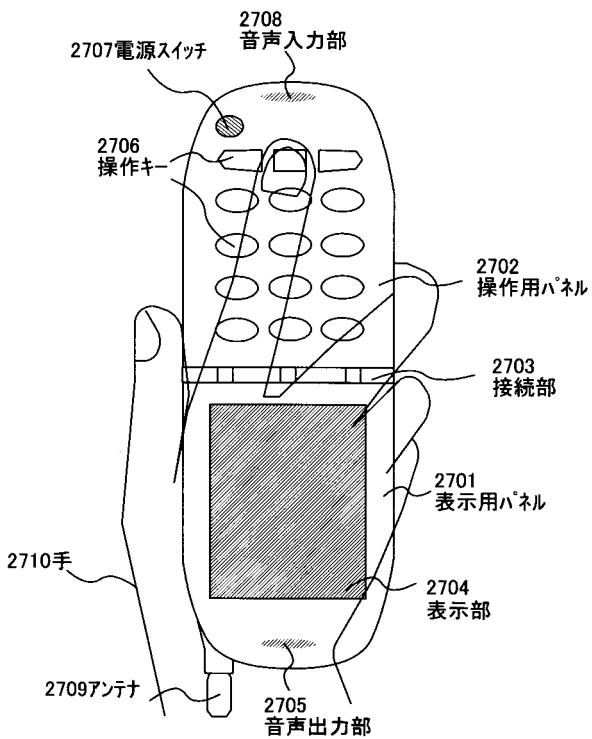

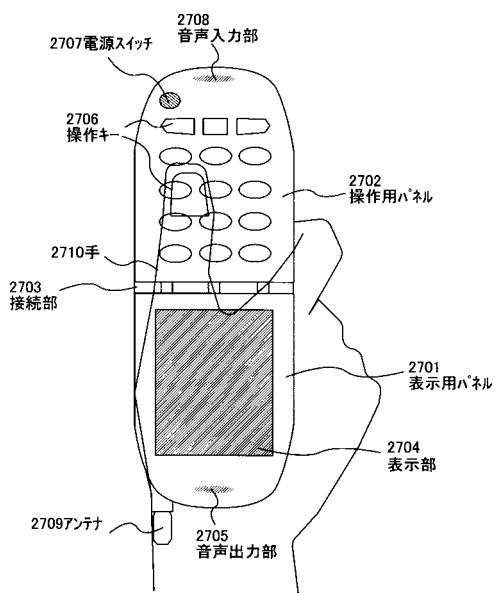

本実施例では、本発明の携帯情報端末の外観図について述べる。図31に示すのは本発明の構成を有する携帯情報端末であり、2701は表示用パネル、2702は操作用パネルである。表示用パネル2701と操作用パネル2702とは接続部2703において接続されている。そして接続部2703における、表示用パネル2701の表示部2704が設けられている面と操作用パネル2702の操作キー2706が設けられている面との角度は、任意に変えることができる。

**【0216】**

表示用パネル2701は表示部2704を有している。また図31に示した携帯情報端末は電話としての機能を有しており、表示用パネル2701は音声出力部2705を有しており、音声が音声出力部2705から出力される。表示部2704には本発明の液晶表示装置が用いられている。

20

**【0217】**

表示部2704のアスペクト比は16:9、4:3など任意に選択することができる。表示部2704のサイズは対角1インチ~4.5インチ程度が望ましい。

**【0218】**

操作用パネル2702は操作キー2706、電源スイッチ2707、音声入力部2708を有している。なお図31では操作キー2706と電源スイッチ2707とを別個に設けたが、操作キー2706の中に電源スイッチ2707が含まれる構成にしても良い。音声入力部2708において、音声が入力される。

30

**【0219】**

なお図31では表示用パネル2701が音声出力部2705を有し、操作用パネル2702が音声入力部2708を有しているが、本実施例はこの構成に限定されない。表示用パネル2701が音声入力部2708を有し、操作用パネル2702が音声出力部2705を有していても良い。また音声出力部2705と音声入力部2708とが共に表示用パネル2701に設けられていても良いし、音声出力部2705と音声入力部2708とが共に操作用パネル2702に設けられていても良い。

**【0220】**

なお図32では図31で示した携帯情報端末の操作キー2706を人差し指で操作している例について示した。また図33では図31で示した携帯情報端末の操作キー2706を親指で操作している例について示した。なお操作キー2706は操作用パネル2702の側面に設けても良い。操作は片手(きき手)の人差し指のみ、または親指のみでも可能である。

40

**【実施例16】**

**【0221】**

本実施例では、本発明の携帯情報装置を応用した電子機器について、図28及び図29を用いて説明する。

**【0222】**

本発明の携帯情報装置としてパソコンがある。図28(A)はパソナ

50

ルコンピュータであり、本体 2801、画像入力部 2802、表示部 2803、キーボード 2804 等を含む。表示部 2803 として、画素毎に記憶回路を有する液晶表示装置を用いることで、パーソナルコンピュータの低消費電力化を実現できる。

#### 【0223】

本発明の携帯情報装置としてナビゲーション装置がある。図 28 (B) はナビゲーション装置であり、本体 2811、表示部 2812、スピーカ部 2813、記憶媒体 2814、操作スイッチ 2815 等を含む。表示部 2812 として、画素毎に記憶回路を有する液晶表示装置を用いることで、ナビゲーション装置の低消費電力化を実現できる。

#### 【0224】

本発明の携帯情報装置として電子書籍がある。図 28 (C) は電子書籍であり、本体 2851、表示部 2852、記憶媒体 2853、操作スイッチ 2854、アンテナ 2855 等を含み、ミニディスク (MD) や DVD (Digital Versatile Disc) に記憶されたデータや、アンテナで受信したデータを表示するものである。表示部 2852 として、画素毎に記憶回路を有する液晶表示装置を用いることで、電子書籍の低消費電力化を実現できる。

10

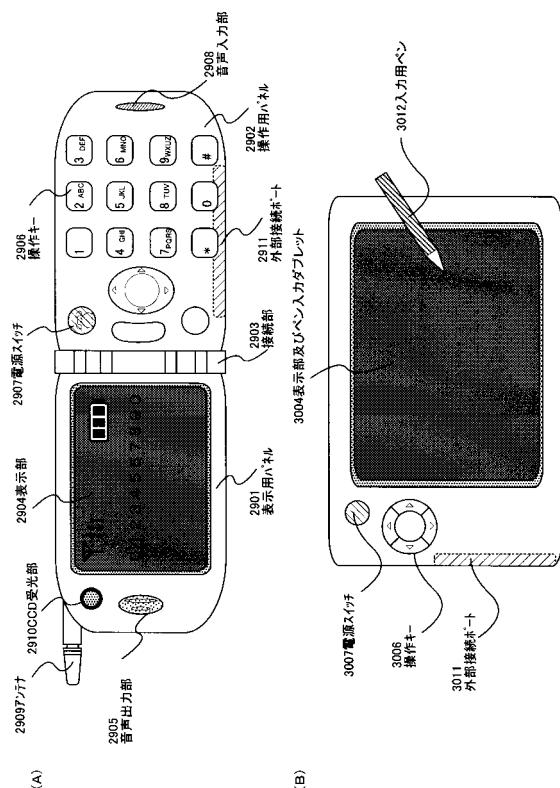

#### 【0225】

本発明の携帯情報装置として携帯電話がある。図 29 (A) は携帯電話であり、表示用パネル 2901、操作用パネル 2902、接続部 2903、表示部 2904、音声出力部 2905、操作キー 2906、電源スイッチ 2907、音声入力部 2908、アンテナ 2909、CCD 受光部 2910、外部入力ポート 2911 等を含む。表示部 2904 として、画素毎に記憶回路を有する液晶表示装置を用いることで、携帯電話の低消費電力化を実現できる。

20

#### 【0226】

本発明の携帯情報装置として PDA がある。図 29 (B) は PDA であり、表示部及びペン入力ダブル렛 3004、操作キー 3006、電源スイッチ 3007、外部入力ポート 3011、入力用ペン 3012 等を含む。表示部 3004 として、画素毎に記憶回路を有する液晶表示装置を用いることで、PDA の低消費電力化を実現できる。

#### 【実施例 17】

#### 【0227】

本実施例では、図 20 に示した構成と同様の構成の画素を有する液晶表示装置において、各画素の有する記憶回路に保持され D/A コンバータに入力されている信号を、対応するアナログ信号に変換する操作を、DAC コントローラ (図示せず) を用いて制御する場合について図 37 を用いて説明する。

30

#### 【0228】

なお、本実施例において、各画素の有する記憶回路に保持され D/A コンバータに入力されている信号を、対応するアナログ信号に変換し、D/A コンバータから出力する操作を、記憶回路の読み出し操作と呼ぶことにする。

#### 【0229】

図 37において、画素は、書き込み用 TFT108～110 と、記憶回路 105～107 と、ソース信号線 101 と、書き込み用ゲート信号線 102～104 と、D/A コンバータ 400 と、液晶素子 LC と、保持容量 Cs とを有する。

40

#### 【0230】

書き込み用 TFT108～110 のソース領域もしくはドレイン領域の一方は、ソース信号線 101 に接続され、もう一方はそれぞれ、記憶回路 105～107 の入力にそれぞれ接続されている。書き込み用 TFT108～110 のゲート電極はそれぞれ、書き込み用ゲート信号線 102～104 にそれぞれ接続されている。記憶回路 105～107 の出力は、D/A コンバータ 400 の入力 in1～in3 にそれぞれ接続されている。D/A コンバータ 400 の出力 out は、液晶素子 LC 及び保持容量 Cs の一方の電極に接続されている。

#### 【0231】

50

D / A コンバータ 400 は、NAND 回路 441 ~ 443、インバータ 444 ~ 446 及び 461、スイッチ 447a ~ 449a、スイッチ 447b ~ 449b、スイッチ 460、コンデンサ C1 ~ C3、リセット用信号線 452、低圧側階調電源線 453、高圧側階調電源線 454、中間圧側階調電源線 455 によって構成されている。

#### 【0232】

記憶回路 105 ~ 107 にデジタル信号を記憶するまでの動作については、実施の形態や実施例 1 で示した動作と同様であるので、説明は省略する。

#### 【0233】

以下、D / A コンバータ 400 の動作について説明する。

#### 【0234】

リセット用信号線 452 に入力された信号 res によって、スイッチ 460 が導通状態になり、容量 C1 ~ C3 の、out 端子に接続された側の電位は、中間圧側階調電源線 455 の電位  $V_M$  に固定されている。また、高圧側階調電源線 454 の電位は、低圧側階調電源線 453 の電位  $V_L$  と等しく設定されている。このとき、in1 ~ in3 にデジタル信号が入力されても、容量 C1 ~ C3 には、信号は書き込まれない。

10

#### 【0235】

この後、リセット用信号線 452 の信号 res が変化し、スイッチ 460 がオフとなつて、容量 C1 ~ C3 の out 端子側の電位の固定が解除される。次に、高圧側階調電源線 454 の電位が、低圧側階調電源線 453 の電位  $V_L$  と異なる値  $V_H$  に変化する。この時端子 in1 ~ in3 に入力された信号に応じて、NAND 回路 441 ~ 443 の出力が変化し、スイッチ 447 ~ 449 のそれぞれにおいて、2つのスイッチのどちらかがオンの状態となって、高圧側階調電源線の電位  $V_H$  もしくは低圧側階調電源線  $V_L$  の電位が、容量 C1 ~ C3 の電極に印加される。

20

#### 【0236】

ここで、この容量 C1 ~ C3 の値は、各ビットに対応して設定されている。例えば、C1 : C2 : C3 が 1 : 2 : 4 となるように設定されている。

#### 【0237】

この容量 C1 ~ C3 に印加された電圧によって容量 C1 ~ C3 の out 端子側の電位が変化し、出力の電位が変化する。つまり、入力された in1 ~ in3 のデジタル信号に応じたアナログの信号が out 端子より出力される。

30

#### 【0238】

リセット用信号線 452 に入力された信号 res 及び、高圧側階調電源線 454 の電位等を、DAC コントローラによって制御することによって、入力されたデジタル信号に対するアナログ信号の、D / A コンバータ 400 からの出力を制御することができる。

#### 【0239】

一旦画素の有する記憶回路にデジタル信号を書き込んだ後は、DAC コントローラを用いて上記動作を繰り返し、記憶回路に保持されたデジタル信号の読み出し操作を反復することによって、静止画を表示することができる。

#### 【0240】

このとき、ソース信号線駆動回路及びゲート信号線駆動回路の動作を停止することができる。

40

#### 【0241】

なお、図 37 では、3 個の記憶回路を配置した構成の画素を例に説明したが、これに限定されない。一般に、各画素に n (n は、2 以上の自然数) 個の記憶回路を配置した構成の画素を有する液晶表示装置に応用することができる。

#### 【0242】

DAC コントローラは、公知の構成の回路を自由に用いることができる。

#### 【実施例 18】

#### 【0243】

本実施例では、本発明の画素の構成の例について図 36 を用いて説明する。

50

**【0244】**

図36において、図1と同じ部分は同じ符号を用いて示し、説明は省略する。

**【0245】**

図36において、記憶回路105～107の出力はそれぞれ、読み出し用TFT121～123を介して、D/A111に入力されている。ここで、読み出し用TFT121～123のゲート電極は、読み出し用ゲート信号線124に接続されている。

**【0246】**

図36の構成の画素において、各記憶回路105～107に信号を書き込む動作は、実施形態及び実施例と同じであるので、ここでは説明は省略する。

**【0247】**

静止画を表示する際、一旦記憶回路105～107にデジタル信号を記憶した後は、読み出し用ゲート信号線124に信号を入力することによって、読み出し用TFT121～123をオンにし、記憶回路105～107に保持されたデジタル信号をD/A111に入力する。ここで本実施例のように各画素が読み出し用TFTを有する場合、記憶回路105～107に保持されたデジタル信号をD/A111に入力することを、記憶回路の信号の読み出し操作と呼ぶことにする。

**【0248】**

読み出し用TFT121～123のオン・オフを切り換え、読み出し操作を、反復することによって、静止画を表示することができる。

**【0249】**

ここで、読み出し操作は、読み出し用ゲート信号線を選択して行われるが、この読み出し用ゲート信号線124は、読み出し用ゲート信号線駆動回路を用いて駆動することができる。

**【0250】**

この読み出し用ゲート信号線駆動回路は、公知のゲート信号線駆動回路等を自由に用いることができる。

**【0251】**

なお、図36では、3個の記憶回路を配置した構成の画素を例に説明したが、これに限定されない。一般に、各画素にn(nは、2以上の自然数)個の記憶回路を配置した構成の画素を有する液晶表示装置に応用することができる。

**【実施例19】****【0252】**

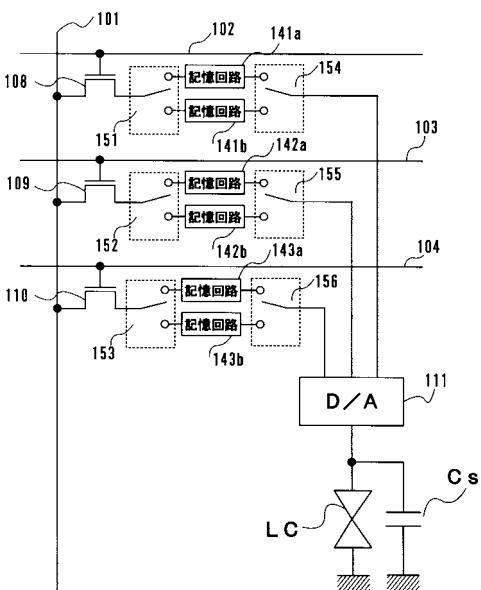

本実施例では、本発明の液晶表示装置の画素の構成を図38に示す。

**【0253】**

図38において、図1と同じ部分は同じ符号を用いて示し、説明は省略する。

**【0254】**

記憶回路141a～143aと、記憶回路141b～143bが各画素に配置されている。

**【0255】**

選択スイッチ151は、書き込み用TFT108と記憶回路141aまたは記憶回路141bとの接続を選択する。選択スイッチ152は、書き込み用TFT109と記憶回路142aまたは記憶回路142bとの接続を選択する。選択スイッチ153は、書き込み用TFT110と記憶回路143aまたは記憶回路143bとの接続を選択する。

**【0256】**

選択スイッチ154は、D/A111と記憶回路141aまたは記憶回路141bとの接続を選択する。選択スイッチ155は、D/A111と記憶回路142aまたは記憶回路142bとの接続を選択する。選択スイッチ156は、D/A111と記憶回路143aまたは記憶回路143bとの接続を選択する。

**【0257】**

選択スイッチ151～153及び選択スイッチ154～156によって、記憶回路14

10

20

30

40

50

1 a ~ 1 4 3 a にデジタル信号を記憶する場合と、記憶回路 1 4 1 b ~ 1 4 3 b にデジタル信号を記憶する場合とを選択することができる。また、記憶回路 1 4 1 a ~ 1 4 3 a からデジタル信号を D / A 1 1 1 に入力する場合と、記憶回路 1 4 1 b ~ 1 4 3 b からデジタル信号を D / A 1 1 1 に入力する場合とを選択することができる。

#### 【0258】

各画素において、選択された各記憶回路にデジタル信号を入力する動作、及び選択された各記憶回路に保持されたデジタル信号を読み出す動作については、実施の形態や実施例 1 と同様であるので説明は省略する。

#### 【0259】

画素は、記憶回路 1 4 1 a ~ 1 4 3 a を用いて、1 フレーム期間分の 3 ビットのデジタル信号を記憶し、記憶回路 1 4 1 b ~ 1 4 3 b を用いて、前記フレーム期間とは別のフレーム期間の 3 ビット分の信号を記憶することができる。10

#### 【0260】

図 38 においては、3 ビット分のデジタル信号を 2 フレーム分記憶する回路を示すが、本実施例はこれに限定されない。一般に、n ( n は、2 以上の自然数 ) ビット分のデジタル信号を m ( m は、2 以上の自然数 ) フレーム分記憶可能な画素を有する液晶表示装置に応用することができる。

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 3 】

【図12】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

(A)

【図20】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 3 1 B |

| G 0 9 G | 3/20  | 6 2 1 M |

| G 0 9 G | 3/20  | 6 6 0 U |

| G 0 9 G | 3/20  | 6 2 3 D |

| G 0 9 G | 3/20  | 6 2 1 A |

| G 0 9 G | 3/20  | 6 1 1 A |

| G 0 2 F | 1/133 | 5 0 5   |

| G 0 2 F | 1/133 | 5 5 0   |

(56)参考文献 特開2007-249215(JP,A)

特開平10-253941(JP,A)

特開平08-286170(JP,A)

特開平06-118908(JP,A)

(58)調査した分野(Int.Cl., DB名)

|         |           |   |         |

|---------|-----------|---|---------|

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8 |

| G 0 2 F | 1 / 1 3 3 |   |         |

|                |                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP5509281B2</a>                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2014-06-04 |

| 申请号            | JP2012194858                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2012-09-05 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 山崎舜平<br>小山潤                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 山崎 舜平<br>小山 潤                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 G09G3/32                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G3/3266 G09G3/3275 G09G3/3648 G09G2300/0426 G09G2300/0809 G09G2300/0828 G09G2300/0857 G09G2300/0861 G09G2310/04 G09G2320/0242 G09G2320/103 G09G2330/021 G09G2330/022                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/36 G09G3/20.624.B G09G3/20.623.G G09G3/20.623.F G09G3/20.623.R G09G3/20.631.B G09G3/20.621.M G09G3/20.660.U G09G3/20.623.D G09G3/20.621.A G09G3/20.611.A G02F1/133.505 G02F1/133.550 G09G3/20.680.A G09G3/20.680.G                                                                                                                             |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZA07 2H193/ZA19 2H193/ZE09 2H193/ZF23 2H193/ZF32 2H193/ZF33 2H193/ZF36 5C006/AF04 5C006/AF05 5C006/AF71 5C006/AF82 5C006/BB16 5C006/BC02 5C006/BC06 5C006/BC12 5C006/BC16 5C006/BC20 5C006/BF02 5C006/BF03 5C006/BF04 5C006/EC02 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD26 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 |         |            |

| 优先权            | 2000249090 2000-08-18 JP<br>2000253196 2000-08-23 JP                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | JP2013011901A                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

要解决的问题：提供一种能够在显示静止图像时降低功耗的液晶显示装置和液晶显示装置。一个目的是提供一种带信息装置。一种液晶显示器，用于通过输入n位的数字信号来显示图像（n是自然数）。在该器件中，每个像素内置n个存储器电路。它们存储在n个存储电路中。通过为每个像素形成的D/A转换器将n位数字信号转换成相应的模拟信号。转换成对数信号，并输入到液晶元件。因此，在显示静止图像时，在存储器路上写入数字信号后，迭代使用存储的数字信号。此时，可以停止源信号线驱动电路等的驱动。这样，降低设备的功耗。点域1