(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2020-46598

(P2020-46598A)

(43) 公開日 令和2年3月26日(2020.3.26)

|                             |           |                                      |

|-----------------------------|-----------|--------------------------------------|

| (51) Int.Cl.                | F 1       | テーマコード (参考)                          |

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36 | 2 H 1 9 3                            |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20 | 6 4 1 P                              |

| <b>G02F 1/133 (2006.01)</b> | G09G 3/20 | 6 1 2 U                              |

| <b>H04N 5/66 (2006.01)</b>  | G09G 3/20 | 6 6 0 E                              |

|                             | G09G 3/20 | 6 4 1 E                              |

|                             |           | 審査請求 未請求 請求項の数 7 O L (全 24 頁) 最終頁に続く |

|           |                              |          |                                                        |

|-----------|------------------------------|----------|--------------------------------------------------------|

| (21) 出願番号 | 特願2018-176695 (P2018-176695) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号             |

| (22) 出願日  | 平成30年9月21日 (2018.9.21)       | (74) 代理人 | 100126240<br>弁理士 阿部 琢磨                                 |

|           |                              | (74) 代理人 | 100124442<br>弁理士 黒岩 創吾                                 |

|           |                              | (72) 発明者 | 山岸 正治<br>東京都大田区下丸子3丁目4番2号 キヤ<br>ノン株式会社内                |

|           |                              |          | F ターム (参考) 2H193 ZA04 ZD25 ZE04 ZF12 ZQ06<br>ZQ11 ZR04 |

最終頁に続く

## (54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】ディスクリネーションによる画質低下を抑制し、画素シフトによる高解像度化を実現することができる。

【解決手段】液晶表示装置であって、液晶素子の各画素に対して、階調変換処理を適用した後の画像の階調値に基づいて所定のON電圧／OFF電圧の印加時間を制御することで、画素毎に光源の光の透過もしくは反射率を変化させる駆動手段と入力画像から複数の画素シフト用画像を生成し時分割で出力する画素シフト画像生成手段と、変調された光を所定の方向にシフトして表示可能な画素シフト手段と、時間的に連続するフレーム画像データに対して異なるゲイン係数を乗じる階調変換処理をそれぞれ適用する階調変換手段と、画素シフト用画像から空間周波数を算出する空間周波数算出手段と、を有し、階調変換手段は、空間周波数算出手段で算出された空間周波数に基づいて、階調変換処理で乗じるゲイン係数の差分を制御することを特徴とする。

【選択図】図1 2

**【特許請求の範囲】****【請求項 1】**

複数の画素を有する液晶素子を用いた液晶表示装置であって、

前記液晶素子の各画素に対して、階調変換処理を適用した後の画像の階調値に基づいて所定のON電圧/OFF電圧の印加時間を制御することで、画素毎に光源の光の透過もしくは反射率を変化させる駆動手段と、

入力画像から複数の画素シフト用画像を生成し時分割で出力する画素シフト画像生成手段と、

前記液晶素子によって変調された光を所定の方向にシフトして表示可能な画素シフト手段と、

時間的に連続するフレーム画像データに対して異なるゲイン係数を乗じる階調変換処理をそれぞれ適用する階調変換手段と、

前記画素シフト用画像から空間周波数を算出する空間周波数算出手段と、

を有し、

前記階調変換手段は、空間周波数算出手段で算出された空間周波数に基づいて、階調変換処理で乗じるゲイン係数の差分を制御することを特徴とする液晶表示装置。

**【請求項 2】**

前記階調変換手段は、乗じるゲイン係数の差分が、前記空間周波数算出手段の算出結果が高い場合には、前記空間周波数算出手段の算出結果が低い場合の時と比較して、小さくなるようなゲイン係数を適用することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記空間周波数算出手段は、入力画像の隣接画素差分値から算出することを特徴とする請求項1又は2に記載の液晶表示装置。

**【請求項 4】**

前記空間周波数算出手段は、入力画像を周波数領域への変換するフーリエ変換法を用いて算出することを特徴とする請求項1又は2に記載の液晶表示装置。

**【請求項 5】**

前記階調変換手段は、入力画像の解像度情報と、入力画像の空間周波数に基づいて、乗じるゲイン係数を決定することを特徴とする請求項1乃至4の何れか一項に記載の液晶表示装置。

**【請求項 6】**

前記階調変換手段は、入力画像の解像度が高いほど、乗じるゲイン係数の差分が小さくなるようなゲイン係数を適用することを特徴とする請求項5に記載の液晶表示装置。

**【請求項 7】**

複数の画素を有する液晶素子を用いた液晶表示装置であって、

前記液晶素子の各画素に対して、階調変換処理を適用した後の画像の階調値に基づいて所定のON電圧/OFF電圧の印加時間を制御することで、画素毎に光源の光の透過もしくは反射率を変化させる駆動手段と、

入力画像から複数の画素シフト用画像を生成し時分割で出力する画素シフト画像生成手段と、

前記液晶素子によって変調された光を所定の方向にシフトして表示可能な画素シフト手段と、

時間的に連続するフレーム画像データに対して異なるゲイン係数を乗じる階調変換処理をそれぞれ適用する階調変換手段と、

前記入力画像の空間周波数を算出する空間周波数算出手段と、

を有し、

前記階調変換手段は、空間周波数算出手段で算出された空間周波数に基づいて、階調変換処理で乗じるゲイン係数の差分を制御することを特徴とする液晶表示装置。

**【発明の詳細な説明】****【技術分野】**

10

20

30

40

50

**【0001】**

本発明は、デジタル駆動方式で駆動される液晶素子を使用した液晶表示装置に関する。

**【背景技術】****【0002】**

液晶素子には、TN (Twisted Nematic) 素子等の透過型液晶素子や、VAN (Vertical Alignment Nematic) 素子等の反射型液晶素子がある。これらの液晶素子の駆動方式には、階調に応じて、液晶層に印加する電圧を変化させることで明るさを制御するアナログ駆動方式と、液晶層に印加する電圧を2値化して電圧印加時間を変化させることで明るさを制御するデジタル駆動方式とがある。このデジタル駆動方式には、1フレーム期間を時間軸上で複数のサブフィールド期間に分割し、サブフィールドごとに画素に対する所定電圧の印加(オン)と非印加(オフ)を制御することで該画素に階調を表示させるサブフィールド駆動方式がある。隣接画素にてオン期間とオフ期間が時間的に重なる、つまり同じ期間で隣接画素の一方では所定電圧が印加され、他方では印加されていない状態が発生すると、いわゆるディスクリネーションが発生してオン期間側の画素の明るさが低下する。

10

**【0003】**

特許文献1には、ディスクリネーションによる画素の明るさの低下を視認されづらくするために、液晶素子の全画素にフレーム毎に周期的に変化する補正值を乗算することで、ディスクリネーションの発生する位置を周期的に変化させる方法が開示されている。

20

**【0004】**

特許文献2には、表示する画像の光路をシフトさせて表示することにより、高解像度化を実現する技術が開示されている。入力画像を基に、複数のフレーム画像を生成し、各フレーム画像の投影位置を1/2画素シフトして表示することで、表示素子が備える解像度以上の高解像度化を実現する。つまり、一つの入力画像から画素シフト位置に基づいて複数のフレーム画像を生成して、これらを画素位置に応じて順次表示することで解像感向上させている。

30

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2017-53945号公報

【特許文献2】特開2011-203460号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

しかしながら、特許文献1開示された方法と、特許文献2に開示された方法はともに、入力フレームから複数のサブフレームを生成する倍速処理が必要である。したがって、これら2つの方法を同時に実施する表示装置を構成する場合、最低でも4倍速処理が必要になるため、高帯域の画像処理が必要であったり、表示素子の高速駆動が必要であったりと、表示装置が高コストになってしまふという課題があった。

40

**【課題を解決するための手段】****【0007】**

上記の課題を解決するために、本発明に係る液晶表示装置は、複数の画素を有する液晶素子を用いた液晶表示装置であって、前記液晶素子の各画素に対して、階調変換処理を適用した後の画像の階調値に基づいて所定のON電圧/OFF電圧の印加時間を制御することで、画素毎に光源の光の透過もしくは反射率を変化させる駆動手段と入力画像から複数の画素シフト用画像を生成し時分割で出力する画素シフト画像生成手段と、前記液晶素子によって変調された光を所定の方向にシフトして表示可能な画素シフト手段と、時間的に連続するフレーム画像データに対して異なるゲイン係数を乗じる階調変換処理をそれぞれ適用する階調変換手段と、前記画素シフト用画像から空間周波数を算出する空間周波数算出手段と、を有し、前記階調変換手段は、空間周波数算出手段で

50

算出された空間周波数に基づいて、階調変換処理で乗じるゲイン係数の差分を制御することを特徴とする。

【発明の効果】

【0008】

本発明に係る液晶表示装置によれば、コストを抑えつつ、ディスクリネーションによる画質低下を抑制し、画素シフトによる高解像度化を実現することができる。

【図面の簡単な説明】

【0009】

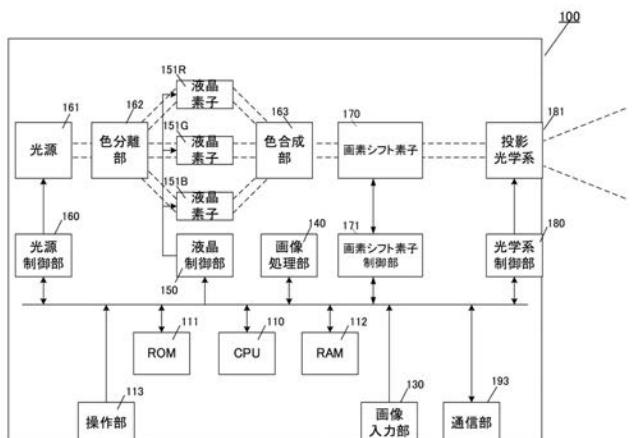

【図1】液晶プロジェクタ100の構成を示す図

10

【図2】実施例1の液晶プロジェクタに用いられる液晶素子151の断面図

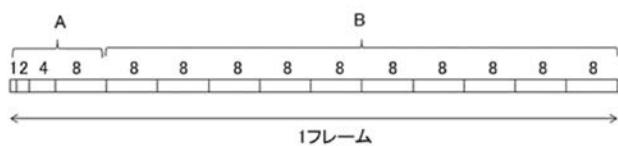

【図3】実施例1における1フレーム期間内の複数のサブフィールド期間を示す図

【図4】実施例1におけるAサブフィールド期間の階調データを示す図

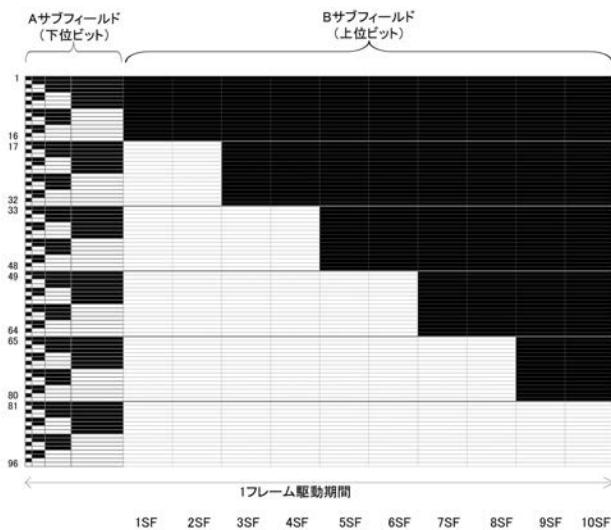

【図5】実施例1における全階調データを示す図

【図6】実施例1における画素ラインを示す図

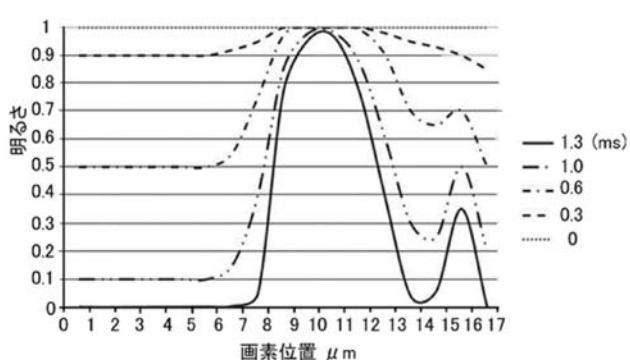

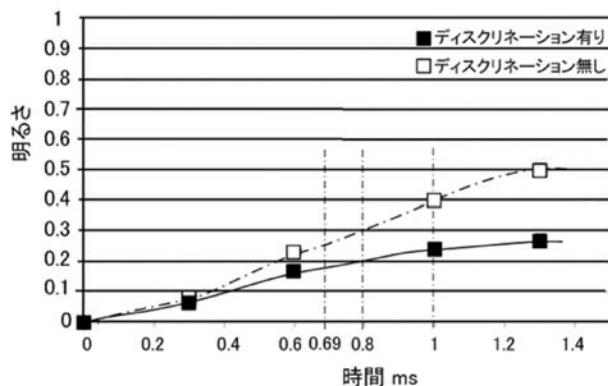

【図7】実施例1における全白表示から白黒表示に切り替えたときの液晶の応答特性を示す図

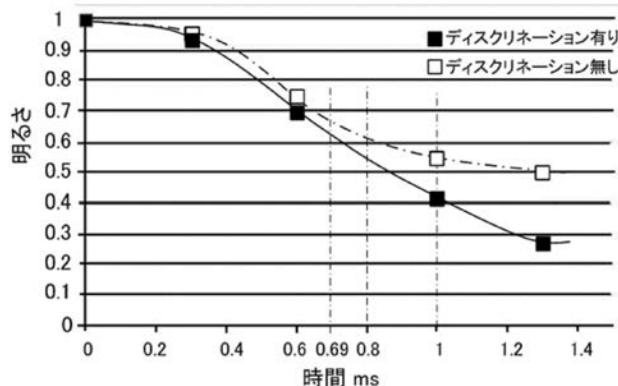

【図8】実施例1における全白表示から白黒表示に切り替えたときの明るさの応答特性を示す図

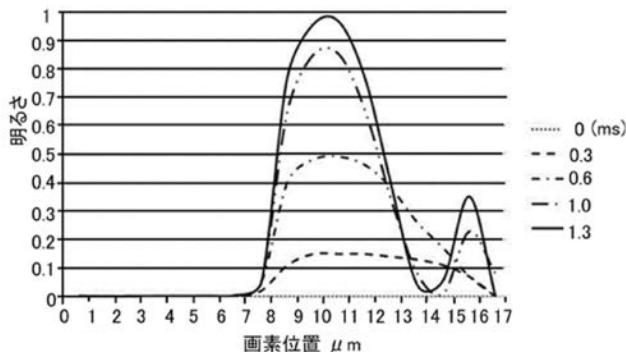

【図9】実施例1における全黒表示から白黒表示に切り替えたときの液晶の応答特性を示す図

20

【図10】実施例1の全面黒から白黒表示に切り替えたときの明るさの応答特性を表す図

【図11】従来例における全階調データを示す図

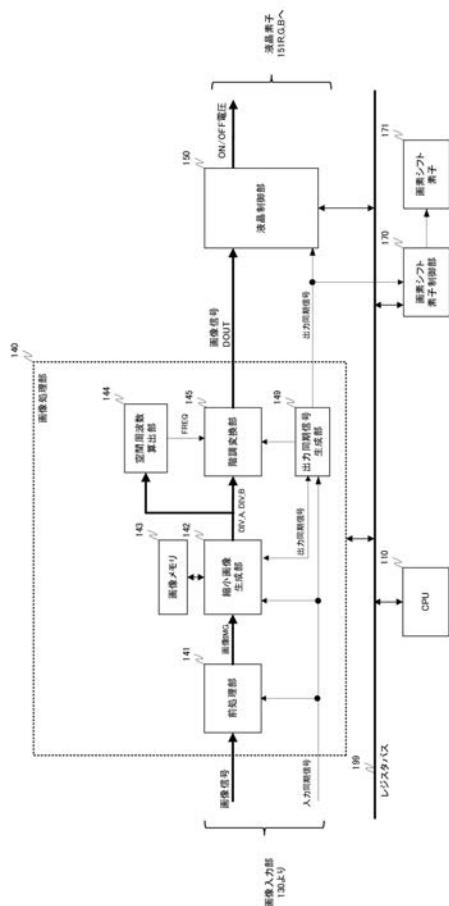

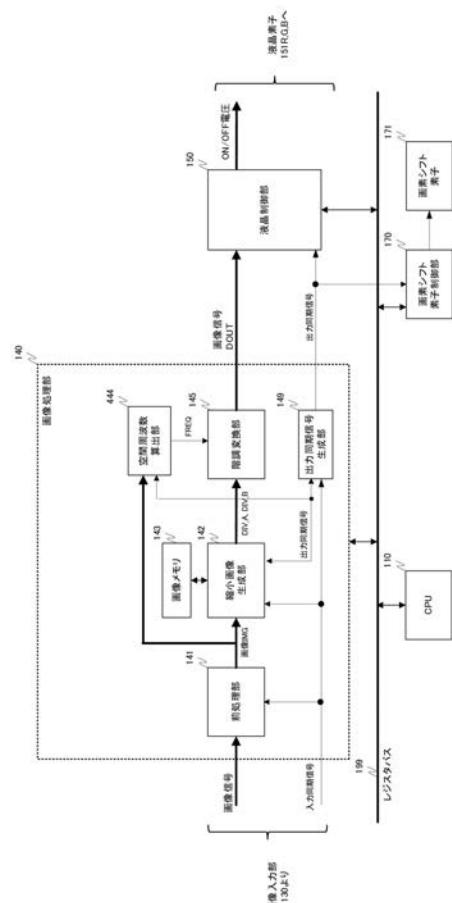

【図12】実施例1における画像処理部140の内部構成を示した図

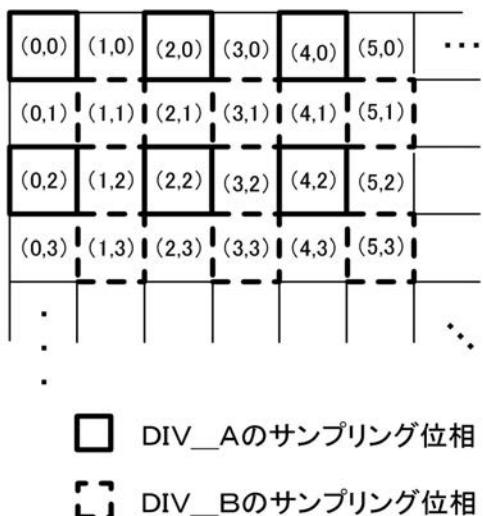

【図13】実施例1における入力画像に対するサンプリング位置の模式図

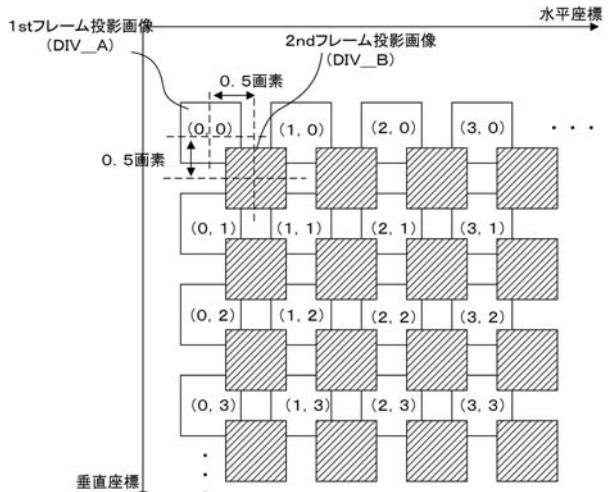

【図14】実施例1における画素シフトの投影位置を説明するための図

【図15】実施例1における検出対象画素位置における画素値の一例を示す図

【図16】実施例1における輝度差分値と空間周波数の変換特性の一例を示す図

【図17】実施例1における階調変換部145の内部構成を示した図

【図18】実施例1におけるフレーム1とフレーム2に適用する変換特性の一例を示す図

【図19】実施例1における階調変換部145が、フレーム1とフレーム2に適用するゲイン処理を示す図

30

【図20】実施例1における階調変換部145が、フレーム1とフレーム2に適用するゲイン処理を示す図

【図21】実施例1における空間周波数の違いによる階調特性の一例を示す図

【図22】階調変換部145が適用するゲインの差分の大きさと画素シフトしたときの高解像度化の効果の違いを説明する図

【図23】実施例2における画像処理部140の内部構成を示す図

【図24】実施例2における階調変換部345の内部構成を示す図

【図25】実施例2における入力解像度と補正係数の関係を示す図

【図26】実施例2における空間周波数と補正レベルの関係を示す図

40

【図27】実施例3における画像処理部140の内部構成を示した図

【発明を実施するための形態】

【0010】

以下、本発明を実施するための形態について、図面を参照しながら説明する。

【0011】

<実施例1>

本実施例における液晶プロジェクタ100は、画素シフト処理のON/OFFおよびゲイン係数を入力画像の解像度に応じて制御することにより、ディスクリネーションによる画質低下を抑制し、画素シフトによる高解像度化を実現することができる。加えて、従来例術の組合せでは4倍速処理が必要なのに対し、本実施例における液晶プロジェクタ10

50

0は、2倍速処理での構成で実現可能であるため、高帯域の画像処理や、表示素子の高速駆動が不要となり、コストを抑えることができる。以下、具体的な構成と方法について述べる。

#### 【0012】

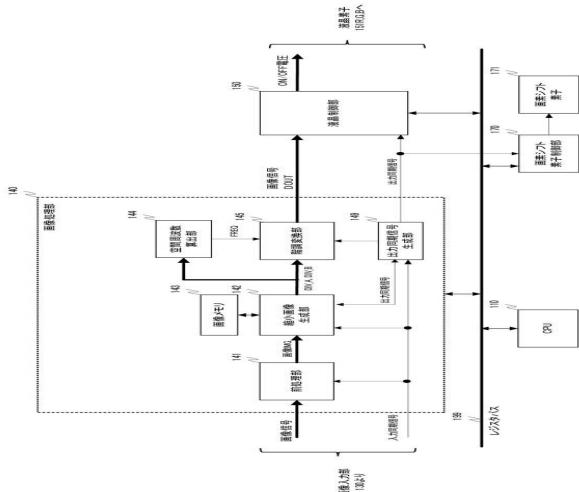

まず、図1を用いて、本実施例の液晶プロジェクタ100の全体構成を説明する。

#### 【0013】

本実施例の液晶プロジェクタ100は、CPU110、ROM111、RAM112、操作部113、画像入力部130、画像処理部140を有する。また、液晶プロジェクタ100は、さらに、液晶制御部150、液晶素子151R、151G、151B、光源制御部160、光源161、色分離部162、色合成部163、画素シフト素子170、画素シフト素子制御部171、光学系制御部180、投影光学系181を有する。

10

CPU110は、液晶プロジェクタ100の各動作ブロックを制御するものあり、ROM111は、CUP110の処理手順を記述した制御プログラムを記憶するためのものあり、RAM112は、ワークメモリとして一時的に制御プログラムやデータを格納するものである。

#### 【0014】

また、操作部113は、ユーザの指示を受け付け、CPU110に指示信号を送信するものであり、例えば、スイッチやボタン、ダイヤルなどからなる。また、操作部113は、例えば、リモコンからの信号を受信する信号受信部（赤外線受信部など）で、受信した信号に基づいて所定の指示信号をCPU110に送信するものであってもよい。また、CPU110は、操作部113や、通信部193から入力された制御信号を受信して、液晶プロジェクタ100の各動作ブロックを制御する。

20

#### 【0015】

画像処理部140は、映像入力部130から受信した映像信号にフレーム数、画素数、画像形状などの変更処理を施して、液晶制御部150に送信するものであり、例えば画像処理用のマイクロプロセッサからなる。また、画像処理部140は、専用のマイクロプロセッサである必要はなく、例えば、ROM111に記憶されたプログラムによって、CPU110が画像処理部140と同様の処理を実行しても良い。画像処理部140は、フレーム間引き処理、フレーム補間処理、解像度変換（スケーリング）処理、歪み補正処理（キーストン補正処理）といった機能を実行することが可能である。また、画像処理部140は、映像入力部130から受信した映像信号以外にも、CPU110によって再生された画像や映像に対して前述の変更処理を施すこともできる。なお、画像処理部240が行う画像処理の詳細については、後述する。

30

#### 【0016】

液晶制御部150は、画像処理部140で処理の施された映像信号に基づいて、液晶素子151R、151G、151Bの画素の液晶に印可する電圧を制御して、液晶素子151R、151G、151Bの反射率若しくは透過率を調整する。

#### 【0017】

液晶素子151Rは、赤色に対応する液晶素子であって、光源161から出力された光のうち、色分離部162で赤色（R）、緑色（G）、青色（B）に分離された光のうち、赤色の光の透過率を調整するためのものである。液晶素子151Gは、緑色に対応する液晶素子であって、光源161から出力された光のうち、色分離部162で赤色（R）、緑色（G）、青色（B）に分離された光のうち、緑色の光の透過率を調整するためのものである。液晶素子151Bは、青色に対応する液晶素子であって、光源161から出力された光のうち、色分離部162で赤色（R）、緑色（G）、青色（B）に分離された光のうち、青色の光の透過率を調整するためのものである。

40

#### 【0018】

光源制御部160は、光源161のオン／オフを制御や明るさの制御をするものあり、制御用のマイクロプロセッサからなる。また、光源制御部160は、専用のマイクロプロセッサである必要はなく、例えば、ROM111に記憶されたプログラムによって、C

50

P U 1 1 0 が光源制御部 1 6 0 と同様の処理を実行しても良い。また、光源 1 6 1 は、不図示のスクリーンに画像を投影するための光を出力するものであり、例えば、レーザー、L E D、ハロゲンランプ、キセノンランプ、高圧水銀ランプなどであっても良い。また、色分離部 1 6 2 は、光源 1 6 1 から出力された光を、赤色 ( R )、緑色 ( G )、青色 ( B ) に分離するものであり、例えば、ダイクロイックミラーやプリズムなどからなる。なお、光源 1 6 1 として、各色に対応するレーザーや、L E D 等を使用する場合には、色分離部 1 6 2 は不要である。また、色合成部 1 6 3 は、液晶素子 1 5 1 R、1 5 1 G、1 5 1 B を透過した赤色 ( R )、緑色 ( G )、青色 ( B ) の光を合成するものであり、例えば、ダイクロイックミラーやプリズムなどからなる。そして、色合成部 1 6 3 により赤色 ( R )、緑色 ( G )、青色 ( B ) の成分を合成した光は、画素シフト素子 1 7 0 に送られる。このとき、液晶素子 1 5 1 R、1 5 1 G、1 5 1 B は、画像処理部 1 4 0 から入力された画像に対応する光の透過率となるように、液晶制御部 1 5 0 により制御されている。そのため、色合成部 1 6 3 により合成された光は、投影光学系 1 8 1 によりスクリーンに投影されると、画像処理部 1 4 0 により入力された画像に対応する画像がスクリーン上に表示されることになる。

10

## 【 0 0 1 9 】

画素シフト素子制御部 1 7 1 は、液晶制御部 1 5 0 が液晶素子 1 5 1 を駆動するタイミングに同期して、画素シフト素子 1 7 0 に印加する電圧または電流を変化させることで、画素シフト素子 1 7 0 を制御し、色合成部 1 6 3 からの合成光の光路をシフトさせる。なお、画素シフト素子 1 7 0 は、色合成部 1 6 3 からの合成光の光路をシフトさせることができる構成であれば手段を限定しないが、例えば、透過性の光学部材から成る平行平板を用いてもよいし、液晶と複屈折材料を貼り合わせた素子を用いてもよい。

20

## 【 0 0 2 0 】

また、1 s t フレームと 2 n d フレームで液晶素子 2 7 0 に表示される画像の生成方法については、後述する。

## 【 0 0 2 1 】

光学系制御部 1 8 0 は、投影光学系 1 8 1 を制御するものであり、制御用のマイクロプロセッサからなる。また、光学系制御部 1 8 0 は、専用のマイクロプロセッサである必要はなく、例えば、R O M 1 1 1 に記憶されたプログラムによって、C P U 1 1 0 が光学系制御部 1 8 0 と同様の処理を実行しても良い。また、投影光学系 1 8 1 は、画素シフト素子 1 7 0 から出力された合成光をスクリーンに投影するためのものであり、複数のレンズ、レンズ駆動用のアクチュエータからなり、レンズをアクチュエータにより駆動することで、投影画像の拡大、縮小、焦点調整などを行うことができる。

30

## 【 0 0 2 2 】

通信部 1 9 3 は、外部機器からの制御信号や静止画データ、動画データなどを受信するためのものであり、例えば、無線L A N、有線L A N、U S B、B l u e t o o t h ( 登録商標 ) などであってよく、通信方式を特に限定するものではない。また、画像入力部 1 3 0 の端子が、例えばH D M I ( 登録商標 ) 端子であれば、その端子を介してC E C 通信を行うものであっても良い。ここで、外部装置は、液晶プロジェクタ 1 0 0 と通信を行うことができるものであれば、パソコンコンピュータ、カメラ、携帯電話、スマートフォン、ハードディスクレコーダ、ゲーム機、リモコンなど、どのようなものであってもよい。

40

## 【 0 0 2 3 】

なお、本実施例の画像処理部 1 4 0 、液晶制御部 1 5 0 、光源制御部 1 6 0 、画素シフト制御部 1 7 1 、光学系制御部 1 8 0 、これらの各ブロックと同様の処理を行うことのできる単数または複数のマイクロプロセッサあっても良い。または、例えば、R O M 1 1 1 に記憶されたプログラムによって、C P U 1 1 0 が各ブロックと同様の処理を実行しても良い。

## 【 0 0 2 4 】

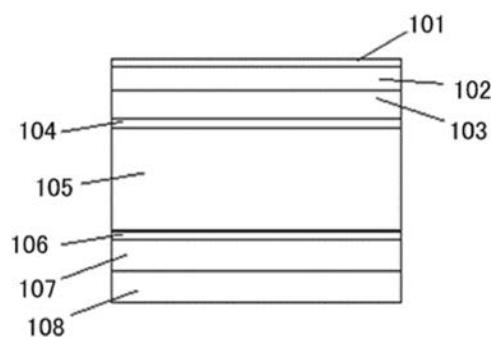

図 2 には、液晶素子 ( 1 5 1 R , 1 5 1 G , 1 5 1 B ) の断面構造を示している。本液

50

液晶素子(151R, 151G, 151B)は、反射型の構成であり、101はARコート膜、102はガラス基板、103は共通電極、104は配向膜、105は液晶層、106は配向膜、107は画素電極、108はSi基板である。なお、液晶素子(151R, 151G, 151B)は透過型の構成であってもよい。

#### 【0025】

図1に示す液晶制御部150は、上述したサブフィールド駆動方式で各画素を駆動する。すなわち、1フレーム期間を時間軸上で複数のサブフィールド期間に分割し、階調データに応じてサブフィールド期間ごとに画素に対する所定電圧のオン(印加)とオフ(非印加)を制御することで該画素に階調を形成(表示)させる。1フレーム期間は、液晶素子に1フレーム画像が表示される期間である。本実施例では液晶素子を120Hzで駆動するものとして、1フレーム期間を8.33msとする。所定電圧のオンとオフは、第1の電圧(所定電圧)の印加と該第1の電圧より低い第2の電圧の印加と言い換えることもできる。

10

#### 【0026】

以下、液晶制御部150におけるサブフィールド期間の設定と階調データについて説明する。液晶制御部150をコンピュータにより構成し、コンピュータプログラムとしての液晶駆動プログラムに従って以下のサブフィールド期間の設定とサブフィールド期間ごとの所定電圧のオン／オフを制御するようにしてもよい。

20

#### 【0027】

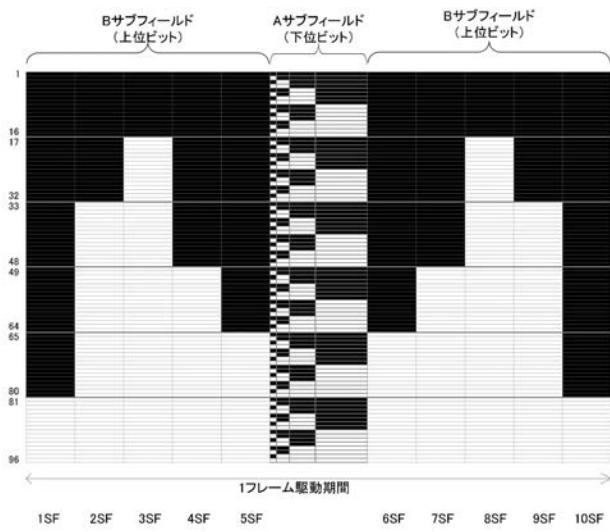

図3には、本実施例における1フレーム期間の複数のサブフィールド期間(ビット長)への分割を示している。各サブフィールド上に記載された数値は、そのサブフィールドの1フレーム期間内での時間重みを示す。本実施例では、96階調を表現する。また、ここでの説明では、時間重み $1 + 2 + 4 + 8$ の期間をAサブフィールド期間(第1の期間)といい、Aサブフィールド期間にてバイナリ表現された階調を示すビットを下位ビットという。また、時間重み8の10個のサブフィールド期間をまとめてBサブフィールド期間(第2期間)といい、Bサブフィールド期間にてバイナリ表現された階調を示すビットを上位ビットという。時間重み1は0.087msに相当し、時間重み8は0.69msに相当する。

20

#### 【0028】

さらに、上述した所定電圧をオン(第1の電圧を印加)するサブフィールド期間をオン期間といい、所定電圧をオフする(第2の電圧を印加する)サブフィールド期間をオフ期間という。

30

#### 【0029】

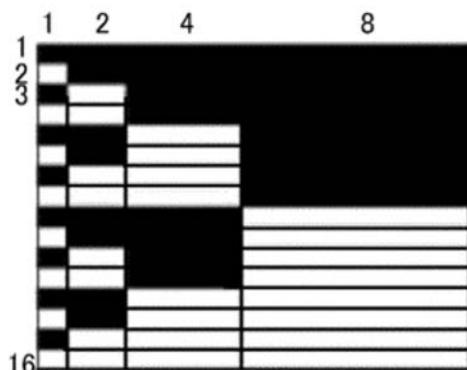

図4には、図3に示したAサブフィールド期間の階調データを示す。縦軸は階調を、横軸は1フレーム期間を示す。Aサブフィールド期間では、16階調を表現する。図中の白いサブフィールド期間は画素が白表示状態となるように上述した所定電圧が印加されたオン期間を示し、黒いサブフィールド期間は画素が黒表示状態となるように所定電圧がオフされたオフ期間を示す。

#### 【0030】

図5には、本実施例におけるAおよびBサブフィールド期間(下位および上位ビット)の階調データを示している。この階調データは、全階調として96階調を表現するための階調データである。この階調データにおいて、1フレーム期間の時間中心にはAサブフィールド期間(下位ビット)が配置され、その前後にBサブフィールド期間(上位ビット)が1SF～5SFと6SF～10SFとに分割されて配置されている。つまり、Bサブフィールド期間が2つに分割され、それぞれのBサブフィールド期間に2つ以上のサブフィールド期間が含まれる。

40

#### 【0031】

この階調データによれば、液晶素子における互いに隣接する2画素である隣接画素に互いに隣接する2階調である隣接階調、例えば48階調と49階調を表示させる場合には、Aサブフィールド期間を48階調ではオン期間、49階調ではオフ期間とする。また、4

50

8 階調では、B サブフィールド期間のうち 1 S F , 4 S F , 5 S F , 6 S F , 7 S F , 10 S F をオフ期間とし、2 S F , 3 S F , 8 S F , 9 S F をオン期間とする。一方、4 9 階調では、B サブフィールド期間のうち 1 S F , 5 S F , 6 S F , 10 S F をオフ期間とし、2 S F , 3 S F , 4 S F , 7 S F , 8 S F , 9 S F をオン期間とする。そして、このような隣接階調を隣接画素に表示される際には、隣接画素においてオン期間とオフ期間とが重なるオン／オフ隣接期間が生ずる。具体的には、隣接画素に 4 8 階調と 4 9 階調を表示させる場合には、B サブフィールド期間のうち 4 S F と 7 S F とがオン／オフ隣接期間となる。

#### 【0032】

ここで、本実施例の階調データを図 11 に示した従来（特許文献 1）の階調データと比較する。図 11 の階調データでは A サブフレーム期間の後に B サブフィールド期間が 1 まとまりで継続しているが、図 5 に示す本実施例の階調データでは A サブフレーム期間の前後に B サブフィールド期間が分割して配置されている。例えば 4 8 階調と 4 9 階調に注目すると、図 11 では B サブフィールド期間のうち 5 S F と 6 S F がオン／オフ隣接期間になってしまっており、時間重みとして 1 6 のオン／オフ隣接期間が継続している。このことは、他の隣接階調である 1 6 階調と 1 7 階調、3 2 階調と 3 3 階調、6 4 階調と 6 5 階調、8 0 階調と 8 1 階調等についても同じである。これに対して、図 5 に示す本実施例では、上記のいずれの隣接階調においても、B サブフィールド期間においてオン／オフ隣接期間が継続するのは時間重みとして 8 の 1 サブフィールド期間（= 0 . 6 9 m s）となっている。そして、この 1 サブフィールド期間であるオン／オフ隣接期間が A サブフレーム期間を挟んで互いに離れて複数（2 つ）存在する。

10

20

30

#### 【0033】

次に、本実施例のようにオン／オフ隣接期間が分散配置されることにより得られる効果について説明する。

#### 【0034】

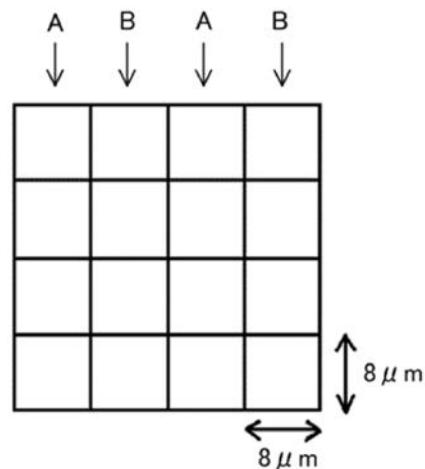

まず、図 6 に示すようにマトリックス状に配置された画素が、全白表示状態から 1 画素ラインごとに白と黒が交互に表示される白黒表示状態に切り替わるとときと、全黒表示状態から白黒表示状態に切り替わるときの液晶の応答特性について説明する。図 6 に示す 4 × 4 個の画素は、8 μm の画素ピッチでマトリックス状に配置されている。全白表示状態では図 6 中の A 画素ラインの画素および B 画素ラインの画素のいずれもが白を表示する。白黒表示状態では、A 画素ラインの画素が白表示状態から黒表示状態に切り替わり、B 画素ラインの画素が白表示状態のまま維持される。

30

#### 【0035】

図 7 には、液晶の応答特性を示している。横軸は画素の位置を、縦軸は各画素における明るさ（ただし、白を 1 としたときの比率）を示している。横軸の 0 ~ 8 μm は図 6 に示した A 画素ラインの画素を、8 μm ~ 16 μm は B 画素ラインの画素を示している。複数の曲線は、全白表示状態から白黒表示状態への切り替え時点を 0 m s としたときの経過時間（0 . 3 m s , 0 . 6 m s , 1 . 0 m s , 1 . 3 m s）ごとの明るさを示す。

40

#### 【0036】

上述したように A 画素ラインの画素が白表示状態から黒表示状態に切り替わるが、液晶におけるプレチルト角度の向きの関係から A 画素ラインの画素はディスクリネーションの影響を受けずに比較的均一に明るさが変化していく（暗くなっていく）。一方、B 画素ラインの画素では、全白表示状態ではディスクリネーションは発生していない。しかし、白黒表示状態になった後からディスクリネーションの影響を受けて時間の経過とともに徐々に明るさ曲線がいびつな形になり、特に 12 μm ~ 16 μm 付近で暗くなる（暗線が現れる）。

#### 【0037】

一般に、入力階調に対する液晶素子の駆動階調を決めるガンマ曲線（ガンマ特性）はディスクリネーションが発生しない液晶素子全面に同じ階調を表示させながらその階調を変化させた場合の応答特性を前提として作成される。このため、そのようなガンマ曲線を用

50

いて液晶素子を駆動すると、白黒表示状態にてディスクリネーションが発生し、そのガンマ曲線に応じた本来の明るさよりも低い明るさしか得ることができない。

#### 【0038】

図8には、液晶素子を全白表示状態から白黒表示状態に切り替えたときのディスクリネーションの有無による明るさの変化を示している。横軸は切り替え時点からの経過時間で、縦軸はAおよびB画素ラインの画素のトータルな明るさの積分値（以下、単に明るさという）の変化を示す。明るさは、全白表示状態を1としたときの比率で示している。ディスクリネーションが発生する（「ディスクリネーション有り」の）場合には、A画素ラインの画素の明るさは図7の1~6μm付近に示す応答特性に近い特性で変化し、B画素ラインの画素の明るさは全域100%の明るさで白が表示された状態となる。そして、この後の時間経過に伴い、ディスクリネーションが発生した場合の明るさの低下量はディスクリネーションが発生しない（「ディスクリネーション無し」の）場合の明るさの低下量に比べて大きくなっていく。

#### 【0039】

一方、全黒表示状態から白黒表示に切り替えるときには、図6に示したA画素ラインの画素およびB画素ラインの画素がともに黒表示状態から、A画素ラインの画素を黒表示状態としたままB画素ラインの画素を白表示状態とする。図9には、このときの液晶の応答特性を示している。横軸は画素の位置を、縦軸は各画素における明るさ（ただし、白を1としたときの比率）を示している。横軸の0~8μmは図6に示したA画素ラインの画素を、8μm~16μmはB画素ラインの画素を示している。複数の曲線は、全黒表示状態から白黒表示状態への切り替え時点を0msとしたときの経過時間（0.3ms, 0.6ms, 1.0ms, 1.3ms）ごとの明るさを示す。

#### 【0040】

上述したようにB画素ラインの画素が黒表示状態から白表示状態に切り替わるが、B画素ラインの画素では、白表示状態になった後からディスクリネーションの影響を受けて時間の経過とともに徐々に明るさ曲線がいびつな形になる。そして、特に12μm~16μm付近で暗くなる（暗線が現れる）。また、時間経過に伴って明るさ曲線のいびつな形が顕著になっていく。

#### 【0041】

先にも説明したように、一般に入力階調に対する液晶素子の駆動階調を決めるガンマ曲線（ガンマ特性）はディスクリネーションが発生しない液晶素子全面に同じ階調を表示させながらその階調を変化させた場合の応答特性を前提として作成される。このため、そのようなガンマ曲線を用いて液晶素子を駆動すると、白黒表示状態にてディスクリネーションが発生し、そのガンマ曲線に応じた本来の明るさよりも低い明るさしか得ることができない。

#### 【0042】

図10には、液晶素子を全黒表示状態から白黒表示状態に切り替えたときのディスクリネーションの有無による明るさの変化を示している。横軸は切り替え時点からの経過時間を、縦軸はAおよびB画素ラインの画素のトータルな明るさの積分値（以下、単に明るさいい、全白表示状態を1としたときの比率で示す）を示す。ディスクリネーションが発生しない（「ディスクリネーション無し」の）場合の明るさとしては、A画素ラインの画素は常に黒表示状態であり、B画素ラインの画素が黒表示状態から白表示状態に切り替わっていくときの明るさの変化を示している。一方、ディスクリネーションが発生する（「ディスクリネーション有り」の）場合は、図9に示したA画素ラインの画素とB画素ラインの画素の明るさの和の積分値の変化を示している。

#### 【0043】

図10において、ディスクリネーションが発生する場合は、ディスクリネーションが発生しない場合に比べて、時間経過に伴う明るさの増加量が少ない。すなわち、全黒表示状態から白黒表示状態に切り替わった後にディスクリネーションが発生する時間が長いほど、ディスクリネーションが発生しない場合に対してより暗くなる。

## 【0044】

次に、図11に示した従来の階調データによってA画素ラインの画素に48階調を表示させ、B画素ラインの画素に49階調を表示させる場合について説明する。この階調データを用いる場合にディスクリネーションが発生する期間は、A画素ラインの画素が黒表示状態でB画素ラインの画素が白表示状態というディスクリネーション発生表示状態となるBサブフィールド期間における5SFと6SFである。5SFの前の4SFはA画素ラインの画素およびB画素ライン画素のいずれも白表示状態であり、ディスクリネーションは発生しない期間である。

## 【0045】

5SFから6SFまでの液晶の応答特性は図8における「ディスクリネーション有り」に相当する特性となる。4SFでは全白表示状態であるため明るさは100%出力されており、5SFの開始時から6SFの終了時までの1.39msの間にディスクリネーションが発生するため、5SFの開始時が図8における0msに相当し、6SFの終了時が1.39msに相当する。このとき、明るさは、ディスクリネーションが発生しない場合の0.5に対して0.27まで低下する。前述したように全面同一階調を前提として作成されるガンマ特性を基準とすると、ディスクリネーションが発生する5SFから6SFまでに比率において54%( $=0.27/0.5$ )と暗くなる。

10

## 【0046】

一方、本実施例において、図5に示した階調データによってA画素ラインの画素(第2の画素)に48階調を表示させ、B画素ラインの画素(第1の画素)に49階調を表示させる場合について説明する。この階調データを用いる場合にディスクリネーションが発生する期間は、A画素ラインの画素とB画素ラインの画素が上記ディスクリネーション発生表示状態となるBサブフィールド期間における4SFと7SFである。4SFの前の3SFはA画素ラインの画素およびB画素ラインの画素がともに白表示状態であり、ディスクリネーションは発生しない期間である。

20

## 【0047】

4SFでの液晶の応答特性は、図8における「ディスクリネーション有り」に相当する特性となる。3SFでは全白表示状態であるため明るさは100%出力されており、4SFの0.69msの間にディスクリネーションが発生するため、4SFの開始時が図8の0msに相当し、4SFの終了時が0.69msに相当する。このとき、明るさは、ディスクリネーションが発生しない場合の0.7に対して0.65までしか低下しない。

30

## 【0048】

また、もう1つのディスクリネーションが発生するサブフィールド期間である7SFでの液晶の応答特性は、図10における「ディスクリネーション有り」に相当する特性となる。6SFでは全黒表示状態であるため明るさは0%であり、7SFの0.69msの間にディスクリネーションが発生するため、7SFの開始時が図10の0msに相当し、7SFの終了時が0.69msに相当する。このとき、明るさは、ディスクリネーションが発生しない場合の0.25に対して0.18までしか低下しない。

## 【0049】

そして、4SFと7SFでディスクリネーションが発生しない場合の明るさの和は0.95( $=0.70+0.25$ )となるのに対して、ディスクリネーションが発生する場合の明るさの和は0.83( $=0.65+0.18$ )となる。全面同一階調を前提として作成されるガンマ特性を基準とすると、ディスクリネーション発生表示状態では比率で87%( $=0.83/0.95$ )までしか暗くならない。すなわち、本実施例によれば、明るさの低下を抑制することができる。

40

## 【0050】

次に、他の隣接階調を表示する場合について説明する。まず図11に示した従来の階調データによって図6に示したA画素ラインの画素に16階調を表示させ、B画素ラインの画素に17階調を表示させる場合について説明する。この階調データを用いる場合にディスクリネーションが発生する期間は、A画素ラインの画素が黒表示状態でB画素ラインの

50

画素が白表示状態というディスクリネーション発生表示状態となるBサブフィールド期間における1SFと2SFである。

#### 【0051】

1SFから2SFまでの液晶の応答特性は、図10における「ディスクリネーション有り」に相当する特性となる。1SFの開始時から2SFの終了時までの1.39msの間にディスクリネーションが発生する。このため、1SFの開始時が図10における0msに相当し、2SFの終了時が1.39msに相当する。このとき、明るさは、ディスクリネーションが発生しない場合の0.5に対して0.27まで低下する。実施例1で述べたように全面同一階調を前提として作成されるガンマ特性を基準とすると、ディスクリネーションが発生する1SFから2SFまでに比率で54% (= 0.27 / 0.5) と暗くなる。10

#### 【0052】

一方、本実施例において、図5に示した階調データによってA画素ラインの画素（第2の画素）に16階調を表示させ、B画素ラインの画素（第1の画素）に17階調を表示させる場合について説明する。この階調データを用いる場合にディスクリネーションが発生する期間は、A画素ラインの画素とB画素ラインの画素が上記ディスクリネーション発生表示状態となるBサブフィールド期間における3SFと8SFである。3SFの前の2SFではA画素ラインの画素およびB画素ラインの画素のいずれも黒表示状態であり、ディスクリネーションは発生しない期間である。3SFでの液晶の応答特性は、図10における「ディスクリネーション有り」に相当する特性となる。2SFでは全黒表示状態であるため明るさは0%であり、3SFの0.69msの間にディスクリネーションが発生するため、3SFの開始時が図10の0msに相当し、3SFの終了時が0.69msに相当する。このとき、明るさは、ディスクリネーションが発生しない場合の0.25に対して0.18までしか低下しない。20

#### 【0053】

また、もう1つのディスクリネーションが発生するサブフィールド期間である8SFでの液晶の応答特性も図10における「ディスクリネーション有り」に相当する特性となる。7SFでは全黒表示状態であるため明るさは0%であり、8SFの0.69msの間にディスクリネーションが発生するため、8SFの開始時が図10の0msに相当し、8SFの終了時が0.69msに相当する。このとき、明るさは、ディスクリネーションが発生しない場合の0.25に対して0.18までしか低下しない。30

#### 【0054】

そして、3SFと8SFでディスクリネーションが発生しない場合の明るさの和は0.50 (= 0.25 + 0.25) となるのに対して、ディスクリネーションが発生する場合の明るさの和は0.36 (= 0.18 + 0.18) となる。全面同一階調を前提として作成されるガンマ特性を基準とすると、ディスクリネーション発生表示状態では比率で72% (= 0.36 / 0.50) までしか暗くならない。すなわち、本実施例によれば、明るさの低下を抑制することができる。

#### 【0055】

このように、本実施例では、隣接階調を表示する際にディスクリネーション発生表示状態となるオン／オフ隣接期間を1フレーム期間内で複数互いに離して（分散させて）設けることで1つの連続したオン／オフ隣接期間を短くしている。すなわち、ディスクリネーションによる明るさ低下が大きくなる前に隣接画素でのディスクリネーション発生表示状態を他の表示状態に移行させる。これにより、ディスクリネーションを原因とした明るさ低下を抑制して暗線が目立たないようにすることができ、良好な画質の画像を表示することができる。40

#### 【0056】

以上説明した液晶素子の駆動方法によってディスクリネーションの発生を抑制することが可能である。しかし、よりディスクリネーションによる暗線を目立たなくするために、本実施例では以下のような駆動方法も併せ用いる。50

**【0057】**

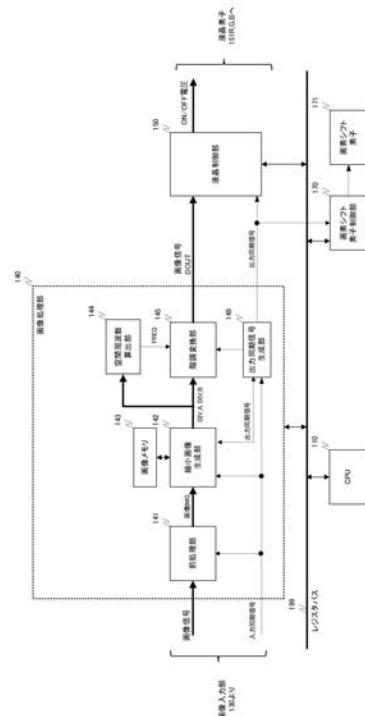

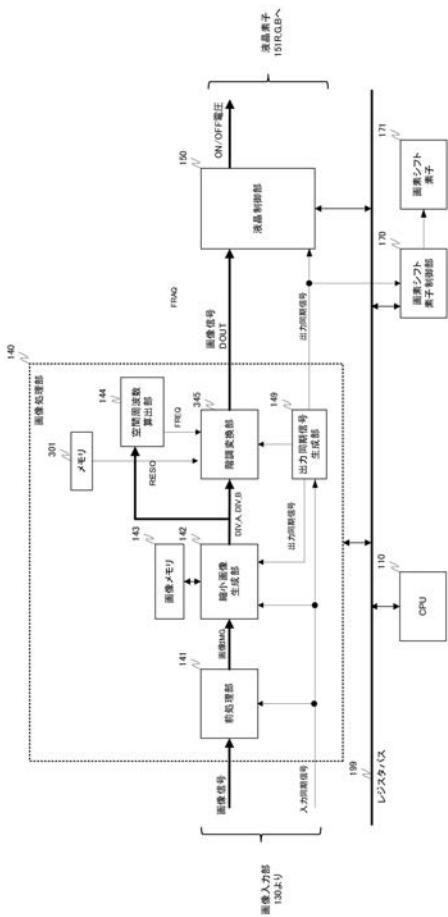

次に、図12を用いて画像処理部140および液晶制御部150の内部構成について説明する。

**【0058】**

画像処理部140は、前処理部141、縮小画像生成部142、画像メモリ143、空間周波数算出部144、階調変換部145および出力同期信号生成部149で構成される。画像処理部140を構成する各部は、レジスタバス199を介してCPU110と接続されている。

**【0059】**

前処理部141は、画像入力部130から入力された画像を、液晶素子151R、151G、151Bに適した色空間、解像度へ変換する。具体的には、色空間変換、幾何学変形補正(ワーピング、台形補正)、拡大縮小処理を含む表示レイアウトの変換処理を行う。また、入力された画像の特徴量を算出する。

10

**【0060】**

縮小画像生成部142は、前処理部141から出力された画像IMGを画像メモリ143に書き込み、画素シフト表示のための1stフレーム画像DIV\_Aと、2ndフレーム画像DIV\_Bを生成する。また、縮小画像生成部142は、1stフレーム画像DIV\_Aと、2ndフレーム画像DIV\_Bを倍速して出力する。すなわち入力周波数が60Hzである場合120Hzで1stフレーム画像DIV\_Aと、2ndフレーム画像DIV\_Bを出力する。また、縮小画像生成部142は、当該タイミングで出力している画像が、1stフレーム画像DIV\_Aか2ndフレーム画像DIV\_Bかを識別可能な同期信号を出力する。

20

**【0061】**

次に、前処理部141から出力された画像IMGから1stフレーム画像DIV\_Aを生成する方法を具体的に説明する。まず、縮小画像生成部142は、画像メモリ143に格納されている画像IMGの水平方向、垂直方向の座標がともに偶数である画素データを図13のようにサンプリングして、1stフレーム画像DIV\_Aとして出力する。そして、次に、縮小画像生成部142は、図13のように画像メモリ143から画像IMGの水平垂直方向の座標がともに奇数である画素データをサンプリングして、2ndフレーム画像DIV\_Bとして出力する。

30

**【0062】**

また、縮小画像生成部142は、縮小画像を生成せずに、縮小画像生成部142へ入力された入力画像をそのまま階調変換部145に出力することもできる。

**【0063】**

次に1stフレーム画像DIV\_Aと、2ndフレーム画像DIV\_Bがどのように投影面上に出力されるかについて説明する。図14に1stフレーム画像DIV\_Aと、2ndフレーム画像DIV\_Bの投影面上における投影位置関係を示す。図14において座標の記載された四角形が1stフレームにおける投影位置の1画素を表しており、この四角形の集合体が1stフレームにおける投影画像投影画像DIV\_Aとなる。一方、ハッチングされた四角形は2ndフレームにおける投影位置の1画素を表しており、この四角形の集合体が2ndフレームにおける投影画像DIV\_Bとなる。1stフレーム画像DIV\_Aと2ndフレーム画像DIV\_Bは、画素シフト素子170によって光路がシフトされることにより、結果として図14のように、水平垂直方向にそれぞれ1/2画素シフトした位置に投影される。

40

**【0064】**

次に空間周波数算出部144の処理の詳細について説明する。

**【0065】**

空間周波数算出部144は、縮小画像生成部142で生成された1stフレーム画像DIV\_Aと、2ndフレーム画像DIV\_Bのいずれかに対する空間周波数FREQを画素ごとに算出する。

50

## 【0066】

本実施例における空間周波数 FREQ は、検出対象画素位置を中心とした時の、空間方向の輝度変化量の度合いで定義する。輝度変化量が大きい場合に空間周波数が高いと算出され、輝度変化量が小さい場合に空間周波数が低いと算出される。

## 【0067】

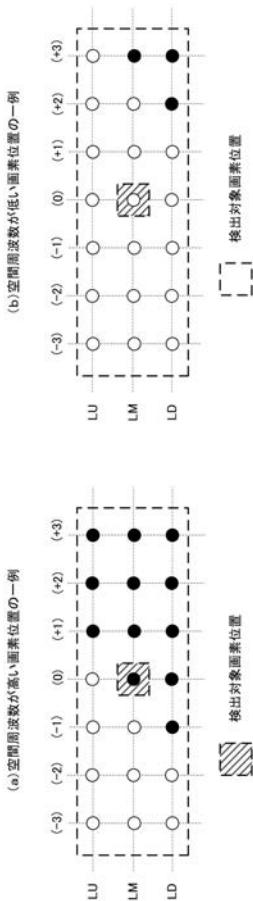

図 15 を用いて、空間周波数 FREQ のより具体的な算出方法を説明する。

## 【0068】

図 15 (a) は空間周波数が高い画素位置の一例を示しており、図 15 (b) は空間周波数が低い画素位置の一例を示している。

## 【0069】

算出用法について、ここでは図 15 (a) を用いて説明する。図 15 (a) において、LM は検出対象画素位置が存在するライン位置を表しており、LU は検出対象画素位置が存在するライン位置の 1 ライン上、LD は検出対象画素位置が存在するライン位置の 1 ライン下のライン位置を示している。また、水平方向の数字は、検出対象画素位置を 0 としたときの、水平相対位置を示している。また、図示した白丸の画素は、階調値が 255 (8bit 換算) の画素を示しており、黒丸の画素は、階調値が 0 の画素を示している。

10

## 【0070】

まず、画素 LM(0) の輝度値 YLM(0) と画素 LM(0) の左側に隣接する画素 LM(-1) の輝度値 YLM(-1) との差分 YGLML を算出する。

## 【0071】

$$YGLML = | YLM(0) - YLM(-1) |$$

20

次に、画素 LM(0) の輝度値 YLM(0) と画素 LM(0) の右側に隣接する画素 LM(+1) の輝度値 YLM(+1) との差分 YGLMR は以下の式で算出される。

## 【0072】

$$YGLMR = | YLM(0) - YLM(+1) |$$

算出した差分 YGLML と差分 YGLMR の大きい方を水平方向の輝度変化量 HDIFF とする。垂直方向についても同様の計算式で、垂直方向の輝度変化量 VDFFF を算出することが出来る。水平方向の輝度変化量 HDIFF と、垂直方向の輝度変化量 VDFFF の大きい方が、検出対象画素位置の輝度変化量 DIFF と算出される。

30

## 【0073】

本実施例では、水平方向の輝度変化量 HDIFF と、垂直方向の輝度変化量 VDFFF の大きい方を輝度変化量 DIFF としたが、斜め方向の輝度変化量を参照してもよい。この時、それぞれの最大値を採用してもよいし、所定の閾値以上の値の平均等でも良い。

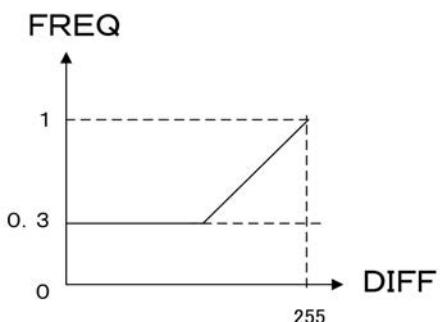

次に、図 16 を用いて輝度変化量 DIFF を空間周波数 FREQ へ変換する特性を説明する。本実施例における変換特性は、図 16 に示した通り、輝度変化量 DIFF が大きいほど、空間周波数 FREQ が大きくなるように制御する。

## 【0074】

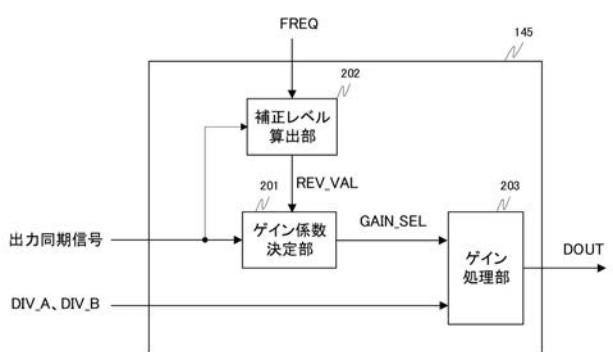

階調変換部 145 は、自身に入力される画像データに対して、フレーム毎にそれぞれ異なる階調変換処理を適用する。図 17 に階調変換部 145 の一構成例を示す。

40

## 【0075】

本例における階調変換部 145 は、ゲイン係数決定部 201、補正レベル算出部 202、及びゲイン処理部 203 で構成される。

## 【0076】

ゲイン係数決定部 201 は、自身に入力される出力同期信号に同期して、フレーム毎に異なるゲイン係数 GAIN\_SEL を決定し、ゲイン処理部 203 に通知する。ゲイン係数決定部 201 は、補正レベル REV\_VAL をゲイン係数 GAIN\_SEL としてフレーム毎に選択してゲイン処理部 203 へ出力する。

## 【0077】

補正レベル算出部 202 は、空間周波数算出部 144 で算出された空間周波数 FREQ に応じて、ゲイン係数決定部 201 で使用する補正レベル REV\_VAL を算出する。補

50

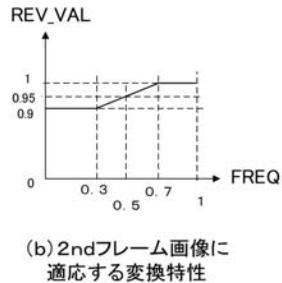

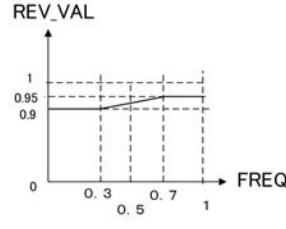

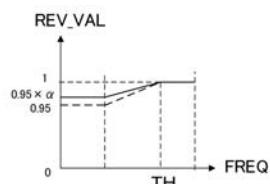

正レベル R E V \_ V A L を算出する際の変換特性の一例を図 18 に示す。

【 0 0 7 8 】

図 18 ( a ) は 1 s t フレーム画像に適応する変換特性であり、空間周波数 F R E Q の値によらず常に 1 を出力する。

【 0 0 7 9 】

図 18 ( b ) は 2 n d フレーム画像に適応する変換特性であり、2 n d フレーム画像に対して、空間周波数 F R E Q が大きい程、補正レベル R E V \_ V A L は大きくなるように制御する。これは、後述するように空間周波数が高いほど、画素ずらし処理による高解像度化の効果を高める制御を行うためである。

【 0 0 8 0 】

また、図 18 ( b )において、空間周波数 F R E Q の値に応じた変換特性の一例を記載したが、この変換特性については高周波成分の表示に影響を与える要素に対して適宜決定すればよい。例えば、液晶素子 151 の画素ピッチが小さいほど空間周波数 F R E Q に対する補正レベル R E V \_ V A L の低減度合いを大きくすればよい。これは、画素ピッチが小さい液晶パネルの方が、より高周波成分を表示可能であるためである。また、ズーム比から実空間での空間周波数を算出してそれに応じて決めてよい。こうすることで、実際に表示される投影面画像に応じた空間周波数に対して制御することが可能になる。

【 0 0 8 1 】

ゲイン処理部 203 は、入力画像信号に対して、ゲイン係数決定部 201 が決定したゲイン係数 G A I N \_ S E L を乗算するゲイン処理を行う。ゲイン係数 G A I N \_ S E L は、1 s t フレーム画像 D I V \_ A 、及び 2 n d フレーム画像 D I V \_ B に対応して算出されるため、それぞれのフレーム画像に対してゲイン処理されることになる。

【 0 0 8 2 】

上記のように階調変換部 145 がフレーム毎に異なるゲイン処理を行うことにより、ディスクリネーションによる画素の明るさの低下を視認されづらくすることができる。この仕組みについて図 19 を用いて説明する。

【 0 0 8 3 】

図 19 ( a ) は、ゲイン係数 100 % の時の入力階調値と出力階調値の関係（入出力階調特性）と観察者により視認される投影画像のイメージを示している。本実施例における液晶素子 151 は、水平方向に 96 画素を有するものとする。また、図 19 ( a ) に示すように、右方向に単純に一階調ずつ増加するグラデーション画像を表示した際には、ディスクリネーションが生じない画素は滑らかな濃淡が表現される。一方で、隣接画素の駆動状態でオン期間とオフ期間が重なる時間が長い隣接階調ではディスクリネーションの影響により明るさが低下し暗線として知覚される。図 19 では、ディスクリネーションによる暗線が 5 箇所知覚されるものとして説明する。

【 0 0 8 4 】

なお、図 19においては、ディスクリネーションによる画素の明るさの低下を視認されづらくすることができる説明を簡単にするために、画素シフト素子 170 が駆動しない場合、すなわちフレームごとに光路をシフトしない場合の投影画像を例にとって説明する。

【 0 0 8 5 】

ここで、入力階調値 64 と階調値 65 が隣接する位置に発生しているディスクリネーションに着目する。ここで、上記と同様のグラデーション画像に対して、ゲイン係数 90 % のゲインを適用した場合のディスクリネーションの位置の変化について図 19 ( b ) を用いて説明する。ゲイン係数 90 % のゲイン処理により、階調値 64 と階調値 65 の隣接関係は位置 71 と位置 72 の画素へと移動する。よって、ディスクリネーションによる暗線は階調値 64 を表示している位置 71 の画素で発生する。

【 0 0 8 6 】

階調変換部 145 はゲイン係数 100 % と 90 % をフレーム毎に交互に切り替えるため、投影される画像も図 19 ( a ) と図 19 ( b ) に示した画像がフレーム毎に交互に切り替わる。この切り替わり周期が一定以上であると、観察者には 2 フレームの画像が積分さ

10

20

30

40

50

れて知覚されるため、ディスクリネーションによる暗線も図 19 ( c ) のように約 1 / 2 の濃さとなって知覚される。これが、階調変換部 145 の動作がディスクリネーションによる暗線を視認されづらくする原理である。なお、この原理は他の位置にて発生しているディスクリネーションに関しても同様である。

#### 【 0087 】

図 19 では、ゲイン係数が 100 % と 90 % をフレーム毎に交互に切り替える例を示したが、これに限定されることはない。

#### 【 0088 】

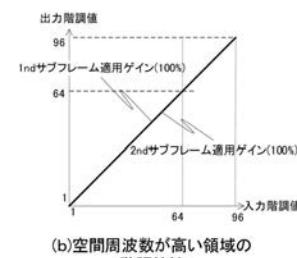

例えば、図 20 に示したように、低周波領域（空間周波数 FREQ が 0 . 3 以下の領域）は、1st フレームのゲインを 100 % 、2nd フレームのゲインを 90 % のゲイン切り替えを行い、高周波領域（空間周波数 FREQ が 0 . 7 以上の領域）は、1st フレーム、2nd フレーム共に 95 % のゲインとしてもよい。このように制御することで、画像信号の空間周波数によらず、ゲイン処理後の 1st フレーム画像と 2nd フレーム画像の平均が 95 % となり、輝度を均一に保つことが出来る。10

#### 【 0089 】

出力同期信号生成部 149 は、出力同期信号を生成するブロックであり、自身に入力されている不図示のドットクロックのベースとなる基準クロックをカウントして出力同期信号を生成する。この出力同期信号は、縮小画像生成部 142 による画像メモリ 143 の読み出しタイミングや、液晶制御部 150 によって駆動される液晶素子 151 R、G、B の更新タイミング、画素シフト素子制御部 170 によって駆動される画素シフト素子 171 の駆動タイミングを同期化するための基準信号として扱われる。20

#### 【 0090 】

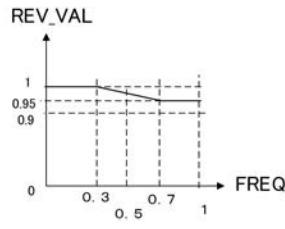

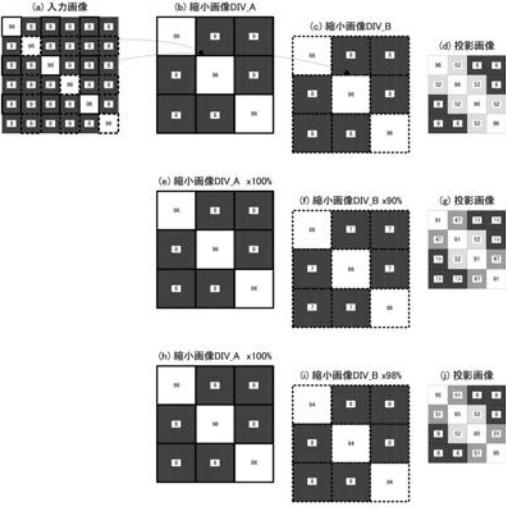

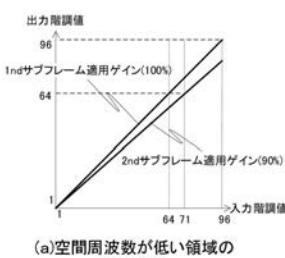

次に図 21 を用いて、本実施例における階調変換部 145 で処理される階調特性の一例を説明する。図 21 ( a ) は空間周波数が低い領域の階調特性の一例を示しており、図 21 ( b ) は空間周波数が高い領域の階調特性の一例を示している。

#### 【 0091 】

なぜ、上記のような処理を行うのかというと、空間周波数の高い領域に、異なるゲイン係数を用いたゲイン処理を行うと画素シフトによる高解像化の効果が低下してしまう場合があるためである。1st フレーム画像 DIV\_A 、2nd フレーム画像 DIV\_B のそれぞれに対して異なるゲイン係数を用いたゲイン処理を行うことにより高解像度化の効果が低下してしまう場合の例を図 22 を用いて説明する。30

#### 【 0092 】

図 22 ( a ) が縮小画像生成部 142 に対する入力画像を表している。なお、四角が各画像データの 1 画素を表し、四角の中の数字が各画素の階調値を表している。

#### 【 0093 】

まず、縮小画像生成部 142 は、図 22 ( a ) の実線で囲った画素をサンプリングし 1st フレーム画像 DIV\_A を、破線で囲った画素をサンプリングし 2nd フレーム画像 DIV\_B を、それぞれ生成する。この場合の、1st フレーム画像 DIV\_A 、2nd フレーム画像 DIV\_B を図 22 ( b ) ( c ) にそれぞれ示す。仮に、この 1st フレーム画像 DIV\_A 、2nd フレーム画像 DIV\_B が階調変換部 145 の処理を経ずに出力された場合の投影画像のイメージを図 22 ( d ) に示す。2nd フレーム画像 DIV\_B は 1st フレーム画像 DIV\_A に対して、右下に 1 / 2 画素シフトして投影されるため、図 22 ( d ) には、1st フレーム画像 DIV\_A と 1 / 2 画素シフトした 2nd フレーム画像 DIV\_B の階調値を時間積分（平均）した階調値となる。40

#### 【 0094 】

次に、1st フレーム画像 DIV\_A 、2nd フレーム画像 DIV\_B が階調変換部 145 の処理を経て出力される場合を考える。1st フレーム画像 DIV\_A 、2nd フレーム画像 DIV\_B はそれぞれ時分割で階調変換部 145 へ出力されるため、階調変換部 145 は 1st フレーム画像 DIV\_A と 2nd フレーム画像 DIV\_B にそれぞれ異なるゲイン係数を適用する。1st フレーム画像 DIV\_A に 100 % のゲイン係数を、2

$n$  d フレーム画像 D I V \_ B に 90 % のゲイン係数をかけた場合の画像を図 22 ( e ) ( f ) にそれぞれ示す。また、図 22 ( e ) ( f ) が画素シフトで投影された場合のイメージを図 22 ( g ) に示す。理想的には、図 22 ( d ) のように、左上から右下にかけての斜めの高階調値のラインが一律に投影されるべきである。しかしながら、図 22 ( g )においては、高階調値 91 の斜めのラインの両脇（右上側と左下側）に階調値 47 の画素と階調値 52 の画素が交互に表示されてしまう。これら階調値 47 の画素と階調値 52 の画素は、入力画像には存在しなかったジャギーのように視認されてしまう。したがって、画素シフト処理 ON の場合に、階調変換部 145 で、1st フレーム画像 D I V \_ A 、 2nd フレーム画像 D I V \_ B のそれぞれに対して、異なったゲイン係数によりゲイン処理を行うと画素シフトによる高解像化の効果が低下してしまう。

10

## 【 0095 】

したがって、画素シフトによる高解像化の効果を低下させないようにするために、1st フレーム画像 D I V \_ A 、 2nd フレーム画像 D I V \_ B のそれぞれに対して、高解像度化の効果の低下が顕著に視認される高周波領域部に適用するゲインの差を小さくすることが望ましい。本実施例において高周波領域部の特徴として、高解像度化の効果が望まれている。また一方でディスクリネーションによる暗線は視認されづらい。そのため、2つのフレーム画像に対して、同じゲイン処理を乗じるように処理することが好ましく、結果として投影される画像は図 22 ( d ) のようになり、理想的な高画質化が実現出来る。一方、低周波領域部においては、高解像度化の効果が視認されづらく、ディスクリネーションによる暗線は視認されやすい。このような場合は、2つのフレーム画像に対して、ゲインの差を大きくすることで、ディスクリネーションの低減効果を優先する。以上の処理を行うことで、画素シフト制御による高解像度化と、ディスクリネーションの低減効果を両立することが出来る。

20

## 【 0096 】

また、本実施例の空間周波数算出部 144 は、別の構成例を用いてもよい。例えば、空間領域の画像データを周波数領域に変換するフーリエ変換法を用いればよい。この場合、フーリエ変換後のデータを用いて空間周波数の度合いを判定すれば、同様の制御が可能になる。

## 【 0097 】

以上説明したように液晶プロジェクタ 100 の各部が動作することによって、コストを抑えつつ、ディスクリネーションによる画質低下を抑制し、画素シフトによる高解像度化を実現することができる。

30

## 【 0098 】

なお、本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

## 【 0099 】

以上説明した各実施例は代表的な例にすぎず、本発明の実施に際しては、各実施例に対して種々の変形や変更が可能である。

40

## 【 0100 】

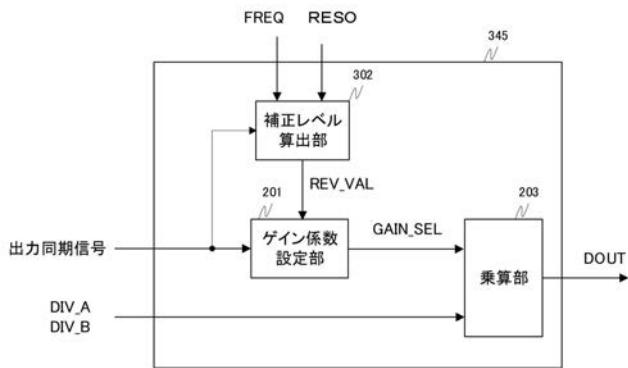

## &lt; 実施例 2 &gt;

実施例 1 では、入力画像の空間周波数に応じて、階調変換部 145 が適用するゲイン係数の制御を行った。一方、実施例 2 では、入力画像の空間周波数とさらに入力解像度とに応じて、階調変換部 145 が適用するゲイン係数の制御を行う点が実施例 1 とは異なる。

## 【 0101 】

以下、実施例 1 と異なる構成や処理について詳しく説明し、実施例 1 と同様の構成や処理についての説明は省略する。

## 【 0102 】

50

図23を用いて画像処理部140および液晶制御部150の内部構成について説明する。実施例1と異なる構成としては、メモリ301と階調変換部345の内部構成が異なる。本実施例における階調変換部345の構成について、図24を用いて詳細に説明する。補正レベル算出部302は、空間周波数算出部144で算出された空間周波数FREQと、メモリ301に保存されているパネル解像度RESOとから補正レベルREV\_VALを算出する。

#### 【0103】

補正レベル算出部302では、まず、入力解像度RESOを補正係数に変換する。変換の特性を図25に示す。図25に示した通り、解像度RESO\_A～RESO\_Dのそれぞれに対応した補正係数が設定されている。本実施例で示す解像度は、RESO\_A < RESO\_B < RESO\_C < RESO\_Dの順に、解像度が高くなる。つまり、入力解像度が高くなるにつれて、補正係数が大きくなるように設定されている。

10

#### 【0104】

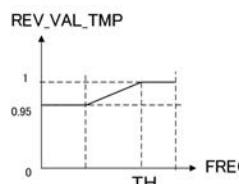

次に、補正レベル算出部302は、空間周波数FREQ、及び補正係数とを用いて、補正レベルREV\_VALに変換する。まず、空間周波数FREQを、基準補正レベルREV\_VAL\_TMPに変換する。

#### 【0105】

変換特性を図26(a)に示す。図26(a)を見て分かる通り、空間周波数FREQが高い程、基準補正レベルREV\_VAL\_TMPは大きくなるように設定されている。

#### 【0106】

次に、空間周波数FREQが所定の閾値THより小さい領域に補正係数を乗算し、補正レベルREV\_VALを算出する。

#### 【0107】

$$REV\_VAL = REV\_VAL\_TMP \times$$

本実施例において、補正係数を入力解像度に応じて可変させることで、ディスクリネーションによる画質低下抑制と、画素シフトによる高解像度化を両立させることができる。

#### 【0108】

入力解像度が高くなるに従って、補正係数が大きくなるように制御するのは、入力解像度が高い画像の方が、中域から高域を含む画像が多く存在する傾向にあるため、ゲイン係数GAIN\_SELが大きくなるようなREV\_VALを算出することで高解像度化効果を高めるためである。

30

#### 【0109】

以上示したように、入力解像度と空間周波数に応じて、ゲイン係数GAIN\_SELの制御を行うことで、高周波領域の影響度合いを入力解像度に応じて制御することが可能になり、より精度良く補正を行うことが可能になる。結果として、実施例1と比較して、さらに精度よくディスクリネーションによる暗線を視認されづらくする効果を維持することができる。

#### 【0110】

したがって、コストを抑えつつ、ディスクリネーションによる画質低下を抑制し、画素シフトによる高解像度化を実現することができる。

40

#### 【0111】

なお、本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

#### 【0112】

以上説明した各実施例は代表的な例にすぎず、本発明の実施に際しては、各実施例に対して種々の変形や変更が可能である。

## 【0113】

## &lt;実施例3&gt;

実施例1では、縮小画像生成部145の出力画像D I V\_A、D I V\_Bを用いて空間周波数を算出する例を示した。一方、実施例3では、縮小画像生成部145に入力される画像I M Gを用いて空間周波数を算出する点が実施例1とは異なる。

## 【0114】

以下、実施例1と異なる構成や処理について詳しく説明し、実施例1と同様の構成や処理についての説明は省略する。

## 【0115】

図27を用いて画像処理部140および液晶制御部150の内部構成について説明する。実施例1と異なる構成としては、空間周波数算出部444の内部構成が異なる。

10

## 【0116】

空間周波数算出部444に入力される縮小画像生成前の入力画像I M Gは、図13に示した画素配列になっている。空間周波数算F R E Qを算出する対象画素は、画像I M Gの水平方向、垂直方向の座標がともに偶数である画素データ(1 s t フレーム画像D I V\_A)、及び画像I M Gの水平垂直方向の座標がともに奇数である画素データ(2 n d フレーム画像D I V\_B)である。これらの画素それぞれにおいて、実施例で説明した空間周波数算出方法を同様に適用すればよい。

## 【0117】

この場合、空間周波数算出部444は、縮小前の画像信号I M Gに対して、縮小する際の1 s t フレーム画像D I V\_Aのサンプリング位置の周辺画素を参照して空間周波数F R E Qを算出する。具体的には、図13において、1 s t フレーム画像D I V\_Aの(2, 2)の空間周波数F R E Qを算出する際に、(1, 1)、(2, 1)、(2, 2)、(1, 2)、(3, 2)(1, 3)(2, 3)(3, 3)の周囲8画素を用いて算出する。

20

## 【0118】

また、縮小する際の2 n d フレーム画像D I V\_Bのサンプリング位置の周辺画素を参照して空間周波数F R E Qを算出する。具体的には、図13において、2 n d フレーム画像D I V\_Bの(3, 2)の空間周波数F R E Qを算出する際に、(2, 1)、(3, 1)、(4, 1)、(2, 2)、(4, 2)(2, 3)(3, 3)(4, 3)の周囲8画素を用いて算出する。

30

## 【0119】

以上示したように、縮小画像生成前の入力画像を用いて空間周波数を算出することで、より高精度に空間周波数成分を算出することが可能になり、より精度良く補正を行うことが可能になる。結果として、実施例1と比較して、さらに精度よくディスクリネーションによる暗線を視認されづらくする効果を維持することができる。

## 【0120】

したがって、コストを抑えつつ、ディスクリネーションによる画質低下を抑制し、画素シフトによる高解像度化を実現することができる。

## 【符号の説明】

## 【0121】

40

100 液晶プロジェクタ、110 C P U、130 画像入力部、

140 画像処理部、141 前処理部、142 縮小画像生成部、

143 画像メモリ、144, 444 空間周波数算出部、

145, 345 階調変換部、150 液晶制御部、

151 R, 151 G, 151 B 液晶素子、160 光源制御部、

161 光源、170 画素シフト素子、171 画素シフト素子制御部、

199 レジスタバス、201 ゲイン係数決定部、

202, 302 補正レベル算出部、203 ゲイン処理部、301 メモリ

【図1】

【図3】

【図4】

【図2】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 1 】

【 図 1 0 】

【 図 1 2 】

【図13】

入力画像の画素配列

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

【図21】

【図23】

【図24】

【図25】

|      | RESO   | $\alpha$ |

|------|--------|----------|

| 解像度低 | RESO_A | 0.985    |

| ↓    | RESO_B | 0.99     |

| ↓    | RESO_C | 0.995    |

| 解像度高 | RESO_D | 1        |

【図26】

(a)「空間周波数」—「基準補正レベル」変換特性の一例

(b)「空間周波数」—「補正レベル」変換特性の一例

【図27】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 5 0 C |

| G 0 9 G | 3/20  | 6 8 0 C |

| G 0 9 G | 3/20  | 6 1 1 D |

| G 0 2 F | 1/133 | 5 5 0   |

| H 0 4 N | 5/66  | 1 0 2 B |

F ターム(参考) 5C006 AA14 AA22 AB01 AF03 AF04 AF42 AF43 AF44 AF45 AF46

AF47 BB11 BC12 BF08 BF15 EA01 EC11 FA22 FA25 FA51

5C058 AA06 BA01 BA07 BA25 BB13 BB17 EA26

5C080 AA10 BB05 CC03 DD05 DD06 DD07 DD10 DD27 EE19 EE21

EE29 GG02 GG05 GG12 GG15 GG17 JJ02 JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2020046598A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2020-03-26 |

| 申请号            | JP2018176695                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2018-09-21 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 山岸正治                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 山岸 正治                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/36 G09G3/20.641.P G09G3/20.612.U G09G3/20.660.E G09G3/20.641.E G09G3/20.650.C<br>G09G3/20.680.C G09G3/20.611.D G02F1/133.550 H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZD25 2H193/ZE04 2H193/ZF12 2H193/ZQ06 2H193/ZQ11 2H193/ZR04 5C006<br>/AA14 5C006/AA22 5C006/AB01 5C006/AF03 5C006/AF04 5C006/AF42 5C006/AF43 5C006/AF44<br>5C006/AF45 5C006/AF46 5C006/AF47 5C006/BB11 5C006/BC12 5C006/BF08 5C006/BF15 5C006<br>/EA01 5C006/EC11 5C006/FA22 5C006/FA25 5C006/FA51 5C058/AA06 5C058/BA01 5C058/BA07<br>5C058/BA25 5C058/BB13 5C058/BB17 5C058/EA26 5C080/AA10 5C080/BB05 5C080/CC03 5C080<br>/DD05 5C080/DD06 5C080/DD07 5C080/DD10 5C080/DD27 5C080/EE19 5C080/EE21 5C080/EE29<br>5C080/GG02 5C080/GG05 5C080/GG12 5C080/GG15 5C080/GG17 5C080/JJ02 5C080/JJ04 5C080<br>/JJ05 5C080/JJ06 |         |            |

| 代理人(译)         | 佐藤安倍晋三<br>黒岩 Soware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

解决的问题:抑制由于旋错而导致的图像质量下降,并通过像素移位实现高分辨率。在液晶显示装置中,基于在施加了灰度转换处理之后的图像的灰度值,针对液晶元件的每个像素,控制预定的导通电压/截止电压施加时间。因此,用于改变来自光源的光对于每个像素的透射率或反射率的驱动装置,用于从输入图像产生多个像素移位图像并以时分方式输出它们的像素移位图像生成装置,以及以预定方式进行调制的光。能够在方向上移动和显示的像素移位装置,分别应用用于将时间上连续的帧图像数据乘以不同的增益系数的灰度转换处理的灰度转换装置以及像素移位图像到空间。用于计算频率的空间频率计算装置,并且灰度转换装置基于由空间频率计算装置计算出的空间频率来控制要乘以灰度转换处理的增益系数的差。和 [选择图]图12