(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-224916

(P2014-224916A)

(43) 公開日 平成26年12月4日(2014.12.4)

| (51) Int.Cl. |              | F 1       | テーマコード (参考) |                 |

|--------------|--------------|-----------|-------------|-----------------|

| <b>G09G</b>  | <b>3/20</b>  | (2006.01) | G09G        | 3/20 622C 2H193 |

| <b>G09G</b>  | <b>3/36</b>  | (2006.01) | G09G        | 3/36 5C006      |

| <b>G02F</b>  | <b>1/133</b> | (2006.01) | G09G        | 3/20 622M 5C080 |

|              |              |           | G09G        | 3/20 622D       |

|              |              |           | G09G        | 3/20 623U       |

審査請求 未請求 請求項の数 6 O L (全 18 頁) 最終頁に続く

|           |                              |            |                                                                                                                         |

|-----------|------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2013-104211 (P2013-104211) | (71) 出願人   | 000103747<br>京セラディスプレイ株式会社<br>滋賀県野洲市市三宅641-1                                                                            |

| (22) 出願日  | 平成25年5月16日 (2013.5.16)       | (74) 代理人   | 100103090<br>弁理士 岩壁 冬樹                                                                                                  |

|           |                              | (74) 代理人   | 100124501<br>弁理士 塩川 誠人                                                                                                  |

|           |                              | (72) 発明者   | 権藤 賢二<br>滋賀県野洲市市三宅641-1 京セラディスプレイ株式会社内                                                                                  |

|           |                              | F ターム (参考) | 2H193 ZA04 ZC24 ZC34 ZF24<br>5C006 AA16 AC24 AC28 AF42 AF43<br>AF44 BB16 FA12<br>5C080 AA10 BB05 DD08 FF11 JJ02<br>JJ04 |

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】選択期間を短くしたとしても、表示品位の低下を防止することができる液晶表示装置を提供する。

【解決手段】第1のゲートドライバ1は、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定する。第2のゲートドライバ2は、奇数番目のゲートラインの選択期間の終了前に、そのゲートラインの次の偶数番目のゲートラインに対する所定のオン電位の設定を開始し、その奇数番目のゲートラインの選択期間の終了後も、その偶数番目のゲートラインを所定のオン電位に設定する。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

コモン電極と、マトリクス状に配置された画素電極とを有するとともに、前記画素電極の行毎にゲートラインを有し、前記画素電極の列毎にソースラインを有する液晶パネルと、

前記液晶パネルの奇数番目のゲートラインを所定のオン電位に設定する第1のゲート駆動部と、

前記液晶パネルの偶数番目のゲートラインを前記所定のオン電位に設定する第2のゲート駆動部と、

前記液晶パネルの各ソースラインの電位を設定するソース駆動部とを備え、

第1のゲート駆動部は、連続する2つのフレームのうち少なくとも一方のフレームで、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、前記所定のオン電位に設定し、

第2のゲート駆動部は、少なくとも前記一方のフレームで、奇数番目のゲートラインの選択期間の終了前に、当該ゲートラインの次の偶数番目のゲートラインに対する前記所定のオン電位の設定を開始し、前記奇数番目のゲートラインの選択期間の終了後も引き続き、前記偶数番目のゲートラインを前記所定のオン電位に設定し、

ソース駆動部は、少なくとも前記一方のフレームで、第1のゲート駆動部が奇数番目のゲートラインを前記所定のオン電位に設定する場合に、各ソースラインを、当該奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該奇数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの次の偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定する

ことを特徴とする液晶表示装置。

## 【請求項 2】

第1のゲート駆動部は、連続する2つのフレームのうち一方のフレームで、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、

第2のゲート駆動部は、前記一方のフレームで、奇数番目のゲートラインの選択期間の終了前に、当該ゲートラインの次の偶数番目のゲートラインに対する前記所定のオン電位の設定を開始し、前記奇数番目のゲートラインの選択期間の終了後も引き続き、前記偶数番目のゲートラインを前記所定のオン電位に設定し、

ソース駆動部は、前記一方のフレームで、第1のゲート駆動部が奇数番目のゲートラインを前記所定のオン電位に設定する場合に、各ソースラインを、当該奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該奇数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの次の偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、

第2のゲート駆動部は、連続する前記2つのフレームのうち他方のフレームで、偶数番目のゲートラインを順に選択し、選択したゲートラインを前記所定の選択期間、前記所定のオン電位に設定し、

第1のゲート駆動部は、前記他方のフレームで、偶数番目のゲートラインの選択期間の終了前に、当該ゲートラインの前の奇数番目のゲートラインに対する前記所定のオン電位の設定を開始し、前記偶数番目のゲートラインの選択期間の終了後も引き続き、前記奇数番目のゲートラインを前記所定のオン電位に設定し、

ソース駆動部は、前記他方のフレームで、第2のゲート駆動部が偶数番目のゲートラインを前記所定のオン電位に設定する場合に、各ソースラインを、当該偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該偶数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの前の奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定する

請求項1に記載の液晶表示装置。

## 【請求項 3】

10

20

30

40

50

第1のゲート駆動部は、連続する2つのフレームのうち一方のフレームで、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、

第2のゲート駆動部は、前記一方のフレームで、第1のゲート駆動部がゲートラインに対する前記所定のオン電位の設定を開始する時に、当該ゲートラインの次の偶数番目のゲートラインに対する前記所定のオン電位の設定を開始し、前記所定の選択期間の倍の期間、当該偶数番目のゲートラインを前記所定のオン電位に設定し、

第2のゲート駆動部は、連続する前記2つのフレームのうち他方のフレームで、偶数番目のゲートラインを順に選択し、選択したゲートラインを前記所定の選択期間、前記所定のオン電位に設定し、

第1のゲート駆動部は、前記他方のフレームで、第2のゲート駆動部がゲートラインに対する前記所定のオン電位の設定を開始する時に、当該ゲートラインの前の奇数番目のゲートラインに対する前記所定のオン電位の設定を開始し、前記所定の選択期間の倍の期間、当該奇数番目のゲートラインを前記所定のオン電位に設定する

請求項2に記載の液晶表示装置。

#### 【請求項4】

第1のゲート駆動部は、各フレームで、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、

第2のゲート駆動部は、各フレームで、奇数番目のゲートラインの選択期間の終了前に、当該ゲートラインの次の偶数番目のゲートラインに対する前記所定のオン電位の設定を開始し、前記奇数番目のゲートラインの選択期間の終了後も引き続き、前記偶数番目のゲートラインを前記所定のオン電位に設定し、

ソース駆動部は、各フレームで、第1のゲート駆動部が奇数番目のゲートラインを前記所定のオン電位に設定する場合に、各ソースラインを、当該奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該奇数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの次の偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定する

請求項1に記載の液晶表示装置。

#### 【請求項5】

第1のゲート駆動部は、各フレームで、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、

第2のゲート駆動部は、各フレームで、第1のゲート駆動部がゲートラインに対する前記所定のオン電位の設定を開始する時に、当該ゲートラインの次の偶数番目のゲートラインに対する前記所定のオン電位の設定を開始し、前記所定の選択期間の倍の期間、当該偶数番目のゲートラインを前記所定のオン電位に設定する

請求項4に記載の液晶駆動装置。

#### 【請求項6】

ソース駆動部は、ソースラインに接続される接続端子を複数備え、フレームの終了後、次のフレームの開始までの期間内で、各接続端子を短絡させる

請求項1から請求項5のうちのいずれか1項に記載の液晶駆動装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶表示装置に関し、特に、奇数番目の行のゲートラインに対応するゲート駆動部と、偶数番目の行のゲートラインに対応するゲート駆動部とを備える液晶表示装置に関する。

##### 【背景技術】

##### 【0002】

TFT (Thin Film Transistor) 等のスイッチング素子を有する液晶パネルは、例えば、コモン電極と、マトリクス状に配置された画素電極とを備える。さらに、その液晶パネ

ルは、画素電極の行毎にゲートラインを備え、画素電極の列毎にソースラインを備える。そして、ゲートドライバが、各行のゲートラインを順次選択し、ソースドライバが、各ソースラインの電位を、選択行の各画素の画像データに応じた電位に設定することで画像を表示する。

【0003】

また、このような液晶パネルと、ゲートドライバおよびソースドライバとを備える液晶表示装置として、奇数番目の行のゲートラインを駆動するゲートドライバと、偶数番目の行のゲートラインを駆動するゲートドライバとを備える構成が提案されている。すなわち、奇数番目の行のゲートラインに対応するゲートドライバと、偶数番目の行のゲートラインに対応するゲートドライバとを別々に設ける構成が提案されている（例えば、特許文献1参照）。

10

【0004】

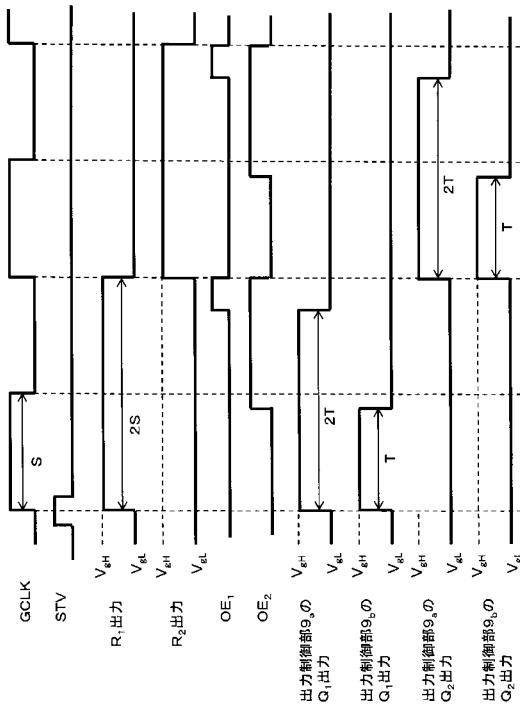

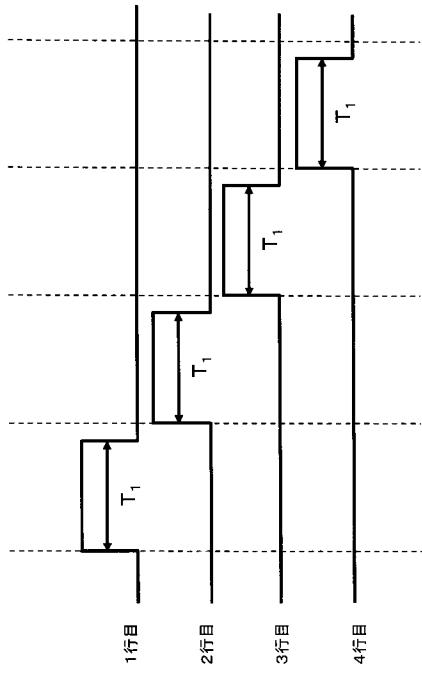

図8は、一般的なゲートラインの駆動波形を示す模式図である。一般に、液晶表示装置のゲートラインは、1本ずつ順番に選択される。そして、選択されたゲートラインは、選択期間 $T_1$ の間、所定の電位に設定される。図8では、4行目のゲートラインまでの駆動波形を示しているが、5行目以降の駆動波形も、図8に示す駆動波形と同様である。

【0005】

選択されたゲートラインが所定の電位に設定されるときに、ソースドライバは、各ソースラインの電位を、そのゲートラインの行の各画素の画像データに応じた電位に設定する。ゲートラインが所定の電位に設定されることによって、その行の各画素電極は、ソースラインと等電位に変化し、その結果、その行の画像を表示することができる。

20

【0006】

奇数番目の行のゲートラインに対応するゲートドライバと、偶数番目の行のゲートラインに対応するゲートドライバとを別々に設けた構成であっても、図8に示すように、ゲートラインが1本ずつ選択され、選択されたゲートラインは、選択期間 $T_1$ の間、所定の電位に設定される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2008-225424号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0008】

近年、液晶パネルの高解像度化が要求されている。そのため、選択期間を短くする必要が生じている。

【0009】

しかし、選択期間を短くすると、ゲートラインを所定の電位に設定することができる時間が短くなってしまう。

【0010】

また、図8では、所定の電位への立ち上がりエッジを模式的に図示しているが、画素電位はゲートラインがあいて所定の電位の設定を開始してから、所定の画素電位になるまでには、時間がかかる。

40

【0011】

従って、選択期間を短くすると、画素電位を所定の電位に設定することができる時間の確保が困難になる。すると、選択行の個々の画素電極をソースラインと等電位に変化させることが困難になる場合も生じ、表示品位が低下する可能性がある。

【0012】

そこで、本発明は、選択期間を短くしたとしても、表示品位の低下を防止することができる液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

50

## 【0013】

本発明による液晶表示装置は、コモン電極と、マトリクス状に配置された画素電極とを有するとともに、画素電極の行毎にゲートラインを有し、画素電極の列毎にソースラインを有する液晶パネル（例えば、液晶パネル5）と、液晶パネルの奇数番目のゲートラインを所定のオン電位に設定する第1のゲート駆動部（例えば、第1のゲートドライバ1）と、液晶パネルの偶数番目のゲートラインを所定のオン電位に設定する第2のゲート駆動部（例えば、第2のゲートドライバ2）と、液晶パネルの各ソースラインの電位を設定するソース駆動部（例えば、ソースドライバ3）とを備え、第1のゲート駆動部が、連続する2つのフレームのうち少なくとも一方のフレーム（例えば、フレームA）で、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、第2のゲート駆動部が、少なくともその一方のフレームで、奇数番目のゲートラインの選択期間の終了前に、当該ゲートラインの次の偶数番目のゲートラインに対する所定のオン電位の設定を開始し、その奇数番目のゲートラインの選択期間の終了後も引き続き、その偶数番目のゲートラインを所定のオン電位に設定し、ソース駆動部が、少なくともその一方のフレームで、第1のゲート駆動部が奇数番目のゲートラインを所定のオン電位に設定する場合に、各ソースラインを、当該奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該奇数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの次の偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定することを特徴とする。

## 【0014】

第1のゲート駆動部が、連続する2つのフレームのうち一方のフレーム（例えば、フレームA）で、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、第2のゲート駆動部が、その一方のフレームで、奇数番目のゲートラインの選択期間の終了前に、当該ゲートラインの次の偶数番目のゲートラインに対する所定のオン電位の設定を開始し、その奇数番目のゲートラインの選択期間の終了後も引き続き、その偶数番目のゲートラインを所定のオン電位に設定し、ソース駆動部が、その一方のフレームで、第1のゲート駆動部が奇数番目のゲートラインを所定のオン電位に設定する場合に、各ソースラインを、当該奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該奇数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの次の偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、第2のゲート駆動部が、連続する2つのフレームのうち他方のフレーム（例えば、フレームB）で、偶数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、第1のゲート駆動部が、他方のフレームで、偶数番目のゲートラインの選択期間の終了前に、当該ゲートラインの前の奇数番目のゲートラインに対する所定のオン電位の設定を開始し、その偶数番目のゲートラインの選択期間の終了後も引き続き、その奇数番目のゲートラインを所定のオン電位に設定し、ソース駆動部が、他方のフレームで、第2のゲート駆動部が偶数番目のゲートラインを所定のオン電位に設定する場合に、各ソースラインを、当該偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該偶数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの前の奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定する構成であってもよい。

## 【0015】

第1のゲート駆動部が、連続する2つのフレームのうち一方のフレーム（例えば、フレームA）で、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、第2のゲート駆動部が、その一方のフレームで、第1のゲート駆動部がゲートラインに対する所定のオン電位の設定を開始する時に、当該ゲートラインの次の偶数番目のゲートラインに対する所定のオン電位の設定を開始し、所定の選択期間の倍の期間、当該偶数番目のゲートラインを所定のオン電位に設定し、第2のゲート駆動部が、連続する2つのフレームのうち他方のフレーム（例えば、フレームB）で、

10

20

30

40

50

偶数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、第1のゲート駆動部が、他方のフレームで、第2のゲート駆動部がゲートラインに対する所定のオン電位の設定を開始する時に、当該ゲートラインの前の奇数番目のゲートラインに対する所定のオン電位の設定を開始し、所定の選択期間の倍の期間、当該奇数番目のゲートラインを所定のオン電位に設定する構成であってもよい。

【0016】

第1のゲート駆動部が、各フレームで、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、第2のゲート駆動部が、各フレームで、奇数番目のゲートラインの選択期間の終了前に、当該ゲートラインの次の偶数番目のゲートラインに対する所定のオン電位の設定を開始し、その奇数番目のゲートラインの選択期間の終了後も引き続き、その偶数番目のゲートラインを所定のオン電位に設定し、ソース駆動部が、各フレームで、第1のゲート駆動部が奇数番目のゲートラインを所定のオン電位に設定する場合に、各ソースラインを、当該奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定し、当該奇数番目のゲートラインの選択期間の終了後に、各ソースラインを、当該ゲートラインの次の偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定する構成であってもよい。

10

【0017】

第1のゲート駆動部が、各フレームで、奇数番目のゲートラインを順に選択し、選択したゲートラインを所定の選択期間、所定のオン電位に設定し、第2のゲート駆動部が、各フレームで、第1のゲート駆動部がゲートラインに対する所定のオン電位の設定を開始する時に、当該ゲートラインの次の偶数番目のゲートラインに対する所定のオン電位の設定を開始し、所定の選択期間の倍の期間、当該偶数番目のゲートラインを所定のオン電位に設定する構成であってもよい。

20

【0018】

ソース駆動部が、ソースラインに接続される接続端子を複数備え、フレームの終了後、次のフレームの開始までの期間内で、各接続端子を短絡させる構成であってもよい。

【発明の効果】

【0019】

本発明によれば、選択期間を短くしたとしても、表示品位の低下を防止することができる。

30

【図面の簡単な説明】

【0020】

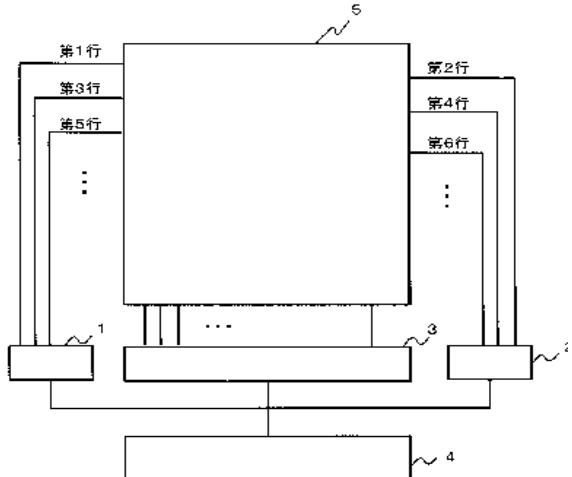

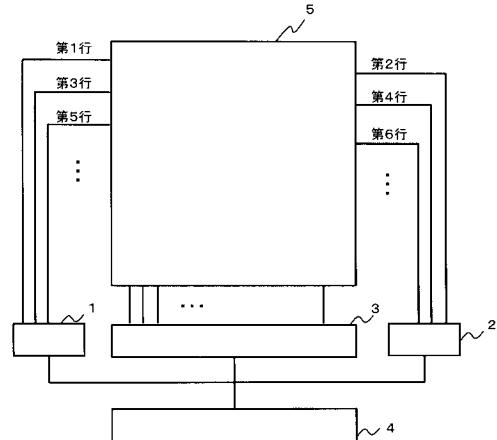

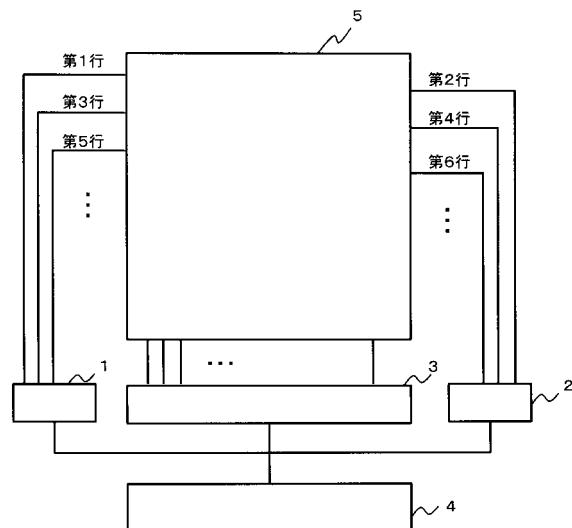

【図1】本発明の液晶表示装置に設けられるTFT液晶パネルの構成例を示す説明図。

【図2】本発明の液晶表示装置の構成例を示すブロック図。

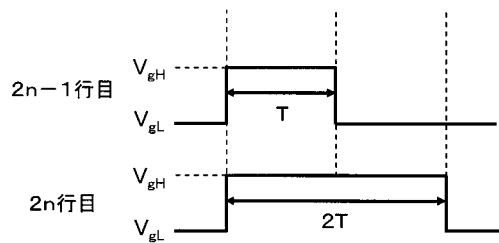

【図3】フレームAで、奇数番目のゲートラインおよび偶数番目のゲートラインを所定のオン電位 $V_{gH}$ に設定する期間の例を示す説明図。

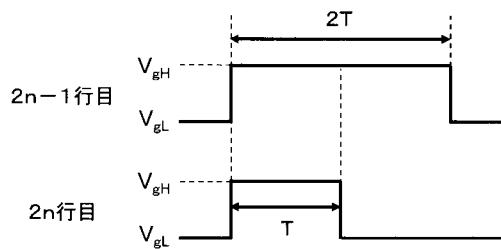

【図4】フレームBで、奇数番目のゲートラインおよび偶数番目のゲートラインを所定のオン電位 $V_{gH}$ に設定する期間の例を示す説明図。

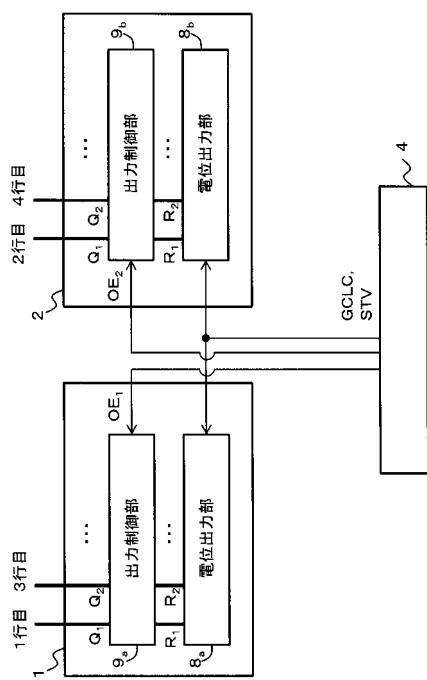

【図5】第1のゲートドライバ1および第2のゲートドライバ2の構成例を示す模式図。

40

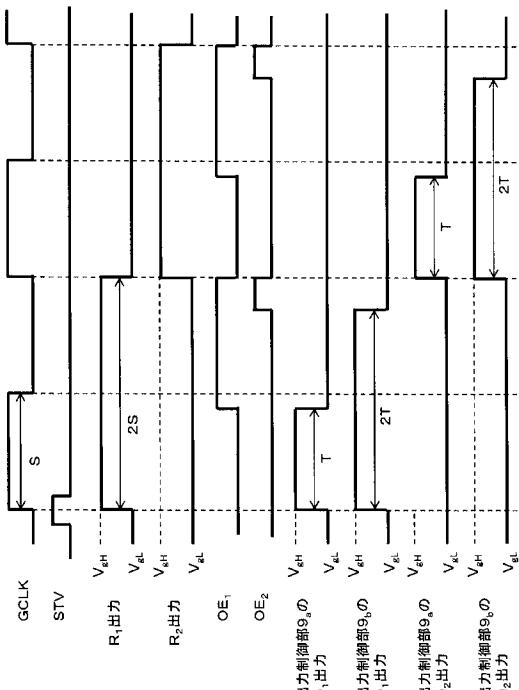

【図6】フレームAでの駆動波形の例を示す説明図。

【図7】フレームBでの駆動波形の例を示す説明図。

【図8】一般的なゲートラインの駆動波形を示す模式図。

【発明を実施するための形態】

【0021】

以下、本発明の実施形態を図面を参照して説明する。以下の説明では、液晶パネルがTFT液晶パネルである場合を例にして説明する。

【0022】

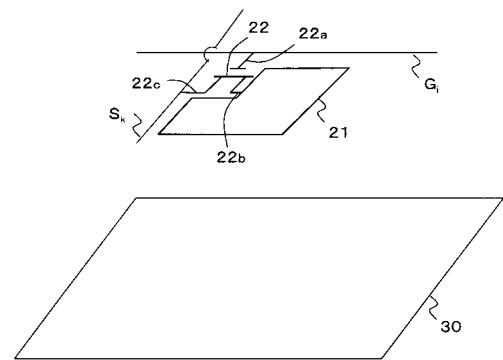

【実施形態1】図1は、本発明の液晶表示装置に設けられるTFT液晶パネルの構成例を示す説明図である。TFT液晶パネルは、画素毎にTFT22と画素電極21を備える。

50

図1では、TFT22と画素電極21を1つだけ図示し、他のTFTおよび画素電極の図

示を省略している。TFT液晶パネルには、各画素電極と対向するコモン電極30が設けられる。本例では、TFT液晶パネルに設けられるコモン電極が1枚である場合を例にして説明する。コモン電極30と各画素電極21とによって液晶層(図示略。)が挟持される。

【0023】

各画素は、マトリクス状に配置される。すなわち、図1に示すTFT22と画素電極21との組み合わせは、マトリクス状に配置される。

【0024】

画素電極21は、TFT22のドレイン22bに接続される。また、TFT22のソース22cは、ソースラインSkに接続され、TFT22のゲート22aは、ゲートラインGiに接続される。ゲートラインGiを介してゲート22aの電位が所定のオン電位に設定されると、ソース22cとドレイン22bとの間が導通状態となり、画素電極21がソースラインSkと等しい電位に設定される。ゲート22aの電位が所定のオフ電位に設定されると、ソース22cとドレイン22bとの間が非導通状態となり、ソースラインSkと画素電極21の間も非導通状態に切り替えられる。所定のオン電位とは、ソース22cとドレイン22bとの間を導通状態にするためのゲート22aの所定電位である。所定のオフ電位とは、ソース22cとドレイン22bとの間を非導通状態にするためのゲート22aの所定電位である。以下、所定のオン電位をVgHと表し、所定のオフ電位をVgLと表すことにする。

10

【0025】

液晶パネルにおいて、マトリクス状に配置された画素電極21の列毎にソースラインが設けられる。また、マトリクス状に配置された画素電極21の行毎にゲートラインが設けられる。図1では、第i行のゲートラインGiおよび第k列のソースラインSkを図示している。

20

【0026】

なお、コモン電極30は、コモン電極ドライバ(図示略)によって一定の電位V0に保たれる。

【0027】

図2は、本発明の液晶表示装置の構成例を示すブロック図である。本発明の液晶表示装置は、液晶パネル5(本実施形態では、TFT液晶パネル)と、第1のゲートドライバ1と、第2のゲートドライバ2と、ソースドライバ3と、タイミングコントローラ4とを備える。

30

【0028】

第1のゲートドライバ1は、タイミングコントローラ4に従って、液晶パネル5の奇数番目のゲートラインを所定のオン電位VgHに設定する。また、第2のゲートドライバ2は、タイミングコントローラ4に従って、液晶パネル5の偶数番目のゲートラインを所定のオン電位VgHに設定する。

【0029】

ソースドライバ3は、液晶パネル5の個々のソースラインに接続される接続端子を複数備える。一つの接続端子には、一本のソースラインが接続される。そして、ソースドライバ3は、タイミングコントローラ4に従って、各ソースラインの電位を設定する。

40

【0030】

タイミングコントローラ4は、第1のゲートドライバ1、第2のゲートドライバ2およびソースドライバ3を制御する。

【0031】

第1のゲートドライバ1、第2のゲートドライバ2およびソースドライバ3は、連続する2つのフレーム(フレームA、Bと記す。)のうち、少なくとも一方のフレーム(ここでは、フレームAとする。)で、タイミングコントローラ4に従って、以下に示す動作を行う。なお、フレームBにおける動作については後述する。

【0032】

50

フレーム A において、第 1 のゲートドライバ 1 は、奇数番目のゲートラインを順に 1 本ずつ選択し、選択したゲートラインを所定の選択期間、所定のオン電位  $V_{g_H}$  に設定する。以下、この選択期間の長さを T とする。第 1 のゲートドライバ 1 は、選択期間 T が経過すると、選択したゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。

【0033】

第 2 のゲートドライバ 2 は、フレーム A で、奇数番目のゲートラインの選択期間の終了前に、そのゲートラインの次の偶数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する。そして、第 2 のゲートドライバ 2 は、その奇数番目のゲートラインの選択期間の終了後も引き続き、その偶数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定し、その後、その偶数番目のゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。

10

【0034】

図 3 は、フレーム A で、奇数番目のゲートラインおよび偶数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定する期間の例を示す説明図である。図 3 および後述の図 4 では、奇数を  $2n - 1$  で表し、偶数を  $2n$  で表す。ただし、 $n = 1, 2, 3, \dots$  である。第 1 のゲートドライバ 1 は、奇数番目のゲートラインを 1 本選択すると、選択期間 T の間、そのゲートラインの電位を所定のオン電位  $V_{g_H}$  に設定する。

【0035】

そして、第 2 のゲートドライバ 2 は、その奇数番目のゲートラインの選択期間の終了前に、そのゲートラインの次の偶数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する。本実施形態では、第 1 のゲートドライバ 1 が奇数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する時に、第 2 のゲートドライバ 2 も、そのゲートラインの次の偶数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する場合を例にして説明する（図 3 参照）。そして、第 2 のゲートドライバ 2 は、その奇数番目のゲートラインの選択期間の終了後も、その偶数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定し、その後、その偶数番目のゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。本実施形態では、第 2 のゲートドライバ 2 が、選択期間 T の倍の期間、その偶数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定する場合を例にして説明する（図 3 参照）。従って、第 2 のゲートドライバ 2 は、偶数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定開始後、 $2T$  の期間が経過すると、その偶数番目のゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。その後、第 1 のゲートドライバ 1 は、次の奇数番目のゲートラインを選択し、第 1 のゲートドライバ 1 および第 2 のゲートドライバ 2 は、同様の動作を繰り返す。

20

【0036】

ソースドライバ 3 は、第 1 のゲートドライバ 1 が奇数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定する場合に、各ソースラインを、その奇数番目のゲートラインの行の各画素の画像データに応じた電位に設定する。そして、ソースドライバ 3 は、その奇数番目のゲートラインの選択期間の終了後に、各ソースラインを、そのゲートラインの次の偶数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定する。従って、例えば  $n = 1$  とすると、ソースドライバ 3 は、各ソースラインの電位を、1 行目の各画素の画像データに応じた電位に設定し、その後、2 行目の各画素の画像データに応じた電位に設定する。このように、奇数番目の行とその次の偶数番目の行との組み合わせに着目した場合、ソースドライバ 3 は、個々のソースラインの電位を、行の並び順に、行の画像データに応じた電位に設定する。よって、フレーム A では、ソースドライバ 3 は、1 行目の画素の画像データ、2 行目の画素の画像データ、3 行目の画素の画像データ、4 行目の画素の画像データ、 $\dots$  の順に、各ソースラインの電位を設定する。

40

【0037】

連続する 2 つのフレーム A, B のうち、もう一方のフレーム B では、第 1 のゲートドライバ 1、第 2 のゲートドライバ 2 およびソースドライバ 3 は、タイミングコントローラ 4 に従って、以下に示す動作を行う。

【0038】

50

フレーム Bにおいて、第 2 のゲートドライバ 2 は、偶数番目のゲートラインを順に 1 本ずつ選択し、選択したゲートラインを選択期間 T の間、所定のオン電位  $V_{g_H}$  に設定する。第 2 のゲートドライバ 2 は、選択期間 T が経過すると、選択したゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。

## 【0039】

第 1 のゲートドライバ 1 は、フレーム B で、偶数番目のゲートラインの選択期間の終了前に、そのゲートラインの前の奇数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する。そして、第 1 のゲートドライバ 1 は、その偶数番目のゲートラインの選択期間の終了後も引き続き、その奇数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定し、その後、その奇数番目のゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。

10

## 【0040】

図 4 は、フレーム B で、奇数番目のゲートラインおよび偶数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定する期間の例を示す説明図である。第 2 のゲートドライバ 2 は、偶数番目のゲートラインを 1 本選択すると、選択期間 T の間、そのゲートラインの電位を所定のオン電位  $V_{g_H}$  に設定する。

## 【0041】

そして、第 1 のゲートドライバ 1 は、その偶数番目のゲートラインの選択期間の終了前に、そのゲートラインの前の奇数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する。本実施形態では、第 2 のゲートドライバ 2 が偶数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する時に、第 1 のゲートドライバ 1 も、そのゲートラインの前の奇数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定を開始する場合を例にして説明する(図 4 参照)。そして、第 1 のゲートドライバ 1 は、その偶数番目のゲートラインの選択期間の終了後も、その奇数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定し、その後、その奇数番目のゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。本実施形態では、第 1 のゲートドライバ 1 が、選択期間 T の倍の期間、その奇数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定する場合を例にして説明する(図 4 参照)。従って、第 1 のゲートドライバ 1 は、奇数番目のゲートラインに対する所定のオン電位  $V_{g_H}$  の設定開始後、2T の期間が経過すると、その奇数番目のゲートラインを所定のオフ電位  $V_{g_L}$  に設定する。その後、第 2 のゲートドライバ 2 は、次の偶数番目のゲートラインを選択し、第 2 のゲートドライバ 2 および第 1 のゲートドライバ 1 は、同様の動作を繰り返す。

20

## 【0042】

ソースドライバ 3 は、第 2 のゲートドライバ 2 が偶数番目のゲートラインを所定のオン電位  $V_{g_H}$  に設定する場合に、各ソースラインを、その偶数番目のゲートラインの行の各画素の画像データに応じた電位に設定する。そして、ソースドライバ 3 は、その偶数番目のゲートラインの選択期間の終了後に、各ソースラインを、そのゲートラインの前の奇数番目のゲートラインに対応する行の各画素の画像データに応じた電位に設定する。従って、例えば  $n = 1$  とすると、ソースドライバ 3 は、各ソースラインの電位を、2 行目の各画素の画像データに応じた電位に設定し、その後、1 行目の各画素の画像データに応じた電位に設定する。このように、奇数番目の行とその次の偶数番目の行との組み合わせに着目した場合、ソースドライバ 3 は、個々のソースラインの電位を、行の並びとは逆順に、行の画像データに応じた電位に設定する。よって、フレーム B では、ソースドライバ 3 は、2 行目の画素の画像データ、1 行目の画素の画像データ、4 行目の画素の画像データ、3 行目の画素の画像データ、・・・の順に、各ソースラインの電位を設定する。

40

## 【0043】

図 5 は、第 1 のゲートドライバ 1 および第 2 のゲートドライバ 2 の構成例を示す模式図である。第 1 のゲートドライバ 1 および第 2 のゲートドライバ 2 は、いずれも、電位出力部 8 と、出力制御部 9 とを備える。各ゲートドライバ 1, 2 には同様の電位出力部 8 が設けられる。また、各ゲートドライバ 1, 2 には同様の出力制御部 9 が設けられる。

## 【0044】

50

電位出力部 8 は、電位出力端  $R_1, R_2, \dots$  を備える。一方の側（図 5 に示す例では左側）から  $i$  番目の電位出力端を  $R_i$  と記す。そして、電位出力部 8 は、タイミングコントローラ 4 に従って、各電位出力端  $R_1, R_2, \dots$  から所定のオン電位  $V_{gH}$  または所定のオフ電位  $V_{gL}$  を出力する。各電位出力部 8 は同様であるが、第 1 のゲートドライバ 1 の電位出力部 8 の各電位出力端  $R_1, R_2, \dots$  は、奇数番目のゲートラインに対応し、第 2 のゲートドライバ 2 の電位出力部 8 の各電位出力端  $R_1, R_2, \dots$  は、偶数番目のゲートラインに対応している。

## 【0045】

出力制御部 9 は、電位出力端  $R_1, R_2, \dots$  に対応する電位出力端  $Q_1, Q_2, \dots$  を備える。第 1 のゲートドライバ 1 の出力制御部 9 の電位出力端  $Q_1, Q_2, \dots$  は、それぞれ順番に奇数番目のゲートラインに接続される。例えば、第 1 のゲートドライバ 1 において、電位出力端  $Q_1$  は、1 行目のゲートラインに接続され、電位出力端  $Q_2$  は、3 行目のゲートラインに接続される。これに対し、第 2 のゲートドライバ 2 の電位出力端  $Q_1, Q_2, \dots$  は、それぞれ順番に偶数番目のゲートラインに接続される。例えば、第 2 のゲートドライバ 2 において、電位出力端  $Q_1$  は、2 行目のゲートラインに接続され、電位出力端  $Q_2$  は、4 行目のゲートラインに接続される。

10

## 【0046】

出力制御部 9 は、電位出力部 8 の電位出力端  $R_i$  が所定のオン電位  $V_{gH}$  を出力した場合、タイミングコントローラ 4 の制御に従って、その電位出力端  $R_i$  に対応する電位出力端  $Q_i$  から、所定のオン電位  $V_{gH}$  または所定のオフ電位  $V_{gL}$  を出力する。従って、電位出力端  $R_i$  から所定のオン電位  $V_{gH}$  が出力されても、電位出力端  $Q_i$  から所定のオン電位  $V_{gH}$  が出力されるとは限らない。

20

## 【0047】

また、出力制御部 9 は、電位出力部 8 の電位出力端  $R_i$  が所定のオフ電位  $V_{gL}$  を出力した場合、その電位出力端  $R_i$  に対応する電位出力端  $Q_i$  から、所定のオフ電位  $V_{gL}$  をそのまま出力する。

30

## 【0048】

以下、第 1 のゲートドライバ 1 の電位出力部 8 および出力制御部 9 を、添え字 “a” を付して表す。また、第 2 のゲートドライバ 2 の電位出力部 8 および出力制御部 9 を、添え字 “b” を付して表す。

## 【0049】

タイミングコントローラ 4 は、電位出力部  $8_a, 8_b$  に対する共通の制御信号としてゲートクロック（以下、GCLC と記す。）およびゲートスタートパルス（以下、STV と記す。）を出力する。また、タイミングコントローラ 4 は、出力制御部  $9_a$  に対する制御信号として、第 1 のアウトプットイネーブル信号（以下、OE<sub>1</sub> と記す。）を出力する。また、タイミングコントローラ 4 は、出力制御部  $9_b$  に対する制御信号として、第 2 のアウトプットイネーブル信号（以下、OE<sub>2</sub> と記す。）を出力する。これらの各制御信号については後述する。

## 【0050】

次に、駆動波形を参照して、本発明の動作を説明する。

40

## 【0051】

図 6 は、フレーム A での駆動波形の例を示す説明図である。タイミングコントローラ 4 は、フレーム A, B に依らずに、GCLK を一定期間毎に、ハイレベル、ローレベルに交互に切り替える。この期間の長さを S とする（図 6 参照）。GCLK は、各電位出力部  $8_a, 8_b$  に、所定のオン電位  $V_{gH}$  を出力する電位出力端を切り替えさせる制御信号である。各電位出力部  $8_a, 8_b$  は、GCLK の立ち上がりエッジ毎に、所定のオン電位  $V_{gH}$  を出力する電位出力端を  $R_i$  から  $R_{i+1}$  に切り替える。また、各電位出力部  $8_a, 8_b$  は、所定のオン電位  $V_{gH}$  を出力している 1 つの電位出力端以外の他の電位出力端から所定のオフ電位  $V_{gL}$  を出力する。

## 【0052】

50

また、STVは、最初の電位出力端R<sub>1</sub>から所定のオン電位V<sub>gH</sub>を出力することを指示するための制御信号である。タイミングコントローラ4は、1つのフレームの開始後に、STVをローレベルからハイレベルに切り替える。各電位出力部8<sub>a</sub>、8<sub>b</sub>は、STVがハイレベルである期間中に、GCLKの立ち上がりエッジを検出すると、最初の電位出力端R<sub>1</sub>から所定のオン電位V<sub>gH</sub>を出力し、他の電位出力端から所定のオフ電位V<sub>gL</sub>を出力する。その後、GCLKの立ち上がりエッジ毎に（換言すれば、2Sの期間が経過する毎に）、所定のオン電位V<sub>gH</sub>を出力する電位出力端を切り替える。また、タイミングコントローラ4は、STVをハイレベルにし、GCLKをハイレベルにした後、STVをローレベルに戻す。そして、そのフレーム内で、STVをローレベルのまま維持する。

## 【0053】

10

OE<sub>1</sub>は、出力制御部9<sub>a</sub>の電位出力端からの出力電位を制御する制御信号である。同様に、OE<sub>2</sub>は、出力制御部9<sub>b</sub>の電位出力端からの出力電位を制御する制御信号である。

## 【0054】

出力制御部9<sub>a</sub>は、OE<sub>1</sub>がローレベルである場合に、電位出力部8<sub>a</sub>の各電位出力端R<sub>1</sub>、R<sub>2</sub>、…から出力された電位を、その各電位出力端R<sub>1</sub>、R<sub>2</sub>、…に対応する各電位出力端Q<sub>1</sub>、Q<sub>2</sub>、…からそのまま出力する。従って、任意の電位出力端R<sub>i</sub>から所定のオン電位V<sub>gH</sub>が出力されている場合、出力制御部9<sub>a</sub>は、電位出力端Q<sub>i</sub>から所定のオン電位V<sub>gH</sub>を出力する。また、出力制御部9<sub>a</sub>は、OE<sub>1</sub>がハイレベルである場合、所定のオン電位V<sub>gH</sub>を出力している電位出力部8<sub>a</sub>の電位出力端（R<sub>i</sub>とする。）に対応する電位出力端Q<sub>i</sub>から、所定のオフ電位V<sub>gL</sub>を出力する。そして、電位出力部8<sub>a</sub>の他の電位出力端からの出力電位は、対応する電位出力端からそのまま出力する。従って、OE<sub>1</sub>がハイレベルである場合、出力制御部9<sub>a</sub>は、各電位出力端から所定のオフ電位V<sub>gL</sub>を出力する。

20

## 【0055】

OE<sub>2</sub>に対する出力制御部9<sub>b</sub>の動作は、OE<sub>1</sub>に対する出力制御部9<sub>a</sub>の動作と同様である。すなわち、出力制御部9<sub>b</sub>は、OE<sub>2</sub>がローレベルである場合に、電位出力部8<sub>b</sub>の各電位出力端R<sub>1</sub>、R<sub>2</sub>、…から出力された電位を、その各電位出力端R<sub>1</sub>、R<sub>2</sub>、…に対応する各電位出力端Q<sub>1</sub>、Q<sub>2</sub>、…からそのまま出力する。また、出力制御部9<sub>b</sub>は、OE<sub>2</sub>がハイレベルである場合、所定のオン電位V<sub>gH</sub>を出力している電位出力部8<sub>b</sub>の電位出力端（R<sub>i</sub>とする。）に対応する電位出力端Q<sub>i</sub>から、所定のオフ電位V<sub>gL</sub>を出力する。そして、電位出力部8<sub>b</sub>の他の電位出力端からの出力電位は、対応する電位出力端からそのまま出力する。

30

## 【0056】

フレームAにおいて、タイミングコントローラ4は、GCLKの立ち上がりエッジから、選択期間Tの間、OE<sub>1</sub>をローレベルに設定し、選択期間Tが終了すると、次のGCLKの立ち上がりエッジまでOE<sub>1</sub>をハイレベルに設定する。次のGCLKの立ち上がりエッジ後も、タイミングコントローラ4は、上記と同様にOE<sub>1</sub>のレベルを設定する（図6参照）。

40

## 【0057】

また、フレームAにおいて、タイミングコントローラ4は、GCLKの立ち上がりエッジから、選択期間Tの2倍の長さの期間（すなわち、期間2Tの間）、OE<sub>2</sub>をローレベルに設定し、その期間2Tが終了すると、次のGCLKの立ち上がりエッジまでOE<sub>2</sub>をハイレベルに設定する。次のGCLKの立ち上がりエッジ後も、タイミングコントローラ4は、上記と同様にOE<sub>2</sub>のレベルを設定する（図6参照）。

## 【0058】

なお、T < Sである。T < Sとする理由は、出力制御部9の電位出力端の電位を、所定のオン電位V<sub>gH</sub>から所定のオフ電位V<sub>gL</sub>に切り替えたとしても、その電位出力端に接続されたゲートラインの電位が実際に所定のオフ電位V<sub>gL</sub>まで低下するのに時間を要するためである。

50

## 【0059】

前述のように各制御信号 GCLK、STV、OE<sub>1</sub>、OE<sub>2</sub> がタイミングコントローラ 4 から出力されることにより、フレーム A では、第 1 のゲートドライバ 1 および第 2 のゲートドライバ 2 は、以下のように動作する。

## 【0060】

第 1 のゲートドライバ 1 の電位出力部 8<sub>a</sub> および第 2 のゲートドライバ 2 の電位出力部 8<sub>b</sub> は、いずれも、STV がハイレベルである期間中に GCLK の立ち上がりエッジを検出すると、次の GCLK の立ち上がりエッジまでの期間中、電位出力端 R<sub>1</sub> から所定のオン電位 V<sub>gH</sub> を出力し、他の電位出力端から所定のオフ電位 V<sub>gL</sub> を出力する。

## 【0061】

10

そして、その GCLK の立ち上がりエッジから、選択期間 T の間、OE<sub>1</sub> はローレベルであり、その後、OE<sub>1</sub> はハイレベルとなる。従って、出力制御部 9<sub>a</sub> は、その選択期間 T の間、電位出力端 Q<sub>1</sub> から所定のオン電位 V<sub>gH</sub> を出力し、その後、所定のオフ電位 V<sub>gL</sub> を出力する。また、その GCLK の立ち上がりエッジから 2T の長さの期間、OE<sub>2</sub> はローレベルであり、その後、OE<sub>2</sub> はハイレベルとなる。出力制御部 9<sub>b</sub> は、その 2T の長さの期間、電位出力端 Q<sub>1</sub> から所定のオン電位 V<sub>gH</sub> を出力し、その後、所定のオフ電位 V<sub>gL</sub> を出力する。

## 【0062】

20

この結果、その GCLK の立ち上がりエッジから選択期間 T の間、液晶パネル 5 の第 1 行のゲートラインの電位は、所定のオン電位 V<sub>gH</sub> となる。また、その GCLK の立ち上がりエッジから 2T の長さの期間、液晶パネル 5 の第 2 行のゲートラインの電位は、所定のオン電位 V<sub>gH</sub> となる。また、その GCLK の立ち上がりエッジから選択期間 T の間、ソースドライバ 3 は、タイミングコントローラ 4 に従って、各ソースラインの電位を、第 1 行の各画素の画像データに応じた電位に設定する。従って、GCLK の立ち上がりエッジから選択期間 T の間に第 1 行の各画素電極は対応するソースラインと等電位になり、各画素電極とコモン電極 30 (図 1 参照) の電位 V<sub>0</sub> との電位差によって、第 1 行の各画素が、第 1 行の画像データに応じた表示状態となる。なお、このとき、第 2 行のゲートラインの電位も所定のオン電位 V<sub>gH</sub> であるので、第 2 行の各画素も、第 1 行の画像データに応じた表示状態となる。

## 【0063】

30

選択期間 T が終了すると、第 1 行のゲートラインの電位は、所定のオフ電位 V<sub>gL</sub> になり、第 1 行の表示状態が維持される。選択期間 T の終了後も、第 2 行のゲートラインの電位は、所定のオン電位 V<sub>gH</sub> に設定されている。そして、選択期間 T が終了後、上記の 2T の長さの期間が終了するまで、ソースドライバ 3 は、タイミングコントローラ 4 に従って、各ソースラインの電位を、第 2 行の各画素の画像データに応じた電位に設定する。よって、選択期間 T が終了後、上記の 2T の長さの期間が終了するまでの間に、第 2 行の各画素電極は対応するソースラインと等電位になり、各画素電極とコモン電極 30 の電位 V<sub>0</sub> との電位差によって、第 2 行の各画素が、第 2 行の画像データに応じた表示状態となる。上記の 2T の長さの期間が終了すると、第 2 行のゲートラインの電位は、所定のオフ電位 V<sub>gL</sub> になり、第 2 行の表示状態が維持される。

## 【0064】

40

電位出力部 8<sub>a</sub> および電位出力部 8<sub>b</sub> は、次の GCLK の立ち上がりエッジを検出すると、所定のオン電位 V<sub>gH</sub> を出力する電位出力端を R<sub>1</sub> から R<sub>2</sub> に切り替える。また、この GCLK の立ち上がりエッジから、選択期間 T の間、OE<sub>1</sub> はローレベルであり、その後、OE<sub>1</sub> はハイレベルとなる。また、その GCLK の立ち上がりエッジから 2T の長さの期間、OE<sub>2</sub> はローレベルであり、その後、OE<sub>2</sub> はハイレベルとなる。この結果、上記の場合と同様に、第 3 行の各画素が、第 3 行の画像データに応じた表示状態となり、第 4 行の各画素が、第 4 行の画像データに応じた表示状態となる。

## 【0065】

以降、同様に、各行が画像データに応じた表示状態となることで、画像が表示される。

50

## 【0066】

図7は、フレームBでの駆動波形の例を示す説明図である。タイミングコントローラ4がGCLK, STVを出力する動作は、フレームAと同様である。従って、各電位出力部8<sub>a</sub>, 8<sub>b</sub>の動作もフレームAと同様である。

## 【0067】

フレームBでは、タイミングコントローラ4は、GCLKの立ち上がりエッジから、選択期間Tの間、OE<sub>2</sub>をローレベルに設定し、選択期間Tが終了すると、次のGCLKの立ち上がりエッジまでOE<sub>2</sub>をハイレベルに設定する。次のGCLKの立ち上がりエッジ後も、タイミングコントローラ4は、上記と同様にOE<sub>2</sub>のレベルを設定する(図7参照)。

10

## 【0068】

また、フレームBにおいて、タイミングコントローラ4は、GCLKの立ち上がりエッジから、選択期間Tの2倍の長さの期間(期間2Tの間)、OE<sub>1</sub>をローレベルに設定し、その期間2Tが終了すると、次のGCLKの立ち上がりエッジまでOE<sub>1</sub>をハイレベルに設定する。次のGCLKの立ち上がりエッジ後も、タイミングコントローラ4は、上記と同様にOE<sub>1</sub>のレベルを設定する(図7参照)。

## 【0069】

このように各制御信号GCLK, STV, OE<sub>1</sub>, OE<sub>2</sub>がタイミングコントローラ4から出力されることにより、フレームBでは、第1のゲートドライバ1および第2のゲートドライバ2は、以下のように動作する。

20

## 【0070】

第1のゲートドライバ1の電位出力部8<sub>a</sub>および第2のゲートドライバ2の電位出力部8<sub>b</sub>は、いずれも、STVがハイレベルである期間中にGCLKの立ち上がりエッジを検出すると、次のGCLKの立ち上がりエッジまでの期間中、電位出力端R<sub>1</sub>から所定のオン電位V<sub>gH</sub>を出力し、他の電位出力端から所定のオフ電位V<sub>gL</sub>を出力する。

## 【0071】

そして、そのGCLKの立ち上がりエッジから、選択期間Tの間、OE<sub>2</sub>はローレベルであり、その後、OE<sub>2</sub>はハイレベルとなる。従って、出力制御部9<sub>b</sub>は、その選択期間Tの間、電位出力端Q<sub>1</sub>から所定のオン電位V<sub>gH</sub>を出力し、その後、所定のオフ電位V<sub>gL</sub>を出力する。また、そのGCLKの立ち上がりエッジから2Tの長さの期間、OE<sub>1</sub>はローレベルであり、その後、OE<sub>1</sub>はハイレベルとなる。出力制御部9<sub>a</sub>は、その2Tの長さの期間、電位出力端Q<sub>1</sub>から所定のオン電位V<sub>gH</sub>を出力し、その後、所定のオフ電位V<sub>gL</sub>を出力する。

30

## 【0072】

この結果、そのGCLKの立ち上がりエッジから選択期間Tの間、液晶パネル5の第2行のゲートラインの電位は、所定のオン電位V<sub>gH</sub>となる。また、そのGCLKの立ち上がりエッジから2Tの長さの期間、液晶パネル5の第1行のゲートラインの電位は、所定のオン電位V<sub>gH</sub>となる。また、そのGCLKの立ち上がりエッジから選択期間Tの間、ソースドライバ3は、タイミングコントローラ4に従って、各ソースラインの電位を、第2行の各画素の画像データに応じた電位に設定する。従って、GCLKの立ち上がりエッジから選択期間Tの間に第2行の各画素電極は対応するソースラインと等電位になり、各画素電極とコモン電極30(図1参照)の電位V<sub>0</sub>との電位差によって、第2行の各画素が、第2行の画像データに応じた表示状態となる。なお、このとき、第1行のゲートラインの電位も所定のオン電位V<sub>gH</sub>であるので、第1行の各画素も、第2行の画像データに応じた表示状態となる。

40

## 【0073】

選択期間Tが終了すると、第2行のゲートラインの電位は、所定のオフ電位V<sub>gL</sub>になり、第2行の表示状態が維持される。選択期間Tの終了後も、第1行のゲートラインの電位は、所定のオン電位V<sub>gH</sub>に設定されている。そして、選択期間Tが終了後、上記の2Tの長さの期間が終了するまで、ソースドライバ3は、タイミングコントローラ4に従つ

50

て、各ソースラインの電位を、第1行の各画素の画像データに応じた電位に設定する。よって、選択期間Tが終了後、上記の2Tの長さの期間が終了するまでの間に、第1行の各画素電極は対応するソースラインと等電位になり、各画素電極とコモン電極30の電位V<sub>0</sub>との電位差によって、第1行の各画素が、第1行の画像データに応じた表示状態となる。上記の2Tの長さの期間が終了すると、第1行のゲートラインの電位は、所定のオフ電位V<sub>g\_L</sub>になり、第1行の表示状態が維持される。

【0074】

電位出力部8<sub>a</sub>および電位出力部8<sub>b</sub>は、次のGCLKの立ち上がりエッジを検出すると、所定のオン電位V<sub>g\_H</sub>を出力する電位出力端をR<sub>1</sub>からR<sub>2</sub>に切り替える。また、このGCLKの立ち上がりエッジから、選択期間Tの間、OE<sub>2</sub>はローレベルであり、その後、OE<sub>2</sub>はハイレベルとなる。また、そのGCLKの立ち上がりエッジから2Tの長さの期間、OE<sub>1</sub>はローレベルであり、その後、OE<sub>1</sub>はハイレベルとなる。この結果、上記の場合と同様に、第4行の各画素が、第4行の画像データに応じた表示状態となり、第3行の各画素が、第3行の画像データに応じた表示状態となる。

10

【0075】

以降、同様に、各行が画像データに応じた表示状態となることで、画像が表示される。

【0076】

そして、タイミングコントローラ4、第1のゲートドライバ1、第2のゲートドライバ2およびソースドライバ3は、フレームAでの動作と、フレームBでの動作を、フレーム毎に切り替えて実行する。

20

【0077】

本実施形態によれば、フレームAでは、ソースドライバ3が、各ソースラインの電位を、偶数番目の行の各画素の画像データに応じた電位に設定するときに、既にその偶数番目の行のゲートラインに対する所定のオン電位V<sub>g\_H</sub>の設定が開始されている。従って、液晶パネル5の高解像度化のため、GCLKの切り替え周期S(図6参照)を短くする必要があり、それに伴い、選択期間Tを短くする必要がある場合であっても、偶数番目の行のゲートラインに対する所定のオン電位V<sub>g\_H</sub>の設定期間を選択期間Tよりも長くとることができ、表示品位の低下を防止することができる。

【0078】

同様に、フレームBでは、ソースドライバ3が、各ソースラインの電位を、奇数番目の行の各画素の画像データに応じた電位に設定するときに、既にその奇数番目の行のゲートラインに対する所定のオン電位V<sub>g\_H</sub>の設定が開始されている。従って、選択期間Tを短くする必要がある場合であっても、奇数番目の行のゲートラインに対する所定のオン電位V<sub>g\_H</sub>の設定期間を選択期間Tよりも長くとることができ、表示品位の低下を防止することができる。

30

【0079】

【実施形態2】第2の実施形態の構成は、図2に示す構成と同様である。また、第1のゲートドライバ1および第2のゲートドライバ2の構成も、図5に示す構成と同様である。

【0080】

ただし、第2の実施形態では、タイミングコントローラ4、第1のゲートドライバ1、第2のゲートドライバ2およびソースドライバ3は、各フレームで、前述のフレームAでの動作を行う。この動作については、第1の実施形態で既に説明しているので、ここでは説明を省略する。従って、第2の実施形態の液晶表示装置は、各フレームで共通の動作を行い、第1の実施形態で示したフレームBでの動作は行わない。

40

【0081】

第2の実施形態においても、ソースドライバ3が、各ソースラインの電位を、偶数番目の行の各画素の画像データに応じた電位に設定するときに、既にその偶数番目の行のゲートラインに対する所定のオン電位V<sub>g\_H</sub>の設定が開始されている。よって、選択期間Tを短くする必要がある場合であっても、偶数番目の行のゲートラインに対する所定のオン電位V<sub>g\_H</sub>の設定期間を選択期間Tよりも長くとることができ、表示品位の低下を防止する

50

ことができる。

【0082】

また、上記の各実施形態において、個々の画素の極性をフレーム毎に反転させることができてほしい。個々の画素の極性をフレーム毎に反転させる方法として、列ライン反転駆動がある。列ライン反転駆動を採用する場合、個々のソースラインの電位は、新たなフレーム開始時に、 $V_0$ より低い電位から $V_0$ より高い電位に、あるいは、 $V_0$ より高い電位から $V_0$ より低い電位に変化する。このため、消費電力が大きくなる。このような消費電力の増加を抑えるために、ソースドライバ3は、フレームの終了後、次のフレームの開始までの期間内で、個々のソースラインに接続される各接続端子同士を短絡させることができてほしい。フレーム間で、ソースドライバ3が、ソースラインに接続される各接続端子同士を短絡させると、各ソースラインの電位は、 $V_0$ に近い電位になる。よって、ソースドライバ3は、新たなフレームの開始時に、個々のソースラインの電位を、約 $V_0$ から、 $V_0$ より高い電位に変化させたり、約 $V_0$ から、 $V_0$ より低い電位に変化させたりすればよい。従って、列ライン反転駆動を採用する場合に、消費電力を抑えることができる。

10

【産業上の利用可能性】

【0083】

本発明は、奇数番目の行のゲートラインに対応するゲート駆動部と、偶数番目の行のゲートラインに対応するゲート駆動部とを備える液晶表示装置に好適に適用される。

【符号の説明】

【0084】

20

- 1 第1のゲートドライバ

- 2 第2のゲートドライバ

- 3 ソースドライバ

- 4 タイミングコントローラ

- 5 液晶パネル

- 8a, 8b 電位出力部

- 9a, 9b 出力制御部

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図6】

【図7】

【図8】

## フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 2 3 C |

|             | G 0 9 G | 3/20 6 4 1 C |

|             | G 0 9 G | 3/20 6 2 1 A |

|             | G 0 9 G | 3/20 6 2 3 D |

|             | G 0 2 F | 1/133 5 5 0  |

|                |                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2014224916A</a>                                                                                                                                                                          | 公开(公告)日 | 2014-12-04 |

| 申请号            | JP2013104211                                                                                                                                                                                           | 申请日     | 2013-05-16 |

| [标]申请(专利权)人(译) | 京瓷显示器株式会社                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 京瓷显示器有限公司                                                                                                                                                                                              |         |            |

| [标]发明人         | 権藤 賢二                                                                                                                                                                                                  |         |            |

| 发明人            | 権藤 賢二                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/20 G09G3/36 G02F1/133                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/20.622.C G09G3/36 G09G3/20.622.M G09G3/20.622.D G09G3/20.623.U G09G3/20.623.C G09G3/20.641.C G09G3/20.621.A G09G3/20.623.D G02F1/133.550                                                         |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZC24 2H193/ZC34 2H193/ZF24 5C006/AA16 5C006/AC24 5C006/AC28 5C006 /AF42 5C006/AF43 5C006/AF44 5C006/BB16 5C006/FA12 5C080/AA10 5C080/BB05 5C080/DD08 5C080/FF11 5C080/JJ02 5C080/JJ04 |         |            |

| 代理人(译)         | 岩冬树<br>盐川正人                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                              |         |            |

### 摘要(译)

解决的问题：提供一种即使缩短选择时间也能够防止显示质量下降的液晶显示装置。第一栅极驱动器1顺序地选择奇数号的栅极线，并且在预定的选择时段内将所选择的栅极线设置为预定的ON电位。第二栅极驱动器2在奇数栅极线的选择周期的结束之前开始为奇数栅极线的下一个偶数栅极线设置预定的ON电势，并且即使在选择时段结束之后，偶数编号的栅极线也被设置为预定的导通电位。[选择图]图2