(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-156326

(P2013-156326A)

(43) 公開日 平成25年8月15日(2013.8.15)

|                             |            |                   |

|-----------------------------|------------|-------------------|

| (51) Int.Cl.                | F 1        | テーマコード (参考)       |

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36  | 2 H 1 9 3         |

| <b>G09G 3/34</b> (2006.01)  | G09G 3/34  | J 5 C 0 0 6       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 6 4 2 C 5 C 0 8 0 |

| <b>H03K 7/08</b> (2006.01)  | H03K 7/08  | A                 |

| <b>G02F 1/133</b> (2006.01) | G02F 1/133 | 5 3 5             |

審査請求 未請求 請求項の数 10 O L (全 18 頁) 最終頁に続く

|           |                            |          |                                                      |

|-----------|----------------------------|----------|------------------------------------------------------|

| (21) 出願番号 | 特願2012-15059 (P2012-15059) | (71) 出願人 | 302020207<br>株式会社ジャパンディスプレイセントラル<br>埼玉県深谷市幡羅町一丁目9番地2 |

| (22) 出願日  | 平成24年1月27日 (2012.1.27)     | (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊                               |

|           |                            | (74) 代理人 | 100159651<br>弁理士 高倉 成男                               |

|           |                            | (74) 代理人 | 100091351<br>弁理士 河野 哲                                |

|           |                            | (74) 代理人 | 100088683<br>弁理士 中村 誠                                |

|           |                            | (74) 代理人 | 100109830<br>弁理士 福原 淑弘                               |

|           |                            | (74) 代理人 | 100075672<br>弁理士 峰 隆司                                |

|           |                            |          | 最終頁に続く                                               |

(54) 【発明の名称】 液晶表示装置のバックライト駆動装置

## (57) 【要約】 (修正有)

【課題】外部垂直同期信号の位相変動に影響を受け難く、結果としてバックライトの輝度を安定化する事ができる液晶表示装置のバックライト駆動装置を提供する。

【解決手段】バックライトにパルス幅変調パルス列に基づいて生成した電圧を供給するバックライト駆動装置において、分周パルス生成手段が、フレーム周期のフレーム基準信号に同期して動作開始し、パルス幅変調パルスのパルス列の1周期毎にパルスを持つ分周パルス列を生成する。パルス幅変調パルス発生手段が、フレーム基準信号に同期して動作開始し、分周パルス列のパルス入力毎に内部クロックの計数を開始し、計数値がパルス幅設定値に対応する値の期間のパルス幅を持つパルス幅変調パルスを出力する。制限手段が、パルス幅変調パルス発生手段から出力されるパルス幅変調パルスの1フレームの時間当たりのパルス数の出力数を所定数に抑制するためにパルス幅変調パルス発生手段に制限信号を与える。

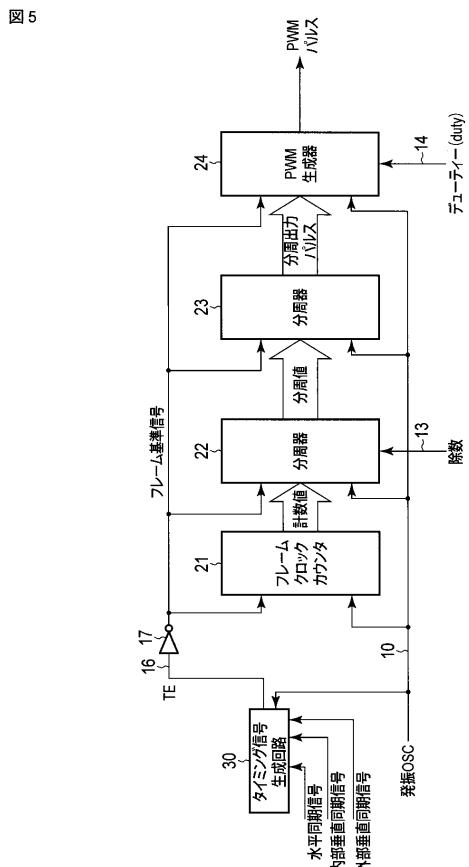

【選択図】図5

図5

**【特許請求の範囲】****【請求項 1】**

液晶パネルのバックライトにパルス幅変調パルス列に基づいて生成した点灯時間制御信号または点灯制御電圧を供給するバックライト駆動装置において、

フレーム同期したフレーム基準信号の1周期で内部クロックを計数し、計数したフレーム期間計数値を除数で割り算して分周値を生成し、この分周値で前記内部クロックを分周してパルス幅変調パルスの1周期毎に発生する分周出力パルスを出力する分周出力パルス生成手段と、

前記フレーム基準信号に同期してリセットし、前記分周出力パルスのパルス入力毎に前記内部クロックの計数を開始して計数値がパルス幅設定値に対応する値となるまで計数し、計数期間のパルス幅を持つ前記パルス幅変調パルスを出力するパルス幅変調パルス発生手段と、

前記パルス幅変調パルス発生手段から出力される前記パルス幅変調パルスの1フレーム期間当たり出力パルス数を所定数に設定するために前記パルス幅変調パルス発生手段に制限信号を与える制限手段を有する

バックライト駆動装置。

**【請求項 2】**

前記制限手段は、前記制限信号として前記フレーム基準信号を採用しており、前記フレーム基準信号は、前記液晶パネルに入力される映像信号の表示期間に位相が同期した期間に発生する信号である請求項1記載のバックライト駆動装置。

**【請求項 3】**

前記制限手段は、前記制限信号として、前記分周出力パルス生成手段が前記分周値を得るために使用した前記除数を採用する請求項1記載のバックライト駆動装置。

**【請求項 4】**

分周出力パルス生成手段は、前記フレーム基準信号の1周期毎に順次得られる前記フレーム期間計数値としては、最小値を採用している請求項3記載のバックライト駆動装置。

**【請求項 5】**

前記分周出力パルス生成手段は、前記分周値を得るために前記除数を補正した補正除数を採用し、前記制限手段は、前記制限信号として、前記除数を採用する請求項1記載のバックライト駆動装置。

**【請求項 6】**

液晶パネルのバックライトにパルス幅変調パルス列に基づいて生成した点灯時間制御信号または点灯制御電圧を供給するバックライト駆動装置において、

フレーム同期したフレーム基準信号の1周期で内部クロックを計数し、計数したフレーム期間計数値を除数で割り算して分周値を生成し、この分周値で前記内部クロックを分周してパルス幅変調パルスの1周期毎に発生する分周出力パルスを出力する分周出力パルス生成手段と、

前記フレーム基準信号に同期してリセットし、前記分周出力パルスのパルス入力毎に前記内部クロックの計数を開始して計数値がパルス幅設定値となるまで計数し、計数期間のパルス幅を持つ前記パルス幅変調パルスを出力するパルス幅変調パルス発生手段と、

前記フレーム基準信号を、前記液晶パネルに入力される映像信号の表示期間に位相が同期した期間に発生する基準信号出力回路と

を備えるバックライト駆動装置。

**【請求項 7】**

液晶パネルのバックライトにパルス幅変調パルス列に基づいて生成した電圧を供給するバックライト駆動装置において、

フレーム同期したフレーム基準信号の1周期で内部クロックを計数し、計数したフレーム期間計数値を除数で割り算して分周値を生成し、この分周値で前記内部クロックを分周してパルス幅変調パルスの1周期毎に発生する分周出力パルスを出力する分周出力パルス生成手段と、

10

20

30

40

50

前記フレーム基準信号に同期してリセットし、前記分周出力パルスのパルス入力毎に前記内部クロックの計数を開始して計数値がパルス幅設定値となるまで計数し、計数期間のパルス幅を持つ前記パルス幅変調パルスを出力するパルス幅変調パルス発生手段と、

前記パルス幅変調パルスの1フレーム期間当たり出力パルス数を所定数に設定するためには、制限信号として前記除数を前記パルス幅変調パルス発生手段に与える制限手段とを備えるバックライト駆動装置。

#### 【請求項8】

分周出力パルス生成手段は、前記フレーム基準信号の1周期毎に順次得られる前記フレーム期間計数値としては、最小値を採用している請求項7記載のバックライト駆動装置。

#### 【請求項9】

液晶パネルのバックライトにパルス幅変調パルス列に基づいて生成した電圧を供給するバックライト駆動装置において、

フレーム同期したフレーム基準信号の1周期で内部クロックを計数し、計数したフレーム期間計数値を補正除数で割り算して分周値を生成し、この分周値で前記内部クロックを分周してパルス幅変調パルスの1周期毎に発生する分周出力パルスを出力する分周出力パルス生成手段と、

前記フレーム基準信号に同期してリセットし、前記分周出力パルスのパルス入力毎に前記内部クロックの計数を開始して計数値がパルス幅設定値となるまで計数し、計数期間のパルス幅を持つ前記パルス幅変調パルスを出力するパルス幅変調パルス発生手段と、

前記パルス幅変調パルスの1フレーム期間当たり出力パルス数を所定数に設定するためには、制限信号として前記補正除数の元となる除数を前記パルス幅変調パルス発生手段に与える制限手段と

を備えるバックライト駆動装置。

#### 【請求項10】

前記除数は、フレーム周波数の倍数の指定されるパルス数よりも前記パルス幅変調パルスが多く出力されない値である請求項1又は7又は9記載のバックライト駆動装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の実施形態は、液晶表示装置のバックライト駆動装置に関する。

##### 【背景技術】

##### 【0002】

光透過型液晶表示装置はバックライトと液晶パネルを有する。液晶パネルの液晶層の液晶分子の傾きは、画像信号で制御される。これによりバックライトから液晶パネルに照射されている透過光量が、液晶分子の傾きにより変化し、結果として、液晶パネル上に画像表示を得ることができる。

##### 【0003】

透過型液晶表示装置は、画像表示を行う場合には常時バックライトを点灯させておく必要がある。このため、液晶表示装置の消費電力の中でもバックライトにより消費される電力の割合が殆どを占める。バッテリーにより駆動されるモバイル機器の場合、機器の使用時間を延ばすためバックライトによる消費電力を低減することが重要である。

##### 【0004】

バックライトの消費電力を低減するために、バックライト駆動装置によってバックライトの輝度を抑制する方法がある。

##### 【0005】

バックライト駆動装置として、パルス幅変調パルス（PWMパルス）とこれよりも周波数が高いクロックパルス（インバータパルスと称される場合もある）を利用する技術がある。即ち、バックライト駆動装置は、PWMパルスによりクロックパルスの連続出力期間を制御して、クロックパルスをバックライトに供給している。したがってPWMパルスのパルス幅が制御されると、クロックパルスの連続出力期間が制御され、結果としてバック

10

20

30

40

50

ライトの輝度も制御される。

【0006】

上記したように、バックライトの輝度を低い輝度に制御可能なバックライト駆動装置は、一方では、バックライトの輝度の変動を抑え、安定化させることが要望される。バックライトの輝度を安定化することで、画質の品位を維持するためである。バックライトの輝度を安定化させるために、上記したインバータパルスの周波数を高い周波数で意図的に変化させて、バックライトの輝度変化が目立たないようにする技術がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2009-300690号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0008】

バックライト駆動装置は、表示する絵柄、すなわち液晶表示装置に入力される画像信号のフレームに同期して動作を行う必要がある。

【0009】

液晶表示装置の液晶パネルで表示される画像の画像信号としては、次の2種類がある。例えば液晶表示装置の外部から液晶パネルへ取り込まれる画像信号と、液晶表示装置の内部のメモリから液晶パネルへ取り込まれる画像信号とがある。

20

【0010】

外部から取り込まれる画像信号は、外部垂直同期信号に同期している。このために外部から取り込まれる画像信号が液晶パネルで表示されるときは、バックライト駆動装置も外部垂直同期信号に同期して動作する必要がある。これに対して、液晶表示装置内部のメモリから液晶パネルへ取り込まれる画像信号が表示されるときは、バックライト駆動装置は内部垂直同期信号に同期して動作する必要がある。

【0011】

内部垂直同期信号は、液晶表示装置内部に設けられているクロック発生器から出力される内部クロックに基づいて生成されている。したがって、内部垂直同期信号と内部クロックは同期している。また、内部垂直同期信号に同期するバックライト駆動装置が生成しているPWMパルスも、内部クロックを用いて生成されているので、PWMパルスと内部垂直同期信号も同期している。

30

【0012】

しかし、外部垂直同期信号が使用されるときは、クロック発生器から出力されている内部クロックと外部垂直同期信号とは非同期である。また外部垂直同期信号は位相変動を伴うことがある。このために、バックライト駆動装置が外部垂直同期信号に同期して動作し、内部クロックを計数することでPWMパルスを作成した場合、PWMパルスの垂直同期信号期間内のパルス数が不安定となる。このことはバックライトの輝度が不安定となることを意味する。このような場合は、画質の品位が低下する。

40

【0013】

そこで本実施形態では、外部垂直同期信号の位相変動に影響を受けにくく、結果的としてバックライトの輝度を安定化することができる液晶表示装置のバックライト駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0014】

本実施形態では、液晶パネルのバックライトにパルス幅変調パルス列に基づいて生成した電圧を供給するバックライト駆動装置において、分周パルス生成手段が、フレーム周期のフレーム基準信号に同期して動作開始し、前記パルス幅変調パルスのパルス列の1周期毎にパルスを持つ分周パルス列を生成する。パルス幅変調パルス発生手段が、前記フレーム基準信号に同期して動作開始し、前記分周パルス列のパルス入力毎に内部クロックの計

50

数を開始し、計数値がパルス幅設定値に対応する値となるまでの期間のパルス幅を持つ前記パルス幅変調パルスを出力する。制限手段が、前記パルス幅変調パルス発生手段から出力される前記パルス幅変調パルスの1フレームの時間当たりのパルス数の出力個数を所定数に抑制するために前記パルス幅変調パルス発生手段に制限信号を与える。

**【図面の簡単な説明】**

**【0015】**

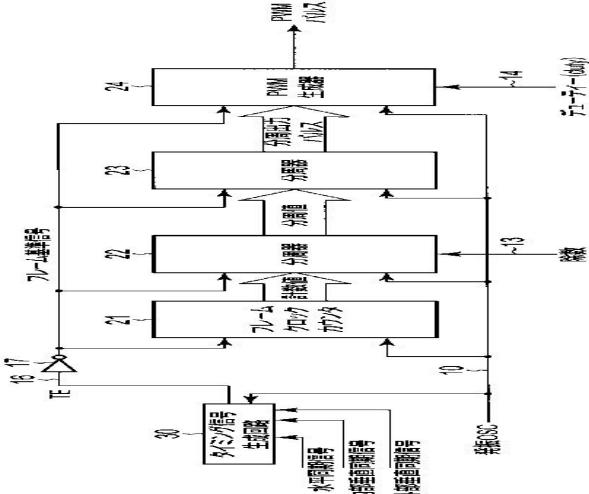

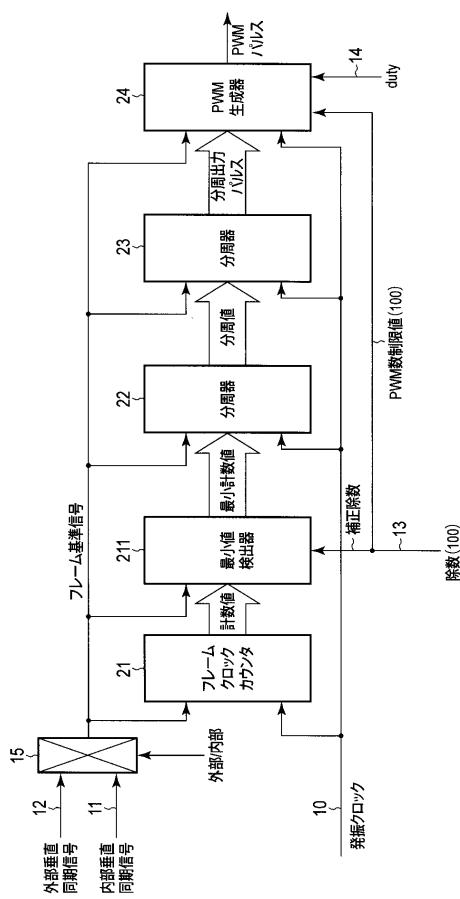

【図1】実施形態の前提となるPWMパルス発生回路の一例を示すブロック図である。

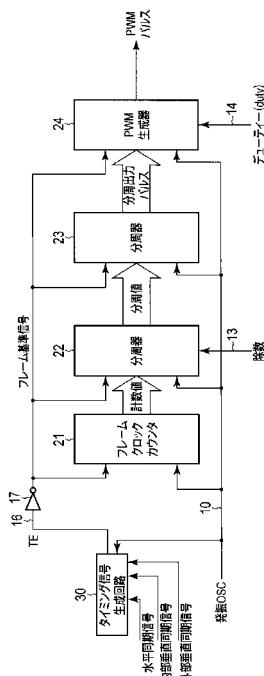

【図2】図1のPWMパルス発生回路の動作例を説明するために示した動作タイミングチャートである。

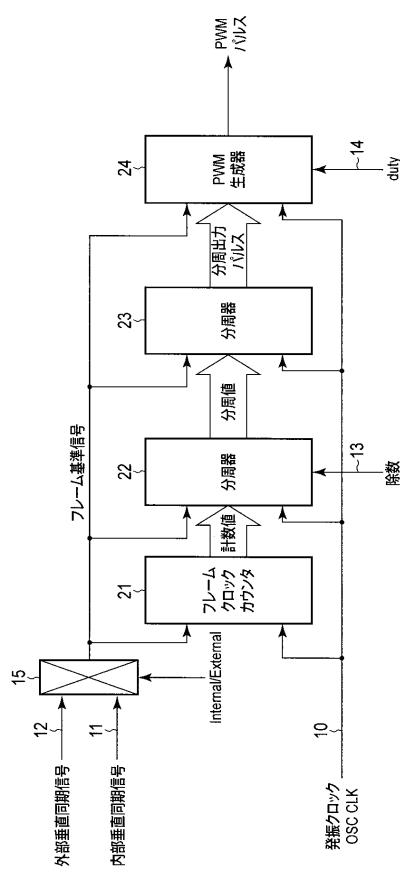

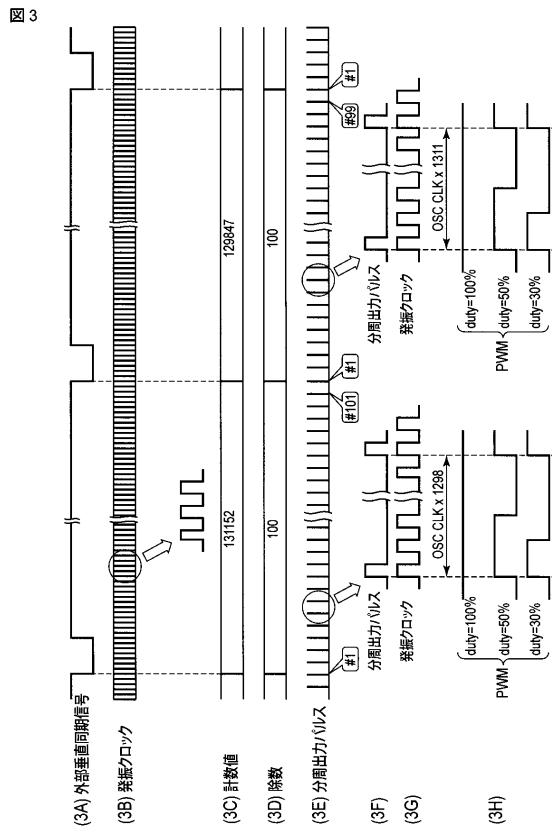

【図3】図1のPWMパルス発生回路の他の動作例を説明するために示した動作タイミングチャートである。10

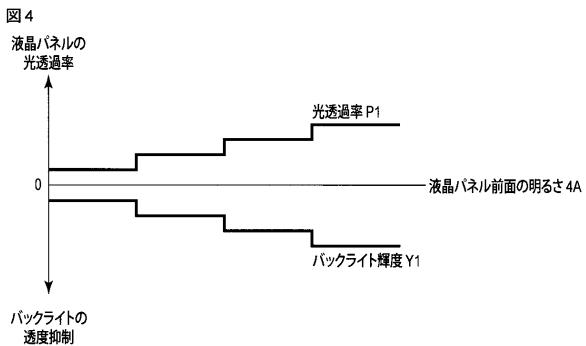

【図4】液晶表示装置において、バックライトのバックライト輝度と液晶パネルの光透過率との関係の一例を示す図である。

【図5】本開示における液晶表示装置のバックライト駆動装置の一実施形態を示すブロック図である。

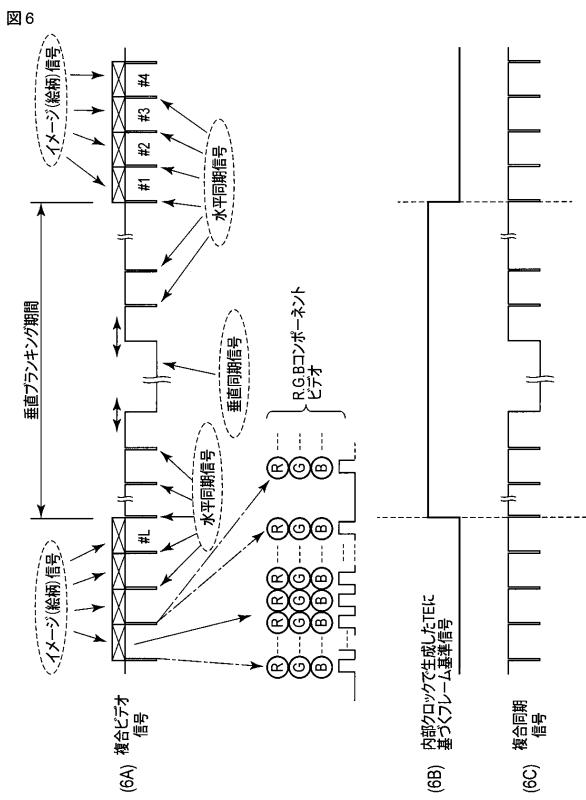

【図6】図5のバックライト駆動装置の動作の要点を説明するために示した動作タイミングチャートである。

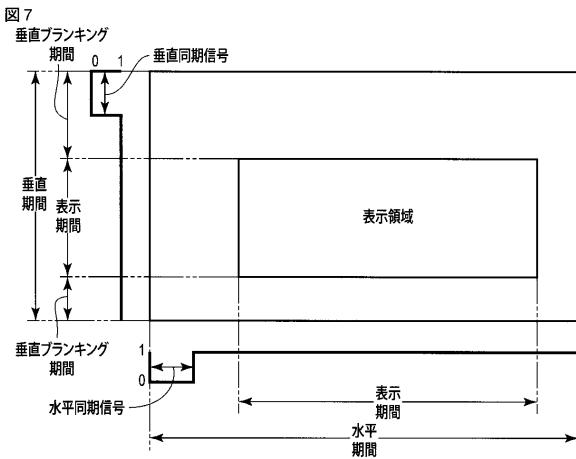

【図7】図5のバックライト駆動装置の動作を液晶パネルの表示領域を参照して説明する図である。

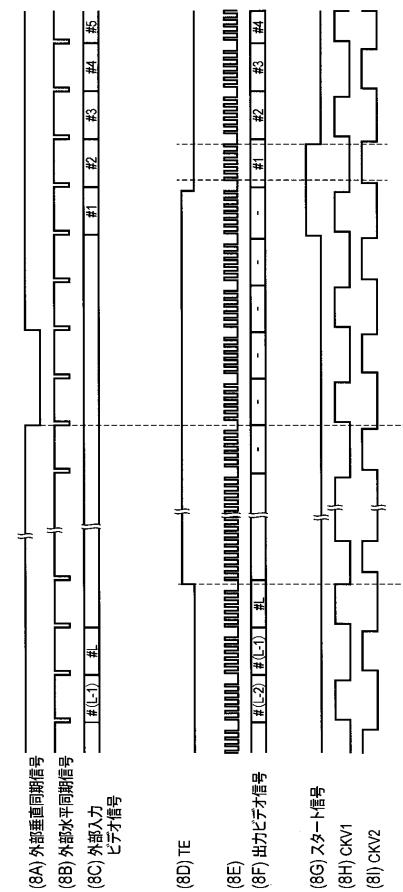

**【図8】**液晶表示装置に使用される液晶パネル駆動回路の動作を説明する図である。

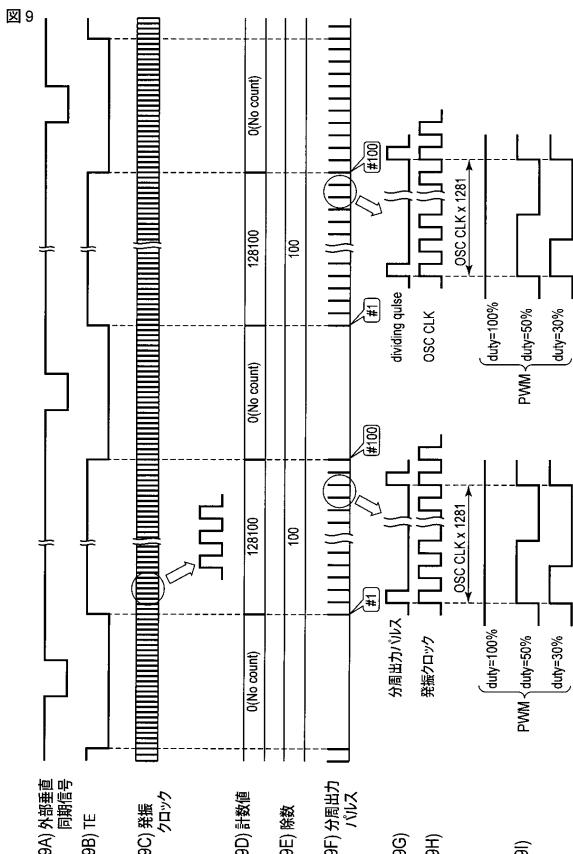

【図9】図5のバックライト駆動装置の動作例を説明するために示した動作タイミングチャートである。

【図10】本開示における液晶表示装置のバックライト駆動装置の他の実施形態を示すブロック図である。

【図11】図10のバックライト駆動装置の動作例を説明するために示した動作タイミングチャートである。

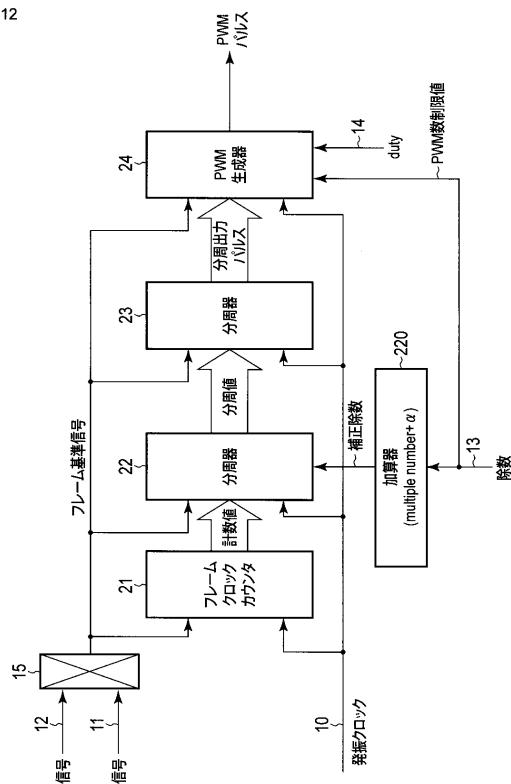

【図12】本開示における液晶表示装置のバックライト駆動装置のさらに他の実施形態を示すブロック図である。

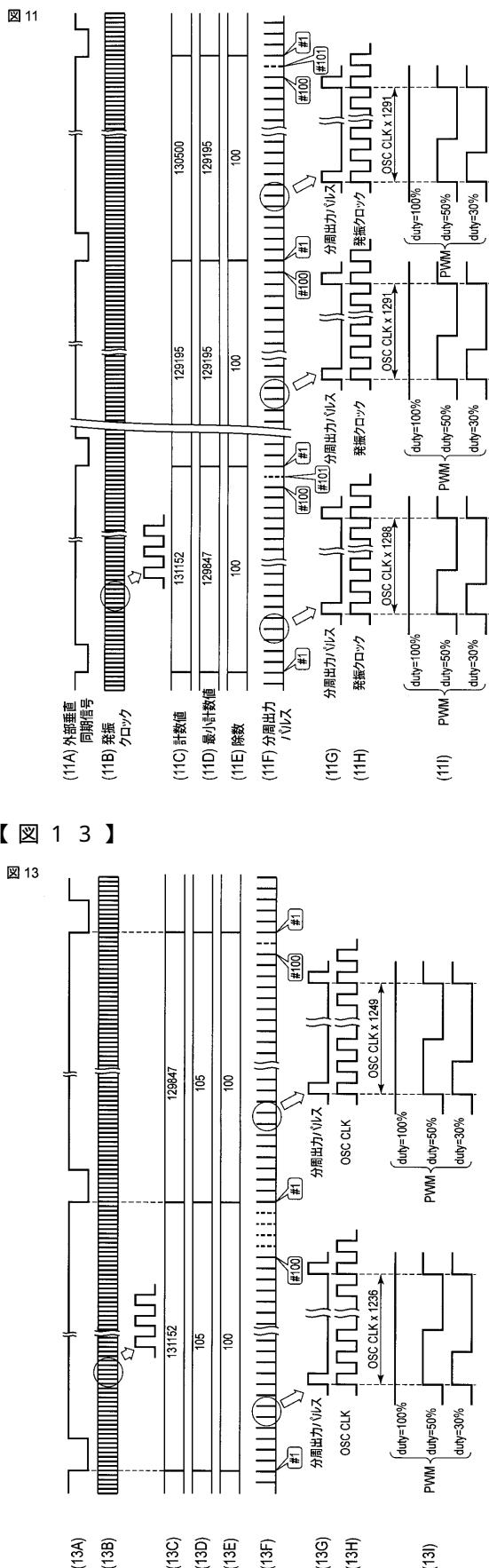

【図13】図12のバックライト駆動装置の動作例を説明するために示した動作タイミングチャートである。30

**【発明を実施するための形態】**

**【0016】**

以下、実施の形態について図面を参照して説明する。まず図1を参照して一実施形態の前提となるPWMパルス発生回路を説明する。

**【0017】**

図1に示すPWMパルス発生回路は、発振クロック(OSC CLK)の入力端子10、垂直同期周波数の内部垂直同期信号(Internal VSYNC)の入力端子11及び外部垂直同期信号(External VSYNC)の入力端子12を有する。入力端子11、12は、セレクタ15に接続されており、何れか一方の同期信号がセレクタ15で選択され、フレーム同期信号(Frame sync signal)(この信号をフレーム基準信号と称しても良い)として出力される。40

**【0018】**

フレーム基準信号は、フレームクロックカウンタ21、分周器(ディバイダと称しても良い)22、分周器(ディバイダと称しても良い)23、PWMパルス生成器24に入力される。また先の発振クロック(OSC CLK)も、フレームクロックカウンタ21、分周器22、分周器23、PWMパルス生成器24に入力される。

**【0019】**

フレームクロックカウンタ21は、フレーム同期信号(Frame sync signal)でリセットされ、1フレームの期間、発振クロック(OSC CLK)をカウントする。つまりフレームクロックカウンタ21は、1フレーム期間(1フレーム時間と称しても良い)を発振クロック(OSC CLK)の計数値に変換することができる。この計数値をフレーム期間計数値と50

称してもよい。フレームクロックカウンタ21からのフレーム期間計数値は、分周器22に入力される。

#### 【0020】

分周器22には、入力端子13から除数(divisor)が与えられる。分周器22は、1フレーム計数値を除数で割り算した結果の値(分割値或いはディバイディング数と称しても良い)を分周器23に送る。

#### 【0021】

分周器23は、ディバイディング数で発振クロック(OSC CLK)を分周し、分周出力パルスを出力する。分周出力パルスのパルス列は、PWM生成器24に入力する。

#### 【0022】

PWM生成器24は、分周出力パルスに同期して、発振クロック(OSC CLK)を取り込む。そしてこのPWM生成器24は、端子14から入力するパルス幅制御信号(duty)に基づいて、分周出力パルスの1周期期当たりに、カウントすべきクロックの数を決定する。PWM生成器24は、第1の分周出力パルスが入力したときクロックの計数を開始するとともに、PWMパルスを立ち上げる。そして、パルス幅制御信号で決められた数のクロックを計数したとき、PWMパルスを立ち下げる。次の第2の分周パルスが入力したとき、またクロックの計数を開始するとともに、PWMパルスを立ち上げる。そして、パルス幅制御信号で決められた数のクロックを計数したとき、PWMパルスを立ち下げる。このような動作を繰り返すことでPWMパルスの連続性(パルス列)を得ている。

#### 【0023】

なおパルス幅制御信号(duty)としては、PWM生成器24の構成に応じて、各種の供給方法が可能である。

#### 【0024】

分周出力パルスの1周期期当たりにカウントされるクロックの数がPWMパルスのディユーティーに対応する。したがって、パルス幅制御信号(duty)を変化させることにより、分周出力パルスの1周期期当たりに出力するクロック数が変化し、つまりPWMパルスのディユーティーが変化し、バックライトの点灯時間または点灯電圧が制御される。

#### 【0025】

図2は、上記した回路の動作を示すタイミングチャートである。図2(2A)は、フレーム基準信号であり、図2(2B)は、発振クロック(OSC CLK)である。図2(2C)は、分周器23から出力される1フレーム期間計数値である。図の例は、発振クロック(OSC CLK)の周波数が7.83MHzで、フレーム周波数が60Hzとした場合の例である。その場合、フレームクロックカウンタ21からの1フレーム期間計数値、つまり1フレーム期間のOSC CLK計数値は $(7830000/60) = 130500$ となる。図2(2D)は、入力端子13にセットされている除数(divisor)を示している。この例では、除数は100である。したがって、分周器22から出力される分周値は、 $(130500/100) = 1305$ として出力される。

#### 【0026】

この分周値は、次の分周器23に入力される。分周器23は、発振クロック(OSC CLK)を1305で分周して、分周出力パルスのパルス列を出力する。図2(2E)が分周出力パルスのパルス列である。図2(2F)は分周出力パルスを拡大して示している。

#### 【0027】

この分周出力パルスは、PWM生成器24に入力される。分周出力パルスは、PWMパルスの1周期を設定する。PWM生成器24は、図2(2F)、図2(2G)、図2(2H)に示すように、分周出力パルスの立ち上がりに同期してPWMパルスを立ち上げる(ハイレベルにする)。そして、パルス幅制御信号(duty)により設定された値だけクロックをカウントすると、PWMパルスを立ち下げる(ローレベルにする)。従って、パルス幅制御信号(duty)を変えることにより、PWMパルスのデューティー(パルス幅)を変化させることができる。このPWMパルスのパルス幅によってバックライトの点灯時間が制御される。すなわち、パルス幅が広いほどバックライトの輝度は明るくなる。

#### 【0028】

10

20

30

40

50

上記した回路において、フレーム周期のフレーム基準信号として、内部垂直同期信号が用いられる場合は、内部垂直同期信号と内部クロックは同期している。したがって、内部垂直同期信号に同期するバックライト駆動装置が生成している PWM パルスも、内部クロックを用いて生成されているので、PWM パルスと内部垂直同期信号も同期している。

#### 【0029】

しかしながら、フレーム周期の基準信号として、外部垂直同期信号が用いられる場合は、外部垂直同期信号と内部クロックは非同期である。

#### 【0030】

この場合は、図3に示すように各部の出力に周波数変動やジッターの影響が出てくる。

図3において、図3(3A)は、外部垂直同期信号であり、図3(3B)は、発振クロック(OSC CLK)である。図3(3C)は、分周器23から出力される1フレーム期間計数值である。図の例は、発振クロック(OSC CLK)の周波数が7.83MHzで、フレーム周波数が60Hzとした場合の例である。ここでは、外部垂直同期信号が採用されているので、1フレーム計数値が変動することがある。周波数変動やジッターの影響を0.5%と仮定すると、図の例のようにフレームクロックカウンタ21からの1フレームの時間計数値は、例えば131152、129847のように変動する。

10

#### 【0031】

図3(3D)は、入力端子13にセットされている除数(divisor)を示している。この例では、除数は100である。フレームクロックカウンタ21の計数結果は、131152や129847などとフレーム毎に異なる計数値が出力されるので、分周器22の出力である分周値は、1311や1298となる。この分周値に基づいてクロックを分周する分周器23の分周出力パルスの数は、図3(3E)、(3F)に示すように、フレーム毎に変動し、分周出力パルスの数が101個や99個などと異なったパルス数で出力される。なお図3(3G)は、分周出力パルスの1周期の期間にカウントされるクロック数を示し、図3(3H)は、PWMパルスの例を示している。

20

#### 【0032】

その結果、PWMパルスはフレーム毎にパルス、すなわちハイレベル時間が異なってしまう。このフレームごとのパルス幅の相違によりフレーム毎にバックライト輝度が異なる現象(ちらつき現象)が発生してしまう。

30

#### 【0033】

そこで、本発明における実施形態では、上記したように分周出力パルスの数をフレーム毎に変動させてしまうような外部垂直同期信号の影響を受けにくいバックライト駆動装置を構成し、結果的としてバックライトの輝度を安定化することができる構成とする。

#### 【0034】

本題を説明する前に図4を参照して、バックライト駆動装置によるバックライトの輝度Y1と、液晶パネルの光透過率P1との関係について簡単に説明する。図4において、線4Aは、バックライトの輝度Y1と、液晶パネルの光透過率P1に応じて得られる画面の明るさ表している。つまり、バックライトの輝度Y1が低下しても、液晶パネルの光透過率P1を大きくすると、画面の明るさを一定に維持することができる。したがって、画面の明るさを犠牲にすることなく、バックライトの輝度を制御して、消費電力を低下させることができる。バックライトの輝度が低下されているときに、分周出力パルスの数が外部垂直同期信号の影響を受けて、フレーム毎に変動すると、画面の明るさの変動が目立ちやすくなる。

40

#### 【0035】

次に、本題に戻る。図5は、一実施形態であり、この実施形態の回路はバックライトの輝度を安定化させることができる。

#### 【0036】

図5において、図1と同一部分には、同一符号を付して説明は省略する。図5の回路が図1の回路と異なる部分は、フレーム基準信号として、垂直表示期間同期信号TEを使用している部分である。垂直表示期間同期信号TEは、インバータ17を介してフレーム基

50

準信号として使用される。なおインバータ 17 は、極性を整備するためのものであり、必ずしも必須のものではない。

#### 【0037】

垂直表示期間同期信号 T\_E は、PWM 発生器 24 から出力される PWM パルスの 1 フレーム当たりの数を所定値に抑制するので、制限信号と称しても良い。また垂直表示期間同期信号 T\_F の供給経路を、制限手段と称しても良い。

#### 【0038】

垂直表示期間同期信号 T\_E は、タイミング信号成生回路 30 にて作成されている。タイミング信号号生成回路 30 は、外部垂直同期信号或いは内部垂直同期信号と、水平同期信号、内部クロックなどを用いて、各種のタイミング信号を生成する。

10

#### 【0039】

またタイミング信号生成回路 30 は、ビデオ信号処理回路（図示せず）に対して、水平及び垂直同期信号に同期した内部クロックを供給している。従って、ビデオ信号処理回路で処理されるビデオ信号は内部クロックに同期して処理される。このためにビデオ信号の表示期間は、内部クロックに同期している。ビデオ（イメージ）信号は、垂直同期信号の後縁から十数個の水平同期信号が存在するプランキング期間の後縁から存在する。フレーム内においてビデオ信号が存在する開始ラインは予め規定されている。

#### 【0040】

図 6 に示すように、垂直同期信号は、垂直プランキング期間（イメージ信号が存在しない垂直方向非表示期間とも称される）を有する。図 6 (6A) は、一般的な複合ビデオ信号を示し、ビデオ（イメージ）信号（輝度信号及びクロミナンス信号）を含む。1 フレーム或いは 1 フィールド内に #1 - #L のラインには、ビデオ（イメージ）信号が存在し、垂直プランキング期間には、ビデオ（イメージ）信号は存在しない。このビデオ信号は、デジタル RGB コンポーネントビデオとして表されることができる。RGB のデータサンプルは、内部クロックに同期した転送パルスに同期して転送される。

20

#### 【0041】

図 6 (6B) は、タイミング信号成生回路 30 にて生成された垂直表示期間同期信号 T\_E をインバータ 17 で反転させた信号（フレーム基準信号）である。この垂直表示期間同期信号 T\_E 、つまりフレーム基準信号は、RGB コンポーネントビデオが存在する走査ラインと、内部クロックに同期してその位相が設定されているので、ビデオ信号の表示期間に正確に同期している。図 6 (6C) は、垂直同期信号及び水平同期信号を含む複合同期信号である。上記の垂直表示期間同期信号 T\_E は、垂直方向非表示期間と、垂直方向表示期間とを識別できる信号として生成される。

30

#### 【0042】

図 7 には、液晶パネルにおける映像の標示領域と、垂直同期信号、水平同期信号、垂直方向の表示期間、水平方向の表示期間との関係を示している。このように垂直表示期間同期信号 T\_E は、バックライトの点灯期間を、垂直方向表示期間のみに設定することができる。

#### 【0043】

上記した実施例では、垂直非表示期間と、表示期間とを識別できるフレーム基準信号（反転垂直表示期間同期信号 T\_E ）を得ている。

40

#### 【0044】

ここで、垂直表示期間の水平ライン数は予め規定されている。この結果、バックライトを点灯させるための PWM パルスは、表示期間のみに各フレームで同じ数で生成されることになる。

#### 【0045】

図 8 は、さらに垂直同期信号の前後の垂直プランキング期間を示している。図 8 (8A) は、液晶パネル駆動回路にインする外部垂直同期信号、図 8 (8B) は外部水平同期信号、図 8 (8C) は、外部入力ビデオ信号である。図 8 (8D) は、タイミング信号生成回路で生成されたフレーム基準信号（反転垂直表示期間同期信号 T\_E ）であり、図 8 (8E)

50

F )は、液晶パネル駆動回路から出力され液晶パネルに入力するビデオ信号である。図8(8F)は、ビデオ信号を構成しているRGB信号を液晶パネル内のR、G、B、各信号線に振り分ける制御を行っているアナログスイッチ回路(ASW回路)の制御を行うASW制御信号(RGB振り分け制御信号と称しても良い)である。図8(8G)は、液晶パネル駆動回路の垂直同期ドライブスタート信号である。図8(8H)のクロックCKV1、CKV2は、スタート信号に同期してゲート制御レベルを液晶パネル駆動回路内の垂直方向シフトレジスタに保持し、保持したゲート制御レベルを垂直方向へシフトさせるためのパルスである。これにより、クロックCKV1、CKV2は、ゲート制御レベルにより、水平ライン上の画素回路に対してビデオ信号の書き込みタイミングを設定することができる。

【0046】

10

図9は、上記した回路の動作により1垂直期間内において、PWMパルスが何個生成されるかを説明するためのタイミングチャートである。

【0047】

図9において、図9(9A)は、外部垂直同期信号であり、図9(9B)は、垂直表示間同期信号TE、図9(9C)は、発振クロック(OSC CLK)である。

【0048】

図9(9D)は、分周器23から出力される表示時間計数値である。図9(9E)は、入力端子13にセットされている除数(divisor)を示している。この例では、除数は100である。したがって、分周器22から出力される分周値は、 $(128100/100) = 1281$ として出力される。

20

【0049】

この分周値は、次の分周器23に入力される。分周器23は、発振クロック(OSC CLK)を1281で分周して、分周出力パルスを出力する。図9(9F)が分周出力パルスである。図9(9G)は分周出力パルスを拡大して示している。図9(9H)は発振クロックを拡大して示している。

【0050】

この分周出力パルスは、PWM生成器24に入力される。分周出力パルスは、PWMパルスの1周期を設定する。PWM生成器24は、図9(9I)に示すように、分周出力パルスの立ち上がりに同期してPWMパルスを立ち上げる(ハイレベルにする)。そして、パルス幅制御信号(duty)により設定された値だけクロックをカウントすると、PWMパルスを立ち下げる(ローレベルにする)。従って、パルス幅制御信号(duty)を変えることにより、PWMパルスのデューティー(パルス幅)を変化させることができる。

30

【0051】

上記実施例の構成はこのような構成に限定されるものではなく、各種の変形が可能であることは勿論である。また図5のフレームクロックカウンタ21、分周器22、23が一体に構成されてもよい。さらに、コードにより記述されたソフトウェアにより動作するデジタルプロセッサにより構成されてもよいことは勿論である。

【0052】

したがって、各ブロックの名称も上記に限定されるものではなく、同等の機能を有する場合は本実施形態の思想の概念に含まれる。したがって、フレームクロックカウンタ21、分周器22、23が含まれる構成部分は分周パルス生成手段と称しても良い。また、PWM生成器24が含まれる構成部分は、パルス幅変調パルス発生手段と称してもよい。またインバータ17が含まれる構成部分は、基準信号出力手段と称してもよい。

40

【0053】

上記した表示制御信号、すなわちフレーム基準信号(反転垂直表示間同期信号TE)などは発振クロックOSC CLKから作成された信号なのでTEで規定される表示信号出力区間を発振クロックOSC CLKでカウントしてもジッターなどの変動の影響は受けない。表示信号が外部入力の場合、従来は外部垂直同期信号をフレーム基準信号として使用し、外部垂直同期信号と発振クロックOSC CLKが非同期であることに起因する周波数変動やジッターの影響を受けたが、本実施形態の場合は発振クロックOSC CLKに由来するフレーム基準信

50

号（反転垂直表示期間同期信号 T E）を基準とする構成であるために、非同期の動作にはならず周波数変動やジッターの影響は受けない。表示を制御する表示コントローラー（図示せず）は入力表示信号に同期させなければならぬが、表示コントローラーにおける同期調整（同期信号の時間方向のゆれ、或いは位相変動）は表示動作に影響しない垂直同期信号の時間的に前後するプランキング期間で吸収される。

#### 【0054】

すなわち、発振クロックOSC CLKと外部垂直同期信号との非同期の影響が出るとすればプランキング期間すなわち反転 T E がローレベルの区間である。逆に反転垂直表示期間同期信号 T E のハイレベルの区間では非同期の影響を受けることが無い。

#### 【0055】

従って、フレーム基準信号（反転垂直表示期間同期信号 T E）がハイレベルの区間の計数値は毎フレーム128100で一定している。計数値が一定しているため、その後の分周器の出力も一定しており、毎フレーム安定した PWM パルスを得ることができる。つまり、外部入力の表示信号であった場合でも各フレーム内の PWM パルス幅の個数が等しくなるためバックライトのちらつきを抑制することが可能となる。

#### 【0056】

さらに、セット側で、あるソフトウェア処理を行う場合でも、信号 T E を利用して、プランキング期間でソフトウェア処理を行うことができる。このようにセット側のソフトウェア処理が行われた場合でも、各フレームの PWM パルスの個数が等しくなるためバックライトのちらつきを抑制することが可能となる。

#### 【0057】

上記したようにバックライト輝度が一定に維持設定された後は、周波数変動やジッターがあった場合及び又はセット側のソフトウェア処理が入った場合も、各フレームの PWM パルスのパルス幅およびパルス数が等しくなるためバックライトのちらつきを抑制することが可能となる。

#### 【0058】

上記したように本実施形態によれば、液晶パネルのバックライトにパルス幅変調パルスに基づいて生成した電圧を供給するバックライト駆動装置において、分周パルス生成手段が、フレーム周期のフレーム基準信号に同期してリセット動作し、1フレーム期間に内部クロックを計数した計数値を除算して、分周値を生成し、この分周値で前記内部クロックを分周することでパルス幅変調パルスの1周期毎に発生する分周パルスを出力する。

#### 【0059】

パルス幅変調パルス発生手段は、前記フレーム基準信号に同期してリセット動作し、前記分周パルスの入力時点から前記内部クロックの計数を開始し、計数値がパルス幅設定値となるまで計数し、この計数期間のパルス幅を持つ前記パルス幅変調パルスを出力する。ここで基準信号出力手段は、前記フレーム基準信号として、前記液晶パネルに入力される映像信号の表示期間に位相が同期した期間に発生する。

#### 【0060】

この発明は上記の実施形態に限定されるものではない。上記したようにフレーム内の PWM パルスの個数を安定化させ、バックライトのちらつきを抑制する手段は以下のように実施することも可能である。

#### 【0061】

図10は、本開示の別の実施形態である。図1の回路ブロックと同一部分には同一符号を付している。図1の回路ブロックと図10の回路ブロックとの相違点を述べると以下の通りである。フレームクロックカウンタ21と分周器22との間に最小値検出器211が配置される。最小値検出器211は、フレームクロックカウンタ21からフレーム毎に出力されている計数値を監視する。そして複数フレームの計数値の中の最小計数値を検出する。この最小計数値が分周器22に与えられる。

#### 【0062】

分周器22には、入力端子13から除数(divisor)が与えられる。分周器22は、最小

10

20

30

40

50

計数値を除数 100 で割り算した結果の値（ディバイドイング数）を分周器 23 に送る。

【0063】

分周器 23 は、ディバイドイング数で発振クロック（OSC CLK）を分周し、分周出力パルスを出力する。分周出力パルスは、PWM 生成器 24 に入力する。

【0064】

PWM 生成器 24 は、分周出力パルスに同期して、発振クロック（OSC CLK）を取り込む。PWM 生成器 24 は、端子 14 から入力するパルス幅制御信号（duty）に基づいて、分周出力パルスの 1 周期期当たりに、カウントすべきクロックの数を決定する。ただし、PWM 生成器 24 には、PWM パルスが 1 フレーム期間に出力されるパルス数を制限するために PWM 数制限値（この例では 100）が入力している。したがって、1 フレーム期間に 101 個以上の PWM パルスの出力は抑制される。10

【0065】

PWM 生成器 24 は、第1の分周出力パルスが入力したときクロックの計数を開始するとともに、PWM パルスを立ち上げる。そして、パルス幅制御信号で決められた数のクロックを計数したとき、PWM パルスを立ち下げる。次の第2の分周パルスが入力したとき、またクロックの計数を開始するとともに、PWM パルスを立ち上げる。そして、パルス幅制御信号で決められた数のクロックを計数したとき、PWM パルスを立ち下げる。このような動作を繰り返すことで PWM パルスの連続性を得ている。

【0066】

ただし、上記したように PWM 生成器 24 には、PWM パルスが 1 フレーム期間に出力されるパルス数を制限する PWM 数制限値（この例では 100）が入力しているので、1 フレーム期間に 101 個以上の PWM パルスが出力されるのは抑制される。1 フレーム期間に 101 個以上の PWM パルスが出力されるのを抑制する方法としては、分周出力パルスが PWM 生成器 24 に 101 個入力するのを入力段で抑制する方法と、PWM パルスが PWM 生成器 24 から 101 個出力するのを出力段で抑制する方法が可能である。20

【0067】

図 11 は、図 10 のバックライト駆動装置の動作例を説明するために示した動作タイミングチャートである。

【0068】

図 11 (11A) は、外部垂直同期信号であり、図 11 (11B) は、発振クロック（OSC CLK）である。図 11 (11C) は、フレームクロックカウンタ 21 から出力されるフレーム毎( $n$ のフレーム・・・・,  $n + x 1$ のフレーム,  $n + x 2$ のフレーム)の計数値である。 $n$  フレームが 131152 であり、ある期間経過後の  $n + x 1$  が 129195, の  $n + x 2$  が 130500, などと変動していくものとする。図 11 (11D) は、最小値検出器 221 から出力される最小値（この例では、129847 に続いてさらに小さい値 129195 が更新されて出力されている例を示している）である。30

【0069】

図 11 (11E) は、分周器 22 に与えられる除数である。したがって、分周器 22 から出力される分周値は、 $(129847 / 100) = 1298$ , 続いて  $(129195 / 100) = 1291$  として出力される。40

【0070】

この分周値は、次の分周器 23 に入力される。分周器 23 は、発振クロック（OSC CLK）を 1298 で分周し、続いて 1291 で分周して、分周出力パルスを出力する。図 11 の (11F) が分周出力パルスである。図 11 (11G) は分周出力パルスを拡大して示している。なお、図 11 の (11F) において破線で示されている分周出力パルスは PWM 生成器 24 から出力される PWM パルスに寄与しない分周出力パルスであることを示している。

【0071】

PWM 生成器 24 は、端子 14 から入力するパルス幅制御信号（duty）に基づいて、分周出力パルスの 1 周期期当たりに、カウントすべきクロックの数を決定する。PWM 生成器 24 は、第1の分周出力パルスが入力したとき PWM パルスを立ち上げ、パルス幅制御

10

20

30

40

50

信号 (duty) により決まる値と同じ数のクロックをカウントしたとき、PWMパルスを立ち下げる。次の第2の分周出力パルスが入力したときPWMパルスを立ち上げ、パルス幅制御信号 (duty) により決まる値と同じ数のクロックをカウントしたとき、PWMパルスを立ち下げる。この動作を、PWM生成器24は、1フレーム期間繰り返すが、PWM生成器24には、PWMパルスが1フレーム期間に出力されるパルス数を制限するためにPWM数制限値 (この例では100) が入力しているので、1フレーム期間にPWMパルスを101個以上出力することは抑制する。PWM数制限値は、PWM発生器24から出力されるPWMパルスの1フレーム当たりの数を所定値に抑制するので、制限信号と称しても良い。またPWM数制限値の供給経路を、制限手段と称しても良い。

## 【0072】

10

この実施形態は、分周器22に印加された除数、すなわちフレーム周波数の倍数指定値を用いて、PWMパルス数の制限を行っているが、この方法に限定されるものではない。別の箇所からPWMパルス数の制限を行う値を与えてよい。

## 【0073】

要は、フレーム周波数の倍数指定値で指定されたパルス数 (例えば120個) よりもPWMパルスが多く出力されないように制限を行う。

## 【0074】

図10、図11の例では100個のPWMパルスよりも多い数のPWMパルスが出力されないように制限されるため、図11に示すように101番目のPWMパルスは削除される。このように、周波数変動やジッターなどによってフレームクロックカウンタ21の計数結果が131152や129195などとフレーム毎に異なった場合でも、常時、最小値検出器21の検出した最小値を用い、かつPWM数制限値を用いてPWMパルス列を作成している。このためにPWMパルスを効率的に作成するとともに、1フレーム内では、常に指定された数のPWMパルスを作成することができる。

20

## 【0075】

また、本実施形態は、最小値を更新して書き換えて行くことによりフレーム時間の変化に追従して、分周値が決まる動作となる。したがって、最小値に応じて、1フレーム期間内の分周出力パルスのパルス数も決まる。最小値が小さい程、1フレーム期間内の分周出力パルスのパルス数は多くなるが、制限値により、100以内に制限される。

## 【0076】

30

上記の最小値の採用は、1フレーム期間内のPWMパルスの生成個数を100個とするために、生成動作の余裕を持たせるための処置である。

## 【0077】

この結果、1フレーム期間内で生成されるPWMパルス数が安定しており、フレーム間でPWMパルスのパルス幅が等しくなるためバックライトのちらつきを抑制することが可能となる。

## 【0078】

40

上記したように本実施形態によると、実施形態によれば、液晶パネルのバックライトにパルス幅変調パルスに基づいて生成した電圧を供給するバックライト駆動装置において、分周パルス生成手段が、フレーム周期のフレーム基準信号に同期してリセット動作し、1フレーム期間に内部クロックを計数した計数値を除算して、分周値を生成し、この分周値で前記内部クロックを分周することでパルス幅変調パルスの1周期毎に発生する分周パルスを出力する。ここで、前記1フレーム期間に内部クロックを計数した計数値としては、前記基準信号の位相が変動する場合、最小計数値が採用されている。

## 【0079】

パルス幅変調パルス発生回路は、前記フレーム基準信号に同期してリセット動作し、前記分周パルスの入力時点から前記内部クロックの計数を開始し、計数値がパルス幅設定値となるまで計数している期間のパルス幅を持つ前記パルス幅変調パルスを出力する。ここで前記パルス幅変調パルスの1フレーム期間内の出力個数は、所定の値に制限されている。

50

## 【0080】

上記実施形態によると、垂直同期信号の周波数変動やジッターがあった場合も各フレームのパルスの個数が等しくなるためバックライトのちらつきを抑制することが可能となる。またフレーム時間の変動にも追従できるため PWM パルス出力数が安定しているためバックライトのチラツキを安定して抑制することが可能となる。

## 【0081】

この発明は上記の実施形態に限定されるものではない。上記したようにフレーム内の PWM パルスの個数を安定化させ、バックライトのちらつきを抑制する手段は以下のように実施することも可能である。

## 【0082】

図 12 は、本開示の別の実施形態である。図 1 の回路ブロックと同一部分には同一符号を付している。図 1 の回路ブロックと図 12 の回路ブロックとの相違点を述べると以下の通りである。

## 【0083】

図 1 の回路では分周器 22 に入力端子 13 より除数が与えられるが、図 12 の回路では、入力端子 13 と分周器 22 との間に加算器 220 が設けられている。従って、入力端子 13 に与えられた除数は、加算器 220 で補正され、補正除数として分周器 22 に供給される。

## 【0084】

また、入力端子 13 の除数は、PWM 生成器 24 に対して、PWM 数制限値として与えられる。この PWM 数制限値は、図 10、図 11 で説明した実施例の場合と同じ目的である。したがって、PWM 数制限値は、PWM 発生器 24 から出力される PWM パルスの 1 フレーム当たりの数を所定値に抑制するので、制限信号と称しても良い。また PWM 数制限値の供給経路を、制限手段と称しても良い。

10

20

## 【0085】

図 13 は、図 12 のバックライト駆動装置の動作例を説明するために示した動作タイミングチャートである。

## 【0086】

図 13 (13A) は、例えば外部垂直同期信号であり、図 13 (13B) は、発振クロック (OSC CLK) である。図 13 (13C) は、フレームクロックカウンタ 21 から出力されるフレーム毎 (n のフレーム, n + 1 のフレーム) の計数値である。131152, 129847 · · · と変動している。

30

## 【0087】

図 13 (13D) は、加算器 220 から出力された補正除数 (例えば 105) であり、図 13 (13E) が入力端子 13 に与えられた除数である。この例では、補正值  $n = 5$  の場合を示している。図 13 (13F)、図 13 (13G) は、分周器 23 から出力され、PWM 生成器 24 で使用される分周出力パルスであり、図 13 (13H) は、発振クロックである。図 13 (13I) は PWM パルスである。

## 【0088】

計数値が 131152, 129847, 131152, 129847 · · · と変動しているものとすると、分周器 22 から出力される分周値は、 $(131152/105)=1249$ ,  $(129847/105)=1236$ ,  $(131152/105)=1249$ ,  $(129847/105)=1236$  · · · と変化する。分周器 23 に与えられる分周値は、除数を 100 とした場合よりも小さくなる。この結果、分周出力パルスの数は、1 フレーム期間内で 100 以上の数となる。つまりこの回路では、余裕を持って安定して 100 以上の分周出力パルスを作成する。一方では、PWM 生成器 24 において 101 個以上の PWM パルスが生成されるのを抑制している。

40

## 【0089】

これにより、周波数変動やジッターによりフレームクロックカウンタ 21 の計数結果が 131152 や 129847 などとフレーム毎に異なった場合でも、各フレームで 100 個の PWM パルスの作成が可能となる、すなわち、周波数変動やジッターがあった場合も各フレームの

50

パルス幅の個数が等しくなるためバックライトのちらつきを抑制することが可能となる。

#### 【0090】

上記したように本実施形態は、周波数変動やジッターがあった場合も各フレームのパルス幅の個数が等しくなるためバックライトのちらつきを抑制することが可能となる。また、加算手段と PWM 生成器にリミッタ（PWM パルス作成を禁止する回路）を追加するだけで、その他のアルゴリズムの変更を必要としない。つまり簡単な回路構成でバックライトのチラツキを抑制することが可能となる。

#### 【0091】

本発明のいくつかの実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

10

#### 【符号の説明】

#### 【0092】

15 . . . セレクタ、17 . . . インバータ、21 . . . フレームクロックカウンタ、22、23 . . . 分周器、24 . . . PWM 生成器、221 . . . 最小値検出器、220 . . . 加算器。

【図1】

図1

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

図 12

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

G 09 G 3/20 612 J

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 藤原 久男

埼玉県深谷市幡羅町一丁目9番地2 東芝モバイルディスプレイ株式会社内

F ターム(参考) 2H193 ZD32 ZG02 ZG50 ZH44 ZH56

5C006 AF44 BB16 BF22 BF23 EA01

5C080 AA10 BB05 DD03 JJ02 JJ04 JJ05

|             |                                                                                                                                                                                 |         |            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 液晶显示装置的背光驱动装置                                                                                                                                                                   |         |            |

| 公开(公告)号     | <a href="#">JP2013156326A</a>                                                                                                                                                   | 公开(公告)日 | 2013-08-15 |

| 申请号         | JP2012015059                                                                                                                                                                    | 申请日     | 2012-01-27 |

| 申请(专利权)人(译) | 有限公司日本展示中心                                                                                                                                                                      |         |            |

| [标]发明人      | 藤原久男                                                                                                                                                                            |         |            |

| 发明人         | 藤原 久男                                                                                                                                                                           |         |            |

| IPC分类号      | G09G3/36 G09G3/34 G09G3/20 H03K7/08 G02F1/133                                                                                                                                   |         |            |

| F1分类号       | G09G3/36 G09G3/34.J G09G3/20.642.C H03K7/08.A G02F1/133.535 G09G3/20.612.J                                                                                                      |         |            |

| F-Term分类号   | 2H193/ZD32 2H193/ZG02 2H193/ZG50 2H193/ZH44 2H193/ZH56 5C006/AF44 5C006/BB16 5C006/BF22 5C006/BF23 5C006/EA01 5C080/AA10 5C080/BB05 5C080/DD03 5C080/JJ02 5C080/JJ04 5C080/JJ05 |         |            |

| 代理人(译)      | 河野 哲<br>中村诚<br>河野直树<br>冈田隆                                                                                                                                                      |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                       |         |            |

### 摘要(译)

本发明提供一种液晶显示装置的背光驱动装置，其不易受外部垂直同步信号的相位波动的影响，因此可以稳定背光的亮度。在用于将基于脉冲宽度调制脉冲串产生的电压提供给背光的背光驱动装置中，分割脉冲生成单元与帧周期的帧参考信号同步地开始操作，并且执行脉冲宽度调制。对脉冲脉冲序列的每个周期产生具有脉冲的分割脉冲序列。脉冲宽度调制脉冲发生装置与帧参考信号同步地开始操作，开始对分割脉冲序列的每个脉冲输入的内部时钟计数，并且计数值对应于脉冲宽度设定值的周期的脉冲输出具有宽度的脉冲宽度调制脉冲。限制装置将限制信号施加到脉冲宽度调制脉冲发生装置，以便将从脉冲宽度调制脉冲发生装置输出的脉冲宽度调制脉冲的一帧每次的输出脉冲数抑制到预定数量。

[选中图]图5