(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-20279

(P2010-20279A)

(43) 公開日 平成22年1月28日(2010.1.28)

| (51) Int.Cl.                 | F 1       | テーマコード (参考) |

|------------------------------|-----------|-------------|

| <b>G09G 3/36 (2006.01)</b>   | G09G 3/36 | 2 H 09 2    |

| <b>G09G 3/20 (2006.01)</b>   | G09G 3/20 | 6 7 O E     |

| <b>G02F 1/1345 (2006.01)</b> | G09G 3/20 | 6 2 2 D     |

| <b>G02F 1/133 (2006.01)</b>  | G09G 3/20 | 6 8 O G     |

|                              | G09G 3/20 | 6 2 1 M     |

|                              |           | 5 C 00 6    |

|                              |           | 5 C 08 0    |

審査請求 未請求 請求項の数 19 O L (全 17 頁) 最終頁に続く

(21) 出願番号 特願2009-3061 (P2009-3061)

(22) 出願日 平成21年1月9日 (2009.1.9)

(31) 優先権主張番号 10-2008-0066228

(32) 優先日 平成20年7月8日 (2008.7.8)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞 416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人 110000408

特許業務法人高橋・林アンドパートナーズ

(72) 発明者 権 英 根

大韓民国京畿道水原市靈通区網浦洞 LG

X i i 3次アパートメント 301 棟 12

03 号

最終頁に続く

(54) 【発明の名称】ゲートドライバ、及びこれを備えた表示装置

## (57) 【要約】

【課題】誤動作を防止することができるゲートドライバ、及びこれを有する表示装置を提供する。

【解決手段】ゲートドライバ、及びこれを有する表示装置で、ダミーステージは、最後の駆動ステージから受信した最後のキャリー信号に応答して、リセット信号とダミーゲート信号とを出力する。ダミーステージから出力されたリセット信号は、複数の駆動ステージのリセット端子に入力され、ダミーゲート信号は、最後の駆動ステージの制御端子に提供される。したがって、最後の駆動ステージに供給されるダミーゲート信号の歪曲を防止することができ、その結果、最後の駆動ステージがダミーゲート信号により、正常にオフされることで液晶表示パネル上にライン不良が発生することを防止することができる。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

直前の駆動ステージから直前のキャリー信号を受信する入力端子と、直後の駆動ステージから直後のゲート信号を受信する制御端子と、現在のゲート信号を出力し、直後の駆動ステージの制御端子に接続された出力端子と、現在のキャリー信号を出力し、直後の駆動ステージの入力端子に接続されたキャリー端子と、リセット信号を受信するリセット端子とを各々含む複数の駆動ステージと、

最後の駆動ステージから最後のキャリー信号を受信する入力端子と、制御信号を受信する制御端子と、前記複数の駆動ステージのリセット端子に、前記リセット信号を提供する第1出力端子と、前記複数の駆動ステージのうちの前記最後の駆動ステージの制御端子にダミーゲート信号を提供する第2出力端子と、を含むダミーステージと、

10 を含むことを特徴とするゲートドライバ。

**【請求項 2】**

前記ダミーステージは、

前記第1出力端子を通じて出力される前記リセット信号をプルアップさせる第1プルアップ部と、

前記第2出力端子を通じて出力される前記ダミーゲート信号をプルアップさせる第2プルアップ部と、

前記最後のキャリー信号に応答して前記第1及び第2プルアップ部をオンさせ、前記制御信号に応答して前記第1及び第2プルアップ部をオフさせるプルアップ駆動部と、

20

前記制御信号に応答して前記リセット信号、及び前記ダミーゲート信号をゲートオフ電圧までプルダウンさせるプルダウン部と、をさらに含むことを特徴とする請求項1に記載のゲートドライバ。

**【請求項 3】**

前記第1プルアップ部は、前記プルアップ駆動部の出力端に接続される制御電極、クロックを受信する入力電極、及び前記第1出力端子に接続される出力電極を含む第1プルアップトランジスタを含み、

前記第2プルアップ部は、前記プルアップ駆動部の前記出力端に接続される制御電極、前記クロックを受信する入力電極、及び前記第2出力端子に接続される出力電極を含む第2プルアップトランジスタを含むことを特徴とする請求項2に記載のゲートドライバ。

30

**【請求項 4】**

前記第2プルアップトランジスタは、前記第1プルアップトランジスタより小さなサイズを有し、ここで前記サイズは、チャネル長さLに対するチャネル幅Wを表すことを特徴とする請求項3に記載のゲートドライバ。

**【請求項 5】**

前記プルダウン部は、

前記制御端子に接続される制御電極、前記ゲートオフ電圧を受信する入力端子、及び前記第1出力端子に接続される出力電極を含む第1プルダウントランジスタと、

前記制御端子に接続される制御電極、前記ゲートオフ電圧を受信する入力端子、及び前記第2出力端子に接続される出力電極を含む第2プルダウントランジスタと、を含むことを特徴とする請求項2に記載のゲートドライバ。

40

**【請求項 6】**

前記第2プルダウントランジスタは、前記第1プルダウントランジスタより小さなサイズを有し、ここで前記サイズはチャネル長さLに対するチャネル幅Wを表すことを特徴とする請求項5に記載のゲートドライバ。

**【請求項 7】**

前記複数の駆動ステージのうち、最初の駆動ステージの入力端子には、前記直前のキャリー信号の代わりに垂直開始信号が提供され、

前記ダミーステージの前記制御端子に提供される前記制御信号は、前記垂直開始信号を含むを特徴とする請求項1に記載のゲートドライバ。

50

**【請求項 8】**

各前記駆動ステージは、

前記出力端子を通じて出力される前記現在のゲート信号をプルアップさせるプルアップ部と、

前記キャリー端子を通じて出力される前記現在のキャリー信号をプルアップさせるキャリー部と、

前記の直前のキャリー信号に応答して前記プルアップ部及びキャリー部をオンさせ、前記直後のゲート信号に応答して前記プルアップ部及びキャリー部をオフさせるプルアップ駆動部と、

前記直後のゲート信号に応答して、前記現在のゲート信号及び前記現在のキャリー信号をゲートオフ電圧までプルダウンさせるプルダウン部と、 10

前記ダミーステージの第1出力端子から出力された前記リセット信号に応答して、前記プルアップ部及び前記キャリー部をオフさせるリセット部と、を含むことを特徴とする請求項1に記載のゲートドライバ。

**【請求項 9】**

前記リセット部は、前記ダミーステージの前記第1出力端子に接続され、前記リセット信号を受信する制御電極、前記ゲートオフ電圧を受信する入力電極、及び前記プルアップ部及び前記キャリー部の制御電極に接続された出力電極を含むリセットトランジスタを含むことを特徴とする請求項8に記載のゲートドライバ。 20

**【請求項 10】**

複数のゲートライン、複数のデータライン、及び前記複数のゲートラインと前記複数のデータラインにより定義された複数の画素領域に各々具備された複数の画素を含み、映像を表示する表示パネルと、

前記複数のデータラインに前記データ信号を提供するデータドライバと、

前記複数のゲートラインに前記ゲート信号を順次出力するゲートドライバと、

を含み、

前記ゲートドライバは、

直前の駆動ステージから直前のキャリー信号を受信する入力端子、直後の駆動ステージから直後のゲート信号を受信する制御端子、現在のゲート信号を出し、直後の駆動ステージの制御端子に接続された出力端子、現在のキャリー信号を出し、直後の駆動ステージの入力端子に接続されたキャリー端子、及びリセット信号を受信するリセット端子を各々含む複数の駆動ステージと、 30

最後の駆動ステージから最後のキャリー信号を受信する入力端子、制御信号を受信する制御端子、前記複数の駆動ステージのリセット端子に前記リセット信号を提供する第1出力端子、及び前記複数の駆動ステージのうちの前記最後の駆動ステージの制御端子にダミーゲート信号を提供する第2出力端子を含むダミーステージと、を含むことを特徴とする表示装置。

**【請求項 11】**

前記ダミーステージは、

前記第1出力端子を通じて出力される前記リセット信号をプルアップさせる第1プルアップ部と、 40

前記第2出力端子を通じて出力される前記ダミーゲート信号をプルアップさせる第2プルアップ部と、

前記最後のキャリー信号に応答して前記第1及び第2プルアップ部をオンさせ、前記制御信号に応答して前記第1及び第2プルアップ部をオフさせるプルアップ駆動部と、

前記制御信号に応答して前記リセット信号及び前記ダミーゲート信号をゲートオフ電圧までプルダウンさせるプルダウン部と、を含むことを特徴とする請求項10に記載の表示装置。

**【請求項 12】**

前記第1プルアップ部は、前記プルアップ駆動部の出力端に接続された制御電極、クロ 50

ックを受信する入力電極、及び前記第1出力端子に接続された出力電極を含む第1プルアップトランジスタを含み、

前記第2プルアップ部は、前記プルアップ駆動部の前記出力端に接続された制御電極、前記クロックを受信する入力電極、及び前記第2出力端子に接続された出力電極を含む第2プルアップトランジスタを含むことを特徴とする請求項11に記載の表示装置。

#### 【請求項13】

前記プルダウン部は、

前記制御端子に接続された制御電極、前記ゲートオフ電圧を受信する入力端子、及び前記第1出力端子に接続された出力電極を含む第1プルダウントランジスタと、

前記制御端子に接続された制御電極、前記ゲートオフ電圧を受信する入力端子、及び前記第2出力端子に接続された出力電極を含む第2プルダウントランジスタと、を含むことを特徴とする請求項11に記載の表示装置。 10

#### 【請求項14】

各前記駆動ステージは、

前記出力端子を通じて出力される前記現在のゲート信号をプルアップさせるプルアップ部と、

前記キャリー端子を通じて出力される前記現在のキャリー信号をプルアップさせるキャリー部と、

前記直前のキャリー信号に応答して前記プルアップ部及びキャリー部をオンさせ、前記直後のゲート信号に応答して前記プルアップ部及びキャリー部をオフさせるプルアップ駆動部と、 20

前記直後のゲート信号に応答して前記現在のゲート信号及び前記現在のキャリー信号をゲートオフ電圧までプルダウンさせるプルダウン部と、

前記ダミーステージの第1出力端子から出力された前記リセット信号に応答して前記プルアップ部及び前記キャリー部をオフさせるリセット部と、を含むことを特徴とする請求項10記載の表示装置。

#### 【請求項15】

前記各駆動ステージの出力端子は、前記複数のゲートラインのうちの対応するゲートラインの第1端部に電気的に接続され、

前記各駆動ステージは、前記対応するゲートラインの第2端部に電気的に接続され、前記直後のゲート信号に応答して前記対応するゲートラインに印加された現在のゲート信号を放電する放電部をさらに含むことを特徴とする請求項14に記載の表示装置。 30

#### 【請求項16】

前記表示パネルは、前記ダミーステージの前記第2出力端子と前記放電部を電気的に接続するダミーゲートラインをさらに含むことを特徴とする請求項15に記載の表示装置。

#### 【請求項17】

前記表示パネルは、前記データラインが延長された方向に長い長方形形状を有し、前記複数のゲートラインの数が、前記複数のデータラインの数より多いことを特徴とする請求項10に記載の表示装置。

#### 【請求項18】

前記ゲートドライバは、薄膜工程を通じて前記表示パネル上に直接形成されることを特徴とする請求項17に記載の表示装置。 40

#### 【請求項19】

複数の駆動ステージを形成し、

ダミーステージを形成すること、

を含み、

各駆動ステージは、直前の駆動ステージから直前のキャリー信号を受信する入力端子と、

直後の駆動ステージから直後のゲート信号を受信する制御端子と、

現在のゲート信号を出力し、前記直後の駆動ステージの制御端子に接続される出力端子

と、

現在のキャリー信号を出力し、前記直後の駆動ステージの入力端子に接続されるキャリー端子と、

リセット信号を受信するリセット端子と、を含み、

前記ダミーステージは、

最後の駆動ステージから最後のキャリー信号を受信する入力端子と、

制御信号を受信する制御端子と、

前記複数の駆動ステージのリセット端子に前記リセット信号を提供する第1出力端子と

、

前記複数の駆動ステージのうち、前記最後の駆動ステージの制御端子にダミーゲート信号を提供する第2出力端子と、を含むことを特徴とするゲートドライバの製造方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ゲートドライバ、及びこれを備えた表示装置に関し、より詳細には、誤動作を防止することのできるゲートドライバ、及びこれを備えた表示装置に関する。

【背景技術】

【0002】

一般的に、液晶表示装置は、下部基板、下部基板と対向し具備される上部基板、及び下部基板と上部基板との間に形成された液晶層からなり、映像を表示する液晶表示パネルを具備する。

20

【0003】

液晶表示パネルには、複数のゲートライン、複数のデータライン、及び複数のゲートラインと複数のデータラインとに接続された複数の画素が具備される。液晶表示パネルには、複数のゲートラインにゲート信号を順次に出力するためのゲート駆動回路が薄膜工程を通じて直接形成される。

【0004】

一般的に、ゲート駆動回路は、連続に接続された複数の駆動ステージからなって順次ゲート信号を出力するシフトレジスタからなる。各駆動ステージは、直前のステージから受信したキャリー信号に応答して、対応するゲートラインにゲート信号を出力し、直後の駆動ステージにキャリー信号を提供する。

30

【0005】

また、各駆動ステージは、直後の駆動ステージのゲート信号により、オフされる。しかし、最後の駆動ステージは、直後の駆動ステージが存在しないために、最後の駆動ステージを正常にオフさせるための方法が要求される。

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、上述の問題点に鑑みてなされたもので、その目的は、最後の駆動ステージの出力特性を改善し、各駆動ステージを正常にリセットさせるためのゲートドライバを提供することである。

40

【0007】

本発明の他の目的は、上述したゲートドライバを具備する表示装置を提供することである。

【課題を解決するための手段】

【0008】

上述した目的を達成するための本発明の一実施形態によるゲートドライバは、複数の駆動ステージ、及びダミーステージを含む。

【0009】

各駆動ステージは、直前の駆動ステージから直前のキャリー信号を受信する入力端子、

50

直後の駆動ステージから直後のゲート信号を受信する制御端子、現在のゲート信号を出力し、直後の駆動ステージの制御端子に接続された出力端子、現在のキャリー信号を出力し、直後の駆動ステージの入力端子に接続されたキャリー端子、及びリセット信号を受信するリセット端子を含む。

## 【0010】

ダミーステージは、最後の駆動ステージから最後のキャリー信号を受信する入力端子、制御信号を受信する制御端子、複数の駆動ステージのリセット端子にリセット信号を提供する第1出力端子、及び最後の駆動ステージの制御端子にダミーゲート信号を提供する第2出力端子を含む。

## 【0011】

本発明の一実施形態による表示装置は、複数のゲートライン、複数のデータライン、及び複数のゲートラインと複数のデータラインにより定義された複数の画素領域に各々具備された複数の画素を含み、映像を表示する表示パネル、複数のデータラインにデータ信号を提供するデータドライバ、及び複数のゲートラインにゲート信号を順次出力するゲートドライバを含む。

10

## 【0012】

ゲートドライバは、複数の駆動ステージ、及びダミーステージを含む。

## 【0013】

各駆動ステージは、直前の駆動ステージから直前のキャリー信号を受信する入力端子、直後の駆動ステージから直後のゲート信号を受信する制御端子、現在のゲート信号を出力し、直後の駆動ステージの制御端子に接続された出力端子、現在のキャリー信号を出力し、直後の駆動ステージの入力端子に接続されたキャリー端子、及びリセット信号を受信するリセット端子を含む。

20

## 【0014】

ダミーステージは、最後の駆動ステージから最後のキャリー信号を受信する入力端子、制御信号を受信する制御端子、複数の駆動ステージのリセット端子にリセット信号を提供する第1出力端子、及び最後の駆動ステージの制御端子にダミーゲート信号を提供する第2出力端子を含む。

## 【発明の効果】

## 【0015】

このようなゲートドライバ、及びこれを備えた表示装置によると、ダミーステージは、最後の駆動ステージから受信した最後のキャリー信号に応答して、リセット信号及びダミーゲート信号を出力する。ダミーステージから出力されたリセット信号は、複数の駆動ステージのリセット端子に入力され、ダミーゲート信号は、最後の駆動ステージの制御端子に提供される。

30

## 【0016】

したがって、本発明によれば、最後の駆動ステージに供給されるダミーゲート信号の歪曲を防止でき、その結果、最後の駆動ステージがそのダミーゲート信号により、正常にオフされることで液晶表示パネル上にライン不良が発生することを防止することができる。

40

## 【図面の簡単な説明】

## 【0017】

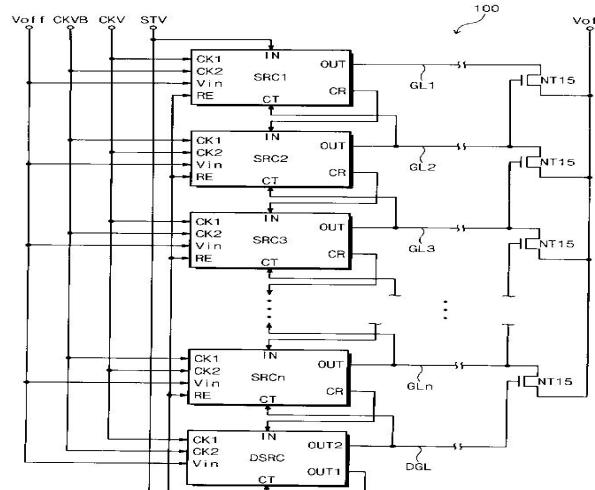

【図1】本発明の実施形態に係るゲートドライバのブロック図である。

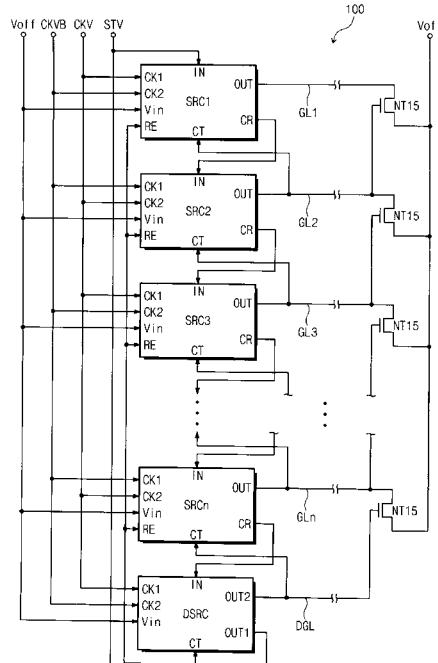

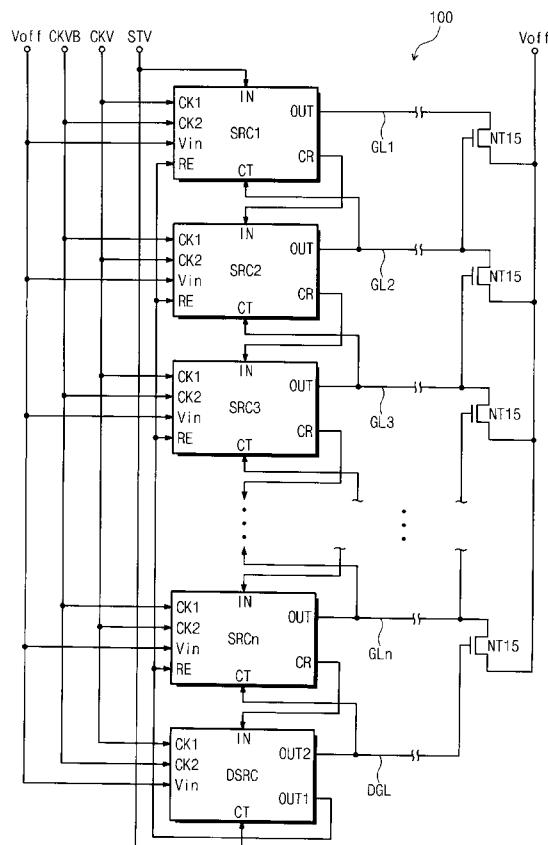

【図2】図1に図示された最後の駆動ステージの回路図である。

【図3】図1に図示されたダミーステージの回路図である。

【図4】従来のゲートドライバから出力されるゲート信号を示す波形図である。

【図5】本発明の実施形態に係るゲートドライバから出力されるゲート信号を示す波形図である。

【図6】本発明の実施形態に係る表示装置の平面図である。

【図7】図6に図示されたゲートラインに印加される信号を示す波形図である。

## 【発明を実施するための形態】

50

## 【0018】

以下、図面を参照して本発明の望ましい実施の形態をより詳細に説明する。

## 【0019】

図1は、本発明の実施形態に係るゲートドライバのブロック図である。

## 【0020】

図1を参照すると、ゲートドライバ100は、互いに連続に接続された複数の駆動ステージSRC1～SRCn、及びダミーステージD SRCからなる一つのシフトレジスタを含む。シフトレジスタは、複数のゲートラインGL1～GLnの第1端部に隣接して具備される。

## 【0021】

各駆動ステージSRC1～SRCnは、入力端子IN、第1及び第2クロック端子CK1、CK2、制御端子CT、電圧入力端子Vin、リセット端子RE、出力端子OUT、及びキャリー端子CRを含む。ダミーステージD SRCは、入力端子IN、第1及び第2クロック端子CK1、CK2、制御端子CT、電圧入力端子Vin、第1出力端子OUT1、及び第2出力端子OUT2を含む。

10

## 【0022】

複数の駆動ステージSRC1～SRCnの入力端子INは、直前のステージのキャリー端子CRに電気的に接続し、直前のキャリー信号を受信する。但し、複数の駆動ステージSRC1～SRCnのうちの最初のステージSRC1の入力端子INには、直前のキャリー信号の代りにゲートドライバ100の駆動を開始する垂直開始信号STVが提供される。複数の駆動ステージSRC1～SRCnの制御端子CTは、直後のステージの出力端子OUTに電気的に接続され、直後のゲート信号を受信する。但し、複数の駆動ステージSRC1～SRCnのうちの最後のステージSRCnの制御端子CTは、ダミーステージD SRCの第2出力端子OUT2に電気的に接続される。本発明の一実施形態では、ダミーステージD SRCの制御端子CTには、直後のステージからの直後のゲート信号の代りに垂直開始信号STVが提供される。

20

## 【0023】

複数の駆動ステージSRC1～SRCnのうちの奇数番目のステージSRC1、SRC3、...、SRCn-1の第1クロック端子CK1には、第1クロックCKVが提供され、第2クロック端子CK2には、第1クロックCKVと反転した位相を有する第2クロックCKVBが提供される。

30

## 【0024】

複数の駆動ステージSRC1～SRCnのうちの偶数番目のステージSRC2、...、SRCnの第1クロック端子CK1には、第2クロックCKVBが提供され、第2クロック端子CK2には、第1クロックCKVが提供される。nが偶数だと仮定すると、ダミーステージD SRCの第1クロック端子CK1には、第1クロックCKVが提供され、第2クロック端子CK2には、第2クロックCKVBが提供される。

40

## 【0025】

複数の駆動ステージSRC1～SRCn及びダミーステージD SRCの電圧入力端子Vinには、ゲートオフ電圧Voffが提供される。ゲートオフ電圧Voffは、グラウンド電圧またはマイナス電圧であってもよい。

## 【0026】

複数の駆動ステージSRC1～SRCnの出力端子OUTには、複数のゲートラインGL1～GLnが電気的に各々接続される。したがって、複数の駆動ステージSRC1～SRCnは、出力端子OUTを通じてゲート信号を順次に出力し、複数のゲートラインGL1～GLnに印加する。

## 【0027】

各駆動ステージSRC1～SRCnのキャリー端子CRは、直後のステージの入力端子INに電気的に接続され、直後のステージにキャリー信号を提供する。最後の駆動ステージSRCnのキャリー端子CRは、ダミーステージD SRCの入力端子INに電気的に接

50

続される。

**【0028】**

ダミーステージD S R C の第1出力端子O U T 1は、複数の駆動ステージS R C 1～S R C nのリセット端子R Eに電気的に接続され、ダミーステージD S R C の第2出力端子O U T 2は、最後の駆動ステージS R C nの制御端子C Tに電気的に接続される。したがって、ダミーステージD S R C は、複数の駆動ステージS R C 1～S R C nのリセット端子R Eにリセット信号を提供し、複数の駆動ステージS R C 1～S R C Nをリセットする。また、ダミーステージD S R C は、最後の駆動ステージS R C nの制御端子C Tにダミー出力信号を提供し、最後の駆動ステージS R C nから出力されるゲート信号を低電圧レベルにする。

10

**【0029】**

各駆動ステージS R C 1～S R C nは、対応するゲートラインG L 1～G L nの第2端部に接続された放電トランジスタN T 1 5を含む。放電トランジスタN T 1 5は、直後のゲートラインに接続された制御電極、ゲートオフ電圧V o f fを受信する入力電極、及び対応するゲートラインに接続された出力電極を含む。したがって、放電トランジスタN T 1 5は、直後のステージから出力された直後のゲート信号に応答して対応するゲートラインをゲートオフ電圧V o f fまで放電させる。

**【0030】**

ここで、最後のゲートラインG L nを放電させる放電トランジスタN T 1 5の制御電極は、ダミーゲートラインD G Lを通じてダミーステージD S R C の第2出力端子O U T 2に電気的に接続される。したがって、最後の放電トランジスタN T 1 5は、ダミーステージD S R C の第2出力端子O U T 2から出力されたダミー出力信号に応答して最後のゲートラインG L nをゲートオフ電圧V o f fまで放電させる。

20

**【0031】**

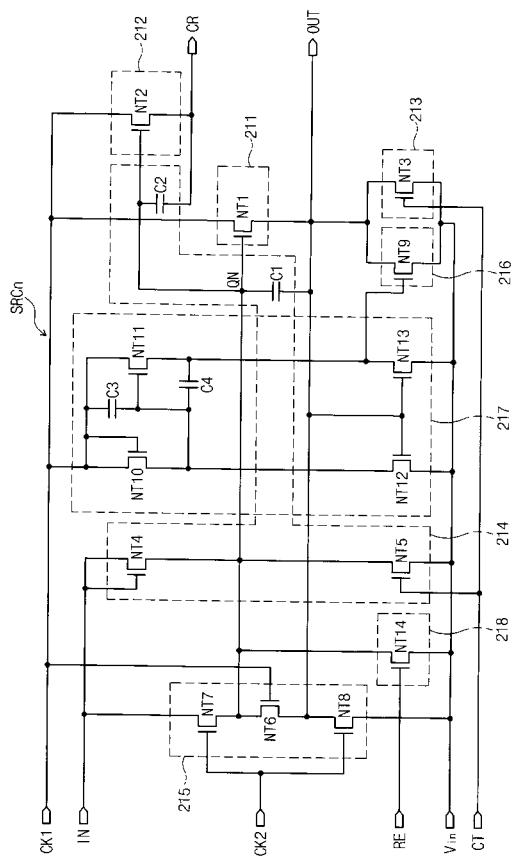

図2は、図1に図示された最後の駆動ステージの回路図である。ゲートドライバ1 0 0に具備される複数の駆動ステージS R C 1～S R C nは、互いに同一な内部構成を有するので、図2で最後の駆動ステージを図示して説明することによって、残りの駆動ステージに対する説明を省略する。

**【0032】**

図2を参照すると、最後の駆動ステージS R C nは、プルアップ部2 1 1、キャリー部2 1 2、プルダウン部2 1 3、プルアップ駆動部2 1 4、リップル防止部2 1 5、ホールディング部2 1 6、インバーター部2 1 7、及びリセット部2 1 8を含む。

30

**【0033】**

プルアップ部2 1 1は、プルアップ駆動部2 1 4の出力端(以下、Q - ノード)Q Nに接続された制御電極、第1クロック端子C K 1に接続された入力電極、及び出力端子O U Tに接続された出力電極からなるプルアップトランジスタN T 1を含む。プルアップトランジスタN T 1は、プルアップ駆動部2 1 4から出力された電圧に応答して、出力端子O U Tを通じて出力される現在のゲート信号を、第1クロック端子C K 1を通じて提供されるクロック(以下、第2クロックC K V B(図1に図示される))のハイレベルまでプルアップさせる。プルアップトランジスタN T 1は、あるフレームにおいて、第2クロックC K V Bのハイ区間(以下、第1区間)の間はオンされ、第1区間の間、現在のゲート信号をハイ状態に維持する。

40

**【0034】**

キャリー部2 1 2は、Q - ノードQ Nに接続された制御電極、第1クロック端子C K 1に接続された入力電極、及びキャリー端子C Rに接続された出力電極からなるキャリートランジスタN T 2を含む。キャリートランジスタN T 2は、プルアップ駆動部2 1 4から出力された電圧に応答して、キャリー端子C Rを通じて出力される現在のキャリー信号を第2クロックC K V Bのハイレベルまでプルアップさせる。キャリートランジスタN T 2は、あるフレームにおいて、第1区間の間はオンされ、第1区間の間、現在のキャリー信号をハイ状態に維持する。

50

## 【0035】

プルダウン部213は、制御端子C Tに接続された制御電極、電圧入力端子V i nに接続された入力電極、及び出力端子O U Tに接続された出力電極からなるプルダウントランジスタN T 3を含む。プルダウントランジスタN T 3は、直後のステージからの直後のゲート信号に応答して、プルアップされた現在のゲート信号を電圧入力端子V i nを通じて供給されたゲートオフ電圧V o f f(図1に図示される)までプルダウンさせる。すなわち、プルダウントランジスタN T 3は、第1区間後に直後のゲート信号によりオンされ、現在のゲート信号をロー状態にプルダウンさせる。

## 【0036】

プルアップ駆動部214は、バッファートランジスタN T 4、第1キャパシターC 1、第2キャパシターC 2、及び放電トランジスタN T 5を含む。バッファートランジスタN T 4は、入力端子I Nに共通に接続された入力電極及び制御電極、及びQ - ノードQ Nに接続された出力電極からなる。第1キャパシターC 1は、Q - ノードQ Nと出力端子O U Tとの間に接続され、第2キャパシターC 2は、キャリートランジスタN T 2の制御電極とキャリー端子C Rとの間に接続される。一方、放電トランジスタN T 5は、バッファートランジスタN T 4の出力電極に接続された入力電極、制御端子C Tに接続された制御電極、及び電圧入力端子V i nに接続された出力電極からなる。

10

## 【0037】

バッファートランジスタN T 4が直前のキャリー信号に応答してオンすると、Q - ノードQ Nの電位が上昇し、プルアップトランジスタN T 1、及びキャリートランジスタN T 2がオンする。オンしたプルアップトランジスタN T 1、及びオンしたキャリートランジスタN T 2により、出力端子O U T、及びキャリー端子C Rの電位が上昇すると、Q - ノードQ Nの電位は、第1及び第2キャパシターC 1、C 2により押し上げられる。したがって、プルアップトランジスタN T 1及びキャリートランジスタN T 2はオン状態を維持し、現在のゲート信号と現在のキャリー信号とは、第2クロックC K V Bの第1区間の間にハイ状態で生成される。

20

## 【0038】

放電トランジスタN T 5が直後のゲート信号に応答してオンすると、第1キャパシターC 1に充電された電荷は、放電トランジスタN T 5を通じてゲートオフ電圧V o f fまで放電される。したがって、Q - ノードQ Nの電位は、ゲートオフ電圧V o f fまで下がり、その結果、プルアップトランジスタN T 1及びキャリートランジスタN T 2は、オフされる。したがって、出力端子O U T及びキャリー端子C Rには、ハイ状態の現在のゲート信号、及び現在のキャリー信号が出力されない。

30

## 【0039】

リップル防止部215は、第1乃至第3リップル防止トランジスタN T 6、N T 7、N T 8からなり、あるフレームのうち、第1区間を除外した第2区間の間、現在のゲート信号及び現在のキャリー信号が第1クロックC K Vまたは第2クロックC K V Bにより、リップルされることを防止する。

40

## 【0040】

第1リップル防止トランジスタN T 6は、第1クロック端子C K 1に接続された制御電極、出力端子O U Tに接続された入力電極、及びQ - ノードQ Nに接続された出力電極を含む。第2リップル防止トランジスタN T 7は、第2クロック端子C K 2に接続された制御電極、入力端子I Nに接続された入力電極、及びQ - ノードQ Nに接続された出力電極からなる。第3リップル防止トランジスタN T 8は、第2クロック端子C K 2に接続された制御電極、出力端子O U Tに接続された入力電極、及び電圧入力端子V i nに接続された出力電極からなる。

40

## 【0041】

第2区間の間、第1リップル防止トランジスタN T 6は、第2クロックC K V Bに応答して出力端子O U Tから出力されたロー状態の現在のゲート信号をQ - ノードQ Nに提供する。したがって、第2区間における第2クロックC K V Bのハイ区間でQ - ノードQ N

50

の電位は、ロー状態に維持される。これにより、第1リップル防止トランジスタNT6は、第2区間における第2クロックCKVBのハイ区間でプルアップトランジスタNT1及びキャリートランジスタNT2がオンされることを防止する。

#### 【0042】

第2区間の間、第2リップル防止トランジスタNT7は、第2クロック端子CK2を通じて提供されたクロック(以下、第1クロックCKV(図1参照))に応答して、入力端子INを通じて入力されるロー状態の直前のキャリー信号をQ-ノードQNに提供する。したがって、第2区間ににおいて、第1クロックCKVのハイ区間でQ-ノードQNの電位は、ロー状態に維持される。この結果、第2リップル防止トランジスタNT7は、第2区間のうち、第1クロックCKVのハイ区間の間、プルアップトランジスタNT1及びキャリートランジスタNT2がオンされることを防止する。10

#### 【0043】

第3リップル防止トランジスタNT8は、第1クロックCKVに応答して、現在のゲート信号をゲートオフ電圧Voffまで放電する。したがって、第3リップル防止トランジスタNT8は、第2区間における第1クロックCKVのハイ区間で現在のゲート信号をゲートオフ電圧Voffに維持する。

#### 【0044】

一方、ホールディング部216は、インバータ部217の出力端に接続された制御電極、電圧入力端子Vinに接続された入力電極、及び出力端子OUTに接続された出力電極からなるホールディングトランジスタNT9を含む。インバータ部217は、第1乃至第4インバータトランジスタNT10、NT11、NT12、NT13と、第3及び第4キャパシターC3、C4とからなり、ホールディングトランジスタNT9をオンまたはオフさせる。20

#### 【0045】

第1インバータトランジスタNT10は、第1クロック端子CK1と共に接続された入力電極及び制御電極、及び第4キャパシターを通じて第2インバータトランジスタNT11の出力電極に接続された出力電極からなる。第2インバータトランジスタNT11は、第1クロック端子CK1に接続された入力電極、第3キャパシターを通じて入力電極と接続された制御電極、及びホールディングトランジスタNT9の制御電極に接続された出力電極からなる。第3インバータトランジスタNT12は、第1インバータトランジスタNT10の出力電極に接続された入力電極、出力端子OUTに接続された制御電極、及び電圧入力端子Vinに接続された出力電極からなる。第4インバータトランジスタNT13は、ホールディングトランジスタNT9の制御電極に接続された入力電極、出力端子OUTに接続された制御電極、及び電圧入力端子Vinに接続された出力電極からなる。30

#### 【0046】

第3及び第4インバータトランジスタNT12、NT13が出力端子OUTを通じて出力されるハイ状態の現在のゲート信号に応答してオンされると、第1及び第2インバータトランジスタNT10、NT11から出力された第2クロックCKVBは、オンした第3及び第4インバータトランジスタNT12、NT13により、ゲートオフ電圧Voffまで放電される。したがって、ホールディングトランジスタNT9は、現在のゲート信号がハイ状態に維持される第1区間の間、オフ状態に維持される。40

#### 【0047】

この後、第2区間で現在のゲート信号がロー状態に転換されると、第3及び第4インバータトランジスタNT12、NT13は、オフされる。したがって、第1及び第2インバータトランジスタNT10、NT11から出力された第2クロックCKVBは、ホールディングトランジスタNT9に印加され、ホールディングトランジスタNT9をオンさせる。結果的に、現在のゲート信号は、ホールディングトランジスタNT9により、第2区間における第2クロックCKVBのハイ区間の間ゲートオフ電圧Voffに維持されてもよい。50

## 【0048】

一方、リセット部218は、リセット端子REに接続された制御電極、プルアップトランジスタNT1の制御電極に接続された入力電極、及び電圧入力端子Vinに接続された出力電極からなるリセットトランジスタNT14を含む。

## 【0049】

リセットトランジスタNT14は、リセット端子REを通じて入力されたダミーステージDSRC(図1に図示される)の第1出力端子から出力されたリセット信号に応答して、Q-ノードQNの電位をゲートオフ電圧Voffまで放電させる。したがって、プルアップトランジスタNT1及びキャリートランジスタNT2がダミーステージDSRCのリセット信号に応答してオフする。図1に図示されたように、ダミーステージDSRCのリセット信号は、n個の駆動ステージSRC1～SRCnのリセット端子REに提供され、各駆動ステージに具備されたプルアップトランジスタNT1及びキャリートランジスタNT2をオフさせ、n個の駆動ステージSRC1～SRCnを全部リセットする。10

## 【0050】

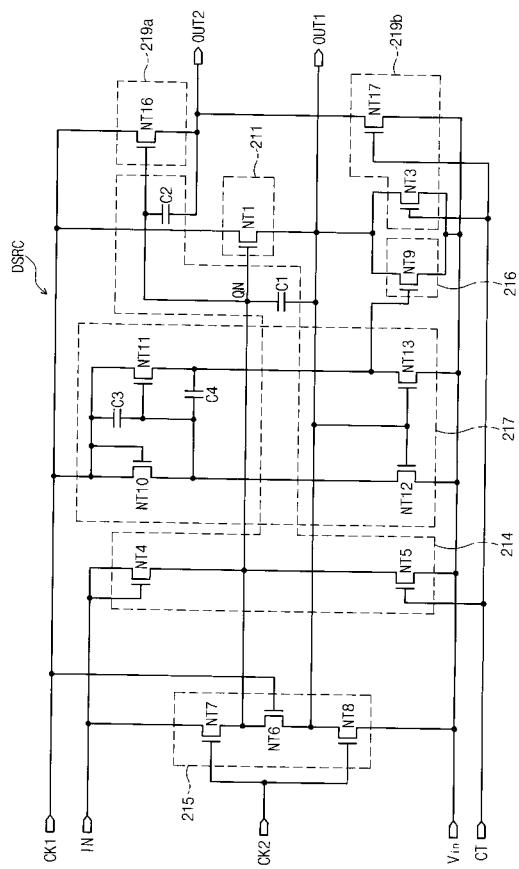

図3は、図1に図示されたダミーステージの回路図である。図3に図示された構成要素のうち、図2に図示された構成要素と同一の構成要素に対しては、同一の符号を使用し、それに対する具体的な説明は省略する。

## 【0051】

図3を参照すると、ダミーステージDSRCは、第1プルアップ部211、第2プルアップ部219a、プルダウン部219b、プルアップ駆動部214、リップル防止部215、ホールディング部216、及びインバーター部217を含む。20

## 【0052】

第1プルアップ部211は、プルアップ駆動部214の出力端(以下、Q-ノード)QNに接続された制御電極、第1クロック端子CK1に接続された入力電極、及び第1出力端子OUT1に接続された出力電極からなる第1プルアップトランジスタNT1を含む。第1プルアップトランジスタNT1は、プルアップ駆動部214から出力された電圧に応答して、第1出力端子OUT1を通じて出力されるリセット電圧を第1クロック端子CK1を通じて提供されたクロック(以下、第1クロックCKV(図1に図示される))のハイレベルまでプルアップさせる。

## 【0053】

第2プルアップ部219aは、Q-ノードQNに接続された制御電極、第1クロック端子CK1に接続された入力電極、及び第2出力端子OUT2に接続された出力電極からなる第2プルアップトランジスタNT16を含む。第2プルアップトランジスタNT16は、プルアップ駆動部214から出力された電圧に応答して、第2出力端子OUT2を通じて出力されるダミーゲート信号を第1クロックCKVのハイレベルまでプルアップさせる。30

## 【0054】

ここで、第2プルアップトランジスタNT16は、第1プルアップトランジスタNT1より小さなサイズを有する。本発明の一例では、第1及び第2プルアップトランジスタNT1、NT16のチャネルの長さが互いに同一だと仮定するとき、第1プルアップトランジスタNT1は、6030μmのチャネル幅を有し、第2プルアップトランジスタNT16は、700μmのチャネル幅を有する。40

## 【0055】

プルダウン部219bは、第1プルダウントランジスタNT3、及び第2プルダウントランジスタNT17を含む。

## 【0056】

第1プルダウントランジスタNT3は、制御端子CTに接続された制御電極、電圧入力端子Vinに接続された入力電極、及び第1出力端子OUT1に接続された出力電極からなる。第2プルダウントランジスタNT17は、制御端子CTに接続された制御電極、電圧入力端子Vinに接続された入力電極、及び第2出力端子OUT2に接続された出力電50

極からなる。

【0057】

第1及び第2プルダウントランジスタNT3、NT17は、垂直開始信号に応答してリセット電圧、及びダミーゲート信号を各々電圧入力端子Vinを通じて供給されたゲートオフ電圧Voffまでプルダウンさせる。

【0058】

ここで、第2プルダウントランジスタNT17は、第1プルダウントランジスタNT3より小さなサイズを有する。本発明の一実施形態では、第1及び第2プルダウントランジスタNT3、NT17のチャネルの長さが互いに同一だと仮定するととき、第1プルダウントランジスタNT3は、 $7000\mu m$ のチャネル幅を有し、第2プルダウントランジスタNT17は、 $700\mu m$ のチャネル幅を有する。

10

【0059】

このように、ダミーステージDSRCで、複数の駆動ステージSRC1～SRCnのリセット端子REに接続される第1出力端子OUT1と最後の駆動ステージSRCnの制御端子CTに接続された第2出力端子OUT2とが分離されて、具備されることにより、最後の駆動ステージSRCnに印加されるダミーゲート信号の出力特性を改善でき、その結果、最後の駆動ステージSRCnから出力されるゲート信号が歪曲されることを防止することができる。

【0060】

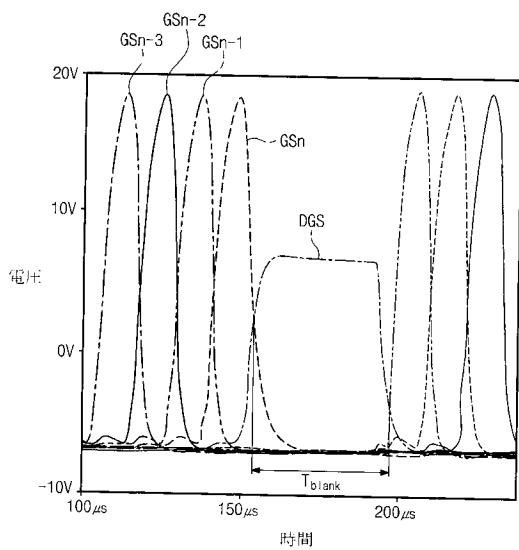

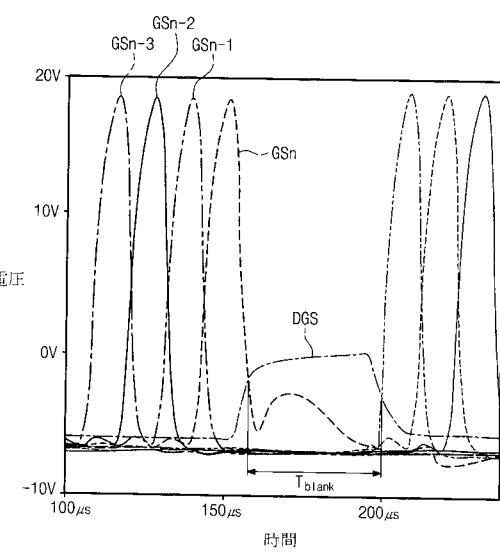

図4は、従来のゲートドライバから出力されるゲート信号を示す波形図であり、図5は、本発明の一実施形態に係るゲートドライバから出力されるゲート信号を示す波形図である。

20

【0061】

図4を参照すると、ダミーステージSRCの出力端子が複数の駆動ステージSRC1～SRCnのリセット端子REと最後の駆動ステージSRCnの制御端子CTとに共通に接続された場合における、最後の駆動ステージSRCnのゲート信号GSnとダミーステージSRCの出力端子から出力されるダミーゲート信号DGsとが図示される。

【0062】

ダミーステージSRCの出力端子が複数の駆動ステージSRC1～SRCnのリセット端子REと最後の駆動ステージ制御端子CTに共通に接続されると、出力端子に接続された負荷が増加する。この負荷により、ダミーゲート信号DGsは、所望のレベル(すなわち、最後の駆動ステージSRCnの制御端子CTに接続されたトランジスタ(例えば、プルダウントランジスタNT3、放電トランジスタNT5、NT15(図1及び図2に図示される))をオンさせるために必要な電圧レベル)まで上昇することができない。その結果、最後の駆動ステージSRCnのゲート信号GSnがブランク区間(Tblank)で望ましくない状態で出力される。

30

【0063】

しかし、ダミーステージSRCが複数の駆動ステージSRC1～SRCnのリセット端子REに接続された第1出力端子OUT1と最後の駆動ステージSRCnの制御端子CTに接続された第2出力端子OUT2とを具備すると、図5に図示されるように、第2出力端子OUT2から出力されるダミーゲート信号DGsは、最後の駆動ステージSRCnの制御端子CTに接続されたトランジスタNT2、NT5、及びNT15の閾値電圧よりも上昇する。したがって、ブランク区間(Tblank)の間に、最後の駆動ステージSRCnのゲート信号GSnがダミーゲート信号DGsにより、正常に放電される。

40

【0064】

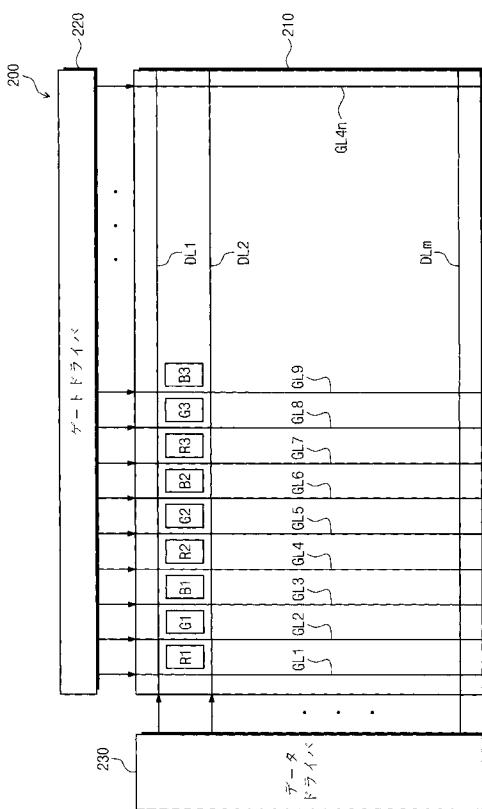

図6は、本発明の他の実施形態に係る表示装置の平面図であり、図7は、図6に図示されたゲートラインに印加されるゲート信号を示す波形図である。

【0065】

図6を参照すると、表示装置200は、映像を表示する表示パネル210、表示パネル210にゲート信号を出力するゲートドライバ220、及び表示パネル210にデータ信

50

号を出力するデータドライバ230を含む。

【0066】

表示パネル210は、下部基板、下部基板と面する上部基板、及び下部基板と上部基板との間に介在された液晶層(図示せず)からなる液晶表示パネルであってもよい。

【0067】

表示パネル210には、複数のゲートラインGL1～GL4n、及び複数のゲートラインGL1～GL4nと絶縁されて交差する複数のデータラインDL1～DLmにより、マトリックス形状の複数の画素領域が定義される。各画素領域には、画素が具備され、画素に対応して一つの色画素が配置される。表示パネル210には、レッド、グリーン、及びブルー色画素R、G、Bが具備されてもよい。

10

【0068】

表示パネル210は、データラインDL1～DLmが延長された方向に長い長方形形状を有し、表示パネル210に具備されるゲートラインGL1～GL4nの個数がデータラインDL1～DLmの個数より多い。色画素R、G、Bは、ゲートライン等GL1～GL4nが延長された方向に長い縦ピクセル形状を有する。

【0069】

ゲートドライバ220は、複数のゲートラインGL1～GL4nに電気的に接続され、複数のゲートラインGL1～GL4nにゲート信号を順次に印加する。データドライバ230は、複数のデータラインDL1～DLmに電気的に接続されて複数のデータラインDL1～DLmにデータ信号を印加する。

20

【0070】

ゲートドライバ220は、表示パネル210に画素を形成する薄膜工程を通じて表示パネル210に直接に形成されてもよく、データドライバ230は、チップの形状を有し、表示パネル210上に実装される。

【0071】

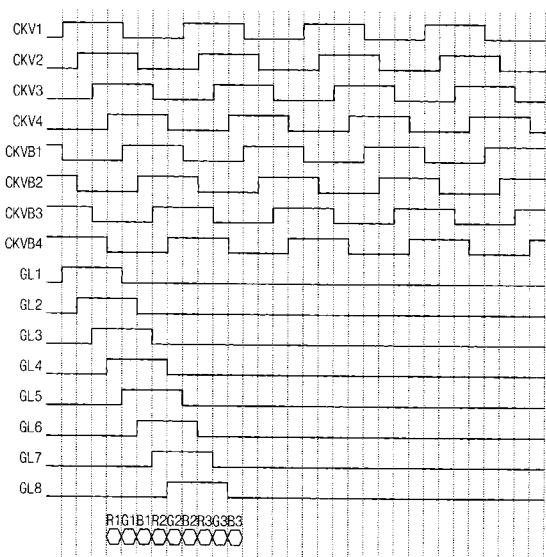

図7を参照すると、ゲートドライバ220には、第1乃至第4クロックCKV1、CKV2、CKV3、CKV4、及び第1乃至第4クロックバーCKVB1、CKVB2、CKVB3、CKVB4が提供される。

【0072】

あるフレームを1F時間だと仮定し、ゲートラインGL1～GL4nが4n個(nは、1以上の正数)からなるとき、第1乃至第4クロックCKV1、CKV2、CKV3、CKV4は、1F/n時間(以下、1H時間)の間ハイ状態を維持し、第2クロックCKV2は第1クロックCKV1より約H/4時間遅延され、第3クロックCKV3は第2クロックCKV2より約H/4時間遅延され、第4クロックCKV4は第3クロックCKV3より約H/4時間遅延される。第1乃至第4クロックバーCKVB1、CKVB2、CKVB3、CKVB4は、第1乃至第4クロックCKV1、CKV2、CKV3、CKV4と各々反転された位相を有する。

30

【0073】

第1乃至第4ゲートラインGL1、GL2、GL3、GL4には、第1乃至第4クロックCKV1、CKV2、CKV3、CKV4のハイ区間に各々対応して生成されたゲート信号が順次印加され、第5乃至第8ゲートラインGL5、GL6、GL7、GL8には、第1乃至第4クロックバーCKVB1、CKVB2、CKVB3、CKVB4のハイ区間に各々対応して生成されたゲート信号が順次印加される。

40

【0074】

図面に図示しないが、ゲートドライバ220は、第1乃至第4クロックCKV1、CKV2、CKV3、CKV4を各々受信し、第1乃至第4クロックバーCKVB1、CKVB2、CKVB3、CKVB4を各々受信する4個のシフトレジスタを含んでもよい。

【0075】

ゲートラインの個数が増加するほど、ゲートドライバ220に具備されるシフトレジスタの個数が増加するが、この場合にも、ダミーステージD SRCは、複数の駆動ステージ

50

のリセット端子 R E に接続された第 1 出力端子 O U T 1 と最後の駆動ステージ S R C n の制御端子 C T に接続された第 2 出力端子 O U T 2 を具備する。

#### 【 0 0 7 6 】

したがって、複数の駆動ステージの個数が増加し、第 1 出力端子 O U T 1 に接続された負荷が増加しても、最後の駆動ステージ S R C n に印加されるダミーゲート信号の歪曲は発生しない。したがって、ダミーゲート信号により、最後の駆動ステージ S R C n は正常にオフすることができ、その結果、最後の駆動ステージ S R C n の誤動作により表示パネル 210 上にライン不良が発生することを防止することができる。

#### 【 0 0 7 7 】

以上、本発明の実施形態を参照して説明したが、本発明が属する技術分野において通常の知識を有する者であれば、本発明は上述の実施形態に限定されるものではなく、特許請求の範囲に記載される本発明の思想、及び領域から抜け出さない範囲の内で、本発明を多様に修正、及び変更することができる。

#### 【 符号の説明 】

#### 【 0 0 7 8 】

1 0 0 、 2 2 0 ゲートドライバ

2 0 0 表示装置

2 1 0 表示パネル

2 3 0 データドライバ

10

【 図 1 】

【 図 2 】

【図3】

【 図 5 】

【 四 4 】

【 四 6 】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |        |         |

|---------|--------|---------|

| G 0 2 F | 1/1345 |         |

| G 0 2 F | 1/133  | 5 5 0   |

| G 0 9 G | 3/20   | 6 2 2 A |

| G 0 9 G | 3/20   | 6 2 2 G |

| G 0 9 G | 3/20   | 6 2 1 J |

(72)発明者 金 晶 日

大韓民国忠 清 南道牙山市排芳面葛梅里排芳 X i i 1次アパートメント106棟103号

F ターム(参考) 2H092 GA59 JA24 NA25 PA06

|       |      |      |      |      |      |      |                |

|-------|------|------|------|------|------|------|----------------|

| 2H093 | NA16 | NC09 | NC10 | NC12 | NC22 | NC34 | ND37           |

| 2H193 | ZA04 | ZF22 | ZF36 |      |      |      |                |

| 5C006 | AA22 | AC22 | AF52 | AF59 | BC03 | BF49 | FA16           |

| 5C080 | AA10 | BB05 | CC03 | DD09 | FF07 | JJ02 | JJ03 JJ04 JJ05 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 栅极驱动器和具有该栅极驱动器的显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2010020279A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2010-01-28 |

| 申请号            | JP2009003061                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2009-01-09 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 權英根<br>金晶日                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 權英根<br>金晶日                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/1345 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G3/3677 G09G2310/0286 G11C19/28                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/36 G09G3/20.670.E G09G3/20.622.D G09G3/20.680.G G09G3/20.621.M G02F1/1345 G02F1/133.550 G09G3/20.622.A G09G3/20.622.G G09G3/20.621.J G11C19/00 G11C19/00.G G11C19/00.H G11C19/00.J G11C19/28.D G11C19/28.230                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H092/GA59 2H092/JA24 2H092/NA25 2H092/PA06 2H093/NA16 2H093/NC09 2H093/NC10 2H093/NC12 2H093/NC22 2H093/NC34 2H093/ND37 2H193/ZA04 2H193/ZF22 2H193/ZF36 5C006/AA22 5C006/AC22 5C006/AF52 5C006/AF59 5C006/BC03 5C006/BF49 5C006/FA16 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD09 5C080/FF07 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 2H193/ZB02 2H193/ZC25 2H193/ZF21 2H193/ZF23 2H193/ZF31 2H193/ZF44 5B074/AA01 5B074/CA01 5B074/DA02 5B074/DA03 5B074/DB01 5B074/EA01 |         |            |

| 优先权            | 1020080066228 2008-07-08 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

### 摘要(译)

要解决的问题：提供防止故障的栅极驱动器，并提供具有栅极驱动器的显示器件。解决方案：本发明涉及栅极驱动器和具有该栅极驱动器的显示装置，其中虚拟级响应于从最后一个驱动级接收的最后一个进位信号输出复位信号和伪栅极信号。从虚设级输出的复位信号被输入到多个驱动级中的每一个的复位端子，并且伪栅极信号被提供给最后驱动级的控制端子。因此，防止了提供给最后驱动级的伪栅极信号失真，从而通过伪栅极信号将最后的驱动级关闭到正常状态，从而防止在液晶显示板上发生线缺陷。