(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-204119

(P2019-204119A)

(43) 公開日 令和1年11月28日(2019.11.28)

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>G02F 1/1368 (2006.01)</b> | G02F 1/1368 | 2 H 1 9 2   |

| <b>G09F 9/30 (2006.01)</b>   | G09F 9/30   | 3 3 8       |

| <b>H01L 51/50 (2006.01)</b>  | G09F 9/30   | 3 6 5       |

| <b>H05B 33/14 (2006.01)</b>  | H05B 33/14  | 5 C 0 9 4   |

|                              | H05B 33/14  | A           |

|                              |             | Z           |

審査請求 有 請求項の数 6 O L (全 80 頁)

|                                                                                                                                                                    |                                   |          |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|---------------------|

| (21) 出願番号                                                                                                                                                          | 特願2019-146059 (P2019-146059)      | (71) 出願人 | 000153878           |

| (22) 出願日                                                                                                                                                           | 令和1年8月8日 (2019.8.8)               |          | 株式会社半導体エネルギー研究所     |

| (62) 分割の表示                                                                                                                                                         | 特願2018-82970 (P2018-82970)<br>の分割 |          | 神奈川県厚木市長谷398番地      |

| 原出願日                                                                                                                                                               | 平成19年5月17日 (2007.5.17)            | (72) 発明者 | 吉田 泰則               |

| (31) 優先権主張番号                                                                                                                                                       | 特願2006-155459 (P2006-155459)      |          | 神奈川県厚木市長谷398番地 株式会社 |

| (32) 優先日                                                                                                                                                           | 平成18年6月2日 (2006.6.2)              |          | 半導体エネルギー研究所内        |

| (33) 優先権主張国・地域又は機関                                                                                                                                                 | 日本国 (JP)                          | (72) 発明者 | 木村 肇                |

|                                                                                                                                                                    |                                   |          | 神奈川県厚木市長谷398番地 株式会社 |

|                                                                                                                                                                    |                                   |          | 半導体エネルギー研究所内        |

| F ターム (参考) 2H192 AA24 BB13 BB53 BB73 BB82<br>CB05 CC04 CC55 DA32 EA22<br>EA43 GD61 JA32<br>3K107 AA01 AA05 BB01 CC02 CC14<br>CC31 DD03 DD21 DD26 DD39<br>FF15 HH04 |                                   |          |                     |

最終頁に続く

## (54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】暗画像を挿入して擬似的にインパルス駆動に近づける方法において、消費電力の増大や、発光時の負荷の増大などの問題が低減された表示装置およびその駆動方法を提供することを課題とする。

【解決手段】1フレーム期間を複数のサブフレーム期間に分割して階調を表現する表示装置であって、1フレーム期間は、少なくとも第1のサブフレーム期間と、第2のサブフレーム期間とに分割され、最大の階調を表示するときの第1のサブフレーム期間における輝度を  $L_{max} \times 1$  とし、最大の階調を表示するときの第2のサブフレーム期間における輝度を  $L_{max} \times 2$  としたとき、1フレーム期間において、 $(1/2)L_{max} \times 2 < L_{max} \times 1 < (9/10)L_{max} \times 2$  を満たすように設ける。

【選択図】図 1

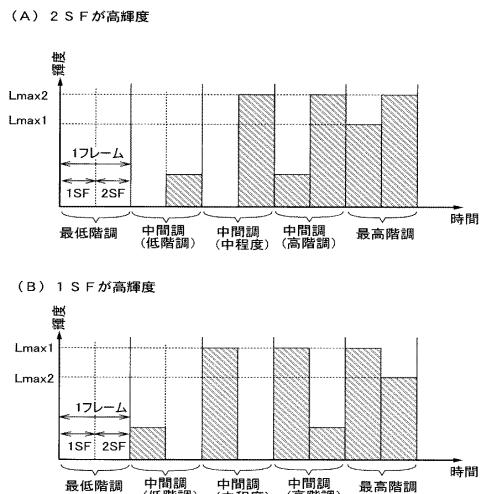

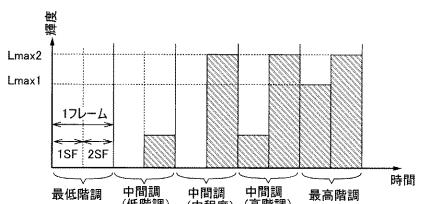

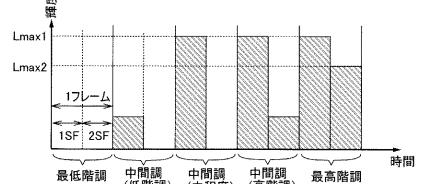

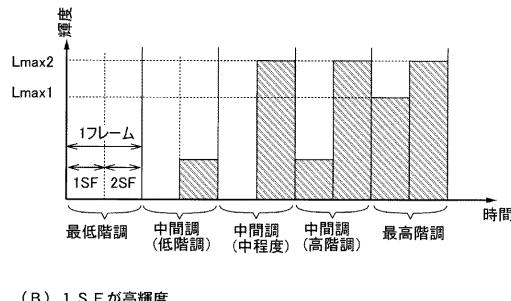

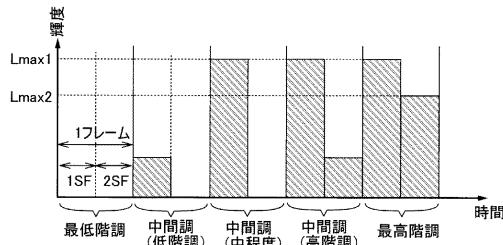

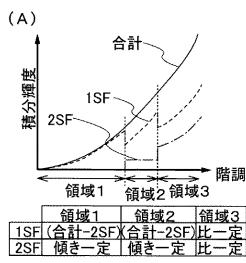

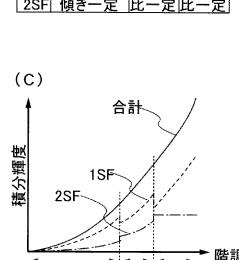

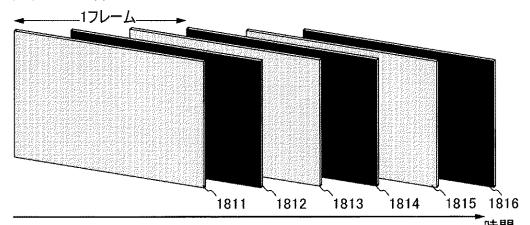

(A) 2SFが高輝度

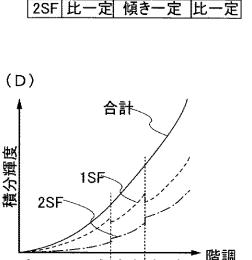

(B) 1SFが高輝度

**【特許請求の範囲】****【請求項 1】**

画素部を有する液晶表示装置であって、

液晶層と、

前記液晶層の下方に設けられた画素電極及び共通電極と、

前記画素電極と電気的に接続するトランジスタと、

前記トランジスタの半導体層と重なる幅広な領域を備えた走査線と、

前記共通電極と電気的に接続する配線と、を有し、

前記配線は、前記画素部において、前記共通電極と接する幅広な領域を有する、液晶表示装置。

10

**【請求項 2】**

請求項 1において、

前記トランジスタのゲートが電気的に接続する走査線を有し、

前記配線は、前記画素部において、前記走査線と同じ方向に延伸し、

前記幅広な領域は、平面視において、片側のみに突出した領域である、液晶表示装置。

**【請求項 3】**

請求項 2において、

前記配線は、平面視において、前記走査線と重ならない、液晶表示装置。

20

**【請求項 4】**

画素部を有する液晶表示装置であって、

液晶層と、

前記液晶層の下方に設けられた画素電極及び共通電極と、

前記画素電極と電気的に接続するトランジスタと、

複数の走査線と、

平面視において隣り合う 2 本の前記走査線の間に配置され、前記共通電極と電気的に接続された配線と、を有し、

前記隣り合う 2 本の走査線の一方は、前記トランジスタの半導体層と重なる幅広な領域を有し、

前記画素電極は、平面視において、前記隣り合う 2 本の走査線の間に配置され、

前記配線は、前記画素部において、前記共通電極と接する幅広な領域を有する、液晶表示装置。

30

**【請求項 5】**

請求項 4において、

前記配線は、前記画素部において、前記隣り合う 2 本の走査線の一方と同じ方向に延伸し、

前記幅広な領域は、平面視において、片側のみに突出した領域である、液晶表示装置。

**【請求項 6】**

請求項 5において、

前記配線は、前記隣り合う 2 本の走査線のいずれにも重ならない、液晶表示装置。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、装置およびその駆動方法に関する。具体的には、半導体装置およびその駆動方法に関する。さらに具体的には、表示装置およびその駆動方法、特にホールド駆動による動画像の画質を向上する方法に関する。

**【背景技術】****【0002】**

近年、薄型の表示装置に対する関心が高まっている。CRTディスプレイに代わり、液晶ディスプレイ、プラズマディスプレイ、プロジェクションディスプレイなどが開発され、普及してきた。さらに、フィールドエミッショングラスレスディスプレイ、無機エレクトロルミネセ

50

ンスディスプレイ、有機エレクトロルミネセンスディスプレイ、電子ペーパーなどが、次世代の表示装置として開発が進められている。

#### 【0003】

上述したような表示装置に備えられた表示部には、画像を構成する最小単位である画素が並置される。そして、それぞれの画素が、画像データにしたがった輝度で発光することで、表示部に画像が形成される。

#### 【0004】

このような表示装置を用いて動画像を表示させるときは、異なる画像を、1秒間に数十回、素早く表示させることで行う。この、画像を表示する周期のことを、1フレーム期間と呼ぶ。

10

#### 【0005】

ここで、表示装置の駆動方法は、画素の輝度が、1フレーム期間内に、どのような時間的分布を持っているかという観点でも分類できる。アクティブマトリクス型の表示装置に代表されるホールド駆動は、1フレーム期間内で、画素の輝度は一定である。一方、CRTに代表されるインパルス駆動は、1フレーム期間内に一度強く発光した後、画素の輝度は直ちに減衰して発光しなくなる。インパルス駆動時、1フレーム期間の大半は非発光状態である。

#### 【0006】

近年の研究により、ホールド駆動には、動画像表示時に輪郭がぼやけたり、動きが不自然に見えてしまうという、本質的問題が存在することが明らかになってきている。この問題は、インパルス駆動の表示装置には存在しない。また、このようなホールド駆動特有の問題を解決するため、1フレーム期間内に一定の期間、何も表示しない黒画像を表示することで、擬似的にインパルス駆動に近づける方法が公開されている。（例えば、特許文献1、特許文献2）また、擬似的にインパルス駆動を実現する別の方法として、非特許文献1が公開されている。これは、1フレーム期間を2つのサブフレーム期間に分け、低階調領域では1フレームの中の後側に位置するサブフレームのみを発光させ、高階調領域では1フレームの中の後側に位置するサブフレームを発光させつつ、1フレームの中の前側に位置するサブフレームを発光させることで、擬似的にインパルス駆動を実現する方法である。

20

#### 【先行技術文献】

30

#### 【特許文献】

#### 【0007】

【特許文献1】特開平9-325715

【特許文献2】特開2000-200063

【非特許文献1】SID'05 DIGEST, 60.2, pp1734, (2005)

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

特許文献1、特許文献2における、黒画像を挿入して擬似的にインパルス駆動に近づける方法は、動画像の画質向上に効果的であるが、黒挿入によって平均輝度が低下する問題がある。また、低下した平均輝度を、黒画像を挿入する前の輝度に戻すためには、画素の瞬間の輝度を大きくする必要があり、そうすると、消費電力の増大や、発光時の負荷の増大を招くという問題がある。

40

#### 【0009】

また、非特許文献1によって公開されている方法においては、明るい階調を表示した後に、また明るい階調を表示する場合において、動画像の画質向上の効果が小さい。特に、最高輝度近傍の輝度で表示される動画像の画質向上の効果は、ほとんど期待できない。なぜなら、この場合は、明るい輝度で光り続けるため、ホールド駆動と同じような駆動となってしまうからである。

#### 【0010】

50

したがって、筆者らはこのような問題に鑑み、黒画像を挿入して擬似的にインパルス駆動に近づける方法において、消費電力の増大や、発光時の負荷の増大などの問題が低減された表示装置およびその駆動方法を提供することを課題とした。また、明るい階調を表示する場合においても、動画像の画質向上の効果の大きい表示装置およびその駆動方法を提供することを課題とした。

#### 【課題を解決するための手段】

##### 【0011】

上記課題を解決する表示装置は、1フレーム期間を複数のサブフレーム期間に分割して階調を表現する表示装置であって、1フレーム期間は、少なくとも第1のサブフレーム期間と、第2のサブフレーム期間とに分割され、最大の階調を表示するときの第1のサブフレーム期間における輝度を  $L_{max1}$  とし、最大の階調を表示するときの第2のサブフレーム期間における輝度を  $L_{max2}$  としたとき、1フレーム期間において、 $(1/2)L_{max2} < L_{max1} < (9/10)L_{max2}$  を満たすことを特徴としている。

10

##### 【0012】

上記課題を解決する表示装置の駆動方法は、複数の表示素子を並置して画像を表示する表示装置の駆動方法であって、1フレーム期間は、第1のサブフレーム期間と、第2のサブフレーム期間と、に分割され、最大の階調を表示するときにおける、第1のサブフレーム期間における輝度を  $L_{max1}$  とし、最大の階調を表示するときにおける、第2のサブフレーム期間における輝度を  $L_{max2}$  としたとき、 $(1/2)L_{max2} < L_{max1} < (9/10)L_{max2}$  が成り立つことを特徴とする。このような特徴を有することにより、ホールド時間を短縮するとともに、発光時の負荷が少ない液晶表示装置あるいは半導体装置の駆動方法を得ることができるので、前述した課題を解決することができる。

20

##### 【0013】

また、上記課題を解決する表示装置の駆動方法は、複数の表示素子を並置して画像を表示する表示装置の駆動方法であって、1フレーム期間は、第1のサブフレーム期間と、第2のサブフレーム期間と、に分割され、最大の階調を表示するときにおける、第1のサブフレーム期間における輝度を  $L_{max1}$  とし、最大の階調を表示するときにおける、第2のサブフレーム期間における輝度を  $L_{max2}$  としたとき、 $(1/2)L_{max1} < L_{max2} < (9/10)L_{max1}$  が成り立つことを特徴とする。このような特徴を有することにより、ホールド時間を短縮するとともに、発光時の負荷が少ない液晶表示装置あるいは半導体装置の駆動方法を得ることができるので、前述した課題を解決することができる。

30

##### 【0014】

また、上記課題を解決する表示装置の駆動方法は、複数の表示素子を並置して画像を表示する表示装置の駆動方法であって、1フレーム期間は、第1のサブフレーム期間と、第2のサブフレーム期間と、に分割され、表示できる階調は、n個（nは2以上の整数）に分割された階調領域で構成され、n個に分割された階調領域のそれぞれが、第1のサブフレーム期間と、第2のサブフレーム期間のいずれか一方において、階調変化に対する輝度変化が一定である階調領域と、第1のサブフレーム期間における輝度と、第2のサブフレーム期間における輝度との比が、階調に対して一定である階調領域と、のいずれかの性質をもつことを特徴とする。このような特徴を有することにより、ホールド時間を短縮するとともに、発光時の負荷が少ない液晶表示装置あるいは半導体装置の駆動方法を得ることができるので、前述した課題を解決することができる。

40

##### 【0015】

また、上記課題を解決する表示装置の駆動方法は、上記した表示装置の駆動方法において、1フレーム期間は、第1のサブフレーム期間と、第2のサブフレーム期間と、第3のサブフレーム期間と、に分割され、第3のサブフレーム期間における最大の輝度を  $L_{max3}$  としたとき、 $L_{max3}$  は、第1のサブフレーム期間の最大輝度および第2のサブフレーム期間の最大輝度の10分の1以下であることを特徴とする。このような特徴を有する

50

ことにより、ホールド時間を短縮するとともに、発光時の負荷が少ない液晶表示装置あるいは半導体装置の駆動方法を得ることができるので、前述した課題を解決することができる。

#### 【0016】

なお、スイッチは、様々な形態のものを用いることができ、一例として、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トランジスタでもよいし、ダイオード（P Nダイオード、P I Nダイオード、ショットキーダイオード、ダイオード接続のトランジスタなど）でもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、L D D領域を設けているものやマルチゲート構造にしているもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源（V<sub>ss</sub>、G N D、0 Vなど）に近い状態で動作する場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源（V<sub>dd</sub>など）に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして、動作させやすいからである。なお、Nチャネル型とPチャネル型の両方を用いて、C M O S型のスイッチにしてもよい。C M O S型のスイッチにすると、スイッチを介して出力する電圧（つまりスイッチへの入力電圧）が、出力電圧に対して、高かったり、低かったりして、状況が変化する場合においても、適切に動作させることができる。

10

20

30

40

#### 【0017】

なお、接続されているとは、電気的に接続されている場合と機能的に接続されている場合と直接接続されている場合とを含むものとする。したがって、所定の接続関係以外のものも含むものとする。例えば、ある部分とある部分との間に、電気的な接続を可能とする素子（例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど）が1個以上配置されていてもよい。また、機能的な接続を可能とする回路（例えば、論理回路（インバータやN A N D回路やN O R回路など）や信号変換回路（D A変換回路やA D変換回路やガンマ補正回路など）や電位レベル変換回路（昇圧回路や降圧回路などの電源回路やH信号やL信号の電位レベルを変えるレベルシフタ回路など）や電圧源や電流源や切り替え回路や增幅回路（オペアンプや差動增幅回路やソースフォロワ回路やバッファ回路など、信号振幅や電流量などを大きく出来る回路など）や信号生成回路や記憶回路や制御回路など）が間に1個以上配置されていてもよい。あるいは、間に他の素子や他の回路を挟まずに、直接接続されて、配置されていてもよい。

なお、素子や回路を間に介さずに接続されている場合のみを含む場合は、直接接続されている、と記載するものとする。また、電気的に接続されている、と記載する場合は、電気的に接続されている場合（つまり、間に別の素子を挟んで接続されている場合）と機能的に接続されている場合（つまり、間に別の回路を挟んで接続されている場合）と直接接続されている場合（つまり、間に別の素子や別の回路を挟まずに接続されている場合）とを含むものとする。

#### 【0018】

なお、表示素子や表示装置や発光素子や発光装置は、様々な形態を用いたり、様々な素子を有することができる。例えば、表示素子や表示装置や発光素子や発光装置としては、E L素子（有機E L素子、無機E L素子又は有機物及び無機物を含むE L素子）、電子放出素子、液晶素子、電子インク、グレーティングライトバルブ（G L V）、プラズマディスプレイ（P D P）、デジタルマイクロミラーデバイス（D M D）、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、E L素子を用いた表示装置としてはE Lディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッショニングディスプレイ（F

50

ED) や SED 方式平面型ディスプレイ (SED: Surface-conductio n Electron-emitter Display) など、液晶素子を用いた表示装置としては液晶ディスプレイ、透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、電子インクを用いた表示装置としては電子ペーパーがある。

#### 【0019】

なお、トランジスタは、様々な形態のトランジスタを適用させることが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、例えば、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を有する薄膜トランジスタ (TFT) などを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、低コストで製造できたり、大型基板上に製造できたり、透光性を有する基板上に製造できたり、トランジスタで光を透過させたりすることが出来る。また、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを適用することが出来る。これらにより、バラツキの少ないトランジスタを製造できたり、電流供給能力の高いトランジスタを製造できたり、サイズの小さいトランジスタを製造できたり、消費電力の少ない回路を構成することが出来る。また、ZnO、a-InGaZnO、SiGe、GaAsなどの化合物半導体を有するトランジスタや、さらに、それらを薄膜化した薄膜トランジスタなどを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、室温で製造できたり、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成することが出来る。また、インクジェットや印刷法を用いて作成したトランジスタなどを適用することが出来る。これらにより、室温での製造、真密度の低い状態での製造、大型基板での製造が可能となる。また、マスク(レチクル)を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。また、有機半導体やカーボンナノチューブを有するトランジスタ、その他のトランジスタを適用することができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などに配置することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。これらの基板を用いることにより、特性のよいトランジスタの形成や、消費電力の小さいトランジスタの形成や、壊れにくい装置とすることや、耐熱性を持たせることが出来る。

#### 【0020】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート電極が2個以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。マルチゲート構造にすることにより、オフ電流を低減することや、トランジスタの耐圧を向上させて信頼性を良くすることや、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることなどができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値を大きくすることや、空乏層ができやすくなってS値を小さくすることができる。チャネルの上下にゲート電極が配置されると、複数のトランジスタが並列に接続されたような構成となる。

また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれてもよいし、並列に接続されてもよいし、直列に接続されていてもよい。また、チャネル(もしくはその一部)にソ-

10

20

30

40

50

ス電極やドレイン電極が重なっていてもよい。チャネル（もしくはその一部）にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流を低減することや、トランジスタの耐圧を向上させて信頼性を良くすることや、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

#### 【0021】

なお、トランジスタは、様々なタイプを用いることができ、様々な基板上に形成させることができる。したがって、回路の全てが、ガラス基板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし、単結晶基板に形成されていてもよいし、SOI基板上に形成されていてもよいし、どのような基板上に形成されていてもよい。回路の全てが同じ基板上に形成されていることにより、部品点数を減らしてコストの低減や、回路部品との接続点数を減らして信頼性の向上を達成することができる。あるいは、回路の一部が、ある基板に形成されており、回路の別の一部が、別の基板に形成されていてもよい。つまり、回路の全てが同じ基板上に形成されていなくてもよい。例えば、回路の一部は、ガラス基板上にトランジスタを用いて形成し、回路の別の一部は、単結晶基板上に形成し、そのICチップをCOG (Chip On Glass) で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB (Tape Automated Bonding) やプリント基板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らしてコストの低減や、回路部品との接続点数を減らして信頼性の向上を達成することができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力の向上を防ぐことができる。

10

20

30

40

#### 【0022】

なお、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R（赤）G（緑）B（青）の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。なお、色要素は、三色に限定されず、それ以上の数を用いても良いし、RGB以外の色を用いても良い。例えば、白色を加えて、RGBW（Wは白）としてもよい。また、RGBに、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色などを一色以上追加したものでもよい。また、例えばRGBの中の少なくとも一色について、類似した色を追加してもよい。例えば、R、G、B1、B2としてもよい。B1とB2とは、どちらも青色であるが、少し周波数が異なっている。このような色要素を用いることにより、より実物に近い表示を行うことができたり、消費電力を低減することが出来る。また、別の例としては、1つの色要素について、複数の領域を用いて明るさを制御する場合は、その領域一つ分を一画素とする。よって、一例としては、面積階調を行う場合、一つの色要素につき、明るさを制御する領域が複数あり、その全体で階調を表現するわけであるが、明るさを制御する領域の一つ分を一画素とする。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。また、その場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。また、一つの色要素につき複数ある、明るさを制御する領域において、つまり、一つの色要素を構成する複数の画素において、各々に供給する信号を僅かに異ならせるようにして、視野角を広げるようにしてよい。

なお、一画素（三色分）と記載する場合は、RとGとBの三画素分を一画素と考える場合であるとする。一画素（一色分）と記載する場合は、一つの色要素につき、複数の画素がある場合、それらをまとめて一画素と考える場合であるとする。

#### 【0023】

なお、画素は、マトリクス状に配置（配列）されている場合を含んでいる。ここで、画素がマトリクスに配置（配列）されているとは、縦方向もしくは横方向において、直線上に

50

並んで配置されている場合や、ギザギザな線上に並んでいる場合を含んでいる。よって、例えば三色の色要素（例えば R G B ）でフルカラー表示を行う場合に、ストライプ配置されている場合や、三つの色要素のドットがいわゆるデルタ配置されている場合も含むものとする。さらに、ベイヤー配置されている場合も含んでいる。なお、色要素は、三色に限らず、それ以上でもよく、例えば、R G B W ( W は白 ) や、R G B に、イエロー、シアン、マゼンタなどを一色以上追加したものなどがある。また、色要素のドット毎にその表示領域の大きさが異なっていてもよい。これにより、消費電力を低下させたり、表示素子の寿命を延ばすことが出来る。

#### 【 0 0 2 4 】

なお、トランジスタとは、それぞれ、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第 1 端子、第 2 端子と表記する場合がある。

なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第 1 端子、第 2 端子と表記する場合がある。

#### 【 0 0 2 5 】

なお、ゲートとは、ゲート電極とゲート配線（ゲート線またはゲート信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域や LDD ( Light ly Doped Drain ) 領域などを形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。ゲート配線とは、各画素のゲート電極の間の接続や、ゲート電極と別の配線とを接続するための配線のことを言う。

#### 【 0 0 2 6 】

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能することになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

#### 【 0 0 2 7 】

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル領域とオーバーラップしていなかったり、別のゲート電極と接続させる機能を有してなかったりする場合がある。しかし、製造プロセスの条件などの関係で、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線とつながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んでも良い。

#### 【 0 0 2 8 】

また、例えば、マルチゲートのトランジスタにおいて、1 つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1 つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。

また、例えば、ゲート電極とゲート配線とを接続してさせている部分の導電膜も、ゲート

10

20

30

40

50

電極と呼んでも良いし、ゲート配線と呼んでも良い。

【0029】

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域について、その一部分のことを言う。

【0030】

なお、ソースとは、ソース領域とソース電極とソース配線（ソース線またはソース信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物（ボロンやガリウムなど）やN型不純物（リンやヒ素など）が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD（Lightly Doped Drain）領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間の接続や、ソース電極と別の配線とを接続するための配線のことを言う。

10

【0031】

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能することになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

20

【0032】

また、ソース電極と同じ材料で形成され、ソース電極とつながっている領域や、ソース電極とソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、ソース配線と呼んでも良い。このような領域は、厳密な意味では、別のソース電極と接続させる機能を有していたりすることがある。しかし、製造プロセスの条件などの関係で、ソース電極やソース配線と同じ材料で形成され、ソース電極やソース配線とつながっている領域がある。よって、そのような領域もソース電極やソース配線と呼んでも良い。

30

【0033】

また、例えば、ソース電極とソース配線とを接続してさせている部分の導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

【0034】

なお、ソース端子とは、ソース領域の領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。

【0035】

なお、ドレインについては、ソースと同様である。

【0036】

なお、半導体装置とは半導体素子（トランジスタやダイオードなど）を含む回路を有する装置をいう。また、半導体特性を利用することで機能しうる装置全般でもよい。また、表示装置とは、表示素子（液晶素子や発光素子など）を有する装置のことを言う。なお、液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が同一基板上に形成された表示パネル本体のことでもよい。また、ワイヤボンディングやバンプなどによって基板上に配置された周辺駆動回路、いわゆるチップオングラス（COG）を含んでいても良い。さらに、フレキシブルプリントサーキット（FPC）やプリント配線基盤（PWB）が取り付けられたもの（ICや抵抗素子や容量素子やインダクタやトランジスタなど）も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライトユニット（導光板やプリズムシートや拡散シート）

40

50

トや反射シートや光源（ＬＥＤや冷陰極管など）を含んでいても良い）を含んでいても良い。また、発光装置とは、特にＥＬ素子やＦＥＤで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。

### 【0037】

なお、ある物の上に形成されている、あるいは、～上に形成されている、というように、～の上に、あるいは、～上に、という記載については、ある物の上に直接接していることに限定されない。直接接してはいない場合、つまり、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上に（もしくは層A上に）、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。また、～の上方に、という記載についても同様であり、ある物の上に直接接していることに限定されず、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、～の下に、あるいは、～の下方に、の場合についても、同様であり、直接接している場合と、接していない場合とを含むこととする。

### 【発明の効果】

### 【0038】

動画像の画質を向上するために行なう黒挿入によって、平均輝度が低下する問題を解決できるため、消費電力を低減し、発光時の負荷を低減することができる。

### 【0039】

また、明るい階調を表示した後に、また明るい階調を表示する場合において、動画像の画質向上の効果を大きくすることができる。特に、最高輝度近傍の輝度で表示される動画像の画質を向上することができる。

### 【図面の簡単な説明】

### 【0040】

【図1】本発明の一形態を説明する図。

【図2】本発明の説明に使用する語句を説明する図。

【図3】本発明の一形態を説明する図。

【図4】本発明の一形態を説明する図。

【図5】本発明の一形態を説明する図。

【図6】本発明の一形態を説明する図。

【図7】本発明の一形態を説明する図。

【図8】本発明の一形態を説明する図。

【図9】本発明の一形態を説明する図。

【図10】本発明の一形態を説明する図。

【図11】本発明の一形態を説明する図。

【図12】本発明の一形態を説明する図。

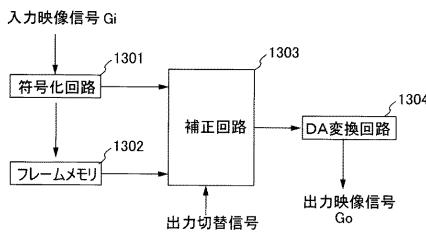

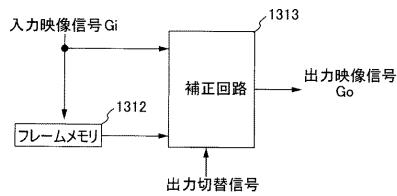

【図13】本発明に適用できる表示装置の駆動方法の一を説明する図。

【図14】本発明に適用できる表示装置の駆動方法の一を説明する図。

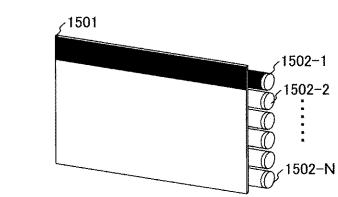

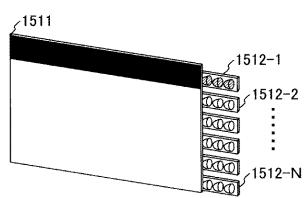

【図15】本発明に適用できる表示装置の駆動方法の一を説明する図。

【図16】本発明に適用できる表示装置の駆動方法の一を説明する図。

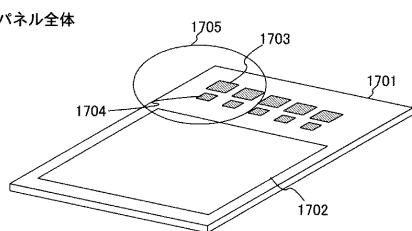

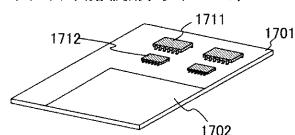

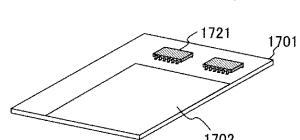

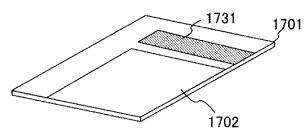

【図17】本発明に適用できる表示装置の回路実装方法の一を説明する図。

【図18】本発明に適用できる表示装置の駆動方法の一を説明する図。

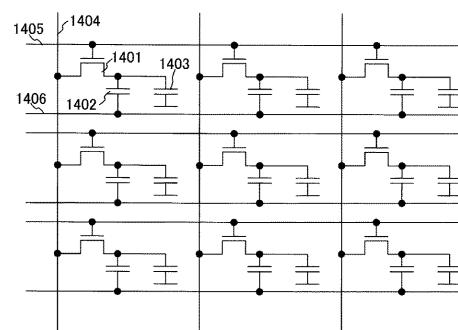

【図19】本発明に適用できる表示装置の表示部の構造の一を説明する図。

【図20】本発明に適用できる表示装置の表示部の構造の一を説明する図。

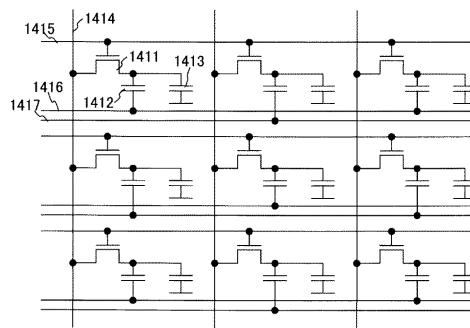

【図21】本発明に適用できる表示装置の表示部の構造の一を説明する図。

【図22】本発明に適用できる表示装置の表示部の構造の一を説明する図。

10

20

30

40

50

【図23】本発明に適用できる表示装置の表示部の構造の一を説明する図。

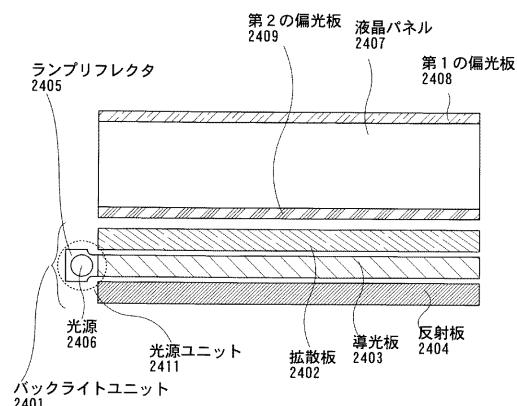

【図24】本発明に適用できる表示装置の構造の一を説明する図。

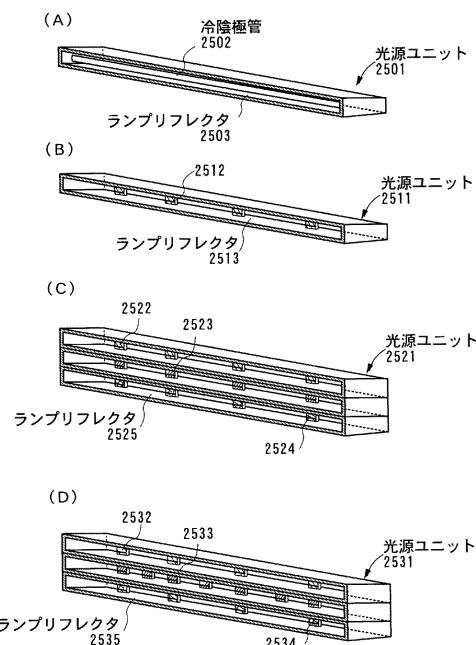

【図25】本発明に適用できる表示装置の構造の一を説明する図。

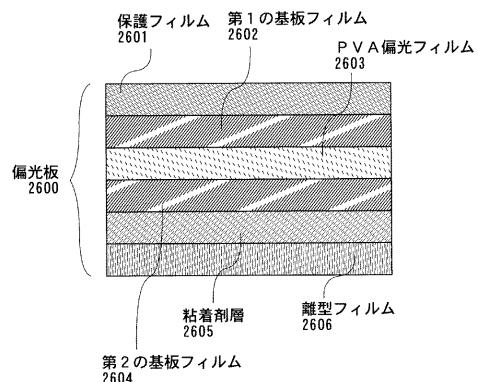

【図26】本発明に適用できる表示装置の構造の一を説明する図。

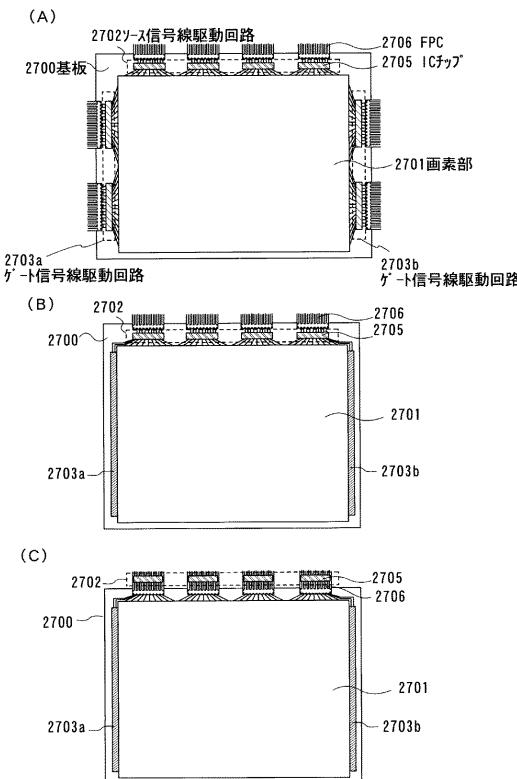

【図27】本発明に適用できる表示装置の周辺駆動回路の構成の一を説明する図。

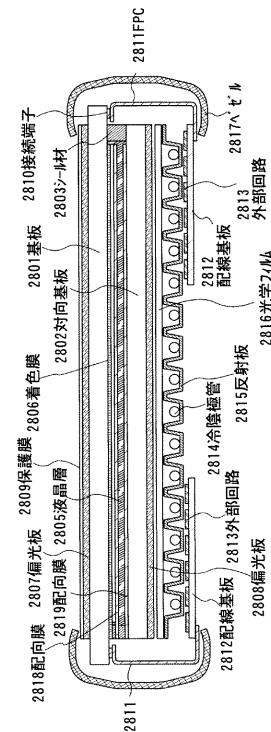

【図28】本発明に適用できる表示装置の構造の一を説明する図。

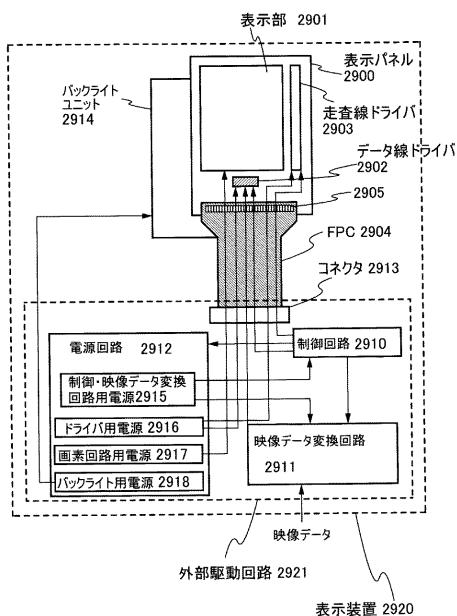

【図29】本発明に適用できる表示装置の周辺駆動回路の構成の一を説明する図。

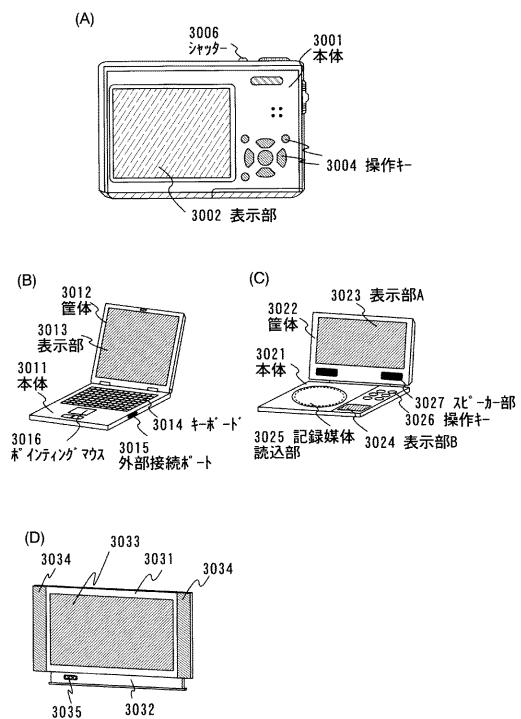

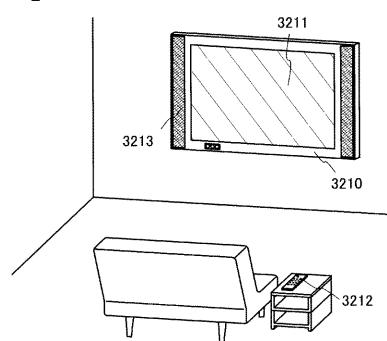

【図30】本発明に適用できる表示装置を用いた電子機器を説明する図。

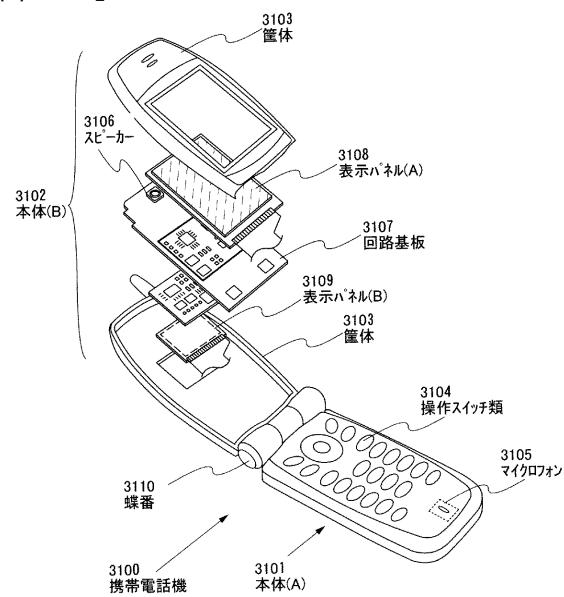

【図31】本発明に適用できる表示装置を用いた電子機器の実装方法を説明する図。

【図32】本発明に適用できる表示装置を用いた建造物の応用形態の一を説明する図。

10

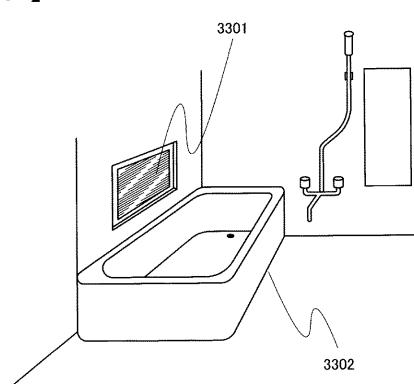

【図33】本発明に適用できる表示装置を用いた建造物の応用形態の一を説明する図。

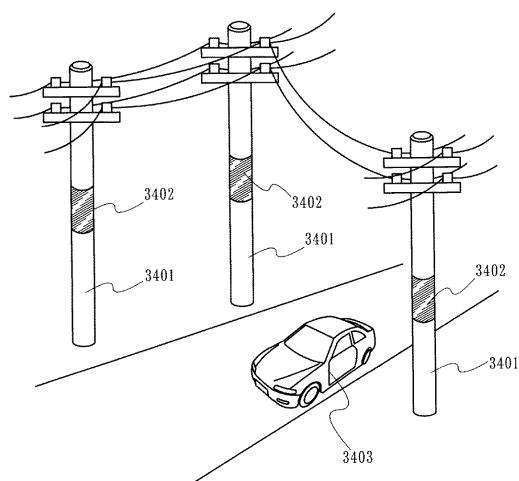

【図34】本発明に適用できる表示装置を用いた柱状体の一を説明する図。

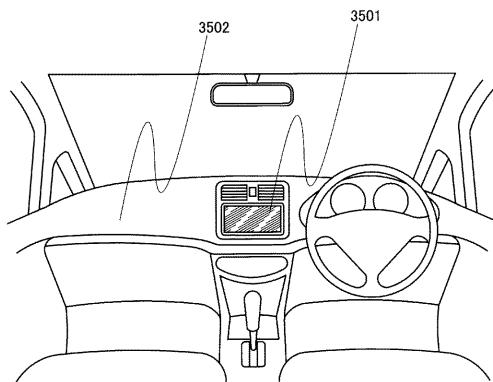

【図35】本発明に適用できる表示装置を用いた移動体の一を説明する図。

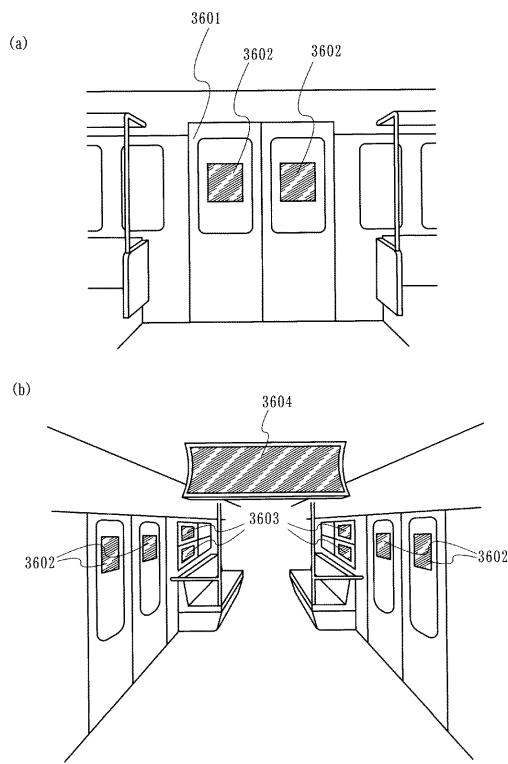

【図36】本発明に適用できる表示装置を用いた移動体の一を説明する図。

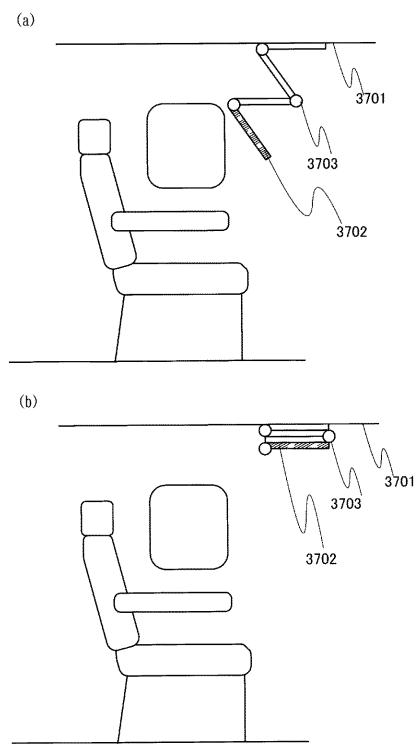

【図37】本発明に適用できる表示装置を用いた移動体の一を説明する図。

【発明を実施するための形態】

【0041】

20

以下に、本発明の実施の形態を図面に基づいて説明する。ただし、本発明は多くの異なる形態で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

【0042】

(実施の形態1)

本実施形態においては、1フレームを2つ以上の複数のサブフレームに分割し、これらの複数のサブフレームを、主に画像表示に用いるもの(明画像)と、主に動画像の残像低減のために用いるもの(暗画像)とに使い分けることで、動画像の画質を向上する方法について説明する。

30

【0043】

ここで、黒画像と暗画像の違いを説明する。黒画像は、画像を形成する全ての画素が、非発光状態または非透過状態となっている画像であり、まさに真っ黒な画像であるとする。一方、暗画像は、画像を形成する画素のうち、比較的小さい輝度で発光している画素が、主であるときに形成される画像であるとする。すなわち、暗画像とは、画像を形成する全ての画素の総発光量が、対応する明画像と比較して小さい画像であるとする。この定義に従えば、暗画像として黒画像が用いられる場合もあり得る。

【0044】

次に、積分輝度について説明する。一般的に、表示装置に並置された画素の集合として形成された画像は、そのままの画像として人間に知覚されるとは限らない。

【0045】

第1に、画素のサイズが十分小さい場合には、分散して配置されている画素であっても、人間の目は空間的に近接した画素と判別できなくなる。たとえば、近接した画素の発光色が違うときは、発光色の違いは知覚されず、近接した画素同士で混ざり合った色として知覚される。この性質は並置混色と呼ばれ、これによりカラー画像を表示させることができる。また、近接した画素で輝度が異なれば、知覚されるのは近接した画素の輝度の中間値となる。この性質を利用して中間輝度を表現する技術としては、ディザブロード、誤差ブロード等の階調補間技術がある。また、発光領域の面積にしたがって階調を表現する面積階調法もこれに含まれる。

40

【0046】

第2に、画素が発光している時間が十分小さく、かつ、時間的に分散させて複数回発光させた場合には、人間の目は時間的に近接した輝度の違いが判別できなくなる。例えば、輝度の大きい発光と小さい発光を連続して行なった場合、その画素は、両者の中間の輝度で

50

発光したと知覚される。この性質を利用して中間輝度を表現する技術は、時間階調法と呼ばれる。また、時間的に近接して発光色が異なれば、その画素の発光色は、近接した時間同士で混ざり合った色として知覚される。この性質を利用してカラー画像を表示させる技術としては、フィールドシーケンシャル法がある。

【0047】

ここで、時間的に分散させて複数回発光させた場合に、人間の目が時間的に近接した輝度の違いが判別できなくなることは、人間の目の時間周波数特性に関係する。人間の目は、ある臨界値より大きな周波数で変動する輝度は、変動しているとは知覚されず、一定の輝度で光り続いているように見える。このとき、人間の目が感じる輝度は、輝度を時間で積分した値（積分輝度）に依存する。

10

【0048】

一方、ある臨界値以下の周波数では、人間の目には、輝度の変化がフリッカ（ちらつき）としてそのまま知覚される。この臨界値は、輝度に依存するが、大体数十Hz（周期は十～数十ms）である。すなわち、積分輝度とは、人間の目には輝度変化が知覚されない数十msまでの時間範囲で、輝度を時間積分した値であるとする。

【0049】

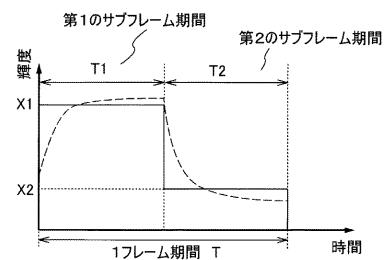

次に、図2を参照して、1フレームを複数のサブフレームに分割した場合に、積分輝度を定式化して表すことを説明する。図2の(A)の実線は、一例として、1フレームを2つのサブフレームに分割したときの、1フレーム中の画素の輝度の時間変化の一例をしたものである。

20

【0050】

図2の(A)において、1フレーム期間の長さをT、第1のサブフレームの期間の長さをT1、第2のサブフレームの期間の長さをT2、第1のサブフレーム期間における画素の平均輝度をX1、第2のサブフレーム期間における画素の平均輝度をX2、とすると、第1のサブフレーム期間における積分輝度は、T1とX1の積となる。同様に、第2のサブフレーム期間における積分輝度は、T2とX2の積となる。

【0051】

なお、実際に表示装置として用いるデバイスの特性上、輝度の時間変化が、図2の(A)の実線のようになり難い場合もある。たとえば、液晶を用いた表示装置の場合、輝度変化が、図2の(A)の破線で示すように、緩やかに変化する。このような場合、厳密には輝度の時間積分をとることで積分輝度を定義するが、本実施形態では、簡単のため、平均輝度とサブフレーム期間の積で積分輝度を定義することにする。このように、各サブフレーム期間における輝度は一定でなくてもよい。

30

【0052】

図2の(B)に、表示する階調に対する、1フレーム期間における積分輝度の配分の一例を示す。横軸は階調であり、縦軸は1フレーム期間における積分輝度である。図2の(B)では、階調0から階調255までを表示する場合を表している。なお、階調5から階調251までは、表示を省略している。各階調において、網掛けで示した部分は、第1のサブフレーム期間における積分輝度を表し、白地で示した部分は、第2のサブフレーム期間における積分輝度を表す。

40

【0053】

このように、1フレーム期間における積分輝度は、第1のサブフレーム期間における積分輝度と、第2のサブフレーム期間における積分輝度の和として表現できる。そして、これらの積分輝度の配分は、表示する階調によって個別に設定できる。

【0054】

ここで、1フレーム期間を分割するサブフレーム期間の数は、2以上の整数であればよい。このことを定式化すると、以下のように表現することができる。すなわち、1フレーム期間は、n個（nは2以上の整数）のサブフレーム期間に分割され、第i（iは1以上n以下の整数）のサブフレーム期間における前記表示素子の平均輝度をXi、

50

第*i*のサブフレーム期間の長さをT<sub>i</sub>としたとき、

輝度の時間に関する関数X(t)を、前記1フレーム期間で時間積分した積分輝度Yは、数式1のように表すことができる。

$$Y = \sum_{i=1}^n X_i T_i \quad \dots \quad (\text{数式1})$$

#### 【0055】

なお、第*i*のサブフレーム期間の長さT<sub>i</sub>は、全てのサブフレーム期間で概ね等しいことが望ましい。それは、画素に画像データを書き込む期間（アドレス期間）は、全てのサブフレーム期間の長さが等しいときに、一番長くすることができるからである。アドレス期間が長ければ、表示装置の周辺駆動回路の動作周波数を遅くすることができる、消費電力を低減できる。また、表示装置の歩留まりも向上する。ただし、これに限定されず、T<sub>i</sub>がサブフレーム期間によって異なっていてもよい。たとえば、明画像を表示するサブフレーム期間の長さの方が長い場合は、消費電力を大きくすることなく、バックライトユニットの平均輝度を上げることができる。また、バックライトユニットの平均輝度を変えることなく、消費電力を小さくすることができる。すなわち、発光の効率を向上できる。また、暗画像を表示するサブフレーム期間の長さの方が長い場合は、動画像の画質の向上が顕著であるという利点を有する。

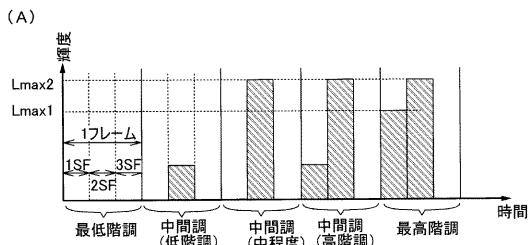

10

#### 【0056】

本実施形態においては、サブフレームの分割数nは2であり、かつ、それぞれのサブフレーム期間の長さは等しい場合について説明する。また、1フレーム期間の前半に位置するサブフレーム期間を1SF、後半に位置するサブフレーム期間を2SFと表記する。

20

#### 【0057】

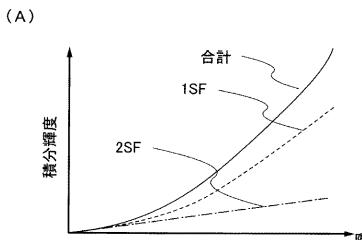

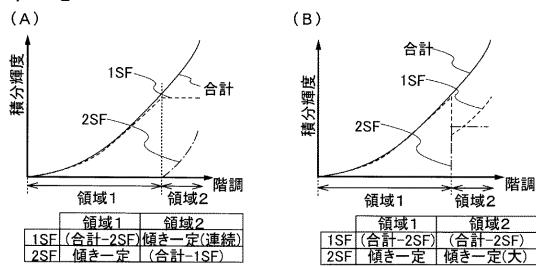

図1は、本実施形態における、表示する階調に対する2つのサブフレーム期間への輝度の配分方法を表す図である。図1の(A)は、2SFにおける輝度が1SFにおける輝度より大きい場合を示しており、図1の(B)は、1SFにおける輝度が2SFにおける輝度より大きい場合を示している。

#### 【0058】

まず、図1の(A)を参照して説明する。図1の(A)の横軸は時間であり、縦の実線はフレームの境界を表している。また、縦の破線は、サブフレームの境界を表している。縦軸は輝度である。すなわち、図1の(A)は、時間とともに輝度が上昇していく場合において、ある画素の輝度の時間に対する変化を、5フレームにわたって表示しているものである。

30

#### 【0059】

横軸の下方に表示されているのは、そのフレームにおいて、どの程度の階調が表されるかを示したものである。すなわち、図1の(A)においては、最初に最低階調を表示し、それから、低階調側の中間調、中程度の中間調、高階調側の中間調、最高階調の順で階調を表示していったときの、ある画素の輝度の時間に対する変化を示している。

#### 【0060】

黒画像を挿入することで動画像の画質は向上するが、本実施形態において説明する表示装置の駆動方法の特徴は、黒画像ではなく、黒に近い、暗い画像（暗画像）を挿入することによって、動画像の画質を向上させる点である。すなわち、1フレーム期間を2つのサブフレーム期間1SFと2SFに分割し、最高階調を表示するときにおける1SFにおける輝度を、2SFにおける輝度よりも小さい輝度で発光させることにより、動画像の画質の向上を実現し、1フレーム期間における輝度を一定に保つ。

40

#### 【0061】

階調の表現方法としては、まず、最低階調から中程度の中間調に至るまでの範囲では、2SFにおける輝度の大小によって表現する。そして、2SFにおける輝度が最大値L<sub>max</sub>×2となってからは、2SFにおける輝度はL<sub>max</sub>×2に固定した上で、1SFにおける

50

輝度の大小によって、階調を表現する。そして、最高階調を表現するとき、1SFにおける輝度  $L_{max} \times 1$  が、 $L_{max} \times 2$  よりも小さいと、動画像の画質を向上する上で、好適である。

#### 【0062】

すなわち、最高階調近傍においても、輝度を維持する時間（ホールド時間）を短くすることで、全ての階調範囲において残像が低減するので、動画像の画質を良好なものとすることができます。かつ、最高階調のときに、1SFにおいて、黒画像ではなく暗画像を表示させることで、 $L_{max} \times 1$  の輝度を小さくすることができる。したがって、消費電力を低減することができる。

10

#### 【0063】

なお、動画像の画質を向上するためには、 $L_{max} \times 1$  を  $L_{max} \times 2$  の 90% 以下、より好ましくは 60% 以下とするのが好適である。また、 $L_{max} \times 1$  を大きくして 1 フレーム内の最高輝度を抑制し、消費電力を抑えるためには、 $L_{max} \times 1$  を  $L_{max} \times 2$  の 50% 以上とするのが好適である。すなわち、1SF で暗画像を挿入する場合、 $L_{max} \times 1$  は、 $(1/2)L_{max} \times 2 < L_{max} \times 1 < (9/10)L_{max} \times 2$  という範囲内であるのが好適であり、より好ましくは、 $(1/2)L_{max} \times 2 < L_{max} \times 1 < (3/5)L_{max} \times 2$  範囲内であるのが好ましい。

#### 【0064】

なお、1 フレーム期間の長さは、フリッカの起こりにくい 1/60 秒以下であることが望ましい。ただし、1 フレーム期間の長さを短くすればするほど、周辺駆動回路の動作周波数が大きくなり、消費電力が増大してしまうので、1 フレーム期間の長さは、1/120 秒から 1/60 までの間であることが好適である。

20

#### 【0065】

次に、1SF における輝度が 2SF における輝度より大きい場合に関して、図 1 の (B) を参照して説明する。図 1 の (B) の横軸は時間であり、縦の実線はフレームの境界を表している。また、縦の破線は、サブフレームの境界を表している。縦軸は輝度である。すなわち、図 1 の (B) は、ある画素の輝度の時間に対する変化を、5 フレームにわたって表示しているものである。図 1 の (A) では、1SF の方が 2SF よりも輝度が小さかったが、これに限定されない。すなわち、図 1 の (B) に示したように、1 フレーム期間を 2 つのサブフレーム期間 1SF と 2SF に分割し、最高階調を表示するときにおける 2SF における輝度を、1SF における輝度よりも小さい輝度で発光させることにより、動画像の画質の向上を実現できる。このように、1SF と 2SF の順序を逆にすることは可能である。

30

#### 【0066】

なお、図 1 の (A)、(B) に示す表示装置の駆動方法は、オーバードライブ駆動と組み合わせて実施してもよい。こうすることで、液晶素子のように、電圧変化に対する応答速度の遅い表示素子を用いる場合においても、動画像の画質が向上する効果を十分に得ることができる。

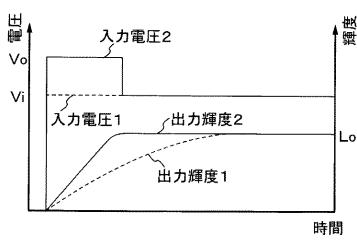

#### 【0067】

オーバードライブ駆動について、図 13 を参照して説明する。図 13 の (A) は、表示素子の、入力電圧に対する出力輝度の時間変化を表したものである。破線で表した入力電圧 1 に対する表示素子の出力輝度の時間変化は、同じく破線で表した出力輝度 1 のようになる。すなわち、目的の出力輝度  $L_o$  を得るための電圧は  $V_i$  であるが、入力電圧として  $V_i$  をそのまま入力した場合は、目的の出力輝度  $L_o$  に達するまでに、素子の応答速度に対応した時間を要してしまう。

40

#### 【0068】

オーバードライブ駆動は、この応答速度を速めるための技術である。具体的には、まず、 $V_i$  よりも大きい電圧である  $V_o$  を素子に一定時間与えることで出力輝度の応答速度を高めて、目的の出力輝度  $L_o$  に近づけた後に、入力電圧を  $V_i$  に戻す、という方法である。このときの入力電圧は入力電圧 2、出力輝度は出力輝度 2 に表したようになる。出力輝度

50

2のグラフは、目的の輝度  $L_o$  に至るまでの時間が、出力輝度 1 のグラフよりも短くなっている。

【0069】

なお、図13の(A)においては、入力電圧に対し出力輝度が正の変化をする場合について述べたが、入力電圧に対し出力輝度が負の変化をする場合も同様に行うことができる。

【0070】

このような駆動を実現するための回路について、図13の(B)および図13の(C)を参照して説明する。まず、図13の(B)を参照して、入力映像信号  $G_i$  がアナログ値(離散値でもよい)をとる信号であり、出力映像信号  $G_o$  もアナログ値をとる信号である場合について説明する。図13の(B)に示すオーバードライブ回路は、符号化回路 1301、フレームメモリ 1302、補正回路 1303、DA変換回路 1304、を備える。

10

【0071】

入力映像信号  $G_i$  は、まず、符号化回路 1301 に入力され、符号化される。つまり、アナログ信号から、適切なビット数のデジタル信号に変換される。その後、変換されたデジタル信号は、フレームメモリ 1302 と、補正回路 1303 と、にそれぞれ入力される。補正回路 1303 には、フレームメモリ 1302 に保持されていた前フレームの映像信号も、同時に入力される。そして、補正回路 1303 において、当該フレームの映像信号と、前フレームの映像信号から、あらかじめ用意された数値テーブルにしたがって、補正された映像信号を出力する。このとき、補正回路 1303 に出力切替信号を入力し、補正された映像信号と、当該フレームの映像信号を切替えて出力できるようにしてもよい。次に、補正された映像信号または当該フレームの映像信号は、DA変換回路 1304 に入力される。そして、補正された映像信号または当該フレームの映像信号にしたがった値のアナログ信号である出力映像信号  $G_o$  が出力される。このようにして、オーバードライブ駆動が実現できる。

20

【0072】

次に、図13の(C)を参照して、入力映像信号  $G_i$  がデジタル値をとる信号であり、出力映像信号  $G_o$  もデジタル値をとる信号である場合について説明する。図13の(C)に示すオーバードライブ回路は、フレームメモリ 1312、補正回路 1313、を備える。

【0073】

入力映像信号  $G_i$  は、デジタル信号であり、まず、フレームメモリ 1312 と、補正回路 1313 と、にそれぞれ入力される。補正回路 1313 には、フレームメモリ 1312 に保持されていた前フレームの映像信号も、同時に入力される。そして、補正回路 1313 において、当該フレームの映像信号と、前フレームの映像信号から、あらかじめ用意された数値テーブルにしたがって、補正された映像信号を出力する。このとき、補正回路 1313 に出力切替信号を入力し、補正された映像信号と、当該フレームの映像信号を切替えて出力できるようにしてもよい。このようにして、オーバードライブ駆動が実現できる。

30

【0074】

なお、補正された映像信号を得るための数値テーブルの組み合わせは、1SFにおいて取りうる階調の数と、2SFにおいて取りうる階調の数の積となる。この組み合わせの数は、小さいほど、補正回路 1313 内に格納するデータ量が小さくなるため、好ましい。本実施の形態においては、明画像を表示するサブフレームが最高輝度となるまでの中間調においては、暗画像の輝度は 0 であり、明画像を表示するサブフレームが最高輝度となってから最高階調となるまでは、明画像の輝度は一定であるため、この組み合わせの数を大幅に小さくできる。したがって、図1の(A)、(B)に示す表示装置の駆動方法は、オーバードライブ駆動と組み合わせて実施することで、大きな効果を奏する。

40

【0075】

なお、オーバードライブ回路は、入力映像信号  $G_i$  がアナログ信号であり、出力映像信号  $G_o$  がデジタル信号である場合も含む。このときは、図13の(B)に示した回路から、DA変換回路 1304 を省略すればよい。また、オーバードライブ回路は、入力映像信号  $G_i$  がデジタル信号であり、出力映像信号  $G_o$  がアナログ信号である場合も含む。このと

50

きは、図 13 の (B) に示した回路から、符号化回路 1301 を省略すればよい。なお、オーバードライブ回路は、上述した数値テーブルによるものだけではなく、様々なものを使うことができる。例えば、フレーム間の輝度の差分データを用いて映像信号を補正するものであってもよい。

#### 【0076】

次に、図 17 を参照して、オーバードライブ回路を表示パネルに実装する方法について説明する。図 17 の (A) は、表示パネルの全体図である。表示パネルは、基板 1701、表示部 1702、周辺駆動回路 1703、オーバードライブ回路 1704、を備えている。なお、複数の周辺駆動回路 1703 およびオーバードライブ回路 1704 を、表示部 1702 の周辺に設けてもよい。ここで、楕円 1705 で囲んだ領域について、図 17 の (B)、(C)、および (D) を参照して説明する。

10

#### 【0077】

図 17 の (B) は、オーバードライブ回路を作りこんだ I C を用いた場合を説明する図である。表示パネルは、基板 1701、表示部 1702、周辺駆動回路 1711、オーバードライブ回路 1712、を備えている。このように、オーバードライブ回路を作りこんだ I C を用いた場合は、周辺駆動回路 1711 は、汎用のドライバ I C を用いることができる、製造コストを低減することができる。なお、このときは、オーバードライブ回路 1712 の入力映像信号はアナログ値、出力映像信号もアナログ値であることが望ましい。

20

#### 【0078】

図 17 の (C) は、周辺駆動回路とオーバードライブ回路を作りこんだ I C を用いた場合を説明する図である。表示パネルは、基板 1701、表示部 1702、I C 1721、を備えている。このように、周辺駆動回路とオーバードライブ回路を作りこんだ I C を用いた場合は、接続点数を削減することができるので、表示装置の信頼性を向上させることができ。また、製造工程が簡略化できるため、製造コストを低減することができる。なお、このときは、I C 1721 内のオーバードライブ回路の出力映像信号は、アナログ値であることが望ましい。

20

#### 【0079】

図 17 の (D) は、周辺駆動回路とオーバードライブ回路を、薄膜トランジスタ (TFT) を用いて作りこんだ、回路を用いた場合を説明する図である。表示パネルは、基板 1701、表示部 1702、回路 1731、を備えている。このように、周辺駆動回路とオーバードライブ回路を作りこんだ回路を用いた場合は、接続点数を大幅に削減することができるので、表示装置の信頼性を大幅に向上させることができ。また、製造工程が簡略化できるため、製造コストを低減することができる。なお、このときは、回路 1731 内のオーバードライブ回路の出力映像信号は、アナログ値であってもよいし、デジタル値であってもよい。

30

#### 【0080】

なお、図 1 の (A)、(B) に示す表示装置の駆動方法は、走査型バックライトと組み合わせた液晶表示装置として実施してもよい。こうすることで、バックライトの平均輝度を低減するので、消費電力を低減することができる。

40

#### 【0081】

走査型バックライトについて、図 15 を参照して説明する。図 15 の (A) は、冷陰極管を並置した走査型バックライトを示す図である。図 15 の (A) に示す走査型バックライトは、拡散板 1501 と、N 個の冷陰極管 1502—1 から 1502—N と、を備える。N 個の冷陰極管 1502—1 から 1502—N を、拡散板 1501 の後ろに並置することで、N 個の冷陰極管 1502—1 から 1502—N は、その輝度を変化させて走査することができる。

#### 【0082】

走査するときの各冷陰極管の輝度の変化を、図 15 の (C) を用いて説明する。まず、冷陰極管 1502—1 の輝度を、一定時間変化させる。図 15 の (C) では、一定期間、輝

50

度を小さくしている。そして、その後に、冷陰極管 1502—1 の隣に配置された冷陰極管 1502—2 の輝度を、同じ時間だけ変化させる。このように、冷陰極管 1502—1 から 1502—N まで、輝度を順に変化させる。なお、図 15 の (C)においては、一定時間変化させる輝度は、元の輝度より小さいものとしたが、元の輝度より大きくてよい。また、冷陰極管 1502—1 から 1502—N まで走査するとしたが、逆方向に冷陰極管 1502—N から 1502—1 まで走査してもよい。

#### 【0083】

図 1 の (A)、(B) に示す表示装置の駆動方法と、走査型バックライトを組み合わせて実施することで、特別な効果を奏する。すなわち、図 1 の (A)、(B) に示す表示装置の駆動方法における、暗画像を挿入するサブフレーム期間と、図 15 の (C) に示した、各冷陰極管の輝度を小さくする期間を同期することで、走査型バックライトを用いない場合と同様の表示を得ることができながら、バックライトの平均輝度と小さくすることができる。したがって、液晶表示装置の消費電力の大部分を占める、バックライトの消費電力を低減することができる。

#### 【0084】

なお、輝度が小さい期間のバックライト輝度は、暗画像を挿入するサブフレームの最高輝度と同程度とするのが好適である。具体的には、暗画像を 1SF に挿入する場合は、1SF の最高輝度  $L_{max1}$ 、暗画像を 2SF に挿入する場合は、2SF の最高輝度  $L_{max2}$ 、とするのが好ましい。こうすることで、液晶素子で遮断される光量が減り、かつ、バックライトの発光輝度を小さくできるので、消費電力を小さくすることができる。また、バックライトの輝度を小さくすることによって、光漏れを小さくすることができる。また、液晶素子では完全に光を遮断することができないので、光漏れが生じ、コントラストを低下させるが、バックライトの輝度を小さくすることにより、光漏れを小さくし、コントラストを向上させることができる。

#### 【0085】

なお、走査型バックライトの光源として、LED を用いてよい。その場合の走査型バックライトは、図 15 の (B) のようになる。図 15 の (B) に示す走査型バックライトは、拡散板 1511 と、LED を並置した光源 1512—1 から 1512—N と、を備える。走査型バックライトの光源として、LED を用いた場合、バックライトを薄く、軽くできる利点がある。また、色再現範囲を広げることができるという利点がある。また、LED を並置した光源 1512—1 から 1512—N のそれぞれに並置した LED も、同様に走査することができるので、点走査型のバックライトとすることもできる。点走査型とすれば、動画像の画質をさらに向上させることができる。特に、LED は点灯と非点灯などの輝度変化を高速に制御することができるため、動画質の向上に好適である。

#### 【0086】

なお、図 1 の (A)、(B) に示す表示装置の駆動方法は、高周波駆動と組み合わせて実施してもよい。こうすることで、動画像の画質をさらに向上させることができる。

#### 【0087】

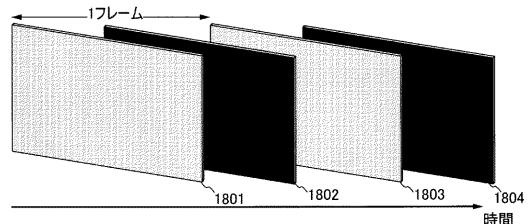

高周波駆動について、図 18 を参照して説明する。図 18 の (A) は、フレーム周波数が 60Hz のときに暗画像を挿入して駆動するときの図である。1801 は当該フレームの明画像、1802 は当該フレームの暗画像、1803 は次フレームの明画像、1804 は次フレームの暗画像である。60Hz で駆動する場合は、映像信号のフレームレートと整合性が取り易く、画像処理回路が複雑にならないという利点がある。

#### 【0088】

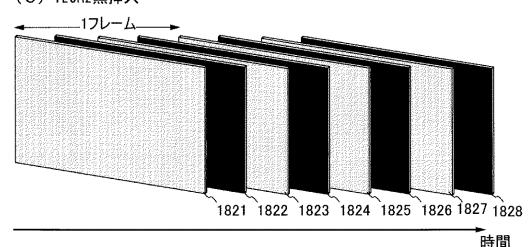

図 18 の (B) は、フレーム周波数が 90Hz のときに暗画像を挿入して駆動するときの図である。1811 は当該フレームの明画像、1812 は当該フレームの暗画像、1813 は当該フレームと次フレームと次々フレームから作成した第 1 の画像の明画像、1814 は当該フレームと次フレームと次々フレームから作成した第 1 の画像の暗画像、1815 は当該フレームと次フレームと次々フレームから作成した第 2 の画像の明画像、1816 は当該フレームと次フレームと次々フレームから作成した第 2 の画像の暗画像である。

90 Hz で駆動する場合は、周辺駆動回路の動作周波数をそれほど高速化することなく、効果的に動画像の画質を向上できるという利点がある。

【0089】

図18の(C)は、フレーム周波数が120Hzのときに暗画像を挿入して駆動するときの図である。1821は当該フレームの明画像、1822は当該フレームの暗画像、1823は当該フレームと次フレームから作成した画像の明画像、1824は当該フレームと次フレームから作成した画像の暗画像、1825は次フレームの明画像、1826は次フレームの暗画像、1827は次フレームと次々フレームから作成した画像の明画像、1828は次フレームと次々フレームから作成した画像の暗画像である。120Hzで駆動する場合は、動画像の画質改善効果が著しく、ほとんど残像を感じることがないという利点がある。

10

【0090】

なお、図1の(A)、(B)に示す表示装置の駆動方法は、コモン線の電位を操作して、表示素子に目的の電圧を印加する駆動方法と組み合わせて実施してもよい。こうすることで、映像信号を画素に書き込む頻度が小さくなるため、画素に映像信号を書き込む際の消費電力を低減することができる。ここで、コモン線とは、画素容量を大きくするための補助容量素子が接続されている配線のことである。また、1画素を複数のサブ画素に分割し、各々のコモン線の電位を個別に制御して表示させてもよい。こうようにすることにより、各々のサブ画素の輝度を異ならせることができるので、視野角を向上させることができる。

20

【0091】

コモン線の電位を操作する駆動について、図14を参照して説明する。図14の(A)は、液晶素子のような容量的な性質を持つ表示素子を用いた表示装置において、走査線1本に対し、コモン線が1本配置されているときの、複数の画素回路を表した図である。図14の(A)に示す画素回路は、トランジスタ1401、補助容量1402、表示素子1403、映像信号線1404、走査線1405、コモン線1406、を備えている。

30

【0092】

トランジスタ1401のゲート電極は、走査線1405に電気的に接続され、トランジスタ1401のソース電極またはドレイン電極の一方は、映像信号線1404に電気的に接続され、トランジスタ1401のソース電極またはドレイン電極の他方は、補助容量1402の一方の電極、および表示素子1403の一方の電極に電気的に接続されている。また、補助容量1402の他方の電極は、コモン線1406に電気的に接続されている。

40

【0093】

まず、走査線1405によって選択された画素は、トランジスタ1401がオンとなるため、それぞれ、映像信号線1404を介して、表示素子1403および補助容量1402に映像信号に対応した電圧がかかる。このとき、その映像信号が、コモン線1406に接続された全ての画素に対して最低階調を表示させるものだった場合、または、コモン線1406に接続された全ての画素に対して最高階調を表示させるものだった場合は、画素にそれぞれ映像信号線1404を介して映像信号を書き込む必要はない。映像信号線1404を介して映像信号を書き込む代わりに、コモン線1406の電位を動かすことで、表示素子1403にかかる電圧を変えることができる。

40

【0094】

コモン線1406の電位を動かすことで、表示素子1403にかかる電圧を変える方法は、図1の(A)、(B)に示す表示装置の駆動方法と組み合わせることで、特に大きな効果を奏する。すなわち、画像全体が暗めの階調を有する場合は、コモン線1406に接続された全ての画素における階調も、全体的に暗くなる。このとき、暗画像を挿入するサブフレームにおいては、全く発光させない画素の割合が非常に大きくなる。すなわち、映像信号線1404を介して映像信号を書き込む代わりに、コモン線1406の電位を動かすことで、表示素子1403にかかる電圧を変えることができる頻度が、非常に大きくなるからである。同様に、画像全体が明るめの階調を有する場合も、映像信号線1404を介

50

して映像信号を書き込む代わりに、コモン線 1406 の電位を動かすことで、表示素子 1403 にかかる電圧を変えることができる頻度が、非常に大きくなる。それは、画像全体が明るめの階調を有する場合は、コモン線 1406 に接続された全ての画素における階調も、全体的に明るくなる。このとき、明画像を挿入するサブフレームにおいては、サブフレームにおける最高輝度で発光させる画素の割合が非常に大きくなるからである。

#### 【0095】

次に、図 14 の (B) は、液晶素子のような容量的な性質を持つ表示素子を用いた表示装置において、走査線 1 本に対し、コモン線が 2 本配置されているときの、複数の画素回路を表した図である。図 14 の (B) に示す画素回路は、トランジスタ 1411、補助容量 1412、表示素子 1413、映像信号線 1414、走査線 1415、第 1 のコモン線 1416、第 2 のコモン線 1417、を備えている。10

#### 【0096】

トランジスタ 1411 のゲート電極は、走査線 1415 に電気的に接続され、トランジスタ 1411 のソース電極またはドレイン電極の一方は、映像信号線 1414 に電気的に接続され、トランジスタ 1411 のソース電極またはドレイン電極の他方は、補助容量 1412 の一方の電極、および表示素子 1413 の一方の電極に電気的に接続されている。また、補助容量 1412 の他方の電極は、第 1 のコモン線 1416 に電気的に接続されている。また、当該画素と隣接する画素においては、補助容量 1412 の他方の電極は、第 2 のコモン線 1417 に電気的に接続されている。20

#### 【0097】

図 14 の (B) に示す画素回路は、コモン線 1 本に対し電気的に接続されている画素が少ないため、映像信号線 1414 を介して映像信号を書き込む代わりに、第 1 のコモン線 1416 または第 2 のコモン線 1417 の電位を動かすことで、表示素子 1413 にかかる電圧を変えることができる頻度が、顕著に大きくなる。また、ソース反転駆動またはドット反転駆動が可能になる。ソース反転駆動またはドット反転駆動により、素子の信頼性を向上させつつ、フリッカを抑えることができる。20

#### 【0098】

このように、図 1 の (A)、(B) に示す表示装置の駆動方法は、コモン線の電位を操作する駆動と組み合わせることで、特に大きな効果を奏する。

#### 【0099】

なお、図 1 の (A)、(B) に示す表示装置の駆動方法は、有機 EL 素子などの電流で駆動する表示素子と組み合わせて実施してもよい。こうすることで、映像信号電流を大きくすることができるので、書き込み時間を小さくすることができる。30

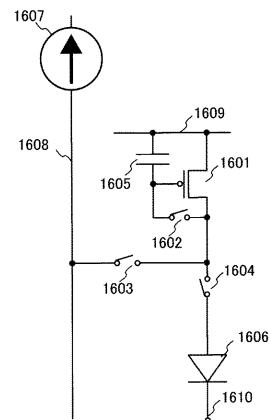

#### 【0100】

電流で駆動する表示素子の駆動方法について、図 16 を参照して説明する。図 16 は、有機 EL 素子などの電流で駆動する表示素子を用いた表示装置において、映像信号として電流を用いた場合の、画素回路を表した図である。図 16 に示す画素回路は、トランジスタ 1601、スイッチ素子 1602、1603、1604、容量素子 1605、表示素子 1606、映像信号線 1608、第 1 の配線 1609、第 2 の配線 1610、を備え、画素領域外に電流源 1607 を備えていてもよい。40

#### 【0101】

トランジスタ 1601 のゲート電極は、容量素子 1605 の一方の電極に電気的に接続され、トランジスタ 1601 のソース電極またはドレイン電極の一方は、第 1 の配線 1609 に電気的に接続され、トランジスタ 1601 のソース電極またはドレイン電極の他方は、表示素子 1606 の一方の電極に電気的に接続されている。また、容量素子 1605 の他方の電極は、第 1 の配線 1609 に電気的に接続されている。また、表示素子 1606 の他方の電極は、第 2 の配線 1610 に電気的に接続されている。また、スイッチ素子 1602 は、トランジスタ 1601 のゲート電極とトランジスタ 1601 のソース電極またはドレイン電極の他方の間に配置されていてもよい。また、スイッチ素子 1603 は、トランジスタ 1601 のソース電極またはドレイン電極の他方と表示素子 1606 の一方の50

電極を電気的に接続する電極と、映像信号線 1608 の間に配置されていてもよい。また、スイッチ素子 1604 は、トランジスタ 1601 のソース電極またはドレイン電極の他方と表示素子 1606 の一方の電極の間に配置されていてもよい。

#### 【0102】

図 16 に示す画素回路は、映像信号書き込み時は、スイッチ素子 1602 および 1603 をオンとし、1604 をオフとしてもよい。このとき、トランジスタ 1601 のソースドレイン間に流れる電流は、電流源 1607 に流れる電流と等しくなる。また、発光時は、スイッチ素子 1602 および 1603 をオフとし、1604 をオンとしてもよい。このとき、電流源 1607 により書き込んだ電流と同等の電流がトランジスタ 1601 および表示素子 1606 を流れる。

10

#### 【0103】

このような方法で映像信号を書き込むとき、特に低階調側の階調を書き込むときにおいて、書き込む電流値が小さいと、映像信号線に付随する寄生容量のために、書き込み時間が遅くなってしまう。したがって、書き込む電流値はできるだけ大きいほうがよい。そこで、図 1 の (A)、(B) に示す表示装置の駆動方法を用いることで、書き込み時間を短くすることができる。

#### 【0104】

すなわち、図 1 の (A)、(B) に示す表示装置の駆動方法は、低階調側において、一方のサブフレーム期間が非発光状態となるため、発光状態とするサブフレームにおいては、輝度を大きくする。輝度を大きくするためには、書き込む電流は大きくする。したがって、低階調側の階調を書き込むときの書き込み時間を短くすることができる。

20

#### 【0105】

このように、図 1 の (A)、(B) に示す表示装置の駆動方法は、有機 E L 素子などの電流で駆動する表示素子と組み合わせることで、特に大きな効果を奏する。

#### 【0106】

なお、図 1 の (A)、(B) に示す表示装置の駆動方法は、インターレース走査と組み合わせて実施してもよい。こうすることで、周辺駆動回路の動作周波数を低減することができる、消費電力を低減することができる。特に、暗画像において非発光となる画素が多い画像であるとき、または、明画像において最高輝度で発光する画素が多い画像であるときに、効果的である。すなわち、階調の変化の少ない画像に対しては、インターレース走査による解像度の低下が少ないからである。

30

#### 【0107】

なお、図 1 の (A)、(B) に示す表示装置の駆動方法は、基準電位を変更できる D A コンバーター回路と組み合わせて実施してもよい。こうすることで、D A コンバーター回路の効率を向上させることができる。特に、明画像を表示するサブフレームと、暗画像を表示するサブフレームで、基準電位を変更できるようにするのが効果的である。すなわち、明画像を表示するときと、暗画像を表示するときでは、必要とされる映像信号の電位の平均値が異なるためである。

#### 【0108】

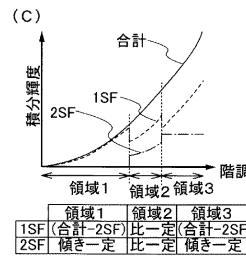

##### (実施の形態 2)

40

本実施形態においては、実施の形態 1 で説明した、1 フレームを複数のサブフレームに分割し、これらの複数のサブフレームを、主に画像表示に用いるもの（明画像）と、主に動画像の残像低減のために用いるもの（暗画像）とに使い分ける方法における、他の実施形態について説明する。

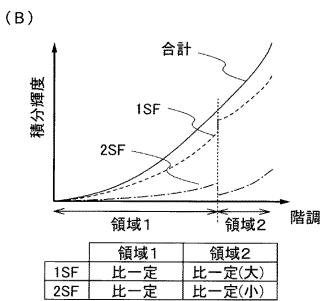

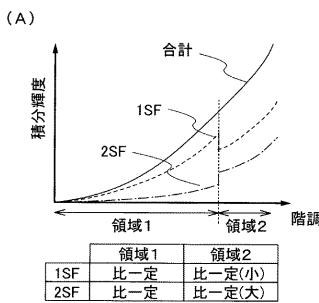

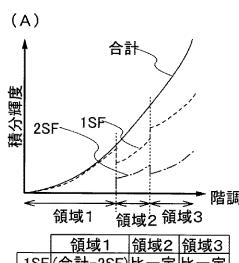

#### 【0109】

表示する画像を明画像と暗画像に分けるときには、表示する画像の階調を表現するときには必要となる輝度を、複数のサブフレームにどのように配分するかという点で、いくつかの方法が存在する。このことを説明するために、本実施形態においては、横軸に階調、縦軸に積分輝度をとり、1 S F における積分輝度と階調の関係、2 S F における積分輝度と階調の関係、1 S F と 2 S F で合計した積分輝度と階調の関係、を表したグラフを参照する

50

。

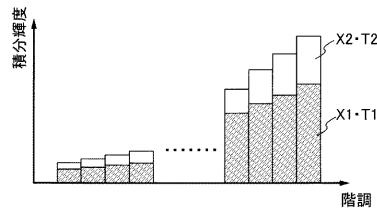

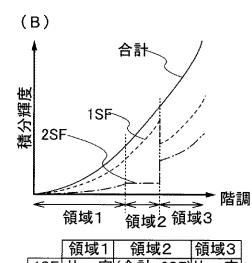

## 【0110】

まず、図3の(A)を参照して、本実施の形態の一形態を説明する。図3の(A)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。表に傾き一定と記載されているサブフレームは、階調に対する積分輝度の変化が一定であることを表している。すなわち、図3の(A)に示す形態においては、2SFの階調に対する積分輝度の変化が一定である。なお、図3の(A)では、傾きの値が正の場合を示しているが、傾きの値は、0であってもよいし、負であってもよい。また、表に(合計 $\times$ SF)と記載されている場合は、当該サブフレームとは別のサブフレームの積分輝度によって、当該サブフレームの積分輝度が決まる場合を表している。ここで、 $\times$ SFには、1SF、2SFなど、様々なサブフレームが当てはまる。すなわち、図3の(A)に示す形態においては、1SFの積分輝度は、合計輝度から2SFの積分輝度を引いた値であることを表している。ここで、合計輝度は別に定められているものとし、本実施の形態においては、下に凸の曲線であるものとする。これは、人間の目の特性を考慮し、ガンマ補正を施している場合である。なお、合計輝度は、階調に対し線形であってもよいし、上に凸の曲線であってもよいし、線分と曲線の組み合わせであってもよい。また、合計輝度やガンマ特性が、表示画像によって切り替わる機構を有していてもよいし、使用者によって調節できる機構を有していてもよい。

10

## 【0111】

図3の(A)に示す形態においては、2SFの階調に対する積分輝度の変化が一定であるため、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。なお、図3の(A)に示す形態において、図1の(A)と図1の(B)で示したとおり、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。

20

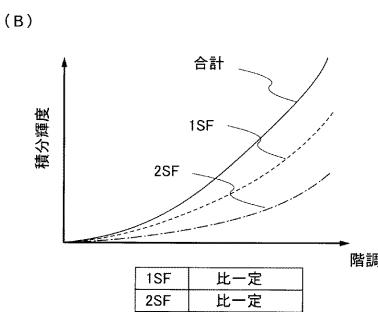

## 【0112】

図3の(B)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。図3の(B)のように、グラフの下方に示した表に比一定と記載したサブフレームは、1SFと2SFの積分輝度比が、各階調において等しい場合を表している。すなわち、図3の(B)に示す形態においては、1SFの積分輝度と2SFの積分輝度の比が、階調によらず等しい場合を表している。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。なお、比一定の特徴を有する場合は、双方のサブフレームにおいて比一定の特徴を有しているとしてもよい。つまり、一方が比一定であって、他方は比一定でない場合はないとしてもよい。なお、図3の(B)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。

30

40

## 【0113】

次に、図4を参照して、本実施の形態の一形態を説明する。図4は、表示できる階調を複数の領域、たとえば、2つの領域に分割し、それぞれの領域で各サブフレームが異なる特徴を有し得る場合において、1フレームで合計した積分輝度を1SFと2SFで配分する方法の例を表したものである。本実施形態では、低階調側の領域から、領域1、領域2、として名づけて説明する。

## 【0114】

50

なお、以下の説明において、領域の境界において積分輝度の値が連続であることは、次のように定義されることとする。すなわち、領域の境界によって隔てられた2つの隣接する階調のうち、低階調側の領域に属する階調を境界階調（低）、高階調側の領域に属する階調を境界階調（高）とし、境界階調（高）における輝度と境界階調（低）における輝度の差の絶対値を境界輝度差としたとき、領域の境界において積分輝度の値が連続であるということは、境界輝度差がある値  $\times$  以下であることをいう。

#### 【0115】

ここで、 $\times$ の値は、境界階調（高）における輝度および境界階調（低）における輝度などにしたがって様々な値をとり得るが、注目している階調 - 輝度特性を人間の目で見たときにおける連続性（つまり、注目している階調 - 載度特性に対応する画像が表示されたとき、当該画像が領域の境界においてなめらかに表示されているかどうか）の観点から決めることができる。具体的には、境界階調（低）における輝度と、境界階調（低）よりも1つ小さい階調における輝度の差の絶対値を第1近傍境界輝度差（低）としたとき、 $\times$ は、第1近傍境界輝度差（低）の2倍程度であることが好ましい。

10

#### 【0116】

本実施形態および他の実施形態においては、一例として、 $\times$ は第1近傍境界輝度差（低）の2倍であるとして説明を行なう。

#### 【0117】

図4の（A）は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。表の領域2の欄に傾き一定（連続）（傾き正）と記載されているサブフレームは、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域（領域1）との境界において積分輝度の値が連続し、かつ、当該領域における階調に対する積分輝度の変化が正の符号をもつことを表している。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が小さくなるので、画像表示時のちらつきが低減するという利点がある。

20

#### 【0118】

図4の（B）は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。表の領域2の欄に傾き一定（連続）（傾き0）と記載されているサブフレームは、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域（領域1）との境界において積分輝度の値が連続し、かつ、当該領域における階調に対する積分輝度の変化が0であることを表している。このような特徴を持つことにより、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。

30

#### 【0119】

図4の（C）は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。表の領域2の欄に傾き一定（連続）（傾き負）と記載されているサブフレームは、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域（領域1）との境界において積分輝度の値が連続し、かつ、当該領域における階調に対する積分輝度の変化が負の符号をもつことを表している。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が大きくなるので、動画像のボケを効率よく低減することができる。

40

#### 【0120】

なお、図4の（A）、（B）および（C）に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であっても

50

よい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域1と領域2であってもよい。

#### 【0121】

このように、表示できる階調が複数の領域に分けられる場合、それぞれの領域における、階調に対する積分輝度の変化（傾きの値）は、様々な値をとることができる。ただし、図4の（D）に示すように、傾きの値は、当該領域の境界における積分輝度の合計値の接線の傾きよりも小さいことが好適である。すなわち、領域の境界における積分輝度の合計値の接線の傾きを  $max$  としたとき、当該領域における傾きの値は、 $-max < < max$  という範囲内であることが好適である。（図4の（D）中のハッチング領域）この範囲内であることによって、階調に対する積分輝度の変化が急激であることによって、領域の境界において当該階調が強調され、不自然な輪郭が発生する現象を低減することができる。

10

#### 【0122】

なお、階調に対する積分輝度の変化が急激であることによって、領域の境界において当該階調が強調され、不自然な輪郭が発生する現象を低減する方法としては、図4の（D）に示す方法とは別に、図4の（E）および（F）に示す方法を用いることもできる。図4の（E）および（F）は、各領域の特徴は図4の（B）に示す形態と同じであり、その領域の境界となる階調が異なっている。このような、領域の境界となる階調が異なっている複数の輝度配分形態を用意し、これらを必要に応じて切替えることによっても、領域の境界において当該階調が強調され、不自然な輪郭が発生する現象を低減することができる。なお、このような方法は、図4の（B）に示す形態だけではなく、様々な輝度配分形態に適用することができる。

20

#### 【0123】

なお、複数の輝度配分形態を切替える方法としては、たとえば、フレーム毎に切替えるよい。こうすることで、効率よく不自然な輪郭が発生する現象を低減することができる。また、表示する画像に従って、輝度配分形態を切替えるよい。このとき、画像の階調分布に閾値が存在する場合は、領域の境界を、その閾値近傍に設定するのが好適である。たとえば、階調100以下の階調の分布がほとんどない明るい画像の場合は、領域の境界を階調100近傍に設定するのが好適である。同様に、階調100以上の階調の分布がほとんどない暗い画像の場合においても、領域の境界を階調100近傍に設定するのが好適である。こうすることで、表示される画像において、閾値近傍をまたぐ階調が少なくなるため、領域の境界において当該階調が強調され、不自然な輪郭が発生する現象を低減することができる。

30

なお、画像の明暗によって、閾値を設定してもよい。たとえば、全体的に暗い画像の場合は、領域の境界を高階調側に設定し、全体的に明るい画像の場合は、領域の境界を低階調側に設定してもよい。こうすることで、示される画像において、閾値近傍をまたぐ階調が少なくなるため、領域の境界において当該階調が強調され、不自然な輪郭が発生する現象を低減することができる。

なお、表示する画像に従って、輝度配分形態を切替える方法は、領域の境界が異なる形態同士だけではなく、様々な輝度配分形態に対して適用することができる。

40

#### 【0124】

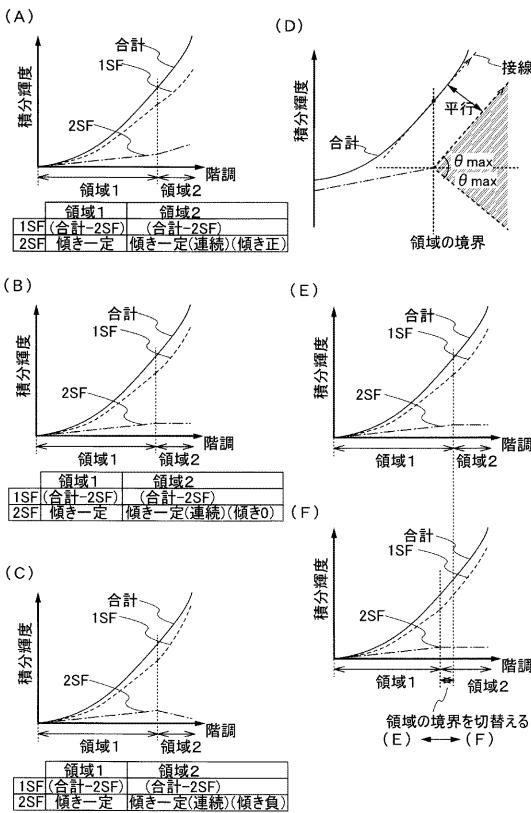

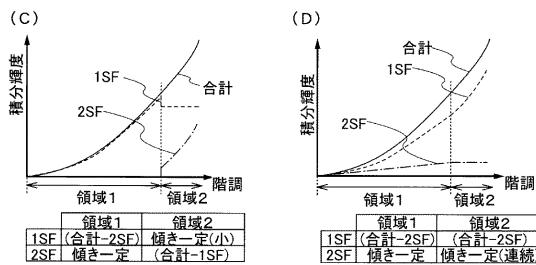

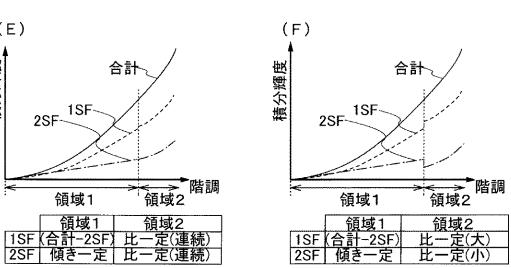

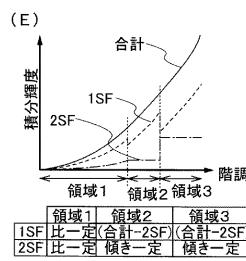

次に、図5を参照して、本実施の形態の一形態を説明する。図5は、表示できる階調を複数の領域、たとえば、2つの領域に分割し、それぞれの領域で各サブフレームが異なる特徴を有し得る場合において、1フレームで合計した積分輝度を1SFと2SFで配分する方法の例を表したものである。特に、双方の領域について、どちらか一方のサブフレームの階調に対する積分輝度の変化が一定である場合について説明する。

#### 【0125】

図5の（A）は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一

50

定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。1SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域（領域1）との境界において積分輝度の値が連続していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。2SFの領域2における特徴は、合計輝度と、1SFの輝度に従った輝度をとることである。このような特徴を持つことにより、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

10

#### 【0126】

図5の（B）は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。2SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域（領域1）との境界において積分輝度の値が大きい方向へ不連続に変化していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域2における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が小さくなるので、画像表示時のちらつきが低減するという利点がある。また、2SFのとる輝度変化が単純になるため、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。特に、オーバードライブ駆動を行なう場合に、メモリ素子の容量を低減できるという利点がある。

20

#### 【0127】

図5の（C）は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。1SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域（領域1）との境界において積分輝度の値が小さい方向へ不連続に変化していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。2SFの領域2における特徴は、合計輝度と、1SFの輝度に従った輝度をとることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が小さくなるので、画像表示時のちらつきが低減するという利点がある。

30

#### 【0128】

図5の（D）は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。2SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域（領域1）との境界において積分輝度の値が連続していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域2における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。このような特徴を持つことにより、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減す

40

50

ることができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

#### 【0129】

図5の(E)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。1SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が大きい方向へ不連続に変化していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。2SFの領域2における特徴は、合計輝度と、1SFの輝度に従った輝度をとることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が大きくなるので、動画像のボケを効率よく低減することができる。

10

#### 【0130】

図5の(F)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。2SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が小さい方向へ不連続に変化していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域2における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が大きくなるので、動画像のボケを効率よく低減することができる。

20

#### 【0131】

なお、図5の(A)、(B)、(C)、(D)、(E)および(F)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わってもよい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であってもよい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域1と領域2であってもよい。

30

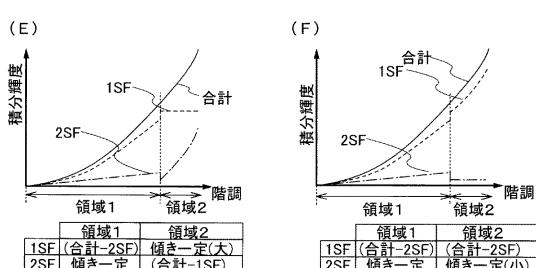

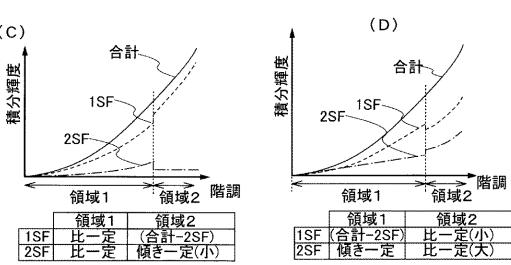

#### 【0132】

次に、図6を参照して、本実施の形態の一形態を説明する。図6は、表示できる階調を複数の領域、たとえば、2つの領域に分割し、それぞれの領域で各サブフレームが異なる特徴を有し得る場合において、1フレームで合計した積分輝度を1SFと2SFで配分する方法の例を表したものである。特に、一方の領域において、どちらか一方のサブフレームの階調に対する積分輝度の変化が一定であり、他方の領域において、1SFと2SFの積分輝度比が、各階調において等しい場合について説明する。

40

#### 【0133】

図6の(A)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。1SFおよび2SFの領域1における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの

50

輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。2SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が連続していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域2における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。このような特徴を持つことにより、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

10

#### 【0134】

図6の(B)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。1SFおよび2SFの領域1における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。2SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が大きい方向へ不連続に変化していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域2における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が小さくなるので、画像表示時のちらつきが低減するという利点がある。

20

#### 【0135】

図6の(C)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。1SFおよび2SFの領域1における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。2SFの領域2における特徴は、階調に対する積分輝度の変化が一定であり、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が小さい方向へ不連続に変化していることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域2における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が大きくなるので、動画像のボケを効率よく低減することができる。

30

#### 【0136】

図6の(D)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。1SFおよび2SFの領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しく、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が、1SFは小さい方向へ、2SFは大きい方向へ、それぞれ不連続に変化していることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が小さくなるので、画像表示時のちらつきが低減するという利点がある。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よ

40

50

りも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

#### 【0137】

図6の(E)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。1SFおよび2SFの領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しく、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が、1SF、2SFともに、連続していることである。このような特徴を持つことにより、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

10

#### 【0138】

図6の(F)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。1SFの領域1における特徴は、合計輝度と、2SFの輝度に従った輝度をとることである。1SFおよび2SFの領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しく、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が、1SFは大きい方向へ、2SFは小さい方向へ、それぞれ不連続に変化していることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が大きくなるので、動画像のボケを効率よく低減することができる。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

20

30

#### 【0139】

なお、図6の(A)、(B)、(C)、(D)、(E)および(F)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であってもよい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域1と領域2であってもよい。

40

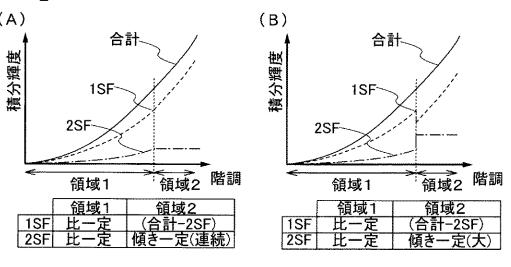

#### 【0140】

次に、図7を参照して、本実施の形態の一形態を説明する。図7は、表示できる階調を複数の領域、たとえば、2つの領域に分割し、それぞれの領域で各サブフレームが異なる特徴を有し得る場合において、1フレームで合計した積分輝度を1SFと2SFで配分する方法の例を表したものである。特に、双方の領域について、1SFと2SFの積分輝度比が、各階調において等しい場合について説明する。

#### 【0141】

図7の(A)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。1SFおよび2SFの領域1における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの

50

輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。1SFおよび2SFの領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しく、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が、1SFは小さい方向へ、2SFは大きい方向へ、それぞれ不連続に変化していることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が小さくなるので、画像表示時のちらつきが低減するという利点がある。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

10

#### 【0142】

図7の(B)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。1SFおよび2SFの領域1における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。1SFおよび2SFの領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しく、かつ、近接する低階調側の領域(領域1)との境界において積分輝度の値が、1SFは大きい方向へ、2SFは小さい方向へ、それぞれ不連続に変化していることである。このような特徴を持つことにより、最大階調における1SFと2SFの輝度差が大きくなるので、動画像のボケを効率よく低減することができる。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

20

#### 【0143】

なお、図7の(A)および(B)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であってもよい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域1と領域2であってもよい。

30

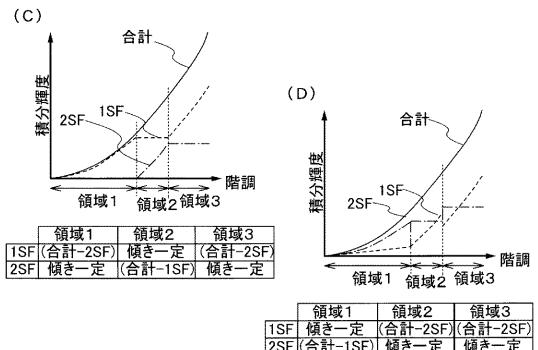

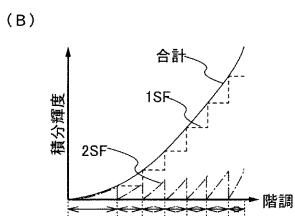

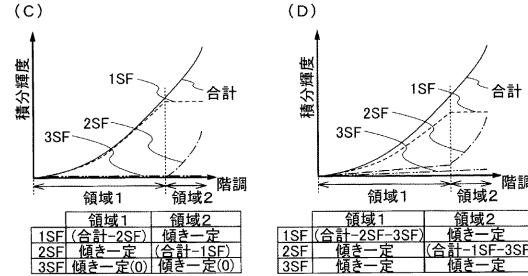

#### 【0144】

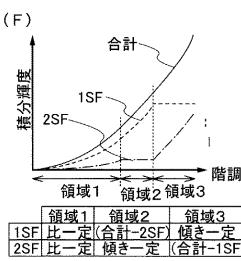

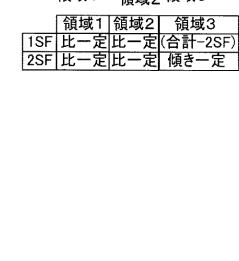

次に、図8を参照して、本実施の形態の一形態を説明する。図8は、表示できる階調を複数の領域、たとえば、3つの領域に分割し、それぞれの領域で各サブフレームが異なる特徴を有し得る場合において、1フレームで合計した積分輝度を1SFと2SFで配分する方法の例を表したものである。特に、全ての領域について、どちらか一方のサブフレームの階調に対する積分輝度の変化が一定である場合について説明する。

40

#### 【0145】

図8の(A)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1および領域2および領域3における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1および領域2および領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。

#### 【0146】

図8の(B)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単

50

に表したものである。2SFの領域1、領域2および1SFの領域3における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1、領域2および2SFの領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。

#### 【0147】

図8の(C)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1、領域3および1SFの領域2における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1、領域3および2SFの領域2における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。

10

#### 【0148】

図8の(D)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。1SFの領域1および2SFの領域2、領域3における特徴は、階調に対する積分輝度の変化が一定であることである。2SFの領域1および1SFの領域2、領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。

20

#### 【0149】

なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。図8においては、この違いについては詳細に説明しないが、全ての領域について、これらの組み合わせを適用することができる。傾きが正または負の値をとるために、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、傾きが正または負の値をとるために、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、傾きが0である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

20

#### 【0150】

なお、すでに述べたように、領域の境界における輝度の状態は、近接する低階調側の領域と比較して、大きい方向へ不連続に変化するか、連続しているか、小さい方向へ不連続に変化するかの、いずれかの状態を取り得る。図8においては、この違いについては詳細に説明しないが、全ての領域の境界について、これらの組み合わせを適用することができる。領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、領域の境界において輝度が連続である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

30

#### 【0151】

なお、図8の(A)、(B)、(C)および(D)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わってもよい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であってもよい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域3のみであってもよいし、領域1と領域2であってもよいし、領域2

40

50

と領域3であってもよいし、領域3と領域1であってもよいし、領域1と領域2と領域3であってもよい。

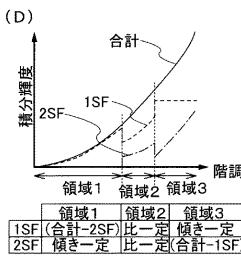

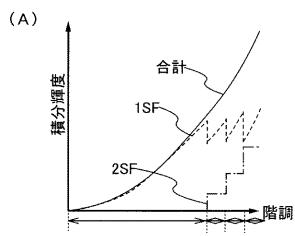

#### 【0152】

次に、図9を参照して、本実施の形態の一形態を説明する。図9は、表示できる階調を複数の領域、たとえば、3つの領域に分割し、それぞれの領域で各サブフレームが異なる特徴を有し得る場合において、1フレームで合計した積分輝度を1SFと2SFで配分する方法の例を表したものである。特に、3つの領域のうちの2つの領域において、どちらか一方のサブフレームの階調に対する積分輝度の変化が一定であり、残り1つの領域において、1SFと2SFの積分輝度比が、各階調において等しい場合について説明する。

10

#### 【0153】

図9の(A)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1および領域2における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1および領域2における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域3および2SFの領域3における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

20

#### 【0154】

図9の(B)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1および1SFの領域2における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1および2SFの領域2における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域3および2SFの領域3における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

30

#### 【0155】

図9の(C)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1および領域3における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1および領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域2および2SFの領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。

40

#### 【0156】

図9の(D)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1および1SFの領域3における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1および2SFの領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域2および2SFの領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画

50

像のボケを効率よく低減することができる。

【0157】

図9の(E)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域2および領域3における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域2および領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域1および2SFの領域1における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。

10

【0158】

図9の(F)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域2および1SFの領域3における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域2および2SFの領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域1および2SFの領域1における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、この場合の比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。

20

【0159】

なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。図9においては、この違いについては詳細に説明しないが、全ての領域について、これらの組み合わせを適用することができる。傾きが正または負の値をとるために、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、傾きが正または負の値をとるために、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、傾きが0である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

30

【0160】

なお、すでに述べたように、領域の境界における輝度の状態は、近接する低階調側の領域と比較して、大きい方向へ不連続に変化するか、連続しているか、小さい方向へ不連続に変化するかの、いずれかの状態を取り得る。図9においては、この違いについては詳細に説明しないが、全ての領域の境界について、これらの組み合わせを適用することができる。領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、領域の境界において輝度が連続である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

40

【0161】

なお、図9の(A)、(B)、(C)、(D)、(E)および(F)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよ

50

い。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であってもよい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域3のみであってもよいし、領域1と領域2であってもよいし、領域2と領域3であってもよいし、領域3と領域1であってもよいし、領域1と領域2と領域3であってもよい。

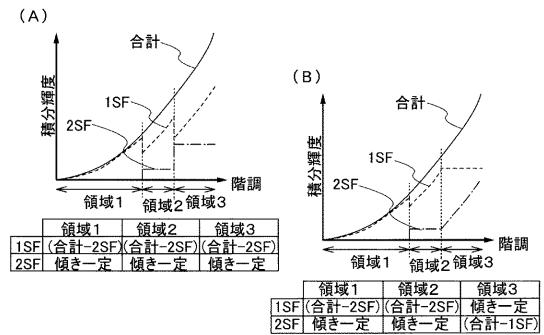

#### 【0162】

次に、図10を参照して、本実施の形態の一形態を説明する。図10は、表示できる階調を複数の領域、たとえば、3つの領域に分割し、それぞれの領域で各サブフレームが異なる特徴を有し得る場合において、1フレームで合計した積分輝度を1SFと2SFで配分する方法の例を表したものである。特に、3つの領域のうちの2つの領域において、1SFと2SFの積分輝度比が、各階調において等しく、残り1つの領域において、どちらか一方のサブフレームの階調に対する積分輝度の変化が一定である場合について説明する。また、全ての領域において、1SFと2SFの積分輝度比が、各階調において等しい場合についても説明する。

#### 【0163】

図10の(A)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域2、領域3および2SFの領域2、領域3における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、領域2における比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。なお、領域3における比の値は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

#### 【0164】

図10の(B)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域2における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域2における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域1、領域3および2SFの領域1、領域3における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、領域1における比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。なお、領域3における比の値は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

#### 【0165】

図10の(C)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域3における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域3における特徴は、合計輝度と、他方のサブフレームの輝度に従った輝度をとることである。1SFの領域1、領域2および2SFの領域1、領域2における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、領域1および領域2における比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こう

10

20

30

40

50

することで、低階調側における 1SF と 2SF の輝度差を大きくできるので、動画像のボケを効率よく低減することができる。

#### 【0166】

図10の(D)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。1SFの領域1、領域2、領域3および2SFの領域1、領域2、領域3における特徴は、1SFと2SFの積分輝度比が、各階調において等しいことである。なお、領域1および領域2における比の値(大きいほうの輝度に対する小さいほうの輝度の大きさ)は、0.5よりも小さく、0.1よりも大きいことが好適である。こうすることで、低階調側における1SFと2SFの輝度差を大きくできるので、動画像のボケを効率よく低減することができる。なお、領域3における比の値は、1よりも小さく、0.5よりも大きいことが好適である。こうすることで、動画像のボケを効率よく低減することができる。

10

#### 【0167】

なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。図10においては、この違いについては詳細に説明しないが、全ての領域について、これらの組み合わせを適用することができる。傾きが正または負の値をとるために、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、傾きが正または負の値をとるために、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、傾きが0である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

20

#### 【0168】

なお、すでに述べたように、領域の境界における輝度の状態は、近接する低階調側の領域と比較して、大きい方向へ不連続に変化するか、連続しているか、小さい方向へ不連続に変化するかの、いずれかの状態を取り得る。図10においては、この違いについては詳細に説明しないが、全ての領域の境界について、これらの組み合わせを適用することができる。領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、領域の境界において輝度が連続である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

30

#### 【0169】

なお、図10の(A)、(B)、(C)および(D)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であってもよい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域3のみであってもよいし、領域1と領域2であってもよいし、領域2と領域3であってもよいし、領域3と領域1であってもよいし、領域1と領域2と領域3であってもよい。

40

#### 【0170】

次に、図11を参照して、本実施の形態の一形態を説明する。図11は、表示できる階調を分割する数を4つ以上にした場合の例について説明したものである。領域の分割数は、それぞれの領域に含まれる階調の種類が複数存在する限りにおいて、いくつでもよい。図

50

11では、その中でも特徴のある例について取り扱う。

【0171】

図11の(A)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。図11の(A)に示す方法の特徴は、2SFに表示する画像を暗画像として用いることに加えて、2SFに表示する画像の輝度の種類を数種類に限定し、階調が大きくなるにつれて段階的に輝度を大きくしていくことである。さらに、それぞれの領域について、明画像を用いて階調を補完することである。こうすることで、2SFに表示する画像を表示するための映像データを作成することが容易になるため、周辺駆動回路の負荷が軽減するという利点がある。また、オーバードライブ駆動と組み合わせた場合に、2SFに表示する輝度の種類が少なくなるため、オーバードライブ回路を簡略化できる利点がある。なお、2SFに表示する輝度の種類は、4種類から16種類程度であることが好適である。また、表示できる階調を分割する数は、SFに表示する輝度の種類の数と同じであることが好適である。

【0172】

図11の(B)は、1フレームで合計した積分輝度を、1SFと2SFで配分する方法の一例を表したものである。図11の(B)に示す方法の特徴は、1SFに表示する画像を明画像として用いることに加えて、1SFに表示する画像の輝度の種類を数種類に限定し、階調が大きくなるにつれて段階的に輝度を大きくしていくことである。さらに、それぞれの領域について、暗画像を用いて階調を補完することである。さらに、領域の境界において、暗画像の輝度は0に近くすることである。こうすることで、1SFに表示する画像を表示するための映像データを作成することが容易になるため、周辺駆動回路の負荷が軽減するという利点がある。また、オーバードライブ駆動と組み合わせた場合に、1SFに表示する輝度の種類が少なくなるため、オーバードライブ回路を簡略化できる利点がある。また、暗画像の平均輝度を大幅に小さくすることができるため、動画像のボケを低減する効果が顕著である。なお、1SFに表示する輝度の種類は、16種類から64種類程度であることが好適である。また、表示できる階調を分割する数は、SFに表示する輝度の種類の数と同じであることが好適である。こうすることによって、たとえば、DAコンバーターの構成を簡易にすることができる。つまり、一方のサブフレーム期間においてはデジタル信号のまま扱い、他方のサブフレーム期間については、アナログ信号の振幅が小さくなる(離散値の種類が少なくなる)ため、消費電力が低減でき、回路規模を縮小できる。なお、両方のサブフレーム期間でアナログ信号である場合においても、両方のアナログ信号の振幅が小さくなるため、消費電力が低減でき、回路規模を縮小できる。

【0173】

なお、図11の(A)および(B)に示す形態において、1SFと2SFは交換可能であり、1SFと2SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わるのは、領域ごとに個別であってもよい。輝度の大小関係が入れ替わる領域は、たとえば、領域1のみであってもよいし、領域2のみであってもよいし、領域3のみであってもよいし、領域1と領域2であってもよいし、領域2と領域3であってもよいし、領域3と領域1であってもよいし、領域1と領域2と領域3であってもよい。領域4以降についても、同様である。

【0174】

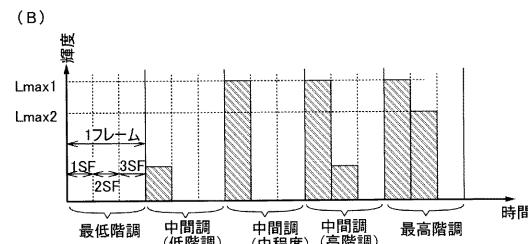

次に、図12を参照して、本実施の形態の一形態を説明する。図12は、1フレームを分割するサブフレームの数を、3つにした場合の例について説明したものである。サブフレームの数について限定はないが、3つにした場合には、特に有益な効果を奏する。ここで、1フレーム期間の1番始めに位置するサブフレーム期間を1SF、2番目に位置するサブフレーム期間を2SF、3番目に位置するサブフレーム期間を3SFと表記する。

【0175】

図12の(A)および(B)に示したグラフの横軸は時間であり、縦の実線はフレームの境界を表している。また、縦の破線は、サブフレームの境界を表している。縦軸は輝度である。すなわち、図12の(A)および(B)は、ある画素の輝度の時間に対する変化を、5フレームにわたって表示しているものである。

#### 【0176】

横軸の下方に表示されているのは、そのフレームにおいて、どの程度の階調が表されるかを示したものである。すなわち、図12の(A)および(B)においては、最初に最低階調を表示し、それから、低階調側の中間調、中程度の中間調、高階調側の中間調、最高階調の順で階調を表示していったときの、ある画素の輝度の時間に対する変化を示している。

10

#### 【0177】

図12の(A)および(B)に示す方法は、1SFと2SFにおける輝度を変化させることによって階調を表現し、かつ、3SFにおいては、輝度を0または非常に小さくすることで、擬似的にインパルス駆動を行なうことを可能にしていることを特徴としている。図12の(A)は、2SFに明画像、1SFに暗画像を表示する場合を表している。また、図12の(B)は、1SFに明画像、2SFに暗画像を表示する場合を表している。

#### 【0178】

なお、3SFにおいて、輝度を0または非常に小さくすることで、動画像のボケを改善する効果が得られるため、1SFの最大輝度  $L_{max1}$  と、2SFの最大輝度  $L_{max2}$  に特に限定はないが、実施形態1で説明したときと同様に、1SFで暗画像を挿入する場合、 $L_{max1}$  は、 $(1/2)L_{max2} < L_{max1} < (9/10)L_{max2}$  という範囲内であるのが望ましい。また、2SFで暗画像を挿入する場合、 $L_{max2}$  は、 $(1/2)L_{max1} < L_{max2} < (9/10)L_{max1}$  という範囲内であるのが望ましい。

20

#### 【0179】

図12の(C)は、1フレームで合計した積分輝度を、1SFと2SFと3SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1および1SFの領域2における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1および2SFの領域2における特徴は、合計輝度と、他のサブフレームの輝度に従った輝度をとることである。ここで、3SFの領域1、領域2における輝度は、0で一定であってもよい。こうすることで、全領域において、動画像のボケを効果的に低減することができる。

30

#### 【0180】

図12の(D)は、1フレームで合計した積分輝度を、1SFと2SFと3SFで配分する方法の一例を表したものである。また、グラフの下方に示した表は、各サブフレームの特徴を簡単に表したものである。2SFの領域1および1SFの領域2における特徴は、階調に対する積分輝度の変化が一定であることである。1SFの領域1および2SFの領域2における特徴は、合計輝度と、他のサブフレームの輝度に従った輝度をとることである。また、3SFの領域1、領域2における輝度の傾きは、小さい値で一定であってよい。なお、3SF最大輝度を  $L_{max3}$  としたとき、 $L_{max3}$  は、1SFの最大輝度および2SFの最大輝度の10分の1以下であることが好適である。こうすることで、全階調領域において、動画像のボケを効果的に低減することができる。

40

#### 【0181】

なお、傾きの値は正の値であっても、0であっても、負の値であってもよい。図12においては、この違いについては詳細に説明しないが、全ての領域について、これらの組み合わせを適用することができる。傾きが正または負の値をとるために、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、傾きが正または負の値をとるために、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、傾きが0である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不

50

自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

#### 【0182】

なお、すでに述べたように、領域の境界における輝度の状態は、近接する低階調側の領域と比較して、大きい方向へ不連続に変化するか、連続しているか、小さい方向へ不連続に変化するかの、いずれかの状態を取り得る。図12においては、この違いについては詳細に説明しないが、全ての領域の境界について、これらの組み合わせを適用することができる。領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が大きくなる場合は、動画像のボケを効率よく低減することができる。また、領域の境界において輝度が不連続に変化した結果、1SFおよび2SFの輝度差が小さくなる場合は、画像表示時のちらつきが低減するという利点がある。また、領域の境界において輝度が連続である場合は、画像処理や印加電圧が単純になり、周辺駆動回路の負荷が軽減するという利点がある。また、不自然な輪郭が発生する現象を低減することができる。また、1SFと2SFにおいて最高輝度を小さくできるので、消費電力を低減できる。

10

#### 【0183】

なお、図12の(A)、(B)、(C)および(D)に示す形態において、1SF、2SF、3SFは交換可能であり、1SF、2SF、3SFの特徴が入れ替わった場合においても、同様の効果を有する。なお、1SFにおける輝度が2SFにおける輝度よりも大きいが、これに限定されない。1SFにおける輝度が2SFにおける輝度よりも小さくてもよい。ただし、合計輝度が非線形の場合は、2SFにおける輝度が小さい方が、階調を制御しやすいため、望ましい。また、1SFと2SFで、輝度の大小関係が入れ替わってもよい。また、領域1のみ1SFと2SFの輝度の大小関係が入れ替わってもよいし、領域2のみ1SFと2SFの輝度の大小関係が入れ替わってもよいし、領域1と領域2で1SFと2SFの輝度の大小関係が入れ替わってもよい。

20

#### 【0184】

なお、本実施形態で説明した全ての形態は、オーバードライブ駆動と組み合わせて実施してもよい。こうすることで、液晶表示素子の応答速度を速め、動画像の画質を向上させることができる。

#### 【0185】

なお、本実施形態で説明した全ての形態は、走査型バックライトと組み合わせた液晶表示装置として実施してもよい。こうすることで、バックライトの平均輝度を低減するので、消費電力を低減することができる。

30

#### 【0186】

なお、本実施形態で説明した全ての形態は、高周波駆動と組み合わせて実施してもよい。こうすることで、動画像の画質をさらに向上させることができる。

#### 【0187】

なお、本実施形態で説明した全ての形態は、コモン線の電位を操作して、表示素子に目的の電圧を印加する駆動方法と組み合わせて実施してもよい。こうすることで、映像信号を画素に書き込む頻度が小さくなるため、画素に映像信号を書き込む際の消費電力を低減することができる。

40

#### 【0188】

なお、本実施形態で説明した全ての形態は、有機EL素子などの電流で駆動する表示素子と組み合わせて実施してもよい。こうすることで、映像信号電流を大きくすることができる。書き込み時間を小さくすることができる。

#### 【0189】

なお、本実施形態で説明した全ての形態は、インターレース走査と組み合わせて実施してもよい。こうすることで、周辺駆動回路の動作周波数を低減することができるので、消費電力を低減することができる。特に、暗画像において非発光となる画素が多い画像であるとき、または、明画像において最高輝度で発光する画素が多い画像であるときに、効果的である。すなわち、階調の変化の少ない画像に対しては、インターレース走査による解像

50

度の低下が少ないからである。

#### 【0190】

なお、本実施形態で説明した全ての形態は、基準電位を変更できるDAコンバーター回路と組み合わせて実施してもよい。こうすることで、DAコンバーター回路の効率を向上させることができる。特に、明画像を表示するサブフレームと、暗画像を表示するサブフレームで、基準電位を変更できるようにするのが効果的である。すなわち、明画像を表示するときと、暗画像を表示するときでは、必要とされる映像信号の電位の平均値が異なるためである。

#### 【0191】

なお、本実施の形態は、他の実施の形態と、自由に組み合わせて実施することができる。

10

#### 【0192】

##### (実施の形態3)

本実施形態においては、表示装置の画素構造について説明する。特に、液晶表示装置の画素構造について説明する。

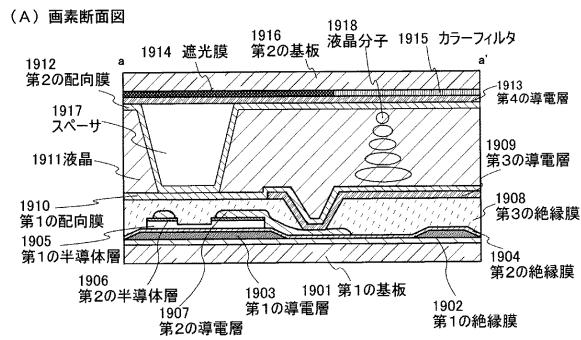

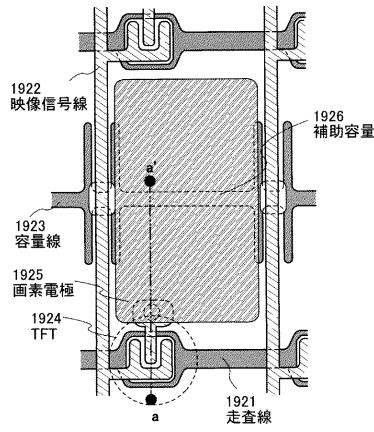

#### 【0193】

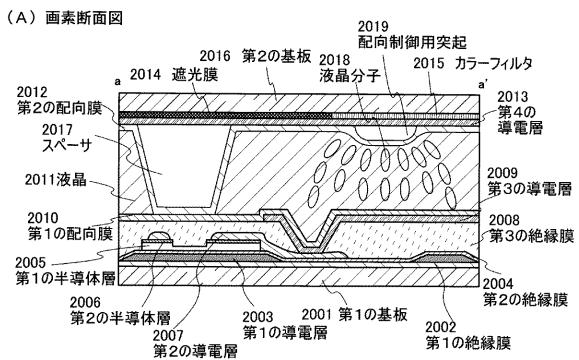

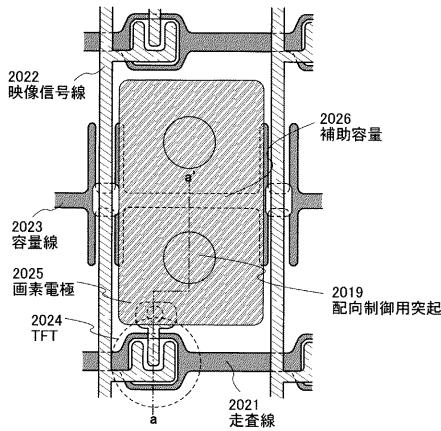

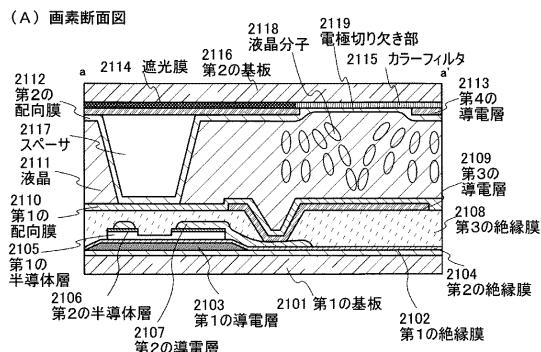

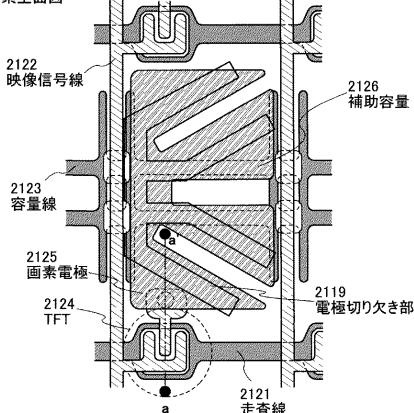

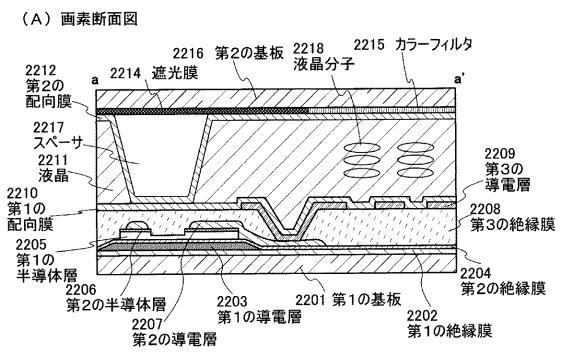

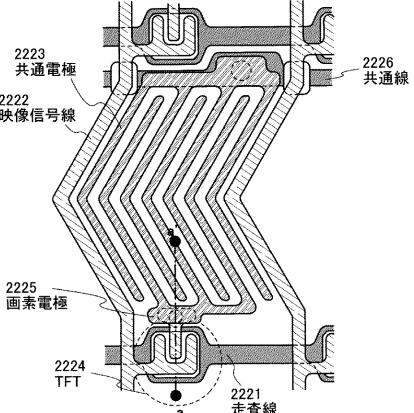

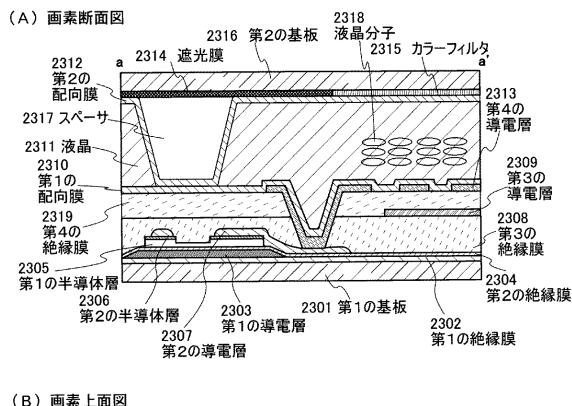

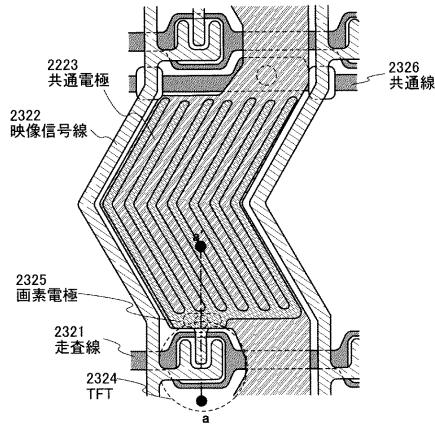

図19は、液晶表示装置の画素構造のうち、TN(Twisted Nematic)方式と呼ばれるものに、薄膜トランジスタ(TFT)を組み合わせた場合の画素の断面図と上面図である。図19の(A)は、画素の断面図であり、図19の(B)は、画素の上面図である。また、図19の(A)に示す画素の断面図は、図19の(B)に示す画素の上面図における線分a-a'に対応している。図19に示す画素構造の液晶表示装置を用いることによって、安価に液晶表示装置を製造することができる。さらに、図19に示す画素構造の液晶表示装置を、実施の形態1および実施の形態2など他の実施形態と組み合わせて実施することで、動画像の画質が向上した液晶表示装置を安価に実現することができる。

20

#### 【0194】

図19の(A)を参照して、TN方式の液晶表示装置の画素構造について説明する。液晶表示装置は、液晶パネルと呼ばれる、画像を表示する基幹部分を有する。液晶パネルは、加工を施した2枚の基板を、数μmのギャップを持たせて貼り合わせ、2枚の基板間に液晶材料を注入することで作製される。図19の(A)において、2枚の基板は、第1の基板1901、および第2の基板1916である。第1の基板には、TFTおよび画素電極を作製し、また、第2の基板には、遮光膜1914、カラーフィルタ1915、第4の導電層1913、スペーサ1917、および第2の配向膜1912を作製してもよい。

30

#### 【0195】

なお、第1の基板1901にTFTを作製しなくとも実施可能である。TFTを作製せずに実施する場合は、工程数が減少するため、製造コストを低減することができる。また、構造が簡単であるので、歩留まりを向上させることができる。一方、TFTを作製して実施する場合は、より大型の表示装置を得ることができる。

#### 【0196】

なお、図19に示すTFTは、非晶質半導体を用いたボトムゲート型のTFTであり、大面积の基板を用いて、安価に作製できるという利点がある。しかし、これに限定されるものではない。使用できるTFTの構造は、ボトムゲート型のTFTではチャネルエッチ型、チャネル保護型などがある。また、トップゲート型でもよい。さらに、非晶質半導体だけではなく、多結晶半導体も用いることができる。

40

#### 【0197】

なお、第2の基板1916に遮光膜1914を作製しなくとも実施可能である。遮光膜1914を作製せずに実施する場合は、工程数が減少するため、製造コストを低減することができる。また、構造が簡単であるので、歩留まりを向上させることができる。一方、遮光膜1914を作製して実施する場合は、黒表示時に光漏れの少ない表示装置を得ることができる。

#### 【0198】

50

なお、第2の基板1916にカラーフィルタ1915を作製しなくとも実施可能である。カラーフィルタ1915を作製せずに実施する場合は、工程数が減少するため、製造コストを低減することができる。また、構造が簡単であるので、歩留まりを向上させることができる。一方、カラーフィルタ1915を作製して実施する場合は、カラー表示ができる表示装置を得ることができる。

#### 【0199】

なお、第2の基板1916にスペーサ1917を作製せず、球状のスペーサを散布することでも実施可能である。球状のスペーサを散布することで実施する場合は、工程数が減少するため、製造コストを低減することができる。また、構造が簡単であるので、歩留まりを向上させることができる。一方、スペーサ1917を作製して実施する場合は、スペーサの位置がばらつかないため、2枚の基板間の距離を一様にすることことができ、表示ムラの少ない表示装置を得ることができる。

10

#### 【0200】

次に、第1の基板1901に施す加工について説明する。第1の基板1901は透光性を有する基板が好適であり、例えば石英基板、ガラス基板またはプラスチック基板でもよい。なお、第1の基板1901は遮光性の基板でもよく、半導体基板、SOI (Silicon on on Insulator) 基板でもよい。

#### 【0201】

まず、第1の基板1901に第1の絶縁膜1902を成膜してもよい。第1の絶縁膜1902は、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜 (SiO<sub>x</sub>N<sub>y</sub>) 等の絶縁膜であってもよい。または、これらの膜の少なくとも2つの膜を組み合わせた積層構造の絶縁膜を用いてもよい。第1の絶縁膜1902を成膜して実施する場合は、基板からの不純物が半導体層に影響を及ぼし、TFTの性質が変化してしまうのを防ぐことができるので、信頼性の高い表示装置を得ることができる。なお、第1の絶縁膜1902を成膜せずに実施する場合は、工程数が減少するため、製造コストを低減することができる。また、構造が簡単であるので、歩留まりを向上させることができる。

20

#### 【0202】

次に、第1の基板1901または第1の絶縁膜1902上に、第1の導電層1903を形成する。なお、第1の導電層1903は、形状を加工して形成してもよい。形状を加工する工程は、次のようなものであることが好適である。まず、第1の導電層を全面に成膜する。このとき、スパッタ装置、またはCVD装置などの成膜装置を用いてもよい。次に、全面に成膜した第1の導電層上に、感光性のレジスト材料を全面に形成する。次に、フォトリソグラフィ法やレーザー直描法などによって、形成したい形状に従ってレジスト材料を感光させる。次に、感光させたレジスト材料、または感光させなかったレジスト材料のうち、どちらか一方を、エッチングによって除去することで、第1の導電層1903を形状加工するためのマスクを得ることができる。その後、形成したマスクパターンに従って、第1の導電層1903をエッチングにより除去することで、所望のパターンに第1の導電層1903を形状加工することができる。なお、第1の導電層1903をエッチングする方法には、化学的な方法 (ウェットエッチング) と、物理的な方法 (ドライエッチング) があるが、第1の導電層1903の材料や、第1の導電層1903の下層にある材料の性質などを勘案し、適宜選択する。なお、第1の導電層1903に使用する材料は、Mo、Ti、Al、Nd、Crなどが好適である。または、これらの積層構造であってもよい。さらに、これらの合金を単層または積層構造として、第1の導電層1903として形成してもよい。

30

#### 【0203】

次に、第2の絶縁膜1904を形成する。このとき、スパッタ装置、またはCVD装置などの成膜装置を用いてもよい。なお、第2の絶縁膜1904に使用する材料は、熱酸化膜、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などが好適である。または、これらの積層構造であってもよい。なお、第1の半導体層1905に接する部分の第2の絶縁膜1904は、酸化シリコン膜であることが、特に好適である。それは、酸化シリ

40

50

コン膜にすると半導体層 1905との界面におけるトラップ準位が少なくなるからである。なお、第1の導電層 1903をMoで形成するときは、第1の導電層 1903と接する部分の第2の絶縁膜 1904は窒化シリコン膜が好ましい。それは、窒化シリコン膜はMoを酸化させないからである。

#### 【0204】

次に、第1の半導体層 1905を形成する。その後、第2の半導体層 1906を連続して形成するのが好適である。なお、第1の半導体層 1905および第2の半導体層 1906は、形状を加工して形成してもよい。形状を加工する工程は、前述したフォトリソグラフィ法等の方法であることが好適である。なお、第1の半導体層 1905に使用する材料は、シリコンまたはシリコングルマニウムなどが好適である。また、第2の半導体層 1906に使用する材料は、リン等を含んだシリコン等が好適である。

10

#### 【0205】

次に、第2の導電層 1907を形成する。このとき、スパッタ法または印刷法を用いるのが好適である。なお、第2の導電層 1907に使用する材料は、透明性を有していても、反射性を有していてもよい。透明性を有する場合は、例えば、酸化インジウムに酸化スズを混ぜたインジウムスズ酸化物 (ITO) 膜、インジウムスズ酸化物 (ITO) に酸化珪素を混ぜたインジウムスズ珪素酸化物膜、酸化インジウムに酸化亜鉛を混ぜたインジウム亜鉛酸化物 (IZO) 膜、酸化亜鉛膜、または酸化スズ膜を用いることができる。なお、IZOとは、ITOに2~20wt%の酸化亜鉛を混合させたターゲットを用いてスパッタリングにより形成される透明導電材料である。一方、反射性を有する場合は、Ti、Mo、Ta、Cr、W、Alなどを用いることができる。また、Ti、Mo、Ta、Cr、WとAlを積層させた2層構造、AlをTi、Mo、Ta、Cr、Wなどの金属で挟んだ3層積層構造としても良い。なお、第2の導電層 1907は、形状を加工して形成してもよい。形状を加工する方法は、前述したフォトリソグラフィ法等の方法であることが好適である。なお、エッティング方法は、ドライエッティングで行なうのが好適である。ドライエッティングは ECR (Electron Cyclotron Resonance) や ICP (Inductive Coupled Plasma) などの高密度プラズマ源を用いたドライエッティング装置によって行われてもよい。

20

#### 【0206】

なお、配線や電極は、アルミニウム (Al)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、タンゲステン (W)、ネオジウム (Nd)、クロム (Cr)、ニッケル (Ni)、白金 (Pt)、金 (Au)、銀 (Ag)、銅 (Cu)、マグネシウム (Mg)、スカンジウム (Sc)、コバルト (Co)、亜鉛 (Zn)、ニオブ (Nb)、シリコン (Si)、リン (P)、ボロン (B)、ヒ素 (As)、ガリウム (Ga)、インジウム (In)、錫 (Sn)、酸素 (O) で構成された群から選ばれた一つ又は複数の元素、もしくは、前記群から選ばれた一つ又は複数の元素を成分とする化合物や合金材料 (例えば、インジウム錫酸化物 (ITO)、インジウム亜鉛酸化物 (IZO)、酸化珪素を添加したインジウム錫酸化物、酸化亜鉛、アルミニネオジウム (Al-Nd)、マグネシウム銀 (Mg-Ag) など)、もしくは、これらの化合物を組み合わせた物質などを有して形成される。もしくは、それらとシリコンの化合物 (シリサイド) (例えば、アルミシリコン、モリブデンシリコン、ニッケルシリサイドなど) や、それらと窒素の化合物 (例えば、窒化チタン、窒化タンタル、窒化モリブデン等) を有して形成される。なお、シリコン (Si)には、n型不純物 (リンなど) やp型不純物 (ボロンなど) を多く含んでいてもよい。これらの不純物を含むことにより、導電率の向上や、通常の導体と同様な振る舞いをするので、配線や電極として利用しやすくなったりする。なお、シリコンは、単結晶でもよいし、多結晶 (ポリシリコン) でもよいし、非晶質 (アモルファスシリコン) でもよい。単結晶シリコンや多結晶シリコンを用いることにより、抵抗を小さくすることが出来る。非晶質シリコンを用いることにより、簡単な製造工程で作ることが出来る。なお、アルミニウムや銀は、導電率が高いため、信号遅延を低減することができ、エッティングしやすいので、微細加工を行うことが出来る。なお、銅は、導電率が高いため、信号遅延を低減する

30

40

50

ことが出来る。なお、モリブデンは、ITOやIZOなどの酸化物半導体や、シリコンと接触しても、材料が不良を起こすなどの問題が生じることなく製造できたり、エッチングがしやすかったり、耐熱性が高いため、望ましい。なお、チタンは、ITOやIZOなどの酸化物半導体や、シリコンと接触しても、材料が不良を起こすなどの問題が生じることなく製造できたり、耐熱性が高いため、望ましい。なお、タンゲステンは、耐熱性が高いため、望ましい。なお、ネオジウムは、耐熱性が高いため、望ましい。特に、ネオジウムとアルミニウムとの合金にすると、耐熱性が向上し、アルミニウムがヒロックをおこしにくくなるため、望ましい。なお、シリコンは、トランジスタが有する半導体層と同時に形成できたり、耐熱性が高いため、望ましい。なお、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を添加したインジウム錫酸化物、酸化亜鉛、シリコン(Si)は、透光性を有しているため、光を透過させるような部分に用いることができるため、望ましい。たとえば、画素電極や共通電極として用いることができる。

10

#### 【0207】

なお、これらが単層で配線や電極を形成していてもよいし、多層構造になっていてもよい。単層構造で形成することにより、製造工程を簡略化することができ、工程日数を少なくでき、コストを低減することができる。また、多層構造にすることにより、それぞれの材料のメリットを生かし、デメリットを低減させ、性能の良い配線や電極を形成することができる。たとえば、抵抗の低い材料(アルミニウムなど)を多層構造の中に含むようすることにより、配線の低抵抗化を図ることができる。また、耐熱性が高い材料を含むようすれば、例えば、耐熱性が弱いが、別のメリットを有する材料を、耐熱性が高い材料で挟むような積層構造にすることにより、配線や電極全体として、耐熱性を高くすることができます。例えば、アルミニウムを含む層を、モリブデンやチタンを含む層で挟んだような形にした積層構造にすると望ましい。また、別の材料の配線や電極などと直接接するような部分がある場合、お互いに悪影響を及ぼすことがある。例えば、一方の材料が他方の材料の中に入つていて、性質を変えてしまい、本来の目的を果たせなくなったり、製造するときに、問題が生じて、正常に製造できなくなったりすることがある。そのような場合、ある層を別の層で挟んだり、覆ったりすることにより、問題を解決することができる。例えば、インジウム錫酸化物(ITO)と、アルミニウムを接触させたい場合は、間に、チタンやモリブデンを挟むことが望ましい。また、シリコンとアルミニウムを接触させたい場合は、間に、チタンやモリブデンを挟むことが望ましい。

20

#### 【0208】

次に、TFTのチャネル領域を形成する。このとき、第2の導電層1907をマスクとして、第2の半導体層1906のエッチングを行なってもよい。こうすることで、マスク枚数を減らすことができるので、製造コストを低減することができる。導電性をもつ第2の半導体層1906のエッチングを行なうことにより選択的に第2の半導体層1906を除去する。その結果当該除去された第2の半導体層1906と重畳する第1の半導体層1905がチャネル領域となる。なお、第2の半導体層1906のエッチングの際に第1の半導体層1905の一部がエッチングされる場合もある。なお、第1の半導体層1905と第2の半導体層1906を連続で形成せずに、第1の半導体層1905の形成のあと、TFTのチャネル領域となる部分にストップーとなる膜を成膜およびパターン加工し、その後、第2の半導体層1906を形成してもよい。こうすることで、第2の導電層1907をマスクとして用いないで、TFTのチャネル領域を形成することができるので、レイアウトパターンの自由度が大きくなる利点がある。また、第2の半導体層1906のエッチング時に第1の半導体層1905までエッチングしてしまわないと、エッチング不良を起こすことなく、確実にTFTのチャネル領域が形成できる利点がある。

30

#### 【0209】

次に、第3の絶縁膜1908を形成する。第3の絶縁膜は、透明性を有していることが好適である。なお、第3の絶縁膜1908に用いる材料は、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)または、低誘電率の有機化合物材料(感光性又は非感光性の有機樹脂材料)などが好適である。また、シロキサンを含む材料を用いてもよい。

40

50

シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される材料である。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基としてフルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。第3の絶縁膜1908は積層構造でも良い。なお、第3の絶縁膜1908は、形状を加工して形成してもよい。形状を加工する方法は、前述したフォトリソグラフィ法等の方法であることが好適である。このとき、同時に第2の絶縁膜1904もエッチングすることで、第2の導電層1907に達するコンタクトホールだけではなく、第1の導電層1903に達するコンタクトホールを形成することができる。なお、第3の絶縁膜1908の表面は、できるだけ平坦であることが好適である。それは、液晶が接する面の凹凸により、液晶分子の配向が影響を受けてしまうからである。

10

#### 【0210】

次に、第3の導電層1909を形成する。このとき、スパッタ法または印刷法を用いるのが好適である。なお、第3の導電層1909に使用する材料は、第2の導電層1907と同じく、透明性を有していても、反射性を有していてもよい。なお、第3の導電層1909として使用できる材料は、第2の導電層1907と同様でもよい。また、第3の導電層1909は、形状を加工して形成してもよい。形状を加工する方法は、第2の導電層1907と同様でもよい。

20

#### 【0211】

次に、第1の配向膜1910を形成する。配向膜1910には、ポリイミドなどの高分子膜を用いることができる。なお、第1の配向膜1910を形成後、液晶分子の配向を制御するために、ラビングを行なってもよい。ラビングは、布で配向膜をこすことによって、配向膜にスジをつける工程である。ラビングを行なうことによって、配向膜に配向性を持たせることができる。

20

#### 【0212】

以上のように作製した第1の基板1901と、遮光膜1914、カラーフィルタ1915、第4の導電層1913、スペーサ1917、および第2の配向膜1912を作製した第2の基板1916を、シール材によって数μmのギャップを持たせて貼り合わせ、2枚の基板間に液晶材料1911を注入することで、液晶パネルが作製できる。なお、図19に示すようなTN方式の液晶パネルにおいては、第4の導電層1913は、第2の基板1916の全面に作製されていてもよい。

30

#### 【0213】

次に、図19に示す、TN方式の液晶パネルの画素構造の特徴について説明する。図19の(A)に示した液晶分子1918は、長軸と短軸を持った細長い分子である。液晶分子1918の向きを示すため、図19の(A)においては、その長さによって表現している。すなわち、長く表現された液晶分子1918は、その長軸の向きが紙面に平行であり、短く表現された液晶分子1918ほど、その長軸の向きが紙面の法線方向に近くなっているとする。つまり、図19の(A)に示した液晶分子1918は、第1の基板1901に近いものと、第2の基板1916に近いものとでは、その長軸の向きが90度異なっており、これらの中間に位置する液晶分子1918の長軸の向きは、これらを滑らかにつなぐような向きとなる。すなわち、図19の(A)に示した液晶分子1918は、第1の基板1901と第2の基板1916の間で、90度ねじれているような配向状態となっている。

40

#### 【0214】

次に、図19の(B)を参照して、TN方式の液晶表示装置の画素のレイアウトの一例について説明する。TN方式の液晶表示装置の画素は、走査線1921と、映像信号線1922と、容量線1923と、TFT1924と、画素電極1925と、画素容量1926と、を備えていてもよい。

#### 【0215】

走査線1921は、TFT1924のゲート電極と電気的に接続されるため、第1の導電

50

層 1 9 0 3 で構成されているのが好適である。

【 0 2 1 6 】

映像信号線 1 9 2 2 は、TFT 1 9 2 4 のソース電極またはドレイン電極と電気的に接続されるため、第 2 の導電層 1 9 0 7 で構成されているのが好適である。また、走査線 1 9 2 1 と映像信号線 1 9 2 2 はマトリックス状に配置されるため、少なくとも、異なる層の導電層で形成されるのが好適である。

【 0 2 1 7 】

容量線 1 9 2 3 は、画素電極 1 9 2 5 と平行に配置されることで、画素容量 1 9 2 6 を形成するための配線であり、第 1 の導電層 1 9 0 3 で構成されているのが好適である。なお、図 1 9 の ( B ) に示すように、容量線 1 9 2 3 は、映像信号線 1 9 2 2 に沿って、映像信号線 1 9 2 2 を囲むように延設されていてもよい。こうすることで、映像信号線 1 9 2 2 の電位変化に伴って、電位を保持するべき電極の電位が変化してしまう現象、いわゆるクロストークを低減することができる。なお、映像信号線 1 9 2 2 との交差容量を低減させるため、図 1 9 の ( B ) に示すように、第 1 の半導体層 1 9 0 5 を容量線 1 9 2 3 と映像信号線 1 9 2 2 の交差領域に設けてもよい。

10

【 0 2 1 8 】

TFT 1 9 2 4 は、映像信号線 1 9 2 2 と画素電極 1 9 2 5 を導通させるスイッチとして動作する。なお、図 1 9 の ( B ) に示すように、TFT 1 9 2 4 のソース領域またはドレイン領域のどちらか一方を、ソース領域またはドレイン領域の他方を囲むように配置してもよい。こうすることで、小さい面積で大きなチャネル幅を得ることができ、スイッチング能力を大きくすることができる。なお、図 1 9 の ( B ) に示すように、TFT 1 9 2 4 のゲート電極は、第 1 の半導体層 1 9 0 5 を囲むように配置してもよい。

20

【 0 2 1 9 】