(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-83733

(P2012-83733A)

(43) 公開日 平成24年4月26日(2012.4.26)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>G09F 9/30</b> (2006.01)   | G09F 9/30  | 338 3K107   |

| <b>H01L 21/336</b> (2006.01) | H01L 29/78 | 612D 4M104  |

| <b>H01L 29/786</b> (2006.01) | H01L 29/78 | 618B 5C094  |

| <b>H01L 21/02</b> (2006.01)  | H01L 29/78 | 617M 5F110  |

| <b>H01L 27/12</b> (2006.01)  | H01L 29/78 | 616V        |

審査請求 未請求 請求項の数 10 O.L. (全 45 頁) 最終頁に続く

|              |                              |            |                                                                                                                                                                                  |

|--------------|------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2011-198182 (P2011-198182) | (71) 出願人   | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地                                                                                                                                   |

| (22) 出願日     | 平成23年9月12日 (2011.9.12)       | (72) 発明者   | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                                                                                                     |

| (31) 優先権主張番号 | 特願2010-204935 (P2010-204935) | (72) 発明者   | 波多野 眞<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                                                                                                     |

| (32) 優先日     | 平成22年9月13日 (2010.9.13)       | F ターム (参考) | 3K107 AA01 BB01 CC23 CC41 CC45<br>EE04 EE46 FF00 FF17 GG28<br>4M104 AA03 AA09 BB02 BB03 BB04<br>BB13 BB14 BB16 BB17 BB18<br>BB36 CC01 CC05 DD34 DD37<br>DD51 DD52 DD53 FF13 GG09 |

| (33) 優先権主張国  | 日本国 (JP)                     |            | 最終頁に続く                                                                                                                                                                           |

(54) 【発明の名称】発光表示装置及び発光表示装置の作製方法

## (57) 【要約】

【課題】薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製する方法を提供する。

【解決手段】剥離層を介して基板上に素子領域を形成する際に、半導体層のエッティングと、画素電極とドレン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッティング工程で行う。更に素子領域を基板から剥離して、じん性の高い第1の支持体に設け、第1の支持体及びじん性の高い第2の支持体で液晶素子を挟持することで、薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製できる。

【選択図】図10

## 【特許請求の範囲】

## 【請求項 1】

基板上に剥離層を形成し、

前記剥離層上に第1の導電層を形成し、

前記第1の導電層上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1の導電層を選択的に除去して第1のゲート電極と第2のゲート電極を形成し、

前記第1のゲート電極及び前記第2のゲート電極上にゲート絶縁層となる第1の絶縁層を形成し、

前記第1の絶縁層上に半導体層を形成し

10

前記半導体層上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のゲート電極に重畳する前記半導体層の一部及び前記第1の絶縁層の一部を選択的に除去して第1の開口部を形成し、

前記半導体層および前記第1の開口部を覆う状態に第2の導電層を形成し、

前記第2の導電層上に第3のレジストマスクを形成し、

前記第3のレジストマスクを用いて前記第2の導電層を選択的に除去して、第1のソース電極及び第1のドレイン電極ならびに第2のソース電極及び第2のドレイン電極を形成することで、前記第1のゲート電極、前記第1のソース電極及び前記第1のドレイン電極を有する第1のトランジスタと前記第2のゲート電極、前記第2のソース電極及び前記第2のドレイン電極を有する第2のトランジスタを形成し、

20

前記第1のドレイン電極と前記第2のゲート電極は、前記第1の開口部を介して電気的に接続されており、

前記第1のソース電極及びドレイン電極、前記第2のソース電極及びドレイン電極、及び前記半導体層上に保護絶縁層となる第2の絶縁層を形成し、

前記第2の絶縁層上に第4のレジストマスクを形成し、

前記第4のレジストマスクを用いて前記第1のソース電極及びドレイン電極、前記第2のソース及びドレイン電極と重畳しない前記第2の絶縁層の一部および前記半導体層の一部を除去して第2の開口部を形成すると同時に、前記第2のドレイン電極と重畳する前記第2の絶縁層の一部を選択的に除去して第3の開口部を形成し、

前記第3の開口部を覆うように前記第2の絶縁層上に第3の導電層を形成し、

30

前記第3の導電層上に第5のレジストマスクを形成し、

前記第5のレジストマスクを用いて前記第3の導電層を選択的に除去して第1の画素電極を形成し、

前記第2の開口部、前記第3の開口部、前記第2の絶縁層及び前記第1の画素電極の端部を覆うように第4の絶縁層を形成することを特徴とする発光表示装置の作製方法。

## 【請求項 2】

基板上に剥離層を形成し、

前記剥離層上に第1の導電層を形成し、

前記第1の導電層上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1の導電層を選択的に除去して第1のゲート電極と第2のゲート電極を形成し、

前記第1のゲート電極及び前記第2のゲート電極上にゲート絶縁層となる第1の絶縁層を形成し、

前記第1の絶縁層上に半導体層を形成し、

前記半導体層上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のゲート電極に重畳する前記半導体層の一部及び前記第1の絶縁層の一部を選択的に除去して第1の開口部を形成し、

前記半導体層及び前記第1の開口部を覆うように第2の導電層を形成し、

前記第2の導電層上に第3のレジストマスクを形成し、

前記第3のレジストマスクを用いて前記第2の導電層を選択的に除去して、

40

50

第1のソース電極及び第1のドレイン電極ならびに第2のソース電極及び第2のドレイン電極を形成することで、前記第1のゲート電極、前記第1のソース電極および前記第1のドレイン電極を有する第1のトランジスタと前記第2のゲート電極、前記第2のソース電極および前記第2のドレイン電極を有する第2のトランジスタを形成し、

前記第1のドレイン電極と前記第2のゲート電極は、前記第1の開口部を介して電気的に接続されており、

前記第1のソース電極及びドレイン電極、前記第2のソース電極及びドレイン電極、及び前記半導体層上に保護絶縁層となる第2の絶縁層を形成し、

前記第2の絶縁層上に平坦化絶縁層となる第3の絶縁層を形成し、

前記第3の絶縁層上に第4のレジストマスクを形成し、

前記第4のレジストマスクを用いて、前記第1のソース電極及びドレイン電極、前記第2のソース及びドレイン電極と重畠しない前記第3の絶縁層の一部、前記第2の絶縁層の一部および前記半導体層の一部を除去して第2の開口部を形成すると同時に、前記第2のドレイン電極に重畠する前記第3の絶縁層の一部及び前記第2の絶縁層の一部を選択的に除去して第3の開口部を形成し、

前記第3の開口部を覆うように前記第3の絶縁層上に第3の導電層を形成し、

前記第3の導電層上に第5のレジストマスクを形成し、

前記第5のレジストマスクを用いて前記第3の導電層を選択的にエッチングして第1の画素電極を形成し、

前記第2の開口部、前記第3の開口部、及び前記第1の画素電極の端部を覆うように第4の絶縁層を形成することを特徴とする発光表示装置の作製方法。 20

### 【請求項3】

請求項1または請求項2において、

前記基板と前記ゲート電極の間に下地層が形成されることを特徴とする発光表示装置の作製方法。

### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記半導体層は酸化物半導体であることを特徴とする発光表示装置の作製方法。

### 【請求項5】

請求項4において、

前記酸化物半導体に加熱処理を行うことを特徴とする発光表示装置の作製方法。 30

### 【請求項6】

請求項1乃至5のいずれか一項において、前記第1の導電層及び前記第2の導電層は、銅を含む材料で形成することを特徴とする発光表示装置の作製方法。

### 【請求項7】

請求項6において、前記第1の導電層または前記第2の導電層形成後の加熱処理の上限温度は450であることを特徴とする発光表示装置の作製方法。

### 【請求項8】

請求項1乃至5のいずれか一項において、前記第1の導電層及び前記第2の導電層は、アルミニウムを含む材料で形成することを特徴とする発光表示装置の作製方法。 40

### 【請求項9】

請求項8において、前記第1の導電層または前記第2の導電層形成後の加熱処理の上限温度は380であることを特徴とする発光表示装置の作製方法。

### 【請求項10】

請求項1乃至請求項8のいずれか一項において、

少なくとも第1のゲート電極、第2のゲート電極、第1の絶縁層、半導体層、第1のソース電極、第1のドレイン電極、第2のソース電極、第2のドレイン電極、第2の絶縁層および第1の画素電極を有する素子領域を、前記基板上に前記剥離層を介して形成した後に、

前記素子領域表面を覆う状態に保護層を形成する工程と、 50

前記保護層および前記素子領域を前記基板から剥離する工程と、

前記素子領域の裏面に  $1.5 [ \text{M Pa} \cdot \text{m}^{1/2} ]$  以上の破壊じん性値を有する第1の支持体を貼り合わせる工程と、

前記第1の支持体から前記保護層を除去する工程と、

前記素子領域に形成された前記第1の画素電極上に有機化合物を含む層を選択的に形成する工程と、

前記有機化合物を含む層を覆う状態に第2の画素電極を形成する工程と、

前記第2の画素電極を覆う状態に  $1.5 [ \text{M Pa} \cdot \text{m}^{1/2} ]$  以上の破壊じん性値を有する第2の支持体を貼り合わせる工程を少なくとも有することを特徴とする発光表示装置の作製方法。

10

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、薄膜トランジスタを有する発光表示装置の作製方法に関する。

## 【背景技術】

## 【0002】

近年、発光表示装置に対して、低価格化、薄型化、軽量化のニーズが非常に高まっている。

## 【0003】

発光表示装置の駆動方式は、パッシブマトリクス型とアクティブマトリクス型の2つに大別されるが、高画質化や高速応答への対応に優れたアクティブマトリクス型の発光表示装置が主流となっている。

20

## 【0004】

上記のようなアクティブマトリクス型発光表示装置の用途は拡大しており、画面サイズの大面積化、高精細化及び高開口率化の要求が高まっている。また、アクティブマトリクス型発光表示装置には高い信頼性が求められ、その生産方法には高い生産性及び生産コストの低減が求められる。生産性を高め、生産コストを低減する方法の一つに、工程の簡略化が挙げられる。

## 【0005】

アクティブマトリクス型発光表示装置は、各画素毎にスイッチング素子が設けられている。スイッチング素子には主に薄膜トランジスタが用いられており、チャネル形成領域がゲート電極より下層に設けられるトップゲート型のトランジスタと、チャネル形成領域がゲート電極より上層に設けられるボトムゲート型のトランジスタに大別される。これらの薄膜トランジスタは、少なくとも5枚以上のフォトマスクを用いて作製されることが一般的である。

30

## 【0006】

発光表示装置を安価に作製するためには、フォトマスクの枚数をいかに少なくできるかが、重要な要素の一つとなっている。フォトマスクの使用枚数を削減するには、裏面露光（例えば特許文献1を参照）、レジストリフロー又はリフトオフ法といった複雑な技術を用いるものが多く、特殊な装置を必要とするものが多い。このような複雑な技術を用いることで、これに起因する様々な問題が生じ、発光表示装置の歩留まり低下や薄膜トランジスタの電気特性悪化の一因となり得てしまう。

40

## 【0007】

また、発光表示装置の薄型化、軽量化を実現する方法の1つとして、発光材料を挟持するための基板を、機械的研磨や化学的研磨などの手法により薄くする事が挙げられる。

## 【0008】

発光材料を挟持するための基板は主としてガラス基板が用いられており、基板を機械的研磨や化学的研磨などの手法により薄くするには限界があり、さらに、薄くするほど基板の強度が低下し、外部からの衝撃により発光表示装置が破壊され易くなるといった課題があるため、発光材料を挟持するための基板としては、高いじん性を備えた支持体（例えば樹

50

脂フィルムや金属フィルムなど)を用いて発光表示装置を作製することが理想とされている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平05-203987号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は、このような技術的背景のもとでなされたものである。したがって、その目的は、複雑な技術や特殊な装置を用いることなくフォトマスクの使用枚数を従来よりも少なくすることを課題の一とする。また、薄く、軽量であり且つ破壊が生じにくい発光表示装置の作製方法を提供することを課題の一つとする。

10

【課題を解決するための手段】

【0011】

すなわち、本発明の一態様は、基板上に剥離層を形成し、剥離層上に第1の導電層を形成し、第1の導電層上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層を部分的に除去して第1のゲート電極と第2のゲート電極を形成し、第1のゲート電極及び第2のゲート電極上にゲート絶縁層となる第1の絶縁層を形成し、第1の絶縁層上に半導体層を形成し、半導体層上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2のゲート電極に重畳する半導体層の一部及び第1の絶縁層の一部を選択的に除去して第1の開口部を形成し、半導体層および第1の開口部を覆うように第2の導電層を形成し、第2の導電層上に第3のレジストマスクを形成し、第3のレジストマスクを用いて第2の導電層を部分的に除去して、第1のソース電極及び第1のドレイン電極ならびに第2のソース電極及び第2のドレイン電極を形成することで、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有する第2のトランジスタを形成し、第1のドレイン電極と第2のゲート電極は第1の開口部を介して電気的に接続されており、第1のソース電極及びドレイン電極、第2のソース電極及びドレイン電極、及び半導体層上に保護絶縁層となる第2の絶縁層を形成し、第2の絶縁層上に第4のレジストマスクを形成し、第4のレジストマスクを用いて第1のソース電極及びドレイン電極、第2のソース電極及びドレイン電極と重畳しない第2の絶縁層の一部および半導体層の一部を除去して第2の開口部を形成すると同時に、第2のドレイン電極と重畳する第2の絶縁層の一部を選択的に除去して第3の開口部を形成し、第3の開口部を覆うように第2の絶縁層上に第3の導電層を形成し、第3の導電層上に第5のレジストマスクを形成し、第5のレジストマスクを用いて第3の導電層を部分的に除去して第1の画素電極を形成し、第2の開口部、第3の開口部、第2の絶縁層及び第1の画素電極の端部を覆うように第4の絶縁層を形成することを特徴とする発光表示装置の作製方法である。

20

【0012】

上記本発明の一態様によれば、コンタクトホールとして機能する第2の開口部形成工程と半導体層をエッチングする第3の開口部形成工程を同時にを行うことによりフォトマスクの使用枚数を従来より少なくした薄膜トランジスタを作製でき、さらに薄膜トランジスタを基板から剥離することができる。

30

【0013】

また、本発明の一態様は、基板上に剥離層を形成し、剥離層上に第1の導電層を形成し、第1の導電層上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層を部分的に除去して第1のゲート電極と第2のゲート電極を形成し、第1のゲート電極及び第2のゲート電極上にゲート絶縁層となる第1の絶縁層を形成し、第1の絶縁層上に半導体層を形成し、半導体層上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2のゲート電極に重畳する半導体層の一部及び第1の絶縁層の一部を選択

40

50

的に除去して第1の開口部を形成し、半導体層及び第1の開口部を覆うように第2の導電層を形成し、第2の導電層上に第3のレジストマスクを形成し、第3のレジストマスクを用いて第2の導電層を部分的に除去して、第1のソース電極及び第1のドレイン電極ならびに第2のソース電極及び第2のドレイン電極を形成することで、第1のゲート電極、第1のソース電極および第1のドレイン電極を有する第1のトランジスタと第2のゲート電極、第2のソース電極および第2のドレイン電極を有する第2のトランジスタを形成し、第1のドレイン電極と第2のゲート電極は、第1の開口部を介して電気的に接続されており、第1のソース電極及びドレイン電極、第2のソース電極及びドレイン電極、及び半導体層上に保護絶縁層となる第2の絶縁層を形成し、第2の絶縁層上に平坦化絶縁層となる第3の絶縁層を形成し、第3の絶縁層上に第4のレジストマスクを形成し、第4のレジストマスクを用いて、第1のソース電極及びドレイン電極ならびに第2のソース電極及びドレイン電極と重畠しない第3の絶縁層の一部、第2の絶縁層の一部および半導体層の一部を除去して第2の開口部を形成すると同時に、第2のドレイン電極に重畠する第3の絶縁層の一部及び第2の絶縁層の一部を選択的に除去して第3の開口部を形成し、第3の開口部を覆うように第3の絶縁層上に第3の導電層を形成し、第3の導電層上に第5のレジストマスクを形成し、第5のレジストマスクを用いて第3の導電層を部分的にエッチングして第1の画素電極を形成し、第2の開口部、第3の開口部、及び第1の画素電極の端部を覆うように第4の絶縁層を形成することを特徴とする発光表示装置の作製方法。

10

## 【0014】

上記本発明の一態様によれば、保護絶縁層となる第2の絶縁層上に平坦化絶縁層となる第3の絶縁層を形成することにより、第1の画素電極表面に生じる凹凸を抑制することができる。これにより、第1の画素電極上に発光材料を形成した際に発光材料の膜厚を均一に保つ事ができる。このため、発光ムラの無い均一な発光面を有する発光表示装置を作製できる。

20

## 【0015】

また、本発明の一態様は、基板とゲート電極の間に下地層が形成されることを特徴とする発光表示装置の作製方法である。

## 【0016】

上記本発明の一態様によれば、基板からの不純物元素の拡散を抑制できる。これにより、半導体層に不純物元素が拡散する事に起因した薄膜トランジスタの特性変化を抑制できる。

30

## 【0017】

また、本発明の一態様は、半導体層が酸化物半導体であることを特徴とする発光表示装置の作製方法である。

## 【0018】

上記本発明の一態様によれば、半導体層に酸化物半導体を用いることで消費電力が少なく、信頼性の高い発光表示装置を実現できる。

## 【0019】

また、本発明の一態様は、酸化物半導体に加熱処理を行うことを特徴とする発光表示装置の作製方法である。

40

## 【0020】

上記発明の一態様によれば、半導体層の電子供与体（ドナー）となる水分または水素などの不純物濃度を十分に低減できる。このため、トランジスタのオフ電流を下げる事ができる。

## 【0021】

なお、電子供与体（ドナー）となる水分または水素などの不純物が低減されて高純度化された酸化物半導体（purified OS）では、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectroscopy）による水素濃度の測定値が、 $5 \times 10^{-9} / \text{cm}^3$  以下、好ましくは  $5 \times 10^{-8} / \text{cm}^3$  以下、より好ましくは  $5 \times 10^{-7} / \text{cm}^3$  以下、さらに好ましくは  $1 \times 10^{-6} / \text{cm}^3$  以下であるこ

50

とが望ましい。また、酸化物半導体のバンドギャップは、2 eV以上、好ましくは2.5 eV以上、より好ましくは3 eV以上であることが望ましい。

【0022】

ここで、酸化物半導体中の水素濃度のSIMS分析について触れておく。SIMS分析は、その原理上、試料表面近傍や、材質が異なる膜との積層界面近傍のデータを正確に得ることが困難であることが知られている。そこで、膜中における水素濃度をSIMSで分析する場合、値に極端な変動が無く、ほぼ一定の値が得られる領域における平均値を、水素濃度として採用する。また、測定の対象となる膜の厚さが小さい場合、隣接する膜内の水素の影響を受けて、ほぼ一定の値が得られる領域を見いだせない場合がある。この場合、水素濃度の最大値または最小値を、当該膜中の水素濃度として採用する。さらに、最大値を意味するピーク、最小値を意味する谷が存在しない場合、変曲点の値を水素濃度として採用する。

10

【0023】

また、本発明の一態様は、第1の導電層および第2の導電層が銅を含む材料で形成されていることを特徴とする発光表示装置の作製方法である。

【0024】

上記発明の一態様によれば、ゲート電極、ソース電極、ドレイン電極、もしくはこれらの電極に接続する配線を、銅を含む材料で形成することにより、配線抵抗を低減し、信号の遅延を防ぐことができる。

20

【0025】

また、本発明の一態様は、第1の導電層および第2の導電層形成後のプロセス温度の上限が450以下であることを特徴とする発光表示装置の作製方法である。

【0026】

上記発明の一態様によれば、ゲート電極、ソース電極、ドレイン電極、もしくはこれらの電極に接続する配線を、銅を含む材料で形成した場合において、熱的な要因によりこれらの電極や配線が変形する、含有する成分が溶出することがない。このため、信頼性の高い発光表示装置を作製できる。

【0027】

また、本発明の一態様は、第1の導電層および第2の導電層がアルミニウムを含む材料で形成されていることを特徴とする発光表示装置の作製方法である。

30

【0028】

本発明の一態様によれば、ゲート電極、ソース電極、またはドレイン電極は、もしくはこれらの電極に接続する配線を、アルミニウムを含む材料で形成することにより、配線抵抗を低減し、信号の遅延を防ぐことができる。

【0029】

また、本発明の一態様は、第1の導電層および第2の導電層形成後のプロセス温度の上限が380以下であることを特徴とする発光表示装置の作製方法である。

【0030】

上記発明の一態様によれば、ゲート電極、ソース電極、ドレイン電極、もしくはこれらの電極に接続する配線を、アルミニウムを含む材料で形成した場合において、熱的な要因によりこれらの電極や配線が変形する、含有する成分が溶出することがない。このため、信頼性の高い発光表示装置を作製できる。

40

【0031】

また、本発明の一態様は、少なくとも第1のゲート電極、第2のゲート電極、第1の絶縁層、半導体層、第1のソース電極、第1のドレイン電極、第2のソース電極、第2のドレイン電極、第2の絶縁層、第4の絶縁層および第1の画素電極を有する素子領域を基板上に剥離層を介して形成した後に、素子領域表面を覆うように剥離用接着剤を形成する工程と、第1の画素電極および素子領域を基板から剥離する工程と、素子領域の裏面に1.5 [MPa · m<sup>1/2</sup>]以上の破壊じん性値を有する第1の支持体を貼り合わせる工程と、第1の支持体から剥離用接着剤を除去する工程と、素子領域に形成された第1の画素電極

50

上に有機化合物を含む層を選択的に形成する工程と、有機化合物を含む層を覆うように第2の画素電極を形成する工程と、第2の画素電極を覆うように1.5 [ MPa · m<sup>1/2</sup> ]以上の破壊じん性値を有する第2の支持体を貼り合わせる工程を少なくとも有することを特徴とする発光表示装置の作製方法である。

## 【0032】

上記発明の一態様によれば、基板上に設けられた素子領域を1.5 [ MPa · m<sup>1/2</sup> ]以上の破壊じん性値を有する第1の支持体上に移すことができる。さらに発光材料を挟持するための第2の支持体も1.5 [ MPa · m<sup>1/2</sup> ]以上の破壊じん性値を有するため、薄く、軽量であり且つ破壊が生じにくい発光表示装置を作製できる。

## 【0033】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能し得る装置全般を指し、半導体回路、記憶装置、撮像装置、表示装置、電気光学装置及び電子機器などは全て半導体装置である。

## 【0034】

また、本明細書においてAの上にBが形成されている、あるいは、A上にBが形成されている、と明示的に記載する場合は、Aの上にBが直接接して形成されていることに限定されない。直接接してはいない場合、つまり、AとBとの間に別の対象物が介在する場合も含むものとする。ここで、A、Bは、対象物（例えば装置、素子、回路、配線、電極、端子、膜、層、または基板など）であるとする。

## 【0035】

従って、例えば層Aの上または層A上に層Bが形成されていると明示的に記載されている場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、別の層（例えば層Cや層Dなど）は、単層でもよいし、複層でもよい。

## 【0036】

また、本明細書における「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

## 【0037】

また、本明細書における「トランジスタ」は半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができ、IGFET (Insulated Gate Field Effect Transistor) や薄膜トランジスタ (TFT: Thin Film Transistor) を含む。

## 【0038】

また、本明細書におけるトランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

## 【0039】

また、本明細書において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

## 【0040】

また、本明細書において「じん性」とは物質の破壊に抵抗する性質を表す言葉であり、高いじん性を備えた材料ほど大きな負荷や衝撃を加えても破壊が進行し難く、例えば基板の一部に生じた小さな傷を起点として破壊が進行しにくい性質をいう。また、じん性の程度は、破壊じん性値  $K_c$  で表すことができる。なお、破壊じん性値  $K_c$  はJIS R 1607に定義される試験方法などで求めることができる。

## 【発明の効果】

10

20

30

40

50

## 【0041】

本発明によれば、複雑な技術や特殊な装置を用いることなくフォトマスクの使用枚数を従来よりも少なくすることができる。また、薄く、軽量であり且つ高いじん性を備えた発光表示装置の作製方法を提供できる。

## 【図面の簡単な説明】

## 【0042】

【図1】発光表示装置の一態様を説明する平面図及び断面図。

【図2】発光表示装置の一態様を説明する平面図。

【図3】本発明の一態様を説明する回路図。

【図4】本発明の一態様を説明する回路図。

10

【図5】発光表示装置の作製方法の一態様を説明する断面図。

【図6】発光表示装置の作製方法の一態様を説明する断面図。

【図7】発光表示装置の作製方法の一態様を説明する断面図。

【図8】発光表示装置の作製方法の一態様を説明する断面図。

【図9】発光表示装置の作製方法の一態様を説明する断面図。

【図10】発光表示装置の一態様を説明する平面図及び断面図。

【図11】発光表示装置の作製方法の一態様を説明する断面図。

【図12】発光表示装置の作製方法の一態様を説明する断面図。

【図13】発光表示装置の作製方法の一態様を説明する断面図。

20

【図14】電子機器の使用形態の例を説明する図。

【図15】電子機器の使用形態の例を説明する図。

## 【発明を実施するための形態】

## 【0043】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しえることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

## 【0044】

30

## (実施の形態1)

本実施の形態では、本発明の一態様における発光表示装置が有する画素部の構成の一例を、図1乃至図4を用いて説明する。なお、本実施の形態では、画素部の構造が上面射出構造（トップエミッション構造）であることを前提として説明を行うが、これに限定されるものではない。上面射出構造以外としては下面射出構造（ボトムエミッション構造）や両面射出構造（デュアルエミッション構造）などが一般的であり、当業者であれば、これらの構造については容易に想像できるため、本実施の形態では射出構造の詳細説明については省略する。

## 【0045】

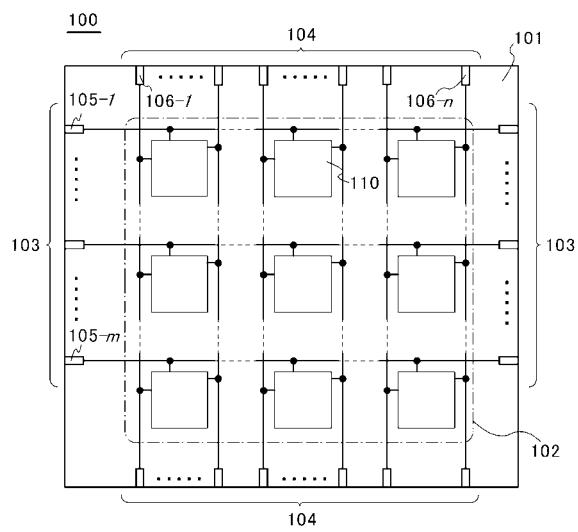

図3に、発光表示装置に用いる半導体装置100の構成の一例を示す。半導体装置100は、基板101上に複数個の画素110を備えた画素領域102と、m個（mは1以上の整数）の端子105を有する端子部103と、n個（nは1以上の整数）の端子106を有する端子部104を有している。

## 【0046】

端子部103及び端子部104は外部配線を接続する端子であり、外部配線により外部に設けられた制御回路と接続される。外部に設けられた制御回路から供給される信号は、端子部103及び端子部104を介して半導体装置100に入力される。図3では、端子部103を画素領域102の左右外側に形成し、2カ所から信号を入力する構成を示している。また、端子部104を画素領域102の上下外側に形成し、2カ所から信号を入力する構成を示している。2カ所から信号を入力することにより、信号の供給能力が高まるた

40

50

め、半導体装置 100 の高速動作が容易となる。また、半導体装置 100 の大型化や高精細化に伴う配線抵抗の増大による信号遅延の影響を軽減することができる。また、半導体装置 100 に冗長性を持たせることができるとなるため、半導体装置 100 の信頼性を向上させることができる。なお、図 3 では端子部 103 及び端子部 104 をそれぞれ 2 力所設ける構成としているが、それぞれ 1 力所設ける構成としても構わない。

【0047】

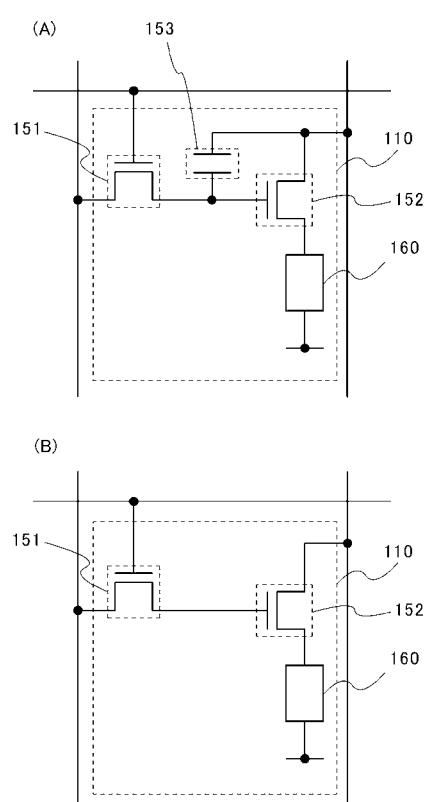

図 4 (A) は、画素 110 の回路構成を示している。画素 110 は、第 1 のトランジスタ 151 および第 2 のトランジスタ 152 と、発光素子 160 と、容量素子 153 を有している。なお、図示はしていないが、発光素子 160 は外部接続端子に接続されている。発光表示装置に設けられる容量素子 153 の保持容量の大きさは、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定される。チャネル領域が形成される半導体層に、高純度化された酸化物半導体を用いたトランジスタを用いることにより、容量素子 153 の保持容量を小さくすることができる。また、図 4 (B) は図 4 (A) の容量素子 153 が無い状態の回路構成である。

10

【0048】

第 1 のトランジスタ 151 および第 2 のトランジスタ 152 のチャネルが形成される半導体には、単結晶半導体、多結晶半導体、微結晶半導体、非晶質半導体等を用いることができる。半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を挙げることができる。

20

【0049】

また、第 1 のトランジスタ 151 および第 2 のトランジスタ 152 のチャネルが形成される半導体層に酸化物半導体を用いることもできる。酸化物半導体は、単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、微結晶（マイクロクリスタル、ナノクリスタルなど）でも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、結晶性を有する部分を含まない非アモルファスでもよい。アモルファスの酸化物半導体は、酸化物半導体のターゲットを用いてスパッタリングをすることにより得ることができる。なお、結晶性を有する酸化物半導体は、スパッタリング時に基板を室温以上の温度に加熱して成膜を行うことで得ることができる。また、酸化物半導体として、実施の形態 2 で示すように、結晶軸の配向が揃った酸化物半導体を用いることができる。本実施の形態では半導体層にキャリア濃度の極めて低減された酸化物半導体（I 型化（真性化）または実質的に I 型化された酸化物半導体ともいえる）を用いる。

30

【0050】

酸化物半導体は、エネルギーギャップが  $3.0 \sim 3.5 \text{ eV}$  以上と大きく、酸化物半導体を有するトランジスタを適切な条件下で作製した場合、オフ電流を使用時の温度条件下（例えば、 $25^\circ\text{C}$ ）において、 $100 \text{ zA}$  ( $1 \times 10^{-19} \text{ A}$ ) 以下、もしくは  $10 \text{ zA}$  ( $1 \times 10^{-20} \text{ A}$ ) 以下、さらには  $1 \text{ zA}$  ( $1 \times 10^{-21} \text{ A}$ ) 以下とすることができる。

40

【0051】

このように、第 1 のトランジスタ 151 および第 2 のトランジスタトランジスタ 152 のチャネルが形成される半導体層に酸化物半導体を用いることにより、オフ状態における電流値（オフ電流値）を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、新たな書き込みをしなくても長い時間信号を保持できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。また、第 1 のトランジスタ 151 および第 2 のトランジスタトランジスタ 152 として、半導体層に酸化物半導体を用いたトランジスタを用いることにより、保持容量を設けなくても、液晶素子に印加された電位の保持が可能となる。

【0052】

また、チャネルが形成される半導体層に酸化物半導体を用いたトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、発光表示装置の画素部に上記トランジスタを用いることで、高画質な画像を提供することができる。また、上

50

記トランジスタは、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、発光表示装置の部品点数を削減することができる。

【0053】

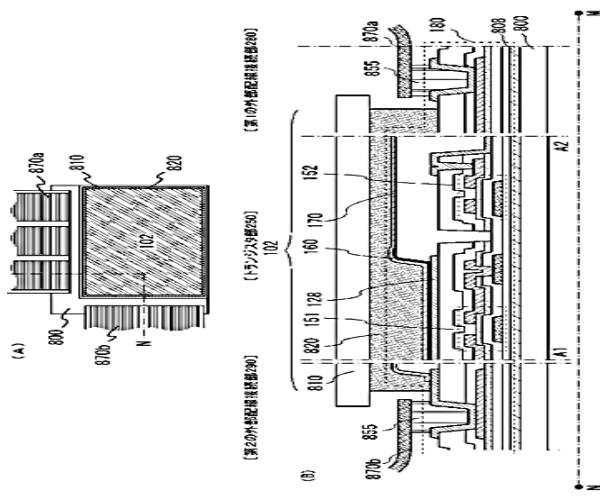

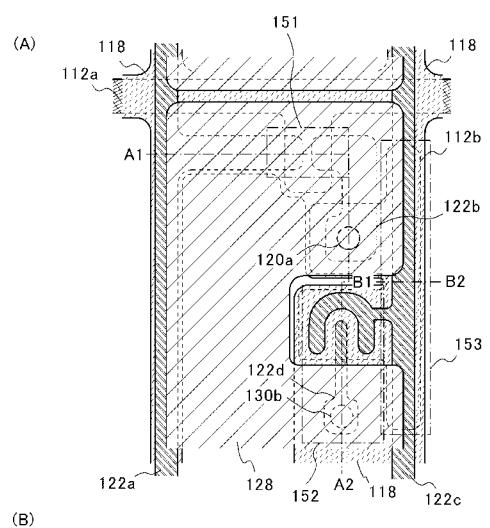

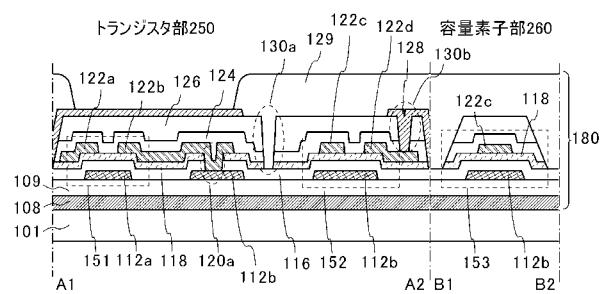

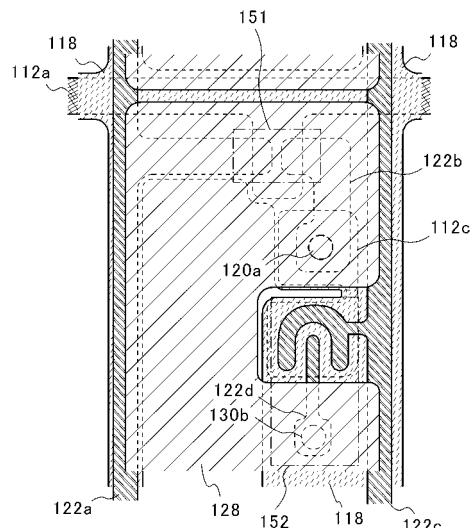

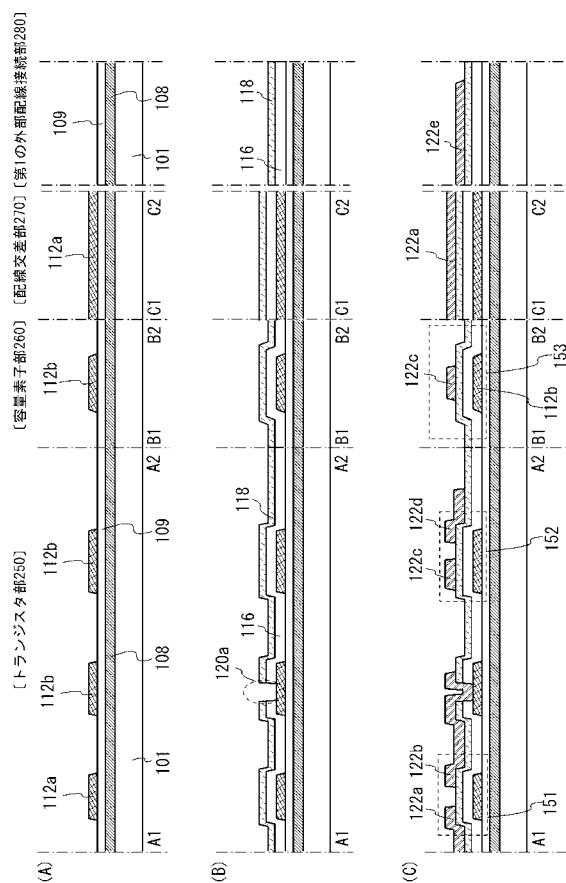

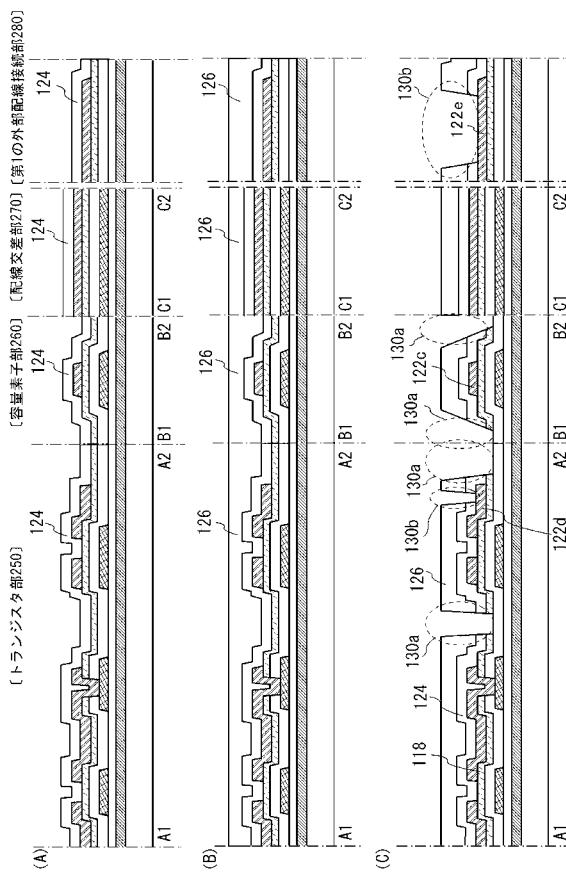

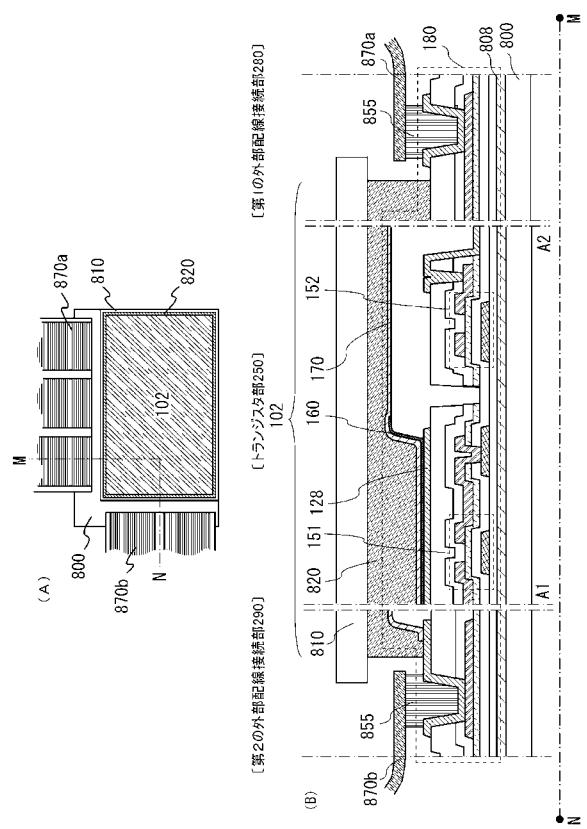

図1(A)、(B)は、本発明の一態様を適用したアクティブマトリクス型の発光表示装置の画素部の一例である。図1(A)は発光表示装置の画素部の平面図であり、図1(B)は、画素部の積層構成を示す断面図である。なお、図1(A)におけるA1-A2、B1-B2の1点鎖線は、図1(B)における断面A1-A2、断面B1-B2の1点鎖線に相当する。なお、発光層及び第2の画素電極(共通電極とも呼ばれる)は図1(A)、(B)には図示されていない。

【0054】

本実施の形態は、発光表示装置の画素部の構成及び作製方法について説明するものである。従って、本実施の形態におけるトランジスタとは、図1(A)、(B)に示す第1のトランジスタ151及び第2のトランジスタ152の両方またはいずれかのことを言う。また、該トランジスタは、後述する酸化物半導体を用いたnチャネル型である。

【0055】

本実施の形態に示すトランジスタ152は、第2のドレイン電極122dを、U字型(C字型、コの字型、または馬蹄型)の第2のソース電極122cで囲む形状としている。このような形状とすることで、トランジスタの面積が少なくとも、十分なチャネル幅を確保することが可能となり、トランジスタの導通時に流れる電流(オン電流ともいう)の量を増やすことが可能となる。

【0056】

図1(B)の断面A1-A2は、第1のトランジスタ151および第2のトランジスタ152の積層構造を示している。第1のトランジスタ151および第2のトランジスタ152は、ボトムゲート構造のトランジスタである。図1(B)の断面B1-B2は、容量素子153の積層構造を示している。

【0057】

断面A1-A2において、基板101上に剥離層108が形成され、剥離層108上に下地層109が形成され、下地層109上に第1のゲート電極112aおよび第2のゲート電極112bが形成されている。また、第1のゲート電極112aおよび第2のゲート電極112b上に、ゲート絶縁層として機能する第1の絶縁層116と半導体層118が形成されている。また、半導体層118上に第1のソース電極122a及び第1のドレイン電極122bならびに第2のソース電極122c及び第2のドレイン電極122dが形成されている。

【0058】

これにより、第1のゲート電極112a、第1のソース電極122aおよび第1のドレイン電極122bからなる第1のトランジスタ151および、第2のゲート電極112b、第2のソース電極122cおよび第2のドレイン電極122dからなる第2のトランジスタ152が形成される。なお、第1のドレイン電極122bは第1の開口部120aを介して第2のゲート電極112bと繋がっている。

【0059】

第1のトランジスタ151及び第2のトランジスタ152上には保護絶縁層として機能する第2の絶縁層124及び平坦化絶縁層として機能する第3の絶縁層126が形成されている。第2の絶縁層124の一部と第3の絶縁層126の一部が開口されて、第2の開口部130aと第3の開口部130bが形成されている。第2の開口部130aでは第1の絶縁層116が露出しており、第3の開口部130bでは第2のドレイン電極122dの一部が露出している。なお、第3の絶縁層126を省いた構成とすることもできる。

【0060】

さらに、第3の開口部130bを覆うように第1の画素電極128を形成し、第3の開口部130bを介して第2のドレイン電極122dと第1の画素電極128を電気的に接続する。その後、第3の絶縁層126上に、第1の画素電極128の端部を覆うように隔壁

10

20

30

40

50

129となる絶縁材料を形成する。ここで、隔壁129は、第1の画素電極128の端部などの凹凸のある領域などを覆うように形成する。隔壁129によって、後に第1の画素電極128上などに形成する発光層や第2の画素電極の断切れを防止することができる。

【0061】

断面B1-B2において、基板101上に剥離層108が形成され、剥離層108上に下地層109が形成され、下地層109上に容量配線として機能する第2のゲート電極112bが形成されている。また、容量配線として機能する第2のゲート電極112b上に、第1の絶縁層116と半導体層118が形成され、半導体層118上に容量配線として機能する第2のソース電極122cが形成されている。また、容量配線として機能する第2のソース電極122c上に第2の絶縁層124および第3の絶縁層126が形成されている。

10

【0062】

第2のゲート電極112bと第2のソース電極122cが、第1の絶縁層116と半導体層118を間に挟んで重なっている部分が容量素子153として機能する。第1の絶縁層116と半導体層118は誘電体層として機能する。第2のゲート電極112bと第2のソース電極122cの間に形成される誘電体層を多層構造とすることで、一つの誘電体層にピンホールが生じても、ピンホールは他の誘電体層で被覆されるため、容量素子153を正常に機能させることができる。また、酸化物半導体の比誘電率は14から16と大きいため、半導体層118に酸化物半導体を用いると、容量素子153の容量値を大きくすることができる。

20

【0063】

なお、図1では第1のトランジスタ151をシングルゲート構造で図示しているが、マルチゲート構造としても良い。マルチゲート構造のトランジスタは、オフ電流が小さく、該トランジスタを含む発光表示装置の表示特性を高めることができる。

【0064】

なお、図1(B)において、剥離層108より表面側に形成された層を以下では素子領域180と呼称する。素子領域180は少なくとも第1のゲート電極112a、第2のゲート電極112b、第1の絶縁層116、半導体層118、第1のソース電極122a、第1のドレイン電極122b、第2のソース電極122c、第2のドレイン電極122d、第2の絶縁層124、第1の画素電極128、隔壁129を有する。素子領域180はその他に、下地層109、第3の絶縁層126などを有してもよい。

30

【0065】

また、図2に示すような容量素子153を設けない構成としてもよい。図2では、図1(B)の第2のゲート電極112bに相当する第2のゲート電極112cを電源配線(図1(B)における第2のソース電極122c)と重ねない構成とし、容量素子を形成していない。この構成の回路図が図4(B)にあたる。

【0066】

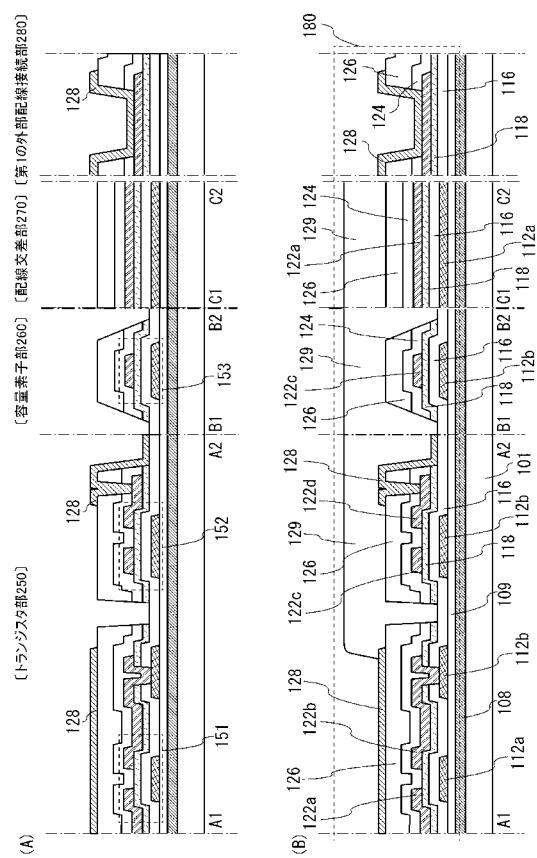

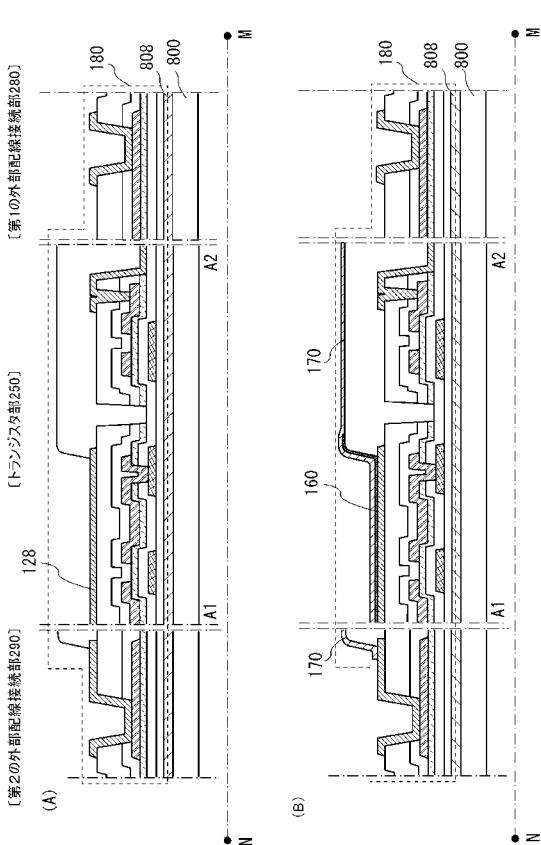

続いて、図1を用いて説明した発光表示装置の画素部の作製方法の一例について、図5乃至図8を用いて説明する。なお、ここではトランジスタ部250の作製方法を主として説明するが、図示してあるように容量素子部260、配線交差部270、及び第1の外部配線接続部280についても必要に応じて説明する。

40

【0067】

まず、基板101上に剥離層108を50nm以上1000nm以下、好ましくは100nm以上500nm以下、より好ましくは100nm以上300nm以下の厚さで形成する。

【0068】

基板101は、ガラス基板、石英基板、サファイア基板、セラミック基板や金属基板などを用いることができる。なお、これら基板は、可撓性を明確に表さない程度に厚みのあるものを使用することで、精度良くトランジスタなどの素子を形成することができる。可撓性を明確に表さない程度とは、通常発光ディスプレイを作製する際に使用されているガラ

50

ス基板の弾性率程度、もしくはより弾性率が大きいことを言う。本実施の形態では、基板 101 にアルミニノホウケイ酸ガラスを用いる。

【0069】

剥離層 108 は、スパッタリング法やプラズマ CVD 法、塗布法、印刷法等により、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、ニオブ (Nb)、ニッケル (Ni)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、珪素 (Si) から選択された元素、又は元素を主成分とする合金材料、又は元素を主成分とする化合物材料からなる層を、単層又は積層して形成する。

【0070】

剥離層 108 が単層構造の場合、好ましくは、タンゲステン、モリブデン、又はタンゲステンとモリブデンの混合物を含む層を形成する。又は、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層、又はタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合金に相当する。

【0071】

剥離層 108 が積層構造の場合、好ましくは、1 層目として金属層を形成し、2 層目として金属酸化物層を形成する。代表的には 1 層目としてタンゲステン層、モリブデン層、又はタンゲステンとモリブデンの混合物を含む層を形成し、2 層目として、タンゲステン、モリブデン又はタンゲステンとモリブデンの混合物の酸化物、窒化物、酸化窒化物又は窒化酸化物を形成すると良い。2 層目の金属酸化物層の形成は、1 層目の金属層上に、酸化物層（例えば酸化シリコンなどの絶縁層として利用できるもの）を形成することで金属層表面に当該金属の酸化物が形成されることを応用しても良い。

【0072】

また、剥離層 108 として、水素を含む非晶質珪素層や、窒素、酸素や水素等を含む層（例えば、水素を含む非晶質珪素膜、水素含有合金膜、酸素含有合金膜など）や、有機樹脂を用いてもよい。

【0073】

本実施の形態では、剥離層 108 として膜厚 150 nm のタンゲステン膜を用いる。なお、このタンゲステン膜は、表面が酸化された状態（つまり、タンゲステン膜の表面にタンゲステン酸化膜が形成された状態）である場合も含むものとする。

【0074】

なお、剥離層 108 は剥離層 108 より上の層に形成された素子領域 180 を基板 101 から剥離することを主目的とした層であるが、それ以外に、基板 101 からの不純物元素の拡散を防止する機能も併せ持つ。

【0075】

次に、剥離層 108 上に下地層 109 となる絶縁層を 50 nm 以上 300 nm 以下、好ましくは 100 nm 以上 200 nm 以下の厚さで形成する。

【0076】

下地層 109 は、窒化アルミニウム、酸化窒化アルミニウム、窒化シリコン、酸化シリコン、窒化酸化シリコンまたは酸化窒化シリコンから選ばれた一又は複数の絶縁層による積層構造により形成することができ、基板 101 や剥離層 108 からの不純物元素の拡散を防止する機能がある。なお、本明細書中において、窒化酸化珪素とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、組成範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、珪素が 25 ~ 35 原子%、水素が 10 ~ 30 原子% の範囲で見積もられることが好ましい。下地層 109 は、スパッタリング法、CVD 法、塗布法、印刷法等を適宜用いることができる。

【0077】

本実施の形態では、下地層 109 として、窒化シリコンと酸化シリコンの積層を用いる。具体的には、基板 101 上に窒化シリコンを 50 nm の厚さで形成し、該窒化シリコン上

10

20

30

40

50

に酸化シリコンを 150 nm の厚さで形成する。なお、下地層 109 中にリン (P) や硼素 (B) がドープされていても良い。

【0078】

また、下地層 109 に、塩素、フッ素などのハロゲン元素を含ませることで、基板 101 からの不純物元素の拡散を防止する機能をさらに高めることができる。下地層 109 に含ませるハロゲン元素の濃度は、SIMS (二次イオン質量分析計) を用いた分析により得られる濃度ピークにおいて、 $1 \times 10^{15} / \text{cm}^3$  以上  $1 \times 10^{20} / \text{cm}^3$  以下とすればよい。

【0079】

また、下地層 109 として酸化ガリウムを用いてもよい。また、下地層 109 を酸化ガリウムと上記絶縁層の積層構造としてもよい。酸化ガリウムは帯電しにくい材料であるため、絶縁層のチャージアップによるしきい値電圧の変動を抑えることができる。

10

【0080】

次に、下地層 109 上にスパッタリング法、真空蒸着法、またはメッキ法を用いて 100 nm 以上 500 nm 以下、好ましくは 200 nm 以上 300 nm 以下の厚さで第 1 の導電層を形成し、第 1 の導電層上に第 1 のレジストマスクを形成し、第 1 のレジストマスクを用いて第 1 の導電層を部分的にエッチングして、第 1 のゲート電極 112a および第 2 のゲート電極 112b を形成する (図 5 (A) 参照)。

【0081】

第 1 のゲート電極 112a および第 2 のゲート電極 112b を形成するための第 1 の導電層は、モリブデン (Mo)、チタン (Ti)、タンゲステン (W)、タンタル (Ta)、アルミニウム (Al)、銅 (Cu)、クロム (Cr)、ネオジム (Nd)、スカンジウム (Sc) 等の金属材料又はこれらを主成分とする合金材料を用いて、単層又は積層して形成することができる。また、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム ( $\text{In}_2\text{O}_3$ )、酸化スズ ( $\text{SnO}_2$ )、酸化亜鉛 ( $\text{ZnO}$ )、酸化インジウム酸化スズ ( $\text{In}_2\text{O}_3 - \text{SnO}_2$ 、ITO と略記する)、酸化インジウム酸化亜鉛 ( $\text{In}_2\text{O}_3 - \text{ZnO}$ ) またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。さらに、導電性高分子 (導電性ポリマーともいう) を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆる 電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはアニリン、ピロールおよびチオフェンの 2 種以上からなる共重合体若しくはその誘導体などがあげられる。また、1 枚乃至 10 枚のグラフェンシート (グラファイトの 1 層分) よりなる材料を用いてもよい。

20

【0082】

本実子の形態では発光素子からの光が基板 101 とは逆方向 (図 5 での上方向) に射出する上方射出構造 (トップエミッション構造) のため、第 1 の導電層に特段の限定はないが、ボトムエミッション構造やデュアルエミッション構造において、第 1 のゲート電極 112a および第 2 のゲート電極 112b が射出光の通過部分に存在する (つまり、射出光が第 1 のゲート電極 112a および第 2 のゲート電極 112b により遮られる) 場合は、第 1 の導電層としては透光性を有する層を形成することが望ましい。

30

【0083】

第 1 の導電層は配線となるため、低抵抗材料である Al や Cu を用いることが好ましい。Al や Cu を用いることで、信号遅延を低減し、高画質化することができる。なお、Al は耐熱性が低く、ヒロック、ウィスカー、あるいはマイグレーションによる不良が発生しやすい。Al のマイグレーションを防ぐため、Al に、Mo、Ti、W などの、Al よりも融点の高い金属材料を積層する、Nd、Ti、Si、Cu などのヒロック防止元素との合金を用いることが好ましい。また、第 1 の導電層に Al を含む材料を用いる場合には、以後の工程におけるプロセス最高温度を 380 以下とすることが好ましく、350 以下とするとよい。

40

50

## 【0084】

また、第1の導電層にCuを用いる場合も、マイグレーションによる不良やCu元素の拡散を防ぐため、Mo、Ti、Wなどの、Cuよりも融点の高い金属材料を積層することが好ましい。また、第1の導電層にCuを含む材料を用いる場合には、以後の工程におけるプロセス最高温度を450℃以下とすることが好ましい。

## 【0085】

本実施の形態では、第1の導電層として下地層109上に厚さ5nmのTi層を形成し、Ti層上に厚さ250nmのCu層を形成する。その後、第1の導電層上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層を部分的にエッチングして除去し、第1のゲート電極112aおよび第2のゲート電極112bを形成する。

10

## 【0086】

なお、第1の導電層上に形成する第1のレジストマスクはインクジェット法で形成してもよい。インクジェット法では、フォトマスクを使用しないため、更に製造コストを低減することができる。また、第1のレジストマスクはエッチング工程の後に剥離するものとし、剥離に関する工程の説明は省略する。

## 【0087】

なお、第1の導電層に対してのエッチング処理は、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素（Cl<sub>2</sub>）、三塩化硼素（BCl<sub>3</sub>）、四塩化珪素（SiCl<sub>4</sub>）、四塩化炭素（CCl<sub>4</sub>）など）を用いることができる。

20

## 【0088】

ドライエッチングとしては、平行平板型RIE（Reactive Ion Etching）法や、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッチング法を用いることができる。また、下地層109は基板101からの不純物元素の拡散を防止する機能を有するため、上記エッチングに際して、下地層109が極力エッチングされることのないように、エッチング条件を調整することが好ましい。

## 【0089】

次に、第1のゲート電極112a、第2のゲート電極112bおよび下地層109上に、ゲート絶縁層として機能する第1の絶縁層116を50nm以上800nm以下、好ましくは100nm以上600nm以下の厚さで形成する。第1の絶縁層116には、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化タンタル、酸化ガリウム、酸化イットリウム、酸化ハフニウム、ハフニウムシリケート（HfSi<sub>x</sub>O<sub>y</sub>（x>0, y>0））、窒素が導入されたハフニウムシリケート、窒素が導入されたハフニウムアルミネート等を用いることができ、プラズマCVD法やスパッタリング法等で形成することができる。また、第1の絶縁層116は単層に限らず異なる層の積層でも良い。例えば、ゲート絶縁層AとしてプラズマCVD法により窒化シリコン層（SiN<sub>y</sub>（y>0））を形成し、ゲート絶縁層Aの上にゲート絶縁層Bとして酸化シリコン層（SiO<sub>x</sub>（x>0））を積層して、第1の絶縁層116としても良い。

30

## 【0090】

第1の絶縁層116の形成は、スパッタリング法やプラズマCVD法などのほか、μ波（例えば周波数2.45GHz）を用いた高密度プラズマCVD法などの成膜方法を適用することができる。

40

## 【0091】

本実施の形態では、第1の絶縁層116として、窒化シリコンと酸化シリコンの積層を用いる。具体的には、第1のゲート電極112a、第2のゲート電極112b上に窒化シリコンを50nmの厚さで形成し、該窒化シリコン上に酸化シリコンを100nmの厚さで形成する。

## 【0092】

50

また、第1の絶縁層116は保護層としても機能する。Cuを含む第1のゲート電極112aおよび第2のゲート電極112bを、窒化シリコンを含む第1の絶縁層116で覆う構成とすることで、第1のゲート電極112aおよび第2のゲート電極112bからのCu拡散を防ぐことができる。

【0093】

また、第1の絶縁層116には、後の工程で形成する半導体層に酸化物半導体を用いる場合には、酸化物半導体と同種の成分を含む絶縁材料を用いてもよい。第1の絶縁層116を異なる層の積層とする場合には、酸化物半導体に接する層を酸化物半導体と同種の成分を含む絶縁材料とすればよい。このような材料は酸化物半導体との相性が良く、これを第1の絶縁層116に用いることで、酸化物半導体との界面の状態を良好に保つことができるからである。ここで、「酸化物半導体と同種の成分」とは、酸化物半導体の構成元素から選択される一または複数の元素を意味する。例えば、酸化物半導体がIn-Ga-Zn系の酸化物半導体材料によって構成される場合、同種の成分を含む絶縁材料としては酸化ガリウムなどがある。

10

【0094】

また、第1の絶縁層116を積層構造とする場合には、酸化物半導体と同種の成分を含む絶縁材料でなる膜と、該膜の成分材料とは異なる材料を含む膜との積層構造としても良い。

【0095】

なお、第1の絶縁層116を成膜する際に用いるスパッタガスは水素、水、水酸基を有する化合物又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。不純物が除去された高純度ガスとしては、例えば、スパッタ装置に導入するガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とすることが望ましい。

20

【0096】

次に、第1の絶縁層116上に、半導体層118を形成する。

【0097】

半導体層118には、単結晶半導体、多結晶半導体、微結晶半導体、非晶質半導体等を用いることができる。半導体材料としては、例えば、シリコン、ゲルマニウム、シリコングルマニウム、炭化シリコン、ガリウムヒ素、あるいは酸化物半導体等を挙げができる。例えば、半導体層118として、In-Ga-Zn-O系酸化物ターゲットを用いて、スパッタリング法により30nmのIn-Ga-Zn-O系酸化物半導体を形成する。なお、半導体層118は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下においてスパッタリング法により形成することができる。

30

【0098】

上記半導体層118には酸化物半導体を用いることが好ましい。i型化または実質的にi型化された酸化物半導体は、極めて抵抗が高く、オフ状態のトランジスタ内では絶縁体とみなすことができる。従って、单一の、連続した半導体層に複数のトランジスタが構成されても互いに干渉することなく、各トランジスタを個別に動作させることができる。

40

【0099】

半導体層118に用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0100】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(

50

Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

## 【0101】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

## 【0102】

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

## 【0103】

例えば、 $In : Ga : Zn = 1 : 1 : 1$  (= 1/3 : 1/3 : 1/3)あるいは $In : Ga : Zn = 2 : 2 : 1$  (= 2/5 : 2/5 : 1/5)の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1$  (= 1/3 : 1/3 : 1/3)、 $In : Sn : Zn = 2 : 1 : 3$  (= 1/3 : 1/6 : 1/2)あるいは $In : Sn : Zn = 2 : 1 : 5$  (= 1/4 : 1/8 : 5/8)の原子数比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

## 【0104】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

## 【0105】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

## 【0106】

なお、例えば、In、Ga、Znの原子数比が $In : Ga : Zn = a : b : c$  ( $a + b + c = 1$ )である酸化物の組成が、原子数比が $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$ )の酸化物の組成の近傍であるとは、a、b、cが、

$$(a/A)^2 + (b/B)^2 + (c/C)^2 = r^2$$

を満たすことを言う。rは、例えば、0.05とすればよい。他の酸化物でも同様である。

## 【0107】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、結晶性領域を持たない非アモルファスでもよい。

10

20

30

40

50

## 【0108】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、トランジスタの界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

## 【0109】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ( $R_a$ )が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

10

## 【0110】

なお、 $R_a$ は、JIS B 0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

## 【0111】

## 【数1】

$$R_a = \frac{1}{S_0} \int_{x2}^{x1} \int_{y2}^{y1} |f(x, y) - Z_0| dx dy$$

20

## 【0112】

なお、上記において、 $S_0$ は、測定面(座標( $x_1, y_1$ ) ( $x_1, y_2$ ) ( $x_2, y_1$ ) ( $x_2, y_2$ )で表される4点によって囲まれる長方形の領域)の面積を指し、 $Z_0$ は測定面の平均高さを指す。 $R_a$ は原子間力顕微鏡(AFM: Atomic Force Microscope)にて評価可能である。

## 【0113】

結晶性を有する酸化物半導体の一例としては、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶(CAAC: C Axis Aligned Crystal)ともいう。)を含む酸化物がある。

30

## 【0114】

CAACを含む酸化物とは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

## 【0115】

CAACは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAACは結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できることもある。

40

## 【0116】

CAACに酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、CAACを構成する個々の結晶部分のc軸は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)に揃っていてもよい。または、CAACを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)を向いていてもよい。

## 【0117】

CAACは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

50

## 【0118】

このようなC A A Cの例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子（または窒素原子）の層状配列が認められる結晶を挙げることもできる。

## 【0119】

半導体層118は、水素、水、水酸基又は水素化物などの不純物が混入しにくいスパッタリング法により成膜することが好ましい。基板加熱温度は100以上600以下、好ましくは150以上550以下、さらに好ましくは200以上500以下とし、酸素ガス雰囲気で成膜する。なお、第1導電層をエッティングして形成された配線層（例えば、ゲート電極202）にA1が用いられている場合は、基板温度を380以下、好ましくは350以下とする。また、第1の導電層をエッティングして形成された配線層にCuが用いられている場合は、基板温度を450以下とする。半導体層118の厚さは、1nm以上40nm以下、好ましくは3nm以上20nm以下とする。成膜時の基板加熱温度が高いほど、得られる半導体層118の不純物濃度は低くなる。また、半導体層118中の原子配列が整い、高密度化され、多結晶またはC A A Cが形成されやすくなる。さらに、酸素ガス雰囲気で成膜することでも、希ガスなどの余分な原子が含まれないため、多結晶またはC A A Cが形成されやすくなる。ただし、酸素ガスと希ガスの混合雰囲気としてもよく、その場合は酸素ガスの割合は30体積%以上、好ましくは50体積%以上、さらに好ましくは80体積%以上とする。なお、半導体層118は薄いほど、トランジスタの短チャネル効果が低減される。ただし、薄くしすぎると界面散乱の影響が強くなり、電界効果移動度の低下が起こることがある。

10

20

30

## 【0120】

半導体層118に水素、水酸基及び水分がなるべく含まれないようにするために、半導体層118の成膜の前処理として、スパッタリング装置の予備加熱室で基板101を予備加熱し、基板101や第1の絶縁層116に吸着した水素、水分などの不純物を脱離させて排気することが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、第1の絶縁層116の成膜前に、第1のゲート電極112aおよび第2のゲート電極112bまで形成した状態でも同様に行ってもよい。

## 【0121】

なお、半導体層118をスパッタリング法で作製するためのターゲットとしては、例えば、組成比として、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  [mol数比] の金属酸化物ターゲットを用い、In-Ga-Zn-O層を成膜する。また、このターゲットの材料及び組成に限定されず、例えば、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol数比] の金属酸化物ターゲットを用いてもよい。

## 【0122】

また、金属酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した半導体層を緻密な膜とすることができる。

## 【0123】

半導体層118を成膜する際に用いるスパッタガスは水素、水、水酸基を有する化合物又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。不純物が除去された高純度ガスとしては、例えば、スパッタ装置に導入するガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上（すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下）とすることが望ましい。

40

## 【0124】

成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水( $H_2O$ )など水素原子を含

50

む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した半導体層118に含まれる不純物の濃度を低減できる。

【0125】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も均一となるために好ましい。

【0126】

酸化物半導体は不純物に対して鈍感であり、膜中にはかなりの金属不純物が含まれていても問題がなく、ナトリウムのようなアルカリ金属が多量に含まれる廉価なソーダ石灰ガラスも使えると指摘されている（神谷、野村、細野、「アモルファス酸化物半導体の物性とデバイス開発の現状」、固体物理、2009年9月号、Vol.44、pp.621-633.）しかし、このような指摘は適切でない。酸化物半導体中のアルカリ金属の濃度を二次イオン質量分析法にて測定した場合、ナトリウム(Na)が $5 \times 10^{16} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{16} \text{ cm}^{-3}$ 以下、さらに好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下、リチウム(Li)が $5 \times 10^{15} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下、カリウム(K)が $5 \times 10^{15} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下であることが望ましい。

10

【0127】

アルカリ金属、及びアルカリ土類金属は酸化物半導体にとっては悪性の不純物であり、少ないほうがよい。特にアルカリ金属のうち、Naイオンは酸化物半導体に接する絶縁膜が酸化物であった場合、絶縁膜から酸化物半導体へ拡散する。また、酸化物半導体内において、金属と酸素の結合を分断し、あるいは結合中に割り込む。その結果、トランジスタ特性の劣化（例えば、ノーマリオン化（しきい値の負へのシフト）、移動度の低下等）をもたらす。加えて、特性のばらつきの原因ともなる。このような問題は、特に酸化物半導体中の水素の濃度が十分に低い場合において顕著となる。したがって、酸化物半導体中の水素の濃度が $5 \times 10^{19} \text{ cm}^{-3}$ 以下、特に $5 \times 10^{18} \text{ cm}^{-3}$ 以下である場合には、アルカリ金属の濃度を上記の値にすることが強く求められる。

20

【0128】

上述のような方法で半導体層118を成膜しても、半導体層118には不純物としての水分又は水素（水酸基を含む）が含まれていることがある。水分又は水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、半導体層118中の水分又は水素などの不純物を低減（脱水化または脱水素化）するために、半導体層118に對して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下などにおいて、脱水化または脱水素化の加熱処理（以下、第1の加熱処理と略記する）を行ってもよい。

30

【0129】

半導体層118に第1の加熱処理を行うことで、表面および内部に存在する水分又は水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。ただし、第1の導電層をエッティングして形成された配線層（ゲート電極202など）にAlが用いられている場合は、加熱処理の温度を380以下、好ましくは350以下とする。また、第1の導電層をエッティングして形成された配線層（ゲート電極202など）にCuが用いられている場合は、加熱処理の温度を450以下とする。

40

【0130】

加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid The

50

rmal Anneal) 装置等の RTA (Rapid Thermal Anneal) 装置を用いることができる。LRTA 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA 装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

## 【0131】

第1の加熱処理においては、減圧雰囲気や、窒素、ヘリウム、ネオンまたはアルゴン等の不活性雰囲気で行う。なお、水分又は水素などが含まれないことが望ましい。また、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが望ましい。

10

## 【0132】

また、第1の加熱処理を行った半導体層118に、更に第2の加熱処理を行ってもよい。第2の加熱処理は酸化性雰囲気にて行い、これにより半導体層118中に酸素を供給して、第1の加熱処理の際に半導体層118中に生じた酸素欠損を補填する。このため、第2の加熱処理は加酸素化処理ということができる。第2の加熱処理は、例えば200以上基板の歪み点未満で行えばよい。好ましくは、250以上450以下とする。処理時間は3分~24時間とする。処理時間を長くするほど非晶質領域に対して結晶領域の割合の多い半導体層を形成することができるが、24時間を超える熱処理は生産性の低下を招くため好ましくない。

20

## 【0133】

酸化性雰囲気とは酸化性ガスを含む雰囲気である。酸化性ガスとは、酸素、オゾンまたは亜酸化窒素などであって、水、水素などが含まれないことが好ましい。例えば、熱処理装置に導入する酸素、オゾン、亜酸化窒素の純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm未満、好ましくは0.1ppm未満)とすることが望ましい。酸化性雰囲気は、酸化性ガスを不活性ガスと混合して用いてもよい。その場合、酸化性ガスが少なくとも10ppm以上含まれるものとする。また、不活性雰囲気とは、窒素、希ガス(ヘリウム、ネオン、アルゴン、クリプトン、キセノン)などの不活性ガスを主成分とする雰囲気である。具体的には、酸化性ガスなどの反応性ガスが10ppm未満とする。

30

## 【0134】

なお、第2の加熱処理に用いる熱処理装置およびガス種は、第1の加熱処理と同じ物を用いることができる。また、脱水化または脱水素化の加熱処理である第1の加熱処理と、加酸素化の加熱処理である第2の加熱処理は連続して行うことが好ましい。連続して行うことで、半導体装置の生産性を向上させることができる。

## 【0135】

このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減された半導体層118では、キャリア濃度が $1 \times 10^{12} / \text{cm}^3$ 未満、 $1 \times 10^{11} / \text{cm}^3$ 未満、あるいは $1.45 \times 10^{10} / \text{cm}^3$ 未満となる。その結果、室温(25)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は、 $100 \text{ zA} / \mu\text{m}$ (1zA(ゼプトアンペア)は $1 \times 10^{-21} \text{ A}$ )以下、あるいは $10 \text{ zA} / \mu\text{m}$ 以下となる。また、85では、 $100 \text{ zA} / \mu\text{m}$ ( $1 \times 10^{-19} \text{ A} / \mu\text{m}$ )以下、あるいは $10 \text{ zA} / \mu\text{m}$ ( $1 \times 10^{-20} \text{ A} / \mu\text{m}$ )以下となる。このようにキャリア濃度の極めて低減された酸化物半導体(I型化(真性化)または実質的にI型化された酸化物半導体ともいえる)を用いることで、極めて優れたオフ電流特性のトランジスタを得ることができる。

40

## 【0136】

また、当該トランジスタは、しきい値電圧やオン電流などの電気的特性に温度依存性がほ

50

とんど見られない。また、光劣化によるトランジスタ特性の変動も少ない。

【0137】

したがって、高純度化し、キャリア濃度の極めて低減された酸化物半導体を有するトランジスタは、電気的特性変動が抑制されており、電気的に安定である。よって安定した電気的特性を有する酸化物半導体を用いることにより、信頼性の高い液晶表示装置を提供することができる。

【0138】

なお、上述では半導体層118を成膜した直後に、半導体層118に対して第1の加熱処理や第2の加熱処理を行う説明を記載したが、当該加熱処理は、半導体層118を成膜した後であれば、どのタイミングで行ってもよい。

10

【0139】

また、半導体層118の成膜後において、半導体層118に以下に述べるような酸素添加処理を行い、第1の熱処理により該酸化物半導体に含まれる水素や水酸基若しくは水分を放出させ、第1の熱処理と同時に又はその後のさらなる熱処理により酸化物半導体を結晶化させてもよい。このような結晶化若しくは再結晶化の処理により、半導体層118の結晶性をより高めることができる。

【0140】

ここで、酸素添加処理とは、酸素（少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む）を半導体層118のバルクに添加することをいう。なお、当該「バルク」の用語は、酸素を、薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、「酸素ドープ」には、プラズマ化した酸素をバルクに添加する「酸素プラズマドープ」が含まれる。酸素添加処理を行うことにより、半導体層118に含まれる酸素を、化学量論的組成比より多くすることができる。また、後の工程にて第2の絶縁層124を成膜した後、第2の絶縁層124に対して酸素添加処理を行い、第2の絶縁層124に含まれる酸素を、化学量論的組成比より多くすることができる。第2の絶縁層124に対して酸素添加処理を行うことにより、当該処理後に加熱処理を行うことで、第2の絶縁層124中の酸素を半導体層118に添加し、半導体層118中の酸素欠損を効率良く補填することができる。

20

【0141】

酸素ドープ処理は、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）方式を用いて、マイクロ波（例えば、周波数2.45GHz）により励起された酸素プラズマを用いて行なうことが望ましい。

30

【0142】

なお、上述酸素添加処理は、半導体層118や第2の絶縁層124等に含まれる酸素を、化学量論比的組成比よりも多くする処理であるため、過酸素化処理とも言える。過剰酸素は主に格子間に存在する酸素であり、その酸素濃度は $1 \times 10^{16} / \text{cm}^3$ 以上 $2 \times 10^{20} / \text{cm}^3$ 以下とすれば、結晶に歪み等を与えることなく酸化物半導体中に含ませることができる。

【0143】

次に、半導体層118上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2のゲート電極112b上の第1の絶縁層116および半導体層118の一部を選択的にエッティングして開口し、第1の開口部120aを形成する（図5（B）参照）。

40

【0144】

なお、第1の絶縁層116および半導体層118に対してのエッティング処理は、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。例えば、半導体層118が酸化物半導体である場合は、エッティング液としては、磷酸、酢酸、及び硝酸を混ぜた溶液などを用いることができる。また、ITO-07N（関東化学社製）を用いてもよい。また、第1の絶縁層116は、フッ酸系のエッティング液を用いれば良い。

【0145】

次に、第1の開口部120aおよび半導体層118上に第2の導電層を形成し、第2の導

50

電層上に第3のレジストマスクを形成し、第3のレジストマスクを用いて第2の導電層に對して部分的にエッチングを行い、第1のソース電極122a、第1のドレイン電極122b、第2のソース電極122c、第2のドレイン電極122dを形成する。また、容量素子153においては、第1の絶縁層116及び半導体層118を介して第2のゲート電極112bと重なるように配線(第2のソース電極122c)を形成する(図5(C)参照)。

#### 【0146】

第2の導電層としては、例えば、モリブデン(Mo)、チタン(Ti)、タングステン(W)タンタル(Ta)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)等の金属材料又はこれらを主成分とする合金材料を用いて、単層又は積層して形成することができる。また、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム(IndO<sub>3</sub>)、酸化スズ(SnO<sub>2</sub>)、酸化亜鉛(ZnO)、酸化インジウム酸化スズIndO<sub>3</sub>SnO<sub>2</sub>、ITOと略記する)、酸化インジウム酸化亜鉛(IndO<sub>3</sub>ZnO)またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。さらに、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することもできる。導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはアニリン、ピロールおよびチオフェンの2種以上からなる共重合体若しくはその誘導体などがあげられる。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。

10

20

30

#### 【0147】

本実施の形態では発光素子からの光が基板101とは逆方向(図5での上方向)に射出する上方射出構造(トップエミッション構造)のため、第2の導電層に特段の限定はないが、ボトムエミッション構造やデュアルエミッション構造において、第1のソース電極122a、第1のドレイン電極122b、第2のソース電極122cおよび第2のドレイン電極122dが射出光の通過部分に存在する(つまり、射出光が第1のソース電極122a、第1のドレイン電極122b、第2のソース電極122cおよび第2のドレイン電極122dにより遮られる)場合は、第2の導電層としては透光性を有する層を形成することが望ましい。

30

#### 【0148】

第2の導電層は配線となるため、低抵抗材料であるAlやCuを用いることが好ましい。AlやCuを用いることで、信号遅延を低減し、高画質化を望むことができる。なお、Alは耐熱性が低く、ヒロック、ウィスカー、あるいはマイグレーションによる不良が発生しやすい。Alのマイグレーションを防ぐため、Alに、Mo、Ti、Wなどの、Alよりも融点の高い金属材料を積層する、Nd、Ti、Si、Cuなどのヒロック防止元素との合金を用いることが好ましい。また、第2の導電層にAlを含む材料を用いる場合には、以後の工程におけるプロセス最高温度を380以下とすることが好ましく、350以下とするとよい。

40

#### 【0149】

また、第2の導電層にCuを用いる場合も、マイグレーションによる不良やCu元素の拡散を防ぐため、Mo、Ti、Wなどの、Cuよりも融点の高い金属材料を積層することが好ましい。また、第2の導電層にCuを含む材料を用いる場合には、以後の工程におけるプロセス最高温度を450以下とすることが好ましい。

50

#### 【0150】

本実施の形態では、第2の導電層として半導体層118上に厚さ5nmのTi層を形成し、Ti層上に厚さ250nmのCu層を形成する。その後、第2の導電層上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層に對してエッチング処理を行い、第1のソース電極122a、第1のドレイン電極122b、第2のソース電極122c、第2のドレイン電極122d及び配線122eを形成する。

## 【0151】

なお、第2の導電層上に形成する第2のレジストマスクはインクジェット法で形成してもよい。インクジェット法では、フォトマスクを使用しないため、更に製造コストを低減することができる。また、第2のレジストマスクはエッティング工程の後に剥離するものとし、説明は省くこととする。

## 【0152】

また、第2の導電層のエッティングに際して、半導体層118が極力エッティングされない様にすることが好ましい。しかしながら、第2の導電層のみをエッティングする条件を得ることは難しく、第2の導電層のエッティングの際に半導体層118の一部がエッティングされ、溝部(凹部)を有する形状となることもある。

10

## 【0153】

以上の工程で第1のトランジスタ151、第2のトランジスタ152、及び容量素子153が形成される(図5(C)参照)。該トランジスタは、水素、水分、水酸基または水素化物(水素化合物ともいう)などの不純物を半導体層118より意図的に排除し、高純度化された酸化物半導体を含むトランジスタである。よって、該トランジスタは、電気的特性変動が抑制されており、電気的に安定である。

## 【0154】

次に、基板101上に形成した上記構成を覆うように第2の絶縁層124を形成する(図6(A)参照。)。第2の絶縁層124は、第1の絶縁層116または下地層109と同様の材料及び方法で形成することができる。なお、水素や水素を含む不純物などが混入しにくいという点では、スパッタリング法による形成が好ましい。第2の絶縁層124に水素が含まれると、その水素の半導体層118への侵入、又は水素による半導体層118中の酸素の引き抜きが生じ、半導体層118が低抵抗化(N型化)して寄生チャネルが形成されてしまう恐れがある。従って、第2の絶縁層124は、水素及び水素を含む不純物が極力含まれない手段を用いて成膜することが重要である。

20

## 【0155】

第2の絶縁層124としては、代表的には酸化シリコン、酸化窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウムなどの無機絶縁材料を用いることができる。酸化ガリウムは帯電しにくい材料であるため、絶縁層のチャージアップによるしきい値電圧の変動を抑えることができる。なお、半導体層118に酸化物半導体を用いる場合、第2の絶縁層124として、または、第2の絶縁層124と積層して、酸化物半導体と同種の成分を含む金属酸化物層を形成してもよい。

30

## 【0156】

本実施の形態では、第2の絶縁層124として膜厚200nmの酸化シリコンをスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化シリコン層のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下において行うことができる。また、ターゲットには、酸化シリコンまたはシリコンを用いることができる。例えば、シリコンをターゲットに用いて、酸素を含む雰囲気下でスパッタを行うと酸化シリコンを形成することができる。

40

## 【0157】

第2の絶縁層124の成膜時における成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。例えば、クライオポンプを用いて排気した成膜室で成膜した第2の絶縁層124は、第2の絶縁層124中に含まれる不純物の濃度を低減することができる。また、成膜室内の残留水分を除去するための他の排気手段としては、ターボ分子ポンプにコールドトラップ機構を加えたものであってもよい。

## 【0158】

なお、第2の絶縁層124を成膜する際に用いるスパッタガスは水素、水、水酸基を有する化合物又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。水

50

素、水、水酸基を有する化合物又は水素化物などの不純物が除去された高純度ガスとしては、例えば、6N(99.9999%)以上、好ましくは7N(99.9999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)の純度を有するガスを用いることが望ましい。

【0159】

また、第2の絶縁層124を成膜した後に、減圧雰囲気下、不活性ガス雰囲気下、酸素ガス雰囲気下、または超乾燥エア雰囲気下で第3の加熱処理(好ましくは200以上600以下、より好ましくは250以上550以下)を行ってもよい。ただし、第1の導電層をエッチングして形成されたゲート電極や、第2の導電層をエッチングして形成されたソース電極およびドレイン電極のいずれか一以上にA1が用いられている場合は、加熱処理の温度を380以下、好ましくは350以下とし、また、上記配線層にCuが用いられている場合は、加熱処理の温度を450以下とする。例えば、窒素雰囲気下で450、1時間の第3の加熱処理を行ってもよい。第3の加熱処理を行うと、半導体層118の一部(チャネル形成領域)が第2の絶縁層124と接した状態で昇温され、酸素を含む第2の絶縁層124から酸素を半導体層118へ供給し、半導体層118中の酸素欠損を低減することができる。なお、第3の加熱処理時の雰囲気は、第2の絶縁層124の成膜室内と同様に、水、水素などの不純物を極力除去することが望ましい。

10

【0160】

次に、第2の絶縁層124上に平坦化絶縁層として機能する第3の絶縁層126を形成する(図6(B)参照)。第3の絶縁層126は、アクリル樹脂、ポリイミド、ポリアミドなどの有機樹脂、またはシロキサンを用いて形成することが望ましい。

20

【0161】

上記樹脂として、感光性樹脂を用いても良い。

【0162】

本実施の形態では、第3の絶縁層126に感光性アクリル樹脂を用い、露光(フォトマスク使用)によって開口部を有する形状を得た後に、第3の絶縁層126をマスクとして第2の絶縁層124及び半導体層118をエッチングし、第2の開口部130a、第3の開口部130bを形成する(図6(C)参照)。

30

【0163】

なお、半導体層118に対してのエッチング処理は、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl<sub>2</sub>)、三塩化硼素(BCl<sub>3</sub>)、四塩化珪素(SiCl<sub>4</sub>)、四塩化炭素(CCl<sub>4</sub>)など)を用いることができる。

【0164】

ドライエッチングとしては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。

【0165】

第2の開口部130aは、第3の絶縁層126、第2の絶縁層124及び半導体層118をエッチングして形成される。第2の開口部130aの形成によって、半導体層118の不要な領域が除去され、半導体層118は島状に切り離された状態になる。

40

【0166】

第3の開口部130bは、第2の絶縁層124の下部にある第2のドレイン電極122d及び配線122eがエッチングストッパーとなるため、第3の絶縁層126及び第2の絶縁層124のみがエッチングされて形成される。

【0167】

通常の方法では、半導体層118を島状に加工する第2の開口部130aの形成と、コンタクトホール開口を行う第3の開口部130bは異なるフォトマスクを用い、フォトリソグラフィ工程およびエッチング処理を別々に行うが、本実施の形態に示す作製工程によれば、第2の開口部130aと第3の開口部130bのフォトリソグラフィ工程およびエッ

50

チング工程を同時に行うことが可能となる。したがって、フォトマスクを削減する事が可能であり、また、フォトリソグラフィ工程およびエッチング工程も削減することが可能となる。

【0168】

さらに、本実施の形態に示す作製工程によれば、半導体層118上にフォトレジストが直接形成されることはなく、フォトレジストの剥離洗浄工程などにおいて半導体層118を汚染する事がないため、トランジスタの電気特性の変動を抑えることができる。

【0169】

次に、第2の開口部130aおよび第3の開口部130bを覆うように第3の導電層を形成する。本実施の形態では、第1のトランジスタ151、第2のトランジスタ152は半導体層118に酸化物半導体を用いたnチャネル型であり、第1の画素電極128となる第3の導電層としては発光素子の陰極となる材料を用いるのが望ましい。具体的には、陰極としては、仕事関数が小さい材料、例えば、Ca、Al、CaF<sub>2</sub>、Mg-Ag、Al-Li等を用いることができる。なお、第3の導電層として透光性導電膜を用いても良い。この場合は、透光性導電膜上に陰極となる上記材料を光が透過する程度に薄く形成すれば良い。なお、透光性導電膜としては、例えば酸化タンゲスタンを含むインジウム酸化物、酸化タンゲスタンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などがある。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。

10

20

30

【0170】

次に、第3の導電層上に第5レジストマスクを形成し、第5のレジストマスクを用いて選択的にエッチングを行って、第1の画素電極128を形成する(図7(A)参照)。なお、第1の画素電極128にITO等の酸化物導電層を用いると、FPC接続部において下層の金属導電層の表面酸化によるFPC端子との接触抵抗の増加を抑えることができ、半導体装置の信頼性を向上させることができる。

【0171】

加えて、I型化(真性化)または実質的にI型化された酸化物半導体を半導体層118に用いることにより、I型化または実質的にI型化された酸化物半導体は、ほぼ絶縁物とみなすことができるため、第1の画素電極128と半導体層118の端部が接しても(例えば第2の開口部130aにおける、半導体層118の側面と第1の画素電極128が接しても)、漏れ電流等の問題は生じない。

30

【0172】

また、半導体層118の端面が第1の画素電極128により覆われているため、外部からの不純物、例えば、水素、水、水酸基を有する化合物、又は水素化物、アルカリ金属(例えば、ナトリウム、リチウム、カリウムなど)、アルカリ土類金属が半導体層118に到達して、トランジスタの電気特性や信頼性に悪影響を及ぼす事を抑制できる。

【0173】

なお、本実施の形態では発光素子からの光が基板101とは逆方向(図5での上方向)に射出する上方射出構造(トップエミッション構造)のため、第3の導電層に特段の限定はないが、ボトムエミッション構造やデュアルエミッション構造において、第3の導電層により形成される第1の画素電極128が射出光の通過部分に存在する(つまり、射出光が第1の画素電極128により遮られる)場合は、第3の導電層としては透光性を有する層を形成することが望ましい。

40

【0174】

次に、第1の画素電極128の端部を覆うように第3の絶縁層126上に隔壁129を形成する。(図7(B)参照)。隔壁129としては、例えばポリイミド、ポリアミド、ポリイミドアミド又はベンゾシクロブテン系樹脂(BCB)といった有機材料や、酸化珪素、窒化珪素、酸化窒化珪素又はこれらを積層させた積層膜といった珪素を含む無機材料や

50

、酸化アルミなどの金属酸化膜であってもよい。また、上記の材料を積層させた膜であってもよい。

【0175】

以上の工程を含む作製方法によって、少なくとも第1のゲート電極112a、第2のゲート電極112b、第1の絶縁層116、半導体層118、第1のソース電極122a、第1のドレイン電極122b、第2のソース電極122c、第2のドレイン電極122d、第2の絶縁層124、第3の絶縁層126、第1の画素電極128および隔壁129を有する素子領域180を基板101上に剥離層108を介して形成できる。

【0176】

図面には記載されていないが、素子領域180に形成されたトランジスタは静電気などにより破壊されやすいため、保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

10

【0177】

なお、上記の方法で形成される構成とは異なり、容量素子153を形成しない構成では、図5(A)において、容量素子を形成する領域に第2のゲート電極112bを設けない構成とすれば良い。

【0178】

また、第3の絶縁層126を設けない構成とすることもできる。この構成の作製方法は、図6(A)までは上述の方法と同様なので、以下にて図6(A)以降の工程について説明する。

20

【0179】

図6(A)までの工程が終了した基板に対し、第2の絶縁層124上に第4のレジストマスクを形成し、第4のレジストマスクを用いて第2の絶縁層124および半導体層118に対して部分的にエッチングを行い、第2の開口部130aおよび第3の開口部130bを形成する(図8(A)参照)。

【0180】

次に、第2の開口部130aおよび第3の開口部130bを覆うように第3の導電層を形成し、第3の導電層上に第5レジストマスクを形成し、第5のレジストマスクを用いて第3の導電層を部分的にエッチングを行って、第1の画素電極128を形成する(図8(B)参照)。

30

【0181】

次に、第1の画素電極128の端部を覆うように第2の絶縁層124上に隔壁129を形成する。(図8(C)参照)。

【0182】

隔壁129として、ポリシロキサンなどの有機樹脂膜、または無機絶縁膜を用いて形成する。特に感光性の材料を用い、第1の画素電極128と重なる領域上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0183】

本実施の形態では、隔壁129としてポリイミド(PI)膜を用いる。

40

【0184】

本実施の形態によれば、従来よりも少ないフォトリソグラフィ工程により発光表示装置を作製することが可能となる。よって、発光表示装置を低コストで、生産性よく作製することができる。また、発光表示装置を動作させるために必要な素子領域180が、剥離層108を介して基板101上に形成されるため、素子領域180を基板101から剥離して他の支持体に移す事ができる。

【0185】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0186】

(実施の形態2)

50

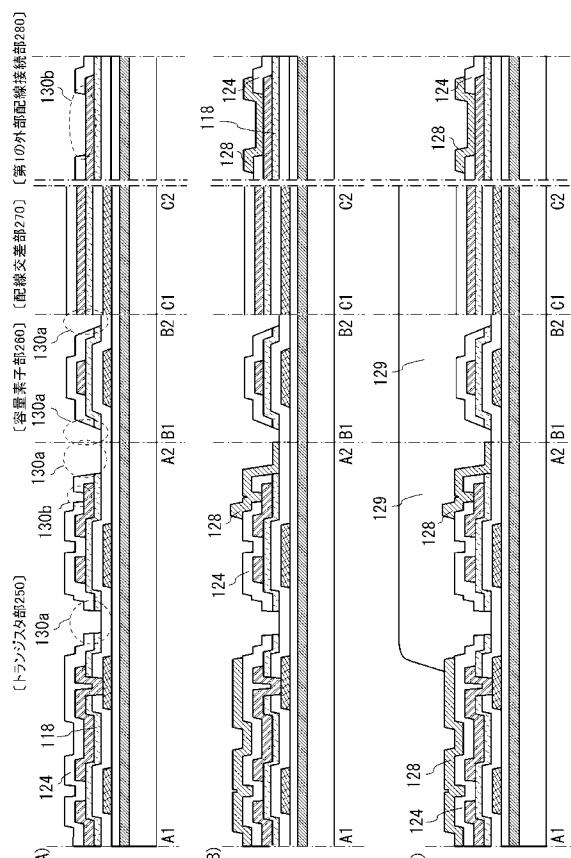

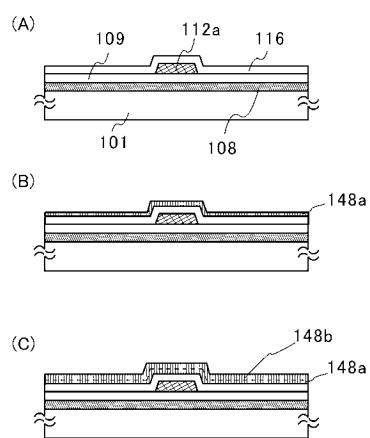

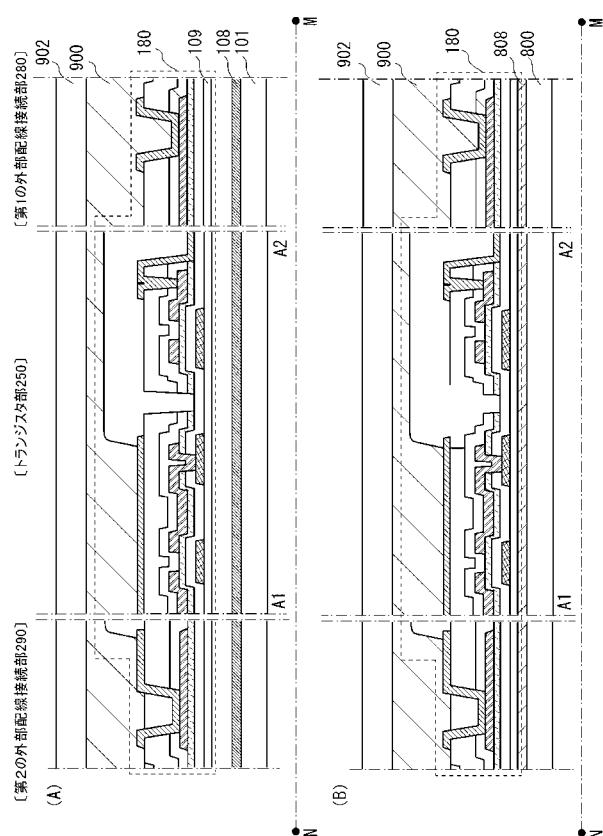

本実施の形態では、実施の形態1と一部異なる工程例を、図9を用いて説明する。なお、図9において、図5と同一の箇所には同じ符号を用い、同じ符号の詳細な説明はここでは省略する。また、本実施の形態は実施の形態1の一部のみの変更であるため、第1のトランジスタ151部分の構造のみに着目して説明を行う。

【0187】

まず、実施の形態1と同様に、絶縁表面を有する基板101上に剥離層108を成膜し、剥離層108上に下地層109を形成し、下地層109上に第1の導電層を形成し、第1の導電層上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層を部分的にエッチングして、第1のゲート電極112aを形成する

10

【0188】

本実施の形態では下地層109として、基板101からの不純物元素(Naなど)の拡散を防止する機能があり、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウムから選ばれた膜で形成すればよい。また、該下地膜は単層に限らず、上記の膜の積層であっても良い。

【0189】

本実施の形態では、後に成膜する半導体膜の成膜温度が200以上450以下、半導体膜の成膜後の加熱処理の温度が200以上450以下であるため、第1のゲート電極112aの材料として、銅を下層とし、モリブデンを上層とする積層、または銅を下層とし、タンゲステンを上層とする積層を用いる。

20

【0190】

次に、実施の形態1と同様に、第1のゲート電極112a上にゲート絶縁層として機能する第1の絶縁層116をスパッタ法やCVD法などを用いて形成する。ここまで工程を経た断面図を図9(A)に示す。

【0191】

次に、第1の絶縁層116上に、1nm以上10nm以下の第1の酸化物半導体膜を形成する。本実施の形態では、酸化物半導体用ターゲット(In-Ga-Zn-O系酸化物半導体用ターゲット(In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:2[mol数比])を用いて、基板とターゲットの間との距離を170mm、基板温度250、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚5nmの第1の酸化物半導体膜を成膜する。

30

【0192】

次いで、基板を配置する雰囲気を窒素、または乾燥空気とし、第1の加熱処理を行う。第1の加熱処理の温度は、200以上450以下とする。また、第1の加熱処理の加熱時間は1時間以上24時間以下とする。第1の加熱処理によって第1の結晶性半導体層148aを形成する(図9(B)参照)。

【0193】

次に、第1の結晶性半導体層148a上に10nmよりも厚い第2の酸化物半導体膜を形成する。本実施の形態では、酸化物半導体用ターゲット(In-Ga-Zn-O系酸化物半導体用ターゲット(In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:2[mol数比])を用いて、基板とターゲットの間との距離を170mm、基板温度400、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚25nmの第2の酸化物半導体膜を成膜する。

40

【0194】

次に、基板を配置する雰囲気を窒素、または乾燥空気とし、第2の加熱処理を行う。第2の加熱処理の温度は、200以上450以下とする。また、第2の加熱処理の加熱時間は1時間以上24時間以下とする。第2の加熱処理によって第2の結晶性半導体層148bを形成する(図9(C)参照)。

【0195】

以降の工程は、実施の形態1に従って、第2の導電層や第2の絶縁層124などを形成し、第1の結晶性半導体層148a、及び第2の結晶性半導体層148bを同一のレジスト

50

マスクを用いてエッチングすることによって、フォトリソグラフィ工程を削減する。

【0196】

この後、実施の形態1と同様の工程を経て図5(C)に示す第1のトランジスタ151、第2のトランジスタ152を含む構成を得ることができる。ただし、本実施の形態を用いた場合、これらのトランジスタのチャネル形成領域を含む半導体層は、第1の結晶性半導体層148a、及び第2の結晶性半導体層148bの積層となる。第1の結晶性半導体層148aを成膜後に第1の加熱処理を行って第1の結晶性半導体層148aをCACC化した後に、第2の結晶性半導体層148bを成膜および第2の加熱処理を行うことで、第2の結晶性半導体層148bは第1の結晶性半導体層148aを種として結晶(CACC)が成長するため、CACC化した酸化物半導体を効率良く形成することができる。

10

【0197】

第1の結晶性半導体層148aと第2の結晶性半導体層148bの積層を有するトランジスタは、トランジスタに光照射が行われ、またはバイアス-熱ストレス(BT)試験前後においてもトランジスタのしきい値電圧の変化量が低減でき、安定した電気的特性を有する。

【0198】

本実施の形態は、他の実施の形態と自由に組み合わせることができる。

【0199】

(実施の形態3)

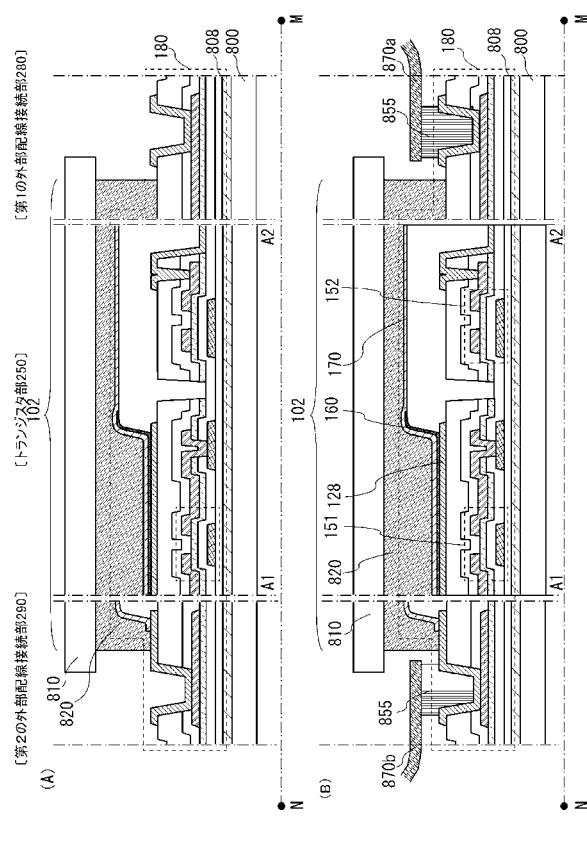

本実施の形態では、実施の形態1および実施の形態2で作製した素子領域180を、基板101から剥離して他の支持体に設置することにより作製される、薄く、軽量であり且つ高いじん性を備えた発光表示装置の構造の一例を図10に示すと共に、当該発光表示装置を作製する方法の一例を、図11乃至図13を用いて説明する。

20

【0200】

なお、発光表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。本明細書では、発光素子として有機EL素子を用いた発光表示装置であることを前提して説明を行う。

30

<発光表示装置の構成例>

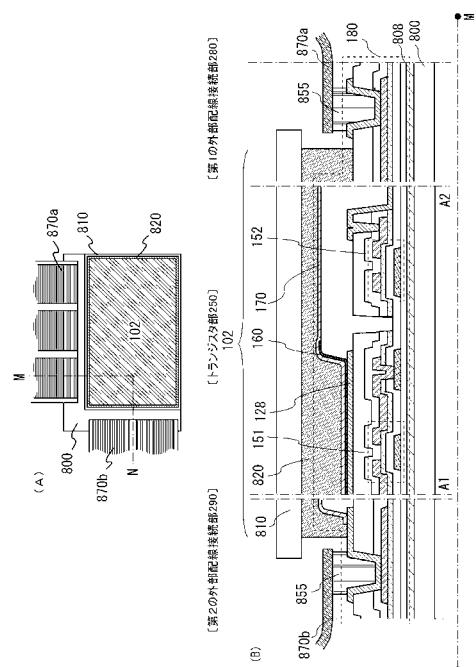

図10(A)は、実施の形態1および実施の形態2で作製した素子領域180を、基板101から剥離して他の支持体に設置することにより作製される、薄く、軽量であり且つ高いじん性を備えた発光表示装置の構造の一例の平面図であり、図10(B)は、図10(A)の一点鎖線M-Nにおける断面図に相当する。

【0201】

なお、図10(B)の断面図によりパネル全面の構造を全て表すことはできないので、本実施の形態では、パネル断面構造として実施の形態1にて記載した画素部のトランジスタ部250および第1の外部配線接続部280を示すと共に、発光素子上に形成した第2の画素電極170と外部装置間で信号や電力を送受するための第2の外部配線接続部290を並記する。

40

【0202】

第1の支持体800は破壊じん性値が1.5 [MPa · m<sup>1/2</sup>]以上の値を有し、固定用接着剤808を介して素子領域180が設けられ、画素領域102内に形成された素子領域180の第1の画素電極128上に発光素子160が形成され、発光素子160を覆うように第2の画素電極170が形成されている。第1の支持体800として破壊じん性値が1.5 [MPa · m<sup>1/2</sup>]以上の値を有した材料を用いているため、薄く、軽量であり且つ高いじん性を備えた発光表示装置を作製できる。なお、図10(B)では素子領域180に発光素子160および第2の画素電極170が含まれているが、これは素子領域180の範囲表示するにあたり発光素子160および第2の画素電極170を分離して表示することが困難なためであり、実際には素子領域180に発光素子160および第2

50

の画素電極 170 は含まれない。

【0203】

第2の支持体 810 は、破壊じん性値が  $1.5 [ \text{M Pa} \cdot \text{m}^{1/2} ]$  以上の値を有した支持体を用いているため、薄く、軽量であり且つ高いじん性を備えた発光表示装置を作製することができる。

【0204】

発光素子 160 および第2の画素電極 170 が形成された素子領域 180 上には、画素領域 102 を覆うようにシール材 820 が設けられ、シール材 820 により、画素領域 102 と第2の支持体 810 が接着されている。

【0205】

また、素子領域 180 上であり、かつシール材 820 の外側の領域に第1の外部配線接続部 280 および第2の外部配線接続部 290 を有し、外部配線 870a、外部配線 870b が導電材料 855 を介して、素子領域 180 に形成された配線に接続されている。外部配線 870a および外部配線 870b は、外部から発光表示装置を動作させるために必要な電力や信号を導電材料 855 を介して素子領域 180 に供給する機能を持つ。

【0206】

上記構造を形成することにより、薄く、軽量であり且つ破壊が生じにくい発光表示装置を作製できる。

【0207】

<発光表示装置の作製方法>

次に、上記発光表示装置の作製方法の一例について、図 11 乃至 図 13 を用いて説明する。なお、本実施の形態における発光表示装置の作成工程は「第1の支持体への素子領域設置工程」、「発光素子形成および封止工程」、の2つに分けて説明を行う。

【0208】

<第1の支持体への素子領域設置工程>

まず、実施の形態 1 にて作製した、基板 101 上に剥離層 108 を介して形成された素子領域 180 の一面に、剥離用接着剤 900 を用いて仮支持基材 902 を接着した後に、素子領域 180 を基板 101 から剥離して仮支持基材 902 側に移し替える（図 11 (A) 参照）。なお、本明細書において、素子領域 180 を剥離層 108 から剥離して仮支持基材 902 側に移し替える工程を転置工程という。

【0209】

剥離用接着剤 900 は、水や有機溶媒に可溶な性質を有するものや、紫外線などの照射により可塑化させることができるとあるよう、必要に応じて仮支持基材 902 と素子領域 180 から除去できる接着剤を用いる。なお、剥離用接着剤 900 は、スピンドルコーター、スリットコーター、グラビアコーター、ロールコーターなどの各種コーティング装置や、フレキソ印刷装置、オフセット印刷装置、グラビア印刷装置、スクリーン印刷装置、インクジェット装置などの各種印刷装置を用いて薄く均一な膜厚で設けることが好ましい。

【0210】

仮支持基材 902 には、UV 剥離型テープ、熱剥離型テープなどのよう、表面の粘着性を任意に低下できるテープを用いることができる。また、ガラス基板、石英基板、サファイア基板、セラミック基板、金属基板、プラスチック基板などを用いてもよい。なお、表面の粘着性を任意に低下できるテープを用いる場合は、剥離用接着剤 900 を必ずしも別途用いる必要はない。また、プラスチック基板を用いる場合は、以降の処理温度に耐えうる耐熱性を有するものを用いることが好ましい。

【0211】

なお、仮支持基材 902 を素子領域 180 に貼り合わせる方法には特に限定はないが、仮支持基材 902 として各種テープのよう可撓性を有する材料を用いる場合は、例えば、ローラーを用いて貼り合わせる事が可能な装置（ロールラミネーターとも呼ぶ）などを用いればよい。これにより、素子領域 180 と仮支持基材 902 の間に気泡などが混入せず、安定した貼り合わせを行うことができる。

10

20

30

40

50

## 【0212】

本実施の形態では、紫外線照射により硬化し、且つ水に可溶な接着剤（以下、水溶性接着剤と呼称する）を剥離用接着剤900として用い、スピンドルコート装置を用いて素子領域180の一面に薄く塗布して硬化処理を行った。その後、剥離用接着剤900上に仮支持基材としてUV剥離型テープ（UVの照射により粘着力を低下できるテープ）を、ロールラミネーターを用いて貼り合わせた。

## 【0213】

素子領域180を基板101から剥離するには、様々な方法を適宜用いることができる。例えば、剥離層108として、タンゲステン（W）、モリブデン（Mo）、チタン（Ti）、タンタル（Ta）、ニオブ（Nb）、ニッケル（Ni）、コバルト（Co）、ジルコニウム（Zr）、亜鉛（Zn）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、珪素（Si）から選択された元素、又は上記元素を主成分とする合金材料、又は上記元素を主成分とする化合物材料からなる層を形成した場合は、当該金属酸化膜を結晶化させることにより脆弱化させ、物理的な力（例えば、仮支持基材902を基板101から引き剥がす力）を加えることにより、素子領域180を剥離層108から剥離することができる。

10

## 【0214】

また、剥離層108として水素を含む非晶質珪素膜を形成した場合は、レーザ光の照射またはエッティングにより当該水素を含む非晶質珪素膜を除去して、素子領域180を基板101から剥離することができる。また、剥離層108として窒素、酸素や水素等を含む膜（例えば、水素を含む非晶質珪素膜、水素含有合金膜、酸素含有合金膜など）を用いた場合には、剥離層108にレーザ光を照射して剥離層108内に含有する窒素、酸素や水素をガスとして放出させ、素子領域180と基板101との剥離を促進することができる。また、剥離層108を溶液やNF<sub>3</sub>、BrF<sub>3</sub>、ClF<sub>3</sub>等のフッ化ハロゲンガスによるエッティングで除去する方法等も用いることができる。

20

## 【0215】

また、剥離層108として有機樹脂を形成した場合は、有機樹脂に内在する応力を利用して剥離を行ってもよい。

## 【0216】

上記剥離方法を複数組み合わせることでより容易に剥離工程を行うことができる。具体的には、レーザ光の照射、ガスや溶液などによる剥離層へのエッティング、鋭いナイフやメスなどの機械的力で剥離層を部分的に除去するなどを行い、剥離層と素子層とを剥離しやすい状態にしてから、物理的な力（機械等による）によって剥離を行う工程などがこれに当たる。剥離層108を金属と金属酸化物との積層構造により形成した場合、レーザ光の照射によって形成される溝や鋭いナイフやメスなどによる傷などをきっかけとして、剥離層から物理的に引き剥がすことも容易となる。

30

## 【0217】

素子領域180を物理的に引き剥がす剥離は、溶液やガスなどを用いて剥離層を除去することで素子領域180を剥離する方法と比較して、短時間で大面積の剥離処理を行うことが可能である。また、溶液やガスを用いないため安全性も高い。したがって、素子領域180を基板101から剥離する方法としては、物理的な力を加えて剥離する方法が生産性や安全性の観点から最も有利である。

40

## 【0218】

また、物理的な手段により剥離を行う場合には、水などの液体をかけながら剥離を行ってもよい。これにより、剥離作業により生じる静電気が、素子領域180に与える悪影響（例えば、半導体素子が静電気により破壊される）を抑制できる。

## 【0219】

なお、半導体層118として酸化物半導体を用いた場合、酸化物半導体はシリコン材料を用いた一般的な半導体層と比較して絶縁破壊を生じにくい。このため、半導体層118として酸化物半導体を用いることにより、剥離作業により静電気が発生した場合においても

50

、半導体層 118 が静電気により破壊されてしまうことを抑制できる。

【0220】

素子領域 180 を剥離層 108 から剥離する際に基板 101 を固定することで、基板 101 の動きおよび撓みを抑制できるため、素子領域 180 に局所的な力が加わることを防止できる。したがって、素子領域 180 を不具合なく（例えば、素子領域 180 にクラックが発生しない）剥離することができる。基板 101 を固定する方法としては、例えば、接着材料（または粘着材料）を用いて安定した台座に固定する、真空チャックにより固定するなどの方法があるが、基板 101 を剥がす手間や基板 101 の再利用を考慮すると、真空チャックにより固定することが望ましい。特に、表面が多孔質状になっている真空チャック（ポーラスチャックとも呼ぶ）を用いることで、基板 101 の全面を均一な力で固定できるため、より望ましい。

10

【0221】

なお、素子領域 180 上に剥離用接着剤 900 を設ける前に、素子領域 180 に対して、ジェット洗浄、超音波洗浄、プラズマ洗浄、UV洗浄、オゾン洗浄などを行い、素子領域 180 表面に付着したゴミや有機成分を除去することが好ましい。

【0222】

次に、素子領域 180 の他の一面に固定用接着剤 808 を用いて第 1 の支持体 800 を接着する（図 11（B）参照。）。

【0223】

固定用接着剤 808 の材料としては、紫外線硬化型接着剤など光硬化型の接着剤、反応硬化型接着剤、熱硬化型接着剤、または嫌気型接着剤など各種硬化型接着剤を用いることができる。

20

【0224】

固定用接着剤 808 は、スピンドルコーティング装置や、フレキソ印刷装置、オフセット印刷装置、グラビア印刷装置、スクリーン印刷装置、インクジェット装置などの各種印刷装置を用いて薄く均一な膜厚で設けることが好ましい。

【0225】

第 1 の支持体 800 としては、高いじん性（具体的には、 $1.5 [M Pa \cdot m^{1/2}]$  以上の破壊じん性値）を備えた各種材料を用いる。例えば、有機樹脂基板および有機樹脂薄膜、または、金属基板および金属薄膜などを用いる。これにより、薄く軽量であり且つ衝撃や曲げなど、外部から力を付加しても破壊の生じにくい発光表示装置を作製できる。なお、高いじん性を備えた各種材料は一般的に、じん性と共に高い可撓性を併持しており、高いじん性を備えた第 1 の支持体 800 は自由に湾曲させる事が可能である。また、第 1 の支持体 800 の厚さは、発光表示装置の使用用途により適宜選択すればよい。例えば、発光表示装置を曲面などの形状に沿った状態に湾曲して設置する、丸めて持ち運ぶといった状態で使用する場合は、第 1 の支持体 800 の厚さを薄くすればよい。また、外部から衝撃などの力がかかるような状況下で使用する場合においては、第 1 の支持体 800 の厚さを厚くすればよい。

30

【0226】

上記有機樹脂基板および有機樹脂薄膜としては、例えば、ポリエチレンテレフタレート樹脂（PET）、ポリエーテルスルホン樹脂（PES）、ポリエチレンナフタレート樹脂（PEN）、ポリビニルアルコール樹脂（PVA）、ポリカーボネート樹脂（PC）、ナイロン樹脂、アクリル樹脂、ポリアクリルニトリル樹脂、ポリエーテルエーテルケトン樹脂（PEEK）、ポリスチレン樹脂（PS）、ポリスルホン樹脂（PSF）、ポリエーテルイミド樹脂（PEI）、ポリアリレート樹脂（PAR）、ポリブチレンテレフタレート樹脂（PBT）、ポリイミド樹脂（PI）、ポリアミド樹脂（PA）、ポリアミドイミド樹脂（PAI）、ポリイソブチレン樹脂（PIB）、塩素化ポリエーテル樹脂（CP）、メラミン樹脂（MF）、エポキシ樹脂（EP）、塩化ビニリデン樹脂（PVdC）ポリプロピレン樹脂（PP）、ポリアセタール樹脂（POM）、フッ素樹脂（PTFE）、フェノ

40

50

ール樹脂( P F )、フラン樹脂( F F )、不飽和ポリエステル樹脂( F R P )、酢酸セルロース樹脂( C A )、ユリア樹脂( U F )、キシレン樹脂( X R )、ジアリルフタレート樹脂( D A P )、ポリ酢酸ビニル樹脂( P V A c )、ポリエチレン樹脂( P E )、A B S樹脂のうち少なくとも1種類以上を構成成分として含む基板および薄膜を用いることができる。

【 0 2 2 7 】

上記金属基板および金属薄膜としては、例えば、アルミ( A l )、チタン( T i )、ニッケル( N i )、クロム( C r )モリブデン( M o )、タンタル( T a )、ベリリウム( B e )、ジルコニウム( Z r )、金( A u )、銀( A g )、銅( C u )、亜鉛( Z n )、鉄( F e )、鉛( P b )、スズ( S n )、またはこれらの合金からなる基板および薄膜を用いることができる。

10

【 0 2 2 8 】

第1の支持体 8 0 0 の材料選定に際して、本実施の形態のように上方射出型(トップエミッショニ型)の発光表示装置では上記材料を用い、さらに熱膨張係数が 2 0 p p m / 以下である材料を用いることが好ましい。これにより第1の支持体 8 0 0 に熱が加わる事による素子領域 1 8 0 へのクラック発生などの不具合を抑制できる。また、発光素子として有機 E L 素子を用いているため、酸素透過率や水蒸気透過率の低い材料を用いることが好ましく、金属基板、金属薄膜を用いることが好ましい。

20

【 0 2 2 9 】

なお、本実施の形態では第1の支持体 8 0 0 は単層構造であるが、第1の支持体 8 0 0 の表面や裏面に保護層を形成してもよい。保護層としては、例えば、酸化珪素( S i O <sub>2</sub> )、窒化珪素( S i N )、酸化窒化珪素( S i O N )、窒化酸化珪素( S i N O )などの無機薄膜や、アルミニウム( A l )、マグネシウム( M g )などの金属膜およびそれら金属の酸化膜などを用いることができ、特に水蒸気透過性、ガス透過性、紫外線透過性の低い膜を用いることが好ましい。これらの保護層は、例えば、スパッタリング法やプラズマ C V D 法を用いて設ければよい。

20

【 0 2 3 0 】

下方射出型(ボトムエミッショニ型)や両方射出型(デュアルエミッショニ型)では、第1の支持体として金属基板や金属薄膜を用いると、発光素子 1 6 0 からの光の射出を妨げてしまうため、第1の支持体として有機樹脂基板や有機樹脂薄膜を用いることが好ましく、さらに金属酸化膜や極薄の金属膜を第1の支持体表面に形成して、酸素透過率や水蒸気透過率を低減することが好ましい。

30

【 0 2 3 1 】

なお、本実施の形態では素子領域 1 8 0 の他の一面に、固定用接着剤 8 0 8 を介して第1の支持体 8 0 0 を接着しているが、第1の支持体 8 0 0 として纖維体に有機樹脂が含浸された構造体(いわゆるプリプレグ)を用いた場合には、含浸された有機樹脂が固定用接着剤 8 0 8 の役割を果たすため、固定用接着剤 8 0 8 を用いず直接素子領域 1 8 0 と第1の支持体 8 0 0 を接着することができる。この際、当該構造体の有機樹脂としては、反応硬化型、熱硬化型、紫外線硬化型など追加処理を施すことによって硬化が進行するものを用いるとよい。

40

【 0 2 3 2 】

本実施の形態では、第1の支持体としてステンレスフィルム(いわゆる S U S フィルム。鉄をベースとしてクロムやニッケルなどを添加した材料から作製されるフィルム)を用い、スクリーン印刷装置を用いて表面に熱硬化型接着剤を薄く設けた。これを素子領域の他の一面に貼り合わせて硬化処理を行った。

【 0 2 3 3 】

なお、第1の支持体 8 0 0 上に固定用接着剤 8 0 8 を設ける前に、第1の支持体 8 0 0 に對して、流体ジェット洗浄、超音波洗浄、プラズマ洗浄、U V 洗浄、オゾン洗浄などを行い、第1の支持体 8 0 0 に付着したゴミや有機成分を除去することが好ましい。

【 0 2 3 4 】

50

また、第1の支持体800に対して加熱処理を行ってもよい。加熱処理を行うことにより、第1の支持体に付着した水分や不純物を除去できる。さらに、減圧状態で加熱処理を行うことにより、より効率的に水分や不純物を除去できる。加熱処理を行う場合は、第1の支持体800には、加熱処理の温度に耐えるだけの耐熱温度を有した基板を用いることが好ましい。

【0235】

なお、上記の各種洗浄方法および加熱処理については、どれか1つを行ってもよいし、複数を組み合わせてもよい。例えば、流体ジェット洗浄を行って第1の支持体800に付着したゴミを除去した後にオゾン洗浄を行って有機成分を除去し、最後に加熱処理を行って、流体洗浄の際に第1の支持体800に付着した水分や内部に吸収された水分を除去することで、第1の支持体800のゴミ、有機成分、水分を効果的に除去できる。

10

【0236】

次に、素子領域180から剥離用接着剤900および、仮支持基材902を取り除く(図12(A)参照)。

【0237】

本実施の形態では、剥離用接着剤900として水溶性接着剤を用い、仮支持基材902とUV剥離型テープを用いているため、まずUV照射処理を行い仮支持基材902を取り除いた後に、流水洗浄により剥離用接着剤900を取り除いた。

20

【0238】

なお、第1の支持体800は高いじん性を備えているため、外部から力が加わることにより変形するだけの可撓性を有している。このため、分離作業時や後の工程にて第1の支持体800に負荷が加わり変形や破壊が生じないように、第1の支持体800に対して接着部材を介して剛性の高い基板を貼り付けた状態で、素子領域180から仮支持基材902を分離することが好ましい。このように、剛性の高い基板を貼り付けることにより、ガラス基板などで用いられる製造装置をそのまま用いることができる。

【0239】

以上の工程により、固定用接着剤808を介して素子領域180が表面に設置された第1の支持体800を作製することができる。

30

【0240】

<発光素子形成および封止工程>

次に、画素領域102内において、素子領域180に形成された第1の画素電極128を覆うように発光素子160を形成し、発光素子160を覆うように第2の画素電極170を形成する。なお、第2の画素電極170は第2の外部配線接続部290に形成された配線部と電気的に接続されている(図12(B))。

【0241】

発光素子160については特に限定はなく、既知の有機EL素子や無機EL素子をもちいればよい。

【0242】

有機EL素子は、発光素子を挟む対の電極(本実施の形態では、第1の画素電極128および第2の画素電極170が、これに相当する)に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。上記のようなメカニズムから、このような発光素子は電流励起型の発光素子と呼ばれる。

40

【0243】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー-アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利

50

用する局在型発光である。なお、本実施の形態では、発光素子として有機EL素子を用いて説明する。

【0244】

第2の画素電極170は、発光素子160を覆うように形成する。第2の画素電極170には、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ( $In_2O_3-SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛( $In_2O_3-ZnO$ )またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。また、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することもできる。導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはアニリン、ピロールおよびチオフェンの2種以上からなる共重合体若しくはその誘導体などがあげられる。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。また、上記透光性導電膜の他に、窒化チタン膜またはチタン膜を用いても良い。第1の画素電極128と発光素子160と第2の画素電極170とが重なり合うことで、EL素子が形成される。この後、発光素子に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の画素電極170及び隔壁129上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC膜等を形成することができる。

10

20

30

40

なお、本実施の形態では、発光素子160からの射出光が第2の画素電極側に射出される構造(トップエミッション構造)を前提として説明しているために第2の画素電極170として上記材料を用いることを説明したが、発光素子160からの射出光が第1の画素電極側に出力される構造(ボトムエミッション構造)の場合は、第2の画素電極170として、例えば、モリブデン( $Mo$ )、チタン( $Ti$ )、タンゲステン( $W$ )、タンタル( $Ta$ )、アルミニウム( $Al$ )、銅( $Cu$ )、クロム( $Cr$ )、ネオジム( $Nd$ )、スカンジウム( $Sc$ )等の金属材料又はこれらを主成分とする合金材料を用いて、単層又は積層して形成した層を用いてもよい。

【0246】

次に、シール材820を用いて第1の支持体800に対して第2の支持体810を貼り合わせ、シール材820を硬化させる(図13(A)参照)。

30

【0247】

なお、貼り合わせ処理は、真空貼り合わせ装置などを用いて、減圧状態が保たれた処理室内で、第1の支持体800および第2の支持体810を貼り合わせる事が好ましい。これにより、シール材や発光材料に気泡が発生しない状態で貼り合わせることができ、また、シール材820の領域内に、大気成分が封入されるのを抑制することができる。

40

【0248】

また、硬化処理は、シール材820の材料成分により、可視光照射、UV光照射、加熱処理の中から1種類または複数の処理を、硬化状態が最適となるように行う。

50

【0249】

また、本実施の形態では第2の画素電極170上に直接シール材820を設けているが、第2の画素電極170上に、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウムから選ばれた膜を単層または積層にて形成しても良い。これにより、外部からの不純物が発光素子160や素子領域180に浸入する事を抑制できる。

50

【0250】

次に、第1の外部配線接続部280および第2の外部配線接続部290に設けられた配線上に、導電材料855を設け、各々に外部配線870a、外部配線870bを貼り合わせる(図13(B)参照)。

50

【0251】

導電材料 855 としては、例えば、導電性粒子と有機樹脂を有する材料を用いる。具体的には、粒径が数 nm から数十  $\mu\text{m}$  の導電性粒子を有機樹脂に分散させた材料を用いる。導電性粒子としては、金 (Au)、銀 (Ag)、銅 (Cu)、ニッケル (Ni)、白金 (Pt)、パラジウム (Pd)、タンタル (Ta)、モリブデン (Mo)、チタン (Ti)、アルミ (Al)、カーボン (C) のいずれか一つ以上の金属粒子、絶縁粒子表面に前記いずれか一つ以上の金属膜が形成された粒子、ハロゲン化銀の微粒子、または半導体などを用いることができる。また、導電材料 855 に含まれる有機樹脂は、金属粒子のバインダ、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコーン樹脂等の有機樹脂が挙げられる。

10

#### 【0252】

導電材料 855 を設ける方法としては、フレキソ印刷装置、オフセット印刷装置、グラビア印刷装置、スクリーン印刷装置、インクジェット装置、ディスペンサー装置などの各種印刷装置を用いればよい。

#### 【0253】

本実施の形態では、導電材料 855 として、数 nm から数十  $\mu\text{m}$  サイズのフレーク状銀粒子が混入されたエポキシ樹脂を用いた。

#### 【0254】

外部配線 870a としては、例えば、プリント配線板や FPC (Flexible Printed Circuit) などがある。本実施の形態における発光表示装置は、ベース基板、対向基板共に高いじん性を備えており、発光表示装置が可撓性を有する状態の場合もあるため、外部配線 870a も可撓性を有することが好ましい。

20

#### 【0255】

接続処理としては、導電材料 855 が硬化する条件 (可視光照射、UV 光照射、加熱処理など) を導電材料 855 に与えればよい。さらに、導電材料 855 自体の導電性向上や、電極 222 と導電材料 855 の導通不良防止のため、導電材料 855 の接続処理時には圧力を加えることが望ましい。なお、接続処理としては、導電材料 855、外部配線 870a に対して加圧処理を行いながら加熱処理を行う圧着装置が広く用いられている。

#### 【0256】

以上の工程により作製された発光表示装置は、発光表示装置の動作に必要な素子領域 180 が従来よりも少ない枚数のフォトマスクで作製されており、且つ、素子領域 180 が、1.5 [MPa  $\cdot$  m<sup>1/2</sup>] 以上の破壊じん性値を有する第 1 の支持体 800 および第 2 の支持体 810 により挟持されている。

30

#### 【0257】

したがって、複雑な技術や特殊な装置を用いることなくフォトマスクの使用枚数を従来よりも少なくすることができると共に、薄く、軽量であり且つ高いじん性を備えた発光表示装置の作製できる。

#### 【0258】

また、第 1 の支持体 800 および第 2 の支持体 810 として、高い可撓性を併持する材料を用いることにより、曲面などの形状に沿った状態に湾曲して設置する、丸めて持ち運ぶといった用途に使用できる発光表示装置を作製する事も可能となる。

40

#### 【0259】

本実施の形態は、他の実施の形態と自由に組み合わせることができる。

#### 【0260】

##### (実施の形態 4)

本実施の形態では、本発明に係る半導体装置の使用形態の一例について説明する。本発明に係る半導体装置は、作製した基板から剥離することによって、可撓性を有する状態とすることができる。以下に、本発明に係る半導体装置を有する電子機器の具体例に関して図 12 を参照して説明する。電子機器とは、EL 表示装置、テレビジョン装置 (単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ) 及び携帯電話等を指す。

50

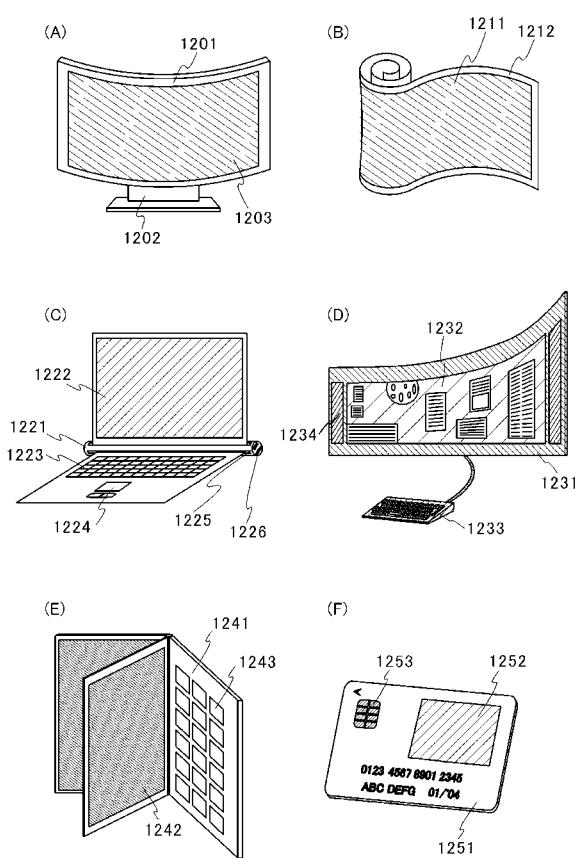

## 【0261】

図14(A)はディスプレイ1201であり、支持台1202、表示部1203を含む。表示部1203は可撓性を有する基板を用いて形成されており、軽量で薄型のディスプレイを実現できる。また、表示部1203を湾曲させることも可能であり、支持台1202から取り外して湾曲した壁に沿ってディスプレイを取り付けることも可能である。上記実施の形態で示した半導体装置を、表示部1203に用いることによって、本発明の半導体装置の使用形態の一つである可撓性を有するディスプレイを作製することができる。このように、可撓性を有するディスプレイは、フラットな面はもちろん湾曲した部分にも設置することが可能となるため、様々な用途に用いることができる。

## 【0262】

図14(B)は巻き取り可能なディスプレイ1211であり、表示部1212を含む。上記実施の形態で示した半導体装置を、表示部1212に用いることによって、本発明の半導体装置の使用形態の一つである、巻取りが可能で薄型の大型ディスプレイを作製することができる。巻き取り可能なディスプレイ1211は可撓性を有する基板を用いて形成されているため、表示部1212と共に折り畳んだり、巻き取ったりして持ち運ぶことが可能である。そのため、巻き取り可能なディスプレイ1211が大型である場合でも折り畳んだり、巻き取ったりして鞄に入れて持ち運ぶことができる。

## 【0263】

図14(C)は、シート型のコンピュータ1221であり、表示部1222、キーボード1223、タッチパッド1224、外部接続ポート1225、電源プラグ1226等を含んでいる。上記実施の形態で示した半導体装置を、表示部1222に用いることによって、本発明の半導体装置の使用形態の一つである、薄型またはシート型のコンピュータを作製することができる。表示部1222は可撓性を有する基板を用いて形成されており、軽量で薄型のコンピュータを実現できる。また、シート型のコンピュータ1221の本体部分に収納スペースを設けることによって表示部1222を本体に巻き取って収納することができる。また、キーボード1223も可撓性を有するように設けることによって、表示部1222と同様にシート型のコンピュータ1221の収納スペースに巻き取って収納することができ、持ち運びが便利になる。また、使用しない場合にも折り畳むことによって場所をとらずに収納することができる。

## 【0264】

図14(D)は、20~80インチの大型の表示部を有する表示装置1231であり、操作部であるキーボード1233、表示部1232、スピーカー1234等を含む。また、表示部1232は可撓性を有する基板を用いて形成されており、キーボード1233を取り外して表示装置1231を折り畳んだり巻き取ったりして持ち運ぶことが可能である。また、キーボード1233と表示部1232との接続は無線で行うことができ、例えば、湾曲した壁に沿って表示装置1231を取り付けながらキーボード1233で無線によって操作することができる。

## 【0265】

図14(D)に示す例では、上記実施の形態で示した半導体装置を、表示部1232に用いている。これによって、本発明の半導体装置の使用形態の一つである、薄型の大型表示装置を作製することができる。

## 【0266】

図14(E)は電子ブック1241であり、表示部1242、操作キー1243等を含む。またモデムが電子ブック1241に内蔵されていても良い。表示部1242は可撓性基板を用いて形成されており、折り曲げたり巻き取ったりすることができる。そのため、電子ブックの持ち運びも場所をとらずに行うことができる。さらに、表示部1242は文字等の静止画像はもちろん動画も表示することができる。

## 【0267】

図14(E)に示す例では、上記実施の形態で示した半導体装置を、表示部1242に用いている。これによって、本発明の半導体装置の使用形態の一つである、薄型の電子ブッ

10

20

30

40

50

クを作製することができる。

【0268】

図14(F)はICカード1251であり、表示部1252、接続端子1253等を含む。表示部1252は可撓性基板を用いて軽量、薄型のシート状になっているため、カードの表面に張り付けて形成することができる。また、ICカードが非接触でデータの受信が行える場合に外部から取得した情報を表示部1252に表示することが可能となっている。

【0269】

図14(F)に示す例では、上記実施の形態で示した半導体装置を、表示部1252に用いている。これによって、本発明の半導体装置の使用形態の一つである、薄型のICカードを作製することができる。

【0270】

このように、本発明に係る半導体装置を電子機器に用いることにより、曲げ等の外力が加わり応力が生じた場合であっても、トランジスタ等の素子の損傷を低減することができるため、半導体装置の歩留まりや信頼性を向上させることができる。

【0271】

以上のように、本発明の適用範囲はきわめて広く、あらゆる分野の電子機器や情報表示手段に用いることができる。

【0272】

(実施の形態5)

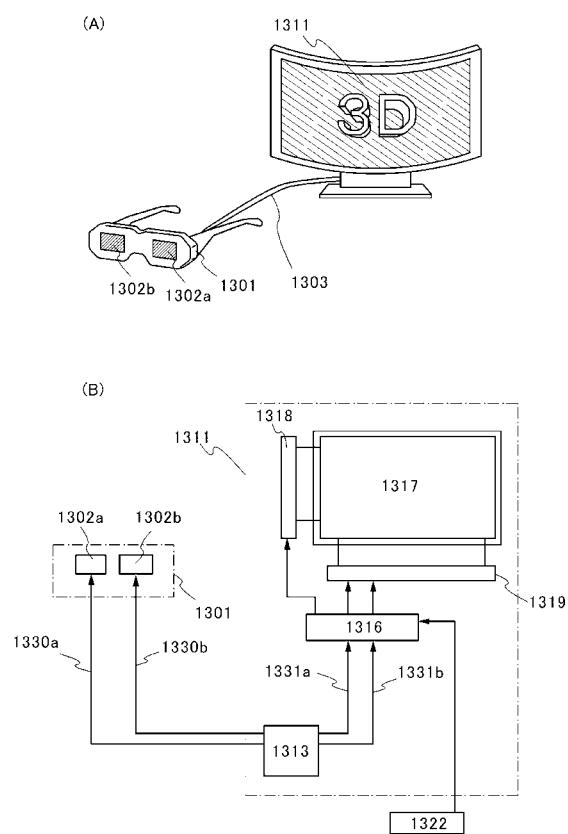

本実施の形態では、左目用の映像と右目用の映像を高速で切り換える表示装置として、先の実施の形態で作製した発光表示装置を用いて、表示装置の映像と同期する専用の眼鏡を用いて動画または静止画である3D映像を視認する例を図15を用いて示す。

【0273】

図15(A)は表示装置1311と、専用の眼鏡本体1301がケーブル1303で接続されている外観図を示す。専用の眼鏡本体1301は、左目用パネル1302aと右目用パネル1302bに設けられているシャッターが交互に開閉することによって使用者が表示装置1311の画像を3Dとして認識することができる。

【0274】

また、表示装置1311と専用の眼鏡本体1301の主要な構成についてのブロック図を図15(B)に示す。

【0275】

図15(B)に示す表示装置1311は、表示制御回路1316、表示部1317、タイミング発生器1313、ソース線側駆動回路1318、外部操作手段1322及びゲート線側駆動回路1319を有する。本発明の半導体装置は表示部1317に用いることができる。なお、キーボード等の外部操作手段1322による操作に応じて、出力する信号を可変する。

【0276】

タイミング発生器1313では、スタートパルス信号などを形成するとともに、左目用映像と左目用パネル1302aのシャッターとを同期させるための信号、右目用映像と右目用パネル1302bのシャッターとを同期させるための信号などを形成する。

【0277】

左目用映像の同期信号1331aを表示制御回路1316に入力して表示部1317に表示すると同時に、左目用パネル1302aのシャッターを開ける同期信号1330aを左目用パネル1302aに入力する。また、右目用映像の同期信号1331bを表示制御回路1316に入力して表示部1317に表示すると同時に、右目用パネル1302bのシャッターを開ける同期信号1330bを右目用パネル1302bに入力する。

【0278】

また、左目用の映像と右目の映像を高速で切り換えるため、表示装置1311は、発光ダイオード(LED)を用いて、時分割によりカラー表示する継時加法混色法(フィールド

10

20

30

40

50

シーケンシャル法)とすることが好ましい。

【0279】

また、フィールドシーケンシャル法を用いるため、タイミング発生器1313は、発光ダイオードのバックライト部にも同期信号1330a、1330bと同期する信号を入力することが好ましい。なお、バックライト部はR、G、及びBのLEDを有するものとする。

【0280】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【符号の説明】

【0281】

100 半導体装置

101 基板

102 画素領域

103 端子部

104 端子部

105 端子

106 端子

107 大版基板

108 剥離層

109 下地層

110 画素

112a 第1のゲート電極

112b 第2のゲート電極

116 第1の絶縁層

118 半導体層

120a 第1の開口部

122a 第1のソース電極

122b 第1のドレイン電極

122c 第2のソース電極

122d 第2のドレイン電極

124 第2の絶縁層

126 第3の絶縁層

128 第1の画素電極

129 隔壁

130a 第2の開口部

130b 第3の開口部

148a 第1の結晶性半導体層

148b 第2の結晶性半導体層

151 パソコン

152 パソコン

153 容量素子

160 発光素子

170 第2の画素電極

180 素子領域

250 トランジスタ部

260 容量素子部

270 配線交差部

280 第1の外部配線接続部

290 第2の外部配線接続部

10

20

30

40

50

|           |           |    |

|-----------|-----------|----|

| 8 0 0     | 第 1 の支持体  |    |

| 8 0 8     | 固定用接着剤    |    |

| 8 1 0     | 第 2 の支持体  |    |

| 8 2 0     | シール材      |    |

| 8 5 5     | 導電材料      |    |

| 8 7 0 a   | 外部配線      |    |

| 8 7 0 b   | 外部配線      |    |

| 9 0 0     | 剥離用接着剤    |    |

| 9 0 2     | 仮支持基材     |    |

| 1 2 0 1   | ディスプレイ    | 10 |

| 1 2 0 2   | 支持台       |    |

| 1 2 0 3   | 表示部       |    |

| 1 2 1 1   | ディスプレイ    |    |

| 1 2 1 2   | 表示部       |    |

| 1 2 2 1   | コンピュータ    |    |

| 1 2 2 2   | 表示部       |    |

| 1 2 2 3   | キーボード     |    |

| 1 2 2 4   | タッチパッド    |    |

| 1 2 2 5   | 外部接続ポート   |    |

| 1 2 2 6   | 電源プラグ     | 20 |

| 1 2 3 1   | 表示装置      |    |

| 1 2 3 2   | 表示部       |    |

| 1 2 3 3   | キーボード     |    |

| 1 2 3 4   | スピーカー     |    |

| 1 2 4 1   | 電子ブック     |    |

| 1 2 4 2   | 表示部       |    |

| 1 2 4 3   | 操作キー      |    |

| 1 2 5 1   | I C カード   |    |

| 1 2 5 2   | 表示部       |    |

| 1 2 5 3   | 接続端子      | 30 |

| 1 3 0 1   | 眼鏡本体      |    |

| 1 3 0 2 a | 左目用パネル    |    |

| 1 3 0 2 b | 右目用パネル    |    |

| 1 3 0 3   | ケーブル      |    |

| 1 3 1 1   | 表示装置      |    |

| 1 3 1 3   | タイミング発生器  |    |

| 1 3 1 6   | 表示制御回路    |    |

| 1 3 1 7   | 表示部       |    |

| 1 3 1 8   | ソース線側駆動回路 |    |

| 1 3 1 9   | ゲート線側駆動回路 |    |

| 1 3 2 2   | 外部操作手段    | 40 |

| 1 3 3 0 a | 同期信号      |    |

| 1 3 3 0 b | 同期信号      |    |

| 1 3 3 1 a | 同期信号      |    |

| 1 3 3 1 b | 同期信号      |    |

【図1】

【図2】

【図3】

【図4】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

【図 1 4】

【図 1 5】

## フロントページの続き

| (51) Int.Cl.            | F I          | テーマコード(参考) |

|-------------------------|--------------|------------|

| H 01 L 29/423 (2006.01) | H 01 L 29/78 | 6 2 7 D    |

| H 01 L 29/49 (2006.01)  | H 01 L 27/12 | B          |

| H 01 L 29/417 (2006.01) | H 01 L 29/78 | 6 2 6 C    |

| H 01 L 51/50 (2006.01)  | H 01 L 29/58 | G          |

| H 05 B 33/10 (2006.01)  | H 01 L 29/50 | M          |

| H 05 B 33/04 (2006.01)  | H 05 B 33/14 | A          |

| H 01 L 27/32 (2006.01)  | H 05 B 33/10 |            |

|                         | H 05 B 33/04 |            |

|                         | G 09 F 9/30  | 3 6 5 Z    |

F ターム(参考) 5C094 AA15 AA36 AA43 AA44 BA03 BA27 CA19 DA13 DB04 EA04

FA02 FB01 FB12 FB14 GB10 HA08 HA10 JA20

5F110 AA16 AA30 BB02 CC07 DD01 DD06 DD12 DD13 DD14 DD15

DD17 EE01 EE02 EE03 EE04 EE06 EE07 EE14 EE27 EE38

EE42 EE43 EE44 FF01 FF02 FF03 FF04 FF09 FF28 FF29

FF30 GG01 GG02 GG03 GG04 GG06 GG12 GG13 GG14 GG15

GG17 GG19 GG25 GG35 GG43 GG57 GG58 HK01 HK02 HK03

HK04 HK06 HK07 HL01 HL02 HL03 HL06 HL07 HL12 HL14

HM04 HM12 NN03 NN04 NN05 NN22 NN23 NN27 NN34 NN71

NN73 QQ08 QQ16

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 发光显示装置和制造发光显示装置的方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2012083733A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2012-04-26 |