(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-65176

(P2011-65176A)

(43) 公開日 平成23年3月31日(2011.3.31)

|                   |                  |                                    |

|-------------------|------------------|------------------------------------|

| (51) Int.CI.      | F 1              | テーマコード (参考)                        |

| <b>G09G 3/36</b>  | <b>(2006.01)</b> | <b>G09G 3/36</b> 2 H 1 9 3         |

| <b>G09G 3/20</b>  | <b>(2006.01)</b> | <b>G09G 3/20</b> 6 2 4 B 5 C 0 0 6 |

| <b>G02F 1/133</b> | <b>(2006.01)</b> | <b>G09G 3/20</b> 6 7 0 J 5 C 0 8 0 |

|                   |                  | <b>G09G 3/20</b> 6 7 0 K           |

|                   |                  | <b>G09G 3/20</b> 6 8 0 H           |

審査請求 有 請求項の数 18 O L (全 33 頁) 最終頁に続く

|              |                                     |          |                                              |

|--------------|-------------------------------------|----------|----------------------------------------------|

| (21) 出願番号    | 特願2010-247913 (P2010-247913)        | (71) 出願人 | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号 |

| (22) 出願日     | 平成22年11月4日 (2010.11.4)              | (74) 代理人 | 100101683<br>弁理士 奥田 誠司                       |

| (62) 分割の表示   | 特願2006-542442 (P2006-542442)<br>の分割 | (74) 代理人 | 100155000<br>弁理士 喜多 修市                       |

| 原出願日         | 平成17年11月4日 (2005.11.4)              | (74) 代理人 | 100139930<br>弁理士 山下 亮司                       |

| (31) 優先権主張番号 | 特願2004-322876 (P2004-322876)        | (74) 代理人 | 100125922<br>弁理士 三宅 章子                       |

| (32) 優先日     | 平成16年11月5日 (2004.11.5)              | (74) 代理人 | 100151817<br>弁理士 川口 寿志                       |

| (33) 優先権主張国  | 日本国 (JP)                            |          |                                              |

最終頁に続く

(54) 【発明の名称】 液晶表示装置およびその駆動方法

## (57) 【要約】

【課題】画素分割構造を有する液晶表示装置の信頼性を向上させる。

【解決手段】本発明の液晶表示装置は、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素を有し、画素は、供給された少なくとも1つの表示信号電圧に対して、第1輝度となる第1副画素と、第1輝度と異なる第2輝度となる第2副画素とを備える液晶表示パネル10と、トランジスタのソースに接続されたソースバスラインに表示信号電圧を供給するソース駆動回路40と、トランジスタのゲートに接続されたゲートバスラインに走査信号電圧を供給するゲート駆動回路30と、第1輝度が第2輝度よりも大きい第1モードと、第1輝度が第2輝度よりも小さい第2モードとの間のモード切替を行う輝度切替回路構成60とを備える。輝度切替回路構成は、83.5 msec以上の時間間隔においてモード切替を行う。

【選択図】図12

## 【特許請求の範囲】

## 【請求項 1】

液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素を有し、前記画素は、供給された少なくとも1つの表示信号電圧に対して、第1輝度となる第1副画素と、前記第1輝度と異なる第2輝度となる第2副画素とを備える液晶表示パネルと、

前記トランジスタのソースに接続されたソースバスラインに表示信号電圧を供給するソース駆動回路と、

前記トランジスタのゲートに接続されたゲートバスラインに走査信号電圧を供給するゲート駆動回路と、

前記第1輝度が前記第2輝度よりも大きい第1モードと、前記第1輝度が前記第2輝度よりも小さい第2モードとの間のモード切替を行う輝度切替回路構成とを備え、

前記輝度切替回路構成は、83.5 msec以上 の時間間隔をおいて前記モード切替を行う、液晶表示装置。

## 【請求項 2】

前記第1副画素および前記第2副画素のそれぞれは、対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、

前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量と、

前記補助容量対向電極に供給する電圧を発生する補助容量対向電圧発生回路とをさらに有し、

前記対向電極は、前記第1副画素および前記第2副画素に対して共通の単一の電極であり、前記補助容量対向電極は、前記第1副画素および前記第2副画素ごとに電気的に独立であり、

前記第1副画素および前記第2副画素のそれぞれに対応して設けられた2つのスイッチング素子を有し、

前記2つのスイッチング素子は、共通のゲートバスラインに供給される走査信号電圧によってオン／オフ制御され、前記2つのスイッチング素子がオン状態にあるときに、前記第1副画素および前記第2副画素のそれぞれが有する前記副画素電極および前記補助容量電極に、共通のソースバスラインから表示信号電圧が供給され、前記2つのスイッチング素子がオフ状態とされた後に、前記第1副画素および前記第2副画素のそれぞれの前記補助容量対向電極の電圧が変化し、その変化の方向および変化の大きさによって規定される変化量が前記第1副画素と前記第2副画素とで異なり、そのことによって前記第1輝度と前記第2輝度とが異なる、請求項1に記載の液晶表示装置。

## 【請求項 3】

前記輝度切替回路構成は、前記第1副画素および前記第2副画素のそれぞれの前記補助容量対向電極に印加する電圧の位相を反転させる回路を有する、請求項2に記載の液晶表示装置。

## 【請求項 4】

前記輝度切替回路構成は、前記第1副画素および前記第2副画素のそれぞれに供給する表示信号電圧の位相を反転させる回路を有する、請求項2に記載の液晶表示装置。

## 【請求項 5】

前記輝度切替回路構成は、前記モード切替を行った後の経過時間をカウントする回路を更に有し、所定の時間が経過するたびに、前記モード切替を行う、請求項1から4のいずれかに記載の液晶表示装置。

## 【請求項 6】

前記第1モードの動作時間と前記第2モードの動作時間を積算する回路を更に有し、

前記輝度切替回路構成は、前記第1モードの積算動作時間と前記第2モードの積算動作時間との差が所定の値を超えたときに、前記モード切替を行う、請求項1から5のいずれ

かに記載の液晶表示装置。

【請求項 7】

全画面の平均輝度を求める回路を更に有し、前記輝度切替回路構成は、前記平均輝度の値が所定の範囲内にあるときに、前記モード切替を行う、請求項 1 から 6 のいずれかに記載の液晶表示装置。

【請求項 8】

前記輝度切替回路構成は、操作者による所定の操作に応じて、前記モード切替を行う、請求項 1 から 7 のいずれかに記載の液晶表示装置。

【請求項 9】

前記モード切替は、前記第 1 モードと前記第 2 モードとをランダムに選択することによって行われる、請求項 1 から 8 のいずれかに記載の液晶表示装置。

【請求項 10】

前記第 1 副画素と前記第 2 副画素の面積は等しい、請求項 1 から 9 のいずれかに記載の液晶表示装置。

【請求項 11】

液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素とを有し、前記画素は、供給された少なくとも 1 つの表示信号電圧に対して、互いに異なる輝度で表示を行う 2 つの副画素を含む複数の副画素を備える液晶表示パネルと、

前記トランジスタのソースに接続されたソースバスラインに表示信号電圧を供給するソース駆動回路と、

前記トランジスタのゲートに接続されたゲートバスラインに走査信号電圧を供給するゲート駆動回路と、

前記複数の副画素のうち最も輝度が大きい副画素の画素内における位置が互いに異なる複数のモード間のモード切替を行う輝度切替回路構成と、

を備え、

前記輝度切替回路構成は、83.5 msec 以上の時間間隔をもいて前記モード切替を行う、液晶表示装置。

【請求項 12】

前記複数の副画素のそれぞれは、対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、

前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量と、

前記補助容量対向電極に供給する電圧を発生する補助容量対向電圧発生回路とをさらに有し、

前記対向電極は、前記複数の副画素に対して共通の単一の電極であり、前記補助容量対向電極は、前記複数の副画素ごとに電気的に独立であり、

前記複数の副画素のそれぞれに対応して設けられた複数のスイッチング素子を有し、

前記複数のスイッチング素子は、共通のゲートバスラインに供給される走査信号電圧によってオン／オフ制御され、前記複数のスイッチング素子がオン状態にあるときに、前記複数の副画素のそれぞれが有する前記副画素電極および前記補助容量電極に、共通のソースバスラインから表示信号電圧が供給され、前記複数のスイッチング素子がオフ状態とされた後に、前記複数の副画素のそれぞれの前記補助容量対向電極の電圧が変化し、その変化の方向および変化の大きさによって規定される変化量が前記 2 つの副画素とで異なり、そのことによって前記 2 つの副画素の輝度が互いに異なる、請求項 1 に記載の液晶表示装置。

【請求項 13】

前記複数の副画素のうち最高輝度となる副画素と最低輝度となる副画素の面積は互いに等しい、請求項 1 1 または 1 2 に記載の液晶表示装置。

【請求項 14】

10

20

30

40

50

前記複数の副画素のそれぞれの面積は等しい、請求項 1 1 から 1 3 のいずれかに記載の液晶表示装置。

【請求項 1 5】

液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素を有し、前記画素は、供給された少なくとも 1 つの表示信号電圧に対して、第 1 輝度となる第 1 副画素と、前記第 1 輝度と異なる第 2 輝度となる第 2 副画素とを備える液晶表示パネルの駆動方法であって、

前記第 1 輝度が前記第 2 輝度よりも大きい第 1 モードと、前記第 1 輝度が前記第 2 輝度よりも小さい第 2 モードとの間のモード切替を行う工程を包含し、

前記モード切替を 83.5 msec 以上の時間間隔をおいて行う、駆動方法。

10

【請求項 1 6】

前記モード切替は、前記第 1 モードと前記第 2 モードとをランダムに選択することによって行われる、請求項 1 5 に記載の駆動方法。

【請求項 1 7】

液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素とを有し、前記画素は、供給された少なくとも 1 つの表示信号電圧に対して、互いに異なる輝度で表示を行う 2 つの副画素を含む複数の副画素を備える液晶表示パネルの駆動方法であって、

前記複数の副画素のうち最も輝度が大きい副画素の画素内における位置が互いに異なる複数のモード間のモード切替を行う工程を包含し、

前記モード切替を 83.5 msec 以上の時間間隔をおいて行う、駆動方法。

20

【請求項 1 8】

前記モード切替は、前記複数のモードをランダムに選択することによって行われる、請求項 1 7 に記載の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置およびその駆動方法に関する。

【背景技術】

【0002】

従来、TN モードの液晶表示装置が使用されていたが、TN モードよりも視角特性の優れたVA モードやIPS モードの液晶表示装置の利用が広がっている。近年、さらに視野角特性を改善したMVA モードやS-IPS モードの液晶表示装置が、TV やモニターに使用されている。

30

【0003】

VA モードはIPS モードに比べて、黒表示の品位が高いため、高コントラスト比の表示を実現できるという利点を有している。しかしながら、特性の視角依存性がIPS モードよりも大きいという欠点を有している。

【0004】

そこで、特許文献 1 には、各画素を複数の副画素に分割し、副画素ごとに異なる電圧を供給することによって、特性における視角依存性を平均化する方法が提案されている。上記特許文献 1 に記載されている液晶表示装置は、画素が有する複数の副画素のそれぞれに表示信号電圧が独立に供給される構成を有している。すなわち、画素が 2 つの副画素（第 1 副画素および第 2 副画素）を有する場合、第 1 副画素に表示信号電圧を供給するソースバスラインと別に第 2 副画素に表示信号電圧を供給するソースバスラインを設ける必要がある。従って、画素を 2 分割すると、ソースバスラインおよびソース駆動回路の数が 2 倍になる。また、第 1 副画素と第 2 副画素との供給する互いに異なる表示信号電圧は、表示すべきデータごとに 2 つずつ予め決められており、ルックアップテーブルに格納されている。

40

【0005】

50

これに対し、特許文献 2 や特許文献 3 には、供給された少なくとも 1 つの表示信号電圧に対して、互いに異なる輝度となる複数の副画素を備える液晶表示装置が記載されている。この液晶表示装置においては、第 1 副画素と第 2 副画素とに共通のソースバスラインから共通の表示信号電圧が供給されるので、ソースバスラインやソース駆動回路の数を分割数に応じて増加させる必要が無いという利点を有している。

【先行技術文献】

【特許文献】

【0006】

【特許文献 1】特開 2003-295160 号公報

10

【特許文献 2】特開 2004-62146 号公報

【特許文献 3】特開 2004-78157 号公報

【特許文献 4】特開平 6-332009 号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、本発明者が特許文献 2 および 3 に記載されている液晶表示装置を試作し評価したところ、十分な信頼性が得られないことがあり、この信頼性の低下は、液晶層に DC 電圧が印加されることに起因することが分かった。

【0008】

一般に、液晶表示装置は、表示モードに拘らず、液晶層に DC 電圧が印加されるのを防止するために、交流駆動される。すなわち、液晶層に生成される電界の向きを一定時間ごとに反転させることによって、時間平均したときに一定方向の電界 (DC 電圧) が残らないように駆動される。アクティブマトリクス型液晶表示装置の各画素の液晶層に印加される電圧は、対向電極に供給される共通電圧 (Vcom) と画素電極に供給される表示信号電圧との差に相当するので、交流駆動においては、対向電極に供給される共通電圧を基準としたときの表示信号電圧の極性を一定時間ごとに反転させていることになる。表示信号電圧の極性を反転させる周期は、例えば一垂直走査期間 (典型的には入力画像信号の 1 フレーム期間) である。

20

【0009】

トランジスタを用いるアクティブマトリクス型液晶表示装置では、トランジスタが非導通状態となった直後に、ゲートとドレインとの間の寄生容量 (Cgd) 等の影響による「引き込み電圧 (ドレイン引き込み電圧)」と呼ばれる電圧が液晶層に印加される。引き込み電圧は、液晶容量 (副画素電極 / 液晶層 / 対向電極によって構成される容量、画素容量は液晶容量と補助容量とで構成される。) の大きさに依存し、液晶容量は電圧に依存する。したがって、引き込み電圧による DC 電圧の発生を防止するためには、表示すべきデータ (画像データ、入力画像信号) ごとに、引き込み電圧をキャンセルするように表示信号電圧が設定される。

30

【0010】

しかしながら、上記特許文献 2 や特許文献 3 に記載されているような、供給された 1 つの表示信号電圧に対して、互いに異なる輝度となる複数の副画素を備える液晶表示装置においては、副画素毎に供給する印加電圧を調節することができないので、引き込み電圧による DC の発生を防止することができず、十分な信頼性が得られないことがある。

40

【0011】

本発明は上記課題を解決するためになされたものであり、その主な目的は、画素分割構造を有する液晶表示装置の信頼性を向上させることにある。

【課題を解決するための手段】

【0012】

本発明の液晶表示装置は、液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素を有し、前記画素は、供給された少なくとも 1 つの表示信号電圧に対して、第 1 輝度となる第 1 副画素と、

50

前記第1輝度と異なる第2輝度となる第2副画素とを備える液晶表示パネルと、前記トランジスタのソースに接続されたソースバスラインに表示信号電圧を供給するソース駆動回路と、前記トランジスタのゲートに接続されたゲートバスラインに走査信号電圧を供給するゲート駆動回路と、前記第1輝度が前記第2輝度よりも大きい第1モードと、前記第1輝度が前記第2輝度よりも小さい第2モードとの間のモード切替を行う輝度切替回路構成とを備えることを特徴とする。

【0013】

なお、ここで用いた「第1輝度」および「第2輝度」は固定された輝度レベルを指すのではなく、それぞれ副画素を特定するために用いている。すなわちある表示状態（あるフレーム）において、第1輝度で表示している副画素を第1副画素（例えば後述するSP1）とし、第1輝度と異なる第2輝度で表示している副画素を第2副画素（例えばSP2）とする。輝度が異なる2つの副画素のいずれを第1副画素としてもよい。このようにして決められた第1副画素および第2副画素は、第1輝度が第2輝度よりも大きい（第1副画素が第2副画素よりも明るい）第1モードと、第1輝度が第2輝度よりも小さい（第1副画素が第2副画素よりも暗い）第2モードとの間で切り替えられる。

10

【0014】

前記モード切替は、前記第1モードと前記第2モードとをランダムに選択することによって行われてもよいし、前記第1モードから前記第2モードへ、または、前記第2モードから前記第1モードへ強制的に切替ることによって行われてもよい。また、輝度切替回路構成は、輝度切替のための輝度切替回路を附加的に設けることによって構成しても良いし、既存の回路（例えば、ソース駆動回路、補助容量電圧発生回路）および／またはこれらの組み合わせによって構成してもよい。

20

【0015】

ある実施形態において、前記第1副画素および前記第2副画素のそれぞれは、対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量と、前記補助容量対向電極に供給する電圧を発生する補助容量対向電圧発生回路とを更に有し、前記対向電極は、前記第1副画素および前記第2副画素に対して共通の単一の電極であり、前記補助容量対向電極は、前記第1副画素および前記第2副画素ごとに電気的に独立であり、前記第1副画素および前記第2副画素のそれぞれに対応して設けられた2つのスイッチング素子を有し、前記2つのスイッチング素子は、共通のゲートバスラインに供給される走査信号電圧によってオン／オフ制御され、前記2つのスイッチング素子がオン状態にあるときに、前記第1副画素および前記第2副画素のそれぞれが有する前記副画素電極および前記補助容量電極に、共通のソースバスラインから表示信号電圧が供給され、前記2つのスイッチング素子がオフ状態とされた後に、前記第1副画素および前記第2副画素のそれぞれの前記補助容量対向電極の電圧が変化し、その変化の方向および変化の大きさによって規定される変化量が前記第1副画素と前記第2副画素とで異なり、そのことによって前記第1輝度と前記第2輝度とが異なる。

30

【0016】

ある実施形態において、前記輝度切替回路構成は、前記第1副画素および前記第2副画素のそれぞれの前記補助容量対向電極に印加する電圧の位相を反転させる回路を有する。

40

【0017】

ある実施形態において、前記輝度切替回路構成は、前記第1副画素および前記第2副画素のそれぞれに供給する表示信号電圧の位相を反転させる回路を有する。

【0018】

ある実施形態において、前記輝度切替回路構成は、入力画像信号の2フレーム以上の時間間隔をもつて前記モード切替を行う。

【0019】

ある実施形態において、前記輝度切替回路構成は、前記モード切替を行った後の経過時

50

間をカウントする回路を更に有し、所定の時間が経過するたびに、前記モード切替を行う。

【0020】

ある実施形態において、前記第1モードの動作時間と前記第2モードの動作時間を積算する回路を更に有し、前記輝度切替回路構成は、前記第1モードの積算動作時間と前記第2モードの積算動作時間との差が所定の値を超えたときに、前記モード切替を行う。

【0021】

ある実施形態において、前記輝度切替回路構成は、前記第1輝度と前記第2輝度との差が所定の値を超えたときに、前記モード切替を行う。

【0022】

ある実施形態において、全画面の平均輝度を求める回路を更に有し、前記輝度切替回路構成は、前記平均輝度の値が所定の範囲内にあるときに、前記モード切替を行う。

【0023】

ある実施形態において、前記所定の範囲内は、前記第1輝度と前記第2輝度の差／前記第1輝度と前記第2輝度との平均輝度の値が最大値の90%以下である階調に相当する。

【0024】

ある実施形態において、前記輝度切替回路構成は、操作者による所定の操作に応じて、前記モード切替を行う。

【0025】

ある実施形態において、前記輝度切替回路構成は、入力画像信号に所定の変化が生じた場合に、前記モード切替を行う。

【0026】

ある実施形態において、前記輝度切替回路構成は、所定の条件が満足されたときに、輝度切替信号を発生する輝度切替信号発生回路を更に有し、前記輝度切替回路構成は、前記輝度切替信号に応じて前記モード切替を行う。

【0027】

ある実施形態において、前記輝度切替信号発生回路は、異なる条件に応じてそれぞれトリガー信号を発生する複数のトリガー信号発生回路と、前記複数のトリガー発生回路から出力された前記複数のトリガー信号に基づいて、前記輝度切替信号を発生する信号発生回路とを備える。

【0028】

ある実施形態において、前記第1副画素と前記第2副画素の面積は略等しい。

【0029】

ある実施形態において、前記画素は、第3副画素をさらに有する。前記第3副画素は、第1副画素または第2副画素と同じ輝度であってもよいし、異なってもよい。

【0030】

本発明の他の液晶表示装置は、液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素とを有し、前記画素は、供給された少なくとも1つの表示信号電圧に対して、互いに異なる輝度で表示を行う2つの副画素を含む複数の副画素を備える液晶表示パネルと、前記トランジスタのソースに接続されたソースバスラインに表示信号電圧を供給するソース駆動回路と、前記トランジスタのゲートに接続されたゲートバスラインに走査信号電圧を供給するゲート駆動回路と、前記複数の副画素のうち最も輝度が大きい副画素の画素内における位置が互いに異なる複数のモード間のモード切替を行う輝度切替回路構成とを備えることを特徴とする。

【0031】

ある実施形態において、前記複数の副画素のそれぞれは、対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量と、前記補助容量対向電極

10

20

30

40

50

に供給する電圧を発生する補助容量対向電圧発生回路とをさらに有し、前記対向電極は、前記複数の副画素に対して共通の单一の電極であり、前記補助容量対向電極は、前記複数の副画素ごとに電気的に独立であり、前記複数の副画素のそれぞれに対応して設けられた複数のスイッチング素子を有し、前記複数のスイッチング素子は、共通のゲートバスラインに供給される走査信号電圧によってオン／オフ制御され、前記複数のスイッチング素子がオン状態にあるときに、前記複数の副画素のそれぞれが有する前記副画素電極および前記補助容量電極に、共通のソースバスラインから表示信号電圧が供給され、前記複数のスイッチング素子がオフ状態とされた後に、前記複数の副画素のそれぞれの前記補助容量対向電極の電圧が変化し、その変化の方向および変化の大きさによって規定される変化量が前記2つの副画素とで異なり、そのことによって前記2つの副画素の輝度が互いに異なる構成を有する。

10

## 【0032】

ある実施形態において、前記複数の副画素のうち最高輝度となる副画素と最低輝度となる副画素の面積は互いに略等しい。

## 【0033】

ある実施形態において、前記複数の副画素のそれぞれの面積は略等しい。

## 【0034】

本発明の液晶表示装置の駆動方法は、液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素を有し、前記画素は、供給された少なくとも1つの表示信号電圧に対して、第1輝度となる第1副画素と、前記第1輝度と異なる第2輝度となる第2副画素とを備える液晶表示パネルの駆動方法であって、前記第1輝度が前記第2輝度よりも大きい第1モードと、前記第1輝度が前記第2輝度よりも小さい第2モードとの間のモード切替を行う工程を包含することを特徴とする。

20

## 【0035】

本発明の他の液晶表示装置の駆動方法は、液晶層と、前記液晶層に電圧を印加する複数の電極と、トランジスタを介して供給される表示信号電圧に応じて輝度が変化する画素とを有し、前記画素は、供給された少なくとも1つの表示信号電圧に対して、互いに異なる輝度で表示を行う2つの副画素を含む複数の副画素を備える液晶表示パネルの駆動方法であって、前記複数の副画素のうち最も輝度が大きい副画素の画素内における位置が互いに異なる複数のモード間のモード切替を行う工程を包含することを特徴とする。

30

## 【0036】

前記モード切替を入力画像信号の2フレーム以上の時間間隔をおいて行なうことが好ましい。

## 【0037】

ある実施形態において、前記モード切替は、前記第1モードと前記第2モードとをランダムに選択することによって行われる。

## 【0038】

ある実施形態において、前記モード切替は、前記第1モードから前記第2モードへ、または、前記第2モードから前記第1モードへ強制的に切替ることによって行われる。

40

## 【発明の効果】

## 【0039】

本発明の液晶表示装置は、その画素が、互いに異なる輝度となる2つの副画素（明副画素および暗副画素）を備え、それによって特性の視角依存性を改善する。画素分割の方法には種々のものがあるが、例えば特許文献2または3に記載されている方法を採用すると、供給された少なくとも1つの表示信号電圧に対して互いに異なる輝度となる2つの副画素を比較的簡単な構成で得ることができる。さらに、2つの副画素の輝度の関係を反対にするモード切替を行うので、副画素に発生するDC電圧が平均化される。従って、副画素電極に供給する表示信号電圧（および対向電圧）を調整することにより、副画素に発生するDC電圧が平均化によって殆ど零となるようにすることが可能となり、液晶表示装置

50

の信頼性が向上する。

【0040】

副画素間の輝度関係を変更するモード切替動作は、副画素に発生するDC電圧を平均化するためのものであり、典型的には数十分から数時間以上の間隔で切替動作を行えばよく、どんなに短くとも2垂直走査期間以上に設定され、液晶の応答時間よりも長く設定されることが好ましい。ここで応答時間とは、画素の液晶層に所定の電圧が供給されてから、当該画素が供給された電圧に対応する輝度に到達するまでの時間を指し、典型的には数ミリ秒から数十ミリ秒である。

【0041】

なお、特許文献1にも、輝度の異なる副画素を切替えることが好ましい旨記載されているが、これはフリッカを防止するためである。1フレーム期間内で入れ替えることが好ましいと記載されているように、人間の視覚の時間分解能に対して十分に速く切替る必要があり、2フレーム以上の間隔で切替えるとフリッカを防止する効果は得られない。

10

【図面の簡単な説明】

【0042】

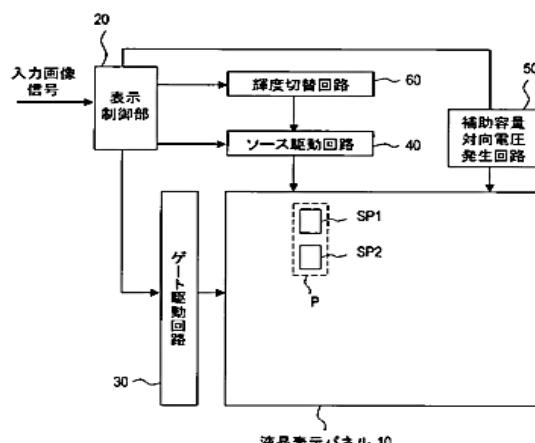

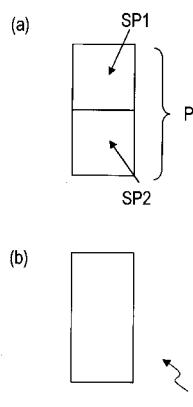

【図1】(a)は、本発明による実施形態の液晶表示装置が有する画素分割構造を示す模式図であり、(b)は通常の画素を示す模式図である。

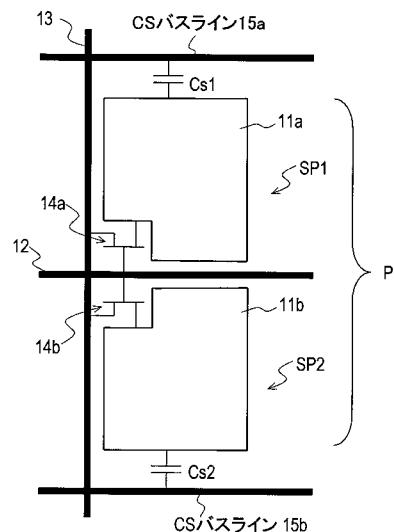

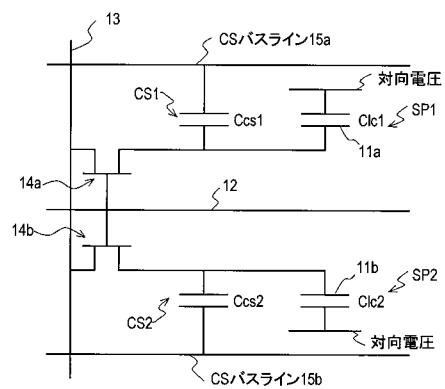

【図2】本発明による実施形態の液晶表示装置が有する画素の電気的な構成を模式的に示す図である。

20

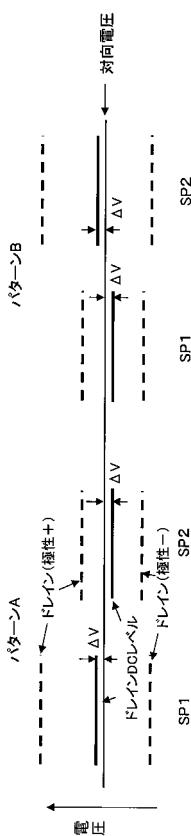

【図3】画素分割構造において、副画素の液晶層にDC成分が印加される現象を説明するための図である。

【図4】画素分割構造を有する従来の液晶表示装置における表示状態(動作状態)を示す図である。

20

【図5】本発明による実施形態の液晶表示装置における表示状態(動作状態)を示す図である。

【図6】本発明による実施形態の液晶表示装置において、副画素の液晶層に印加されるDC成分が低減される原理を説明するための図であり、各副画素のドレインの電圧レベルと対向電極の電圧レベルを示す図である。

【図7】本発明による他の実施形態の液晶表示装置において、副画素の液晶層に印加されるDC成分が低減される原理を説明するための図であり、各副画素のドレインの電圧レベルと対向電極の電圧レベルを示す図である。

30

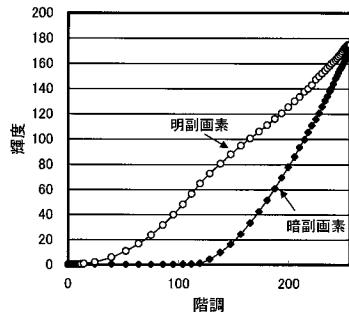

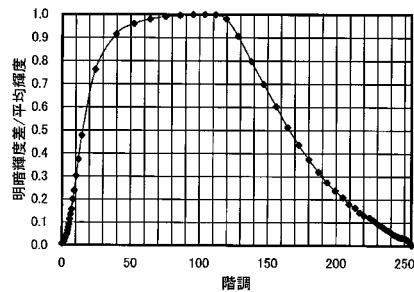

【図8】本発明による実施形態のMVAモード液晶表示装置における副画素の間の輝度差の階調依存性を示すグラフである。

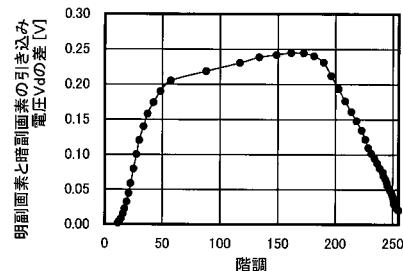

【図9】本発明による実施形態のMVAモード液晶表示装置における副画素間のドレイン引き込み電圧Vdの差の階調依存性を示すグラフである。

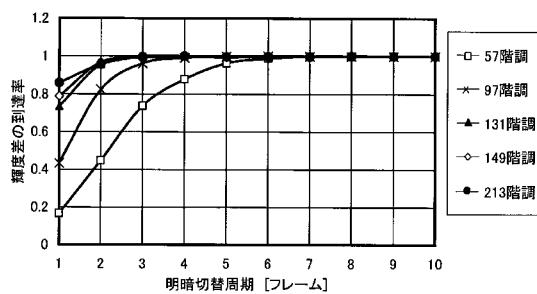

【図10】本発明による実施形態のMVAモード液晶表示装置における明暗のモード切替周期に対する各表示階調における明副画素と暗副画素の輝度差の到達率の変化を示すグラフである。

【図11】本発明による実施形態のMVAモード液晶表示装置における副画素間の輝度差を平均輝度で除した値(F値)の階調依存性を示すグラフである。

40

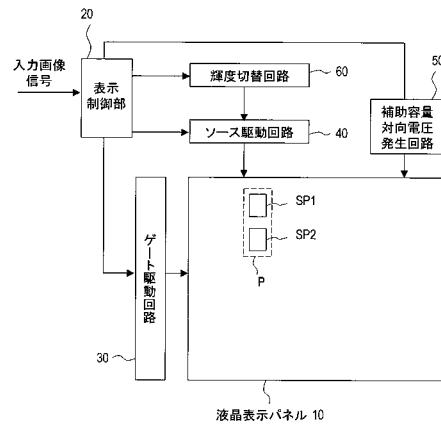

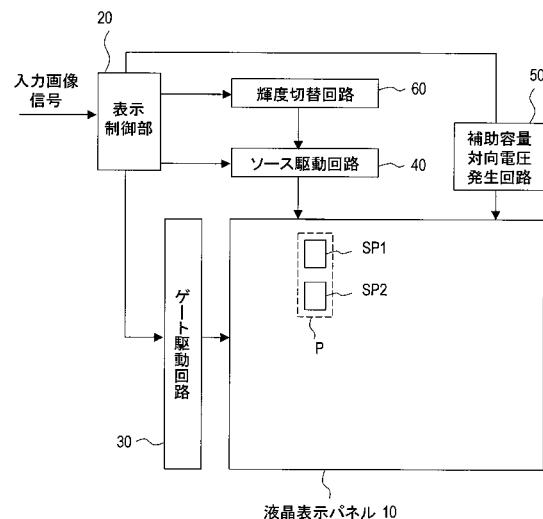

【図12】本発明による実施形態の液晶表示装置の回路構成を示す模式図である。

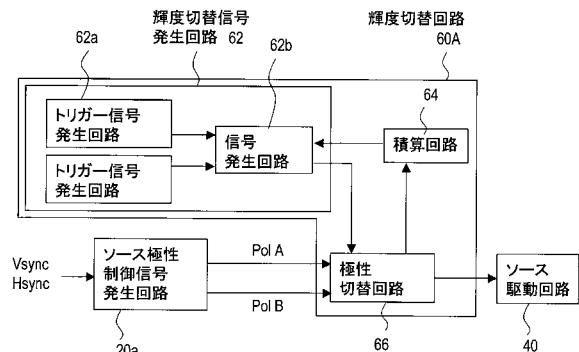

【図13】図12に示した液晶表示装置の輝度切替回路60として好適に用いられる輝度切替回路60Aの構成を示す模式図である。

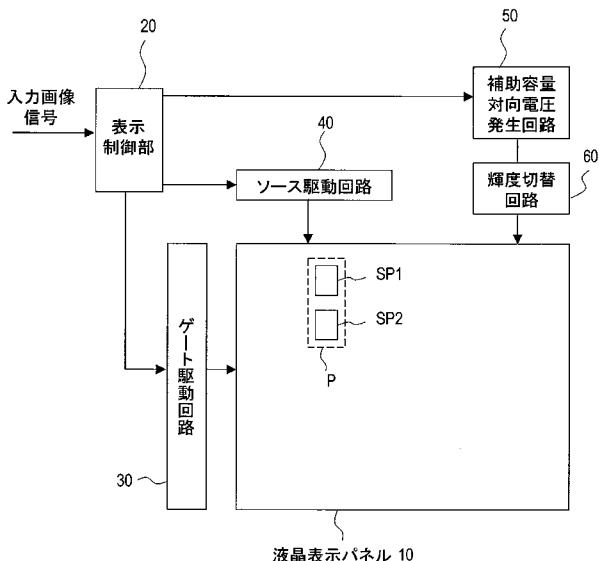

【図14】本発明による他の実施形態の液晶表示装置の回路構成を示す模式図である。

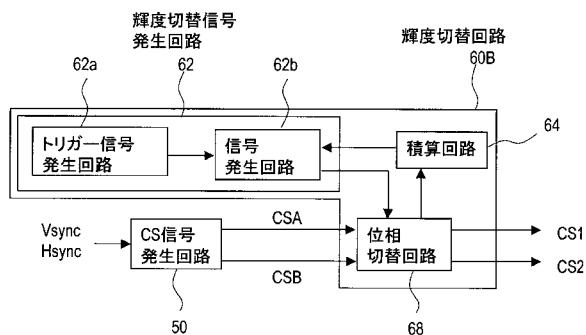

【図15A】図14に示した液晶表示装置の輝度切替回路60として好適に用いられる輝度切替回路60Bの構成を示す模式図である。

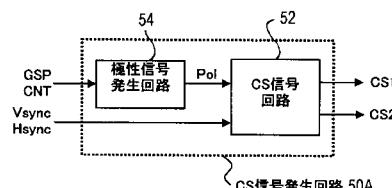

【図15B】図14に示した液晶表示装置の輝度切替回路60の機能を含む、CS信号発生回路50Aの構成を示す模式図である。

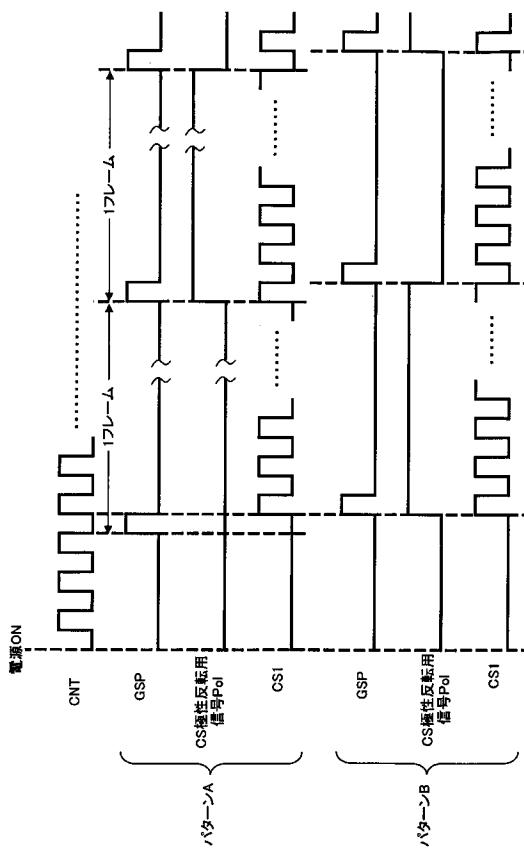

【図15C】図15Bに示したCS信号発生回路50Aの動作を説明するための各信号の電圧波形を示す図である。

50

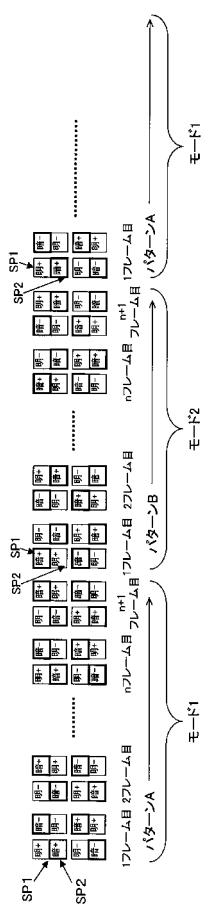

【図16】本発明による実施形態1の液晶表示装置における表示状態（動作状態）を示す図である。

【図17】本発明による実施形態1の液晶表示装置の等価回路を示す図である。

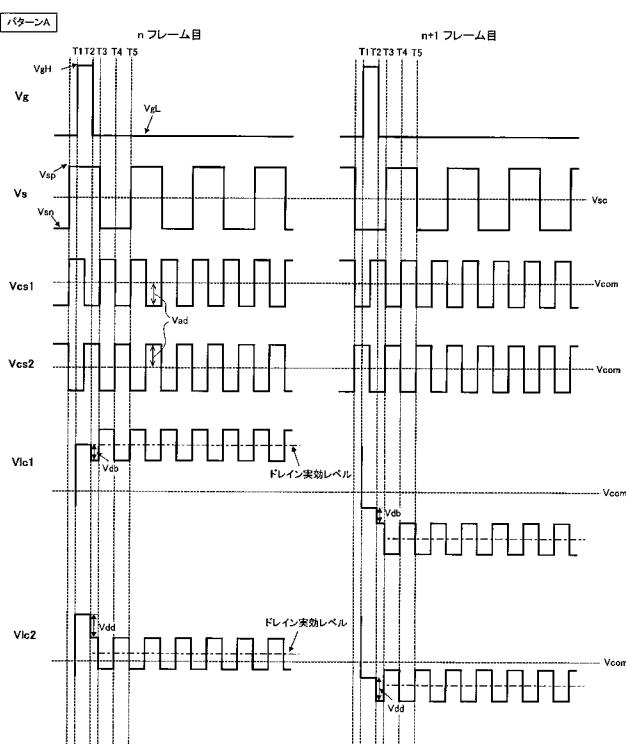

【図18】図17に示した液晶表示装置を駆動する各信号の電圧波形およびタイミングを示す図である（パターンA）。

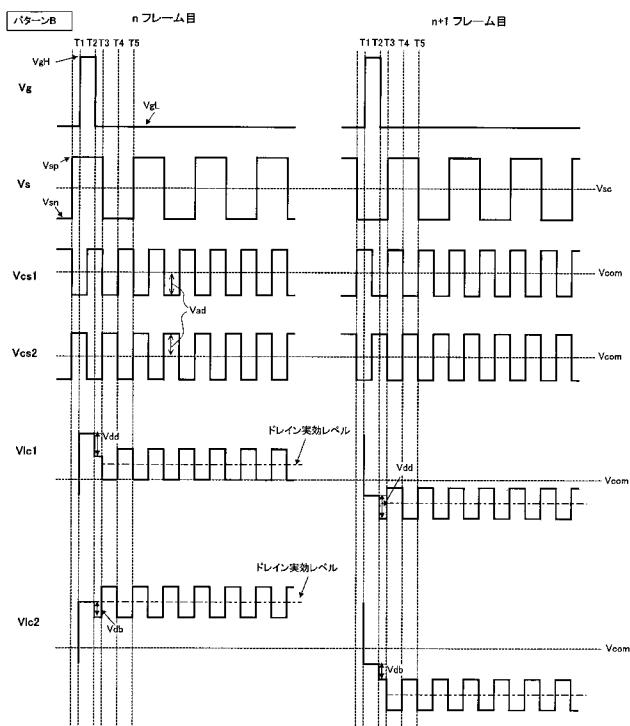

【図19】図17に示した液晶表示装置を駆動する各信号の電圧波形およびタイミングを示す図である（パターンB）。

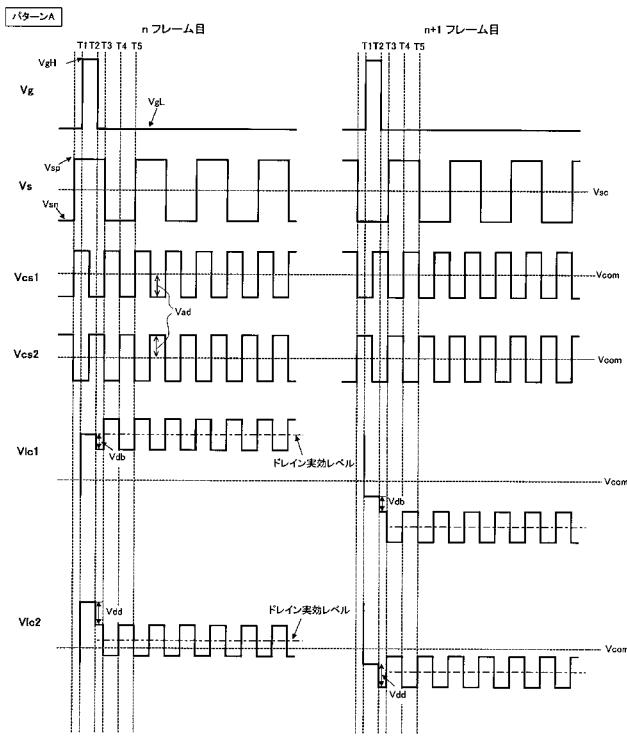

【図20】本発明による実施形態2の液晶表示装置を駆動する各信号の電圧波形およびタイミングを示す図である（パターンA）。 10

【図21】本発明による実施形態2の液晶表示装置を駆動する各信号の電圧波形およびタイミングを示す図である（パターンB）。

【図22】本発明による実施形態3の液晶表示装置の画素分割構造を示す模式図である。

【図23】本発明による実施形態3の液晶表示装置の等価回路を示す図である。

【図24】本発明による実施形態3の液晶表示装置に用いられる輝度切替回路60Cの構成を示す模式図である。

【図25】本発明による実施形態3の液晶表示装置における表示状態（動作状態）を示す図である。

【図26】本発明による実施形態3の液晶表示装置における各副画素のドレインの電圧レベルと対向電極の電圧レベルを示す図である。

【図27】本発明による実施形態3の他の液晶表示装置における各副画素のドレインの電圧レベルと対向電極の電圧レベルを示す図である。 20

#### 【発明を実施するための形態】

##### 【0043】

以下、図面を参照しながら、本発明による実施形態の液晶表示装置およびその駆動方法を説明する。ここでは、画素を2つの副画素に分割した構成を例示し、本発明の実施形態を説明するが、本発明はこれに限られず、分割数（各画素の副画素の数）は3以上であつてもよい。

##### 【0044】

本発明による実施形態の液晶表示装置は、図1(a)に模式的に示すように画素分割構造を有する。すなわち、図1(b)に示す1つの画素Pが2つの副画素SP1およびSP2に分割されており、それぞれの副画素SP1およびSP2に異なる電圧を供給できるように構成されている。副画素SP1およびSP2に供給する電圧を異ならせ、各副画素に異なる特性を持たせることにより、特性の視角依存性を改善する。 30

##### 【0045】

互いに異なる電圧を供給することができる2つの副画素を設けるために、単純に画素数を2倍した構成としても良いが、それではコストが高くなるので、種々の構成が提案されているが、本実施形態では、特許文献2に記載されている構成を採用する。これに対し、例えば、特許文献4に記載されているように、一方の副画素の液晶容量に直列に接続された付加的な容量を設け、副画素間で容量分割される電圧の内、一方の液晶容量に印加される電圧を低下させる構成を採用すると、2つの副画素間の輝度の関係は固定され、輝度の関係を反対にすることはできない。 40

##### 【0046】

図2に本発明の実施形態の液晶表示装置が有する画素の電気的な構成を模式的に示す。

##### 【0047】

図2に示すように、画素Pは、副画素SP1と副画素SP2とに分割されている。副画素SP1およびSP2を構成する副画素電極11aおよび11bには、それぞれ対応するTFT14a、TFT14b、および補助容量CS1、CS2が接続されている。TFT14aおよびTFT14bのゲート電極は共通のゲートバスライン（走査線）12に接続され、TFT14aおよびTFT14bのソース電極は共通の（同一の）ソースバスライン（信号線）13に接続されている。補助容量CS1およびCS2は、それぞれ対応する 50

C S バスライン（補助容量配線）15a および C S バスライン 15b に接続されている。補助容量 C S 1 および C S 2 は、それぞれ副画素電極 11a および 11b に電気的に接続された補助容量電極と、C S バスライン 15a および 15b に電気的に接続された補助容量対向電極と、これらの間に設けられた絶縁層（不図示、例えばゲート絶縁膜）によって形成されている。補助容量 C S 1 および C S 2 の補助容量対向電極は互いに独立しており、それぞれ C S バスライン 15a および 15b から互いに異なる補助容量対向電圧（「C S 信号」ともいう。）が供給され得る構造を有している。

#### 【0048】

副画素電極 11a および副画素電極 11b に、共通のソースバスライン 13 から表示信号電圧が供給され、TFT14a および TFT14b がオフ状態とされたあと、補助容量 C S 1 および C S 2 の補助容量対向電極の電圧（すなわち、C S バスライン 15a または C S バスライン 15b から供給される電圧）の変化量（変化の方向および大きさによって規定される）を異ならせることによって、それぞれの副画素 S P 1 および S P 2 の液晶容量に印加される実効電圧が異なる状態、すなわち、輝度が異なる状態が得られる。この構成を採用すると、1本のソースバスライン 13 から 2つの副画素 S P 1 および S P 2 に表示信号電圧を供給することができるので、ソースバスラインの数およびソースドライバの数を増加することなく、副画素 S P 1 および S P 2 の輝度を互いに異ならせることができる。例えば、副画素 S P 1 は供給されたある表示信号電圧について副画素 S P 2 よりも大きい輝度で表示する。ここで、副画素 S P 1 は全ての表示信号電圧（階調表示信号）に対して副画素 S P 2 よりも大きい輝度で表示する必要はなく、少なくとも 1つの中間調の表示信号電圧に対して大きい輝度で表示すればよい。典型的には、黒（最低階調）および白（最高階調）を除く全ての中間調において、副画素 S P 1 は副画素 S P 2 よりも大きい輝度で表示を行う。

10

20

30

40

50

#### 【0049】

しかしながら、このような画素分割構成を採用すると、副画素ごとに独立に表示信号電圧を調整することが出来ないため、複数の副画素のそれぞれについて引き込み電圧 V d をキャンセルすることができず、DC 電圧が印加されるという問題が発生する。

#### 【0050】

ここで、この現象を少し詳しく説明する。

#### 【0051】

引き込み電圧 V d は下の（1）式のようになる。ここで、V g H と V g L はそれぞれ TFT のゲートオンとゲートオフ時の電圧、C g d は TFT のゲートとドレインとの間に生じる寄生容量、C l c (V) は液晶容量の静電容量（容量値）、C c s は補助容量の静電容量（容量値）を示す。なお、液晶容量の静電容量 C l c は液晶層に印加する電圧の大きさに依存する。これは誘電率異方性を有する液晶分子の配向方向が電圧によって変化するためであり、表示する輝度によって液晶容量の静電容量は異なることになる。

#### 【0052】

$$V d = (V g H - V g L) \times C g d / (C l c (V) + C g d + C c s) \quad \dots (1)$$

#### 【0053】

式（1）からわかるように、引き込み電圧 V d は、液晶容量の静電容量に依存する、すなわち、表示する輝度（階調）に依存する。

#### 【0054】

V d が階調によって異なるため、ドレイン電圧の DC レベル（交流駆動する場合の副画素電極の電位の中央値であり、ドレイン電圧の実効レベルともいう。）も階調によって異なる。従って、全ての階調に対して対向電圧のレベルを一定にすると、液晶層に DC 成分が印加される階調が生じることになる。これを防ぐために、従来から、階調に応じて表示信号電圧（ソース電圧またはドレイン電圧）の中央値（それぞれの階調で交流駆動する場合の副画素電極の電位の中央値）をその階調の V d を補償するように設定し、ドレイン電圧の DC レベルと対向電圧とを略一致させ、液晶層に DC 成分が印加されないようにして

いるのである。

【0055】

しかしながら、特許文献2または特許文献3に記載されているような画素分割技術を採用すると、図3に示すように、副画素SP1（ここでは明副画素）と副画素SP2（ここでは暗副画素）とでVdが異なるために、副画素SP1のドレイン電圧のDCレベルを対向電圧と一致させると、副画素SP2のドレイン電圧のDCレベルは対向電圧と一致せず、副画素SP2の液晶層にDC成分が印加されることになる。

【0056】

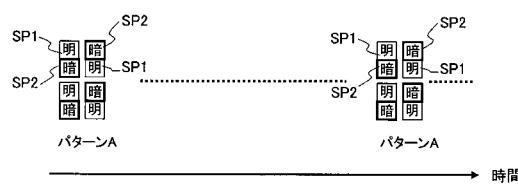

また、上記画素分割技術では、副画素間の輝度の順序は、予め決められた順序で一定しており、例えば、図4に示すように、副画素SP1が明副画素で、副画素SP2が暗副画素のパターン（以下、「パターンA」という。）が、液晶表示装置を動作させる限り常に全表示期間に亘って維持されるため、少なくとも一方の副画素の液晶層（および配向膜）にDC成分が印加され、分極を生じる。その結果として、液晶表示装置の信頼性に問題が生じる。

【0057】

なお、図4に示した例では、ちらつき（フリッカ）を視認し難くするために、明るい副画素SP1同士および暗い副画素SP2同士が行方向および列方向において隣接しないように、副画素SP1およびSP2を市松模様状に配列している。

【0058】

本発明による実施形態の液晶表示装置は、画素分割された液晶表示装置において、明副画素と暗副画素とを入れ換えることによって、各副画素の液晶層にDC成分が継続的に印加されることを抑制・防止する。

【0059】

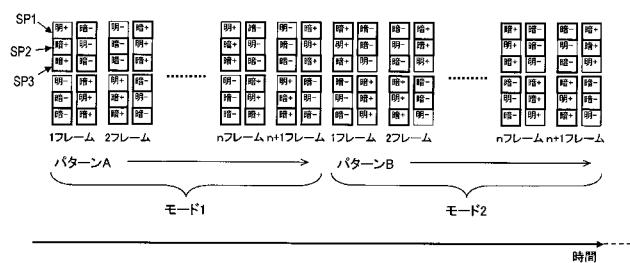

本発明による実施形態の液晶表示装置では、図5に示すように、副画素SP1が明副画素で副画素SP2が暗副画素のパターンAで表示するモード1と、副画素SP1が暗副画素で副画素SP2が明副画素のパターンBで表示するモード2とを切替えることによって、副画素SP1またはSP2の液晶層に印加されるDC成分を低減する。すなわち、副画素SP1（第1輝度）が明るい表示を行い、副画素SP2（第2輝度）が暗い（第2輝度<第1輝度）表示を行うのがパターンAであり、副画素SP1（第1輝度）が暗い表示を行い、副画素SP2（第2輝度）が明るい（第2輝度>第1輝度）表示を行うのがパターンBであり、副画素SP1と副画素SP2との間の輝度関係を逆にすることによって、DC成分を低減する。すなわち、本発明による実施形態の液晶表示装置は、第1輝度が第2輝度よりも大きい第1モードと、第1輝度が第2輝度よりも小さい第2モードとの間のモード切替を行う輝度切替回路構成を備えている。

【0060】

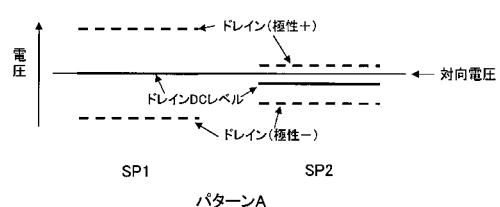

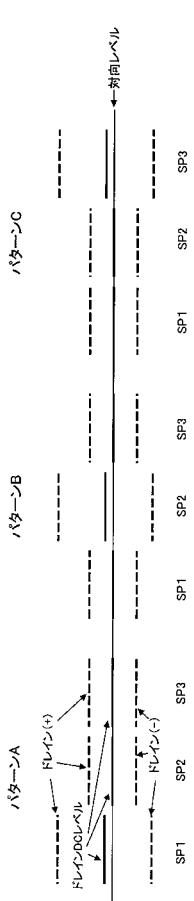

パターンAとパターンBにおける各副画素のドレイン電圧のDCレベルと対向電圧（「対向レベル」ともいう）を図6に示す。図6には、明副画素のドレイン電圧のDCレベルを対向電圧と一致させた場合を示している。

【0061】

図6に示すように、パターンAにおいては、明副画素である副画素SP1のドレイン電圧のDCレベルが対向レベルと一致しているので、暗副画素である副画素SP2のドレイン電圧のDCレベルはドレイン引き込み量の差の分、対向レベルとズレが生じ、副画素SP2の液晶層にDC成分が印加される。一方、パターンBにおいては、副画素SP2が明副画素となるため、暗副画素である副画素SP1の液晶層にDC成分が印加されることになる。

【0062】

このパターンAで表示を行うモード1とパターンBで表示を行うモード2との間でモード切替えを行うと、DC成分が副画素SP1およびSP2の内のどちらか一方の副画素に継続してDC成分が印加されることが無く、DC成分が副画素SP1およびSP2の間で平均化され、その結果、液晶表示装置の信頼性を向上することができる。なお、ドレイン

10

20

30

40

50

電圧の D C レベルと対向レベルとの相対関係の設定（対向レベルの設定ということもある）は、ドレンイン電圧として副画素電極に印加される表示信号電圧および対向電圧を設定することによって行われる。

【 0 0 6 3 】

図 6 に示した例では、対向電極の電圧レベルと明副画素のドレンイン電圧の D C レベルとを一致させた例を示したが、対向レベルと暗副画素のドレンイン電圧の D C レベルとを一致させても同様の効果が得られる。

【 0 0 6 4 】

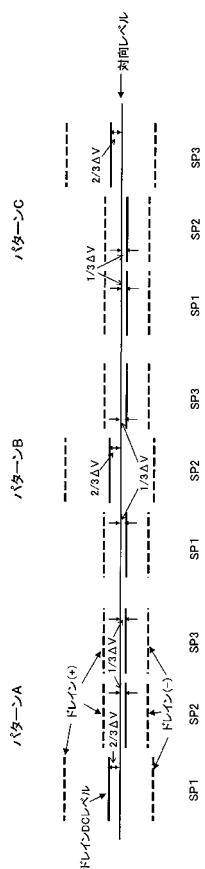

さらに、図 7 に示すように、対向電極の電圧レベルを明副画素のドレンイン電圧の D C レベルと暗副画素のドレンイン電圧の D C レベルの丁度中間のレベルに合わせてもよい。

10

【 0 0 6 5 】

図 7 に示すように、パターン A では明副画素である副画素 S P 1 のドレンイン電圧の D C レベルと暗副画素である副画素 S P 2 のドレンイン電圧の D C レベルとの中央のレベルを対向電圧のレベルとすると、副画素 S P 1 には + V の D C 成分が印加され、副画素 S P 2 には - V の D C 成分が印加される。

【 0 0 6 6 】

一方、パターン B では、対向電圧のレベルはパターン A と同様のまま、副画素 S P 1 を暗副画素とし、副画素 S P 2 を明副画素とするので、パターン A とは逆に、副画素 S P 1 には - V の D C 成分が印加され、副画素 S P 2 には + V の D C 成分が印加される。

20

【 0 0 6 7 】

このパターン A で表示を行うモード 1 とパターン B で表示を行うモード 2 との間でモード切替えを行うと、副画素 S P 1 および副画素 S P 2 のそれぞれの液晶層に印加される D C 成分は、モード 1 で表示している間に発生する D C 成分とモード 2 で表示している間に発生する D C 成分とが互いに打ち消し合い、時間平均として D C 成分の印加をなくすことができる。

【 0 0 6 8 】

ここでは、各画素が 2 つの副画素に分割された実施形態の液晶表示装置を例示したが、画素を 3 以上の副画素に分割した場合にも本発明を同様に適用できる。例えば、互いに輝度が異なる 3 つの副画素に分割した場合、最も輝度が大きい副画素と、最も輝度が小さい副画素との 2 つの副画素を、それぞれ上記の明副画素および暗副画素として（中間の輝度の副画素は固定して）、上述のように構成してもよい。あるいは、3 つの副画素に分割し、例えば、その内の 1 つを明副画素とし、他の 2 つを暗副画素（同じ輝度を表示する）とした場合、2 つの暗副画素のドレンイン電圧の D C レベルを対向レベルに合わせてもよい。また、1 つの副画素を暗副画素とし、2 つを明副画素とした場合は、2 つの明副画素のドレンイン電圧の D C レベルを対向レベルに合わせてもよい。画素を 3 つの副画素に分割する場合、画素内における副画素の輝度順序に対応する 3 つの異なるパターンで表示を行う 3 つのモード間で切替えを行うことによって、各副画素の液晶層に印加される D C 成分を低減することができる。いずれの場合においても、画素に含まれる少なくとも 2 つの副画素は互いに輝度が異なり、これら 2 つの副画素間の輝度の大小関係が逆の 2 つのモードで表示が行なわれる。

30

【 0 0 6 9 】

本実施形態の液晶表示装置は、以下のように特徴づけることもできる。

【 0 0 7 0 】

本発明の実施形態の液晶表示装置が備える画素は、供給された少なくとも 1 つの表示信号電圧に対して、互いに異なる輝度で表示を行う 2 つの副画素を含む複数の副画素を有しており、上記輝度切替回路構成は、複数の副画素のうち最も輝度が大きい副画素の画素内における位置が互いに異なる複数のモード間のモード切替を行っていることができる。例えば、画素を列方向に沿って 2 つの副画素に分割した場合には、明副画素が上側に位置するモードと明副画素が下側に位置するモードとの間でモード切替を行う。また、画素の列方向に沿って 3 つの副画素に分割した場合、明副画素が上側に位置するモードと、

40

50

明副画素が中央に位置するモードと、明副画素が下側に位置するモードとの間でモード切替を行う。

【0071】

一般に、VAモードの液晶表示装置は、黒および白に近い、低い階調と高い階調において特性の視角依存性が小さく、中間調において特性の視角依存性が大きい。図2に示した画素分割構造は、MVAモードなどの垂直配向モード(VAモード)の液晶表示装置の特性の視角依存性を改善するために好適である。MVAモードでは、図2に示した画素分割構造を採用すると、図8に示すように、各副画素の間の輝度差を中間の階調で大きく、低い階調と高い階調において小さくすることができる。そのため、この画素分割構造は、図9に示すように、明副画素と暗副画素との間のドレイン引き込み電圧Vdの差が、低階調と高階調では小さく、中間調で大きい。

10

【0072】

図10に、図2に示した画素分割構造を有するMVAモードの液晶表示装置における明暗の輝度切替(上記モード1とモード2との間の切替)周期に対する各表示階調における明副画素と暗副画素の輝度差の到達率の変化を示す。ここでは、60Hz駆動を行った場合を例示しており、1フレーム=16.7msである。図10には、明副画素と暗副画素との輝度差が大きい、中間調での結果を示している。

【0073】

画素分割方式は、輝度差のある複数の副画素で1つの画素を構成することにより視野角特性を改善するので、明副画素と暗副画素との輝度差はある程度以上ないと、その効果が得られない。図10を見ると、輝度差の到達率が90%を超えるのは切替え周期が2フレーム以降であり、応答の遅い低階調では、90%を超えるのは5フレームである。したがって、明暗の輝度切替えを1フレームごとに行うと、液晶の応答が1フレーム内で完了しない場合には、明暗副画素の輝度差が小さくなる、あるいは消失するので好ましくない。すなわち、MVAモード等の一般的な液晶表示装置の場合、明暗の輝度の切替え周期を2フレーム以上毎、好ましくは5フレーム以上とすることが好ましい。なお、輝度の切替えは一定の時間間隔を開けて(周期的に)行う必要はなく、輝度切替えの間隔が2周期以上、好ましくは5周期以上であれば、切替えのタイミングは任意であってよい。但し、上述したように、各モード(輝度パターン)での表示時間が異なると、副画素間のDC成分の平均化またはキャンセルが十分に行われないので、各モードでの表示時間の合計が等しくなるように制御することが好ましい。なお、ここでは、1フレームが16.7msの場合を例に説明したが、1フレーム(画像を書き換える期間)が長い場合には、1フレームでモード切替を行ってもよい。

20

【0074】

次に、明暗の輝度の切替えのタイミングについて詳細に説明する。

【0075】

上述したように、本発明による実施形態の液晶表示装置では、2フレーム以上の時間おきに各副画素の明暗を切替える。この輝度切替(モード切替)を行うタイミングとして、2フレーム以上の一定の時間間隔で行ってもよいが、表示している画像によっては、観察者が違和感を覚える可能性がある。この違和感を無くすために、以下のタイミングをトリガーとして、明暗副画素を切替えることが好ましい。垂直同期信号Vsyncや水平同期信号Hsyncを用いずに、下記AからCのタイミングで必要に応じてトリガー信号を発生させ、モード切替を行うようにする。

30

【0076】

A：一定時間おきではあるが、フレーム単位ではなく、30分や1時間という比較的長い時間単位で行う。切替を数フレーム単位や秒単位で頻繁に行うと、観察者がモード切替による違和感を生じる頻度が増すため、30分や1時間のような、比較的長い周期で切替を行うことが好ましい。

40

【0077】

B：明副画素と暗副画素との輝度差が無い、または小さいときに行う。

50

## 【0078】

明副画素と暗副画素との輝度差が小さいまたは無い場合、モード切替えを行っても各副画素の輝度は変化しないため違和感を覚えることはない。実際の表示画面では、白や黒のベタ画面が出現することは少ないため、明副画素と暗副画素の輝度差が所定の値よりも小さい場合に切替えを行うように設定する。図8に示したように、明副画素と暗副画素との輝度差が小さいのは、低階調と高階調であるので、画面全体の表示階調の平均値がある階調以上またはある階調以下の場合にモード切替えを行う。例えば、表示階調の平均値を算出し、ある閾値に達したときをトリガーとしてモード切替えを行えばよい。後に説明するように、明暗の輝度差はCS電圧(振幅電圧)により変化するため、モード切替を行うトリガーとなる閾値はCS電圧に応じて適宜決定すればよい。

10

## 【0079】

具体的には、例えば、以下のようにして閾値を決定することができる。

## 【0080】

閾値を決定するために、明副画素と暗副画素との輝度差を判別するパラメーターとして次式に示すFを用いる。

## 【0081】

$$F = I / I_{ave}$$

## 【0082】

Iは明副画素と暗副画素との輝度差であり、I<sub>ave</sub>は明副画素と暗副画素との平均輝度である。

20

## 【0083】

図11に、縦軸にF値、横軸に階調をとったグラフを示す。100階調付近の中間調でFが大きく、これを中心に低階調と高階調側でFが小さい。

## 【0084】

閾値となる輝度差F<sub>th</sub>を次式のようにFの最大値(F<sub>max</sub>)のX%とする。

## 【0085】

$$F_{th} = X / 100 * F_{max} \quad (* \text{は乗算を表す})$$

## 【0086】

この閾値を決定するXは、液晶パネルや駆動条件により適宜決定すればよい。図11からわかるように、50~120階調ではF値がほぼ一定になっており、50階調以下、120階調以上で急激にF値が減少している。したがって、例えば、X=90%を閾値とすることができる、より好ましくはX=50%である。

30

## 【0087】

F=F<sub>th</sub>となるときの低階調側の閾値をY<sub>thL</sub>、高階調側をY<sub>thH</sub>とすると、図11からY<sub>thL</sub>=16、Y<sub>thH</sub>=166となる。表示画面の平均階調Y<sub>ave</sub>を算出し、Y<sub>ave</sub>Y<sub>thL</sub>、Y<sub>ave</sub>Y<sub>thH</sub>のとき、モード切替を行う。例えば、画面全体の表示階調の平均値がY<sub>ave</sub>16、Y<sub>ave</sub>166のときモード切替を行う条件とすることができる。

## 【0088】

C:電源ON/OFF時、チャンネル切替え時、入力切替え時のように、操作者による所定の操作に応じて画面全体が切り替わるタイミング、または、CM画像が挿入されたときなど入力画像信号に所定の変化が生じた場合、画面全体が切り替わるため、明副画素と暗副画素が切り替わっても画面全体の切り替わりと区別できないので、観察者が違和感を覚えることはない。

40

## 【0089】

上述したように、パターンA(副画素SP1:明、副画素SP2:暗)で表示するモード1とパターンB(副画素SP1:暗、副画素SP2:明)で表示するモード2との表示時間を互いに等しくすることが、各副画素にDC成分が印加されるのを最も効果的に防止できるが、上述のタイミングをトリガーとしてモード切替えを行うと、一般に各モードでの表示時間が一致しない。そこで、例えば、積算カウンターでパターンAとパターンBの

50

表示時間をカウントし、それぞれの表示時間が互いに等しくなるように、上記の条件で発生したトリガー信号を取捨選択し、表示時間が長くなるにつれて表示時間が互いに等しくなるようになることが好ましい。例えば、モード切替を行った後の経過時間をカウントする回路を設け、所定の時間が経過するたびに、モード切替を行うようにする。あるいは、モード1の積算動作時間とモード2の積算動作時間との差が所定の値を超えたときに、モード切替を行うようにしてもよい。

【0090】

上述のように、モード1からモード2へ、またはモード2からモード1へ強制的にモード切替を行ってもよいが、モード1とモード2とをランダムに選択することによって行つてもよい。すなわち、上記タイミングにおいて、パターンAとパターンBの選択（切り替え）をランダムに1/2の確率で行つてもよい。ランダムに行うことにより時間平均として2つのモードの表示時間を等しくすることができる。たとえば、電源をONするたびに、モード1およびモード2のいずれかをランダムにかつ1/2の確率で選択するように構成してもよい。

10

【0091】

次に、図2に示した画素分割構造を有する本実施形態の液晶表示装置において、輝度切替えを行うための具体的な回路構成を説明する。

【0092】

図2に示した画素分割構造を有する液晶表示装置では、副画素電極11aおよび副画素電極11bに、共通のソースバスライン13から表示信号電圧が供給され、TFT14aおよびTFT14bがオフ状態とされたあと、補助容量CS1およびCS2の補助容量対向電極の電圧（すなわち、CSバスライン15aまたはCSバスライン15bから供給される電圧）の変化量（変化の方向および大きさによって規定される）を異ならせることによって、それぞれの副画素SP1およびSP2の液晶容量に印加される実効電圧が異なる状態、すなわち、輝度が異なる状態が得られる。従って、副画素SP1および副画素SP2のそれぞれの補助容量対向電極に印加する電圧の位相を反転させる、または、副画素SP1および副画素SP2のそれぞれに供給する表示信号電圧の位相を反転させることによって、副画素SP1と副画素SP2との輝度を切替える（輝度の大小関係を逆にする）ことができる。

20

【0093】

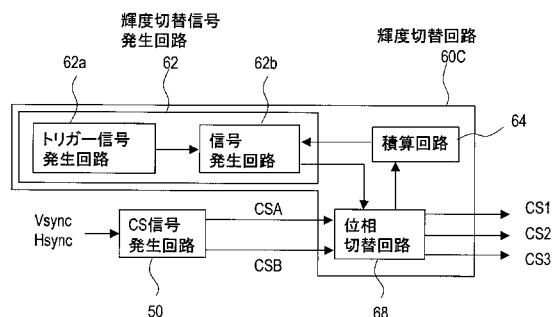

本発明による実施形態による液晶表示装置は、例えば、図12に示す構成を有することによって、モード切替（輝度切替）を行う。

30

【0094】

図12に示した液晶表示装置は、画素Pが2つの副画素SP1およびSP2を含む液晶表示パネル10と、入力画像信号を受け取り液晶表示パネル10に所定の駆動信号を供給する表示制御部20とを有している。表示制御部20は、ゲート駆動回路30、ソース駆動回路40、補助容量対向電圧発生回路50および輝度切替回路60に所定のタイミングで所定の信号を供給する。ここでは、輝度切替回路60がモード切替のトリガー信号を生成し、ソース駆動回路40から液晶表示パネル10に出力される表示信号電圧（ソース電圧）の位相を反転させる。

40

【0095】

図12に示した輝度切替回路60として、例えば、図13に示す輝度切替回路60Aを好適に用いることができる。

【0096】

輝度切替回路60Aは、輝度切替信号発生回路62と、極性切替回路66と、積算回路64とを有している。ソース極性制御信号発生回路20aは、例えば図12の表示制御部20に含まれる。

【0097】

水平同期信号Hsyncと垂直同期信号Vsyncをソース極性制御信号発生回路20aに入力し、極性が異なる（すなわち位相が180°異なる）P01AとP01B信号（

50

表示信号電圧)を発生する。輝度切替回路60Aの極性切替回路66は、この2つの極性が異なる表示信号電圧のうちにいずれか一方をソース駆動回路40に出力する。この極性の選択を輝度切替信号に基づいて行うことによって、モード切替を行う。

【0098】

輝度切替信号発生回路62は、少なくとも1つのトリガー信号発生回路62aと、信号発生回路62bとを有しており、トリガー信号発生回路62aは、上述した条件のいずれかを満足したときに、それぞれトリガー信号を発生する。信号発生回路62bは、積算回路64からの所定の信号を受けたときに、輝度切替信号を極性回路に出力する。すなわち、信号発生回路62bは、積算回路64からの信号に応じて、トリガー信号を取捨選択し、各モードでの積算動作時間が等しくなるように、モード切替を行う。

10

【0099】

例えば、全画面の平均階調を算出し、平均階調が所定の閾値の条件を満たすときに、トリガー信号発生回路62aがトリガー信号を出力し、信号発生回路62bに入力される。極性切替回路66がP01信号を切替え、パターンBの表示にしたとき、積算回路64に信号を送り、積算回路64でパターンAのカウントを記憶して、カウンターをリセットし、パターンBの表示時間のカウントを開始する。パターンBのカウントが記憶したパターンAのカウントに満たない場合は、トリガー信号が信号発生回路62bに入力されても、信号発生回路62bは輝度切替信号を出力しない。パターンBのカウントが記憶したパターンAのカウントと一致したときに、積算回路64から信号発生回路62bに信号を送り、輝度切替信号の発生のスタンバイをする。このスタンバイ状態でトリガー信号がトリガー信号発生回路62aから信号発生回路62bに入力されると、輝度切替信号が極性切替回路66に入力され、P01信号を切替、パターンAの表示を行い、同時にパターンBのカウントを記憶し、カウンターをリセットし、パターンAのカウントを開始する。

20

【0100】

この動作を繰り返すことにより、パターンAとパターンBの表示時間をほぼ等しくすることができる。ただし、画素分割による視野角改善効果を発揮するためには、パターンAとパターンBの切替を2フレーム以上毎で行うように、設定する。

30

【0101】

本発明による他の実施形態による液晶表示装置は、例えば、図14に示す構成を有することによって、モード切替(輝度切替)を行う。

【0102】

図14に示した液晶表示装置は、補助容量対向電圧発生回路50で発生された補助容量対向電圧(CS電圧)の位相を反転させることによって、モードを切替える輝度切替回路60を有している。

40

【0103】

図14に示した輝度切替回路60として、例えば、図15Aに示す輝度切替回路60Bを好適に用いることができる。

【0104】

輝度切替回路60Bは、輝度切替信号発生回路62と、積算回路64および位相切替回路68とを有している。輝度切替信号発生回路62は、少なくとも1つのトリガー信号発生回路62aと、信号発生回路62bとを有し、トリガー信号発生回路62aは、上述した条件のいずれかを満足したときにトリガー信号を発生する。信号発生回路62bは、積算回路64からの所定の信号を受けたときに、輝度切替信号を極性回路に出力する。すなわち、信号発生回路62bは、積算回路64からの信号に応じて、トリガー信号を取捨選択し、各モードでの積算動作時間が等しくなるように、モード切替を行う。

【0105】

ここでは、CS信号の位相を反転させることによりモード切替を行う。

【0106】

CS信号発生回路50は、水平同期信号Hsyncと垂直同期信号Vsyncから、位相が互いに異なるCS信号(補助容量対向電圧)CSAとCSBとを生成する。この位相

50

の異なる2つのCS信号は、位相切替回路68を通して液晶表示パネルの補助容量配線CS1またはCS2に伝送される。この位相切替回路68で、補助容量配線CS1およびCS2にCSAとCSBのどちらのCS信号を出力するかを切替る、すなわち、モード切替を行う。

【0107】

例えば、積算回路64が算出した全画面の平均階調が閾値の条件を満たすときに、トリガー信号発生回路62aが切替えを行うトリガー信号を出力し、信号発生回路62bに入力される。

【0108】

位相切替回路68でCS信号を切替え、パターンBの表示にしたとき、積算回路64に信号を送り、積算回路64でパターンAのカウントを記憶し、カウンターをリセットして、パターンBの表示時間のカウントを開始する。パターンBのカウントがパターンAのカウントに満たない場合は、トリガー信号が信号発生回路62bに入力されても、輝度切替信号を出力しない。パターンBのカウントが記憶しているパターンAのカウントと一致したときに積算回路64から信号発生回路62bに信号を送り、輝度切替信号発生のスタンバイをする。このスタンバイ状態でトリガー信号が信号発生回路62bに入力されると、輝度切替信号が位相切替回路68に入力され、CS信号の位相を切替え、パターンAの表示を行い、同時にパターンBのカウントを記憶し、カウンターをリセットしてパターンAのカウントを行う。この動作を繰り返すことにより、パターンAとパターンBの表示時間をほぼ等しく制御することができる。ただし、画素分割による視野角改善効果を発揮するためには、パターンAとパターンBの切替を2フレーム以上毎で行う必要があるため、トリガー信号が1フレーム間隔である場合はCS信号を切替えないように設定しておく。

10

20

30

【0109】

上記の例では、輝度切替回路60を付加的に設けることによって、輝度切替を行う構成を示したが、既存の回路を用いて、輝度切替を行う回路を構成することも出来る。

【0110】

図15Bおよび図15Cを参照しながら、図14に示した液晶表示装置の輝度切替回路60の機能を含む、CS信号発生回路50Aの構成と動作を説明する。図15Bは、CS信号発生回路50Aの構成を示す模式図であり、図15Cは、CS信号発生回路50Aの動作を説明するための各信号の電圧波形を示す図である。

30

【0111】

図15Bに示すように、CS信号発生回路50Aは、CS信号回路52と極性信号発生回路54とを有している。CS信号回路52は例えば2つの電圧レベルの間を振動する振幅電圧（「振動電圧」ともいう。）を生成する。

【0112】

極性信号発生回路54は、ゲートスタートパルスGSPとカウント信号CNTとを受け取り、CS極性反転用信号Po1を出力する。カウント信号CNTは1フレームに対して十分に短い周期を有しており、例えばゲートクロック信号を用いることができる。

【0113】

CS信号回路52は、CS極性反転用信号Po1が示す極性に応じて、振幅電圧の極性を決定してCS信号として出力する。

40

【0114】

ここで、図15Cを参照して各信号のタイミングを説明する。

【0115】

液晶表示装置の電源が投入されると、カウンター信号CNTの生成が開始され極性信号発生回路54に入力される。その後、不定時間後に、ゲートスタートパルスGSPが極性信号発生回路54に入力される。

【0116】

パターンAとパターンBとでは、電源投入後からゲートスタートパルスGSPが入力されるまでの時間が異なっており、この時間の違いによって、パターンAとパターンBとが

50

選択される。

【0117】

例えば、パターンAでは、ゲートスタートパルスGSPがH(High)のときにカウンター信号CNTがL(Low)であれば、CS極性反転信号Po1の初期状態をLとし、その後、CS極性反転用信号Po1は1フレーム毎(ゲートスタートパルスがHとなる毎)にHとLとが反転する。

【0118】

一方、パターンBでは、ゲートスタートパルスGSPがH(High)のときにカウンター信号CNTがH(High)であれば、CS極性反転信号Po1の初期状態をHとし、その後、CS極性反転用信号Po1は1フレーム毎(ゲートスタートパルスがHとなる毎)にHとLとが反転する。

10

【0119】

このように設定されているCS極性反転用信号Po1がCS信号回路52に入力されると、出力されるCS信号の極性がCS反転信号Po1の極性に応じて選択されることになる。

【0120】

図15Cに示したように、CS信号回路52に入力されるCS極性反転用信号Po1がパターンAの場合、CSバスラインCS1(例えば、図2の副画素SP1に接続されているCSバスライン15a)には一意的にパターンAに示す極性のCS信号が出力される。一方、CS信号回路52に入力されるCS極性反転用信号Po1がパターンBの場合、CSバスラインCS1(例えば、図2の副画素SP1に接続されているCSバスライン15a)には一意的にパターンBに示す極性のCS信号が出力される。このとき、他方のCSバスラインCS2(図2の副画素SP2に接続されているCSバスライン15b)には、パターンAおよびBのいずれの場合も、CS1に出力されるCS信号の極性を反転した信号がCS信号として出力される。

20

【0121】

このように構成されると、電源が投入された時点からゲートスタートパルスGSPが極性信号発生回路54に入力される時点までの時間が不定であるので、ゲートスタートパルスGSPがHの時のカウンター信号CNTがHであるかLであるかはランダムである。従って、パターンAが選択されるか、パターンBが選択されるかは、ランダムであり、何れが選択される確率も1/2である。

30

【0122】

従って、このような輝度切替回路構成を有する液晶表示装置を長期間使用すれば、時間平均として2つのモードの表示時間が等しくなる。

【0123】

輝度切替をランダムに行う上記の構成は、ソース信号電圧の極性を切替えることによって輝度切替を行う構成にも適用できる。

【0124】

以下に、ネガ型液晶を用いたノーマリーブラックのMVAモードの液晶表示装置の実施形態を説明する。

40

【0125】

(実施形態1)

図2に示すように本実施形態にかかる液晶表示装置は、1画素を複数の副画素に分割した画素構造であり、アクティブマトリクス型の液晶表示装置である。ここでは、1画素を2つの副画素に分割した例を示すが、3つ以上の副画素に分割していてもよい。

【0126】

図16に示すように、副画素SP1が明副画素、副画素SP2が暗副画素である表示をパターンAとし、明暗表示を入れ換えて、副画素SP1が暗副画素、副画素SP2が明副画素となる表示をパターンBとして、パターンAとパターンBを交互に切替える。

50

【0127】

駆動方法について、図17に示した液晶表示装置の等価回路と各バスラインの電圧のタイミングを示した図18、図19を用いて説明する。本実施形態では1フレーム = 16.7 msで駆動を行う。

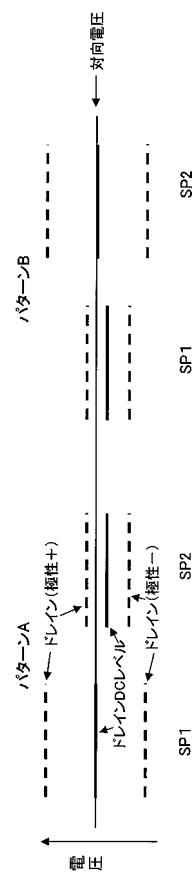

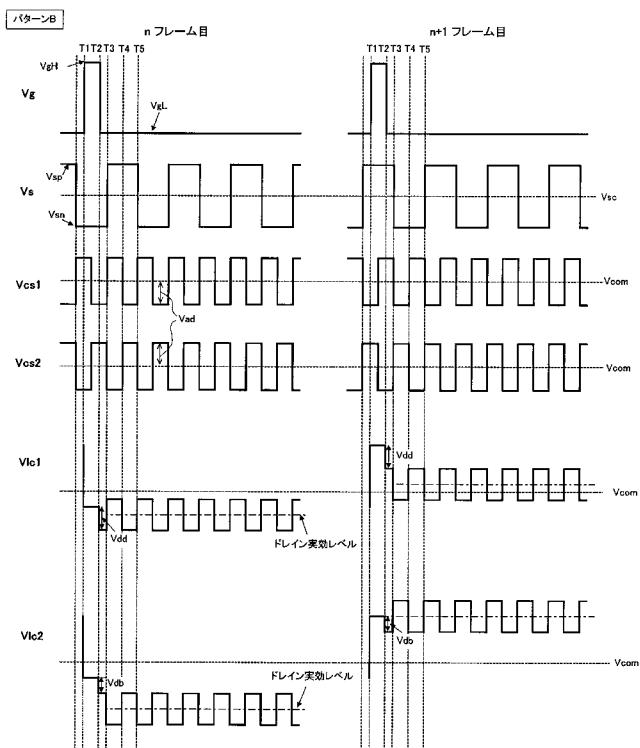

#### 【0128】

図18に示すパターンAでは副画素S P 1が明副画素、副画素S P 2が暗副画素となる各バスラインの電圧のタイミングであり、図19のパターンBでは副画素S P 1が暗副画素、副画素S P 2が明副画素となる各バスラインの電圧のタイミングである。V gはゲート電圧、V sはソース電圧、V c s 1とV c s 2は副画素S P 1と副画素S P 2それぞれの補助容量の電圧、V l c 1とV l c 2はそれぞれ副画素S P 1と副画素S P 2の画素電極の電圧を示す。一般に液晶が分極しないようにフレーム反転、ライン反転、ドット反転といった交流駆動を行う。

10

#### 【0129】

本実施形態では図18、図19に示すようにnフレーム目にソース電圧の中央値V s cに対して、プラス極性としてソース電圧にV s pを与える、次の(n+1)フレーム目にマイナス極性としてソース電圧にV s nを与える、図16に示すようにフレームごとにドット反転駆動を行う。C S 1とC S 2には、電圧を振幅電圧V a dで振幅させ、C S 1とC S 2の位相を180度ずらした信号を入力する。

20

#### 【0130】

まず、図18に示すパターンAにおけるnフレーム目のときの各信号の電圧の経時変化を説明する。

#### 【0131】

時刻T1のとき、V gがV g LからV g Hに変化し、両副画素のT F TがON状態となり、副画素S P 1、副画素S P 2と補助容量C S 1、C S 2にV s pの電圧が充電される。

30

#### 【0132】

時刻T2のとき、V gがV g HからV g Lに変化し、両副画素のT F TがOFF状態となり、副画素S P 1、副画素S P 2と補助容量C S 1、C S 2がソースバスラインと電気的に絶縁される。なお、この直後に寄生容量等の影響による引き込み現象のために、副画素S P 1と副画素S P 2のそれぞれにV d bとV d dの引き込み電圧が発生し、各副画素の電圧は

$$V l c 1 = V s p - V d b$$

$$V l c 2 = V s p - V d d$$

となる。引き込み電圧V d bとV d dについては後で詳細に説明する。

#### 【0133】

またこのとき、

$$V c s 1 = V c o m - V a d$$

$$V c s 2 = V c o m + V a d$$

である。

#### 【0134】

次に時刻T3のとき、補助容量バスラインC S 1の電圧V c s 1がV c o m - V a dからV c o m + V a dへ変化し、補助容量バスラインC S 2の電圧、V c s 2がV c o m + V a dからV c o m - V a dへ変化する。このとき各副画素の画素電圧V l c 1とV l c 2は、

$$V l c 1 = V s p - V d b + 2 * K * V a d$$

$$V l c 2 = V s p - V d d - 2 * K * V a d$$

40

となる。ただし、K = C c s / (C l c (V) + C c s)である。

#### 【0135】

時刻T4では、V c s 1がV c o m + V a dからV c o m - V a dへ変化し、V c s 2がV c o m - V a dからV c o m + V a dへ変化する。このとき副画素電圧V l c 1とV l c 2は、

50

$$\begin{aligned}V_{1c1} &= V_{sp} - V_{db} \\V_{1c2} &= V_{sp} - V_{dd}\end{aligned}$$

となる。

【0136】

時刻T5では、 $V_{cs1}$ が $V_{com} - V_{ad}$ から $V_{com} + V_{ad}$ へ変化し、 $V_{cs2}$ が $V_{com} + V_{ad}$ から $V_{com} - V_{ad}$ へ変化する。このとき副画素電圧 $V_{1c1}$ と $V_{1c2}$ は、

$$\begin{aligned}V_{1c1} &= V_{sp} - V_{db} + 2 * K * V_{ad} \\V_{1c2} &= V_{sp} - V_{dd} - 2 * K * V_{ad}\end{aligned}$$

となる。

10

【0137】

後は、次に $V_g = V_{gH}$ となり書き込みが行われるまで、水平書き込み時間1Hの整数倍ごとに、 $V_{cs1}$ 、 $V_{cs2}$ と $V_{1c1}$ 、 $V_{1c2}$ は時刻T4と時刻T5を交互に繰り返す。したがって、 $V_{1c1}$ と $V_{1c2}$ の実効値は、

$$\begin{aligned}V_{1c1} &= V_{sp} - V_{db} + K * V_{ad} \\V_{1c2} &= V_{sp} - V_{dd} - K * V_{ad}\end{aligned}$$

となる。

【0138】

nフレーム目において、各副画素の液晶層に印加される実効電圧は、

$$V_1 = V_{sp} - V_{db} + K * V_{ad} - V_{com} \quad (2)$$

$$V_2 = V_{sp} - V_{dd} - K * V_{ad} - V_{com} \quad (3)$$

となるため、副画素SP1が明副画素、副画素SP2が暗副画素となる。

20

【0139】

次に、図18のパターンAにおける( $n + 1$ )フレーム目のときの各信号の電圧の経時変化を説明する。

【0140】

( $n + 1$ )フレーム目では、極性を反転させるため、 $V_s$ を反転させる。時刻T1のとき、 $V_g$ が $V_{gL}$ から $V_{gH}$ に変化し、両副画素のTFTがON状態となり、補助容量CS1、CS2に $V_{sn}$ の電圧が充電される。

30

【0141】

時刻T2では、nフレーム目と同様に両副画素のTFTがOFF状態となり、この直後に副画素SP1と副画素SP2のそれぞれに $V_{db}$ と $V_{dd}$ の引き込み電圧が発生し、各副画素の電圧は、

$$\begin{aligned}V_{1c1} &= V_{sn} - V_{db} \\V_{1c2} &= V_{sn} - V_{dd}\end{aligned}$$

となる。

【0142】

時刻T3のとき、補助容量バスラインCS1の電圧 $V_{cs1}$ が $V_{com} + V_{ad}$ から $V_{com} - V_{ad}$ へ変化し、補助容量バスラインCS2の電圧、 $V_{cs2}$ が $V_{com} - V_{ad}$ から $V_{com} + V_{ad}$ へ変化する。このとき各副画素の画素電圧 $V_{1c1}$ と $V_{1c2}$ は

40

$$\begin{aligned}V_{1c1} &= V_{sn} - V_{db} - 2 * K * V_{ad} \\V_{1c2} &= V_{sn} - V_{dd} + 2 * K * V_{ad}\end{aligned}$$

となる。

【0143】

時刻T4では、 $V_{cs1}$ が $V_{com} - V_{ad}$ から $V_{com} + V_{ad}$ へ変化し、 $V_{cs2}$ が $V_{com} + V_{ad}$ から $V_{com} - V_{ad}$ へ変化する。このとき副画素電圧 $V_{1c1}$ と $V_{1c2}$ は、

$$\begin{aligned}V_{1c1} &= V_{sn} - V_{db} \\V_{1c2} &= V_{sn} - V_{dd}\end{aligned}$$

50

となる。

【0144】

時刻  $T_5$  では、 $V_{cs1}$  が  $V_{com} + V_{ad}$  から  $V_{com} - V_{ad}$  へ変化し、 $V_{cs2}$  が  $V_{com} - V_{ad}$  から  $V_{com} + V_{ad}$  へ変化する。このとき副画素電圧  $V_{lc1}$  と  $V_{lc2}$  は、

$$V_{lc1} = V_{sn} - V_{db} - 2 * K * V_{ad}$$

$$V_{lc2} = V_{sn} - V_{dd} + 2 * K * V_{ad}$$

となる。

【0145】

後は、 $n$  フレームと同様に、 $V_{cs1}$ 、 $V_{cs2}$  と  $V_{lc1}$ 、 $V_{lc2}$  は時刻  $T_4$  と時刻  $T_5$  を交互に繰り返す。よって、 $V_{lc1}$  と  $V_{lc2}$  の実効値は、

$$V_{lc1} = V_{sn} - V_{db} - K * V_{ad}$$

$$V_{lc2} = V_{sn} - V_{dd} + K * V_{ad}$$

となる。

【0146】

( $n + 1$ ) フレーム目の各副画素の液晶層に印加される実効電圧は、

$$V_1 = V_{sn} - V_{db} - K * V_{ad} - V_{com} \quad (4)$$

$$V_2 = V_{sn} - V_{dd} + K * V_{ad} - V_{com} \quad (5)$$

となるため、副画素  $SP_1$  が明副画素、副画素  $SP_2$  が暗副画素となる。

【0147】

+ 極性である  $n$  フレーム目と - 極性である ( $n + 1$ ) フレーム目の副画素  $SP_1$  と副画素  $SP_2$  の画素電極に印加される電圧の DC 電圧はそれぞれ、

$$V_{1dc} = V_{sc} - V_{db} \quad (6)$$

$$V_{2dc} = V_{sc} - V_{dd} \quad (7)$$

となる。ただし、 $V_{sc}$  はソース電圧の中央値であり、 $V_{sc} = (V_{sp} + V_{sn}) / 2$  である。

【0148】

ここで、時刻  $T_2$  で生じる副画素  $SP_1$  と副画素  $SP_2$  の引き込み電圧  $V_{db}$  と  $V_{dd}$  について説明する。引き込み電圧は (1) 式に示すように液晶の容量  $C_{lc}$  (V) が影響する。液晶層に印加される電圧が変化すると、誘電率異方性を有する液晶分子の配向方向が変化するため、 $C_{lc}$  (V) は変化する。時刻  $T_2$  では、副画素  $SP_1$  と副画素  $SP_2$  の各副画素電極の電圧は  $n$  フレーム目では  $V_{sp}$ 、( $n + 1$ ) フレーム目では  $V_{sn}$  であるから、液晶が  $T = T_2 - T_1$  以内に応答し、遷移を完了すれば、各液晶容量は  $C_{lc1}$  (V) =  $C_{lc2}$  (V) となり、(1) 式から  $V_{db} = V_{dd}$  となる。

【0149】

しかしながら、 $V_{gH}$  である時間 ( $T$ ) はおよそ  $10 \mu sec$  と非常に短いのに対して、液晶の応答は  $ms$  オーダーであるため、 $T$  以内に液晶は応答を完了できず、時刻  $T_2$  において液晶は、 $T_1$  より前の状態からほぼ変位していない。本実施形態のパターン A では、副画素  $SP_1$  が明副画素、副画素  $SP_2$  が暗副画素であるので、 $V_{lc1} > V_{lc2}$  となり、誘電率異方性が負の液晶 (すなわち、ネガ型液晶) では  $C_{lc1}$  (V) >  $C_{lc2}$  (V) となる。よって、時刻  $T_2$  においても  $C_{lc1}$  (V) >  $C_{lc2}$  (V) となり、(1) 式から  $V_{db} < V_{dd}$  となる。

【0150】

したがって、副画素  $SP_1$  と副画素  $SP_2$  の画素電極に印加される電圧の DC 電圧  $V_{1dc}$  と  $V_{2dc}$  は (6) (7) 式から  $V_{1dc} > V_{2dc}$  となる。

【0151】

対向電圧  $V_{com}$  を副画素  $SP_1$  の画素電極に印加される電圧の DC 電圧  $V_{1dc}$  に一致させると、

$$V_{1dc} = V_{com} = V_{sc} - V_{db}$$

となる。

10

20

30

40

50

## 【0152】

一方、 $V_{2dc} < V_{com}$ となるため、副画素SP1を明副画素、副画素SP2を暗副画素として表示し続けると、副画素SP1のドレイン電圧のDCレベルと対向レベルが一致し、副画素SP2のドレイン電圧のDCレベルと対向レベルがずれる。

## 【0153】

2フレーム以上の後に、パターンBの表示に切替えるために、図19に示すようにCSの入力信号の $V_{cs1}$ 、 $V_{cs2}$ ともに位相を180度ずらす。このとき、nフレーム目の $V_{1c1}$ と $V_{1c2}$ の実効値は、

$$V_{1c1} = V_{sp} - V_{dd} - K * V_{ad}$$

$$V_{1c2} = V_{sp} - V_{db} + K * V_{ad}$$

10

となる。 $(n+1)$ フレーム目の $V_{1c1}$ および $V_{1c2}$ の実効値はそれぞれ、

$$V_{1c1} = V_{sn} - V_{dd} + K * V_{ad}$$

$$V_{1c2} = V_{sn} - V_{db} - K * V_{ad}$$

となる。

## 【0154】

+極性であるnフレーム目と-極性である $(n+1)$ フレーム目の副画素SP1と副画素SP2の画素電極に印加される電圧のDC電圧はそれぞれ、

$$V_{1dc} = V_{sc} - V_{dd} \quad (8)$$

$$V_{2dc} = V_{sc} - V_{db} \quad (9)$$

20

パターンBでは、副画素SP1が暗副画素、副画素SP2が明副画素であるので、 $V_{1c1} < V_{1c2}$ となり、ネガ型液晶では $C_{1c1}(V) < C_{1c2}(V)$ となる。よって、時刻T2においても $C_{1c1}(V) < C_{1c2}(V)$ となり、(1)式から $V_{dd} > V_{db}$ となる。

## 【0155】

対向電圧は $V_{com} = V_{sc} - V_{db}$ なので、 $V_{2dc}$ と一致する。副画素SP1を暗副画素、副画素SP2を明副画素として表示するパターンBでは、副画素SP2のドレイン電圧のDCレベルと対向レベルが一致し、副画素SP1のドレイン電圧のDCレベルと対向レベルが一致しない。

## 【0156】

パターンAとパターンBの表示を繰り返すことにより、図6にドレイン電圧のDCレベルと対向電圧の関係に示すように、一方の副画素への継続的なDC印加を防止することができる。 $V_{com} = V_{sc} - V_{dd}$ としても同様の効果が得られる。

30

## 【0157】

画素分割による視野角改善効果を発揮するためには、パターンAとパターンBとの切替を2フレーム以上の時間間隔で行うことが好ましい。また、頻繁に切替を行うと、観察者に違和感を与える可能性があるため、フレーム単位や秒単位の切替は避けたほうがよい。例えば、本実施形態では切替間隔を1時間ごとに行う。もちろん、図14、図15Aおよび図15Bを参照しながら説明した構成を用いて、上述した条件BやCのタイミングでモード切替を行ってもよい。

## 【0158】

## [実施形態2]

本実施形態の液晶表示装置は実施形態1で説明した図17とほぼ同じ構成であるので詳細は省略する。本実施形態では、図16に示すパターンAとパターンBにおける明副画素と暗副画素の切替えをソース信号の極性を切替えることにより行う。パターンAとパターンBにおける各信号の電圧波形を図20と図21に示す。図中の記号等は実施形態1と同様である。本実施形態では実施形態1と同様に1フレーム = 16.7msで駆動を行う。

40

## 【0159】

図20に示すように、パターンAでは、nフレーム目に $V_{sp}$ 、 $(n+1)$ フレーム目に $V_{sn}$ のソース信号を入力する。よって、nフレーム目における $V_{1c1}$ と $V_{1c2}$ の実効値は、

50

$$V_{1c1} = V_{sp} - V_{db} + K * V_{ad}$$

$$V_{1c2} = V_{sp} - V_{dd} - K * V_{ad}$$

となる。 $(n + 1)$  フレーム目における  $V_{1c1}$  と  $V_{1c2}$  の実効値は、

$$V_{1c1} = V_{sn} - V_{db} - K * V_{ad}$$

$$V_{1c2} = V_{sn} - V_{dd} + K * V_{ad}$$

となる。よって、パターン A では副画素  $SP_1$  が明副画素、副画素  $SP_2$  が暗副画素となる。

#### 【0160】

図 21 に示すように、パターン B では、 $n$  フレーム目に  $V_{sn}$ 、 $(n + 1)$  フレーム目に  $V_{sp}$  のソース信号を入力する。よって、 $n$  フレーム目における  $V_{1c1}$  と  $V_{1c2}$  の実効値は、

$$V_{1c1} = V_{sn} - V_{dd} + K * V_{ad}$$

$$V_{1c2} = V_{sn} - V_{db} - K * V_{ad}$$

となる。 $(n + 1)$  フレーム目における  $V_{1c1}$  と  $V_{1c2}$  の実効値は、

$$V_{1c1} = V_{sp} - V_{dd} - K * V_{ad}$$

$$V_{1c2} = V_{sp} - V_{db} + K * V_{ad}$$

となる。よって、パターン B では副画素  $SP_1$  が暗副画素、副画素  $SP_2$  が明副画素となる。

#### 【0161】

パターン A における副画素  $SP_1$  と副画素  $SP_2$  の  $V_{1c1}$  と  $V_{1c2}$  の DC 電圧は、

$$V_{1dc} = V_{sc} - V_{db}$$

$$V_{2dc} = V_{sc} - V_{dd}$$

であり、パターン B における副画素  $SP_1$  と副画素  $SP_2$  の  $V_{1c1}$  と  $V_{1c2}$  の DC 電圧は、

$$V_{1dc} = V_{sc} - V_{dd}$$

$$V_{2dc} = V_{sc} - V_{db}$$

である。ただし、 $V_{sc}$  はソース電圧の中央値であり、 $V_{sc} = (V_{sp} + V_{sn}) / 2$  である。また、実施形態 1 で述べたように、 $V_{db} < V_{dd}$  である。

#### 【0162】

対向電圧  $V_{com} = V_{1dc} = V_{sc} - V_{db}$  とすると、パターン A では副画素  $SP_1$  が最適対向となり、副画素  $SP_2$  が最適対向からずれる。パターン B に切替えると、副画素  $SP_1$  の対向がずれ、副画素  $SP_2$  が最適対向となる。したがって、一方の副画素への継続的な DC 印加を防止できる。 $V_{com} = V_{2dc}$  としても同様の効果が得られる。

#### 【0163】

ソースの極性を反転させることによるモードの切替は、例えば、図 12 および図 13 を参照しながら説明した輝度切替回路 60 を用いて行うことができる。

#### 【0164】

また、本実施形態ではドット反転駆動のためソース信号の極性をフレームごとに反転している。パターン A とパターン B の切替をソース信号の極性を反転させて行うと、パターン切替時のみドット反転による極性反転が起こらない。そのため、ドット反転による DC 印加防止やフリッカ防止の効果を低減させないためにパターン A とパターン B の切替は頻繁に行なわないほうがよい。したがって、本実施形態では切替間隔を 30 分以上となるように設定しておく。もちろん、上述した条件 B や C のタイミングでモード切替を行ってよい。

#### 【0165】

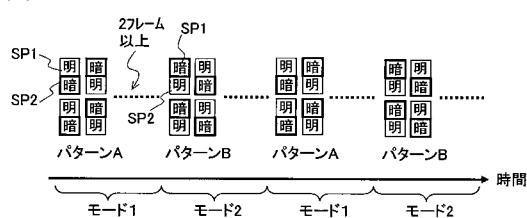

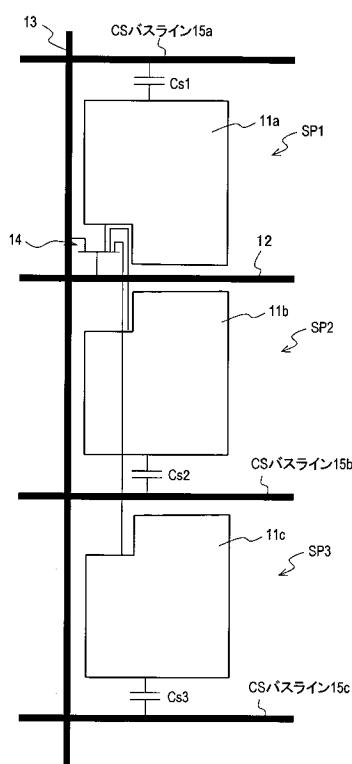

##### [実施形態 3]

本実施形態の液晶表示装置は図 22 に示すように、1 画素を 3 つの副画素に分割したものである。図 23 に示す等価回路のように、1 本のゲートバスラインと 1 本のソースバスラインで 3 副画素を駆動させる。実施形態 1 および 2 と同様に、各副画素はそれぞれ CS バスラインの振幅電圧により、印加電圧を変化させる。副画素の数が多い方が、視野角特

性は改善されるが、透過率低下等の弊害もあるため、使用目的に合わせて適宜選択すればよい。

#### 【0166】

一般に画素分割技術では、1画素当りの暗副画素の面積比が大きいほうが、視角特性が良くなるため、本実施形態では、図25に示すように、パターンAでは副画素S P 1が明副画素、副画素S P 2と副画素S P 3が暗副画素であり、パターンBでは副画素S P 1とS P 3が暗副画素、副画素S P 2が明副画素であり、パターンCでは副画素S P 3が明副画素、副画素S P 1と副画素S P 2が暗副画素とする。明るい画素と暗い画素を時間おきに入れ換えるため、パターンA、パターンB、パターンCの順に表示を2フレーム以上の間隔で切替える。本実施形態では実施形態1と同様に1フレーム = 16.7 msで駆動を行う。

10

#### 【0167】

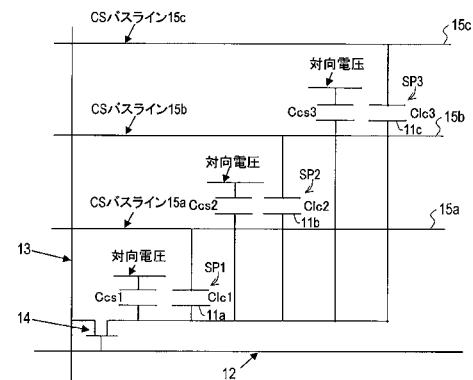

明副画素と暗副画素の表示の切替方法として、CS信号の位相をずらす、または、ソース電圧を反転させる、のいずれを用いてもよい。例えば、CS信号の位相をずらす構成を採用する場合は、図24に示す輝度切替回路60Cを用いることが出来る。輝度切替回路60Cは、図15Aに示した輝度切替回路60Bと基本的に同じ構成を有し、位相切替回路68が3つの副画素のそれぞれに対応する3つのCSバストライインに、極性の異なる2種類のCS信号CSAまたはCSBを出力できるように構成されている点で異なる。

20

#### 【0168】

本実施形態では、あらかじめ設定した時間（カウント）に達した後に、トリガー入力で切替を行う。位相の異なるCS信号CSAとCSBは水平同期信号Hsyncと垂直同期信号VsyncからCS信号発生回路50を通して生成する。この位相の異なる2つのCS信号が位相切替回路68を通してCS1かCS2かCS3に伝送される。この位相切替回路68でCS1とCS2とCS3にCSAとCSBのどちらのCS信号を出力するかを切替る、つまりパターンA、パターンB、パターンCの切替を行う。

20

#### 【0169】

例えば、算出した全画面の平均階調が閾値の条件を満たすときに、切替えを行うトリガー信号を出力し、信号発生回路62bに入力される。位相切替回路68でCS信号を切替、パターンAからパターンBの表示に変更したとき、積算回路64に信号を送り、積算回路64でパターンAのカウントを終了し、カウンターをリセットして、パターンBの表示時間のカウントを開始する。パターンBのカウントが設定したカウントに満たない場合は、トリガー信号が信号発生回路62bに入力されても、制御信号を出力しない。パターンBのカウントが設定したカウントと一致したときに積算回路64から信号発生回路62bに信号を送り、輝度切替信号のスタンバイをする。このスタンバイ状態でトリガー信号が信号発生回路62bに入力されると、輝度切替信号が位相切替回路68に入力され、CS信号の位相を切替、パターンCの表示を行い、同時にパターンBのカウントを終了し、カウンターをリセットし、パターンCのカウントを開始する。カウントが設定値になった後に入力されたトリガー信号で位相切替回路68が動作して、パターンAへの切替を行う。この時、パターンCのカウントを終え、カウンターをリセットして、パターンAのカウントを開始する。この動作を繰り返すことにより、パターンAとパターンBとパターンCの表示時間を設定した時間に制御することができる。ただし、画素分割による視野角改善効果を発揮するためには、パターンAとパターンBとパターンCの切替を2フレーム以上毎で行う必要があるため、設定カウントは2フレーム以上とする。

30

#### 【0170】

図26に各副画素のドレインの電圧レベルと対向電極の電圧レベルを示す。本実施形態では、明副画素にくらべ暗副画素の面積比が大きいので、DC印加が起こる面積を小さくするために暗副画素のドレイン電圧のDCレベルに対向電圧を調整する。

40

#### 【0171】

パターンAでは副画素S P 2および副画素S P 3に対して最適な対向レベルであり、副画素S P 1で対向レベルがずれ、DC成分の印加が起こる。パターンBに切替えると、副

50

画素 S P 1 および副画素 S P 3 に対して最適な対向レベルとなり、副画素 S P 2 で D C 成分が印加されることになる。パターン C に切替えると、副画素 S P 1 および副画素 S P 2 で最適な対向レベルとなり、副画素 S P 3 で D C 成分が印加されることになる。これらパターン A ~ C を相互に切替えることにより、特定の副画素への継続的な D C 成分の印加を防止できる。

【 0 1 7 2 】

副画素のドレイン電圧の D C レベルと対向レベルの設定の方法は、上記の例に限られず、図 27 に示すように設定してもよい。

【 0 1 7 3 】

図 27 に各副画素のドレイン電圧の D C レベルと対向電極の電圧レベルを示す。ここでは、明副画素と暗副画素のドレイン電圧の D C レベルの差を  $V$  としたとき、明副画素のドレイン電圧の D C レベルを対向電圧に対して  $+ 2 / 3 V$  とし、暗副画素のドレイン電圧の D C レベルを対向レベルに対して  $- 1 / 3 V$  と設定する。

10

【 0 1 7 4 】

パターン A では副画素 S P 1 に  $+ 2 / 3 V$ 、副画素 S P 2 と副画素 S P 3 に  $- 1 / 3 V$  の D C が印加される。パターン B では副画素 S P 2 に  $+ 2 / 3 V$ 、副画素 S P 1 と副画素 S P 3 に  $- 1 / 3 V$  の D C が印加される。パターン C では副画素 S P 3 に  $+ 2 / 3 V$ 、副画素 S P 1 と副画素 S P 2 に  $- 1 / 3 V$  の D C が印加される。各副画素 S P 1, S P 2, S P 3 においてはパターン A, B, C の表示時間を等しくすることにより時間平均で D C 成分の印加をキャンセルすることができ、D C 印加の防止を図れる。

20

【 0 1 7 5 】

上記の例では、各画素を 2 または 3 つの副画素に分割した例を説明したが、4 以上の副画素に分割した場合にも本発明の効果が得られることは言うまでもない。

【 産業上の利用可能性 】

【 0 1 7 6 】

本発明によると、1 つの画素を複数の副画素で構成する画素分割構造を有する液晶表示装置において、副画素に発生する D C 電圧が平均化によって殆ど零となるようにすることが可能となり、液晶表示装置の信頼性が向上する。本発明は、液晶テレビなどの大画面の液晶表示装置の表示品位と信頼性を向上する。

30

【 符号の説明 】

【 0 1 7 7 】

- 1 0 液晶表示パネル

- 2 0 表示制御部

- 3 0 ゲート駆動回路

- 4 0 ソース駆動回路

- 5 0 補助容量対向電圧発生回路 ( C S 信号発生回路 )

- 6 0, 6 0 A, 6 0 B, 6 0 C 輝度切替回路

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

【図14】

【図15A】

【図15B】

【図15C】

【図16】

【図17】

【図18】

【図19】

【 図 2 0 】

【 図 2 1 】

【 図 2 2 】

【 図 2 3 】

【 図 2 4 】

【図25】

【図26】

【図27】

## フロントページの続き

|              |         |              |

|--------------|---------|--------------|

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|              | G 0 9 G | 3/20 6 2 4 C |

|              | G 0 2 F | 1/133 5 5 0  |

|              | G 0 2 F | 1/133 5 2 5  |

(72)発明者 入江 健太郎

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 下敷領 文一

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

F ターム(参考) 2H193 ZA04 ZA07 ZB02 ZB03 ZB05 ZB14 ZB18 ZC16 ZD23 ZD36

ZF03 ZF60 ZQ11

5C006 AC25 BB16 BC06 BF22 FA33 FA55

5C080 AA10 BB05 DD01 DD29 JJ02 JJ03 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2011065176A</a>                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2011-03-31 |

| 申请号            | JP2010247913                                                                                                                                                                                                                                                                                                                   | 申请日     | 2010-11-04 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 入江 健太郎<br>下敷領文一                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 入江 健太郎<br>下敷領 文一                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G02F1/13306 G02F1/136213 G02F1/1368 G09G3/2018 G09G3/3614 G09G3/3648 G09G3/3655<br>G09G2300/0443 G09G2300/0447 G09G2300/0876 G09G2320/0219 G09G2320/0276 G09G2360/16                                                                                                                                                           |         |            |

| FI分类号          | G09G3/36 G09G3/20.624.B G09G3/20.670.J G09G3/20.670.K G09G3/20.680.H G09G3/20.624.C<br>G02F1/133.550 G02F1/133.525                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZA07 2H193/ZB02 2H193/ZB03 2H193/ZB05 2H193/ZB14 2H193/ZB18 2H193<br>/ZC16 2H193/ZD23 2H193/ZD36 2H193/ZF03 2H193/ZF60 2H193/ZQ11 5C006/AC25 5C006/BB16<br>5C006/BC06 5C006/BF22 5C006/FA33 5C006/FA55 5C080/AA10 5C080/BB05 5C080/DD01 5C080<br>/DD29 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 2H193/ZA08 |         |            |

| 代理人(译)         | 奥田诚治<br>三宅明子                                                                                                                                                                                                                                                                                                                   |         |            |

| 优先权            | 2004322876 2004-11-05 JP                                                                                                                                                                                                                                                                                                       |         |            |

| 其他公开文献         | JP5129314B2                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

要解决的问题：提高具有像素分割结构的液晶显示器的可靠性。解决方案：本发明的液晶显示器具有响应于通过晶体管提供的显示信号电压而改变亮度的像素，并且该像素配备有：液晶显示面板10，其具有引入的第一子像素。第一亮度，响应于所提供的至少一个显示信号电压，第二子像素进入与第一亮度不同的第二亮度；源极驱动电路40，用于将显示信号电压提供给连接到晶体管的源极的源极总线；栅极驱动电路30，用于向连接到晶体管栅极的栅极总线提供扫描信号电压；和亮度切换电路装置60，用于在第一亮度高于第二亮度的第一模式和第一亮度低于第二亮度的第二模式之间进行切换。亮度切换电路装置以83.5毫秒或更长的时间间隔切换模式。 〔