(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-185339

(P2012-185339A)

(43) 公開日 平成24年9月27日(2012.9.27)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 1 9 3   |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 5 C 0 0 6   |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5 C 0 8 0   |

|                             | G09G 3/20 | 6 2 4 B     |

|                             | G09G 3/20 | 6 2 1 B     |

|                             | G09G 3/20 | 6 1 1 J     |

|                             | G09G 3/20 | 6 4 1 J     |

審査請求 未請求 請求項の数 3 O L (全 14 頁) 最終頁に続く

|           |                            |                       |                                                                                                                                                                                      |

|-----------|----------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2011-48468 (P2011-48468) | (71) 出願人              | 308036402                                                                                                                                                                            |

| (22) 出願日  | 平成23年3月7日 (2011.3.7)       | 株式会社 J V C ケンウッド      |                                                                                                                                                                                      |

|           |                            | 神奈川県横浜市神奈川区守屋町3丁目12番地 |                                                                                                                                                                                      |

|           |                            | (74) 代理人              | 100085235                                                                                                                                                                            |

|           |                            | 弁理士                   | 松浦 兼行                                                                                                                                                                                |

|           |                            | (72) 発明者              | 樋口 潤                                                                                                                                                                                 |

|           |                            |                       | 神奈川県横浜市神奈川区守屋町3丁目12番地                                                                                                                                                                |

|           |                            | F ターム (参考)            | 2H193 ZA03 ZA07 ZA19 ZB03 ZB07<br>ZC03 ZC20 ZD23 ZF31 ZF34<br>ZF45 ZH46<br>5C006 AA17 AC27 AF21 AF50 BB16<br>BC06 BC20 BF25 FA25<br>5C080 AA10 BB05 DD01 EE29 FF11<br>JJ02 JJ03 JJ04 |

(54) 【発明の名称】 液晶表示素子

## (57) 【要約】

【課題】 絵柄によって動作中の配線容量が変化することに起因する疑似信号の発生を抑圧し、表示品質を向上させる。

【解決手段】 液晶表示素子10は、バッファアンプ11が制御信号用配線S+とスイッチングトランジスタTr5のゲートとの間に接続され、バッファアンプ12が制御信号用配線S-とスイッチングトランジスタTr6のゲートとの間に接続されている。このため、画面全体で一様な中間階調(グレー)の画像を表示する場合と、中間階調の画面内に四角の白いボックスで表示される画像を表示する場合とで、トランジスタTr5、Tr6のドレインに印加される保持容量Cs1、Cs2の保持電圧が異なったとしても、それが配線S+、S-に反映されることがない。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

2本のデータ線を一組とする複数組のデータ線と複数本のゲート線とがそれぞれ交差する交差部に複数の画素が設けられ、前記複数の画素のそれぞれが、

対向する画素電極と共に通電極との間に液晶層が挟持された表示素子と、

入力画像データの画素値と単調的に水平走査周期で値が変化する基準階調データが示す階調値とが一致した時に、一組の前記2本のデータ線のうち一方のデータ線を介して供給される前記基準階調データと同期して水平走査周期内で最小階調値を示す電圧から最大階調値を示す電圧まで単調的にレベル増加する正極性用ランプ信号の電圧をサンプリングして一定期間第1の保持容量に保持する第1のサンプリング及び保持手段と、

前記入力画像データの画素値と前記基準階調データが示す階調値とが一致した時に、一組の前記2本のデータ線のうち他方のデータ線を介して供給される前記基準階調データと同期して水平走査周期内で最小階調値を示す電圧から最大階調値を示す電圧まで単調的にレベル減少する、前記正極性用ランプ信号とは逆極性の負極性用ランプ信号の電圧をサンプリングして一定期間第2の保持容量に保持する第2のサンプリング及び保持手段と、

第1の配線を介して供給される第1の制御信号によりオンに制御されて前記第1の保持容量の第1の保持電圧を前記画素電極に印加する第1のスイッチングトランジスタと、第2の配線を介して供給される第2の制御信号によりオンに制御されて前記第2の保持容量の第2の保持電圧を前記画素電極に印加する第2のスイッチングトランジスタとを、垂直走査周期よりも短い所定の周期で交互にオンとする保持電圧読み出し手段と、

前記第1の配線と前記第1のスイッチングトランジスタとの間に接続されて前記第1の制御信号を前記第1のスイッチングトランジスタに供給する第1のバッファ回路と、

前記第2の配線と前記第2のスイッチングトランジスタとの間に接続されて前記第2の制御信号を前記第2のスイッチングトランジスタに供給する第2のバッファ回路と

を備えることを特徴とする液晶表示素子。

## 【請求項 2】

前記第1及び第2のバッファ回路は、それぞれインバータであることを特徴とする請求項1記載の液晶表示素子。

## 【請求項 3】

前記第1のバッファ回路は、前記第1の配線に接続されている同じ1ラインの複数の前記画素のうち2以上の設定した数の画素内の前記第1のスイッチングトランジスタと前記第1の配線との間に共通に接続され、前記第2のバッファ回路は、前記第2の配線に接続されている同じ1ラインの複数の前記画素のうち2以上の前記設定した数の画素内の前記第2のスイッチングトランジスタと前記第2の配線との間に共通に接続されていることを特徴とする請求項1又は2記載の液晶表示素子。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は液晶表示素子に係り、特に画像データをランプ信号を用いてデジタル-アナログ変換(DA変換)して得られた正極性信号電圧と負極性信号電圧とをそれぞれ2つの保持容量に別々にサンプリング保持し、それら2つの保持容量の正極性及び負極性の各保持電圧を交互に画素電極に印加する構成の画素を備えたアクティブマトリクス型の液晶表示素子に関する。

## 【背景技術】

## 【0002】

近年、プロジェクタ装置やプロジェクションテレビには画像を投影するための中心部品としてL C O S (Liquid Crystal on Silicon)型の液晶表示装置が多く用いられている。このL C O S型の液晶表示装置は、透明電極、液晶層、マトリクス状に配置された光反射性を有する画素電極、及びシリコン基板上に液晶駆動回路が形成された液晶駆動素子などが重なった構造を有している。

## 【0003】

この液晶表示装置では、アナログ映像信号を入力して液晶表示素子を駆動するため、連続して光透過率を制御でき、良好な階調特性が得られる。一方、デジタル信号処理技術の進展と共に液晶駆動素子の外部回路のデジタル化が進んでいる。それに伴い、映像信号としてデジタル信号を液晶駆動回路に入力し、液晶駆動回路側でデジタル映像信号をD/A変換してアナログ映像信号として液晶表示素子に供給するようにした方がシステム全体として好都合である。

## 【0004】

そこで、本出願人は先に、2本のデータ線（列信号線）を一組とする複数組のデータ線と、複数本のゲート線（行走査線）との各交差部にそれぞれ画素をマトリクス状に配置し、それらの各画素においてデジタル映像信号をランプ信号を用いてD/A変換して得られる正極性映像信号と負極性映像信号とを2つの保持容量に別々にサンプリング保持した後、それらの保持電圧を交互に画素電極に印加して液晶表示素子を交流駆動する液晶表示装置を提案した（例えば、特許文献1参照）。

10

## 【0005】

この特許文献1記載の液晶表示装置では、正極性用ビデオスイッチと負極性用ビデオスイッチとを一組とするビデオスイッチが、1ラインの複数の画素の各画素毎に組単位に設けられると共に、各組の正極性用ビデオスイッチが一組のデータ線の一方のデータ線を介して各画素に接続され、負極性用ビデオスイッチが他方のデータ線を介して各画素に接続されている。

20

## 【0006】

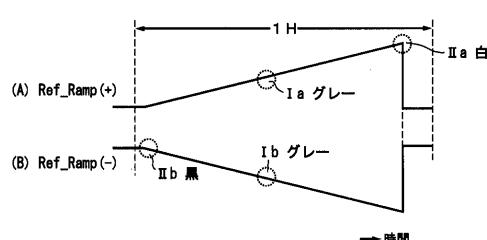

また、1水平走査期間（1H）内で最小階調（黒レベル）から最大階調（白レベル）まで単調的にレベル増加する図6（A）に示す1H周期の正極性ランプ信号Ref\_Ramp（+）と、上記正極性ランプ信号Ref\_Ramp（+）に対し反転関係にあり、かつ、1H内で最小階調（黒レベル）から最大階調（白レベル）まで単調的にレベル減少する図6（B）に示す1H周期の負極性ランプ信号Ref\_Ramp（-）とを、各組の上記正極性用ビデオスイッチと負極性用ビデオスイッチにそれぞれ共通に供給する。各組の上記正極性用ビデオスイッチと負極性用ビデオスイッチとは、各水平走査期間の開始毎に同時にオンとされる。

## 【0007】

そして、正極性ランプ信号Ref\_Ramp（+）及び負極性ランプ信号Ref\_Ramp（-）に同期したクロックをカウントするカウンタから最小階調の階調値から最大階調の階調値まで1H周期で値が変化する基準階調データを出力させ、その基準階調データとラインバッファにラッピングされているデジタル映像信号の1ラインの画素値とをコンパレータにおいて画素単位で比較し、基準階調データと画素値とが一致した時コンパレータから出力される一致パルスによりその画素に対応する同じ組の正極性用ビデオスイッチと負極性用ビデオスイッチとを同時にオフとし、このときの正極性ランプ信号Ref\_Ramp（+）及び負極性ランプ信号Ref\_Ramp（-）の電圧をオフとされた正極性用ビデオスイッチと負極性用ビデオスイッチにゲート線を介して接続された画素に保持することでアナログ映像信号への変換が行われる。

30

## 【0008】

各画素内の正極性用保持容量と負極性用保持容量とは、上記のビデオスイッチのオフ時の正極性ランプ信号Ref\_Ramp（+）及び負極性ランプ信号Ref\_Ramp（-）の電圧をサンプリング保持し、それらの保持電圧を交互に液晶表示素子の画素電極に印加することで液晶表示素子を交流駆動する。

40

## 【0009】

この液晶表示装置は、画素電極に印加する電圧を2つの保持容量に1フレーム期間それぞれ保持しておくことができる所以、液晶表示素子の交流駆動周波数は、垂直走査周波数によらず、画素回路での反転制御周期で自由に設定することができる。これにより、この液晶表示装置によれば、交流駆動周波数を垂直走査周波数よりも極めて高く設定でき、それにより従来に比べて焼き付きを防止でき、信頼性や安定性、シミなどの表示品位低下を防止でき、更にデジタルのパルス幅変調（PWM）方式より階調を正しく表現できるなど

50

の特長が得られる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2009-223289号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、この液晶表示装置では、上記のような特長を有する反面、デジタル映像信号の画素値に応じたランプ信号の電圧をビデオスイッチをオフとしてデータ線にサンプルホールドして画素に供給する方式であり、ランプ信号線に接続されるビデオスイッチのうちオフとされるビデオスイッチの数が入力デジタル映像信号の絵柄によって変動することにより、データ線となるアルミニウム配線による寄生抵抗と、ビデオスイッチ後の画素部の負荷容量が変動して基準となるランプ信号波形が変動する。例えば、一様な中間階調（グレー）画面を表示する場合、図6（A）、（B）に示すランプ信号のグレーの階調レベルIa、Ibで1ラインの複数の画素にそれぞれ対応して設けられた複数のビデオスイッチの全てが一斉にオフとなり、負荷容量が短時間で大きく変化し、この影響でランプ信号波形が変動する。

【0012】

また、画素内の正極性用保持容量の保持電圧と負極性用保持容量の保持電圧とは、2つのスイッチングトランジスタを別々に介して画素電極に印加される構成であるため、絵柄に応じた保持電圧の大小によって2つのスイッチングトランジスタに入力されるスイッチング信号の前縁の傾斜が変化して疑似信号が発生し、表示画像の品質に問題が発生する場合がある。

【0013】

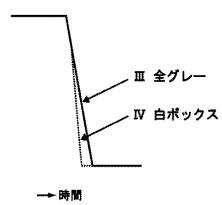

ここで、1ラインの各画素内の正極性用保持容量の保持電圧を画素電極に印加する正極性用スイッチングトランジスタはそれぞれのゲートに印加される同じ第1の制御信号によりスイッチング制御され、負極性用保持容量の保持電圧を画素電極に印加する負極性用スイッチングトランジスタはそれぞれのゲートに印加される同じ第2の制御信号によりスイッチング制御される。第1の制御信号のローレベル期間オフとされる正極性用スイッチングトランジスタは、画面全体で一様な中間階調（グレー）の画像を表示する場合、正極性用保持容量の保持電圧が図6（A）にIaで示す中間レベルであるため、第1の制御信号の立下りは図7に実線IIIで示すように比較的傾斜が緩やかである。これは、負極性用保持容量の保持電圧を画素電極に印加する負極性用スイッチングトランジスタをスイッチング制御する第2の制御信号も同様である。

【0014】

一方、中間階調の画面内に四角の白いボックスで表示される画像を表示する場合は、その白いボックスの画像の正極性用保持容量の保持電圧は図6（A）にIaで示すVddに近い高電圧となるため、正極性用スイッチングトランジスタは一様な中間階調（グレー）画面を表示する場合に比べて速いタイミングでオフとなるため、同じ1ラインの各画素内の正極性用スイッチングトランジスタのゲート容量の総和が小さくなり、第1の制御信号の立下りが図7に点線IVで示すように全グレー表示のときに比較して急峻になる。第1の制御信号の立下りが急峻になると、その分フィードスルーによる電圧変動が大きくなり画素電極電圧が小さくなる現象が発生する。これは黒ボックス時の第2の制御信号の場合も同様である。従って、中間階調の画面内に四角の白いボックスで表示される画像を表示する場合は、画面全体が中間階調（グレー）の画像を表示する場合に比較して、画素電極電圧が小さくなりその分暗くなるためそれが表示画像に反映されてしまう。

【0015】

本発明は上記の点に鑑みなされたもので、絵柄によって動作中の配線容量が変化することに起因する疑似信号の発生を抑圧し、表示品質を向上させた液晶表示素子を提供するこ

10

20

30

40

50

とを目的とする。

【課題を解決するための手段】

【0016】

上記の目的を達成するため、本発明の液晶表示素子は、2本のデータ線を一組とする複数組のデータ線と複数本のゲート線とがそれぞれ交差する交差部に複数の画素が設けられ、複数の画素のそれぞれが、

対向する画素電極と共に通電極との間に液晶層が挟持された表示素子と、入力画像データの画素値と単調的に水平走査周期で値が変化する基準階調データが示す階調値とが一致した時に、一組の2本のデータ線のうち一方のデータ線を介して供給される基準階調データと同期して水平走査周期内で最小階調値を示す電圧から最大階調値を示す電圧まで単調的にレベル増加する正極性用ランプ信号の電圧をサンプリングして一定期間第1の保持容量に保持する第1のサンプリング及び保持手段と、入力画像データの画素値と基準階調データが示す階調値とが一致した時に、一組の2本のデータ線のうち他方のデータ線を介して供給される基準階調データと同期して水平走査周期内で最小階調値を示す電圧から最大階調値を示す電圧まで単調的にレベル減少する、正極性用ランプ信号とは逆極性の負極性用ランプ信号の電圧をサンプリングして一定期間第2の保持容量に保持する第2のサンプリング及び保持手段と、第1の配線を介して供給される第1の制御信号によりオンに制御されて第1の保持容量の第1の保持電圧を画素電極に印加する第1のスイッチングトランジスタと、第2の配線を介して供給される第2の制御信号によりオンに制御されて第2の保持容量の第2の保持電圧を画素電極に印加する第2のスイッチングトランジスタとを、垂直走査周期よりも短い所定の周期で交互にオンとする保持電圧読み出し手段と、第1の配線と第1のスイッチングトランジスタとの間に接続されて第1の制御信号を第1のスイッチングトランジスタに供給する第1のバッファ回路と、第2の配線と第2のスイッチングトランジスタとの間に接続されて第2の制御信号を第2のスイッチングトランジスタに供給する第2のバッファ回路とを備えることを特徴とする。

【0017】

また、上記の目的を達成するため、本発明の液晶表示素子は、第1及び第2のバッファ回路は、それぞれインバータであることを特徴とする。

【0018】

また、上記の目的を達成するため、本発明の液晶表示素子は、第1のバッファ回路は、第1の配線に接続されている同じ1ラインの複数の画素のうち2以上の設定した数の画素内の第1のスイッチングトランジスタと第1の配線との間に共通に接続され、第2のバッファ回路は、第2の配線に接続されている同じ1ラインの複数の画素のうち2以上の設定した数の画素内の第2のスイッチングトランジスタと第2の配線との間に共通に接続されていることを特徴とする。

【発明の効果】

【0019】

本発明によれば、絵柄によって動作中の配線容量が変化することに起因する疑似信号の発生を抑圧し、絵柄によって表示画像が変化することを防止し、表示品質を向上することができる。

【図面の簡単な説明】

【0020】

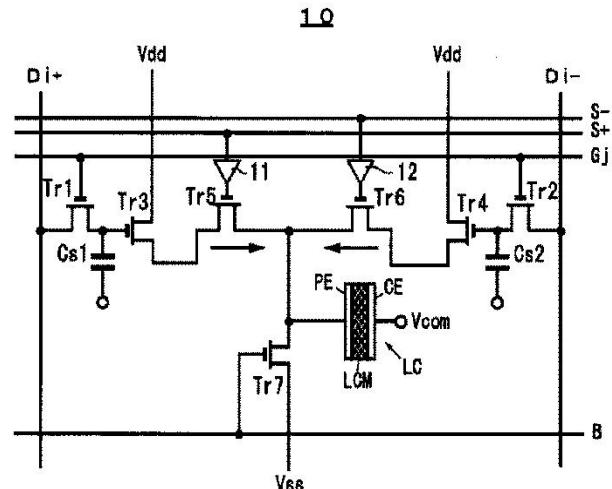

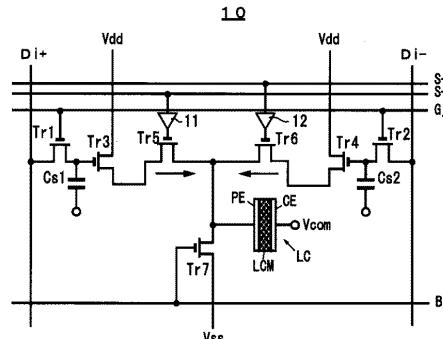

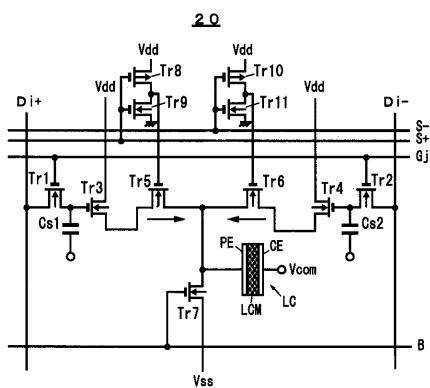

【図1】本発明の液晶表示素子の第1の実施の形態の回路図である。

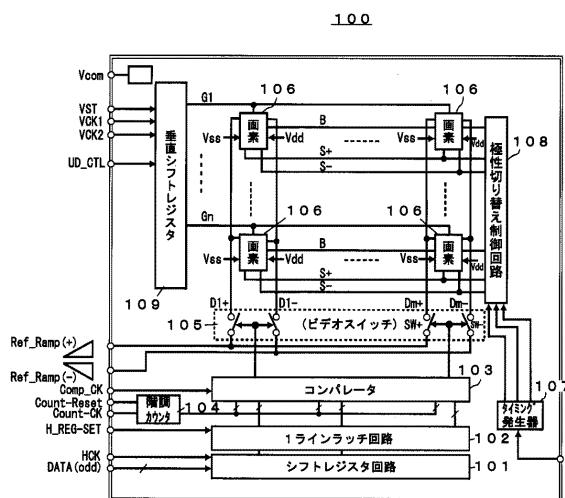

【図2】本発明の液晶表示素子を備える液晶表示装置の一例の構成図である。

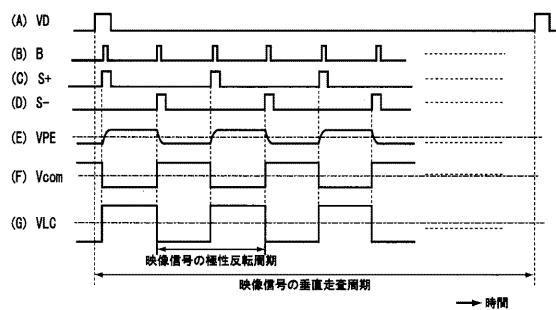

【図3】図2の液晶表示装置の交流駆動制御の概要の説明用タイミングチャートである。

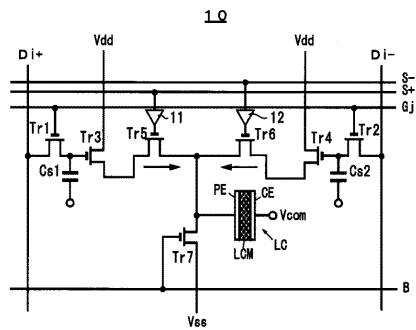

【図4】本発明の液晶表示素子の第2の実施の形態の回路図である。

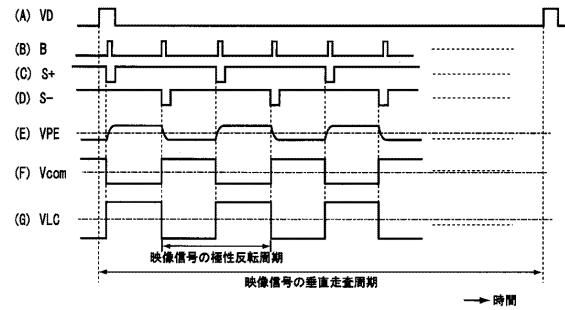

【図5】図4の動作説明用タイミングチャートである。

【図6】液晶表示装置で使用するランプ信号波形を示す図である。

【図7】従来の液晶表示素子の課題を説明する信号波形図である。

【発明を実施するための形態】

10

20

30

40

50

## 【0021】

次に、本発明の実施の形態について図面を参照して説明する。

## 【0022】

## (第1の実施の形態)

図1は、本発明になる液晶表示素子の第1の実施の形態の回路図、図2は、本発明になる液晶表示素子を備える液晶表示装置の一例の構成図を示す。

## 【0023】

本発明になる液晶表示素子を備える液晶表示装置は、図2に100で示すように、シフトレジスタ回路101、1ラインラッチ回路102、コンパレータ103、階調カウンタ104、アナログスイッチであるビデオスイッチ105、2本のデータ線(列信号線)を一組とするm組(mは1ラインの画素数)のデータ線(D1+～Dm+)及び(D1-～Dm-)と、n本(nは垂直方向の画素数)のゲート線(行走査線)G1～Gnとの各交差部にそれぞれ配置された全部でm×n個の画素106、タイミング発生器107、極性切り替え制御回路108、及び垂直シフトレジスタ109を含む構成とされている。

10

## 【0024】

シフトレジスタ回路101、1ラインラッチ回路102、コンパレータ103、及び階調カウンタ104は、水平ドライバ回路を構成している。なお、コンパレータ103は、図1では図示の簡単のために一つのブロックで示しているが、実際には各画素列毎に設けられている。ビデオスイッチ105は、各画素列毎に正極性用及び負極性用の2つ1組のサンプリング用ビデオスイッチが配置された構成である。極性切り替え制御回路108は、タイミング発生器107からのタイミング信号に基づいて、配線S+に正極性ゲート制御信号、配線S-に負極性ゲート制御信号、配線Bに負荷特性制御信号をそれぞれ出力する。垂直シフトレジスタ109は、行走査線G1～Gnに対して行選択信号を1水平走査周期で順次出力して、行走査線G1～Gnを1水平走査周期で各行走査線単位で順次選択する。

20

## 【0025】

この液晶表示装置100の基本的な構成は特許文献1に記載の液晶表示装置と同様であるが、各画素106が図1に示す本実施形態の液晶表示素子10である点に特徴がある。

## 【0026】

まず、液晶表示装置100の概略動作について説明する。水平同期信号に同期した、複数ビットの画素データ(DATA)が時系列的に合成されたデジタル映像信号は、シフトレジスタ回路101で1ライン分のデータとして順次展開され、1ライン分の展開が終了した時点で、1ラインラッチ回路102でラッチされる。1ラインラッチ回路102は、シフトレジスタ回路101から出力される1ライン期間の画素データDATAを保持した後、各画素列のコンパレータ103の第1のデータ入力部に供給する。

30

## 【0027】

階調カウンタ104は、水平同期信号に同期したクロックCount-CKをカウントして、階調値が1水平走査期間(1H)内で最小値から最大値まで一巡するカウント値(基準階調データ)C-outを水平走査期間毎に出力し、各画素列のコンパレータ103の第2のデータ入力部に供給する。コンパレータ103は、第1のデータ入力部の入力画素データDATAの値と第2のデータ入力部の入力基準階調データC-outの値(階調値)とを比較し、両者の値が一致したタイミングで一致パルスを生成して出力する。

40

## 【0028】

ビデオスイッチ105を構成する正極性用及び負極性用の2つ1組のサンプリング用ビデオスイッチのうち、正極性用のサンプリング用ビデオスイッチは、入力側共通配線に図示しないランプ信号発生器から正極性用ランプ信号である基準ランプ電圧Ref\_Ramp(+)が印加される。一方、負極性用のサンプリング用ビデオスイッチは、入力側共通配線に図示しないランプ信号発生器から負極性用ランプ信号である基準ランプ電圧Ref\_Ramp(-)が印加される。

## 【0029】

50

前述したように、上記の基準ランプ電圧Ref\_Ramp(+)及びRef\_Ramp(-)のうち、Ref\_Ramp(+)は、図6(A)に示したように1H内で映像の黒レベルから白レベルにレベルが単調的に増加する方向に変化する1H周期の正極性掃引信号である。一方、上記の基準ランプ電圧Ref\_Ramp(-)は、図6(B)に示したように1H内で映像の黒レベルから白レベルにレベルが単調的に減少する方向に変化する1H周期の負極性掃引信号である。従って、基準ランプ電圧Ref\_Ramp(+)とRef\_Ramp(-)は、所定の基準電位について反転関係となっている。

#### 【0030】

m組のビデオスイッチ105は、SW-Start信号を受け、各水平走査期間の開始時点で同時にオンとなった後、対応する画素のコンパレータ103から一致パルスを受けた時点でオフに移行するように画素単位に開閉制御される。正極性用及び負極性用の2つ1組のサンプリング用ビデオスイッチが、上記一致パルスを受けて同時にオフした時点の基準ランプ電圧Ref\_Ramp(+)とRef\_Ramp(-)の対応レベルが同時にサンプリングされて、それぞれ前述した正極性映像信号、負極性映像信号として、その画素列の画素データ線Di+、Di-に出力される。この時点の基準ランプ電圧レベルは、画素データDATAをデジタル-アナログ変換して得られたアナログ電圧である。

10

#### 【0031】

m組のビデオスイッチ105は、各水平走査期間の開始毎にすべてが同時にオンとされるが、オフになるタイミング、すなわち基準ランプ電圧をサンプル・ホールドするタイミングはそのときに表示しようとする絵柄によって対応して設けられた画素毎に異なり、すべて同時の時もあれば別々のときもある。オフになる順序も固定されているわけではなく、絵柄によってその都度オフの順番は異なる。このような液晶表示装置100では、ランプ信号を用いたDA変換方式の動作により直線性が良いなどの特長がある。

20

#### 【0032】

次に、図1中の画素106を構成する本実施の形態の液晶表示素子10について説明する。液晶表示素子10は、正極性の映像信号及び負極性の映像信号を書き込むための画素選択トランジスタTr1及びTr2と、各々の極性の映像信号電圧を並列的に保持する独立した2つの保持容量Cs1及びCs2と、トランジスタTr3～Tr7と、バッファ回路の一例としてのバッファアンプ11及び12と、表示素子LCとからなる。なお、トランジスタTr1～Tr7は、ここではすべてNチャンネル電界効果トランジスタ(FET)であるが、これに限定されるものではない。表示素子LCは、互いに対向して配置された画素電極PEと共に電極CEとの間に液晶層(表示体)LCMが挟持された周知の構造である。トランジスタTr3とTr7、及びトランジスタTr4とTr7は、それぞれ所謂ソースフォロワ・バッファであり、トランジスタTr3、Tr4が信号入力トランジスタ、トランジスタTr7が定電流源負荷として機能する。トランジスタTr7は極性切り替えスイッチングトランジスタTr5、Tr6の後段、すなわち画素電極PEノードに配置され、正極性、負極性のソースフォロワ・バッファ双方の負荷として共通に機能する構成となっている。MOSトランジスタのソースフォロワ・バッファの入力抵抗はほぼ無限大で、保持容量Cs1及びCs2の蓄積電荷はリークすることなく、1垂直走査期間後に信号が新たに書き込まれるまで保持される。

30

#### 【0033】

また、トランジスタTr5、Tr6は、バッファアンプ11、12の出力端子と、画素電極PE間とを接続する。画素電極PEに対してバッファアンプ11、12の出力の導通・非導通を個別に制御することが可能な構成となっている。

40

#### 【0034】

また、画素部データ線は、各画素について正極性用データ線Di+、負極性用データ線Di- (ただし、iは1～mのうちの任意の自然数)の2本一組で構成され、図示しないデータ線駆動回路でサンプリングされた互いに極性の異なる映像信号が供給される。画素選択トランジスタTr1、Tr2の各ドレイン端子は各々正極性用データ線Di+、負極性用データ線Di-に接続され、各ゲート端子は同一行について行走査線(ゲート線)Gjに接続

50

されている。また、配線 B がトランジスタ Tr 7 のゲートに接続されている。また、配線 S+、S- はゲート制御信号用の配線で、それぞれバッファアンプ 11、12 を通してトランジスタ Tr 5、Tr 6 のゲートに別々に接続されている。更に、行走査線 Gj が同じ行の複数の画素のトランジスタ Tr 1 及び Tr 2 にそれぞれ共通接続されている。

【0035】

次に、この液晶表示素子 10 の交流駆動制御の概要について図 3 のタイミングチャートと共に説明する。図 3 (A) は、垂直同期信号 VD を示し、図 3 (B) は、図 1 の液晶表示素子 10 におけるトランジスタ Tr 7 のゲートに印加される配線 B の負荷特性制御信号を示す。また、図 3 (C) は、上記液晶表示素子 10 における正極性側駆動電圧を転送するスイッチングトランジスタ Tr 5 のゲートに印加される配線 S+ のゲート制御信号、同図 (D) は、上記液晶表示素子 10 における負極性側駆動電圧を転送するスイッチングトランジスタ Tr 6 のゲートに印加される配線 S- のゲート制御信号の各信号波形を示す。

【0036】

図 1 において、図 3 (C) に示す配線 S+ のゲート制御信号がハイレベルの期間、正極性側スイッチングトランジスタ Tr 5 がオンとなり、この期間に配線 B に供給される負荷特性制御信号を図 3 (B) に示すようにハイレベルとすると、ソースフォロワ・バッファがアクティブとなり、画素電極 PE ノードが正極性の映像信号レベルに充電される。画素電極 PE の電位が完全に充電された状態となった時点で、配線 B の負荷特性制御信号をローレベルとし、かつ、そのとき配線 S+ のゲート制御信号もローレベルに切り替えると、画素電極 PE はフローティングとなり、液晶容量に正極性駆動電圧が保持される。

【0037】

一方、図 3 (D) に示す配線 S- のゲート制御信号がハイレベルの期間、負極性側スイッチングトランジスタ Tr 6 がオンとなり、この期間に配線 B に供給される負荷特性制御信号を同図 (B) に示すようにハイレベルとすると、ソースフォロワ・バッファがアクティブとなり、画素電極 PE ノードが負極性の映像信号レベルに充電される。画素電極 PE の電位が完全に充電された状態となった時点で、配線 B の負荷特性制御信号をローレベルとし、かつ、そのとき配線 S- のゲート制御信号もローレベルに切り替えると、画素電極 PE はフローティングとなり、液晶容量に負極性駆動電圧が保持される。

【0038】

以下、上記のスイッチングトランジスタ Tr 5 及び Tr 6 を交互にオンとするスイッチングに同期して、配線 B の負荷特性制御信号によりトランジスタ Tr 7 を間欠的にアクティブとする動作を繰り返すことで、表示素子 LC の画素電極 PE には正極性と負極性の各映像信号で交流化された駆動電圧 VPE が図 3 (E) に示すように印加される。液晶表示素子 10 は保持電荷を直接画素電極 PE に転送するのではなく、ソースフォロワ・バッファを介して電圧を供給する構成のため、正負極性での繰り返し充放電を行っても電荷の中和の問題はなく、電圧レベルの減衰がない駆動が実現できる。

【0039】

また、図 3 (F) に示す Vcom は、液晶表示装置の対向基板に形成した共通電極 CE に印加する電圧を表している。液晶層 LCM の実質的な交流駆動電圧は、この共通電極 CE の印加電圧 Vcom と画素電極 PE の印加電圧との差電圧である。図 3 (F) に示すように、共通電極 CE の印加電圧 Vcom は、画素電極電位の反転基準レベル Vc とほぼ等しい基準レベルに対して、画素極性切り替えと同期して反転されている。これにより、共通電極 CE の印加電圧 Vcom と画素電極 PE の印加電圧との電位差の絶対値が常に同一となり、液晶層 LCM には図 3 (G) に示すような直流成分の無い交流電圧 VLC が印加される。このように、液晶表示素子 10 では、共通電極 CE の印加電圧を画素電極 PE と逆相で切り替えることによって、画素電極 PE 側に供給する電圧の振幅を小さくするため、駆動回路側のトランジスタ耐圧や消費電力を低減できる。

【0040】

また、保持容量 Cs1、Cs2 にそれぞれサンプリング保持された正極性、負極性の各映像信号電圧 (具体的には基準ランプ電圧 Ref\_Ramp (+) と Ref\_Ramp (-) の電圧) は、高入力抵抗

10

20

30

40

50

のソースフォロワ回路であるトランジスタ Tr 3、Tr 4 を介して読み出され、図 3 (C)、(D) に示したように配線 S+、S- に交互に供給されるゲート制御信号によりオンとされるスイッチングトランジスタ Tr 5、Tr 6 により交互に選択されて画素電極 PE に正極性、負極性に反転する図 3 (E) に示した駆動電圧 VPE として印加される。この図 1 に示した液晶表示素子 10 は、1 垂直走査期間 (1 フレーム) に 1 度、保持容量 Cs1、Cs2 に正極性、負極性の各映像信号電圧を書き込んでしまえば、次のフレームの映像信号電圧が保持されるまでの 1 フレーム期間、何回でも保持容量 Cs1、Cs2 から映像信号電圧を読み出し、トランジスタ Tr 5、Tr 6 を交互に切り替えて表示素子 LC を交流駆動できる。従って、液晶表示素子 10 は、映像信号の書き込み周期とは独立に垂直走査周波数の制約のない、高い駆動周波数で表示素子 LC を交流駆動することができる。

10

#### 【0041】

以上の動作は前述した特許文献 1 の画素の動作と同様であるが、本実施の形態では、特許文献 1 に記載した画素の構成に加えて、バッファアンプ 11 及び 12 を設けているため、疑似信号の発生を抑制し、表示品質を向上させることができる。以下、このことについて説明する。

#### 【0042】

従来は画面全体で一様な中間階調 (グレー) の画像を表示する場合と、中間階調の画面内に四角の白いボックスで表示される画像を表示する場合とでは、正極性用保持容量 (図 1 の Cs1 に相当) の保持電圧が異なるために、配線 S+ に接続される寄生容量が異なってしまい、それにより図 7 に示したように配線 S+ のゲート制御信号の立下りの傾斜が異なる波形となっていた (これは、全グレーと黒ボックス時の配線 S- のゲート制御信号も同様)。この立下りの傾斜が異なるゲート制御信号の波形のため、トランジスタ Tr 5 のフィードスルーによる電圧変動が異なり、それが画像に現れる結果となっていた。

20

#### 【0043】

これに対し、本実施の形態の液晶表示素子 10 では、バッファアンプ 11 が配線 S+ とトランジスタ Tr 5 のゲートとの間に接続されているため、画面全体で一様な中間階調 (グレー) の画像を表示する場合と、中間階調の画面内に四角の白ボックスで表示される画像を表示する場合とで、トランジスタ Tr 5 のドレインに印加される正極性用保持容量 Cs1 の保持電圧が異なったとしても、それが配線 S+ に反映されることがない。

30

#### 【0044】

同様に、本実施の形態の液晶表示素子 10 では、バッファアンプ 12 が配線 S- とトランジスタ Tr 6 のゲートとの間に接続されているため、画面全体で一様な中間階調 (グレー) の画像を表示する場合と、中間階調の画面内に四角の黒ボックスで表示される画像を表示する場合とで、トランジスタ Tr 6 のドレインに印加される負極性用保持容量 Cs2 の保持電圧が異なったとしても、それが配線 S- に反映されることがない。

40

#### 【0045】

従って、本実施の形態の液晶表示素子 10 によれば、画面全体で一様な中間階調 (グレー) の画像を表示する場合と、中間階調の画面内に四角の白いボックスで表示される画像を表示する場合のいずれの場合も、配線 S+、S- の各ゲート制御信号はその立下りの傾斜が同じ波形となる。従って、本実施の形態の液晶表示素子 10 によれば、画面全体で一様な中間階調 (グレー) の画像を表示する場合と、中間階調の画面内に四角の白いボックスで表示される画像における中間階調の画像を表示する場合のいずれにおいても、画素電極 PE の印加電圧は中間階調 (グレー) の画像を表示する同じ電圧となり、トランジスタ Tr 5、Tr 6 のフィードスルーによる電圧変動による表示画像への影響を受けないようにできる。すなわち、本実施の形態の液晶表示素子 10 によれば、絵柄によって動作中の配線容量が変化することに起因する疑似信号の発生を抑圧し、絵柄によって表示画像が変化することを防止し、表示品質を向上することができる。

#### 【0046】

##### (第 2 の実施の形態)

次に、本発明の第 2 の実施の形態について説明する。

50

## 【0047】

図4は、本発明になる液晶表示素子の第2の実施の形態の回路図を示す。同図中、図1と同一構成部分には同一符号を付し、その説明を省略する。図4に示す本実施の形態の液晶表示素子20は、第1の実施の形態の液晶表示素子10と同様に、図2に示した液晶表示装置100における画素106として用いることができる液晶表示素子であり、バッファアンプ11、12の代わりに、バッファ回路としてインバータを用いた点に特徴がある。

## 【0048】

すなわち、図4において、互いにドレイン同士とゲート同士とが接続されたPチャンネルMOS型電界効果トランジスタ（以下、PMOSトランジスタという）Tr8とNチャンネルMOS型電界効果トランジスタ（以下、NMOSトランジスタという）Tr9とは第1のCMOSインバータを構成しており、PMOSトランジスタTr8のゲートとNMOSトランジスタTr9のゲートとはそれぞれ配線S+に接続され、PMOSトランジスタTr8のドレインとNMOSトランジスタTr9のドレインとはそれぞれスイッチングトランジスタTr5のゲートに接続されている。

## 【0049】

また、互いにドレイン同士とゲート同士とが接続されたPMOSトランジスタTr10とNMOSトランジスタTr11とは第2のCMOSインバータを構成しており、PMOSトランジスタTr10のゲートとNMOSトランジスタTr11のゲートとはそれぞれ配線S-に接続され、PMOSトランジスタTr10のドレインとNMOSトランジスタTr11のドレインとはそれぞれスイッチングトランジスタTr6のゲートに接続されている。

## 【0050】

次に、本実施の形態の動作について、図5のタイミングチャートと共に説明する。なお、図5（A）、（B）、（E）、（F）、（G）は、図3（A）、（B）、（E）、（F）、（G）と同じ信号波形であり、その説明を省略する。一方、図5（C）、（D）に示す配線S+、S-のゲート制御信号はCMOSインバータにより反転されるため、図3（C）、（D）に示した配線S+、S-のゲート制御信号の逆極性の信号となっている。

## 【0051】

図4において、配線S+を介して入力される図5（C）に示す正極性用ゲート制御信号がローレベルになると、そのローレベル期間は第1のCMOSインバータを構成するPMOSトランジスタTr8及びNMOSトランジスタTr9のうちTr8のみがオンとなり、それによりトランジスタTr5のゲートにVddに近いハイレベルの信号が印加されるため、トランジスタTr5がオンとされる。トランジスタTr5がオンとなると、正極性用保持容量Cs1に保持されていた正極性信号電圧がソースフォロワトランジスタTr3及びスイッチングトランジスタTr5を通して画素電極PEに印加される。その後、図5（C）に示す正極性用ゲート制御信号がハイレベルになると、第1のCMOSインバータを構成するPMOSトランジスタTr8及びNMOSトランジスタTr9のうちTr9のみがオンとなり、それによりトランジスタTr5のゲートにGND電圧に近いローレベルの信号が印加されるため、トランジスタTr5がオフとされ、正極性信号電圧の画素電極PEへの印加が遮断される。

## 【0052】

続いて、配線S-を介して入力される図5（D）に示す負極性用ゲート制御信号がローレベルになり、そのローレベル期間、第2のCMOSインバータを構成するPMOSトランジスタTr10及びNMOSトランジスタTr11のうちTr10のみがオンとなり、それによりトランジスタTr6のゲートにVddに近いハイレベルの信号が印加されるため、トランジスタTr6がオンとされる。トランジスタTr6がオンとなると、負極性用保持容量Cs2に保持されていた負極性信号電圧がソースフォロワトランジスタTr4及びスイッチングトランジスタTr6を通して画素電極PEに印加される。その後、図5（D）に示す負極性用ゲート制御信号がハイレベルになると、第2のCMOSインバータを構

10

20

30

40

50

成するPMOSトランジスタTr10及びNMOSトランジスタTr11のうちTr10のみがオンとなり、それによりトランジスタTr6のゲートにGND電圧に近いローレベルの信号が印加されるため、トランジスタTr6がオフとされ、負極性信号電圧の画素電極PEへの印加が遮断される。

#### 【0053】

本実施の形態の液晶表示素子20は、配線S+、S-とトランジスタTr5、Tr6のゲートとの間に、バッファアンプ11、12の代わりにCMOSインバータを接続する構成としており、CMOSインバータもバッファアンプ11、12と同様にトランジスタTr5、Tr6の状態を配線S+、S-に反映させることができないので、第1の実施の形態の液晶表示素子10と同様に、保持容量Cs1、Cs2から配線S+、S-への影響を遮断することができ、絵柄によって表示画像が変化することを防止できる。

10

#### 【0054】

なお、第1の実施の形態の液晶表示素子10ではバッファアンプ11及び12を設けているが、バッファアンプ11及び12を構成するには多数のトランジスタが必要になり、スペースが限られている画素内に配置するには不利である。これに対し、本実施の形態の液晶表示素子20で設けている第1及び第2のCMOSインバータはそれぞれ2個のトランジスタで構成できるので、画素内への配置がバッファアンプ11及び12を設ける場合に比べて容易である。

#### 【0055】

なお、本発明は以上の実施の形態に限定されるものではなく、例えば、図4の第1及び第2のCMOSインバータを同一の配線S+、S-に接続されている水平方向に隣接する複数の画素（例えば2画素）で共有することもできる。この場合は、画素に追加する回路を第1及び第2の実施の形態に比べてより少なくすることができる。なお、水平方向に隣接する複数の画素でインバータを共有する構成とした場合も、以上の各実施の形態と同様に絵柄による表示画像の変化を防止することができる。

20

#### 【符号の説明】

#### 【0056】

10、20 液晶表示素子

30

11、12 バッファアンプ

100 液晶表示装置

103 コンパレータ

104 階調カウンタ

105 ビデオスイッチ

106 画素（液晶表示素子）

108 極性切り替え制御回路

109 垂直シフトレジスタ

Tr1、Tr2 画素選択トランジスタ

Tr3、Tr4 ソースフォロワトランジスタ

Tr5、Tr6 スイッチング用トランジスタ

Tr7 定電流負荷用トランジスタ

40

Tr8、Tr9 第1のCMOSインバータを構成するトランジスタ

Tr10、Tr11 第2のCMOSインバータを構成するトランジスタ

D1+～Dm+、Di+ 正極性用データ線（列信号線）

D1-～Dm-、Di- 負極性用データ線（列信号線）

G1～Gn、Gj ゲート線（行走査線）

S+、S- ゲート制御信号用配線

LC 表示素子

PE 画素電極

CE 共通電極

LCM 液晶層

50

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 2 F 1/133 5 5 0

テーマコード(参考)

|                |                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示元件                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2012185339A</a>                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2012-09-27 |

| 申请号            | JP2011048468                                                                                                                                                                                                                                                                                                                   | 申请日     | 2011-03-07 |

| [标]申请(专利权)人(译) | JVC 建伍株式会社                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | JVC建伍公司                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 樋口 潤                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 樋口 潤                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/36 G09G3/20.624.B G09G3/20.621.B G09G3/20.611.J G09G3/20.641.J G02F1/133.550                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H193/ZA03 2H193/ZA07 2H193/ZA19 2H193/ZB03 2H193/ZB07 2H193/ZC03 2H193/ZC20 2H193/ZD23 2H193/ZF31 2H193/ZF34 2H193/ZF45 2H193/ZH46 5C006/AA17 5C006/AC27 5C006/AF21 5C006/AF50 5C006/BB16 5C006/BC06 5C006/BC20 5C006/BF25 5C006/FA25 5C080/AA10 5C080/BB05 5C080/DD01 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                      |         |            |

### 摘要(译)

解决的问题：抑制由于操作期间布线电容的变化而导致的伪信号的产生，该伪电容取决于图案，并提高显示质量。在液晶显示元件中，缓冲放大器11连接在控制信号线S+与开关晶体管Tr5的栅极之间，缓冲放大器12连接在控制信号线S-与开关晶体管Tr6的栅极之间。由于这个原因，晶体管Tr5和Tr6用于在整个屏幕上显示具有均匀灰度（灰色）的图像，并且用于在具有中间灰度的屏幕上显示以白色方框显示的图像。即使施加到漏极的保持电容器Cs1和Cs2的保持电压彼此不同，它们也不会在布线S+和S-上反射。[选型图]图1