(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-170376

(P2011-170376A)

(43) 公開日 平成23年9月1日(2011.9.1)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36  | 2 H 1 9 3   |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 5 C 0 0 6   |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20  | 5 C 0 8 0   |

|                             | GO2F 1/133 | 5 7 5       |

|                             | GO2F 1/133 | 5 1 0       |

審査請求 有 請求項の数 10 O L (全 19 頁) 最終頁に続く

|            |                                     |          |                                                              |

|------------|-------------------------------------|----------|--------------------------------------------------------------|

| (21) 出願番号  | 特願2011-90727 (P2011-90727)          | (71) 出願人 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部 1753 番地       |

| (22) 出願日   | 平成23年4月15日 (2011.4.15)              | (71) 出願人 | 000233594<br>株式会社ルネサス北日本セミコンダクタ<br>北海道亀田郡七飯町字中島 145 番地       |

| (62) 分割の表示 | 特願2004-150016 (P2004-150016)<br>の分割 | (74) 代理人 | 100089071<br>弁理士 玉村 静世                                       |

| 原出願日       | 平成16年5月20日 (2004.5.20)              | (72) 発明者 | 山口 聰<br>北海道千歳市泉沢 1007 番地 39 株式<br>会社ルネサス北日本セミコンダクタ内<br>遠藤 祐弘 |

|            |                                     | (72) 発明者 | 北海道千歳市泉沢 1007 番地 39 株式<br>会社ルネサス北日本セミコンダクタ内                  |

最終頁に続く

(54) 【発明の名称】 液晶表示駆動装置、液晶表示システムおよび液晶駆動用半導体集積回路装置

## (57) 【要約】

【課題】 D A 変換回路を内蔵しデジタル画像データをアナログ階調電圧に変換してカラー液晶パネルの信号線(ソース線)に印加される電圧を出力する液晶ドライバ(液晶駆動用半導体集積回路)の小型化を図る。

【解決手段】 階調電圧に変換された画像信号を出力する最終段の出力アンプ(160 : AMP1 ~ AMP480)を複数のグループに分け、画像データを階調電圧に変換するD A 変換回路(160 : DAC1 ~ DAC40)を上記グループに共通の回路として設けて、グループを切り替えながらD A 変換回路を時分割動作させ、上記最終段の出力アンプは同一色の画像信号に関わるもの同士を選択してグループ化し、D A 変換回路と出力アンプとの間にはセレクタ機能を設けてD A 変換回路で階調電圧に変換された画像信号を所望のホールド回路に振り分けるようにした。

【選択図】 図2

## 【特許請求の範囲】

## 【請求項 1】

複数個組み合わせて使用されることでカラー表示装置の駆動が可能な液晶表示駆動装置は、

第1の端子と、

第2の端子と、

第3の端子と、

第1のデータラッチ回路と、

第2のデータラッチ回路と、

変換回路と、

サンプルホールド回路と、

出力アンプ回路と、を有し、

10

前記第1の端子には、画像データの伝送開始通知制御信号が入力され、

前記第2の端子には、前記画像データの入力許可信号が入力され、

前記第3の端子には、前記画像データが入力され、

前記第1のデータラッチ回路は、前記第3の端子より入力された前記画像データを順次取り込み、

第2のデータラッチ回路は、前記第1データラッチ回路に取り込まれた前記画像データを取り込み、一括して前記変換回路に送り、

前記変換回路は、前記第2のデータラッチ回路より送られてきた前記画像データ対応するアナログの駆動電圧に変換して出力し、

20

前記サンプルホールド回路は、前記カラー表示装置の前記駆動に使用される出力端子の出力端子数に対応した数だけ設けられ、前記変換回路から出力された前記アナログの駆動電圧を保持し、

前記出力アンプ回路は、前記出力端子数に対応した数だけ設けられ前記サンプルホールド回路に保持された前記アナログの駆動電圧を前記出力端子から出力し、

画像データの伝送開始通知制御信号が入力される第1の端子と、

前記第1の端子に前記伝送開始通知制御信号が入力され前記第2の端子に前記入力許可信号が入力されることによって前記第3の端子から入力される画像データを前記第1のデータラッチ回路に取り込み可能とされ、

30

前記変換回路は、前記サンプルホールド回路および前記出力アンプの複数のグループに共通の回路として設けられることによって時分割動作され、

前記変換回路により一度に変換される前記画像データは、前記カラー表示装置によるカラー表示の赤色と緑色と青色のいずれかの同一色の画像データであり、

前記画像データは同一色の複数の画像データが連続して入力され前記変換回路で前記アナログの駆動電圧に変換され、前記駆動電圧は前記サンプルホールド回路に保持され前記出力アンプに入力されることを特徴とする液晶表示駆動装置。

## 【請求項 2】

前記第1のデータラッチ回路への前記画像データの取り込みのデータラッチタイミングを示すクロック信号が入力される第4の端子と、

40

前記第1のデータラッチ回路に取り込まれた前記画像データが全て前記第2のデータラッチ回路から前記変換回路に送られ、前記変換回路によって前記アナログの駆動電圧に変換されて前記サンプルホールド回路および前記出力アンプを介して前記カラー表示装置に出力されたことを示す画像出力完了信号を出力する第5の端子と、

前記第4の端子より入力されるクロック信号を計数するカウンタとを有し、

前記画像データの前記入力許可信号の入力後に前記カウンタは前記クロック信号の計数を開始し、前記カウンタの計数値が所定値に達したときに前記画像出力完了信号を前記第5の端子に出力し、前記画像出力完了信号は複数個組み合わせて使用される他のカラー表示装置のうちの1つのカラー表示装置の画像データの入力許可信号として用いられることを特徴とする請求項1に記載の液晶表示駆動装置。

50

**【請求項 3】**

前記画像データは、前記カラー表示の前記赤色の画像データと前記緑色の画像データと前記青色の画像データであり、

前記出力端子および前記出力アンプは、前記赤色の画像信号に関わるものと、前記緑色の画像信号に関わるものと、前記青色の画像信号に関わるものとが、所定の順序で繰り返し配置され、

前記出力アンプは、2つおきに配置されているもの同士が同一色のグループとされることを特徴とする請求項2に記載の液晶表示駆動装置。

**【請求項 4】**

前記第1端子に入力された初回の前記画像データの前記伝送開始通知制御信号と2回目の画像データの前記伝送開始通知制御信号との間に前記第4の端子に入力されたクロック信号の数を保持するレジスタと、

前記レジスタに保持された数と前記カウンタにより計数されたクロック信号の数とを比較する比較手段とを備え、

前記第1の端子に入力される前記伝送開始通知制御信号が、初回の前記伝送開始通知制御信号と2回目の前記伝送開始通知制御信号との間のクロック信号数に対応する時間よりも長くなったときに、前記カウンタの計数値が前記レジスタに保持された数よりも数多くなり、前記第2のデータラッチ回路に対してデータの取り込みを指示する信号を与えるように構成されていることを特徴とする請求項2に記載の液晶表示駆動装置。

**【請求項 5】**

前記赤色と前記緑色と前記青色から選択された第1の色の複数の画像データが連続して前記第3の端子に入力された後、前記赤色と前記緑色と前記青色から選択された第2の色の複数の画像データが連続して前記第3の端子に入力される前に該第2の色に対応した画素のガンマ特性に応じて前記変換回路に供給される階調電圧値を調整するガンマ補正がなされるように構成されていることを特徴とする請求項2～請求項4のいずれかに記載の液晶表示駆動装置。

**【請求項 6】**

外部より印加された電圧を分圧して複数の階調電圧を生成し前記変換回路へ供給する階調電圧生成回路を備え、

前記階調電圧生成回路に前記外部から印加される前記電圧が変化されることにより、前記ガンマ補正がなされるように構成されていることを特徴とする請求項5に記載の液晶表示駆動装置。

**【請求項 7】**

請求項5に記載の構成を有する複数個の液晶表示駆動装置と、

該複数個の液晶表示駆動装置の前記出力端子から出力される駆動電圧を信号入力端子に受け表示を行なう前記カラー表示装置としてのカラー液晶表示パネルと、

該カラー液晶表示パネルの複数の走査線を順次駆動する走査線駆動装置と、

前記第1の端子に入力される前記画像データの前記伝送開始通知制御信号を生成し前記液晶表示駆動装置を制御する制御装置と、を備え、

前記複数個の液晶表示駆動装置の前記第1の端子の各端子には前記制御装置が出力する前記伝送開始通知制御信号が入力され、

前記複数個の液晶表示駆動装置のうち1番目の液晶表示駆動装置の前記第2の端子は定電位点に接続され、

前記複数個の液晶表示駆動装置のうちで2番目以降の各液晶表示駆動装置の前記第2の端子はその前段の液晶表示駆動装置の前記第5の端子に接続されていることを特徴とする液晶表示システム。

**【請求項 8】**

前記複数個の液晶表示駆動装置の各液晶表示駆動装置は外部より印加された電圧を分圧して複数の階調電圧を生成し前記変換回路へ供給する階調電圧生成回路を備え、

前記制御装置は、

10

20

30

40

50

前記液晶表示駆動装置へ前記赤色と前記緑色と前記青色から選択された第1の色の画像データを複数の前記カラー表示装置全てに供給した後、前記赤色と前記緑色と前記青色から選択された第2の色の画像データを複数の前記カラー表示装置全てに供給して、その後、前記赤色と前記緑色と前記青色から選択された第3の色の画像データを複数の前記カラー表示装置全てに供給する動作を繰り返して、複数の前記カラー表示装置全てに同一色の画像データを供給されるまでは前記伝送開始通知制御信号を同一の周期で発生し、各色の画像データを切り替える際は前記周期よりも長い周期で前伝送開始通知制御信号を発生し、前記第3の色の画像データの供給終了後に、前記階調電圧生成回路に与える電圧を切り替えて階調電圧を調整してガンマ補正を行なわせることを特徴とする請求項7に記載の液晶表示システム。

10

#### 【請求項9】

外部より入力される画像データを順次取り込む第1ラッチ回路と、

前記第1ラッチ回路に順次取り込まれた画像データを一括して取り込む第2ラッチ回路と、

前記第2ラッチ回路に順次取り込まれた画像データに応じた電圧を画像信号として出力する変換回路と、

前記変換回路により出力された画像信号を保持するホールド回路と、

前記ホールド回路に保持されている画像信号に応じた駆動電圧を出力する出力アンプと、を備え、

前記変換回路は前記半導体チップの長手方向と直交する方向に沿って複数個並んで配置され、

前記複数個の変換回路の形成領域の上方に前記変換回路に階調電圧を供給する複数の配線が配設されていることを特徴とする1個の半導体チップに形成された液晶駆動用半導体集積回路装置。

20

#### 【請求項10】

前記変換回路は、正の電圧を生成するものと、負の電圧を生成するものとからなり、

前記正の電圧を生成する複数の変換回路の形成領域と前記負の電圧を生成する複数の変換回路の形成領域は、前記半導体チップの長手方向に並んで設けられ、

各形成領域において、複数の変換回路がそれぞれ前記半導体チップの長手方向と直交する方向に沿って並んで配置され、

30

前記正の電圧を生成する前記複数の変換回路の前記形成領域および前記負の電圧を生成する前記複数の変換回路の前記形成領域の上方に前記変換回路へ前記階調電圧を供給する複数の配線がそれぞれ配設されていることを特徴とする請求項9に記載の液晶駆動用半導体集積回路装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、カラー表示パネルを駆動する表示駆動装置、カラー液晶パネルを駆動する液晶表示駆動装置、さらには、半導体集積回路化された液晶表示駆動装置に適用して有効な技術に関し、例えば、カラー液晶表示パネルを有するカラーテレビジョンシステムの上記カラー液晶表示パネルを駆動する液晶表示駆動装置を利用して有効な技術に関する。

40

#### 【背景技術】

#### 【0002】

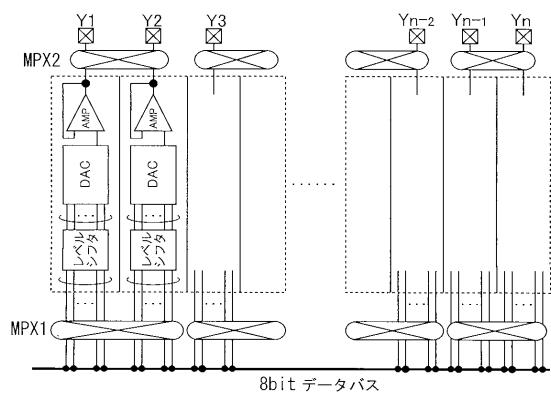

表示装置の1つとしての液晶表示装置は、表示パネルとしての液晶表示パネル（以下、液晶パネルとも言う）と表示制御装置としての液晶表示制御装置（液晶コントローラ）や該制御装置の制御下で液晶表示パネルを駆動する表示駆動装置としての液晶表示駆動装置（液晶表示ドライバ）などにより構成されている。液晶パネルの画素信号が印加される信号線としてのソース線を駆動するソースドライバは、一般に、図16に示されているように、各画像信号出力端子Y1, Y2……Ynごとにデジタル画像データ信号をアナログ電圧に変換するデジタル-アナログ（D/A）変換回路D A C 1, D A C 2……D A C n

50

が設けられていた。

【0003】

なお、図16のドライバにおいては、DA変換回路D A C 1, D A C 2 …… D A C n は正電圧出力用と負電圧出力用のものが交互に配置され、あるソース線の画素のデータはマルチプレクサM P X 1により、正電圧出力用DA変換回路D A C iと負電圧出力用DA変換回路D A C i+1に交互に入力されてアナログ電圧に変換されマルチプレクサM P X 2を介してソース線に印加されることによって、各画素の電極は交流駆動され、液晶の劣化が防止されるようになっている。

【先行技術文献】

【特許文献】

10

【0004】

【特許文献1】特開2001-27750号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、液晶表示装置における画像データは複数の画素データから構成される。1つの画素データは、1画素あたり、8ビットの赤色データ(R)と、8ビットの緑色データ(G)と、8ビットの青色データ(B)とで構成されており、液晶パネルの諧調表示は各色(R/G/B)あたり256段階であるものが多い。しかしながら、液晶表示装置の高画質化に伴い、より高諧調度の表示が行なえる液晶表示装置が要求されるようになって来た。

そこで、本発明者らは、例えば、1画素の画素データを構成する各色(R/G/B)データを10ビットとし、各色(R/G/B)あたり1024段階のような諧調表示を行なえるソースドライバについて検討した。

20

【0006】

その結果、画像信号出力端子Y1, Y2 …… YnごとにDA変換回路D A C 1, D A C 2 …… D A C nを設ける方式にあっては、DA変換回路に諧調電圧を供給する配線の数が正負合わせて2048本必要になる。そのため、諧調電圧を供給する配線の配線領域の幅が広くなり、これらの諧調電圧を供給する配線(給電線とも言う)の下に、DA変換回路を配置したとしても、無駄なスペースが生じることになる。従って、液晶ドライバ、すなわち、ソースドライバが形成される半導体チップのサイズが大きくなり、ソースドライバの大額なコストアップにつながるという課題があることを、発明者らは見出した。これを解決するには、ソースドライバに搭載するDA変換回路の数を減らし、DA変換回路を時分割動作させればよいが、そのようにすると画像データを入力してからアナログ電圧として出力されるまでの時間が長くなってしまう。

30

【0007】

また、表示画面の大型化や高精細化に伴いソース線の数の多い液晶パネルが提供されるようになってきているため、ソース線の数の異なる液晶パネルが共存している。それらの液晶パネルに共通のソースドライバを使用できるようにするには、最大のソース線の液晶パネルに合わせて画像信号出力端子を設けることも解決法のひとつである。しかし、そのようなソースドライバは、そのチップサイズが極端に大きくなってしまうため、有効な手法ではないことも発明者らは見出した。

40

【0008】

そこで、1つのソースドライバの有する画像信号出力端子の数を制限し、複数のソースドライバを用いて液晶表示システムを構成することが考えられる。かかる手法は、ソースドライバのチップサイズを小さくする上で有効である。しかしながら、この場合、画像データを送るべきソースドライバを切り換える際のタイミングに注意を払う必要がある。そのタイミングが不正確であると、画像データをソースドライバに正しく取り込めなかったり、画像データをソースドライバに伝送するための伝送時間が長くなったりするなどのおそれが発生する。

【0009】

50

この発明の目的は、表示駆動装置（液晶ドライバ、液晶駆動用半導体集積回路）の小型化を図ることにある。

【0010】

この発明の他の目的は、複数の表示駆動装置（液晶ドライバ）を組み合わせて表示装置（液晶表示装置）を構成する可能な表示駆動装置（液晶ドライバ）を提供することにある。

【0011】

この発明のさらに他の目的は、カラー表示パネル（カラー液晶パネル）の各色の特性に応じたガンマ補正を動的に行なえる複数の表示駆動装置（液晶ドライバ）を提供することにある。

10

【0012】

この発明のさらに他の目的は、チップサイズの増大を抑えつつ高譜調度の表示を行なうことができる複数の表示駆動装置（液晶ドライバ）を提供することにある。

【0013】

この発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち代表的なものの概要を説明すれば、下記のとおりである。

20

【0015】

すなわち、アナログ階調電圧に変換された画像信号を出力する最終段の出力アンプを複数のグループに分け、画像データをアナログ階調電圧に変換するディジタル-アナログ（D/A）変換回路を上記グループに共通の回路として設けて、グループを切り替えながらD/A変換回路を時分割動作させる。また、上記最終段の出力アンプは同一色の画像信号に関わるもの同士を選択してグループ化し、D/A変換回路と出力アンプとの間にはセレクタ機能を設けてD/A変換回路でアナログ階調電圧に変換された画像信号を所望の出力アンプに振り分けるようにしたものである。

【0016】

上記した手段によれば、D/A変換回路を時分割動作させるためD/A変換回路の数が画像信号出力端子の数よりも少なくて済み、表示駆動装置（液晶ドライバ）の小型化を図ることができる。

30

【0017】

本発明の表示駆動装置（液晶ドライバ）を複数個組み合わせて使用する画像表示システムでは、ある表示駆動装置（液晶ドライバ）でD/A変換している間に、他の表示駆動装置（液晶ドライバ）ではD/A変換された画像信号を出力アンプへ伝送させることができる。そのため、画像データを入力してから所定の時間内に階調電圧として出力させることができ、画像データを表示駆動装置（液晶ドライバ）に正しく取り込めなかつたり、データ伝送所要時間が長くなったりするのを防止することができる。

【0018】

また、最終段の出力アンプは同一色の画像信号に関わるもの同士を選択してグループ化しているため、表示制御装置（液晶コントローラ）は表示パネル（液晶パネル）の1ラインに関し、同一色の画像データを連続して転送することができる。色データの切替えは1ラインにR/G/B各データの3回で済むため、色データの切替えの際に、各色の階調電圧を動的に変更することによってガンマ補正を行なうことが可能となる。それに伴う遅れは極めて小さいので、データ伝送タイミングやシステム構成を大きく変えることなくガンマ補正を行なうことができる。

40

【0019】

さらに、本願の他の発明は、画像データをアナログ階調電圧に変換する複数のD/A変換回路を、半導体チップのほぼ中央に、半導体チップの長手方向と直交する方向に並べて配

50

置し、D A 変換回路に諧調電圧を供給する複数の配線を半導体チップの長手方向と直交する方向に沿って配設するようにしたものである。

【0020】

上記した手段によれば、表示駆動装置（液晶ドライバ）が1024階調のような多段階の画像信号を出力するものであり、諧調電圧を供給する配線の領域の幅が広くなる場合にも、これらの諧調電圧を供給する配線（給電線）の下にD A 変換回路を配置したときに無駄なスペースが生じさせることなく、これにより半導体チップのサイズを低減させることができる。

【発明の効果】

【0021】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0022】

すなわち、本出願の発明に従うと、表示駆動装置（液晶ドライバ、液晶駆動用半導体集積回路）の小型化を実現することができる。

【0023】

また、本出願の発明に従うと、複数の表示駆動装置（液晶ドライバ）を組み合わせて表示装置（液晶表示システム）を構成する可能な表示駆動装置（液晶ドライバ）を実現する。

【0024】

さらに、本出願の発明に従うと、カラー表示パネル（カラー液晶パネル）の各色の特性に応じたガンマ補正を動的に行なえる表示駆動装置（液晶ドライバ）を実現することができる。

【0025】

また、チップサイズの増大を抑えつつ高諧調度の表示を行なうことができる表示駆動装置（液晶ドライバ、液晶駆動用半導体集積回路）を実現することができる。

【図面の簡単な説明】

【0026】

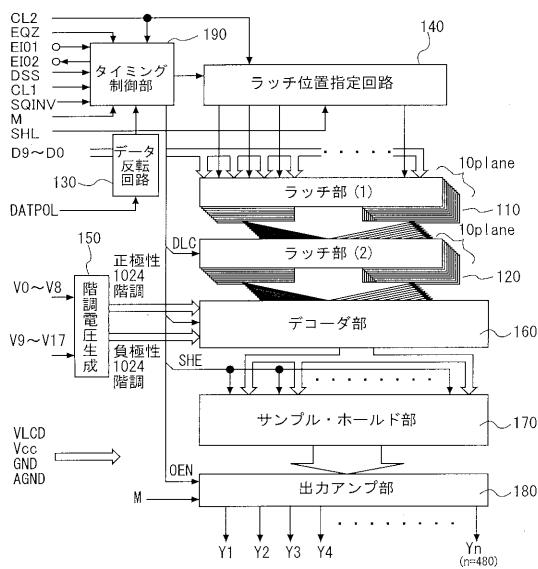

【図1】本発明を適用した液晶ドライバ回路の概略構成を示すブロック図である。

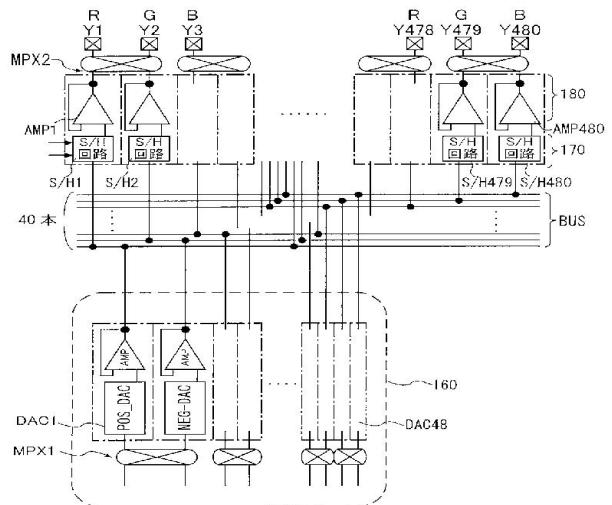

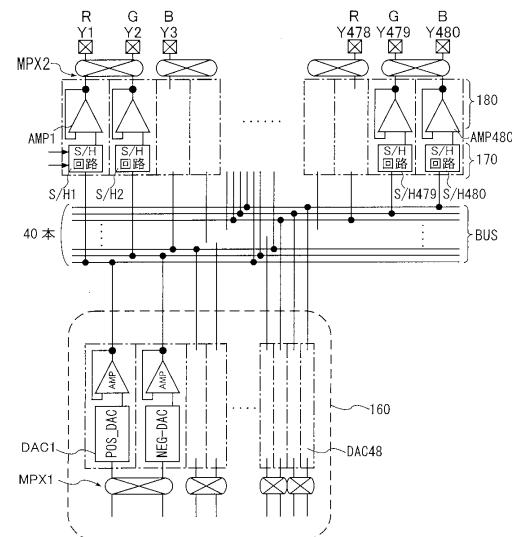

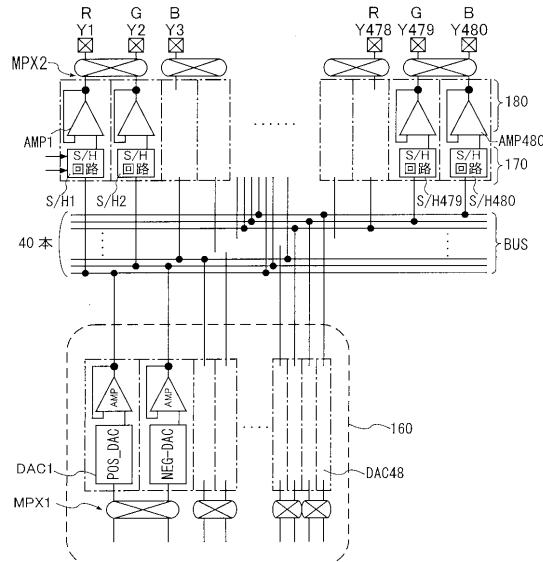

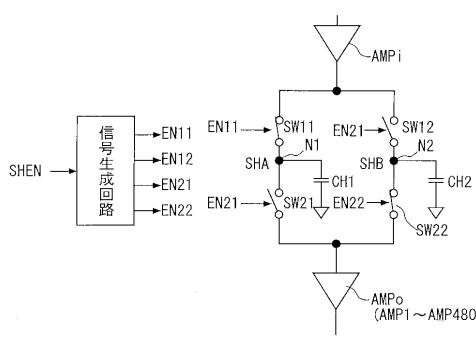

【図2】図1の液晶ドライバ回路のうちデコーダ部とサンプル・ホールド部および出力アンプ部を取り出してより詳細な構成を示したブロック図である。

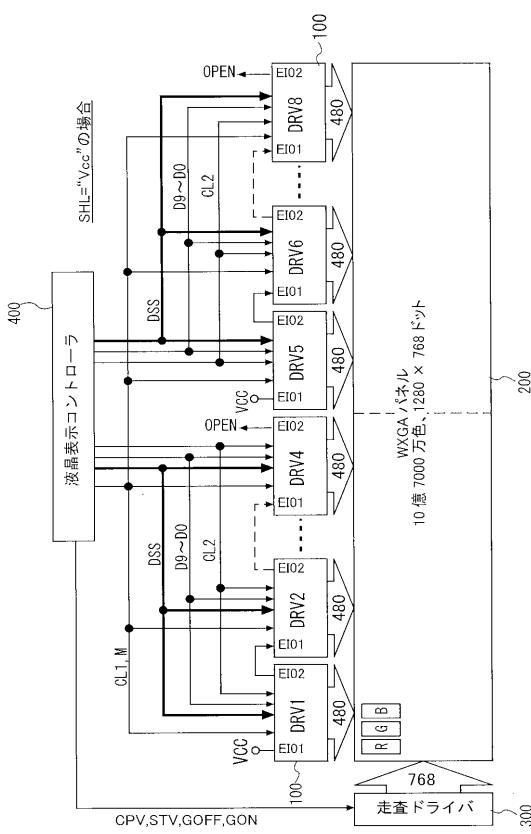

【図3】本実施例の液晶ドライバ回路を複数個使用した液晶表示システムの構成例を示すブロック図である。

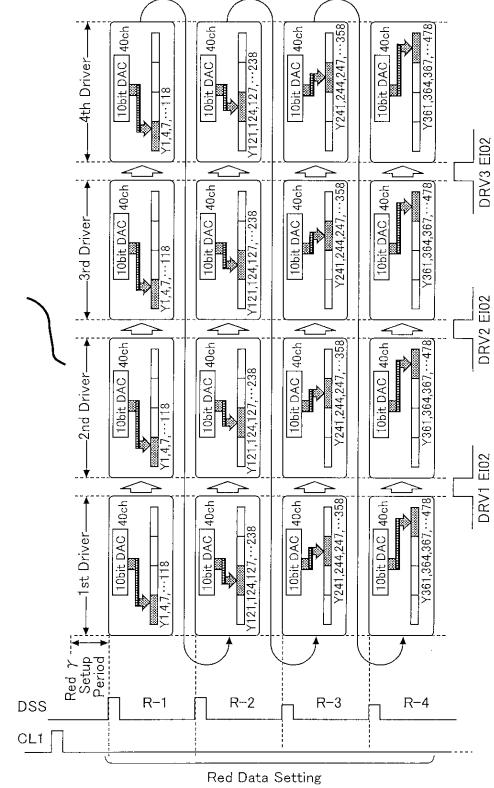

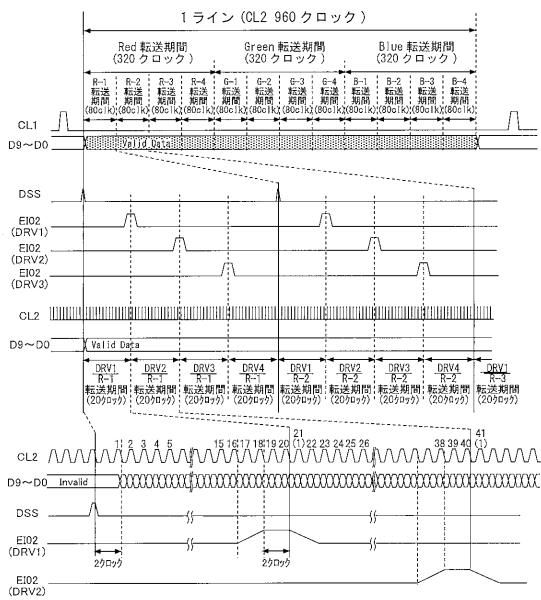

【図4】図3の液晶表示システムにおいて、それぞれ組をなす4つの液晶ドライバ回路のデコーダ部からサンプル・ホールド部へ供給される赤色画像信号の伝送タイミングを示すタイミングチャートである。

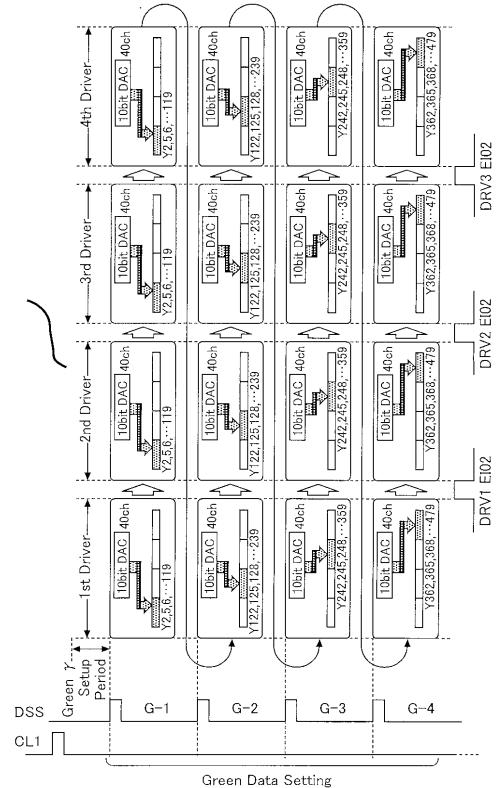

【図5】図3の液晶表示システムにおいて、それぞれ組をなす4つの液晶ドライバ回路のデコーダ部からサンプル・ホールド部へ供給される緑色画像信号の伝送タイミングを示すタイミングチャートである。

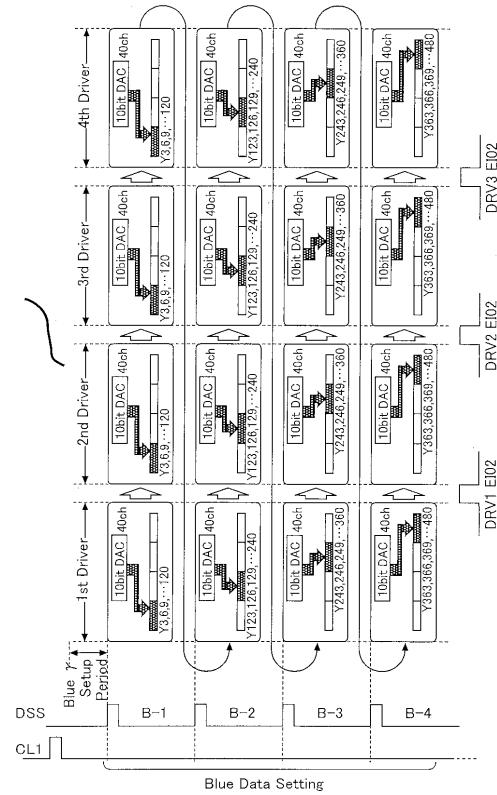

【図6】図3の液晶表示システムにおいて、それぞれ組をなす4つの液晶ドライバ回路のデコーダ部からサンプル・ホールド部へ供給される青色画像信号の伝送タイミングを示すタイミングチャートである。

【図7】図3の液晶表示システムにおける液晶表示コントローラから液晶ドライバ回路に對して供給される制御信号やクロックのタイミングを示すタイミングチャートである。

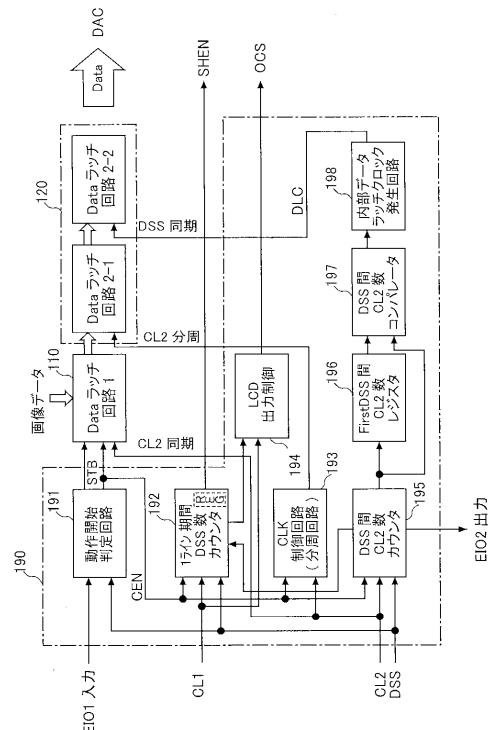

【図8】タイミング制御部の構成例を示すブロック図である。

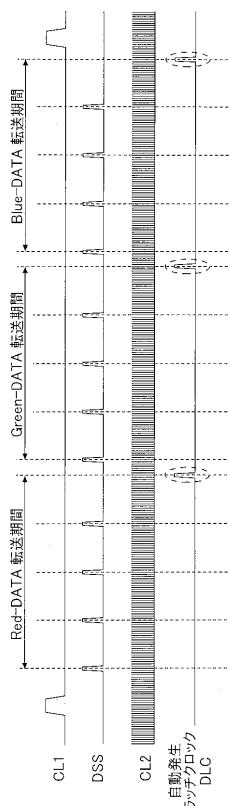

【図9】タイミング制御部で自動生成されるラッチクロックのタイミングを示すタイミングチャートである。

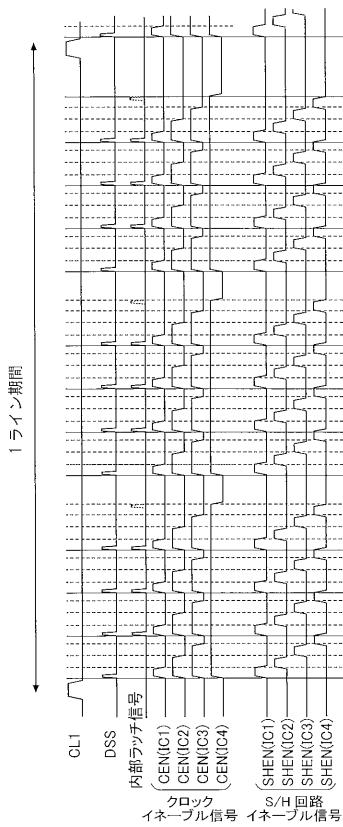

【図10】図3の液晶表示システムにおける各種信号のタイミングを示すタイミングチャートである。

【図11】サンプル・ホールド部の単位サンプル・ホールド回路の構成例を示すブロック

10

20

30

40

50

図である。

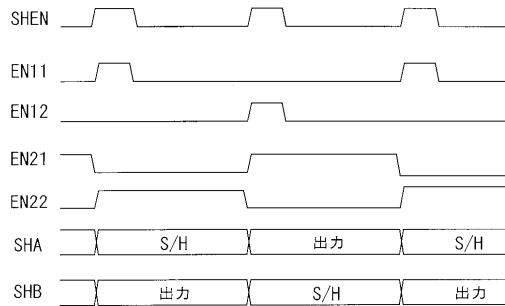

【図12】サンプル・ホールド部の単位サンプル・ホールド回路の動作タイミングを示すタイミングチャートである。

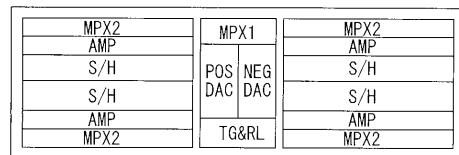

【図13】本実施例の液晶ドライバ回路を構成する各回路ブロックの半導体チップ上でのレイアウトの一例を示す平面図である。

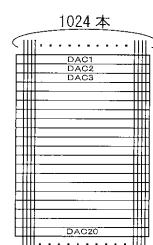

【図14】図13の実施例のデコーダ部におけるDA変換回路の配置を示す平面図である。

【図15】本発明に先立って検討した液晶ドライバ回路のレイアウトを示す平面図である。

【図16】本発明に先立って検討した液晶ドライバ回路の概略構成を示すブロック図である。 10

#### 【発明を実施するための形態】

##### 【0027】

以下、本発明の好適な実施例を図面に基づいて説明する。

##### 【0028】

図1は、本発明を適用した液晶ドライバ回路の概略構成を示す。特に制限されるものでないが、図1に示されている各回路ブロックは単結晶シリコンのような1個の半導体チップ上に半導体集積回路として構成される。本実施例の液晶ドライバ回路は、複数の走査線と複数の信号線とが格子状に配設され各交点に画素が設けられているドットマトリックス型のカラー液晶パネルの信号線に印加される画像信号Y1～Ynを出力する回路である。 20

##### 【0029】

本発明において、特に制限されないが、1画素の画素データは、赤色(R)／緑色(G)／青色(B)の各色データがそれぞれ10ビットとされた30ビットで構成されるものとして、以下実施例が説明される。

##### 【0030】

本実施例の液晶ドライバ回路は、10ビットの入力画像データ(赤色(R)／緑色(G)／青色(B)の3つ色データのうち、1つの色データの10ビットを示す)D9～D0を順次取り込む第1ラッチ部110と、該第1ラッチ部110に取り込まれた画像データを一括して転送する第2ラッチ部120と、入力画像データD9～D0がオール"1"のときに画素を"黒"とするかオール"0"のときに画素を"黒"とするかに応じてデータを反転させるデータ反転回路130と、上記第1ラッチ部110のどこに入力画像データD9～D0を取り込ませるか指定するラッチ位置指定回路140と、外部から供給される階調電圧V0～V8, V9～V17をラダー抵抗で分圧して正極性および負極性それぞれ1024階調の電圧を生成する階調電圧生成回路150と、生成された電圧の中から前記第2ラッチ部120に保持されている画像データに応じた電圧を選択することでデジタル信号をアナログ階調電圧に変換するデコーダ(セレクタ)部160と、変換されたアナログ電圧を保持するサンプル・ホールド部170と、ホールドされた電圧に応じた画像信号Y1～Ynを生成して出力する出力アンプ部180と、外部から入力されるクロック信号や制御信号に基づいて半導体チップ内部の回路を所定の順序に従って動作させる内部制御信号を生成するタイミング制御部190などから構成される。 30

##### 【0031】

タイミング制御部190には、本実施例の液晶ドライバ回路を複数個シリーズに接続して当該回路の出力数(n本)よりも多い信号線を有する液晶パネルを駆動するシステムを構成する場合に、所定の端子EIO1の状態に応じて先頭の液晶ドライバ回路(最初の画像データが供給されるIC)か否かを判定するとともに、当該回路がすべての画像信号Y1～Ynを出力したことを示す信号を所定の端子EIO2より出力する機能が設けられている。具体的には、先頭の液晶ドライバ回路の端子EIO1を電源電圧Vccに固定するとともに、前段の液晶ドライバ回路の端子EIO2を次段の端子EIO1に接続することにより、複数の液晶ドライバ回路を順次画像データ取込み状態にさせることができる。 40

##### 【0032】

図2は、図1に示されている液晶ドライバ回路のうちデコーダ部160とサンプル・ホールド部170および出力アンプ部180を取り出してより詳細に構成を示したものである。

#### 【0033】

本実施例においては、サンプル・ホールド部170および出力アンプ部180にそれぞれ480個の単位サンプル・ホールド回路S/H1~S/H480とボルテージフォロワとして動作する出力アンプAMP1~AMP480が設けられているのに対し、1/12の数(40個)のDA変換回路DAC1~DAC40およびボルテージフォロワとして動作するアンプが設けられている。ここでは、デコーダ部160を構成する40個の回路を便宜的にDA変換回路と呼んでいるが、階調電圧生成回路150から供給される複数の階調電圧の中から入力コードに応じた電圧を選択して出力させるスイッチ素子のみからなるセレクタによりデコーダ部160を構成することができる。

10

#### 【0034】

上記デコーダ部160の40個の出力は、40本の信号線からなるバスBUSを介して上記480個の単位サンプル・ホールド回路S/H1~S/H480のうちいずれか40個に取り込まれるように構成されている。具体的には、デコーダ部160には同一色の画像データが40個まとめて入力されるようにされ、480個の出力端子Y1~Y480のうち、Y1, Y4, Y7.....Y478は液晶パネルの赤色(R)画素に接続された信号線に対応して赤色画像信号が、Y2, Y5, Y8.....Y479は液晶パネルの緑色(G)画素に接続された信号線に対応して緑色画像信号が、Y3, Y6, Y9.....Y480は液晶パネルの青色(B)画素に接続された信号線に対応して青色画像信号がそれぞれ出力されるように、デコーダ部160において変換された40個の画像信号はサンプル・ホールド回路S/H1~S/H480のうち2つおき計40個のサンプル・ホールド回路に取り込まれる。

20

#### 【0035】

DA変換回路DAC1.....DAC40は正電圧出力用と負電圧出力用のものが交互に配置されている。つまり、奇数番目のDA変換回路DAC1, DAC3.....DAC47が正電圧を出力するようになると、偶数番目のDA変換回路DAC2, DAC4.....DAC48は負電圧を出力するようになる。そして、あるビットの画素データはマルチプレクサMPX1により、正電圧出力用DA変換回路DACiと負電圧出力用DA変換回路DACi+1に交互に入力されてアナログ電圧に変換され、サンプル・ホールド回路に伝送されマルチプレクサMPX2を介して出力される。

30

#### 【0036】

このとき、マルチプレクサMPX1とMPX2は同じように動作される。すなわち、マルチプレクサMPX1が画像データをスルーさせている時はマルチプレクサMPX2も画像信号をスルーさせ、マルチプレクサMPX1が画像データを交差させている時はマルチプレクサMPX2も画像信号を交差させるように信号経路を切り替える。これによって、液晶パネルの各画素の電極は正の電圧と負の電圧が交互に印加されて交流駆動され、液晶の劣化が防止されるようになっている。

40

#### 【0037】

図3には、本実施例の液晶ドライバ回路100を複数個使用して $1280 \times 768$ ドットのカラー液晶パネル200を駆動するシステムを構成した場合のブロック図が示されている。カラー液晶パネル200のライン方向には、8個の液晶ドライバ回路DRV1~DRV8が配置され、これらの液晶ドライバ回路DRV1~DRV8が4個ずつ2組に分けられ、各組の先頭の液晶ドライバ回路DRV1, DRV5の端子EIO1は電源電圧Vccに固定されるとともに、残りの液晶ドライバ回路DRV2~DRV4, DRV6~8の端子EIO1には、前段の液晶ドライバ回路の端子EIO2が電気的に結合されることにより、4個ずつ直列形態に接続されている。

#### 【0038】

300はカラー液晶パネル200のコモン線(TFTパネルではゲート線と呼ばれる)

50

を順番に選択レベルにする走査線駆動回路(コモンドライバ)、400は走査線駆動回路300に対するタイミング制御信号を生成したり、上記液晶ドライバ回路に供給する画像データD9～D0や液晶ドライバ回路を制御する制御信号DSS、動作クロックCL1, CL2を生成する液晶表示コントローラである。

#### 【0039】

液晶表示コントローラ400は、2つの走査線駆動回路に対する画像データD9～D0を同時に出力するようにされる。また、この実施例では、画像データの伝送開始を知らせる制御信号DSSや取込みタイミングを知らせるクロックCL2を2組の液晶ドライバ回路DRV1～DRV4, DRV5～DRV8に対してそれぞれ別個に生成して与えるように構成されているが、これらの信号は共通の信号として与えるようにすることも可能である。

10

#### 【0040】

図4～図6には、図3のような液晶表示システムにおいて、それぞれ組をなす4つの液晶ドライバ回路DRV1～DRV4またはDRV5～DRV8のデコーダ部160からサンプル・ホールド部160へ送る画像信号の伝送タイミングが示されている。図4～図6における時間の流れは、図4 図5 図6であり、また各図においては先ず左から右へ向かい、右端に達するとその下の左端へ向かうというような流れである。

#### 【0041】

図4～図6から分かるように、本実施例の液晶表示システムでは、先ず赤色の画像データが40個ずつ16回に分けて伝送されDA変換されてホールドされた後、緑色の画像データが40個ずつ16回に分けて伝送されDA変換されてホールドされ、その後、青色の画像データが40個ずつ16回に分けて伝送されDA変換されてホールドされる。

20

#### 【0042】

これによって、液晶パネルの1ラインの半分の640個のドットに対する1920個の画像データの伝送、ホールドが行われる。そして、本実施例の液晶表示システムでは、赤色の画像データの伝送から、緑色の画像データの伝送、さらに青色の画像データの伝送へと移る際に若干の遅延時間を設け、その間に各色の画素のガンマ特性に応じて出力する電圧を変化させるガンマ補正を動的に行なうようになっている。このように、本実施例の液晶表示システムでは、比較的容易にガンマ補正を動的に行なうことができるのは、赤、緑、青の各色の画像データがそれぞれまとめて伝送されるためである。

30

#### 【0043】

カラー液晶パネルの構成に応じて一方の端の信号線に対する画像データから他方の端の信号線に対する画像データまで順番に伝送する方式の表示システムにおいては、赤色の画像データの伝送と、緑色の画像データの伝送と、青色の画像データの伝送が繰り返されるか混在して伝送されるので、各色の画像データの伝送ごとにガンマ補正を行わなくてはならない。そのため、画像データの数だけガンマ補正のための遅延時間を設けなくてはならず、そのようにすると1水平期間中にすべての画像データの伝送を終了することができなくなる。

#### 【0044】

これに対し、本実施例の液晶表示システムでは、赤、緑、青の各色の画像データがそれぞれまとめて伝送されるため、1水平期間中に3回だけガンマ補正のための遅延時間を設けてやればよいので、1水平期間中にすべての画像データの伝送を終了することができる。

40

#### 【0045】

なお、本実施例の液晶ドライバ回路におけるガンマ補正は、図1の階調電圧生成回路150に外部から与える電圧V0～V8, V9～V17を、赤、緑、青の各色のガンマ特性に応じて切り替えてやることで実現することができる。

#### 【0046】

図7には、図3の液晶表示システムにおける液晶表示コントローラ400から液晶ドライバ回路DRV1～DRV4(DRV5～DRV8についても同様)に対して供給される

50

データサンプリング開始制御信号 DSS やデータの取込みタイミング等を知らせるクロック CL1, CL2、画像データ D9 ~ D0、各液晶ドライバ回路DRV1 ~ DRV4 から出力されるデータ伝送終了信号 EIO2 のタイミングが示されている。

#### 【0047】

このうち、クロック CL1 は 1 水平期間を示す信号、制御信号 DSS は各液晶ドライバ回路 DRV1 ~ DRV4 のそれぞれのデータサンプリング開始タイミングを知らせる信号で、1 水平期間中にすなわちクロック CL1 の 1 周期に 4 回制御信号 DSS が立ち上がる。

#### 【0048】

一方、CL2 は画像データ D9 ~ D0 の取込みタイミングを知らせるクロックで、この実施例ではクロック CL2 の立下がりと立上がりのそれぞれで画像データを取り込むように液晶ドライバ回路が構成されているため、1 つの液晶ドライバ回路が 40 個のまとった画像データを取り込む期間すなわちデータサンプリング開始制御信号 DSS の 1 周期の期間におけるクロック CL2 のパルス数は 20 個である。

#### 【0049】

なお、最初の液晶ドライバ回路 DRV1 が画像データの取り込みを開始するのは、データサンプリング開始制御信号 DSS が変化してからクロック CL2 の 2 パルスだけ後の時点からとされている。また、各液晶ドライバ回路が 40 個の画像データを取り込んだことを知らせる信号 EIO2 は、実際の最後のデータの取り込みタイミングよりもクロック CL2 の 2 パルス前に立ち上がるようになっている。これにより、液晶ドライバ回路 DRV2 ~ DRV4 は、画像データを前段のドライバのデータ取込み終了から時間遅れなく連続して取り込むことができる。

#### 【0050】

次に、実施例の液晶ドライバ回路 DRV のチップ内部の動作について説明する。液晶ドライバ回路 DRV の内部の各回路ブロックは、タイミング制御部 190 からの制御信号によって所定のタイミングで動作され、タイミング制御部 190 は外部から入力されるクロック信号や制御信号に基づいて内部の回路を所定の順序に従って動作させる内部制御信号を生成する。

#### 【0051】

図 8 には、タイミング制御部 190 の構成例が示されている。本実施例のタイミング制御部 190 は、入力信号 EIO1 に基づいて画像データを取り込む初段ラッチ回路 110 やクロックを計数する後述のカウンタを動作させるかスタンバイ状態にさせるかを示す制御信号 STB, CEN 等を生成する動作開始判定回路 191 と、1 水平期間を示すクロック CL1 に基づいて 1 水平期間中のデータサンプリング開始制御信号 DSS の数を計数しサンプル・ホールド部 170 に対するイネーブル信号 SHEN を生成する DSS カウンタ 192 と、データラッチタイミングを与えるクロック CL2 を分周して第 1 ラッチ部 110 に取り込まれた画像データを一括して第 2 ラッチ部 120 に転送させるタイミングを与えるラッチタイミング信号 DLT を生成するクロック制御回路 193 と、出力アンプ部 180 に対し LCD 画像信号の出力を許可する出力イネーブル信号 OEN を生成する LCD 出力制御回路 194などを備える。

#### 【0052】

図 1 には示されていないが、実施例の液晶ドライバ回路は、第 2 ラッチ部 120 が 1 段目のラッチ回路 121 と 2 段目のラッチ回路 122 からなる 2 段構成とされており、タイミング制御部 190 は 1 段目のラッチ回路 121 と 2 段目のラッチ回路 122 を順次ラッチ動作させるクロックを生成して供給するようにされている。これにより、1 段目のラッチ回路 121 がマスタラッチとして動作し、2 段目のラッチ回路 122 がスレーブラッチとして動作して、第 2 ラッチ部 120 に取り込まれた画像データが直ちに次段のデコーダ部 160 へ供給されてしまうのを防止することができる。

#### 【0053】

さらに、タイミング制御部 190 は、データサンプリング開始制御信号 DSS 間のクロ

10

20

30

40

50

ック CL 2 の数を計数する CL 2 カウンタ 195 や、1 ライン中初回の DSS 信号間のクロック CL 2 の数を保持する CL 2 数レジスタ 196 、1 ライン中初回の DSS 信号間のクロック CL 2 の数と 2 回目以降の DSS 信号間のクロック CL 2 の数とを比較するコンパレータ 197 、該コンパレータ 197 の比較結果に基づいて、外部からの DSS 信号が初回の DSS 信号間のクロック CL 2 の数よりも長い期間入力されなかった場合に、第 2 ラッチ部 120 の後段のラッチ回路 122 に対してデータのラッチを指示するためのクロック信号 DLC を半導体チップ内部で自動的に発生するラッチクロック発生回路 198 を備える。

#### 【 0054 】

ラッチクロック発生回路 198 を設けたのは、本実施例の液晶ドライバ回路を使用し gamma 補正を行なう表示システムにおいては、図 9 に示すように、各色の画像データの転送期間に gamma 補正のための余裕期間 (Ta) を設けるために DSS 信号を少し遅れて入力させることがあるので、DSS 信号にのみ基づいてラッチ回路 122 に対するラッチクロック信号 DLC を生成したのでは、ラッチのタイミングが遅れてしまうためである。

10

#### 【 0055 】

また、本実施例のタイミング制御回路においては、CL 2 カウンタ 195 が所定数 (16 クロック) を計数した時点で次段の液晶ドライバ回路に対する EIO 2 信号を立ち上げるようにすることができる。これにより、次段の液晶ドライバ回路がこの信号を EIO 1 端子に受けるように接続をしておくことによって、複数の液晶ドライバ回路を使用した表示システムにおいて、液晶表示コントローラは各ドライバに対して独自の開始信号を送ることなく、連続した画像データの伝送が可能となる。そのため、表示システムの設計者の負担を軽減することができる。

20

#### 【 0056 】

図 10 には、実施例の液晶ドライバ回路を 8 個使用して 4 個ずつペアにして順に画像データを転送することで液晶パネルへのカラー表示を行なわせる図 3 のような液晶表示システムにおける液晶ドライバ回路DRV1 ~ DRV4 (DRV5 ~ DRV8 についても同様) に対して供給されるデータサンプリング開始制御信号 DSS やクロック CL1 のタイミングと、各液晶ドライバ回路DRV1 ~ DRV4 内で生成されるクロックイネーブル信号 CEN と、サンプルホールドイネーブル信号 SHEN と、次段の液晶ドライバ回路に対する EIO 2 信号のタイミングが示されている。

30

#### 【 0057 】

図 11 には、サンプル・ホールド部 170 の単位サンプル・ホールド回路の構成例が、図 12 にはその動作タイミングが示されている。

#### 【 0058 】

本実施例の単位サンプル・ホールド回路は、デコーダ部 160 で AD 変換された電圧を保持ための 1 組のホールド容量 CH1 , CH2 と、入力側のアンプ AMPi の出力端子と前記ホールド容量 CH1 , CH2 の一方の端子がそれぞれ接続されたノード N1 , N2 との間に接続された一対のスイッチ SW11 , SW12 と、前記ノード N1 , N2 と出力側のアンプ AMPo の入力端子との間に接続された一対のスイッチ SW21 , SW22 とにより構成されている。図 2 のアンプ AMP1 ~ AMP4 80 が図 11 のアンプ AMPo に相当する。

40

#### 【 0059 】

上記一対のスイッチ SW11 , SW12 は制御信号 EN11 , EN12 によってオン・オフされるとともに、スイッチ SW21 , SW22 は制御信号 EN21 , EN22 によってオン・オフされる。そして、スイッチ SW11 がオンされるときは SW22 がオンされ、スイッチ SW12 がオンされるときは SW21 がオンされるように制御信号 EN11 , EN12 , EN21 , EN22 によって制御される。さらに、スイッチ SW11 と SW21 は同時にオン状態にされることがないように、またスイッチ SW12 と SW22 も同時にオン状態にされることがないように、サンプルホールドイネーブル信号 SHEN に基づいてそれぞれの制御信号 EN11 , EN12 , EN21 , EN22 が生成される。

50

## 【0060】

本実施例の単位サンプル・ホールド回路は、スイッチSW11がオン状態にされるとスイッチSW21がオフ状態にされて、ホールド容量CH1にデコーダ部160でA/D変換された電圧(画像信号)がサンプリングされる。このとき、反対側のホールド容量CH2はスイッチSW22がオン状態にされスイッチSW12がオフ状態にされることにより、直前にサンプリングした電圧を出力する状態となる。

## 【0061】

ホールド容量CH1に入力電圧がサンプリングされると、スイッチSW11がオフ状態にされスイッチSW12がオン状態にされることにより、サンプリングした電圧を出力する状態となる。このとき、反対側のホールド容量CH2はスイッチSW12がオン状態にされ、スイッチSW22がオフ状態にされて、デコーダ部160でA/D変換された電圧で充電されてサンプリングを行なうようにされる。

10

## 【0062】

上記のような動作を繰り返すことにより、1組のホールド容量CH1とCH2がサンプリング状態とホールド状態を交互に繰り返し、デコーダ部160から出力された電圧(画像信号)が連続して画像信号がサンプリングされ、次々と出力される。

## 【0063】

図13には、本実施例の液晶ドライバ回路を構成する各回路ブロックの半導体チップ上でのレイアウトの一例が示されている。図13において、図2に示されている回路と同一の回路には同一の符号が付されている。

20

## 【0064】

図13から分かるように、本実施例の液晶ドライバICにおいては、半導体チップのほぼ中央に、正電圧を出力するD/A変換回路POS-DACと負電圧を出力するD/A変換回路NEG-DACが半導体チップの長手方向に並んで配置され、その上方にマルチプレクサMPXが、また下方にランダムロジックからなるタイミング制御回路(190)および抵抗ラダーからなる諧調電圧生成回路(150)TGRが配置されている。そして、これらの回路の左右には、対称的に、上から順に、マルチプレクサMPX2、出力アンプAMP、サンプル・ホールド回路S/Hが配置され、さらにこれらと同一の回路が上下対称的に、サンプル・ホールド回路S/H、出力アンプAMP、マルチプレクサMPX2の順に配置されている。

30

## 【0065】

さらに、正電圧を出力するD/A変換回路POS-DACと負電圧を出力するD/A変換回路NEG-DACは、図14に示すように、それぞれ20個の単位D/A変換回路DAC1～DAC20が半導体チップの長手方向と直交する方向に並んで配置され、その上に諧調電圧生成回路TGRから出力される階調電圧を供給する1024本の給電線が配設されている。

## 【0066】

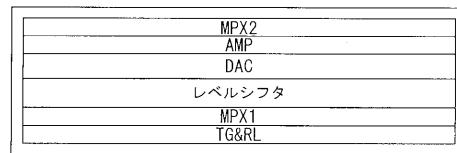

画像データが8ビットで256階調の液晶ドライバICは、図15に示すように、マルチプレクサMPX2、出力アンプAMP、デコーダ部DAC、レベルシフタ、マルチプレクサMPX1、タイミング制御回路および諧調電圧生成回路TGRが順に配置され、デコーダ部の単位D/A変換回路は半導体チップの長手方向に沿って出力端子の数と同じ数だけ配置されたチップレイアウトが一般であった。かかるレイアウトを本実施例の液晶ドライバICのように画像データが10ビットで1024階調の液晶ドライバICに適用すると、D/A変換回路列の上に従来の4倍の数の給電線を半導体チップの長手方向に沿って配設しなければならなくなり、給電線の長さが非常に長くなるとともに給電線の幅が大幅に増加して給電線の下方にむだなスペースが生じてしまう。

40

## 【0067】

これに対し、図13および図14に示すようなレイアウトに従うと、階調電圧の給電線を半導体チップの長手方向と直交する方向に沿って配設すればよいため、給電線の長さが短くなるとともに、複数の給電線のレイアウト幅が大幅に増加しても給電線の下方にむだ

50

なスペースを生じさせることなく D A 変換回路を配置することができるようになる。その結果、高階調化に伴うチップサイズの増加を大幅に抑制することができるという利点がある。

#### 【0068】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。例えば、前記実施例では、画像データが 10 ビットで階調電圧が 1024 段階である場合について説明したが、それに限定されるものでなく、画像データが 9 ビットで階調電圧が 512 段階の場合や、画像データが 11 ビットで階調電圧が 2048 段階の場合にも適用することができる。また、前記実施例では、480 個の出力アンプに対して 40 個すなわち 1 / 12 個の D A 変換回路を設けているが、1 / 8 個あるいは 1 / 16 個などであっても良い。10

#### 【0069】

さらに、前記実施例では、画像データに同期して入力されるクロック信号を計数するカウンタの計数値が所定値に達したときに画像データの取り込み終了を示す信号 E I O 2 を出力する端子を設け、該端子の信号を次段のドライバ I C にデータ取り込み許可信号 E I O 1 として入力しているが、信号 E I O 2 を出力する端子を省略し、データ取り込み許可信号 E I O 1 を液晶表示コントローラ 400 から与えるように構成することも可能である。20

#### 【産業上の利用可能性】

#### 【0070】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野である液晶パネルを駆動する液晶ドライバ回路に適用したものについて説明したが、本発明はそれに限定されるものでなく、ディジタルコードで与えられたカラーの画像データをアナログ電圧に変換して出力するカラー表示装置の駆動回路一般に適用することができる。30

#### 【符号の説明】

#### 【0071】

100 液晶表示駆動装置（液晶ドライバ I C）

110 第 1 ラッチ部

120 第 2 ラッチ部

130 データ反転回路

140 ラッチ位置指定回路

150 階調電圧生成回路

160 デコーダ（セレクタ）部

170 サンプル・ホールド部

180 出力アンプ部

190 タイミング制御部

200 液晶パネル

300 走査線駆動回路（コモンドライバ）

400 液晶表示コントローラ

D R V 1 ~ D R V 8 液晶ドライバ I C

M P X 1 , M P X 2 マルチプレクサ

D A C D A 変換回路

A M P 出力アンプ

S / H サンプル・ホールド回路

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 1 M

G 0 9 G 3/20 6 2 3 V

(72)発明者 久保 健彦

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 2H193 ZC25 ZD11 ZD23 ZF05 ZF13 ZF33 ZF34 ZF35 ZF36

5C006 AA01 AA22 AF43 AF46 AF82 BC16 BC23 BF04 BF11 BF22

BF25 BF43 FA42 FA43 FA51

5C080 AA10 BB05 CC03 DD22 EE19 FF09 FF11 GG08 JJ02 JJ04

KK43

|                |                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器驱动装置，液晶显示系统和用于液晶驱动的半导体集成电路器件                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2011170376A</a>                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2011-09-01 |

| 申请号            | JP2011090727                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2011-04-15 |

| [标]申请(专利权)人(译) | 瑞萨电子株式会社<br>RENASAS日本北部SEMICON                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 瑞萨电子公司<br>瑞萨北日本半导体公司                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 山口聰<br>遠藤祐弘<br>久保健彦                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 山口聰<br>遠藤祐弘<br>久保健彦                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F1分类号          | G09G3/36 G09G3/20.611.F G09G3/20.623.F G02F1/133.575 G02F1/133.510 G09G3/20.621.M G09G3/20.623.V                                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 2H193/ZC25 2H193/ZD11 2H193/ZD23 2H193/ZF05 2H193/ZF13 2H193/ZF33 2H193/ZF34 2H193/ZF35 2H193/ZF36 5C006/AA01 5C006/AA22 5C006/AF43 5C006/AF46 5C006/AF82 5C006/BC16 5C006/BC23 5C006/BF04 5C006/BF11 5C006/BF22 5C006/BF25 5C006/BF43 5C006/FA42 5C006/FA43 5C006/FA51 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD22 5C080/EE19 5C080/FF09 5C080/FF11 5C080/GG08 5C080/JJ02 5C080/JJ04 5C080/KK43 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                        |         |            |

### 摘要(译)

要解决的问题：提供一种紧凑型液晶驱动器（用于驱动液晶的半导体集成电路），具有内置DA转换器电路，用于将数字图像数据转换为模拟灰度电压并输出施加到信号线的电压（源线）彩色液晶面板。解决方案：输出转换为灰度电压的图像信号的最终级的输出放大器（160：AMP1-AMP480）被分成多个组。将图像数据转换为灰度电压的D/A转换器电路（160：DAC1-DAC40）被布置为对这些组共用的电路，并且在改变组的同时执行D/A转换器电路的时间共享操作。选择最后一级的输出放大器以对与相同颜色的图像信号有关的输出放大进行分组。选择器功能布置在D/A转换电路和输出放大器之间，并且由D/A转换电路转换成灰度电压的图像信号被分配到期望的保持电路。