(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-53693

(P2011-53693A)

(43) 公開日 平成23年3月17日(2011.3.17)

| (51) Int.Cl.                | F 1        | テーマコード (参考)       |

|-----------------------------|------------|-------------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36  | 2 H 1 9 3         |

| <b>G09G 3/34</b> (2006.01)  | G09G 3/34  | J 5 C 0 0 6       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 6 1 1 E 5 C 0 8 0 |

| <b>G02F 1/133</b> (2006.01) | G02F 1/133 | 5 7 5             |

|                             | G02F 1/133 | 5 1 O             |

審査請求 有 請求項の数 13 O L (全 12 頁) 最終頁に続く

|              |                                     |          |                                                                                                                                                         |

|--------------|-------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2010-215449 (P2010-215449)        | (71) 出願人 | 390019839<br>三星電子株式会社<br>SAMSUNG ELECTRONICS CO., LTD.<br>大韓民国京畿道水原市靈通区梅灘洞 416<br>416, Maetan-dong, Yeongtong-gu, Suwon-si,<br>Gyeonggi-do 442-742 (KR) |

| (22) 出願日     | 平成22年9月27日 (2010.9.27)              |          |                                                                                                                                                         |

| (62) 分割の表示   | 特願2001-325224 (P2001-325224)<br>の分割 |          |                                                                                                                                                         |

| 原出願日         | 平成13年10月23日 (2001.10.23)            |          |                                                                                                                                                         |

| (31) 優先権主張番号 | 2000-82004                          | (74) 代理人 | 100094145<br>弁理士 小野 由己男                                                                                                                                 |

| (32) 優先日     | 平成12年12月26日 (2000.12.26)            | (74) 代理人 | 100106367<br>弁理士 稲積 朋子                                                                                                                                  |

| (33) 優先権主張国  | 韓国 (KR)                             |          |                                                                                                                                                         |

最終頁に続く

(54) 【発明の名称】 フリッカが低減された液晶表示装置及びフリッカ低減方法

(57) 【要約】 (修正有)

【課題】 フリッカが低減された液晶表示装置及びフリッカ低減方法を提供する。

【解決手段】 色信号 R G B を構成するビットのトグリングをトグリング検出器 6 1 で検出し、トグリングされたビット数を加算器 6 2 により計算する。第 1 比較器 6 3 は計算結果と Ref 1 の比較結果を第 1 カウンタ 6 5 に出力する。第 1 カウンタ 6 5 は 1 ラインでのフリッカの個数をカウントし、第 2 比較器 6 6 はカウント結果と Ref 2 の比較結果を第 2 カウンタ 6 7 に出力する。第 2 カウンタ 6 7 は 1 フレームでのフリッカの個数をカウントし、第 3 比較器 6 8 はカウント結果と Ref 3 の比較結果をバックライトの制御信号 Dim として出力する。以上のような構成により、1 つのフレームで所定比率以上のフリッカが発生する時、バックライトの明るさを調節して、液晶表示装置で視覚的に感知されるフリッカを減少させる。

【選択図】 図 3

## 【特許請求の範囲】

## 【請求項 1】

複数の画素を備える液晶パネルと、

前記液晶パネルに均一な明るさの平面光を提供するためのバックライトと、

ゲートクロック信号及び複数の制御信号を発生させ、前記液晶パネルに表示される色信号が階調値に応じてビットで表現される時、前記色信号の各ビットと前記ビットを遅延させて生成された遅延ビットを利用し、前記色信号の各ビットが反転しているか否かを判別し、全てのビットが反転された画素の数に応じて前記バックライトの明るさを調節するための制御信号を発生させるタイミング制御回路と、

前記ゲートクロック信号に応じて色信号に対応する複数の階調電圧を発生させるための階調電圧発生回路と、

前記ゲートクロック信号に応じて前記複数の画素を1ラインずつ順番にスキャンするためのゲート駆動回路と、

前記複数の制御信号に応じて前記複数の階調電圧から色信号に対応するデータ電圧を発生させ、前記ゲート駆動回路によるスキャンに合わせて前記データ電圧を前記液晶パネルに印加するためのソース駆動回路と、

を含み、同一階調値であり、互いに異なる極性の色信号は、互いに全てのビットが反転するように表現される液晶表示装置。

## 【請求項 2】

前記タイミング制御回路は、

前記ゲートクロック信号及び前記複数の制御信号を発生させるための信号発生手段と、前記2つの色信号の間で各ビットが反転しているか否かを判別し、前記2つの色信号の間で全てのビットが反転している画素の数に応じて前記制御信号を発生させるフリッカ低減手段と、

を含む、請求項1に記載の液晶表示装置。

## 【請求項 3】

前記フリッカ低減手段は、

前記液晶パネルの画素ごとに前記2つの色信号の間で全てのビットが反転していることを検出するフリッカ感知部と、

前記フリッカ感知部によって検出された結果に応じ、1つのラインに含まれる画素のうち、前記2つの色信号の間で全てのビットが反転している画素の個数をカウントするための第1カウンタと、

前記第1カウンタでカウントされた結果を第1基準値と比較して、前記1つのラインに含まれる全ての画素について前記2つの色信号の間で全てのビットが反転していることを検出するための第1比較器と、

前記第1比較器によって検出された結果に応じ、前記2つの色信号の間で全てのビットが反転している画素しか含まないラインの本数をカウントするための第2カウンタと、

前記第2カウンタでカウントされた結果を第2基準値と比較して、前記カウントされた結果が前記第2基準値より大きいか、同一である場合、前記バックライトを暗くする制御信号を発生させるための第2比較器と、

を含む、請求項2に記載の液晶表示装置。

## 【請求項 4】

前記フリッカ感知部は、

前記2つの色信号の間で対応するビットに対してXOR演算を実行して、前記2つの色信号の間で反転しているビットを検出するためのビット反転検出器と、

前記ビット反転検出器によるXOR演算の結果に応じて、前記2つの色信号ごとに反転しているビットの個数をカウントするための加算器と、

前記加算器によってカウントされたビットの個数を第3基準値と比較して、前記2つの色信号の間で全てのビットが反転していることを検出するための第3比較器と、

を含む、請求項3に記載の液晶表示装置。

10

20

30

40

50

**【請求項 5】**

前記フリッカ低減手段は、前記バックライトを暗くする制御信号を発生させた後、新たなフレームについて前記第2カウンタでカウントされたラインの本数が前記第2基準値未満である時、前記バックライトを明るく調節するための制御信号を発生させる、請求項3に記載の液晶表示装置。

**【請求項 6】**

前記フリッカ低減手段は、前記バックライトの明るさを2段階に調節できる、請求項5に記載の液晶表示装置。

**【請求項 7】**

各画素に対する色信号を液晶表示装置に入力する段階と、

各画素について連続して入力され、階調値に応じてビットで表現された2つの隣接する色信号の間で各ビットが反転しているか否かを判別する段階と、

液晶パネルの1つのラインに含まれる画素のうち、前記2つの色信号の間で全てのビットが反転している画素の個数をカウントして第1カウント値として求める段階と、

前記第1カウント値に基づき、前記2つの色信号の間で全てのビットが反転している画素しか含まないラインの本数をカウントして第2カウント値として求める段階と、

前記第2カウント値に応じて前記液晶表示装置の明るさを調節する段階と、

を含み、同一階調値であり、互いに異なる極性の色信号は、互いに全てのビットが反転するように表現される液晶表示装置のフリッカ低減方法。

**【請求項 8】**

前記2つの色信号の間で各ビットが反転しているか否かを判別する段階は、

前記2つの色信号の間で対応するビットに対してXOR演算を実行して、前記2つの色信号の間で反転しているビットを検出する段階と、

前記XOR演算の結果に応じて、前記2つの色信号ごとに反転しているビットの個数をカウントして第3カウント値として求める段階と、

前記第3カウント値を第1基準値と比較して、前記2つの色信号の間で全てのビットが反転していることを検出する段階と、

を含む、請求項7に記載の液晶表示装置のフリッカ低減方法。

**【請求項 9】**

前記第1カウント値を求める段階は、前記第3カウント値が前記第1基準値と同一である場合、前記第1カウント値を増加させる段階を含み、

前記第2カウント値を求める段階は、前記第1カウント値を第2基準値と比較する段階を含む、

請求項8に記載の液晶表示装置のフリッカ低減方法。

**【請求項 10】**

前記第2カウント値を求める段階は、前記第1カウント値が前記第2基準値と同一である場合、前記第2カウント値を増加させる段階を含む、請求項9に記載の液晶表示装置のフリッカ低減方法。

**【請求項 11】**

前記液晶表示装置の明るさを調節する段階は、

前記第2カウント値を第3基準値と比較する段階と、

前記第2カウント値が前記第3基準値より大きいか、同一である場合、バックライトを暗く調節して、視覚的に認識されるフリッカを低減させる段階と、

を含む、

請求項10に記載の液晶表示装置のフリッカ低減方法。

**【請求項 12】**

前記液晶表示装置の明るさを調節する段階は、前記バックライトが暗く調節された後、前記第2カウント値が前記第3基準値未満であると、前記バックライトを明るく調節する段階を含む、請求項11に記載の液晶表示装置のフリッカ低減方法。

**【請求項 13】**

10

20

30

40

50

前記バックライトの明るさは2段階で調節される、請求項12に記載の液晶表示装置のフリッカ低減方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置(liquid crystal display:LCD)に関し、さらには薄膜トランジスタ(thin film transistor:TFT)をスイッチング素子として使用するアクティブマトリックス液晶表示装置の残像又はフリッカを低減できる装置及び方法に関する。

10

【背景技術】

【0002】

アクティブマトリックスLCDの駆動方式はマトリックス状に配列された各画素に非線形特性を有するアクティブ素子を付加して各画素をスイッチングすることであり、アクティブ素子としては、通常、薄膜トランジスタを使用する。

【0003】

このようなTFTLCDの光学的な表示特性は、TFT素子、液晶材料、配向膜材料、セル間隔、カラーフィルタ等の影響を受け、長時間使用することによって表示特性を低下させるフリッカ又は残像が現れることである。

【0004】

このようなフリッカを低減する方法は、1993年10月、Kimura等による米国特許第5,253,091号の“LIQUID CRYSTAL DISPLAY HAVING REDUCED FLICKERS”と、1995年7月、Suzuki等による米国特許第5,436,747号の“REDUCED FLICKER LIQUID CRYSTAL DISPLAY”に開示されている。

20

【0005】

一般に、液晶表示装置は画素電極及びTFTが形成されたTFT基板と、共通電極及びカラーフィルタが形成されたカラーフィルタと、その間に注入されている液晶物質とで構成される。

【0006】

このような液晶表示装置では、カラーフィルタ基板に形成された共通電極とTFT基板に形成された画素電極に電圧を印加して2つの電極の間に電位差を与えて液晶分子を駆動させる。通常、2つの電極の間に印加される電界の方向を周期的に変える。

30

【0007】

例えば、共通電極に加える共通電極電圧を $V_{com}$ にすると、TFTを通じて画素電極に印加される信号電圧は共通電極電圧 $V_{com}$ に対して周期的に反転される。この時、共通電極電圧に対してプラスである電圧の実効値とマイナスである電圧の実効値が同一であると、残像もフリッカも発生しない。しかし、2つの電圧の実効値が異なると、2つの電極の間には直流成分を有する電界が印加され、この直流成分によって残像が発生する。即ち、同一の階調に対するプラス電圧とマイナス電圧のデータ電圧が共通電極電圧を中心にして対称に印加されないと、プラス電圧及びマイナス電圧各々に従って画素の明るさが異なり、このような明るさの差がフリッカとして現れる。又、2つの基板の間に直流成分の電圧が印加されて残像又は焼付き(image sticking)が生じる。最初は共通電極電圧が正確に調節されて直流成分がなくても、液晶表示装置を使用するに従ってパネルの薄膜トランジスタ又は配向膜又は保護膜に物理的な変化が生じるので、共通電極電圧が最適条件から外れて、フリッカが増加する。さらに、液晶表示装置の大型化と高輝度化に従って、目によって認識されるフリッカの量は増加する。

40

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、前述した問題点を解決するためのものであり、視覚的に認識されるフリッカ

50

の量を減少させ得る装置及び方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

複数の画素を備える液晶パネルと、

前記液晶パネルに均一な明るさの平面光を提供するためのバックライトと、

ゲートクロック信号及び複数の制御信号を発生させ、前記液晶パネルに表示される色信号が階調値に応じてビットで表現され時、前記色信号の各ビットと前記ビットを遅延させて生成された遅延ビットを利用し、前記色信号の各ビットが反転しているか否かを判別し、全てのビットが反転された画素の数に応じて前記バックライトの明るさを調節するための制御信号を発生させるタイミング制御回路と、

前記ゲートクロック信号に応じて色信号に対応する複数の階調電圧を発生させるための階調電圧発生回路と、

前記ゲートクロック信号に応じて前記複数の画素を1ラインずつ順番にスキャンするためのゲート駆動回路と、

前記複数の制御信号に応じて前記複数の階調電圧から色信号に対応するデータ電圧を発生させ、前記ゲート駆動回路によるスキャンに合わせて前記データ電圧を前記液晶パネルに印加するためのソース駆動回路と、

を含み、同一階調値であり、互いに異なる極性の色信号は、互いに全てのビットが反転するように表現される液晶表示装置を提供する。

【0010】

また、このような液晶表示装置を駆動するための方法を提供する。

【発明の効果】

【0011】

前述のような本発明によると、簡単な回路構成によって液晶表示装置で視覚的に感知されるフリッカの量を減少させ得る。

【図面の簡単な説明】

【0012】

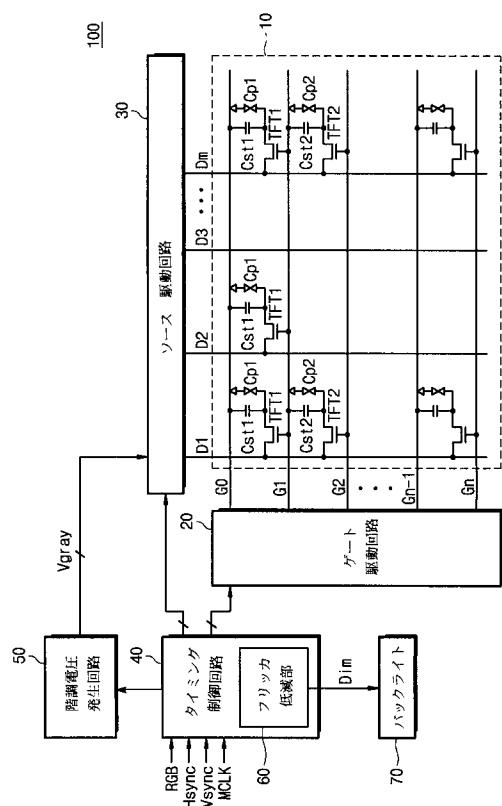

【図1】本発明による液晶表示装置の構成を示す構成図である。

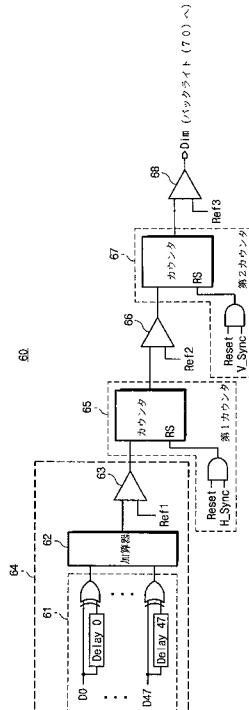

【図2】図1に示すタイミング制御回路の構成を示す構成図である。

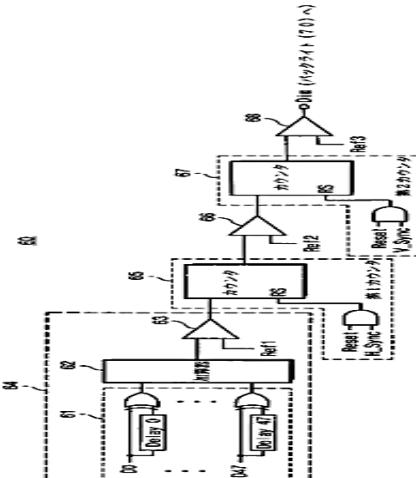

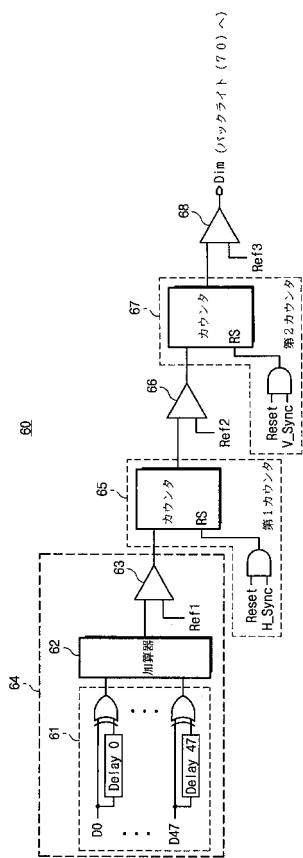

【図3】図2に示すフリッカ低減部の構成を示す回路図である。

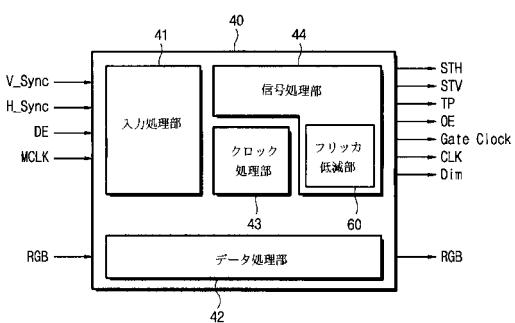

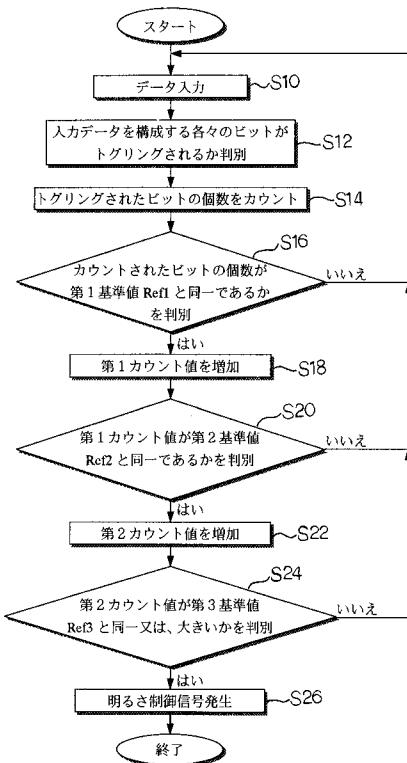

【図4】本発明による液晶表示装置のフリッカ低減方法を示すフローチャートである。

【発明を実施するための形態】

【0013】

以下、添付した図を参照して、本発明の望ましい実施形態を詳細に説明する。

【0014】

本発明の液晶表示装置は、液晶パネルに表示される1つのフレーム全体のフリッカの量を感知し、感知されたフリッカの量に従って液晶パネルの明るさを調節する制御信号を発生するフリッカ低減部を備えるタイミング制御回路を含む。タイミング制御回路は1つのフレームで所定比率以上のフリッカが発生すると、バックライトの明るさが暗くなるよう40に調節する制御信号を発生して、液晶表示装置において視覚的に感知されるフリッカの量を減少させる。

【0015】

図1は本発明による液晶表示装置100の構成を示す構成図である。図を参照すると、液晶表示装置100は液晶パネル10と、液晶パネル10に連結されたゲート駆動回路20と、ソース駆動回路30と、フリッカ低減部60を備えるタイミング制御回路40と、階調電圧発生回路50と、バックライト70とを含む。

【0016】

液晶パネル10は、複数のゲートラインG0～Gnと、ゲートラインG0～Gn各々に垂直に交差する複数のデータラインD1～Dmで構成される。各々のゲートラインG0～Gnにはゲート駆動回路20が連結され、各々のデータラインD1～Dmにはソース駆動回

路30が連結される。液晶パネル10を通じて表示される画像は赤(red:R)、緑(green:G)、青(blue:B)、3種類のカラーフィルタの組合せによって得られ、液晶表示装置100はこれらの組合せによってカラー画像だけでなく純粋な赤、緑、青の階調値を示す。バックライト70は液晶パネル10に連結され、液晶パネル10に明るさが均一な平面光を提供する。階調電圧発生回路50はソース駆動回路30に連結され、液晶駆動電圧を発生するのに基準になる電圧Vgrayを発生する。ゲート駆動回路20が液晶パネル10の画素を1列ずつ順次にスキャンニングすると、ソース駆動回路30は階調電圧発生回路50から出力される基準電圧Vgrayに応じてタイミング制御回路40を通じて入力される色信号RGBによる液晶駆動電圧を発生し、発生された液晶駆動電圧を毎スキャンニングごとに液晶パネル10に印加する。

10

## 【0017】

一方、タイミング制御回路40は色信号RGB、ライン区別信号H\_Sync、フレーム区別信号V\_Sync及びクロック信号MCLKに応じてゲート駆動回路20及びソース駆動回路30で必要な制御信号を発生する。そして、タイミング制御回路40はその内部に備えられたフリッカ低減部60によって色信号RGBに含まれたフリッカを検出し、検出されたフリッカの量に従って液晶パネル10の明るさを調節することによって、液晶パネル10を通じて表示されるフリッカの量を視覚的に減少させる。

## 【0018】

通常、フリッカに対する実際的な認識は個人差があり、又、個人の状態等によっても変化する。従って、表示技術分野ではフリッカを精神生理学的な方法によって測定することを論議している。例えば、フリッカに対する敏感性は年を取るほど減少し、疲労度に従って減少する。このように、フリッカは視覚的な感度に従って異なって感じられ、照度が高い時に容易に感知されるのに対して、照度が低くなるほど感知しにくい特徴がある。従って、本発明によるタイミング制御回路40はこのような特徴を利用してフリッカが所定レベル以上発生する場合、画面の明るさを暗くしてフリッカが視覚的によく感知されないようにし、フリッカが所定レベル以下発生する場合、画面の明るさを元の状態に復元する。このような動作を実行するタイミング制御回路40の構成は次のとおりである。

20

## 【0019】

図2は図1に示すタイミング制御回路40の構成を示す構成図である。図2を参照すると、タイミング制御回路40の構成は設計方法により異なるが、入力処理部41と、データ処理部42と、クロック処理部43と、信号処理部44などで構成される。そして、信号処理部44の内部にはフリッカの量に従って液晶パネル10の明るさを調節するフリッカ低減部60を含む。

30

## 【0020】

データ処理部42は色信号RGBのタイミングを調節し、クロック処理部43はクロック信号MCLKのタイミングを調節する。信号処理部44は、グラフィックコントローラから入力されるライン区別信号H\_Sync及びフレーム区別信号V\_Sync、色信号RGBが出力される間にハイレベルを示すDE信号、そして、クロック信号MCLKに応じて、ゲート駆動回路20とソース駆動回路30で必要な制御信号(例えば、STH(start horizontal signal)、STV(start vertical signal)、ロード信号(load signal:TP)、ゲートクロック信号(gate clock)、ゲートオンイネーブル信号(OE)等)を発生する。これら制御信号の内、ゲートクロック信号は階調電圧を発生するための階調電圧発生回路や、液晶パネルの画素を1列ずつ順次にスキャンニングするためのゲート駆動回路を制御している。入力処理部41はグラフィックコントローラ(図示しない)から入力される可変的な信号を一定した信号に変換し、データ処理部42と信号処理部44での作業を容易にする。そして、タイミング制御回路40に備えられたフリッカ低減部60は液晶パネル10に表示される1つのフレーム全体のフリッカの量を感知し、感知されたフリッカの量に従って液晶パネル10の明るさを調節する制御信号Dimをバックライト70に供給する。バックライト70にはディミング回路(dimming circuit)(図示

40

50

しない)が備えられ、タイミング制御回路40から発生される制御信号Dimに応じてバックライト70の明るさを調節する。このようなバックライト70のディミング回路は、1999年8月、Praiswaterによる米国特許第5,939,830号“MET HOD AND APPARATUS FOR DIMMING A LAMP IN A BACKLIGHT OF A LIQUID CRYSTAL DISPLAY”に開示されている。

#### 【0021】

図3は本発明の望ましい実施形態によるフリッカ低減部60の構成を示す回路図である。図3を参照すると、本発明によるフリッカ低減部60はトグリング検出器61と、加算器62及び第1比較器63を備えるフリッカ感知部64と、第1カウンタ65と、第2比較器66と、第2カウンタ67と、第3比較器68とを含む。第1乃至第3比較器63, 66, 68に入力される第1乃至第3基準値Ref1~Ref3は液晶表示装置100の解像度及び液晶表示装置100の駆動方法に従って異なるが、本発明では $1280 \times 1024$ の解像度を有するSXGA(super extended graphics arrays)と、奇数番目の画素と偶数番目の画素を同時に入力できるデュアルポート駆動を例にして説明する。

#### 【0022】

フリッカ感知部64に備えられたトグリング検出器61は、入力される色信号RGBがフリッカされることを感知するために、色信号RGBを構成する各々のビットがトグリングされるかを検出する。このために、トグリング検出器61は色信号RGBを各々のビット別D0~D47に区分して取り込み、入力されたビットD0~D47をディレイDelay0~Delay47を通じて所定時間遅延させた後、遅延されない元のビットD0~D47と所定時間遅延されたビット各々に対するXOR演算を実行する。入力されたビットがトグリングされる場合、XOR演算結果は1になり、入力されたビットがトグリングされない場合、XOR演算結果は0になる。このようなトグリング検出器61のXOR演算結果は加算器62に入力されて加算され、入力された色信号RGBのうち、トグリングされたビットの個数が計算される。加算器62によって得られたトグリングされたビットの個数は第1比較器63によって第1基準値Ref1と比較され、0又は1の値を有する比較結果が第1カウンタ65に入力される。ここで、第1基準値Ref1は一度に入力されるデータのビットの個数を基準にする。例えば、8ビットで構成された色信号RGBが入力される場合、赤、緑、青の色信号ごとに各々8ビットのデータが要求されるので、1つの画素を示すのに要求されるビットの数は $8 \times 3 = 24$ である。近年、幅広く使用されるデュアルポート駆動の時は奇数番目の画素と偶数番目の画素が同時に入力されるので、一度に入力されるデータのビットの数は $8 \times 3 \times 2 = 48$ である。

#### 【0023】

フリッカ感知部64は入力されるデータを構成する各々のビットD0~D47に対してトグリングされるかを検出して、入力されるデータがフリッカされるかを感知する。なぜならば、フリッカはトグリングデータとして発生されるためである。又、フリッカ感知部64は入力されるデータを構成する各々のビットD0~D47が全部トグリングされる場合、入力データがフリッカされることを意味する1を出力し、そうではない場合、0を出力する。

#### 【0024】

フリッカ感知部64によって入力データがフリッカされるかが感知されると、1又は0の値を有する感知結果が第1カウンタ65に入力される。第1カウンタ65は10ビットカウンタで構成されたトグリングされた画素格納庫として、感知結果の他にANDゲートを通じてリセット信号Reset及びライン区別信号H\_Syncを取り込む。即ち、第1カウンタ65はフリッカ感知部64から伝送される感知結果に応じてフリッカが発生された入力データの個数を画素単位でカウントし、ライン区別信号H\_Syncが入力されるとリセットされて、1つのラインで発生したフリッカの数を示す。このような動作によって、1つのライン内でフリッカが発生した画素の個数が分かる。

10

20

30

40

50

## 【0025】

第1カウンタ65によって1つのラインで発生したフリッカの個数がカウントされると、カウントされた結果（即ち、第1カウント値）は第2比較器66によって第2基準値Ref2と比較される。ここで、第2基準値Ref2は1つのラインを構成する画素の個数を意味し、液晶表示装置100が2つの画素に対応するデータが同時に入力されるデュアルポート駆動であり、SXGAのように $1280 \times 1024$ の解像度を有する場合、第2基準値Ref2は640になる。第2比較器66は第1カウンタ65のカウント結果（即ち、第1カウント値）が第2基準値Ref2と同一であるかを判別して、カウント結果が第2基準値Ref2と同一であると1を出力し、同一ではないと0を出力する。即ち、第2比較器66は前述した比較動作によってライン全体でフリッカが発生するかを検出する。

10

## 【0026】

第1カウンタ65及び第2比較器66によってライン全体でフリッカが発生するかが検出されると、1又は0の値を有する各ラインに対するフリッカ検出結果は第2カウンタ67に入力される。第2カウンタ67は10ビットカウンタで構成されたトグリングされた画素格納庫として、フリッカが発生したラインの個数の他にリセット信号Reset及びフレーム区別信号V\_SyncをANDゲートを通じて取り込む。即ち、第2カウンタ67は第2比較器66から出力される各ラインに対するフリッカ検出結果をカウントし、フレーム区別信号V\_Syncが入力されるとリセットされて、1つのフレームに対するフリッカ発生ラインの個数だけをカウントする。このような動作によって、1つのフレーム内でフリッカが発生したラインの個数が分かる。

20

## 【0027】

第2カウンタ67によって1つのフレームに対するフリッカ発生ラインの個数がカウントされると、カウントされた結果（即ち、第2カウント値）は第3比較器68によって第3基準値Ref3と比較される。ここで、第3基準値Ref3は1つのフレームを構成するラインの個数に所定比率を掛け算した値として、 $1280 \times 1024$ の解像度を有するSXGAの場合、第3基準値Ref3は1024の約90%レベルに該当する値の921になる。これは1つのフレームを構成する画素の90%以上でフリッカが発生する場合、バックライト70の明るさを暗く調節して視覚的に認識されるフリッカの量を低減するためである。そのため、第3比較器68は第2カウンタ67のカウント結果（即ち、第2カウント値）を第3基準値Ref3と比較して、カウント結果が第3基準値Ref3より大きいか、同一である場合は、1の値を有する制御信号Dimをバックライト70に供給してバックライト70の明るさを暗く調節し、小さい場合は、0の値を有する制御信号Dimをバックライト70に供給する。

30

## 【0028】

このような動作を実行する本発明によるフリッカ低減部60は、図に示すように別途のメモリは不要であり、カウンタ及び比較器のような簡単な回路構成であるので、少量の回路面積を必要とするのみであり、回路の単価も減少する。

## 【0029】

前述のように、本発明によるタイミング制御回路40は1つのフレームを構成する各々の画素に対してフリッカが発生するかを感知し、フリッカが所定レベル以上発生する場合、バックライト70の明るさが暗くなるように調節する制御信号Dimを発生する。これに対して、タイミング制御回路40の制御によってバックライト70の明るさが暗くなり、1つのフレームの間に発生したフリッカの量が所定レベル以下に減少されると、タイミング制御回路40はバックライト70の明るさを元のように明るくなるように調節する制御信号Dimをバックライト70に供給して、視覚的に感知されるフリッカの量を低減する。この時、バックライト70に対する明るさ調節基準は基準値Ref1, Ref2, Ref3によって適切に調節される。基準値Ref1, Ref2, Ref3を適切に調節することによって、バックライト70に対する明るさの段階も調節可能である。

40

## 【0030】

50

図4は本発明の望ましい実施形態による液晶表示装置のフリッカ低減方法を示すフローチャートであり、図3に示すフリッカ低減部60で実行される動作手順を示す。図4を参照すると、段階S10では液晶表示装置の各画素に対応する色信号RGBが入力され、段階S12では入力された色信号RGBを構成する各々のビットに対してトグリングされるかが判別される。続いて、段階S14ではトグリングされたビットの個数がカウントされ、段階S16ではカウントされたビットの個数が第1基準値Ref1と同一であるかが判別される。ここで、第1基準値Ref1は一度に入力される色信号RGBの全体ビットの個数を意味し、デュアルポート駆動方式であり、SXGAのように $1280 \times 1024$ の解像度を有する液晶表示装置の場合、第1基準値Ref1は48になる。

## 【0031】

10

段階S16の判別結果、カウントされたビットの個数が第1基準値Ref1と同一であると、手順は段階S18に進行して第1カウント値を増加させ、カウントされたビットの個数が第1基準値Ref1と同一ではないと、手順は段階S10に戻って前述のような手順を繰り返す。カウントされたビットの個数が第1基準値Ref1と同一であるということは入力された色信号RGBの全てのビットがトグリングされてフリッカが発生することを意味し、第1カウント値は1つのラインのうち、トグリングされた画素の個数（即ち、フリッカが発生した画素の個数）を意味する。

## 【0032】

20

段階S20では、第1カウント値が第2基準値Ref2と同一であるかを判別する。第2基準値Ref2は1つのラインを構成する画素の個数を意味し、デュアルポート駆動方式であり、SXGAのように $1280 \times 1024$ の解像度を有する液晶表示装置の場合、第2基準値Ref2は640になる。段階S20の判別結果、第1カウント値が第2基準値Ref2と同一であると、即ち、1つのライン全体でフリッカが発生すると、手順は段階S22に進行して第2カウント値を増加させる。一方、第1カウント値が第2基準値Ref2と同一ではないと、即ち、1つのライン全体でフリッカが発生しないと、手順は段階S10に戻って前述のような手順を繰り返す。第2カウント値は1つのフレームのうち、トグリングされたラインの個数（即ち、フリッカが発生したラインの個数）を意味する。

## 【0033】

30

続いて、段階S24では第2カウント値が第3基準値Ref3と同一であるかを判別する。第3基準値Ref3は1つのフレームを構成するラインの個数に所定比率（例えば、90%）を掛け算した値を意味し、デュアルポート駆動方式であり、SXGAのように $1280 \times 1024$ の解像度を有する液晶表示装置の場合、第3基準値Ref3は比率が90%である時、約921になる。段階S24の判別結果、第2カウント値が第3基準値Ref3と大きいか、同一である場合、即ち、1つのフレーム全体で所定比率（例えば、90%）以上のフリッカが発生すると、手順は段階S26に進行してバックライト70の明るさが暗くなるように調節する制御信号Dimを発生する。一方、第2カウント値が第3基準値Ref3より小さい場合、即ち、1つのフレーム全体で所定比率以下のフリッカが発生すると、手順は段階S10に戻って前述のような手順を繰り返す。

## 【0034】

40

図4では1つのフレーム全体で所定比率以上のフリッカが発生する時、バックライト70の明るさが暗くなるように調節する制御信号Dimの発生に対して示している。一方、バックライト70の明るさが暗くなるように調節されている間、1つのフレーム全体でフリッカが所定比率以下になると、本発明によるタイミング制御回路40はバックライト70の明るさが明るくなるように調節する制御信号Dimを発生してバックライト70の明るさを調節する。前記方法において、バックライト70の明るさを調節する明るさ調節基準は、基準値を調節することによって適切に変更可能である。バックライトの明るさの段階は1段階以上の調節が可能である。

## 【0035】

50

本発明による回路の構成及び動作を説明したが、これは一例に過ぎない。本発明の思想から逸脱しない範囲で様々なに変化及び変更できる。

## 【符号の説明】

## 【0036】

- 1 0 液晶パネル

2 0 ゲート駆動回路

3 0 ソース駆動回路

4 0 タイミング制御回路

4 1 入力処理部

4 2 データ処理部

4 3 クロック処理部

4 4 信号処理部

5 0 階調電圧発生回路

6 0 フリッカ低減部

7 0 バックライト

1 0 0 液晶表示装置

10

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

|              |         |              |

|--------------|---------|--------------|

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|              | G 0 2 F | 1/133 5 3 5  |

|              | G 0 2 F | 1/133 5 5 0  |

|              | G 0 9 G | 3/20 6 1 2 U |

(72)発明者 朴 倖 源

大韓民国京畿道城南市寿井区新興 2 洞韓新アパート 3 棟 708 号

(72)発明者 田 万 福

大韓民国京畿道龍仁市器興邑旧葛里 405 - 1 豊林アパート 1108 号

(72)発明者 羅 根 植

大韓民国仁川光域市南洞区万寿 4 洞住公アパート 215 洞 1205 号

F ターム(参考) 2H193 ZA04 ZA06 ZC01 ZC25 ZF05 ZG02 ZH25 ZH43 ZH57

5C006 AA22 AF44 BB16 BF14 BF22 BF26 BF28 EA01 FA23

5C080 AA10 BB05 CC03 DD06 JJ02

|                |                                                                                                                                                                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 具有减少的闪烁的液晶显示装置和减少闪烁的方法                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2011053693A</a>                                                                                                                                                                                                                                | 公开(公告)日 | 2011-03-17 |

| 申请号            | JP2010215449                                                                                                                                                                                                                                                 | 申请日     | 2010-09-27 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 朴倖源<br>田万福<br>羅根植                                                                                                                                                                                                                                            |         |            |

| 发明人            | 朴倖源<br>田万福<br>羅根植                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | G09G3/36 G09G3/34 G09G3/20 G02F1/133 H04N5/66                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/3406 G09G3/3648 G09G2320/0247 G09G2320/0626                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/36 G09G3/34.J G09G3/20.611.E G02F1/133.575 G02F1/133.510 G02F1/133.535 G02F1/133.550 G09G3/20.612.U                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZA06 2H193/ZC01 2H193/ZC25 2H193/ZF05 2H193/ZG02 2H193/ZH25 2H193/ZH43 2H193/ZH57 5C006/AA22 5C006/AF44 5C006/BB16 5C006/BF14 5C006/BF22 5C006/BF26 5C006/BF28 5C006/EA01 5C006/FA23 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD06 5C080/JJ02 |         |            |

| 优先权            | 1020000082004 2000-12-26 KR                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                    |         |            |

### 摘要(译)

提供了一种具有减少的闪烁的液晶显示装置和减少闪烁的方法。解决方案：切换检测器61检测形成彩色信号RGB的位的切换，并通过加法器62计算切换位的数量。第一比较器63将计算结果和Ref1的比较结果输出到第一计数器65。第一计数器65对一条线上的闪烁次数进行计数，第二比较器66将计数结果和Ref2的比较结果输出至第二计数器67。第二计数器67对一帧中的闪烁次数进行计数，并且第三比较器68将计数结果和Ref3的比较结果作为背光控制信号Dim输出。利用上述配置，当在一帧中发生预定比率或更大比率的闪烁时，调节背光的亮度以减少液晶显示装置视觉上看到的闪烁。[选择图]图3