(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-14191

(P2012-14191A)

(43) 公開日 平成24年1月19日(2012.1.19)

| (51) Int.CI.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 193     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 5 C 006     |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5 C 058     |

| <b>H04N 5/66</b> (2006.01)  | G09G 3/20 | 5 C 080     |

|                             | G09G 3/20 | 6 1 2 U     |

審査請求 有 請求項の数 37 O L (全 28 頁) 最終頁に続く

|              |                                     |          |                                                                                                                                                              |

|--------------|-------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2011-204480 (P2011-204480)        | (71) 出願人 | 390019839<br>三星電子株式会社<br>Samsung Electronics Co., Ltd.<br>大韓民国京畿道水原市靈通区梅灘洞416<br>416, Maetan-dong, Yeongtong-gu, Suwon-si,<br>Gyeonggi-do, Republic of Korea |

| (22) 出願日     | 平成23年9月20日 (2011. 9. 20)            |          |                                                                                                                                                              |

| (62) 分割の表示   | 特願2004-168910 (P2004-168910)<br>の分割 |          |                                                                                                                                                              |

| 原出願日         | 平成16年6月7日 (2004. 6. 7)              |          |                                                                                                                                                              |

| (31) 優先権主張番号 | 2003-037232                         | (74) 代理人 | 100121382<br>弁理士 山下 託嗣                                                                                                                                       |

| (32) 優先日     | 平成15年6月10日 (2003. 6. 10)            | (72) 発明者 | 趙賢相<br>大韓民国京畿道水原市八達区靈通洞ビヨック骨8<br>8号地斗山アパート802棟601号                                                                                                           |

| (33) 優先権主張国  | 韓国(KR)                              |          |                                                                                                                                                              |

| (31) 優先権主張番号 | 2003-071030                         |          |                                                                                                                                                              |

| (32) 優先日     | 平成15年10月13日 (2003. 10. 13)          |          |                                                                                                                                                              |

| (33) 優先権主張国  | 韓国(KR)                              |          |                                                                                                                                                              |

最終頁に続く

(54) 【発明の名称】表示システム、表示システムの駆動方法及び表示システムの駆動装置

## (57) 【要約】

【課題】液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる表示システム、表示システムの駆動方法及び表示システムの駆動装置を提供する。

【解決手段】液晶表示装置における液晶の応答速度を向上させるための第1補償データを複数の温度区間別に記憶する第1メモリと、液晶表示装置の特性を考慮して設定された第2補償データを記憶する第2メモリと、以前フレームの階調データ及び現在フレームの階調データを考慮して、第1補償データに基づいて前記階調データを補償するか、あるいは第2補償データに基づいて階調データを補償するタイミング制御部を備え、タイミング制御部は、第1メモリからクロック信号に応答してパラレル変換される第1補償データ及び第2メモリに記憶される前記第2補償データのうちいずれか一方を出力する第1スイッチング部を含む。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

画像信号ソースから提供される階調データに基づいて画像を表示する液晶表示装置を備える表示システムであって、

複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を有する液晶パネルと、

前記ゲートラインにスキャン信号を提供するスキャン駆動部と、

前記データラインにデータ信号を提供するデータ駆動部と、

前記液晶表示装置における液晶の応答速度を向上させるための第1補償データを複数の温度区間に記憶する第1メモリと、

前記液晶表示装置の特性を考慮して設定された第2補償データを記憶する第2メモリと、

、以前フレームの前記階調データ及び現在フレームの前記階調データを考慮して、前記第1補償データを前記第1メモリから選択して読み出し前記第1補償データに基づいて前記階調データを補償する、あるいは前記第2補償データを前記第2メモリから読み出し前記第2補償データに基づいて前記階調データを補償するタイミング制御部と、

を含み、

前記タイミング制御部は、

前記第1メモリからクロック信号に応答してパラレル変換される前記第1補償データ及び前記第2メモリに記憶される前記第2補償データのうちいずれか一方を出力する第1スイッチング部と、

を含む表示システム。

**【請求項 2】**

前記タイミング制御部は、前記液晶表示装置の周辺又は内部の温度に関する情報である温度情報に基づいて、前記第1補償データを前記第1メモリから選択して読み出す、請求項1に記載の表示システム。

**【請求項 3】**

前記タイミング制御部は、前記第1補償データを前記第1メモリから選択して読み出すことが不能な場合に、前記第2補償データを前記第2メモリから読み出す、請求項1に記載の表示システム。

**【請求項 4】**

前記第1メモリは、不揮発性メモリである、請求項1に記載の表示システム。

**【請求項 5】**

前記第1メモリは、EEPROMである、請求項1に記載の表示システム。

**【請求項 6】**

前記第2メモリは、ROMである、請求項1に記載の表示システム。

**【請求項 7】**

前記タイミング制御部は、前記以前フレームの前記階調データと前記現在フレームの前記階調データとを考慮して前記第1補償データを選択する、請求項1に記載の表示システム。

**【請求項 8】**

前記液晶表示装置の周辺又は内部の温度に関する情報である温度情報を感知する温度感知部を更に含み、

前記タイミング制御部は、前記温度情報を前記温度感知部から受け取る、請求項1に記載の表示システム。

**【請求項 9】**

前記第1メモリは、複数の温度区間に応するルックアップテーブルを有し、

各ルックアップテーブルは、階調の値と前記第1補償データとを対応づけたテーブル

10

20

30

40

50

を備えた、請求項 1 に記載の表示システム。

**【請求項 1 0】**

前記第 1 メモリは、前記第 1 補償データの伝送におけるエラーの有無を区別するための情報であるサブチェックサムビットを各前記ルックアップテーブルについてさらに有する、請求項 9 に記載の表示システム。

**【請求項 1 1】**

前記第 1 メモリは、前記複数の前記ルックアップテーブルに対応する前記サブチェックサムビットの値を合計した情報であるトータルチェックサムビットを更に有する、請求項 1 0 に記載の表示システム。

**【請求項 1 2】**

前記タイミング制御部は、10

前記画素を制御するためのクロック信号であるドットクロック及び前記シリアル・パラレル変換部を制御するためのクロック信号であるシリアルクロックの少なくとも一方に応答して、前記第 1 補償データ及び前記第 2 補償データのいずれか一方を記憶する RAM をさらに有する、請求項 1 に記載の表示システム。

**【請求項 1 3】**

前記伝送クロックに応答して、前記シリアルクロック及び前記ドットクロックのいずれか一方を出力する第 2 スイッチング部と、

前記シリアル・パラレル変換部への前記第 1 補償データの伝送を完了させるためのクロック信号である伝送完了クロックに応答して、前記第 2 スイッチング部から出力されるクロック及び前記ドットクロックのいずれか一方を前記 RAM に出力する第 3 スイッチング部と、20

を更に含む、請求項 9 に記載の表示システム。

**【請求項 1 4】**

前記タイミング制御部は、30

前記第 1 メモリから読み出された前記第 1 補償データ及び第 2 メモリから読み出された前記第 2 補償データのいずれか一方をフレームプランキング期間に記憶する、請求項 1 に記載の表示システム。

**【請求項 1 5】**

前記タイミング制御部は、30

パラレル変換された前記第 1 補償データを一時的に記憶して、前記第 1 メモリから前記シリアル・パラレル変換部に前記第 1 補償データを伝送するためのクロック信号である伝送クロックと前記シリアル・パラレル変換部への前記第 1 補償データの伝送を完了させるためのクロック信号である伝送完了クロックと垂直同期信号とに基づいて、一時的に記憶された前記第 1 補償データを出力するバッファーと、

前記画素を制御するためのクロック信号であるドットクロックに応答して、前記第 1 スイッチング部から出力される前記第 1 補償データ及び前記第 1 スイッチング部から出力される第 2 補償データのいずれか一方を記憶する RAM と、

をさらに有する、請求項 6 に記載の表示システム。

**【請求項 1 6】**

前記伝送クロックに応答して、前記シリアル・パラレル変換部を制御するためのクロック信号であるシリアルクロック及び前記ドットクロックのいずれか一方を出力する第 2 スイッチング部と、40

前記伝送完了クロックと前記垂直同期信号とをアンド演算するアンドゲートと、

前記アンドゲートがアンド演算したクロックに応答して、前記第 2 スイッチング部から出力されるクロック及び前記ドットクロックのいずれか一方を前記バッファーに出力する第 3 スイッチング部と、

を更に含む、請求項 1 5 に記載の表示システム。

**【請求項 1 7】**

前記ドットクロックは、前記画像信号ソースから前記階調データが提供されることに同50

期している、請求項 1 5 に記載の表示システム。

**【請求項 1 8】**

前記シリアルクロックは、前記伝送クロックに同期している、請求項 1 7 に記載の表示システム。

**【請求項 1 9】**

前記第 2 メモリは、複数の温度区間に応じて複数のルックアップテーブルを有し、各前記ルックアップテーブルは、階調の値と前記第 1 補償データとを対応づけたテーブルを備えた、請求項 1 に記載の表示システム。

**【請求項 2 0】**

前記第 2 メモリは、前記第 2 補償データの伝送におけるエラーの有無を区別するための情報であるサブチェックサムビットを各前記ルックアップテーブルについてさらに有する、請求項 1 9 に記載の表示システム。 10

**【請求項 2 1】**

前記第 2 メモリは、前記複数の前記ルックアップテーブルに対応する前記サブチェックサムビットの値を合計した情報であるトータルチェックサムビットを更に有する、請求項 1 9 に記載の表示システム。

**【請求項 2 2】**

複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を備えた表示システムの駆動方法において、 20

( a ) 前記ゲートラインにスキャン信号が順次供給される段階と、

( b ) 前記表示システムの周辺又は内部の温度に関する情報である温度情報と現在フレームの階調データと以前フレームの階調データとを考慮して、前記液晶表示装置における液晶の応答速度を向上させるための第 1 補償データを複数の温度区間別に記憶する第 1 メモリから前記第 1 補償データが読み出されるか、または、前記液晶表示装置の特性を考慮して設定された第 2 補償データを記憶する第 2 メモリから前記第 2 補償データが読み出される段階と、

( c ) 前記第 1 メモリからクロック信号に応答してパラレル変換される前記第 1 補償データ及び前記第 2 メモリに記憶される前記第 2 補償データのうちいずれか一方を出力する段階と、 30

( d ) 前記第 1 及び第 2 補償データに基づいて前記階調データが補償され、補償された前記階調データに基づいてデータ電圧が前記データラインに供給される段階と、を含む、表示システムの駆動方法。

**【請求項 2 3】**

複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を備えた表示システムの駆動方法において、

( a ) 前記ゲートラインにスキャン信号が順次供給される段階と、

( b ) 前記表示システムの周辺又は内部の温度に関する情報である温度情報と垂直同期信号の周波数と、現在フレームの階調データと以前フレームの階調データとを考慮して、第 1 補償データを複数の温度区間別に記憶する第 1 メモリから前記第 1 補償データが読み出されたか、または、前記液晶表示装置の特性を考慮して設定された第 2 補償データを記憶する第 2 メモリから前記第 2 補償データが読み出される段階と、

( c ) 前記第 1 メモリから前記シリアルパラレル変換部に前記第 1 補償データを伝送するためのクロック信号の伝送クロックに応答してパラレル変換される前記第 1 補償データ及び前記第 2 メモリに記憶される前記第 2 補償データのうちいずれか一方を出力する段階と、

( d ) 前記第 1 及び第 2 補償データに基づいて前記階調データが補償され、補償された 50

前記階調データに基づいてデータ電圧が前記データラインに供給される段階と、

を含む、表示システムの駆動方法。

**【請求項 24】**

前記補償データは、前記温度情報に対応するルックアップテーブルに記憶され、

前記(b)段階では、前記ルックアップテーブルが参照されることにより、前記補償データが生成される、請求項23に記載の表示システムの駆動方法。

**【請求項 25】**

前記ルックアップテーブルは、複数存在する、請求項24に記載の表示システムの駆動方法。

**【請求項 26】**

前記(b)段階では、フレームプランキング期間に前記ルックアップテーブルが参照される、請求項24に記載の表示システムの駆動方法。

**【請求項 27】**

複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を備えた表示システムの駆動装置であって、

前記ゲートラインにスキャン信号を提供するスキャン駆動部と、

前記データラインにデータ信号を提供するデータ駆動部と、

前記液晶表示装置における液晶の応答速度を向上させるための第1補償データを複数の温度区間に記憶する第1メモリと、

前記液晶表示装置の特性を考慮して設定された第2補償データを記憶する第2メモリと、

以前フレームの前記階調データ及び現在フレームの前記階調データを考慮して、前記第1補償データを前記第1メモリから読み出し前記第1補償データに基づいて前記階調データを補償する、あるいは前記第2補償データを前記第2メモリから読み出し前記第2補償データに基づいて前記階調データを補償するタイミング制御部と、

を含み、

前記タイミング制御部は、

前記第1メモリからクロック信号に応答してパラレル変換される前記第1補償データ及び前記第2メモリに記憶される前記第2補償データのうちいずれか一方を出力する第1スイッチング部と、

を含む、表示システムの駆動装置。

**【請求項 28】**

前記タイミング制御部は、

前記画素を制御するためのクロック信号であるドットクロック及び前記シリアル・パラレル変換部を制御するためのクロック信号であるシリアルクロックの少なくとも一方に応答して、前記第1補償データ及び前記第2補償データのいずれか一方を記憶するRAMをさらに有する、請求項27に記載の表示システムの駆動装置。

**【請求項 29】**

前記伝送クロックに応答して、前記シリアルクロック及び前記ドットクロックのいずれか一方を出力する第2スイッチング部と、

前記シリアル・パラレル変換部への前記第1補償データの伝送を完了させるためのクロック信号である伝送完了クロックに応答して、前記第2スイッチング部から出力されるクロック及び前記ドットクロックのいずれか一方を前記RAMに出力する第3スイッチング部と、

を更に含む、請求項28に記載の表示システムの駆動装置。

**【請求項 30】**

前記タイミング制御部は、

前記第1メモリから読み出された前記第1補償データ及び第2メモリから読み出された

10

20

30

40

50

前記第2補償データのいずれか一方をフレームプランギングきかんに記憶する、請求項27に記載の表示システムの駆動装置。

**【請求項31】**

前記タイミング制御部は、

パラレル変換された前記第1補償データを一時的に記憶して、前記第1メモリから前記シリアル-パラレル変換部に前記第1補償データを伝送するためのクロック信号である伝送クロックと前記シリアル-パラレル変換部への前記第1補償データの伝送を完了させるためのクロック信号である伝送完了クロックと垂直同期信号とに基づいて、一時的に記憶された前記第1補償データを出力するバッファーと、

前記画素を制御するためのクロック信号であるドットクロックに応答して、前記第1スイッチング部から出力される前記第1補償データ及び前記第1スイッチング部から出力される第2補償データのいずれか一方を記憶するRAMと、

をさらに有する、請求項27に記載の表示システムの駆動装置。

**【請求項32】**

前記伝送クロックに応答して、前記シリアル-パラレル変換部を制御するためのクロック信号であるシリアルクロック及び前記ドットクロックのいずれか一方を出力する第2スイッチング部と、

前記伝送完了クロックと前記垂直同期信号とをアンド演算するアンドゲートと、

前記アンドゲートがアンド演算したクロックに応答して、前記第2スイッチング部から出力されるクロック及び前記ドットクロックのいずれか一方を前記バッファーに出力する第3スイッチング部と、

を更に含む、請求項31に記載の表示システムの駆動装置。

**【請求項33】**

前記ドットクロックは、前記画像信号ソースから前記階調データが提供されることに同期している、請求項31に記載の表示システムの駆動装置。

**【請求項34】**

前記シリアルクロックは、前記伝送クロックに同期している、請求項33に記載の表示システムの駆動装置。

**【請求項35】**

前記第2メモリは、複数の温度区間に応するルックアップテーブルを有し、

各前記ルックアップテーブルは、階調の値と前記第1補償データとを対応づけたテーブルを備えた、請求項34に記載の表示システムの駆動装置。

**【請求項36】**

前記第2メモリは、前記第2補償データの伝送におけるエラーの有無を区別するための情報であるサブチェックサムビットを各前記ルックアップテーブルについてさらに有する、請求項35に記載の表示システムの駆動装置。

**【請求項37】**

前記第2メモリは、前記複数の前記ルックアップテーブルに対応する前記サブチェックサムビットの値を合計した情報であるトータルチェックサムビットを更に有する、請求項35に記載の表示システムの駆動装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、表示システム、表示システムの駆動方法及び表示システムの駆動装置に関する。

**【背景技術】**

**【0002】**

一般に、液晶表示装置(Liquid Crystal Display)は、スリムなデザイン、低消費電力、高解像度等の長所に基づいて、ノートパソコン、デスクトップ用等の各種応用製品が製造されている。特に、液晶パネルの大型化が可能になるにつれて

10

20

30

40

50

、TV用として注目されている。しかし、主に動画像を表示するTVに採用されるためには、液晶の応答速度が重要である。

### 【0003】

特に、TV用液晶表示装置は、従来のCRTを代替するものであるため、各特性項目もCRTを基準に比較するのが一般的であり、このような場合、液晶表示装置においては、応答速度が特に改善すべき特性である。

### 【発明の概要】

#### 【発明が解決しようとする課題】

### 【0004】

しかし、従来の液晶表示装置は、動画像を表示する際に応答速度が十分でないことがある。このような応答速度の問題を改善するために、従来の技術では、OCB(Optical Compensated Band)モードが使用されるか、強誘電性液晶物質FLCを使用する液晶表示装置が使用されることがある。ところが、このようにOCBモードやFLCなどが使用される場合には、液晶表示装置の周辺又は内部の温度変化に対する応答速度が不均一になるおそれがある。具体的には、次のようなおそれがある。

### 【0005】

このような液晶表示装置に必須的に備えられる液晶(Liquid Crystal)は、温度によってそれぞれの誘電率値が異なる。即ち、液晶分子が基板に平行な方向に配列された場合、即ち、液晶分子が光の方向と垂直方向に配列された場合の平行誘電率( )や、液晶分子が基板に垂直方向に配列された場合、即ち、液晶分子が光の方向と平行方向に配列された場合の垂直誘電率( )、平行誘電率( )と垂直誘電率( )との差誘電率( )は、温度によって変化する。これは、液晶のオーダーパラメーター(order parameter)が変化するためである。

### 【0006】

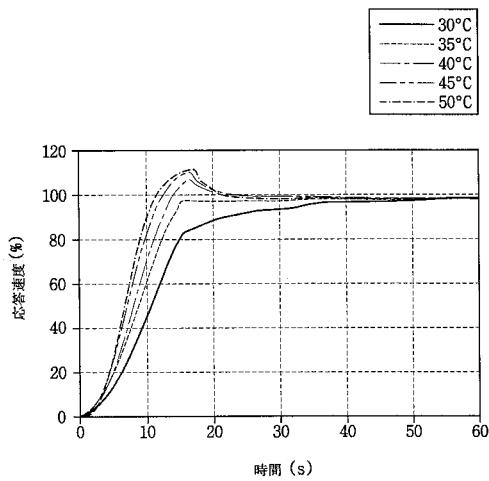

図1は、中間グレー階調での周辺温度(ambient temperature)別に液晶の応答速度変化を示したグラフである。図1に示したように、周辺の温度が高いほど、液晶の活性化程度が高くなって、液晶の応答速度は速くなる傾向がある。すなわち、動画像を表示する装置、例えば、TVに採用される液晶表示装置では、液晶表示装置の周辺又は内部の温度変化により応答速度が不均一になるおそれがある。

### 【0007】

特に、TVに採用される液晶表示装置が0以下のような低温環境で駆動される場合、応答速度は、正常的な環境の応答速度より遅いのみならず、はっきりしない画像を表示するおそれがある。

### 【0008】

本発明は、このような問題点を勘案したものであって、本発明の目的は、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる表示システム、表示システムの駆動方法及び表示システムの駆動装置を提供することにある。

### 【課題を解決するための手段】

### 【0009】

本発明に係る表示システムは、画像信号ソースから提供される階調データに基づいて画像を表示する液晶表示装置を備える表示システムであって、複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を有する液晶パネルと、前記ゲートラインにスキャン信号を提供するスキャン駆動部と、前記データラインにデータ信号を提供するデータ駆動部と、前記液晶表示装置における液晶の応答速度を向上させるための第1補償データを複数の温度区間に記憶する第1メモリと、前記液晶表示装置の特性を考慮して設定された第2補償データを記憶する第2メモリと、以前フレームの前記階調データ及び現在フレームの前記階調データを考慮して、前記第1補償データを前記第1メモリから選択して読み出し前記第1補償データに基

10

20

30

40

50

づいて前記階調データを補償する、あるいは前記第2補償データを前記第2メモリから読み出し前記第2補償データに基づいて前記階調データを補償するタイミング制御部とを含み、タイミング制御部は、前記第1メモリからクロック信号に応答してパラレル変換される前記第1補償データ及び前記第2メモリに記憶される前記第2補償データのうちいずれか一方を出力する第1スイッチング部を含む。

**【0010】**

この表示システムでは、第1メモリが、第1補償データを複数の温度区間別に記憶する。液晶表示装置の周辺又は内部の温度に関する情報である温度情報に基づいて、第1補償データを選択することができる。第2メモリが、第2補償データを記憶する。タイミング制御部が、以前フレームの階調データ及び現在フレームの階調データを考慮して、第1補償データを第1メモリから選択して読み出し、第1補償データに基づいて階調データを補償する。あるいは、タイミング制御部が、以前フレームの階調データ及び現在フレームの階調データを考慮して、第2補償データを第2メモリから読み出し、第2補償データに基づいて階調データを補償する。

10

**【0011】**

したがって、温度情報に基づいて選択された第1補償データに基づいて液晶表示装置が階調データを補償することができるので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる。また、第1補償データに基づいて階調データを補償できない場合でも、第2補償データに基づいて階調データを暫定的に補償することができる。

20

**【0012】**

また、本発明に係る表示システムの駆動方法は、複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を備えた表示システムの駆動方法であって、(a)前記ゲートラインにスキャン信号が順次供給される段階と、(b)前記表示システムの周辺又は内部の温度に関する情報である温度情報と現在フレームの階調データと以前フレームの階調データとを考慮して、前記液晶表示装置における液晶の応答速度を向上させるための第1補償データを複数の温度区間別に記憶する第1メモリから前記第1補償データが読み出されるか、または、前記液晶表示装置の特性を考慮して設定された第2補償データを記憶する第2メモリから前記第2補償データが読み出される段階と、(c)前記第1メモリからクロック信号に応答してパラレル変換される前記第1補償データ及び前記第2メモリに記憶される前記第2補償データのうちいずれか一方を出力する段階と、(d)前記第1及び第2補償データに基づいて前記階調データが補償され、補償された前記階調データに基づいてデータ電圧が前記データラインに供給される段階とを含む。

30

**【0013】**

この表示システムの駆動方法では、(b)段階において、温度情報と垂直同期信号の周波数とに基づいて、補償データが生成される。(b)段階において、現在フレームの階調データと以前フレームの階調データとを考慮して、補償データが読み出される。(b)段階において、補償データに基づいて階調データが補償される。(c)段階では、第1メモリからクロック信号に応答してパラレル変換される第1補償データ及び第2メモリに記憶される第2補償データのうちいずれか一方を出力する。(d)段階において、補償データに基づいて階調データが補償され、補償された階調データに基づいてデータ電圧がデータラインに供給される。

40

**【0014】**

したがって、温度情報に基づいて選択された補償データに基づいて液晶表示装置が階調データを補償するので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる。

**【0015】**

50

また、本発明の他の実施例による表示システムの駆動方法は、複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を備えた表示システムの駆動方法であって、(a)前記ゲートラインにスキャン信号が順次供給される段階と、(b)前記表示システムの周辺又は内部の温度に関する情報である温度情報と垂直同期信号の周波数と、現在フレームの階調データと以前フレームの階調データとを考慮して、第1補償データを複数の温度区間に記憶する第1メモリから前記第1補償データが読み出されたか、または、前記液晶表示装置の特性を考慮して設定された第2補償データを記憶する第2メモリから前記第2補償データが読み出される段階と、(c)前記第1メモリから前記シリアルパラレル変換部に前記第1補償データを伝送するためのクロック信号の伝送クロックに応答してパラレル変換される前記第1補償データ及び前記第2メモリに記憶される前記第2補償データのうちいずれか一方を出力する段階と、(d)前記第1及び第2補償データに基づいて前記階調データが補償され、補償された前記階調データに基づいてデータ電圧が前記データラインに供給される段階と、を含む。

10

## 【0016】

この表示システムの駆動方法では、(b)段階において、温度情報に基づいて、複数の補償データが読み出される。(c)段階において、現在フレームの階調データと以前フレームの階調データとに基づいて、液晶表示装置における液晶の応答速度を向上させるのに適した補償データが、複数の補償データから読み出される。(d)段階において、補償データに基づいて階調データが補償され、補償された階調データに基づいてデータ電圧が液晶表示装置に供給される。

20

## 【0017】

したがって、温度情報に基づいて選択された補償データに基づいて液晶表示装置が階調データを補償するので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる。

30

## 【0018】

本発明に係る表示システムの駆動装置は、複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートラインと前記データラインとにより囲まれた領域に形成され前記ゲートライン及び前記データラインに連結されている複数のスイッチング素子と、前記スイッチング素子により制御される複数の画素と、を備えた表示システムの駆動装置であって、前記ゲートラインにスキャン信号を提供するスキャン駆動部と、前記データラインにデータ信号を提供するデータ駆動部と、前記液晶表示装置における液晶の応答速度を向上させるための第1補償データを複数の温度区間に記憶する第1メモリと、前記液晶表示装置の特性を考慮して設定された第2補償データを記憶する第2メモリと、以前フレームの前記階調データ及び現在フレームの前記階調データを考慮して、前記第1補償データを前記第1メモリから読み出し前記第1補償データに基づいて前記階調データを補償する、あるいは前記第2補償データを前記第2メモリから読み出し前記第2補償データに基づいて前記階調データを補償するタイミング制御部とを含み、前記タイミング制御部は、前記第1メモリからクロック信号に応答してパラレル変換される前記第1補償データ及び前記第2メモリに記憶される前記第2補償データのうちいずれか一方を出力する第1スイッチング部とを含む。

40

## 【0019】

この表示システムの駆動装置では、タイミング制御部が、温度情報に基づいて選択された補償データを外部の画像信号ソースから受け取って記憶する。タイミング制御部が、以前フレームの階調データと現在フレームの階調データとを考慮して、補償データを読み出す。タイミング制御部が、補償データに基づいて、階調データを補償して出力する。データ駆動部が、補償された階調データに基づいて、データ電圧をデータラインに供給する。スキャン駆動部が、ゲートラインにスキャン信号を順次供給する。

50

**【0020】**

したがって、温度情報に基づいて選択された補償データに基づいて液晶表示装置が階調データを補償するので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる。

**【発明の効果】****【0021】**

本発明に係る表示システムでは、温度情報に基づいて選択された第1補償データに基づいて液晶表示装置が階調データを補償することができるので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる。また、第1補償データに基づいて階調データを補償できない場合でも、第2補償データに基づいて階調データを暫定的に補償することができる。

10

**【0022】**

本発明に係る表示システムの駆動方法では、温度情報に基づいて選択された補償データに基づいて液晶表示装置が階調データを補償するので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる。

**【0023】**

本発明の他の実施例による表示システムの駆動方法では、温度情報に基づいて選択された補償データに基づいて液晶表示装置が階調データを補償するので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができる。

20

**【0024】**

本発明に係る表示システムの駆動装置では、温度情報に基づいて選択された補償データに基づいて液晶表示装置が階調データを補償するので、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができ、第1補償データに基づいて階調データを補償できない場合でも、第2補償データに基づいて階調データを暫定的に補償することができる。

**【図面の簡単な説明】****【0025】**

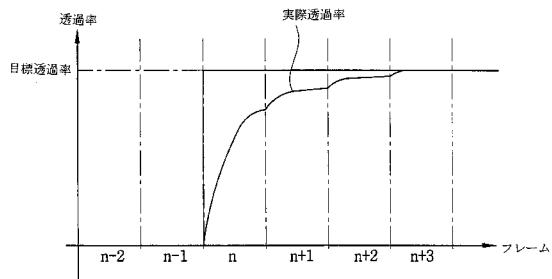

【図1】図1は、中間グレーでの周辺温度別液晶の応答速度の変化を示すグラフである。

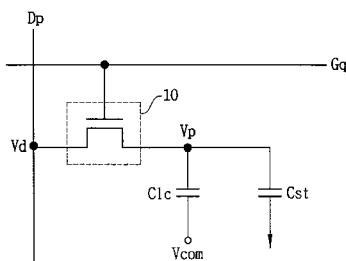

【図2】図2は、液晶表示装置において各画素の等価回路を示す図である。

30

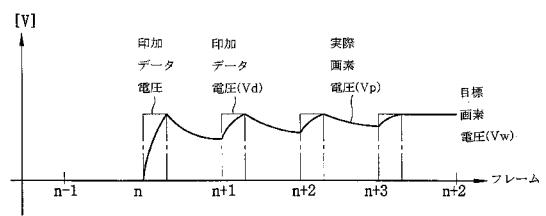

【図3】図3は、一般的な駆動方式で印加される場合のデータ電圧及び画素電圧を示す図である。

【図4】図4は、図3による駆動方法による液晶表示装置の透過率を示す図である。

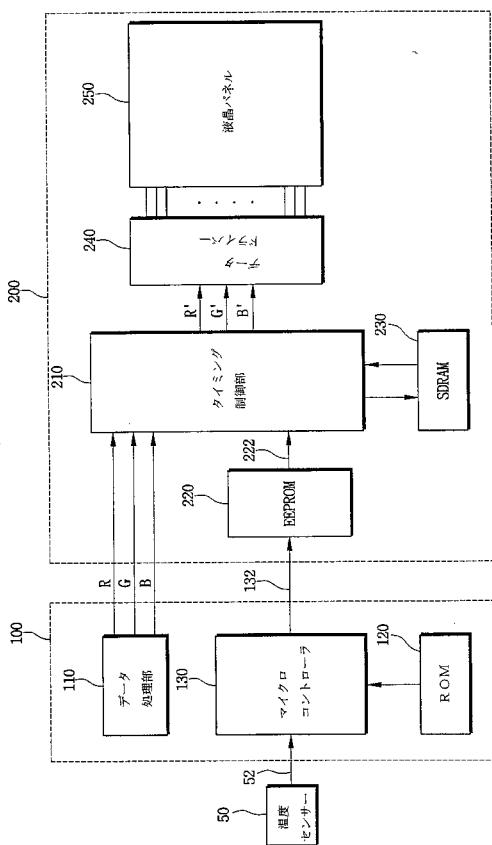

【図5】図5は、本発明による表示システムを説明するための図である。

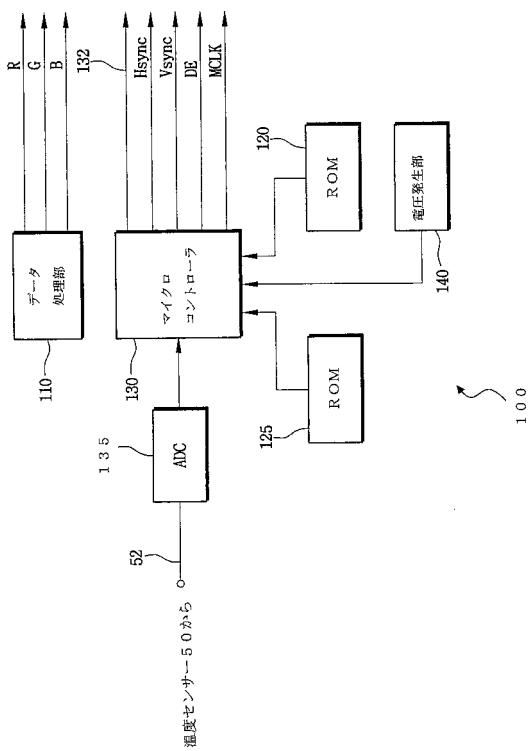

【図6】図6は、図5の画像信号ソースの一例を説明するための図である。

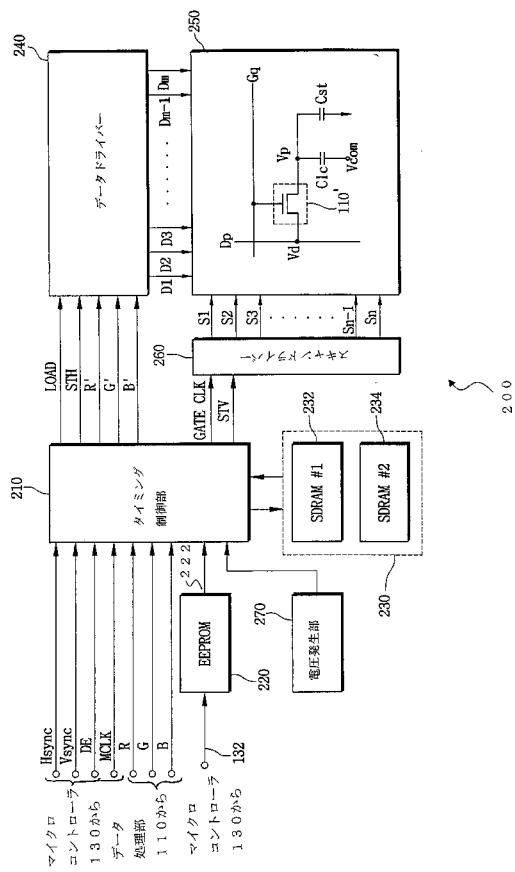

【図7】図7は、図5の液晶表示装置の一例を説明するための図である。

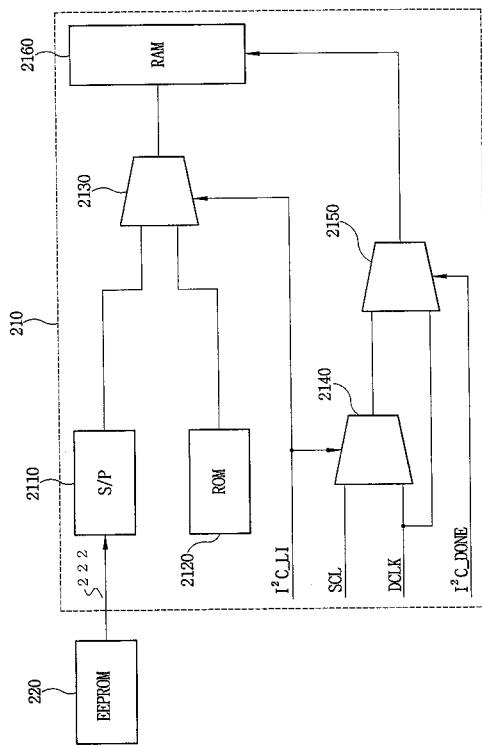

【図8】図8は、図7の液晶表示装置の一実施例を説明するための図である。

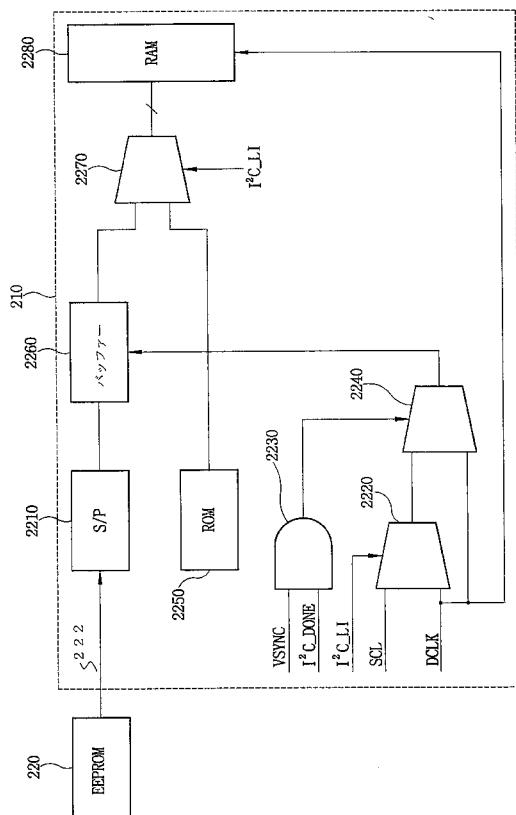

【図9】図9は、図7の液晶表示装置の他の実施例を説明するための図である。

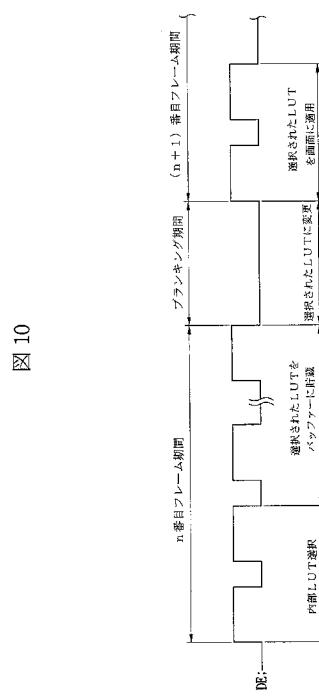

【図10】図10は、図9のタイミング制御部の外部EEPROMを用いてフレームプランギング期間でLUTを変更するタイミング図である。

40

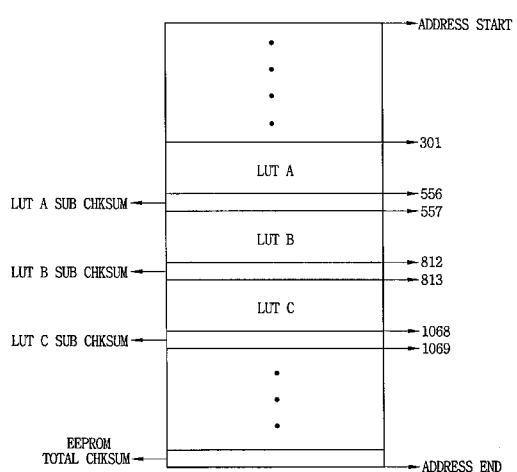

【図11】図11は、EEPROMに記憶される複数のLUT及び前記LUTのそれぞれに対応するチェックサムデータの一例を説明するための図である。

**【発明を実施するための形態】****【0026】**

以下、添付図面を参照して、本発明をより詳細に説明する。

**【0027】**

一般に、液晶表示装置は、スキャン信号を伝達する複数のゲートラインと、ゲートラインに交差して形成されてデータ電圧を伝達する複数のデータラインとを含む。また、液晶表示装置は、ゲートラインとデータラインとにより囲まれた領域に形成されゲートラインとデータラインとに連結される複数のスイッチング素子と、スイッチング素子により制御される複数の画素とをさらに含む。

50

## 【0028】

液晶表示装置において、各画素は液晶を誘電体として有するキャパシタ、即ち、液晶キャパシタとしてモデリングすることができるが、このような液晶表示装置での各画素の等価回路は図2のようである。

## 【0029】

図2に示したように、液晶表示装置の各画素は、データライン( $D_p$ )とゲートライン( $G_q$ )とにそれぞれソース電極とゲート電極とが連結される薄膜トランジスタ(以下、TFT)10により制御される。ここで、各画素は、TFT10のドレーン電極に接続された画素電極(図示せず)と、共通電圧( $V_{com}$ )が印加されている共通電極(図示せず)と、その間に存在する液晶とを含む。TFT10がON/OFFすることにより、画素電極(図示せず)と共通電極(図示せず)との間にかけられる電圧が変えられて、画素電極(図示せず)と共通電極(図示せず)との間にある液晶における光の透過率が変化させられる。このとき、画素電極(図示せず)と共通電極(図示せず)との間にある液晶は、液晶キャパシタ( $C_{1c}$ )として作用する。また、液晶キャパシタ( $C_{1c}$ )の容量を保持するために、TFT10のドレーン電極にストレージキャパシタ( $C_{st}$ )が液晶キャパシタ( $C_{1c}$ )と並列に連結されている。

10

## 【0030】

動作時、ゲートライン( $G_q$ )にゲートオン信号が印加されてTFT10がターンオンされると、データライン( $D_p$ )に供給されたデータ電圧( $V_d$ )がTFT10を通じて画素電極(図示せず)に印加される。そうすると、画素電極(図示せず)に印加される画素電圧( $V_p$ )と共通電極(図示せず)に印加される共通電圧( $V_{com}$ )との差に該当する電界が液晶(図2では、等価的に液晶キャパシタ( $C_{1c}$ )で示した)に印加され、電界の強さに対応する透過率で光が透過されるようにする。この際、画素電圧( $V_p$ )は、1フレーム期間維持されなければならないが、図2において、ストレージキャパシタ( $C_{st}$ )は、画素電極に印加された画素電圧( $V_p$ )を1フレーム期間維持するために、補助的に用いられる。

20

## 【0031】

一方、液晶は、誘電率異方性を有するので、液晶の方向によって誘電率が相違するという特性がある。即ち、電圧が印加されるにしたがって、液晶の方向子が変化すると、誘電率も変化して、これによって液晶キャパシタ( $C_{1c}$ )のキャパシタンス(以下では、これを液晶キャパシタンスという)も変化する。TFT10がターンオンされる期間に液晶キャパシタ( $C_{1c}$ )に電荷を供給した後、TFT10がターンオフ状態になるが、 $Q = CV$ であるので、液晶キャパシタンスが変化すると、液晶にかかる画素電圧( $V_p$ )も変化する。

30

## 【0032】

ノーマリーホワイトモード(Normally white mode)であるTN(Twisted Nematics)液晶表示装置を例として挙げると、画素に供給される画素電圧が0Vである場合には、液晶分子が基板に平行な方向に配列されているので、液晶キャパシタンスは、 $C(0V) = A/d$ になる。ここで、Aは、液晶分子が基板に平行な方向に配列された場合、即ち、液晶分子が光の方向と垂直方向に配列された場合の誘電率を示し、Aとdとは、それぞれ液晶表示装置基板の面積と基板間の距離を示す。フルブラック(full black)を実現するための電圧が5Vとすると、液晶に5Vが印加される場合、液晶分子が基板に垂直方向に配列されるので、液晶キャパシタンスは、 $C(5V) = -A/d$ になる。TNモードに用いられる液晶の場合には、

40

$> 0$ であるので、液晶に印加される画素電圧が高くなるほど、液晶キャパシタンスが大きくなる。

## 【0033】

n番目フレームでフルブラックを作るために、TFTが充電させなければならない電荷量は、 $C(5V) \times 5V$ である。しかし、以前フレームであるn-1番目フレームでフルホワイト( $V_{n-1} = 0V$ )であったと仮定すると、TFTがターンオンする瞬間は、液

50

晶が応答する前の状態であるので、液晶キャパシタンスは  $C(0V)$  の状態である。従って、フルブラックを作るために、 $n$  番目フレームで  $5V$  のデータ電圧 ( $V_d$ ) を印加しても、実際に画素に充電される電荷量は  $C(0V) \times 5V$  になり、 $C(0V) < C(5V)$  であるので、液晶に実際に供給される画素電圧 ( $V_p$ ) は、 $5V$  未満の画素電圧が（例えば、 $3.5V$ ）が印加されて、フルブラックが実現されない。

#### 【0034】

また、次フレームである  $n+1$  番目フレームでフルブラックを実現するためにデータ電圧 ( $V_d$ ) を  $5V$  印加した場合に、液晶に充電される電荷量が  $C(3.5V) \times 5V$  になり、結果的に液晶に供給される電圧 ( $V_p$ ) は、 $3.5V \sim 5V$  になる。このような過程を繰り返すと、結局幾つかのフレーム期間の後でなければ画素電圧 ( $V_p$ ) が所望する電圧に到達しないことになる。10

#### 【0035】

これを階調の観点で説明すると、任意の画素に印加される信号（画素電圧）が低い階調から高い階調に（または、高い階調から低い階調に）変化する場合、現在フレームの階調は、以前フレームの階調の影響を受けるので、すぐ所望する階調に到達せず、幾つかのフレーム期間が経過した後でなければ所望する階調に到達しない。同様に、現在フレームの画素の透過率は、以前フレームの画素の透過率の影響を受けて、幾つかのフレーム期間が経過した後でなければ所望する透過率にならない。

#### 【0036】

一方、以前フレームである  $n-1$  番目フレームがフルブラックであり、即ち、画素電圧 ( $V_p$ ) が  $5V$  であり、現在フレームである  $n$  番目フレームでフルブラックを実現するために、 $5V$  のデータ電圧が印加されたとすると、液晶キャパシタンスは  $C(5V)$  であるので、画素には  $C(5V) \times 5V$  に該当する電荷量が充電され、これにより液晶の画素電圧 ( $V_p$ ) は  $5V$  になる。20

#### 【0037】

このように、液晶に実際に供給される画素電圧 ( $V_p$ ) は、現在フレームに供給されるデータ電圧のみならず、以前フレームの画素電圧 ( $V_p$ ) によっても決定されることが分かる。

#### 【0038】

図3は、一般的な駆動方式で印加される場合のデータ電圧及び画素電圧を示す図である30。

#### 【0039】

図3に示したように、一般的な駆動方式では、以前フレームの画素電圧 ( $V_p$ ) を考慮せず、目標画素電圧 ( $V_w$ ) に該当するデータ電圧 ( $V_d$ ) をフレームごとに印加している。従って、実際液晶に印加される電圧である実際画素電圧 ( $V_p$ ) は、前述したように以前フレームの画素電圧に対応する液晶キャパシタンスにより目標画素電圧 ( $V_w$ ) より低くまたは高くなる。従って、幾つかのフレーム期間が経過した後でなければ目標画素電圧 ( $V_w$ ) に到達しないことになる。

#### 【0040】

図4は、図3に示す一般的な駆動方法による液晶表示装置の透過率を示す図である。40

#### 【0041】

図4に示したように、一般的な駆動方式では、前述したように1フレーム期間に実際画素電圧 ( $V_p$ 、図3参照) が目標画素電圧 ( $V_w$ 、図3参照) に到達しないので、液晶の透過率が幾つかのフレーム期間を経過した後でなければ目標透過率に到達しないことになる。

#### 【0042】

しかし、本発明では、現在フレームの画像信号 ( $P_n$ ) が入力されて、以前フレームの画像信号 ( $P_{n-1}$ ) と次フレームの画像信号 ( $P_{n+1}$ ) とを比較して次のような補償画像信号 ( $P_n$ ) を生成した後、補償画像信号 ( $P_n$ ) を各画素に印加する。ここで、画像信号 ( $P_n$ ) は、液晶表示装置がアナログ駆動方式を採用する場合には、データ電

圧を意味するが、デジタル駆動方式を採用する場合には、データ電圧を制御するために二進化された階調信号（または、階調データ）を用いるので、実際に画素に印加される電圧の補償は、階調信号の補償を通じて達成される。

#### 【0043】

第一に、現在フレームの画像信号（データ電圧または階調信号）が以前フレームの画像信号と同じであるか、類似していると、補償を行わない。

#### 【0044】

第二に、現在フレームの階調信号が以前フレームの階調信号より高い場合には、現在フレームの階調信号より更に高い補償された階調信号を出力し、現在フレームの階調信号が以前フレームの階調信号より低い場合には、現在フレームの階調信号より更に低い補償された階調信号を出力する。この際、補償が行われる程度は、現在フレームの階調信号と以前フレームの階調信号と次フレームの階調信号との差に比例する。

10

#### 【0045】

以上では、液晶の応答速度を高速化する概念を簡略に説明し、以下では本発明と関連して温度変化に対応して液晶の応答速度を補償することにより、応答速度を高速化するための実施例を説明する。

20

#### 【0046】

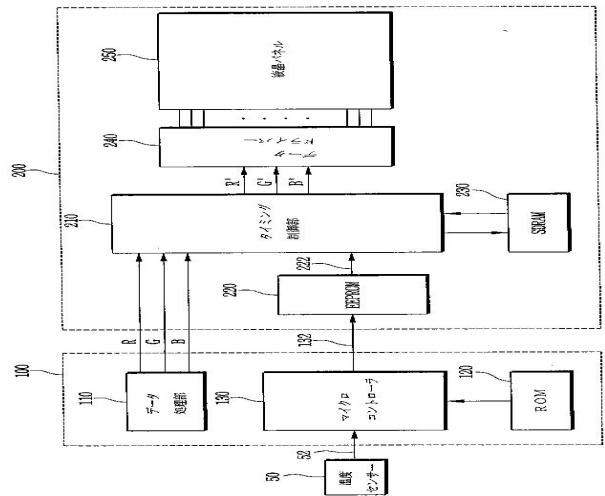

図5は、本発明による表示システムを説明するための図であって、特に、温度補償のための表示システムを示す。

#### 【0047】

図5を参照すると、温度補償のための表示システムは、原始階調データと補償データとを出力する画像信号ソース100と、原始階調データ及び補償データに基づいて画像を表示する液晶表示装置200とを含む。

30

#### 【0048】

画像信号ソース100は、データ処理部110、メモリ（ROM）120及びマイクロコントローラ130を含む。画像信号ソース100は、画像を表示するための原始階調データを液晶表示装置200に出力し、感知される温度信号に対応する補償データを液晶表示装置200に出力する。ここで、画像信号ソース100は、コンピュータに採用される本体やTVに採用される信号処理ブロック等として液晶表示装置200に連結される多様なホストである。

30

#### 【0049】

より詳細には、データ処理部110は、画像を表示するための原始階調データ（R, G, B）を液晶表示装置200に出力する。

#### 【0050】

メモリ（ROM）120は、液晶表示装置200に具備される液晶の応答速度を向上させるための温度区間別に補償データを記憶する。この際、補償データは、一定温度区間別に分離された互いに異なる複数のルックアップテーブル（以下、LUTとする）としてメモリ（ROM）120に記憶されることが好ましい。ここで、LUTは、階調の値と補償データとを対応づけたテーブルである。

40

#### 【0051】

マイクロコントローラ130は、外部の温度センサー50により感知される温度信号に対応して、メモリ（ROM）120に記憶されている複数のLUTのうちいずれか一つから、該当温度に対応する補償データ132を選択して読み出して液晶表示装置200に出力する。

#### 【0052】

一方、液晶表示装置200は、タイミング制御部210、第1メモリ（EEPROM）220、第3メモリ（SDRAM）230、データドライバー240及び液晶パネル250を含み、画像信号ソース100から原始階調データ（R, G, B）が提供されることにより、第1メモリ（EEPROM）220を経由して入力される補償データ222に基づいて液晶の応答速度を高速化するための補償階調データ（R', G', B'）を生成して

50

画像を表示する。ここで、補償データ222は、液晶表示装置200の周辺温度に適応するデータであることが好ましく、周辺温度が変動することによって画像信号ソースにより更新されることが好ましい。

#### 【0053】

具体的には、タイミング制御部210は、データ処理部110から原始階調データ(R,G,B)が提供されて、原始階調データ(R,G,B)を液晶パネル250に適合するように変換してデータドライバー240に提供する。すなわち、タイミング制御部210は、液晶の応答速度を高速化するために、以前フレームに対応する原始階調データと現在フレームに対応する原始階調データとに基づいて、補償階調データ(R',G',B')を生成してデータドライバー240に提供する。

10

#### 【0054】

第1メモリ(EEPROM)220は、マイクロコントローラ130から補償データ132の提供を受けて記憶し、タイミング制御部210の要請に応答して補償データ222をタイミング制御部210に提供する。この際、補償データは、一定温度区間別に分離された互いに異なる複数のルックアップテーブル(以下、LUTとする)として第1メモリ(EEPROM)220に記憶されることが好ましい。

20

#### 【0055】

仮に、原始階調データが8ビット(RGBデータは、24ビット)であると、全体階調である8ビットそれぞれに対応する補償データである可能性もあり、8ビットよりは小さい4または6ビット等それぞれに対応する補償データである可能性もある。4ビットまたは6ビットの提供を受けると、マイクロコントローラ130では、液晶の応答速度を高速化するための補償として、4ビットまたは6ビットに対応したLUTを用いて補償し、残りのビットに対応して補間法(interpolation)を用いて8ビットに補間して補償することが好ましい。

30

#### 【0056】

第3メモリ(SDRAM)230は、タイミング制御部210を経由して原始階調データが提供されて、原始階調データを記憶する。第3メモリ(SDRAM)230は、タイミング制御部210の要請に応答して該当原始階調データをタイミング制御部210に出力する。

#### 【0057】

データドライバー240は、タイミング制御部210から補償階調データ(R',G',B')が提供されて、これをアナログ電圧形態に変換して液晶パネル250に形成されたデータラインに提供する。

#### 【0058】

動作時、前記した表示システムを零下(0以下)で動作させた時、初期には低温区間に適合したLUTを用いて液晶の応答速度を高速化する動作を行い、時間が経過して内部発熱によって漸次温度が上昇することにより、上昇された温度区間に適合したLUTを用いて液晶の応答速度を高速化する動作を行う。

40

#### 【0059】

仮に、表示システムが自動方式に設定されている場合、温度センサー50により感知される温度区間が変更されたとマイクロコントローラ130が判断したときに、マイクロコントローラ130がLUT変更を待機し、チャンネル変更等のイベント発生時点にLUTに対応する補償データ132をメモリ(ROM)120から読み出して第1メモリ(EEPROM)220に提供する。これにより、温度に適応して液晶の応答速度を高速化する。この際、補償データ132、222を伝送する途中、液晶表示装置200による記憶の誤動作を防止するためには、液晶表示装置200の電源も共に制御することが好ましい。

#### 【0060】

一方、表示システムが受動方式に設定されている場合、マイクロコントローラ130と第1メモリ(EEPROM)220との間に連結されたI2Cバスを制御することにより、第1メモリ(EEPROM)220のLUTを変更することが可能である。この際にも

50

、 I<sub>2</sub>C バスを通じて LUT に記憶されたデータを伝送する途中、液晶表示装置 200 による記憶の誤動作を防止するためには、液晶表示装置 200 の電源も共に制御することが好ましい。

#### 【 0 0 6 1 】

LUT が第 1 メモリ (EEPROM) 220 に記憶された後に、マイクロコントローラ 130 でタイミング制御部 210 を直接制御して、第 1 メモリ (EEPROM) 220 でタイミング制御部 210 の内部 ROM に LUT をダウンロードすることが可能である。

#### 【 0 0 6 2 】

この際、ユーザは、LUT が変更される時間が過度に長いと判断される場合、画面が消える現象を不良であると認識する可能性がある。この際、画像信号ソース 100 のメモリ (ROM) 120 に既に記憶された特定アラームメッセージを見せることにより、ユーザの不満を低減することが可能である。

10

#### 【 0 0 6 3 】

図 6 は、図 5 の画像信号ソース 100 の一例を説明するための図であって、特に、温度補償のための画像信号ソース 100 の一例を説明するための図である。

#### 【 0 0 6 4 】

図 6 を参照すると、画像信号ソース 100 は、データ処理部 110 、メモリ (ROM) 120 、補助メモリ (ROM) 125 、マイクロコントローラ 130 、アナログ - デジタル変換部 (ADC) 135 及び電圧発生部 140 を含む。

20

#### 【 0 0 6 5 】

データ処理部 110 は、画像を表示するための原始階調データ (R, G, B) を液晶表示装置 200 に出力する。

#### 【 0 0 6 6 】

メモリ (ROM) 120 は、液晶表示装置 200 に備えられる液晶の応答速度を向上させるための補償データ、好ましくは温度区間別に補償データを記憶する。この際、補償データは、一定温度区間別に区別された互いに異なる複数の LUT としてメモリ (ROM) 120 に記憶されることが好ましい。例えば、-10 ~ 0 の温度区間に対応して補償データを記憶する第 1 LUT と、0 ~ 10 の温度区間に対応して補償データを記憶する第 2 LUT と、10 ~ 20 の温度区間に対応して補償データを記憶する第 3 LUT と、20 ~ 30 の温度区間に対応して補償データを記憶する第 4 LUT 等が、メモリ (ROM) 120 に記憶される。

30

#### 【 0 0 6 7 】

補助メモリ (ROM) 125 は、本体またはリモコンで項目別特性値を変更するに必要なデータである OSD (On Screen Display) データを記憶する。一般に、TV のような画像信号ソースには、表示装置の多様な機能をユーザが直接制御することができるようになる OSD 機能が存在するが、この際に用いられるデータが OSD データである。特に、本発明に関して、液晶表示装置の応答速度をユーザが直接制御することができる OSD 項目が記憶されていることが好ましい。例えば、OSD 項目に < 温度に反応するモード > と < 基本値維持モード > 等に分割して設定することにより、動画像画質に敏感なユーザの不満を解消することができる。

40

#### 【 0 0 6 8 】

マイクロコントローラ 130 は、データ処理部 110 が原始階調データ (R, G, B) を出力することによって、原始階調データを表示するための各種同期信号 (H sync, V sync) と、データイネイブル信号 (DE) と、メインクロック (MCLK) を液晶表示装置 200 に出力する。また、マイクロコントローラ 130 は、外部の温度信号をデジタル形態に変換するアナログ - デジタル変換部 (ADC) 135 を経由して温度データが入力されて、複数の LUT のうち、該当温度に対応する補償データ 132 を読み出して液晶表示装置 200 に出力する。

#### 【 0 0 6 9 】

即ち、温度信号が、温度センサー 50 からアナログ - デジタル変換部 (ADC) 135

50

に入力されて、アナログ - デジタル変換部（A D C）135でアナログ信号からデジタル信号に変換され、アナログ - デジタル変換部（A D C）135からマイクロコントローラ130へ出力される。温度信号が既に設定された温度区間を外れるか否かをマイクロコントローラ130がチェックして、温度区間を外れるとチェックされる場合には、該当温度に対応するL U Tがメモリ（R O M）120から読み出され、読み出されたL U Tから補償データ132が読み出されて液晶表示装置200に提供される。この際、補償データ132の伝送経路としては、集積回路間の通信リンクを提供する2つの線の両方向直列バスであるI 2 C（I n t e r - I C）バス方式を採用することが好ましい。

#### 【0070】

電圧発生部140は、マイクロコントローラ130の動作のための電源を供給する。特に、マイクロコントローラ130が補償データ132を液晶表示装置200に提供する時、誤動作を防止するためにマイクロコントローラ130に独立的に電源を供給することが好ましい。

10

#### 【0071】

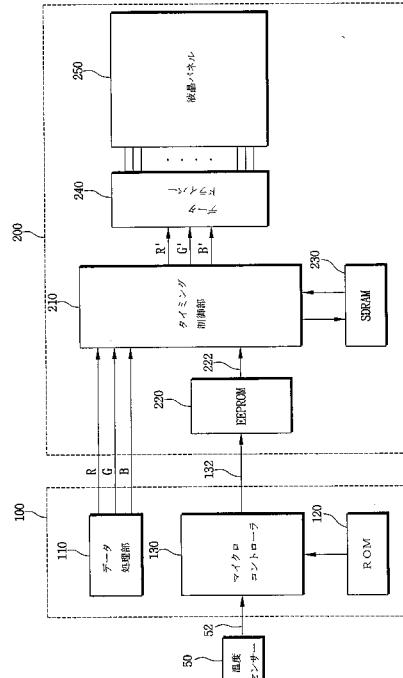

図7は、図5の液晶表示装置200の一例を説明するための図であって、特に、温度補償のための液晶表示装置200の一例を説明するための図である。

#### 【0072】

図7に示したように、液晶表示装置200は、タイミング制御部210、第1メモリ（E E P R O M）220、第3メモリ（S D R A M）230、データドライバー240、液晶パネル250、スキャンドライバー260及び電圧発生部270を含む。

20

#### 【0073】

タイミング制御部210は、画像信号ソース100（図5参照）のデータ処理部110（図5参照）から原始階調データ（R，G，B）を受け取る。タイミング制御部210は、画像信号ソース100（図5参照）のマイクロコントローラ130（図5参照）から、各種同期信号（H s y n c、V s y n c）とデータタイネイブル信号（D E）とメインクロック（M C L K）とを受け取る。タイミング制御部210は、温度に適応して液晶の応答速度を高速化するための補償階調データ（R'，G'，B'）と補償階調データ（R'，G'，B'）を出力するためのデータ駆動信号（L O A D、S T H）とをデータドライバー240に出力し、補償階調データ（R'，G'，B'）を出力するためのスキャン駆動信号（G A T E C L K、S T V）をスキャンドライバー260に出力する。

30

#### 【0074】

具体的には、タイミング制御部210が、第1メモリ（E E P R O M）220を経由してマイクロコントローラ130から補償データ222を受け取る。タイミング制御部210が、補償データ222をL U Tとして記憶する。もちろん、前記したL U T形態の補償データ222を記憶するために、タイミング制御部210は、別のメモリ（図示せず）を更に具備してもよい。

#### 【0075】

次に、タイミング制御部210は、画像信号ソース100に具備されるデータ処理部110から原始階調データ（R，G，B）を受け取る。タイミング制御部210は、L U T形態に記憶された補償データ222に基づいて、液晶の応答速度を高速化するために、現在フレームの階調データと以前フレームの階調データとを考慮して補償階調データ（R'，G'，B'）を生成する。タイミング制御部210は、補償階調データ（R'，G'，B'）をデータ信号に変換してデータドライバー240に出力する。

40

#### 【0076】

第1メモリ（E E P R O M）220は、液晶の応答速度を高速化する補償のための補償データ132を一時的に記憶し、タイミング制御部210の要請に応答して記憶された補償データ222を提供する。特に、補償データ222は、温度に適応するようデータ補償程度を決定して記憶されることが好ましい。仮に温度の変動がある場合、第1メモリ（E E P R O M）220は、マイクロコントローラ130から変動された温度に対応される補償データ132を受け取って記憶し、タイミング制御部210の要請に応答して記憶さ

50

れた補償データ222をタイミング制御部210に出力する。

【0077】

第3メモリ(SDRAM、Synchronous DRAM)230は、原始階調データを記憶する。具体的に、第3メモリ(SDRAM)230を、第1メモリバンク(SDRAM #1)232と第2メモリバンク(SDRAM #2)234とに論理的に分割する。第1メモリバンク(SDRAM #1)232には、現在フレームの1/2に該当する原始階調データが記録される間、第2メモリバンク(SDRAM #2)234から以前フレームの1/2に該当される原始階調データが読み取られる。もちろん、その逆も可能である。このように、第3メモリ(SDRAM)230を第1メモリバンク(SDRAM #1)232と第2メモリバンク(SDRAM #2)234とに論理的に分割することにより、データの記録動作と読み取り動作を連続的に行うことができる。10

【0078】

データドライバー240は、タイミング制御部210から補償階調データ(R', G', B')が受信されるにつれて、該当階調電圧(データ電圧またはデータ信号)に変更し、変更されたデータ信号(D1、D2、...、Dm)を液晶パネル250に供給する。

【0079】

液晶パネル250には、ゲートオン信号を伝達するための複数のゲートライン(走査ラインまたはスキャンライン)が形成されており、変更されたデータ信号(D1、D2、...、Dm)を伝達するためのデータライン(またはソースライン)が形成されている。ゲートラインとデータラインとにより囲まれた領域は、それぞれ画素を形成する。各画素、データライン(Dp)とゲートライン(Gq)とにそれぞれソース電極とゲート電極とが連結される薄膜トランジスタ110'により制御される。ここで、各画素は、薄膜トランジスタ110'のドレーン電極に接続された画素電極(図示せず)と、共通電圧(Vcom)が印加されている共通電極(図示せず)と、その間に存在する液晶とを含む。薄膜トランジスタ110'がON/OFFすることにより、画素電極(図示せず)と共通電極(図示せず)との間にかけられる電圧が変えられて、画素電極(図示せず)と共通電極(図示せず)との間にある液晶における光の透過率が変化させられる。このとき、画素電極(図示せず)と共通電極(図示せず)との間にある液晶は、液晶キャパシタ(C1c)として作用する。また、液晶キャパシタ(C1c)の容量を保持するために、薄膜トランジスタ110'のドレーン電極にストレージキャパシタ(Cst)が液晶キャパシタ(C1c)と並列に連結されている。20

【0080】

スキャンドライバー260は、スキャン駆動信号(GATE CLK、STV)に基づいて、ゲートラインを活性化させて薄膜トランジスタ110'をターンオンさせるためのゲートオン信号(S1、S2、S3、...、Sn)を順次印加する。

【0081】

第2電圧発生部270は、液晶表示装置200の電源を制御する。通常に温度に適応する補償データ132を記憶するLUTを第1メモリ(EEPROM)220に記憶する間、誤動作を防止しなければならないので、第2電圧発生部270を用いて液晶表示装置200の電源を制御することが好ましい。30

【0082】

以上では、デジタルインターフェースを具備して、外部からデジタル値である階調データの提供を受ける液晶表示装置を主として説明したが、当業者なら外部から提供されるアナログ値をデジタル値に変換するインターフェースを具備するアナログ液晶表示装置にも同様に適用することができるのは自明である。

【0083】

以上では、液晶表示装置が画像信号ソースから原始階調データと共に原始階調データを用いて表示する時、液晶の応答速度を温度に適応して高速化するために、補償データの提供を受けることを説明した。しかし、当業者なら、液晶表示装置が画像信号ソースから原始階調データのみを提供受け、液晶表示装置が自体の内部温度を感知して原始階調データ40

50

50

50

50

50

を温度によって補償することもできる。

【0084】

この際、液晶表示装置は、温度区間別に補償データを記憶する複数のLUTを具備し、感知される温度によってLUTを選択し、選択されたLUTを用いた補償を通じて温度に適応する液晶の応答速度を維持することもできるのは自明である。

【0085】

図8は、図7の液晶表示装置200の他の一例を説明するための図である。説明の便宜上、図7で説明したタイミング制御部210と第1メモリ(EEPROM)220のみを図示する。

【0086】

図8に示したように、本発明の他の実施例によるタイミング制御部210は、シリアル-パラレル変換部2110、第2メモリ(ROM)2120、第1スイッチング部2130、第2スイッチング部2140、第3スイッチング部2150及びRAM2160を含む。第1メモリ(EEPROM)220には、複数のLUTが記憶されている。ここで、LUTは、階調の値と第1補償データとを対応づけたテーブルである。第1メモリ(EEPROM)220は、TVセット(図5に示す画像信号ソース100)から提供されるLUT選択信号に基づいて、LUT選択信号に対応するLUTを選択する。RAM2160は、選択されたLUTを受け取り記憶する。タイミング制御部210は、RAM2160に記憶されたLUTを用いて液晶の応答速度を高速化する補正動作を行う。第1スイッチング部2130、第2スイッチング部2140及び第3スイッチング部2150は、マルチプレクサで実現する。

【0087】

シリアル-パラレル変換部2110は、第1メモリ(EEPROM)220から提供されるシリアルタイプの第1補償データをパラレル変換して、第1スイッチング部2130に出力する。

【0088】

第2メモリ(ROM)2120は、液晶表示装置に具備される液晶の応答速度を向上させるための第2補償データを記憶する。第2メモリ(ROM)2120に記憶される第2補償データは、液晶表示装置200を製造する製造者側で液晶表示装置200に最適に設定したデータである。例えば、第2補償データは、周辺温度が平均的な温度である場合の補償データとしてもよい。

【0089】

第1スイッチング部2130は、伝送クロック(I2C\_LI)に応答して、シリアル-パラレル変換部2110から出力される第1補償データ222及び第2メモリ(ROM)2120から出力される第2補償データのいずれか一方がRAM2160に記憶されるように出力する。

ここで、伝送クロック(I2C\_LI)は、第1メモリ(EEPROM)220からシリアル-パラレル変換部2110に第1補償データを伝送するためのクロック信号である。例えば、伝送クロック(I2C\_LI)がアクティブ状態である場合、シリアル-パラレル変換部2110から出力される第1補償データをRAM2160に出力し、伝送クロック(I2C\_LI)が非アクティブ状態である場合、第2メモリ(ROM)2120から出力される第2補償データをRAM2160に出力する。これにより、第1補償データが伝送されない場合でも、第2補償データにより液晶の応答速度を向上させるための補償を行うことができる。

【0090】

第2スイッチング部2140は、伝送クロック(I2C\_LI)に応答して、シリアルクロックSCL及びドットクロックDCLKのいずれか一方を第3スイッチング部2150に出力する。ここで、シリアルクロックSCLは、シリアル-パラレル変換部2110を制御するためのクロック信号である。ドットクロックDCLKは、画素を制御するためのクロック信号である。例えば、伝送クロック(I2C\_LI)がアクティブ状態である

10

20

30

40

50

場合、シリアルクロック SCL を第 3 スイッチング部 2150 に出力し、伝送クロック (I2C\_LI) が非アクティブ状態である場合、ドットクロック DCLK を第 3 スイッチング部 2150 に出力する。これにより、第 1 補償データのシリアル - パラレル変換部 2110 への传送が開始されるまでは、ドットクロック DCLK に同期して第 1 補償データ又は第 2 補償データが RAM2160 に記憶されるようにし、第 1 補償データのシリアル - パラレル変換部 2110 への传送が開始された後は、シリアルクロック SCL に同期して第 1 補償データ又は第 2 補償データが RAM2160 に記憶されるようにすることが可能である。

#### 【0091】

第 3 スイッチング部 2150 は、传送完了クロック (I2C\_DONE) に応答して、

第 1 スイッチング部 2130 から出力されるデータが RAM2160 に記憶されることを

制御するために、第 2 スイッチング部 2140 から出力されるクロック及びドットクロック DCLK のいずれか一方を RAM2160 に出力する。ここで、传送完了クロック (I2C\_DONE) は、シリアル - パラレル変換部 2110 への第 1 補償データの传送を完了させるためのクロック信号である。例えば、传送完了クロック (I2C\_DONE) が

アクティブ状態である場合、ドットクロック DCLK を RAM2160 に出力し、传送完了クロック (I2C\_DONE) が非アクティブ状態である場合、第 2 スイッチング部 2140 から出力されるクロックを RAM2160 に出力する。これにより、第 1 補償データのシリアル - パラレル変換部 2110 への传送が行われていないときは、ドットクロック DCLK に同期して第 1 補償データ又は第 2 補償データが RAM2160 に記憶される

ようにし、第 1 補償データのシリアル - パラレル変換部 2110 への传送が行われている

間は、シリアルクロック SCL に同期して第 1 補償データ又は第 2 補償データが RAM2160 に記憶される

ようにすることができる。すなわち、第 1 補償データのシリアル - パラレル変換部 2110 への传送が行われているか否かに応じて、第 1 補償データ又は第 2 補償データが RAM2160 に記憶されるタイミングを変えることができる。

#### 【0092】

以上では、液晶の応答速度を高速化するために、周辺温度に基づいて互いに異なる温度区間に對応する複数の LUT のうち、いずれか一つを読み出して用いることを説明した。

#### 【0093】

しかし、液晶の応答速度に影響する要素には、前記した周辺温度以外に、周波数すなわち垂直同期信号が更に存在する。即ち、液晶の応答速度を補償するための補償量は、周辺温度が高温であるほど、小さくても所望する目標電圧値に到達することができる（図 1，図 3 参照）。また、液晶の応答速度を補償するための補償量は、垂直同期信号の周波数が上昇するほど、より短くなった 1 フレーム期間内に目標電圧値に到達する必要が生ずるため、大きくならなければならない（図 3 参照）。

#### 【0094】

一方、第 1 メモリ (EEPROM) 220 で選択された LUT に對応するデータが传送

クロック (I2C\_LI) により電源オフなしに RAM2160 に記憶される時、ドット

クロック DCLK より非常に遅い（クロック周期が長い）シリアルクロック SCL を用い

るので、フレームとフレームとの間の時間すなわちフレームブランкиング期間で、LUT

を RAM2160 に記憶する動作を行わなければならない。

#### 【0095】

これにより、動画像のように実時間に入力される階調データに対するオーバーシュートする従来の LUT 値を用いると、データ衝突及びローディング時間遅延によりユーザに観察される画面上には、ノイズや色反転、階調変化等の歪曲現象を誘発するおそれがある。

#### 【0096】

即ち、一つのフレーム内に変動前の温度区間に對応する LUT と変動後の温度区間に對応する LUT とが混在しているので、ユーザ側では画面に歪曲が発生したと誤解するおそれがある。

#### 【0097】

10

20

30

40

50

以下では、液晶の応答速度を高速化するために、周辺温度のみならず垂直同期信号の変化をも考慮して選択されたLUTを適用することにより、別に電源をオフさせなくても、ユーザ側になめらかな画像を表示することが可能な例について、図9を参照して説明する。

#### 【0098】

図9は、図7に図示された液晶表示装置の他の実施例を説明するための図である。説明の便宜上、図7で説明したタイミング制御部210と第1メモリ(EEPROM)220のみを図示する。

#### 【0099】

図9に示したように、本発明の他の実施例によるタイミング制御部210は、シリアル-パラレル変換部2210、第1スイッチング部2220、アンドゲート2230、第2スイッチング部2240、第2メモリ(ROM)2250、バッファ-2260、第3スイッチング部2270及びRAM2280を含む。第1メモリ(EEPROM)220には、複数のLUTが記憶されている。第1メモリ(EEPROM)220は、TVセット(図5に示す画像信号ソース100)から提供されるLUT選択信号に基づいて、LUT選択信号に対応するLUTを選択する。RAM2280は、選択されたLUTを受け取り記憶する。タイミング制御部210は、RAM2280に記憶されたLUTを用いて液晶の応答速度を高速化するための補償動作を行う。第1スイッチング部2220、第2スイッチング部2240及び第3スイッチング部2270は、マルチプレクサで実現する。

#### 【0100】

シリアル-パラレル変換部2210は、第1メモリ(EEPROM)220から提供されるシリアルタイプの第1補償データ222をパラレル変換して、バッファ-2260に出力する。

#### 【0101】

第1スイッチング部2220は、伝送クロック(I2C\_LI)に応答して、シリアルクロックSCLまたはドットクロックDCLKのいずれか一方を第2スイッチング部2240に出力する。ここで、伝送クロック(I2C\_LI)は、第1メモリ(EEPROM)220からシリアル-パラレル変換部2210に第1補償データ222を伝送するためのクロック信号である。例えば、伝送クロック(I2C\_LI)がアクティブ状態である場合、シリアルクロックSCLを第2スイッチング部2240に出力し、伝送クロック(I2C\_LI)が非アクティブ状態である場合、ドットクロックDCLKを第2スイッチング部2240に出力する。これにより、第1補償データのシリアル-パラレル変換部2110への伝送が開始されるまでは、ドットクロックDCLKを第2スイッチング部2240に供給するようにし、第1補償データのシリアル-パラレル変換部2110への伝送が開始された後は、シリアルクロックSCLを第2スイッチング部2240に供給するようになることが可能である。

#### 【0102】

アンドゲート2230は、传送完了クロック(I2C\_DONE)と垂直同期信号VSYNCとをアンド演算して、アンド演算されたクロック(VSYNC & I2C\_DONE)を第2スイッチング部2240に出力する。

ここで、传送完了クロック(I2C\_DONE)は、シリアル-パラレル変換部2210への第1補償データ222の传送を完了させるためのクロック信号である。これにより、第1補償データ222のシリアル-パラレル変換部2110への传送が完了したことと垂直同期信号の周波数とを考慮したクロック信号を生成することができる。

#### 【0103】

第2スイッチング部2240は、アンド演算されたクロック(VSYNC & I2C\_DONE)に応答して、第1スイッチング部2220から出力されるクロックとドットクロックDCLKとのいずれか一方をバッファ-2260に出力する。例えば、アンド演算されたクロック(VSYNC & I2C\_DONE)がアクティブ状態である場合、第1スイッチング部2220から出力されるクロックをバッファ-2260に出力し、アンド演算

10

20

30

40

50

されたクロック ( V S Y N C & I 2 C\_D O N E ) が非アクティブ状態である場合、ドットクロック D C L K をバッファ - 2 2 6 0 に出力する。これにより、第 1 補償データのシリアル - パラレル変換部 2 1 1 0 への传送が行われておらず垂直同期信号がアクティブ状態であるときは、ドットクロック D C L K をバッファ - 2 2 6 0 に供給するようにし、第 1 補償データのシリアル - パラレル変換部 2 1 1 0 への传送が行われているか垂直同期信号が非アクティブ状態であるときは、シリアルクロック S C L をバッファ - 2 2 6 0 に供給するようにすることができる。

#### 【 0 1 0 4 】

第 2 メモリ ( R O M ) 2 2 5 0 は、液晶表示装置 2 0 0 に具備される液晶の応答速度を向上させるための第 2 補償データを記憶する。第 2 メモリ ( R O M ) 2 2 5 0 に記憶される第 2 補償データは、液晶表示装置 2 0 0 を製造する製造者側で液晶表示装置 2 0 0 に最適に設定したデータである。例えば、第 2 補償データは、周辺温度が平均的な温度である場合の補償データである。

10

#### 【 0 1 0 5 】

バッファ - 2 2 6 0 は、シリアル - パラレル変換部 2 2 1 0 でパラレル変換された第 1 補償データを一時的に記憶する。バッファ - 2 2 6 0 は、第 2 スイッチング部 2 2 4 0 から出力されるクロックに応答して、第 1 補償データを第 3 スイッチング部 2 2 7 0 に出力する。例えば、ドットクロック D C L K が入力された場合、一時的に記憶された第 1 補償データ 2 2 2 をスイッチング部 2 2 7 0 に出力し、シリアルクロック S C L が入力された場合、一時的に記憶された第 1 補償データ 2 2 2 の出力を遮断する。これにより、第 1 補償データのシリアル - パラレル変換部 2 1 1 0 への传送が行われておらず垂直同期信号がアクティブ状態であるときは、第 1 補償データ 2 2 2 をスイッチング部 2 2 7 0 に出力するようにし、第 1 補償データのシリアル - パラレル変換部 2 1 1 0 への传送が行われているか垂直同期信号が非アクティブ状態であるときは、第 1 補償データ 2 2 2 をスイッチング部 2 2 7 0 に出力するようになる。

20

#### 【 0 1 0 6 】

第 3 スイッチング部 2 2 7 0 は、传送クロック ( I 2 C\_L I ) に応答して、バッファ - 2 2 6 0 から出力される第 1 補償データ 2 2 2 と第 2 メモリ ( R O M ) 2 2 5 0 から出力される第 2 補償データとのいずれか一方を R A M 2 2 8 0 に出力する。例えば、传送クロック ( I 2 C\_L I ) がアクティブ状態である場合、バッファ - 2 2 6 0 から出力される第 1 補償データ 2 2 2 を R A M 2 2 8 0 に出力し、传送クロック ( I 2 C\_L I ) が非アクティブ状態である場合、第 2 メモリ ( R O M ) 2 2 5 0 から出力される第 2 補償データを R A M 2 2 8 0 に出力する。これにより、第 1 補償データ 2 2 2 のシリアル - パラレル変換部 2 1 1 0 への传送が開始されるまでは、第 2 メモリ ( R O M ) 2 2 5 0 から出力される第 2 補償データを R A M 2 2 8 0 に出力するようにし、第 1 補償データのシリアル - パラレル変換部 2 1 1 0 への传送が開始された後は、バッファ - 2 2 6 0 から出力される第 1 補償データ 2 2 2 を R A M 2 2 8 0 に出力するようになることが可能である。

30

#### 【 0 1 0 7 】

R A M 2 2 8 0 は、ドットクロック D C L K に応答して、シリアル - パラレル変換部 2 2 1 0 とバッファ - 2 2 6 0 と第 3 スイッチング部 2 2 7 0 とを経由する第 1 補償データ 2 2 2 並びに第 2 メモリ ( R O M ) 2 2 5 0 と第 3 スイッチング部 2 2 7 0 とを経由する第 2 補償データのいずれか一方を記憶する。これにより、第 1 補償データ 2 2 2 及び第 2 補償データのいずれか一方を、画素の動作と同期して R A M 2 2 8 0 に記憶させることができる。

40

#### 【 0 1 0 8 】

図 1 0 は、図 9 の第 1 メモリ ( E E P R O M ) 2 2 0 とタイミング制御部 2 1 0 とを用いてフレームプランギング期間で L U T を変更するタイミング図である。

#### 【 0 1 0 9 】

図 9 及び図 1 0 に示したように、第 1 メモリ ( E E P R O M ) 2 2 0 にアドレス別に複数の L U T が記憶されており、n 番目フレーム期間で画像を表示している時、タイミング

50

制御部 210 は、TV セット（図 5 に示す画像信号ソース 100）で変換された周辺温度に該当される LUT（第 1 補償データ）でありオーバーシュート電圧を発生させる（ブラック ホワイトに変化するとき、ホワイト ブラックに変化するとき）ための LUT（第 1 補償データ）を選択する信号を、I2C バス通信を通じて TV セット（図 5 に示す画像信号ソース 100）から受け取る。例えば、タイミング制御部 210 は、LUT（第 1 補償データ）を選択する信号に基づき、第 1 メモリ（EEPROM）220 を参照して、該当 LUT（第 1 補償データ）が記憶された場所のアドレスを取得する。タイミング制御部 210 は、該当 LUT（第 1 補償データ）が記憶された場所のアドレスと読み出し命令とを第 1 メモリ（EEPROM）220 に渡し、該当 LUT（第 1 補償データ）のデータの全部を受け取りバッファ－ 2260 に記憶させる。この処理における伝達所要時間は、特定の LUT に記憶された補償データが 256 個である場合、数十 ms 程度である。このため、電源オフなしに画面上でなめらかに補償データ（第 1 補償データ又は第 2 補償データ）の値を変更することができる。

10

## 【0110】

続いて、フレームが変換されるフレームプランキング期間でバッファ－ 2260 に記憶された LUT（第 1 補償データ）が RAM2280 に記憶された後、(n+1) 番目フレーム期間に対応するデータタイネイブル信号 DE が印加されて、RAM2280 に記憶された LUT（第 1 補償データ又は第 2 補償データ）を用いて表示動作が行われる。

20

## 【0111】

このように、垂直同期信号が印加される期間（フレームプランキング期間）に、バッファ－に記憶された LUT の第 1 補償データ又は ROM に記憶された LUT の第 2 補償データが RAM2280 に記憶されるため、周辺温度に対応する LUT が RAM2280 に記憶されるので、別に電源をオフしなくても、液晶の応答速度を高速化する補償値が変更されて、ユーザ側になめらかな画像を表示することが可能である。

30

## 【0112】

以上では、複数の LUT をタイミング制御部の外部にある EEPROM に記憶させて TV セットから提供される LUT 選択信号に基づいて該当 LUT を選択した後、プランキング期間の間に RAM に記憶することを説明したが、当業者なら複数の LUT をタイミング制御部の内部に記憶させて TV セットから提供される LUT 選択信号に基づいて該当 LUT を選択した後、RAM に記憶することもできる。

30

## 【0113】

具体的には、図 9 に示すタイミング制御部 210 が、内部に複数の LUT を記憶する第 2 メモリ（ROM）2250 を有している。ここで、LUT は、階調の値と第 2 補償データとを対応づけたテーブルである。タイミング制御部 210 が、TV セット（図 5 に示す画像信号ソース 100）と液晶表示装置 200（図 5 参照）との間の相互伝達方式（例えば、I<sup>2</sup>C 方式）で任意の LUT を選択する信号の提供を受けることにより、第 2 メモリ（ROM）2250 に記憶されている LUT をバッファ－ 2260 に記憶する。

40

## 【0114】

次に、フレームが変換されるフレームプランキング期間でバッファ－ 2260 に記憶された LUT を RAM2280 に記憶させた後、次フレームに対応するデータタイネイブル信号がタイミング制御部 210 に印加されることにより、RAM2280 に記憶された LUT を用いて表示動作を行う。

## 【0115】

このように、垂直同期信号が印加される期間（フレームプランキング期間）に、バッファ－に記憶された LUT の第 1 補償データ又は ROM に記憶された LUT の第 2 補償データが RAM2280 に記憶されるため、周辺温度に対応する LUT が RAM2280 に記憶されるので、別に電源をオフしなくても、液晶の応答速度を高速化する補償値が変更されて、ユーザ側になめらかな画像を表示することが可能である。

## 【0116】

回路構成によって異なるが、オーバーシュート用 LUT サイズを最少化するために原始

50

階調信号が 8 - 階調である場合、原始階調信号は、256 個の階調データを有することになる。入力クロックの周期に対して、256 個の階調データに対するブランкиング期間は、非常に短い時間であるが、充分にバッファー 2260 に記憶された第 1 補償データ（又は第 2 補償データ）を RAM 2280 に記憶することが可能である。これにより、一般ユーザは LUT 変更による画像変化を認識しないので、ユーザ側になめらかな画像を表示することが可能であるという長所がある。また、特定の LUT を選択する信号がタイミング制御部 210 に受け取られてからその LUT に応じて画像が表示されるまで、最大時間は 1 フレーム時間（16.7 ms）であるので、大きな問題はない。

#### 【0117】

一方、第 1 メモリ（EEPROM）220 に複数の LUT を記憶する際に、図 11 に示したように、それぞれの LUT ごとにアドレス領域を割り当てて記憶しなければならない。なぜならば、周辺温度及び垂直同期信号による LUT 変更を第 1 メモリ（EEPROM）220 からタイミング制御部 210 が読み込む際に、タイミング制御部 210 は第 1 メモリ（EEPROM）220 に記憶された複数の LUT それぞれに記憶された全体データを読み込むことなく、周辺温度変化に最適化させるために、該当 LUT のみを読み込むと良いためである。

#### 【0118】

この際、第 1 メモリ（EEPROM）220 全体のデータのうち、該当アドレスに位置する LUT を読み込む伝送過程でエラーが発生すると、正確な応答速度の補償が不可能になるで、LUT 種類別に別のサブチェックサムビットを割り当てる方式を取る。

#### 【0119】

例えば、一つの LUT サイズを 256 と仮定する時、アドレス 301 からアドレス 556 に対応する領域には第 1 LUT（LUT\_A）を記憶し、アドレス 556 からアドレス 557 に対応する領域には第 1 LUT のサブチェックサムの値（LUT\_A\_SUB\_C\_HKSUM）を記憶する。また、アドレス 557 からアドレス 812 に対応する領域には第 2 LUT（LUT\_B）を記憶し、アドレス 812 からアドレス 813 に対応する領域には第 2 LUT のサブチェックサムの値（LUT\_B\_SUB\_C\_HKSUM）を記憶する。このような方式を通じて、複数の LUT と、LUT の伝送上のエラーを防止するためのサブチェックサムの値とを記憶する。

#### 【0120】

このような方式によると、選択された LUT に対応する階調データの伝送時のエラーが発生したとチェックされる場合に、エラーがなくなるまで読み込む動作を繰り返すことになる。これにより、無エラーの LUT に対応する階調データを RAM に記憶することが可能になる。

#### 【0121】

もちろん、サブチェックサムの値は、LUT 別に互いに相違するように付与することにより、互いに異なる LUT データが同一 LUT データであると混同されることを防止することができる。例えば、第 1 LUT のサブチェックサム（LUT\_A\_SUB\_C\_HKSUM）を AAHEXA、第 2 LUT のサブチェックサム（LUT\_B\_SUB\_C\_HKSUM）を BBHEXA、第 3 LUT のサブチェックサム（LUT\_C\_SUB\_C\_HKSUM）を CCHEXA 等として付与する方式のように、明確に区分する必要がある。

#### 【0122】

また、第 1 メモリ（EEPROM）220 の最後のアドレスに対応する領域には、第 1 LUT のサブチェックサムの値、第 2 LUT のサブチェックサムの値、・・・の合計であるトータルチェックサム（EEPROM\_TotalCHKSUM）を記憶する。

#### 【0123】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離ることなく、本発明を修正または変更できる。

#### 【産業上の利用可能性】

10

20

30

40

50

## 【0124】

本発明にかかる表示システム、表示システムの駆動方法及び表示システムの駆動装置は、液晶表示装置の周辺又は内部の温度に適応して液晶の応答速度を高速化することができるという効果を有し、表示システム、表示システムの駆動方法及び表示システムの駆動装置等として有用である。

## 【符号の説明】

## 【0125】

|            |                   |    |

|------------|-------------------|----|

| 10         | TFT               |    |

| 50         | 温度センサー            |    |

| 100        | 画像信号ソース           | 10 |

| 110        | データ処理部            |    |

| 110'       | 薄膜トランジスタ          |    |

| 120        | メモリ(ROM)          |    |

| 125        | 補助メモリ(SDRAM)      |    |

| 230        | 第3メモリ(SDRAM)      |    |

| 130        | マイクロコントローラ        |    |

| 132        | 補償データ             |    |

| 135        | アナログ-デジタル変換部(ADC) |    |

| 140, 270   | 電圧発生部             |    |

| 200        | 液晶表示装置            | 20 |

| 210        | タイミング制御部          |    |

| 220        | 第1メモリ(EEPROM)     |    |

| 232, 234   | メモリバンク            |    |

| 240        | データドライバー          |    |

| 250        | 液晶パネル             |    |

| 260        | スキャンドライバー         |    |

| 2110, 2210 | シリアル-パラレル変換部      |    |

| 2120, 2250 | 第2メモリ(ROM)        |    |

| 2130, 2220 | 第1スイッチング部         |    |

| 2140, 2240 | 第2スイッチング部         | 30 |

| 2150, 2270 | 第3スイッチング部         |    |

| 2160, 2280 | RAM               |    |

| 2230       | アンドゲート            |    |

| 2260       | バッファー             |    |

【図 1】

【図 3】

【図 4】

【図 2】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

220

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 3 1 B |

| G 0 9 G | 3/20  | 6 3 1 K |

| G 0 9 G | 3/20  | 6 7 0 L |

| G 0 9 G | 3/20  | 6 3 1 V |

| G 0 9 G | 3/20  | 6 1 2 K |

| G 0 9 G | 3/20  | 6 2 3 J |

| G 0 9 G | 3/20  | 6 3 3 H |

| G 0 9 G | 3/20  | 6 1 2 T |

| G 0 9 G | 3/20  | 6 6 0 V |

| G 0 9 G | 3/20  | 6 7 0 F |

| G 0 9 G | 3/20  | 6 7 0 G |

| G 0 2 F | 1/133 | 5 7 0   |

| G 0 2 F | 1/133 | 5 8 0   |

| H 0 4 N | 5/66  | 1 0 2 B |

(72)発明者 田 萬 福

大韓民国京畿道龍仁市器興邑上葛里463番地金花マウル住公グリーンビル404棟1204号

|           |       |      |      |      |      |      |      |      |      |      |      |

|-----------|-------|------|------|------|------|------|------|------|------|------|------|

| F ターム(参考) | 2H193 | ZA04 | ZA05 | ZB16 | ZC25 | ZD01 | ZD23 | ZF02 | ZF13 | ZF15 | ZF16 |

|           | ZF17  | ZF20 | ZF21 | ZF31 | ZH18 | ZH34 | ZH35 | ZH53 | ZQ06 | ZQ14 |      |

|           | ZQ22  |      |      |      |      |      |      |      |      |      |      |

| 5C006     | AA01  | AA16 | AA22 | AC11 | AC21 | AF03 | AF04 | AF06 | AF11 | AF25 |      |

| AF27      | AF44  | AF45 | AF46 | AF47 | AF51 | AF53 | AF62 | AF65 | AF67 |      |      |

| AF72      | AF73  | AF81 | AF83 | BB16 | BC12 | BC13 | BC16 | BF02 | BF08 |      |      |

| BF09      | BF14  | BF16 | BF24 | BF26 | BF38 | BF42 | BF44 | EB01 | EC02 |      |      |

| FA12      | FA14  | FA19 | FA29 | FA31 |      |      |      |      |      |      |      |

| 5C058     | AA06  | BA07 | BB14 |      |      |      |      |      |      |      |      |

| 5C080     | AA10  | BB05 | CC03 | CC09 | DD02 | DD06 | DD08 | DD09 | DD12 | DD13 |      |

| DD16      | DD20  | EE01 | EE19 | EE25 | EE26 | EE29 | FF03 | FF11 | GG05 |      |      |

| GG08      | GG11  | GG12 | GG13 | GG15 | GG17 | JJ02 | JJ03 | JJ04 | JJ05 |      |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示系统，显示系统的驱动方法和驱动系统                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2012014191A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2012-01-19 |

| 申请号            | JP2011204480                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2011-09-20 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 趙賢相<br>田萬福                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 趙 賢 相<br>田 萬 福                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 H04N5/66 G09G5/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/2011 G09G3/20 G09G3/2096 G09G3/3611 G09G3/3648 G09G2310/08 G09G2320/0252<br>G09G2320/0261 G09G2320/041 G09G2320/08 G09G2340/16 G09G2360/18 G09G2370/045                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/36 G09G3/20.621.F G09G3/20.641.P G09G3/20.650.M G09G3/20.612.U G09G3/20.631.B<br>G09G3/20.631.K G09G3/20.670.L G09G3/20.631.V G09G3/20.612.K G09G3/20.623.J G09G3/20.633.<br>H G09G3/20.612.T G09G3/20.660.V G09G3/20.670.F G09G3/20.670.G G02F1/133.570 G02F1/133.<br>580 H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZA05 2H193/ZB16 2H193/ZC25 2H193/ZD01 2H193/ZD23 2H193/ZF02 2H193<br>/ZF13 2H193/ZF15 2H193/ZF16 2H193/ZF17 2H193/ZF20 2H193/ZF21 2H193/ZF31 2H193/ZH18<br>2H193/ZH34 2H193/ZH35 2H193/ZH53 2H193/ZQ06 2H193/ZQ14 2H193/ZQ22 5C006/AA01 5C006<br>/AA16 5C006/AA22 5C006/AC11 5C006/AC21 5C006/AF03 5C006/AF04 5C006/AF06 5C006/AF11<br>5C006/AF25 5C006/AF27 5C006/AF44 5C006/AF45 5C006/AF46 5C006/AF47 5C006/AF51 5C006<br>/AF53 5C006/AF62 5C006/AF65 5C006/AF67 5C006/AF72 5C006/AF73 5C006/AF81 5C006/AF83<br>5C006/BB16 5C006/BC12 5C006/BC13 5C006/BC16 5C006/BF02 5C006/BF08 5C006/BF09 5C006<br>/BF14 5C006/BF16 5C006/BF24 5C006/BF26 5C006/BF38 5C006/BF42 5C006/BF44 5C006/EB01<br>5C006/EC02 5C006/FA12 5C006/FA14 5C006/FA19 5C006/FA29 5C006/FA31 5C058/AA06 5C058<br>/BA07 5C058/BB14 5C080/AA10 5C080/BB05 5C080/CC03 5C080/CC09 5C080/DD02 5C080/DD06<br>5C080/DD08 5C080/DD09 5C080/DD12 5C080/DD13 5C080/DD16 5C080/DD20 5C080/EE01 5C080<br>/EE19 5C080/EE25 5C080/EE26 5C080/EE29 5C080/FF03 5C080/FF11 5C080/GG05 5C080/GG08<br>5C080/GG11 5C080/GG12 5C080/GG13 5C080/GG15 5C080/GG17 5C080/JJ02 5C080/JJ03 5C080<br>/JJ04 5C080/JJ05 |         |            |

| 代理人(译)         | 山下大沽嗣                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 优先权            | 1020030037232 2003-06-10 KR<br>1020030071030 2003-10-13 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP5474017B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

**摘要(译)**

要解决的问题：提供一种显示系统，其中液晶的响应速度可以自适应地加速到液晶显示装置周围或内部的温度，驱动显示系统的方法和用于驱动显示器的装置系统解决方案：一种显示系统，包括：第一存储器，用于存储多个温度区域中的每一个的第一补偿数据，以加速液晶显示装置中液晶的响应速度；第二存储器，用于存储在考虑液晶显示装置的特性的同时设定的第二补偿数据；以及定时控制部分，用于在考虑前一帧的灰度数据或当前帧的灰度数据的同时，基于第一补偿数据或基于第二补偿数据来补偿灰度数据。定时控制部分包括第一切换部分，用于响应于来自第一存储器的时钟信号或存储在第二存储器中的第二补偿数据输出要并行转换的第一补偿数据。