(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-180259

(P2011-180259A)

(43) 公開日 平成23年9月15日(2011.9.15)

(51) Int.Cl.

**G02F 1/1368 (2006.01)**

**G02F 1/1335 (2006.01)**

**G02F 1/1339 (2006.01)**

F 1

GO2F 1/1368

GO2F 1/1335 505

GO2F 1/1339 500

テーマコード(参考)

2H092

2H189

2H191

審査請求 未請求 請求項の数 5 O L (全 15 頁)

(21) 出願番号

特願2010-42540 (P2010-42540)

(22) 出願日

平成22年2月26日 (2010.2.26)

(71) 出願人 302020207

東芝モバイルディスプレイ株式会社

埼玉県深谷市幡羅町一丁目9番地2

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100095441

弁理士 白根 俊郎

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【要約】

【課題】生産性の低下を抑制することが可能な液晶表示装置及びその製造方法を提供することを目的とする。

【解決手段】第1スイッチング素子及び第2スイッチング素子と、第1スイッチング素子上に配置された第1カラーフィルタ層と、第2スイッチング素子上に配置されるとともに第1カラーフィルタ層の一部に重なった重畳部を形成する第2カラーフィルタ層と、第1カラーフィルタ層及び第2カラーフィルタ層を覆うとともに重畳部の直上に凹部が形成された絶縁膜と、第1カラーフィルタ層の上方に位置する絶縁膜上に配置され第1スイッチング素子に電気的に接続された第1画素電極と、第2カラーフィルタ層の上方に位置する絶縁膜上に配置され第2スイッチング素子に電気的に接続された第2画素電極と、を備えた第1基板と、第1基板に対向して配置された第2基板と、第1基板と第2基板とを貼り合わせる閉ループ状のシール材とを備えた液晶表示装置。

【選択図】 図3

図3

**【特許請求の範囲】****【請求項 1】**

第1スイッチング素子及び第2スイッチング素子と、前記第1スイッチング素子上に配置された第1カラーフィルタ層と、前記第2スイッチング素子上に配置されるとともに前記第1カラーフィルタ層の一部に重なった重畠部を形成する第2カラーフィルタ層と、前記第1カラーフィルタ層及び前記第2カラーフィルタ層を覆うとともに前記重畠部の直上に凹部が形成された絶縁膜と、前記第1カラーフィルタ層の上方に位置する前記絶縁膜上に配置され前記第1スイッチング素子に電気的に接続された第1画素電極と、前記第2カラーフィルタ層の上方に位置する前記絶縁膜上に配置され前記第2スイッチング素子に電気的に接続された第2画素電極と、を備えた第1基板と、

10

前記第1基板に対向して配置された第2基板と、

前記第1基板と前記第2基板とを貼り合わせる閉ループ状のシール材と、

前記第1基板と前記第2基板との間であって前記シール材によって囲まれた内側に保持された液晶層と、

を備えたことを特徴とする液晶表示装置。

**【請求項 2】**

前記絶縁膜は、ポジ型レジストによって形成されたことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

絶縁基板の上方に第1スイッチング素子及び第2スイッチング素子を形成し、

20

前記第1スイッチング素子上に第1コンタクトホールが形成された第1カラーフィルタ層を形成し、

前記第2スイッチング素子上に第2コンタクトホールが形成されるとともに前記第1カラーフィルタ層の一部に重なった重畠部を形成する第2カラーフィルタ層を形成し、

前記第1カラーフィルタ層上及び前記第2カラーフィルタ層上にレジストを塗布し、

第1コンタクトホールの直上及び前記第2コンタクトホールの直上に位置する前記レジストを第1露光量で露光するとともに前記重畠部の直上に位置する前記レジストを第1露光量とは異なる第2露光量で露光し、

前記レジストにより前記第1コンタクトホール及び前記第2コンタクトホールに連通した貫通孔が形成された絶縁膜を形成し、

30

前記第1カラーフィルタ層の上方に位置する前記絶縁膜上に前記第1スイッチング素子に電気的に接続された第1画素電極を形成するとともに、前記第2カラーフィルタ層の上方に位置する前記絶縁膜上に前記第2スイッチング素子に電気的に接続された第2画素電極を形成する第1基板の製造工程と、

前記第1基板の前記第1画素電極及び前記第2画素電極が形成された面に閉ループ状のシール材を塗布する工程と、

前記第1基板の前記シール材で囲まれた内側に液晶材料を滴下する工程と、

前記第1基板に第2基板を貼り合わせる工程と、

を備えたことを特徴とする液晶表示装置の製造方法。

**【請求項 4】**

前記レジストはポジ型レジストであり、前記第2露光量は前記第1露光量よりも低露光量であることを特徴とする請求項3に記載の液晶表示装置の製造方法。

40

**【請求項 5】**

前記重畠部の直上に位置する前記絶縁膜の上面は、前記第1画素電極及び前記第2画素電極が形成される前記絶縁膜の上面よりも窪んでいることを特徴とする請求項3に記載の液晶表示装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は、液晶表示装置及びその製造方法に関する。

50

**【背景技術】****【0002】**

液晶表示装置は、軽量、薄型、低消費電力などの特徴を生かして、パーソナルコンピュータなどのOA機器やテレビなどの表示装置として各種分野で利用されている。近年では、液晶表示装置は、携帯電話などの携帯端末機器や、カーナビゲーション装置、ゲーム機などの表示装置としても利用されている。

**【0003】**

このような液晶表示装置において、一对の基板間に液晶層を形成する方法として、滴下注入法が知られている。この滴下注入法は、一方の基板にシール材を閉ループ状に塗布した後、ループ内に液晶材料を滴下し、他方の基板を重ね合わせ、液晶材料を広げて液晶層を形成し、シール材を硬化するものである。

10

**【0004】**

例えば、特許文献1によれば、ディスペンサーでの描画し始めにシール材が出てきにくく、描画し終わり時には糸曳き状態となりやすいといった課題に対し、シール材を塗布する工程は、閉ループ状シールパターンの外部の箇所から描画し始め、且つ、閉ループ状シールパターンの外部の箇所で描画し終わる工程を有する液晶表示素子の製造方法が開示されている。

20

**【先行技術文献】****【特許文献】****【0005】****【特許文献1】特開2003-222883号公報****【発明の概要】****【発明が解決しようとする課題】****【0006】**

この発明の目的は、生産性の低下を抑制することが可能な液晶表示装置及びその製造方法を提供することにある。

**【課題を解決するための手段】****【0007】**

この発明の一態様によれば、

30

第1スイッチング素子及び第2スイッチング素子と、前記第1スイッチング素子上に配置された第1カラーフィルタ層と、前記第2スイッチング素子上に配置されるとともに前記第1カラーフィルタ層の一部に重なった重畠部を形成する第2カラーフィルタ層と、前記第1カラーフィルタ層及び前記第2カラーフィルタ層を覆うとともに前記重畠部の直上に凹部が形成された絶縁膜と、前記第1カラーフィルタ層の上方に位置する前記絶縁膜上に配置され前記第1スイッチング素子に電気的に接続された第1画素電極と、前記第2カラーフィルタ層の上方に位置する前記絶縁膜上に配置され前記第2スイッチング素子に電気的に接続された第2画素電極と、を備えた第1基板と、前記第1基板に対向して配置された第2基板と、前記第1基板と前記第2基板とを貼り合わせる閉ループ状のシール材と、前記第1基板と前記第2基板との間であって前記シール材によって囲まれた内側に保持された液晶層と、を備えたことを特徴とする液晶表示装置が提供される。

40

**【0008】**

この発明の他の態様によれば、

絶縁基板の上方に第1スイッチング素子及び第2スイッチング素子を形成し、前記第1スイッチング素子上に第1コンタクトホールが形成された第1カラーフィルタ層を形成し、前記第2スイッチング素子上に第2コンタクトホールが形成されるとともに前記第1カラーフィルタ層の一部に重なった重畠部を形成する第2カラーフィルタ層を形成し、前記第1カラーフィルタ層上及び前記第2カラーフィルタ層上にレジストを塗布し、第1コンタクトホールの直上及び前記第2コンタクトホールの直上に位置する前記レジストを第1露光量で露光するとともに前記重畠部の直上に位置する前記レジストを第1露光量とは異なる第2露光量で露光し、前記レジストにより前記第1コンタクトホール及び前記第2コ

50

ンタクトホールに連通した貫通孔が形成された絶縁膜を形成し、前記第1カラーフィルタ層の上方に位置する前記絶縁膜上に前記第1スイッチング素子に電気的に接続された第1画素電極を形成するとともに、前記第2カラーフィルタ層の上方に位置する前記絶縁膜上に前記第2スイッチング素子に電気的に接続された第2画素電極を形成する第1基板の製造工程と、前記第1基板の前記第1画素電極及び前記第2画素電極が形成された面に閉ループ状のシール材を塗布する工程と、前記第1基板の前記シール材で囲まれた内側に液晶材料を滴下する工程と、前記第1基板に第2基板を貼り合わせる工程と、を備えたことを特徴とする液晶表示装置の製造方法が提供される。

【発明の効果】

【0009】

10

この発明によれば、生産性の低下を抑制することが可能な液晶表示装置及びその製造方法を提供することができる。

【図面の簡単な説明】

【0010】

【図1】図1は、この発明の一実施の形態における液晶表示装置の構成を概略的に示す図である。

【図2】図2は、図1に示した液晶表示パネルのアレイ基板の構造を概略的に示す平面図である。

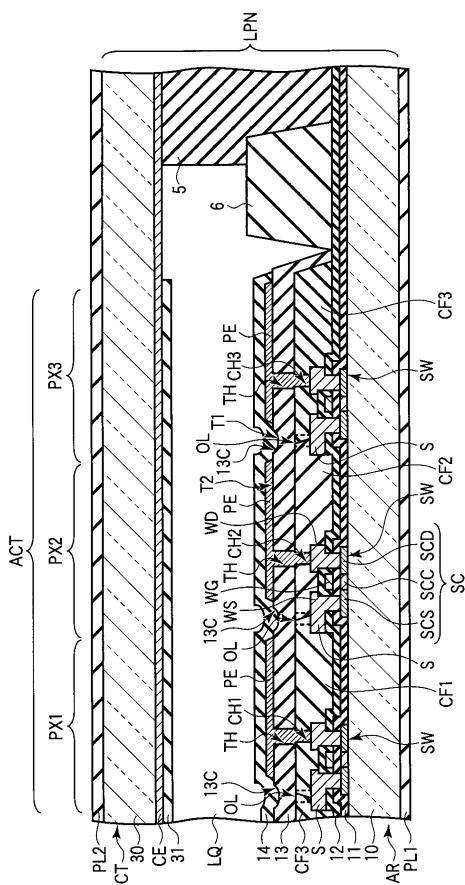

【図3】図3は、図1に示した液晶表示パネルの構造を概略的に示す断面図である。

【図4】図4は、本実施形態の液晶表示装置の製造方法を説明するための図であり、第1絶縁基板上にスイッチング素子などを形成する工程を説明するための概略断面図である。

20

【図5】図5は、本実施形態の液晶表示装置の製造方法を説明するための図であり、第1絶縁基板上に第1乃至第3カラーフィルタ層を形成する工程を説明するための概略断面図である。

【図6】図6は、本実施形態の液晶表示装置の製造方法を説明するための図であり、第1乃至第3カラーフィルタ層の上にレジストを塗布する工程を説明するための概略断面図である。

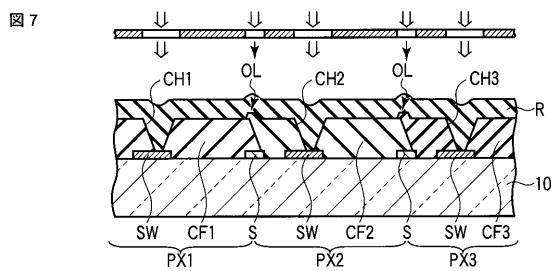

【図7】図7は、本実施形態の液晶表示装置の製造方法を説明するための図であり、塗布されたレジストを露光する工程を説明するための概略断面図である。

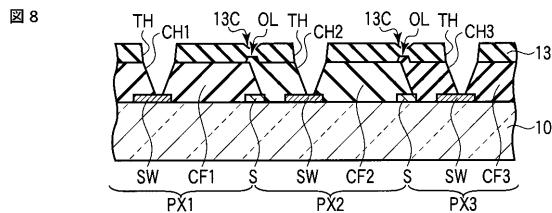

【図8】図8は、本実施形態の液晶表示装置の製造方法を説明するための図であり、露光されたレジストにより上面に凹部を有するオーバーコート層を形成する工程を説明するための概略断面図である。

30

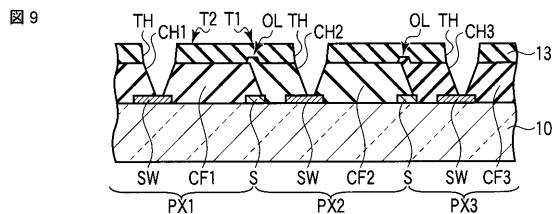

【図9】図9は、本実施形態の液晶表示装置の製造方法を説明するための図であり、露光されたレジストにより上面が平坦化されたオーバーコート層を形成する工程を説明するための概略断面図である。

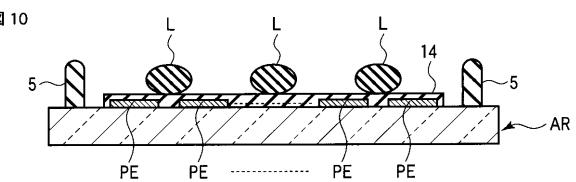

【図10】図10は、本実施形態の液晶表示装置の製造方法を説明するための図であり、アレイ基板にシール材を塗布する工程、及びその後に液晶材料を滴下する工程を説明するための概略断面図である。

40

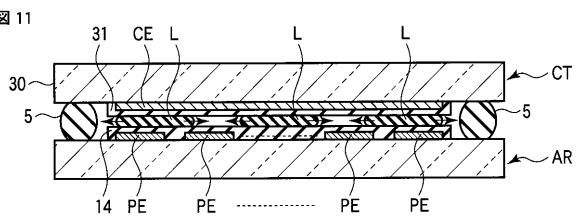

【図11】図11は、本実施形態の液晶表示装置の製造方法を説明するための図であり、アレイ基板と対向基板とを貼り合わせる工程を説明するための概略断面図である。

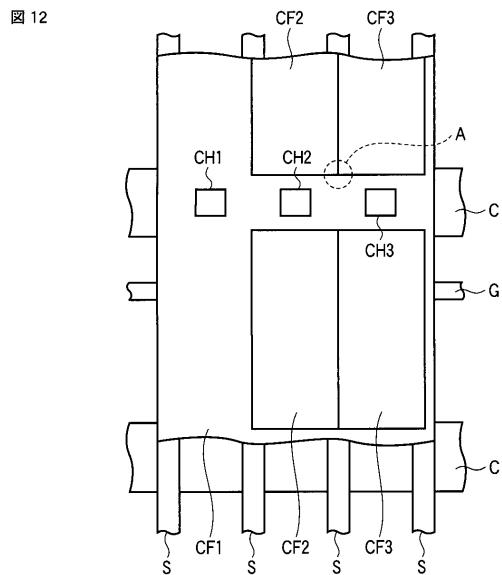

【図12】図12は、本実施形態の変形例における第1乃至第3カラーフィルタ層が配置された各画素の概略平面図である。

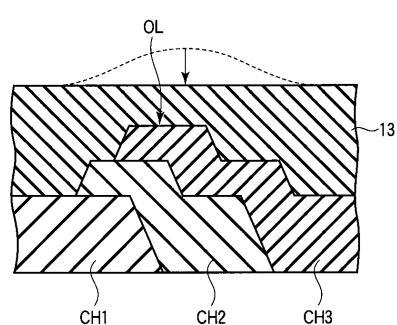

【図13】図13は、図12に示した本実施形態の変形例における位置Aでの第1乃至第3カラーフィルタ層及びオーバーコート層の概略断面図である。

【発明を実施するための形態】

【0011】

以下、本発明の一態様について、図面を参照しながら詳細に説明する。なお、各図において、同一又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

【0012】

50

図1は、本実施形態における液晶表示装置の構成を模式的に示す図である。

【0013】

すなわち、液晶表示装置1は、アクティブマトリクスタイプの液晶表示パネルLPN、液晶表示パネルLPNに接続された駆動ICチップ2及びフレキシブル配線基板3、液晶表示パネルLPNを照明するバックライト4などを備えている。

【0014】

液晶表示パネルLPNは、第1基板としてのアレイ基板ARと、アレイ基板ARに対向して配置された第2基板としての対向基板CTと、これらのアレイ基板ARと対向基板CTとの間に保持された図示しない液晶層と、を備えて構成されている。これらのアレイ基板ARと対向基板CTとは、シール材5によって貼り合わせられている。このシール材5は、アレイ基板ARと対向基板CTとの間ににおいて、略矩形枠状に形成されている。10

【0015】

このような液晶表示パネルLPNは、シール材5によって囲まれた内側に、画像を表示する略矩形状のアクティブエリアACTを備えている。このアクティブエリアACTは、 $m \times n$ 個のマトリクス状に配置された複数の画素PXによって構成されている（但し、m及びnは正の整数である）。

【0016】

バックライト4は、図示した例では、アレイ基板ARの背面側に配置されている。このようなバックライト4としては、種々の形態が適用可能であり、また、光源として発光ダイオード(LED)を利用したものや冷陰極管(CFL)を利用したものなどのいずれでも適用可能であり、詳細な構造については説明を省略する。20

【0017】

図2は、図1に示したアレイ基板ARを対向基板CTの側から見た概略上面図である。なお、図2においては、説明に必要な主要部のみを図示している。

【0018】

まず、アクティブエリアACTの一画素PXの構成について説明する。アレイ基板ARは、第1方向Xに沿ってそれぞれ延出したゲート線G及び補助容量線C、第1方向Xと交差する第2方向Yに沿って延出したソース線S、ゲート線Gとソース線Sとの交差部近傍に配置されたスイッチング素子SWなどを備えている。30

【0019】

アクティブエリアACTにおいて、複数本のゲート線G及び補助容量線Cは、第2方向Yに沿って交互に並列配置されている。また、複数本のソース線Sは、第1方向に沿って並列配置されている。ゲート線G及び補助容量線Cとソース線Sとは略直交するため、これらは格子状に形成され、アクティブエリアACTにおいてブラックマトリクスを形成する。例えば、補助容量線Cとソース線Sとが成すマス目が画素PXの開口部に相当する。

【0020】

各スイッチング素子SWは、例えば、nチャネル薄膜トランジスタ(TFT)によって構成されている。このスイッチング素子SWは、半導体層SCを備えている。この半導体層SCは、例えば、ポリシリコンやアモルファスシリコンなどによって形成可能であり、ここではポリシリコンによって形成されている。40

【0021】

スイッチング素子SWのゲート電極WGは、ゲート線Gに電気的に接続されている。図示した例では、ゲート電極WGはゲート線Gと一体的に形成されている。スイッチング素子SWのソース電極WSは、ソース線Sに電気的に接続されている。図示した例では、ソース電極WSはソース線Sと一体に形成されている。スイッチング素子SWのドレイン電極WDは、画素電極PEと電気的に接続されている。

【0022】

このようなゲート電極WGは、ゲート線Gや補助容量線Cなどと同一の導電材料を用いて同一工程で形成可能である。また、ソース電極WS及びドレイン電極WDは、ソース線Sなどと同一の導電材料を用いて同一工程で形成可能である。これらのゲート線Gやソーラー

10

20

30

40

50

ス線 S などは、例えばアルミニウム、モリブデン、タングステン、チタンなどの低抵抗な導電材料によって形成されている。ここに示した導電材料は、いずれも光の透過率が極めて低い（あるいはほとんど透過率がゼロである）遮光性の材料である。

【 0 0 2 3 】

カラーフィルタ層 C F は、スイッチング素子 S W の上に配置されている。このようなカラーフィルタ層 C F には、互いに異なる色に着色された複数種類のカラーフィルタ層が含まれる。ここに示した例では、カラーフィルタ層 C F として、例えば赤色に着色された樹脂材料からなる第 1 カラーフィルタ層 C F 1、青色に着色された樹脂材料からなる第 2 カラーフィルタ層 C F 2、緑色に着色された樹脂材料からなる第 3 カラーフィルタ層 C F 3 が配置されている。

10

【 0 0 2 4 】

これらの第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 は、アクティブエリア A C T の第 2 方向 Y に沿って延在している。また、これらの第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 は、第 1 方向 X に交互に配置され、図示した例では、アクティブエリア A C T の左側から右側に向かって順に、第 1 カラーフィルタ層 C F 1、第 2 カラーフィルタ層 C F 2、第 3 カラーフィルタ層 C F 3、第 1 カラーフィルタ層 C F 1、…、第 3 カラーフィルタ層 C F 3 と交互に配置されている。

20

【 0 0 2 5 】

また、これらの第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 は、互いに離間することなく、それぞれの周縁部が重なるように配置されている。つまり、第 1 カラーフィルタ層 C F 1 の周縁部は、第 1 方向 X に隣接する第 2 カラーフィルタ層 C F 2 の周縁部と重なって重疊部を形成している。同様に、第 2 カラーフィルタ層 C F 2 の周縁部は第 1 方向 X に隣接する第 3 カラーフィルタ層 C F 3 の周縁部と重なり、また、第 3 カラーフィルタ層 C F 3 の周縁部は第 1 方向 X に隣接する第 1 カラーフィルタ層 C F 1 の周縁部と重なり、それぞれ重疊部を形成している。これらの重疊部は、図示した例では、ソース線 S の略直上に位置している。このため、第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 の下層の導電層、例えばソース線 S やゲート線 G や補助容量線 C がむき出しとならず、第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 の上に画素電極 P E を形成した際のショートの発生を防止できる。

30

【 0 0 2 6 】

これらの第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 のそれぞれは、第 2 方向 Y に並んだ画素 P X の各スイッチング素子 S W を覆うように配置されている。また、これらの第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 の上には、それぞれ第 2 方向 Y に並んだ複数の画素電極 P E が配置されている。各画素電極 P E は、スイッチング素子 S W のドレイン電極 W D に電気的に接続されている。このような画素電極 P E は、各画素 P X の開口部に対応して配置されている。

40

【 0 0 2 7 】

上述したアレイ基板 A R において、アクティブエリア A C T の外側には、シール材 5 が配置されている。図示した例では、シール材 5 は、略矩形状のアクティブエリア A C T の外周に沿って矩形枠状に形成されている。特に、このシール材 5 は、閉ループ状に形成されており、いわゆる注入口を確保するべく途中で途切れた形状とは異なる。なお、図示した例では、アレイ基板 A R の画素電極 P E などが形成された面にシール材 5 を配置したが、図示しない対向基板 C T のアレイ基板 A R と向かい合う面にシール材を配置しても良い。

【 0 0 2 8 】

また、上述したアレイ基板 A R において、アクティブエリア A C T の外側であってシール材 5 よりも内側には、遮光層 6 が配置されている。図示した例では、遮光層 6 は、略矩形状のアクティブエリア A C T の外周に沿って矩形枠状に形成されている。このような遮光層 6 は、例えば、黒色に着色された樹脂材料によって形成されている。

50

【 0 0 2 9 】

液晶表示パネル L P N の構造について、以下により詳細に説明する。

【0030】

図3は、図2に示したアレイ基板 A R を図中の A - B 線で切断したときの液晶表示パネル L P N の概略断面図である。

【0031】

アレイ基板 A R は、ガラス板などの光透過性を有する第1絶縁基板 10 を用いて形成されている。スイッチング素子 S W は、第1絶縁基板 10 の上に形成された半導体層 S C を備えている。この半導体層 S C は、チャネル領域 S C C を挟んだ両側にそれぞれソース領域 S C S 及びドレイン領域 S C D を有している。なお、第1絶縁基板 10 と半導体層 S C との間には、絶縁膜であるアンダーコート層が介在していても良い。半導体層 S C は、ゲート絶縁膜 11 によって覆われている。また、ゲート絶縁膜 11 は、第1絶縁基板 10 の上にも配置されている。

10

【0032】

ゲート電極 W G は、ゲート絶縁膜 11 の上に形成され、半導体層 S C のチャネル領域 S C C の直上に位置している。ゲート電極 W G は、層間絶縁膜 12 によって覆われている。また、この層間絶縁膜 12 は、ゲート絶縁膜 11 の上にも配置されている。これらのゲート絶縁膜 11 及び層間絶縁膜 12 は、例えば、酸化シリコン及び窒化シリコンなどの無機系材料によって形成されている。

20

【0033】

スイッチング素子 S W のソース電極 W S 及びドレイン電極 W D は、層間絶縁膜 12 の上に形成されている。ソース電極 W S は、ゲート絶縁膜 11 及び層間絶縁膜 12 を貫通するコンタクトホールを通して半導体層 S C のソース領域 S C S にコンタクトしている。同様に、ドレイン電極 W D は、ゲート絶縁膜 11 及び層間絶縁膜 12 を貫通するコンタクトホールを通して半導体層 S C のドレイン領域 S C D にコンタクトしている。

20

【0034】

このような構成のスイッチング素子 S W の上にはカラーフィルタ層が配置されている。すなわち、画素 P X 1 において、第1カラーフィルタ層 C F 1 は、ソース電極 W S 及びドレイン電極 W D を覆うとともに、層間絶縁膜 12 の上にも配置され、さらに、第1方向 X に隣接する2本のソース線 S の上にもそれぞれ延在している。この第1カラーフィルタ層 C F 1 は、概略テーパ状の断面を有している。第1カラーフィルタ層 C F 1 が延在した2本のソース線 S のうちの一方のソース線 S の直上近傍では、第1カラーフィルタ層 C F 1 の上に第3カラーフィルタ層 C F 3 が重なり、重畠部 O L を形成している。このような第1カラーフィルタ層 C F 1 には、画素 P X 1 に配置されたスイッチング素子 S W のドレイン電極 W D に到達するコンタクトホール C H 1 が形成されている。

30

【0035】

画素 P X 2 においても同様に第2カラーフィルタ層 C F 2 が配置されている。この第2カラーフィルタ層 C F 2 は、画素 P X 1 と画素 P X 2 との間のソース線 S の直上近傍で第1カラーフィルタ層 C F 1 の上に重なり、重畠部 O L を形成している。この第2カラーフィルタ層 C F 2 には、画素 P X 2 に配置されたスイッチング素子 S W のドレイン電極 W D に到達するコンタクトホール C H 2 が形成されている。

40

【0036】

また、画素 P X 3 においても同様に第3カラーフィルタ層 C F 3 が配置されている。この第3カラーフィルタ層 C F 3 は、画素 P X 2 と画素 P X 3 との間のソース線 S の直上近傍で第2カラーフィルタ層 C F 2 の上に重なり、重畠部 O L を形成している。この第3カラーフィルタ層 C F 3 には、画素 P X 3 に配置されたスイッチング素子 S W のドレイン電極 W D に到達するコンタクトホール C H 3 が形成されている。

【0037】

図示した重畠部 O L は、いずれもソース線 S の直上付近において、第1カラーフィルタ層 C F 1 と第2カラーフィルタ層 C F 2 、第2カラーフィルタ層 C F 2 と第3カラーフィルタ層 C F 3 、第3カラーフィルタ層 C F 3 と第1カラーフィルタ層 C F 1 といった2種

50

類のカラーフィルタ層が積層された2層構造であるが、第1乃至第3カラーフィルタ層C F 1乃至3が積層された3層構造であっても良い。また、重畠部O Lは、ソース線Sの直上付近に限らず、ゲート線Gの直上付近や、補助容量線Cの直上付近に形成されても良い。

【0038】

これらの第1乃至第3カラーフィルタ層C F 1乃至3は、重畠部O Lを含む略全体が絶縁膜であるオーバーコート層13によって覆われている。つまり、オーバーコート層13は、第1乃至第3カラーフィルタ層C F 1乃至3のうち、第1カラーフィルタ層C F 1のみが配置された部分、第1カラーフィルタ層C F 1と第2カラーフィルタ層C F 2との重畠部O L、第2カラーフィルタ層C F 2のみが配置された部分、第2カラーフィルタ層C F 2と第3カラーフィルタ層C F 3との重畠部O L、第3カラーフィルタ層C F 3のみが配置された部分、さらには、第3カラーフィルタ層C F 3と第1カラーフィルタ層C F 1との重畠部O Lのそれぞれの上面に配置されている。

10

【0039】

このオーバーコート層13には、貫通孔T Hが形成されている。貫通孔T Hは、第1乃至第3カラーフィルタ層C F 1乃至3のそれぞれに形成されたコンタクトホールC H 1乃至3に連通している。このようなオーバーコート層13は、例えば、ポジ型レジストなどの光透過性を有するフォトレジストによって形成されている。

20

【0040】

このようなオーバーコート層13は、概ね上方（つまり対向基板C Tの側）に突出することなく、略平坦に形成されている、もしくは、一部に凹部が形成されている。図示した例では、オーバーコート層13において、重畠部O Lの直上には凹部13Cが形成されている。換言すると、重畠部O Lの直上に位置するオーバーコート層13の上面T 1は、画素電極P Eが配置される下地となるオーバーコート層13の上面T 2よりも窪んでいる。このような凹部13Cは、ソース線Sの直上付近に位置している。第1乃至第3カラーフィルタ層C F 1乃至3が図2に示したようなパターンで形成された場合、凹部13Cは、アクティブエリアA C Tにおいて第2方向Yに延在し、ストライプ状に形成されている。オーバーコート層13の上面が略平坦が形成された例については後述する。

20

【0041】

画素電極P Eは、アクティブエリアA C Tにおいて各画素P Xに配置されている。すなわち、この画素電極P Eは、オーバーコート層13の上に配置されている。このような画素電極P Eは、インジウム・ティン・オキサイド（ITO）やインジウム・ジンク・オキサイド（IZO）などの光透過性を有する導電材料によって形成されている。

30

【0042】

画素P X 1に配置された画素電極P Eは、オーバーコート層13に形成された貫通孔T H及び第1カラーフィルタ層C F 1に形成されたコンタクトホールC H 1を通してドレイン電極W Dと電気的に接続されている。同様に、画素P X 2に配置された画素電極は貫通孔T H及びコンタクトホールC H 2を通してドレイン電極と電気的に接続されている。同様に、画素P X 3に配置された画素電極は貫通孔T H及びコンタクトホールC H 3を通してドレイン電極と電気的に接続されている。

40

【0043】

これらの画素電極P Eの表面は、第1配向膜14によって覆われている。すなわち、第1配向膜14は、アレイ基板A Rの対向基板C Tと向かい合う側の表面、つまり、液晶層L Qに接する面に配置されている。

【0044】

アレイ基板A RのアクティブエリアA C Tの外側においては、遮光層6が配置され、さらにその外側にはシール材5が配置されている。

【0045】

一方、液晶表示パネルL P Nの対向基板C Tは、ガラス板などの光透過性を有する第2絶縁基板30を用いて形成されている。この対向基板C Tは、第2絶縁基板30に対向電

50

極 C E などを備えている。

【 0 0 4 6 】

対向電極 C E は連続膜であり、アクティブエリア A C T においては、液晶層 L Q を介して各画素電極 P E と対向している。また、この対向電極 C E は、アクティブエリア A C T の外側にも延在し、シール材 5 よりも外側において図示しない導電部材を介してアレイ基板 A R の側から所定の電圧が印加される。このような対向電極 C E は、ITO や IZO などの光透過性を有する導電材料によって形成されている。

【 0 0 4 7 】

対向電極 C E の表面は、第 2 配向膜 3 1 によって覆われている。すなわち、第 2 配向膜 3 1 は、対向基板 C T のアレイ基板 A R と向かい合う側の表面、つまり液晶層 L Q に接する面に配置されている。

【 0 0 4 8 】

上述したようなアレイ基板 A R と対向基板 C T とは、それぞれの第 1 配向膜 1 4 及び第 2 配向膜 3 1 が対向するように配置されている。このとき、アレイ基板 A R の第 1 配向膜 1 4 と対向基板 C T の第 2 配向膜 3 1 との間には、例えば、樹脂材料によって一方の基板に一体的に形成された柱状スペーサが配置され、これにより、所定のギャップ、例えば 3 ~ 7  $\mu$ m のギャップが形成される。アレイ基板 A R と対向基板 C T とは、所定のギャップが形成された状態でシール材 5 によって貼り合わせられている。

【 0 0 4 9 】

液晶層 L Q は、上述したセルギャップに封入されている。すなわち、液晶層 L Q は、アレイ基板 A R の画素電極 P E と対向基板 C T の対向電極 C E との間に保持された液晶材料によって構成されている。液晶層 L Q と画素電極 P E との間には、第 1 配向膜 1 4 が介在している。液晶層 L Q と対向電極 C E との間には、第 2 配向膜 3 1 が介在している。

【 0 0 5 0 】

液晶表示パネル L P N の一方の外面、つまり、アレイ基板 A R を構成する第 1 絶縁基板 1 0 の外面には、第 1 偏光板 P L 1 が接着剤などにより貼付されている。また、液晶表示パネル L P N の他方の外面、つまり、対向基板 C T を構成する第 2 絶縁基板 3 0 の外面には、第 2 偏光板 P L 2 が接着剤などにより貼付されている。

【 0 0 5 1 】

次に、上述した液晶表示パネル L P N の製造方法について説明する。

【 0 0 5 2 】

まず、図 4 に示すように、第 1 絶縁基板 1 0 の上方にソース線 S や図示しないゲート線及び補助容量線を形成するとともにスイッチング素子 S W を形成する。なお、ここでは、説明に必要な構成のみを図示しており、スイッチング素子 S W を簡略化して図示するとともに、ゲート絶縁膜や層間絶縁膜は省略している。スイッチング素子 S W は、画素 P X 1 乃至 P X 3 にそれぞれ形成される。

【 0 0 5 3 】

続いて、図 5 に示すように、画素 P X 1 に第 1 カラーフィルタ層 C F 1 を形成する。この第 1 カラーフィルタ層 C F 1 は、例えば、第 1 絶縁基板 1 0 の上面全体に着色された樹脂材料を成膜した後に、フォトリソグラフィプロセスを経て所望の形状にパターン化されることによって形成される。このような樹脂材料のバーニングの際に、画素 P X 1 に配置されたスイッチング素子 S W に到達するコンタクトホール C H 1 も同時に形成される。その後、同様にして、画素 P X 2 にコンタクトホール C H 2 が形成された第 2 カラーフィルタ層 C F 2 を形成する。さらにその後、同様にして、画素 P X 3 にコンタクトホール C H 3 が形成された第 3 カラーフィルタ層 C F 3 を形成する。

【 0 0 5 4 】

これらの第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 は、それらの周縁部で互いに重なるように配置される。このため、図示したように、第 1 カラーフィルタ層 C F 1 の上に第 2 カラーフィルタ層 C F 2 が重なった重畠部 O L では、第 2 カラーフィルタ層 C F 2 が上方に向かって盛り上がっている。同様に、第 2 カラーフィルタ層 C F 2 の上に第 3 カラーフィルタ層 C F 3 が重なった重畠部 O L では、第 3 カラーフィルタ層 C F 3 が上方に向かって盛り上がっている。

10

20

30

40

50

フィルタ層 C F 3 が重なった重畠部 O L では、第 3 カラーフィルタ層 C F 3 が上方に向かって盛り上がっている。図示していないが、第 1 カラーフィルタ層 C F 1 の上に第 3 カラーフィルタ層 C F 3 が重なった重畠部 O L でも同様に、第 3 カラーフィルタ層 C F 3 が上方に向かって盛り上がっている。

## 【0055】

重畠部 O L における盛り上がりの高さは、カラーフィルタ層の材料特性や厚さ、カラーフィルタ同士の重なり量、加工プロセスなどの条件によって変わるが、一例として、塗布したレジスト R の厚さが約 2  $\mu\text{m}$  である場合に、重畠部 O L の直上付近でレジスト R が 0.2 ~ 1.0  $\mu\text{m}$  程度盛り上がることがある。

## 【0056】

続いて、図 6 に示すように、第 1 乃至第 3 カラーフィルタ層 C F 1 乃至 3 の上にレジスト R を塗布する。ここでは、レジスト R として、光照射により分解が促進され現像液に溶解するポジ型レジストを適用している。このレジスト R は、塗布された際に下地の凹凸を吸収する傾向にあるが、重畠部 O L の直上付近ではその上面は依然として上方に向かって盛り上がっている。

## 【0057】

続いて、図 7 に示すように、レジスト R のうち、コンタクトホール C H 1 乃至 3 の直上に位置するレジスト R を第 1 露光量で露光するとともに、重畠部 O L の直上に位置するレジスト R を第 1 露光量とは異なる第 2 露光量で露光する。このような位置に応じて露光量が異なる露光工程は、たとえば、第 1 露光量で露光する工程と第 2 露光量で露光する工程とを分けて行っても良いが、コンタクトホール C H 1 乃至 3 に対向する領域が第 1 透過率（高透過率）であり且つ重畠部 O L に対向する領域が第 1 透過率より低い第 2 透過率である露光マスクを用いて一括して行っても良い。また、露光マスクとして、重畠部 O L に対向する領域にグラデーションが形成されたハーフトーンマスクを用いても良い。

## 【0058】

ここでは、ポジ型レジストを適用しているため、露光量が大きいほどレジスト R の分解が促進される。このため、コンタクトホール C H 1 乃至 3 の直上においては、レジスト R を完全に除去し、コンタクトホール C H 1 乃至 3 に連通した貫通孔 T H を形成する必要があるため、第 1 露光量は高露光量に設定される。一方で、重畠部 O L の直上においては、レジスト R の盛り上がりを除去することが目的であり、レジスト R を完全に除去することはないため、第 2 露光量は第 1 露光量よりも低露光量に設定される。

## 【0059】

続いて、図 8 に示すように、上述したレジスト R に対して現像処理などを施すことにより、コンタクトホール C H 1 乃至 3 に連通した貫通孔 T H が形成されたオーバーコート層 1 3 が形成される。また、このオーバーコート層 1 3 においては、重畠部 O L の直上における盛り上がりが除去される。図 8 に示した例では、重畠部 O L の直上におけるオーバーコート層 1 3 には凹部 1 3 C が形成されている。このような凹部 1 3 C は、重畠部 O L まで貫通していない。

## 【0060】

なお、図 9 に示したように、オーバーコート層 1 3 において、重畠部 O L の直上が略平坦に形成されても良い。この場合、重畠部 O L の直上に位置するオーバーコート層 1 3 の上面 T 1 は、画素電極 P E が配置される下地となるオーバーコート層の上面 T 2 と同一平面を形成している。図 8 及び図 9 のいずれに示した例についても、重畠部 O L はオーバーコート層 1 3 によって覆われている。

## 【0061】

その後、図示を省略するが、画素 P X 1 乃至画素 P X 3 のそれぞれにおいて、オーバーコート層 1 3 の上に画素電極 P E が形成され、さらにその後、画素電極 P E の上に第 1 配向膜 1 4 が形成される。以上のような工程を経てアレイ基板 A R が製造される。

## 【0062】

続いて、図 10 に示すように、アレイ基板 A R の画素電極 P E が形成された面にシール

10

20

30

40

50

材5を塗布する。このとき、シール材5は、図2などに示した通り、閉ループ状に形成される。その後、アレイ基板ARのシール材5で囲まれた内側に液晶材料Lを滴下する。このとき、液晶材料Lは、アレイ基板ARのシール材5が形成された面に滴下され、配向膜14の上に位置している。

【0063】

続いて、図11に示すように、アレイ基板ARと対向基板CTとを貼り合わせる。なお、ここで用意した対向基板CTは、第2絶縁基板30の上に対向電極CEを形成した後、この対向電極CEの上に第2配向膜31を形成したものである。この貼り合わせ工程では、例えば、真空にした組立チャンバー内に、液晶材料Lが滴下されたアレイ基板AR及び別個に用意した対向基板CTを挿入し、アレイ基板ARの上の液晶材料Lと対向基板CTの第2配向膜31とが向かい合うように配置される。そして、アレイ基板ARと対向基板CTとの間隔が小さくなるに従い、滴下した液晶材料Lがアレイ基板ARの第1配向膜14と対向基板CTの第2配向膜31との間で周囲に向かって広がり、これらの基板間を満たすことによって液晶注入が行われる。そして、シール材5の硬化処理がなされ、貼り合わせられたアレイ基板ARと対向基板CTとの間に液晶層LQを保持した液晶表示パネルが製造される。

【0064】

上述した本実施形態によれば、アレイ基板ARに形成されたカラーフィルタ層CFの段差、つまり対向基板CTに向かって突出した盛り上がり（凸部）が低減されている。このため、アレイ基板ARに滴下した液晶材料Lは、アレイ基板ARと対向基板CTとの間で周囲に向かって広がる際、アレイ基板ARの表面（つまり第1配向膜14の上面）及び対向基板CTの表面（つまり第2配向膜31の上面）に沿ってスムースに進み、短時間で均一な液晶層LQを形成することが可能となる。したがって、効率よく液晶注入を行うことが可能となり、歩留りを改善できる。

【0065】

また、本実施形態によれば、重畠部OLの直上における不所望な盛り上がりが低減されたため、液晶分子の配向不良またはセルギャップ変化を抑制することが可能となる。このため、重畠部OLの直上付近での画質低下、例えば透過率やコントラストや視野角の変化がなく、表示品位の改善に貢献できる。

【0066】

一方、カラーフィルタ層CFの盛り上がりが残っている場合、例えば、図2に示したようなパターンの第1乃至第3カラーフィルタ層CF1乃至3を形成した場合、第2方向Yに沿って伸びた盛り上がりが形成されるため、液晶材料Lの第1方向Xへの広がりに対する抵抗となり、均一な液晶層を形成するまでに要する時間が本実施形態よりも長く、場合によってはアクティブエリアACTの周辺、特にコーナー部に僅かに気泡が残る場合もあった。

【0067】

上述した実施の形態では、第1乃至第3カラーフィルタ層CF1乃至3のいずれもが第2方向Yに沿って直線的に延在していた例について説明したが、この例に限らない。

【0068】

例えば、図12に示した例は、図2などに示した例と比較して、第2カラーフィルタ層CF2及び第3カラーフィルタ層CF3が画素PXの開口部に配置される一方で、第1カラーフィルタ層CF1が画素PXの開口部のみならずコンタクトホールCH1乃至3が形成される補助容量線Cの上にも延在している点で相違している。

【0069】

このような例の場合にも、第1乃至第3カラーフィルタ層CF1乃至3は、それぞれの周縁部が重なるように配置され、重畠部OLが形成されている。このような重畠部OLのうち、特に図中のAで示した位置では、第1乃至第3カラーフィルタ層CF1乃至3の3層が積層されている。このため、位置Aに形成された重畠部OLは、2層のカラーフィルタ層が積層されて形成された他の位置の重畠部OLよりも高く盛り上がる。

## 【0070】

これらの第1乃至第3カラーフィルタ層C F 1乃至3の上にオーバーコート層1 3を配置した場合、重疊部O Lの直上付近で盛り上がり、特に、位置Aでは高く盛り上がる。このため、位置A付近で液晶材料の広がりに対する抵抗が大きくなる。

## 【0071】

そこで、上述した例と同様に、オーバーコート層1 3を形成する際に、露光量を調整することにより、図13の概略断面図に示すように、位置Aを含む重疊部O Lの直上に位置するオーバーコート層1 3の盛り上がりを低減することができる。これにより、液晶材料をよりスムースに広げることができ、短時間で均一な液晶層L Qを形成することが可能となる。

10

## 【0072】

なお、この発明は、上記実施形態そのものに限定されるものではなく、その実施の段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せててもよい。

## 【0073】

例えば、上述した実施の形態では、オーバーコート層を形成するレジストとしてポジ型レジストを適用した例について説明したが、ネガ型レジストを適用することも可能である。

20

## 【0074】

また、本実施形態では、第1乃至第3カラーフィルタ層C F 1乃至3をアレイ基板A Rに形成するいわゆるカラーフィルタ・オン・アレイ(C O A)構造について説明したが、これらの第1乃至第3カラーフィルタ層C F 1乃至3は、対向基板C Tに形成されても良い。この場合、第1乃至第3カラーフィルタ層C F 1乃至3は、第2絶縁基板3 0と対向電極C Eとの間に配置され、さらに、これらの第1乃至第3カラーフィルタ層C F 1乃至3と対向電極C Eとの間にオーバーコート層1 3が配置される。このような構成においても、重疊部O Lの直上に位置するオーバーコート層1 3の盛り上がりを低減することにより、本実施形態と同様の効果が得られる。

## 【0075】

さらに、本実施形態では、液晶層L Qに印加する電界をアレイ基板A Rに形成した画素電極P Eと対向基板C Tに形成した対向電極C Eとの間で形成した場合について説明したが、一方の基板に画素電極P Eと対向電極C Eとを形成したいわゆる横電界モードを適用しても良い。

30

## 【0076】

さらに、本実施形態では、液晶注入を滴下注入方式にて説明したが、シールによって注入口を設け、真空排気後に注入口に液晶を付けた後に大気圧に戻す従来の注入方式でも同様な効果が期待できる。

## 【符号の説明】

## 【0077】

40

L P N … 液晶表示パネル A R … アレイ基板 C T … 対向基板 L Q … 液晶層

A C T … アクティブエリア P X … 画素

G … ゲート線 C … 補助容量線 S … ソース線 S W … スイッチング素子

P E … 画素電極 C E … 対向電極

C F … カラーフィルタ層 O L … 重疊部 C H … コンタクトホール

1 3 … オーバーコート層 1 3 C … 凹部 T H … 貫通孔

【図1】

図1

【図2】

図2

【図3】

図3

【図7】

【 図 8 】

【 図 9 】

【図12】

【図10】

【図 1 1】

【図13】

---

フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 真鍋 敦行

埼玉県深谷市幡羅町一丁目9番地2 東芝モバイルディスプレイ株式会社内

(72)発明者 庄原 潔

埼玉県深谷市幡羅町一丁目9番地2 東芝モバイルディスプレイ株式会社内

(72)発明者 井上 浩治

埼玉県深谷市幡羅町一丁目9番地2 東芝モバイルディスプレイ株式会社内

(72)発明者 濱元 美奈子

埼玉県深谷市幡羅町一丁目9番地2 東芝モバイルディスプレイ株式会社内

F ターム(参考) 2H092 GA29 GA50 JA24 JB58 JB64 KA04 KA12 KB25 KB26 MA15

NA27 PA04 PA08

2H189 DA07 DA72 FA23 HA12 LA10 LA14

2H191 FA02Y GA19 LA13 LA19

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2011180259A</a>                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2011-09-15 |

| 申请号            | JP2010042540                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2010-02-26 |

| [标]申请(专利权)人(译) | 东芝移动显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 东芝移动显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 真鍋敦行<br>庄原潔<br>井上浩治<br>濱元美奈子                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 真鍋 敦行<br>庄原潔<br>井上 浩治<br>濱元 美奈子                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G02F1/1368 G02F1/1335 G02F1/1339                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G02F1/1368 G02F1/1335.505 G02F1/1339.500                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA29 2H092/GA50 2H092/JA24 2H092/JB58 2H092/JB64 2H092/KA04 2H092/KA12 2H092/KB25 2H092/KB26 2H092/MA15 2H092/NA27 2H092/PA04 2H092/PA08 2H189/DA07 2H189/DA72 2H189/FA23 2H189/HA12 2H189/LA10 2H189/LA14 2H191/FA02Y 2H191/GA19 2H191/LA13 2H191/LA19 2H192/AA24 2H192/CB02 2H192/DA12 2H192/DA42 2H192/EA02 2H192/EA32 2H192/EA42 2H192/EA56 2H192/FA73 2H192/FB22 2H192/GD25 2H192/HA45 2H291/FA02Y 2H291/GA19 2H291/LA13 2H291/LA19 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚<br>河野直树<br>冈田隆<br>山下 元                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

本发明的目的是提供一种能够抑制生产率下降的液晶显示装置及其制造方法。第一开关元件和第二开关元件，布置在第一开关元件上的第一滤色器层以及布置在第二开关元件上的第一滤色器层的一部分。形成重叠的重叠部分的第二滤色器层，覆盖第一滤色器层和第二滤色器层并具有在重叠部分的正上方和第一滤色器层上方形成的凹部的绝缘膜。布置在绝缘膜上的第一像素电极被电连接到第一开关元件，并且被电连接到布置在绝缘膜上的第二开关元件，该第二膜位于第二滤色器层上方。与第一基板相对设置的第二基板，以及将第一基板和第二基板结合在一起的闭环密封材料。液晶显示装置。[选择图]图3