(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-3896

(P2017-3896A)

(43) 公開日 平成29年1月5日(2017.1.5)

(51) Int.Cl.

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1343

G02F 1/1368

テーマコード(参考)

2H092

2H192

審査請求 未請求 請求項の数 6 O L (全 14 頁)

(21) 出願番号

特願2015-119929 (P2015-119929)

(22) 出願日

平成27年6月15日 (2015.6.15)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

100088672

弁理士 吉竹 英俊

100088845

弁理士 有田 貴弘

齊藤 嘉也

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 南 昭宏

東京都千代田区丸の内二丁目7番3号

三菱電機株式会社内

F ターム(参考) 2H092 GA14 JA24 JB11 JB52 JB53

JB54 NA14 PA08 PA09 QA06

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】 E S D が与えられた場合でも、ドライバー回路に流れる電流を小さくできる液晶表示装置を提供する。

【解決手段】 カラーフィルタ基板は、第1の透明基板の一方の主面上に配設された透明導電膜と、透明導電膜上に配設された複数の着色層と、複数の着色層間に遮光し、連続して設けられた導電性を有する第1および第2の遮光層とを備え、薄膜トランジスタ基板は、第2の透明基板の一方の主面上の複数の薄膜トランジスタが配設された領域で規定される画像表示領域の外側に配置され、液晶を駆動する電子回路を備え、第1の遮光層は、第2の遮光層よりも低い抵抗値を有して接地電位に電気的に接続され、薄膜トランジスタ基板とカラーフィルタ基板とを対向配置した場合に、第2の遮光層は、少なくとも平面視的に電子回路に近い側に配置される。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

複数の薄膜トランジスタが配設された薄膜トランジスタ基板と、

前記薄膜トランジスタ基板に対向配置されたカラーフィルタ基板と、

前記薄膜トランジスタ基板と前記カラーフィルタ基板との間に挟持された液晶層と、を備え、

前記薄膜トランジスタ基板および前記カラーフィルタ基板に対して平行に発生させる電界により液晶を駆動する横電界方式の液晶表示装置であって、

前記カラーフィルタ基板は、

第1の透明基板の一方の主面上に配設された透明導電膜と、

前記透明導電膜上に配設された複数の着色層と、

前記複数の着色層間を遮光し、連続して設けられた導電性を有する第1および第2の遮光層と、を備え、

前記薄膜トランジスタ基板は、

第2の透明基板の一方の主面上の前記複数の薄膜トランジスタが配設された領域で規定される画像表示領域の外側に配置され、前記液晶を駆動する電子回路を備え、

前記第1の遮光層は、前記第2の遮光層よりも低い抵抗値を有して接地電位に電気的に接続され、

前記薄膜トランジスタ基板と前記カラーフィルタ基板とを対向配置した場合に、前記第2の遮光層は、少なくとも平面視的に前記電子回路に近い側に配置される、液晶表示装置。

## 【請求項 2】

前記薄膜トランジスタ基板は、

前記第2の透明基板上の前記画像表示領域と前記電子回路との間の領域に設けられた絶縁層と、

前記絶縁層上に設けられたシールド層と、をさらに備え、

前記絶縁層および前記シールド層は、少なくとも前記電子回路の最大寸法よりも長い部分を有し、

前記シールド層は接地電位に電気的に接続される、請求項1記載の液晶表示装置。

## 【請求項 3】

前記透明導電膜は、接地電位に電気的に接続される、請求項1または請求項2記載の液晶表示装置。

## 【請求項 4】

前記第1の遮光層は、

前記電子回路から最も遠い部分において接地電位に電気的に接続される領域を有する、請求項3記載の液晶表示装置。

## 【請求項 5】

前記シールド層は、導電性テープを介して接地電位に電気的に接続される、請求項2記載の液晶表示装置。

## 【請求項 6】

前記第1の遮光層および前記透明導電膜は、導電性テープを介して接地電位に電気的に接続される、請求項3記載の液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は液晶表示装置に関し、特に、横電界方式の液晶表示装置に関する。

## 【背景技術】

## 【0002】

液晶表示装置の中には、液晶駆動用のドライバー回路などの静電気に敏感な電子回路が含まれているため、静電気放電(ESD)に対する保護が重要な検討事項となっている。

10

20

30

40

50

## 【0003】

近年、液晶表示装置として、IPS (In-Plane Switching) 方式のような横電界方式の液晶表示装置が脚光を浴びている (IPS は登録商標)。この方式は、液晶に印加する電解の方向を基板面に対しほぼ平行とする方式であり、TN (Twisted Nematic) 方式などと比較して広視野角を得ることができるといった利点がある。この方式では、カラーフィルタ基板側に液晶を駆動する電極 (対向電極) を設けないのが一般的である。そのため、液晶表示装置外部からカラーフィルタ基板に対して ESD が与えられると、カラーフィルタ基板には電極層が設けられていないので、カラーフィルタ基板の外側表面が帯電し、それによって画素電極との間で縦電界 (基板面に対して垂直な電界) を作るため、液晶分子が傾いて表示に影響を及ぼす可能性がある。

10

## 【0004】

この静電気対策として、特許文献 1 の例えば図 2 に示すように、カラーフィルタ基板における液晶層と反対側の表面にシールド層として透明導電膜を設け、透明導電膜を導電性テープを介して接地する方式が提案されている。このような構成を採ることで、外部から静電気が侵入して透明導電膜に静電気がチャージされても、蓄積された電荷は導電性テープを介して逃がすことができる。

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献 1】特開 2008 - 203448 号公報

20

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、上記透明導電膜は、薄膜トランジスタ (TFT : Thin Film Transistor) 基板上のソース配線との間で大きな容量を形成するため、外部から ESD が与えられた際に、カップリングによってソース配線への ESD 電流のルートを形成することがある。その結果、ESD 電流がソース配線を伝わってドライバー回路に流れ込み、回路の破壊が発生する可能性がある。特に、フレームを有さない液晶表示装置では、透明導電膜を導電性テープ、銀ペーストなどで接地電位に接続 (グランド接続) することになるが、導電性テープ等を接続できる場所に制限があって接続状態が不十分となる場合は、電流をグランドに逃がし切れずにドライバー回路に大きな電流が流れる可能性がある。

30

## 【0007】

本発明は上記のような問題を解決するためになされたものであり、ESD が与えられた場合でも、ドライバー回路に流れる電流を小さくできる液晶表示装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0008】

本発明に係る液晶表示装置は、複数の薄膜トランジスタが配設された薄膜トランジスタ基板と、前記薄膜トランジスタ基板に対向配置されたカラーフィルタ基板と、前記薄膜トランジスタ基板と前記カラーフィルタ基板との間に挟持された液晶層と、を備え、前記薄膜トランジスタ基板および前記カラーフィルタ基板に対して平行に発生させる電界により液晶を駆動する横電界方式の液晶表示装置であって、前記カラーフィルタ基板は、第 1 の透明基板の一方の主面上に配設された透明導電膜と、前記透明導電膜上に配設された複数の着色層と、前記複数の着色層間を遮光し、連続して設けられた導電性を有する第 1 および第 2 の遮光層と、を備え、前記薄膜トランジスタ基板は、第 2 の透明基板の一方の主面上の前記複数の薄膜トランジスタが配設された領域で規定される画像表示領域の外側に配置され、前記液晶を駆動する電子回路を備え、前記第 1 の遮光層は、前記第 2 の遮光層よりも低い抵抗値を有して接地電位に電気的に接続され、前記薄膜トランジスタ基板と前記カラーフィルタ基板とを対向配置した場合に、前記第 2 の遮光層は、少なくとも平面視的に前記電子回路に近い側に配置される。

40

50

## 【発明の効果】

## 【0009】

本発明に係る液晶表示装置によれば、第2の遮光層が、少なくとも平面視的に電子回路に近い側に配置されることで、ESD電流が電子回路に流れ込むことを抑制できる。

## 【図面の簡単な説明】

## 【0010】

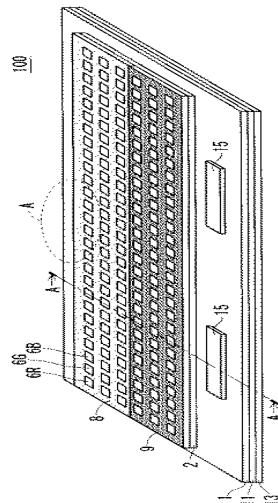

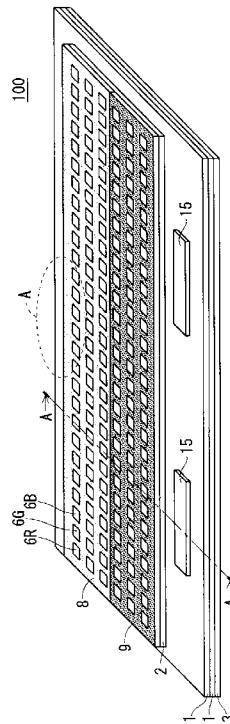

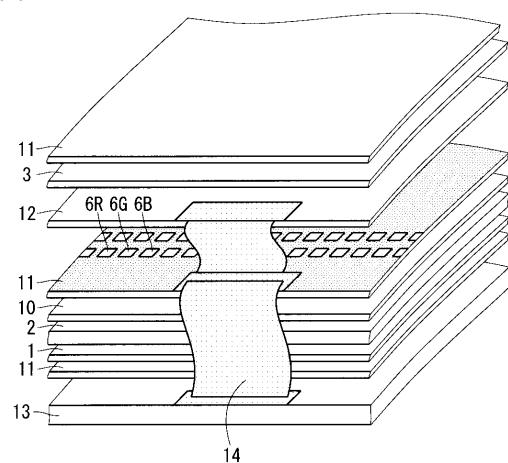

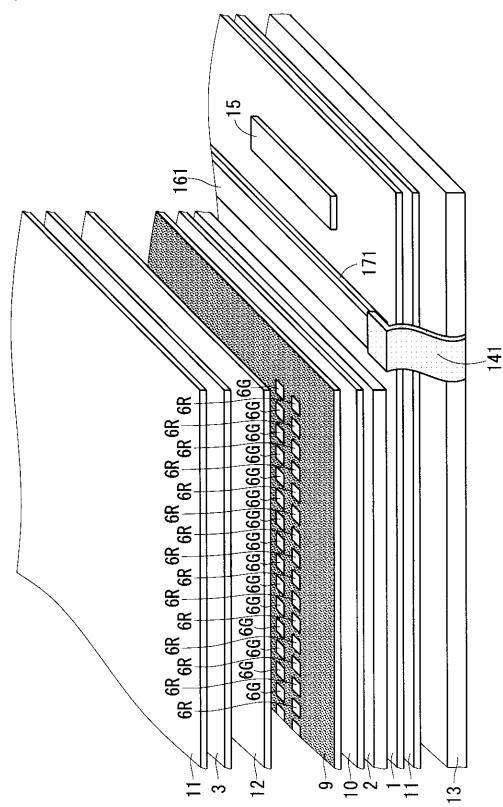

【図1】本発明に係る実施の形態1の液晶表示装置の特徴部の構成を示す斜視図である。

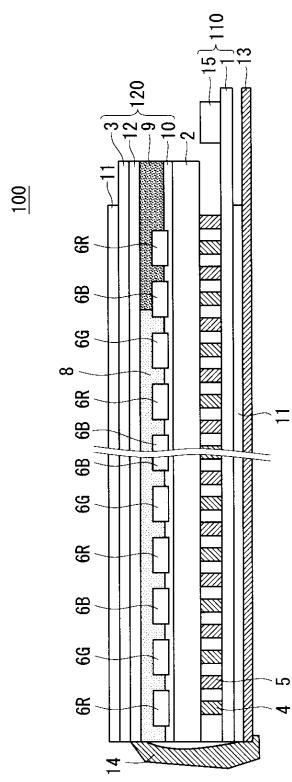

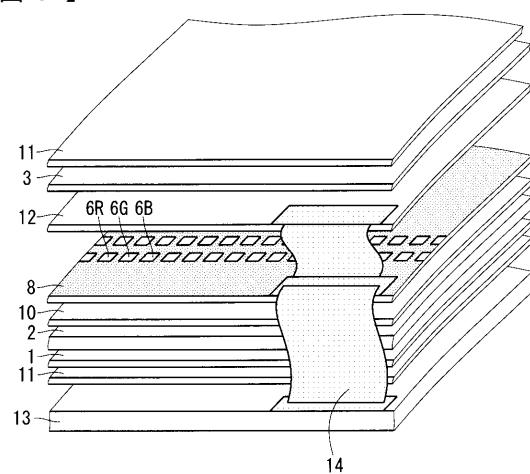

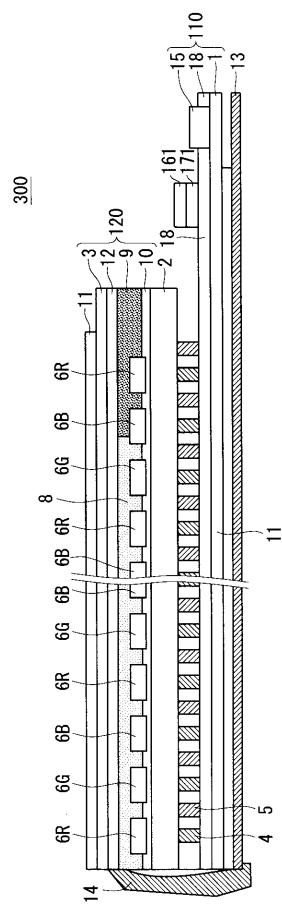

【図2】本発明に係る実施の形態1の液晶表示装置の断面構成を示す図である。

【図3】本発明に係る実施の形態1の液晶表示装置のグランド接続部の構成を示す斜視図である。

10

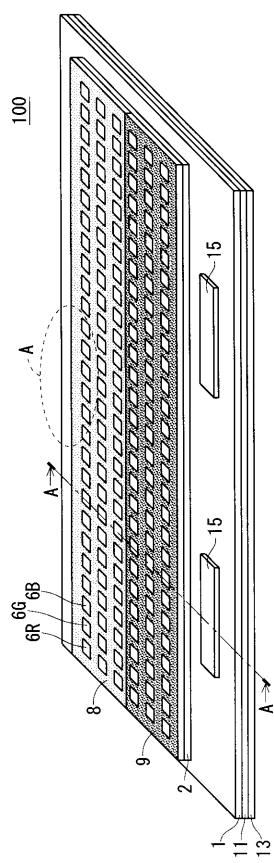

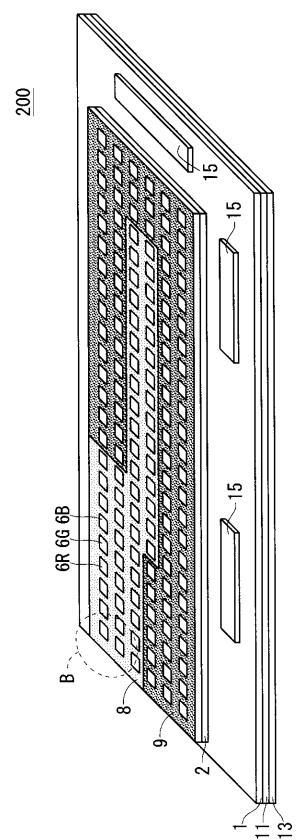

【図4】本発明に係る実施の形態2の液晶表示装置の特徴部の構成を示す斜視図である。

【図5】本発明に係る実施の形態2の液晶表示装置のグランド接続部の構成を示す斜視図である。

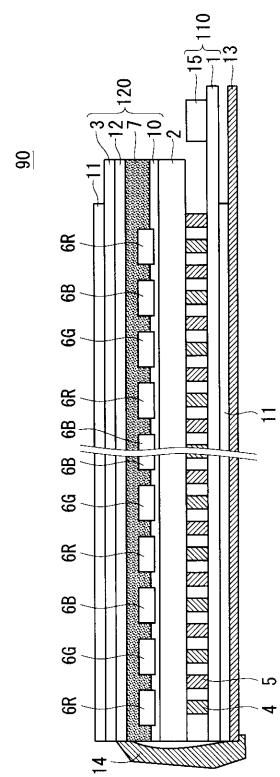

【図6】本発明との比較対象としての従来の液晶表示装置の断面構成を示す図である。

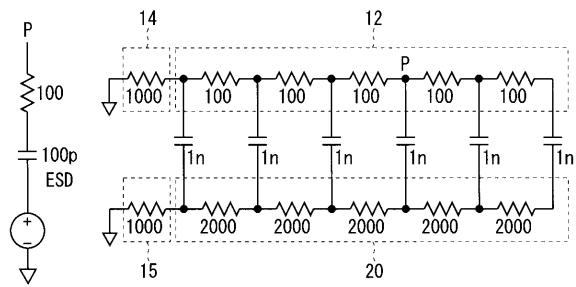

【図7】従来の液晶表示装置をモデルとした場合のシミュレーション回路図である。

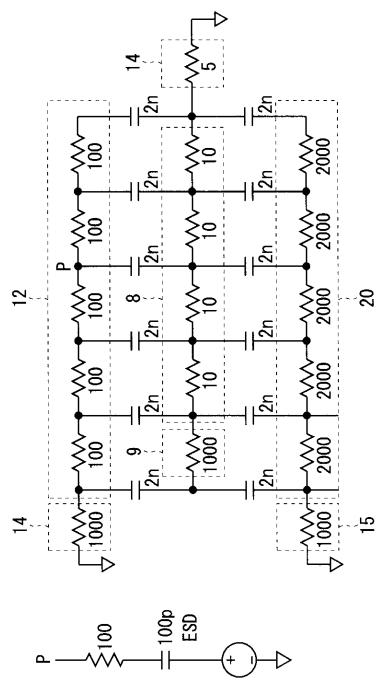

【図8】本発明に係る液晶表示装置をモデルとした場合のシミュレーション回路図である。

。

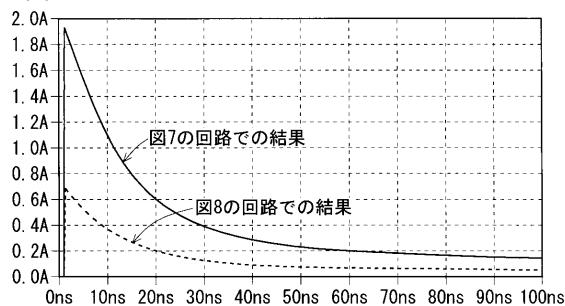

【図9】ドライバー回路に流れる電流のシミュレーション結果を示す図である。

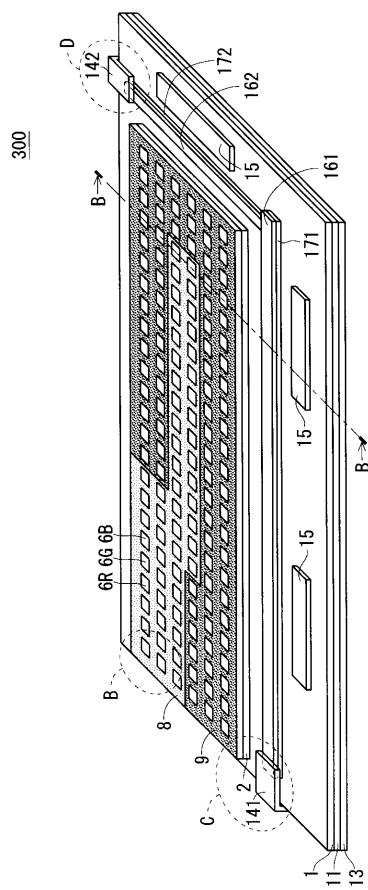

【図10】本発明に係る実施の形態3の液晶表示装置の特徴部の構成を示す斜視図である。

20

【図11】本発明に係る実施の形態3の液晶表示装置のシールド層のグランド接続部の構成を示す斜視図である。

【図12】本発明に係る実施の形態3の液晶表示装置の断面構成を示す図である。

## 【発明を実施するための形態】

## 【0011】

## &lt;実施の形態1&gt;

図1は、本発明に係る実施の形態1の液晶表示装置100の特徴部の構成を示す斜視図であり、カラーフィルタ基板側にシールド層として設けた透明導電膜よりも下側（液晶層側）の構成を示している。また、図2には、図1におけるA-A線での断面構成を示しているが、これにはシールド層として設けた透明導電膜も含めた構成を示している。

30

## 【0012】

図1に示すように液晶表示装置100においては、矩形のTFTガラス基板1の一方の長辺側のみにドライバー回路15（電子回路）が実装された構成となっている。そして、TFTガラス基板1上の複数のTFTが配設された領域で規定される画像表示領域には液晶層2が設けられ、液晶層2上には高抵抗ブラックマトリクス層9（第2の遮光層）と、低抵抗ブラックマトリクス層8（第1の遮光層）が、画像表示領域を二分するように設けられている。すなわち、液晶層2上の領域を短辺の長さで二分したうちのドライバー回路15側の領域には高抵抗ブラックマトリクス層9を配設し、ドライバー回路15側とは反対の領域には低抵抗ブラックマトリクス層8を配設している。

40

## 【0013】

ブラックマトリクスは、R（赤）、G（緑）およびB（青）の着色層間に配設される遮光層であり、高抵抗ブラックマトリクス層9および低抵抗ブラックマトリクス層8によって区画された領域にはカラーフィルタを構成するR、G、Bのそれぞれの着色層6R、6G、6Bが設けられ、R、G、Bの着色層の配列を形成している。

## 【0014】

次に、図2を用いて液晶表示装置100の断面構成について説明する。図2に示すように液晶表示装置100は、液晶を制御するスイッチング素子として、複数のTFTがマトリクス状に配列されてTFTアレイを構成するTFT基板110と、TFT基板110に對して対向して配置され、画像を表示する画像表示領域を有するカラーフィルタ基板120とを有し、TFT基板110とカラーフィルタ基板120との間の間隙には、少なくと

50

も画像表示領域に対応する領域に液晶層2が封入されている。

【0015】

TFT基板110は、TFTガラス基板1(第2の透明基板)のカラーフィルタ基板120と対向する一方の主面上に、画素電極4および対向電極5を有しており、画素電極4と対向電極5との間で発生する横電界(基板面に対して平行な電界)により液晶を駆動する。なお、TFT基板110の一方の主面上には、マトリクス状に配設された複数のTFTと、TFTに信号を供給する配線である複数のゲート配線およびソース配線と、これらの配線に接続されTFTを構成するゲート電極、ソース電極およびドレイン電極なども設けられるが、図2では便宜的に省略している。また、画素電極4および対向電極5は液晶を配向させる配向膜で覆われているが便宜的に図示は省略している。

10

【0016】

また、TFTガラス基板1の画素電極4等が設けられた側とは反対側の主面上には、少なくとも画像表示領域に対応する領域に偏光板11が配設され、偏光板11の外側には、導電体のリフレーム13が配設されている。

【0017】

カラーフィルタ基板120は、カラーフィルタガラス基板3(第1の透明基板)の一方の主面上に配設されたITO(Indium Tin Oxide)などで構成される透明導電膜12と、透明導電膜12上に配設されたR、G、Bのそれぞれの着色層6R、6G、6Bが設けられ、着色層間を遮光する高抵抗ブラックマトリクス層9および低抵抗ブラックマトリクス層8を有している。

20

【0018】

着色層6R、6Gおよび6Bは、レジスト材などの樹脂中に、それぞれ赤、緑および青の顔料などを分散して構成され、赤、緑、青などの特定の波長範囲の光を選択的に透過する。

【0019】

ブラックマトリクス層は、レジスト材などの樹脂中にクロム、ニッケル、チタン、カーボンなどの導電性材料の粒子を分散させた樹脂系の材料で構成され、導電性を有しており、高抵抗ブラックマトリクス層9と低抵抗ブラックマトリクス層8とでは、これらの導電性材料の比率を変えることで、抵抗値が異なった層となっている。すなわち、導電性材料の量を多くすれば抵抗値がより低くなり、導電性材料の量を少なくすれば抵抗値がより高くなる。

30

【0020】

着色層6R、6G、6Bと、高抵抗ブラックマトリクス層9および低抵抗ブラックマトリクス層8を覆うように透明樹脂で構成されるオーバーコート膜10が設けられている。なお、オーバーコート膜10上の画像表示領域に対応する領域には、液晶を配向させる配向膜が設けられているが便宜的に図示は省略している。

【0021】

また、カラーフィルタガラス基板3のカラーフィルタ等が設けられた側とは反対側の主面上には、少なくとも画像表示領域に対応する領域に偏光板11が配設されている。

【0022】

図3は、液晶表示装置100において、低抵抗ブラックマトリクス層8を導電性テープ14を用いて接地電位(グランド)となっているリフレーム13に電気的に接続した構成を示す斜視図である。なお、導電性テープ14は、低抵抗ブラックマトリクス層8に加えて透明導電膜12にも接続されており、低抵抗ブラックマトリクス層8および透明導電膜12は、接地電位に電気的に接続されることとなる。導電性テープ14を用いることで、電気的な接続を簡便に実現できる。導電性テープ14としては、アルミニウムなどを用いることができる。なお、図3においては液晶表示装置100の導電性テープ14が接続される領域の近傍だけを示している。

40

【0023】

ここで、液晶表示装置100においては、外部からESDが与えられた場合に、図1に

50

示す低抵抗ブラックマトリクス層 8 の領域 A、すなわち何れのドライバー回路 15 から最も遠い領域の低抵抗ブラックマトリクス層 8 に接地電位との接続部を設けることで、何れのドライバー回路 15 から最も遠い領域に ESD 電流を集中させることができ、ドライバー回路 15 に流れ込む ESD 電流を抑制することができる。

【0024】

また、透明導電膜 12 もグランド接続されているので、ドライバー回路 15 に流れ込む ESD 電流の抑制に寄与する。

【0025】

なお、高抵抗ブラックマトリクス層 9 および低抵抗ブラックマトリクス層 8 の配置については、配置領域を完全に分離するのではなく、配置頻度を変えることで抵抗分布を形成するようにしても良い。例えば、ドライバー回路 15 側の領域には比較的多くの高抵抗ブラックマトリクス層 9 を配置し、低抵抗ブラックマトリクス層 8 はそれよりも少なく配置し、ドライバー回路 15 側とは反対の領域には比較的多くの低抵抗ブラックマトリクス層 8 を配置し、高抵抗ブラックマトリクス層 9 はそれよりも少なく配置することで、抵抗分布を形成しても良い。

10

【0026】

<実施の形態 2>

図 4 は、本発明に係る実施の形態 2 の液晶表示装置 200 の特徴部の構成を示す斜視図であり、カラーフィルタ基板側にシールド層として設けた透明導電膜よりも下側（液晶層側）の構成を示している。

20

【0027】

図 4 に示すように液晶表示装置 200 においては、矩形の TFT ガラス基板 1 の直交する二辺に沿ってドライバー回路 15 が実装された構成となっている。そして、TFT ガラス基板 1 上の画像表示領域には液晶層 2 が設けられ、液晶層 2 上には画像表示領域の中央部に矩形の低抵抗ブラックマトリクス層 8 が配設され、ドライバー回路 15 が実装された側の TFT ガラス基板 1 の直交する二辺がなす角部とは対角位置にある画像表示領域の角部にも低抵抗ブラックマトリクス層 8 が配設されている。そして、画像表示領域の中央部の低抵抗ブラックマトリクス層 8 を囲むように高抵抗ブラックマトリクス層 9 が配設されている。

30

【0028】

図 5 は、液晶表示装置 200 において、低抵抗ブラックマトリクス層 8 を導電性テープ 14 を用いてリアフレーム 13 に電気的に接続した構成を示す斜視図である。なお、導電性テープ 14 は、低抵抗ブラックマトリクス層 8 に加えて透明導電膜 12 にも接続されており、低抵抗ブラックマトリクス層 8 および透明導電膜 12 は、接地電位に電気的に接続されることとなる。導電性テープ 14 を用いることで、電気的な接続を簡便に実現できる。なお、図 5 においては液晶表示装置 200 の導電性テープ 14 が接続される領域の近傍だけを示している。

【0029】

ここで、液晶表示装置 200 においては、外部から ESD が与えられた場合に、図 4 に示す低抵抗ブラックマトリクス層 8 の領域 B、すなわち何れのドライバー回路 15 から最も遠い領域の低抵抗ブラックマトリクス層 8 に接地電位との接続部を設けることで、何れのドライバー回路 15 から最も遠い領域に ESD 電流を集中させることができ、ドライバー回路 15 に流れ込む ESD 電流を抑制することができる。

40

【0030】

また、透明導電膜 12 もグランド接続されているので、ドライバー回路 15 に流れ込む ESD 電流の抑制に寄与する。

【0031】

なお、以上説明した実施の形態 1 および実施の形態 2 では、TFT ガラス基板 1 の一方の長辺側のみにドライバー回路 15 が実装された構成および、TFT ガラス基板 1 の直交する二辺に沿ってドライバー回路 15 が実装された構成を例示したが、TFT ガラス基板

50

1の三辺に沿ってドライバー回路が実装された構成においても、ドライバー回路が実装された側の液晶層2上には高抵抗ブラックマトリクス層9を配設し、ドライバー回路が実装されていないTFTガラス基板1の残る一辺側に低抵抗ブラックマトリクス層8を配設する構成とすれば良い。当該低抵抗ブラックマトリクス層8を接地電位(グランド)となっているリアフレーム13に電気的に接続することで、ドライバー回路15に流れ込むESD電流を抑制することができる。

【0032】

＜発明の有効性の検証＞

以下、実施の形態1および実施の形態2の有効性についての検証結果を説明する。図6は、比較対象としての従来的な液晶表示装置90の断面構成を示す断面図である。図6に示す液晶表示装置90は、基本的な構成は、図2を用いて説明した液晶表示装置100と同じであるが、透明導電膜12上に配設されたブラックマトリクス層7は、全体に渡って抵抗値が均一な層である。

10

【0033】

図7は、液晶表示装置90をモデルとした場合のシミュレーション回路図であり、TFT基板110上のソース配線等のアレイ配線20を5個の抵抗の直列接続で模擬し、それぞれの抵抗値を2000としている。アレイ配線20の一方端はドライバー回路15を模擬した抵抗値1000の抵抗に接続され、当該抵抗はグランドに接続されている。

20

【0034】

また、アレイ配線20の各配線抵抗はコンデンサを介して透明導電膜12を模擬する5個の抵抗とそれぞれ並列に接続されている。なお、透明導電膜12を模擬する5個の抵抗は、それぞれの抵抗値が100であり、コンデンサのそれぞれの容量値は1nFである。また、透明導電膜12は、導電性テープ14を模擬した抵抗値1000の抵抗に接続され、当該抵抗はグランドに接続されている。このモデルでは、導電性テープ14を介してESD電流がグランドに完全に逃げないような状況を仮定するために、透明導電膜12に接続された導電性テープ14を模擬した抵抗の抵抗値は、透明導電膜12を模擬した抵抗に比べて高くしている。

20

【0035】

そして、ESDとして100pFの静電気が抵抗値100の抵抗を介して、透明導電膜12を模擬する抵抗の接続ノードPに与えられた場合について、100nsecのトランジエント解析を行った。

30

【0036】

図8は、実施の形態1の液晶表示装置100をモデルとした場合のシミュレーション回路図であり、TFT基板110上のソース配線等のアレイ配線20を5個の抵抗の直列接続で模擬し、それぞれの抵抗値を2000としている。アレイ配線20の一方端はドライバー回路15を模擬した抵抗値1000の抵抗に接続され、当該抵抗はグランドに接続されている。そして、透明導電膜12を模擬する5個の抵抗の直列接続とアレイ配線20を模擬する5個の抵抗の直列接続との間には、高抵抗ブラックマトリクス層9を模擬する抵抗値1000の1個の抵抗と、低抵抗ブラックマトリクス層8を模擬する抵抗値10の4個の抵抗との直列接続が設けられている。

40

【0037】

また、アレイ配線20の各配線抵抗は、コンデンサを介して高抵抗ブラックマトリクス層9および低抵抗ブラックマトリクス層8を模擬する5個の抵抗とそれぞれ並列に接続されており、また、高抵抗ブラックマトリクス層9および低抵抗ブラックマトリクス層8を模擬する5個の抵抗は、コンデンサを介して透明導電膜12を模擬する5個の抵抗とそれ並列に接続されている。なお、コンデンサのそれぞれの容量値は2nFである。

【0038】

なお、このモデルでは、透明導電膜12に接続された導電性テープ14を介してESD電流がグランドに完全に逃げないような状況を仮定するために、導電性テープ14を模擬した抵抗の抵抗値は1000とし、透明導電膜12を模擬した抵抗に比べて高くしてい

50

る。一方、低抵抗ブラックマトリクス層8を模擬した4個の抵抗の一方端は導電性テープ14を模擬した抵抗を介してグランドに接続されているが、この抵抗の抵抗値は低抵抗ブラックマトリクス層8の各抵抗値よりも小さい5に設定している。

【0039】

そして、ESDとして100pFの静電気が抵抗値100の抵抗を介して、透明導電膜12を模擬する抵抗の接続ノードPに与えられた場合について、100nsecのトランジエント解析を行った。

【0040】

図9は、図7および図8に示したシミュレーション回路において、透明導電膜12を模擬する抵抗の接続ノードPにESDとして同じ量の静電気を与えた場合のドライバー回路15に流れる電流値のシミュレーション結果を示している。

10

【0041】

図9において横軸に経過時間を示し、縦軸に電流値を示しているが、図8に示したシミュレーション回路でのシミュレーション結果は、100nsec間の全体で図7に示したシミュレーション回路でのシミュレーション結果を下回っており、ESDが与えられ始めてから20nsecまで期間では、特に差が顕著となっている。このように、実施の形態1および実施の形態2の液晶表示装置は、ドライバー回路15に流れ込むESD電流の抑制に有効であることが確認できた。

【0042】

<実施の形態3>

図10は、本発明に係る実施の形態3の液晶表示装置300の特徴部の構成を示す斜視図であり、カラーフィルタ基板側にシールド層として設けた透明導電膜よりも下側（液晶層側）の構成を示している。

20

【0043】

図10に示すように液晶表示装置300においては、矩形のTFTガラス基板1の直交する二辺に沿ってドライバー回路15が実装された構成となっている。そして、TFTガラス基板1上の画像表示領域には液晶層2が設けられ、液晶層2上には画像表示領域の中央部に矩形の低抵抗ブラックマトリクス層8が配設され、ドライバー回路15が実装された側のTFTガラス基板1の直交する二辺がなす角部とは対角位置にある画像表示領域の角部にも低抵抗ブラックマトリクス層8が配設されている。そして、画像表示領域の中央部の低抵抗ブラックマトリクス層8を囲むように高抵抗ブラックマトリクス層9が配設されている。

30

【0044】

なお、図10に示す低抵抗ブラックマトリクス層8の領域B、すなわち何れのドライバー回路15からも最も遠い領域には、領域Bの低抵抗ブラックマトリクス層8を接地電位（グランド）となっているリアフレーム13に電気的に接続する導電性テープ14が設けられている点では、図4に示した液晶表示装置200と同じである。

【0045】

また、TFTガラス基板1上には、ドライバー回路15が実装された側のTFTガラス基板1の直交する二辺とそれぞれ平行するように、画像表示領域とドライバー回路15との間の領域に設けられたストライプ状の絶縁層171および172を有している。絶縁層171および172は直交しており、それぞれの一方端が互いに接触し、それぞれの他方端はTFTガラス基板1の端縁部まで延在している。

40

【0046】

そして、絶縁層171および172の上部には、低抵抗の導電性材料、例えばアルミニウムやモリブデンで構成されるストライプ状のシールド層161および162が設けられている。シールド層161および162は、絶縁層171および172と同様に、それぞれの一方端が互いに接触し、それぞれの他方端はTFTガラス基板1の端縁部まで延在しており、TFTガラス基板1の端縁部の領域Cおよび領域Dにおいて、導電性テープ141および142を介して、グランドとなっているリアフレーム13に電気的に接続される

50

構成となっている。

【0047】

図11は、液晶表示装置300において、シールド層161を導電性テープ141を用いてリアフレーム13に電気的に接続した構成を示す斜視図である。なお、導電性テープ141の代わりに銀ペースト等の導電性材料を使用しても良い。導電性テープを用いる場合は電気的な接続を簡便に実現でき、銀ペーストを用いる場合には、電気的な接続のためのコストを削減できる。

【0048】

なお、図11においては液晶表示装置300の導電性テープ141が接続される領域の近傍だけを示しているが、導電性テープ142が接続される領域においても同様の構成となる。

【0049】

ここで、図10におけるB-B線での断面構成を図12に示す。図12に示されるように、TFTガラス基板1上には、ソース配線等がアレイ配線20として設けられており、絶縁層171はシールド層161がアレイ配線20と電気的に接触しないように（絶縁を保つように）設けられている。これは、絶縁層172とシールド層162においても同じである。なお、TFTガラス基板1上におけるアレイ配線は、実際にはソース配線、ゲート配線などで構成されており、それらは電気的に絶縁されるように構成されているので、図11に示される断面構成よりも複雑な構成となっているが、図12においては簡略化して示している。

【0050】

実施の形態1および2の液晶表示装置100および200では、ESDが与えられる場所がドライバー回路15に近いほど、ドライバー回路15に流れる電流は大きくなる。しかし、図10に示した液晶表示装置300においては、画像表示領域とドライバー回路15との間のTFTガラス基板1上の領域にストライプ状の絶縁層171および172設け、それぞれの上部にシールド層161および162を設けて、シールド層161および162をグランドに接続している。このため、ドライバー回路15の近く、例えば、画像表示領域よりも外側のTFTガラス基板1上の領域にESDが与えられた場合には、シールド層161および162にESD電流が集中し、集中したESD電流をグランドに逃がすことができるので、ドライバー回路15に流れ込むESD電流を小さくすることができる。

【0051】

なお、ドライバー回路15から遠い場所、例えば、低抵抗ブラックマトリクス層8上および高抵抗ブラックマトリクス層9のどこかにESDが与えられた場合には、低抵抗ブラックマトリクス層8の領域B、すなわち何れのドライバー回路15からも最も遠い領域にESD電流を集中させることで、ドライバー回路15に流れ込むESD電流を抑制することができる。

【0052】

なお、上記では、絶縁層171および172、シールド層161および162は、ストライプ状として説明したが、ESD電流を集中させることができるのであればこの形状に限定されず、少なくともドライバー回路15の最大寸法よりも長い部分を有した形状であれば良く、例えば、ドライバー回路15を全包囲または半包囲するような形状としても良い。

【0053】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

【符号の説明】

【0054】

1 TFTガラス基板、2 液晶層、3 カラーフィルタガラス基板、8 低抵抗ブラックマトリクス層、9 高抵抗ブラックマトリクス層、12 透明導電膜、14, 141

， 1 4 2 導電性テープ、 1 5 ドライバー回路、 1 6 1 , 1 6 2 シールド層、 1 7 1 , 1 7 2 絶縁層。

【図1】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

### 【 図 1 1 】

【図12】

---

フロントページの続き

F ターム(参考) 2H192 AA24 BB01 BB31 EA23 EA32 EA43 FB22 FB42 FB81 GA04

|                |                                                                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2017003896A</a>                                                                                                                                                                                               | 公开(公告)日 | 2017-01-05 |

| 申请号            | JP2015119929                                                                                                                                                                                                                | 申请日     | 2015-06-15 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 三菱电机株式会社                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 齊藤 嘉也<br>南 昭宏                                                                                                                                                                                                               |         |            |

| 发明人            | 齊藤 嘉也<br>南 昭宏                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                       |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/JA24 2H092/JB11 2H092/JB52 2H092/JB53 2H092/JB54 2H092/NA14 2H092/PA08 2H092/PA09 2H092/QA06 2H192/AA24 2H192/BB01 2H192/BB31 2H192/EA23 2H192/EA32 2H192/EA43 2H192/FB22 2H192/FB42 2H192/FB81 2H192/GA04 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                   |         |            |

## 摘要(译)

即使当静电给出本发明，提供一种能够减少通过驱动电路中流动的电流的液晶显示装置。一种彩色滤光片基板，设置在第一透明衬底的一个主表面上，多个设置在透明导电膜，多个着色层的着色层构成的透明导电膜从光，以及第一和第二光屏蔽层保护的具有得到的导电连续地设置，该薄膜晶体管基该板被布置在其中，第二透明衬底的一个主表面上的多个薄膜晶体管被设置在由所述区域所限定的图像显示区域外，包括电子电路，用于驱动液晶，第一遮光层电连接具有比第二光屏蔽层的低电阻值到地电位，薄膜虎一个Njisuta基板和相对地放置时，滤色器基板，第二光屏蔽层布置靠近至少所述平面图的电子电路。