(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-169680

(P2015-169680A)

(43) 公開日 平成27年9月28日(2015.9.28)

(51) Int.Cl.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

テーマコード(参考)

2H192

審査請求 未請求 請求項の数 14 O L (全 14 頁)

(21) 出願番号

特願2014-42026 (P2014-42026)

(22) 出願日

平成26年3月4日 (2014.3.4)

(71) 出願人 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 園田 大介

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

(72) 発明者 石垣 利昌

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

(72) 発明者 石崎 剛司

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

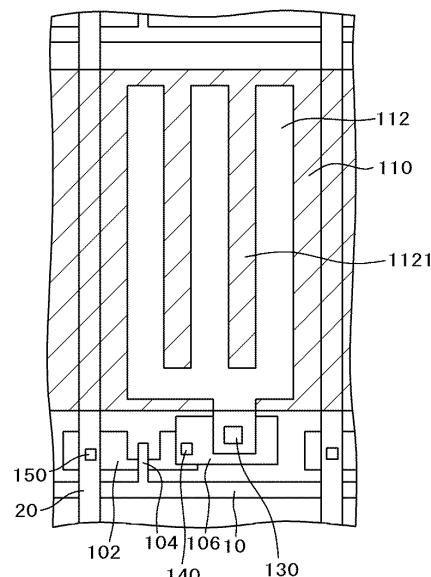

図 1

【課題】画素面積が小さい高精細画面の液晶表示装置において、配線幅を小さくし、かつ、配線からの反射を小さくする。

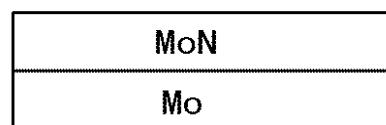

【解決手段】第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成された TFT 基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であって、走査線または映像信号線は、M o の表面の対向基板側にM o Nが形成された構成を有しており、M o Nの膜厚は50nm乃至150nmであることを特徴とする液晶表示装置。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成された TFT 基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、

前記走査線または前記映像信号線は、Mo の表面の前記対向基板側に MoN が形成された構成を有しており、前記 MoN の膜厚は 50 nm 乃至 150 nm であることを特徴とする液晶表示装置。

**【請求項 2】**

前記映像信号線は、Al または Al 合金を主体とし、Al または Al 合金の下層に下層 Mo が形成され、上層に上層 Mo が形成されている構成であり、前記 MoN は前記上層 Mo の上に形成されていることを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 3】**

第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成された TFT 基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、

前記走査線または前記映像信号線は、Ti の表面の前記対向基板側に TiN が形成された構成を有しており、前記 TiN の膜厚は 50 nm 乃至 150 nm であることを特徴とする液晶表示装置。

**【請求項 4】**

前記映像信号線は、Al または Al 合金を主体とし、Al または Al 合金の下層に下層 Ti が形成され、上層に上層 Ti が形成されている構成であり、前記 TiN は前記上層 Ti の上に形成されていることを特徴とする請求項 3 に記載の液晶表示装置。

**【請求項 5】**

第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成された TFT 基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、

前記走査線または前記映像信号線は、Mo の表面の前記対向基板側に ITO が形成された構成を有しており、前記 ITO の膜厚は 30 nm 乃至 100 nm であることを特徴とする液晶表示装置。

**【請求項 6】**

前記 ITO の膜厚は 40 乃至 90 nm であることを特徴とする請求項 5 に記載の液晶表示装置。

**【請求項 7】**

前記映像信号線は、Al または Al 合金を主体とし、Al または Al 合金の下層に下層 Mo が形成され、上層に上層 Mo が形成されている構成であり、前記 ITO は前記上層 Mo の上に形成されていることを特徴とする請求項 5 に記載の液晶表示装置。

**【請求項 8】**

第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成された TFT 基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、

前記走査線または前記映像信号線は、Ti の表面の前記対向基板側に ITO が形成された構成を有しており、前記 ITO の膜厚は 30 nm 乃至 100 nm であることを特徴とする液晶表示装置。

**【請求項 9】**

前記 ITO の膜厚は 40 乃至 90 nm であることを特徴とする請求項 8 に記載の液晶表

10

20

30

40

50

示装置。

【請求項 1 0】

前記映像信号線は、A1またはA1合金を主体とし、A1またはA1合金の下層に下層Tiが形成され、上層に上層Tiが形成されている構成であり、前記ITOは前記上層Tiの上に形成されていることを特徴とする請求項8に記載の液晶表示装置。

【請求項 1 1】

第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であって、10

前記走査線または前記映像信号線は、Moの表面の前記対向基板側にMoNが形成され、前記MoNの表面にITOが形成された構成を有しており、前記MoNの膜厚は50nm乃至150nmであり、前記ITOの膜厚は30nm乃至100nmであることを特徴とする液晶表示装置。

【請求項 1 2】

前記映像信号線は、A1またはA1合金を主体とし、A1またはA1合金の下層に下層Moが形成され、上層に上層Moが形成されている構成であり、前記MoNおよび前記ITOは前記上層Moの上に形成されていることを特徴とする請求項11に記載の液晶表示装置。20

【請求項 1 3】

第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であって、20

前記走査線または前記映像信号線は、Tiの表面の前記対向基板側にTiNが形成され、前記TiNの表面にITOが形成された構成を有しており、前記TiNの膜厚は50nm乃至150nmであり、前記ITOの膜厚は30nm乃至100nmであることを特徴とする液晶表示装置。

【請求項 1 4】

前記映像信号線は、A1またはA1合金を主体とし、A1またはA1合金の下層に下層Tiが形成され、上層に上層Tiが形成されている構成であり、前記TiNおよび前記ITOは前記上層Tiの上に形成されていることを特徴とする請求項13に記載の液晶表示装置。30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示装置に係り、特に高精細画面であっても、輝度およびコントラストの低下の小さい液晶表示装置に関する。

【背景技術】

【0002】

液晶表示装置に使用される液晶表示パネルは、画素電極および薄膜トランジスタ(TFT Thin Film Transistor)等を有する画素がマトリクス状に形成されたTFT基板と、TFT基板に対向して、TFT基板の画素電極と対応する場所にブラックマトリクスやカラーフィルタ等が形成された対向基板が配置され、TFT基板と対向基板の間に液晶が挟持されている。そして液晶分子による光の透過率を画素毎に制御することによって画像を形成している。40

【0003】

液晶表示装置はフラットで軽量であることから、色々な分野で用途が広がっている。携帯電話、DSC(Digital Still Camera)等に使用される小型の液晶表示装置では、画素の大きさを小さくして高精細画面が要求されている。液晶表示装置で50

は、例えば走査線が画面水平方向に延在し、画面垂直方向に配列している。また、映像信号線が画面垂直方向に延在し、画面水平方向に配列している。

#### 【0004】

従来は、このような配線にCrが使用されていた。このCrからの反射を防止するために、特許文献1には、Cr配線の表面に酸化Crを形成することによって配線からの反射を軽減する構成が記載されている。

#### 【0005】

また、TFTを用いた液晶表示装置では、導電層や絶縁層が多層に形成されている。したがって、これらの膜間の密着性が問題となる。また、配線と基板との密着性も問題となる。特許文献2には、配線にMoを使用した場合に、配線と基板、あるいは、配線と配線を覆う絶縁層との密着度を向上させるために、Moの上層および下層にMoNを形成する構成が記載されている。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】特開平9-61842号公報

【特許文献2】特開2001-147424号公報

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

TFT基板においては、例えば横方向に延在し、縦方向に配列した走査線と、縦方向に延在し、横方向に配列した映像信号線で囲まれた領域に画素が形成されている。画面が高精細となるにしたがって、画素の大きさが小さくなり、その分、配線の割合が大きくなつて、液晶表示パネルの透過率が低下する。これを防止するために、配線の幅を細くする必要がある。配線は一般には金属が使用されるので、反射率が大きい。したがって、配線がむき出しになつていると画像のコントラストが低下する。

#### 【0008】

これを防止するために、配線に対応する部分の対向基板にはブラックマトリクスが形成されている。ブラックマトリクスで覆われた部分は光を透過せず、ブラックマトリクスの開口部が画像に寄与する。高精細画面になると、ブラックマトリクスの開口部の面積が相対的に小さくなるので、輝度が低下する。

30

#### 【0009】

このために、高精細画面においては、ブラックマトリクスの幅を十分に大きくとることが出来ない。場合によつては、画面輝度の要請からブラックマトリクスを形成できない場合も存在する。このような場合、配線からの反射が、画像のコントラストに対して大きな影響を与える。したがって、高精細画面においては、配線幅を狭くするとともに、配線からの反射ができるだけ小さくする必要がある。

#### 【0010】

特許文献1に記載のように、配線にCrを用いると、Crは抵抗が大きいために、配線の幅を十分に小さくすることが困難である。また、特許文献1には、Crからの反射を防止するために、Crの表面に酸化Crを形成することが記載されているが、酸化Crは絶縁物であり、例えば、スルーホールを介して下層配線と上層配線を接続する場合には、接触抵抗が問題になる。

40

#### 【0011】

一方、特許文献2には、配線にCrよりは抵抗の小さいMoを使用し、Moと基板あるいは絶縁層との接着強度を向上させるために、Moの表面にMo-Nを形成することが記載されている。しかし、特許文献2の構成は、Mo配線と基板あるいは絶縁層との接着強度を増大させる構成であるから、Mo-Nの厚さは極めて小さく形成され、例えば、20nm程度かそれ以下である。Mo-Nの厚さがこの程度では、十分な反射防止効果は得られない。

50

**【0012】**

本発明の課題は、配線を低抵抗の材料で形成して配線の幅を狭くするとともに、配線からの反射を防止し、画面が高精細となつても、画面の輝度とコントラストの低下を抑えることである。

**【課題を解決するための手段】****【0013】**

本発明は上記問題を克服するものであり、具体的な手段は次のとおりである。

**【0014】**

(1) 第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、前記走査線または前記映像信号線は、Moの表面の前記対向基板側にMoNが形成された構成を有しており、前記MoNの膜厚は50nm乃至150nmであることを特徴とする液晶表示装置。10

**【0015】**

(2) 第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、前記走査線または前記映像信号線は、Tiの表面の前記対向基板側にTiNが形成された構成を有しており、前記TiNの膜厚は50nm乃至150nmであることを特徴とする液晶表示装置。20

**【0016】**

(3) 第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、前記走査線または前記映像信号線は、Moの表面の前記対向基板側にITOが形成された構成を有しており、前記ITOの膜厚は30nm乃至100nmであることを特徴とする液晶表示装置。

**【0017】**

(4) 前記ITOの膜厚は40乃至90nmであることを特徴とする(3)に記載の液晶表示装置。30

**【0018】**

(5) 第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、前記走査線または前記映像信号線は、Tiの表面の前記対向基板側にITOが形成された構成を有しており、前記ITOの膜厚は30nm乃至100nmであることを特徴とする液晶表示装置。

**【0019】**

(6) 前記ITOの膜厚は40乃至90nmであることを特徴とする(5)に記載の液晶表示装置。40

**【0020】**

(7) 第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であつて、前記走査線または前記映像信号線は、Moの表面の前記対向基板側にMoNが形成され、前記MoNの表面上にITOが形成された構成を有しており、前記MoNの膜厚は50nm乃至150nmであり、前記ITOの膜厚は30nm乃至100nmであることを特徴とする液晶表示装置。

**【0021】**

50

20

30

40

50

(8) 第1の方向に延在し、第2の方向に配列した走査線と、第2の方向に延在し、第1の方向に配列した映像信号線で囲まれた領域に画素がマトリクス状に形成されたTFT基板と、ブラックマトリクスが形成された対向基板の間に液晶が挟持された液晶表示装置であって、

前記走査線または前記映像信号線は、Tinの表面の前記対向基板側にTinが形成され、前記Tinの表面にITOが形成された構成を有しており、前記Tinの膜厚は50nm乃至150nmであり、前記ITOの膜厚は30nm乃至100nmであることを特徴とする液晶表示装置。

#### 【発明の効果】

#### 【0022】

本発明によれば、配線抵抗の抵抗を小さくし、配線表面の反射率を低下させることが出来るので、高精細画面においても、輝度の低下を抑制し、かつ、画像のコントラストの低下を防止することが出来る。

#### 【図面の簡単な説明】

#### 【0023】

【図1】TFT基板の画素部の平面図である。

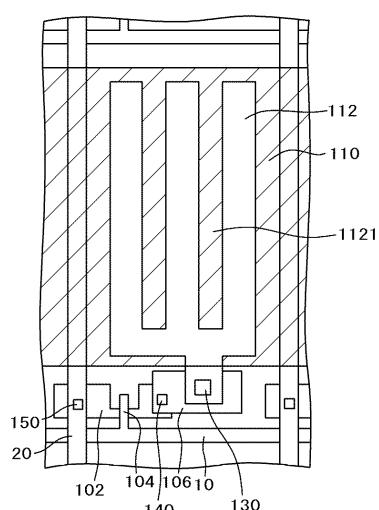

【図2】TFT基板の画素部の断面図である。

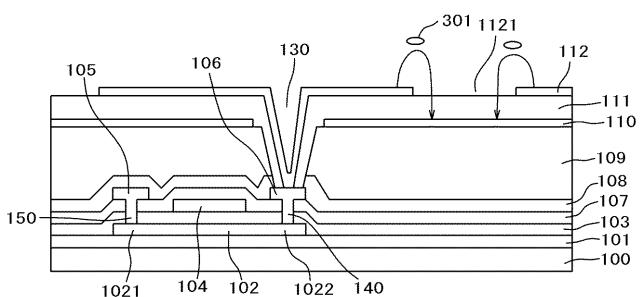

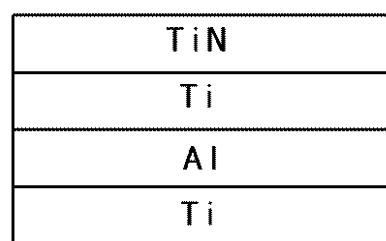

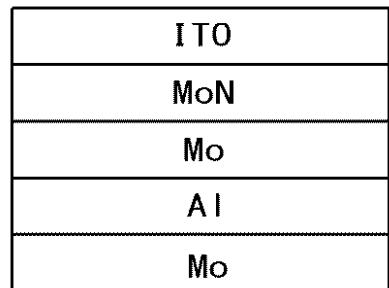

【図3】実施例1の配線構造である。

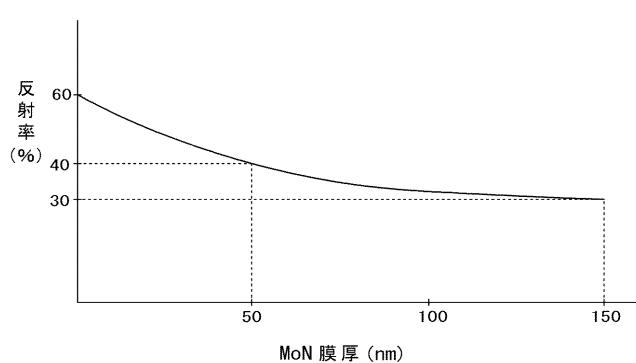

【図4】MONの膜厚と反射率の関係を示すグラフである。

【図5】実施例1他の配線構造である。

【図6】実施例1さらに他の配線構造である。

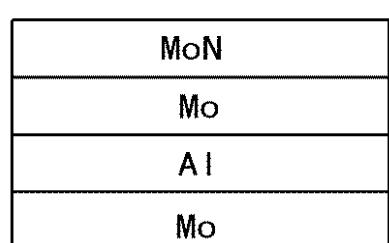

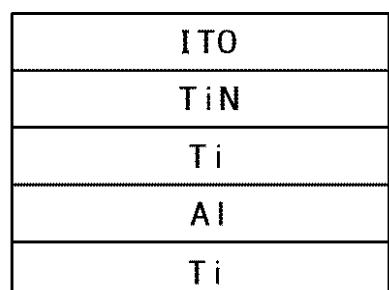

【図7】実施例2の配線構造である。

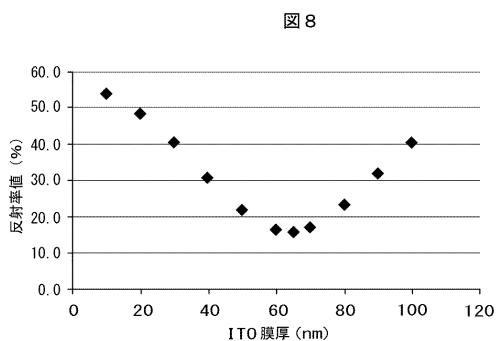

【図8】ITOの膜厚と反射率の関係を示すグラフである。

【図9】実施例2の他の配線構造である。

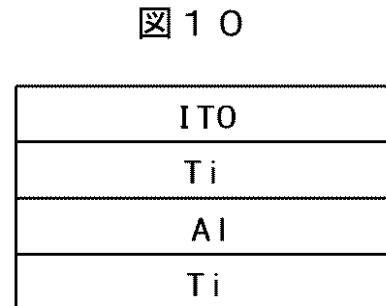

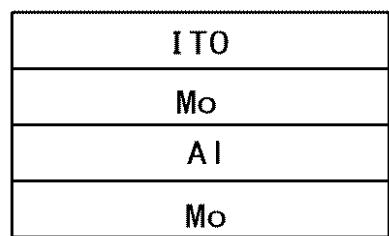

【図10】実施例2のさらに他の配線構造である。

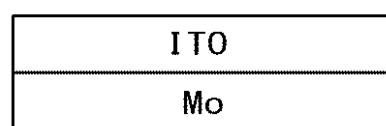

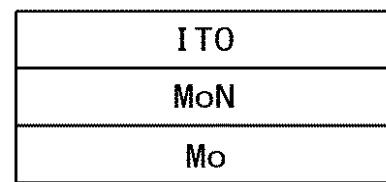

【図11】実施例3の他の配線構造である。

【図12】TFT基板の画素部の断面図である。

【図13】実施例3のさらに他の配線構造である。

#### 【発明を実施するための形態】

#### 【0024】

以下に本発明の内容を実施例によって詳細に説明する。

#### 【実施例1】

#### 【0025】

図1は、IPS方式の液晶表示装置の画素部の平面図である。液晶表示装置は視野角が問題である。IPS方式液晶表示装置は、基板と平行方向の電界によって液晶分子を回転させて画素の透過率を制御するものであり、優れた視野角特性を有している。以下にIPS方式の液晶表示装置を例にとって説明するが、本発明は、IPS方式の液晶表示装置に限らず、他の方式の液晶表示装置にも適用することが出来る。

#### 【0026】

図1において、走査線10が水平方向に延在し、第1のピッチで垂直方向に配列している。映像信号線20が垂直方向に延在して第2のピッチで水平方向に配列している。走査線10と映像信号線20とで囲まれた領域に画素が形成されている。

#### 【0027】

画素の下側にTFTが形成されている。図1におけるTFTは、ゲート電極104が半導体層102の上側に存在するいわゆるトップゲートタイプのTFTである。そして、半導体層102にはpolyl-Siが使用されている。但し、本発明は、ゲート電極104が半導体層102の上側にあるいわゆるボトムゲートの場合にも適用できるし、半導体層がa-Siの場合にも適用することが出来る。

#### 【0028】

図2において、TFTの半導体層102のドレイン1021は、映像信号線とスルーホ

10

20

30

40

50

ール 150 を介して接続している。図 1 におけるドレイン電極は映像信号線 20 が兼ねている。TFT のソース 1022 はスルーホール 140 を介してソース電極 106 と接続している。半導体層 102 の上には、走査線 10 から分岐したゲート電極 104 が存在している。図 1 において、スルーホール 130 を介して画素電極 112 がソース電極 106 と接続している。画素電極 112 は櫛歯状である。

#### 【0029】

画素電極 112 の下層には、図 1 では図示しない第 2 層間絶縁膜を介してコモン電極 110 が平面状に形成されている。図 1 におけるコモン電極 110 は、走査線 10 の延在方向に幅広で、各画素に共通に延在している。画素電極 112 に TFT を介して映像信号が供給されると、図 2 に示すように、画素電極 112 から電気力線が液晶層を介し、画素電極 112 のスリット 1121 を通過して下層に形成されたコモン電極 110 に伸びる。この電気力線の横成分で液晶分子が回転し、画素の光の透過率を制御する。

10

#### 【0030】

図 2 は、図 1 で説明した画素構造の断面図である。図 2 においてガラスで形成された TFT 基板 100 に下地膜 101 が SiN あるいは SiO<sub>2</sub> によって形成されている。下地膜 101 の役割はガラスの不純物が半導体層 102 に侵入することを防止することである。図 2 では、下地膜 101 は 1 層であるが、2 層形成される場合がある。この場合は、下層が SiN 膜、上層が SiO<sub>2</sub> 膜である場合が多い。

20

#### 【0031】

図 2 において、下地膜 101 の上に半導体層 102 が形成されている。半導体層 102 は poly-Si によって形成されている。poly-Si は、最初は CVD によって a-Si を形成し、これをレーザアニールすることによって poly-Si に変換することによって形成される。半導体層 102 の上にゲート絶縁膜 103 を介してゲート電極 104 が形成され、この部分の半導体層 102 が TFT のチャンネル部を形成している。ゲート電極 104 で覆われた部分以外の半導体層 102 には、P あるいは B 等の不純物がドープされ、例えば、半導体層 102 の左側にドレイン 1021 が形成され、右側にソース 1022 が形成される。

20

#### 【0032】

ゲート電極 104 の上には第 1 層間絶縁膜 107 が形成され、映像信号線 20 あるいは映像信号線 20 と同層で形成されるソース電極 106 と、ゲート電極 104 あるいは走査線を絶縁している。図 2 において、半導体層 102 のドレイン 1021 は第 1 層間絶縁膜 107 に形成されたスルーホール 150 を介して映像信号線 20 が兼用するドレイン電極と接続する。また、半導体層 102 のソース 1022 は、第 1 層間絶縁膜 107 に形成されたスルーホール 140 を介してソース電極 106 と接続する。

30

#### 【0033】

第 1 層間絶縁膜 107 の上には無機パッシベーション膜 108 が形成され、TFT、映像信号線等を保護する。無機パッシベーション膜 108 の上には、平坦化膜を兼ねた有機パッシベーション膜 109 が形成されている。有機パッシベーション膜 109 は 1 乃至 3 μm と、厚く形成される。有機パッシベーション膜 109 の上には、図 1 で説明したように、平面状にコモン電極 110 が形成される。コモン電極 110 の上には第 2 層間絶縁膜 111 が形成され、第 2 層間絶縁膜 111 の上には、スリット 1121 を有する櫛歯状の画素電極 112 が形成される。

40

#### 【0034】

画素電極 112 には、ソース電極 106 から無機パッシベーション膜 108 および有機パッシベーション膜 109 に形成されたスルーホール 130 を介して映像信号が供給される。画素電極 112 に映像信号が供給されると図 2 に示すように、電気力線が液晶層およびスリット 1121 を介して下層のコモン電極 110 に形成される。この電界の横成分によって液晶分子 301 が回転し、画素の透過率を制御する。

#### 【0035】

図 2 には示さないが、TFT 基板 100 と対向して対向電極が形成され、TFT 基板と

50

対向電極との間に液晶層が挟持される。対向基板において、TFT基板の画素に対応する部分にはカラーフィルタが形成され、カラーフィルタとカラーフィルタの間にはブラックマトリクスが形成されて、画素間の混色を防止するとともに、バックライトからの不要な光を遮光し、あるいは、外光の反射を防止して画像のコントラストを向上させる。

#### 【0036】

画面が高精細になると、画素の面積が小さくなり、画素内において、画像の形成に寄与する画素電極の相対面積が小さくなる。画像を形成しない画素の周辺部は、ブラックマトリクスによって遮光される。しかし、遮光のために、ブラックマトリクスの幅を大きくすると、ブラックマトリクスの開口部が小さくなり、画素の透過率が低下し、画面の輝度が低下する。

10

#### 【0037】

これを防止するには、ブラックマトリクスの幅を極力小さくするか、場合によってはブラックマトリクスを部分的に省略する必要もある。しかし、走査線や映像信号線は金属で形成されているので、ブラックマトリクスで覆わないと、外光が走査線や映像信号線において反射し、画像のコントラストを低下させる。

#### 【0038】

走査線は、例えば、従来はMoによって形成されていた。Moの反射率は60%程度である。また、映像信号線は、例えば、従来はAlを主体とし、Alの下層(バリア層)および上層(キャップ層)にMoが使用されていた。バリア層あるいはキャップ層の役割は、Alのヒロックが成長して絶縁破壊を生ずるのを防止することである。また、バリア層はAlが半導体層を汚染することを防止する役割も有し、キャップ層はAlの表面にAl<sub>2</sub>O<sub>3</sub>が形成されて、スルーホールにおけるコンタクト抵抗が大きくなることを防止する。

20

#### 【0039】

このように、Moを使用した場合は、反射率が大きく、ブラックマトリクスで遮光出来ない場合は、配線からの反射が問題となる。なお、特許文献1には配線にCrを使用する場合が記載されているが、Crの比抵抗は12.7μcmと、Moの場合の5.07μcmに比較して大きい。したがって、配線の幅を小さくする場合は配線抵抗の問題が生ずる。

30

#### 【0040】

本発明は、例えば、走査線にMoを使用した場合、Mo表面にMoよりも反射率の小さいMoNを形成し、配線からの反射を小さくするものである。これによって、配線部分をブラックマトリクスによって十分遮光できない場合であっても、配線からの反射を防止し、画像のコントラストの低下を防止することが出来る。以下では、金属配線によって画像のコントラストが低下するとして説明するが、これは、ブラックマトリクスによって金属配線が遮光されない場合、あるいは、十分に遮光されない場合のことを意味する。

#### 【0041】

図3は、例えば、走査線をMoNで形成した例である。Moはスパッタリングによって形成するが、所定の厚さ、例えば、100nm乃至200nm、Moを形成したあと、チャンバー内に窒素を導入してスパッタリングを行い、MoNを形成する。なお、明細書においては、窒化MoをMoNで表すが、形成条件によっては、MoNxが形成される場合もあるが、本明細書ではこのような窒化Moも含む。

40

#### 【0042】

このような配線の反射率は、Mo表面に形成されるMoNの厚さに依存する。図4は、Mo表面に形成されたMoNの厚さと反射率の関係を示すグラフで、横軸は、MoNの厚さで、縦軸は反射率である。表面がMoの場合の反射率は60%程度である。MoNを表面に形成すると膜厚の増加とともに反射率が低下する。図4において、50nm程度で反射率は40%程度に低下し、150nmで30%に低下する。

#### 【0043】

一方、MoNはMoに比べて抵抗率が大きいので、MoNの厚さが厚くなるとスルーホ

50

ールにおけるコンタクト抵抗が大きくなる。 $M_oN$ の比抵抗は、 $6\,000\,\mu\text{cm}$ 程度であるから、 $150\,\text{nm}$ の厚さであればコンタクト抵抗に対する影響は殆どない。このように、本発明では、 $M_o$ の表面に形成する $M_oN$ を $50\,\text{nm}$ 乃至 $150\,\text{nm}$ とすることによって、コンタクト抵抗を増大させること無く、配線からの反射を抑制するものである。また、本発明は、配線からの外光の反射を抑制するものであるから、 $M_o$ 配線の対向基板側に $M_oN$ を形成すればよい。

#### 【0044】

なお、特許文献2には、 $M_o$ 配線の表面に $M_oN$ を形成することが記載されているが、特許文献2において、 $M_oN$ を形成する目的は、上層あるいは下層に形成される膜との接着力を向上させることであるから、形成する膜厚は $20\,\text{nm}$ 以下であり、反射防止の効果は殆どない。

10

#### 【0045】

なお、走査線であっても、配線抵抗を小さくするために、 $M_o$ の下層に $A_1$ を形成する場合もあるが、この場合も、以上で説明したと同様に $M_o$ 表面に $M_oN$ を形成することで、同様に配線からの反射を防止することが出来る。

#### 【0046】

映像信号線は、従来は $A_1$ を主体とし、 $A_1$ の下層（バリア層）および上層（キャップ層）に $M_o$ が使用されていた。この場合、キャップ層の $M_o$ の反射によって、画像のコントラストが低下することは同様である。したがって、図5に示すように、この場合も $M_o$ 表面に $M_oN$ を形成することによって、以上で説明した走査線と同様に、映像信号線からの反射を抑制し、画像のコントラストの低下を抑えることが出来る。

20

#### 【0047】

なお、映像信号線においては、 $A_1$ を主体とし、 $A_1$ の下層（バリア層）および上層（キャップ層）に $T_i$ を使用する場合もある。この場合も $T_i$ の表面に $T_iN$ を形成することによって $T_i$ からの反射率を防止することが出来る。 $T_i$ の反射率も $M_o$ の反射率と同様である。また、 $T_iN$ の反射率の膜厚依存性も図4に示す $M_oN$ の反射率の膜厚依存性と同様である。さらに $T_iN$ の比抵抗も $M_oN$ と同様である。

#### 【0048】

したがって、 $A_1$ を主体とし、 $A_1$ の下層（バリア層）および上層（キャップ層）に $T_i$ を使用する場合も、図6に示すように、キャップ層の $T_i$ の表面に $T_iN$ を形成することによって、外光の反射を防止することが出来る。以上で説明したように、この場合の $T_iN$ の膜厚も $50\,\text{nm}$ 乃至 $150\,\text{nm}$ とするのがよい。

30

#### 【実施例2】

#### 【0049】

図7は、走査線に $M_o$ 配線を用いた場合、配線からの反射を防止するために、 $M_o$ 表面にITO(Indium Tin Oxide)を形成するものである。ITOは屈折率が大きいので、ある範囲の膜厚を $M_o$ 表面に形成すると、干渉効果によって反射を抑制することが出来る。

#### 【0050】

図8は、 $M_o$ 表面にITOを形成した場合のITOの膜厚と反射率の関係を示すグラフである。図8において、表面が $M_o$ の場合の反射率は $60\%$ である。 $M_o$ 表面にITOを堆積するにしたがって、反射率が低下し、ITOの膜厚が $60\,\text{nm}$ 程度になると、反射率は $16\%$ 程度にまで低下する。さらにITOの膜厚を大きくすると、反射率は上昇し、 $100\,\text{nm}$ で $40\%$ 程度となる。

40

#### 【0051】

このように、 $M_o$ 表面にITOを所定の範囲形成することによって、反射率低下させることが出来る。図8に示すように、ITOの好適な膜厚は $30\,\text{nm}$ 乃至 $100\,\text{nm}$ であり、この範囲であれば、反射率を $40\%$ 以下とすることが出来る。膜厚のさらに好ましい範囲は $40\,\text{nm}$ 乃至 $90\,\text{nm}$ であり、この範囲であれば、反射率を $30\%$ 以下に抑制することが出来る。ITOの比抵抗は $130\,\mu\text{cm}$ 程度であるから、 $50\,\text{nm}$ 乃至 $100\,\text{nm}$

50

であればスルーホールにおけるコンタクト抵抗への影響は殆どない。

#### 【0052】

この場合のITOもスパッタリングによって形成することが出来る。すなわち、Moをスパッタリングによって形成した後、スパッタリングのターゲットをITOに変えて、所定の膜厚にITOをスパッタリングすればよい。また、走査線であっても、配線抵抗を小さくするために、Moの下層にAlを形成する場合もあるが、この場合も、以上で説明したと同様にMo表面にITOを形成することで、同様に配線からの反射を防止することが出来る。

#### 【0053】

また、映像信号線は、従来はAlを主体とし、Alの下層（バリア層）および上層（キャップ層）にMoが使用されていた。この場合、キャップ層のMoの反射によって、画像のコントラストが低下することは同様である。図9は、本発明による映像信号線の構成であり、Moで形成されたキャップ層の上にITO膜が形成されている。図9の構成においても、図7において説明したと同様に、Moからの反射を抑制することが出来る。この場合のITO膜の膜厚の好適な範囲は30nm乃至100nmであり、より好ましい範囲は40nm乃至90nmである。10

#### 【0054】

映像信号線の他の構成として、Alを主体とし、Alの下層（バリア層）および上層（キャップ層）にTiを使用する場合がある。この場合もキャップ層として使用されるTiの反射率が問題となり、画像のコントラストを低下させる。図10は、この構成の配線に対し、表面のキャップ層にITOを形成することによって、Tiからの反射を低減することが出来る。この場合のITOの好適な膜厚も30nm乃至100nmであり、より好ましい範囲は40nm乃至90nmである。20

#### 【実施例3】

#### 【0055】

図11は、実施例3によるMo配線の反射率を抑制する構成である。図11において、Moの上にMoNを形成し、さらにその上にITOを形成している。ITOの好適な膜厚は、図8に示すように、30nm乃至100nmであり、より好ましい範囲は40nm乃至90nmである。この範囲は下地膜によっては大きな影響を受けない。ITOの下には、MoNが形成されている。MoNの好適な膜厚は実施例1において説明したと同様、50nm乃至150nmである。30

#### 【0056】

本実施例によれば、ITOによる反射率の低減とMoNによる反射率の低減の相乗効果があるので、配線の反射率を大幅に低減することが出来る。一方、スルーホール部分におけるコンタクト抵抗に対しては、MoNの比抵抗が $6000\mu$ で、ITOの比抵抗が $130\mu cm$ であるから、ITOが存在しても、コンタクト抵抗はMoNだけの場合とほぼ同じである。したがって、この場合もスルーホールにおけるコンタクト抵抗は問題ない。。

#### 【0057】

図12は、映像信号線等において、Alを主体とし、Alの下層（バリア層）および上層（キャップ層）にMoを使用した構成の配線について、MoNおよびITOを積層した構成を示す断面図である。Mo1層だけの場合と同様に、キャップ層であるMoの上に、MoNおよびITOを積層して形成することによって、配線による反射を大幅に低下させることが出来る。MoNおよびITOの好適な膜厚は、図11で説明したのと同様である。40

#### 【0058】

図13は、映像信号線等において、Alを主体とし、Alの下層（バリア層）および上層（キャップ層）にTiを使用した構成の配線について、TiNおよびITOを積層した構成を示す断面図である。図11あるいは図12の場合と同様に、キャップ層であるTiの上に、TiNおよびITOを積層して形成することによって、配線による反射を大幅に50

低下させることが出来る。

**【0059】**

ITOおよびTiNの好適な膜厚は、図11で説明したのと同様である。すなわち、ITOの好適な膜厚は30nm乃至100nmであり、より好ましい範囲は40nm乃至90nmである。また、TiNの好適な膜厚は50nm乃至150nmである。この場合のスルーホールにおけるコンタクト抵抗も、TiNの比抵抗が $6000\mu\text{cm}$ 程度で、ITOの比抵抗が $130\mu\text{cm}$ であるから、ITOが存在しても、コンタクト抵抗はTiNだけの場合とほぼ同じである。したがって、この場合もスルーホールにおけるコンタクト抵抗は問題ない。

**【0060】**

以上の説明においては、Moが走査線に使用され、A1を主体とし、A1の下層(バリア層)および上層(キャップ層)にMoを使用した構成、あるいは、A1を主体とし、A1の下層(バリア層)および上層(キャップ層)にTiを使用した構成が映像信号線に使用されるとして説明したが、Moが映像信号線に使用され、A1を主体とし、A1の下層(バリア層)および上層(キャップ層)にMoを使用した構成、あるいは、A1を主体とし、A1の下層(バリア層)および上層(キャップ層)にTiを使用した構成が走査線に使用されることもありうる。この場合も本発明は問題なく適用することが出来る。

**【0061】**

以上の説明では、配線にMoが使用されたとしたが、MoW等の合金の場合も同様にして、本発明を適用することが出来る。このような場合、表面に形成される反射防止膜はMoWNとなる。また、以上の説明において、A1を主体とし、A1の下層(バリア層)および上層(キャップ層)にMoを使用した構成、あるいは、A1を主体とし、A1の下層(バリア層)および上層(キャップ層)にTiを使用した構成を説明したが、この場合も、A1はAisi等の合金が用いられることが一般的であるが、本発明は問題なく適用することが出来る。

**【0062】**

以上の実施例では、反射率を低減するために、配線の最表面にITOを形成する例を示したが、ITOに限らず、ITOに代えて、IZO(Indium Zinc Oxide)、あるいは、IGO(Indium Garium Oxide)を使用することもできる。この場合の適正な膜厚の範囲は、ITOの場合に準じて決めることが出来る。

**【符号の説明】**

**【0063】**

10...走査線、20...映像信号線、100...TFT基板、101...下地膜、102...半導体層、103...ゲート絶縁膜、104...ゲート電極、105...ドレイン電極、106...ソース電極、107...第1層間絶縁膜、108...無機パッシベーション膜、109...有機パッシベーション膜、110...コモン電極、111...第2層間絶縁膜、112...画素電極、130...スルーホール、140...スルーホール、150...スルーホール、301...液晶分子、1021...ドレイン、1022...ソース、1121...スリット

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図6】

図6

【図5】

図5

【図7】

図7

【図 8】

【図 10】

【図 9】

図9

【図 11】

図11

【図 12】

図12

【図 13】

図13

---

フロントページの続き

F ターム(参考) 2H192 AA24 BB13 BB73 CB02 CC32 CC72 EA04 EA22 EA34 GD45

JA33

|                |                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2015169680A</a>                                                                                                                                                                                                        | 公开(公告)日 | 2015-09-28 |

| 申请号            | JP2014042026                                                                                                                                                                                                                         | 申请日     | 2014-03-04 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 園田大介<br>石垣利昌<br>石崎剛司                                                                                                                                                                                                                 |         |            |

| 发明人            | 園田 大介<br>石垣 利昌<br>石崎 剛司                                                                                                                                                                                                              |         |            |

| IPC分类号         | G02F1/1368                                                                                                                                                                                                                           |         |            |

| FI分类号          | G02F1/1368                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H192/AA24 2H192/BB13 2H192/BB73 2H192/CB02 2H192/CC32 2H192/CC72 2H192/EA04 2H192 /EA22 2H192/EA34 2H192/GD45 2H192/JA33                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                            |         |            |

| 摘要(译)          | <p>解决的问题：在像素面积小的高清屏幕的液晶显示装置中，为了减小布线宽度和来自布线的反射。在由在第一方向上延伸并在第二方向上排列的扫描线和在第二方向上延伸并在第一方向上排列的视频信号线围绕的区域中设置像素。在将液晶夹在以矩阵形式形成的TFT基板和其上形成有黑矩阵的对向基板之间的液晶显示装置中，在Mo的表面的对向基板侧设置扫描线或视频信号线。一种具有其中形成有MoN的结构的液晶显示装置，其中，MoN的膜厚度为50nm至150nm。[选型图]图1</p> |         |            |

| (21)出願番号       | 特願2014-42026(P2014-42026)                                                                                                                                                                                                            |         |            |

| (22)出願日        | 平成26年3月4日(2014.3.4)                                                                                                                                                                                                                  |         |            |

| (71)出願人        | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号                                                                                                                                                                                       |         |            |

| (74)代理人        | 110000350<br>ボレール特許業務法人                                                                                                                                                                                                              |         |            |

| (72)発明者        | 園田 大介<br>東京都港区西新橋三丁目7番1号 株式会<br>社ジャパンディスプレイ内                                                                                                                                                                                         |         |            |

| (72)発明者        | 石垣 利昌<br>東京都港区西新橋三丁目7番1号 株式会<br>社ジャパンディスプレイ内                                                                                                                                                                                         |         |            |

| (72)発明者        | 石崎 剛司<br>東京都港区西新橋三丁目7番1号 株式会<br>社ジャパンディスプレイ内                                                                                                                                                                                         |         |            |

| 最終頁に続く         |                                                                                                                                                                                                                                      |         |            |