(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-220910

(P2012-220910A)

(43) 公開日 平成24年11月12日(2012.11.12)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36  | 2 H 1 9 3   |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 5 C 0 0 6   |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20  | 5 C 0 8 0   |

|                             | G09G 3/20  | 6 4 1 E     |

|                             | G09G 3/20  | 6 4 1 C     |

|                             | G02F 1/133 | 5 5 0       |

審査請求 未請求 請求項の数 7 O L (全 27 頁) 最終頁に続く

|           |                            |          |                                               |

|-----------|----------------------------|----------|-----------------------------------------------|

| (21) 出願番号 | 特願2011-89825 (P2011-89825) | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日  | 平成23年4月14日 (2011.4.14)     | (74) 代理人 | 100095728<br>弁理士 上柳 雅善                        |

|           |                            | (74) 代理人 | 100107261<br>弁理士 須澤 修                         |

|           |                            | (74) 代理人 | 100127661<br>弁理士 宮坂 一彦                        |

|           |                            | (72) 発明者 | 小林 淳也<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

最終頁に続く

(54) 【発明の名称】 液晶表示装置及び電子機器

## (57) 【要約】

【課題】領域走査駆動方式とリセット駆動方式とを一体とした駆動方式を実現する。

【解決手段】液晶装置1は、複数の走査線21と、複数のデータ線22と、前記複数のデータ線22と交差する複数の容量線24と、前記複数の走査線21と前記複数のデータ線22との交差に対応して設けられた複数の画素回路23と、走査線駆動回路31と、データ線駆動回路32とを備え、データ線駆動回路32は、第1リセット期間Tr1において第1リセット信号Vr1を出力し、第1画像信号書き期間Twd1において第1画像信号Vd1を出力し、第2リセット期間Tr2において第1リセット信号Vr1と同極性の第2リセット信号Vr2を出力し、第2画像信号書き期間Twd2において第1画像信号Vd1と逆極性の第2画像信号Vd2を出力する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

複数の走査線と、

複数のデータ線と、

前記複数のデータ線と交差する複数の容量線と、

前記複数の走査線と前記複数のデータ線との交差に対応して設けられた複数の画素回路と、

第1リセット期間、第1画像信号書込期間、第2リセット期間、及び第2画像信号書込期間を含む各水平走査期間において、前記第1リセット期間にアクティブとなる第1リセット選択信号、前記第1画像信号書込期間にアクティブとなる第1書込選択信号、前記第2リセット期間にアクティブとなる第2リセット選択信号、及び前記第2画像信号書込期間にアクティブとなる第2書込選択信号を各々生成して、水平走査期間毎に出力先の走査線を順次切り替えながら、互いに異なる4つの前記走査線に対して前記第1リセット選択信号、前記第1書込選択信号、前記第2リセット選択信号、及び前記第2書込選択信号を出力する走査線駆動回路と、

前記第1リセット期間において第1リセット信号を前記複数のデータ線に出力し、前記第1画像信号書込期間において第1画像信号を前記複数のデータ線に出力し、前記第2リセット期間において第2リセット信号を前記複数のデータ線に出力し、前記第2画像信号書込期間において第2画像信号を前記複数のデータ線に出力するデータ線駆動回路と、

を備え、

前記複数の画素回路の各々は、共通電位が印加される共通電極、画素電極、及び前記共通電極と画素電極との間に挟持された液晶を有する液晶素子と、前記画素電極と前記データ線との間に設けられたスイッチング素子と、前記画素電極と前記容量線との間に設けられた保持容量とを有し、

前記データ線駆動回路は、前記共通電位を基準として信号レベルが同極性となるように前記第1リセット信号及び前記第2リセット信号を生成し、前記共通電位を基準として信号レベルが逆極性となるように前記第1画像信号及び前記第2画像信号を生成し、

ある走査線に対して供給される前記第1書込選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第1書込選択信号がアクティブとなった後に、当該走査線に対して供給される前記第2リセット選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第1期間とし、

当該走査線に対して供給される前記第2書込選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第2書込選択信号がアクティブとなった後に、当該走査線に対して供給される前記第1リセット選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第2期間としたとき、

前記共通電位を基準として前記第1リセット信号と前記第1画像信号とが逆極性の場合、前記第1期間は、前記第2期間よりも長く、

前記共通電位を基準として前記第1リセット信号と前記第1画像信号とが同極性の場合、前記第1期間は、前記第2期間よりも短い、

ことを特徴とする液晶表示装置。

## 【請求項 2】

ある走査線に対して供給される前記第1リセット選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第1リセット選択信号がアクティブとなった後に、当該走査線に対して供給される前記第1書込選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第3期間とし、

当該走査線に対して供給される前記第2リセット選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第2リセット選択信号がアクティブとなった後に、当該走査線に対して供給される前記第2書込選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第4期間としたとき、

前記第3期間と、前記第4期間とは、等しい長さである

10

20

30

40

50

ことを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 3】

前記共通電位を基準として前記第 1 リセット信号と前記第 1 画像信号とが逆極性の場合、前記第 1 期間は、前記第 2 期間、前記第 3 期間、及び前記第 4 期間を合計した以上の長さを有し、

前記共通電位を基準として前記第 1 リセット信号と前記第 1 画像信号とが同極性の場合、前記第 2 期間は、前記第 1 期間、前記第 3 期間、及び前記第 4 期間を合計した以上の長さを有する、

ことを特徴とする請求項 1 または 2 に記載の液晶表示装置。

【請求項 4】

前記データ線駆動回路は、前記第 1 リセット信号のレベルと前記第 2 リセット信号のレベルが同じになるように前記第 1 リセット信号及び前記第 2 リセット信号を生成する、

ことを特徴とする請求項 1 乃至 3 のうちいずれか 1 項に記載の液晶表示装置。

【請求項 5】

前記第 1 リセット期間と前記第 1 画像信号書込期間との間には第 1 プリチャージ期間が設けられており、前記第 2 リセット期間と前記第 2 画像信号書込期間との間には第 2 プリチャージ期間が設けられており、

前記走査線駆動回路は、前記第 1 プリチャージ期間及び前記第 1 画像信号書込期間において前記第 1 書込選択信号をアクティブとし、前記第 2 プリチャージ期間及び前記第 2 画像信号書込期間において前記第 2 書込選択信号をアクティブとし、

前記データ線駆動回路は、前記第 1 プリチャージ期間において第 1 プリチャージ信号を前記複数のデータ線に出力し、前記第 2 プリチャージ期間において第 2 プリチャージ信号を前記複数のデータ線に出力する、

ことを特徴とする請求項 1 乃至 4 のうちいずれか 1 項に記載の液晶表示装置。

【請求項 6】

前記データ線駆動回路は、

前記共通電位を基準として前記第 1 リセット信号と前記第 1 画像信号とが逆極性の場合、前記第 1 プリチャージ信号のレベルを前記第 1 リセット信号のレベルから前記共通電位までの範囲に設定し、

前記共通電位を基準として前記第 2 リセット信号と前記第 2 画像信号とが逆極性の場合、前記第 2 プリチャージ信号のレベルを前記第 2 リセット信号のレベルから前記共通電位までの範囲に設定する、

ことを特徴とする請求項 1 乃至 5 のうちいずれか 1 項に記載の液晶表示装置。

【請求項 7】

請求項 1 乃至 6 のうちいずれか 1 項に記載の液晶表示装置を備えた電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、領域走査駆動及びリセット駆動により、液晶装置の表示特性を向上する技術に関する。

【背景技術】

【0002】

従来、液晶装置においては、焼き付きや劣化を防止するため、各画素に対して正極性及び負極性の画像信号を交互に供給する反転駆動方式が一般的に採用されている。

反転駆動方式の一つとして、データ線に印加する電圧の極性を 1 フレーム周期で反転させるフレーム反転駆動方式が存在する。

【0003】

フレーム反転駆動方式では、ある 1 垂直走査期間を対象とした場合、データ線からは、正極性または負極性のいずれか一方の画像信号が、画面の上部に位置する画素から画面の

10

20

30

40

50

下部に位置する画素へと順次供給されるため、画面の上部に位置する画素は、1垂直走査期間のうち多くの期間において、データ線から供給される画像信号と同極性の電位を有するのに対して、画面の下部に位置する画素は、1垂直走査期間のうち多くの期間において、データ線から供給される画像信号とは逆極性の電位を保持する。

すなわち、各画素の画面中での位置により、画素とデータ線との間の電位差が大きく異なり、画素からデータ線に対して発生するリーク電流の方向及びリーク電流の強さが大きく異なることになるため、画面の場所により表示が不均一になるという問題が生じていた。

#### 【0004】

そこで、このような画面の場所による表示の不均一性という問題を解消するために、1垂直走査期間において、同一画面内で一定距離だけ離れた2つの画素に対して、正極性の画像信号と負極性の画像信号とを交互に供給する、領域走査駆動方式が提案されている。

領域走査駆動方式では、表示領域内の正極性の電位を有する画素数と負極性の電位を有する画素数とが、任意のタイミングにおいてほぼ等しくなる。また、データ線に印加される電圧は、1水平走査期間の短い周期内で極性が反転されるため、各画素とデータ線との電位差が、一定値のままで長期間維持されることもない。

このような領域走査駆動方式によって、画素とデータ線との間の電位の関係が、画面の場所により大きく偏った状態が長期間持続されることを防ぐことが可能となるため、画面の場所による表示の不均一性が解消される。

#### 【先行技術文献】

10

#### 【特許文献】

20

#### 【0005】

#### 【特許文献1】特願2004-177930号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

ところで液晶装置の小型化、高精細化が進み、画素ピッチについても狭くなると、互いに隣接する画素間で生じる横電界の影響により、液晶分子が不安定な状態になり、配向不良が生じることがある。

この配向不良の問題を解決するために、ある画素に画像信号を供給する前に、当該画素の液晶に大きな電圧（リセット信号）を印加して、液晶分子を配向不良の状態から正常な状態へと復元するリセット駆動方式が存在する。そして、ある画素に対して正極性の画像信号が供給される前に、当該画素の液晶に正極性のリセット信号を印加し、ある画素に対して負極性の画像信号が供給される前に、当該画素の液晶に負極性のリセット信号を印加する、領域操作駆動方式とリセット駆動方式とを一体とした駆動方式により、焼き付きや表示の不均一を防止しつつ、配向不良についても防止可能となる。

#### 【0007】

30

しかし、このような、領域操作駆動方式とリセット駆動方式とを一体とした駆動方式を採用した場合、各水平走査期間において、正極性及び負極性の画像信号と、正極性及び負極性のリセット信号とがデータ線に出力されるため、データ線の電位は大きく変化する。データ線の電位が大きく変化した場合、各画素が備える容量が接続する容量線と、データ線とは、寄生容量によりカップリングしているため、容量線の電位も変化する。そして、容量線の電位が変化する場合には、各画素が画像信号の指定する階調を正確に表示できなくなる。

#### 【0008】

40

そこで、本発明では、領域走査駆動方式と、リセット駆動方式とを一体とした駆動方式を採用した場合に、データ線の急激な電位変化に伴う容量線の電位変化に起因する表示不具合の問題を低減させることを解決課題とする。

#### 【課題を解決するための手段】

#### 【0009】

50

上述した課題を解決するため、本発明に係る液晶表示装置は、複数の走査線と、複数のデータ線と、前記複数のデータ線と交差する複数の容量線と、前記複数の走査線と前記複数のデータ線との交差に対応して設けられた複数の画素回路と、第1リセット期間、第1画像信号書き込み期間、第2リセット期間、及び第2画像信号書き込み期間を含む各水平走査期間において、前記第1リセット期間にアクティブとなる第1書き込み選択信号、前記第1画像信号書き込み期間にアクティブとなる第1書き込み選択信号、前記第2リセット期間にアクティブとなる第2リセット選択信号、及び前記第2画像信号書き込み期間にアクティブとなる第2書き込み選択信号を各々生成して、水平走査期間毎に出力先の走査線を順次切り替えながら、互いに異なる4つの前記走査線に対して前記第1リセット選択信号、前記第1書き込み選択信号、前記第2リセット選択信号、及び前記第2書き込み選択信号を出力する走査線駆動回路と、前記第1リセット期間において第1リセット信号を前記複数のデータ線に出力し、前記第1画像信号書き込み期間において第1画像信号を前記複数のデータ線に出力し、前記第2リセット期間において第2リセット信号を前記複数のデータ線に出力し、前記第2画像信号書き込み期間において第2画像信号を前記複数のデータ線に出力するデータ線駆動回路と、を備え、前記複数の画素回路の各々は、共通電位が印加される共通電極、画素電極、及び前記共通電極と画素電極との間に挟持された液晶を有する液晶素子と、前記画素電極と前記データ線との間に設けられたスイッチング素子と、前記画素電極と前記容量線との間に設けられた保持容量とを有し、前記データ線駆動回路は、前記共通電位を基準として信号レベルが同極性となるように前記第1リセット信号及び前記第2リセット信号を生成し、前記共通電位を基準として信号レベルが逆極性となるように前記第1画像信号及び前記第2画像信号を生成し、ある走査線に対して供給される前記第1書き込み選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第1書き込み選択信号がアクティブとなった後に、当該走査線に対して供給される前記第2リセット選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第1期間とし、当該走査線に対して供給される前記第2書き込み選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第2書き込み選択信号がアクティブとなった後に、当該走査線に対して供給される前記第1リセット選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第2期間としたとき、前記共通電位を基準として前記第1リセット信号と前記第1画像信号とが逆極性の場合、前記第1期間は、前記第2期間よりも長く、前記共通電位を基準として前記第1リセット信号と前記第1画像信号とが同極性の場合、前記第1期間は、前記第2期間よりも短い、ことを特徴とする。

#### 【0010】

この発明によれば、各水平走査期間において、共通電位を基準として信号レベルが逆極性となるような第1画像信号及び第2画像信号がデータ線に印加して、例えば、画面の上部に正極性の画像信号を書き込み、画面の下部に負極性の画像信号を書き込む領域走査駆動方式を採用するため、表示の不均一性を抑制することが可能となる。さらに、画像信号の印加とは別にリセット信号を印加するリセット駆動方式を採用するので、液晶の配向不良による表示品質の劣化を防止することが可能となる。

#### 【0011】

また、この発明によれば、第1リセット信号及び第2リセット信号を、共通電位を基準として信号レベルが同極性となるように生成する。リセット信号と画像信号とが逆極性となる場合、データ線に出力される信号が、リセット信号及び画像信号の一方から他方へと切り替わる際に、データ線に急峻且つ大きな電位変化が生じることがある。複数のデータ線の各々は、複数の容量線の各々と交差しており、データ線及び容量線は、寄生容量によりカップリングしている。従って、データ線に、急峻且つ大きな電位変化が生じる場合、容量線の電位も変化する。そして、容量線の電位が変化した場合、画素回路の備える保持容量は容量線と接続しているため、画素回路の保持容量を介して、画素電極の電位も変化することになる。この結果、画素回路により表示される階調は、画像信号が指定する階調とは異なる階調となり、表示品質が劣化する。

これに対して、この発明では、第1リセット信号及び第2リセット信号は、第1画像信

10

20

30

40

50

号または第2画像信号のうちいずれか一方と同極性の信号となるため、データ線に生じる急峻且つ大きな電位変化の回数を低減させることができるとなる。この結果、データ線の電位変化に伴い発生する容量線の電位変化に起因する表示不具合が視認される可能性を低減することができる。

【0012】

さらに、この発明によれば、共通電位を基準として第1画像信号と第1リセット信号とが逆極性となる場合には、ある画素回路に対して第1画像信号が供給されてから第2リセット信号が供給されるまでの第1期間が、当該画素回路に対して第2画像信号が供給されてから第1リセット信号が供給されるまでの第2期間に比べて長く設定される。

従って、画面の中で、第1画像信号を保持している画素回路が存在する領域と、第1画像信号とは逆極性の第1リセット信号、第2画像信号、及び第2リセット信号を保持している画素回路が存在する領域とを、ほぼ等しい面積とすることができます。この場合、データ線に印加される電位の1垂直走査期間における平均値が、正極性または負極性の一方に偏ることを防ぐことができる。これにより、画素回路とデータ線と間の電位差の1垂直走査期間における平均値が、画面内の位置により大きく異なることを防止することができ、表示の不均一を防止することが可能となる。

同様に、共通電位を基準として第1画像信号と第1リセット信号とが同極性となる場合、すなわち、第2画像信号と第2リセット信号とが逆極性となる場合には、第2期間が、第1期間に比べて長く設定されるため、データ線に印加される電位が、正極性または負極性の一方に偏ることを防ぐことができ、表示の不均一の問題が解消される。

【0013】

また、上述した液晶表示装置において、ある走査線に対して供給される前記第1リセット選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第1リセット選択信号がアクティブとなった後に、当該走査線に対して供給される前記第1書込選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第3期間とし、当該走査線に対して供給される前記第2リセット選択信号がアクティブとなる水平走査期間が開始される時間から、当該走査線に供給される第2リセット選択信号がアクティブとなった後に、当該走査線に対して供給される前記第2書込選択信号が最初にアクティブとなる水平走査期間が開始される時間までの期間を第4期間としたとき、前記第3期間と、前記第4期間とは、等しい長さであることが好ましい。

この場合には、画素回路が正極性の画像信号に基づいた表示をする際に発生する配向不良と、負極性の画像信号に基づいた表示をする際に発生する配向不良とを等しく防止することができるとなり、表示品質の劣化、及び画面内の位置による表示品質の偏りの発生を防止することが可能となる。

【0014】

また、上述した液晶表示装置において、前記共通電位を基準として前記第1リセット信号と前記第1画像信号とが逆極性の場合、前記第1期間は、前記第2期間、前記第3期間、及び前記第4期間を合計した以上の長さを有し、前記共通電位を基準として前記第1リセット信号と前記第1画像信号とが同極性の場合、前記第2期間は、前記第1期間、前記第3期間、及び前記第4期間を合計した以上の長さを有する、ことが好ましい。

この場合には、共通電位を基準として第1画像信号と第1リセット信号とが逆極性であれば、画面の中で、第1画像信号を保持している画素回路が存在する領域が、第1画像信号とは逆極性の第1リセット信号、第2画像信号、及び第2リセット信号を保持している画素回路が存在する領域以上の面積を有する。よって、第1画像信号のレベルが、共通電位に近い場合であっても、1垂直走査期間においてデータ線に印加される電位が、正極性または負極性の一方に偏ることを防ぐことが可能となる。これにより、画素回路とデータ線との電位差が、画面内の位置により異なることを防止することができ、表示の不均一の問題が解消される。

同様に、共通電位を基準として第1画像信号と第1リセット信号とが同極性となる場合、すなわち、第2画像信号と第2リセット信号とが逆極性となる場合には、画面の中で、

10

20

30

40

50

第2画像信号を保持している画素回路が存在する領域が、第2画像信号とは逆極性の第2リセット信号、第1画像信号、及び第1リセット信号を保持している画素回路が存在する領域以上の面積を有するため、表示の不均一の問題が解消される。

【0015】

また、上述した液晶表示装置において、前記データ線駆動回路は、前記第1リセット信号のレベルと前記第2リセット信号のレベルが同じになるように前記第1リセット信号及び前記第2リセット信号を生成する、ことが好ましい。

この場合には、第1リセット信号と、第2リセット信号とを、同一の信号として生成することが可能となるため、液晶表示装置の構造を簡素化することができる。

【0016】

また、上述した液晶表示装置において、前記第1リセット期間と前記第1画像信号書き込み期間との間には第1プリチャージ期間が設けられており、前記第2リセット期間と前記第2画像信号書き込み期間との間には第2プリチャージ期間が設けられており、前記走査線駆動回路は、前記第1プリチャージ期間及び前記第1画像信号書き込み期間において前記第1書き込み選択信号をアクティブとし、前記第2プリチャージ期間及び前記第2画像信号書き込み期間において前記第2書き込み選択信号をアクティブとし、前記データ線駆動回路は、前記第1プリチャージ期間において第1プリチャージ信号を前記複数のデータ線に出力し、前記第2プリチャージ期間において第2プリチャージ信号を前記複数のデータ線に出力する、ことが好ましい。

この場合、複数のデータ線には、画像信号が出力される前に、プリチャージ信号が出力される。従って、リセット信号の信号レベルと、画像信号の信号レベルとが大きく異なる場合であっても、プリチャージ信号により、複数のデータ線に対する電荷の充電または放電を、画像信号の書き込みに先立って行うことができるため、画像信号の書き込みが容易になる。この結果、各画素回路により表示される階調が、画像信号に指定された階調となる。

【0017】

また、上述した液晶表示装置において、前記データ線駆動回路は、前記共通電位を基準として前記第1リセット信号と前記第1画像信号とが逆極性の場合、前記第1プリチャージ信号のレベルを前記第1リセット信号のレベルから前記共通電位までの範囲に設定し、前記共通電位を基準として前記第2リセット信号と前記第2画像信号とが逆極性の場合、前記第2プリチャージ信号のレベルを前記第2リセット信号のレベルから前記共通電位までの範囲に設定する、ことが好ましい。

この場合、プリチャージ信号の信号レベルが、リセット信号の信号レベルと、画像信号の信号レベルとの間であるため、データ線にリセット信号が出力されてから、画像信号が出力されるまでの、データ線の電位変化を緩やかにでき、データ線の電位変化に伴う容量線の電位変化を抑制し、容量線の電位変化に起因した表示の不具合を防止することが可能となる。

【0018】

次に、本発明に係る電子機器としては、例えば、携帯電話機、パーソナルコンピュータ、あるいは投写型表示装置などが該当する。

【図面の簡単な説明】

【0019】

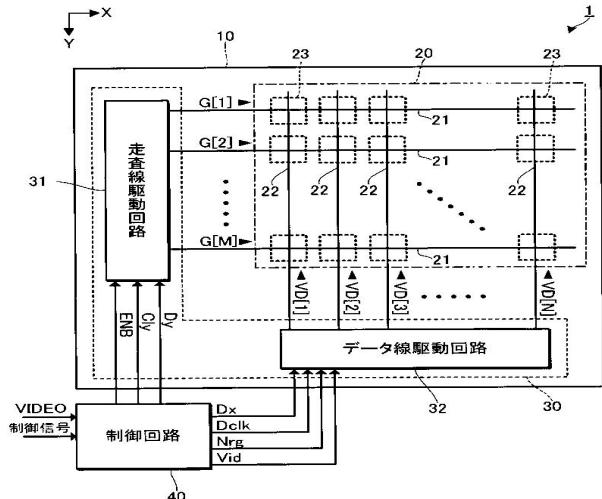

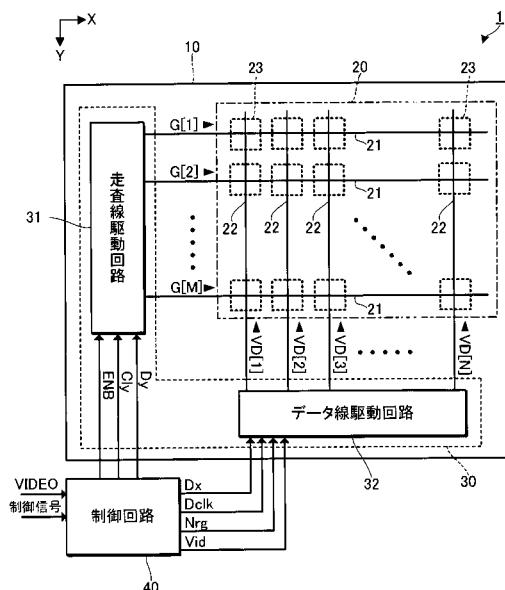

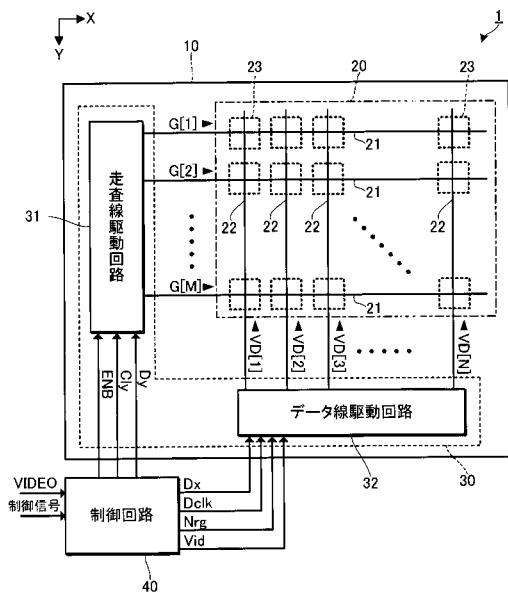

【図1】本発明の実施形態に係る液晶表示装置を示すブロック図である。

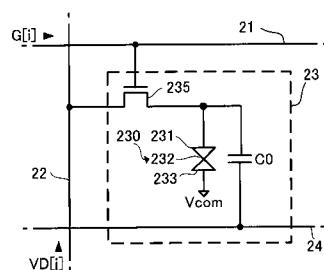

【図2】画素回路を示す回路図である。

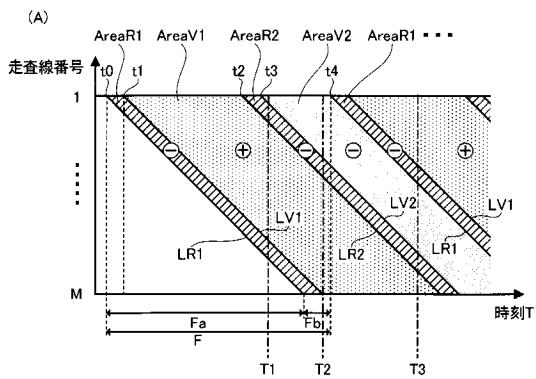

【図3】表示領域内の液晶素子が保持する信号の遷移を示す図である。

【図4】走査線駆動回路の構成を示すブロック図である。

【図5】Y入力パルスの波形を示すタイミングチャートである。

【図6】Yシフトパルスの波形を示すタイミングチャートである。

【図7】制御回路及び駆動回路の動作を示すタイミングチャートである。

【図8】選択信号の波形を示すタイミングチャートである。

10

20

30

40

50

【図9】データ信号及び容量線の電位変化を示すタイミングチャートである。

【図10】データ信号及び容量線の電位変化を示すタイミングチャートである。

【図11】電子機器（パーソナルコンピュータ）の斜視図である。

【図12】電子機器（携帯電話機）の斜視図である。

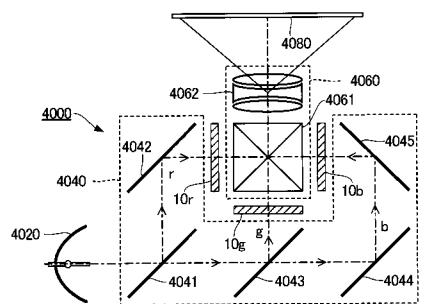

【図13】電子機器（プロジェクタ）の斜視図である。

【発明を実施するための形態】

【0020】

< A : 実施形態 >

以下、添付の図面を参照しながら本発明に係る様々な実施の形態を説明する。図面においては、各部の寸法の比率は実際のものとは適宜に異ならせてある。

10

【0021】

図1は、本発明の形態に係る液晶装置1のブロック図である。液晶装置1は、画像を表示する表示体として、電子機器に搭載することができる。図1に示すように、液晶装置1は、画像を表示する表示パネル10と、これを制御する制御回路40と、を備える。

表示パネル10は、複数の画素回路23を有する表示領域20と、複数の画素回路23を駆動する駆動回路30とを備える。

【0022】

表示領域20は、X方向に延在するM本（Mは1以上の自然数）の走査線21と、X方向に交差するY方向に延在するN本（Nは1以上の自然数）のデータ線22と、X方向に延在するM本の容量線24（図示略）と、各走査線21と各データ線22との交差に対応して縦M行×横N列の行列状に配置された複数の画素回路23とを備える。

20

駆動回路30は、M本の走査線21と接続する走査線駆動回路31と、N本のデータ線22と接続するデータ線駆動回路32とより構成される。駆動回路30は、例えば複数の集積回路に分散して実装される。ただし、駆動回路30の少なくとも一部は、画素回路23と共に基板上に形成された薄膜トランジスタで構成され得る。なお、本実施形態では、表示パネル10は駆動回路30を含んで構成されているが、駆動回路30の少なくとも一部を表示パネル10とは別に形成しても良い。

【0023】

走査線駆動回路31は、複数の走査線21を行単位で順次に走査（選択）する手段であり、選択信号G[1]～G[M]を生成して、M本の各走査線21に対して出力する。

30

また、データ線駆動回路32は、制御回路40より供給されるデータ信号Vidに基づいて、各画素回路23の階調を指定する画像信号VD[1]～VD[N]を生成する。そして、データ線駆動回路32は、制御回路40より供給されるX入力パルスDx、ドットクロック信号Dclk、及び制御信号Nregに基づいて、画像信号VD[1]～VD[N]を含むデータ信号Vidをデータ線22に対して出力する。

【0024】

制御回路40は、図示しない上位装置より供給される、表示領域20の有する画素の階調を指定する表示データVIDEOに基づいて、アナログのデータ信号Vidを生成し、これをデータ線駆動回路32に供給する。

また、制御回路40は、図示しない上位装置から供給される制御信号に基づいて、1垂直走査期間Fの半分に相当する周期でアクティブになるパルス信号であるY転送開始パルスDyin、及び1水平走査期間Hに相当する周期を有するクロック信号であるインバータ信号INV、等の内部信号を生成する。そして、制御回路40は、これらの制御信号及び内部信号に基づき、表示パネル10を制御するための各種信号を生成する。具体的には、制御回路40は、1垂直走査期間Fにおいて4回アクティブになるパルス信号であるY入力パルスDy、1水平走査期間Hの2個分に相当する周期を有するクロック信号であるYクロック信号Cly、及び1水平走査期間Hのうち所定の期間を指定する信号であるイネーブル信号ENBを生成して、走査線駆動回路31に供給すると共に、1水平走査期間Hの半分に相当する周期でアクティブになるパルス信号であるX入力パルスDx、1水平走査期間Hを細分化し、各画素に対してデータ信号Vidが供給される期間を指定するド

40

50

ットクロック信号  $D_{c1k}$ 、及び 1 水平走査期間  $H$  のうち所定の期間を指定する制御信号  $N_{rg}$  を生成して、データ線駆動回路 32 に供給する。

【0025】

図 2 は、画素回路 23 の回路図である。ここでは、第  $i$  行 ( $i$  は、1  $\leq i \leq M$  を満たす自然数) 第  $j$  列 ( $j$  は、1  $\leq j \leq N$  を満たす自然数) に位置する画素回路 23 を代表的に図示している。画素回路 23 は、選択トランジスタ (スイッチング素子) 235 と、透明な画素電極 231 と透明な共通電極 233 との間に設けられた液晶 232 とを備える液晶素子 230 と、保持容量  $C_0$  とを有する。

【0026】

選択トランジスタ 235 のゲート電極は  $i$  行目の走査線 21 に接続され、ソース電極及びドレイン電極の一方は  $j$  列目のデータ線 22 に接続され、ソース電極及びドレイン電極の他方は画素電極 231 に接続されている。保持容量  $C_0$  は、画素電極 231 と容量線 24 との間に設けられる。容量線 24 には一定の電位  $V_{co}$  が供給される。

10

【0027】

走査線 21 に供給され選択信号  $G[i]$  がハイレベルになると、選択トランジスタ 235 はオンし、データ信号  $V_{id}$  がデータ線 22 より選択トランジスタ 235 を介して画素電極 231 に供給される。また、走査線 21 に供給される選択信号  $G[i]$  がローレベルになると、選択トランジスタ 235 はオフし、データ線 22 と画素電極 231 とは非導通の状態となるが、選択トランジスタ 235 はオフである間も、画素電極 231 に印加されたデータ信号  $V_{id}$  は、液晶素子 230 の容量及び保持容量  $C_0$  により保持される。

20

【0028】

図示は省略するが、表示パネル 10 は、一定の間隔を保って貼り合わされた素子基板と対向基板とを備える。液晶 232 は、素子基板と対向基板との間隙に封止されている。素子基板上には、走査線駆動回路 31、データ線駆動回路 32、走査線 21、データ線 22、選択トランジスタ 235、及び画素電極 231 が形成され、対向基板上には共通電極 233 が形成される。共通電極 233 は、複数の画素電極 231 に共通であり、そこには共通電位  $V_{com}$  が印加される。

30

以下の説明では、共通電位  $V_{com}$  を基準として、データ信号  $V_{id}$  の電位が共通電位  $V_{com}$  以上でとなる場合を正極性、データ信号  $V_{id}$  の電位が共通電位  $V_{com}$  を下回る場合を負極性と称する。

【0029】

ところで、液晶に対して、同一の極性の電圧を長時間印加し続けた場合、液晶の容量性による帯電が生じ、帯電の影響により残像が表示される、いわゆる焼き付きの問題が存在する。このような問題に対応するために、一定周期で画素回路に対して印加する電圧の極性を反転させることで、液晶に帯電した電荷を除去し焼き付きを防止する、反転駆動方式が一般的に採用されている。

30

【0030】

反転駆動方式としては、極性の反転を 1 垂直走査期間  $F$  每に行うフレーム反転駆動方式が存在するが、その場合、各画素とデータ線との電位差が、1 画面の上部に位置する画素と下部に位置する画素との間で偏りが生じるため、画面の上部と下部との間で表示が不均一になるという問題が生じていた。

40

そこで、1 垂直走査期間  $F$  の各々において正極性または負極性のいずれか一方の極性を有する画像信号を書き込むのではなく、一定の間隔を隔てた 2 つの画素に対して、それぞれ交互に正極性と負極性の画像信号の書き込みを行う領域走査駆動方式により、このような表示不均一の問題に対応している。

【0031】

一方、近年の液晶装置の小型化、高精度化に伴い、画素間の間隔が狭まっている。そのため、画素電極間の電位差により、本来、基板面に対して縦方向の電界により駆動されるべき液晶に対して、横方向の電界が加わるため、液晶分子の配向が乱れるという配向不良の問題が生じる。

50

この配向不良の問題は、隣接する画素間の電位差が大きい場合に生じやすい。例えば、隣接する2つの画素間において、一方の画素に白表示相当の電圧  $V_{w,t}$  (ノーマリーブラックモードの場合)、または、黒表示相当の電圧  $V_{b,k}$  (ノーマリー ホワイトモードの場合)等の共通電位  $V_{c,0,m}$  と大きな電位差を有する電圧を印加し、他方の画素に光学的閾値電圧  $V_{t,h}$  以下の小さな電圧が印加されている場合には、画素間の電位差が大きくなり、横電界の影響による配向不良が生じやすくなる。

本実施形態では、このような配向不良の問題に対応するため、液晶に対して、横電界の影響を受けた液晶をその影響下から脱するのに十分な大きさの電圧を有するリセット信号  $V_r$  を印加して、液晶を正常な状態に戻したうえで、画像信号を印加する。この駆動方式をリセット駆動と称する。

10

#### 【0032】

なお、本実施形態は、液晶232はVA(Vertical Alignment)方式であり、液晶素子230に対して電圧が印加されない状態において画素が黒表示(画素の相対透過率が0%)となるノーマリーブラックモードを想定する。

また、リセット信号  $V_r$  のレベルは、光学的飽和電圧  $V_{s,a,t}$  以上のとなるように設定すればよい。具体的には、本実施形態では、リセット信号  $V_r$  のレベルは、白表示相当の電圧  $V_{w,t}$  とする。

ここで、相対透過率とは、ノーマリーブラックモードの場合、表示パネル10において液晶素子230に電圧を印加しない場合の透過率を0%とし、液晶素子230に最大電圧を印加した場合の透過率を100%として、液晶素子230の透過率をスケーリングしたものである。そして、(社)電子情報技術産業協会が制定した「液晶表示パネル及びその構成材料の測定方法」に関する規格JEITA ED-2521Bによれば、相対透過率が10%となる印加電圧が光学的閾値電圧  $V_{t,h}$  であり、相対透過率が90%となる印加電圧が光学的飽和電圧  $V_{s,a,t}$  である。

20

#### 【0033】

本実施形態では、以上に述べたような、領域走査駆動方式とリセット駆動方式とを一体とした駆動方式を採用することにより、焼き付きの問題、表示不均一の問題、及び配向不良の問題を解決する。

以下では、図3を参照しつつ、本駆動方式の動作の概要について説明する。

#### 【0034】

本実施形態では、一定の間隔の行数を隔てた2つの画素に対して、交互にリセット信号  $V_r$  を供給し、その一定期間後に、これら2つの画素に対して、交互に正極性と負極性の画像信号  $V_D$  を供給する。より具体的には、各水平走査期間  $H$  において、選択信号  $G[i]$  が4行の走査線21を選択し、これら4行の走査線21に接続する複数の画素回路23に対して、それぞれ、正極性の画像信号  $V_D$  (第1画像信号  $V_{d,1}$ )、正極性の画像信号  $V_D$  が供給される前に供給されるリセット信号  $V_r$  (第1リセット信号  $V_{r,1}$ )、負極性の画像信号  $V_D$  (第2画像信号  $V_{d,2}$ )、及び負極性の画像信号  $V_D$  が供給される前に供給されるリセット信号  $V_r$  (第2リセット信号  $V_{r,2}$ )を供給する。そして、このような、第1リセット信号  $V_{r,1}$ 、第1画像信号  $V_{d,1}$ 、第2リセット信号  $V_{r,2}$ 、及び第2画像信号  $V_{d,2}$  の各信号は、互いに異なる4つの走査線21に対して、1水平走査期間  $H$  に1行ずつ順次シフトしながら、供給される。

40

#### 【0035】

なお、本実施形態では、第1リセット信号  $V_{r,1}$  及び第2リセット信号  $V_{r,2}$  は、共に負極性とする。

詳細は後述するが、仮に、第1リセット信号  $V_{r,1}$  と第2リセット信号  $V_{r,2}$  とを逆極性とした場合、データ線駆動回路32からデータ線22に出力される信号が、第1画像信号  $V_{d,1}$  から第2リセット信号  $V_{r,2}$  へと切り替わるタイミング、及び、第2画像信号  $V_{d,2}$  から第1リセット信号  $V_{r,1}$  へと切り替わるタイミングにおいて、データ線22の電位が大きく変化する。複数のデータ線22の各々は、複数の容量線24の各々と交差しており、データ線22及び容量線24は、寄生容量によりカップリングしている。従って、

50

データ線 2 2 の電位変化が急峻且つ大きな場合には、容量線 2 4 の電位も変化する。そして、容量線 2 4 の電位が変化した場合、画素回路 2 3 の備える保持容量 C O は容量線 2 4 と接続しているため、画素回路 2 3 の保持容量 C O を介して、画素電極 2 3 1 の電位も変化することになる。この結果、画素回路 2 3 により表示される階調は、画像信号 V D が指定する階調とは異なる階調となり、表示品質が劣化する。

これに対して、本実施形態のように、第 1 リセット信号 V r 1 及び第 2 リセット信号 V r 2 を同極性とした場合には、データ線駆動回路 3 2 からデータ線 2 2 に出力される信号が、第 1 画像信号 V d 1 から第 2 リセット信号 V r 2 へと切り替わるタイミング、または、第 2 画像信号 V d 2 から第 1 リセット信号 V r 1 へと切り替わるタイミングのうちのいずれかにおいて、データ信号 V i d の電位は同極性のままであるため、データ線 2 2 に生じる急峻且つ大きな電位変化の回数を低減させることができるとなる。この結果、データ線 2 2 の電位変化に伴い発生する容量線 2 4 の電位変化に起因する表示不具合が視認される可能性を低減することができる。

#### 【 0 0 3 6 】

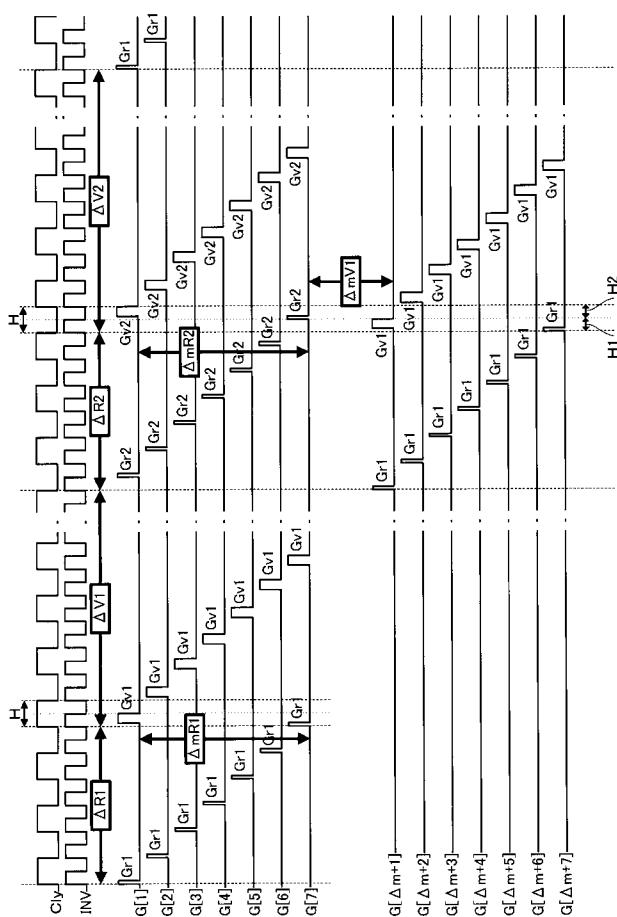

図 3 ( A ) は、選択信号 G [ i ] が選択する走査線 2 1 の行数と、選択する時間との関係を表す図である。図 3 ( A ) の縦軸は走査線 2 1 の行数 ( 1 から M までの自然数 ) を表し、横軸は時間を表す。

直線 L R 1 は、第 1 リセット信号 V r 1 が供給される複数の画素回路 2 3 が接続する走査線 2 1 の行と、供給される時間との関係を示す。同様に、直線 L V 1 は第 1 画像信号 V d 1 が供給される走査線 2 1 について、直線 L R 2 は第 2 リセット信号 V r 2 が供給される走査線 2 1 について、直線 L V 2 は第 2 画像信号 V d 2 が供給される走査線 2 1 について、それぞれの供給される行数と供給される時間との関係を示す。

また、直線 L R 1 上のある点が示す行の走査線 2 1 に対して、当該点が示す時間に第 1 リセット信号 V r 1 が供給された場合、その後、当該走査線 2 1 に接続する複数の画素回路 2 3 は、複数の画素回路 2 3 の各々が有する保持容量 C O により、第 1 リセット信号 V r 1 を保持する。領域 Area R 1 は、当該領域の左側で接する直線 L R 1 において供給された第 1 リセット信号 V r 1 を保持する画素回路 2 3 の行数と、保持している時間との関係を表している。同様に、領域 Area V 1 、領域 Area R 2 、及び領域 Area V 2 の各領域は、それぞれの領域の左側に接する、直線 L V 1 、直線 L R 2 、及び直線 L V 2 において供給された第 1 画像信号 V d 1 、第 2 リセット信号 V r 2 、及び第 2 画像信号 V d 2 を保持している画素回路 2 3 の行数と、保持している時間との関係を表している。

#### 【 0 0 3 7 】

例えば、第 1 行目の走査線 2 1 に接続する複数の画素回路 2 3 には、直線 L R 1 と交差する時刻 T = t 0 において第 1 リセット信号 V r 1 が供給され、供給された第 1 リセット信号 V r 1 は、領域 Area R 1 の範囲である t 0 ～ T = t 1 の期間、保持される。その後、第 1 行目の走査線 2 1 に接続する複数の画素回路 2 3 は、直線 L V 1 と交差する時刻 T = t 1 に供給される第 1 画像信号 V d 1 を、領域 Area V 1 の範囲である t 1 ～ T = t 2 の期間保持し、直線 L R 2 と交差する時刻 T = t 2 に供給される第 2 リセット信号 V r 2 を、領域 Area R 2 の範囲である t 2 ～ T = t 3 の期間保持し、直線 L V 2 と交差する時刻 T = t 3 に供給される第 2 画像信号 V d 2 を、領域 Area V 2 の範囲である t 3 ～ T = t 4 の期間保持する。

このような、第 1 リセット信号 V r 1 、第 1 画像信号 V d 1 、第 2 リセット信号 V r 2 、及び第 2 画像信号 V d 2 の各信号は、互いに異なる 4 つの走査線 2 1 に対して、1 水平走査期間 H に 1 行ずつ順次シフトしながら、供給される。

#### 【 0 0 3 8 】

図 3 ( B ) ( C ) ( D ) は、図 3 ( A ) の時刻 T = T 1 、時刻 T = T 2 、及び時刻 T = T 3 のそれぞれの瞬間ににおける、表示領域 2 0 の画素回路 2 3 が保持する電圧を示した図である。図 3 ( B ) に示すように、時刻 T = T 1 では、画面下方から上方に向けて順に、画素回路 2 3 が第 1 リセット信号 V r 1 を保持する領域 Area R 1 、画素回路 2 3 が第 1 画像信号 V d 1 を保持する領域 Area V 1 、画素回路 2 3 が第 2 リセット信号 V r 2

を保持する領域 Area R 2、画素回路 2 3 が第 2 画像信号 Vd 2 を保持する領域 Area V 2 が順番に並ぶ。時刻 T = T 1 以降、これらの各領域は、その幅を保ったまま、1 水平走査期間 H 每に 1 行ずつ下方に遷移し、やがて、領域 Area R 1 が画面下部に消滅する。そして、時刻 T = T 2 では、図 3 (C) に示すように、画面下部より、領域 Area V 1、領域 Area R 2、領域 Area V 2 が順番に並ぶ。さらに、時刻 T = T 3 では、図 3 (D) に示すように、画面下部より、領域 Area V 1、領域 Area R 2、領域 Area V 2 が順番に並ぶと共に、画面上部より、新たに、領域 Area R 1、領域 Area V 1 が出現する。

#### 【0039】

図 3 の中で、ある時刻における、ある直線 LR 1 と、当該直線 LR 1 に隣り合う直線 LV 1 との間隔を、間隔 mR 1 とする。具体的には、ある 1 水平走査期間 H において、第 1 リセット信号 Vr 1 が供給される行と、第 1 画像信号 Vd 1 が供給される行との間隔を、間隔 mR 1 とする。同様に、互いに隣り合う、直線 LV 1 と直線 LR 2 との間隔、すなわち、ある 1 水平走査期間 H において、第 1 画像信号 Vd 1 が供給される行と、第 2 リセット信号 Vr 2 が供給される行との間隔を、間隔 mV 1 とする。

また、互いに隣り合う、直線 LR 2 と直線 LV 2 との間隔、すなわち、ある 1 水平走査期間 H において、第 2 リセット信号 Vr 2 が供給される行と、第 2 画像信号 Vd 2 が供給される行との間隔を、間隔 mR 2 とする。同様に、互いに隣り合う、直線 LV 2 と直線 LR 1 との間隔、すなわち、ある 1 水平走査期間 H において、第 2 画像信号 Vd 2 が供給される行と、第 1 リセット信号 Vr 1 が供給される行の間隔 mV 2 とする ( mR 1、10 mR 2、mV 1、及び mV 2 は、いずれも 1 以上の自然数)。

#### 【0040】

本実施形態では、間隔 mR 1 及び間隔 mR 2 は等しい値に設定される。

また、間隔 mR 1 及び間隔 mR 2 は、間隔 mV 2 及び間隔 mV 1 に比べて十分小さな値 ( 例えば、「6」) に設定される。前述の通り、第 1 リセット信号 Vr 1 及び第 2 リセット信号 Vr 2 は、液晶素子 230 に対して白表示相当の電圧 Vwt を印加するものである。液晶素子 230 に対して白表示相当の電圧 Vwt を長時間印加する場合、本来表示すべき階調とは異なる階調 ( 例えば、ノーマリーブラックモードの場合、白表示 ) として観察者に知覚される。よって、間隔 mR 1 及び間隔 mR 2 を、間隔 mV 2 または間隔 mV 1 に比べて十分に小さな値に設定して、液晶素子 230 にリセット信号 Vr を印加する時間を十分に短くすることにより、液晶素子 230 の透過率の変化を観察者に近くされることなく、液晶 232 を配向不良の状態から脱する契機を与えることができる。

#### 【0041】

また、本実施形態では、間隔 mV 1 は、間隔 mV 2 よりも大きな値に設定される。より具体的には、間隔 mV 1 は、間隔 mV 2、間隔 mR 1、及び間隔 mR 2 を合計した値に等しくなるように設定される ( すなわち、mV 1 = mV 2 + mR 1 + mR 2 )。

前述したように、本実施形態では、第 1 リセット信号 Vr 1 及び第 2 リセット信号 Vr 2 は、共に負極性である。従って、仮に、間隔 mV 1 と間隔 mV 2 とを等しい値とした場合には、表示領域 20 において、画素回路 23 が負極性の電位を保持している領域 ( 領域 Area R 1、領域 Area R 2、及び領域 Area V 2 を合計した領域 ) が、画素回路 23 が正極性の電位を保持している領域 ( 領域 Area V 1 ) よりも大きくなる。この場合、各画素回路 23 とデータ線 22 との電位差が、表示領域 20 内の位置によって偏りが生じるため、表示領域 20 内の位置により表示が不均一になるという問題が生じる可能性がある。

これに対して、本実施形態では、間隔 mV 1 を、間隔 mV 2、間隔 mR 1、及び間隔 mR 2 の合計に等しい値にすることで、表示領域 20 において、画素回路 23 が正極性の電位を保持している領域と、画素回路 23 が負極性の電位を保持している領域とを、等しい面積とする。これにより、データ線 22 に印加される電位の 1 垂直走査期間 F に

おける平均値が、正極性または負極性の一方に偏ることを防止することが可能となる。その結果、画素回路 23 とデータ線 22 との間の電位差の 1 垂直走査期間  $F$  における平均値が、表示領域 20 内の位置に依存して大きく偏ることを防止でき、表示の不均一を防止することが可能となる。

#### 【0042】

前述のとおり、1 垂直走査期間  $F$  は、 $Y$  転送開始パルス  $D_{y\ in}$  の 2 周期分に相当する期間であり、図 3 (A)において、第 1 リセット信号  $V_{r\ 1}$  が 1 行目に供給されるタイミング ( 時刻  $T = t_0$  ) から、再び 1 行目に供給されるタイミング ( 時刻  $T = t_4$  ) までの期間である。また、垂直有効期間  $F_a$  は、各信号が 1 行目から  $M$  行目まで供給されるのに要する期間であり、水平走査期間  $H$  の  $M$  個分の期間に相当する。垂直帰線期間  $F_b$  は、垂直走査期間  $F$  より垂直有効期間  $F_a$  を除いた時間である。

10

#### 【0043】

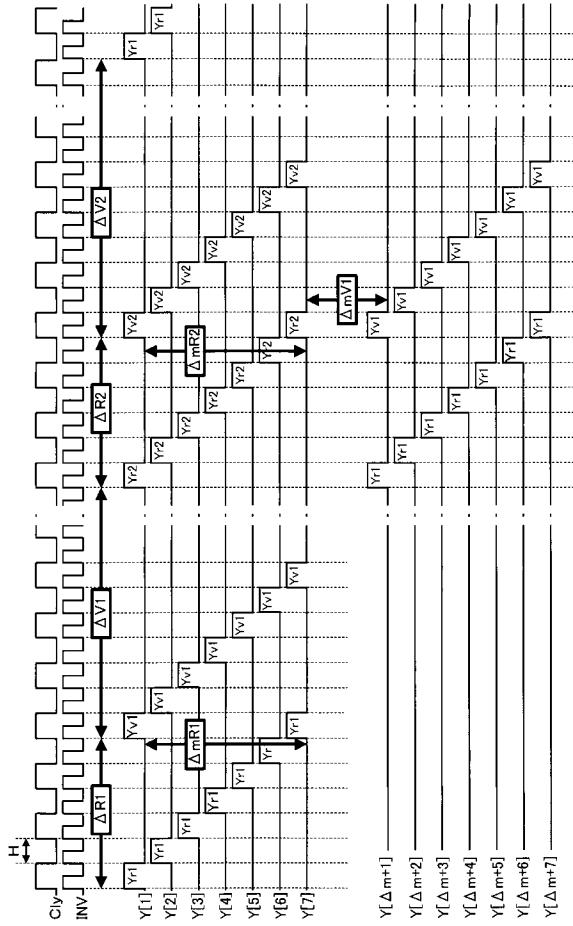

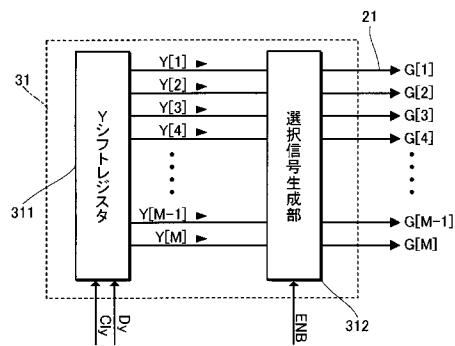

図 4 は、走査線駆動回路 31 の構成を示す図である。走査線駆動回路 31 は、 $Y$  シフトレジスタ 311 と、選択信号生成部 312 とを備える。

$Y$  シフトレジスタ 311 は、 $Y$  入力パルス  $D_y$  が供給されると、これを  $Y$  クロック信号  $C_{1\ y}$  に従って順次転送することによって、 $Y$  シフトパルス  $Y[1] \sim Y[M]$  を生成する。 $Y$  シフトパルス  $Y[1] \sim Y[M]$  は、1 水平走査期間  $H$  に相当するパルス幅を有するパルス信号であり、 $Y$  シフトパルス  $Y[1] \sim Y[M]$  の各々は、互いに 1 水平走査期間  $H$  ずつ遅れて順次出力される。

20

#### 【0044】

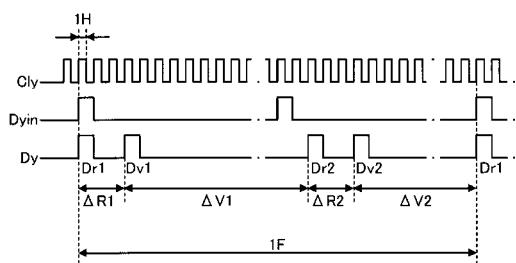

図 5 に示すように、 $Y$  入力パルス  $D_y$  は、1 垂直走査期間  $F$  において 4 回アクティブになるパルス信号である。具体的には、 $Y$  入力パルス  $D_y$  は、各垂直走査期間  $F$  の開始されるタイミングでアクティブになる第 1 リセット入力パルス  $D_{r\ 1}$ 、第 1 リセット入力パルス  $D_{r\ 1}$  がアクティブになるよりも期間  $R_1$  ( 第 3 期間 ) だけ遅れてアクティブになる第 1 書込入力パルス  $D_{v\ 1}$ 、第 1 リセット入力パルス  $D_{r\ 1}$  がアクティブになるよりも期間  $V_1$  ( 第 1 期間 ) だけ遅れてアクティブになる第 2 リセット入力パルス  $D_{r\ 2}$ 、及び第 2 リセット入力パルス  $D_{r\ 2}$  がアクティブになるよりも期間  $R_2$  ( 第 4 期間 ) だけ遅れてアクティブになる第 2 書込入力パルス  $D_{v\ 2}$  を有する。なお、第 2 書込入力パルス  $D_{v\ 2}$  がアクティブになった後、期間  $V_2$  ( 第 2 期間 ) の後に、当該垂直走査期間  $F$  が終了し、再び、第 1 リセット入力パルス  $D_{r\ 1}$  がアクティブになる。

30

ここで、期間  $R_1$  は、1 水平走査期間  $H$  の  $mR_1$  個分に相当する期間であり、期間  $R_2$  は、1 水平走査期間  $H$  の  $mR_2$  個分に相当する期間であり、期間  $V_1$  は、1 水平走査期間  $H$  の  $mV_1$  個分に相当する期間であり、期間  $V_2$  は、1 水平走査期間  $H$  の  $mV_2$  個分に相当する期間である。

30

#### 【0045】

前述の通り、 $Y$  入力パルス  $D_y$  は、制御回路 40 で生成され、走査線駆動回路 31 に対して出力される信号である。具体的には、制御回路 40 は、各垂直走査期間  $F$  の開始時を起点として、期間  $R_1$ 、期間  $V_1$ 、期間  $R_2$ 、及び期間  $V_2$  を示すカウント値と、インバータ信号  $INV$  に基づいて 1 水平走査期間  $H$  に 1 ずつカウントアップするカウンタとを有する。そして、制御回路 40 は、各種カウント値と、カウンタとに基づいて、 $Y$  入力パルス  $D_y$  ( 第 1 リセット入力パルス  $D_{r\ 1}$ 、第 1 書込入力パルス  $D_{v\ 1}$ 、第 2 リセット入力パルス  $D_{r\ 2}$ 、及び第 2 書込入力パルス  $D_{v\ 2}$  ) を生成する。

40

#### 【0046】

$Y$  シフトレジスタ 311 は、これら 4 種類の  $Y$  入力パルス  $D_y$  の各々に対して、 $Y$  入力パルス  $D_y$  を順次シフトした  $Y$  シフトパルス  $Y[1] \sim Y[M]$  を生成する。

具体的には、図 6 に示すように、 $Y$  シフトレジスタ 311 は、第 1 リセット入力パルス  $D_{r\ 1}$  を順次シフトさせて第 1 リセットシフトパルス  $Y_{r\ 1}$  を生成し、第 1 書込入力パルス  $D_{v\ 1}$  を順次シフトさせて第 1 書込シフトパルス  $Y_{v\ 1}$  を生成し、第 2 リセット入力パルス  $D_{r\ 2}$  を順次シフトさせて第 2 リセットシフトパルス  $Y_{r\ 2}$  を生成し、及び第 2 書込入力パルス  $D_{v\ 2}$  を順次シフトさせて第 2 書込シフトパルス  $Y_{v\ 2}$  を生成する。

50

第1リセットシフトパルスY<sub>r</sub>1、第1書込シフトパルスY<sub>v</sub>1、第2リセットシフトパルスY<sub>r</sub>2、及び第2書込シフトパルスY<sub>v</sub>2の出力が開始される間隔は、4つのY入力パルスD<sub>y</sub>の間隔と等しい。すなわち、ある走査線21に対して、第1書込シフトパルスY<sub>v</sub>1は第1リセットシフトパルスY<sub>r</sub>1よりも期間R1の後に出力され、第2リセットシフトパルスY<sub>r</sub>2は第1書込シフトパルスY<sub>v</sub>1よりも期間V1の後に出力され、第2書込シフトパルスY<sub>v</sub>2は第2リセットシフトパルスY<sub>r</sub>2よりも期間R2の後に出力され、第1リセットシフトパルスY<sub>r</sub>1は第2書込シフトパルスY<sub>v</sub>2よりも期間V2の後に出力される。

#### 【0047】

選択信号生成部312は、4種類のYシフトパルスY[1]～Y[M]と、イネーブル信号ENBとに基づいて、4種類の選択信号G[1]～G[M]、すなわち、第1リセット選択信号Gr1、第1書込選択信号Gv1、第2リセット選択信号Gr2、及び第2書込選択信号Gv2を生成する。図7を参照しつつ、イネーブル信号ENB及び4種類の選択信号G[1]～G[M]の詳細について説明する。

10

#### 【0048】

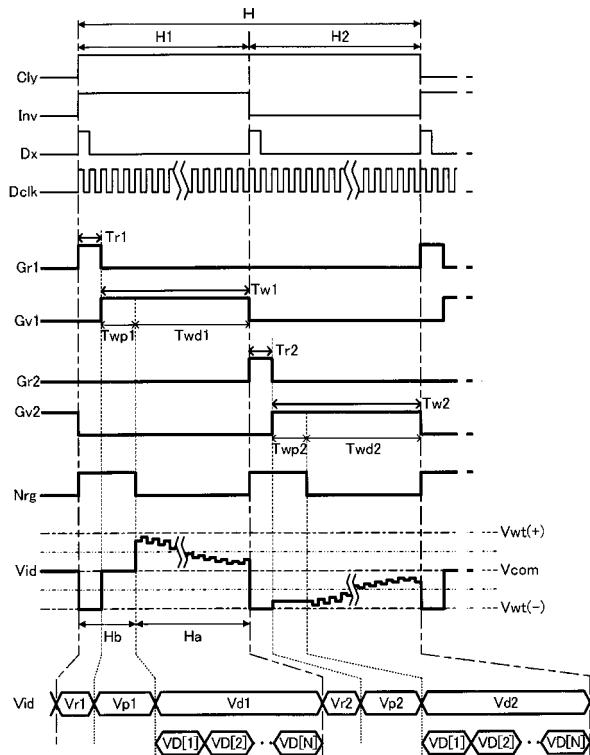

図7は、駆動回路30及び制御回路40の動作を規定するタイミングチャートである。

図7に示すように、1水平走査期間Hは、等しい長さの第1期間H1と第2期間H2から成り立つ。第1期間H1は、インバータ信号INVがハイレベルである期間であり、各水平走査期間Hの開始と同時に開始され、1水平走査期間Hの半分に相当する期間である。第2期間H2は、インバータ信号INVがローレベルである期間であり、各水平走査期間HにおいてX入力パルスDxが2回目にアクティブになるタイミングで開始される、1水平走査期間Hの半分に相当する期間である。

20

また、第1期間H1は、第1リセット期間Tr1と、第1書込期間Tw1とより成り立ち、第2期間H2は、第2リセット期間Tr2と、第2書込期間Tw2とより成り立つ。

#### 【0049】

イネーブル信号ENBは、各水平走査期間Hにおいて、第1リセット期間Tr1を指定する信号R1、第1書込期間Tw1を指定する信号V1、第2リセット期間Tr2を指定する信号R2、及び第2書込期間Tw2を指定する信号V2を含む信号である。

なお、イネーブル信号ENBは、前述の通り、制御回路40で生成される。具体的には、制御回路40は、各水平走査期間Hの開始時を起点として、第1リセット期間Tr1、第1書込期間Tw1、第2リセット期間Tr2、及び第2書込期間Tw2の各々の開始時間及び終了時間を示す各種カウント値と、ドットクロック信号Dclkに基づいてカウントアップするカウンタとを備える。そして、制御回路40は、各種カウント値とカウンタとに基づいて、イネーブル信号ENBを生成する。

30

#### 【0050】

選択信号生成部312は、第1リセットシフトパルスY<sub>r</sub>1及び信号R1の論理積を演算して、第1リセット期間Tr1においてアクティブとなる第1リセット選択信号Gr1を生成し、第1書込シフトパルスY<sub>v</sub>1及び信号V1の論理積を演算して、第1書込期間Tw1においてアクティブとなる第1書込選択信号Gv1を生成し、第2リセットシフトパルスY<sub>r</sub>2及び信号R2の論理積を演算して、第2リセット期間Tr2においてアクティブとなる第2リセット選択信号Gr2を生成し、第2書込シフトパルスY<sub>v</sub>2及び信号V2の論理積を演算して、第2書込期間Tw2においてアクティブとなる第2書込選択信号Gv2を生成する。

40

図8に示すように、第1リセット選択信号Gr1、第1書込選択信号Gv1、第2リセット選択信号Gr2、及び第2書込選択信号Gv2は、各水平走査期間Hにおいて排他的なタイミングで4本の走査線21に対して各々出力される。また、第1リセット選択信号Gr1、第1書込選択信号Gv1、第2リセット選択信号Gr2、及び第2書込選択信号Gv2の各々は、第1行～第M行の走査線21に対して、1水平走査期間H毎に1行ずつシフトして出力される。これら4種類の選択信号G[1]～G[M]が出力される走査線21及びその間隔は、4種類のYシフトパルスY[1]～Y[M]が出力される走査線2

50

1及びその間隔と等しい。

【0051】

図7に示すように、第1書込期間Tw1は、制御信号Nrgがハイレベルとなる第1プリチャージ期間Twp1と、制御信号Nrgがローレベルとなる第1画像信号書込期間Twd1とを含む。また、第2書込期間Tw2は、制御信号Nrgがハイレベルとなる第2プリチャージ期間Twp2と、制御信号Nrgがローレベルとなる第2画像信号書込期間Twd2とを含む。

なお、第1期間H1において、第1リセット期間Tr1及び第1プリチャージ期間Twp1が水平帰線期間Hbに該当し、第1画像信号書込期間Twd1は水平有効期間Haに該当する。また、第2期間H2において、第2リセット期間Tr2及び第2プリチャージ期間Twp2が水平帰線期間Hbに該当し、第2画像信号書込期間Twd2は水平有効期間Haに該当する。

【0052】

第1プリチャージ期間Twp1及び第2プリチャージ期間Twp2は、画素回路23に對して画像信号VDを供給するのに先立って、プリチャージ信号Vpを供給するための期間である。以下では、図7に示すように、第1プリチャージ期間Twp1において供給されるプリチャージ信号Vpを第1プリチャージ信号Vp1と称し、第2プリチャージ期間Twp2において供給されるプリチャージ信号Vpを第2プリチャージ信号Vp2と称する。

なお、本実施形態では、第1プリチャージ信号Vp1のレベルは、共通電位Vcomに設定される。また、第2プリチャージ信号Vp2のレベルは、負極性の白表示相当の電圧Vwt(-)から、共通電位Vcom及び負極性の白表示相当の電圧Vwt(-)の中間の電位{(Vcom + Vwt(-)) / 2}までの範囲となるように設定される。

【0053】

制御信号Nrgは、1水平走査期間Hの半分の期間に相当する周期を有する信号であり、第1期間H1の開始時から、第1リセット期間Tr1及び第1プリチャージ期間Twp1の合計に相当する期間と、第2期間H2の開始時から、第2リセット期間Tr2及び第2プリチャージ期間Twp2の合計に相当する期間とにおいてハイレベルになる。

前述の通り、制御信号Nrgは、制御回路40で生成され、データ線駆動回路32に對して出力される信号である。具体的には、制御回路40は、第1期間H1及び第2期間H2の開始時を起点として、制御信号Nrgがハイレベルに立ち上がる時間及びローレベルに立ち下がる時間を示す各種カウント値を有し、ドットクロック信号Dclkに基づいてカウントアップするカウンタと、各種カウント値に基づいて、制御信号Nrgを生成する。

【0054】

データ信号Vidは、水平有効期間Haに画像信号VDを、水平帰線期間Hbにリセット信号Vr及びプリチャージ信号Vpを時分割多重した信号である。

制御信号Nrgがハイレベルとなる期間において、データ線駆動回路32は、N本のデータ線22に対して、データ信号Vidを同時に出力する。具体的には、データ線駆動回路32は、第1リセット期間Tr1において、第1リセット選択信号Gr1により選択された走査線21に接続するN個の画素回路23に対して、第1リセット信号Vr1を供給し、第1プリチャージ期間Twp1において、第1書込選択信号Gv1により選択された走査線21に接続するN個の画素回路23に対して、第1プリチャージ信号Vp1を供給する。同様に、データ線駆動回路32は、第2リセット期間Tr2において、第2リセット選択信号Gr2により選択された走査線21に接続するN個の画素回路23に対して、第2リセット信号Vr2を供給し、第2プリチャージ期間Twp2において、第2書込選択信号Gv2により選択された走査線21に接続するN個の画素回路23に対して、第2プリチャージ信号Vp2を供給する。

【0055】

一方、制御信号Nrgがローレベルとなる期間において、データ線駆動回路32は、N

10

20

30

40

50

本のデータ線 2 2 に対して、データ信号  $V_{id}$  を、ドットクロック信号  $D_{clk}$  に基づいて、順次排他的なタイミングで出力する。

具体的には、データ線駆動回路 3 2 は、第 1 画像信号書込期間  $T_{wd1}$  において、第 1 書込選択信号  $G_{v1}$  により選択された走査線 2 1 に接続する  $N$  個の画素回路 2 3 に対して、第 1 画像信号  $V_{d1}$  (画像信号  $V_D[1] \sim V_D[N]$ ) をドットクロック信号  $D_{clk}$  に基づいて順次排他的に出力し、第 2 画像信号書込期間  $T_{wd2}$  において、第 2 書込選択信号  $G_{v2}$  により選択された走査線 2 1 に接続する  $N$  個の画素回路 2 3 に対して、第 2 画像信号  $V_{d2}$  (画像信号  $V_D[1] \sim V_D[N]$ ) をドットクロック信号  $D_{clk}$  に基づいて順次排他的に出力する。

【0056】

10

このように、ある走査線 2 1 に接続する  $N$  個の画素回路 2 3 には、ある水平走査期間  $H$  の第 1 リセット期間  $T_{r1}$  に、第 1 リセット信号  $V_{r1}$  が供給された後、第 1 リセット信号  $V_{r1}$  が供給された水平走査期間  $H$  よりも期間  $R_1$  後に開始される水平走査期間  $H$  の第 1 書込期間  $T_{wd1}$  のうち、第 1 プリチャージ期間  $T_{wp1}$  に、第 1 プリチャージ信号  $V_{p1}$  が供給されると共に、第 1 画像信号書込期間  $T_{wd1}$  に、第 1 画像信号  $V_{d1}$  が供給される。

また、これら  $N$  個の画素回路 2 3 には、第 1 画像信号  $V_{d1}$  が供給された水平走査期間  $H$  よりも期間  $V_1$  後に開始される水平走査期間  $H$  の第 2 リセット期間  $T_{r2}$  に、第 2 リセット信号  $V_{r2}$  が供給され、その後、第 2 リセット信号  $V_{r2}$  が供給された水平走査期間  $H$  よりも期間  $R_2$  後に開始される水平走査期間  $H$  の第 2 書込期間  $T_{wd2}$  のうち、第 2 プリチャージ期間  $T_{wp2}$  に、第 2 プリチャージ信号  $V_{p2}$  が供給されると共に、第 2 画像信号書込期間  $T_{wd2}$  に、第 2 画像信号  $V_{d2}$  が供給される。

20

そして、これら  $N$  個の画素回路 2 3 には、第 2 画像信号  $V_{d2}$  が供給された水平走査期間  $H$  よりも期間  $V_2$  後に開始される水平走査期間  $H$  の第 1 リセット期間  $T_{r1}$  に、第 1 リセット信号  $V_{r1}$  が供給される。

【0057】

ところで、画素回路 2 3 の階調を指定する画像信号  $V_D$  は、前述の通り、保持容量  $C_O$  及び液晶素子 2 3 0 の容量により保持される。

すなわち、容量線 2 4 の電位  $V_c$  が基準電位  $V_{co}$  に保たれた状態で、当該容量線 2 4 に接続する画素回路 2 3 に画像信号  $V_D$  が供給されると、当該画素回路 2 3 の保持容量  $C_O$  には、その両電極間の電位差が  $V_D - V_{co}$  となるような電荷が蓄積される。そして、当該画素回路 2 3 の選択トランジスタ 2 3 5 がオフした後も、容量線 2 4 の電位  $V_c$  が基準電位  $V_{co}$  を保つ場合には、保持容量  $C_O$  の両電極間の電位差も  $V_D - V_{co}$  に保たれ、画素電極 2 3 1 の電位も画像信号  $V_D$  の示す電位に保たれる。この結果、当該画素回路 2 3 により表示される階調は、画像信号  $V_D$  の指定する階調となる。

30

【0058】

しかし、容量線 2 4 の電位  $V_c$  が基準電位  $V_{co}$  とは異なる電位  $V_{co} + V$  に変化したタイミングで、当該容量線 2 4 に接続する画素回路 2 3 に対して画像信号  $V_D$  が供給される場合、当該画素回路 2 3 の保持容量  $C_O$  には、両電極間の電位差が  $V_D - (V_{co} + V)$  となるような電荷が蓄積される。そして、画素回路 2 3 の選択トランジスタ 2 3 5 がオフした後に、容量線 2 4 の電位  $V_c$  が、電位  $V_{co} + V$  から、基準電位  $V_{co}$  へと変化する場合、画素電極 2 3 1 の電位も、画像信号  $V_D$  の示す電位から、画像信号  $V_D$  の示す電位とは異なる電位へと変化する。このとき、当該画素回路 2 3 により表示される階調は、画像信号  $V_D$  の指定する階調とは異なる階調となる。

40

【0059】

領域走査駆動方式とリセット駆動方式とを一体とした駆動方式では、一定の間隔を隔てた 2 行の走査線 2 1 に接続する 2 つの画素回路 2 3 に対して、交互に正極性及び負極性の画像信号  $V_D$  を供給するため、データ線 2 2 の電位も、交互に正極性及び負極性を繰り返すことになる。

Y 方向に延在する  $N$  本のデータ線 2 2 の各々は、X 方向に延在する  $M$  本の容量線 2 4 と

50

交差する。そして、各データ線 2 2 と各容量線 2 4 との間には寄生容量が存在する。従って、データ線 2 2 の電位（データ信号  $V_{id}$ ）が急激に変化した場合には、データ信号  $V_{id}$  の高周波成分の影響を受け、容量線 2 4 の電位  $V_c$  も変化する。そして、データ線 2 2 の電位変化が大きくなるに従って、また、電位変化の発生するデータ線 2 2 の本数が多くなるに従って、容量線 2 4 の電位  $V_c$  の変化も大きくなる。

#### 【0060】

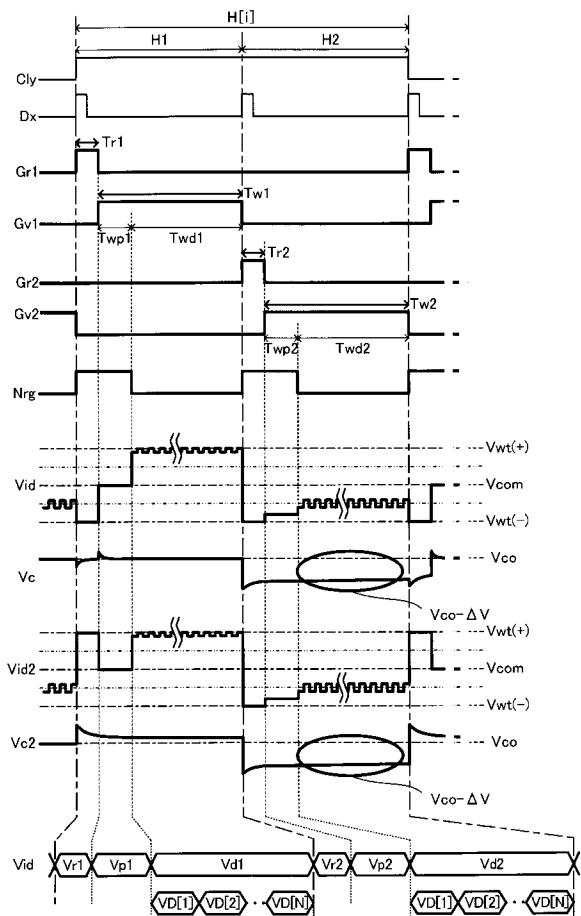

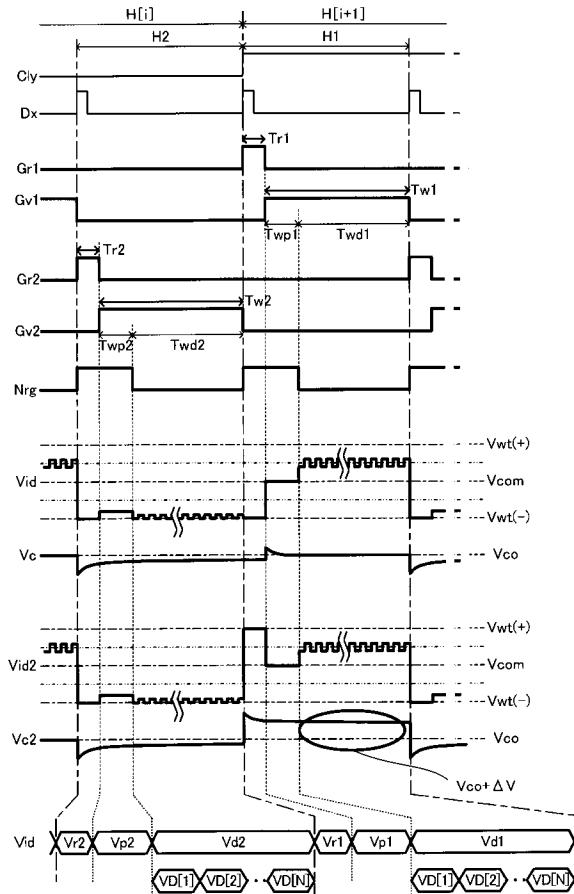

図 9 及び図 10 は、本実施形態に係る液晶装置 1 において、複数のデータ線 2 2 にデータ信号  $V_{id}$  が供給されたときの容量線電位  $V_c$  の変化を表したタイミングチャートである。

なお、本実施形態では、データ信号  $V_{id}$  の中に第 1 リセット信号  $V_{r1}$  及び第 2 リセット信号  $V_{r2}$  は共に負極性としているが、図 9 及び図 10 では、本実施形態と比較するための対比例として、第 1 リセット信号  $V_{r1}$  を正極性とした場合のデータ信号  $V_{id2}$  及びデータ信号  $V_{id2}$  がデータ線 2 2 に出力される場合の容量線電位  $V_{c2}$  の変化についても表示している。

10

#### 【0061】

図 9 は、水平走査期間  $H[i]$  の第 2 期間  $H2$  において、第 2 書込選択信号  $G_{v2}$  が選択する走査線 2 1 に接続する N 個の画素回路 2 3 の各々に対して供給される第 2 画像信号  $V_{d2}$ （画像信号  $V_D[1] \sim V_D[N]$ ）が、白表示相当の電圧  $V_{wt}$  に近い信号レベルであり、その後、水平走査期間  $H[i+1]$  の第 1 期間  $H1$  において、第 1 書込選択信号  $G_{v1}$  が選択する走査線 2 1 に接続する N 個の画素回路 2 3 の各々に対して供給される第 1 画像信号  $V_{d1}$ （画像信号  $V_D[1] \sim V_D[N]$ ）が、中間階調である場合を示している。

20

#### 【0062】

図 9 に示すように、対比例に係るデータ信号  $V_{id2}$  は、水平走査期間  $H[i+1]$  が開始されるタイミングで、負極性の白表示相当の電圧  $V_{wt}(-)$  から、第 1 リセット信号  $V_{r1}$  の指定する正極性の白表示相当の電圧  $V_{wt}(+)$  へと大きく変化する。つまり、N 本のデータ線 2 2 が、負極性の白表示相当の電圧  $V_{wt}(-)$  から、正極性の白表示相当の電圧  $V_{wt}(+)$  へと大きく変化する。この影響により、N 本のデータ線 2 2 と交差する M 本の容量線 2 4 の電位  $V_{c2}$  も、基準電位  $V_{co}$  相当の電位から、基準電位  $V_{co}$  よりも高い電位  $V_{co} + V$  へと変化する。そして、容量線 2 4 の電位  $V_{c2}$  が基準電位  $V_{co}$  に戻る前に、水平走査期間  $H[i+1]$  の第 1 画像信号書込期間  $T_{wd1}$  が開始される。

30

従って、水平走査期間  $H[i+1]$  において第 1 書込選択信号  $G_{v1}$  の選択する走査線 2 1 に接続する N 個の画素回路 2 3 には、容量線 2 4 の電位  $V_{c2}$  が電位  $V_{co} + V$  に変化している間に、第 1 画像信号  $V_{d1}$  が供給される。

#### 【0063】

その後、容量線 2 4 の電位  $V_{c2}$  が、電位  $V_{co} + V$  から、基準電位  $V_{co}$  に戻る場合、第 1 画像信号  $V_{d1}$  が供給された N 個の画素回路 2 3 の画素電極 2 3 1 の電位は、第 1 画像信号  $V_{d1}$  の指定する電位から、第 1 画像信号  $V_{d1}$  の指定する電位よりも低い電位に変化する。従って、これら N 個の画素回路 2 3 によって表示される階調の各々は、第 1 画像信号  $V_{d1}$  の指定する階調とは異なる階調となる。

40

このように、ある行の画素回路 2 3 に対して供給される負極性の画像信号  $V_D$  が高階調である場合には、当該画素回路 2 3 から、「 $mV1 + mR2 + 1$ 」行離れた行に位置する N 個の画素回路 2 3 によって表示される階調の各々は、正極性の画像信号  $V_D$  の指定する階調と異なる階調となる。

なお、容量線 2 4 の電位  $V_{c2}$  が、基準電位  $V_{co}$  から電位  $V_{co} + V$  へと変化する場合には、第 1 書込選択信号  $G_{v1}$  により選択される走査線 2 1 に接続する N 個の画素回路 2 3 以外の画素回路 2 3 によって表示される階調の各々は、画像信号  $V_D$  の指定する階調と異なる階調となる。容量線 2 4 の電位  $V_{c2}$  が変化すると、画素電極 2 3 1 の電位も変化し、画素電極 2 3 1 の電位を、画像信号  $V_D$  が示す電位に保てないためである。

50

## 【0064】

これに対して、本実施形態に係るデータ信号  $V_{id}$  は、第1リセット信号  $V_{r1}$  及び第2リセット信号  $V_{r2}$  が共に負極性となるように設定される。従って、水平走査期間  $H[i+1]$  が開始されるタイミングにおいて、データ信号  $V_{id}$  の示す電位に大きな変化は生じない。この場合、水平走査期間  $H[i+1]$  が開始されるタイミングで、M本の容量線24の電位  $V_c$  も、基準電位  $V_{co}$  に近い電位に保たれる。従って、水平走査期間  $H[i+1]$  において第1画像信号  $V_{d1}$  が供給されるN個の画素回路23によって表示される階調の各々は、水平走査期間  $H[i+1]$  以降、第1画像信号  $V_{d1}$  の指定する階調となる。

なお、前述の通り、本実施形態では、第1プリチャージ信号  $V_{p1}$  を、共通電位  $V_{co}$  に等しく設定している。これにより、第1リセット期間  $T_{r1}$  と第1書き込み期間  $T_{w1}$  の間で、データ信号  $V_{id}$  の示す電位の変動幅を小さく抑えることが可能となり、容量線24の電位  $V_c$  の変動を小さく抑えることが可能となる。

## 【0065】

図10は、水平走査期間  $H[i]$  において、第1画像信号  $V_{d1}$  が、白表示相当の電圧  $V_{wt}$  に相当する高階調の信号であり、第2画像信号  $V_{d2}$  が中間階調の信号である場合を示している。この場合、データ信号  $V_{id}$  及びデータ信号  $V_{id2}$  の双方は、第1画像信号書き込み期間  $T_{wd1}$  において、第1画像信号  $V_{d1}$  の指定する正極性の白表示相当の電圧  $V_{wt}(+)$  に相当する電位となり、その後、第2リセット期間  $T_{r2}$  が開始されるタイミングで、第2リセット信号  $V_{r2}$  の指定する負極性の白表示相当の電圧  $V_{wt}(-)$  に相当する電位へと大きく変化する。つまり、N本のデータ線22の電位は、正極性から負極性へと大きく変化するため、N本のデータ線22と交差するM本の容量線24の電位  $V_c$  も、基準電位  $V_{co}$  相当の電位から、基準電位  $V_{co}$  よりも低い電位  $V_{co}-V$  へと変化する。

その後、容量線24の電位  $V_c$  が基準電位  $V_{co}$  に戻る前に、第2画像信号書き込み期間  $T_{wd2}$  が開始される。従って、容量線24の電位  $V_c$  が電位  $V_{co}-V$  に変化している間に、第2書き込み選択信号  $G_{v2}$  の選択する走査線21に接続するN個の画素回路23に対して、第2画像信号  $V_{d2}$  が供給される。

よって、水平走査期間  $H[i]$  以降、容量線24の電位  $V_c$  が、基準電位  $V_{co}$  に戻る場合、これらのN個の画素回路23によって表示される階調の各々は、第2画像信号  $V_{d2}$  の指定する階調とは異なる階調となる。

## 【0066】

このように、本実施形態に係る液晶装置1は、対比例と同様に、ある画素回路23に供給される正極性の画像信号  $V_D$  が高階調である場合には、その後、負極性の画像信号  $V_D$  が供給される画素回路23によって表示される階調が、画像信号  $V_D$  により指定される階調とはならない場合がある。

しかし、本実施形態に係る液晶装置1は、領域走査駆動方式を採用し、ある画素回路23に対して、1垂直走査期間  $F$  の間に、正極性の第1画像信号  $V_{d1}$  と、負極性の第2画像信号  $V_{d2}$  とを供給する。従って、ある画素回路23に対して高階調な正極性の第1画像信号  $V_{d1}$  を供給する際に、当該画素回路23から「 $mV2 + mR1$ 」行離れた画素回路23において表示上の不具合が発生することがあるが、その後、1垂直走査期間  $F$  よりも短い期間の後に、当該画素回路23に、高階調な負極性の第2画像信号  $V_{d2}$  が供給される際に、表示上の不具合が解消される。

従って、画像信号  $V_D$  の指定する階調が高階調である場合に発生する、データ線22の急激な電位変化に伴う容量線24の電位変化に起因する表示上の不具合が、利用者に視認される可能性を低減させることが可能となる。

## 【0067】

以上、説明したように、上記実施形態によれば、液晶装置1の駆動方式として一定の間隔を隔てた2つの画素回路23に対してそれぞれ交互に正極性の画像信号（第1画像信号  $V_{d1}$ ）及び負極性の画像信号（第2画像信号  $V_{d2}$ ）の2つの画像信号  $V_D$  の書き込み

10

20

30

40

50

を行う領域走査駆動方式を採用すると共に、2つの画像信号V Dの書き込みを行う直前にリセット信号V rを書き込むリセット駆動方式を採用した。

本実施形態に係る液晶装置1は、領域走査駆動方式とリセット駆動方式とを一体とした駆動方式を実装することで、画面の場所による表示の不均一が解消されるという利点を有すると共に、液晶232の配向不良を抑制できるという利点を有する。

#### 【0068】

また、本実施形態は、第1リセット信号V r 1と第2リセット信号V r 2とを共に負極性とすることで、負極性の第1リセット信号V r 1がデータ線22に出力されるタイミングにおけるデータ線22の電位変化を小さく抑えた。

データ線22に急峻且つ大きな電位変化が発生する場合、その影響で容量線24の電位V cも変化する。容量線24の電位が変化する場合、当該容量線24に接続するN個の画素回路23によって表示される階調の各々は、画像信号V Dが指定する階調とは異なる階調となる。しかし、本実施形態では、第1リセット信号V r 1がデータ線22に出力されるタイミングにおけるデータ線22の電位変化を小さく抑えたため、画素回路23によって表示される階調を、第1画像信号V d 1の指定する階調とすることができます。

#### 【0069】

また、本実施形態は、第1書込入力パルスD v 1がアクティブになる時間から、第2リセット入力パルスD r 2がアクティブになる時間までの期間V 1が、第2書込入力パルスD v 2がアクティブになる時間から、第1リセット入力パルスD r 1がアクティブになる時間までの期間V 2よりも、長く設定される。つまり、ある水平走査期間Hにおいて、第1リセット信号V r 1が供給される走査線21と、第2リセット信号V r 2が供給される走査線21との間隔m V 1が、第2画像信号V d 2が供給される走査線21と、第1リセット信号V r 1が供給される走査線21との間隔m V 2よりも、大きくなる。

これにより、表示領域20において、正極性の電位を有する画素回路23が存在する領域と、負極性の電位を有する画素回路23が存在する領域とを、ほぼ等しい面積にすることができる、データ線22に印加される電位の1垂直走査期間Fにおける平均値が、正極性または負極性の一方に偏ることを防止することが可能となった。その結果、画素回路23とデータ線22との間の電位差の1垂直走査期間Fにおける平均値が、表示領域20内の位置に依存して大きく偏ることを防止でき、表示の不均一を防止することが可能となった。

#### 【0070】

また、本実施形態は、第1プリチャージ信号V p 1のレベルを、共通電位V c o mと等しくすることにより、第1リセット期間T r 1から第1書込期間T w 1に変化する際のデータ信号V i dの示す電位の変化を小さく抑えた。これにより、第1リセット期間T r 1から第1書込期間T w 1に変化するタイミングで、容量線24の電位V cの変化を小さく抑えることが可能となり、容量線24の電位変化に起因する表示上の不具合の発生を抑えることが可能となる。

#### 【0071】

次に、本実施形態では、リセット駆動を採用し、画素回路23に対して、画像信号V Dを供給する前に、リセット信号V rとして白表示相当の電圧V w tに相当する電圧を供給している。画素回路23がリセット信号V rを保持している時間は、画素回路23が画像信号V Dを保持している時間に比べて十分短い時間である。これにより、本実施形態に係る液晶装置1は、画素回路23によって表示される階調の変化を観察者に知覚されることなく、液晶232の配向不良を解消することが可能となるという利点を有する。

#### 【0072】

本実施形態では、画素回路23に対して、リセット信号V rとプリチャージ信号V pとを水平帰線期間H bにおいて供給している。これにより、本実施形態は、画素回路23に画像信号V Dを供給する期間である水平有効期間H aを短縮することなくリセット駆動とプリチャージとを可能とし、液晶素子230に対して画像信号V Dを書き込む期間をより長く確保することができるため、画像の安定的な表示が可能になるという利点を有す

10

20

30

40

50

る。

【0073】

また、本実施形態では、データ線駆動回路32は、第1リセット信号V<sub>r</sub>1、第2リセット信号V<sub>r</sub>2、第1画像信号V<sub>d</sub>1、第2画像信号V<sub>d</sub>2、第1プリチャージ信号V<sub>p</sub>1、及び第2プリチャージ信号V<sub>p</sub>2を時分割多重した信号であるデータ信号V<sub>i</sub>dを、データ線22に対して供給するものである。これにより、リセット信号V<sub>r</sub>が供給される配線、プリチャージ信号V<sub>p</sub>が供給される配線、及び画像信号V<sub>D</sub>が供給される配線を個別に設ける場合と比べて配線数の大幅な低減が可能であり、液晶装置1の小型化を可能にするという利点を有する。

【0074】

<B：変形例>

本発明は上述した実施形態に限定されるものではなく、例えば、以下の変形が可能である。また、以下に示す変形例のうちの2以上の変形例を組み合わせることもできる。

(1) 変形例

上述した実施形態では、第1リセット信号V<sub>r</sub>1及び第2リセット信号V<sub>r</sub>2を共に負極性の信号としているが、第1リセット信号V<sub>r</sub>1及び第2リセット信号V<sub>r</sub>2は、共通電位V<sub>com</sub>を基準として信号レベルが同極性であれば良い。

例えば、第1リセット信号V<sub>r</sub>1及び第2リセット信号V<sub>r</sub>2を共に正極性の信号としても良い。この場合には、ある水平走査期間Hの第1画像信号書込期間T<sub>wd</sub>1においてデータ線22に高階調の第1画像信号V<sub>d</sub>1を出力した場合であっても、その後の第2リセット期間T<sub>r</sub>2が開始されるタイミングにおいて、データ線22の電位が急激に変化することなく、容量線24の電位変化も抑制できるため、画素回路23により正確な階調を表示することができる。

【0075】

(2) 変形例2

上述した実施形態では、間隔m<sub>V</sub>1を、間隔m<sub>V</sub>2、間隔m<sub>R</sub>1、及び間隔m<sub>R</sub>2を合計した値に等しくなるように設定し、表示領域20において、正極性の信号を保持する画素回路23が存在する領域と、負極性の信号を保持する画素回路23が存在する領域とを、等しい面積としたが、間隔m<sub>V</sub>1を、間隔m<sub>V</sub>2、間隔m<sub>R</sub>1、及び間隔m<sub>R</sub>2を合計した値よりも大きな値に設定しても良い。

負極性の信号のうち、第1リセット信号V<sub>r</sub>1及び第2リセット信号V<sub>r</sub>2のレベルは、負極性の白表示相当の電圧V<sub>wt</sub>(-)であり、一方で、正極性の信号である第1画像信号V<sub>d</sub>1のレベルは、白表示相当の電圧V<sub>wt</sub>(+)よりも小さな電位である場合がある。従って、間隔m<sub>V</sub>1を、間隔m<sub>V</sub>2、間隔m<sub>R</sub>1、及び間隔m<sub>R</sub>2を合計した値よりも大きな値に設定し、第1画像信号V<sub>d</sub>1を保持する画素回路23が存在する領域を、負極性の信号を保持する画素回路23が存在する領域よりも大きくすることにより、1垂直走査期間Fにおいてデータ線22に供給される信号レベルの平均値が、正極性または負極性の一方に偏ることを防止することができる。これにより、表示領域20の表示する階調が全体として低階調である場合にも、表示領域20内の位置により画素回路23とデータ線22との電位差に偏りが発生することを防止し、表示不均一の発生を防止することが可能となる。

【0076】

(3) 変形例3

上述した実施形態では、各水平走査期間Hの中で、第1リセット選択信号G<sub>r</sub>1、第1書込選択信号G<sub>v</sub>1、第2リセット選択信号G<sub>r</sub>2、及び第2書込選択信号G<sub>v</sub>2の順番でアクティブになるが、これ以外の順番でアクティブとなっても良い。

例えば、第2リセット選択信号G<sub>r</sub>2、第2書込選択信号G<sub>v</sub>2、第1リセット選択信号G<sub>r</sub>1、及び第1書込選択信号G<sub>v</sub>1の順番でアクティブとしても良い。この場合にも、互いに異なる4つの画素回路23に対して、第1リセット信号V<sub>r</sub>1、第1プリチャージ信号V<sub>p</sub>1及び第1画像信号V<sub>d</sub>1、第2リセット信号V<sub>r</sub>2、及び第2プリチャージ

10

20

30

40

50

信号  $V_{p2}$  及び第 2 画像信号  $V_{d2}$  の各々を供給することができる。

また、第 1 書込選択信号  $G_{v1}$ 、第 1 リセット選択信号  $G_{r1}$ 、第 2 書込選択信号  $G_{v2}$ 、第 2 リセット選択信号  $G_{r2}$  の順番でアクティブとしても良い。この場合、制御信号  $N_{rg}$  は、第 1 書込選択信号  $G_{v1}$  がアクティブとなる期間のうち第 1 プリチャージ信号  $V_{p1}$  がデータ線 2 2 に出力される期間、第 1 リセット選択信号  $G_{r1}$  がアクティブとなる期間、第 2 書込選択信号  $G_{v2}$  がアクティブとなる期間のうち第 2 プリチャージ信号  $V_{p2}$  がデータ線 2 2 に出力される期間、及び第 2 リセット選択信号  $G_{r2}$  がアクティブとなる期間においてハイレベルになる。

#### 【0077】

##### (4) 変形例 4

上述した実施形態では、水平走査期間  $H$  の開始と第 1 リセット期間  $T_{r1}$  の開始とが同時であり、第 1 リセット期間  $T_{r1}$  の終了と第 1 書込期間  $T_{w1}$  の開始とが同時であり、第 1 書込期間  $T_{w1}$  の終了と第 2 リセット期間  $T_{r2}$  の開始とが同時であり、第 2 リセット期間  $T_{r2}$  の終了と水平走査期間  $H$  とが同時であるが、これら各種期間の開始または終了を、異なるタイミングとしても良い。

例えば、水平走査期間  $H$  が開始された後、間隔をあけて第 1 リセット期間  $T_{r1}$  を開始し、第 1 リセット期間  $T_{r1}$  終了後、間隔をあけて第 1 書込期間  $T_{w1}$  を開始し、第 1 書込期間  $T_{w1}$  終了後、間隔をあけて第 2 リセット期間  $T_{r2}$  を開始し、第 2 リセット期間  $T_{r2}$  終了後、間隔をあけて第 2 書込期間  $T_{w2}$  を開始しても良い。

#### 【0078】

##### (5) 変形例 5

上述した実施形態においては、プリチャージ信号  $V_p$  をデータ線 2 2 に供給したが、本発明はこれに限定されるものではなく、プリチャージ信号  $V_p$  を供給しなくてもよい。この場合、データ信号  $V_{id}$  は、リセット信号  $V_r$  と画像信号  $V_D$  とから構成される。また、第 1 書込期間  $T_{w1}$  は正極性の画像信号  $V_D$  を書き込むための第 1 画像信号書込期間  $T_{wd1}$  と一致し、第 2 書込期間  $T_{w2}$  は負極性の画像信号  $V_D$  を書き込むための第 2 画像信号書込期間  $T_{wd2}$  と一致する。

#### 【0079】

##### (6) 変形例 6

上述した実施形態においては、第 1 プリチャージ信号  $V_{p1}$  のレベルを、共通電位  $V_{com}$  と等しくなるように設定したが、第 1 プリチャージ信号  $V_{p1}$  のレベルを、第 1 リセット信号  $V_{r1}$  のレベルから、共通電位  $V_{com}$  までの範囲としても良い。この場合、第 1 リセット期間  $T_{r1}$  から第 1 書込期間  $T_{w1}$  に変化するタイミングで、容量線 2 4 の電位  $V_c$  の変化を小さく抑えることが可能となり、容量線 2 4 の電位変化に起因する表示上の不具合の発生を抑止することが可能となる。

#### 【0080】

##### (7) 変形例 7

上述した実施形態においては、第 1 プリチャージ信号  $V_{p1}$  のレベルを、共通電位  $V_{com}$  と等しくなるように設定し、第 2 プリチャージ信号  $V_{p2}$  のレベルを、負極性の白表示相当の電圧  $V_{wt}(-)$  から、共通電位  $V_{com}$  及び負極性の白表示相当の電圧  $V_{wt}(+)$  の中間の電位  $\{(V_{com} + V_{wt}(-)) / 2\}$  までの範囲となるように設定しているが、第 1 プリチャージ信号  $V_{p1}$  のレベルを、第 1 画像信号  $V_{d1}$  が取り得る範囲に設定し、第 2 プリチャージ信号  $V_{p2}$  のレベルを、第 2 画像信号  $V_{d2}$  が取り得る範囲に設定しても良い。

例えば、第 1 プリチャージ信号  $V_{p1}$  を、正極性の白表示相当の電圧  $V_{wt}(+)$  と共通電位  $V_{com}$  の中間の電位  $\{(V_{com} + V_{wt}(+)) / 2\}$  とし、第 2 プリチャージ信号  $V_{p2}$  を、負極性の白表示相当の電圧  $V_{wt}(-)$  と共通電位  $V_{com}$  の中間の電位  $\{(V_{com} + V_{wt}(-)) / 2\}$  としても良い。この場合、データ線 2 2 の電位が、画像信号  $V_D$  に近い電位となるため、画素回路 2 3 に対する画像信号  $V_D$  の印加を容易にすることができます。

## 【0081】

## (8) 変形例8

上述した実施形態においては、リセット信号 $V_r$ のレベルを白表示相当の電圧 $V_{wt}$ としたリセット駆動を採用しているが、リセット信号 $V_r$ のレベルを、これよりも小さな電圧、例えば、光学的飽和電圧 $V_{sat}$ としても良い。光学的飽和電圧 $V_{sat}$ は、液晶232が配向不良の状態から脱するために十分な大きさの電圧であり、液晶素子230に光学的飽和電圧 $V_{sat}$ 相当のリセット信号 $V_r$ を印加するリセット駆動を採用することで、液晶232の配向不良の問題を解決することができる。

## 【0082】

## (9) 変形例9

上述した実施形態において、液晶232はVA方式であったが、TN (Twisted Nematic) 方式の液晶232を採用しても良い。また、上述した実施形態において、液晶装置1はノーマリーブラックモードであったが、ノーマリーホワイトモードであっても良い。この場合、リセット信号 $V_r$ のレベルを、例えば、黒表示相当の電圧 $V_{bk}$ としても良い。

## 【0083】

## &lt;C:応用例&gt;

次に、以上の各様に係る液晶装置1を利用した電子機器について説明する。図11ないし図13には、液晶装置1を表示装置として採用した電子機器の形態が図示されている。

図11は、液晶装置1を採用したモバイル型のパーソナルコンピュータの構成を示す斜視図である。パーソナルコンピュータ2000は、各種の画像を表示する液晶装置1と、電源スイッチ2001やキーボード2002が設置された本体部2010とを具備する。

## 【0084】

図12は、液晶装置1を適用した携帯電話機の構成を示す斜視図である。携帯電話機3000は、複数の操作ボタン3001及びスクロールボタン3002と、各種の画像を表示する液晶装置1とを備える。スクロールボタン3002を操作することによって、液晶装置1に表示される画面がスクロールされる。

## 【0085】

図13は、投写型表示装置(プロジェクタ)4000を電子機器として例示する模式図である。投射型表示装置4000は、照明装置4020と分離光学系4040と以上の各形態に係る3個の表示パネル10(10r、10g、10b)と投射光学系4060と図示せぬ制御回路40(40r、40g、40b)とを具備する。

3つの制御回路40は、3つの表示パネル10の間で画像表示の同期を取りつつ、リセット駆動及び領域走査駆動がなされるように、各種制御信号を生成する。また、3つの制御回路40は、それぞれ、外部上位装置より供給される赤色、緑色、青色を表す表示データVIDEO(VIDEO\_r、VIDEO\_g、VIDEO\_b)に基づき、赤色、緑色、青色に対応するデータ信号VID(VID\_r、VID\_g、VID\_b)を生成する。

各表示パネル10には、3つの制御回路40より、それぞれ、各種制御信号と、赤色、緑色、青色に対応するデータ信号VIDとが供給される。

分離光学系4040は、照明装置4020から出射した照明光を複数の単色光(赤色光、緑色光、青色光)に分離して各表示パネル10に照射する。具体的には、照明光のうちの赤色光rは、ダイクロイックミラー4041及びミラー4042による反射後に表示パネル10rに入射する。ダイクロイックミラー4041を透過した緑色光gは、ダイクロイックミラー4043にて反射されて表示パネル10gに入射する。ダイクロイックミラー4043を透過した青色光bは、ミラー4044及びミラー4045を介して表示パネル10bに入射する。

各表示パネル10は、入射光を変調して画像を形成する光変調器(ライトバルブ)として利用される。表示パネル10rは、ミラー4042から到来する赤色光rを変調して赤色の画像を形成する。同様に、表示パネル10gは緑色の画像を形成し、表示パネル10bは青色の画像を形成する。投射光学系4060は、各表示パネル10からの出射光を表

10

20

30

40

50

示面 4080 に投射する。投射光学系 4060 は、各表示パネル 10 からの出射光（赤色光、緑色光、青色光）を合成するダイクロイックプリズム 4061 と、ダイクロイックプリズム 4061 からの出射光を表示面 4080 に投射する投射レンズ 4062 とを含んで構成される。したがって、表示面 4080 にはカラー画像が表示される。

### 【0086】

なお、本発明に係る液晶装置が適用される電子機器としては、図 11 から図 13 に例示した機器のほか、携帯情報端末（PDA：Personal Digital Assistants）、デジタルスチルカメラ、テレビ、ビデオカメラ、カーナビゲーション装置、ページャ、電子手帳、電子ペーパー、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS 端末、プリンタ、スキャナ、複写機、ビデオプレーヤ、タッチパネルを備えた機器等などが挙げられる。

10

### 【符号の説明】

### 【0087】

1 … 液晶装置、21 … 走査線、22 … データ線、23 … 画素回路、230 … 液晶素子、231 … 画素電極、235 … 選択トランジスタ、24 … 容量線、31 … 走査線駆動回路、32 … データ線駆動回路、R1 … 第 3 期間、R2 … 第 4 期間、V1 … 第 1 期間、V2 … 第 2 期間、CO … 保持容量、Gr1 … 第 1 リセット選択信号、Gr2 … 第 2 リセット選択信号、Gv1 … 第 1 書込選択信号、Gv2 … 第 2 書込選択信号、Tr1 … 第 1 リセット期間、Tr2 … 第 2 リセット期間、Twd1 … 第 1 画像信号書込期間、Twd2 … 第 2 画像信号書込期間、Twp1 … 第 1 プリチャージ期間、Twp2 … 第 2 プリチャージ期間、Vc … 容量線電位、Vcom … 共通電位、Vd1 … 第 1 画像信号、Vd2 … 第 2 画像信号、Vp1 … 第 1 プリチャージ信号、Vp2 … 第 2 プリチャージ信号、Vr1 … 第 1 リセット信号、Vr2 … 第 2 リセット信号。

20

【図 1】

【図 2】

【図3】

(D) 画面 (T-T3)

【 図 6 】

【 図 4 】

【図5】

【 図 7 】

【図8】

【 図 1 0 】

〔 四 9 〕

【 図 1 1 】

【 図 1 2 】

【図 1 3】

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

G 0 2 F 1/133 5 7 5

F ターム(参考) 2H193 ZA04 ZA07 ZB03 ZB06 ZB13 ZC16 ZC24 ZD02 ZD23 ZD34

ZE06 ZF05 ZF11 ZF22 ZF36 ZF44 ZQ11 ZR04

5C006 AA14 AA16 AC26 AF33 BB16 BC20 EC11 FA21 FA34

5C080 AA10 BB05 DD01 DD29 FF11 JJ02 JJ04 KK02 KK47

|                |                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置及び電子機器                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2012220910A</a>                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2012-11-12 |

| 申请号            | JP2011089825                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2011-04-14 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 小林淳也                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 小林 淳也                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/36 G09G3/20.621.B G09G3/20.641.E G09G3/20.641.C G02F1/133.550 G02F1/133.575                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H193/ZA04 2H193/ZA07 2H193/ZB03 2H193/ZB06 2H193/ZB13 2H193/ZC16 2H193/ZC24 2H193/ZD02 2H193/ZD23 2H193/ZD34 2H193/ZE06 2H193/ZF05 2H193/ZF11 2H193/ZF22 2H193/ZF36 2H193/ZF44 2H193/ZQ11 2H193/ZR04 5C006/AA14 5C006/AA16 5C006/AC26 5C006/AF33 5C006/BB16 5C006/BC20 5C006/EC11 5C006/FA21 5C006/FA34 5C080/AA10 5C080/BB05 5C080/DD01 5C080/DD29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/KK02 5C080/KK47 |         |            |

| 代理人(译)         | 须泽 修<br>宮坂和彦                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

### 摘要(译)

要解决的问题：实现一种集成了区域扫描驱动方法和复位驱动方法的驱动方法。液晶装置1包括多条扫描线21，多条数据线22，与多条数据线22交叉的多条电容线23，多条扫描线21和多条数据对应于与线22交叉设置的多个像素电路23，扫描线驱动电路31和数据线驱动电路32。数据线驱动电路32提供第一输出复位信号Vr 1，在第一图像信号写入时段Twd 1中输出第一图像信号Vd 1，在第二复位时段Tr 2中输出具有与第一复位信号Vr 1相同极性的第二复位信号Vr 2，并且输出在2图像信号写入时段Twd 2中具有与第一图像信号Vd 1的极性相反的极性的第二图像信号Vd 2。点域1