(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-230744

(P2010-230744A)

(43) 公開日 平成22年10月14日(2010.10.14)

(51) Int.Cl.

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1343

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 未請求 請求項の数 13 O L (全 24 頁)

(21) 出願番号

特願2009-75454 (P2009-75454)

(22) 出願日

平成21年3月26日 (2009.3.26)

(71) 出願人 508375398

ビデオコン グローバル リミテッド

Videocon Global Limitedプリティッシュ ヴィージン アイランド、

トートラ、ロード タウン、インターナシ

ヨナル トラスト ビルディング、ピー.

オー. ボックス 659

International Trust

Building, P. O. Box

659, Road Town, Ta

rtola, British Virg

in Island

(74) 代理人 100106699

弁理士 渡部 弘道

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【要約】

【課題】FFSモードの液晶表示装置において、保持容量を増加させることなく液晶に印加される電界強度を維持又は増加させ、液晶駆動電圧の低電圧化、及びこれにともなう信号線ドライバー回路の発熱防止、高フレームレート化を実現する。

【解決手段】液晶の誘電率よりも誘電率の小さい絶縁層をコモン電極と複数のスリットが設けられている画素電極との間に設け、画素電極のスリット下の絶縁層の厚さを画素電極の透明導電層下の絶縁層の厚さよりも薄くなるように絶縁層をエッチングする。これにより、スリット下の絶縁層には凹部が形成され、液晶に印加される電界強度が増加し、より低電圧駆動が可能となる。また、絶縁層を一様に薄くするものではないため、保持容量の増加は少ない。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

対向する基板間に液晶を挟持し一方の該基板上に画素部がマトリックス状に複数形成されてなる液晶表示装置であって、

スリットを複数備え透明導電層からなる画素電極と、

該画素電極と平面視で重なり合うように形成されてなり該画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極と、

該コモン電極の上に形成され該スリットの下の厚さが該画素電極の該透明導電層の下の厚さよりも薄く該液晶の誘電率よりも小さい誘電率を備える絶縁層と、

該画素電極に接続された薄膜トランジスタと

を該画素部に備えることを特徴とする液晶表示装置。

10

**【請求項 2】**

前記液晶の誘電率異方性が正であって、該液晶の誘電率が該液晶の液晶分子の長軸方向の誘電率であることを特徴とする請求項 1 記載の液晶表示装置。

**【請求項 3】**

前記液晶表示装置はノーマルブラックモードの液晶表示装置であることを特徴とする請求項 1 又は請求項 2 記載の液晶表示装置。

**【請求項 4】**

前記絶縁層の前記スリットの下の厚さが前記透明導電層の下の厚さよりも薄くなるような凹部が該絶縁層に形成されてなることを特徴とする請求項 1 ないし請求項 3 のいずれかに記載の液晶表示装置。

20

**【請求項 5】**

前記画素電極の平面形状が、櫛歯状、階段状、梯子状又はマルチドメイン構造をなすことを特徴とする請求項 1 ないし請求項 4 のいずれかに記載の液晶表示装置。

**【請求項 6】**

前記絶縁層は前記薄膜トランジスタのゲート絶縁膜と該ゲート絶縁膜及び該薄膜トランジスタの上に形成されたパッシベーション層とを含む積層構造を備え、前記コモン電極は該ゲート絶縁膜の下に形成されていることを特徴とする請求項 1 ないし請求項 5 のいずれかに記載の液晶表示装置。

30

**【請求項 7】**

前記絶縁層は前記薄膜トランジスタの上に形成されたパッシベーション層を含み、前記コモン電極は該パッシベーション層の下であって該薄膜トランジスタのゲート絶縁膜の上に形成されていることを特徴とする請求項 1 ないし請求項 5 のいずれかに記載の液晶表示装置。

**【請求項 8】**

前記薄膜トランジスタの半導体層は In、Ga 及び Zn を含む透明酸化物半導体からなり、前記コモン電極が紫外線の照射により高導電率化された In、Ga 及び Zn を含む透明酸化物からなることを特徴とする請求項 7 記載の液晶表示装置。

**【請求項 9】**

対向する基板間に液晶を挟持する液晶表示装置の製造方法であって、

画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極を一方の該基板上に形成する第 1 工程と、

該液晶の誘電率よりも小さい誘電率を備える絶縁層を該コモン電極の上に形成する第 2 工程と、

スリットを複数備え透明導電層からなる画素電極を該コモン電極と平面視で重なり合うように該絶縁層の上に形成する第 3 工程と、

40

該絶縁層の該スリットの下の厚さが該透明導電層の下の厚さよりも薄くなるように該絶縁層にエッチングを施す第 4 工程と

を含むことを特徴とする液晶表示装置の製造方法。

**【請求項 10】**

50

対向する基板間に液晶を挟持する液晶表示装置の製造方法であって、

第1金属層からなる薄膜トランジスタのゲート電極を一方の該基板上に形成する第1工程と、

該ゲート電極の上に第1絶縁層を形成する第2工程と、

画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極を該第1絶縁層の上に形成する第3工程と、

該第1絶縁層の上にアモルファスシリコン半導体からなる該薄膜トランジスタの半導体層及び低抵抗半導体層を順に形成する第4工程と、

該低抵抗半導体層の上に第2金属層からなるソース電極及びドレイン電極を形成する第5工程と、

該第2金属層、該低抵抗半導体層及び該コモン電極の上に該液晶の誘電率よりも小さい誘電率を備える第2絶縁層を形成する第6工程と、

該ソース電極と導通しスリットを複数備え透明導電層からなる該画素電極を該コモン電極と平面視で重なり合うように該第2絶縁層の上に形成する第7工程と、

該第2絶縁層の該スリットの下の厚さが該透明導電層の下の厚さよりも薄くなるように該第2絶縁層にエッチングを施す第8工程と

を含むことを特徴とする液晶表示装置の製造方法。

#### 【請求項 1 1】

対向する基板間に液晶を挟持する液晶表示装置の製造方法であって、

第1金属層からなる薄膜トランジスタのゲート電極を一方の該基板上に形成する第1工程と、

該ゲート電極の上に第1絶縁層を形成する第2工程と、

画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極と該薄膜トランジスタの半導体層とを  $I_n$ 、 $G_a$  及び  $Z_n$  を含む透明酸化物半導体を材料として該第1絶縁層の上に形成する第3工程と、

該半導体層のソース領域、ドレイン領域及びコモン電極に紫外線を照射することにより高導電率化する第4工程と、

該ソース領域及び該ドレイン領域の上に第2金属層からなるソース電極及びドレイン電極をそれぞれ形成する第5工程と、

該第2金属層、該半導体層及び該コモン電極の上に該液晶の誘電率よりも小さい誘電率を備える第2絶縁層を形成する第6工程と、

該ソース電極と導通しスリットを複数備え透明導電層からなる該画素電極を該コモン電極と平面視で重なり合うように該第2絶縁層の上に形成する第7工程と、

該第2絶縁層の該スリットの下の厚さが該透明導電層の下の厚さよりも薄くなるように該第2絶縁層にエッチングを施す第8工程と

を含むことを特徴とする液晶表示装置の製造方法。

#### 【請求項 1 2】

前記エッチングは、前記スリットを備える前記画素電極をマスクとして行うこと特徴とする請求項 9 ないし請求項 1 1 のいずれかに記載の液晶表示装置の製造方法。

#### 【請求項 1 3】

前記エッチングは、6フッ化イオウ、塩素、又はテトラフルオロカーボンのいずれかを含むガスを用いたドライエッチングによってなされること特徴とする請求項 9 ないし請求項 1 2 のいずれかに記載の液晶表示装置の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0 0 0 1】

本発明は、液晶表示装置及びその製造方法に関し、特に、FFS (Fringe Field Switching) モードで動作するアクティブマトリックス型の液晶表示装置の画素部の構造に関する。

#### 【背景技術】

## 【0002】

近年、表示装置の一つとしてアクティブマトリックス型の液晶表示装置が広く利用されている。そして、液晶の動作モードについても、いわゆる TN (Twisted Nematic) モード、VA (Vertical Alignment) モードのように 2 枚の基板によって挟持された液晶層に対して垂直方向（縦方向）に発生させたいわゆる縦電界によって液晶分子の配向を制御する方式だけでなく、IPS (In-Plane Switching) モードのように、液晶層に対して平行な方向（横方向）に発生させたいわゆる横電界によって液晶分子の配向を制御する方式が実用化されるようになってきた。さらに、最近では、FFS モードの液晶表示装置が提案されている。FFS モードは、一般に IPS モードよりもより低電圧で駆動することができ、同一基板上の異なる層に形成した画素電極とコモン電極との間に発生させたフリンジ電界（斜め電界とも呼ばれる）によって液晶分子の配向を制御する方式である。そして、この FFS モードは、視野角、透過率に特に優れるため、テレビ受像機等の大型液晶表示装置に十分利用できることが知られている（特許文献 1 等）。

10

## 【先行技術文献】

## 【特許文献】

## 【0003】

【特許文献 1】特開 2001-235763 号公報

20

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

しかしながら、FFS モードで動作する液晶表示装置においては、液晶の駆動電圧、即ち画素電極とコモン電極との間に印加すべき電圧が IPS モードほどではないが、TN モードに比べて高い。そのため消費電力も多くなり、その結果、高いフレームレート（フレーム周波数）で駆動する場合には液晶を駆動するドライバー回路等の駆動装置、特に、画像信号を供給する信号線ドライバー回路の発熱の問題が生じる。フレームレートは、ある画素に書き込みを行った後再度書き込みがなされるまでに時間の逆数であり、従来は 60 Hz が一般的であるが、より高いフレームレートで駆動することにより、表示画面のちらつきを防止するとともに動画表示性能を改善して液晶表示装置の表示品質をより向上させることができ期待されている。

30

## 【0005】

液晶の駆動電圧を低下させる手段としては、画素電極とコモン電極の間のパッシベーション層等の絶縁層の厚さを一様に薄くすることが考えられる。しかし、画素電極とコモン電極との間の絶縁層を単純に一様に薄くしても画素電極とコモン電極との間に形成される保持容量（蓄積容量） $C_s$  が著しく増大してしまうため、このような手段は画像信号の画素電極への書き込み時間を確保して画像信号の電圧に応じた電荷を十分に画素電極に充電するという観点からは不利であり、高フレームレートのもとではいわゆる選択期間が短くなりとりわけ困難が生じる。従って、高フレームレートでの書き込み動作を確実にするためには、保持容量の著しい増加が生じるような手段は好ましくない。

## 【0006】

40

また、低消費電力化のために液晶の印加電圧を単純に低下させても、液晶が所定の速度で駆動され表示素子として十分な光変調機能を果たすためには、液晶には一定の強さの電界が印加される必要がある。従って、単に印加電圧を低下させるだけではなく、液晶に印加される電界強度を維持又は増加させるような手段が必要とされる。

## 【0007】

50

信号線ドライバー回路等の駆動装置の発熱を防止し、書き込み速度を向上するという両者を実現する技術としては、薄膜トランジスタ及び画素を千鳥配置するとともに列毎反転駆動をするという手段も考えられる（特開 2007-47664）。しかし、この方法は、ゲート電極を構成する層と信号線を構成する層との合わせズレにより、ゲート・ソース間容量  $C_{gs}$  のばらつきが千鳥状に発生し画質上問題となる場合があり、ソース電極等のパターン形状にもよるが、特に 方向に合わせズレが生じたときに問題となりやすい。

## 【0008】

本発明は、以上の点に鑑みてなされたものであり、液晶に印加される電界強度を維持又は増加させつつ、液晶の駆動電圧を低下させることができる液晶表示装置を提供することを目的とする。また、本発明は、駆動電圧の低下により、信号線ドライバー回路等の駆動装置の発熱を低減し、より低消費電力の液晶表示装置を提供することを目的とする。さらに、保持容量の増加を抑えることにより、フレームレートを高速化しても書き込み動作を確実に行うことができる、より表示品質の高い液晶表示装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0009】

本発明にかかる液晶表示装置は、対向する基板間に液晶を挟持し一方の該基板上に画素部がマトリックス状に複数形成されてなる液晶表示装置であって、スリットを複数備え透明導電層からなる画素電極と、該画素電極と平面視で重なり合うように形成されてなり該画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極と、該コモン電極の上に形成され該スリットの下の厚さが該画素電極の該透明導電層の下の厚さよりも薄く該液晶の誘電率よりも小さい誘電率を備える絶縁層と、該画素電極に接続された薄膜トランジスタとを該画素部に備えることを特徴とする。

10

## 【0010】

本発明は、かかる構成をとることにより、コモン電極の上に絶縁層が形成されており、その上にスリットを備え透明導電層からなる画素電極がコモン電極と平面視で重なり合うように形成される。そして、層を異にする画素電極とコモン電極との間に生じるフリンジ電界によって液晶の配向が制御されるFFSモードの液晶表示装置が構成される。そして、スリットの下の絶縁層の厚さが画素電極の透明導電層の下の絶縁層の厚さよりも薄くなるように形成されているため、スリット下にも液晶が入り込み、スリット下の絶縁層の表面は液晶と絶縁層との界面となり、また、画素電極から液晶層及び絶縁層を経由してコモン電極に至るまでの電極間においては、絶縁層の厚さを薄くした分(寸法d2)だけ液晶層の厚さが厚くなる。そして、絶縁層の誘電率よりも誘電率が高い液晶を用いているため、このような構造においては、画素電極とコモン電極との間に印加される電圧Vが同じ場合に、画素電極と液晶と絶縁層界面との間に印加される電界強度、即ち液晶層に印加される電界強度は、スリット下の絶縁層を薄くしない(d2=0)構造のものと比べて増加する。

20

## 【0011】

言い換えれば、液晶層と同じ電界強度で配向制御を行うのであれば、液晶の駆動電圧V、即ち画素電極とコモン電極との間に印加される電圧Vを低下させても液晶分子の配向を十分に制御することができ、液晶の駆動電圧は低くてもよいことになり、その結果、液晶の駆動電圧の低電圧化及び低消費電力化を実現することができる。また、スリット下の絶縁層を薄くしても、保持容量Csは画素電極の透明導電層とコモン電極と間に液晶層を経由することなく直接に形成される容量Ci2によってそのほとんどが構成されており、しかも透明導電層下の絶縁層の厚さを変更するものではないから容量Ci2が増加しない。そのため、スリット下の絶縁層を薄くすることによる保持容量Csの増加は少ない。従つて、本発明によれば、液晶に印加される電界強度を維持又は増加させつつ、液晶の駆動電圧を低下させることができる液晶表示装置を提供することができる。また、駆動電圧の低下により、信号線ドライバー回路等の駆動装置の発熱を低減し、より低消費電力の液晶表示装置を提供することができる。さらに、保持容量の増加を抑えることができるため、書き込み動作を確実に行うことができフレームレートの高速化が可能となり、より表示品質が向上した液晶表示装置を提供することができる。

30

## 【0012】

本発明にかかる液晶表示装置は、前記液晶の誘電率異方性が正であって、該液晶の誘電率が該液晶の液晶分子の長軸方向の誘電率であることを特徴とする。本発明は、かかる構成をとることにより、誘電率異方性が正であるような液晶においては、液晶分子は駆動電圧印加時に液晶分子の長軸方向が液晶層内に生じた電界及び電気力線と平行となるように

40

50

配列させられる。そのため、液晶に電圧を印加した状態における液晶の誘電率は液晶分子の長軸方向の誘電率  $\epsilon_{\parallel}$  が支配的になる。従って、液晶分子の長軸方向の誘電率  $\epsilon_{\parallel}$  が絶縁層の誘電率よりも大きい液晶材料を用いることにより、より低い駆動電圧であっても液晶に印加される電界強度を維持又は増加し、液晶を十分に駆動することができる。

#### 【0013】

本発明にかかる液晶表示装置は、前記液晶表示装置はノーマルブラックモードの液晶表示装置であることを特徴とする。FFSモードの液晶表示装置の場合には、液晶に電界が印加されていないとき（ノーマル時）に黒表示（暗表示）となり、電界が印加されているときに白表示（明表示）となるノーマルブラックモードで動作するような構造のものが一般的に使用される。本発明は、かかる構成をとることにより、液晶の駆動電圧を低電圧化しても液晶の電界強度は低下しないため、ノーマルブラックモードの液晶表装置であっても十分な白表示を行うことができ、表示品質を向上させることができる。

10

#### 【0014】

また、ノーマルブラックモードで動作するFFSモードの液晶表示装置において、誘電率異方性  $\epsilon_{\perp} - \epsilon_{\parallel}$  が正であるような液晶（ポジ型液晶）を用いることにより、電界印加時に液晶分子の長軸が電界方向、即ち電気力線と平行になるように配列する。従って、ノーマルブラックモードで動作するFFSモードの液晶表示装置において液晶にフリンジ電界が印加され白表示をしている状態においては、その液晶の誘電率、特に、液晶分子の長軸に平行な方向の誘電率  $\epsilon_{\perp}$  が液晶分子の長軸に直角な方向の誘電率  $\epsilon_{\parallel}$  よりも大きければ、液晶分子はその長軸方向をフリンジ電界と平行になるように配列させられる。換言すれば、信号線ドライバー回路は、このような白表示に必要とされる強さの電界を生じさせる必要があるため、本発明によれば、駆動電圧を低下させても液晶の電界強度は低下することではなく十分な白表示を行うことができ、しかも信号線ドライバー回路の発熱を抑制することができる。

20

#### 【0015】

本発明にかかる液晶表示装置は、前記絶縁層の前記スリットの下の厚さが前記透明導電層の下の厚さよりも薄くなるような凹部が該絶縁層に形成されてなることを特徴とする。

#### 【0016】

本発明は、かかる構成をとることにより、スリット下の絶縁層に凹部が形成されることになり、凹部の底部にまで液晶が入り込む。従って、上記効果を奏すとともに、凹部の深さや数、形状、寸法等を制御することにより液晶に印加される電界強度や低電圧化の程度を制御することができる。

30

#### 【0017】

本発明にかかる液晶表示装置は、前記画素電極の平面形状が、櫛歯状、階段状、梯子状又はマルチドメイン構造をなすことを特徴とする。本発明は、かかる構成をとることにより、前記効果を奏すだけでなく、フリンジ電界を効率的に発生させ液晶分子をむらなく配向させることができる。また、マルチドメイン構造の電極形状をもつことによって、一つの画素部内での色変化を抑えることができる。

#### 【0018】

本発明にかかる液晶表示装置は、前記絶縁層は前記薄膜トランジスタのゲート絶縁膜と該ゲート絶縁膜及び該薄膜トランジスタの上に形成されたパッシベーション層とを含む積層構造を備え、前記コモン電極は該ゲート絶縁膜の下に形成されていることを特徴とする。本発明は、かかる構成をとることにより、コモン電極と画素電極の透明導電層との間の絶縁層の厚さを確保することができ両電極間の距離が短くなることはない。従って、コモン電極と画素電極の透明導電層との間の絶縁層の厚さを一様に薄くする必要がなく、保持容量の増加を抑えつつ液晶に印加される電界強度を維持又は増加させ、駆動電圧の低電圧化等の上記効果を奏することができる。

40

#### 【0019】

本発明にかかる液晶表示装置は、前記絶縁層は前記薄膜トランジスタの上に形成されたパッシベーション層を含み、前記コモン電極は該パッシベーション層の下であって該薄膜

50

トランジスタのゲート絶縁膜の上に形成されていることを特徴とする。本発明は、かかる構成をとることにより、コモン電極と画素電極の透明導電層との間の絶縁層の厚さは一様にゲート絶縁膜の厚さ分だけ薄くなるため、それだけでその分だけ保持容量も液晶に印加される電界強度も相対的に増加する。しかし、駆動電圧の低減が望まれる場合には、このような構成によっても画素電極の透明導電層下の絶縁層の厚さよりもスリット下の絶縁層の厚さを薄くすることにより、さらに液晶に印加される電界強度を維持又は増加させて駆動電圧の低電圧化及び低消費電力化を行うことができる。また、パッシベーション層の誘電率が液晶の誘電率よりも小さければ足り、ゲート絶縁膜の誘電率にかかわらないため、絶縁材料や液晶材料の選択の幅を広げることができる。

## 【0020】

本発明にかかる液晶表示装置は、前記薄膜トランジスタの半導体層はIn、Ga及びZnを含む透明酸化物半導体からなり、前記コモン電極が紫外線の照射により高導電率化されたIn、Ga及びZnを含む透明酸化物からなることを特徴とする。本発明は、かかる構成をとることにより、透明であるだけでなく移動度も比較的高い透明酸化物半導体を用いて薄膜トランジスタ及びコモン電極を形成することができる。特に、In、Ga及びZnを含む透明酸化物（以下、「IGZO」という）からなる半導体の場合には、成膜時に酸素分圧等の条件を調整することにより導電率を高めることができ、また、成膜後においてもIGZOに紫外線照射等を行うことにより導電材料並みに導電率を高めることができあり、移動度も向上するため、薄膜トランジスタの駆動能力を向上させることができ、また、薄膜トランジスタの半導体層とコモン電極とを同一材料及び同一工程で形成できる。従って、コモン電極の形成のみを目的とした製造工程は不要となり、製造工程の合理化に寄与する。

10

20

30

40

50

## 【0021】

本発明にかかる液晶表示装置の製造方法は、対向する基板間に液晶を挟持する液晶表示装置の製造方法であって、画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極を一方の該基板上に形成する第1工程と、該液晶の誘電率よりも小さい誘電率を備える絶縁層を該コモン電極の上に形成する第2工程と、スリットを複数備え透明導電層からなる画素電極を該コモン電極と平面視で重なり合うように該絶縁層の上に形成する第3工程と、該絶縁層の該スリットの下の厚さが該透明導電層の下の厚さよりも薄くなるように該絶縁層にエッチングを施す第4工程とを含むことを特徴とする。

## 【0022】

本発明は、かかる構成をとることにより、スリット下の絶縁層にはエッチングにより凹部が形成される。そして、上記作用効果を奏する液晶表示装置を製造することができる。

## 【0023】

本発明にかかる液晶表示装置の製造方法は、対向する基板間に液晶を挟持する液晶表示装置の製造方法であって、第1金属層からなる薄膜トランジスタのゲート電極を一方の該基板上に形成する第1工程と、該ゲート電極の上に第1絶縁層を形成する第2工程と、画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極を該第1絶縁層の上に形成する第3工程と、該第1絶縁層の上にアモルファスシリコン半導体からなる該薄膜トランジスタの半導体層及び低抵抗半導体層を順に形成する第4工程と、該低抵抗半導体層の上に第2金属層からなるソース電極及びドレイン電極を形成する第5工程と、該第2金属層、該低抵抗半導体層及び該コモン電極の上に該液晶の誘電率よりも小さい誘電率を備える第2絶縁層を形成する第6工程と、該ソース電極と導通しスリットを複数備え透明導電層からなる該画素電極を該コモン電極と平面視で重なり合うように該第2絶縁層の上に形成する第7工程と、該第2絶縁層の該スリットの下の厚さが該透明導電層の下の厚さよりも薄くなるように該第2絶縁層にエッチングを施す第8工程とを含むことを特徴とする。

## 【0024】

本発明は、かかる構成をとることにより、アモルファスシリコン半導体を半導体層とする薄膜トランジスタをスイッチング素子とし、第1絶縁層であるゲート絶縁膜と第2絶縁

層であるパッシベーション層との間にコモン電極を形成した液晶表示装置を製造することができる。そして、エッティングによりスリットの下の第2絶縁層に凹部が形成される。第2絶縁層の誘電率が液晶の誘電率よりも小さければ足り、第1絶縁層の誘電率にかかわらない。

#### 【0025】

本発明にかかる液晶表示装置の製造方法は、対向する基板間に液晶を挟持する液晶表示装置の製造方法であって、第1金属層からなる薄膜トランジスタのゲート電極を一方の該基板上に形成する第1工程と、該ゲート電極の上に第1絶縁層を形成する第2工程と、画素電極との間に生じるフリンジ電界によって該液晶の配向を制御するコモン電極と該薄膜トランジスタの半導体層とをIn、Ga及びZnを含む透明酸化物半導体を材料として該第1絶縁層の上に形成する第3工程と、該半導体層のソース領域、ドレイン領域及びコモン電極に紫外線を照射することにより高導電率化する第4工程と、該ソース領域及び該ドレイン領域の上に第2金属層からなるソース電極及びドレイン電極をそれぞれ形成する第5工程と、該第2金属層、該半導体層及び該コモン電極の上に該液晶の誘電率よりも小さい誘電率を備える第2絶縁層を形成する第6工程と、該ソース電極と導通しスリットを複数備え透明導電層からなる該画素電極を該コモン電極と平面視で重なり合うように該第2絶縁層の上に形成する第7工程と、該第2絶縁層の該スリットの下の厚さが該透明導電層の下の厚さよりも薄くなるように該第2絶縁層にエッティングを施す第8工程とを含むことを特徴とする。

#### 【0026】

本発明は、かかる構成をとることにより、第1絶縁層であるゲート絶縁膜と第2絶縁層であるパッシベーション層との間にコモン電極を形成するとともに、コモン電極と薄膜トランジスタの半導体層の両方を透明で移動度も比較的高い透明酸化物半導体で形成した液晶表示装置を製造することができる。特に、透明酸化物半導体にIGZOを用いた場合には、成膜時に酸素分圧等の条件を調整することにより導電率を高めることができ、また、成膜後においてもIGZOに紫外線照射等を行うことにより導電材料並みに導電率を高めることができあり、移動度も向上するため、薄膜トランジスタの駆動能力を向上させることができ、また、薄膜トランジスタの半導体層とコモン電極とを同一材料及び同一工程で形成できる。また、コモン電極に紫外線を照射する工程を備えるため、コモン電極の導電率は導電材料に近い値にまで向上し、電極として十分使用可能となる。従って、コモン電極の形成のみを目的とした製造工程は不要となり、製造工程の合理化に寄与する。そして、エッティングによりスリットの下の絶縁層を薄くすることができ、これにより第2絶縁層に凹部が形成される。従って、透明酸化物半導体を用いた液晶表示装置においても駆動電圧の低下等の効果を奏する。また、第2絶縁層の誘電率が液晶の誘電率よりも小さければ足り、第1絶縁層の誘電率にかかわらない。

#### 【0027】

本発明にかかる液晶表示装置の製造方法は、前記エッティングは、前記スリットを備える前記画素電極をマスクとして行うこと特徴とする。本発明は、かかる構成をとることにより、スリットを備える画素電極を形成した後にエッティングによりスリット下の絶縁層を薄くして凹部を形成することができる。そして、画素電極自体を、即ち透明導電層からなる電極部をマスクとしてこのようなエッティングを行うため、凹部はスリットに対して自己整合的に形成される。従って、スリットと凹部とが平面的にずれて形成されてしまうというような不都合が生じない。また、凹部形成用のマスクも不要である。

#### 【0028】

本発明にかかる液晶表示装置の製造方法は、前記エッティングは、6フッ化イオウ、塩素、又はテトラフルオロカーボンのいずれかを含むガスを用いたドライエッティングによってなされること特徴とする。本発明は、かかる構成をとることにより、ウェットエッティングのように画素電極もエッティングしてしまうという不都合がないため、スリット下の絶縁層のエッティング条件が緩和され精度良くエッティングすることができる。

#### 【発明の効果】

10

20

30

40

50

## 【0029】

本発明は、かかる構成をとることにより、液晶に印加される電界強度を維持又は増加させつつ、液晶の駆動電圧を低下させることができる液晶表示装置を提供することができる。また、本発明は、駆動電圧の低下により、信号線ドライバー回路等の駆動装置の発熱を低減し、より低消費電力の液晶表示装置を提供することができる。さらに、保持容量の増加を抑えることにより、フレームレートを高速化しても書き込み動作を確実に行うことができ、より表示品質の高い液晶表示装置を提供することができる。

## 【図面の簡単な説明】

## 【0030】

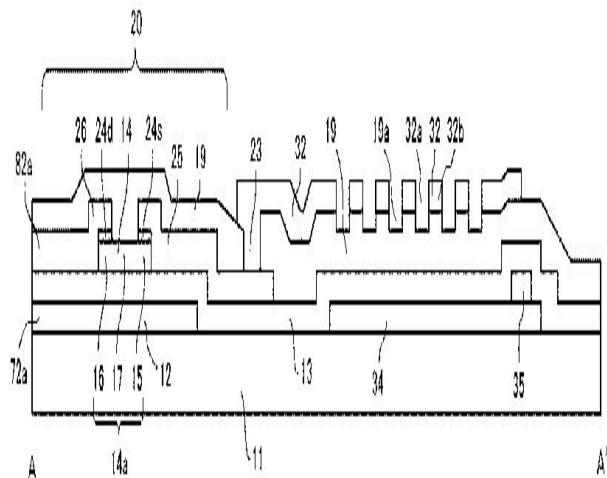

【図1】一実施の形態である液晶表示装置の模式的な構成図である。10

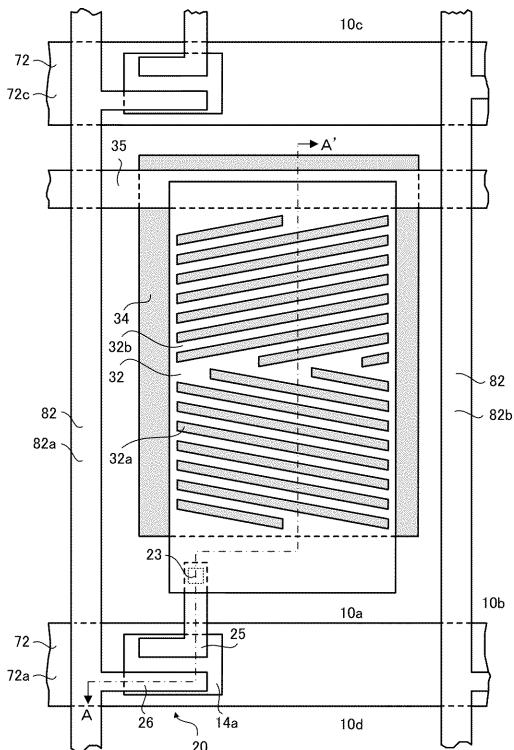

【図2】本発明の実施の形態である画素部の概略の構成図である。

【図3】本発明の実施の形態である画素部の概略の断面構成図である。

【図4】本発明の画素電極のスリット近傍の断面構造と作用を説明するための図である。

【図5】本発明の実施の形態である画素部の概略の構成図である。

【図6】本発明の実施の形態である画素部の概略の構成図である。

## 【発明を実施するための形態】

## 【0031】

以下、図面を参照しながら本発明の実施の形態を説明する。なお、本発明においては、薄膜トランジスタの半導体層の画素電極に接続される側をソースと呼び、信号線が接続される側をドレインと呼ぶことにすると、前者をドレインと呼び、後者をソースと呼ぶ場合であっても本発明と同様の作用、効果を奏する。20

## 【0032】

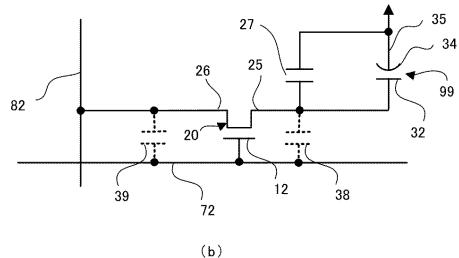

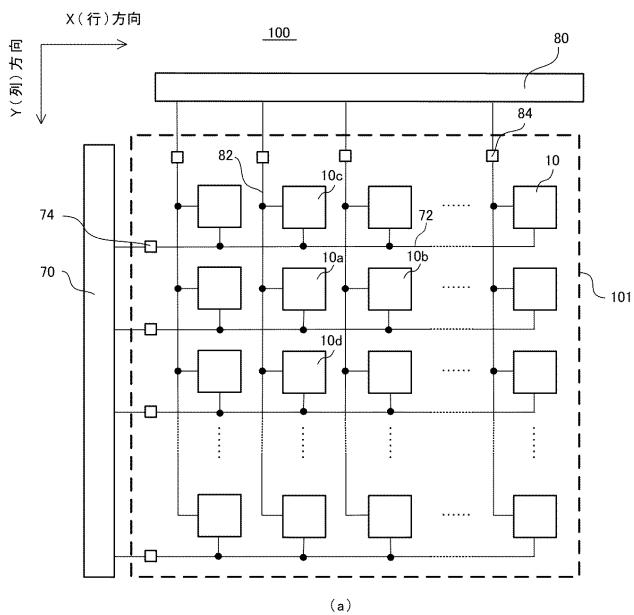

## [全体構成]

本実施の形態にかかるアクティブマトリックス型の液晶表示装置は、セル・アレイ基板と対向基板との間に液晶を挟持した液晶パネルを含んで構成される。図1は、本発明にかかるアクティブマトリックス型の液晶表示装置の液晶パネル部の模式的な構成図である。図1(a)は、セル・アレイ基板101の模式的な平面図であり、図1(b)は、画素部10及びその周辺の各部材の機能を説明するための等価回路図である。セル・アレイ基板101には、X(行)方向に延び走査線外部端子74と画素部10内の薄膜トランジスタのゲート電極とに接続された複数本の走査線72が形成されている。走査線72を介して、薄膜トランジスタを選択的にスイッチングするための信号である走査信号が薄膜トランジスタに供給される。なお、複数本の走査線72に対応する複数の走査線外部端子74がセル・アレイ基板101の端部近くにY方向に沿って設けられている。走査線外部端子74は、図示しないACF(異方性導電体)等を介して走査線ドライバー回路等の走査線駆動装置70の図示しない所定の端子に接続される。30

## 【0033】

また、セル・アレイ基板101には、Y(列)方向に延び信号線外部端子84と画素部10内の薄膜トランジスタのドレイン電極とに接続された複数本の信号線82が形成されている。信号線82を介して、走査信号によって選択された薄膜トランジスタに画像信号が供給される。なお、複数本の信号線82に対応する複数の信号線外部端子84がセル・アレイ基板101の端部近くにX方向に沿って設けられている。信号線外部端子84は、図示しないACF等を介して信号線ドライバー回路等の信号線駆動装置80の図示しない所定の端子に接続される。なお、上記走査線駆動装置70や信号線駆動装置80は、セル・アレイ基板101上に配設されていてよい。そして、走査線72と信号線82の各交差に対応して、走査線72と信号線82とによって区画された領域に画素部10がマトリックス状に配列されている。なお、参考番号10b、10c及び10dは、画素部10a(注目画素部ともいう)に隣接する隣接画素部を示している。また、図1(a)ではコモン配線の図示を省略している。40

## 【0034】

## [画素部]

10

20

30

40

50

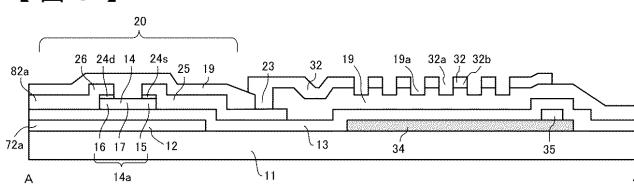

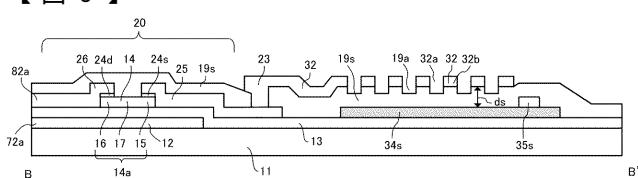

次に、図1( b )、図2及び図3を参照しながら、スイッチング素子としてボトムゲート型薄膜トランジスタを用いたFFSモードの画素部及びその周辺部の構成を説明する。図2は、本実施の形態にかかる画素部10及びその周辺を含む概略の平面図であり、図3は、図2のA-A'線における矢視方向の概略の断面構成図である。なお、本明細書において説明に用いる各図面では、説明の便宜上、縮尺又は縦横比等を適宜変更している。また、図2においては、わかりやすく描くためにゲート絶縁膜13、低抵抗半導体層24s、24d、及びパッシベーション層19を取り除いて記載し、また、見る層を適宜変更しており、後述の図5においても同様である。また、図3の断面図では、画素電極32に備えられたスリット32a、電極部32b及びパッシベーション層19に形成された凹部19aの図示を適宜省略しており、後述の図6においても同様である。

10

## 【0035】

図1( b )、図2及び図3に示す一つの画素部10は、薄膜トランジスタ20、画素電極32及びコモン電極34を含んで構成される。薄膜トランジスタ20は、走査線72と信号線82との交差部の近傍に設けられる。薄膜トランジスタ20は、基板11上に形成された走査線72上の一部の領域であるゲート電極12と、ゲート電極12の上に第1絶縁層であるゲート絶縁膜13を介して形成された半導体からなる半導体層14aと、半導体層14aの上に形成された低抵抗半導体層24s及び24dと、低抵抗半導体層24s及び24dの上の層にそれぞれ形成されたソース電極25及びドレイン電極26とを含んで構成される。

20

## 【0036】

走査線72のうちの薄膜トランジスタの半導体層14aと平面視で重なり合う領域があおむね、薄膜トランジスタ20のゲート電極12として機能し、これにより、ゲート電極12は走査線72と導通することになる。また、ドレイン電極26は、信号線82から枝状に分岐して低抵抗半導体層24dを介して半導体層14aの一部であるドレイン領域16と導通している。ソース電極25は、低抵抗半導体層24sを介して半導体層14aの一部であるソース領域15と導通するとともに、コンタクトホール23を介して透明導電層から形成された透明な画素電極32と導通している。薄膜トランジスタ20のチャネル領域17は、ソース領域15とドレイン領域16との間に挟まれるように形成されている。なお、図2に示すように、走査線72a、信号線82a、コモン配線35は画素部10aにかかる配線であり、隣接画素部10cにかかる走査線である隣接走査線72cは、走査線72aの延びる方向に沿って形成されている。隣接画素部10bにかかる信号線である隣接信号線82bは、信号線82aの延びる方向に沿って形成されている。

30

## 【0037】

次に、画素電極32について説明する。画素電極32は、ゲート電極12、ドレイン電極26、走査線72及び信号線82と平面視で重なり合わないような形状と大きさを備え、画素部10の内側におさまるように平板状に成形されている。画素電極32には開口であるスリット32aが複数備えられており、そのため、画素電極32は梯子状の外形形状をなすように成形されており、画素電極32は透明導電層からなるこのような梯子状の電極部32bを含んで構成される。

40

## 【0038】

本実施の形態における画素電極32は、マルチドメイン構造となっている。画素電極32には、ほぼ走査線の延びる方向に沿った方向を長辺とする細長い平行四辺形形状の開口である複数のスリット32aが、信号線の延びる方向に沿った方向に所定の間隔をもって設けられている。画素電極32は、平行に形成された複数の細長い平行四辺形のスリット32aが、上半分と下半分で左側では接近し、右側では離れるように対向させて配置することで、あおむね梯子状をなしている。そして、画素電極32は、「<」記号に似た形状をもつ幅の細い複数の板を走査線の延びる方向に沿った方向に所定の間隔をもって並べ、これらの板の端部が矩形の枠に連絡したような形状をなしている。

## 【0039】

本実施の形態においては、画素電極32に設けられているスリット32aは、画素電極

50

3 2 のうちの走査線 7 2 a と近接する側にあるほぼ半分の領域（図 2 上において画素電極 3 2 の下半分の領域）においては、スリット 3 2 a の信号線 8 2 b 側の端部と走査線 7 2 a との距離が信号線 8 2 a 側の端部と走査線 7 2 a との距離よりも短い位置に設けられている。これにより、スリット 3 2 a は走査線の延びる方向に対して同図上において右下に傾いて形成されている。一方、画素電極 3 2 のうちの隣接する画素部 1 0 c にかかる走査線 7 2 c と近接する側にあるほぼ半分の領域（同図上において画素電極 3 2 の上半分の領域）では、スリット 3 2 a の信号線 8 2 b 側の端部と走査線 7 2 a との距離が信号線 8 2 a 側の端部と走査線 7 2 a との距離よりも長い位置に設けている。これにより、スリット 3 2 a は走査線の延びる方向に対して同図上において右上に傾いて形成されている。なお、スリット 3 2 a の傾きの方向は、このような方向に限定されるものではなく、下半分の領域では右上に傾き上半分の領域では右下に傾いているような、即ち同図上において左右を逆にしたようなものでもよい。スリット 3 2 a の傾きの方向がこのような場合であっても同様の効果を奏する。なお、スリット 3 2 a の短辺は、すべて信号線 8 2 の延びる方向に沿った方向に形成されている。

#### 【 0 0 4 0 】

また、スリット 3 2 a の傾きを異にする上記 2 つの領域の境界近くにおいては、スリット 3 2 a は、上記上半分及び下半分のそれぞれの領域から境界近くにまで形成されている。そして、上半分の領域から延びたスリット 3 2 a の先端と下半分の領域から延びたスリット 3 2 a の先端とは、互い違いに境界近くにまで延びている。境界近くのスリットの先端位置をこのような位置に設けることにより、境界付近においてフリンジ電界が形成されない領域を少なくすることができ、表示品質が向上する。

#### 【 0 0 4 1 】

画素電極の平面形状は、これに限られず、櫛歯状、階段状又は梯子状でもよい。このような形状をとることにより、フリンジ電界を効率的に発生させ液晶分子をむらなく配向させることができるが、このようなマルチドメイン構造の電極形状をもつことによって、一つの画素部内での色変化を抑えることができる。なお、櫛歯状の画素電極の場合には、スリットは閉じた開口ではなく、一端が開いた開口となる。

#### 【 0 0 4 2 】

次に、コモン電極 3 4 について説明する。コモン電極 3 4 は、各画素部にパターニング形成された透明電極であり、FFS モード液晶表示装置では画素電極 3 2 が形成される基板 1 1 と同一の基板に形成される。コモン電極 3 4 は、ゲート電極 1 2 、ドレイン電極 2 6 、走査線 7 2 及び信号線 8 2 と平面視で重なり合わないような形状と大きさを備え、画素部 1 0 の内側におさまるように平板状にゲート絶縁膜 1 3 の下に成形されている。コモン電極 3 4 の少なくとも一部と画素電極 3 2 の少なくとも一部は、平面視で重なり合う（オーバーラップする）ように形成されている。

#### 【 0 0 4 3 】

次に、パッシベーション層 1 9 について説明する。コモン電極 3 4 と画素電極 3 2 との間には、ゲート絶縁膜 1 3 及びこれに積層されたパッシベーション層 1 9 とが挟まれている。そして、本実施の形態においては、このようにしてパッシベーション層 1 9 とゲート絶縁膜 1 3 とが積層された一の絶縁層が構成される。

#### 【 0 0 4 4 】

パッシベーション層 1 9 の厚さは、画素電極 3 2 のスリット 3 2 a が開口されている領域（スリット下の領域）とスリット 3 2 a が開口されていない領域（画素電極の透明導電層下の領域）とでは異なる。即ち、スリット 3 2 a 下のパッシベーション層 1 9 の厚さが、画素電極 3 2 の透明導電層下のパッシベーション層 1 9 の厚さよりも薄くなるような構造となっている。このような構造は、例えば、パッシベーション層 1 9 の画素電極側の面に、スリット 3 2 a の平面的形状及び寸法とほぼ同様な形状及び寸法をもつ凹部 1 9 a を、スリット 3 2 a 每に、個々のスリット 3 2 a と平面視で重なる位置に形成した構造であるともいえる。パッシベーション層 1 9 の厚さをこのようにすることにより、後述のように、液晶 9 9 に印加される電界強度が増加し、液晶の駆動電圧をより低電圧化することが

できる。

【0045】

次にコモン配線（共通電極線ともいう）35について説明する。コモン配線35は、各画素部内のコモン電極34に共通に接続されており、所定の電圧のコモン信号を各コモン電極34に供給する。コモン配線35は、その延びる方向に並ぶ複数の画素部10内を通過するように設けられており、通過する複数の画素部にあるそれぞれのコモン電極34と接続し導通している。また、例えば、コモン配線35は、平面視で隣接走査線72cの近くを延び、コモン電極34の上に形成されている。コモン配線35と画素電極32とはゲート絶縁膜13及びパッシベーション層19からなる絶縁層によって絶縁されている。

【0046】

コンタクトホール23は、パッシベーション層19を貫通し第2金属層からなるソース電極25に到達するものであり、これにより、透明導電層からなる画素電極32とソース電極25とを電気的に接続をすることができる。なお、図1(b)に示す参照番号27は画素電極32とコモン電極34との間に形成された保持容量Csであり、参照番号38及び39は、それぞれゲート・ソース間寄生容量Cgs及びゲート・ドレイン間寄生容量Cgdである。

【0047】

このような画素部10を備える液晶表示装置100の動作は次のとおりである。走査線駆動装置70は、液晶表示装置100に入力される図示しない画像信号の同期信号その他の情報に基づいて、信号線82からの画像信号を書き込むべき画素部10を行単位で選択する走査信号を出力する。信号線駆動装置80は、同じく画像信号の輝度情報等に基づいて、走査信号に同期して動作し、走査期間に選択された画素部10に画像信号を供給する。そして、選択された画素部10内にある薄膜トランジスタ20を介して、信号線駆動装置からの画像信号に応じた電圧が画素電極32に印加される。これによって、層を異にする画素電極32とコモン電極34とからなる一対の電極の間にフリンジ電界が生じ、このフリンジ電界によって液晶99の分子の向き（液晶分子の配向）が制御される。そして、この配向変化を利用することにより液晶を透過する光を変調することで画像等の表示作用が行われる。このようにしてFFSモードで動作する液晶表示装置が構成される。

【0048】

次に、画素部及びその周辺について、より詳細に説明する。セル・アレイ基板101の基板11としては、絶縁性と透明性を備えるガラス基板又は石英基板等のほか、プラスチック系の基板を使用することができる。コモン電極34は、透明導電層をパターニングすることにより形成される。透明導電層の材質は、特に限定されないが、多結晶化（ポリ化）したITO（インジウムスズ酸化物：Indium Tin Oxide）等を使用することができる。その膜厚は、20から100nm程度が望ましく、50nm程度がより望ましい。

【0049】

走査線72、ゲート電極12及びコモン配線35は、第1金属層をパターニングすることにより形成される。第1金属層は、例えば、AlNd、Al、又はMoの単層膜、あるいはAlNd、Al、Mo、及びCuから選択された任意の要素を組み合わせて形成された積層膜でもよい。本実施の形態におけるコモン配線35のように、ITOからなる透明導電層であるコモン電極34と接続されるような場合には、第1金属層を積層構造とすることが望ましい。例えば、Mo-AlNd-Moというような、AlNd金属層をMoの層でサンドイッチ状に構成した積層金属層を用いることが望ましい。このような材質や構造をとることにより、Mo層がAlNd層のカバーメタルとして機能し、ITOとAlNdとが直接に接することによるAlNdとITOとの界面における酸化膜の生成を回避し、良好な電気的接続をとることができる。なお、AlNdは、Alに2%程度のNdを含有させたものが望ましい。第1金属層の厚さは200nmから400nmが望ましい。

【0050】

第1絶縁層であるゲート絶縁膜13は、その材質としてSiNxを用いることが望ましいが、このほかにも酸化シリコン系や窒化シリコン系のSiOx又はSiOxNyの単

層膜、あるいはこれらを組み合わせた積層膜を使用することもでき、膜厚を薄く形成できる場合には液体性の酸化シリコンを用いることも可能である。これにより、絶縁性と透明性のある層を形成することができる。ゲート絶縁膜13は、第1金属層から形成されたゲート電極12を含む走査線72、コモン電極34及びコモン配線35を覆うように設けられている。ゲート絶縁膜13の膜厚は、100nmから500nmが望ましく、300nm程度がより望ましい。

#### 【0051】

次に、半導体層について説明する。半導体層14をパターニングすることによって形成された薄膜トランジスタ20の半導体層14aは、その材質として、アモルファスシリコン（以下、「a-Si」という）を使用することができる。その膜厚は、50nmから300nmが望ましい。また、低抵抗半導体層24s及び24dは、いわゆるn+半導体層であり、例えば、リン（P）がドープされたアモルファスシリコンを用いることができる。その膜厚は、10nmから50nmである。

10

#### 【0052】

ソース電極25、ドレイン電極26及び信号線82は、第2金属層をパターニングすることにより形成される。第2金属層の材質又は構造は特に限定されず、AlやMoの単層膜でもよいが、その上層や下層にITO等の透明導電層が形成される可能性のあるときは、第1金属層と同様、例えばMo-Al-Moのような3層構造の金属層を用いることにより、ITO等がMoを介してAlと接続されるような構造にすることが望ましい。第2金属層の厚さは200nmから400nmが望ましい。

20

#### 【0053】

第2絶縁層であるパッシベーション層19は、絶縁性と透明性とを備えるSiNx等の窒化シリコンを用いて形成される。パッシベーション層19は、第2金属層から形成されたソース電極25及びドレイン電極26を含む薄膜トランジスタ20、信号線82及びコモン電極34上のゲート絶縁膜13等を覆うように形成されている。このように、パッシベーション層19は、薄膜トランジスタ20等が形成されているセル・アレイ基板の表面を保護する保護膜としての役割を果たす絶縁層である。パッシベーション層19の厚さの詳細については後述するが、200nmから500nmが望ましい。画素電極32は、透明導電層をパターニングして形成される。その材質としては、後述するパッシベーション層19のエッチングに対して、パッシベーション層との選択性が高いことが望まれることから、例えば、ITOが用いられる。透明導電層の成膜後、パターニングをすることにより、透明導電層からなりスリット32aを備える画素電極32が形成される。画素電極32の厚さは20nmから150nmが望ましく、50nm程度とするのがより望ましい。

30

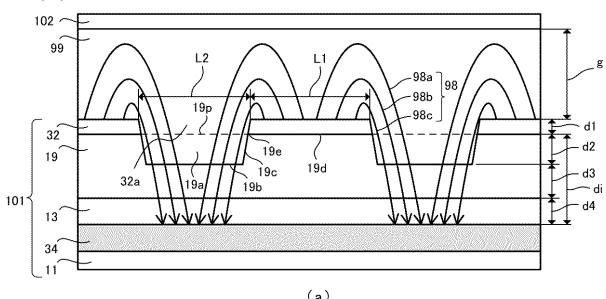

#### 【0054】

##### [パッシベーション層]

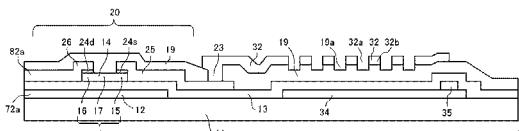

次に、図4を用いて、パッシベーション層19の構造、特に、スリット32a、パッシベーション層19及び凹部19aの関係について説明する。同図は、本実施の形態にかかる液晶表示装置のスリット32a付近のパッシベーション層19と凹部19aの構造及び作用を説明するための図であり、同図(a)は、本実施の形態にかかる液晶表示装置のスリット32aの周辺の概略の断面構造を示す図であり、同図(b)は、電気的作用を説明するための等価回路図である。

40

#### 【0055】

同図(a)に示すように、本実施の形態にかかる液晶表示装置は、セル・アレイ基板101と対向基板102とがセルギャップgの間隔をもって液晶99を挟持するような構成をなしており、凹部19aの近傍のセル・アレイ基板101は、基板11とその上に順に積層されたコモン電極34、ゲート絶縁膜13、パッシベーション層19、画素電極32及び図示しない配向膜とを含む断面構造を備えている。また、対向基板102は、図示しないカラーフィルタや配向膜等を備えている。なお、同図(a)においては本明細書で用いるほかの図面と同様に、セル・アレイ基板101及び対向基板102のいずれについても偏光板等のその他の光学部材等の記載を省略している。

50

## 【0056】

画素電極32は、その厚さはd1であり、幅寸法L2のスリット32aを複数備え、スリット32a同士の間の幅、即ち画素電極の透明導電層からなる部分の幅はL1である。L1及びL2の寸法は、特に限定されるものではないが、一般的に4ないし6μmである。パッシベーション層19の厚さは、画素電極32の透明導電層が形成されている領域の下においてはd2+d3であり、画素電極32の透明導電層が形成されていない領域の下においてはd3であり、少なくともスリット32a下においてはその厚さはd3である。つまり、画素電極32の透明導電層が形成されていない領域の下においては、パッシベーション層の厚さがd2だけ薄くなっている。このような構造をとることにより、スリット32aが図2に示すような閉じた開口をなす場合には、開口されている部分のパッシベーション層19には、深さd2をもつ凹部19aが、スリット32aと平面視で重なるように設けられていることになる。凹部19aの深さd2とは、パッシベーション面19pから凹部19aの底部19bまでの距離である。また、凹部19aの深さd2は、画素電極32の透明導電層下の絶縁層(パッシベーション層19及びゲート絶縁膜13)の厚さとスリット32a下の絶縁層(パッシベーション層19及びゲート絶縁膜13)の厚さとの差でもある。凹部19aの深さd2については、液晶の駆動電圧、液晶に必要な電界強度、絶縁層全体の厚さ、絶縁層の下に形成されている金属層又は半導体層との絶縁性、保持容量等を考慮して適宜選択することができる。

10

## 【0057】

なお、パッシベーション面19pとは、パッシベーション層19と画素電極32との界面である19dを延長した面であり、パッシベーション層19に凹部19aが形成されなければパッシベーション層19の表面をなす面である。また、底部19bは、図示しない配向膜を度外視すれば、おおむね、液晶99とパッシベーション層19との界面となる。なお、本明細書においては、画素電極32の透明導電層の下の絶縁層とは、本発明の作用及び効果を奏するような画素電極32の透明導電層の下の絶縁層をいい、例えばゲート絶縁膜13のうちコンタクトホール23の下に位置するようなゲート絶縁膜の部分を含まない。

20

## 【0058】

凹部19aは、その底部19bと側壁19cとを含んで構成される。底部19bの形状はスリット32aの形状とおおむね相似し、底部19bの面積はスリット32aの面積と同程度又はやや狭い程度とすることが望ましい。凹部の底部19bは、おおむね平面状とすることが望ましい。凹部19aは、少なくともスリット32aの内周と凹部19aの側壁19cの上端部19eとがほぼ一致するように形成されている。なお、画素電極32の形状が櫛歯型形状をなしている場合には、スリット32aは一端が開いたものとなり閉じた開口とはならないが、この場合にも画素電極の透明導電層下では厚くスリット下では薄いパッシベーション層を形成することは可能であり、凹部19aも形成されることになる。

30

## 【0059】

側壁19cの基板11に対する角度は、特に限定されないが、基板11に対して即ちパッシベーション層19に対して略垂直に、又は同図に示すように凹部19aの内側に向けてやや傾斜するように形成することが望ましい。ゲート絶縁膜13の膜厚はd4であるから、画素電極32の透明導電層下、即ち凹部19aが形成されていない領域下では、画素電極32とコモン電極34との間の絶縁層の厚さdiは、 $d_i = d_2 + d_3 + d_4$ となる。また、スリット下即ち凹部19aが形成されている領域下での絶縁層の厚さは $d_3 + d_4$ 、即ち $d_i - d_2$ となる。このような構造をもつ液晶表示装置において、このような凹部19aの存在により、液晶99は凹部19a内にも入り込み、凹部19aの形状や寸法、特に凹部の深さd2を適切にすることにより、液晶99に印加される電界強度が増加し、液晶の駆動電圧をより低電圧化することができる。以下、この点について説明する。

40

## 【0060】

画素電極32にコモン電極34よりも高い電圧Vを印可すると、画素電極32からは、

50

同図(a)に示すように、液晶99を経由しさらに絶縁層(パッシベーション層19及びゲート絶縁膜13)を経由してコモン電極34に向かう電気力線98が生じる。このため、このような電気力線の経路においては、画素電極32とコモン電極34との間は、液晶99による容量 $C_{Lc}$ と絶縁層による容量 $C_{i1}$ とが凹部19aの底部19bにおいて直列に接続されたような回路としてモデル化することができる。また、画素電極32から液晶99を経由せずに絶縁層(パッシベーション層19及びゲート絶縁膜13)を経由して直接にコモン電極34へ向かう電気力線(図示せず)も生じ、このような電気力線の経路においては画素電極32とコモン電極34との間に容量 $C_{i2}$ が構成されるため、結局、画素電極32とコモン電極34との間を回路的にモデル化すれば同図(b)のような等価回路となる。

10

### 【0061】

次に、同図(b)を参照して、液晶99に印加される電界強度 $E_{Lc}$ と深さ $d_2$ との関係を説明する。ここで、パッシベーション層19及びゲート絶縁膜13はいずれも同一材質(例えば、SiNx)で形成し、その誘電率を $\epsilon_i$ とする。また、液晶の誘電率を $\epsilon_{Lc}$ とする。なお、 $C_{Lc}$ 、 $C_{i1}$ 及び $C_{i2}$ の電極面積はいずれもSとし、画素電極32の厚さ $d_1$ は他の層と比べて薄いため $d_1 = 0$ として説明する。また、 $C_{Lc}$ にかかる電圧、即ち液晶99にかかる電圧を $V_{Lc}$ とし、 $C_{i1}$ にかかる電圧を $V_i$ とする。

### 【0062】

このような条件下において、 $C_{Lc}$ は、その電極は画素電極32及び底部19bであるから、電極間隔を $d_{Lc} + d_2$ とすることにより、

$$C_{Lc} = \epsilon_{Lc} \cdot S / (d_{Lc} + d_2)$$

となる。ここで、 $d_{Lc}$ は、本モデルにおいて、画素電極32からパッシベーション面19pに至るまでの画素電極とパッシベーション面との間の平均的な又は実効的な距離である。 $d_{Lc}$ は、対向基板102の近傍にまで張り出した電気力線98aについては、フリンジ電界は電極間だけでなく電極の上にも生じるからセルギャップgの寸法に加えて電極幅 $L_1$ 及び $L_2$ の寸法の影響を考慮すれば、少なくともセルギャップgの2倍以上になると考えられる。また、凹部19aの側壁の上端部19e近傍から発した電気力線98cについてであれば $d_{Lc}$ はゼロに近くなるであろうし、電気力線98bについてであればこれらの中間的な値となると考えられる。そのため、 $d_{Lc}$ は電気力線の液晶層内の空間的に分布に応じた平均的な又は実効的な距離と考えることができる。そして、パッシベーション面19pから底部19bまでの距離は $d_2$ であるから、結局、画素電極32と底部19bとの間の電極間距離は $d_{Lc} + d_2$ と考えることができる。

20

30

### 【0063】

$C_{i1}$ については、その電極は底部19b及びコモン電極34であるから、電極間隔は $d_i - d_2$ であり、

$$C_{i1} = \epsilon_i \cdot S / (d_i - d_2)$$

となる。

### 【0064】

なお、容量 $C_{i2}$ は、

$$C_{i2} = \epsilon_i \cdot S / d_i$$

40

となる。

### 【0065】

直列接続された $C_{Lc}$ と $C_{i1}$ との合成容量 $C_t$ は、

$$1/C_t = (1/C_{Lc}) + (1/C_{i1})$$

であるから、

$$\begin{aligned} 1/C_t &= (d_{Lc} + d_2) / (\epsilon_{Lc} \cdot S) + (d_i - d_2) / (\epsilon_i \cdot S) \\ &= d_{Lc} / (\epsilon_{Lc} \cdot S) + d_i / (\epsilon_i \cdot S) \\ &\quad + (1/\epsilon_{Lc} - 1/\epsilon_i) \cdot d_2 / S \end{aligned}$$

となる。 $C_{Lc}$ にかかる電圧、即ち液晶99にかかる電圧を $V_{Lc}$ とすると、

$$V_{Lc} = C_{i1} \cdot V / (C_{Lc} + C_{i1})$$

50

であるから、液晶層に印加される電界強度  $E_{LC}$  と凹部の深さ  $d_2$  との関係は、

$$\begin{aligned} E_{LC} &= V_{LC} / (d_{LC} + d_2) \\ &= V / ((1 - \frac{d_{LC}}{d_i}) \cdot d_2 + d_{LC} + (\frac{d_{LC} \cdot d_i}{d_i})) \\ &= V / ( \dots \cdot d_2 + \dots ) \end{aligned}$$

となる。但し、

$$\begin{aligned} &= 1 - \frac{d_{LC}}{d_i} \\ &= d_{LC} + (\frac{d_{LC} \cdot d_i}{d_i}) = \text{正の定数} \end{aligned}$$

従って、 $d_{LC} > d_i$  の場合には、 $< 0$  となるため、凹部の深さ  $d_2$  の増加に従って液晶に印加される電界  $E_{LC}$  も強くなる。従って、 $d_2$  を大きくすることにより、同じ電圧  $V = V_0$  で液晶を駆動しても液晶にかかる電界は強くなり、換言すれば、同じ電界強度であれば画素電極とコモン電極との間に印可する電圧  $V$  を  $V_0$  よりも低い電圧  $V_1$  に低下させることができる。従って、本発明によれば、低電圧駆動が可能となる。なお、電圧  $V$  を  $V_0$  から  $V_1$  に低下させたうえで、さらに  $d_2$  を大きくすることにより、液晶に印加される電界強度を  $V_0$  から  $V_1$  に低電圧化した以上に増加させることも可能である。

#### 【0066】

液晶の誘電率  $\epsilon_{LC}$  は、液晶の誘電異方性により、液晶分子の長軸に平行な方向の誘電率  $\epsilon_{||}$  と、液晶分子の長軸に直角な方向の誘電率  $\epsilon_{\perp}$  によって表わされる。 $\epsilon_{||}$  及び

$\epsilon_{\perp}$  の値は液晶材料によって異なるが、いずれの誘電率も絶縁層の誘電率  $\epsilon_i$  よりも大きければ本発明の効果を奏する。また、 $\epsilon_{||}$  が絶縁層の誘電率  $\epsilon_i$  よりも小さい場合であっても、本発明が液晶の駆動電圧の低減を課題の一つとしていることから、液晶に電圧が印加されている状態における誘電率が重要となるため、本発明における液晶の誘電率  $\epsilon_{LC}$  とは、 $\epsilon_{||}$  に相当すると考えるのが妥当であり、従って、 $\epsilon_{||}$  は絶縁層の誘電率  $\epsilon_i$  よりも高いことが望ましい。即ち、液晶分子は、誘電率異方性が正であるような液晶においては、駆動電圧印加時に液晶分子の長軸方向が液晶層内に生じた電界及び電気力線と平行となるように配列させられる。そのため、液晶の誘電率は液晶分子の長軸方向の誘電率  $\epsilon_{||}$  が支配的になる。従って、液晶分子の長軸方向の誘電率  $\epsilon_{||}$  が絶縁層の誘電率よりも大きい液晶材料を用いることにより、より低い駆動電圧であっても液晶に印加される電界強度を維持又は増加し、液晶を十分に駆動することができる。

#### 【0067】

本発明は、特に限定するものではないが、ノーマルブラックモードの液晶表示装置にも適する。例えば、FFSモードの液晶表示装置の場合には、IPSモード又はVAモードと同様に、液晶に電界が印加されていないとき（ノーマル時）に黒表示（暗表示）となり、電界が印加されているときに白表示（明表示）をするノーマルブラックモードで動作するような構造のものが一般的に使用される。本発明によれば液晶の駆動電圧を低電圧化しても液晶の電界強度は低下しないため、ノーマルブラックモードの液晶表示装置であっても十分な白表示を行うことができ、表示品質を向上させることができる。

#### 【0068】

また、FFSモードの液晶表示装置においては、IPSモードの液晶表示装置と同様にポジ型の液晶を用いることが一般的である。ポジ型液晶とは、誘電率異方性  $= -$

が正であるような液晶であり、このようなポジ型液晶に所定の強さの電界を印加すると、液晶分子の長軸が電界方向と即ち電気力線と平行になるように配列する。従って、ノーマルブラックモードで動作しポジ型液晶を用いたFFSモードの液晶表示装置では、液晶にフリンジ電界が印加され白表示をしている状態においては液晶分子はその長軸方向をフリンジ電界と平行になるように配列させられる。そして、信号線ドライバーは、このような白表示に必要とされる強さの電界を生じさせる必要があるため、本発明によれば、駆動電圧を低下させても液晶の電界強度は低下することなく十分な白表示を行うことができ、しかも信号線ドライバー回路の発熱を抑制することができる。

#### 【0069】

なお、 $\epsilon_{LC} > \epsilon_i$  の場合には、 $C_t$  も  $d_2$  とともに増加するが、一般に保持容量  $C_s$

10

20

30

40

50

のほとんどは C<sub>i</sub> 2 の寄与によるものであるため、スリット 3 2 a 下の絶縁層の厚さを画素電極 3 2 の透明導電層下の絶縁層の厚さよりも薄く形成しても、保持容量 C<sub>s</sub> の増加は少なく、保持容量の増加をほとんど抑えることができる。なお、保持容量 C<sub>s</sub> が増加する場合には、走査線 7 2 が供給する走査信号の電圧を高く設定することにより高フレームレート化を実現することも可能である。

#### 【 0 0 7 0 】

本発明は、かかる構成をとることにより、コモン電極 3 4 の上に絶縁層が形成されており、その上にスリット 3 2 a を備え透明導電層からなる画素電極 3 2 がコモン電極 3 4 と平面視で重なり合うように形成される。そして、層を異にする画素電極 3 2 とコモン電極 3 4 との間に生じるフリンジ電界によって液晶の配向が制御される FFS モードの液晶表示装置が構成される。そして、スリット 3 2 a の下の絶縁層（パッシベーション層 1 9 及びゲート絶縁膜 1 3 ）の厚さが画素電極 3 2 の透明導電層の下の絶縁層の厚さよりも薄くなるように形成されているため、スリット下にも液晶が入り込み、スリット下の絶縁層の表面は液晶と絶縁層との界面 1 9 b となり、また、画素電極 3 2 から液晶層 9 9 及び絶縁層を経由してコモン電極 3 4 に至るまでの電極間においては、絶縁層の厚さを薄くした分（寸法 d 2 ）だけ液晶層の厚さが厚くなる。

#### 【 0 0 7 1 】

そして、絶縁層の誘電率よりも誘電率が高い液晶を用いているため、このような構造においては、画素電極 3 2 とコモン電極 3 4 との間に印加される電圧 V が同じ場合に、画素電極 3 2 と液晶と絶縁層界面 1 9 b との間に印加される電界強度、即ち液晶層に印加される電界強度は、スリット下の絶縁層を薄くしない（d 2 = 0）構造のものと比べて増加する。言い換れば、液晶層を同じ電界強度で配向制御を行うのであれば、液晶の駆動電圧 V、即ち画素電極とコモン電極との間に印加される電圧 V を低下させても液晶分子の配向を十分に制御することができ、液晶の駆動電圧は低くてもよいことになり、その結果、液晶の駆動電圧の低電圧化及び低消費電力化を実現することができる。

#### 【 0 0 7 2 】

また、スリット下の絶縁層を薄くしても、保持容量 C<sub>s</sub> は画素電極 3 2 の透明導電層とコモン電極 3 4 と間に液晶層を経由することなく直接に形成される容量 C<sub>i</sub> 2 によってそのほとんどが構成されており、しかも透明導電層下の絶縁層の厚さを変更するものではないから容量 C<sub>i</sub> 2 が増加しない。そのため、スリット下の絶縁層を薄くすることによる保持容量 C<sub>s</sub> の増加は少ない。従って、本発明によれば、液晶に印加される電界強度を維持又は増加させつつ、液晶の駆動電圧を低下させることができる液晶表示装置を提供することができる。また、駆動電圧の低下により、信号線ドライバー回路等の駆動装置の発熱を低減し、より低消費電力の液晶表示装置を提供することができる。さらに、保持容量の増加を抑えるため、書き込み動作を確実に行うことができフレームレートの高速化が可能となり、より表示品質が向上した液晶表示装置を提供することができる。

#### 【 0 0 7 3 】

##### [ 製造方法 ]

次に、図 2 及び図 3 を参照して、本実施の形態にかかる液晶表示装置の製造方法を工程順に説明する。まず、セル・アレイ基板 1 0 1 となる基板 1 1 の上に、透明導電層を成膜し、これをパターニングしてコモン電極 3 4 を形成する（第 1 ステップ（第 1 P E P (Photo Engraving Process) ））。透明導電層の材質は、特に限定されないが、ITO を用いることができる。ITO の場合には、スパッタリング法によってアモルファスの ITO 層を成膜し、コモン電極 3 4 としてパターニングした後、ゲート電極等となる第 1 金属層を形成する前に、アニール処理を施すことによって多結晶化（ポリ化）することが望ましい。このようなアニール処理を施すことにより、ITO の結晶化を促進することができ導電率が向上する。

#### 【 0 0 7 4 】

次に、第 1 金属層を成膜し、これをパターニングし、少なくとも、ゲート電極 1 2 を含む走査線 7 2 、コモン配線 3 5 等のパターンを形成する（第 2 ステップ（第 2 P E P ））

10

20

30

40

50

。第1金属層の形成方法は、特に限定されないが、スパッタリング方式を使用してもよい。次に、ゲート絶縁膜13、半導体層14及び低抵抗半導体層24を、このような順序でもって、CVD法により、真空を破らずに原料ガスを適宜変更して連続して一括して成膜する。これにより、第1金属層で形成されたゲート電極12やコモン配線35等のパターンはゲート絶縁膜13により覆われるとともに(第3ステップ)、ゲート絶縁膜13の上に半導体層14(第4ステップ)、低抵抗半導体層24(第5ステップ)が積層される。低抵抗半導体層24形成後、薄膜トランジスタの半導体層をパターニングするためのマスクを用いて半導体層14と低抵抗半導体層24とを一括してエッチングを施す。これにより、薄膜トランジスタ20の半導体層14aと、半導体層14aとほぼ同一寸法及び同一形状の低抵抗半導体層とが積層された島状構造物が形成される(第3PEP)。

10

## 【0075】

次に、第2金属層をスパッタリング法等により成膜し、第2金属層の上に所定の形状でレジストを施した後、第2金属層をエッチングしてソース電極25、ドレイン電極26及び信号線82等を形成する。そして、同じレジストを利用してさらにエッチングすることによりn+アモルファスシリコンからなる低抵抗半導体層24をエッチングする。これにより、半導体層14a上の低抵抗半導体層のうち、ソース電極25及びドレイン電極26と平面視で重なり合わない領域の低抵抗半導体層が除去され、チャネル領域17上の低抵抗半導体層も除去される(第6ステップ(第4PEP))。このように、ソース電極25及びドレイン電極26と半導体層14aとの間に残った低抵抗半導体層24s及び24dを介することにより、ソース電極25及びドレイン電極26と半導体層14aとは、それぞれオーミックで良好な電気的導通をとることができる。

20

## 【0076】

次に、窒化シリコン等を用いてCVD法によりパッシベーション層19を形成する。これにより薄膜トランジスタ20、第2金属層及びコモン電極34上のゲート絶縁膜13等はパッシベーション層19によって覆われることになる。そして、これをエッチングによりパターニングを行い、その一部を除去することによりコンタクトホール23を形成する(第7ステップ(第5PEP))。

30

## 【0077】

次に、ITO等の透明導電層をスパッタリング法により成膜した後、蔥酸等を用いてこれをパターニングすることにより、複数のスリット32aを備えアモルファスのITOからなる透明導電層である画素電極32を形成する(第8ステップ(第6PEP))。次に、このようなスリット32aの下のパッシベーション層19をエッチングする。エッチングはウェットエッチングでも可能であるが、ドライエッチングによることが望ましい。ドライエッチングを用いることにより、ウェットエッチングのように画素電極もエッチングしてしまうという不都合がないため、スリット下の絶縁層のエッチング条件が緩和され精度良くエッチングすることができる。そして、エッチングは、スリット32aを備える画素電極32そのものをマスクとして行う。ドライエッチングのエッチングガスとしては、例えば、SF<sub>6</sub>(6フッ化イオウ)、Cl<sub>2</sub>(塩素)、又はCF<sub>4</sub>(テトラフルオロカーボン)ガスのいずれかを含み、これにN<sub>2</sub>(窒素)又はO<sub>2</sub>(酸素)を混合させたガスを用いることができる。

40

## 【0078】

これにより、スリット32aの下のパッシベーション層19がエッチングされて薄くなり、パッシベーション層19の画素電極側の面に凹部19aが形成される。そして、このような方法でパッシベーション層19をエッチングすることにより、凹部19aはスリット32aに対して自己整合的に形成されるため、スリット32aと凹部19aとが平面的にずれてしまうというような不都合が生じない。また、凹部19a形成用のマスクも不要である。

## 【0079】

以上の工程を経ることにより、画素電極32、コモン電極34及びボトムゲート型の薄膜トランジスタ20を含む画素部10、及び走査線、信号線、コモン配線等の各種配線を

50

基板 11 上に備えるセル・アレイ基板 101 を形成することができる。

【0080】

次に、このようなセル・アレイ基板 101 とカラーフィルタ等を設けた対向基板 102 とに配向処理等を行い、その後、両基板をシール材で貼り合わせる（第 9 ステップ）。シール材は、例えば光硬化型のアクリル樹脂のような、紫外線硬化型のシール材を用いる。次に、このようにしてシールされた液晶基板の間に液晶を注入し、駆動回路や偏光板、バックライト等の光学部材などを取り付けることにより液晶表示装置 100 が完成する（第 10 ステップ）。

【0081】

[変形例 1] 10

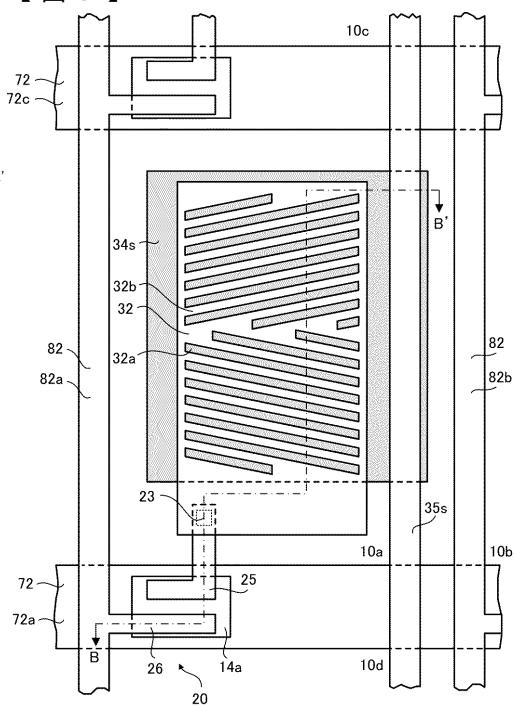

本発明は、画素電極 32 とコモン電極 34 との間の積層構造が他の様式を備える液晶表示装置にも適用することが可能であり、このような場合の実施の形態を一変形例として図面に基づいて説明する。図 5 は、本変形例にかかる画素部 10 及びその周辺を含む概略の平面図であり、図 6 は、図 5 の B-B' 線における矢視方向の概略の断面構成図である。本変形例においては、コモン電極、絶縁層、コモン配線の積層構造や材質等いくつかの点で相違するに過ぎないため、このような相違点を中心に説明するとともに、前記実施の形態で説明した構成要素と同一又は相当するものには同一符号を付し、その詳細な説明を省略する。図 5 及び図 6 はそれぞれ図 2 及び図 3 に対応する。

【0082】

本変形例においては、コモン電極 34s は、図 6 に示すとおり、基板 11 とゲート絶縁膜 13 との間ではなく、ゲート絶縁膜 13 とパッシベーション層 19s との間に形成されている。また、コモン配線 35s は、第 2 金属層をパターニングすることにより、コモン電極 34s の上であって、図 5 に示すとおり、隣接信号線 82b の近くを信号線 82 に沿った方向に延びて形成されている。コモン配線 35s は、平面視で、隣接信号線 82b と画素部 10a の画素電極 32 との間に形成されている。また、図 6 に示すとおり、コモン配線 35s は、コモン電極 34s の端部のうちの、隣接信号線 82b が延びる方向に沿った端部であって、かつ、隣接信号線 82b に近い端部の上に形成されている。コモン電極 34s の次に形成される第 2 金属層をコモン配線 35s の材料として使用することができるため、コンタクトホール等を形成することなく、コモン配線 35s とコモン電極 34s とが平面視で重なり合う領域において両者を接続し導通させることができる。 20

【0083】

本変形例におけるパッシベーション層 19s は、図 2 及び図 3 で示した構造のパッシベーション層 19 と比べて、その材質は同じでもよいが、その厚さを異にする。即ち、本変形例でのパッシベーション層 19s の画素電極 32 の透明導電層下の厚さ d<sub>s</sub> は、前述の実施の形態におけるパッシベーション層 19 の厚さ (d<sub>2</sub> + d<sub>3</sub>) とゲート絶縁膜 13 の厚さ (d<sub>4</sub>) とを加えた厚さになるように形成されている（図 6 及び図 4 参照）。従って、本変形例における画素電極 32 の透明導電層とコモン電極 34s との間の絶縁層の厚さ d<sub>s</sub> は、d<sub>s</sub> = d<sub>2</sub> + d<sub>3</sub> + d<sub>4</sub> であり、図 2 及び図 3 で示した実施の形態での厚さ d<sub>i</sub> と同じである。また、凹部 19a の構造は前述の実施の形態で説明したとおりである。 30

【0084】

本変形例にかかる液晶表示装置の製造方法は、まず、基板 11 上に第 1 金属層からなるゲート電極 12、走査線 72 を形成し、その上にゲート絶縁膜 13 を形成する。次に、ITO からなるコモン電極 34s をゲート絶縁膜 13 上に成膜しパターニングする。次に、a-Si からなる半導体層 14 及び n+ の a-Si からなる低抵抗半導体層 24 を成膜し、この 2 層を一括エッチングする。次に、第 2 金属層からなるソース電極 25、ドレイン電極 26、信号線 82 及びコモン配線 35s を形成する。次に、液晶 99 の誘電率よりも小さい誘電率を備え第 2 絶縁層であるパッシベーション層 19s を形成した後、スリット 32a を備えた画素電極 32 をコモン電極 34s と平面視で重なり合うように第 2 絶縁層の上に形成し、その後、画素電極 32 をマスクとしてパッシベーション層 19s に対してドライエッチングを施す。これにより、パッシベーション層 19s の厚さは、画素電極 32 40

10

20

30

40

50

のスリット下の厚さが画素電極 3 2 の透明導電層下の厚さよりも薄くなり、凹部 1 9 a が形成される。これにより、セル・アレイ基板 1 0 1 が形成される。これ以降の工程は前述のとおりである。

#### 【 0 0 8 5 】

このように、本変形例においては、コモン電極 3 4 s は、ゲート絶縁膜 1 3 とパッシベーション層 1 9 sとの間に、即ち、コモン電極 3 4 s はパッシベーション層 1 9 s の下であってゲート絶縁膜 1 3 の上に形成されている。画素電極 3 2 とコモン電極 3 4 sとの間の絶縁層はパッシベーション層 1 9 sのみとなり、スリット下の絶縁層の厚さは画素電極の透明導電層下の絶縁層の厚さよりも薄くなり、また、画素電極 3 2 の透明導電層とコモン電極 3 4 sとの間のパッシベーション層 1 9 sの厚さ d s を図 2 及び図 3 にかかる前述の実施の形態で説明した液晶表示装置の場合の d i と同じにしてあるため、画素電極 3 2 の透明導電層とコモン電極 3 4 s とこれらの間の絶縁層（即ちパッシベーション層 1 9 s）によって構成される容量 C<sub>i 2</sub> が著しく増加するような不具合は生じない。そのため、保持容量 C<sub>s 2 7</sub> の増加は少ない。従って、保持容量 C<sub>s 2 7</sub> の増加を抑えつつ、駆動電圧の低下等の図 2 及び図 3 にかかる前述の実施の形態で説明した液晶表示装置と同様の効果を奏することができる。また、パッシベーション層 1 9 s の誘電率が液晶の誘電率よりも小さければ足り、ゲート絶縁膜 1 3 の誘電率にかかわらないため、絶縁層（パッシベーション層 1 9 s）の材料や液晶材料の選択の幅を広げることができる。

10

#### 【 0 0 8 6 】

なお、本変形例においてパッシベーション層 1 9 s の厚さをゲート絶縁膜の厚さ分だけ厚くしない場合には、スリット下の絶縁層の厚さだけでなく画素電極 3 2 の透明導電層下の絶縁層の厚さもゲート絶縁層の厚さだけ薄くなるため、電圧 V が同じであれば画素電極 3 2 とコモン電極 3 4 sとの間の液晶層内の電界も強くなり、同じ電界強度を得るのであれば駆動電圧 V を低下できることは言うまでもない。このような場合においても、スリット下の絶縁層の厚さを画素電極の透明導電層下の絶縁層の厚さよりも薄くして凹部を形成することにより液晶層に印加される電界をさらに強めることができ、このような凹部を形成しない場合に比べて低電圧駆動及び低消費電化をすることが可能である。そして、このような場合には、保持容量 C<sub>s</sub> の増加を許容できる限り、高フレームレート化も実現することができる。また、保持容量 C<sub>s</sub> が増加する場合には、画素電極 3 2 とコモン電極 3 4 sとの間に印加される電圧を低くしたうえで、走査線 7 2 が供給する走査信号の電圧を高く設定することにより高フレームレート化を実現することも可能である。このようにすることにより、信号線ドライバー回路の発熱も抑えることができる。

20

30

#### 【 0 0 8 7 】

##### [ 変形例 2 ]

次に、コモン電極及び薄膜トランジスタの半導体層として、InGaZnO<sub>4</sub> のような In、Ga 及び Zn を含む透明酸化物半導体 (IGZO) を用いた例を他の変形例として図 5 及び図 6 を援用して説明する。IGZO 等の透明酸化物半導体は、コモン電極 3 4 s 及び薄膜トランジスタ 2 0 の半導体層 1 4 a の材料として使用することができる。透明酸化物半導体としては、IGZO のほかに、例えば、MgIn<sub>2</sub>O<sub>4</sub>、ZnGa<sub>2</sub>O<sub>4</sub>、In<sub>2</sub>O<sub>3</sub>、ZnO などを用いることもできる。このような透明酸化物半導体は、透明であるだけでなく、移動度も比較的高いため半導電性の材料としても使用できる。特に、IGZO の場合には、InGaZnO<sub>4</sub> のインゴットをスパッタリング法によって成膜することにより、成膜された薄膜（層）は透明なアモルファス IGZO 半導体層となり、酸素分压等の成膜条件を調整することにより導電率を高めることができ、また、成膜後においても IGZO に紫外線照射等を行うことにより導電材料並みに導電率を高めることも可能であるため、コモン電極 3 2 s として使用できる。

40

#### 【 0 0 8 8 】

従って、半導体層 1 4 a の材質を a - Si に代えて IGZO とし、また、コモン電極 3 4 s をITO に代えて IGZO で形成しこれに適切な紫外線照射を施すことにより導電率の高いコモン電極 3 4 s を形成することも可能である。このように半導体層 1 4 a 及びコ

50

モン電極 34 s の両方を I G Z O を用いて形成することにより、半導体層 14 a とコモン電極 34 s とは同一の P E P で、即ち同一の成膜及びエッチング工程で同時に形成することができるため、製造工程を簡素化することができる。そして、コモン電極 34 s は、ゲート絶縁膜 13 の上に形成され、コモン配線 35 s は第 2 金属層を用いてソース電極 25 、ドレイン電極 26 及び信号線 82 と同一の P E P で形成することができる。パッシベーション層の厚さや凹部については変形例 1 と同様である。

#### 【 0089 】

図 6 を援用して製造方法について説明する。まず、第 1 金属層からなる走査線及び薄膜トランジスタ 20 のゲート電極 12 を基板 11 上に形成し、ゲート電極 12 の上に第 1 絶縁層であるゲート絶縁膜 13 を形成し、次に画素電極 32 との間に生じるフリンジ電界によって液晶 99 の配向を制御するコモン電極 34 s と薄膜トランジスタ 20 の半導体層 14 a とを I G Z O を材料として第 1 絶縁層の上に形成する。次に、コモン電極 34 s に紫外線を照射することによりコモン電極 34 s を高導電率化し、その後、半導体層 14 a の上に第 2 金属層からなるソース電極 25 及びドレイン電極 26 を、また、コモン電極 34 s の上にコモン配線 35 s を形成し、さらに、第 2 金属層、半導体層 14 a 及びコモン電極 34 s 及びコモン配線 35 s の上に液晶 99 の誘電率よりも小さい誘電率を備える第 2 絶縁層であるパッシベーション層 19 s を形成する。そして、ソース電極 25 と導通し、透明導電層からなり、スリット 32 a を複数備える画素電極 32 を、コモン電極 34 s と平面視で重なり合うように第 2 絶縁層の上に形成し、第 2 絶縁層のスリット 32 a の下の厚さが画素電極 32 の透明導電層の下の厚さよりも薄くなるように第 2 絶縁層にドライエッチングを施す。これにより、セル・アレイ基板 101 が形成される。これ以降の工程は前述のとおりである。

#### 【 0090 】

なお、本変形例においては、変形例 1 とは異なり、図 6 における低抵抗層半導体層 24 s 及び 24 d を形成しない。即ち、半導体層 14 a に I G Z O を用いるため、コモン電極 34 s への紫外線照射工程において、半導体層 14 a のうちソース電極 25 の下のソース領域 15 及びドレイン電極 26 の下のドレイン領域 16 にも同時に紫外線を照射することにより、これらの領域の導電率を向上させることができる。従って、本変形例においては、a - S i を用いた薄膜トランジスタの形成に必要とされた低抵抗半導体層 24 s 及び 24 d に相当する層を別途形成する必要がない。

#### 【 0091 】

このように、本変形例においては、変形例 1 と同様に、コモン電極 34 s がゲート絶縁膜 13 とパッシベーション層 19 s との間に形成される。画素電極 32 とコモン電極 34 s との間の絶縁層はパッシベーション層 19 s のみとなり、スリット下の絶縁層の厚さは画素電極 32 の透明導電層下の絶縁層の厚さよりも薄くなり、また、画素電極 32 の透明導電層とコモン電極 34 s との間のパッシベーション層 19 s の厚さ d s を図 2 及び図 3 にかかる前述の実施の形態で説明した液晶表示装置の場合と同じ d i としているため、画素電極 32 の透明導電層とコモン電極 34 s とこれらの間の絶縁層（即ちパッシベーション層 19 s ）によって構成される容量 C<sub>i2</sub> が著しく増加するような不具合は生じない。そのため、保持容量 C<sub>s27</sub> の増加は少ない。従って、保持容量 C<sub>s27</sub> の増加を抑えつつ、駆動電圧の低下等の図 2 及び図 3 にかかる前述の実施の形態で説明した液晶表示装置と同様の効果を奏することができる。また、本変形例においてパッシベーション層 19 s の厚さをゲート絶縁膜 13 の厚さ分だけ厚くしない場合については、変形例 1 で説明したのと同様である。

#### 【 0092 】

なお、図 1 ないし図 6 は本実施の形態を説明するために、本実施の形態に関連する主要な部材や部材間の関係を簡略化して記載したに過ぎないものである。ここまで説明で言及した以外にも、薄膜トランジスタや液晶表示装置を構成するには多くの部材が使われる。しかしそれらは当業者には周知であるので、ここでは詳しく言及しない。また、本実施の形態で説明した液晶表示装置はあくまで一例に過ぎず、それら以外の液晶表示装置であ

10

20

30

40

50

っても、当業者が任意に選択することができる範囲においては本発明の範囲に含まれる。

【0093】

図面に示した特定の実施の形態をもって説明してきたが、本発明は図面に示した実施の形態に限定されるものではなく、本発明の効果を奏する限り、これまで知られたいかなる構成であっても採用することができますはいうまでもないことである。

【符号の説明】

【0094】

10 1 0 ... 画素部

1 1 ... 基板

1 2 ... ゲート電極

1 3 ... 第1絶縁層（ゲート絶縁膜）

1 4 a ... 薄膜トランジスタの半導体層

1 9、1 9 s ... パッシベーション層（第2絶縁層）

1 9 a ... 凹部

1 9 b ... 凹部の底部（液晶と絶縁層との界面）

2 0 ... 薄膜トランジスタ

2 4、2 4 s、2 4 d ... 低抵抗半導体層

2 5 ... ソース電極

2 6 ... ドレイン電極

2 7 ... 保持容量 C s

20

3 2 ... 画素電極

3 2 a ... スリット

3 4、3 4 s ... コモン電極（対向電極）

7 2、7 2 a、7 2 c ... 走査線

8 2、8 2 a、8 2 b ... 信号線

9 9 ... 液晶

1 0 0 ... 液晶表示装置

1 0 1 ... セル・アレイ基板

1 0 2 ... 対向基板

【図1】

【図3】

【図4】

【図2】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100077584

弁理士 守谷 一雄

(72)発明者 鴨志田 健太

神奈川県川崎市高津区坂戸3 - 2 - 1 ビデオコン・ディスプレイズ・リサーチ株式会社内

(72)発明者 永山 和由

神奈川県川崎市高津区坂戸3 - 2 - 1 ビデオコン・ディスプレイズ・リサーチ株式会社内

F ターム(参考) 2H092 GA14 GA17 HA04 JA26 JA35 JA36 JB05 JB14 JB57 JB69

KA05 KA12 KB24 NA01 NA05 NA23 NA25 PA01

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2010230744A</a>                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2010-10-14 |

| 申请号            | JP2009075454                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2009-03-26 |

| [标]申请(专利权)人(译) | Videocon的全球限量<br>维迪奥肯全球有限公司                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | Videocon的全球限量                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 鴨志田 健太<br>永山 和由                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 鴨志田 健太<br>永山 和由                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F1分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-Term分类号      | 2H092/GA14 2H092/GA17 2H092/HA04 2H092/JA26 2H092/JA35 2H092/JA36 2H092/JB05 2H092/JB14 2H092/JB57 2H092/JB69 2H092/KA05 2H092/KA12 2H092/KB24 2H092/NA01 2H092/NA05 2H092/NA23 2H092/NA25 2H092/PA01 2H192/AA24 2H192/BB13 2H192/BB55 2H192/BB73 2H192/BB84 2H192/BC31 2H192/CB05 2H192/CB37 2H192/CB44 2H192/CB61 2H192/CC04 2H192/DA12 2H192/DA32 2H192/DA72 2H192/EA68 2H192/HA36 2H192/HA47 2H192/HA63 2H192/HA81 2H192/JA34 |         |            |

| 代理人(译)         | 渡边弘道<br>守谷一夫                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

### 摘要(译)

FFS模式的液晶显示装置在不增加保持容量的情况下维持或增加施加到液晶的电场强度，降低液晶驱动电压，并相应地防止信号线驱动电路产生热量。实现高帧率。在公共电极和设置有多个狭缝的像素电极之间设置介电常数小于液晶的介电常数的绝缘层，并且在像素电极的狭缝下面的绝缘层的厚度设置为像素电极蚀刻绝缘层以使其比透明导电层下的绝缘层的厚度薄。结果，在狭缝下方的绝缘层中形成凹部，施加到液晶的电场强度增加，并且可以进行低电压驱动。另外，由于绝缘层不均匀地变薄，因此保持容量的增加很小。点域