(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5026450号

(P5026450)

(45) 発行日 平成24年9月12日(2012.9.12)

(24) 登録日 平成24年6月29日(2012.6.29)

(51) Int.CI.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

請求項の数 7 (全 45 頁)

|              |                                                                 |           |                                                |

|--------------|-----------------------------------------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2009-43907 (P2009-43907)                                      | (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号     |

| (22) 出願日     | 平成21年2月26日(2009.2.26)                                           | (74) 代理人  | 100098464<br>弁理士 河村 利                          |

| (62) 分割の表示   | 特願2001-72890 (P2001-72890)<br>の分割<br>原出願日 平成13年3月14日(2001.3.14) | (74) 代理人  | 100149630<br>弁理士 藤森 洋介                         |

| (65) 公開番号    | 特開2009-122697 (P2009-122697A)                                   | (74) 代理人  | 100154449<br>弁理士 谷 征史                          |

| (43) 公開日     | 平成21年6月4日(2009.6.4)                                             | (72) 発明者  | 小林 和弘<br>熊本県合志市御代志997番地 株式会社<br>アドバンスト・ディスプレイ内 |

| 審査請求日        | 平成21年2月26日(2009.2.26)                                           | (72) 発明者  | 中村 伸宏<br>熊本県合志市御代志997番地 株式会社<br>アドバンスト・ディスプレイ内 |

| (31) 優先権主張番号 | 特願2000-72766 (P2000-72766)                                      |           | 最終頁に続く                                         |

| (32) 優先日     | 平成12年3月15日(2000.3.15)                                           |           |                                                |

| (33) 優先権主張国  | 日本国(JP)                                                         |           |                                                |

| (31) 優先権主張番号 | 特願2000-82141 (P2000-82141)                                      |           |                                                |

| (32) 優先日     | 平成12年3月23日(2000.3.23)                                           |           |                                                |

| (33) 優先権主張国  | 日本国(JP)                                                         |           |                                                |

(54) 【発明の名称】 液晶表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極・ゲート配線および画素電極のパターンを透明導電体層と金属層との少なくとも2層からなる構成とし、前記金属層が前記透明導電体層の上層になるように成膜し、第1の写真製版工程により、前記ゲート電極・ゲート配線および前記画素電極のそれぞれのパターン形状のホトレジストを形成してエッチングを行ない、それぞれの所定のパターンを形成する工程と、

ゲート絶縁膜、半導体能動層およびコンタクト層を形成し、第2の写真製版工程により、ホトレジストの厚みを少なくとも前記半導体能動層およびコンタクト層を残す部分を厚くした領域(A)と、少なくとも画素電極の光を透過する部分を露出させるためホトレジストを除去した領域(C)と、前記コンタクト層と前記半導体能動層とを除去し前記ゲート絶縁膜を残す部分であってホトレジストの厚みを前記領域(A)のホトレジストの厚みより薄くした領域(B)とを形成する工程と、

前記コンタクト層、前記半導体能動層、前記ゲート絶縁膜を前記厚み形状のホトレジストを用いてそれぞれの形状のパターンでエッチングを行ない画素電極のパターンを露出させる工程と、

該露出した画素電極のパターンにおいて前記少なくとも2層構造の上層にある前記金属層をエッチングで取り除く工程と、

前記領域(A)のホトレジストを残しつつ前記領域(B)上からホトレジストを取り除き、前記領域(A)以外の部分の前記コンタクト層と前記半導体能動層とを取り除く工程と

、

金属膜を成膜し、第3の写真製版工程により、ソース・ドレイン電極の形成と、ソース電極とドレイン電極との間の前記コンタクト層を除去する工程と

を含むことを特徴とする液晶表示装置の薄膜トランジスタアレイ基板の製造方法。

【請求項2】

前記ソース・ドレイン電極の形成後に、保護膜を形成する工程をさらに有し、第4の写真製版工程により、ゲート端子部およびソース端子部にコンタクトホールを形成する請求項1記載の液晶表示装置の薄膜トランジスタアレイ基板の製造方法。

【請求項3】

前記画素電極のパターンの上層にある金属層をエッチングで取り除く工程を、前記ソース・ドレイン電極の形成工程の前には行なわないで、該ソース・ドレイン電極を、前記ゲート配線の上層に適用したものと同じ金属材料からなる金属により形成し、該ソース・ドレイン電極のバーニングの際に前記画素電極パターンの上層にある金属層も同時にエッチングで取り除くことを特徴とする請求項1または2記載の液晶表示装置の薄膜トランジスタアレイ基板の製造方法。

10

【請求項4】

保持容量がさらに形成され、該保持容量の一方の電極を前記ゲート電極・ゲート配線および画素電極パターンと同時に形成し、該保持容量の他方の電極を前記ソース・ドレイン電極の形成と同時に形成し、かつ、前記画素電極に接続する請求項1ないし3のいずれか1項に記載の液晶表示装置の薄膜トランジスタアレイ基板の製造方法。

20

【請求項5】

保持容量がさらに形成され、該保持容量の一方の電極と接続する共通配線を、前記ゲート電極・ゲート配線および画素電極のパターンと同時に形成する請求項1ないし4のいずれか1項に記載の液晶表示装置の薄膜トランジスタアレイ基板の製造方法。

【請求項6】

前記領域(A)、(B)および(C)の厚みの異なるホトレジストの形成を、露光の際のマスクの光の透過率を制御するマスクにより行う請求項1ないし5のいずれか1項に記載の薄膜トランジスタアレイ基板の製造方法。

【請求項7】

ゲート電極・ゲート配線用の導電性物質を成膜し、第1の写真製版工程により、前記ゲート電極・ゲート配線のパターン形状のホトレジストを用いてエッチングを行ない、それぞれの所定のパターンを形成する工程と、

30

ゲート絶縁膜、半導体能動層およびコンタクト層を形成し、第2の写真製版工程により、ホトレジストの厚みを前記半導体能動層およびコンタクト層を残す部分を厚くした領域(A)と、少なくとも前記ゲート配線の一部を露出させるためホトレジストを除去した領域(C)と、前記コンタクト層と前記半導体能動層とを除去し前記ゲート絶縁膜を残す部分であってホトレジストの厚みを前記領域(A)のホトレジストの厚みより薄くした領域(B)とを形成する工程と、

前記コンタクト層、前記半導体能動層、前記ゲート絶縁層を前記形状のホトレジストを用いてエッチングを行ないゲート配線の少なくとも一部を露出させる工程と、

40

前記領域(A)のホトレジストを残しつつ前記領域(B)のホトレジストを取り除き、前記残存するホトレジストを用いて前記領域(A)以外の部分の前記コンタクト層と前記半導体能動層とを取り除く工程と、

少なくとも一部が前記コンタクト層に接するよう透明導電層および金属層をこの順で成膜し、第3の写真製版工程により、ソース・ドレイン電極および画素電極のパターン形状のホトレジストを用いてソース・ドレイン電極および画素電極のパターンの形成と、ソース電極とドレイン電極との間の前記コンタクト層を除去する工程と、

保護膜を全面に形成し、第4の写真製版工程により、該保護膜の少なくとも前記画素電極上の光を透過する部分を取り除くと共に、コンタクト孔を形成する工程と、

前記画素電極上に形成された保護膜が取り除かれた領域から前記透明導電層上の前記金属

50

層を取り除いて前記画素電極を形成する工程と

を含むことを特徴とする液晶表示装置の薄膜トランジスタアレイ基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は薄膜トランジスタアレイ基板の製造方法に関する。さらに詳しくは、点欠陥および線欠陥が少なくかつ、薄膜トランジスタ(TFT)のリーク電流を低減できる薄膜トランジスタアレイ基板を4回の写真製版工程で製造するものであり、本発明はTFT-LCDの表示特性および生産性を向上するものである。

【背景技術】

10

【0002】

液晶を用いた電気光学素子はディスプレイへの応用がさかんになされている。液晶を用いた電気光学素子は一般に、上下に電極を備えた2枚の基板の間に液晶を挟持した構成のものに、さらに上下に偏光板を設置した構成をとり、透過型のものでは背面にバックライトが設置される。上下の電極基板の表面はいわゆる配向処理がなされ、液晶分子の平均的な向きであるダイレクターが所望の初期状態に制御される。液晶には複屈折性があり、バックライトより偏光板を通して入射された光は複屈折により橢円偏光に変化し、反対側の偏光板に入射される。この状態で、上下の電極間に電圧を印加するとダイレクターの配列状態が変化することにより、液晶層の複屈折率が変化し、反対側の偏光板に入射される橢円偏光状態が変化し、従って電気光学素子を透過する光強度およびスペクトルが変化する。この電気光学効果は用いる液晶相の種類、初期配向状態、偏光板の偏向軸の向き、液晶層の厚さ、あるいは光が透過する途中に設置されるカラーフィルターや各種干渉フィルムによって異なるが、公知の文献等によって詳細に報告されている。一般にはネマチック液晶相を用いて、TNまたはSTNと呼ばれる構成のものが用いられる。

20

【0003】

液晶を用いたディスプレイ用電気光学素子には、単純マトリックス型のものと、薄膜トランジスタ(TFT)をスイッチング素子として用いるTFT-LCDがある。携帯性、表示品位の点でCRTや単純マトリックス型液晶表示装置より優れた特徴を持つTFT-LCDがノート型パソコンなどに広く実用されている。TFT-LCDでは、一般にTFTをアレイ状に形成したTFTアレイ基板と共に電極が形成されたカラーフィルター付きの対向基板との間に液晶を挟持した構成の上下に偏向板が設置され、さらに背後にバックライトを設置した構成をとる。このような構成によって良好なカラー表示が得られる特徴を持つ。

30

【0004】

TFT-LCDでは液晶に電圧を印加するため、ゲートラインの選択時間内にTFTをオン状態とし、ソース配線から画素電極に電荷を流入し、画素電位をソース配線と同電位とする。その後ゲートが非選択状態になると、TFTはオフ状態になり画素の電荷は保持されるが、実際にはTFTや液晶内のリーク電流により画素の電荷量は減少し、結果的には画素の電位が減少する。これらの画素電位の変動を防ぐため、通常は補助容量を設けて単位電荷量の変化に対する画素電位の変化量が小さくなるようにする。またTFT-LCDの生産性向上のためFTFアレイの製造工程数を削減する試みがなされている。そのうち写真製版工程を削減する試みが特許文献1、特許文献2、特許文献3にしめされている。

40

【0005】

従来の製法を用いてTFTアレイを作製する場合、少なくとも5回の写真製版工程を必要とするため、製造工程が長くなり、特に生産設備の稼動コストが高い露光工程を多く使う問題がある。このため、必然的に製作されるTFTアレイのコストが増加する。

【0006】

本発明は、従来技術の前記の問題点を解消するためになされたものであり、TFTアレイを製造するために必要な写真製版の回数、ひいてはマスクの枚数を削減することにより

50

、生産性を改善し、コストを低減することをも目的とする。

【0007】

従来の製法を用いて TFT アレイを作製する場合、少なくとも 5 回の写真製版工程以上必要とするため、製造工程が長くなり、とくに生産設備の稼動コストが高い露光工程を多く使う問題がある。このため、必然的に作製される TFT アレイのコストが増加した。

【先行技術文献】

【特許文献】

【0008】

【特許文献 1】特開平 6 - 202153 号公報

【特許文献 2】特開平 8 - 328040 号公報

【特許文献 3】特開平 8 - 50308 号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明の目的は、アクティブマトリクス型液晶表示装置の生産性向上あるいはコスト低減を目的として、TFT アレイを製造するために必要とする写真製版の回数（マスク枚数）を低減することを目的としている。

【課題を解決するための手段】

【0013】

本発明の製造方法によれば、写真製版工程数を削減するために、ゲート電極・ゲート配線および画素電極のパターンを透明導電体層と金属層との少なくとも 2 層からなる構成とし、前記金属層が前記透明導電体層の上層になるように成膜し、第 1 の写真製版工程により、前記ゲート電極・ゲート配線および前記画素電極のそれぞれのパターン形状のホトレジストを形成してエッチングを行ない、それぞれの所定のパターンを形成する工程と、ゲート絶縁膜、半導体能動層およびコンタクト層を形成し、第 2 の写真製版工程により、ホトレジストの厚みを少なくとも前記半導体能動層およびコンタクト層を残す部分を厚くした領域（A）と、少なくとも画素電極の光を透過する部分を露出させるためホトレジストを除去した領域（C）と、前記コンタクト層と前記半導体能動層とを除去し前記ゲート絶縁膜を残す部分であってホトレジストの厚みを前記領域（A）のホトレジストの厚みより薄くした領域（B）とを形成する工程と、前記コンタクト層、前記半導体能動層、前記ゲート絶縁膜を前記厚み形状のホトレジストを用いてそれぞれの形状のパターンでエッチングを行ない画素電極のパターンを露出させる工程と、該露出した画素電極のパターンにおいて前記少なくとも 2 層構造の上層にある前記金属層をエッチングで取り除く工程と、前記領域（A）のホトレジストを残しつつ前記領域（B）上からホトレジストを取り除き、前記領域（A）以外の部分の前記コンタクト層と前記半導体能動層とを取り除く工程と、金属膜を成膜し、第 3 の写真製版工程により、ソース・ドレイン電極の形成と、ソース電極とドレイン電極との間の前記コンタクト層を除去する工程とを含むことにより、写真製版工程数を削減した。

20

30

【0014】

本発明のさらに他の態様によれば、写真製版回数を削減するために、ゲート電極・ゲート配線用の導電性物質を成膜し、第 1 の写真製版工程により、前記ゲート電極・ゲート配線のパターン形状のホトレジストを用いてエッチングを行ない、それぞれの所定のパターンを形成する工程と、ゲート絶縁膜、半導体能動層およびコンタクト層を形成し、第 2 の写真製版工程により、ホトレジストの厚みを前記半導体能動層およびコンタクト層を残す部分を厚くした領域（A）と、少なくとも前記ゲート配線の一部を露出させるためホトレジストを除去した領域（C）と、前記コンタクト層と前記半導体能動層とを除去し前記ゲート絶縁膜を残す部分であってホトレジストの厚みを前記領域（A）のホトレジストの厚みより薄くした領域（B）とを形成する工程と、前記コンタクト層、前記半導体能動層、前記ゲート絶縁層を前記形状のホトレジストを用いてエッチングを行ないゲート配線の少なくとも一部を露出させる工程と、前記領域（A）のホトレジストを残しつつ前記領域（

40

50

B ) のホトレジストを取り除き、前記残存するホトレジストを用いて前記領域 ( A ) 以外の部分の前記コンタクト層と前記半導体能動層とを取り除く工程と、少なくとも一部が前記コンタクト層に接するように透明導電層および金属層をこの順で成膜し、第 3 の写真製版工程により、ソース・ドレイン電極および画素電極のパターン形状のホトレジストを用いてソース・ドレイン電極および画素電極のパターンの形成と、ソース電極とドレイン電極との間の前記コンタクト層を除去形成する工程と、保護膜を全面に形成し、第 4 の写真製版工程により、該保護膜の少なくとも前記画素電極上の光を透過する部分を取り除くと共に、コンタクト孔を形成する工程と、前記画素電極上に形成された保護膜が取り除かれた領域から前記透明導電層上の前記金属層を取り除いて前記画素電極を形成する。これにより、写真製版回数を 4 枚に短縮できる。

10

**【発明の効果】**

**【0015】**

本発明の薄膜トランジスタアレイ基板およびその製造方法においては、絶縁性基板、該絶縁性基板上に形成された第 1 の金属パターン、該第 1 の金属パターン上の絶縁膜、該絶縁膜上の半導体パターン、該半導体パターン上の第 2 の金属パターンを具備し、該半導体パターンは該第 2 の金属パターンを内包しているので、4 回の写真製版工程で作成され、ソース配線下に半導体層段差が存在しないため、ソース断線が発生しにくく、かつソース電極、ドレイン電極のパターンが半導体パターンに内包されて交差しないため、リーク電流も低く抑えられる。

**【0016】**

20

また、ソース配線とドレイン電極を内包する半導体パターンの外縁の少なくとも一部がゲート配線の外縁の内側に入り込んでいるので、光リークなどによるリーク電流の発生を抑制することができる。

**【0017】**

以上のように本発明によればマスクの写真製版工程数を 4 回で TFT アレイを形成することができるので低コストの TFT アレイを実現することができ、コスト低減、生産量アップを実現することができる。

**【図面の簡単な説明】**

**【0018】**

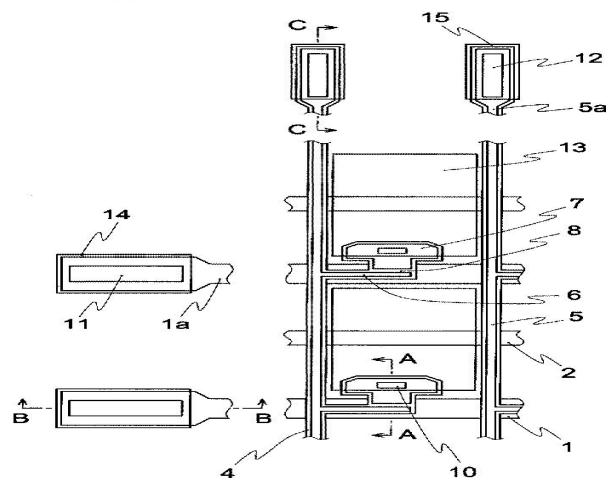

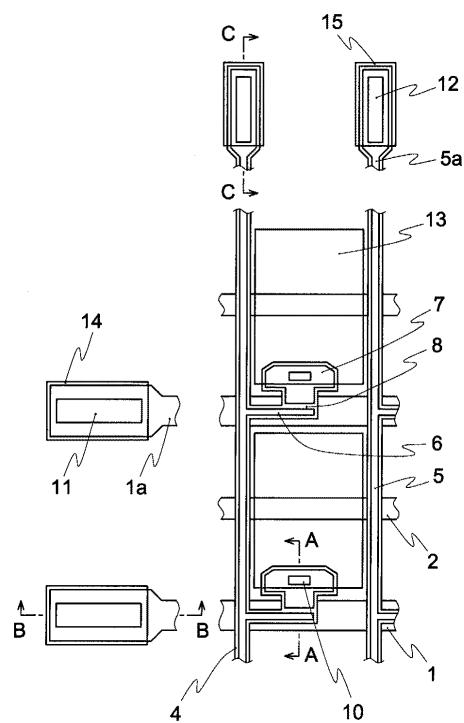

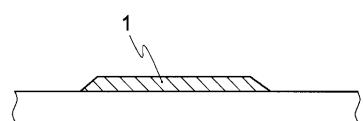

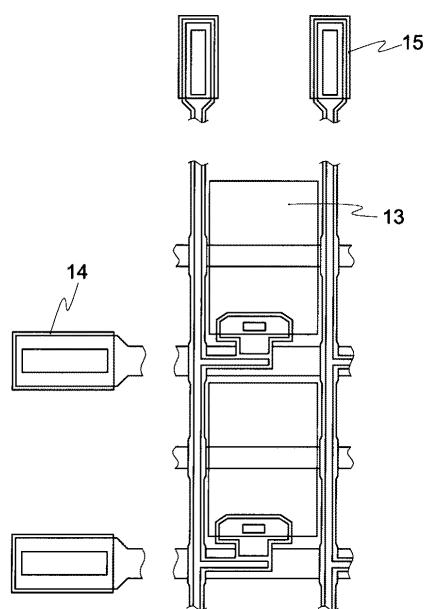

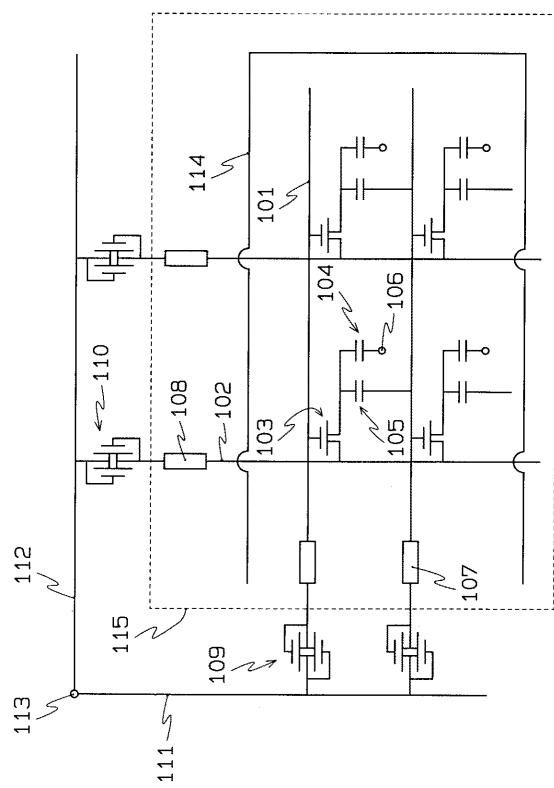

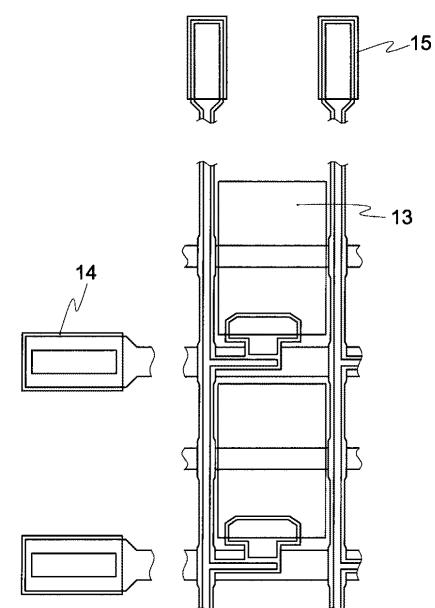

**【図 1】** 本発明を説明するための第 1 の参考例を示す薄膜トランジスタアレイ平面図である。

30

**【図 2】** ( a ) は図 1 の A - A 断面図、( b ) は図 1 の B - B 断面図、( c ) は図 1 の C - C 断面図である。

**【図 3】** 本発明を説明するための第 1 の参考例の薄膜トランジスタアレイ平面図である。

**【図 4】** 第 1 の参考例の各工程での薄膜トランジスタアレイ平面図である。

**【図 5】** 第 1 の参考例の各工程での薄膜トランジスタアレイ平面図である。

**【図 6】** 第 1 の参考例の各工程での薄膜トランジスタアレイ平面図である。

**【図 7】** 第 1 の参考例の各工程での薄膜トランジスタアレイ平面図である。

**【図 8】** 第 1 の参考例の各工程での図 1 の A - A における断面図である。

**【図 9】** 第 1 の参考例の各工程での図 1 の A - A における断面図である。

40

**【図 10】** 第 1 の参考例の各工程での図 1 の A - A における断面図である。

**【図 11】** 第 1 の参考例の各工程での図 1 の A - A における断面図である。

**【図 12】** 第 1 の参考例の各工程での図 1 の A - A における断面図である。

**【図 13】** 第 1 の参考例の各工程での図 1 の A - A における断面図である。

**【図 14】** 第 1 の参考例の各工程での図 1 の A - A における断面図である。

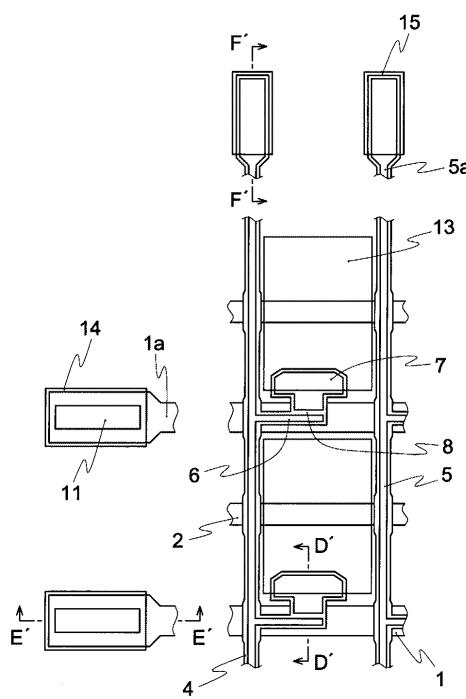

**【図 15】** 本発明を説明するための第 2 の参考例を示す薄膜トランジスタアレイ平面図である。

**【図 16】** 第 2 の参考例の各工程での薄膜トランジスタアレイ平面図である。

**【図 17】** 第 2 の参考例の各工程での薄膜トランジスタアレイ平面図である。

**【図 18】** 第 2 の参考例の各工程での薄膜トランジスタアレイ平面図である。

50

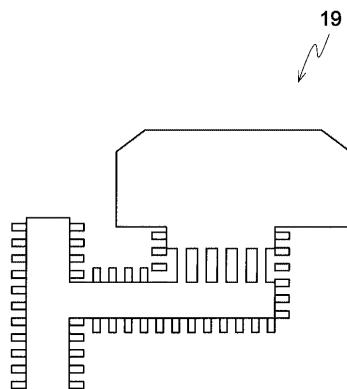

【図19】第2の参考例の各工程での薄膜トランジスタアレイ平面図である。

【図20】第2の参考例の各工程での薄膜トランジスタアレイ平面図である。

【図21】第2の参考例の第2写真製版に用いるマスクのTFT部パターンである。

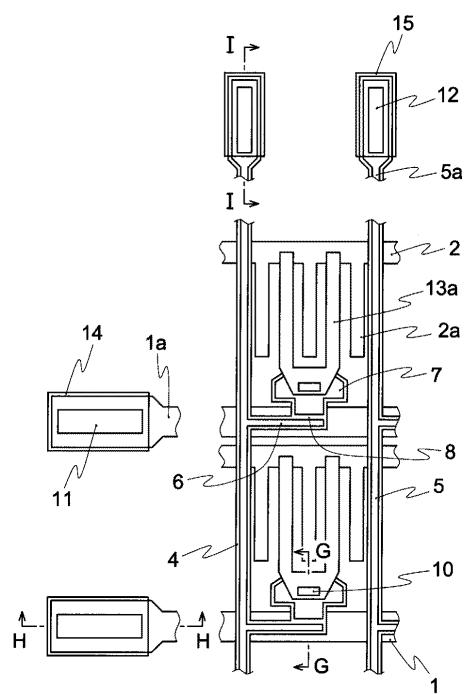

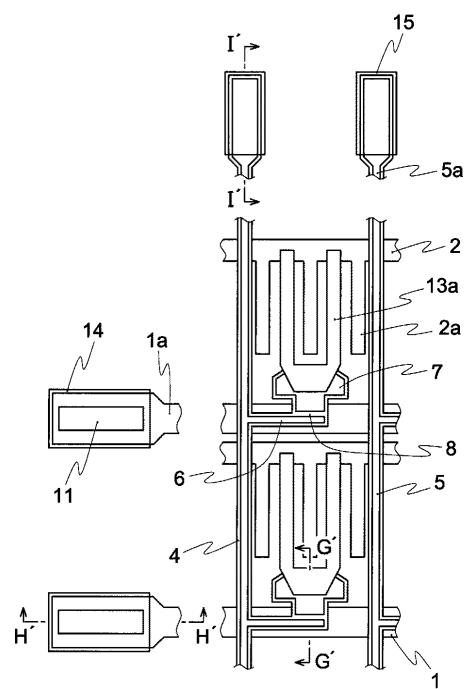

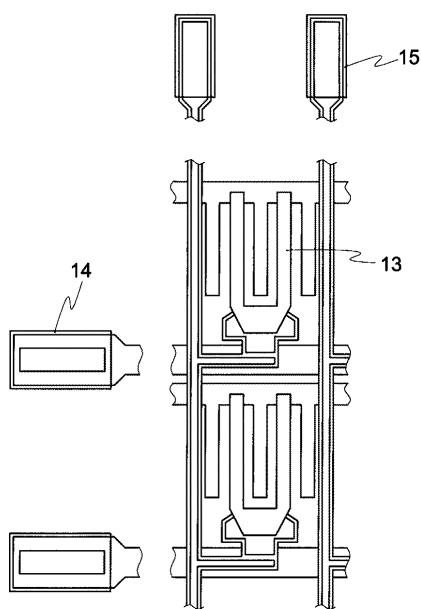

【図22】本発明を説明するための第3の参考例を示す薄膜トランジスタアレイ平面図である。

【図23】第3の参考例の各工程での薄膜トランジスタアレイ平面図である。

【図24】第3の参考例の各工程での薄膜トランジスタアレイ平面図である。

【図25】第3の参考例の各工程での薄膜トランジスタアレイ平面図である。

【図26】第3の参考例の各工程での薄膜トランジスタアレイ平面図である。

【図27】第3の参考例の各工程での薄膜トランジスタアレイ平面図である。

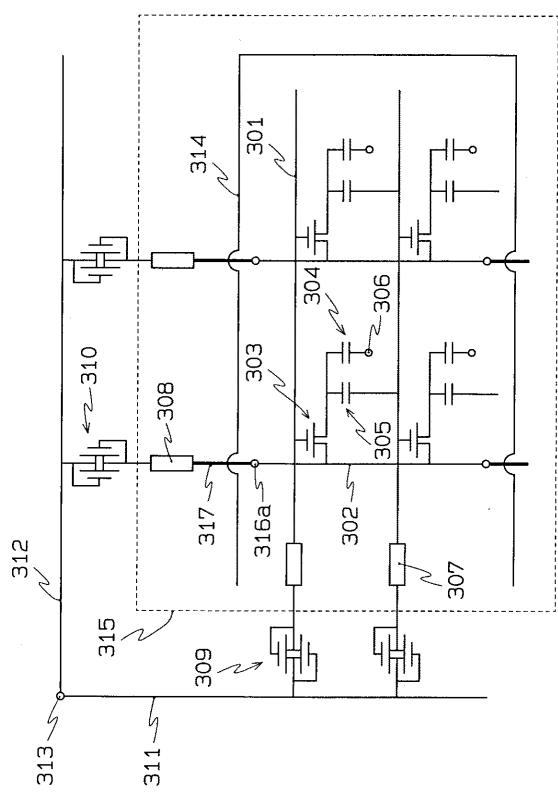

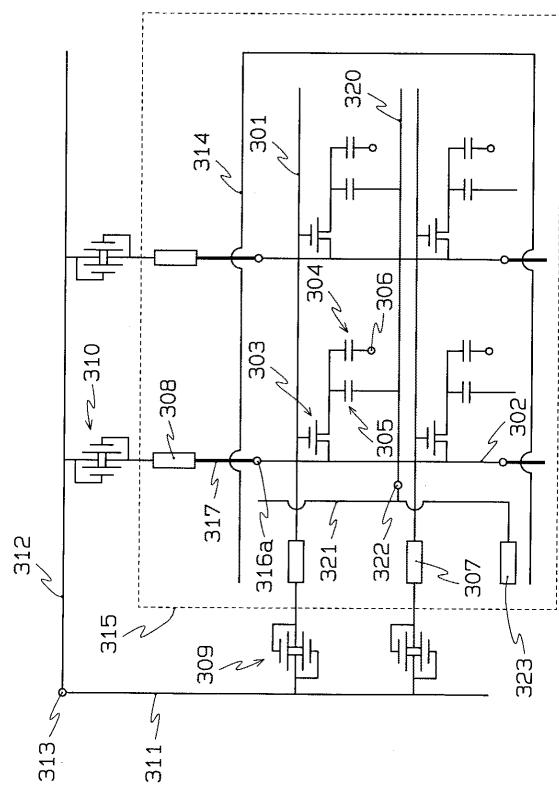

【図28】本発明が適用されるアクティブマトリクス型液晶表示装置のTFTアレイ基板の回路図である。

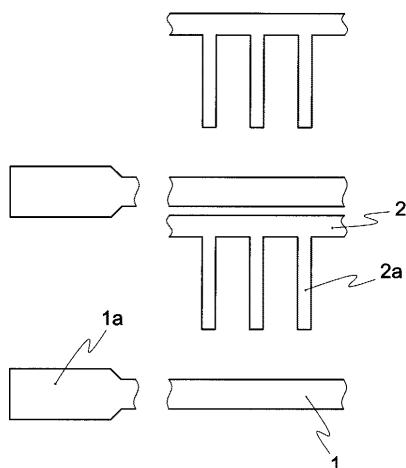

【図29】本発明のTFTアレイ基板の製造工程を示す断面図である。

【図30】本発明のTFTアレイ基板の製造工程を示す断面図である。

【図31】本発明のTFTアレイ基板の製造工程を示す断面図である。

【図32】図29、図30、図31に対応する平面図である。

【図33】ハーフトーンマスクのパターンの例を示す図である。

【図34】ソース配線とリペア配線の交差部の例を示す回路図である。

【図35】保持容量配線をゲート配線と別に設ける共通配線方式を示す回路図である。

【図36】共通配線方式の構成を示す断面図である。

【図37】図9に対応する平面図である。

【図38】共通配線方式の他の例を示す平面図である。

【図39】共通配線方式におけるソース配線とリペア配線の交差部を示す回路図である。

【図40】画素電極の周囲に遮光パターンを形成する平面配置例を示す平面図である。

【図41】IPSモードの平面配置例を示す平面図である。

【図42】本発明のTFTアレイ基板の他の製造方法を示す断面図である。

【図43】本発明のTFTアレイ基板の他の製造方法を示す断面図である。

【図44】本発明のTFTアレイ基板の製造工程を示す断面図である。

【図45】本発明のTFTアレイ基板の製造工程を示す断面図である。

【図46】図44、図45に対応する平面図である。

【図47】図44、図45に対応する平面図である。

【図48】本発明が適用されるアクティブマトリクス型液晶表示装置のTFTアレイ基板の回路図である。

【図49】ソース部子部の一例の断面図である。

【図50】保持容量の共通配線方式を示す回路図である。

【図51】本発明のTFTアレイ基板の断面構造を示す断面図である。

【図52】図51に対応する平面図である。

【図53】図51に対応する平面図である。

【図54】保持容量の共通配線方式を示す回路図である。

【図55】保持容量の共通配線方式を示す回路図である。

【図56】保持容量の共通配線方式を示す回路図である。

【図57】横方向電界用TFTアレイ基板の平面図である。

【図58】図57(c)に対応する製造工程を示す断面図である。

【図59】図1に相当する他の態様を示す平面図である。

【図60】(a)～(d)は図2の(a)～(d)に相当する他の態様を示す断面図である。

【図61】図3～5に示す製造工程に追加される、さらなる工程を示す説明図である。

【図62】図13に相当する他の態様の製作工程を示す説明図である。

【図63】図14に相当する他の態様の製作工程を示す説明図である。

【図64】図15に相当する他の態様を示す平面図である。

10

20

30

40

50

【図65】図16～18に示す製作工程に追加される、さらなる工程を示す説明図である。

【図66】図22に相当する他の態様を示す平面図である。

【図67】図23～25に示す製作工程のつぎに、図26～27に示す工程に代えて行う工程を示す説明図である。

【図68】半導体領域の他の態様を示す図32の(d)に相当する説明図である。

【図69】半導体領域のさらに他の態様を示す図32の(d)に相当する説明図である。

【発明を実施するための形態】

【0019】

参考例1

10

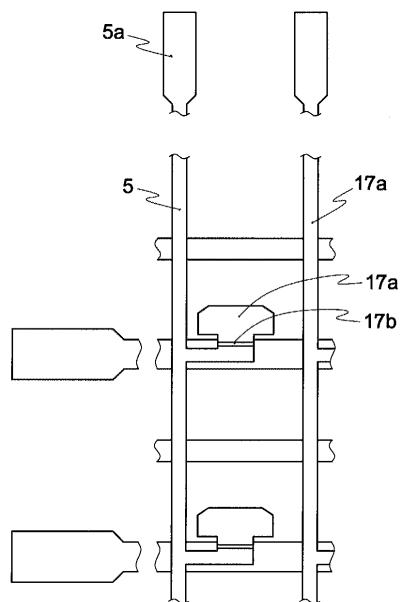

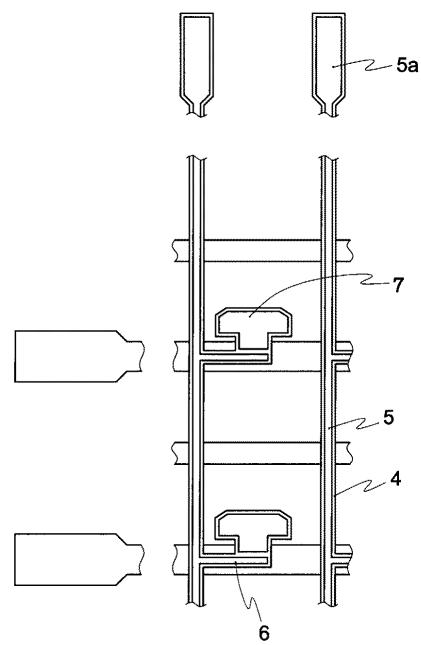

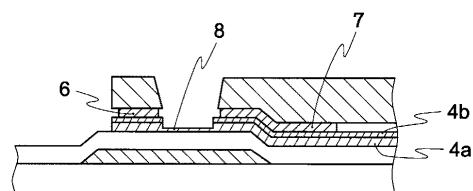

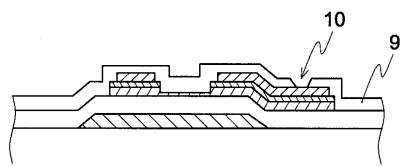

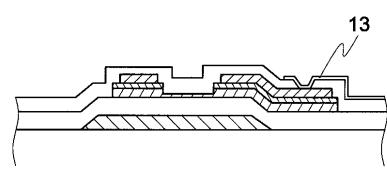

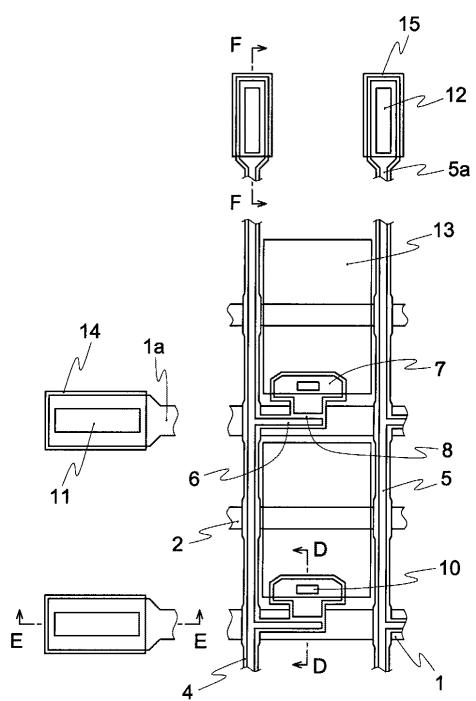

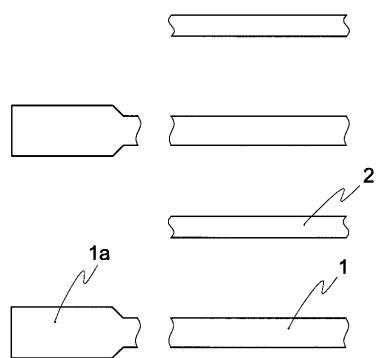

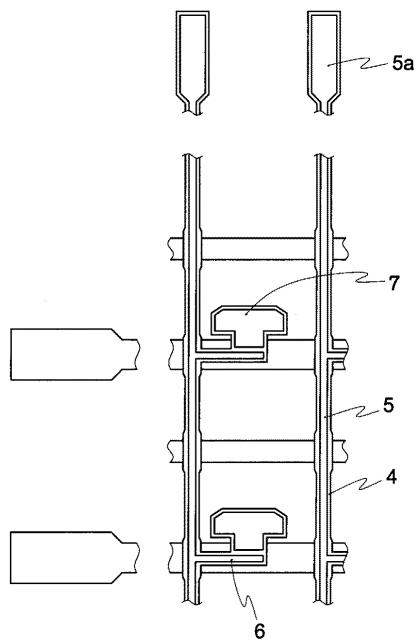

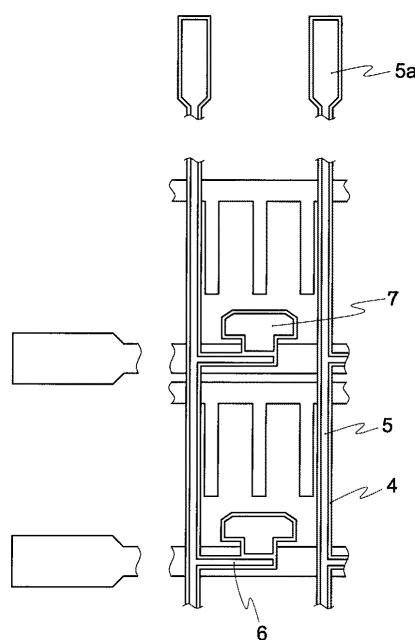

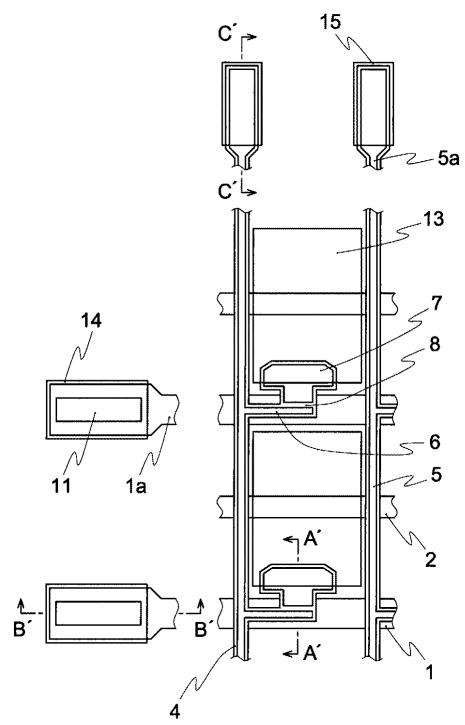

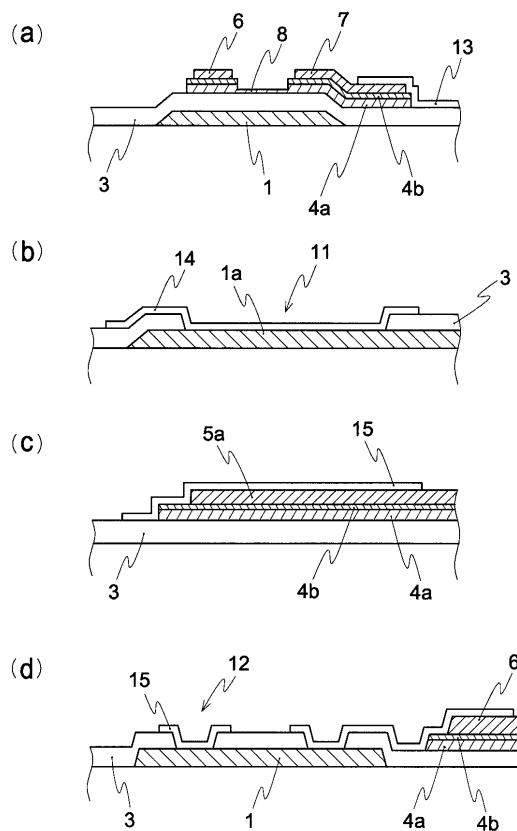

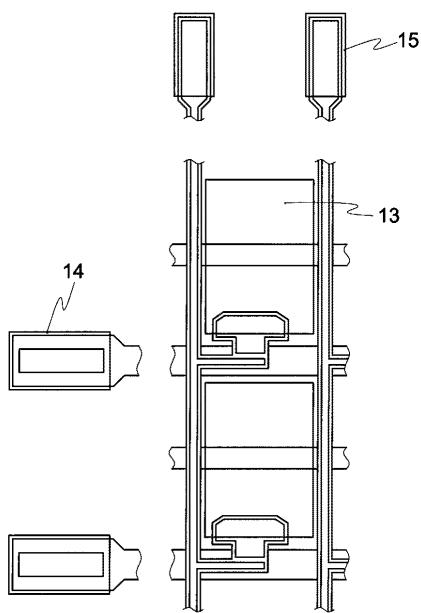

図1、図2は、本発明を説明するための第1の参考例である薄膜トランジスタ基板であり図1は平面図、図2(a)は図1におけるA-Aでの断面図、図2(b)は図1におけるB-Bでの断面図、図2(c)は図1におけるC-Cでの断面図である。図1、2において、1はゲート配線、1aはゲート端子部金属パッド、2は補助容量配線、3はゲート絶縁膜、4は半導体パターン、4aは半導体層(半導体能動膜)、4bはオーミック層(オーミックコンタクト膜)、5はソース配線、5aはソース端子部金属パッド、6はソース電極、7はドレイン電極、8は薄膜トランジスタの半導体活性層、9は層間絶縁膜、10はドレイン電極コンタクトホール、11はゲート端子部コンタクトホール、12はソース端子部コンタクトホール、13は画素電極、14はゲート端子接続パッド、15はソース端子接続パッドである。

20

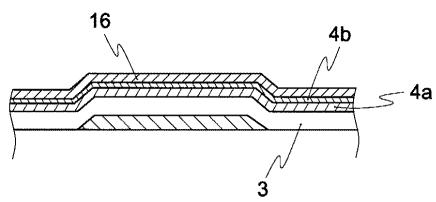

【0020】

つぎに製造方法について説明する。図3から7までが各工程での平面図であり、図8から図14までが各工程での図1A-A断面を示している。まず透明基板上に400nm程度の厚さでCr、Ta、Mo、Alなどの第1の導電性金属薄膜が形成される。つぎに第1の写真製版工程で第1の導電性金属薄膜をパターニングして図3、図8のようにゲート配線1、ゲート端子部金属パッド1a、補助容量配線2を形成する。このとき、第1の導電性金属薄膜がCrの場合には、例えば $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$ 液を用いてウエットエッチング処理される。つぎに図9に示すようにゲート絶縁膜3として $\text{SiN}_x$ 膜、半導体能動膜4aとしてa-Si膜、オーミックコンタクト膜4bとして $n^+a-Si$ 膜、第2の金属膜16としてCrをそれぞれ400nm、150nm、30nm、400nm程度の膜厚で積層する。 $\text{SiN}_x$ 、a-Si、 $n^+a-Si$ 膜はプラズマCVD装置を用いて成膜し、オーミック層成膜時には $\text{PH}_3$ をドープして $n^+a-Si$ を形成する。Cr成膜についてはDCマグネットロン型スパッタ装置を用いて成膜する。

30

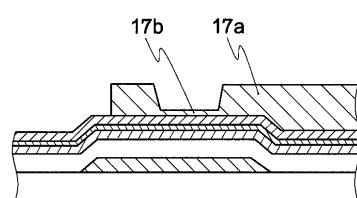

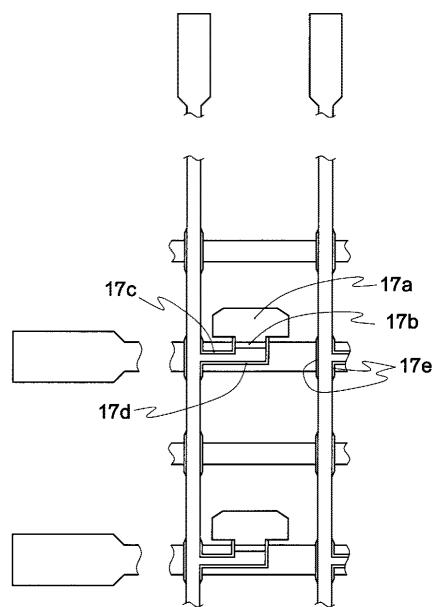

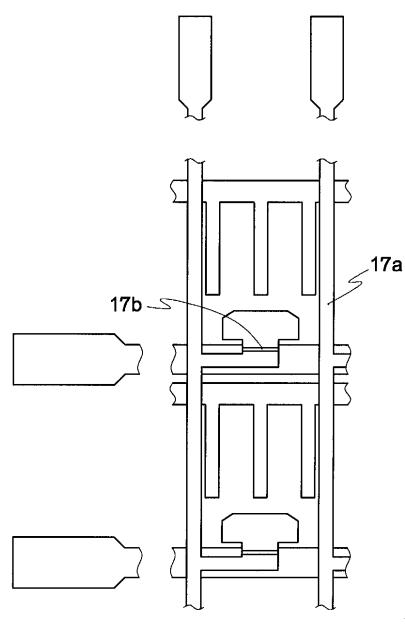

【0021】

つぎに第2の写真製版工程で図4に示すようにソース配線5、ソース端子部金属パッド5a、ドレイン電極7を形成するための通常膜厚のレジストパターン17aおよび薄膜トランジスタの半導体活性層8を形成するための薄膜のレジストパターン17bを形成する。ここでレジストはノボラック樹脂系のポジ型レジストを用い、レジスト塗布はスピンドルにより1.5μmとする。レジスト塗布後は120～90秒プリベークを実施し、その後、レジストパターン17aおよびレジストパターン17bを包括するマスクパターンで1000ms exposure露光を行い、その後半導体活性層部のレジストパターン17bのみ露光できるマスクパターンを用いて400ms exposure追加露光を行った。この2段階の露光を行なうことにより、通常膜厚のレジストパターン17aと薄膜レジストパターン17bの膜厚を異なるものとしている。露光機はステッパーあるいはミラープロジェクションタイプの露光機であり、光源には高圧水銀ランプのg線、h線を用いた。ついで、有機アルカリ系の現像液を用いて現像したのち、100～120でポストベークを180秒実施、レジスト中の溶媒を揮発させると同時にレジストとCrの密着力を高める。これらのプロセスによって、薄膜トランジスタ部のレジスト形状は図10に示すような形状となる。ここで通常膜厚レジストパターン17aのレジスト膜厚は1.4μm程度、薄膜レジストパターン17bのレジスト膜厚は0.4μm程度となる。

40

50

## 【0022】

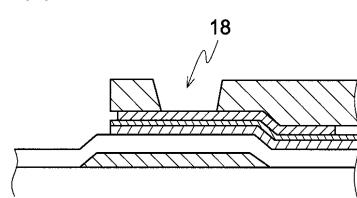

その後さらに120から130でオープンベークを実施し、さらにレジスト・Cr間の密着力を高める。このときベーク温度が高すぎる場合にはレジスト端面がだれてしまうので注意を要する。その後Cr膜16のエッティングを $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$ 液を用いて実施する。その後HCl + SF<sub>6</sub> + Heガスを用いてオーミック膜4bおよび半導体膜4aをエッティングする。その後酸素プラズマによりレジストをアッティングし、図11に示すように薄膜レジストパターン17bを除去して薄膜トランジスタ活性層8の該当部のCr膜を露出するようにする。アッティングは圧力が40Paで60秒実施した。またアッティングする際はRIEモードの方がPEモードに比べて、図11の18に示すレジスト開口部の大きさが制御しやすい。

10

## 【0023】

その後130から140でオープンベークを実施した後、 $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$ 液を用いて開口部18にあるCr膜16をエッティングする。このときCrパターン全体にサイドエッティングが入るため、a-Siパターンに比べCrパターンは1.5から2μm程度細くなる(a-Siパターンより内側となる)。このことによってソース電極からドレイン電極でのa-Siパターン端面を通じてのリーク電流を抑制することができる。このCrエッティングではある程度のオーバーエッティングが必要となる。オーバーエッティングの量は50%程度が望ましい。ついで図12に示すようにSF<sub>6</sub> + HClを用いて半導体活性層該当部8にあるオーミック層4bおよび半導体層4aの一部を合計100nm程度エッティングする。その後レジストを除去すると図5に示すとおり、半導体パターン4、ソース配線5、ソース電極6、ドレイン電極7、ソース端子部金属パッド5aが形成される。

20

## 【0024】

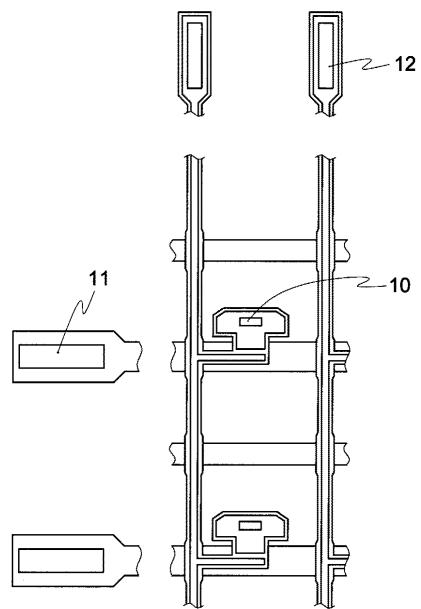

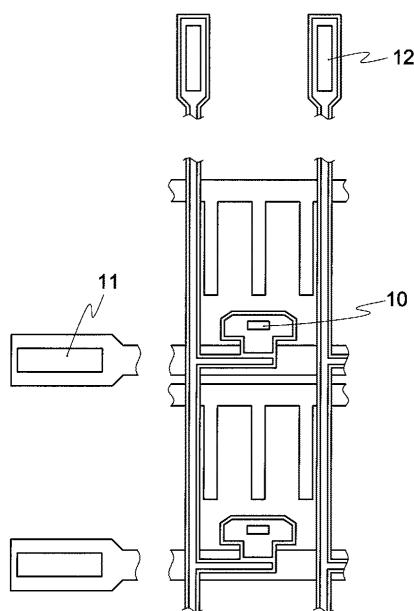

つぎに図6および図13に示すとおり、PCVD装置を用いて層間絶縁膜9であるSi<sub>N</sub><sub>x</sub>を300nm形成し、第3の写真製版工程でパターニングして、図2(a)、図2(b)、図2(c)、図6、図13に示すドレイン電極7に通じるコンタクトホール10、ゲート端子部金属パッド1aに通じるコンタクトホール11、ソース端子部金属パッドに通じるコンタクトホール12をCF<sub>4</sub> + O<sub>2</sub>を用いたドライエッティングで形成する。つぎに図7および図14に示すように100nm程度の厚さでITOよりなる透明導電膜をDCマグネットロン型スパッタ装置を用いて形成する。つぎに第4の写真製版工程でITOをパターニングして透明画素電極13、ゲート端子部パッド14およびソース端子部パッド15を形成する。このとき、例えばHCl + HNO<sub>3</sub> + H<sub>2</sub>O液を用いてITO膜がウエットエッティング処理される。

30

## 【0025】

このようにして製造された薄膜トランジスタアレイ基板は4回の写真製版工程で作成され、ソース配線下に半導体層段差が存在しないため、ソース断線が発生しにくく、かつソース電極、ドレイン電極のパターンが半導体パターンの内側に内包されて交差しないため、薄膜トランジスタ部のリーク電流も低く抑えられた。また第2金属膜16を単層の金属とすることにより、第2金属膜16のエッティング回数を2回で済むようにしている。またその金属をCrにすることにより、画素をITOで形成するとき、そのエッチャントによる層間絶縁膜9に存在するピンホールを介してソース配線などが腐食されることを防止している。

40

## 【0026】

図2(a)はTFT部分の断面図、図2(b)はゲート端子部の断面図、図2(c)、(d)はソース端子部の断面図である。ソース端子部は、図2(c)に示すようにソース配線層5aの上にたとえば透明導電層からなるソース端子パッド15を接続した構成を用いてもよいが、図2(d)に示すように途中でソース配線層5aからゲート配線材料1に変換してもよい。ソース端子部の配線材料を変換する位置はソース配線用のリペア線の下部(この場合、リペア線はソース配線材料で形成する)または、シール部近傍または液晶部などで変換することができる。配線材料をソース配線材料からゲート配線材料に変換す

50

ることにより、ソース端子部近傍でのソース配線材料の腐食による断線を防ぐことができる。

【0027】

ソース配線をゲート配線材料1に変換する場合のソース端子部の構造を図2(d)により説明する。ゲート配線パターンを形成する工程でゲート配線材料1によりソース配線変換部1'を形成する。さらに層間絶縁膜9およびゲート絶縁膜3を貫通して第1、第2、第3のコンタクトホール10、11、12を形成する工程で第4、第5のコンタクトホール12'、12"を形成し、画素電極13を形成する工程でソース配線上のコンタクトホール12"とソース配線変換部1'の一端のコンタクトホール12'とを接続する透明導電膜15'および、ソース配線変換部1'の他端のコンタクトホール12に形成されるソース端子パッド15を形成する。

10

【0028】

本実施の形態においては層間絶縁膜9を用いていたが、この層間絶縁膜9を用いなくてもよい。この場合図1に相当する平面図は図59に、製造工程を示す図2(a)、(b)、(c)、(d)に相当する断面図は図60(a)、(b)、(c)、(d)となる。また、製造工程を示す平面図、図3~7において、図3~5に示す工程は前記と同様な工程となり、次の工程を示す平面図は図61となる。

【0029】

また、工程断面図8~14において、図8~12に相当する工程は前記と同様であり、図13、14に相当する製作工程は図62、63で示され、図63に示す工程時における端子部の構造断面図は図60となる。

20

【0030】

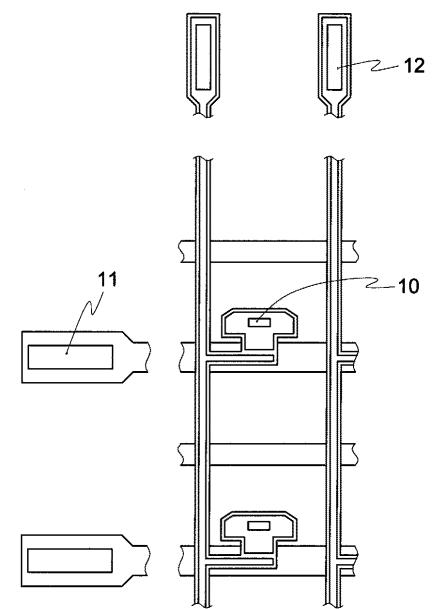

参考例2

図15は、本発明を説明するための第2の参考例である薄膜トランジスタ基板であり、図15中のD-D、E-E、F-F断面は第1の実施形態と同じであり、それぞれ図2(a)、図2(b)、図2(c)に示す。ここに1はゲート配線、1aはゲート端子部金属パッド、2は補助容量配線、3はゲート絶縁膜、4は半導体パターン、4aは半導体層、4bはオーミック層、5はソース配線、5aはソース端子部金属パッド、6はソース電極、7はドレイン電極、8は薄膜トランジスタの半導体活性層、9は層間絶縁膜、10はドレイン電極コンタクトホール、11はゲート端子部コンタクトホール、12はソース端子部コンタクトホール、13は画素電極、14はゲート端子接続パッド、15はソース端子接続パッドである。

30

【0031】

つぎに製造方法について説明する。図16から図20までが各工程での平面図であり、第1の実施形態と同様、図8から図14までが各工程での図15のD-D断面を示している。

【0032】

まず透明基板上に400nm程度の厚さでCr、Ta、Mo、Alなどの第1の導電性金属薄膜が形成される。つぎに第1の写真製版工程で第1の導電性金属薄膜をパターニングして図16、図8のようにゲート配線1、ゲート端子部金属パッド1a、補助容量配線2を形成する。このとき、第1の導電性金属薄膜がCrの場合には、例えば(NH<sub>4</sub>)<sub>2</sub>[Ce(NO<sub>3</sub>)<sub>6</sub>] + HNO<sub>3</sub> + H<sub>2</sub>O液を用いてウエットエッティング処理される。つぎに図9に示すようにゲート絶縁膜3としてSiN<sub>x</sub>膜、半導体能動膜4aとしてa-Si膜、オーミックコンタクト膜4bとしてn<sup>+</sup>a-Si膜、第2の金属膜16としてCrをそれぞれ400nm、105nm、30nm、400nm程度の膜厚で積層する。SiN<sub>x</sub>、a-Si、n<sup>+</sup>a-Si膜はプラズマCVD装置を用いて成膜し、オーミック成膜時にはPH<sub>3</sub>をドープしてn<sup>+</sup>a-Siを形成する。Cr成膜についてはDCマグネットロン型スパッタ装置を用いて成膜する。

40

【0033】

つぎに第2の写真製版工程で図17に示すようにソース配線、ソース端子部金属パッド

50

、ドレイン電極を形成するためのレジストパターン17aおよび薄膜トランジスタの半導体活性層8を形成するためのレジストパターン17b、半導体端面リーケ防止用レジストパターン17c、17d、およびゲート・ソース配線間ショート防止用レジストパターン17eを形成する。ここでレジストはノボラック樹脂系のポジ型レジストを用い、レジスト塗布はスピンドルコータにより1.5μmとする。レジスト塗布後は120で90秒ブリーバークを実施し、その後、レジストパターン17aは通常のCr全面マスクパターンでありかつ、レジストパターン17b、17c、17d、17eをライン/スペース=1.5μm/1.5μmのCrストライプ形状を有するマスクパターンを用いて1000ms曝光を行った。ストライプマスクパターンを図21に示す。露光機は通常のステッパーあるいはミラープロジェクションタイプの露光機であり、光源には高圧水銀ランプのg線、h線を用いた。このとき、ストライプパターンは露光装置の解像限界よりも微細なパターンなので、レジストはストライプ状には露光されず、平均的で他の露光部よりも少ない露光量となる。

#### 【0034】

ついで、有機アルカリ系の現像液を用いて現像したのち、100から120でポストブリーバークを180秒実施、レジスト中の溶媒を揮発させると同時にレジストとCrの密着力を高める。これらのプロセスによって、薄膜トランジスタ部のレジスト形状は図10に示すような形状となる、ここでレジストパターン17aの膜厚は1.4μm程度、レジストパターン17b、17c、17d、17eの膜厚は0.4から0.6μm程度となる。その後さらに120から130でオーブンブリーバークを実施し、さらにレジスト・Cr間の密着力を高める。このときブリーバーク温度が高すぎる場合にはレジスト端面がだれてしまうので注意を要する。その後Cr膜16のエッチャリングを $(NH_4)_2[Ce(NO_3)_6] + HNO_3 + H_2O$ 液を用いて実施する。その後HCl+SF<sub>6</sub>ガスを用いてオーミック膜4bおよび半導体膜4aをエッチャリングする。その後酸素プラズマによりレジストをアッシングし、レジストパターン17b、17c、17d、17e部のCr膜を露出するようにする。アッシングは圧力が40Paで60秒実施した。またアッシングする際はRIEモードの方がPEモードに比べて、図11の18に示すレジスト開口部の大きさが制御しやすい。

#### 【0035】

その後130から140でオーブンブリーバークを実施した後、 $(NH_4)_2[Ce(NO_3)_6] + HNO_3 + H_2O$ 液を用いて17b、17c、17d、17eにあるCr膜16をエッチャリングする。本パターンではソース電極およびドレイン電極付近の半導体パターンをより離して配置してあるため、実施の形態1に比べさらに半導体端面リーケの発生抑制効果およびCrオーバーエッチマージンが広い。このパターンの場合は20から50%程度のCrオーバーエッチャリングが可能となる。但しこの場合注意しなければならないのは、17cのパターンにより形成されるa-Siパターンが連続してゲート配線の外縁からはみ出している場合には、保持状態のときに、この部分にゲートオフバイアスが印加されずかつ、ゲートパターンで遮光されないためリーケ電流が多くなる。したがって、ソース配線とドレイン電極を内包する半導体パターンの外縁の少なくとも一部が、図17の17cに示すようにゲート配線の外縁より内側に入り込んでいる必要がある。すなわち、半導体パターンのうち、薄膜トランジスタを内包する領域がソース配線を内包する領域へ向けて延長される経路上の少なくとも一部において、半導体パターンの両側の外縁がともにゲート配線上の外縁と交差するように形成する必要がある。17dについては薄膜トランジスタの配置により自動的に交差が行なわれるが、17cについては意図的に交差させことが有効である。ついで図12に示すようにSF<sub>6</sub>+HClを用いてレジストパターン17b、17c、17d、17e部にあたるオーミック層4bおよび半導体層4aの一部を合計100nm程度エッチャリングする。その後レジストを除去すると図18に示すとおり、半導体パターン4、ソース配線5、ソース電極6、ドレイン電極7、ソース端子部金属パッド5aが形成される。

#### 【0036】

10

20

30

40

50

つぎに P C V D 装置を用いて層間絶縁膜 9 である  $\text{SiN}_x$  を 300 nm 形成し、第 3 の写真製版工程でパターニングして、図 2 (a)、図 2 (b)、図 2 (c)、図 13、図 19 に示すドレイン電極 7 に通じるコンタクトホール 10、ゲート端子部金属パッド 1a に通じるコンタクトホール 11、ソース端子部金属パッドに通じるコンタクトホール 12 を  $\text{CF}_4 + \text{O}_2$  を用いたドライエッティングで形成する。つぎに 100 nm 程度の厚さで ITO よりなる透明導電膜を DC マグネトロン型スパッタ装置を用いて形成する。つぎに第 4 の写真製版工程で ITO をパターニングして図 2 (a)、図 2 (b)、図 2 (c)、図 14、図 20 に示す透明画素電極 13、ゲート端子部パッド 14 およびソース端子部パッド 15 を形成する。このとき、例えば  $\text{HCl} + \text{HNO}_3 + \text{H}_2\text{O}$  液を用いて ITO 膜がウエットエッティング処理される。

10

#### 【0037】

このようにして製造された薄膜トランジスタアレイは 4 回の写真製版工程で作成され、ソース配線下に半導体層段差が存在しないため、ソース断線が発生しにくく、かつソース電極、ドレイン電極のパターンが半導体パターンと交差しない上、薄膜トランジスタ半導体パターン端面とソース電極およびドレイン電極との間隔が広がっているため、リーク電流もより低く抑えられた。また、ソース配線とドレイン電極を内包する半導体パターンの外縁の少なくとも一部がゲート配線の外縁の内側に入り込んだ構造を有することにより、光リーク等によるリーク電流の増加を防止している。

#### 【0038】

以上の実施形態においては層間絶縁膜 9 を用いていたが、この層間絶縁膜 9 を用いなくともよい。この場合、図 15 に相当する平面図は図 64 のようになる。また、製造工程を示す平面図である図 16 ~ 20 に示す工程において、図 16 ~ 18 に示す工程は前記と同様に実施し、ついで図 65 に示す工程を実施する。

20

#### 【0039】

この実施の形態においては、ゲート端子パッド 14 およびソース端子パッド 15 として透明導電膜（画素電極 13）が第 1 の金属膜 1a および第 2 の金属膜 5a 上にそれぞれのコンタクトホール 11 および 12 を覆って形成されていたが、透明導電膜 13 を端子パッド 14、15 上に形成せず、第 1 の金属膜 1a および第 2 の金属膜 5a をそれぞれのコンタクトホールで露出させたままでし、それに直接実装などをしてよい。

#### 【0040】

30

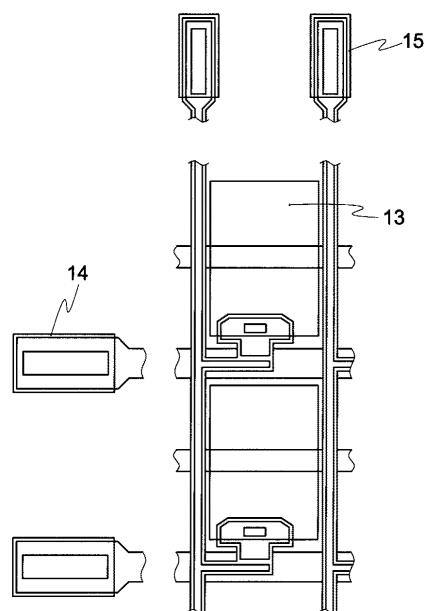

#### 参考例 3

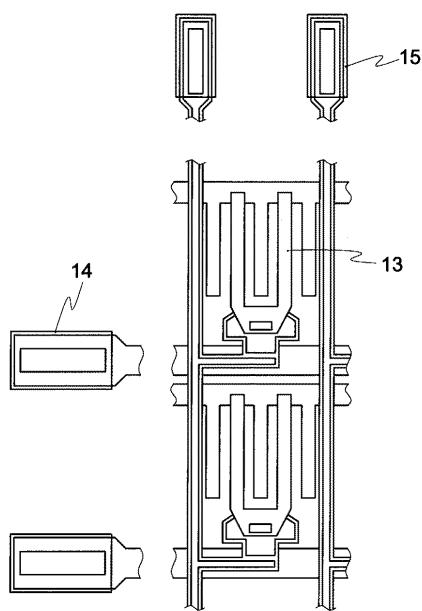

図 22 は、本発明を説明するための第 3 の参考例である薄膜トランジスタ基板であり G - G での断面、H - H での断面、I - I での断面はそれぞれ図 2 (a)、図 2 (b)、図 2 (c) と同様である。ここに 1 はゲート配線、1a はゲート端子部金属パッド、2 は補助容量配線、2a は IPS 対向電極、3 はゲート絶縁膜、4 は半導体パターン、4a は半導体層、4b はオーミック層、5 はソース配線、5a はソース端子部金属パッド、6 はソース電極、7 はドレイン電極、8 は薄膜トランジスタの半導体活性層、9 は層間絶縁膜、10 はドレイン電極コンタクトホール、11 はゲート端子部コンタクトホール、12 はソース端子部コンタクトホール、13a は IPS 電極、14 はゲート端子接続パッド、15 はソース端子接続パッドである。

40

#### 【0041】

つぎに製造方法について説明する。図 23 から図 27 までが各工程での平面図であり、第 1 の実施の形態と同様に図 8 から図 14 までが各工程での図 22 G - G 断面を示している。

#### 【0042】

まず透明基板上に 400 nm 程度の厚さで Cr、Ta、Mo、Al などの第 1 の導電性金属薄膜が形成される。つぎに第 1 の写真製版工程で第 1 の導電性金属薄膜をパターニングして図 23、図 8 のようにゲート配線 1、ゲート端子部金属パッド 1a、補助容量配線 2、IPS 対向電極 2a を形成する。このとき、第 1 の導電性金属薄膜が Cr の場合には、例えば  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$  液を用いてウエットエッティング

50

処理される。つぎに図9に示すようにゲート絶縁膜3としてSiN<sub>x</sub>膜、半導体能動膜4aとしてa-Si膜、オーミックコンタクト膜4bとしてn<sup>+</sup>a-Si膜、第2の金属膜16としてCrをそれぞれ400nm、150nm、30nm、400nm程度の膜厚で積層する。SiN<sub>x</sub>、a-Si、n<sup>+</sup>a-Si膜はプラズマCVD装置を用いて成膜し、オーミック成膜時にはPH<sub>3</sub>をドープしてn<sup>+</sup>a-Siを形成する。Cr成膜についてはDCマグネットロン型スパッタ装置を用いて成膜する。

#### 【0043】

つぎに第2の写真製版工程で図24に示すようにソース配線、ソース端子部金属パッド、ドレイン電極を形成するためのレジストパターン17aおよび薄膜トランジスタの半導体活性層8を形成するためのレジストパターン17bを形成する。ここでレジストはノボラック樹脂系のポジ型レジストを用い、レジスト塗布はスピンドルコータにより1.5μmとする。レジスト塗布後は120℃で90秒プリベークを実施し、その後、レジストパターン17aおよびレジストパターン17bを包括するマスクパターンで1000msc露光を行い、その後半導体活性層部のレジストパターン17bのみ露光できるマスクパターンを用いて400msc追加露光を行った。露光機はステッパあるいはミラープロジェクションタイプの露光機であり、光源には高圧水銀ランプのg線、h線を用いた。ついで、有機アルカリ系の現像液を用いて現像したのち、100℃から120℃でポストベークを180秒実施、レジスト中の溶媒を揮発させると同時にレジストとCrの密着力を高める。これらのプロセスによって、薄膜トランジスタ部のレジスト形状は図10に示すような形状となる。ここで17aのレジスト膜厚は1.4μm程度、17bのレジスト膜厚は0.4μm程度となる。

#### 【0044】

その後さらに120℃から130℃でオーブンベークを実施し、さらにレジスト・Cr間の密着力を高める。このときベーク温度が高すぎる場合にはレジスト端面がだれてしまうので注意を要する。その後Cr膜16のエッティングを(NH<sub>4</sub>)<sub>2</sub>[Ce(NO<sub>3</sub>)<sub>6</sub>] + HNO<sub>3</sub> + H<sub>2</sub>O液を用いて実施する。その後HCl + SF<sub>6</sub> + Heガスを用いてオーミック層4bおよび半導体層4aをエッティングする。その後酸素プラズマによりレジストをアッシングし、図11に示すように半導体活性層8の該当部のCr膜を露出するようにする。アッシングは圧力が40Paで60秒実施した。またアッシングする際はRIEモードの方がPEモードに比べて、図11の18に示すレジスト開口部の大きさが制御しやすい。

#### 【0045】

その後130℃から140℃でオーブンベークを実施した後、(NH<sub>4</sub>)<sub>2</sub>[Ce(NO<sub>3</sub>)<sub>6</sub>] + HNO<sub>3</sub> + H<sub>2</sub>O液を用いて開口部18にあるCr膜16をエッティングする。(NH<sub>4</sub>)<sub>2</sub>[Ce(NO<sub>3</sub>)<sub>6</sub>] + HNO<sub>3</sub> + H<sub>2</sub>O液を用いて開口部18にあるCr膜16をエッティングする。このときCrパターン全体にサイドエッティングが入るため、a-Siパターンに比べCrパターンは1.5から2μm程度細くなる。このことによってソース電極からドレイン電極でのa-Siパターン端面を通じてのリーク電流を抑制することができる。このCrエッティングではある程度のオーバーエッティングが必要となる。オーバーエッティングの量は50%程度が望ましい。

#### 【0046】

ついで図12に示すようにSF<sub>6</sub> + HClを用いて半導体活性層8の該当部にあるオーミック膜4bおよび半導体層4aの一部を合計100nm程度エッティングする。その後レジストを除去すると図25に示すとおり、半導体パターン4、ソース配線5、ソース電極6、ドレイン電極7、ソース端子部金属パッド5aが形成される。つぎに図6および図13に示すとおり、PCVD装置を用いて層間絶縁膜9であるSiN<sub>x</sub>を300nm形成し、第3の写真製版工程でパターンングして、図26、図2(a)、図2(b)、図2(c)に示すドレイン電極7に通じるコンタクトホール10、ゲート端子部金属パッド1aに通じるコンタクトホール11、ソース端子部金属パッドに通じるコンタクトホール12をCF<sub>4</sub> + O<sub>2</sub>を用いたドライエッティングで形成する。

10

20

30

40

50

## 【0047】

つぎに図27および図14に示すように100nm程度の厚さでCrよりなる導電膜をDCマグネットロン型スパッタ装置を用いて形成する。つぎに第4の写真製版工程でCrをパターニングしてIPS電極13a、ゲート端子部パッド14およびソース端子部パッド15を形成する。このとき、例えば $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$ 液を用いてCr膜がウエットエッチング処理される。

## 【0048】

このようにして製造された薄膜トランジスタアレイは4回の写真製版工程で作成され、ソース配線下に半導体層段差が存在しないため、ソース断線が発生しにくく、かつソース電極、ドレイン電極のパターンが半導体パターンに内包されて交差しないため、リーク電流も低く抑えられた。 10

## 【0049】

また最上層に配置されたIPS電極をCrで形成したことにより、パネル組み立て工程等後工程でのブラシ洗浄においても、傷等のパターンの乱れの発生を防止することができる。

## 【0050】

以上の実施形態においては層間絶縁膜9を用いていたが、この層間絶縁膜9を用いなくともよい。この場合、図22に相当する平面図は図66のようになる。また、製造工程を示す平面図である図23～27に示す工程において、図23～25に示す工程は前記と同様に実施し、ついで図67に示す工程を実施する。 20

## 【0051】

## 実施の形態4

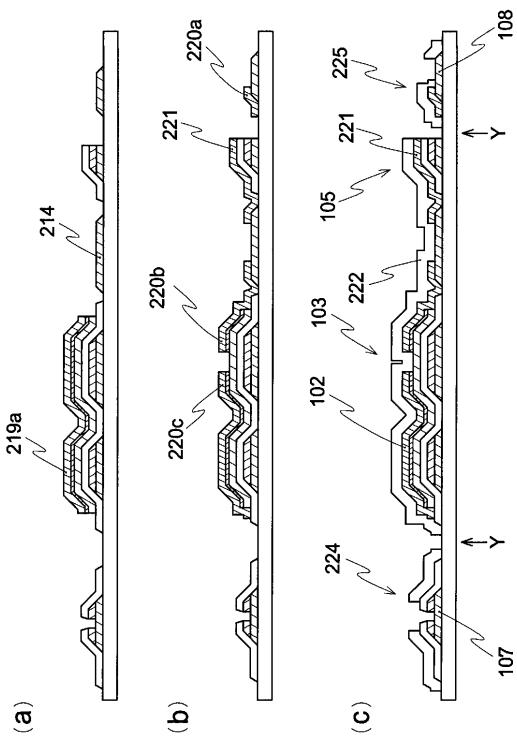

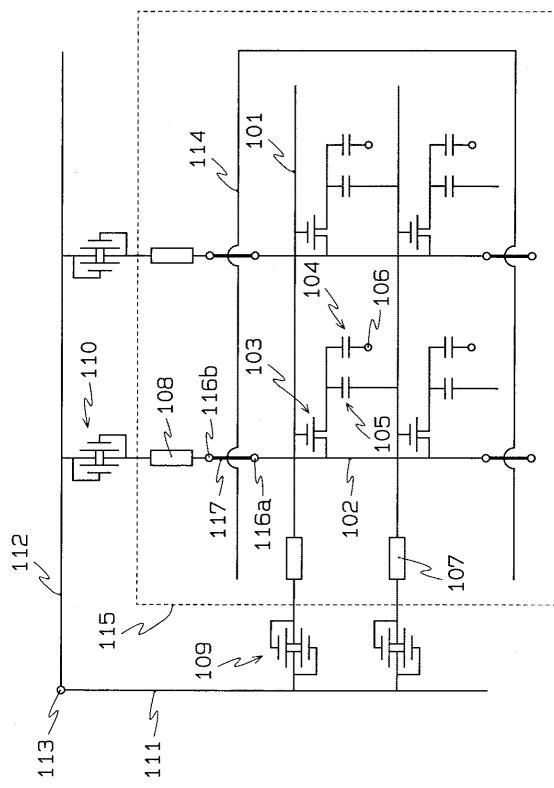

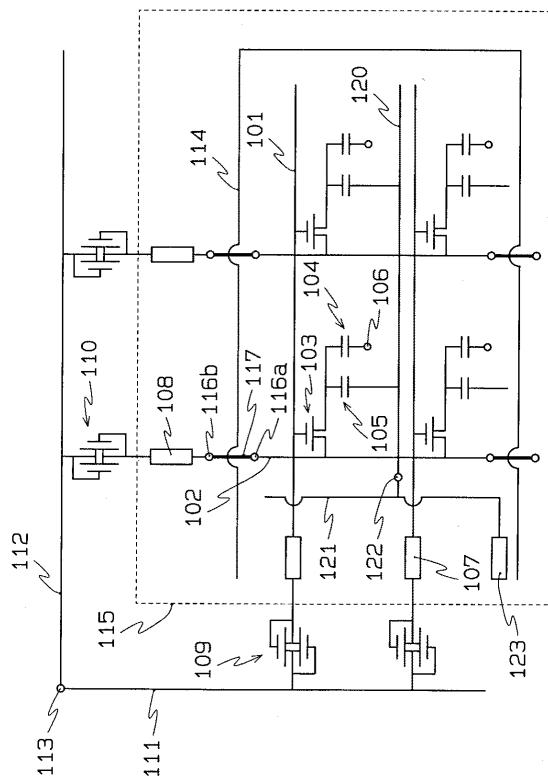

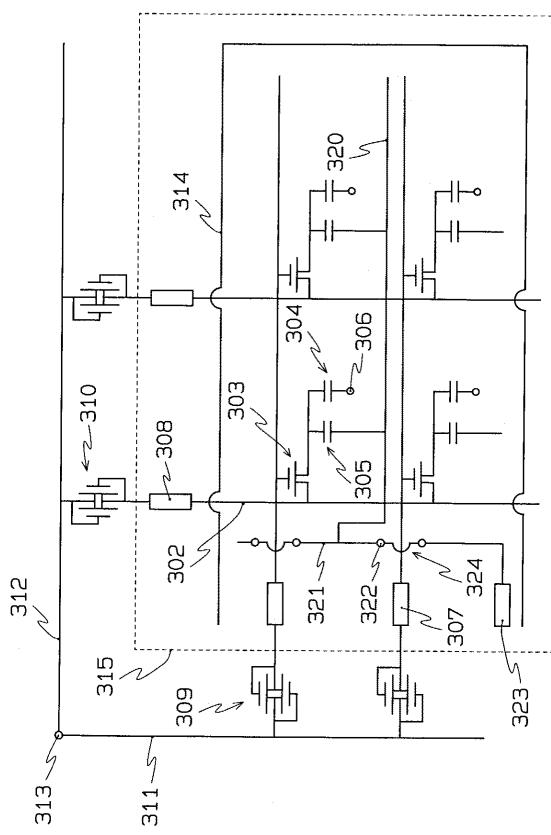

図28に本発明が適用されるアクティブマトリクス型液晶表示装置(AMLCD)のTFTアレイ基板の回路図の一例を示す。図28に示す回路構成は、保持容量Csを画素電極とゲート配線で形成するCs on gate型と呼ばれるものである。ここで、101は走査電圧を供給するためのゲート配線、102は信号電圧を供給するためのソース配線、103は液晶に電圧を印加する際のスイッチング素子として用いる薄膜トランジスタ(TFT)、104は光の透過/非透過のスイッチングを行なう液晶を等価回路的に容量で示したもの、105は液晶104に並列に配置されTFTの寄生容量の影響を低減するための保持容量Cs、106は液晶104の片側の電極をコモン電圧に接続するコモン電極、107はゲート側外部回路をゲート配線101にTCPなどを用いて接続するためのゲート端子、108はソース側外部回路とソース配線102をTCPなどを用いて接続するためのソース端子、109、110はそれぞれTFTや高低坑の線形あるいは非線形素子で形成され、ゲート端子107とソース端子108を信号印加時には電気的に分離し、高電圧の静電気が入った場合には電気的に結合するための高抵抗素子。111はゲート配線101に高抵抗素子109を介して接続されている配線A、112はソース配線102に高抵抗素子110を介して接続されている配線B、113は静電気対策のために配線A(111)と配線B(112)を接続するための接続部である。114はソース配線がオープン故障となっている場合などに用いるリペア配線である。TFTアレイ基板に対向してカラーフィルタが形成された対向基板を組み合わせ、液晶を注入後、一般的には図中の点線で示した領域115の外側を切り離してLCD(液晶ディスプレイ)パネルとする。 30

## 【0052】

また、場合によってはTFTアレイ形成時に点線で示した115の外側の部分の少なくとも一部は形成しなくともよい。

## 【0053】

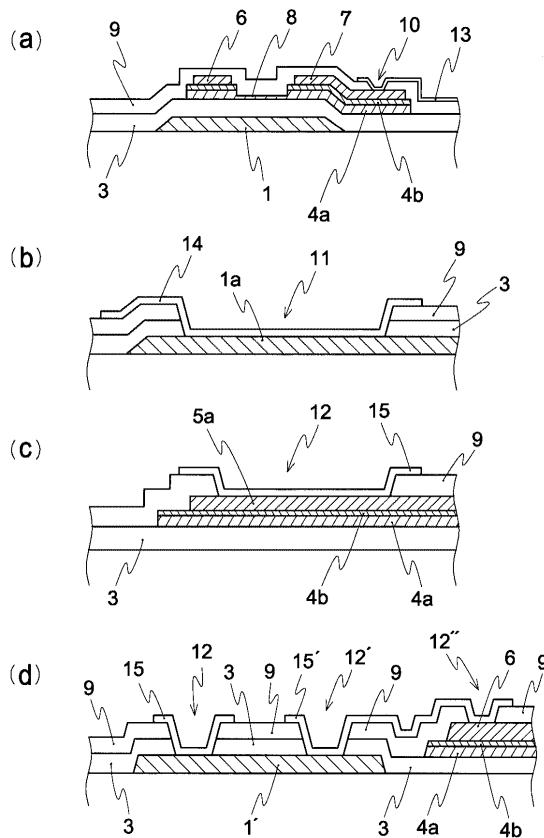

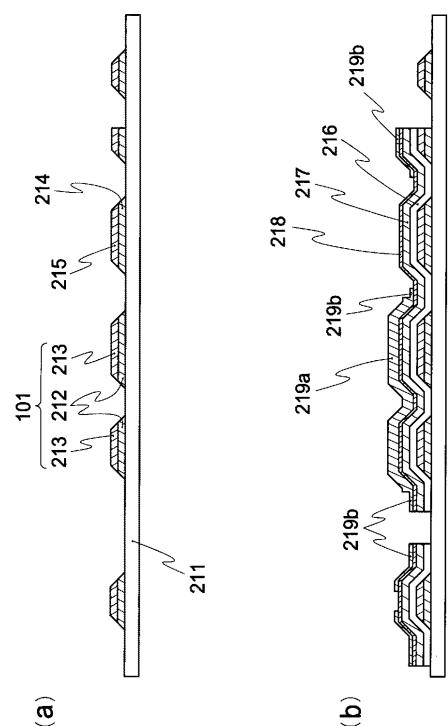

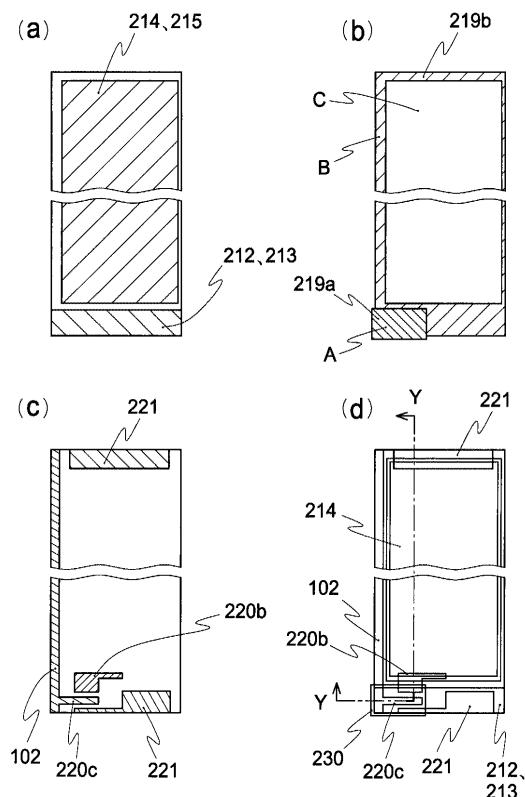

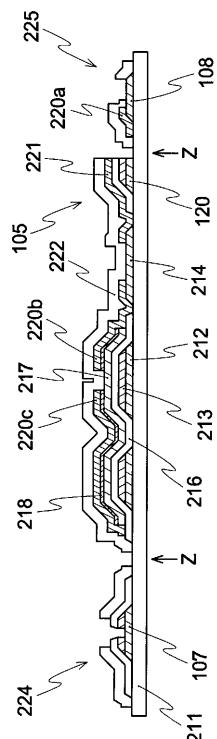

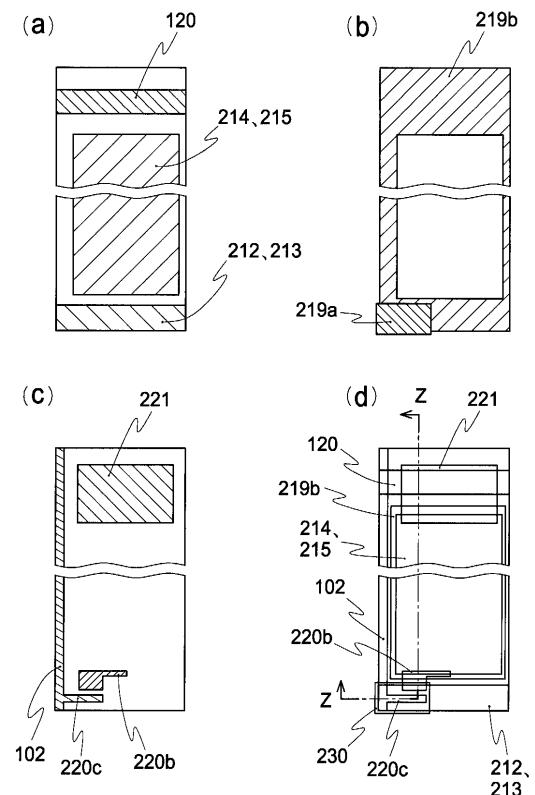

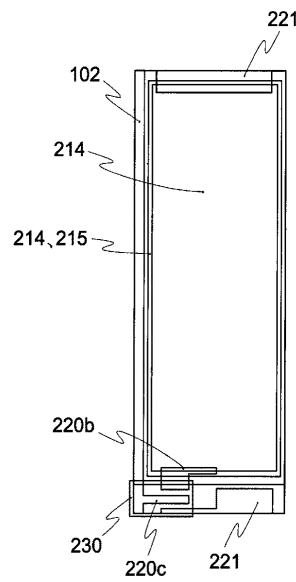

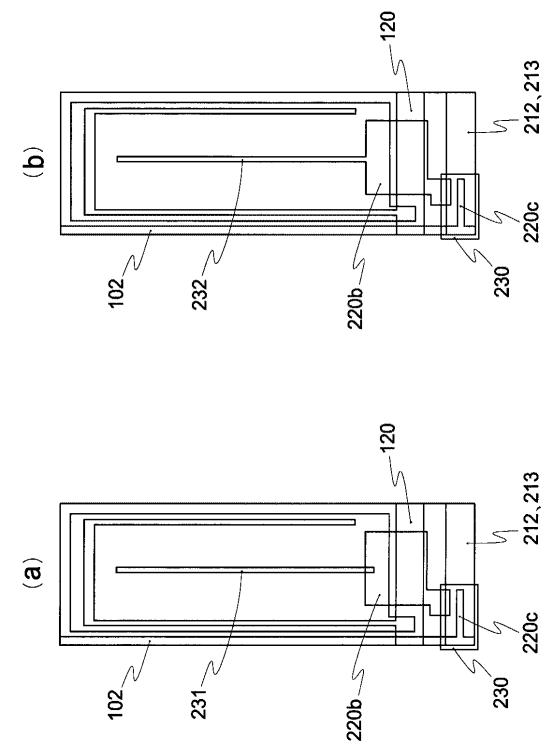

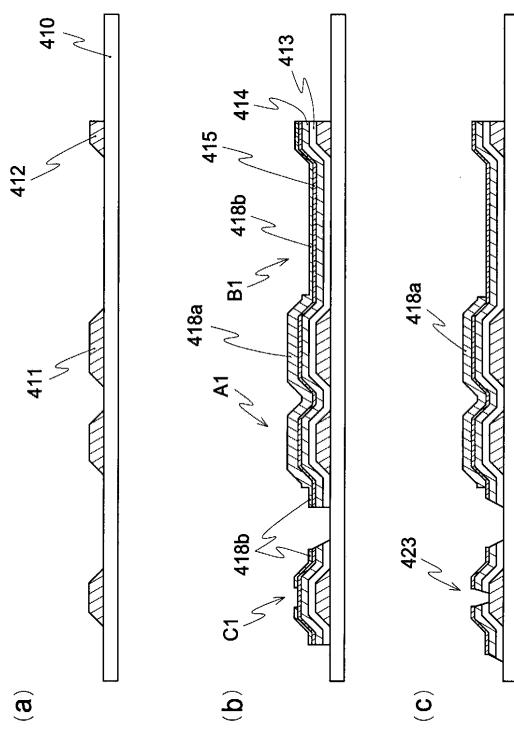

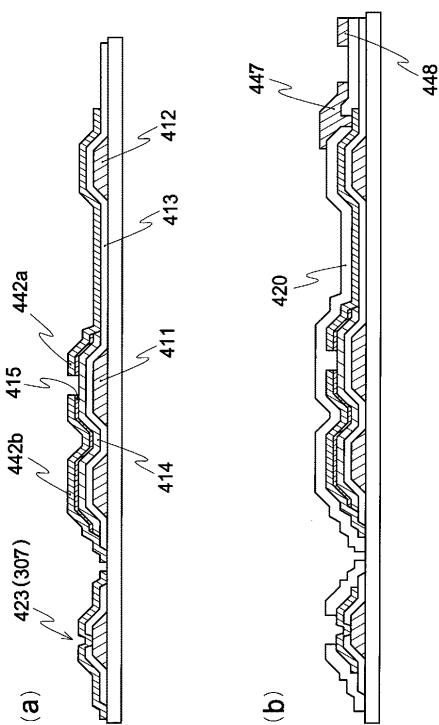

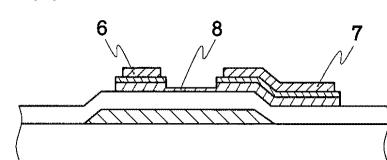

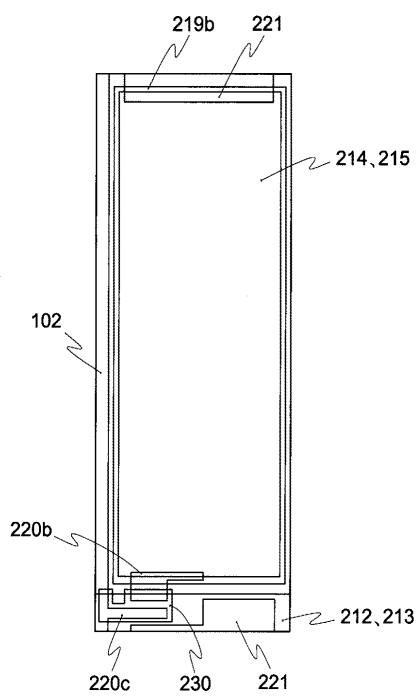

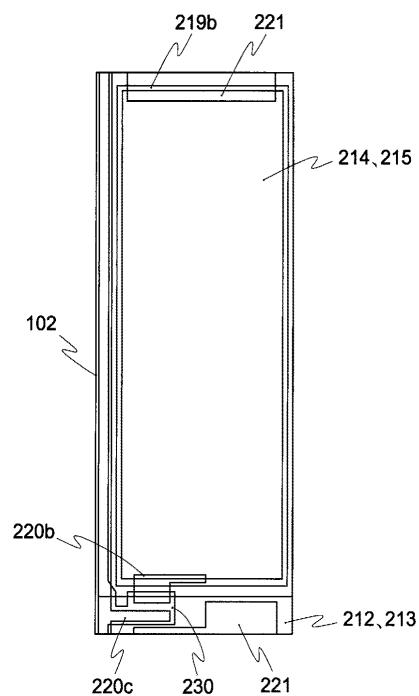

図29、30、31は、本発明の写真製版工程数(マスク数)を削減したTFTアレイ基板の製造工程を示す断面図であり、図28に示すTFTアレイ基板の回路を実現する製造工程を示す。図32は図29、30、31に対応する平面図であり、図29、30、31は図32のY-Y断面およびゲート・ソース端子部の断面構造を示している。

## 【0054】

10

20

30

40

50

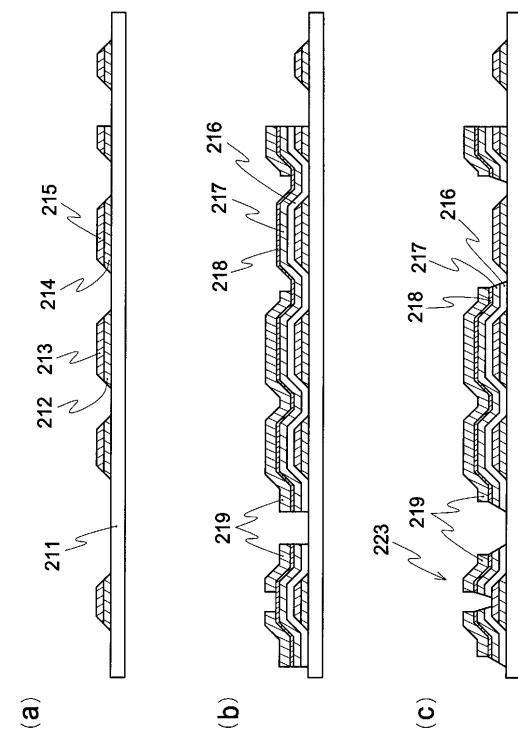

図29、30、31において211は絶縁性基板、212は透明導電体層よりなるゲート電極およびゲート配線、213は金属層からなるゲート電極およびゲート配線であり、212と213でゲート配線101を形成する。214は透明導電体層よりなる画素電極、215は金属層よりなる画素電極、216はゲート絶縁膜、217は半導体層（能動層）、218はPあるいはBなどの不純物を高濃度に含有した半導体層（コンタクト層）、219（219a、b）はホトレジストとして用いることのできる感光性有機樹脂、220（220a、b、c）はソース電極およびドレイン電極となる導電体層、102はソース配線、103は薄膜トランジスタ（TFT）部、221は保持容量電極、222はSi<sub>3</sub>N<sub>4</sub>などの絶縁膜、230は平面図（図32）上の半導体領域である。

【0055】

10

図32において使用している番号で図28～31と同一の番号は、同一の内容を示す。

【0056】

つぎに、本発明の製造方法について説明する。

【0057】

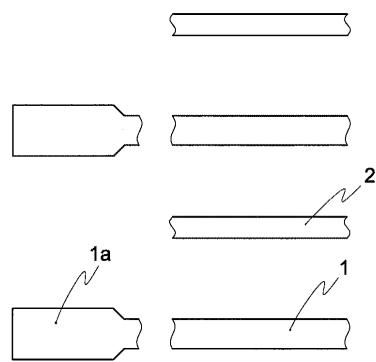

ITO (Indium Tin Oxide)、SnO<sub>2</sub>、InZnOなどの透明導電体層あるいはこれらの積層、あるいは混合層からなる透明導電体層を絶縁性基板211上にスパッタ、蒸着、塗布、CVD、印刷法、ゾルゲル法などの手法で形成する。ついで、その透明導電体層上にCr、Al、Mo、W、Ti、Cu、Ag、Au、Taなど金属やそれらを主成分とする合金あるいはそれらを積層した金属などからなり、前記透明導電体層より抵抗が低い物質の層をスパッタ、蒸着、CVD、印刷法などの手法で形成する。これにより、透明導電体層の上に少なくとも一層の金属からなる低抵抗層が積層された配線構造ができる。ついで、ホトレジストなどを用いて写真製版法およびそれに続くエッチング法などで透明導電体層および金属などの低抵抗層からなるゲート電極およびゲート配線パターン212、213を形成する。このとき同時にゲート配線と同じ材料および構成である透明導電体層と金属などの低抵抗層からなる層構造で画素電極パターン214、215を形成する（図29（a）および図32（a））。

20

【0058】

ITOなどの透明導電体層は、一般的には多結晶も用いる。この場合は、ITOなどのエッチャントとして、たとえば塩化第2鉄あるいはHClおよび硝酸を主成分とするものを用いている。

30

【0059】

しかし、たとえばITO層214を非晶質で形成し、かつその上に成膜する金属層215をそのITOが結晶化する温度以下で成膜すると、ゲート電極などの形成時においてITOは非晶質状態であるため、シュウ酸などの比較的弱酸でエッチングでき、金属層としてAlなどを使用した場合、ITOのエッチング時にAlなどの金属がエッチングされることが少なく、構造形成にあたっては、金属のエッチングが完了するまでITOを非晶質の状態にしておいてもよい。このためAlなど金属の成膜はITOが結晶化しない160以下で行なうのが望ましい。

【0060】

また、ITOのエッチングとしては、HCl、HBr、HIなどのガスを用いてエッチング行なってもよい。

40

【0061】

ついで、プラズマCVDなどの各種CVD法や、スパッタ法、蒸着、塗布法などで形成したゲート絶縁膜となるSi<sub>3</sub>N<sub>4</sub>、SiO<sub>x</sub>N<sub>y</sub>、SiO<sub>2</sub>、Ta<sub>2</sub>O<sub>5</sub>、Al<sub>2</sub>O<sub>5</sub>などあるいはこれらの物質で化学量論組成より幾分ずれたものあるいはそれらの積層物からなる絶縁膜216、たとえばプラズマCVD法やスパッタ法で形成した意図的にドーパントとなる不純物をドーピングしていないあるいは意図的にドーピングしていてもその不純物の濃度が50ppm程度以下またはTFTの実使用電圧条件の暗時のリーク電流が50pAを超えない程度以下にドーパントの濃度が抑えてあるチャンネル用半導体層（能動層）として用いるa-Si:H膜（水素化非晶質シリコン膜）217、金属とのコンタクトを取る

50

ためにプラズマCVDやスパッタ法で形成したリン、アンチモン、ボロンなどの不純物を膜中に原子比でたとえば0.05%以上存在させた高濃度に不純物をドーピングした半導体層（コンタクト層）であるたとえば $n^+a-Si:H$ 膜やマイクロクリスタル $n^+Si$ 膜<sup>218</sup>連続的に形成する。

#### 【0062】

ついで、ホトレジストをまず全面に塗布する。ついでホトマスクを用いた露光によりホトレジストパターンを形成する。このホトレジストパターンの形状は、以下のようにする。まず、図29(b)あるいは図32(b)に示すように少なくとも画素電極となる部分の1部およびコンタクトホール部はホトレジストを形成しない（領域C）。 $a-Si:H$ 膜からなる半導体層を残す部分は厚さAのホトレジストを形成する（領域A<sup>219a</sup>）。たとえば $a-Si:H$ 膜<sup>217</sup>およびたとえば $n^+a-Si:H$ 膜<sup>218</sup>のみをエッチングしゲート絶縁膜<sup>216</sup>を残したい領域には厚さBのホトレジストを形成する（領域B<sup>219b</sup>）。領域A（<sup>219a</sup>）のホトレジストの厚さは領域Bのホトレジスト（<sup>219b</sup>）の厚さより厚くなるように設定する。ゲート配線上で隣り合うソース配線間には、たとえば領域B（<sup>219b</sup>）を形成してその部分の $a-Si:H$ 膜<sup>217</sup>および $n^+a-Si:H$ などの膜<sup>218</sup>を取り除き、電気的に隣り合うソース配線間は絶縁状態にしておくことが望ましい。また、ソース配線の少なくとも一部は領域Aとして下層に半導体層<sup>217</sup>、<sup>218</sup>を残し、ソース配線の断線防止に役立つようにしてもよい。

#### 【0063】

このような、場所によるホトレジストの厚みの違いは以下のように形成する。ポジ型ホトレジストについて説明する。ネガ型にあっても基本的に同等な方法でパターンを形成する。

#### 【0064】

ホトレジストを形成しない部分はマスク上をほぼ透明な状態としておき、充分に光を通過させホトレジストが現像時に残存しないだけの充分な光量を当てる。この結果、ホトレジストが形成されない領域Cが形成される。一方、ホトレジストの厚みAの部分はたとえば、その位置に対応するマスクの部分はほぼ光が透過しないように充分な厚さのCrなどの光を通さない材料で遮光しておく。この結果、この部分のホトレジストには充分の光が露光時にあたらないため、現像時にホトレジストが充分な厚さで残存する領域Aが実現できる。ホトレジストの厚みBを持つ領域Bは、ホトレジストに露光量が領域Aと領域Cの中間の露光量が照射されるようにする。この露光量の調整で、現像時に領域Bの厚みは領域Aより薄く設定される。この結果、図29(b)、図32(b)のホトレジストの形状が実現される。露光量あるいは光量は照射される光強度×時間で示される。

#### 【0065】

ホトレジストの厚みが、領域A > 領域B > 領域C（実質的に0）に設定するために、領域Bのホトレジストへ照射される露光量が領域Aと領域Cの間の露光量が照射されるようするが（露光量は、領域A < 領域B < 領域C）、それにはいくつかの方法が存在する。たとえば、領域Bを形成するマスク上のパターンの透過率を、領域Aを形成する際に用いたマスク上の領域Aの部分の透過率よりも高くし、領域Cを形成する部分の透過率よりも低くする。このためにはたとえば、領域Bを形成する部分のホトレジストの遮光膜として用いるCrなどの遮光材料の厚みを領域Aを形成する部分のそれの厚みより薄くし、光量を制御してもよい。あるいは領域Bの部分に絶縁膜を1層あるいは多層に形成し透過率、反射率、あるいは位相などを変え、実質的に領域Bの透過率を領域Cの透過率より低くしてもよい。

#### 【0066】

また、露光量が領域A（実質的に0）<領域B<領域Cとなるように設定するためには、以下の方法もある。領域Aと領域Bに対してともに同等程度の低い透過率を持つ遮光部分でマスク上にパターンを形成し、領域C用には充分な透過率を持つたとえば一切の遮光パターンを形成しないパターンをマスク上に形成する。ついで、この領域A+領域Bの遮光パターンをもつマスクを用いて露光量1で露光のみを行ない領域Cに光を照射する。つ

10

20

30

40

50

いで、領域 A に対応する部分のみを遮光したパターンを持つマスクを用いて露光を露光量 2 で行ない、領域 A を形成する部分以外を露光量 2 で光を照射する。このとき露光量 1 は現像時に領域 C のホトレジストが充分に除去できる強度で露光を行ない、露光量 2 は現像時に領域 B に必要な厚みのホトレジストが残るように設定する。一般的にはポジ型のホトレジストを用いた場合には露光量 1 は露光量 2 よりも、光照射時の光強度 × 光照射時間の計算結果が大きくなる用に設定する。

#### 【0067】

ホトレジストの厚みが、領域 A > 領域 B > 領域 C ( 実質的に 0 ) に設定するための第 3 の方法としては、領域 A を形成するためには低い透過率を持つ遮光層でマスク上にパターンを形成し、領域 C 用には充分な透過率を持つたとえば一切の遮光パターンを形成しないパターンをマスク上に形成する。

#### 【0068】

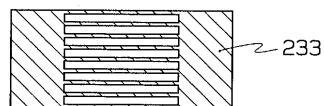

領域 B 用として、たとえば図 33 に示すようないわゆるハーフトーンマスクを用いてもよい。ハーフトーンマスクは、パターン 233 のようにマスク上の遮光パターンの空間周波数を露光機のパターン分解能力 ( たとえば 1 / 6  $\mu\text{m}$  ) より高くし、ホトレジスト上でマスクのパターンが解像できない状態とし、領域 C よりも露光強度が少なくなるようにする。ハーフトーンマスクの微細度は、遮光部と透光部の幅が合計 6  $\mu\text{m}$  以下となる周期でくり返されるように形成する。

#### 【0069】

この結果ホトレジストの厚みが領域 A > 領域 B > 領域 C ( 実質的に 0 ) に設定でき、その結果、図 29 ( b ) 、図 32 ( b ) のホトレジスト形状が実現される。

#### 【0070】

ついで、 $n^+ a - Si : H$  膜、 $a - Si : H$  膜といった半導体膜と、 $Si_3N_4$  などのゲート絶縁膜をエッチングする。このエッチングはたとえば HCl を主成分とするガスや  $CF_4$  を主成分とするガスや  $CF_4$  と  $O_2$  の混合ガス、  $SF_6$  を主成分とするガスなどが行なう。この結果、少なくとも画素電極となる部分で光を透過させようとする部分上のこれらの膜は取り除く。また、ゲート配線と外部から信号を入力するため T C P などと接続する端子部分 224 、たとえば、静電気防止のため直接ソース配線あるいは TFT あるいは抵抗を介してソース配線部と短絡する部分 ( 図 28 、 113 など ) においては、この工程で  $n^+ a - Si : H$  膜、  $a - Si : H$  膜、  $Si_3N_4$  などのゲート絶縁膜の一部を除去してもよい ( 図 30 ( a ) ) 。

#### 【0071】

前記  $n^+ a - Si : H$  膜、  $a - Si : H$  膜、  $Si_3N_4$  などのゲート絶縁膜のエッチングは  $CF_4$  や  $CH_4 + O_2$  などの単一ガスで全膜をエッチングしてもよいが、たとえば  $a - Si$  TFT 膜エッチング時に  $SiN$  膜のエッチングを抑えられるようなガスを用いるなど、少なくとも  $a - Si : H$  膜と  $Si_3N_4$  膜を別々のエッチングガスでドライエッチングしてもよい。この場合  $a - Si : H$  のエッチングとして  $SF_6$  、 HCl 、 F123 あるいはこれらの混合ガスあるいはこれらと不活性ガスあるいは  $O_2$  との混合ガスを用い、  $Si_3N_4$  膜のエッチングとして  $CF_4$  、  $SF_6$  あるいはこれらの混合ガスあるいはこれらと  $O_2$  や不活性ガスとの混合ガスを用いてもよい。

#### 【0072】

ついで、酸素プラズマなどのレジストの膜厚を低減できるプラズマを用い、アッティングを行なってレジストを削り、領域 B ( 219b ) からレジストを取り除く。このとき領域 A ( 219a ) のレジストの膜厚は初期の膜厚より薄くなるが、以下のエッチング時にエッチングしない部分を充分保護できるような厚みを保つように制御する。ついで、少なくとも  $n^+ a - Si : H$  膜、  $a - Si : H$  膜をドライエッチング法などでエッチングし領域 B より取り除く ( 図 30 ( b ) ) 。

#### 【0073】

このレジストの膜厚を低減させる工程は独立に行なわず、  $n^+ a - Si : H$  膜、  $a - Si : H$  膜、  $Si_3N_4$  などのゲート絶縁膜のエッチング行なうなど、ホトレジスト自身も幾

10

20

30

40

50

分削れる現象を利用し、同時に領域Bのホトレジストを削ってもよい。

【0074】

その後、図30(b)で画素電極上で $n^+a-Si:H$ 膜、 $a-Si:H$ 膜、および $Si_3N_4$ などのゲート絶縁膜のエッチングで取り除いた部分の画素電極214上の金属層215をウエットエッチングやドライエッチングで取り除く(図31(a))。ついで、ホトレジストを取り除く。

【0075】

ついで、たとえばCr、Al、Ti、Ta、W、Mo、Mo-W、Cuあるいはこれらを主成分とする合金あるいはそれらの多層積層物などからなるソース電極およびソース配線、ドレイン電極となる導電体層220(220a、b、c)を成膜する。ついで写真製版法でソース電極およびソース配線、ドレイン電極の形状に配線パターンを形成後ウエット、ドライなどでエッチングし、ついで、ソース電極220cとドレイン電極220b間の $a-Si:H$ 膜などで形成した $n^+$ 半導体層218をドライエッチングなどで取り除き、最後にレジストを剥離することで所定のパターンを形成する(図31(b)、図32(c))。このとき、保持容量Csを形成するため、ソース配線と同時に作製する保持容量電極221を少なくともゲート絶縁膜216を介してたとえば212、213よりなる次段あるいは前段のゲート配線と対向させる。このとき、保持容量電極221とゲート絶縁膜216の間にはゲート絶縁膜216のみでなく $n^+a-Si:H$ 膜、 $a-Si:H$ 膜を残してもよい。保持容量電極は、図に示すように画素電極の少なくとも一部に接続させることが必要である。

10

20

【0076】

ついで、 $Si_3N_4$ 、 $SiO_2$ あるいはこれらの混合物および積層物からなる絶縁膜で形成した保護膜222を成膜する。写真製版で少なくとも信号を入れるために外部のTCPなどに接続するゲート端子部223、ソース端子部225にコンタクトホールが形成できるようにパターンを形成し、ついでCF<sub>4</sub>系などのガスを用いたドライエッチングやウエットエッチング法でコンタクトホールをあける。エッチング完了後ホトレジストを除去する。これにより、TFTアレイが形成される(図31(c)、図32(d))。

30

【0077】

ついで、TFTアレイ上に配向膜を形成し、少なくとも表面に配向膜とコモン電極を形成した対向基板と向かい合わせその間に液晶を注入し、アクティブマトリクス型液晶ディスプレイを形成する。

【0078】

以上のプロセスによって図28に示した構成図を持つTFTアレイおよびそれを用いた液晶ディスプレイが形成される。

【0079】

図28においてたとえばゲート配線材料を用いて形成したソース配線用のリペア配線114が図示されているが、これは状況によっては形成しなくともよい。

【0080】

また、図34に示すように、リペア配線114との交差部において、ソース配線102をコントクトホール116a、116bを利用してゲート配線材料で形成したゲート配線と同層の配線117に一旦変換してもよい。この時リペア配線114はソース配線材料を用いて形成する。

40

【0081】

図31では、図31(a)でゲート電極材料で形成した画素電極214上の金属層215を除き、図31(b)でソース・ドレイン電極220b、c、ソース配線102をエッチングパターニングしているが、両者が同じ材料の場合は図31(a)で示したゲート電極材料215のエッチングを省略し、図31(b)でソース配線220をエッチングするときに同時にゲート電極材料で形成した画素電極215をエッチングで除いてもよい。

【0082】

半導体領域230の形状は図32(d)ではゲート配線213の両側にはみ出している

50

が、図68のように片側または両側がゲート配線の内側に入っていてもよい。図32(d)において半導体領域230の上側の外縁はゲート電極213の外側にはみ出していてゲートオフバイアスがかからないため、光の照射によってリーク電流を発生する可能性がある。これを避けるためには、図68のように半導体領域230の上側の外縁に切欠きを設け、半導体領域230の外縁をゲート電極213の外縁と交差させることがとくに有効である。

#### 【0083】

また、図68のように半導体領域230の少なくともソース電極側、できればソース、ドレイン電極の両側ともゲート配線の内側に入れ、ソース電極部の半導体層がゲート配線(ゲート電極)の上のみに存在するようにすると、ゲート電極がその下部から照射される光をさえぎり、ソース電極部の半導体層への光の照射を防ぐことができるので、光によるリーク電流を防ぐことができる。

#### 【0084】

また、半導体領域230を図69のように延長し、薄膜トランジスタ部からソース配線102の下部に連続的に形成してもよい。このようにすれば、ソース配線102が半導体層23の端部の段差部で生じやすい断線を防ぐことができる。このような半導体領域230の形状の変更は、以下の実施の形態においても同様に有効である。図1に示される実施の形態1も同様な配置となっている。

#### 【0085】

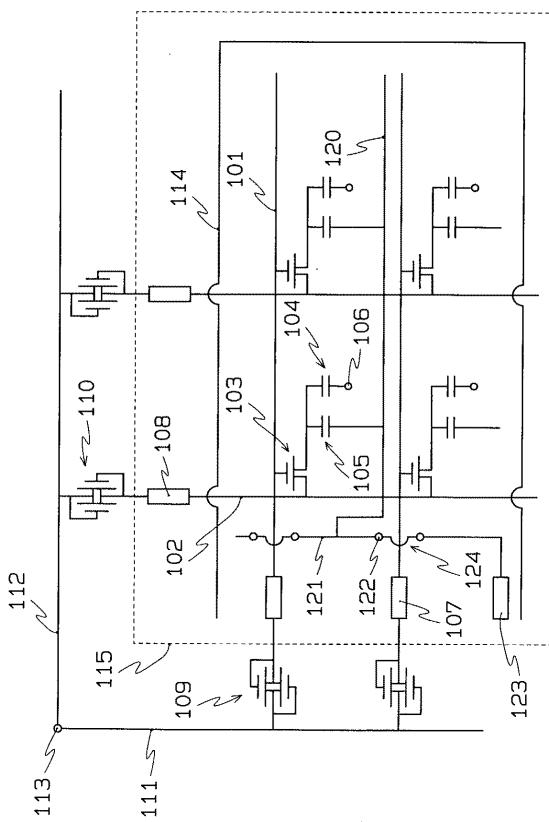

##### 実施の形態5

10

前記実施の形態では保持容量105が次段あるいは前段のゲート配線との間で形成されたいわゆるC<sub>s</sub> on gate構造に関して説明したが、図35の回路図に示すような、1ゲート遅延に有利な保持容量配線をゲート配線と別に形成した共通配線構造としてもよい。ここで、保持容量105は共通配線120に接続されている。また、共通配線120はコントクトホール122を介して、共通配線引き出し線121に接続されている。コモン電圧は共通配線引き出し線121に接続されている共通配線端子123を介して外部から電圧を印加する。その他の部分の機能と符号は図28と同じである。

#### 【0086】

共通配線方式においては、たとえば図36に示すような断面構造と図37に示す平面配置をとる。また、図38に示すように画素の中に共通配線120を形成し、画素電極を2分化し、その間をソース配線と同時に形成する保持容量電極221でブリッジし、そこに保持容量105を形成してもよい。

20

#### 【0087】

図37に示すように共通配線構造をとる場合はゲート配線と平行に引き出される共通配線120とそれをまとめゲート配線と垂直に走る共通配線引き出し線121が必要となる。共通配線はゲート配線101と同じ材料で同時に形成することが最もよく、共通配線引き出し線は少なくともそのゲート配線との交差部124はゲート配線とは異層のソース配線102の材料を用いる。場合によってはゲート配線との交差部以外は、ゲート配線材料で共通配線引き出し線を形成してもよい。

#### 【0088】

また、図39に示すように、リペア配線114との交差部において、ソース配線102をコントクトホール116a、116bを利用してゲート配線材料で形成したゲート配線と同層の配線117に一旦変換してもよい。

30

#### 【0089】

##### 実施の形態6

前記実施の形態ではTFTアレイ全面を覆うように絶縁膜222が形成されているが、この絶縁膜を形成しなくともよい。この絶縁膜形成を省くとマスク数は3枚となる。この場合、液晶シールの外部でソース配線の腐蝕が問題となるが、シールの外部へ出る以前にシールの内側でコンタクトホールを用いてゲート配線材料に変換しておく。これにより、ソース配線の腐蝕を防ぐことができる。

40

50

## 【0090】

## 実施の形態7

図29(b)の工程において、領域Bのレジストパターン219bを画素電極のパターン(214、215)とオーバーラップさせて配置してもよい。このようにすると、図40に示すように画素電極(透明導電体層)214の外周には金属層215が残されて、214・215の2層からなる遮光パターンが形成される。

## 【0091】

## 実施の形態8

前記実施の形態では、液晶自身に電圧を印加するコモン電極が対向基板にある場合に関する説明したが、広視野を実現できるIPS(In-plane switching)モードなどの横方向電界印加TFT基板に液晶電圧を印加するすべての電極がある場合に關しても適用できる。この場合は、たとえば画素電極214は透明導電体層である必要はなく、Crなどの金属でもよい。IPSモードの平面図の例を図41(a)、(b)に示す。ここで、図32、図37と同じものには同じ番号を用いている。

10

## 【0092】

図41(a)において、画素電極231は図29(a)の画素電極214/215形成時に作成する。

## 【0093】

図41(b)において、画素電極232は図31(b)のドレイン電極形成時に作成する。この場合、図29(a)での画素電極形成は行なわない。

20

## 【0094】

図41(a)、(b)において、ゲート電極および配線は金属層213のみでもよい。また、画素電極214/215も金属層215のみでよい。

## 【0095】

## 実施の形態9

前記実施の形態では、a-Si:H膜の島状化のため図29(a)、(b)、図30(a)で示したようにハーフトーンマスクなどの技術を用いレジストの厚みを平面上で部分的に変換していたが、この工程をやめ、a-Si:H膜の島状化の写真製版を別に行なってもよい。この場合は、たとえば、レジストの厚みは空間的には変化させない。図29(b)の状態で平面的にレジストの厚みを変化させず、画素電極214、215上とコンタクト部223上のSiN216/a-SiH217/n+a-Si:H218を抜く工程を実施後、レジストを除去し、再度トランジスタの島を形成するパターンを作成し、TFT部以外のa-Si:H膜217とn+a-Si:H膜218をエッティングで取り除き、図30(a)の構造を作成する。この場合、図29~31に示した実施の形態よりは写真製版回数が増えるが、従来の技術よりは低減できる。

30

## 【0096】

## 実施の形態10

実施の形態4においてはSiNなどからなるゲート絶縁膜216、a-Si:H層218およびゲート配線材料からなる画素電極214上の金属層215をエッティングした後に、ソース・ドレイン電極および配線220を形成していた。それに対して、ホトレジストの厚みを空間的に変化させる工程を用いず、図42(a)、42(b)、42(c)、図43(a)、43(b)に示すように、少なくとも画素部の光を透過させる部分のゲート絶縁膜216、a-SiH層217、n+a-Si:H層218をエッティングで取り除いた後にソース・ドレイン電極220を形成してもよい。この場合、チャネルとして用いるSi膜217の島状化は一般的にはできない。

40

## 【0097】

ITO(Indium Tin Oxide)、SnO<sub>2</sub>、InZnOなどの透明導電体層あるいはこれらの積層、あるいは混合層からなる透明導電体層212、214を絶縁性基板211上にスパッタ、蒸着、塗布、CVD、印刷法、ゾルゲル法などの手法で形成する。ついで、その透明導電体層上にCr、Al、Mo、W、Ti、Cu、Ag、Au、Taなど金属やそ

50

これらを主成分とする合金あるいはそれらの積層した金属などからなり前記透明導電体層より抵抗が低い物質の層 213、215をスパッタ、蒸着、CVD、印刷法などの手法で形成する。これにより、透明導電体層の上に少なくとも一層の金属からなる低抵抗層が積層された配線構造ができる。ついで、ホトレジストなどを用いて写真製版法およびそれに続くエッティング法などで透明導電体層および金属などの低抵抗層からなるゲート電極およびゲート配線パターン 212、213を形成する。このとき同時にゲート配線と同じ材料および構成である透明導電体層と金属などの低抵抗層からなる層構造で画素電極パターン 214、215を形成する(図 42(a))。

#### 【0098】

ついで、プラズマCVDなどの各種CVD法や、スパッタ法、蒸着、塗布法などで形成したゲート絶縁膜とする $\text{Si}_3\text{N}_4$ 、 $\text{SiO}_x\text{N}_y$ 、 $\text{SiO}_2$ 、 $\text{Ta}_2\text{O}_5\text{Al}_2\text{O}_5$ などあるいはこれらの物質で化学量論組成より幾分ずれたものあるいはそれらの積層物からなる絶縁膜 216、プラズマCVD法やスパッタ法で形成した意図的にドーパントとなる不純物をドーピングしていないあるいは意図的にドーピングしていてもその不純物の濃度が50 ppm程度下またはTFTの実使用電圧条件の暗時のリーク電流が50 pAを超えない程度以下にドーパントの濃度が抑えてあるチャンネル用半導体層として用いるa-Si:H膜(水素化非晶質シリコン膜) 217、金属とのコンタクトを取るためにプラズマCVDやスパッタ法で形成したリン、アンチモン、ボロンなどの不純物を膜中に原子比でたとえば0.05%以上存在させた高濃度に不純物をドーピングした半導体層であるたとえばn+a-Si:H膜やマイクロクリスタルn+Si層 218を連続的に形成する。

#### 【0099】

ついで、少なくとも光を透過する画素部からSiNなどからなるゲート絶縁膜 216、a-Si:H層 217、n+a-Si:H層 218を取り除くようにホトレジストを形成後、エッティングする(図 42(b)、42(c))。ここで、ホトレジスト 219を除去する。

#### 【0100】

ついで、たとえばCr、Al、Ti、Ta、W、Mo、Mo-W、Cuあるいはこれらを主成分とする合金あるいはそれらの多層積層物などからなるソース電極およびソース配線、ドレイン電極となる導電体層 220(220a、b、c)を成膜する。ついで写真製版法でソース電極およびソース配線、ドレイン電極の形状に配線パターンを形成後ウエット、ドライなどでエッティングし、ついで、ソース電極 220cとドレイン電極 220b間のn+a-Si:H膜などで形成したn+半導体層 218をドライエッティングなどで取り除き、最後にレジストを剥離することで所定のパターンを形成する(図 43(a))。

#### 【0101】

ついで、 $\text{Si}_3\text{N}_4$ 、 $\text{SiO}_2$ などあるいはそれらの混合物および積層物からなる絶縁膜で形成した保護膜を成膜する。写真製版で少なくとも、信号を入れるために外部のTCPなどに接続するゲート端子部 223、ソース端子部 225にコンタクトホールが形成できるようにパターンを形成し、ついでCF<sub>4</sub>系などのガスを用いたドライエッティングやウエットエッティング法でエッティングする。エッティング完了後ホトレジストを除去する。これにより、TFTアレイが形成される。(図 43(b))この方法によれば、a-Si:H膜 217などはTFT部以外にも残るが、写真製版回数(マスク数)は4回(4枚)で完了できる。

#### 【0102】

##### 実施の形態 1 1

前記実施の形態によれば半導体層はa-Si:H膜で形成されていたが、poly-Si(多結晶シリコン)であってもよい。

#### 【0103】

##### 実施の形態 1 2

図 28 に本発明に用いるアクティブマトリクス液晶ディスプレイ(AMLCD)のTFTアレイ基板の回路図の他の例を示す。図 28 に示す回路構成は、保持容量を画素電極と

10

20

30

40

50

ゲート配線で構成するいわゆる C S o n g a t e 型と呼ばれるものである。ここで、101は走査電圧を供給するためのゲート配線、102はソース配線、103は液晶に電圧を印加する際のスイッチング素子として用いる薄膜トランジスタ(TFT)、104は光の透過非透過のスイッチングを行なう液晶を等価回路的に容量で示したもの、105は液晶104に並列に配置されTFTの寄生容量の影響を低減するための保持容量、106は液晶105の片側の電極をコモン電圧に接続する接続部、107はゲート側外部回路をゲート配線101にTCPなどを用いて接続するためのゲート端子、108はソース側外部回路とソース配線102をTCPなどを用いて接続するためのソース端子、109、110はそれぞれTFTや高抵抗の線形あるいは非線形素子で形成され、ゲート端子107とソース端子108を信号印加時には電気的に分離し、静電気などの高電圧が印加された場合には電気的に結合するための高抵抗素子。111はゲート配線101に高抵抗素子109を介して接続されている配線A、112はソース配線102に高抵抗素子110を介して接続されている配線B、113は静電気対策のために配線A(111)と配線B(112)を接続するための接続部である。この部分は抵抗素子やTFTなどの非線形素子を介して接続してもよい。114はソース配線がオープンとなっている場合などに用いるリペア配線である。TFTアレイはカラーフィルターが形成された対向基板と組み合わせて液晶を注入後、一般的には図中の点線で示した領域115の外側を切り離してLCD(液晶ディスプレイ)とする。

#### 【0104】

また、場合によってはTFTアレイ形成時に点線で示した115の外側の部分の少なくとも一部は形成しなくともよい。

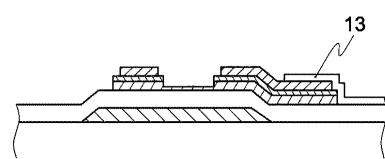

#### 【0105】

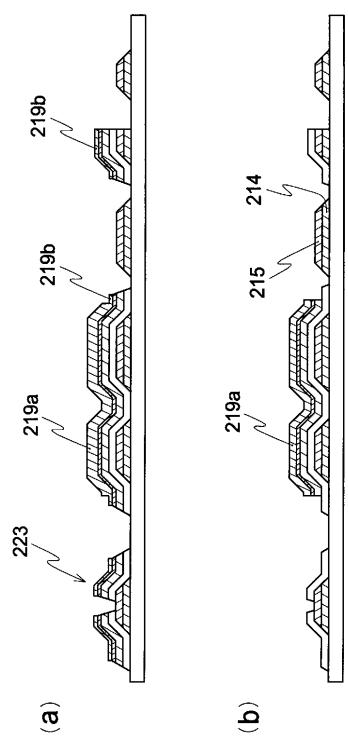

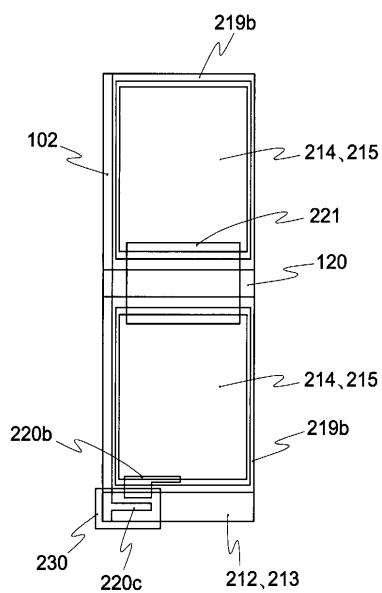

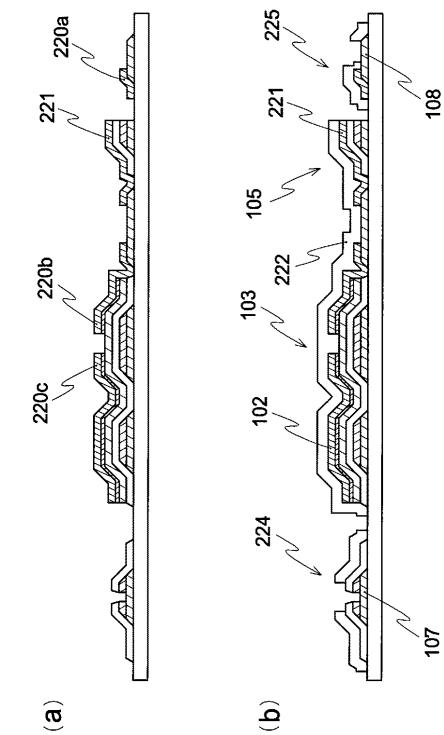

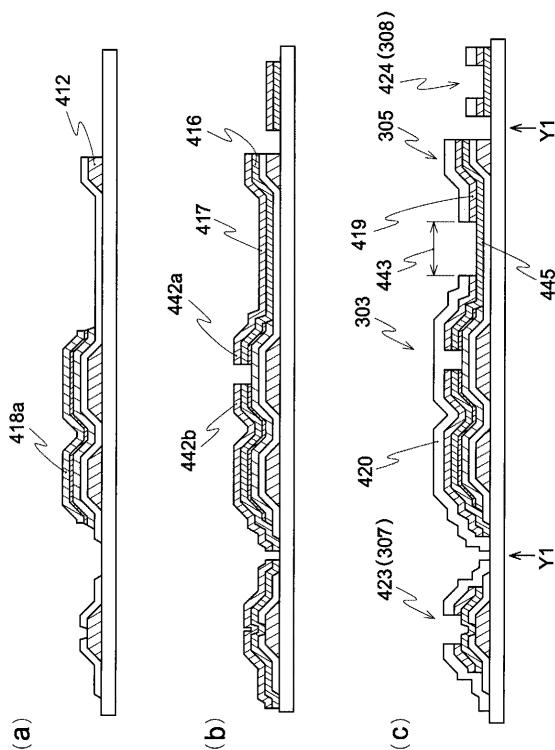

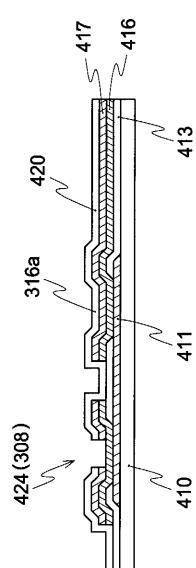

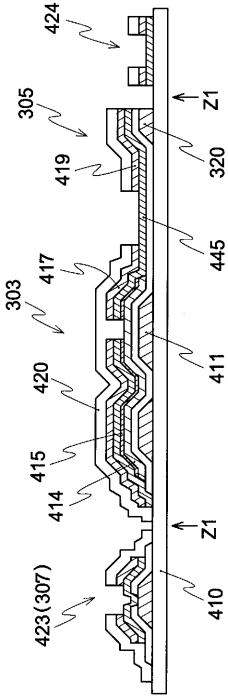

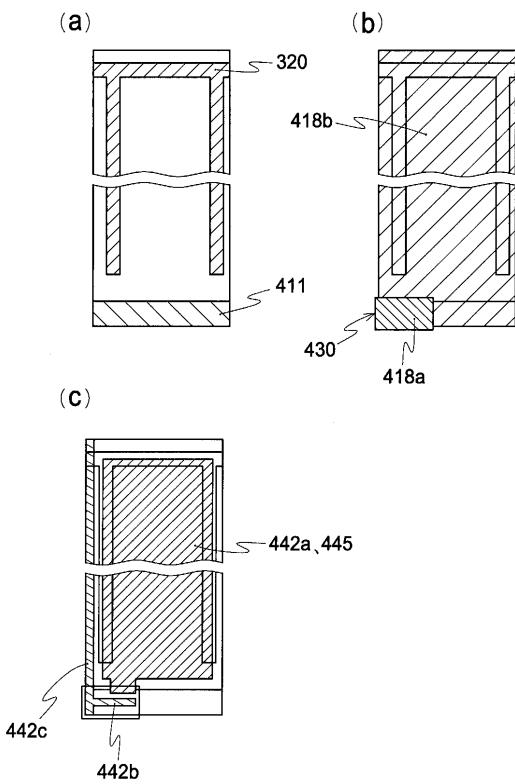

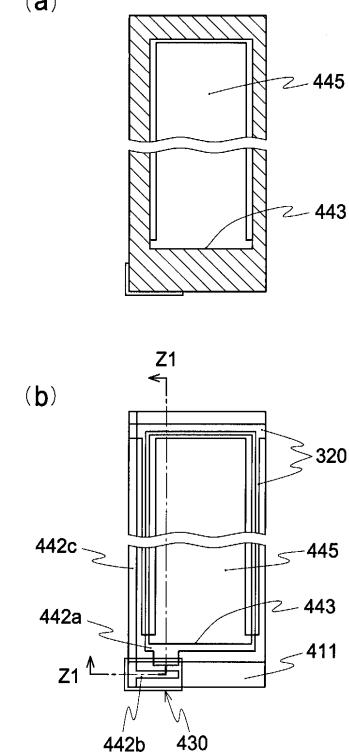

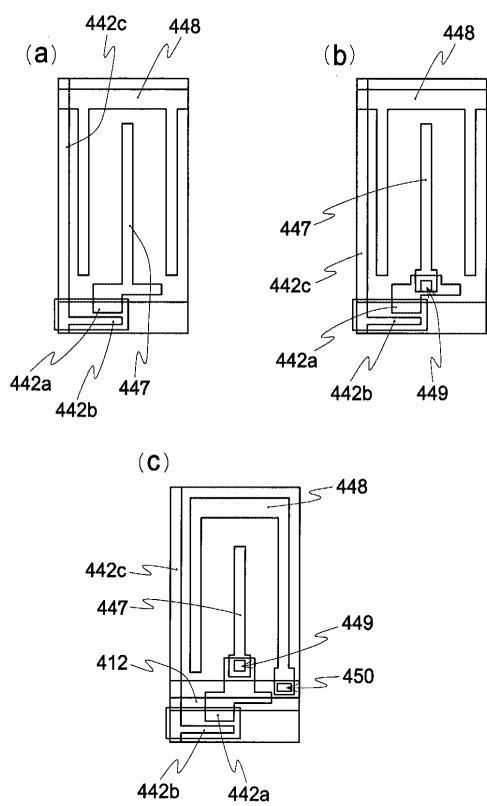

図44(a)、44(b)、44(c)、図45(a)、45(b)、45(c)は、本発明の写真製版工程数を削減したTFTアレイ基板の製造工程を示す断面図であり、図1に示したTFTアレイ基板の回路を実現する構造の一例を示す。図44(a)、44(b)、44(c)、図45(a)、45(b)、45(c)は図46(a)、46(b)、46(c)、図47(a)、47(b)のY1-Y1断面の部分およびゲート・ソース端子部の断面構造を示している。

#### 【0106】

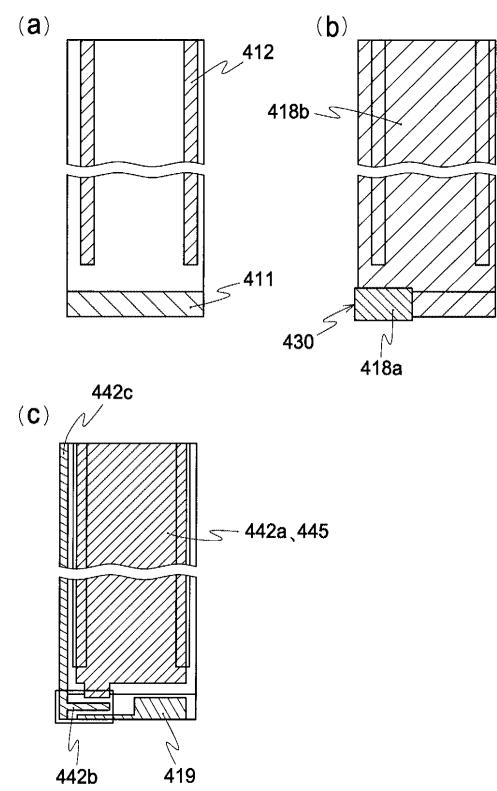

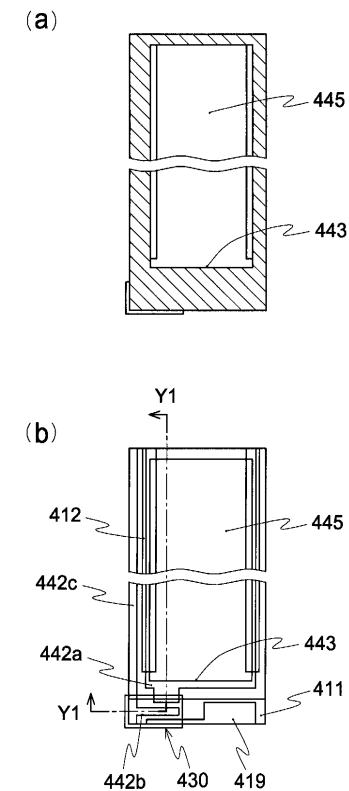

図44(a)、44(b)、44(c)、図45(a)、45(b)、45(c)において410は絶縁性基板、411は金属層からなるゲート電極あるいはゲート配線、412は前段あるいは次段の隣接するゲート配線/電極である。413はゲート絶縁膜、414は半導体層(能動層)、415はPあるいはBなどの不純物を高濃度に含有した半導体層からなるオーミックコンタクト層、416はソース/ドレイン電極および画素電極として用いる透明導電体層、417は金属層からなるソース/ドレイン電極でソース配線102も形成する。418はホトレジストとして用いることのできる感光性有機樹脂、419は保持容量電極、420はSi<sub>3</sub>N<sub>4</sub>などの保護膜として用いる保護絶縁膜である。

#### 【0107】

図46(a)、46(b)、46(c)、図47(a)、47(b)において使用している符号のうち図28、図44(a)、44(b)、44(c)、図45(a)、45(b)、45(c)と同一の番号は同一の部分を示す。また、442aはドレイン電極、442bはソース電極、430は半導体領域、445は画素電極、443は画素電極上で保護絶縁膜420および金属層417が取り除かれた光を透過させる領域である。

#### 【0108】

つぎに、本発明の製法について説明する。

#### 【0109】

絶縁性基板410上にCr、Al、Mo、W、Ti、Cu、Ag、Taなど金属やそれらを主成分とする合金あるいはそれらの積層した金属などからなる物質をスパッタ、蒸着、CVD、印刷法などの手法で形成する。ついで、ホトレジストなどを用いて写真製版法およびそれに続くエッティング法などで金属などの低抵抗層からなるゲート電極およびゲー

ト配線パターン 411 および次段あるいは前段の隣接するゲート配線 412 を形成する(図 44 (a) および図 46 (a) )。

【0110】

ついで、プラズマ CVD などの各種 CVD 法や、スパッタ法、蒸着、塗布法などで形成したゲート絶縁膜となる  $Si_3N_4$ 、 $SiO_xN_y$ 、 $SiO_2$ 、 $Ta_2O_5$ 、 $Al_2O_5$  などあるいはこれらの物質で化学量論組成より幾分ずれたものあるいはそれらの積層物からなるゲート絶縁膜 413、プラズマ CVD 法やスパッタ法で形成した意図的にドーパントとなる不純物をドーピングしていないあるいは意図的にドーピングしていてもその不純物の濃度が 50 ppm 程度以下または TFT の実使用電圧条件の暗時のリーク電流が 50 pA を超えない程度以下にドーパントの濃度が抑えてあるチャンネル用半導体層として用いる a-Si : H 膜(水素化非晶質シリコン膜)からなる半導体層 414、金属とのコンタクトを取るためにプラズマ CVD やスパッタ法で形成したリン、アンチモン、ボロンなどの不純物を膜中に原子比でたとえば 0.05% 以上存在させた高濃度に不純物をドーピングした半導体層であるたとえば  $n^+a-Si : H$  膜やマクロクリスタル  $n^+Si$  層からなるオームックコンタクト層 415 を連続的に形成する。

10

【0111】

ついで、ホトレジストをまず全面に塗布する。ついでホトマスクを用いた露光によりホトレジストパターンを形成する。このホトレジストパターンの形状は、以下のようにする。まず、図 44 (b) あるいは図 46 (b) に示すように少なくともゲート電極 / 配線 411 のコンタクトを取るためにゲート絶縁膜 413、半導体層 414、オームックコンタクト層 415 にゲート端子部 423 においてコンタクトホールをあけるため、その部分の少なくとも一部はホトレジストを形成しない(領域 C)。a-Si : H 膜からなる半導体層を残す部分は厚さ A のホトレジストを形成する(領域 A (418a、430))。また、a-Si : H 膜 414 および  $n^+a-Si : H$  膜 415 のみをエッチングしゲート絶縁膜 413 を残したい領域には厚さの薄いホトレジストを形成する(領域 B (418b))。領域 A (418a、430) のホトレジストの厚さは領域 B のホトレジストの厚さ (418b) より厚くなるように設定する。ゲート配線上で隣り合うソース配線間には領域 B (418b) を形成してその部分の a-Si : H 膜 414 および  $n^+a-Si : H$  などの膜 415 を取り除き、隣り合うソース配線間は電気的に絶縁状態にしておくことが望ましい。

20

【0112】

このようなホトレジストの厚みの違いは以下のように形成する。ポジ型ホトレジストを用いる場合について説明する。ネガ型にあっても基本的に同等な方法でパターンを形成できる。

30

【0113】

ホトレジストを形成しない部分はマスク上をほぼ透明な状態としておき充分に光を透過させホトレジストが現像時に残存しないだけの充分な光量を当てる。この結果、ホトレジストが形成されない領域 C が形成される。一方、ホトレジスト厚み A の部分はたとえば、その位置に対応するマスクの部分をほぼ光が透過しないように充分な厚さの Cr などの光を通さない材料で遮光しておく。この結果、この部分のホトレジストには充分の光が露光時にあたらないため、現像時にホトレジストが充分な厚さで残存する領域 A が実現できる。中間のホトレジストの厚みをもつ領域 B は、ホトレジストに露光量が領域 A と領域 C の間の露光量が照射されるようにする。この露光量の調整で、現像時に領域 B の厚みは領域 A より薄く設定される。この結果図 44 (b)、図 46 (b) の形状が実現される。露光量あるいは光量はホトレジストに照射される光強度 × 時間で示される。ホトレジストの厚みが、領域 A > 領域 B > 領域 C (実質的に 0) に設定するために、領域 B のホトレジストへ照射される露光量が領域 A と領域 C の中間の露光量が照射されるようにするが(露光量は、領域 A < 領域 B < 領域 C)、それにはいくつかの方法が存在する。たとえば、領域 B を形成するマスク上のパターンの透過率を、領域 B を形成する際に用いたマスク上の透過率を領域 A の部分の透過率よりも高くし、領域 C を形成する部分の透過率よりも低くする

40

50

。このためにはたとえば、領域 B を形成する部分のホトレジストの遮光膜として用いる Cr などの遮光材料の厚みを領域 A を形成する部分のそれの厚みより薄くして光量を制御してもよい。あるいは領域 B の部分に絶縁膜を 1 層あるいは多層に形成し、透過率、反射率、あるいは位相などを変えて実効的に領域 B の透過率を領域 C の透過率より低くしてもよい。

#### 【 0 1 1 4 】

また、露光量を領域 A ( 実質的に 0 ) < 領域 B < 領域 C に設定するためには、以下の方法もある。領域 A と領域 B に対してともに同等程度の低い透過率をもつ遮光部分でマスク上にパターンを形成し、領域 C 用には充分な透過率をもつたとえば一切の遮光パターンを形成しないパターンをマスク上に形成する。ついで、この領域 A + 領域 B の遮光パターンをもつマスクを用いて露光量 1 で露光を行ない、領域 C に対応する部分のホトレジストに光を照射する。ついで、領域 A の遮光パターンマスクを用いて領域 A を形成する部分以外に露光量 2 で光を照射する。このとき露光量 1 は現像時に領域 C のホトレジストが充分に除去できる強度で露光を行ない、露光量 2 は現像時に領域 B に必要な厚みのホトレジストが残るように設定する。一般的にはポジ型のホトレジストを用いた場合には露光量 1 は露光量 2 よりも、光照射時の光強度 × 光照射時間の計算結果が大きくなるように設定する。

10

#### 【 0 1 1 5 】

ホトレジストの厚みが、領域 A > 領域 B > 領域 C ( 実質的に 0 ) に設定するための第 3 の方法としては、領域 A を形成するためには金属などの低い透過率をもつ遮光層でマスク上にパターンを形成し、領域 C 用には充分な透過率をもつたとえば一切の遮光パターンを形成しないパターンをマスク上に形成する。

20

#### 【 0 1 1 6 】

領域 B 用としては、たとえばいわゆるハーフトーンマスクを用いてもよい。実際のパターンの例を図 3 3 に示す。ハーフトーンマスク 2 3 3 はマスク上の遮光パターンの空間周波数を露光機のパターン分解能力より充分高くし、ホトレジスト上でマスクのパターンが充分解像できない状態とし、領域 C よりもホトレジストに入射する露光強度が少なくなるようにする。ハーフトーンマスクのパターンは、まったく光を通さない領域と、透過率がホトマスクのガラスと同等の領域が、合計 6  $\mu$ m 以下の幅で周期的に形成されていることが望ましい。

#### 【 0 1 1 7 】

30

この結果、ホトレジストの厚みが領域 A > 領域 B > 領域 C ( 実質的に 0 ) に設定でき、その結果、図 4 4 ( b )、図 4 6 ( b ) のホトレジスト形状が実現される。

#### 【 0 1 1 8 】

ついで、たとえばゲート配線上の  $n^+ a - Si : H$  膜 4 1 5、 $a - Si : H$  膜 4 1 4 といった半導体膜と、 $Si_3N_4$  などのゲート絶縁膜 4 1 3 をエッチングする。このエッチングは、たとえば H C 1 を主成分とするガスや C F<sub>4</sub> を主成分とするガスや C F<sub>4</sub> と O<sub>2</sub> の混合ガス、 S F<sub>6</sub> を主成分とするガスなどで行なう。この結果、少なくともたとえばゲート配線と外部から信号を入力するため T C P などと接続するゲート端子部分 4 2 3 、静電気防止のため直接ソース配線あるいは T F T あるいは抵抗を介してソース配線部と短絡する部分 ( 図 2 8 、 1 1 3 など ) において、  $n^+ a - Si : H$  膜 4 1 5、 $n - Si : H$  膜 4 1 4 、ゲート絶縁膜 4 1 3 はエッチングされる。このエッチング完了時に、領域 B のホトレジストは残存するように膜厚が設定されている。この工程で  $n^+ a - Si : H$  膜 4 1 5、 $a - Si : H$  膜 4 1 4、 $Si_3N_4$  などのゲート絶縁膜 4 1 3 のエッチングは C F<sub>4</sub> や C F<sub>4</sub> + O<sub>2</sub> などの単一ガスで全膜をエッチングしてもよいが、たとえば a - Si : H 膜エッチング時に Si N 膜のエッチングが抑えられるようなガスを用いるなど、少なくとも a - Si : H 膜と Si<sub>3</sub>N<sub>4</sub> 膜を別々のエッチングガスでドライエッチングしたり、別々の条件でエッチングしてもよい。この場合 a - Si : H のエッチングとして S F<sub>6</sub>、 H C 1 、 F 1 2 3 あるいはこれらの混合ガスあるいはこれらと不活性ガスあるいは O<sub>2</sub> との混合ガスを Si<sub>2</sub>N<sub>4</sub> 膜のエッチングとして C F<sub>4</sub>、 S F<sub>6</sub> あるいはこれらの混合ガスあるいはそれらと O<sub>2</sub> や不活性ガスと混合ガスを用いてもよい。

40

50

## 【0119】

ついで、たとえば酸素プラズマなどのレジストの膜厚を低減できるプラズマを用いてアッティングを行なってレジストを削り、領域B(418b)からレジストを取り除く(図44(c))。このとき領域A(418a)のレジストの膜厚は初期の膜厚より薄くなるが、以下のエッティング時にエッティングしない部分を充分保護できるような厚みを保つように制御する。ついで、少なくともn<sup>+</sup>a-Si:H膜415、a-Si:H膜414をドライエッティング法などでエッティングし領域Bよりこれらの膜を取り除く(図45(a))。

## 【0120】

このとき、領域Bのレジストの膜厚を低減させる工程は独立に行なわず、n<sup>+</sup>a-Si:H膜415、a-Si:H膜414、Si<sub>3</sub>N<sub>4</sub>などのゲート絶縁膜413のエッティング行なう際に、ホトレジスト自身も幾分削れる現像を利用し、同時に領域Bのホトレジストを削ってもよい。ついで、ホトレジスト418aを取り除く。

10

## 【0121】

ついで、たとえばITO(インジウムスズ酸化物)やSnO<sub>2</sub>、InZnOなどの透明導電膜あるいはこれらの積層、あるいは混合層からなる透明導電層416と、Cr、Al、Ti、Ta、Au、Ag、W、Mo、Mo-W、Cuあるいはこれらを主成分とする合金あるいはそれらの多層積層物などからなるソース電極442bおよびソース配線102、ドレイン電極442aとなる金属層417を成膜する。ついで写真製版法でソース電極及びソース配線、ドレイン電極、画素電極の形状に配線パターンを形成後、透明導電層416と金属層417を同一のホトレジストパターンを用いてウエットあるいはドライなどでエッティングし、ソース電極、ソース配線、ドレイン電極および画素電極を形成する。ついで、ソース電極442bとドレイン電極442a間のn<sup>+</sup>a-Si:H膜などで形成したオーミックコンタクト層415をドライエッティングなどで取り除き、最後にレジストを剥離することで所定のパターンを形成する(図44(b)、図45(c))。

20

## 【0122】

このとき、保持容量を形成するため、ソース配線と同時に作製する保持容量電極419を少なくともゲート絶縁膜413を介して次段あるいは前段のゲート配線412と対抗させる。このとき、保持容量電極419とゲート絶縁膜413の間にはゲート絶縁膜413のみでなくn<sup>+</sup>a-Si:H膜415、a-Si:H膜414を残してもよい。保持容量電極は、容量値を増加させるため図46(c)に示すように画素電極445の少なくとも一部を前段または次段のゲート配線412上にを張り出させる構造を取ることが必要である。

30

## 【0123】

ついで、Si<sub>3</sub>N<sub>4</sub>、SiO<sub>2</sub>などあるいはこれらの混合物および積層物からなる絶縁膜で形成した保護膜420を成膜する。写真製版で少なくとも信号を入れるために外部のTCPなどに接続するゲート端子部423、ソース端子部424にコンタクトホールが形成できるように保護膜420を取り除くホトレジストパターンを形成するとともに、画素電極445として光を透過させる領域443の上の保護膜420を取り除くことができるようなホトレジストパターンを形成後、CF<sub>4</sub>系などのガスを用いたドライエッティングやウエットエッティング法で保護膜420を取り除く。さらに、2層のソース配線材料層のうち上層の金属層を取り除く。エッチャントとしては上層の金属膜をエッティングするが、下層のITO膜をエッティングしない溶液やガス等を使用し、ウエットあるいはドライエッティングする。これにより、コンタクトホールと画素電極のITO膜が露出する。エッティング完了後ホトレジストを除去する。これにより、TFTアレイが形成される(図45(c)、図47(a))。完成した平面パターン図は図47(b)に示す。

40

## 【0124】

ついでTFTアレイ上に配向膜を形成し、少なくとも表面に配向膜とコモン電極を形成した対向基板と向かい合わせ、両ガラス基板を保持し、かつ液晶を保つシール部を周辺に形成しその間に液晶を注入し、注入孔を封止してアクティブマトリクス型液晶ディスプレイを形成する。

50

## 【0125】

以上のプロセスによって図28に示した構成図をもつTFTアレイおよびそれを用いた液晶ディスプレイが形成される。

## 【0126】

図28においてたとえばゲート配線材料を用いて形成したソース配線のリペア配線114が図示されているが、これは状況によっては形成しなくともよい。

## 【0127】

また、図34に示すように、リペア配線114との交差部において、ソース配線102をコンタクトホール116a、116bを利用してゲート配線材料で形成したゲート配線と同層の配線117に一旦変換してもよい。このときリペア配線114はソース配線材料を用いて形成する。10

## 【0128】

また、図48、図49のようにソース配線302においてコンタクトホールを介してゲート配線材料に変換してソース端子308までつなげてもよい。たとえば、保護膜420が薄い場合など、ピンホールを介して水分が進入し、シール部の外側に存在するソース端子部308近傍でソース配線が腐食することがあるが、このようにゲート配線材料に変換すればソース配線の腐食の問題を避けることができる。

## 【0129】

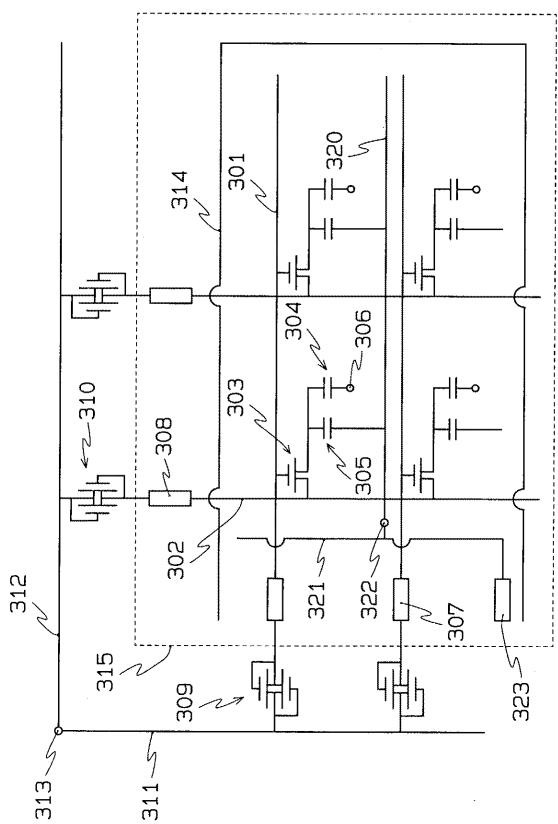

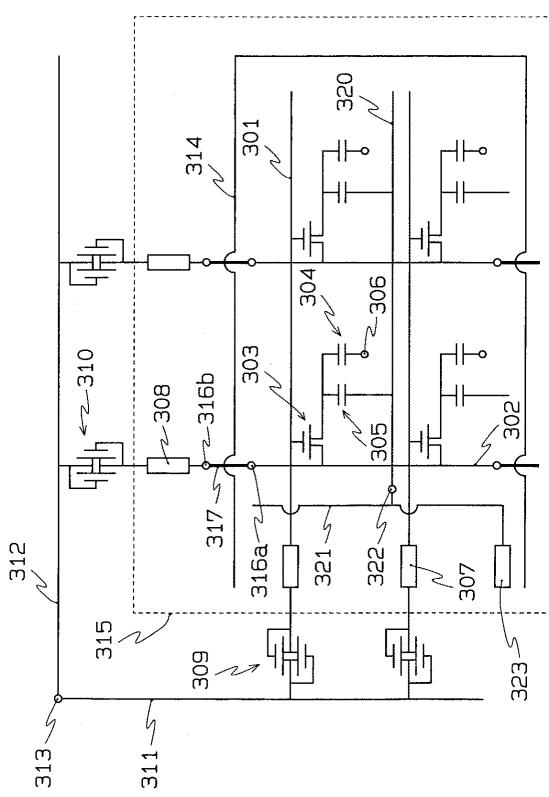

実施の形態13

前記実施の形態では保持容量が次段あるいは前段のゲート配線との間で形成されたいわゆるCS on gate構造に関して説明したが、図50の回路図に示すように、ゲート遅延に有利な保持容量配線をゲート配線と別に形成した共通配線構造としてもよい。ここで、保持容量305は共通配線320に接続されている。また、共通配線320はコンタクトホール322を介して共通配線引き出し線321に接続されている。コモン電圧は共通配線引き出し線321に接続されている共通配線端子323を介して外部から電圧を印加する。その他の部分の機能と図番号は図28と同じである。20

## 【0130】

共通配線方式においては、たとえば図51に示すような断面構造、図52(a)、52(b)、52(c)、図53(a)、53(b)に示す平面配置を取る。図52(a)、52(b)、52(c)、図53(a)、53(b)には平面図をフローごとに示す。ここで図51は図52(a)、52(b)、52(c)、図53(a)、53(b)のZ1-Z1断面図である。断面のフローは図44(a)、44(b)、44(c)と基本的に同じである。30

## 【0131】

図50に示すように、共通配線構造を用いる場合はゲート配線と平行に引き出される共通配線320とそれをまとめてゲート配線301と垂直に走る共通配線引き出し線321が必要となる。図50の場合はゲート配線301と同時に作製した共通配線320を左端でコンタクトホール322を介してソース配線302と同時に作製した共通配線引き出し線321と接続している。

## 【0132】

図54のように共通配線320はゲート配線301と同じ材料で同時に形成することが最もよく、共通配線引き出し線321は少なくともそのゲート配線との交差部324はゲート配線とは異層のソース配線材料を用いる。場合によってはゲート配線との交差部以外は、ゲート配線材料で共通配線引き出し線を形成してもよい。40

## 【0133】

また、図55に示すように、リペア配線314との交差部において、ソース配線302をコンタクトホール315a、315bを利用してゲート配線材料で形成したゲート配線と同層の配線316に一旦変換してもよい。

## 【0134】

また、図56のようにソース配線302においてコンタクトホールを介してゲート配線

10

20

30

40

50

と同じ材料に変換してソース端子 308までつなげてもよい。たとえば、保護膜 420が薄い場合などピンホールを介して水分が進入し、シール部の外側に存在する端子部 308近傍でソース配線が腐食することがあるが、このようにゲート配線材料に変換すればソース配線の腐食の問題を避けることができる。この構造の端子部の断面図は図 49と同じである。

【0135】

実施の形態 14

図 47(a)、47(b)、図 53(a)、53(b)に示すように画素電極に光を通すための金属を取り除くため保護膜 420を取り除く領域 443は 442a の内側に書かれているが、443の外側に配置してもよい。

10

【0136】

実施の形態 15

前記実施の形態 12～14では、液晶自身に電圧を印加するコモン電極が対向基板にある場合に關して説明したが、広視野角を実現できるIPS(In-plane switching)モードなどの横方向電界印加用 TFT 基板に關しても適用できる。この場合は、ソース配線は透明導電膜 416と金属層 417の2層にする必要はなく金属層 417のみでもよい。そしてゲート電極と同時に形成する横電界用の少なくとも 2 本の電極(図 57(b))、あるいはソース電極と同時に形成する横方向用の少なくとも 2 本の電極、あるいはソース電極と同時に形成する少なくとも 1 本の横方向電界用の電極とゲート電極と同時に形成する少なくとも 1 本の横方向電界用電極が組となった少なくとも 2 本の横方向電界用の電極(図 62(a))を用いて横方向の電界を液晶に印加する電極構成を作ることができる。この場合は保護絶縁膜 420は図 45(c)のように画素電極上を取り除かなくてもよい。また、保護絶縁膜を形成しなくてもよい。

20

【0137】

また、図 45(b)、45(c)の部分を図 58(a)、58(b)のようなフローにしてもよい。この時ソース電極 / 配線は金属一層で作る。ここで図 58(a)のようにドレイン電極 442a、ソース電極 442bを形成後、図 58(b)のように保護絶縁膜 420(SiN)を形成する。ついで、ドレイン電極 442a 上と共通配線 412 上にコンタクトホールを形成後、ドレイン電極側のIPS電極 447、共通配線側のIPS電極 448となる第3の電極を形成する。平面図を図 57(c)に示す。

30

【0138】

実施の形態 16

前記実施の形態では、a-Si:H膜の島状化のため、図 44で示したようにハーフトーンなどの技術を用い、レジストの厚みを平面状で部分的に変更していたが、この工程を止め、a-Si:H膜の島化の写真製版を別に行ってもよい。この場合は、たとえば、レジストの厚みには空間的には変化させない。図 44(b)の状態で平面的にレジストの厚みを変化させず、コンタクト部 423 上の SiN 膜 413 / a-Si:H 414 / n+a-Si:H 415を抜く工程を実施後、レジストを除去し、再度トランジスタの島を形成するパターンを作製し、TFT 部以外の a-Si:H 膜 414 と n+a-Si:H 膜 415をエッティングで取り除き、図 45(a)の構造を作製する。この場合、図 28 よりは写真製版回数が増えるが、従来例よりは低減できる。

40

【0139】

実施の形態 17

前記実施の形態によれば、半導体層は a-Si:H 膜で形成されていたが、poly-Si であってもよい。

【0140】

実施の形態 18

n+a-Si:H 膜 415 は n+マイクロクリスタル Si 層であってもよくこの場合、ITO 層 416 と n+a-Si:H 膜 415 間のコンタクト抵抗が低下し、TFT のオン電流が改善が図れる。

50

## 【0141】

## 実施の形態19

ソース配線としても用いているITO層416はアモルファスITOであってもよく、同時にソース金属としてAlやCr/AlなどのAl系を用いた場合は、ITOをエッチング時にAlの腐食を低減できる、ショウ酸などのAlに対する腐食性が低いエッチャントと使用できる。

## 【0142】

## 実施の形態20

前記実施の形態においてゲートとしてAl系材料を用いる場合は、Alおよびその合金の表面をAlの窒化物あるいは酸化物とするとITO層とのコンタクトを改善できる。

10

## 【0143】

## 実施の形態21

前記実施の形態においてn<sup>+</sup>a-Si:H膜415の表面は若干酸化プラズマなどに曝し酸化処理をしておいてもよく、これによりITO416とn<sup>+</sup>a-Si:H膜415間のコンタクト抵抗のバラツキを低減できる。

## 【符号の説明】

## 【0144】

- |                     |                          |    |

|---------------------|--------------------------|----|

| 1                   | ゲート配線                    |    |

| 1 a                 | ゲート端子部金属パッド              |    |

| 2                   | 補助容量配線                   | 20 |

| 2 a                 | IPS対向電極                  |    |

| 3                   | ゲート絶縁膜                   |    |

| 4                   | 半導体パターン                  |    |

| 4 a                 | 半導体層                     |    |

| 4 b                 | オーミック層                   |    |

| 5                   | ソース配線                    |    |

| 5 a                 | ソース端子部金属パッド              |    |

| 6                   | ソース電極                    |    |

| 7                   | ドレイン電極                   |    |

| 8                   | 薄膜トランジスタ半導体活性層           | 30 |

| 9                   | 層間絶縁膜                    |    |

| 10                  | ドレイン電極コンタクトホール           |    |

| 11                  | ゲート端子部コンタクトホール           |    |

| 12                  | ソース端子部コンタクトホール           |    |

| 13                  | 画素電極                     |    |

| 13 a                | IPS電極                    |    |

| 14                  | ゲート端子接続パッド               |    |

| 15                  | ソース端子接続パッド               |    |

| 16                  | 第2金属膜                    |    |

| 17 a                | 第2写真製版通常膜厚レジストパターン       | 40 |

| 17 b、17 c、17 d、17 e | 第2写真製版薄膜パターン             |    |

| 18                  | 第2写真製版レジストパターンアッシング後の開口部 |    |

| 19                  | TFT部パターン                 |    |

| 5 1                 | ゲート配線                    |    |

| 5 2                 | ゲート絶縁膜                   |    |

| 5 3                 | 半導体層                     |    |

| 5 4                 | オーミック層                   |    |

| 5 5                 | ソース配線                    |    |

| 5 6                 | ソース電極                    |    |

| 5 7                 | ドレイン電極                   | 50 |

|                         |                          |    |

|-------------------------|--------------------------|----|

| 5 8                     | 薄膜トランジスタ半導体活性層           |    |

| 5 9                     | 層間絶縁膜                    |    |

| 6 0                     | コンタクトホール                 |    |

| 6 1                     | 画素電極                     |    |

| 6 2                     | 端面リーコンタクト                |    |

| 1 0 1                   | ゲート配線                    |    |

| 1 0 2                   | ソース配線                    |    |

| 1 0 3                   | 薄膜トランジスタ ( TFT )         |    |

| 1 0 4                   | 液晶 ( 容量 )                |    |

| 1 0 5                   | 保持容量                     | 10 |

| 1 0 6                   | コモン電極                    |    |

| 1 0 7                   | ゲート端子                    |    |

| 1 0 8                   | ソース端子                    |    |

| 1 0 9、 1 1 0            | 高抵抗素子                    |    |

| 1 1 1                   | 配線 A                     |    |

| 1 1 2                   | 配線 B                     |    |

| 1 1 3                   | 配線 A、 B の接続部             |    |

| 1 1 4                   | リペア配線                    |    |

| 1 1 5                   | 切離し線                     |    |

| 1 2 0                   | 共通配線                     | 20 |

| 1 2 1                   | 共通配線引き出し線                |    |

| 2 1 1                   | 絶縁性基板                    |    |

| 2 1 2                   | ゲート電極およびゲート配線 ( 透明導電体層 ) |    |

| 2 1 3                   | ゲート電極およびゲート配線 ( 金属層 )    |    |

| 2 1 4                   | 画素電極 ( 透明導電体層 )          |    |

| 2 1 5                   | 画素電極 ( 金属層 )             |    |

| 2 1 6                   | ゲート絶縁膜                   |    |

| 2 1 7                   | 半導体層 ( 能動層 )             |    |

| 2 1 8                   | 半導体層 ( コンタクト層 )          |    |

| 2 1 9、 2 1 9 a、 2 1 9 b | ホトレジスト                   | 30 |

| 2 2 0 a                 | ソース配線                    |    |

| 2 2 0 b                 | ドレイン電極                   |    |

| 2 2 0 c                 | ソース電極                    |    |

| 2 2 1                   | 保持容量電極                   |    |

| 2 2 2                   | 絶縁膜                      |    |

| 2 2 4                   | ゲート端子部                   |    |

| 2 2 5                   | ソース端子部                   |    |

| 2 3 0                   | 半導体領域                    |    |

| 2 3 1、 2 3 2            | 画素電極                     |    |

| 2 3 3                   | ハーフトーンマスク                | 40 |

| 3 0 2                   | ソース配線                    |    |

| 3 0 5                   | 保持容量                     |    |

| 3 0 8                   | ソース端子                    |    |

| 3 1 4                   | リペア配線                    |    |

| 3 2 0                   | 共通配線                     |    |

| 3 2 1                   | 共通配線引出線                  |    |

| 4 1 0                   | 絶縁性基板                    |    |

| 4 1 1                   | ゲート電極 / 配線               |    |

| 4 1 2                   | ゲート電極 / 配線 ( 隣接 )        |    |

| 4 1 3                   | ゲート絶縁膜                   | 50 |

- 4 1 4 半導体層

4 1 5 オーミックコンタクト層

4 1 6 透明導電体層

4 1 7 金属層

4 1 8 ホトレジスト

4 1 9 保持容量電極

4 2 0 保護絶縁膜

4 2 3 ゲート端子部

4 3 0 半導体領域

4 4 3 光透過領域

4 4 5 画素電極

4 4 7、4 4 8 IPS電極

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図53】

### 【図54】

【図55】

【図56】

【図57】

【図58】

【図59】

【図60】

【図61】

【図62】

【図63】

【図65】

【図64】

【図66】

【図67】

【図68】

【図69】

---

フロントページの続き

(31)優先権主張番号 特願2000-82142(P2000-82142)

(32)優先日 平成12年3月23日(2000.3.23)

(33)優先権主張国 日本国(JP)

(72)発明者 井上 和式

熊本県合志市御代志 997番地 株式会社アドバンスト・ディスプレイ内

(72)発明者 吉田 卓司

熊本県合志市御代志 997番地 株式会社アドバンスト・ディスプレイ内

(72)発明者 中嶋 健

熊本県合志市御代志 997番地 株式会社アドバンスト・ディスプレイ内

(72)発明者 升谷 雄一

熊本県合志市御代志 997番地 株式会社アドバンスト・ディスプレイ内

(72)発明者 青木 宏憲

熊本県合志市御代志 997番地 株式会社アドバンスト・ディスプレイ内

審査官 小濱 健太

(56)参考文献 特開平06-235939(JP, A)

特開平07-175088(JP, A)

特開平5-303112(JP, A)

特開平6-97445(JP, A)

特開平6-250217(JP, A)

特開平7-92488(JP, A)

特開平7-110496(JP, A)

特開平8-76144(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP5026450B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2012-09-12 |

| 申请号            | JP2009043907                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2009-02-26 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 小林和弘<br>中村伸宏<br>井上和式<br>吉田卓司<br>中嶋健<br>升谷雄一<br>青木宏憲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 小林 和弘<br>中村 伸宏<br>井上 和式<br>吉田 卓司<br>中嶋 健<br>升谷 雄一<br>青木 宏憲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/1368 G02F1/136 G02F1/1362                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G02F1/13458 G02F1/136227 G02F1/136286 G02F1/1368 G02F2001/136236                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/HA04 2H092/HA06 2H092/JA26 2H092/JA35 2H092/JA40 2H092/JA44 2H092/JA46 2H092/JA47 2H092/JB24 2H092/JB33 2H092/JB57 2H092/JB64 2H092/JB68 2H092/JB69 2H092/KA04 2H092/KA05 2H092/KA12 2H092/KA18 2H092/KB24 2H092/KB25 2H092/MA05 2H092/MA08 2H092/MA15 2H092/MA16 2H092/MA18 2H092/MA27 2H092/MA37 2H092/NA15 2H092/NA22 2H092/NA27 2H092/NA29 2H192/AA24 2H192/BB02 2H192/BB03 2H192/BC23 2H192/BC31 2H192/CB05 2H192/CB35 2H192/CB45 2H192/CB82 2H192/CC04 2H192/CC32 2H192/CC75 2H192/DA02 2H192/DA12 2H192/DA24 2H192/DA32 2H192/EA04 2H192/FA35 2H192/FA46 2H192/FA65 2H192/GA13 2H192/GA15 2H192/GA41 2H192/HA35 2H192/HA44 2H192/HA45 2H192/HA64 2H192/HA81 2H192/HB37 2H192/HB50 2H192/JA02 2H192/JA32 |         |            |

| 优先权            | 2000072766 2000-03-15 JP<br>2000082141 2000-03-23 JP<br>2000082142 2000-03-23 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | JP2009122697A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

**摘要(译)**

要解决的问题：通过减少光刻工艺和缩短制造工艺来降低TFT阵列的成本。ŽSOLUTION：栅极线 - 栅极电极包括两层作为上层的金属层和作为下层的透明导体层，像素电极由与透明导体层相同的层的透明导体层形成。栅极线 - 栅极电极，保持电容电极由与源极导线相同的层的电极材料形成，并连接到像素电极，金属层作为栅极导线的上层 - 栅极在像素电极部分中去除电极。Ž

【 図 1 】