(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6227530号

(P6227530)

(45) 発行日 平成29年11月8日(2017.11.8)

(24) 登録日 平成29年10月20日(2017.10.20)

|                      |                |

|----------------------|----------------|

| (51) Int.CI.         | F 1            |

| G09G 3/36 (2006.01)  | GO9G 3/36      |

| G09G 3/20 (2006.01)  | GO9G 3/20 622E |

| G02F 1/133 (2006.01) | GO9G 3/20 622B |

|                      | GO9G 3/20 622R |

|                      | GO2F 1/133 550 |

請求項の数 9 (全 13 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-526374 (P2014-526374)  |

| (86) (22) 出願日 | 平成24年8月21日 (2012.8.21)        |

| (65) 公表番号     | 特表2014-524598 (P2014-524598A) |

| (43) 公表日      | 平成26年9月22日 (2014.9.22)        |

| (86) 国際出願番号   | PCT/CN2012/080420             |

| (87) 国際公開番号   | W02013/026387                 |

| (87) 国際公開日    | 平成25年2月28日 (2013.2.28)        |

| 審査請求日         | 平成27年7月13日 (2015.7.13)        |

| (31) 優先権主張番号  | 201110241400.8                |

| (32) 優先日      | 平成23年8月22日 (2011.8.22)        |

| (33) 優先権主張国   | 中国 (CN)                       |

|           |                                                             |

|-----------|-------------------------------------------------------------|

| (73) 特許権者 | 507134301<br>北京京東方光電科技有限公司<br>中華人民共和国北京經濟技術開發區西環中<br>路8號    |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                      |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                       |

| (74) 代理人  | 100110364<br>弁理士 実広 信哉                                      |

| (72) 発明者  | ▲陳▼ 希<br>中華人民共和国 100176 北京市▲經▼<br>▲濟▼技▲術▼▲開▼▲發▼区地▲澤▼路<br>9号 |

最終頁に続く

(54) 【発明の名称】ゲートドライバ集積回路、シフトレジスタ及びディスプレイスクリーン

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲートドライバ集積回路であって、

ゲート電極が前記ゲートドライバ集積回路の入力端に接続され、ドレイン電極が電源電圧 VDD に接続され、ソース電極がブルアップノードとしての第 1 のノードに接続される第 1 の薄膜トランジスタ TFT と、

ゲート電極が前記ゲートドライバ集積回路のリセット端に接続され、ソース電極が共通接続電圧 VSS に接続され、ドレイン電極が前記第 1 のノードに接続される第 2 の TFT と、

ゲート電極が前記第 1 のノードに接続され、ドレイン電極が第 1 のクロック信号の入力端に接続され、ソース電極が出力端に接続される第 3 の TFT と、

ゲート電極が第 2 のクロック信号の入力端に接続され、ドレイン電極が出力端に接続され、ソース電極が低電圧信号端に接続される第 4 の TFT と、

前記第 1 のノードと出力端との間に接続される電気容量と、

第 1 のクロック信号の入力端、第 2 のクロック信号の入力端、及び前記第 1 のノードと出力端との間に接続され、かつ低レベル信号端に接続され、前記ゲートドライバ集積回路が作動しない時期内に、前記第 1 のノードと出力端を低レベルに維持するプルダウンモジュールと、を備え、

前記プルダウンモジュールは、

ドレイン電極が第 2 のクロック信号の入力端に接続され、ソース電極がプルダウンノード

10

20

ドとしての第2のノードに接続される第5のTFTと、

ドレイン電極が前記第2のノードに接続され、ゲート電極が前記第1のノードに接続され、ソース電極が低電圧信号端に接続される第6のTFTと、

ゲート電極及びドレイン電極が第2のクロック信号の入力端にともに接続され、ソース電極が前記第5のTFTのゲート電極に接続される第7のTFTと、

ドレイン電極が前記第7のTFTのソース電極に接続され、ゲート電極が前記第1のノードに接続され、ソース電極が低電圧信号端に接続される第8のTFTと、

ドレイン電極が前記第1のノードに接続され、ゲート電極が前記第2のノードに接続され、ソース電極が低電圧信号端に接続される第9のTFTと、

ドレイン電極が前記出力端に接続され、ゲート電極が前記第2のノードに接続され、ソース電極が低電圧信号端に接続される第10のTFTと、を備える

ことを特徴とするゲートドライバ集積回路。

#### 【請求項2】

前記ゲートドライバ集積回路が奇数行目のゲートライン信号を制御する場合、第1のクロック信号の入力端が第1のクロック信号線に接続され、第2のクロック信号の入力端が第2のクロック信号線に接続され、

前記ゲートドライバ集積回路が偶数行目のゲートライン信号を制御する場合、第2のクロック信号の入力端が第1のクロック信号線に接続され、第1のクロック信号の入力端が第2のクロック信号線に接続され、

ことを特徴とする請求項1に記載のゲートドライバ集積回路。

#### 【請求項3】

シフトレジスタであって、

複数のゲートドライバ集積回路を備え、各ゲートドライバ集積回路は、対応する行のゲートライン信号を制御するものであり、第N行のゲートライン信号を制御するゲートドライバ集積回路は、入力端が第N-1行のゲートライン信号を制御するゲートドライバ集積回路の出力端に接続され、出力端が第N+1行のゲートライン信号を制御するゲートドライバ集積回路の入力端に接続され、リセット端が第N+1行のゲートライン信号を制御するゲートドライバ集積回路の出力端に接続され、Nが2以上であり、

各ゲートドライバ集積回路は、

ゲート電極が前記ゲートドライバ集積回路の入力端に接続され、ドレイン電極が電源電圧VDDに接続され、ソース電極がプルアップノードとしての第1のノードに接続される第1の薄膜トランジスタTFTと、

ゲート電極が前記ゲートドライバ集積回路のリセット端に接続され、ソース電極が共通接続電圧VSSに接続され、ドレイン電極が前記第1のノードに接続される第2のTFTと、

ゲート電極が前記第1のノードに接続され、ドレイン電極が第1のクロック信号の入力端に接続され、ソース電極が出力端に接続される第3のTFTと、

ゲート電極が第2のクロック信号の入力端に接続され、ドレイン電極が出力端に接続され、ソース電極が低電圧信号端に接続される第4のTFTと、

前記第1のノードと出力端との間に接続される電気容量と、

第1のクロック信号の入力端、第2のクロック信号の入力端、及び前記第1のノードと出力端との間に接続され、かつ低レベル信号端に接続され、前記ゲートドライバ集積回路が作動しない時期内に、前記第1のノードと出力端を低レベルに維持するプルダウンモジュールと、を備え、

前記プルダウンモジュールは、

ドレイン電極が第2のクロック信号の入力端に接続され、ソース電極がプルダウンノードとしての第2のノードに接続される第5のTFTと、

ドレイン電極が前記第2のノードに接続され、ゲート電極が前記第1のノードに接続され、ソース電極が低電圧信号端に接続される第6のTFTと、

ゲート電極及びドレイン電極が第2のクロック信号の入力端にともに接続され、ソース

10

20

30

40

50

電極が前記第 5 の T F T のゲート電極に接続される第 7 の T F T と、

ドレイン電極が前記第 7 の T F T のソース電極に接続され、ゲート電極が前記第 1 のノードに接続され、ソース電極が低電圧信号端に接続される第 8 の T F T と、

ドレイン電極が前記第 1 のノードに接続され、ゲート電極が前記第 2 のノードに接続され、ソース電極が低電圧信号端に接続される第 9 の T F T と、

ドレイン電極が前記出力端に接続され、ゲート電極が前記第 2 のノードに接続され、ソース電極が低電圧信号端に接続される第 10 の T F T と、を備える

ことを特徴とするシフトレジスタ。

**【請求項 4】**

奇数行目のゲートライン信号を制御するゲートドライバ集積回路は、第 1 のクロック信号の入力端が第 1 のクロック信号線に接続され、第 2 のクロック信号の入力端が第 2 のクロック信号線に接続され、10

偶数行目のゲートライン信号を制御するゲートドライバ集積回路は、第 2 のクロック信号の入力端が第 1 のクロック信号線に接続され、第 1 のクロック信号の入力端が第 2 のクロック信号線に接続される

ことを特徴とする請求項 3 に記載のシフトレジスタ。

**【請求項 5】**

順方向走査をスタートする場合、前記 V D D がコンスタントな高レベルを提供し、前記 V S S がコンスタントな低レベルを提供し、奇数行目のゲートライン信号を制御するゲートドライバ集積回路では、20

前記ゲートドライバ集積回路の入力端に高レベルのパルス信号を入力し、前記第 1 の T F T のドレイン電極で前記第 1 のノードに充電し、

第 1 のクロック信号の入力端が第 1 のクロック信号線に提供される高レベルのクロック信号を受信し、前記第 3 の T F T が高レベルを出力するように前記出力端を制御し、前記第 6 の T F T を導通し、前記第 2 のノードの電圧を低電圧信号端の電圧までプルダウンし、

前記第 2 の T F T のゲート電極に接続される前記リセット端が高レベルであって、前記第 1 のノードを放電し、

第 2 のクロック信号の入力端が第 2 のクロック信号線に提供される高レベルのクロック信号を受信し、前記第 4 の T F T で前記出力端を放電し、前記第 5 の T F T で前記第 2 のノードに充電し、前記第 1 のノードに放電するように第 9 の T F T を制御し、出力端を放電するように前記第 10 の T F T を制御する30

ことを特徴とする請求項 4 に記載のシフトレジスタ。

**【請求項 6】**

順方向走査をスタートする場合、前記 V D D がコンスタントな高レベルを提供し、前記 V S S がコンスタントな低レベルを提供し、偶数行目のゲートライン信号を制御するゲートドライバ集積回路では、

ゲートドライバ集積回路の入力端に高レベルのパルス信号を入力し、前記第 1 の T F T のドレイン電極で前記第 1 のノードに充電し、

第 1 のクロック信号の入力端が第 2 のクロック信号線に提供される高レベルのクロック信号を受信し、前記第 3 の T F T によって高レベルを出力するように前記出力端を制御し、前記第 6 の T F T を導通し、前記第 2 のノードの電圧を低電圧信号端の電圧までプルダウンし、40

前記第 2 の T F T のゲート電極に接続される前記リセット端が高レベルであって、前記第 1 のノードを放電し、第 2 のクロック信号の入力端が第 1 のクロック信号線に提供される高レベルのクロック信号を受信し、前記第 4 の T F T で前記出力端を放電し、前記第 5 の T F T で前記第 2 のノードに充電し、前記第 1 のノードに放電するように第 9 の T F T を制御し、出力端を放電するように前記第 10 の T F T を制御する

ことを特徴とする請求項 4 に記載のシフトレジスタ。

**【請求項 7】**

10

20

30

40

50

逆方向走査をスタートするとき、前記VDDがコンスタントな低レベルを提供し、前記VSSがコンスタントな高レベルを提供し、奇数行目のゲートライン信号を制御するゲートドライバ集積回路では、

ゲートドライバ集積回路のリセット端に高レベルのパルス信号を入力し、前記第2のTFTのソース電極で前記第1のノードに充電し、

第1のクロック信号の入力端が第1のクロック信号線に提供される高レベルのクロック信号を受信し、前記第3のTFTによって高レベルを出力するように前記出力端を制御し、前記第6のTFTを導通し、前記第2のノードの電圧を低電圧信号端の電圧までプルダウンし、

前記第1のTFTのゲート電極に接続される前記入力端が高レベルであって、前記第1のノードを放電し、10

第2のクロック信号の入力端が第2のクロック信号線に提供される高レベルのクロック信号を受信し、前記第4のTFTで前記出力端を放電し、前記第5のTFTで前記第2のノードに充電し、前記第1のノードを放電するように第9のTFTを制御し、出力端を放電するように前記第10のTFTを制御する

ことを特徴とする請求項4に記載のシフトレジスタ。

#### 【請求項8】

逆方向走査をスタートするとき、前記VDDがコンスタントな低レベルを提供し、前記VSSがコンスタントな高レベルを提供し、偶数行目のゲートライン信号を制御するゲートドライバ集積回路では、20

ゲートドライバ集積回路のリセット端に高レベルのパルス信号を入力し、前記第2のTFTのソース電極で前記第1のノードに充電し、

第1のクロック信号の入力端が第2のクロック信号線に提供される高レベルのクロック信号を受信し、前記第3のTFTによって高レベルを出力するように前記出力端を制御し、前記第6のTFTを導通し、前記第2のノードの電圧を低電圧信号端の電圧までプルダウンし、

前記第1のTFTのゲート電極に接続される前記入力端が高レベルであり、前記第1のノードを放電し、第2のクロック信号の入力端が第1のクロック信号線に提供される高レベルのクロック信号を受信し、前記第4のTFTによって前記出力端を放電し、前記第5のTFTによって前記第2のノードに充電し、前記第1のノードを放電するように第9のTFTを制御し、出力端を放電するように前記第10のTFTを制御する30

ことを特徴とする請求項4に記載のシフトレジスタ。

#### 【請求項9】

ディスプレイスクリーンであって、請求項3～8のいずれか1項に記載のシフトレジスタ及び画素回路を構成する素子のアレイ基板を備え、

前記シフトレジスタの信号出力端が前記アレイ基板のゲートラインに接続される

ことを特徴とするディスプレイスクリーン。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶ディスプレイという技術分野に関し、特に、ゲートドライバ集積回路、シフトレジスタ及びディスプレイスクリーンに関する。40

##### 【背景技術】

##### 【0002】

GOA(Gate Drive on Array、ゲートドライバ集積)とは、LCD(Liquid Crystal Display、液晶ディスプレイ)パネルのゲートドライバをガラス基板上に集積する技術である。そして、GOA回路は、アレイ基板のゲートラインに接続され、シフトレジスタとして、ゲートライン信号を制御する。GOA技術は、従来のCOF(Chip On Film、チップオンフィルム)及びCOG(Chip On Glass、チップオングラス)技術に対して、コストを低減しただけではない50

。

### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0003】

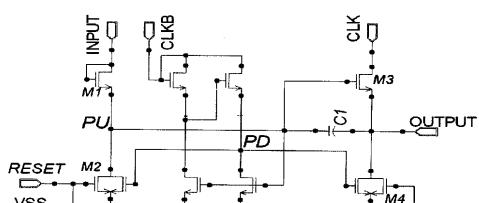

然し、従来技術では、G O A パネルの走査方向は、上から下へ走査し、または下から上へ走査するような単一方向に限る。図1は、従来技術に係る単一方向に走査するG O A回路であり、入力端I N P U Tの信号が高レベルである場合、T F T (Thin Film Transistor、薄膜トランジスタ) M 1をオンし、P U ノードに充電し、クロック信号C L Kが高レベルである場合、M 3を導通し、出力端O U T P U TがC L Kのパルス信号を出力するとともに、電気容量C 1のブートストラッピング(Boots trap pinning)作用によって、P U ノードをさらに向上させ、そして、リセット端R E S E Tが高レベルになり、T F T M 2及びM 4をオンし、P U ノード及びO U T P U Tを放電し、そして、クロック信号C L K BによってP D ノードを制御し、P U ノード及びO U T P U Tを放電する。これによって、この行が作動しない時期に、ノイズが生じないことが確保された。このようなパネルをシステムエンドと組み合わせて用いるとき、システムエンドによってI Cが異なる(I Cが上または下向け)ため、デバッグソフトウェアによって画像を逆にする必要がある可能性があり、不便である。

#### 【課題を解決するための手段】

##### 【0004】

本発明は、G O A回路の双方向走査を図れるとともに、ゲートドライバ集積回路の安定性を確保できるゲートドライバ集積回路、シフトレジスタ及びディスプレイスクリーンを提供する。

##### 【0005】

本発明の実施例に係るゲートドライバ集積回路は、

ゲート電極が上記ゲートドライバ集積回路の入力端に接続され、ドレイン電極が電源電圧V D Dに接続され、ソース電極がプルアップノードとしての第1のノードに接続される第1の薄膜トランジスタT F Tと、

ゲート電極が上記ゲートドライバ集積回路のリセット端に接続され、ソース電極が共通接続電圧V S Sに接続され、ドレイン電極が上記第1のノードに接続される第2のT F Tと、

ゲート電極が上記第1のノードに接続され、ドレイン電極が第1のクロック信号の入力端に接続され、ソース電極が出力端に接続される第3のT F Tと、

ゲート電極が第2のクロック信号の入力端に接続され、ドレイン電極が出力端に接続され、ソース電極が低電圧信号端に接続される第4のT F Tと、

上記第1のノードと出力端との間に接続される電気容量と、

第1のクロック信号の入力端、第2のクロック信号の入力端、及び第1のノードと出力端との間に接続され、かつ低レベル信号端に接続され、上記ゲートドライバ集積回路が作動しない時期内に、上記第1のノードと出力端を低レベルに維持するプルダウンモジュールと、を備える。

##### 【0006】

本発明の実施例は、シフトレジスタであって、複数の上記ゲートドライバ集積回路を備え、各ゲートドライバ集積回路は、対応する行のゲートライン信号を制御するものであり、第N行のゲートライン信号を制御するゲートドライバ集積回路は、入力端が第N - 1行のゲートライン信号を制御するゲートドライバ集積回路の出力端に接続され、出力端が第N + 1行のゲートライン信号を制御するゲートドライバ集積回路の入力端に接続され、リセット端が第N + 1行のゲートライン信号を制御するゲートドライバ集積回路の出力端に接続され、Nが2以上である。

##### 【0007】

本発明の実施例はディスプレイスクリーンであって、上記シフトレジスタ及びアレイ基板を備え、

10

20

30

40

50

上記シフトレジスタの信号出力端が上記アレイ基板のゲートラインに接続される。

**【発明の効果】**

**【0008】**

本発明の実施例に係るゲートドライバ集積回路、シフトレジスタ及びディスプレイスクリーンは、ゲートドライバ集積回路における入力端およびリセット端の機能を対称にして実現することによって、ゲートドライバ集積回路を双方向走査することができるようになり、かつノードの充放電特性が変更されなく、回路の信頼性及び安定性が確保された。

**【図面の簡単な説明】**

**【0009】**

【図1】従来技術に係るG O A回路を示す概略図である。

10

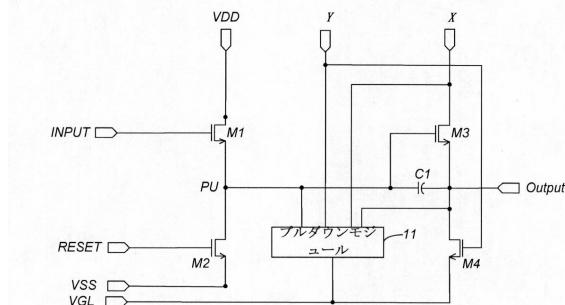

【図2】本発明の実施例に係るゲートドライバ集積回路の構造概略図である。

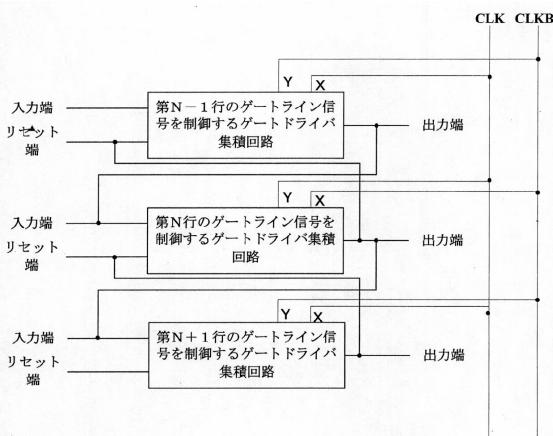

【図3】本発明の他の実施例に係るシフトレジスタの構造概略図である。

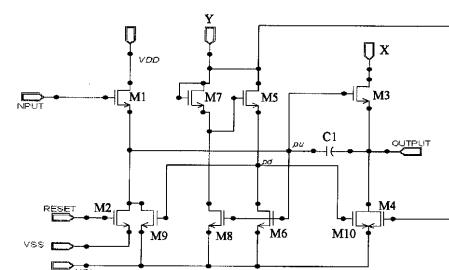

【図4】本発明の実施例に係るゲートドライバ集積回路の具体的な構造概略図である。

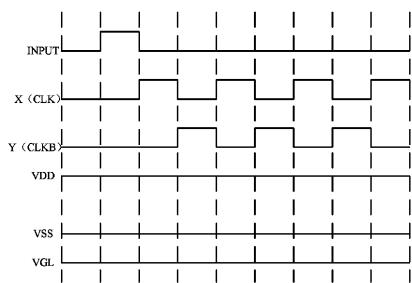

【図5】本発明の実施例に係る、順方向走査時に、奇数行目のゲートライン信号を制御するゲートドライバ集積回路の各エンドの電圧のシーケンス図である。

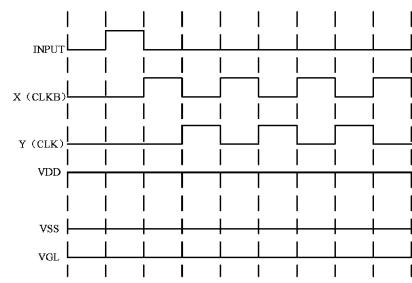

【図6】本発明の実施例に係る、順方向走査時に、偶数行目のゲートライン信号を制御するゲートドライバ集積回路の各エンドの電圧のシーケンス図である。

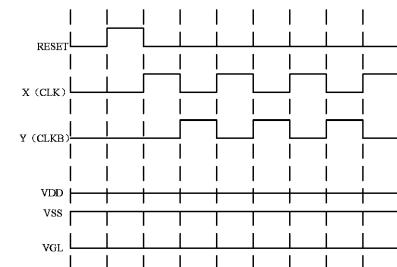

【図7】本発明の実施例に係る、逆方向走査時に、奇数行目のゲートライン信号を制御するゲートドライバ集積回路の各エンドの電圧のシーケンス図である。

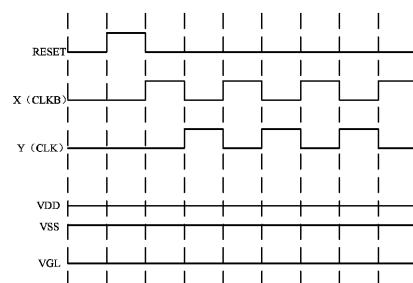

【図8】本発明の実施例に係る、逆方向走査時に、偶数行目のゲートライン信号を制御するゲートドライバ集積回路の各エンドの電圧シーケンス図である。

20

**【発明を実施するための形態】**

**【0010】**

以下、図面を参照しながら、本発明の実施例をさらに詳しく説明する。

**【0011】**

本発明の実施例はゲートドライバ集積回路であり、図2に示すように、このゲートドライバ集積回路は、

ゲート電極が上記ゲートドライバ集積回路の入力端I N P U Tに接続され、ドレイン電極が電源電圧V D Dに接続され、ソース電極がプルアップノードとしての第1のノードP Uに接続される第1の薄膜トランジスタT F T M 1と、

30

ゲート電極が上記ゲートドライバ集積回路のリセット端R E S E Tに接続され、ソース電極が共通接続電圧V S Sに接続され、ドレイン電極が上記第1のノードP Uに接続される第2のT F T M 2と、

ゲート電極が上記第1のノードP Uに接続され、ドレイン電極が第1のクロック信号の入力端Xに接続され、ソース電極が出力端O U T P U Tに接続される第3のT F T M 3と、

ゲート電極が第2のクロック信号の入力端Yに接続され、ドレイン電極が出力端O U T P U Tに接続され、ソース電極が低電圧信号端V G Lに接続される第4のT F T M 4と、

上記第1のノードP Uと出力端O U T P U Tとの間に接続される電気容量C 1と、

第1のクロック信号の入力端X、第2のクロック信号の入力端Y、及び第1のノードP Uと出力端O U T P U Tとの間に接続され、且つ低レベル信号端V G Lに接続され、上記ゲートドライバ集積回路が作動しない時期内に上記第1のノードP U及び出力端O U T P U Tを低レベルに維持するプルダウンモジュール1 1と、を備える。

40

**【0012】**

上記プルダウンモジュール1 1は、

ドレイン電極が第2のクロック信号の入力端に接続され、ソース電極がプルダウンノードとしての第2のノードに接続される第5のT F Tと、

ドレイン電極が上記第2のノードに接続され、ゲート電極が上記第1のノードに接続され、ソース電極が低電圧信号端に接続される第6のT F Tと、

50

ゲート電極及びドレイン電極が第2のクロック信号の入力端とともに接続され、ソース電極が上記第5のTFTのゲート電極に接続される第7のTFTと、

ドレイン電極が上記第7のTFTのソース電極に接続され、ゲート電極が上記第1のノードに接続され、ソース電極が低電圧信号端に接続される第8のTFTと、

ドレイン電極が上記第1のノードに接続され、ゲート電極が上記第2のノードに接続され、ソース電極が低電圧信号端に接続される第9のTFTと、

ドレイン電極が上記出力端に接続され、ゲート電極が上記第2のノードに接続され、ソース電極が低電圧信号端に接続される第10のTFTと、を備える。

#### 【0013】

ゲートドライバ集積回路は、奇数行目のゲートライン信号を制御する場合、第1のクロック信号の入力端XがCLKのような第1のクロック信号線に接続され、第2のクロック信号の入力端YがCLKBのような第2のクロック信号線に接続され、偶数行目のゲートライン信号を制御する場合、第2のクロック信号の入力端Yが第1のクロック信号線に接続され、第1のクロック信号の入力端Xが第2のクロック信号線に接続されることが好ましい。10

#### 【0014】

上記複数のゲートドライバ集積回路をカスケードして、双方向走査を行える。それは以下の状況を含む。

#### 【0015】

(1) 順方向走査、即ち、第1の行から最後の行へ走査し、且つ該ゲートドライバ集積回路が奇数行目のゲートライン信号を制御する。20

順方向走査をスタートする場合、VDDがコンスタントな高レベルを提供し、VSSがコンスタントな低レベルを提供し、ゲートドライバ集積回路の入力端に高レベルのパルス信号を入力し、第1のTFTのドレイン電極で第1のノードに充電し、第1のクロック信号の入力端が第1のクロック信号線に提供される高レベルのクロック信号を受信し、上記第3のTFTは高レベルを出力するように上記出力端を制御し、上記第6のTFTは導通され、上記第2のノードの電圧を低電圧信号端の電圧までプルダウンし、上記第2のTFTのゲート電極が接続する上記リセット端は高レベルであって、上記第1のノードを放電し、第2のクロック信号の入力端が第2のクロック信号線に提供される高レベルのクロック信号を受信し、上記第4のTFTで上記出力端を放電し、上記第5のTFTで上記第2のノードに充電し、上記第1のノードを放電するように第9のTFTを制御し、出力端を放電するように上記第10のTFTを制御する。30

#### 【0016】

(2) 順方向走査、即ち、第1の行から最後の行まで走査し、且つ該ゲートドライバ集積回路が偶数行目のゲートライン信号を制御する。

順方向走査をスタートする場合、VDDがコンスタントな高レベルを提供し、VSSがコンスタントな低レベルを提供し、ゲートドライバ集積回路の入力端に高レベルのパルス信号を入力し、上記第1のTFTのドレイン電極で上記第1のノードに充電し、第1のクロック信号の入力端が第2のクロック信号線に提供される高レベルのクロック信号を受信し、上記第3のTFTによって高レベルを出力するように上記出力端を制御し、上記第6のTFTを導通し、上記第2のノードの電圧を低電圧信号端の電圧までプルダウンし、上記第2のTFTゲート電極に接続される上記リセット端が高レベルであって、上記第1のノードを放電し、第2のクロック信号の入力端が第1のクロック信号線に提供される高レベルのクロック信号を受信し、上記第4のTFTで上記出力端を放電し、上記第5のTFTで上記第2のノードに充電し、上記第1のノードを放電するように第9のTFTを制御し、出力端を放電するように上記第10のTFTを制御する。40

#### 【0017】

(3) 逆方向走査、即ち、最後の行から第1の行に走査し、該ゲートドライバ集積回路が奇数行目のゲートライン信号を制御する。

逆方向走査をスタートするとき、VDDがコンスタントな低レベルを提供し、VSSが50

コンスタントな高レベルを提供し、ゲートドライバ集積回路のリセット端に高レベルのパルス信号を入力し、上記第2のTFTのソース電極で上記第1のノードに充電し、第1のクロック信号の入力端が第1のクロック信号線に提供される高レベルのクロック信号を受信し、上記第3のTFTによって高レベルを出力するように上記出力端を制御し、上記第6のTFTを導通し、上記第2のノードの電圧を低電圧信号端の電圧までプルダウンし、上記第1のTFTのゲート電極に接続される上記入力端が高レベルであって、上記第1のノードを放電し、第2のクロック信号の入力端が第2のクロック信号線に提供される高レベルのクロック信号を受信し、上記第4のTFTで上記出力端を放電し、上記第5のTFTで上記第2のノードに充電し、上記第1のノードを放電するように第9のTFTを制御し、出力端を放電するように上記第10のTFTを制御する。

10

#### 【0018】

(4) 逆方向走査、即ち、最後の行から第1の行に走査し、該ゲートドライバ集積回路が偶数行目のゲートライン信号制御する。

逆方向走査をスタートするとき、VDDがコンスタントな低レベルを提供し、VSSがコンスタントな高レベルを提供し、ゲートドライバ集積回路のリセット端に高レベルのパルス信号を入力し、上記第2のTFTのソース電極で上記第1のノードに充電し、第1のクロック信号の入力端が第2のクロック信号線に提供される高レベルのクロック信号を受信し、上記第3のTFTによって高レベルを出力するように上記出力端を制御し、上記第6のTFTを導通し、上記第2のノードの電圧を低電圧信号端の電圧までプルダウンし、上記第1のTFTゲート電極に接続される上記入力端が高レベルであり、上記第1のノードを放電し、第2のクロック信号の入力端が第1のクロック信号線に提供される高レベルのクロック信号を受信し、上記第4のTFTによって上記出力端を放電し、上記第5のTFTによって上記第2のノードに充電し、上記第1のノードを放電するように第9のTFTを制御し、出力端を放電するように上記第10のTFTを制御する。

20

#### 【0019】

上記低電圧信号端は、コンスタントな低レベルを当該ゲートドライバ集積回路に提供することが好ましい。

#### 【0020】

上記から分かるように、本発明に係るゲートドライバ集積回路は、ゲートドライバ集積回路における入力端およびリセット端の機能を対称にして設計することによって、ゲートドライバ集積回路が双方向走査することができるようになり、かつノードの充放電特性が変更されなく、回路の信頼性及び安定性が向上される。

30

#### 【0021】

同じ構想に基づき、本発明の実施例は複数の上記ゲートドライバ集積回路を有するシフトレジスタであって、各ゲートドライバ集積回路が対応する行のゲートライン信号を制御する。図3に示すように、第N行のゲートライン信号を制御するゲートドライバ集積回路は、入力端が第N-1行のゲートライン信号を制御するゲートドライバ集積回路の出力端に接続され、出力端が第N+1行のゲートライン信号を制御するゲートドライバ集積回路の入力端に接続され、リセット端が第N+1行のゲートライン信号を制御するゲートドライバ集積回路の出力端に接続され、Nが2以上である。奇数行目のゲートライン信号を制御するゲートドライバ集積回路は、第1のクロック信号の入力端XがCLKのような第1のクロック信号線に接続され、第2のクロック信号の入力端YがCLKBのような第2のクロック信号線に接続され、偶数行目のゲートライン信号を制御するゲートドライバ集積回路は、第2のクロック信号の入力端Yが第1のクロック信号線に接続され、第1のクロック信号の入力端Xが第2のクロック信号線に接続される。

40

#### 【0022】

以下、具体的な実施例によって、10T1Cを例として、本発明に係るシフトレジスタにおけるゲートドライバ集積回路を詳しく説明する。図4に示すように、第1の薄膜トランジスタTFTM1は、ゲート電極が該ゲートドライバ集積回路の入力端INPUTに接続され、ドレイン電極が電源電圧VDDに接続され、ソース電極がプルアップノードと

50

しての第 1 のノード P U に接続され、第 2 の T F T M 2 は、ゲート電極が該ゲートドライバ集積回路のリセット端 R E S E T に接続され、ソース電極が共通接続電圧 V S S に接続され、ドレイン電極が第 1 のノード P U に接続され、第 3 の T F T M 3 は、ゲート電極が第 1 のノード P U に接続され、ドレイン電極が第 1 のクロック信号の入力端 X に接続され、ソース電極が出力端 O U T P U T に接続され、第 4 の T F T M 4 は、ゲート電極が第 2 のクロック信号の入力端 Y に接続され、ドレイン電極が出力端 O U T P U T に接続され、ソース電極が低電圧信号端 V G L に接続され、電気容量 C 1 は、第 1 のノード P U と出力端 O U T P U Tとの間に接続され、第 5 の T F T は、ドレイン電極が第 2 のクロック信号の入力端 Y に接続され、ソース電極がプルダウンノードとしての第 2 のノード P D に接続され、第 6 の T F T M 6 は、ドレイン電極が第 2 のノード P D に接続され、ゲート電極が第 1 のノード P U に接続され、ソース電極が低電圧信号端 V G L に接続され、第 7 の T F T M 7 は、ゲート電極及びドレイン電極が第 2 のクロック信号の入力端 Y とともに接続され、ソース電極が第 5 の T F T M 5 のゲート電極に接続され、第 8 の T F T M 8 は、ドレイン電極が第 7 の T F T M 7 のソース電極に接続され、ゲート電極が第 1 のノード P U に接続され、ソース電極が低電圧信号端 V G L に接続され、第 9 の T F T M 9 は、ドレイン電極が第 1 のノード P U に接続され、ゲート電極が第 2 のノード P D に接続され、ソース電極が低電圧信号端 V G L に接続され、第 10 の T F T M 10 は、ドレイン電極が出力端 O U T P U T に接続され、ゲート電極が第 2 のノード P D に接続され、ソース電極が低電圧信号端 V G L に接続され。それにおいて、T F T M 3 のドレイン電極が第 1 のクロック信号の入力端 X であり、T F T M 5 のドレイン電極が第 2 のクロック信号の入力端 Y である。この行が奇数行目であるとき、第 1 のクロック信号の入力端 X が第 1 のクロック信号線 C L K に接続され、第 2 のクロック信号の入力端 Y が第 2 のクロック信号線 C L K B に接続される。この行が偶数行目であるとき、第 1 のクロック信号の入力端 X が第 2 のクロック信号線 C L K B に接続され、第 2 のクロック信号の入力端 Y が第 1 のクロック信号線 C L K に接続される。10

20

#### 【 0 0 2 3 】

図 5 は、順方向走査時に奇数行目のゲートライン信号を制御するゲートドライバ集積回路の各入力信号エンドの電圧のシーケンス図である。図に示すように、順方向走査（第 1 の行から最後の行へ）するととき、V D D がコンスタントな高電圧を提供し、V S S がコンスタントな低電圧を提供し、入力端 I N P U T に高レベルのパルス信号を入力し、M 1 を導通させ、電圧制御バスバーの P U ノードに充電し、そして、第 1 のクロック信号の入力端 X が第 1 のクロック信号線 C L K に提供される高レベルクのロック信号を入力し、M 3 を導通させ、高レベルを出力するように出力端 O U T P U T を制御するとともに、電気容量 C 1 に蓄積される電荷が P U ノードへ移動し、P U ノードの電圧をさらに向上する。それとともに、P U ノード電圧が上昇して M 6 を導通させ、第 2 のノード P D の電圧を低電圧信号端 V G L の電圧までプルダウンする。そして、リセット端 R E S E T が高レベルであり、M 2 を導通させ、P U ノードを放電するとともに、第 2 のクロック信号の入力端 Y が第 2 のクロック信号線 C L K B に提供される高レベルのクロック信号を入力し、M 4 を導通させ、出力端 O U T P U T を放電し、さらに、M 5 を導通させ、P D ノードに充電し、P U ノードを放電するよう P D ノードに対応するプルダウン M 9 を制御し、出力端 O U T P U T を放電するよう P D ノードに対応するプルダウン T F T M 10 を制御する。30

40

#### 【 0 0 2 4 】

図 6 は、順方向走査時に、偶数行目のゲートライン信号を制御するゲートドライバ集積回路の各エンドの電圧のシーケンス図である。この図に示すように、順方向走査（第 1 の行から最後の行）時に、V D D がコンスタントな高電圧を提供し、V S S がコンスタントな低電圧を提供し、入力端 I N P U T に高レベルのパルス信号を入力し、M 1 を導通させ、P U ノードに充電し、そして、第 1 のクロック信号の入力端 X に第 2 のクロック信号線 C L K B に提供される高レベルのクロック信号を入力し、M 3 を導通させ、このとき、出力端 O U T P U T が高レベルを出力するとともに、電気容量 C 1 に蓄積する電荷が P U ノードへ移動し、P U ノードの電圧をさらに向上する。50

ードに移動し、P U ノードの電圧をさらに向上する。それとともに、P U ノードの電圧がM 6 を導通させるまで上昇し、第2 のノードP D の電圧を低電圧信号端V G L の電圧までプルダウンする。そして、リセット端R E S E T が高レベルであり、M 2 を導通させ、P U ノードを放電するとともに、第2 のクロック信号の入力端Y に第1 のクロック信号線C L K に提供される高レベルのクロック信号を入力し、M 4 を導通させ、出力端O U T P U T を放電し、さらに、M 5 を導通させ、P D ノードに充電し、P U ノードを放電するよう にP D ノードに対応するプルダウンT F T M 9 を制御し、出力端O U T P U T を放電するよう にP D ノードに対応するプルダウンM 1 0 を制御する。

#### 【 0 0 2 5 】

図7は、逆方向走査時に奇数行目のゲートライン信号を制御するゲートドライバ集積回路の各入力信号エンドの電圧のシーケンス図である。この図に示すように、逆方向走査(最後の行から第1の行)時に、V D D がコンスタントな低電圧を提供し、V S S がコンスタントな高電圧を提供し、リセット端R E S E T に高レベルのパルス信号を入力し、M 2 を導通させ、P U ノードに充電し、そして、第1のクロック信号の入力端X が第1のクロック信号線C L K に提供される高レベルのクロック信号を入力し、M 3 を導通させ、このとき、出力端O U T P U T が高レベルを出力するとともに、電気容量C 1 に蓄積する電荷がP U ノードに移動し、P U ノードの電圧をさらに向上する。それとともに、P U ノード電圧がM 6 を導通させるまで上昇し、第2のノードP D の電圧を低電圧信号端V G L の電圧までプルダウンする。そして、入力端I N P U T が高レベルであり、M 1 を導通させ、P U ノードを放電するとともに、第2のクロック信号の入力端Y が第2のクロック信号線C L K B に提供される高レベルのクロック信号を入力し、M 4 を導通させ、出力端O U T P U T を放電し、さらに、M 5 を導通し、P D ノードに充電し、P U ノードを放電するよう にP D ノードに対応するプルダウンM 9 を制御し、出力端O U T P U T を放電するよう にP D ノードに対応するM 1 0 を制御する。

#### 【 0 0 2 6 】

図8は、逆方向走査時に偶数行目のゲートライン信号を制御するゲートドライバ集積回路の各入力信号エンドの電圧のシーケンス図である。この図に示すように、逆方向走査(最後の行から第1の行)時に、V D D がコンスタントな低電圧を提供し、V S S がコンスタントな高電圧を提供し、リセット端R E S E T に高レベルのパルス信号を入力し、M 2 を導通させ、P U ノードに充電し、そして、第1のクロック信号の入力端X が第2のクロック信号線C L K B に提供される高レベルのクロック信号が入力し、M 3 を導通させ、このとき、出力端O U T P U T が高レベルを出力するとともに、電気容量C 1 に蓄積する電荷がP U ノードに移動し、P U ノードの電圧をさらに向上する。それとともに、P U ノード電圧がM 6 を導通させるまで上昇し、第2のノードP D の電圧を低電圧信号端V G L の電圧までプルダウンする。そして、入力端I N P U T が高レベルであり、M 1 を導通させ、P U ノードを放電するとともに、第2のクロック信号の入力端Y が第1のクロック信号線C L K に提供される高レベルのクロック信号を入力し、M 4 を導通させ、出力端O U T P U T を放電し、さらに、M 5 を導通させ、P D ノードに充電し、P U ノードを放電するよう にP D ノードに対応するM 9 を制御し、出力端O U T P U T を放電するよう にP D ノードに対応するM 1 0 を制御する。

#### 【 0 0 2 7 】

上記から分かるように、本発明に係るゲートドライバ集積回路は、ゲートドライバ集積回路における入力端およびリセット端の機能を対称にして設計することによって、ゲートドライバ集積回路が双方向走査することができるようになり、ノードの充放電特性が変更されなく、回路の信頼性及び安定性が確保される。

#### 【 0 0 2 8 】

同じ構想に基づき、本発明の実施例はディスプレイスクリーンであって、上記シフトレジスタ及びアレイ基板を備え、上記シフトレジスタの各ゲートドライバ集積回路の信号出力端は、上記アレイ基板の、該ゲートドライバ集積回路に制御されるゲートライン信号のゲートラインに接続される。

10

20

30

40

50

## 【0029】

上記から分かるように、本発明に係るゲートドライバ集積回路、シフトレジスタ及びディスプレイスクリーンは、ゲートドライバ集積回路における入力端およびリセット端の機能を対称にして設計することによって、ゲートドライバ集積回路が双方向走査することができるようになり、ノードの充放電特性が変更されなく、回路の信頼性及び安定性が確保される。

## 【0030】

本発明の精神と範囲から逸脱しない範囲で本発明を修正する、または変更することができる。本発明に対する修正または変更は、本発明の特許請求の範囲及びそれに均等する範囲内であれば、本発明はこれらの修正または変更を含む。

10

【図1】

图1

【図2】

【図3】

【図4】

图4

【図5】

图 5

【図6】

图 6

【図7】

图 7

【図8】

图 8

---

フロントページの続き

審査官 橋本 直明

(56)参考文献 特開2009-086620(JP,A)

米国特許出願公開第2008/0012818(US,A1)

特開2009-092982(JP,A)

特開2011-060411(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3 / 36

G02F 1 / 133

G09G 3 / 20

|                |                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 栅极驱动器集成电路，移位寄存器和显示屏                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP6227530B2</a>                                                          | 公开(公告)日 | 2017-11-08 |

| 申请号            | JP2014526374                                                                         | 申请日     | 2012-08-21 |

| [标]申请(专利权)人(译) | 北京京东方光电科技有限公司                                                                        |         |            |

| 申请(专利权)人(译)    | 北京京东方光电科技有限公司                                                                        |         |            |

| 当前申请(专利权)人(译)  | 北京京东方光电科技有限公司                                                                        |         |            |

| [标]发明人         | 陳希                                                                                   |         |            |

| 发明人            | ▲陳▼ 希                                                                                |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                          |         |            |

| CPC分类号         | G09G3/3674 G09G2300/0408 G09G2310/0283 G09G2310/0286 G09G2310/08 G11C19/28 H03K5/153 |         |            |

| FI分类号          | G09G3/36 G09G3/20.622.E G09G3/20.622.B G09G3/20.622.R G02F1/133.550                  |         |            |

| 代理人(译)         | 村山彥<br>渡邊 隆                                                                          |         |            |

| 审查员(译)         | Naoaki桥本                                                                             |         |            |

| 优先权            | 201110241400.8 2011-08-22 CN                                                         |         |            |

| 其他公开文献         | JP2014524598A                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                            |         |            |

## 摘要(译)

本发明涉及液晶显示器领域，尤其涉及栅极驱动器集成电路，移位寄存器和显示屏。集成电路栅极驱动器包括：第一薄膜晶体管TFT，第二TFT，第三TFT，第四TFT，包括一电容，和一个下拉模块，下拉模块下拉模块，第一时钟信号，第二时钟信号输入端的输入端，和连接在输出端之间的第一个节点，以及连接到低电平信号端，栅极驱动器集成电路不操作并且在该时段内将第一节点和输出终端维持在低水平。由输入端的对称来实现功能和栅极驱动器集成电路的复位端子，栅极驱动器集成电路将能够双向扫描，而不是被改变的节点的充放电特性，的电路可靠性和稳定性得到保证。

| (19)日本国特許庁(JP)                                                                                         | (12)特許公報(B2)                                                                                | (11)特許番号<br>特許第6227530号<br>(P6227530) |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------|

| (45)発行日 平成29年11月8日(2017.11.8)                                                                          |                                                                                             | (24)登録日 平成29年10月20日(2017.10.20)       |

| (51)Int.Cl.<br><b>G09G 3/36 (2006.01)</b><br><b>G09G 3/20 (2006.01)</b><br><b>G02F 1/133 (2006.01)</b> | F I<br>G09G 3/36<br>G09G 3/20 622 E<br>G09G 3/20 622 B<br>G09G 3/20 622 R<br>G02F 1/133 550 |                                       |

| (21)出願番号 特願2014-526374 (P2014-526374)                                                                  | (73)特許権者 507134301<br>北京京東方光電科技有限公司                                                         |                                       |

| (86)(22)出願日 平成24年8月21日(2012.8.21)                                                                      |                                                                                             | 中華人民共和国北京市朝陽區東三環中路8號                  |

| (65)公表番号 特表2014-524598 (P2014-524598A)                                                                 |                                                                                             |                                       |

| (43)公表日 平成26年9月22日(2014.9.22)                                                                          |                                                                                             |                                       |

| (66)国際出願番号 PCT/CN2012/080420                                                                           |                                                                                             |                                       |

| (87)国際公開日 平成25年2月28日(2013.2.28)                                                                        |                                                                                             |                                       |

| (77)審査請求日 平成27年7月13日(2015.7.13)                                                                        |                                                                                             |                                       |

| (31)優先権主張番号 201110241400.8                                                                             | (74)代理人 100108455<br>弁理士 村山 清彦                                                              |                                       |

| (32)優先日 平成23年8月22日(2011.8.22)                                                                          | (74)代理人 100089037<br>弁理士 渡邊 隆                                                               |                                       |

| (33)優先権主張国 中国(CN)                                                                                      | (74)代理人 100110364<br>弁理士 実広 信哉                                                              |                                       |

|                                                                                                        | (72)発明者 ▲陳▼ 希<br>中華人民共和国北京市朝陽區東三環中路8號                                                       |                                       |

(54)【発明の名称】ゲートドライバ兼横回路、シフトレジスタ及びディスプレイスクリーン

最終頁に続く