(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5667104号

(P5667104)

(45) 発行日 平成27年2月12日(2015.2.12)

(24) 登録日 平成26年12月19日(2014.12.19)

(51) Int.Cl.

F 1

**G02F 1/1345 (2006.01)**

**G02F 1/1368 (2006.01)**

**G02F 1/1339 (2006.01)**

**G09F 9/30 (2006.01)**

GO2 F 1/1345

GO2 F 1/1368

GO2 F 1/1339 505

GO9 F 9/30 330

GO9 F 9/30 309

請求項の数 16 (全 29 頁) 最終頁に続く

(21) 出願番号 特願2012-45457 (P2012-45457)

(22) 出願日 平成24年3月1日 (2012.3.1)

(62) 分割の表示 特願2005-179932 (P2005-179932)

の分割

原出願日 平成17年6月20日 (2005.6.20)

(65) 公開番号 特開2012-113321 (P2012-113321A)

(43) 公開日 平成24年6月14日 (2012.6.14)

審査請求日 平成24年3月1日 (2012.3.1)

(31) 優先権主張番号 10-2004-0058708

(32) 優先日 平成16年7月27日 (2004.7.27)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2004-0077500

(32) 優先日 平成16年9月24日 (2004.9.24)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 512187343

三星ディスプレイ株式會社

Samsung Display Co., Ltd.

大韓民国京畿道龍仁市器興区三星二路95

95, Samsung 2 Ro, Gih

eung-Gu, Yongin-City

, Gyeonggi-Do, Korea

(74) 代理人 110000671

八田國際特許業務法人

(72) 発明者 金 東 奎

大韓民国京畿道龍仁市豊徳川洞 三星5次

アパート523棟1305号

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ表示板、これを含む表示装置及び液晶表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート線、データ線、画素電極及び薄膜トランジスタが設けられている基板、及び前記基板上に設けられ、外部からの信号を受信する配線部と前記配線部からの信号に応答してゲート信号を前記ゲート線に出力する回路部とを備えるゲート駆動部、を含み、

前記配線部は、前記配線部に重畳する光硬化性の結合部材に光を透過させるための開口部が設けられている信号線を含み、

前記配線部は開口部が設けられていない信号線をさらに含み、

前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畳する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる薄膜トランジスタ表示板。

## 【請求項 2】

前記開口部が設けられている信号線の線幅は 100 μm 以上である、請求項 1 に記載の薄膜トランジスタ表示板。

## 【請求項 3】

前記信号線は、アルミニウムやアルミニウム合金、または銀や銀合金からなる第1導電膜と、クロムまたはモリブデンまたはチタニウムまたはタンタルからなる第2導電膜とを含む、請求項 1 または請求項 2 に記載の薄膜トランジスタ表示板。

## 【請求項 4】

10

20

前記信号線は、前記ゲート線または前記データ線と同一層で形成された、請求項1～3のいずれか一項に記載の薄膜トランジスタ表示板。

**【請求項5】**

前記回路部は、従属連結され順に出力信号を生成する複数のステージからなるシフトレジスタを備え、

前記開口部が設けられている信号線は、前記シフトレジスタに電源電圧と互いに異なる位相の第1クロック信号及び第2クロック信号を伝達する第1信号線乃至第3信号線を備えている、請求項1～4のいずれか一項に記載の薄膜トランジスタ表示板。

**【請求項6】**

前記開口部が設けられていない信号線は前記シフトレジスタに初期化信号を伝達する第4信号線を含む、請求項5に記載の薄膜トランジスタ表示板。 10

**【請求項7】**

前記第1乃至第4信号線は、前記シフトレジスタから遠い方から近い方へ順に配置されている、請求項6に記載の薄膜トランジスタ表示板。

**【請求項8】**

前記配線部は、前記第1乃至第4信号線のうちの少なくとも一つ及び前記シフトレジスタを連結する複数の連結線をさらに含む、請求項6または請求項7に記載の薄膜トランジスタ表示板。

**【請求項9】**

前記連結線は、前記信号線と異なる層で形成される、請求項8に記載の薄膜トランジスタ表示板。 20

**【請求項10】**

前記連結線及び前記信号線は、連結補助部材を通じて連結されている、請求項8または請求項9に記載の薄膜トランジスタ表示板。

**【請求項11】**

前記連結補助部材は、透明で、前記連結線及び前記信号線と複数の接触孔を通じて連結されている、請求項10に記載の薄膜トランジスタ表示板。

**【請求項12】**

前記トランジスタよりも小さい前記複数のトランジスタ間の間隔は100μm以下である、請求項1～11のいずれか一項に記載の薄膜トランジスタ表示板。 30

**【請求項13】**

複数のゲート線と複数のデータ線が設けられた第1基板と、前記第1基板と対向する第2基板、及び前記第1基板と前記第2基板との間に介在し前記第1及び第2基板を結合する光硬化性の結合部材からなり、データ信号及びゲート信号に応答して映像を表示する表示パネル。

前記複数のデータ線に前記データ信号を出力するデータ駆動部、及び前記第1基板上に設けられ、外部から複数の信号を受信する配線部及び前記外部信号に応答して前記ゲート信号を前記複数のゲート線に出力する回路部からなるゲート駆動部、を含み、

前記配線部は、前記結合部材と重畳し前記結合部材に光を透過させるための開口部が設けられている信号線を含み、 40

前記配線部は開口部が設けられていない信号線をさらに含み、

前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畳する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる表示装置。

**【請求項14】**

第1基板上に、重畳する光硬化性の結合部材に光を透過させるための開口部を備える信号線を含む配線部と、前記配線部からの信号によってゲート信号を生成する回路部を含むゲート駆動回路を形成する段階、

第2基板上に遮光膜を形成する段階、

50

前記第1または第2基板上に液晶を滴下する段階、

前記第1または第2基板上に密封材を塗布する段階、

前記第1基板と前記第2基板を整列する段階、及び

前記第1基板の開口部を通じて前記密封材に光を照射する段階、を含み、

前記配線部は開口部が設けられていない信号線をさらに含み、

前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畳する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる液晶表示装置の製造方法。

**【請求項15】**

10

ゲート線、データ線、画素電極及び薄膜トランジスタが設けられている基板、及び前記基板上に設けられ、外部からの信号を受信する配線部と前記配線部からの信号に応答してゲート信号を前記ゲート線に出力する回路部とを備えるゲート駆動部、を含み、

前記配線部は、開口部が設けられている信号線を含んでおり、前記開口部は一対の横辺と一対の縦辺で形成された四角形であり、前記横辺の長さと前記縦辺の長さが互いに異なり、

前記配線部は開口部が設けられていない信号線をさらに含み、

前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畳する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる薄膜トランジスタ表示板。

**【請求項16】**

20

前記開口部の前記縦辺は前記信号線の長さ方向に延びてあり、

前記開口部の前記縦辺の長さは前記開口部の前記横辺の長さより長い、請求項15に記載の薄膜トランジスタ表示板。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は薄膜トランジスタ表示板、これを含む表示装置及び液晶表示装置の製造方法に関する。

30

**【背景技術】**

**【0002】**

一般に、表示装置は、ゲート線、データ線、画素電極及び薄膜トランジスタが具備された薄膜トランジスタ表示板と、共通電極表示板を備える表示パネルと、ゲート線にゲート信号を出力するゲート駆動部、及びデータ線にデータ信号を出力するデータ駆動部で構成される。

**【0003】**

ゲート駆動部及びデータ駆動部は、チップ形態で表示パネルに実装されている。ところが近来、表示装置の小型化及び生産性の増大を実現するために、ゲート駆動部を表示パネルに内蔵する構造が開発されつつある。

40

**【0004】**

表示パネルを代表する液晶表示パネルの場合、ゲート線、データ線、画素電極及び薄膜トランジスタが具備された薄膜トランジスタ表示板と、薄膜トランジスタ表示板と対向する共通電極表示板と、薄膜トランジスタ表示板と共通電極表示板との間に介在された液晶層、及び薄膜トランジスタ表示板と共に共通電極表示板を結合する密封材からなる。

**【0005】**

ゲート駆動部が表示パネルの薄膜トランジスタ表示板に内蔵される構造では、ゲート駆動部と共に共通電極表示板に設けられた共通電極との間で寄生容量が発生し、この寄生容量はゲート駆動部の誤動作を誘発する。このため最近では、寄生容量を減少させるために密封材をゲート駆動部と共に共通電極との間に配置する構造が提示されている。

50

## 【0006】

一方、液晶表示パネルの大型化に伴い、薄膜トランジスタ表示板と共に電極表示板との間に液晶層を注入する方法として、液晶滴下方式の他に、薄膜トランジスタ表示板と共に電極表示板との間の整列の誤差を減らすため光硬化性密封材が一般に用いられている。光硬化性密封材は、光によって硬化し薄膜トランジスタ表示板と共に電極表示板を結合させる。この時、共通電極表示板には、ゲート駆動部が設けられた領域に対応し遮光層が形成されており、一般に光は、薄膜トランジスタ表示板の背面から入射される背面露光方式で照射される。

## 【0007】

しかし、下記特許文献1に示すように、密封材がゲート駆動部と共に電極との間に備わる構造において、密封材に光を提供し硬化させるとき、ゲート駆動部のため密封材に入射された光量が減少する。特に、高電流が流れる電源電圧配線のように、その線幅が100μmより大きくて照射された光の回折が弱い場合、該部分の密封材に照射される光量が減少して密封材の硬化が不完全状態となる。その結果、薄膜トランジスタ表示板と共に電極表示板の結合力が低下する。また、不完全な結合状態の密封材を通じて外部から湿気が流入し易くゲート駆動部の腐蝕が発生し、ゲート駆動部の誤動作が生じる。

10

## 【0008】

また、前記構造において、外部から流入する静電気によって信号線と連結線が短絡する現象が発生する場合、ゲート駆動部は深刻なダメージを受けることになる。更に、ゲート駆動部が集積されている構造では、ダメージの修理が不可能であるため、製品全体に対し致命的な不良を起こす。

20

## 【先行技術文献】

## 【特許文献】

## 【0009】

## 【特許文献1】特開平11-52394号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0010】

したがって、本発明の目的は、光硬化性結合部材を用いた共通電極表示板との結合が容易である薄膜トランジスタ表示板及びこれを含む表示装置を提供することである。また、容易に修理を行うこともできる薄膜トランジスタ表示板及びこれを含む表示装置を提供することである。

30

## 【課題を解決するための手段】

## 【0011】

本発明の一特徴による薄膜トランジスタ表示板は、ゲート線、データ線、画素電極及び薄膜トランジスタが設けられている基板、及び前記基板上に設けられ、外部からの信号を受信する配線部と前記配線部からの信号に応答してゲート信号を前記ゲート線に出力する回路部とを備えるゲート駆動部、を含み、前記配線部は、前記配線部に重畳する光硬化性の結合部材に光を透過させるための開口部が設けられている信号線を含み、前記配線部は開口部が設けられていない信号線をさらに含み、前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畳する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる。

40

## 【0012】

本発明の一特徴による表示装置は、複数のゲート線と複数のデータ線が設けられた第1基板と、前記第1基板と対向する第2基板、及び前記第1基板と前記第2基板との間に介在し前記第1及び第2基板を結合する光硬化性の結合部材からなり、データ信号及びゲート信号に応答して映像を表示する表示パネル、前記複数のデータ線に前記データ信号を出力するデータ駆動部、及び前記第1基板上に設けられ、外部から複数の信号を受信する配線部、及び前記外部信号に応答して前記ゲート信号を前記複数のゲート線に出力する回路

50

部からなるゲート駆動部、を含み、前記配線部は、前記結合部材と重畠し前記結合部材に光を透過させるための開口部が設けられている信号線を含み、前記配線部は開口部が設けられていない信号線をさらに含み、前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畠する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる。

#### 【0013】

本発明の一特徴による液晶表示装置の製造方法は、第1基板上に、重畠する光硬化性の結合部材に光を透過させるための開口部を備える信号線を含む配線部と、前記配線部からの信号によってゲート信号を生成する回路部を含むゲート駆動回路を形成する段階、第2基板上に遮光膜を形成する段階、前記第1または第2基板上に液晶を滴下する段階、前記第1または第2基板上に密封材を塗布する段階、前記第1基板と前記第2基板を整列する段階、及び前記第1基板の開口部を通じて前記密封材に光を照射する段階、を含み、前記配線部は開口部が設けられていない信号線をさらに含み、前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畠する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる。

#### 【0014】

本発明の一特徴による薄膜トランジスタ表示板は、ゲート線、データ線、画素電極及び薄膜トランジスタが設けられている基板、及び前記基板上に設けられ、外部からの信号を受信する配線部と前記配線部からの信号に応答してゲート信号を前記ゲート線に出力する回路部とを備えるゲート駆動部、を含み、前記配線部は、開口部が設けられている信号線を含んでおり、前記開口部は一対の横辺と一対の縦辺で形成された四角形であり、前記横辺の長さと前記縦辺の長さが互いに異なり、前記配線部は開口部が設けられていない信号線をさらに含み、前記回路部は、複数のトランジスタを備え、前記トランジスタのうちの少なくとも一つは、前記回路部に重畠する光硬化性の結合部材に光を透過させるための間隙が形成されるように互いに間隔を置いて設けられた、前記トランジスタよりも小さい複数の小さいトランジスタからなる。

#### 【発明の効果】

#### 【0015】

本発明によれば、光硬化性物質を含む密封材がゲート駆動部の一部分をカバーするよう第1基板と第2基板との間に介在する構造において、ゲート駆動部の信号配線には密封材を硬化するため、第1基板の背面を通じて入射された光を透過する開口部が設けられ、密封材によって第1及び第2基板間の結合力が向上される。その結果、外部から流入する湿気による腐蝕不良などを改善することができる。更に、容易に修理を行うこともできる。

#### 【図面の簡単な説明】

#### 【0016】

【図1】本発明の一実施形態による表示装置の平面図である。

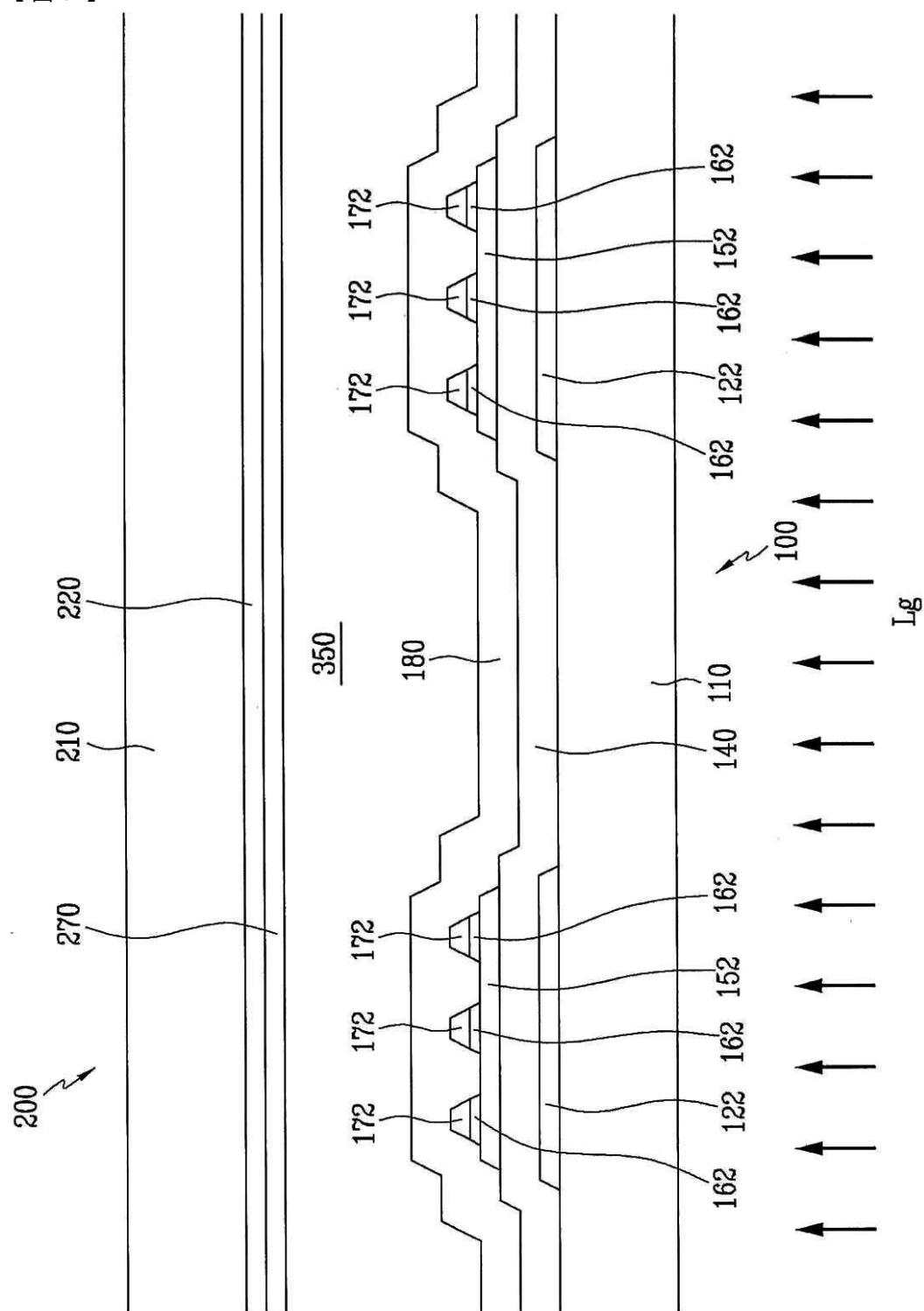

【図2】図1に示した表示装置のI—I'I'線による断面図である。

【図3】図1に示したゲート駆動部として用いられるシフトレジスタブロック図の一例である。

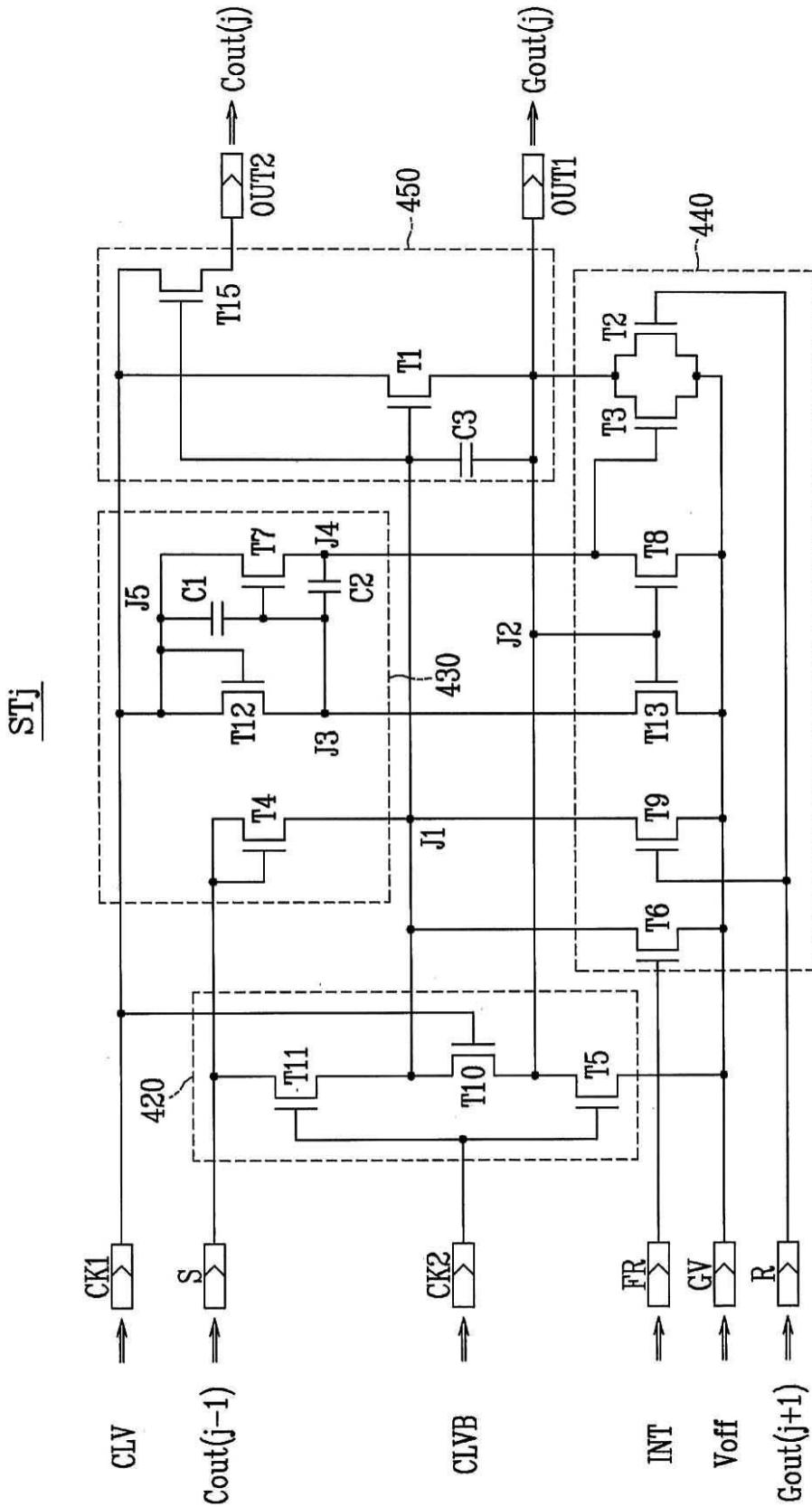

【図4】図3に示したシフトレジスタのステージの回路図の一例である。

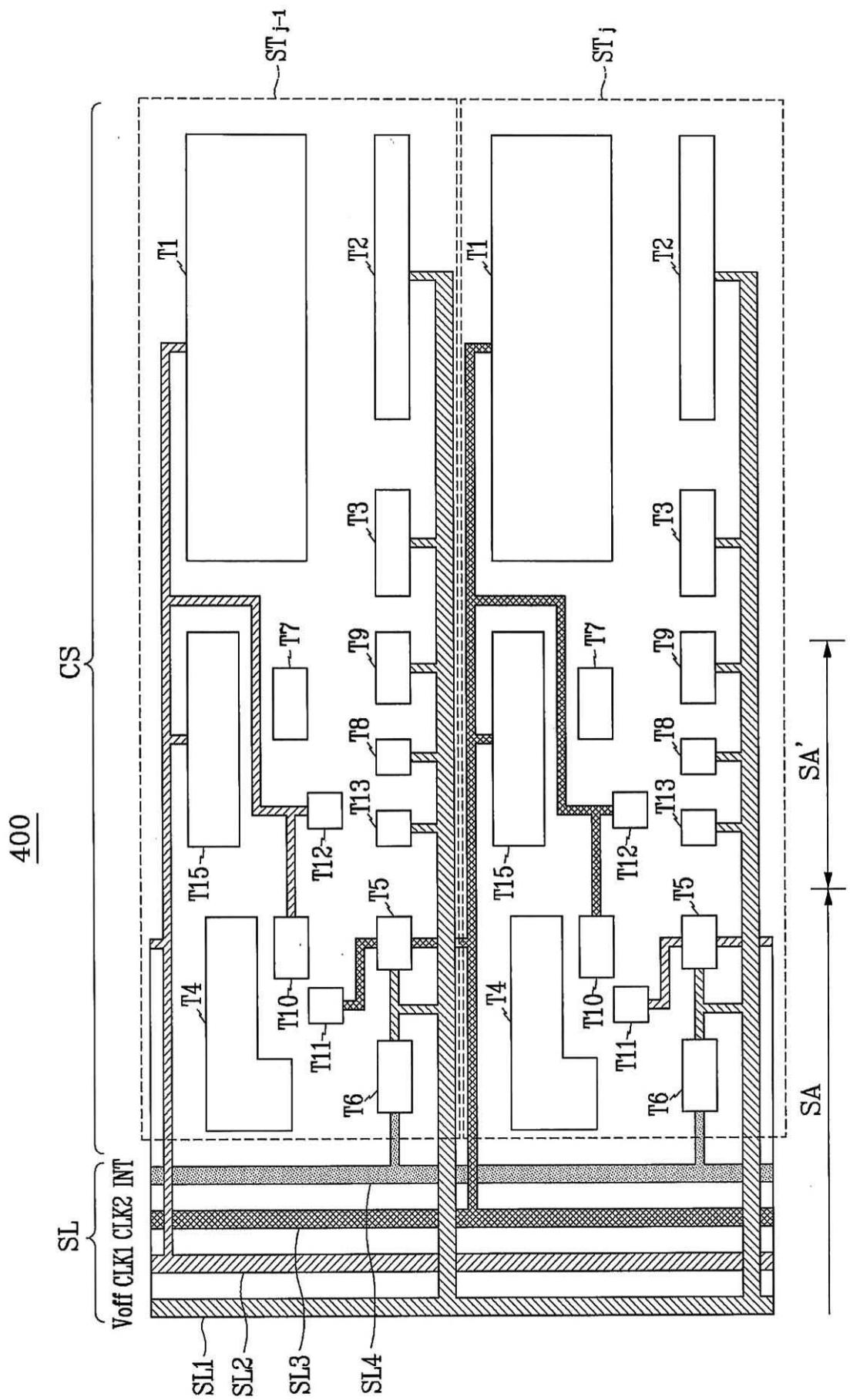

【図5】本発明の一実施形態によるゲート駆動部の概略的な配置図である。

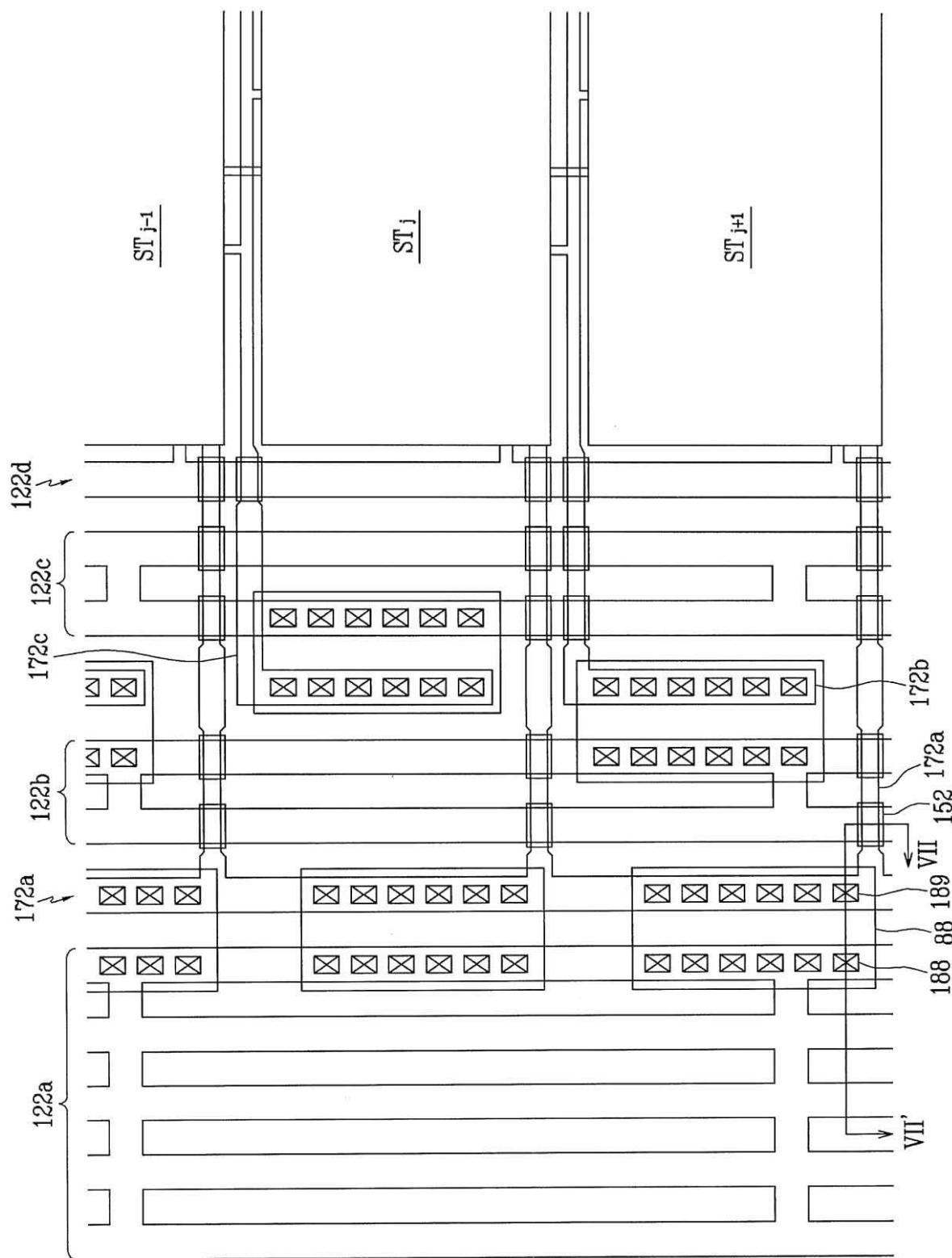

【図6】図5に示したゲート駆動部の配線部の配置図の一例である。

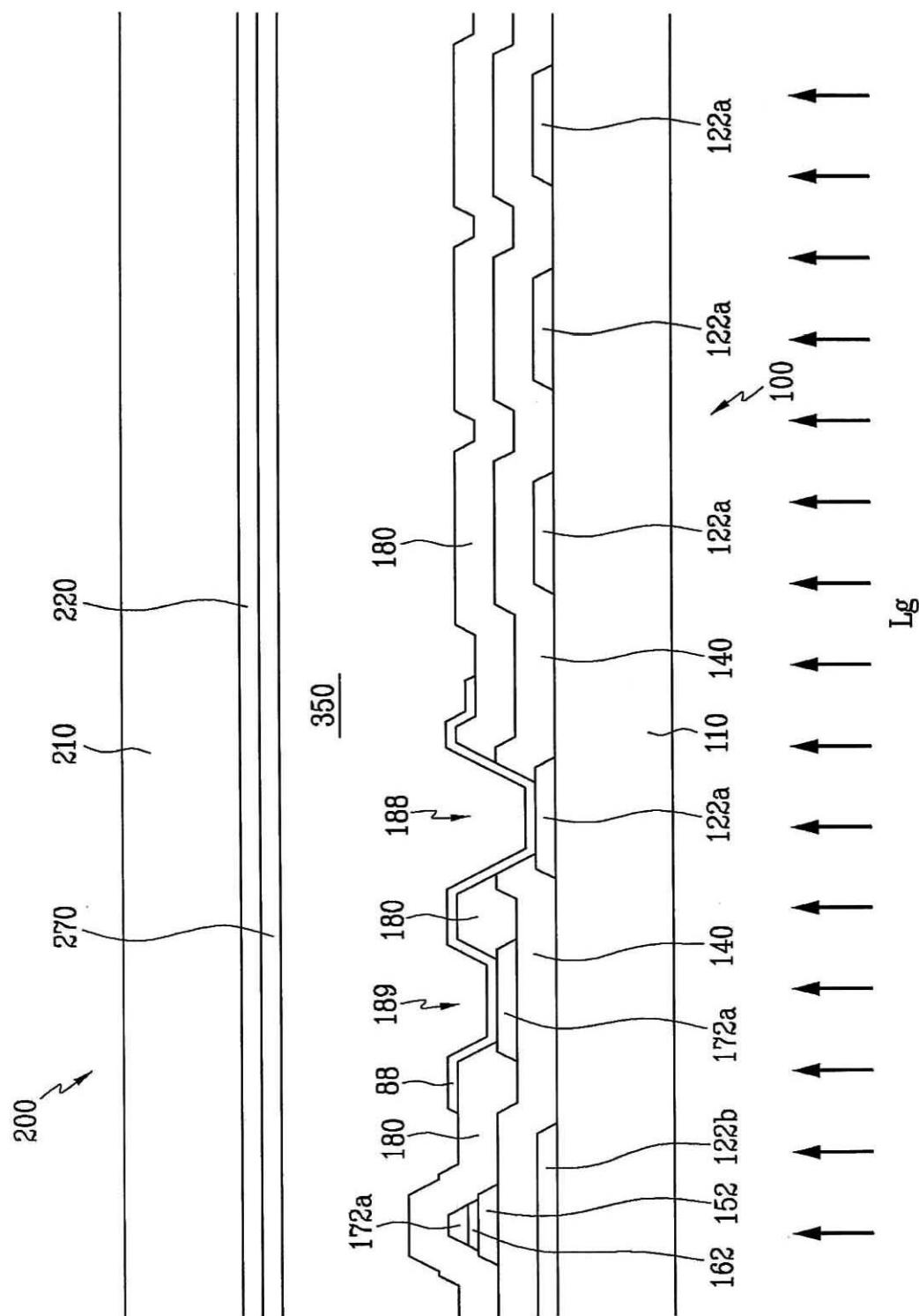

【図7】図6に示した配線部のVII-VII'線による断面図である。

【図8】図5に示したゲート駆動部の回路部の一部の配置図の一例である。

【図9】図8に示した配線部のIX-IX'線による断面図である。

【図10】表示領域DAの画素の配置図である。

【図11】図10に示した画素のXI-XI'線による断面図である。

【図12】図6に示した配置図において修理された状態の一例を示すものである。

10

20

30

40

50

**【発明を実施するための形態】**

**【0017】**

以下、添付した図面を参照して、本発明の実施形態に対して、本発明が属する技術分野における通常の知識を有する者が容易に実施することができるよう詳細に説明する。

**【0018】**

図面は、各種層及び領域を明確に表現するために、厚さを拡大して示している。明細書全体を通じて類似した部分については同一な図面符号を付けている。層、膜、領域、板などの部分が、他の部分の“上に”あるとする時、これは他の部分の“すぐ上に”ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上に”あるとする時、これは中間に他の部分がない場合を意味する。

10

**【0019】**

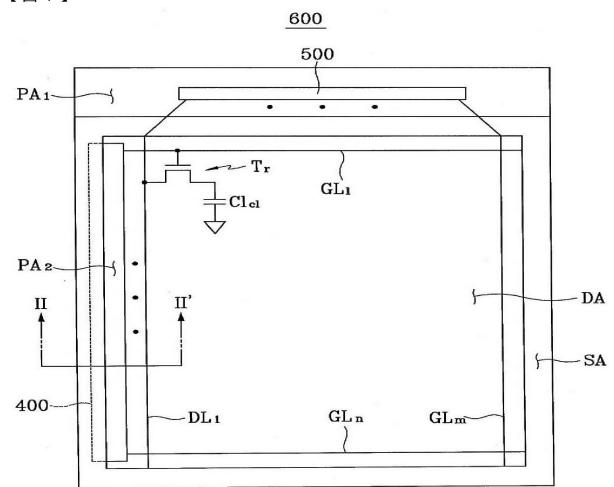

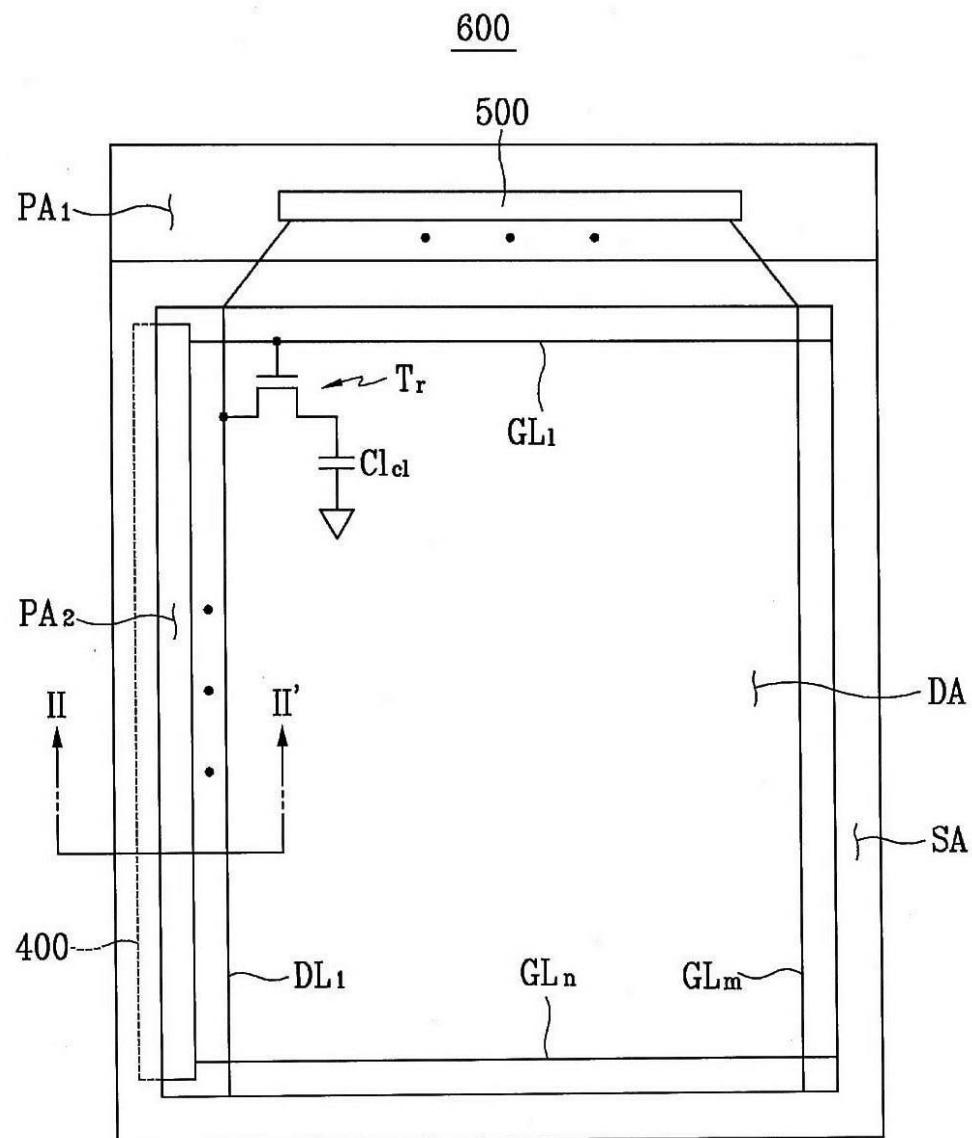

図1は、本発明の一実施形態による表示装置の平面図であり、図2は、図1に示した表示装置のI I - I I'線による断面図である。

**【0020】**

図1及び図2を参照すれば、本発明の一実施形態による表示装置600は、データ信号及びゲート信号に応答して映像を表示する表示パネル300、表示パネル300に具備され表示パネル300にデータ信号及びゲート信号をそれぞれ出力するデータ駆動部500及びゲート駆動部400を含む。

**【0021】**

表示パネル300は、薄膜トランジスタ表示板100、薄膜トランジスタ表示板100と対向する共通電極表示板200、薄膜トランジスタ表示板100と共に通電極表示板200との間に介在する液晶層330及び密封材350を含む。

20

**【0022】**

表示パネル300は、映像を表示する表示領域DA、表示領域DAを囲むシールライン(seal line)領域SA、シールライン領域SAの外側に位置する第1周辺領域PA1、及び表示領域DAとシールライン領域SAの一部との間に設けられた第2周辺領域PA2に区画することができる。共通電極表示板200は、シールライン領域SA及びその内側に位置しており、薄膜トランジスタ表示板100は、シールライン領域SAの外側に第1周辺領域PA1まで延長されている。

30

**【0023】**

表示パネル300は、等価回路によれば、複数のゲート線GL<sub>1</sub>～GL<sub>n</sub>と複数のデータ線DL<sub>1</sub>～DL<sub>m</sub>、及びこれと接続されている複数の画素を含む。

**【0024】**

ゲート線GL<sub>1</sub>～GL<sub>n</sub>及びデータ線DL<sub>1</sub>～DL<sub>m</sub>は、薄膜トランジスタ表示板100の基板110上に形成されている。ゲート線GL<sub>1</sub>～GL<sub>n</sub>及びデータ線DL<sub>1</sub>～DL<sub>m</sub>は、表示領域DAで互いに絶縁されて交差し、各々第2及び第1周辺領域PA2、PA1まで延長されてゲート駆動部400及びデータ駆動部500に接続される。

**【0025】**

各画素は、表示領域DAに位置し、ゲート線GL<sub>1</sub>～GL<sub>n</sub>及びデータ線DL<sub>1</sub>～DL<sub>m</sub>に接続されている薄膜トランジスタTrと、これに接続されている液晶キャパシタC1cとを含む。

40

**【0026】**

薄膜トランジスタTrは、薄膜トランジスタ表示板100に形成され、ゲート線GL<sub>1</sub>～GL<sub>n</sub>に接続されている制御端子、データ線DL<sub>1</sub>～DL<sub>m</sub>に接続されている入力端子、及び液晶キャパシタC1cに接続されている出力端子を備える。薄膜トランジスタTrは、非晶質シリコンを含むのが好ましいが、多結晶シリコンを含むこともできる。

**【0027】**

液晶キャパシタC1cは、薄膜トランジスタ表示板100に形成されている画素電極(図示せず)と、共通電極表示板200の基板210上に形成されている共通電極270、及びこれらの間の液晶層330を備えてなる。画素電極は薄膜トランジスタTrに接続さ

50

れており、共通電極 270 は共通電極表示板 200 の全面に形成され共通電圧の印加を受ける。

**【0028】**

第1周辺領域 PA1 の薄膜トランジスタ表示板 100 上には、チップ形態のデータ駆動部 500 が装着されている。データ駆動部 500 は、データ線 DL<sub>1</sub> ~ DL<sub>m</sub> と電気的に接続されデータ信号を印加する。

**【0029】**

一方、第2周辺領域 PA2 に隣接するシールライン領域 SA 及び第2周辺領域 PA2 上の薄膜トランジスタ表示板 100 には、ゲート駆動部 400 が設けられている。ゲート駆動部 400 は、ゲート線 GL<sub>1</sub> ~ GL<sub>n</sub> と電気的に接続されゲート信号を印加する。

10

**【0030】**

密封材 350 は、シールライン領域 SA に位置しており、薄膜トランジスタ表示板 100 と共に共通電極表示板 200 を結合し、液晶層 330 の液晶を封じ込める役割を果たす。密封材 350 は光硬化性物質を含む。

**【0031】**

密封材 350 は、シールライン領域 SA に位置したゲート駆動部 400 の一部分と重畳している。液晶層 330 の誘電定数が約 10 以上であるのに対し、密封材 350 の誘電定数は約 4.0 以下であるため、このようにすれば、共通電極表示板 200 の共通電極 270 とゲート駆動部 400 との間で発生する寄生容量を低減させることができる。

20

**【0032】**

図 2 のように、共通電極表示板 200 にはまた、シールライン領域 SA 及び第2周辺領域 PA2 に位置する遮光層 220 が設けられている。共通電極表示板 200 の第2基板 210 と共に共通電極 270 との間にカラーフィルタ層（図示せず）が具備できるが、カラーフィルタ層は三原色、例えば赤色、緑色及び青色を表示する。ところが、カラーフィルタ層は、薄膜トランジスタ表示板 100 に備えられるか、場合によっては省略することもできる。

**【0033】**

前記液晶表示装置において液晶層 330 は、滴下方式によって二つの表示板 100、200 の間に密封材 350 で密封されており、滴下方式に関しては、液晶層 330 は、二つの表示板 100、200 を密封材 350 で結合する前に共通電極表示板 200 または薄膜トランジスタ表示板 100 の上に液晶を滴下した後、二つの表示板 100、200 を整列し密封材 350 に光を照射して硬化させる。ところが、共通電極表示板 200 には遮光層 220 が存在し光を遮断するため、密封材 350 を硬化させる際には、薄膜トランジスタ表示板 100 の背面から光を入射する。

30

**【0034】**

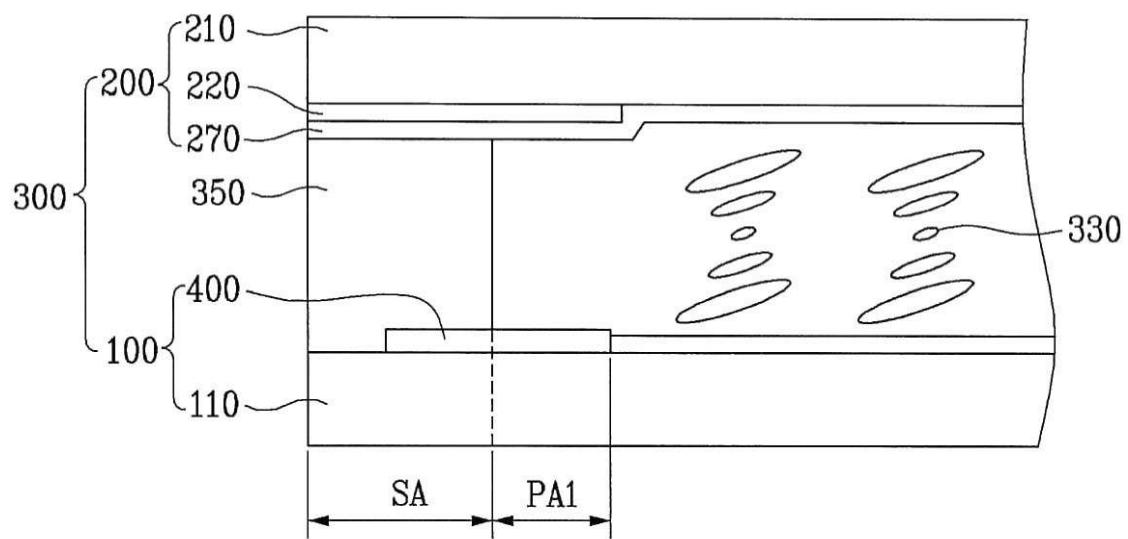

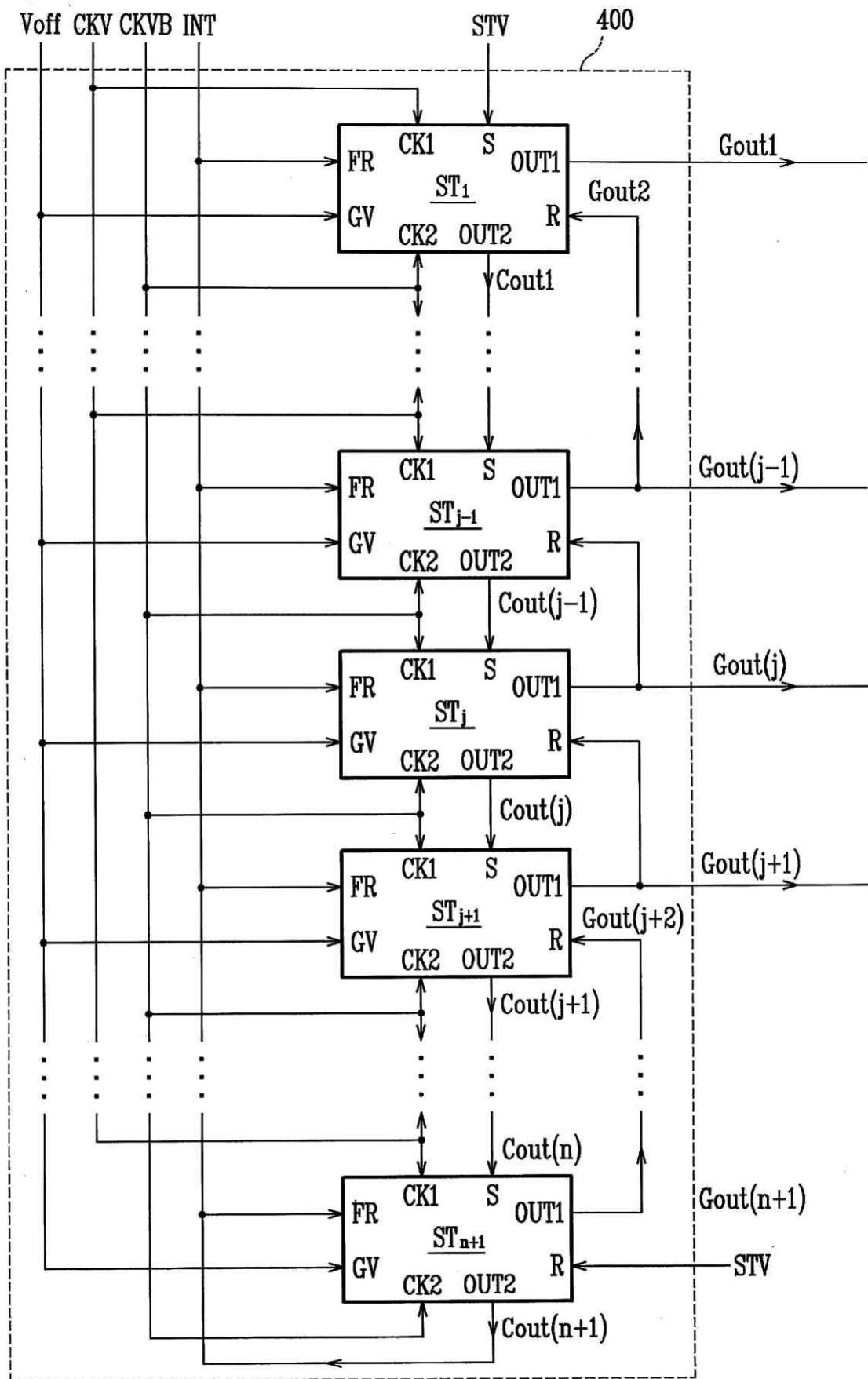

図 3 は、図 1 に示したゲート駆動部のブロック図の例であり、図 4 は、図 3 に示したゲート駆動部の一ステージの回路図の例である。

**【0035】**

図 3 及び図 4 を参照すれば、ゲート駆動部 400 は、互いに従属的に接続され、順にゲート信号を出力する複数のステージ ST<sub>1</sub> ~ ST<sub>n+1</sub> を含み、ゲートオフ電圧 V<sub>off</sub>、第1及び第2クロック信号 CKV、CKVB 及び初期化信号 INT が入力される。最後のステージ ST<sub>n+1</sub> を除く全てのステージ ST<sub>1</sub> ~ ST<sub>n+1</sub> は、ゲート線 GL<sub>1</sub> ~ GL<sub>n</sub> と 1 対 1 に接続されている。

40

**【0036】**

各ステージ ST<sub>1</sub> ~ ST<sub>n+1</sub> は、第1クロック端子 CK1、第2クロック端子 CK2、セット端子 S、リセット端子 R、電源電圧端子 GV、フレームリセット端子 FR、及びゲート出力端子 OUT1 及びキャリー出力端子 OUT2 を備えている。

**【0037】**

各ステージ、例えば j 番目ステージ ST<sub>j</sub> のセット端子 S には、前段ステージ ST<sub>j-1</sub> のキャリー出力、つまり前段キャリー出力 Cout(j-1) が、リセット端子 R には

50

後段ステージ  $S T_{j+1}$  のゲート出力、つまり後段ゲート出力  $G_{out}(j+1)$  が入力され、第 1 及び第 2 クロック端子  $C K_1$ 、 $C K_2$  にはクロック信号  $C KV$ 、 $C KVB$  が入力され、ゲート電圧端子  $GV$  にはゲートオフ電圧  $V_{off}$  が入力され、フレームリセット端子  $FR$  には初期化信号  $INT$  が入力される。ゲート出力端子  $OUT_1$  はゲート出力  $G_{out}(j)$  を出力し、キャリー出力端子  $OUT_2$  はキャリー出力  $C_{out}(j)$  を出力する。最後のステージ  $S T_{n+1}$  のキャリー出力  $C_{out}(n+1)$  は、初期化信号  $INT$  として各ステージ  $S T_1 \sim S T_n$  に提供される。

#### 【0038】

但し、シフトレジスタ 400 の第 1 ステージ  $S T_1$  には、前段キャリー出力の代わりに走査開始信号  $STV$  が入力され、最後のステージ  $S T_{n+1}$  には後段ゲート出力の代わりに走査開始信号  $STV$  が入力される。また、 $j$  番目ステージ  $S T_j$  の第 1 クロック端子  $CK_1$  に第 1 クロック信号  $C KV$  が、第 2 クロック端子  $CK_2$  に第 2 クロック信号  $C KVB$  が入力される場合、これに隣接した ( $j-1$ ) 番目及び ( $j+1$ ) 番目ステージ  $S T_{j-1}$ 、 $S T_{j+1}$  の第 1 クロック端子  $CK_1$  には第 2 クロック信号  $C KVB$  が、第 2 クロック端子  $CK_2$  には第 1 クロック信号  $C KV$  が入力される。10

#### 【0039】

第 1 及び第 2 クロック信号  $C KV$ 、 $C KVB$  は、画素のトランジスタ  $Tr$  を駆動できるように、電圧レベルがハイの場合はゲートオン電圧  $V_{on}$  と同一で、ローの場合はゲートオフ電圧  $V_{off}$  と同一であるのが好ましい。第 1 及び第 2 クロック信号  $C KV$ 、 $C KVB$  は、デューティ比が 50 % であり、その位相差は 180 ° であることができる。20

#### 【0040】

図 4 を参照すれば、本発明の一実施形態によるゲート駆動部 400 の各ステージ、例えば  $j$  番目ステージは、入力部 420、プルアップ駆動部 430、プルダウン駆動部 440 及び出力部 450 を含む。これらは少なくとも一つの NMOS トランジスタ  $T_{1-T14}$  を含み、プルアップ駆動部 430 及び出力部 450 は、キャパシタ  $C_{1-C3}$  をさらに含む。ところが、NMOS トランジスタの代わりに PMOS トランジスタを用いることもできる。実際にキャパシタ  $C_{1-C3}$  は、工程時に設けられるゲートとドレイン / ソース間の寄生容量 (parasitic capacitance) であり得る。

#### 【0041】

入力部 420 は、セット端子  $S$  及びゲート電圧端子  $GV$  に順に直列に連結されている三つのトランジスタ  $T_{11}$ 、 $T_{10}$ 、 $T_5$  を備える。トランジスタ  $T_{11}$ 、 $T_5$  のゲートは、第 2 クロック端子  $CK_2$  に接続され、トランジスタ  $T_5$  のゲートは、第 1 クロック端子  $CK_1$  に接続されている。トランジスタ  $T_{11}$  とトランジスタ  $T_{10}$  間の接続点は接続点  $J_1$  に接続され、トランジスタ  $T_{10}$  とトランジスタ  $T_{11}$  間の接続点は接続点  $J_2$  に接続されている。30

#### 【0042】

プルアップ駆動部 430 は、セット端子  $S$  と接続点  $J_1$ との間に接続されているトランジスタ  $T_4$  と、第 1 クロック端子  $CK_1$  と接続点  $J_3$  との間に接続されているトランジスタ  $T_{12}$ 、及び第 1 クロック端子  $CK_1$  と接続点  $J_4$  との間に接続されているトランジスタ  $T_7$  を含む。トランジスタ  $T_4$  のゲート及びドレインは、セット端子  $S$  に共通に接続され、ソースは接続点  $J_1$  に接続されており、トランジスタ  $T_{12}$  のゲート及びドレインは、第 1 クロック端子  $CK_1$  に共通に接続され、ソースは接続点  $J_3$  に接続されている。トランジスタ  $T_7$  のゲートは、接続点  $J_3$  に接続されると同時に、キャパシタ  $C_1$  を通じて第 1 クロック端子  $CK_1$  に接続され、ドレインは第 1 クロック端子  $CK_1$  に、ソースは接続点  $J_4$  に接続され、接続点  $J_3$  と接続点  $J_4$  との間にキャパシタ  $C_2$  が接続されている。40

#### 【0043】

プルダウン駆動部 440 は、ソースを通じてゲートオフ電圧  $V_{off}$  を受信して、ドレインを通じて接続点  $J_1$ 、 $J_2$ 、 $J_3$ 、 $J_4$  に出力する複数のトランジスタ  $T_9$ 、 $T_{13}$ 、 $T_8$ 、 $T_3$ 、 $T_2$ 、 $T_6$  を備える。トランジスタ  $T_9$  のゲートはリセット端子  $R$  に、ド50

レインは接続点 J 1 に接続され、トランジスタ T 13、T 8 のゲートは接続点 J 2 に共通に接続され、ドレインはそれぞれ接続点 J 3、J 4 に接続されている。トランジスタ T 3 のゲートは接続点 J 4 に、トランジスタ T 2 のゲートはリセット端子 R に接続され、二つのトランジスタ T 3、T 2 のドレインは接続点 J 2 に接続されている。トランジスタ T 6 のゲートはフレームリセット端子 F R に接続され、ドレインは接続点 J 1 に、ソースはゲートオフ電圧端子 G V に接続されている。

#### 【 0 0 4 4 】

出力部 450 は、ドレイン及びソースが各々第 1 クロック端子 C K 1 と出力端子 O U T 1、O U T 2 との間に接続され、ゲートが接続点 J 1 に接続されている一対のトランジスタ T 1、T 15 と、トランジスタ T 1 のゲートとドレインとの間、つまり接続点 J 1 と接続点 J 2 との間に接続されているキャパシタ C 3 を備える。トランジスタ T 1 のソースは接続点 J 2 に接続されている。

#### 【 0 0 4 5 】

以下、前記ステージの動作について説明する。

#### 【 0 0 4 6 】

説明の便宜のため、第 1 及び第 2 クロック信号 C K V、C K V B のハイレベルに当たる電圧を高電圧とし、第 1 及び第 2 クロック信号 C K V、C K V B のローレベルに当たる電圧の大きさはゲートオフ電圧 V o f f と同一であり、これを低電圧とする。

#### 【 0 0 4 7 】

まず、第 2 クロック信号 C K V B 及び前段キャリー出力 C o u t ( j - 1 ) がハイになるとき、トランジスタ T 11、T 5 及びトランジスタ T 4 が導通する。すると、二つのトランジスタ T 11、T 4 は、高電圧を接続点 J 1 に伝達し、トランジスタ T 5 は、低電圧を接続点 J 2 に伝達する。これにより、トランジスタ T 1、T 15 が導通し第 1 クロック信号 C K V が出力端 O U T 1、O U T 2 に出力されるが、この時、接続点 J 2 の電圧と第 1 クロック信号 C K V がいずれも低電圧であるため、出力電圧 G o u t ( j )、C o u t ( j ) は低電圧になる。これと同時に、キャパシタ C 3 は、高電圧と低電圧の差に相当する大きさの電圧を充電する。

#### 【 0 0 4 8 】

この時、第 1 クロック信号 C K V 及び後段ゲート出力 G o u t ( j + 1 ) はローであり、接続点 J 2 もローであるため、これにゲートが接続されているトランジスタ T 10、T 9、T 12、T 13、T 8、T 2 はいずれもオフ状態である。

#### 【 0 0 4 9 】

次に、第 2 クロック信号 C K V B がローになるとき、トランジスタ T 11、T 5 が遮断され、これと同時に、第 1 クロック信号 C K V がハイになるとき、トランジスタ T 1 の出力電圧及び接続点 J 2 の電圧が高電圧になる。この時、トランジスタ T 10 のゲートには高電圧が印加されるが、接続点 J 2 に接続されているソースの電位がまた同じ高電圧であるため、ゲートソース間の電位差が 0 となり、トランジスタ T 10 はターンオフ状態を維持する。この結果、接続点 J 1 は浮遊状態になり、このため、キャパシタ C 3 によって高電圧の分だけ電位が上昇する。

#### 【 0 0 5 0 】

一方、第 1 クロック信号 C K V 及び接続点 J 2 の電位が高電圧であるため、トランジスタ T 12、T 13、T 8 が導通する。この状態でトランジスタ T 12 及びトランジスタ T 13 が高電圧と低電圧の間で直列に接続され、これにより、接続点 J 3 の電位は、二つのトランジスタ T 12、T 13 の導通時の抵抗状態の抵抗値によって分圧された電圧値を有する。しかし、二つのトランジスタ T 13 の導通時の抵抗状態の抵抗値がトランジスタ T 12 の導通時の抵抗状態の抵抗値に比べて極めて大きく、例えば約 10,000 倍に設定されている場合は、接続点 J 3 の電圧は高電圧と略同一である。従って、トランジスタ T 7 が導通しトランジスタ T 8 と直列に接続され、これによって接続点 J 4 の電位は、二つのトランジスタ T 7、T 8 の導通時の抵抗状態の抵抗値によって分圧された電圧値を有する。また、二つのトランジスタ T 7、T 8 の抵抗状態の抵抗値が略同一に設定されている

10

20

30

40

50

場合には、接続点 J 4 の電位は高電圧と低電圧の中間値を有し、これによってトランジスタ T 3 は、遮断状態を維持する。この時、後段ゲート出力 Gout ( j+1 ) が依然としてローであるため、トランジスタ T 9 、 T 2 も遮断状態を維持する。よって、出力端 OUT 1 、 OUT 2 は第 1 クロック信号 CKV にのみ接続され、低電圧と遮断されて高電圧を出力する。

#### 【 0051 】

一方、キャパシタ C 1 及びキャパシタ C 2 は、両端の電位差に相当する電圧をそれぞれ充電し、接続点 J 3 の電圧が接続点 J 5 の電圧より低い。

#### 【 0052 】

次に、後段ゲート出力 Gout ( j+1 ) 及び第 2 クロック信号 CKVB がハイになり 10 、第 1 クロック信号 CKV がローになるとき、トランジスタ T 9 、 T 2 が導通し接続点 J 1 、 J 2 に低電圧を伝達する。この時、接続点 J 1 の電圧は、キャパシタ C 3 が放電によって低電圧に変わると、キャパシタ C 3 の放電時間によって完全に低電圧に変わるためにはある程度の時間が必要である。従って、二つのトランジスタ T 1 、 T 15 は、後段ゲート出力 Gout ( j+1 ) がハイになってからも当分の間導通状態を維持することになり 20 、これによって出力端 OUT 1 、 OUT 2 が第 1 クロック信号 CKV と接続されて低電圧を出力する。次に、キャパシタ C 3 が完全に放電して接続点 J 1 の電位が低電圧に到達したとき、トランジスタ T 15 が遮断されて出力端 OUT 2 が第 1 クロック信号 CKV と遮断され、キャリー出力 Cout ( j ) は浮遊状態になって低電圧を維持する。これと同時に、出力端 OUT 1 は、トランジスタ T 1 が遮断されても、トランジスタ T 2 を通じて低電圧と接続され継続して低電圧を出力する。

#### 【 0053 】

一方、トランジスタ T 12 、 T 13 が遮断されるため接続点 J 3 が浮遊状態になる。また、接続点 J 5 の電圧が接続点 J 4 の電圧より低くなるが、キャパシタ C 1 によって接続点 J 3 の電圧が接続点 J 5 の電圧より低い状態を維持し、トランジスタ T 7 は遮断される。同時に、トランジスタ T 8 も遮断状態になって接続点 J 4 の電圧もその分低くなり、トランジスタ T 3 も遮断状態を維持する。また、トランジスタ T 10 は、ゲートが第 1 クロック信号 CKV の低電圧に接続され、接続点 J 2 の電圧もローであるため、遮断状態を維持する。

#### 【 0054 】

次に、第 1 クロック信号 CKV がハイになるとき、トランジスタ T 12 、 T 7 が導通し 30 、接続点 J 4 の電圧が上昇してトランジスタ T 3 を導通させて低電圧を接続点 J 2 に伝達するため、出力端 OUT 1 は継続して低電圧を出力する。即ち、後段ゲート出力 Gout ( j+1 ) の出力がローであるときにも、接続点 J 2 の電圧が低電圧になるようとする。

#### 【 0055 】

一方、トランジスタ T 10 のゲートが第 1 クロック信号 CKV の高電圧に接続され、接続点 J 2 の電圧が低電圧であるため導通されて接続点 J 2 の低電圧を接続点 J 1 に伝達する。一方、二つのトランジスタ T 1 、 T 15 のドレインには、第 1 クロック端子 CK1 が接続されていて第 1 クロック信号 CKV が継続して印加される。特に、トランジスタ T 1 は、その他のトランジスタに比べて相対的に大きく作製されるが、このためゲートドレイン間の寄生容量が大きくドレインの電圧変化がゲート電圧に影響を及ぼす可能性がある。この結果、第 1 クロック信号 CKV がハイになるとき、ゲートドレイン間の寄生容量によってゲート電圧が上昇し、トランジスタ T 1 が導通することもある。従って、接続点 J 2 の低電圧を接続点 J 1 に伝達してトランジスタ T 1 のゲート電圧を低電圧に維持し、トランジスタ T 1 が導通するのを防止する。

#### 【 0056 】

その後は、前段キャリー出力 Cout ( j-1 ) がハイになるまで接続点 J 1 の電圧は低電圧を維持し、接続点 J 2 の電圧は、第 1 クロック信号 CKV がハイで、第 2 クロック信号 CKVB がローであるときは、トランジスタ T 3 を通じて低電圧になり、その逆のときは、トランジスタ T 5 を通じて低電圧を維持する。

10

20

30

40

50

**【 0 0 5 7 】**

一方、トランジスタ T<sub>6</sub> は、最後のダミーステージ S<sub>T\_{n+1}</sub> のキャリー出力 C<sub>out</sub>(n+1) である初期化信号 I<sub>NT</sub> を受信して、ゲートオフ電圧 V<sub>off</sub> を接続点 J<sub>1</sub> に伝達し、接続点 J<sub>1</sub> の電圧をもう 1 度低電圧に設定する。

**【 0 0 5 8 】**

このような方法で、ステージ S<sub>T\_j</sub> は、前段キャリー信号 C<sub>out</sub>(j-1) 及び後段ゲート信号 G<sub>out</sub>(j+1) に基づき、第 1 及び第 2 クロック信号 C<sub>KV</sub>、C<sub>KVB</sub> に同期してキャリー信号 C<sub>out</sub>(j) 及びゲート信号 G<sub>out</sub>(j) を生成する。

**【 0 0 5 9 】**

以下、図 4 に示したゲート駆動部 400 の薄膜トランジスタ表示板 100 上の配置について、図 5、図 6 及び図 8 を参照して詳細に説明する。 10

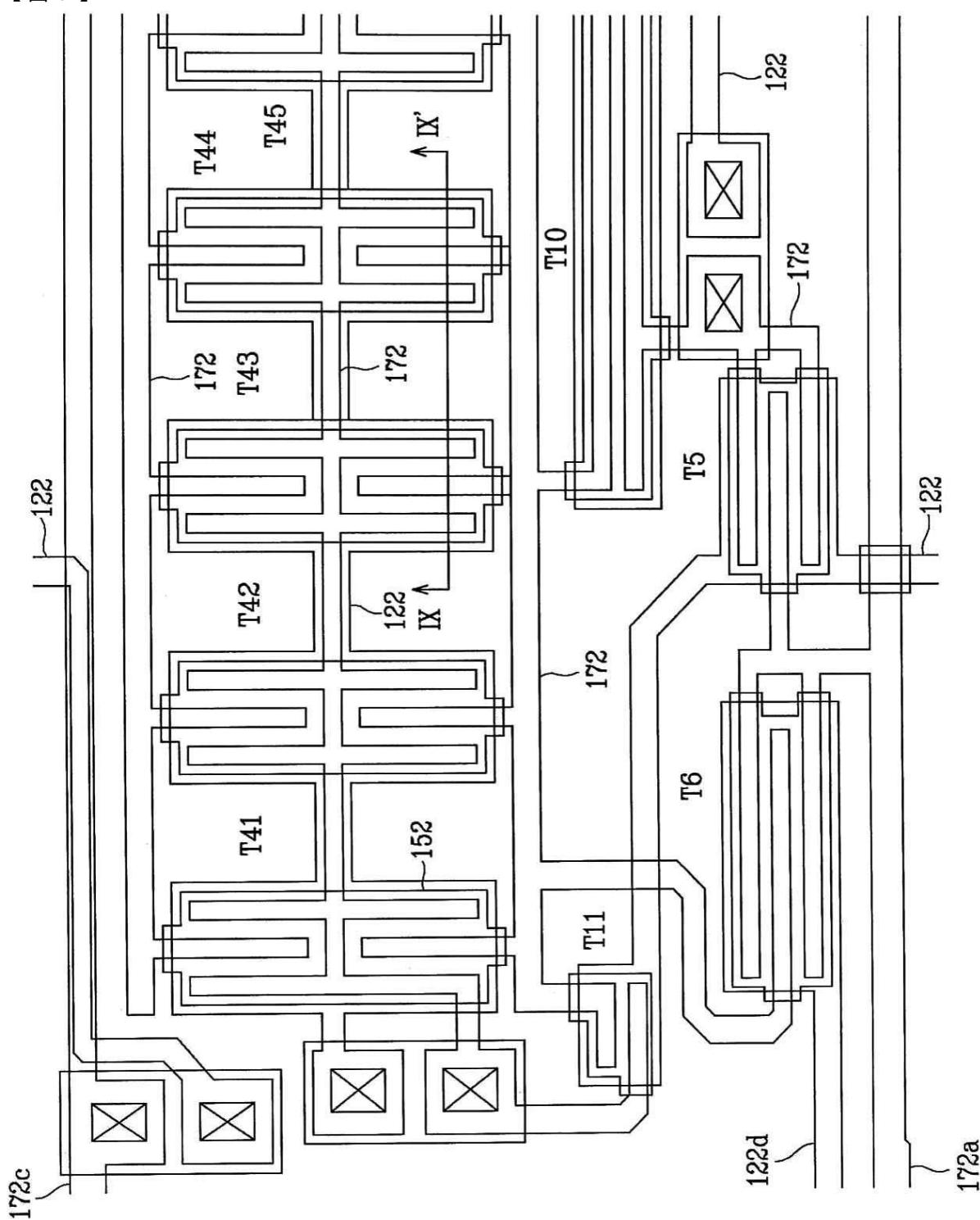

**【 0 0 6 0 】**

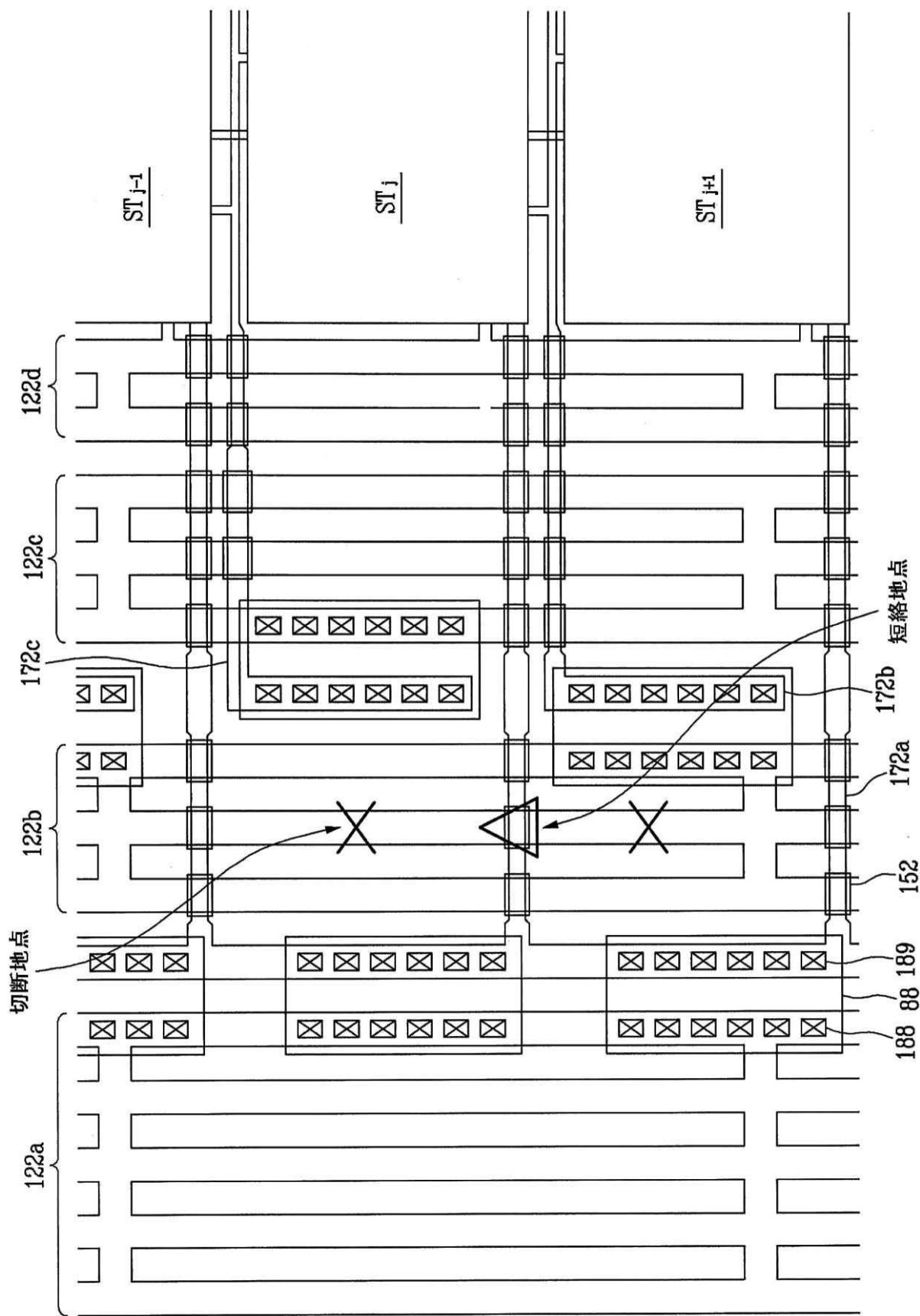

図 5 は、本発明の一実施形態によるゲート駆動部の概略的な配置図であり、図 6 は、図 5 に示したゲート駆動部の配線部の配置図であり、図 8 は、図 5 に示したゲート駆動部の回路部を一部示した配置図である。

**【 0 0 6 1 】**

図 5 を参照すれば、本実施形態によるゲート駆動部 400 は、既に説明したステージ S<sub>T\_1</sub> ~ S<sub>T\_{n+1}</sub> からなる回路部 CS と、これらステージ S<sub>T\_1</sub> ~ S<sub>T\_{n+1}</sub> に入力される各種信号 V<sub>off</sub>、C<sub>KV</sub>、C<sub>KVB</sub>、I<sub>NT</sub> を伝達する配線部 LS を備える。 20

**【 0 0 6 2 】**

配線部 LS は、ゲートオフ電圧 V<sub>off</sub> を伝達するゲートオフ電圧線 SL<sub>1</sub>、第 1 及び第 2 クロック信号 C<sub>KV</sub>、C<sub>KVB</sub> をそれぞれ伝達する第 1 及び第 2 クロック信号線 SL<sub>2</sub>、SL<sub>3</sub>、及び初期化信号 I<sub>NT</sub> を伝達する初期化信号線 SL<sub>4</sub> を含む。各信号線 SL<sub>1</sub> ~ SL<sub>4</sub> は、主に縦方向に延びており、ゲートオフ電圧線 SL<sub>1</sub>、クロック信号線 SL<sub>2</sub>、SL<sub>3</sub> 及び初期化信号線 SL<sub>4</sub> の順に左側から配置されシフトレジスタ 400 に近づく。また、前記信号線 SL<sub>1</sub> ~ SL<sub>4</sub> は、ステージ S<sub>T\_1</sub> ~ S<sub>T\_{n+1}</sub> に向けて横に延びた連結線を有し、ゲートオフ電圧線 SL<sub>1</sub> 及び初期化信号線 SL<sub>4</sub> は、一つのステージ S<sub>T\_1</sub> ~ S<sub>T\_{n+1}</sub> に一つずつ連結線を出しているが、第 1 及び第 2 クロック信号線 SL<sub>2</sub>、SL<sub>3</sub> は、ステージ S<sub>T\_1</sub> ~ S<sub>T\_{n+1}</sub> の境界付近に位置して交互に一つずつ連結線を出している。 30

**【 0 0 6 3 】**

回路部 CS における各ステージ S<sub>T\_1</sub> ~ S<sub>T\_{n+1}</sub>、例えば(j-1) 番目ステージ内のトランジスタ T<sub>1</sub> ~ T<sub>13</sub>、T<sub>15</sub> の配置によれば、前段ステージに近い左側上に前段キャリー信号 C<sub>out</sub>(j-1) が入力されるトランジスタ T<sub>4</sub> が配置され、上側に横方向に延びた第 1 クロック信号線 SL<sub>2</sub> の連結線に沿って第 1 クロック信号 C<sub>KV</sub> を受信するトランジスタ T<sub>1</sub>、T<sub>15</sub> が配置され、トランジスタ T<sub>15</sub> の下側にも第 1 クロック信号 C<sub>KV</sub> を受信するトランジスタ T<sub>7</sub>、T<sub>10</sub>、T<sub>12</sub> が配置されている。また、下側から延びている第 2 クロック信号線 SL<sub>3</sub> の連結線に接続され第 2 クロック信号 C<sub>KVB</sub> を受信するトランジスタ T<sub>11</sub>、T<sub>5</sub> が左側下に配置され、左側から延びている初期化信号線 SL<sub>4</sub> の連結線に接続され初期化信号 I<sub>NT</sub> を受信するトランジスタ T<sub>6</sub> は最も左側に配置されている。これと共に、下側に横方向に延びているゲートオフ電圧線 SL<sub>1</sub> の連結線に沿ってゲートオフ電圧 V<sub>off</sub> を受信するトランジスタ T<sub>2</sub>、T<sub>3</sub>、T<sub>8</sub>、T<sub>9</sub>、T<sub>13</sub> が配置されている。 40

**【 0 0 6 4 】**

これと隣接した j 番目ステージ S<sub>T\_j</sub> の場合、第 1 クロック信号線 SL<sub>2</sub> 及び第 1 クロック信号 C<sub>KV</sub> が第 2 クロック信号線 SL<sub>3</sub> 及び第 2 クロック信号 C<sub>KVB</sub> に変わり、これと逆に、第 2 クロック信号線 SL<sub>3</sub> 及び第 2 クロック信号 C<sub>KVB</sub> が第 1 クロック信号線 SL<sub>2</sub> 及び第 1 クロック信号 C<sub>KV</sub> に変わることを除いて、各トランジスタの配置は、J-1 番目ステージ S<sub>T\_{j-1}</sub> と同一である。

**【 0 0 6 5 】**

10

20

30

40

50

この時、配線部 S L はシールライン領域 S A に位置し、回路部 C S の一部もシールライン領域 S A に位置し、回路部 C S の他の一部はシールライン領域 S A の工程マージン領域 S A' に位置している。工程マージン領域 S A' の幅は 0.3 mm 程度であって、これは密封材 350 をシールライン領域 S A に塗布する際に生じ得る最大の誤差範囲である。

#### 【0066】

既に説明したように、密封材 350 を硬化する際に、薄膜トランジスタ表示板 100 の背面から光を照射するため、シールライン領域 S A とシールライン工程マージン領域 S A' に位置する信号線及びトランジスタは、光をうまく通過させるための平面構造を有する。

#### 【0067】

図 6 を参照すれば、幅の広い信号線 S L 1 ~ S L 3 は梯形または網形態であり、光を通過させる開口部を複数備えている。よって、信号線 S L 1 ~ S L 3 それぞれは、縦に長く伸びている一対若しくはそれ以上の縦部と、これらを連結する複数の横部とからなり、これらで囲まれた開口部を備える。縦部の幅及び間隔は、光が回折して透過できる程度とする。約 20 乃至 30 μm、好ましくは 25 μm 程度であるのが好ましい。各信号線 122 a ~ 122 c 全体の線幅は、開口部を備えることで発生する抵抗の増加を考慮して適切に定める。開口部を設けない場合の線幅が約 100 μm 以上であって光を回折できない場合には、このような構造を有するのが好ましい。

#### 【0068】

図 8 によれば、シールライン領域 S A 及びシールライン工程マージン領域 S A' に位置するサイズの大きい薄膜トランジスタ、例えば図 5 に示すトランジスタ T 4 、 T 15 は、複数の小さいトランジスタ T 41 ~ T 45 に分けられており、これらの間に充分な間隔があつて小さいトランジスタ T 41 ~ T 45 の間から光が通過することができる。小さい薄膜トランジスタ T 41 ~ T 45 の幅及び間隔に対しても光が回折して透過できる程度とする。約 100 μm 以下が好ましい。

#### 【0069】

以下、前記のようなゲート駆動部 400 を備える薄膜トランジスタ表示板の構造について、図 7 及び図 9 乃至図 11 、図 6 及び図 8 を参照して詳細に説明する。

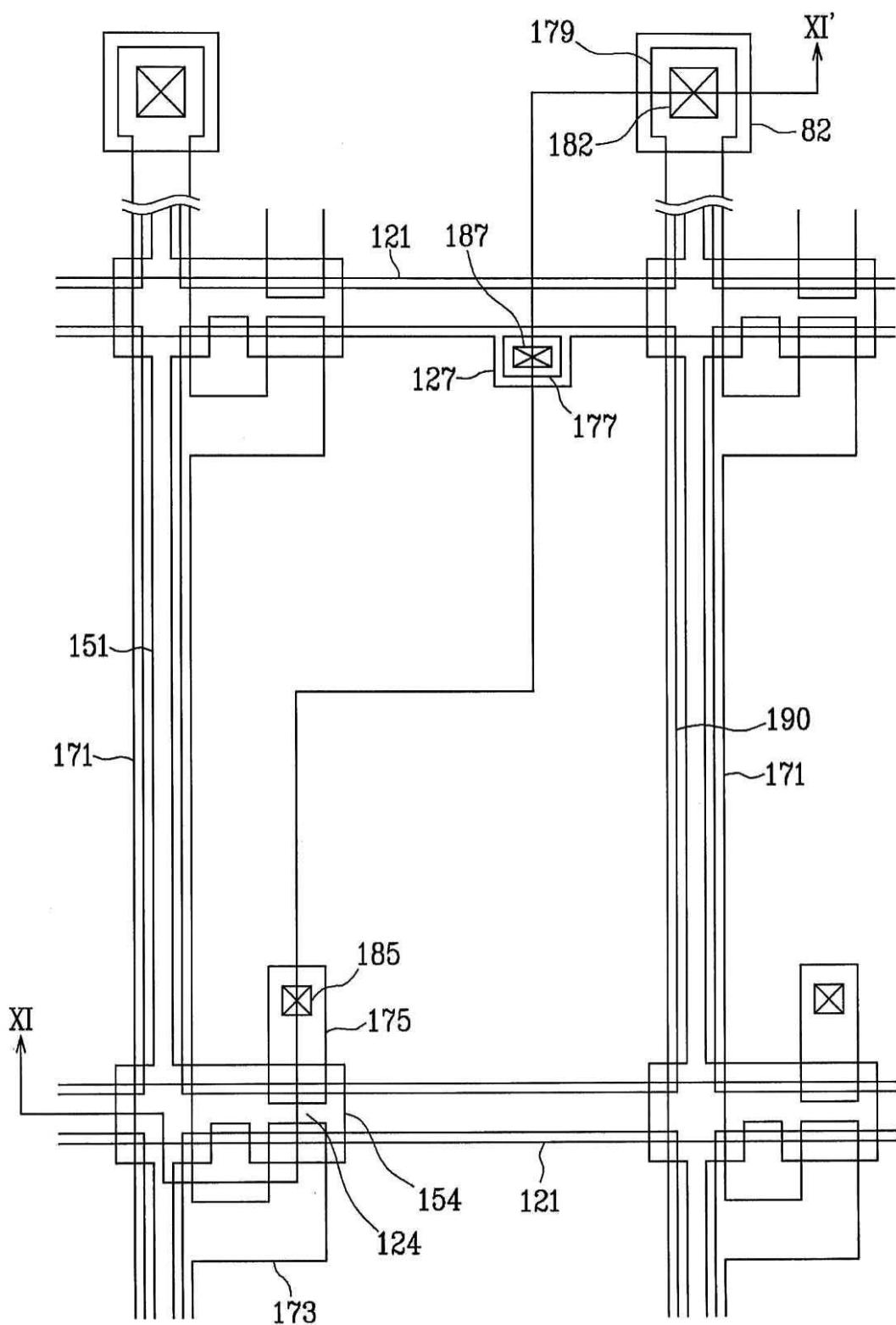

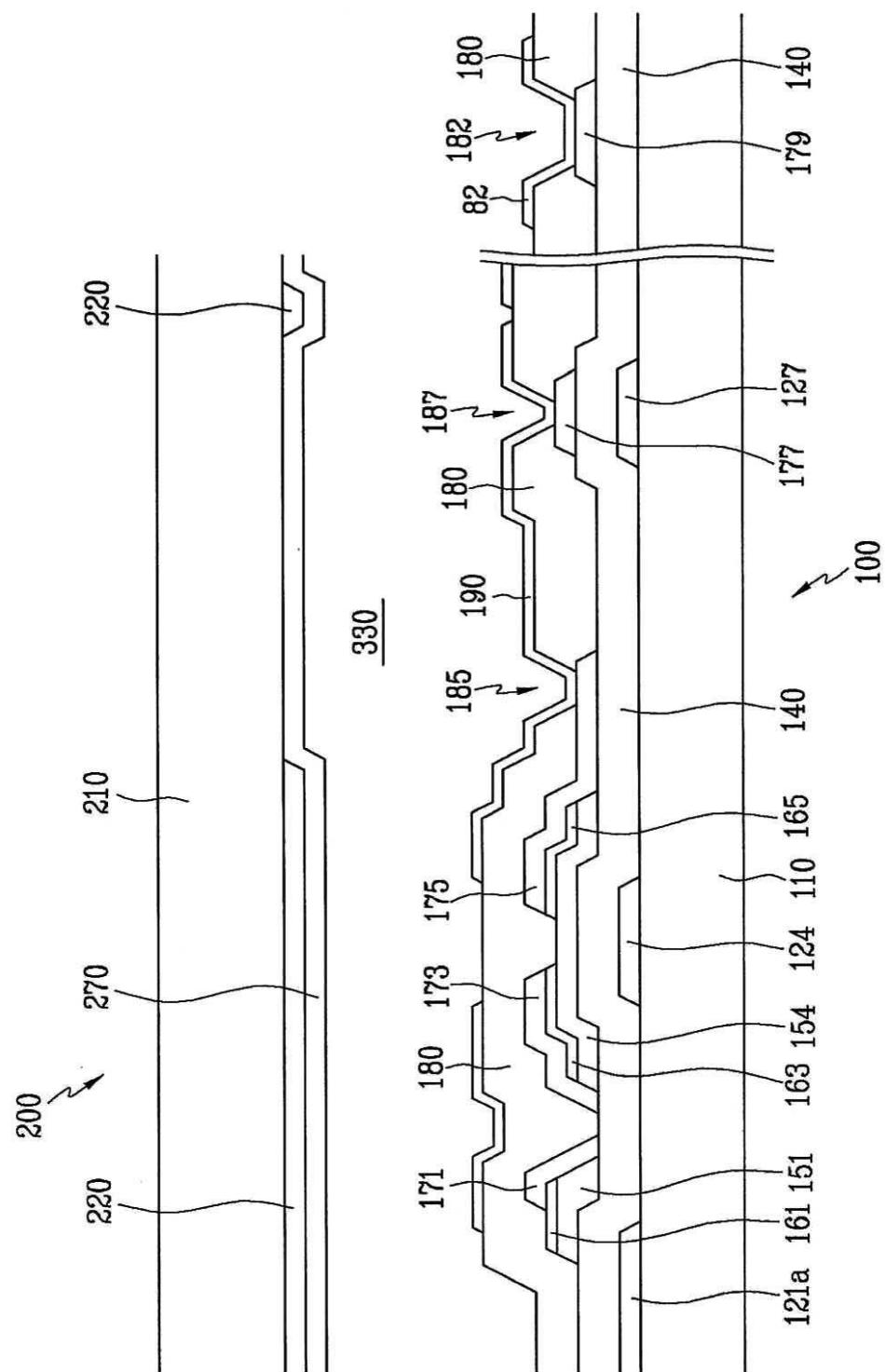

#### 【0070】

図 7 は、図 6 に示した配線部の V II - V II' 線による断面図であり、図 9 は、図 8 に示した配線部の IX - IX' 線による断面図であり、図 10 は、表示領域 D A における画素の配置図であり、図 11 は、図 10 に示した画素の XI - XI' 線による断面図である。

#### 【0071】

絶縁基板 110 上に複数のゲート線 121 及び複数の駆動信号線 122 、 122 a ~ 122 d が形成されている。

#### 【0072】

図 10 を参照すれば、ゲート線 121 は、ゲート信号を伝達し、主に横方向に延びて延長されゲート駆動部 400 と連結される。各ゲート線 121 の一部は複数のゲート電極 124 をなし、他の一部は下方向に突出して複数の突出部 127 をなしている。

#### 【0073】

図 6 を参照すれば、駆動信号線 122 a ~ 122 d は、それぞれゲートオフ電圧 V off 、第 1 及び第 2 クロック信号 CKV 、 CKVB 及び初期化信号 INT を伝達し、主に縦方向に伸びている。最も幅の狭い初期化信号線 122 c を除くその他の駆動信号線 122 a ~ 122 c は梯形であって、縦に長く伸びた一対若しくはそれ以上の縦部とこれらを連結する複数の横部とからなり、これらで囲まれた開口部を備える。縦部の幅及び間隔は、光が回折して透過できる程度とし、約 20 乃至 30 μm、好ましくは 25 μm 程度が好ましい。各信号線 122 a ~ 122 c の全体の線幅は、開口部を備えることで発生する抵抗の増加を考慮して適切に定める。開口部を設けない場合の線幅が約 100 μm 以上であつて光を回折できない場合には、このような構造を有するのが好ましい。一方、初期化信号

10

20

30

40

50

線 1 2 2 d は、各ステージに向けて横方向に伸びた複数の分枝を有する。

【 0 0 7 4 】

図 8 を参照すれば、駆動信号線 1 2 2 は、ゲート駆動部内で信号を伝達し、拡張されてゲート駆動部の薄膜トランジスタの制御電極の役割を果たす。

【 0 0 7 5 】

ゲート線 1 2 1 及び駆動信号線 1 2 2 、 1 2 2 a ~ 1 2 2 d は、アルミニウム ( A l ) やアルミニウム合金等のアルミニウム系金属、銀 ( A g ) や銀合金等の銀系金属、銅 ( C u ) や銅合金等の銅系金属、モリブデン ( M o ) やモリブデン合金等のモリブデン系金属、クロム ( C r ) 、タンタル ( T a ) 及びチタニウム ( T i ) などからなる。ところが、ゲート線 1 2 1 は、物理的な性質の異なる二つの膜、つまり下部膜 ( 図示せず ) 及びその上の上部膜 ( 図示せず ) を含むこともできる。上部膜は、ゲート線 1 2 1 の信号遅延や電圧降下を減らせるように低い比抵抗の金属、例えばアルミニウム ( A l ) やアルミニウム合金等のアルミニウム系金属、銀 ( A g ) や銀合金等の銀系金属、銅 ( C u ) や銅合金等の銅系金属からなることができる。これとは異なって、下部膜は他の物質、特に I T O ( i n d i u m t i n o x i d e ) 及び I Z O ( i n d i u m z i n c o x i d e ) との接触特性が優れた物質、例えばクロム、モリブデン ( M o ) 、モリブデン合金、タンタル ( T a ) 、またはチタニウム ( T i ) などからなることができる。クロム下部膜とアルミニウム-ネオジム ( N d ) 合金上部膜、モリブデン上部膜とアルミニウム-ネオジム ( N d ) 合金下部膜は、その好適な例である。

10

【 0 0 7 6 】

ゲート線 1 2 1 及び駆動信号線 1 2 2 、 1 2 2 a ~ 1 2 2 d の側面は、基板 1 1 0 の表面に対して傾斜されており、傾斜角は約 3 0 ~ 8 0 ° の範囲である。

20

【 0 0 7 7 】

ゲート線 1 2 1 及び駆動信号線 1 2 2 、 1 2 2 a ~ 1 2 2 d の上には、窒化ケイ素 ( S i N x ) などからなるゲート絶縁膜 1 4 0 が形成されている。

【 0 0 7 8 】

ゲート絶縁膜 1 4 0 上部には、水素化非晶質シリコン ( 非晶質シリコンは a - S i と略称する。 ) などからなる複数の線状半導体 1 5 1 及び島状半導体 1 5 2 が形成されている。線状半導体 1 5 1 は、主に縦方向に伸びており、ここから複数の突出部 1 5 4 がゲート電極 1 2 4 に向けて伸び、ゲート線 1 2 1 と出会う地点付近で幅が大きくなっているゲート線 1 2 1 の広い面積を覆っている。島状半導体 1 5 2 は、図 8 に示したように、ゲート駆動部の制御電極上に位置したり、図 6 及び図 8 に示したように、駆動信号線 1 2 2 、 1 2 2 a ~ 1 2 2 d の一部の上に位置したりし、駆動信号線 1 2 2 、 1 2 2 a ~ 1 2 2 d の外側に突出した部分を有する。

30

【 0 0 7 9 】

半導体 1 5 1 、 1 5 2 の上部には、シリサイドまたは n 型不純物が高濃度にドーピングされている n+ 水素化非晶質シリコンなどの物質で形成された複数の線状及び島状抵抗性接觸部材 ( o h m i c c o n t a c t ) 1 6 1 、 1 6 2 、 1 6 5 が設けられている。線状接觸部材 1 6 1 は、複数の突出部 1 6 3 を備えており、該突出部 1 6 3 と島状接觸部材 1 6 5 が対をなして半導体 1 5 1 の突出部 1 5 4 上に位置している。島状抵抗性接觸部材 1 6 2 は、島状半導体 1 5 2 上に位置している。

40

【 0 0 8 0 】

半導体 1 5 1 、 1 5 2 及び抵抗性接觸部材 1 6 1 、 1 6 2 、 1 6 5 の側面も傾斜されており、その傾斜角は 3 0 ~ 8 0 ° である。

【 0 0 8 1 】

抵抗性接觸部材 1 6 1 、 1 6 2 、 1 6 5 及びゲート絶縁膜 1 4 0 の上には、複数のデータ線 1 7 1 、複数の出力電極 1 7 5 、複数のストレージキャパシタ用導電体 ( storage capacitor conductor ) 1 7 7 、及び複数の連結信号線 1 7 2 、 1 7 2 a ~ 1 7 2 c が設けられている。

【 0 0 8 2 】

50

図10を参照すれば、データ線171は、主に縦方向に延びてゲート線121と交差し、データ電圧を伝達する。各データ線171から出力電極175に向けて延びた複数の分枝が入力電極173をなす。一对の入力電極173と出力電極175は互いに分離されており、制御電極124に対して互いに反対側に位置している。

#### 【0083】

ストレージキャパシタ用導電体177は、ゲート線121の拡張部127と重畠している。

#### 【0084】

図6で、連結信号線172aは、ゲートオフ電圧線122aと第1クロック信号線122bとの間に位置し、主に縦方向に延びた幹と、幹から各ステージに向けて横方向に延びた複数の分枝を有する。連結信号線172b、172cそれぞれは、第1クロック信号線122bと第2クロック信号線122cとの間に位置し、主に縦方向に延びた縦部とその端に連結され各ステージに向けて横方向に延びた複数の横部とを備える。

10

#### 【0085】

図8で、連結信号線172は、ゲート駆動部内で信号を伝達し、島状半導体152及び島状抵抗性接触部材162の上に位置した部分は、薄膜トランジスタの入力電極及び出力電極の役割を果たす。薄膜トランジスタ上に位置した部分は、トランジスタの駆動電流を増加させるために交錯形態となっている。

#### 【0086】

データ線171、ドレイン電極175及びストレージキャパシタ用導電体177は、モリブデン系金属、クロム、タンタル、チタニウムなどの耐火性金属からなるのが好ましく、低い抵抗の上部膜と優れた接触特性の下部膜とを備える多層膜構造であることができる。各データ線171の端部179は、他の層または外部装置との連結のために幅が拡張されている。

20

#### 【0087】

データ線171、出力電極175、連結信号線172、172a～172c、及びストレージキャパシタ用導電体177の側面も、基板110表面に対して傾斜されており、その傾斜角は約30～80°の範囲である。

#### 【0088】

抵抗性接触部材161、162、165は、その下部の半導体151、152とその上部のデータ線171、連結信号線172及び出力電極175の間にのみ存在し、接触抵抗を低くする役割を果たす。線状半導体151は、ソース電極173とドレイン電極175との間を始めとして、データ線171及びドレイン電極175で覆われずに露出された部分を有し、殆どの所で線状半導体151の幅がデータ線171の幅より小さいが、既に説明したように、ゲート線121と出会う部分では幅が大きくなつてデータ線171の断線を防止する。島状半導体152も駆動信号線122、122a～122dと連結信号線172、172a～172cとが交差する部分に位置し、連結信号線172、172a～172cの断線を防止する。

30

#### 【0089】

データ線171と出力電極175、連結信号線172、172a～172c、及びストレージキャパシタ用導電体177と露出された半導体151部分の上には、平坦化特性が優れて感光性を有する有機物質、プラズマ化学気相蒸着（PECVD）で形成されるa-Si:C:O、a-Si:O:F等、誘電率4.0以下の低誘電率絶縁物質、または無機物質である窒化ケイ素などからなる保護膜180が設けられている。なお、保護膜180は、有機物及び窒化ケイ素の二重層からなることができる。

40

#### 【0090】

保護膜180には、データ線171の端部179と、出力電極175、ストレージキャパシタ用導電体177及び連結信号線172、172a～172cの端部をそれぞれ露出する複数の接触孔(contact hole)182、185、187、188が設けられ、ゲート絶縁膜140と共に駆動信号線122、122a～122dを露出する複数

50

の接触孔 189 が設けられている。

【0091】

保護膜 180 上には、ITO または IZO からなる複数の画素電極 190 と複数の接触補助部材 82 及び連結補助部材 88 が設けられている。

【0092】

画素電極 190 は、接触孔 185、187 を通じて出力電極 175 及びストレージキャパシタ用導電体 177 と各々物理的・電気的に接続されて出力電極 175 からデータ電圧の印加を受け、導電体 177 にデータ電圧を伝達する。

【0093】

データ電圧が印加された画素電極 190 は、共通電圧の印加を受ける他の表示板 200 の共通電極 270 と共に電場を生成することによって、二つの電極 190、270 間の液晶層 3 の液晶分子を再配列する。 10

【0094】

また、前述したように、画素電極 190 及び共通電極 270 は液晶キャパシタを構成して、薄膜トランジスタが遮断された後にも印加された電圧を維持しており、電圧維持能力を強化するため液晶キャパシタと並列に接続された別のキャパシタを設ける。これを“ストレージキャパシタ”と言う。ストレージキャパシタは、画素電極 190 及びこれと隣接するゲート線 121（これを“前段ゲート線”と言う。）の重畠などで形成され、ストレージキャパシタの静電容量、つまり保持容量を増加させるためゲート線 121 を拡張した拡張部 127 を設けて重畠面積を拡大する一方、画素電極 190 と接続され拡張部 127 と重畠しているストレージキャパシタ用導電体 177 を保護膜 180 下に設けて両者間の距離を短くする。更に、ストレージキャパシタは、別に具備された維持電極と画素電極 190 の重畠で形成されることがある。 20

【0095】

画素電極 190 はまた、隣接するゲート線 121 及びデータ線 171 と重なって開口率を向上させているが、重ならない場合もある。

【0096】

接触補助部材 82 は、接触孔 182 を通じてデータ線の端部 179 と連結される。接触補助部材 82 は、データ線 171 の端部 179 と外部装置との接着性を補完し、これらを保護する役割をするものであって必須ではなく、これらの適用は選択的である。 30

【0097】

連結補助部材 88 は、接触孔 188、189 を通じて駆動信号線 122a～122c 及び連結信号線 172a～172c と連結され、駆動信号線 122a～122c から各種信号の印加を受けて連結信号線 172a～172c に伝達する。連結補助部材 88 は、面積が大きく、複数の接触孔を通じて一つの信号線と連結される。連結補助部材 88 を小さく分けない理由は、連結補助部材 88 が透明で光を通過させるため、敢えて小さくする必要がなく、大きいほど抵抗が小さくなるためである。なお、接触孔を複数作って連結させる場合、連結補助部材 88 の断線可能性がその分少なくなる。

【0098】

本発明の他の実施形態によれば、画素電極 190 の材料に透明な導電性ポリマーなどを用いており、反射型（reflective）液晶表示装置の場合には、不透明な反射性金属を用いても構わない。この時、接触補助部材 82 は、画素電極 190 と異なる物質、特に ITO または IZO で形成することができる。 40

【0099】

前記例と異なって、駆動信号線 122、122a～122d をデータ線 171 と同一層で、連結信号線 172、172a～172c をゲート線 121 と同一層で形成することもでき、この他にも種々の方法を用いることができる。

【0100】

このように、駆動信号線 S L 1～S L 3 に開口部が設けられており、薄膜トランジスタ表示板 100 の背面から提供された光が開口部を透過し、光硬化性密封材 350 に容易に 50

到達して密封材 350 が安定的に硬化される。その結果、薄膜トランジスタ表示板 100 と共に通電極表示板 200 との結合力が増加し、外部から流入する湿気による腐蝕を防止し、ゲート駆動部 400 の誤動作による駆動不良が減少する。

#### 【0101】

一方、前記のような構造の表示装置において、外部から静電気が流入して信号線と連結線のうちの一つが短絡した場合、図 12 のように、容易に修理することができる。これについて図 12 を参照して説明する。

#### 【0102】

図 12 によれば、例えば第 1 クロック線 122b の縦線のうちの一つとゲートオフ電圧線 122a の横線が短絡した場合、三角形で表示した短絡地点の上側及び下側の X 字表示の地点をそれぞれ切断する。すると、ゲートオフ電圧線 122a の横線は、ステージ ST<sub>j</sub> にのみ接続されてゲートオフ電圧 V<sub>off</sub> を伝達できるようになる。

10

#### 【0103】

このような表示装置によれば、光硬化性物質を含む密封材がゲート駆動部の一部分をカバーするよう第 1 基板と第 2 基板との間に介在される構造において、ゲート駆動部の信号配線には密封材を硬化するために第 1 基板の背面を通じて入射された光を透過する開口部が設けられ、密封材によって第 1 及び第 2 基板間の結合力が向上される。その結果、外部から流入する湿気による腐蝕不良などを改善することができる。更に、容易に修理を行うこともできる。

#### 【0104】

20

以上、実施形態を参照して説明したが、該当技術分野における通常の知識を有する者であれば、特許請求の範囲に記載された本発明の思想及び領域の範囲内で様々な修正及び変形が可能であることが理解できるであろう。

#### 【符号の説明】

#### 【0105】

- 100 薄膜トランジスタ表示板、

- 110 第 1 基板、

- 500 データ駆動部、

- 400 ゲート駆動部、

- 200 共通電極表示板、

- 210 第 2 基板、

- 270 共通電極、

- 300 表示パネル、

- 330 液晶層、

- 350 密封材、

- 600 表示装置。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |       |

|---------|------|-------|

| G 0 9 F | 9/30 | 3 3 8 |

| G 0 9 F | 9/30 | 3 3 6 |

(72)発明者 文 勝 煥

大韓民国京畿道龍仁市上 けん 洞 マンヒョンマウル2団地6次アパート205棟1504号

(72)発明者 李 龍 淳

大韓民国忠清南道天安市木川邑應院里 セグアンエンリチビル107棟404号

(72)発明者 姜 南 淳

大韓民国京畿道安山市常緑区四1洞 プルンマウル住公5団地アパート517棟704号

(72)発明者 朴 僉 源

大韓民国京畿道城南市中院区銀杏2洞 住公アパート117棟602号

審査官 弓指 洋平

(56)参考文献 特開2002-110343 (JP, A)

特開平11-084427 (JP, A)

国際公開第03/087921 (WO, A1)

特開2000-066240 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 2 F 1 / 1 3 3 9

G 0 2 F 1 / 1 3 4 5

G 0 2 F 1 / 1 3 6 8

G 0 9 F 9 / 3 0

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管阵列面板，包括该薄膜晶体管阵列面板的显示装置，以及该液晶显示装置的制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP5667104B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2015-02-12 |

| 申请号            | JP2012045457                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2012-03-01 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 三星显示器的股票会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 金東奎<br>文勝煥<br>李龍淳<br>姜南洙<br>朴倖源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | 金 東 奎<br>文 勝 煥<br>李 龍 淳<br>姜 南 洄<br>朴 倮 源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G02F1/1345 G02F1/1368 G02F1/1339 G09F9/30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G02F1/13454 G02F1/1339 G02F1/1345 G02F1/136286 G02F2001/13629 H01L27/1222 H01L27/124 H01L27/1255 H01L29/78669 H01L29/78678                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G02F1/1345 G02F1/1368 G02F1/1339.505 G09F9/30.330 G09F9/30.309 G09F9/30.338 G09F9/30.336 G09F9/30.330.Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA29 2H092/GA59 2H092/GA60 2H092/JA26 2H092/JA46 2H092/JB69 2H092/JB74 2H092 /KA04 2H092/KA05 2H092/KA10 2H092/KA12 2H092/KB04 2H092/MA47 2H092/NA23 2H092/NA29 2H092/PA04 2H092/PA06 2H092/PA09 2H189/EA04Y 2H189/FA22 2H189/FA52 2H189/HA12 2H189 /LA08 2H189/LA10 2H189/LA15 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CC04 2H192/DA02 2H192/DA42 2H192/EA22 2H192/EA43 2H192/FA32 2H192/FA35 2H192/FA52 2H192/FA65 2H192 /FB03 2H192/FB27 2H192/GD25 5C094/AA41 5C094/AA43 5C094/BA03 5C094/BA43 5C094/DA07 5C094/DA09 5C094/DA13 5C094/DB04 5C094/EA04 5C094/EA05 5C094/EA10 5C094/EB02 5C094 /ED15 5C094/FA01 5C094/FA10 5C094/FB12 5C094/FB20 5C094/GB10 5C094/JA08 |         |            |

| 优先权            | 1020040058708 2004-07-27 KR<br>1020040077500 2004-09-24 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 其他公开文献         | JP2012113321A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

**摘要(译)**

要解决的问题：提供一种薄膜晶体管阵列面板，其可以使用光固化接合构件容易地耦合到公共电极显示板。一种基板，设置有栅极线，数据线，像素电极和薄膜晶体管，以及布线部分，设置在基板上并被配置为从外部接收信号和栅极以及用于向栅极线输出信号的电路部分，其中布线部分设置有开口部分，用于允许光通过与布线部分重叠的光固化耦合构件并且配线部分还包括没有开口的信号线。点域6