(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-293817

(P2005-293817A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

**G11C 19/00**

**G02F 1/133**

**G09G 3/20**

**G09G 3/36**

**H03K 17/687**

F 1

G 11 C 19/00 J

G 11 C 19/00 G

G 02 F 1/133 5 5 O

G 09 G 3/20 6 1 1 J

G 09 G 3/20 6 1 2 K

テーマコード(参考)

2 H 0 9 3

5 C 0 0 6

5 C 0 8 0

5 J 0 5 5

審査請求 有 請求項の数 26 O L (全 22 頁) 最終頁に続く

(21) 出願番号 特願2004-373155 (P2004-373155)

(22) 出願日 平成16年12月24日 (2004.12.24)

(31) 優先権主張番号 2004-021986

(32) 優先日 平成16年3月31日 (2004.3.31)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 2004-030337

(32) 優先日 平成16年4月30日 (2004.4.30)

(33) 優先権主張国 韓国(KR)

(71) 出願人 501426046

エルジー・フィリップス エルシーテー

カンパニー、リミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

イドードン 20

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100096943

弁理士 白井 伸一

最終頁に続く

(54) 【発明の名称】シフトレジスタとその駆動方法及び液晶表示パネルの駆動装置

## (57) 【要約】

【課題】出力バッファ部を制御するノードの電圧が薄膜トランジスタの寄生キャパシタにより変動されることを防止することができるシフトレジスタ及びその駆動方法を提供する。

【解決手段】本発明のシフトレジスタは、多数のステージのそれぞれが、第1ノード(Q)により制御された第1クロック信号(C1)を出力ライン(Out)に供給するプルアップトランジスタ(T5)と、第2ノード(QB)により制御された第1駆動電圧を出力ラインに供給するプルダウントランジスタ(T6)と、第1及び第2ノードを互いに相反するように制御する制御部(10)と、前記第1ノードと前記第1クロック信号及び前記プルアップトランジスタとの間の寄生キャパシタ(CDG、CGS)による変動量を償う、第1ノードと第2クロック信号の入力ラインの間に接続された補償キャパシタとを具備する。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

スタートパルスをシフトさせた出力信号を次の段のスタートパルスとして供給する多数のステージから構成されたシフトレジスタにおいて、前記多数のステージのそれぞれは、第1ノードにより制御された第1クロック信号を出力ラインに供給するプルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインに供給する第1プルダウントランジスタと、前記第1及び第2ノードを互いに相反するように制御する制御部と、前記第1ノードと第2クロック信号の入力ラインとの間に接続された補償キャパシタとを具備し、前記第2クロック信号は前記第1クロック信号とは異なることを特徴とするシフトレジスタ。10

**【請求項 2】**

前記補償キャパシタの容量は前記プルアップトランジスタの寄生キャパシタの容量より大きいことを特徴とする請求項1記載のシフトレジスタ。

**【請求項 3】**

前記第1ノードがフローティングされながら前記寄生キャパシタを通じて伝達した前記第1クロック信号の移行電圧に従って前記第1ノードの電圧が変化する前に、または前記第1ノードの電圧変化とおおよそ同一な時点に、前記第1ノードの電圧は前記第2クロック信号の移行電圧に従って反対方向に変わることを特徴とする請求項2記載のシフトレジスタ。20

**【請求項 4】**

前記制御部は、前記第2クロック信号に応答して前記スタートパルスを前記第1ノードに供給する第1トランジスタと、前記第2クロック信号に応答して第2駆動電圧を前記第2ノードに供給する第2トランジスタと、前記第1クロック信号に応答して前記第2ノードに前記第1駆動電圧を供給する第3トランジスタと、前記第1ノードの電圧に応答して前記第1駆動電圧を前記第3トランジスタに供給する第4トランジスタとを具備することを特徴とする請求項1記載のシフトレジスタ。

**【請求項 5】**

前記シフトレジスタは硝子基板上に形成されることを特徴とする請求項1記載のシフトレジスタ。30

**【請求項 6】**

前記ステージのそれぞれは、第3ノードにより制御された前記出力ラインと前記第1駆動電圧の供給ラインの間で前記第1プルダウントランジスタと並列接続された第2プルダウントランジスタをさらに具備することを特徴とする請求項1記載のシフトレジスタ。

**【請求項 7】**

前記制御部は、前記第2クロック信号に応答して前記スタートパルスを前記第1ノードに供給するための第1ノード制御部と、前記第1及び第2クロック信号に応答して第4ノードの電圧と前記第1駆動電圧を選択的に供給する第2ノード制御部と、前記第1及び第2クロック信号に応答して前記第4ノードの電圧と前記第2駆動電圧を反対の形態で供給するための第3ノード制御部と、前記第1及び第2駆動電圧を前記第4ノードに選択的に供給する第4ノード制御部とを具備することを特徴とする請求項1記載のシフトレジスタ。40

**【請求項 8】**

前記第1ノード制御部は、前記第2クロック信号に応答して前記スタートパルスを前記第1ノードに供給するための第1トランジスタを具備することを特徴とする請求項7記載のシフトレジスタ。

**【請求項 9】**

前記第4ノード制御部は、前記第2クロック信号に応答して第2駆動電圧を前記第4ノードに供給する第2トランジスタと、前記第1クロック信号に応答して前記第4ノードに前記第2駆動電圧を供給する第3トランジスタと、前記第1ノードの電圧に応答して前記第1駆動電圧を前記第4ノードに供給する第4トランジスタとを具備することを特徴とす50

る請求項 7 記載のシフトレジスタ。

【請求項 10】

スタートパルスをシフトさせてシフトされたスタートパルスを次段のステージに供給するシフトレジスタのステージのそれぞれが第1ノードにより制御された第1クロック信号を出力ラインに供給するプルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインに供給する第1プルダウントランジスタと、前記第1及び第2ノードを互いに相反するように制御する制御部と、前記第1ノードと第2クロック信号の入力ラインの間に接続される補償キャパシタとを具備するシフトレジスタの駆動方法において、前記第1ノードをフローティングする段階と、前記補償キャパシタを経由して伝達する前記第2クロック信号の移行電圧に従って反対方向で前記フローティングされた第1ノードの電圧を変化させる段階とを含むことを特徴とするシフトレジスタの駆動方法。10

【請求項 11】

前記フローティングされた第1ノードの電圧を変化させる段階は、前記第1ノードがフローティングされながら前記寄生キャパシタを通じて伝達した前記第1クロック信号の移行電圧に従って前記第1ノードの電圧が変化する前に、または前記第1ノードの電圧変化とおおよそ同一な時点に、遂行されることを特徴とする請求項10記載のシフトレジスタの駆動方法。

【請求項 12】

スタートパルスをシフトさせてシフトされたスタートパルスを次段のステージに出力する多数のステージから構成されたシフトレジスタを有する液晶表示パネルの駆動装置において、前記多数のステージのそれぞれは、第1ノードにより制御された第1クロック信号を出力ラインに供給するプルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインに供給する第1プルダウントランジスタと、前記第1及び第2ノードを互いに相反するように制御する制御部と、前記第1ノードと第2クロック信号の入力ラインの間に接続される補償キャパシタとを具備し、前記第2クロック信号は前記第1クロック信号と異なることを特徴とする液晶表示パネルの駆動装置。20

【請求項 13】

前記シフトレジスタは硝子基板上に形成されることを特徴とする請求項12記載の液晶表示パネルの駆動装置。

【請求項 14】

前記ステージのそれぞれの出力ラインは前記液晶表示パネルのゲートラインに接続されることを特徴とする請求項12記載の液晶表示パネルの駆動装置。30

【請求項 15】

スタートパルスをシフトさせた出力信号を次の段のスタートパルスとして供給する多数のステージから構成されたシフトレジスタにおいて、前記多数のステージのそれぞれは、第1ノードにより制御された第1クロック信号を出力ラインに供給するプルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインに供給するプルダウントランジスタと、前記第1及び第2ノードを制御する制御部と、前記第1ノードに接続された補償回路部とを具備し、前記補償回路部は前記第1ノードに前記第1駆動電圧を選択的に供給することを特徴とするシフトレジスタ。40

【請求項 16】

前記補償回路部は、前記第1ノードがフローティングされることを選択的に防止することを特徴とする請求項15記載のシフトレジスタ。

【請求項 17】

前記補償回路部は、前記第1ノードがフローティングされる時に前記第1ノードに前記第1駆動電圧を供給することを特徴とする請求項15記載のシフトレジスタ。

【請求項 18】

前記補償回路部は、第2駆動電圧により制御された前記第1クロック信号を第3ノードに供給する第1トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第1ノードに供給する第2トランジスタと、前記第3ノードの電圧により制御さ50

れた前記第1駆動電圧を前記第3ノードに供給する第3トランジスタとを具備することを特徴とする請求項15記載のシフトレジスタ。

【請求項19】

前記補償回路部は、前記第1クロック信号により制御された第2駆動電圧を第3ノードに供給する第1トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第1ノードに供給する第2トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第3ノードに供給する第3トランジスタとを具備することを特徴とする請求項15記載のシフトレジスタ。

【請求項20】

前記補償回路部は、前記第1クロック信号により制御された前記第1クロック信号を第3ノードに供給する第1トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第1ノードに供給する第2トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第3ノードに供給する第3トランジスタとを具備することを特徴とする請求項15記載のシフトレジスタ。

【請求項21】

スタートパルスをシフトさせてシフトされたスタートパルスを次段のステージに供給する多数のステージから構成されたシフトレジスタを駆動する方法であって、前記多数のステージのそれぞれは、第1ノードにより制御された第1クロック信号を出力ラインで供給するプルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインで供給するプルダウントランジスタと、前記第1及び第2ノードを制御する制御部と、前記第1ノードに接続された補償回路部とを具備し、前記方法は、前記補償回路部を利用して前記第1ノードに前記第1駆動電圧を選択的に供給する段階を含むことを特徴とするシフトレジスタの駆動方法。

【請求項22】

前記第1駆動電圧は、前記第1ノードがフローティングされることを防止するために前記第1ノードに選択的に供給されることを特徴とする請求項21記載のシフトレジスタの駆動方法。

【請求項23】

前記第1ノードに前記第1駆動電圧を選択的に供給する段階は、前記第1ノードがフローティングされる時に遂行されることを特徴とする請求項21記載のシフトレジスタの駆動方法。

【請求項24】

スタートパルスをシフトさせてシフトされたスタートパルスを次段のステージに出力する多数のステージから構成されたシフトレジスタを有する液晶表示パネルの駆動装置において、前記多数のステージのそれぞれは、第1ノードにより制御された第1クロック信号を出力ラインに供給するプルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインに供給するプルダウントランジスタと、前記第1及び第2ノードを制御する制御部と、前記第1ノードに接続された補償回路部とを具備し、前記補償回路部は前記第1ノードに前記第1駆動電圧を選択的に供給することを特徴とする液晶表示パネルの駆動装置。

【請求項25】

前記シフトレジスタは硝子基板上に形成されることを特徴とする請求項24記載の液晶表示パネルの駆動装置。

【請求項26】

前記ステージのそれぞれの出力ラインは、前記液晶表示パネルのゲートラインに接続されることを特徴とする請求項24記載の液晶表示パネルの駆動装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置の駆動回路に関し、特にアモルファスシリコン薄膜トランジスタ

10

20

30

40

50

(amorphous silicon thin film transistor)を利用したシフトレジスタとその駆動方法に関するものである。また、本発明は前記シフトレジスタを利用した液晶表示パネルの駆動装置に関するものである。

#### 【背景技術】

##### 【0002】

テレビ及びコンピューターの表示装置で使われる液晶表示装置は、電界を利用して液晶の光透過率を調節することによって画像を表示する。このために、液晶表示装置は、液晶セルがマトリックス形態に配列された液晶パネルと、液晶パネルを駆動するための駆動回路を具備する。

##### 【0003】

液晶パネルにはゲートラインとデータラインが交差するように配列され、そのゲートラインとデータラインの交差で用意される領域に液晶セルが位置する。この液晶パネルには液晶セルのそれぞれに電界を印加するための画素電極と共に通電極が用意される。画素電極のそれぞれはスイッチング素子である薄膜トランジスタのソース及びドレイン端子を経由してデータラインのいずれか一つに接続される。薄膜トランジスタのゲート端子はゲートラインのいずれか一つに接続される。

##### 【0004】

駆動回路は、ゲートラインを駆動するためのゲートドライバと、データラインを駆動するためのデータドライバとを具備する。ゲートドライバは、スキャン信号をゲートラインに順次に供給して液晶パネル上の液晶セルを順次に駆動する。データドライバは、ゲートラインのいずれか一つにスキャン信号が供給される度に、データラインのそれぞれにビデオ信号を供給する。これによって、液晶表示装置は、液晶セル別にビデオ信号に従って、画素電極と共に通電極の間に印加される電界により光透過率を調節して画像を表示する。

##### 【0005】

このような駆動回路で、ゲートドライバは、シフトレジスタを利用してゲートラインを順次に駆動させるためのスキャン信号を発生する。さらに、データドライバは、シフトレジスタを利用して、外部から入力されるビデオ信号を一定単位ずつ順次にサンプリングすることができるようとするサンプリング信号を発生する。

##### 【0006】

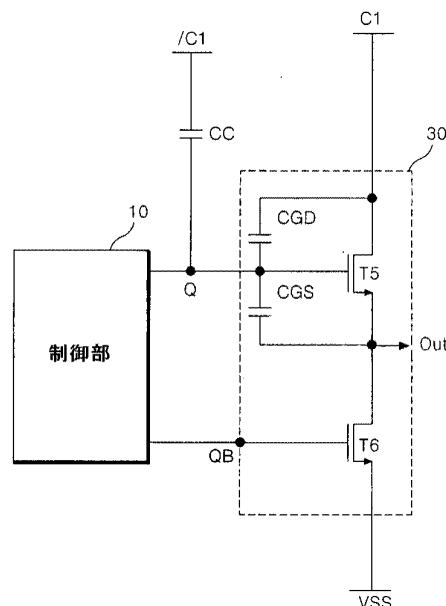

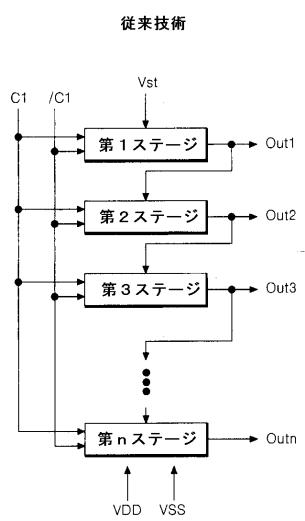

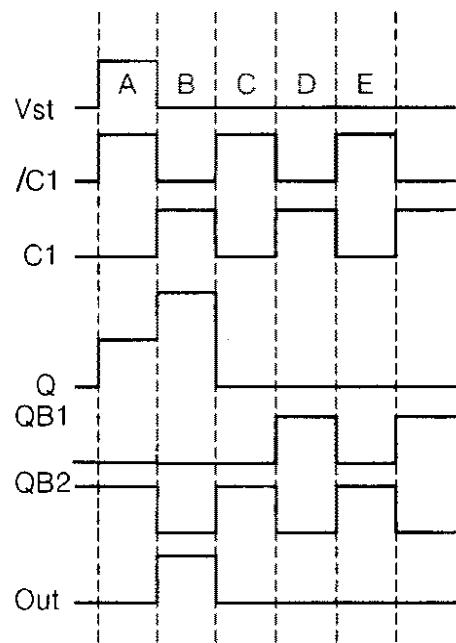

図1は一般的な2像シフトレジスタを図示したブロック図であり、図1に図示されたシフトレジスタは、従属的に接続された第1乃至第nステージを具備する。

##### 【0007】

第1乃至第nステージには、高電位及び高電位駆動電圧(図示しない)と一緒に第1クロック信号(C1)及び第2クロック信号(/C1)が共通に供給され、スタートパルス(Vst)または前全段ステージの出力信号が供給される。第1ステージはスタートパルス(Vst)と第1クロック信号(C1)及び第2クロック信号(/C1)に応答して第1出力信号(Out1)に出力する。さらに、第2乃至第nステージは前段ステージの出力信号と第1クロック信号(C1)及び第2クロック信号(/C1)に応答して第2乃至第n出力信号(Out2乃至Outn)のそれぞれを出力する。このような第1乃至第nステージは同一の回路構成を有し、スタートパルス(Vst)の特定電圧を順次にシフトさせる。第1乃至第n出力信号(Out1乃至Outn)は液晶パネルのゲートラインを順次に駆動するためのスキャン信号に供給されるか、データドライバ内からビデオ信号を順次にサンプリングするためのサンプリング信号に供給される。

##### 【0008】

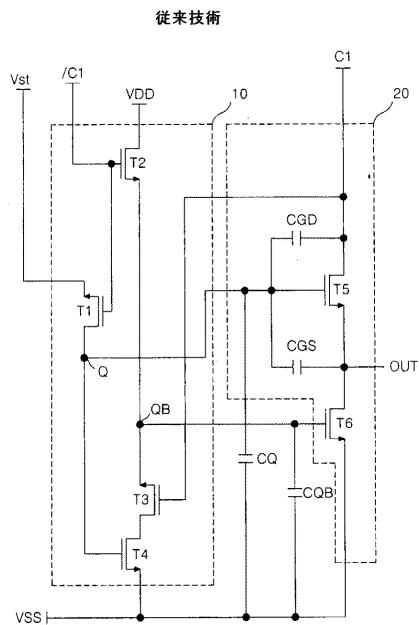

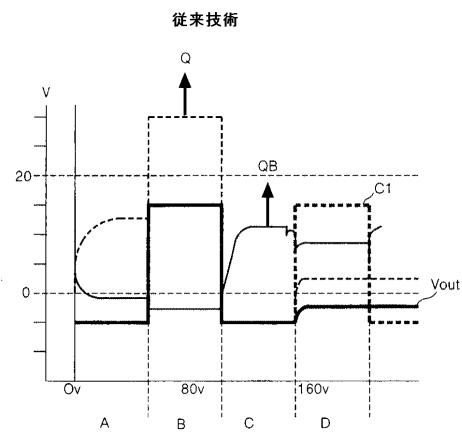

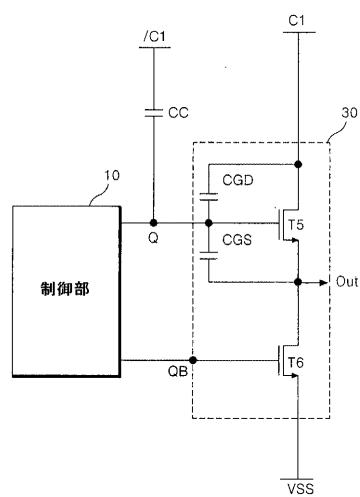

図2は図1に図示された1ステージの具体的な回路構成を示したものである。

図2に図示されたステージはQノードの制御により第1クロック信号(C1)を出力ラインに出力する第5 NMOSトランジスタ(T5)と、QBノードの制御により低電位駆動電圧(VSS)を出力ラインに出力する第6 NMOSトランジスタ(T6)から構成された出力バッファ部20と、QノードとQBノードを制御する第1乃至第4 NMOSトランジスタ(T1乃至T4)から構成された制御部10とを具備する。

##### 【0009】

10

20

30

40

50

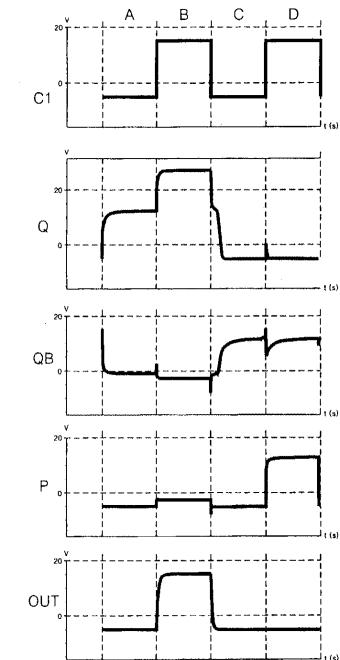

このようなステージには高電位及び低電位電圧(VDD,VSS)が供給されると同時にスタートパルス(Vst)、第1クロック信号(C1)及び第2クロック信号(/C1)が供給される。ここで、第1クロック信号(C1)では図3のように一定のパルス幅を持つハイ状態電圧及びロー状態電圧が交番的に供給されて、第2クロック信号(/C1)(図示しない)が第1クロック信号(C1)と相反した極性を持つように供給される。スタートパルス(Vst)は外部から供給されるか、前段ステージの出力信号が供給される。以下、ステージの動作過程を図3に図示された駆動波形を参照して説明する事にする。

## 【0010】

A期間で第2クロック信号(/C1)のハイ電圧と同期してスタートパルス(Vst)のハイ電圧が供給される。これによって、第2クロック信号(/C1)のハイ電圧により第1NMOSトランジスタ(T1)がターン-オンされてスタートパルス(Vst)のハイ電圧がQノードで供給、すなわちプレチャージ(pre-charge)される。Qノードでプレチャージされたハイ電圧により第5NMOSトランジスタ(T5)がターン-オンされて第1クロック信号(C1)のロー電圧を出力ラインに供給する。この時、第2NMOSトランジスタ(T2)も第2クロック信号(/C1)のハイ電圧によりターン-オンされてQBノードに高電位駆動電圧(VDD)を供給して、QBノードに供給された高電位駆動電圧(VDD)により第6NMOSトランジスタ(T6)もターン-オンされて低電位駆動電圧(VSS)を供給する。これによって、A期間でステージの出力ラインはロー状態の出力信号(OUT)を出力するようになる。

## 【0011】

B期間で第2クロック信号(/C1)のロー電圧により第1NMOSトランジスタ(T1)がターン-オフされることによってQノードはハイ状態にフローティングされるから第5NMOSトランジスタ(T5)はターン-オン状態を維持する。この時、第1クロック信号(C1)にハイ電圧が供給されるに従ってフローティングされたQノードは第5NMOSトランジスタ(T5)のゲート電極とソース電極の重畠に形成された寄生キャパシタ(CGS)の影響でブートストラッピング(Bootstrapping)される。これによって、Qノード電圧がもっと上昇して第5NMOSトランジスタ(T5)がはっきりとターン-オンされることによって第1クロック信号(C1)のハイ電圧が出力ラインに早く供給される。そして、ハイ状態にフローティングされたQノードにより第4NMOSトランジスタ(T4)が、ハイ状態の第1クロック信号(C1)により第3NMOSトランジスタ(T3)がターン-オンされてQBノードには低電位駆動電圧(VSS)が供給されるから第6NMOSトランジスタ(T6)はターン-オフされる。これによって、B期間でステージの出力ラインはハイ状態の出力信号(OUT)を出力する。

## 【0012】

C期間で第2クロック信号(/C1)のハイ電圧により第1NMOSトランジスタ(T1)がターン-オンされてスタートパルス(Vst)のロー電圧がQノードに供給されるから第5NMOSトランジスタ(T5)はターン-オフされる。この時、第2クロック信号(/C1)のハイ電圧により第2NMOSトランジスタ(T2)がターン-オンされて高電位駆動電圧(VDD)がQBノードに供給されることによって第6NMOSトランジスタ(T6)がターン-オンされて低電位駆動電圧(VSS)を出力ラインに出力する。この時、第3NMOSトランジスタ(T3)は第1クロック信号(C1)のロー電圧によりターン-オフされて、第4NMOSトランジスタ(T4)はQノードのロー電圧によりターン-オフされてQBノードに高電位駆動電圧(VDD)が維持される。これによって、C期間でステージの出力ラインはロー状態の出力信号(OUT)を出力する。

## 【0013】

D期間で第2クロック信号(/C1)のロー電圧により第1NMOSトランジスタ(T1)がターン-オフされるからQノードはロー状態にフローティングされる。さらに、第2クロック信号(/C1)のロー電圧により第2NMOSトランジスタ(T2)がターン-オフ、ロー状態にフローティングされたQノードにより第4NMOSトランジスタ(T4)がターン-オフされるから、QBノードは第1クロック信号(C1)のハイ電圧により第3NMOSトランジスタ(T3)がターン-オンされても前の期間(C)で供給された高電位駆動電圧(VDD)より少し低くなったハイ状態を維持しながらフローティングされる。これによって、第6NMOSトランジスタ(T6)はターン-オン状態を維持して低電位駆動電圧(VSS)を出力ラインに出力する。この結果、D

10

20

30

40

50

期間でステージの出力ラインはロー状態の出力信号(OUT)を出力する。

【0014】

そして、他の期間では前記C期間及びD期間が交番的に反復されるからステージの出力信号(OUT)はずっとロー状態を維持するようになる。

【発明の開示】

【発明が解決しようとする課題】

【0015】

ここで、アモルファスシリコン薄膜トランジスタ工程に形成される第1乃至第6 NMOSトランジスタ(T1乃至T6)のそれぞれはゲート電極がソース及びドレイン電極のそれぞれと重畳される構造を持つようになるから不可避にも寄生キャパシタ(CGD,CGS)を含む。そして、アモルファスシリコン薄膜トランジスタの低い移動度を償うために出力バッファ部20を構成する第5及び第6 NMOSトランジスタ(T5,T6)の大きさがよほど大きくなることによって、それによって寄生キャパシタ(CGD,CGS)も増加するようになる。ここで、ブルアップトランジスタ(pull-up transistor)である第5 NMOSトランジスタ(T5)でゲート電極とソース電極の重畳部に形成された寄生キャパシタ(CGS)はQノードをブーストロッピングさせるのに有用になる。反面に、第5 NMOSトランジスタ(T5)のゲート電極とドレイン電極の重畳部に形成された寄生キャパシタ(CGD)はドレイン電極に供給される第1クロック信号(C1)が図3のようにローからハイに移行(transition)する度にフローティング状態であるQノードの電圧を変動させることによって出力電圧(Vout)も揺れる問題点がある。

図3を参照すると、D期間からハイ電圧に移行した第1クロック信号(C1)により、ロー状態にフローティングされたQノードの電圧が少し高い状態で変わって、それによって出力電圧(OUT)もロー電圧で少し上昇することを分かる。このように歪曲された出力電圧(OUT)は次のステージの入力で使われるから多数のステージを経るほど出力電圧(OUT)の歪曲量が増加するようになって、どの時点では回路誤動作を持って来ることがある問題点がある。

【課題を解決するための手段】

【0016】

したがって、本発明の目的は出力バッファ部を制御するノード(Q)の電圧が薄膜トランジスタの寄生キャパシタにより変動されることを防止することができるシフトレジスタとその駆動方法を提供するものである。

【0017】

本発明の他の目的は前記シフトレジスタを利用した液晶表示パネルの駆動装置を提供するものである。

【0018】

上記目的を達成するために、本発明の第1実施例に係るシフトレジスタのステージのそれぞれは、第1ノードにより制御された第1クロック信号を出力ラインに供給するブルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインに供給する第1プルダウントランジスタ(pull-down transistor)と、前記第1及び第2ノードを互いに相反するように制御する制御部と、前記第1ノードと第2クロック信号の入力ラインの間に接続される補償キャパシタとを具備し、前記第2クロック信号は前記第1クロック信号と異なる。

【0019】

前記補償キャパシタの容量は前記ブルアップトランジスタの寄生キャパシタの容量より大きい。

前記第1ノードがフローティングされながら前記寄生キャパシタを通じて伝達した前記第1クロック信号の移行電圧に従って前記第1ノードの電圧が変化する前に、または前記第1ノードの電圧変化とおおよそ同一な時点に、前記第1ノードの電圧は前記第2クロック信号の移行電圧に従って反対方向に変わる。

【0020】

前記制御部は、前記第2クロック信号に応答して前記スタートパルスを前記第1ノード

10

20

30

40

50

で供給する第1トランジスタと、前記第2クロック信号に応答して第2駆動電圧を前記第2ノードで供給する第2トランジスタと、前記第1クロック信号に応答して前記第2ノードに前記第1駆動電圧を供給する第3トランジスタと、前記第1ノードの電圧に応答して前記第1駆動電圧を前記第3トランジスタで供給する第4トランジスタとを具備する。

## 【0021】

前記ステージのそれぞれは、第3ノードにより制御された前記出力ラインと前記第1駆動電圧の供給ラインの間で前記第1プルダウントランジスタと並列接続された第2プルダウントランジスタをさらに具備する。

## 【0022】

前記制御部は、前記第2クロック信号に応答して前記スタートパルスを前記第1ノードに供給するための第1ノード制御部と、前記第1及び第2クロック信号に応答して第4ノードの電圧と前記第1駆動電圧を選択的に供給する第2ノード制御部と、前記第1及び第2クロック信号に応答して前記第4ノードの電圧と前記第2駆動電圧を反対の形態で供給するための第3ノード制御部と、前記第1及び第2クロック信号と前記第1ノードの電圧に応答して前記第1及び第2駆動電圧を前記第4ノードに選択的に供給する第4ノード制御部とを具備する。

## 【0023】

前記第1ノード制御部は前記第2クロック信号に応答して前記スタートパルスを前記第1ノードに供給するための第1トランジスタを具備する。

## 【0024】

前記第4ノード制御部は前記第2クロック信号に応答して第2駆動電圧を前記第4ノードに供給する第2トランジスタと、前記第1クロック信号に応答して前記第4ノードに前記第2駆動電圧を供給する第3トランジスタと、前記第1ノードの電圧に応答して前記第1駆動電圧を前記第4ノードに供給する第4トランジスタとを具備する。

## 【0025】

本発明の第1実施例に係るシフトレジスタの駆動方法は前記第1ノードをフローティングする段階と、前記補償キャパシタを経由して伝達する前記第2クロック信号の移行電圧に従って反対方向で前記フローティングされた第1ノードの電圧を変化させる段階とを含む。

## 【0026】

前記フローティングされた第1ノードの電圧を変化させる段階は、前記第1ノードがフローティングされながら前記寄生キャパシタを通じて伝達した前記第1クロック信号の移行電圧に従って前記第1ノードの電圧が変化する前に、または前記第1ノードの電圧変化とおよそ同一な時点に遂行される。

## 【0027】

本発明の第1実施例に係る液晶表示パネルの駆動装置において、シフトレジスタのステージのそれぞれは第1ノードにより制御された第1クロック信号を出力ラインに供給するためのプルアップトランジスタ、第2ノードにより制御された第1駆動電圧を前記出力ラインに供給するための第1プルダウントランジスタ、前記第1及び第2ノードを互いに相反するように制御する制御部、及び前記第1ノードと第2クロック信号の入力ラインの間に接続される補償キャパシタを具備し、前記第2クロック信号は前記第1クロック信号と異なる。

## 【0028】

本発明の第2実施例に係るシフトレジスタのステージのそれぞれは、第1ノードにより制御された第1クロック信号を出力ラインで供給するためのプルアップトランジスタと、第2ノードにより制御された第1駆動電圧を前記出力ラインで供給するためのプルダウントランジスタと、前記第1及び第2ノードを制御するための制御部と、前記第1ノードに接続された補償回路部とを具備し、前記補償回路部は前記第1ノードに前記第1駆動電圧を選択的に供給する。

## 【0029】

10

20

30

40

50

前記補償回路部は前記第1ノードがフローティングされることを選択的に防止する。

前記補償回路部は前記第1ノードがフローティングされる時に前記第1ノードに前記第1駆動電圧を供給する。

#### 【0030】

前記補償回路部は、第2駆動電圧により制御された前記第1クロック信号を第3ノードに供給する第1トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第1ノードに供給する第2トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第3ノードに供給する第3トランジスタとを具備する。

#### 【0031】

前記補償回路部は、前記第1クロック信号により制御された第2駆動電圧を第3ノードに供給する第1トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第1ノードに供給する第2トランジスタと、前記第3ノードの電圧により制御された前記第1駆動電圧を前記第3ノードに供給する第3トランジスタとを具備する。

#### 【0032】

前記補償回路部は、前記第1クロック信号により制御された前記第1クロック信号を第3ノードに供給する第1トランジスタと、前記第3ノードの電圧により制御されて前記第1駆動電圧を前記第1ノードに供給する第2トランジスタと、前記第3ノードの電圧により制御されて前記第1駆動電圧を前記第3ノードに供給する第3トランジスタとを具備する。

#### 【0033】

本発明の第2実施例に係るシフトレジスタの駆動方法は前記補償回路部を利用して前記第1ノードに前記第1駆動電圧を選択的に供給する段階を含む。

前記第1駆動電圧は前記第1ノードがフローティングされることを防止するために前記第1ノードに選択的に供給される。

前記第1ノードに前記第1駆動電圧を選択的に供給する段階は、前記第1ノードがフローティングされる時に遂行される。

#### 【0034】

本発明の第2実施例に係る液晶表示パネルの駆動装置において、シフトレジスタのステージのそれぞれは、第1ノードにより制御されて第1クロック信号を出力ラインで供給するためのプルアップトランジスタと、第2ノードにより制御されて第1駆動電圧を前記出力ラインで供給するためのプルダウントランジスタと、前記第1及び第2ノードを制御するための制御部と、前記第1ノードに接続された補償回路部とを具備して、前記補償回路部は前記第1ノードに前記第1駆動電圧を選択的に供給する。

#### 【0035】

前記シフトレジスタは硝子基板上に形成される。

前記ステージのそれぞれの出力ラインは前記液晶表示パネルのゲートラインに接続される。

#### 【発明の効果】

#### 【0036】

本発明に係るシフトレジスタは反転クロック信号及び補償キャパシタを利用してプルアップトランジスタの制御ノード(Q)がクロック信号に従って変わることを防止することによって出力電圧の歪曲を減少させることができるようになる。これによって、出力電圧の歪曲による回路誤動作を防止することができるようになる。

#### 【発明を実施するための最良の形態】

#### 【0037】

以下、本発明の望ましい実施例を図4乃至図12を参照して説明する事にする。

#### 【実施例】

#### 【0038】

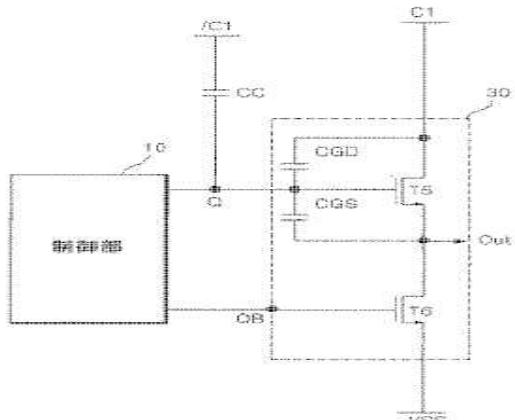

図4は本発明の第1実施例に係るシフトレジスタで従属的に接続された多数のステージの中からいざれか一つのステージを出力バッファ部30の中心に図示し、図5は駆動波形

10

20

30

40

50

図を図示したものである。

図4に図示されたシフトレジスタのステージは、Qノードの制御に1クロック信号(C1)を出力ラインに出力する第5NMOSトランジスタ(T5)と、QBノードの制御により低電位駆動電圧(VSS)を出力ラインに出力する第6NMOSトランジスタ(T6)から構成された出力バッファ部20と、QノードとQBノードを制御する制御部10と、Qノードの変動電圧を償うための補償キャパシタ(CC)とを具備する。このようなシフトレジスタはLCDの硝子基板上に直接形成される。

#### 【0039】

補償キャパシタ(CC)はQノードと第2クロック信号(/C1)の供給ラインの間に接続される。これによって、補償キャパシタ(CC)はブルアップトランジスタである第5NMOSトランジスタ(T5)のゲート電極とドレイン電極の重畠部に形成された寄生キャパシタ(CGD)とは相反した電圧がQノードに印加されることによってQノードの変動を防止するようになる。具体的に、図5のようにC及びD期間のエッジ部で第1クロック信号(C1)がローからハイに移行する前に、第2クロック信号(/C1)及び補償キャパシタ(CC)によりQノードは第1クロック信号(C1)と反対方向に変わることになる。これは補償キャパシタ(CC)の容量が寄生キャパシタ(CGD)より大きく設定されることによってQノードが第1クロック信号(C1)の移行より第2クロック信号(/C1)の移行に先に応答するからである。これによって、第1クロック信号(C1)がハイ電圧に移行する時は第5NMOSトランジスタ(T5)の寄生キャパシタ(CGD)によりQノードはほとんど元々状態のロー電圧で戻ることができるようになる。この結果、出力電圧(OUT)の歪曲を減少させることができるようになる。

10

20

30

#### 【0040】

図4で、制御部10は、図2に図示したように第1乃至第4NMOSトランジスタ(T1乃至T4)から構成されるか、Qノード及びQBノードを制御することができるいかなる構成も可能である。ここでは説明上の便宜上、制御部40が図2に図示された制御部10と同一な構成を持つ場合のみを例あげて、図5に図示された駆動波形を参照して説明する事にする。

#### 【0041】

A期間で第2クロック信号(/C1)のハイ電圧と同期してスタートパルス(Vst)のハイ電圧が供給される。これによって、第2クロック信号(/C1)のハイ電圧により第1NMOSトランジスタ(T1)がターン-オンされてスタートパルス(Vst)のハイ電圧がQノードで供給、すなわちプレチャージされる。Qノードでプレチャージされたハイ電圧により第5NMOSトランジスタ(T5)がターン-オンされて第1クロック信号(C1)のロー電圧を出力ラインに供給する。この時、第2NMOSトランジスタ(T2)も第2クロック信号(/C1)のハイ電圧によりターン-オンされてQBノードに高電位電圧(VDD)を供給して、QBノードに供給された高電位電圧(VDD)により第6NMOSトランジスタ(T6)もターン-オンされて低電位電圧(VSS)を供給する。これによって、A期間でステージの出力ラインはロー状態の出力信号(OUT)を出力するようになる。

40

#### 【0042】

B期間で第2クロック信号(/C1)のロー電圧により第1NMOSトランジスタ(T1)がターン-オフされることによってQノードはハイ状態にフローティングされるから第5NMOSトランジスタ(T5)はターン-オン状態を維持する。この時、第1クロック信号(C1)にハイ電圧が供給されることによってフローティングされたQノードは第5NMOSトランジスタ(T5)のゲート電極とソース電極の重畠に形成された寄生キャパシタ(CGS)の影響でブートストラッピング(Bootstrapping)される。これによって、Qノード電圧がもっと上昇して第5NMOSトランジスタ(T5)がはっきりとターン-オンされることによって第1クロック信号(C1)のハイ電圧が出力ラインに早く供給される。さらに、ハイ状態にフローティングされたQノードにより第4NMOSトランジスタ(T4)が、ハイ状態の第1クロック信号(C1)により第3NMOSトランジスタ(T3)がターン-オンされてQBノードには低電位電圧(VSS)が供給されるから第6NMOSトランジスタ(T6)はターン-オフされる。これによって、B期間でステージの出力ラインはハイ状態の出力信号(OUT)を出力する。

50

## 【 0 0 4 3 】

C期間で第2クロック信号(/C1)のハイ電圧により第1NMOSトランジスタ(T1)がターン-オンされてスタートパルス(Vst)のロー電圧がQノードに供給されるから第5NMOSトランジスタ(T5)はターン-オフされる。この時、第2クロック信号(/C11)のハイ電圧により第2NMOSトランジスタ(T2)がターン-オンされて高電位電圧(VDD)がQBノードに供給されることによって第6NMOSトランジスタ(T6)がターン-オンされて低電位電圧(VSS)を出力ラインに出力する。この時、第3NMOSトランジスタ(T3)は第1クロック信号(C1)のロー電圧によりターン-オフされて、第4NMOSトランジスタ(T4)はQノードのロー電圧によりターン-オフされてQBノードに高電位電圧(VDD)が維持される。これによって、C期間でステージの出力ラインはロー状態の出力信号(OUT)を出力する。

10

## 【 0 0 4 4 】

D期間で第2クロック信号(/C1)のロー電圧により第1NMOSトランジスタ(T1)がターン-オフされるからQノードはロー状態にフローティングされる。さらに、第2クロック信号(/C1)のロー電圧により第2NMOSトランジスタ(T2)がターン-オフ、ロー状態にフローティングされたQノードにより第4NMOSトランジスタ(T4)がターン-オフされるから、QBノードは第1クロック信号(C1)のハイ電圧により第3NMOSトランジスタ(T3)がターン-オンされても前の期間(C)で供給された高電位電圧(VDD)より少し低くなったハイ状態を維持しながらフローティングされる。これによって、第6NMOSトランジスタ(T6)はターン-オン状態を維持して低電位電圧(VSS)を出力ラインに出力する。この結果、D期間でステージの出力ラインはロー状態の出力信号(OUT)を出力する。

20

## 【 0 0 4 5 】

特に、D期間の手始め点で第5NMOSトランジスタ(T5)の寄生キャパシタ(CGD)を通じてローからハイに移行された第1クロック信号(C1)が伝達する前に、ハイでローに移行された第2クロック信号(/C1)が補償キャパシタ(CC)を通じてQノードに伝達する。これによって、Qノードの電圧は下降する第2クロック信号(/C1)に従ってもっと低くなった後、上昇する第1クロック信号(C1)に従って元々状態のロー電圧に戻ることができるようになる。この結果、出力電圧(OUT)の歪曲を減少させることができる。

さらに、他の期間では前記C期間及びD期間が交番的に反復されるからステージの出力信号(OUT)はずっと歪曲がほとんどないロー状態を維持するようになる。

30

## 【 0 0 4 6 】

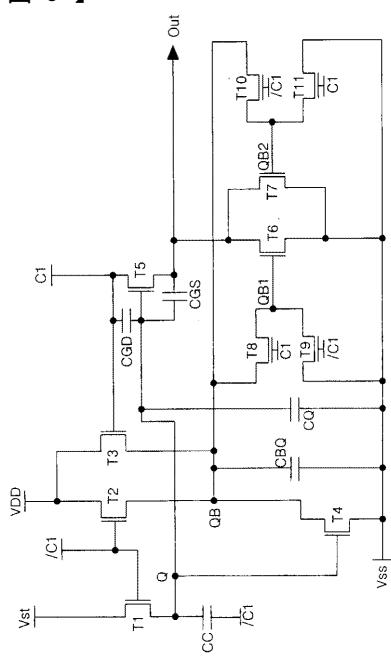

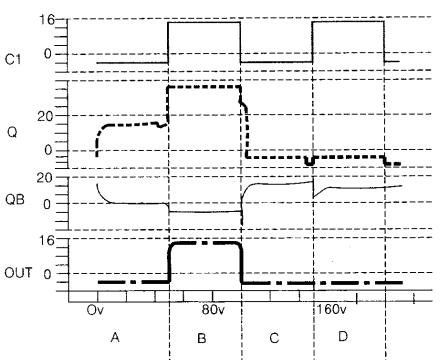

図6は本発明の第2実施例に係るシフトレジスタの中で従属的に接続された多数のステージの中からいざれか一つのステージの詳細回路を図示したことで、図7は駆動波形図を図示したものである。

## 【 0 0 4 7 】

図6に図示されたシフトレジスタの各ステージは、Qノードの制御により第1クロック信号(C1)を出力ラインに出力する第5NMOSトランジスタ(T5)と、QB1及びQB2ノードの制御により低電位駆動電圧(VSS)を出力ラインに出力する第6及び第7NMOSトランジスタ(T6,T7)を具備する出力バッファと、Qノードを制御する第1NMOSトランジスタ(T1)を具備するQノード制御部と、QBノードを制御する第2乃至第4NMOSトランジスタ(T2,T3,T4)を具備するQBノード制御部と、QB1ノードを制御する第8及び第9NMOSトランジスタ(T8,T9)を具備するQB1ノード制御部と、QB2ノードを制御する第10及び第11NMOSトランジスタ(T10,T11)を具備するQB2ノード制御部と、Qノードの変動電圧を償うための補償キャパシタ(CC)とを具備する。

40

## 【 0 0 4 8 】

出力バッファで、プルアップトランジスタである第5NMOSトランジスタ(T5)は、第1クロック信号(C1)の入力ラインとステージの出力ラインの間に接続されてQノードにより制御される。そして、プルダウントランジスタである第6及び第7NMOSトランジスタ(T6,T7)は、ステージの出力ラインと低電位電圧(VSS)の入力ラインの間に並列接続されてQB1及びQB2ノードのそれぞれにより制御される。

## 【 0 0 4 9 】

50

Qノード制御部の第1 NMOSトランジスタ(T1)はスタートパルス(Vst)の入力ラインとQノードの間に接続されて第2クロック信号(/C1)により制御される。

【 0 0 5 0 】

QB ノード制御部の第 2 NMOSトランジスタ(T2)は、高電位駆動電圧(VDD)の供給ラインと QB ノードの間に接続されて第 2 クロック信号により制御されて、第 3 NMOSトランジスタ(T3)は第 2 NMOSトランジスタ(T2)と並列接続されて第 1 クロック信号(C1)により制御されて、第 4 NMOSトランジスタ(T4)はQB ノードと低電位電圧(VSS)の入力ラインの間に接続されてQノードにより制御される。

【 0 0 5 1 】

QB1ノード制御部の第8NMOSトランジスタ(T8)はQBノードとQB1ノードの間に接続され、第1クロック信号(C1)により制御されて、第9NMOSトランジスタ(T9)は低電位電圧(VSS)の入力ラインとQB1ノードの間に接続されて第2クロック信号(/C1)により制御される。

【 0 0 5 2 】

QB2ノード制御部の第10NMOSトランジスタ(T10)はQBノードとQB2ノードの間に接続されて第2クロック信号(C1)により制御されて、第11NMOSトランジスタ(T11)は低電位電圧(VSS)の入力ラインとQB2ノードの間に接続されて第2クロック信号(/C1)により制御される。

[ 0 0 5 3 ]

Qノードと低電位電圧(VSS)の入力ラインの間に接続されたキャパシタ(CB)と、QBノードと低電位電圧(VSS)の入力ラインの間に接続されたキャパシタ(CQB)はQノード及びQBノードのノイズを除去する。

[ 0 0 5 4 ]

このようなステージの動作過程を図7に図示された駆動波形を参照して説明する事にする。

[ 0 0 5 5 ]

A期間でスタートパルス( $V_{st}$ )のハイ電圧により第1 NMOSトランジスタ(T1)がターン-オンされて高電位駆動電圧(VDD)がQノードに供給されて、Qノードはハイ状態にプレチャージされる。ハイ状態にプレチャージされたQノードにより第5 NMOSトランジスタ(T5)がターン-オンされて第1クロック信号(C1)のロー電圧が出力ラインに供給される。この時、第2クロック信号(/C1)によりターン-オンされた第2 NMOSトランジスタ(T2)を通じてQBノードには高電位電圧(VDD)が供給される。さらに、第2クロック信号(/C1)により第9及び第10 NMOSトランジスタ(T9, T10)がターン-オンされることによって、QB1ノードには低電位電圧(VSS)が、QB2ノードにはQBノードに供給された高電位電圧(VDD)が供給される。これによって、第7 NMOSトランジスタ(T7)がターン-オンされて出力ラインで低電位電圧(VSS)が供給される。この結果、A期間でステージの出力ラインはロー状態の出力信号(Out)を出力する。

【 0 0 5 6 】

B期間で第2クロック信号( $C_1$ )のロー電圧により第1NMOSトランジスタ( $T_1$ )がターンオフされることによってQノードはハイ状態にフローティングされるから第5NMOSトランジスタ( $T_5$ )はターン-オン状態を維持する。この時、第1クロック信号( $C_1$ )のハイ電圧が供給されることによってフローティングされたQノードは第5NMOSトランジスタ( $T_5$ )のゲートとドレインの間に形成されたキャパシタ(CGS)の影響でブートストラッピング(Bootstrapping)される。これによって、Qノード電圧がもっと上昇して第5NMOSトランジスタ( $T_5$ )が明確にターン-オンされることによって第1クロック信号( $C_1$ )のハイ電圧が出力ラインに早く供給される。この時、第1クロック信号( $C_1$ )により第3NMOSトランジスタ( $T_3$ )はターン-オンされて、ブートストレーピングされたQノードにより第4PMOSトランジスタ( $T_4$ )がターン-オンされることによってQBノードにはロー状態になる。さらに、第1クロック信号( $C_1$ )により第8及び第11NMOSトランジスタ( $T_8, T_{11}$ )がターン-オンされることによって、QB1ノードにはQBノードに供給された低電位電圧(VSS)が、QB2ノードにはハイ電位電圧(VDD)が供給される。

ードには低電位電圧(VSS)が供給される。これによって、第6及び第7 NMOSトランジスタ(T6,T7)はターン-オフされる。この結果、B期間でステージの出力ラインはハイ状態の出力信号(Out)を出力する。

#### 【0057】

C期間で第2クロック信号(/C1)のハイ電圧により第1 NMOSトランジスタ(T1)がターン-オンされてQノードにはスタートパルス(Vst)のロー電圧が供給されるから第5 NMOSトランジスタ(T5)はターン-オフされる。この時、第2クロック信号(/C1)により第2 NMOSトランジスタ(T2)がターン-オンされてQBノードには高電位電圧(VDD)が供給される。さらに、第2クロック信号(/C1)により第9及び第10 NMOSトランジスタ(T9,T10)がターン-オンされることによって、QB1ノードには低電位駆動電圧(VSS)が、QB2ノードにはQBノードに供給された高電位駆動電圧(VDD)が供給される。これによって、第7 NMOSトランジスタ(T7)がターン-オンされて出力ラインで低電位駆動電圧(VSS)が供給される。この結果、C期間でステージの出力ラインはロー状態の出力信号(Out)を出力する。

10

#### 【0058】

D期間で第2クロック信号(/C1)のロー電圧により第1及び第2 NMOSトランジスタ(T1,T2)はターン-オフされる。これによって、Qノードは以前のロー状態にフローティングされるから第5 NMOSトランジスタ(T5)はターン-オフされる。この時、第1クロック信号(C1)のハイ電圧により第3 NMOSトランジスタ(T3)がターン-オンされてQBノードには高電位駆動電圧(VDD)が供給される。そして、第1クロック信号(C1)により第8及び第11 NMOSトランジスタ(T9)がターン-オンされることによって、QB1ノードにはQBノードに供給された高電位電圧(VDD)が、QB2ノードには低電位電圧(VSS)が供給される。これによって、第6 NMOSトランジスタ(T6)がターン-オンされて出力ラインで低電位駆動電圧(VSS)を供給する。この結果、B期間でステージの出力ラインはロー状態の出力信号(Out)を出力する。

20

#### 【0059】

さらに、他の期間でもステージは前記C及びD期間と同一に動作するからステージの出力信号(OUT)はロー状態を維持するようになる。

#### 【0060】

このように図6に図示された本発明の第2実施例に係るシフトレジスタの各ステージは第6 NMOSトランジスタ(T6)に相反動作する第7 NMOSトランジスタ(T7)を並列で接続させて、そのゲートノードであるQB1及びQB2ノードを第1クロック信号(C1)及び第2クロック信号(/C1)により交流駆動させるようになる。これは第6及び第7 NMOSトランジスタ(T6,T7)のゲートノードに直流バイアスが印加されることを防止することによって高温駆動の時第6及び第7 NMOSトランジスタ(T6,T7)がゲートバイアスストレスにより誤動作することを防止することができる。

30

#### 【0061】

ところが、図6に図示されたシフトレジスタでは図4に図示されたシフトレジスタと対備して一つのプルダウントランジスタ(T6)が形成されなければならない領域に一番のプルダウントランジスタ(T6,T7)が形成されることによって大きさが減少するしかない。これによって、相対的に小さな大きさを持つようになった第6及び第7 NMOSトランジスタ(T6,T7)を交番的にターン-オンさせて出力電圧(OUT)を充分にロー電圧に保持させることができない場合、すなわち出力電圧(OUT)が歪曲される場合が発生することができる。この時、前述したところのようにプルアップトランジスタである第5 NMOSトランジスタ(T5)の寄生キャパシタ(CGD)及び第1クロック信号(C1)により図8aに図示されたD期間のようにQノードの電圧が変わって出力電圧(OUT)を歪曲させる場合、出力電圧(OUT)の歪曲は増加するしかない。

40

#### 【0062】

これを防止するために、図6に図示されたシフトレジスタの各ステージはQノードと第2クロック信号(/C1)の入力ラインの間に接続された補償キャパシタ(CC)をさらに具備する。補償キャパシタ(CC)は図8bに図示されたD期間のように第5 NMOSトランジスタ(T5)

50

の寄生キャパシタ(CGD)を通じてローでハイに移行された第1クロック信号(C1)が伝達する前に、ハイからローに移行した第2クロック信号(/C1)がQノードに伝達するようになる。これによって、Qノードの電圧は下降する第2クロック信号(/C1)に従ってもっと低くなつた後、上昇する第1クロック信号(C1)に従つて元々状態のロー電圧に戻ることができるようになる。この結果、出力電圧(OUT)の歪曲を減少させることができるようになる。

#### 【0063】

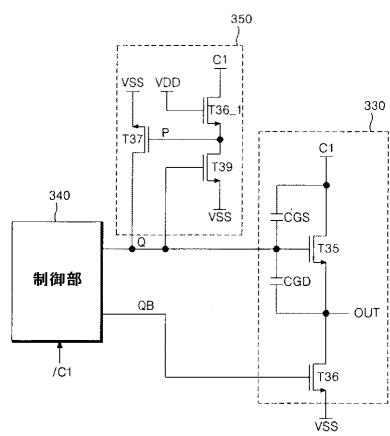

図9は、本発明の第3実施例に係るシフトレジスタで継続的に接続された多数のステージのいずれか一つのステージを出力バッファ部330の中心に図示し、図10はそのステージの駆動波形を図示したものである。

10

#### 【0064】

図9に図示されたシフトレジスタのステージはQノードの制御により第1クロック信号(C1)を出力ラインに出力するプルアップNMOSトランジスタ(T38)と、QBノードの制御により低電位駆動電圧(VSS)を出力ラインに出力するプルダウンNMOSトランジスタ(T39)から構成された出力バッファ部330と、QノードとQBノードを制御する制御部340と、Qノードの変動電圧を償うための補償回路部350とを具備する。このようなシフトレジスタは硝子基板上に直接形成される。

#### 【0065】

補償回路部350はPノードの制御により低電位電圧(VSS)をQノードで供給するための第5NMOSトランジスタ(T35)と、Pノードを制御するための第6及び第7NMOSトランジスタ(T36\_1,T37)とを具備する。第6NMOSトランジスタ(T36\_1)は高電位電圧(VDD)により常にターン-オン状態を維持して第1クロック信号(C1)をPノードに供給する。第7NMOSトランジスタ(T37)はQノードの制御により低電位電圧(VSS)をPノードに供給する。このような補償回路部350は、現ステージでハイ状態の出力(OUT)があった後、第1クロック信号(C1)がハイ状態になる期間(D)ごとにQノードに低電位電圧(VSS)を供給してQノードがロー状態にフローティングされることを防止するようになる。換言すれば、補償回路部350は、Qノードがロー状態にフローティングされることを防止して、プルアップトランジスタ(T38)の第2期生キャパシタ(CGS)のカップルリングによるQノードの電圧変動を防止するようになる。これによって、Qノードの電圧変動による出力信号(OUT)の歪曲を防止することができるようになる。

20

30

#### 【0066】

図9で制御部340は、図2に図示したように、第1乃至第4NMOSトランジスタ(T1乃至T4)から構成されるか、Qノード及びQBノードを制御することができるいかなる構成も可能である。ここでは説明の便宜上に制御部340が図2に図示された制御部10と同一な構成を持つ場合のみを例あげて、図10に図示された駆動波形を参照して説明する事にする。

#### 【0067】

A期間で第1クロック信号(C1)のロー電圧、第2クロック信号(/C1)のハイ電圧、及びスタートパルス(Vst)のハイ電圧が供給される。第2クロック信号(/C1)のハイ電圧により第1NMOSトランジスタ(T1)がターン-オンされてスタートパルス(Vst)のハイ電圧がQノードで供給、すなわちプレチャージされる。Qノードのハイ電圧によりプルアップNMOSトランジスタ(T38)がターン-オンされて第1クロック信号(C1)のロー電圧がステージの出力ラインに供給される。この時、高電位電圧(VDD)によりターン-オン状態を維持する第6NMOSトランジスタ(T36\_1)と、Qノードのハイ電圧によりターン-オンされた第7NMOSトランジスタ(T37)によりPノードには低電位電圧(VSS)が供給されるから第5NMOSトランジスタ(T35)はターン-オフされる。さらに、第2クロック信号(/C1)のハイ電圧により第2NMOSトランジスタ(T2)がターン-オンされてQBノードに高電位電圧(VDD)が供給されるからプルダウンNMOSトランジスタ(T39)がターン-オンされて低電位電圧(VS)がステージの出力ラインに供給される。これによって、A期間でステージの出力ラインはロー状態の出力信号(OUT)を出力するようになる。

40

50

## 【 0 0 6 8 】

B期間で第1クロック信号(C1)のハイ電圧、第2クロック信号(/C1)のロー電圧、及びスタートパルス(Vst)のロー電圧が供給される。第2クロック信号(/C1)のロー電圧により第1NMOSトランジスタ(T1)がターン-オフされてQノードがハイ状態にフローティングされる。ハイ状態にフローティングされたQノードはプルアップNMOSトランジスタ(T3\_8)のゲート電極とソース電極の重畳に形成された第1寄生キャパシタ(CGD)のカップルリング作用で第1クロック信号(C1)のハイ電圧に従ってブートストレッピング(Bootstrapping)される。これによって、Qノード電圧がもっと上昇してプルアップNMOSトランジスタ(T3\_8)が明確にターン-オンされることによって第1クロック信号(C1)のハイ電圧が出力ラインに早く供給される。ここで、Qノードのブートストラッピング効果を高めるために、別途のキャパシタを第1寄生キャパシタ(CGD)と並列に形成する。この場合、ハイ状態のQノードにより第7NMOSトランジスタ(T3\_7)がターン-オンされてPノードには低電位電圧(VSS)が供給されることと同時に、ターン-オン状態を維持する第6PMOSトランジスタ(T3\_6\_1)により第1クロック信号(C1)のハイ電圧が供給される。ここで、第7NMOSトランジスタ(T3\_7)が第6NMOSトランジスタ(T3\_6\_1)より大きく形成することによってPノードに低電位電圧(VSS)が供給されるようにする。例えば、第7NMOSトランジスタ(T3\_7)と第6NMOSトランジスタ(T3\_6\_1)の大きさは、おおよそ3:1位の比を持つように形成される。さらに、ハイ状態のQノードにより第4NMOSトランジスタ(T4)が、ハイ状態の第1クロック信号(C1)により第3NMOSトランジスタ(T3)がターン-オンされてQBノードには低電位電圧(VSS)が供給されるからプルダウンNMOSトランジスタ(T3\_9)はターン-オフされる。これによって、B期間でステージの出力ラインはハイ状態の出力信号(OUT)を出力する。

## 【 0 0 6 9 】

C期間で第1クロック信号(C1)のロー電圧、第2クロック信号(/C1)のハイ電圧、及びスタートパルス(Vst)のロー電圧が供給される。第2クロック信号(/C1)のハイ電圧により第1NMOSトランジスタ(T1)がターン-オンされてスタートパルス(Vst)のロー電圧がQノードに供給されるからプルアップNMOSトランジスタ(T3\_8)はターン-オフされる。さらに、高電位電圧(VDD)によりターン-オン状態を維持する第6NMOSトランジスタ(T3\_6\_1)と、Qノードのロー電圧によりターン-オフされた第7NMOSトランジスタ(T3\_7)によりPノードには低電位電圧(VSS)が供給されるから第5NMOSトランジスタ(T3\_5)はターン-オフされる。この時、第2クロック信号(/C1)のハイ電圧により第2NMOSトランジスタ(T2)がターン-オンされて高電位電圧(VDD)がQBノードに供給されることによってプルダウンNMOSトランジスタ(T3\_9)がターン-オンされて低電位電圧(VSS)が出力ラインに供給される。第3及び第4NMOSトランジスタ(T3,T4)は第1クロック信号(C1)のロー電圧及びQノードのロー電圧のそれぞれによりターン-オフされる。これによって、C期間でステージの出力ラインはロー状態の出力信号(OUT)を出力する。

## 【 0 0 7 0 】

D期間で第1クロック信号(C1)のハイ電圧、第2クロック信号(/C1)のロー電圧、及びスタートパルス(Vst)のロー電圧が供給される。第2クロック信号(/C1)のロー電圧により第1NMOSトランジスタ(T1)がターン-オフされるからQノードは以前のロー状態を維持するから第7NMOSトランジスタ(T3\_7)はターン-オフされる。この時、いつもターン-オン状態を維持する第6NMOSトランジスタ(T3\_6\_1)によりPノードには第1クロック信号(C1)のハイ電圧が供給されるから第5NMOSトランジスタ(T3\_5)がターン-オンされる。これによって、Qノードはターン-オンされた第5NMOSトランジスタ(T3\_5)を通じて供給された低電位電圧(VSS)によりロー状態に固定される。従って、QノードがフローティングされないからプルアップNMOSトランジスタ(T3\_8)の第2寄生キャパシタ(CGS)のカップルリング作用で第1クロック信号(C1)のハイ電圧に従って変動されることを防止することができるようになる。この結果、D期間でQノード電圧の変動による出力信号(OUT)の歪曲を防止することができるようになる。一方、第2クロック信号(/C1)のロー電圧により第2NMOSトランジスタ(T2)がターン-オフ、ロー状態のQノードにより第4NMOSトランジ

10

20

30

40

50

スタ(T4)がターン-オフされるからQBノードは、第1クロック信号(C1)のハイ電圧により第3NMOSトランジスタ(T3)がターン-オンされても前の期間(C)で供給された高電位電圧(VDD)より少し低くなったハイ状態を維持しながらフローティングされる。これによって、プルダウンNMOSトランジスタ(T39)はターン-オン状態を維持して低電位電圧(VSS)を出力ラインで供給する。この結果、D期間でステージの出力ラインはロー状態の出力信号(OUT)を出力する。

#### 【0071】

そして、他の期間では前記C期間及びD期間が交番的に反復されるからステージの出力信号(OUT)はずっと歪曲がないロー状態を維持するようになる。

#### 【0072】

このように、本発明に係るシフトレジスタは補償回路部350を利用してプルアップNMOSトランジスタ(T38)を制御するQノードがD期間でフローティングされることを防止することによってハイ電圧の第1クロック信号(C1)によりQノードの電圧が変わることを防止することができるようになる。

#### 【0073】

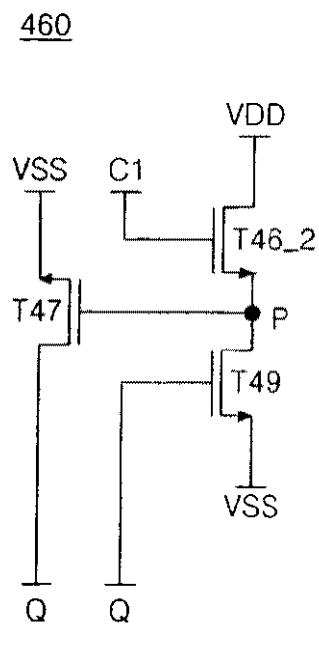

図11は本発明の第4実施例に係る補償回路部460のみを図示したものである。

図11に図示された補償回路部460は第6NMOSトランジスタ(T46\_2)が第1クロック信号(C1)により制御されてPノードに高電位電圧(VSS)を供給することを除いては図9に図示された補償回路部250と同一な構成要素を具備する。

#### 【0074】

A期間で第1クロック信号(C1)のロー電圧により第6NMOSトランジスタ(T46\_2)はターン-オフ、ハイ電圧でプレチャージされたQノードにより第7NMOSトランジスタ(T47)がターン-オンされてPノードには低電位電圧(VSS)が供給される。これによって、第5NMOSトランジスタ(T45)はターン-オフされる。

#### 【0075】

B期間で第1クロック信号(C1)のハイ電圧により第6NMOSトランジスタ(T46\_2)がターンオン、ブートストラッピングにハイ電圧がさらに上昇したQノードにより第7NMOSトランジスタ(T47)がターン-オンされる。この時、第7NMOSトランジスタ(T47)が第6NMOSトランジスタ(T46\_2)より大きい大きさに形成されることによって同時にターン-オンされてもPノードには第6NMOSトランジスタ(T46\_2)を経由した高電位電圧(VDD)よりも第7NMOSトランジスタ(T47)を経由した低電位電圧(VSS)が供給されるから第5NMOSトランジスタ(T45)はターン-オフされる。このために、第7及び第6NMOSトランジスタ(T47,T46\_2)は少なくとも3:1位の大きさの比率を持つように形成される。

#### 【0076】

C期間で第1クロック信号(C1)のロー電圧により第6NMOSトランジスタ(T46\_2)はターン-オフ、ロー電圧に変換されたQノードにより第7NMOSトランジスタ(T47)がターン-オフされるからPノードは以前のロー状態でフローティングされる。これによって、第5NMOSトランジスタ(T45)はターン-オフされる。

#### 【0077】

D期間で第1クロック信号(C1)のハイ電圧により第6NMOSトランジスタ(T46\_2)がターン-オン、ロー電圧であるQノードにより第7NMOSトランジスタ(T47)がターン-オフされるからPノードには高電位電圧(VDD)が供給される。これによって、第5NMOSトランジスタ(T45)がターン-オンされてQノードに低電位電圧(VSS)を供給するからQノードがハイ電圧の第1クロック信号(C1)により変わることを防止することができるようになる。

#### 【0078】

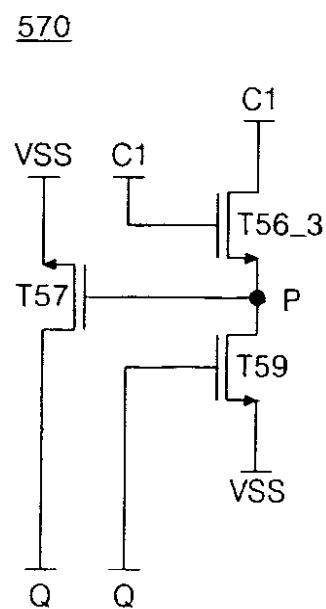

図12は本発明の第5実施例に係る補償回路部570のみを図示したものである。

図12に図示された補償回路部570は第6NMOSトランジスタ(T56\_3)が第1クロック信号(C1)により制御されてPノードに第1クロック信号(C1)を供給することを除いては図9に図示された補償回路部250と同一な構成要素を具備する。

#### 【0079】

10

20

30

40

50

A期間で第1クロック信号(C1)のロー電圧により第6NMOSトランジスタ(T5\_6\_2)はターン-オフ、ハイ電圧でプレチャージされたQノードにより第7NMOSトランジスタ(T5\_7)がターン-オンされてPノードには低電位電圧(VSS)が供給される。これによって、第5NMOSトランジスタ(T5\_5)はターン-オフされる。

#### 【0080】

B期間で第1クロック信号(C1)のハイ電圧により第6NMOSトランジスタ(T5\_6\_2)がターン-オン、ブートストラッピングにハイ電圧がさらに上昇したQノードにより第7NMOSトランジスタ(T5\_7)がターン-オンされる。この時、第7NMOSトランジスタ(T5\_7)が第6NMOSトランジスタ(T5\_6\_2)より大きい大きさに形成されることによって同時にターン-オンされてもPノードには第6NMOSトランジスタ(T5\_6\_2)を経由した第1クロック信号(C1)のハイ電圧よりも第7NMOSトランジスタ(T5\_7)を経由した低電位電圧(VSS)が供給されるから第5NMOSトランジスタ(T5\_5)はターン-オフされる。このために、第7及び第6NMOSトランジスタ(T5\_7,T5\_6\_2)は少なくとも3:1位の大きさの比率を持つよう形成される。

#### 【0081】

C期間で第1クロック信号(C1)のロー電圧により第6NMOSトランジスタ(T5\_6\_2)はターン-オフ、ロー電圧に変換されたQノードにより第7NMOSトランジスタ(T5\_7)がターン-オフされるからPノードは以前のロー状態でフローティングされる。これによって、第5NMOSトランジスタ(T5\_5)はターン-オフされる。

#### 【0082】

D期間で第1クロック信号(C1)のハイ電圧により第6NMOSトランジスタ(T5\_6\_2)がターン-オン、ロー電圧であるQノードにより第7NMOSトランジスタ(T5\_7)がターン-オフされるからPノードには第1クロック信号(C1)のハイ電圧が供給される。これによって、第5NMOSトランジスタ(T5\_5)がターン-オンされてQノードに低電位電圧(VSS)を供給するからQノードがハイ電圧の第1クロック信号(C1)により変わることを防止することができるようになる。

#### 【0083】

このようなシフトレジスタを利用した液晶表示パネルの駆動装置は従来の駆動装置に比べてより安定的に動作する。

#### 【0084】

以上説明した内容を通じて当業者であれば本発明の技術思想を逸脱しない範囲で多様な変更及び修正ができる。したがって、本発明の技術的範囲は明細書の詳細な説明に記載した内容に限定されるのではなく特許請求の範囲により決められなければならない。

#### 【図面の簡単な説明】

#### 【0085】

【図1】従来の2像シフトレジスタを図示したブロック図。

【図2】図1に図示された第1ステージの詳細回路図。

【図3】図2に図示されたステージの駆動波形図。

【図4】本発明の第1実施例に係るシフトレジスタの一つのステージを出力部中心に図示した回路図。

【図5】図4に図示されたステージの駆動波形図。

【図6】本発明の第2実施例に係るシフトレジスタの一つのステージに対する詳細回路図。

【図7】図6に図示されたステージの駆動波形図。

【図8A】図6に図示されたステージで補償キャパシタ(CC)がない場合の駆動波形を比べて図示した図面。

【図8B】図6に図示されたステージで補償キャパシタ(CC)がある場合の駆動波形を比べて図示した図面。

【図9】本発明の第3実施例に係るシフトレジスタの一つのステージを出力部中心に図示した回路図。

10

20

30

40

50

【図10】図9に図示されたステージの駆動波形図。

【図11】本発明の第4実施例に係るシフトレジスタの補償回路部に対する詳細回路図。

【図12】本発明の第5実施例に係るシフトレジスタの補償回路部に対する詳細回路図。

【符号の説明】

【0086】

10、40、340 制御部

20、30、330 出力バッファ部

350、460、570 補償回路部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8 A】

【図8 B】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

|                           |              |            |

|---------------------------|--------------|------------|

| (51) Int.Cl. <sup>7</sup> | F I          | テーマコード(参考) |

| H 03K 23/44               | G 09G 3/20   | 622E       |

|                           | G 09G 3/20   | 670E       |

|                           | G 09G 3/36   |            |

|                           | H 03K 23/44  |            |

|                           | H 03K 17/687 | F          |

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 文 秀 ファン

大韓民国 慶尚北道 漆谷郡 北三面 仁坪里 シティ タウン 301 - 302号

F ターム(参考) 2H093 NA16 NA43 NC10 NC22 NC34 NC35 NC62 NC67 ND60

5C006 AC22 AF50 BB16 BC03 BC20 BF03 BF34 BF37 FA18 FA26

5C080 AA10 BB05 DD09 FF01 FF11 JJ02 JJ03 JJ04

5J055 AX37 BX16 CX30 DX22 DX56 DX72 DX73 DX83 EX02 EY10

EY21 EZ00 EZ12 FX18 FX37 GX01 GX02 GX04 GX05

【要約の続き】

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 移位寄存器及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2005293817A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2005-10-20 |

| 申请号            | JP2004373155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2004-12-24 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 文秀ファン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 文秀▲ファン▼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/133 G09F9/35 G09G3/20 G09G3/36 G11C19/00 G11C19/18 G11C19/28 H03K5/13 H03K5/15 H03K17/687 H03K23/44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G11C19/00 G11C19/184 G11C19/28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G11C19/00.J G11C19/00.G G02F1/133.550 G09G3/20.611.J G09G3/20.612.K G09G3/20.622.E G09G3/20.670.E G09G3/36 H03K23/44 H03K17/687.F G11C19/00 G11C19/00.K G11C19/28.D G11C19/28.230                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NC10 2H093/NC22 2H093/NC34 2H093/NC35 2H093/NC62 2H093/NC67 2H093/ND60 5C006/AC22 5C006/AF50 5C006/BB16 5C006/BC03 5C006/BC20 5C006/BF03 5C006/BF34 5C006/BF37 5C006/FA18 5C006/FA26 5C080/AA10 5C080/BB05 5C080/DD09 5C080/FF01 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5J055/AX37 5J055/BX16 5J055/CX30 5J055/DX22 5J055/DX56 5J055/DX72 5J055/DX73 5J055/DX83 5J055/EX02 5J055/EY10 5J055/EY21 5J055/EZ00 5J055/EZ12 5J055/FX18 5J055/FX37 5J055/GX01 5J055/GX02 5J055/GX04 5J055/GX05 2H193/ZA04 2H193/ZF22 2H193/ZH40 2H193/ZH45 5B074/AA01 5B074/AA03 5B074/CA01 5B074/DA01 5B074/DB01 |         |            |

| 代理人(译)         | 臼井伸一<br>朝日伸光                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 优先权            | 1020040021986 2004-03-31 KR<br>1020040030337 2004-04-30 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

### 摘要(译)

要解决的问题：提供一种能够防止由薄膜晶体管的寄生电容器引起的用于控制输出缓冲器部分的节点电压波动的移位寄存器及其驱动方法。

ŽSOLUTION：该移位寄存器带有一个上拉晶体管（T5），用于提供第一个时钟信号（C1），用于通过第一个节点（Q）控制多个级到输出线（Out），一个下拉晶体管（T6）用于将由第二节点（QB）控制的第一驱动电压提供给输出线，用于控制第一和第二节点彼此相对的控制单元（10），以及连接在输入线之间的补偿电容器。第一节点和第二时钟信号用于补偿由第一节点，第一时钟信号和上拉晶体管之间的寄生电容器（CDG和CGS）引起的波动量。 Ž