(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-62582

(P2005-62582A)

(43) 公開日 平成17年3月10日(2005.3.10)

(51) Int.Cl.<sup>7</sup>

**G09F 9/00**

**G02F 1/1345**

**H01L 21/60**

**H05B 33/06**

**H05B 33/14**

F 1

G09F 9/00 348Z

G02F 1/1345

H01L 21/60 311S

H05B 33/06

H05B 33/14 A

テーマコード(参考)

2H092

3K007

5F044

5G435

審査請求 未請求 請求項の数 10 O L (全 21 頁)

(21) 出願番号

特願2003-294089 (P2003-294089)

(22) 出願日

平成15年8月18日 (2003.8.18)

(71) 出願人

502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(74) 代理人

100093506

弁理士 小野寺 洋二

(72) 発明者

竹中 雄一

千葉県茂原市早野3300番地 日立ディスプレイズ内

(72) 発明者

中山 貴徳

千葉県茂原市早野3300番地 日立ディスプレイズ内

F ターム(参考) 2H092 GA48 GA50 JB56 MA32 NA15

NA18 NA29 PA06 PA11

3K007 AB11 AB18 BA06 BB07 CC05

DB03 FA02

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】 絶縁基板に有するL C D端子と駆動回路チップのバンプ間の接続抵抗を安定にし、残留応力による駆動回路チップの絶縁基板からの剥離を防ぐ。

【解決手段】 駆動回路チップI Cの実装面に設けられた第1入出力バンプI / O - B U M Pの当該駆動回路チップの端縁E G L側に第2入出力バンプA - B U M Pを設け、絶縁基板に形成された入出力配線L Lの入出力配線端子部L L Tと第1入出力バンプI / O - B U M Pを接合する異方性導電膜に加わる応力を緩和する。第1入出力バンプI / O - B U M Pは第2入出力バンプA - B U M Pが設けられた分、駆動回路チップI Cの端縁E G Lから遠ざかるため、その入出力配線端子部L L Tとの接合部が表示装置の雰囲気から隔離され、当該接合部の破損やこれに伴い当該接合部で生じる駆動信号波形の歪みなどが抑制され、また入出力配線L Lの電蝕等による破損も回避される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

絶縁基板、

前記絶縁基板の正面に複数の画素を配置して形成された表示領域、

前記絶縁基板の前記正面の周縁部に搭載され且つ前記表示領域に信号又は電力を供給する少なくとも一つの駆動回路素子、及び

前記正面の前記周縁部に形成され且つ該正面の前記駆動回路素子が搭載される搭載部分に該駆動回路素子に接続される端子部が夫々設けられ且つ該端子部から該正面の搭載部分の外側へ夫々延びる複数の配線を備え、

前記複数の配線に夫々設けられた前記端子部は、一つおきに前記搭載部分の一端に近付けて該一端沿いに並び、

前記駆動回路素子の前記正面の搭載部分に対向する実装面には、異方性導電膜により前記端子部の夫々に接続される複数のバンプが該実装面の前記搭載部分の一端に対向する一辺沿いに並設され、

前記複数のバンプに属し且つ前記端子部の前記搭載部分の一端に近付けて設けられた一群に夫々接続される第1バンプは、該複数のバンプの該第1バンプ以外の各々より前記実装面の前記一辺に近付けて配置され、

前記実装面には前記第1バンプの前記実装面の前記一辺側に隣接して前記複数のバンプとは別の第2バンプが形成されている表示装置。

**【請求項 2】**

前記第2バンプは、これに隣接する前記第1バンプと同じ電位である請求項1に記載の表示装置。

**【請求項 3】**

前記第1バンプに接続される前記端子部の一つは、該第1バンプとともにこれに隣接する前記第2バンプにも接する面積を有する請求項1又は請求項2に記載の表示装置。

**【請求項 4】**

前記第2バンプは、該第2バンプに隣接する前記第1バンプに接続する前記配線と対向し且つ該第1バンプと離間されている請求項1又は請求項2に記載の表示装置。

**【請求項 5】**

前記第1バンプとこれに隣接する第2バンプとに接続する一つの端子部の面積は、該第1バンプに電気的に接続される前記配線の一つに隣接する該配線の他の一つに設けられた前記端子部の他の一つより大きい請求項3に記載の表示装置。

**【請求項 6】**

前記複数の配線は絶縁膜で覆われ、前記端子部は該絶縁膜に形成された該配線の夫々を露出する開口にて該配線に接し且つ該絶縁膜上に延びる請求項2に記載の表示装置。

**【請求項 7】**

前記第2バンプは、前記絶縁膜を介して該第2バンプに隣接する前記第1バンプに接続する前記配線と対向し且つ該第1バンプと離間されている請求項6に記載の表示装置。

**【請求項 8】**

絶縁基板、

前記絶縁基板の正面に複数の画素を配置して形成された表示領域、

前記絶縁基板の前記正面の周縁部に搭載され且つ前記表示領域に信号又は電力を供給する少なくとも一つの駆動回路素子、及び

前記正面の前記周縁部に形成され且つ該正面の前記駆動回路素子が搭載される搭載部分に該駆動回路素子に接続される端子部が夫々設けられ且つ該端子部から該正面の搭載部分の外側へ夫々延びる複数の配線を備え、

前記複数の配線に夫々設けられた前記端子部は、一つおきに前記搭載部分の一端に近付けて該一端沿いに並び、

前記駆動回路素子の前記正面の搭載部分に対向する実装面には、異方性導電膜により前記端子部の夫々に接続される複数のバンプが該実装面の前記搭載部分の一端に対向する一

10

20

30

40

50

辺沿いに並設され、

前記端子部の前記搭載部分の一端に近付けて設けられた一群に夫々接続される前記複数のバンプの一群は、該バンプの他の群より前記実装面の前記一辺側に配置され、

前記一群のバンプは、前記他の群のバンプより前記実装面の前記一辺側に長く延びて形成されている表示装置。

【請求項 9】

前記一群のバンプの前記実装面の一辺側に延びる長さは、前記他群のバンプのそれの2倍以上である請求項8に記載の表示装置。

【請求項 10】

前記駆動回路素子が複数個、前記絶縁基板の前記主面の一辺沿いに並べて搭載され、前記複数の配線は該複数の駆動回路素子の隣接する一対に夫々設けられた前記複数のバンプの夫々を電気的に接続する請求項1乃至9のいずれかに記載の表示装置。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置における駆動回路チップ実装構造に関するものであるが、特に表示装置の表示パネルを構成する基板の周辺上に駆動回路チップを直接実装した、所謂フリップチップ実装方式（あるいは、チップオングラス実装方式とも言う）の表示装置に関する。

20

【背景技術】

【0002】

画素毎に薄膜トランジスタTFTなどのアクティブ素子を有し、このアクティブ素子をスイッチング駆動するアクティブ・マトリクス型の表示装置は、液晶表示装置や有機EL表示装置などのパネル型表示装置として知られている。本発明は、この種のパネル型表示装置に適用される表示パネルに対する駆動回路チップの実装構造に特徴を有する。この駆動回路チップの実装構造は液晶表示装置や有機EL表示装置などのパネル型表示装置では略同様であるので、以下では、液晶パネルを用いた液晶表示装置を例として説明する。

【0003】

例えば、アクティブ素子に薄膜トランジスタを用いたアクティブ・マトリクス型液晶表示装置は、ガラス板を好適とする一対の絶縁基板間に封止した液晶層を有し、その表示領域にマトリクス配置された多数の画素を形成している。そして、絶縁基板の一方の表示領域の外側に前記画素に画像を表示するための表示信号や電圧を供給する入出力配線を有し、絶縁基板の周辺に沿って、接着性を有する異方性導電膜を介して上記入出力配線の端子部に接続して少なくとも一つの駆動回路チップを直接搭載する、所謂フリップチップ実装方式（FCA方式）、あるいはチップオングラス実装方式（COG方式）と称する実装方式を採用したものが知られている。

30

【0004】

このようなアクティブ・マトリクス型液晶表示装置は、薄膜トランジスタを介して画素電極に液晶駆動電圧（階調電圧）を印加するため、各画素間のクロストークがなく、単純マトリクス型の表示装置のようにクロストークを防止するための特殊な駆動方法を用いることなく多階調表示が可能である。

40

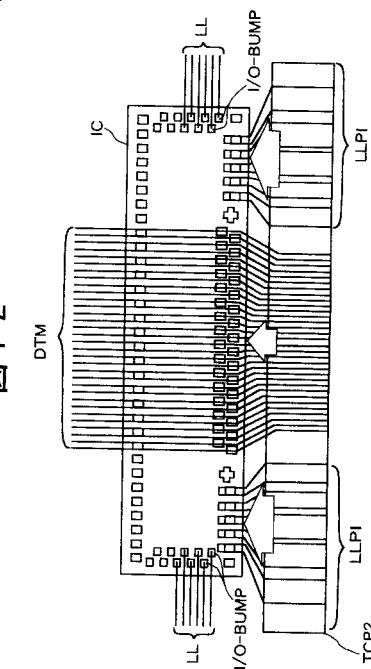

【0005】

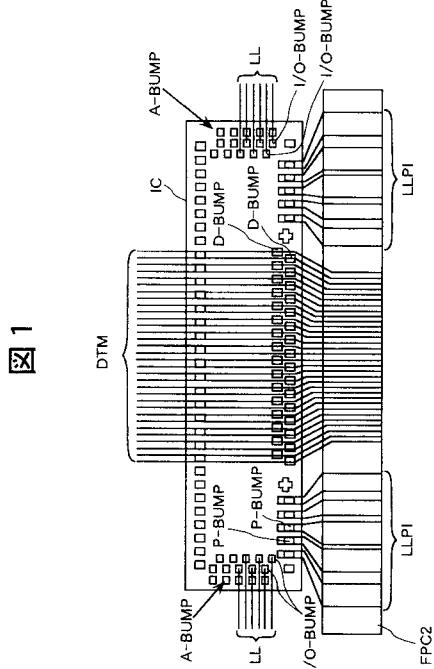

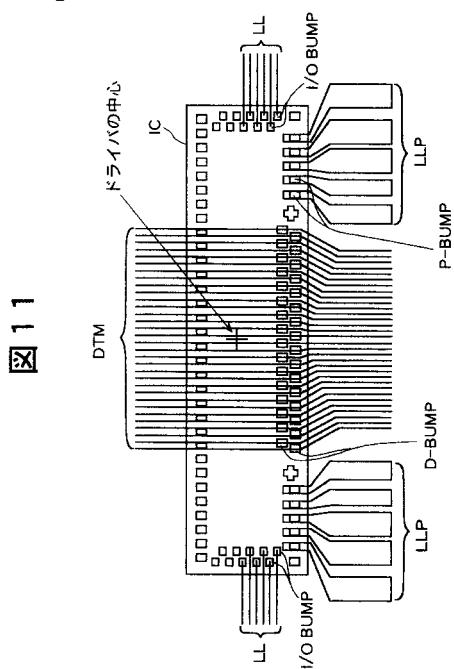

図11は液晶表示パネルの一方の基板の端縁に実装される駆動回路チップ周りの配置構造例を模式的に説明する平面図である。また、図12は図11に示した駆動回路電源入力用配線にフレキシブルプリント基板を実装した状態を示す平面図である。図11と図12において、絶縁基板の一方の表示領域の外側に実装される駆動回路チップICは、その実装面（絶縁基板主面と対向する面、回路面、腹面とも呼ばれる）に絶縁基板主面に設けられた配線端子に接続するための突出端子（以下、バンプと言ふ）を有する。図11、図12には、このバンプを四角で示してある。絶縁基板には、駆動回路チップICの短辺に有する入出力バンプI/O-BUMPに外部信号源からの駆動信号および電圧を複数の駆動

50

回路チップICの一つに対して供給し、当該一つの駆動回路チップに隣接する複数の駆動回路チップの他の一つ（当該一つの駆動回路チップの次段に位置する駆動回路チップ）へ順次伝送するための入出力配線LLが形成されている。各配線には、バンプと電気的に接続される端子部が、例えばその一端に形成されている。

【0006】

また、駆動回路チップICの長辺の一方（絶縁基板の端縁側）には、絶縁基板上を表示領域から延びるデータ配線（ドレイン線引き出し線）DTMに接続するデータ出力バンプD-BUMP、駆動回路電源入力用配線LLPと接続する電源入力バンプP-BUMPが形成されている。なお、バンプの中には、絶縁基板との間の実装間隙を平均化するためのダミーバンプも含まれている。図中、太い十字記号は実装時の位置決め用のアライメントマークである。

【0007】

駆動回路チップICは、その実装面に形成された複数のバンプとその夫々に対応して絶縁基板の正面に形成された複数の配線（入出力配線）との位置を合わせて当該絶縁基板正面に搭載され、当該複数のバンプと当該複数の配線とを異方性導電膜を介して熱圧着することにより絶縁基板に接着される。このような実装方式が、前記したフリップチップ方式（FCA方式）又はチップオングラス方式（COG方式）と称される。また、フレキシブルプリント基板FPC2も同様に異方性導電膜を用いて、その配線を駆動回路電源入力用配線LLPに熱圧着して固定される。以下では、チップオングラス実装方式（COG方式）の用語を用いることとする。

【0008】

なお、COG方式で絶縁基板に駆動回路チップを実装する液晶表示装置に関しては、特許文献1を挙げることができる。特許文献1には、駆動回路チップの四隅にダミーバンプを設けて、実装時の位置決めと圧着状態を目視で確認することが記載されている。

【特許文献1】特開平11-125837号公報

【発明の開示】

【発明が解決しようとする課題】

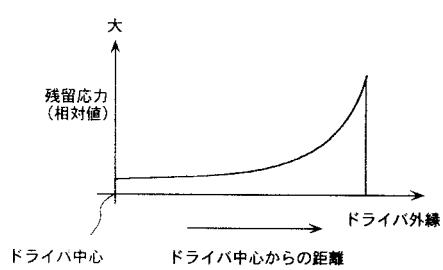

【0009】

COG方式を用いた駆動回路チップの実装では、駆動回路チップの四隅に位置するバンプと絶縁基板に形成した入出力配線端子との間の接続抵抗が高くなったり、抵抗値が不安定となる現象が生じ易い。このような現象は、駆動回路チップを熱圧着した後に圧着面に残留する応力（残留応力）に起因する。

【0010】

図13は実装した駆動回路チップの圧着面における残留応力の説明図であり、図11の駆動回路チップの中心（図11ではドライバ中心と表記）から駆動回路チップICの短辺外縁（図11ではドライバ外縁と表記）に向けた残留応力分布を示す。残留応力は、図11に示したような駆動回路チップの中心からの距離に依存し、駆動回路チップICの短辺外縁で最も大きくなる。

【0011】

さらに、図12に示した如く、フレキシブルプリント基板FPC2を異方性導電膜で駆動回路チップICの近傍に熱圧着する場合には、この熱圧着時の熱が図12に矢印で示したように駆動回路チップICに流入し、駆動回路チップICの実装面と絶縁基板との間に充填された異方性導電膜と当該絶縁基板との接着面がダメージを受ける。このダメージは残留応力と流入した熱量に依存する。したがって、フレキシブルプリント基板FPC2に近い駆動回路チップICの2つの角近傍で異方性導電膜を介在させたバンプと配線端子部との接続抵抗は高抵抗かつ不安定となる場合がある。その結果、表示領域に表示される画像に表示不良が生じる。これは、図12に示したように、駆動回路チップICの中央部分に比べて角近傍での熱伝導が良い構造となっている場合に顕著となる。このような現象が解決すべき課題となっていた。このような課題は、液晶表示装置に限るものではなく、他の同様な駆動回路チップを用いた表示装置でも発生する。

10

20

30

40

50

## 【0012】

本発明は、上記背景技術における課題を解決して、表示装置を構成する絶縁基板に形成された配線または配線端子部と駆動回路チップに有するバンプとの間の高抵抗化を回避し、接続抵抗を安定化して表示不良の発生を防止し、高品質の画像表示を得ることのできる信頼性の高い表示装置を提供することにある。

## 【課題を解決するための手段】

## 【0013】

(1) 絶縁基板、(2) 前記絶縁基板の正面に複数の画素を配置して形成された表示領域、(3) 前記絶縁基板の前記正面の一辺に沿う周縁部(Peripheral Portion)に搭載され且つ前記表示領域に信号又は電力を供給する少なくとも一つの駆動回路素子(駆動回路チップ)、及び(4) 前記正面の前記周縁部に形成され且つ当該正面の前記駆動回路素子が搭載される搭載部分(Mounting Portion)に当該駆動回路素子に接続される端子部が夫々設けられ且つ当該端子部から当該正面の前記駆動回路素子に覆われる部分(当該端子部が形成される)の外側に向けて夫々延びる複数の配線を備え、(5) 前記複数の配線に夫々設けられた前記端子部は一つおきに前記搭載部分の一端に近付けてこの一端沿いに並び、且つ

(6) 前記駆動回路素子の前記正面の搭載部分に対向する実装面(Mounting Surface)には異方性導電膜により前記端子部の夫々に接続(熱圧着)される複数のバンプ(Bump)が当該実装面の前記搭載部分の一端に対向する一辺沿いに並設される表示装置において、本願発明は、以下に記す構造を導入する。

## 【0014】

構造1(請求項1の発明)：前記複数のバンプに属し且つ前記端子部の前記搭載部分の一端に近付けて設けられた一群に夫々接続される第1バンプは、当該複数のバンプの当該第1バンプ以外の各々より前記実装面の前記一辺に近付けて配置される。また、前記実装面には前記第1バンプの前記実装面の前記一辺側に隣接して前記複数のバンプとは別の第2バンプが形成される。前記複数のバンプが前記駆動回路素子に信号又は電力を入力する入力バンプである場合、第2バンプは当該入力バンプが並ぶ駆動回路素子の入力側(前記実装面の前記一辺側の端部)に追加される追加バンプとして設けられる。なお、前記絶縁基板の前記正面において、前記周縁部は、前記表示領域の外側に位置し、表示装置の画面(Screen)に対して「額縁(Picture Flame)」となる領域に相当する。

## 【0015】

構造2(請求項2の発明)：前記構造1において、前記第2バンプは、これに隣接する前記第1バンプと同じ電位である。例えば、前記駆動回路素子にて、前記第1バンプとその前記実装面の一辺側に隣接する前記第2バンプとを導通させる。

## 【0016】

構造3(請求項3の発明)：前記構造1又は前記構造2において、前記第1バンプに接続される前記端子部の一つは、当該第1バンプとともにこれに隣接する前記第2バンプにも接する面積を有する。

## 【0017】

構造4(請求項4の発明)：前記構造1又は前記構造2において、前記第2バンプは、該第2バンプに隣接する前記第1バンプに接続する前記配線と対向し、また当該第1バンプと離間される。

## 【0018】

上述の構造3において、前記第1バンプとこれに隣接する第2バンプとに接続する一つの端子部の面積を、当該第1バンプに電気的に接続される前記配線の一つに隣接する該配線の他の一つに設けられた前記端子部の他の一つより大きくするとよい。

## 【0019】

上述の構造2において、前記複数の配線を絶縁膜で覆い、当該絶縁膜に該配線の夫々を露出する開口を形成して、この開口により前記端子部を当該配線に接触させ、且つこの端子部を当該絶縁膜上に延ばすとよい。さらに、前記第2バンプを、前記絶縁膜を介して当

10

20

30

40

50

該第2バンプに隣接する前記第1バンプに接続した前記配線と対向させてもよく、また、当該第2バンプを当該第1バンプと離間させてもよい。

#### 【0020】

構造5（請求項8の発明）：上述の構造1にて、前記複数のバンプとは別の第2バンプを前記第1バンプの前記実装面の一辺側に隣接させて設ける代わりに、当該第1バンプを前記実装面の一辺側に向けて延ばす。この第1のバンプを前記複数のバンプの一群に属する各々とした場合、当該一群のバンプは、当該複数のバンプの他の群に属するバンプより前記実装面の一辺側に長く延びる。他の群に属するバンプは、第1バンプが夫々圧着される複数の端子部の一群より前記絶縁基板正面の前記搭載部分の内側に（当該搭載部分の一端から離れて）形成される当該複数の端子部の他の群に夫々圧着される。構造5において、前記一群のバンプ（前記第1バンプ）の前記実装面の一辺側に延びる長さは、前記他群のバンプのそれ（換言すれば、当該第1バンプに本来要される長さ）の2倍以上にするといい。

10

#### 【0021】

なお、以上に述べた構造において、前記駆動回路素子を複数個、前記絶縁基板の前記正面の一辺沿いに並べて搭載してもよく、前記複数の配線で当該複数の駆動回路素子の隣接する一対に夫々設けられたバンプを接続してもよい。

#### 【発明の効果】

#### 【0022】

前記構造1が導入された表示装置では、駆動回路素子（チップ）の実装面に当該駆動回路素子の一端（例えば、駆動回路素子への信号又は電力の入力側）に近付けて配置される第1バンプと当該一端との距離が第2バンプにより長くなるため、第1バンプを異方性導電膜により絶縁基板正面に形成された端子部に接続する工程及びその後において、当該第1バンプと当該端子部との接続面に加わる応力が緩和される。第1バンプと端子部とを異方性導電膜で熱圧着した後、第1バンプと端子部とに挟まれた異方性導電膜の温度が下がるにつれて、この異方性導電膜には絶縁基板正面に沿う方向の剪断（せんだん）応力が加わる。この剪断応力は、第1バンプと端子部とに挟まれた異方性導電膜を当該第1バンプ又は当該端子部から剥がす原因となり、その弊害は後述するように熱圧着されるバンプの位置が駆動回路素子（チップ）の端部に近づくほど指数関数的に顕著となる。従って、駆動回路素子の端部（前記実装面の一辺側）に第2バンプを設けるだけでも、駆動回路素子の端部側に配置された第1バンプとこれに対向する端子部との電気的な接続の信頼性は向上する。

20

#### 【0023】

このような構造1の利点は、駆動回路素子の端部側に配置された第1バンプを当該端部側に延ばす前記構造5が導入された表示装置においても得られる。第1バンプの駆動回路素子の端部（前記実装面の一辺側）に向けた長さを、当該駆動回路素子の端部側に設けられ且つ当該第1バンプより当該端部から離れた他のバンプより長くすることで、第1バンプと端子部との接合面積が他のバンプとこれに対応する端子部との接合面積より拡がる。従って、第1バンプと端子部との間に挟まれた異方性導電膜は、その一部分（駆動回路素子の端部側）で上記応力の弊害を受けたとしても、その残りの部分で当該応力の弊害を回避し、第1バンプと端子部との電気的な接続を良好に維持する。なお、第1バンプの実装面の一辺側に向けた長さは、前記駆動回路素子が前記絶縁基板正面に搭載されたとき、前記正面の搭載部分の内部から当該実装面の一辺に對向する当該搭載部分の一端に向けて延びる方向に沿う長さとなる。

30

#### 【0024】

前記構造1が導入された表示装置及び前記構造5が導入された表示装置のいずれにおいても、上述の効果に加えて、次の効果も得られる。

40

#### 【0025】

その一つは、駆動回路素子の第1バンプと絶縁基板正面に設けられた端子部との異方性導電膜による接合部での電力損失や信号の遅延又は歪の低減である。この効果は、当該接

50

合部を通した第1バンプと端子部との間の電気抵抗が低減されることに拠り得られる。第1バンプと端子部との接合部分が駆動回路素子の実装面の一辺から離れるに伴い、当該接合部分は、絶縁基板正面、これに対向する駆動回路素子の実装面、及び異方性導電膜により、表示装置が利用される雰囲気からより確実に隔離されるため、第1バンプと端子部との間の電気抵抗は、長期に亘り低く且つ安定に維持される。

【0026】

他の一つは、前記絶縁基板正面の周縁部（前記正面の搭載部分を含む）に設けられた異方性導電膜に駆動回路素子の実装面を対向させた状態で、熱圧着ヘッドを駆動回路素子の上面（実装面の反対側）に当てて駆動回路素子の実装面に設けたバンプ（前記第1バンプを含む夫々）と絶縁基板正面の周縁部に設けた端子部とを接合（熱圧着）する工程において、当該第1バンプと端子部とに挟まれてこれらを接合する異方性導電膜に余剰の応力が加わらず、且つ第1バンプと端子部との接合の信頼性が損なわれないことである。第1バンプが駆動回路素子の実装面の内側に位置する（その一辺から離れている）ため、この接合工程にて駆動回路素子の上面に接する熱圧着ヘッドの当該上面に対する傾きが第1バンプと端子部との接合（熱圧着）に及ぼす影響が軽減される。

【0027】

前記構造2が導入された表示装置では、前記第2バンプとこれに隣接する前記第1バンプとが同じ電位であるため、当該第1バンプに接続される配線沿いに生じる寄生容量も低減される。これにより、当該配線により伝送される信号に生じる波形歪も抑制される。第2バンプが、これに隣接する第1バンプに接続される配線に接する場合でも、駆動回路素子において第2バンプと第1バンプとを導通し、又は同電位となるように結線するとよい。一方、第2バンプが、これに隣接する第1バンプに接続される配線と絶縁膜を介して対向する場合、当該絶縁膜の上面と下面との間に電位差は実質生じないため、当該配線を形成する導体膜（特に金属膜）が電蝕により溶ける可能性がなくなる。従って、配線の電気抵抗は好ましい低さに維持される。また、配線と絶縁されて対向する第2バンプが浮遊電位にある場合に比べて、当該配線と第2バンプとの間に生じる寄生容量も低くなる。

【0028】

前記構造3が導入された表示装置では、前記第1バンプに接続される端子部の面積を、当該第1バンプに隣接する前記第2バンプにも接合し得る大きさにすることにより、絶縁基板正面（その周縁部）に駆動回路素子を搭載する工程における絶縁基板正面に形成された複数の端子部と駆動回路素子の実装面に形成された複数のバンプとの位置合わせ（Alignment）の精度が向上する。従って、複数のバンプと複数の端子部とが夫々好ましく電気的に接続される。また、構造3と前記構造2とを組み合わせると、第1バンプとこれに対応する端子部との間の電気的な接続に対して、当該端子部と第2バンプとの電気的な接続が並列に形成されるため、当該第1バンプと当該端子部との接合面積の拡大に等しい効果が得られる。換言すれば、異方性導電膜に含まれる導電粒子をより多く、第1バンプと端子部との電気的な接続に寄与させられる。

【0029】

前記構造4が導入された表示装置では、前記第2バンプとこれに隣接する前記第1バンプとの間に生じた間隙により、当該第1バンプを前記端子部に接合する工程で溶融した異方性導電膜のバインダが、絶縁基板正面とこれに対向する駆動回路素子の実装面とに挟まれた空間から効率よく排出される。従って、当該第1バンプと当該端子部との接合部の周辺に余剰の異方性導電膜及びこれにフィラとして分散された導電粒子が残りにくくなり、これにより上述した当該接合部に加わる応力が助長される可能性もなくなる。

【0030】

なお、前記配線が、前記絶縁基板正面の搭載部分の一端に対して斜めに延びる部分を有する場合は、当該部分の当該搭載部分の一端となす角度が小さくなるにつれて、当該配線とこれに隣接する他の配線との間隔が狭くなる。従って、前記第2バンプとこれに隣接する前記第1バンプに接続される前記配線とは、当該配線とこれに隣接する他の配線との短絡や、当該第2バンプによる当該他の配線への電気的な干渉を避ける観点で、当該配線の

10

20

30

40

50

前記主面の搭載部分の一端に対して斜めに延びる部分以外で対向させるとよい。

【0031】

本発明は、上記した各請求項に記載の発明に限定されるものではなく、本発明の技術思想を逸脱することなく、種々の変形は可能であることは言うまでもない。

【発明を実施するための最良の形態】

【0032】

以下、本発明の実施例を詳細に説明する。

【実施例1】

【0033】

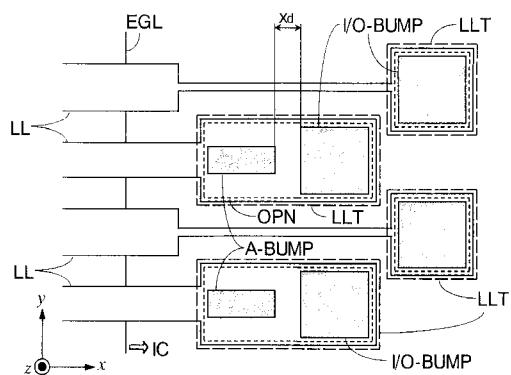

図1は液晶表示パネルの一方の基板主面の端縁に実装される本実施例の駆動回路チップ(駆動回路素子と呼ばれる集積回路素子)も周りの配置構造例を模式的に説明する平面図であり、駆動回路電源入力用配線にフレキシブルプリント基板を実装した状態を示す。本実施例の駆動回路チップICは画素を構成する薄膜トランジスタのドレインに表示データを供給するドレイン線駆動用の駆動回路チップであり、その実装面(絶縁基板と対向する面、回路面、腹面とも呼ばれる)の両短辺側に複数の第1入出力バンプI/O-BUMP、第2入出力バンプA-BUMPを有している。また、絶縁基板の外縁に位置する長辺の一方には液晶表示パネルの表示領域に接続する複数のドレイン端子DTMに接続する複数のデータ出力バンプD-BUMPと複数の電源入力バンプP-BUMPがそれぞれ複数設けられている。駆動回路チップICの長辺の他方に有してドレイン端子DTMの下面に有するバンプはダミーバンプである。

10

20

【0034】

図1では、絶縁基板主面に画素をマトリクス状に配置して形成される表示領域が省略されているが、図1に示される駆動回路チップICは、絶縁基板主面の周縁部(Peripheral Portion、表示領域の外側)に搭載される。駆動回路チップICの長辺の一方は表示領域に対向し、その他方は絶縁基板主面の一辺に対向する。図1に示される上述のドレイン端子DTM及びに後述されるその他の配線LL, L L P Iは、絶縁基板主面の駆動回路チップICが搭載される搭載部分(Mounting Portion)の内部からその外側へ向けて延びる。絶縁基板主面の搭載部分は、ここに搭載された駆動回路チップICの実装面(Mounting Surface)と向き合い、絶縁基板主面に形成されたドレイン端子DTM及びに配線LL, L L P Iは駆動回路チップICに覆われる夫々の部分において、その実装面に形成された複数のバンプ(ドレイン端子DTM、及び配線LL, L L P Iに対応するその夫々)に電気的に接続される。

30

【0035】

なお、本実施例にて、本発明を特徴付ける先述の第1バンプに対応するバンプI/O-BUMPに「入出力バンプ(Input/Output Bump)」なる名称を付ける理由は、バンプI/O-BUMPの夫々が駆動回路チップICへの信号入力及び当該駆動回路チップICからの信号出力のいずれにも用いられることによる。また、このバンプI/O-BUMPに結線される絶縁基板上に形成された配線LLも「入出力配線(Input/Output Wiring Line)」と記す。

40

【0036】

電源入力バンプP-BUMPにはフレキシブルプリント基板FPC2の電源配線LLPIが異方性導電膜を介して熱圧着される。第1入出力バンプI/O-BUMPは駆動回路チップICの短辺側端縁と平行な直線に関して互い違いに配置されている。絶縁基板上に形成されている入出力配線LLは、絶縁基板主面の搭載部分(駆動回路チップICに覆われる部分)の外側からその一端を通過してその内部に延びる。搭載部分の内部に延在した入出力配線LLの各々(の終端)には、駆動回路チップICの実装面に形成された入出力バンプI/O-BUMPの一つに接続される端子部(以降、入出力配線端子部(Input/Output Wiring Terminal Portion)と記す)が設けられる。配線LLは、これに設けられた入出力配線端子部から絶縁基板主面の搭載部分の外側に向けて延びる。

50

【0037】

図1に示されるように、駆動回路チップICの右側及び左側の各々にて、その実装面に形成された入出力バンプI/O-BUMPは、この駆動回路チップICの一辺（短辺）沿いに並び、その一つおきに当該駆動回路チップICの一辺側に近付けられる。従って、駆動回路チップICの右端及び左端の各々に沿って、入出力バンプI/O-BUMPは、千鳥格子状に互い違いに並ぶ。このような入出力バンプI/O-BUMPの配置に対応して、絶縁基板正面の搭載部分に形成される入出力配線LLの端子部も、当該搭載部分の右側及び左側の各々の一端沿いに千鳥格子状に互い違いに並ぶ。このため、入出力配線LLの各々は、これに対応する入出力バンプI/O-BUMPから搭載部分の一端（例えば、当該入出力配線LLの端子部に最も近い）及びその外側へ向けて引き出されるようにして図1に示される。

10

## 【0038】

図1の左側に並ぶ配線LLは、駆動回路チップICの左側の短辺に沿って並設された第1入出力バンプI/O-BUMP、または第1入出力バンプI/O-BUMPとその駆動回路チップICの左短辺側に隣接する第2入出力バンプA-BUMPに異方性導電膜を介して熱圧着される。同様に、図1の右側の配線LLは駆動回路チップICの右側の短辺に沿って並設される第1入出力バンプI/O-BUMP、または第1入出力バンプI/O-BUMPとその駆動回路チップICの右短辺側に隣接する第2入出力バンプA-BUMPに異方性導電膜を介して熱圧着される。駆動回路チップICの左側に配置された第1入出力バンプI/O-BUMPとこれに対応する配線LL及び駆動回路チップICの右側に配置された第2入出力バンプI/O-BUMPとこれに対応する配線LLは、熱圧着ヘッドを駆動回路チップICの上面に当てて行う1回の熱圧着工程により、一括して接合される。

20

## 【0039】

絶縁基板上に形成されている左側の入出力配線LLから駆動回路チップICに入力した表示信号を構成する信号や電圧は当該駆動回路チップICで処理されてデータ出力バンプD-BUMPからドレイン端子DTMに出力される。次の駆動回路チップで処理される表示信号を構成する信号や電圧は駆動回路チップICから右側の入出力配線LLに出力され、次の駆動回路チップICに入力する。

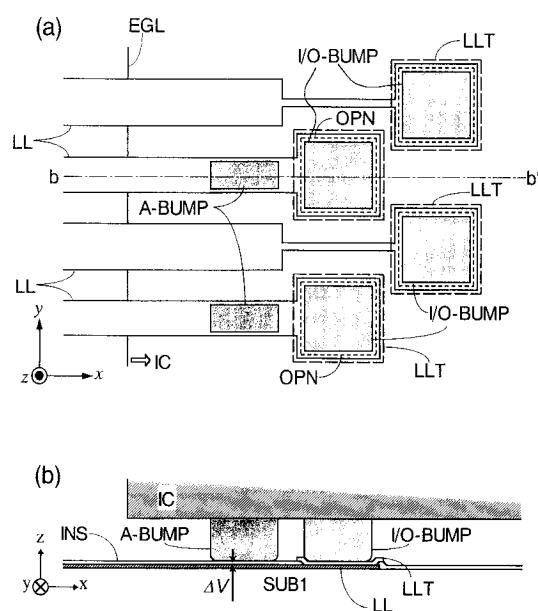

## 【0040】

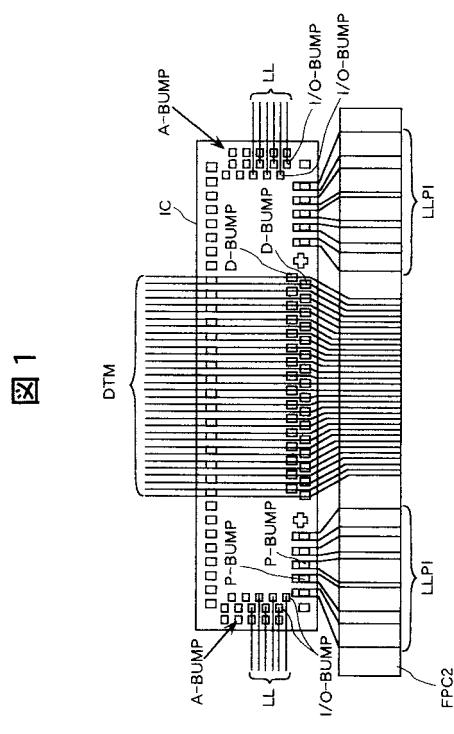

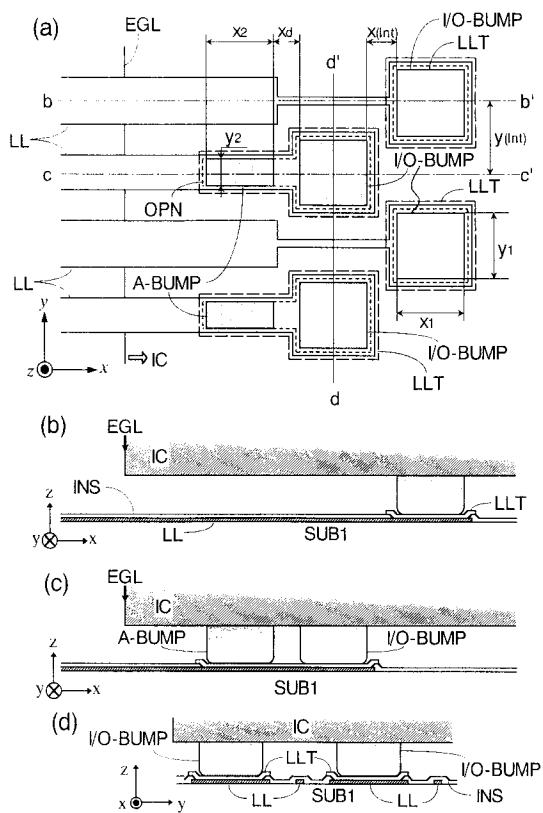

図2(a)は、図1における左側短辺の入出力配線LLと駆動回路チップICに有する第1入出力バンプと第2入出力バンプの構成を説明する一部拡大平面図である。図2(a)における線EGLは駆動回路チップICのチップ端（上述した駆動回路チップの実装面の一辺）を示し、これに対向する絶縁基板正面のチップ端EGLから右側は上述した「搭載部分」となる。図2(b)は図2(a)のb-b'線に沿う断面を、図2(c)は図2(a)のc-c'線に沿う断面を、図2(d)は図2(a)のd-d'線に沿う断面を夫々示す。図2及び後に参照する図3、図4、並びに図14の各々には、夫々に示された絶縁基板SUB1及び駆動回路チップICの配置関係を明らかにするために、x、y、zの3軸からなる直交座標が示される。図1にて、x方向は駆動回路チップICの左端から右端に至る方向を、y方向は駆動回路チップICの下端から上端に至る方向を、z方向は絶縁基板正面に駆動回路チップICが重なる方向（絶縁基板SUB1の厚み方向）を夫々示す。

30

## 【0041】

絶縁基板に形成されている入出力配線LLはメタル（金属）やアロイ（合金）からなり、SiO<sub>2</sub>（酸化珪素）やSiN<sub>x</sub>（窒化珪素）からなる絶縁膜INSにより覆われる。この入出力配線LLは駆動回路チップICの実装面に対向する上述の搭載部分（絶縁基板正面の一部）で終端する。絶縁膜INSには、入出力配線LLの終端部分（又はその付近）を露出する開口OPN（図2(a)に点線で示される）が形成され、この開口にて入出力配線LLに接し且つ絶縁膜INSの上面に延びる導体膜により端子部LLT（以下、LCD端子とも言う）が形成される。図2(a)において、この端子部LLTの平面的な形状は破線で示される。端子部LLTとなる導体膜は、腐蝕し難いITO(Indium-Tin-Oxide)

40

50

de) や IZO (Indium-Zinc-Oxide) 等の導電性を有する酸化物で形成するとよい。

【0042】

図2(a)と図2(b)及び図2(c)とを相互に参照して明らかのように、端子部LLTは、その並設方向に沿って交互に、図2(b)に示される如く絶縁基板正面の搭載部分の一端(チップ端EGLに対向する部分)から離れ、また図2(c)に示される如く当該搭載部分の一端に近づく。駆動回路チップの実装面における入出力バンプI/O-BUMPの位置も、その並設方向に沿い交互に、図2(b)に示される如くチップ端EGLから離れ、また対する図2(c)に示される如く当該チップ端EGLに近づく。搭載部分の一端(チップ端EGL)から遠ざけられた端子部LLTに接続する配線LL(図2(b)参照)は、これとこれに隣接する配線LL(搭載部分の一端に近付けられた端子部LLTに接続する、図2(c)参照)との間で、相互の短絡や電気的な干渉(夫々に伝送される信号間に生じる)を避けるために、その幅が狭められている。

10

【0043】

なお、本発明による表示装置を特徴付ける構造1として先述された「複数のバンプ」は、本実施例における入出力バンプI/O-BUMPに相当し、これに属する第1バンプは、この入出力バンプI/O-BUMPの図2(a)にてc-c'線が付された一群に相当する。なお、図2(a)にてb-b'線が付された入出力バンプI/O-BUMPは、上記複数のバンプの上記第1バンプ以外の他の群に属する一つに相当する。

【0044】

駆動回路チップICの実装面には、上記LCD端子LLTのそれぞれと接続するためのバンプであるI/O-BUMPバンプが形成されている。本実施例では、このI/O-BUMPバンプのチップ端EGLに近い位置にLCD端子LLTを有する入出力配線LLと対向する部分にバンプが追加されている。この追加バンプを第2入出力バンプA-BUMPとし、入出力配線LLの端部に有するバンプを第1入出力バンプI/O-BUMPとしている。第1入出力バンプI/O-BUMPは正方形で、そのサイズは例えば60μm×60μmである。

20

【0045】

入出力端子LLの幅:y<sub>2</sub>(y方向に沿う長さ)は約30μm、LCD端子LLTの幅:y<sub>1</sub>(y方向に沿う長さ)と長さ:x<sub>1</sub>(x方向に沿う長さ)はそれぞれ60μm+、LCD端子LLTのチップ端EGLと平行な方向の中心間距離:y(Int)(y方向に沿う長さ)

30

は55μmである。なお、上記の「+」は第1入出力バンプI/O-BUMPより若干大きいという意味を表す。また、チップ端EGLと平行な方向(y方向)に沿って隣接し合う一対の第1入出力バンプI/O-BUMPのチップ端EGLと垂直な方向(x方向)に沿う間隔:x(Int)は25μmである。これらのサイズはあくまで一例である。以下に記述するサイズも同様に一例である。

【0046】

第2入出力バンプA-BUMPのチップ端EGLと平行な方向の辺の長さ(上記y<sub>2</sub>)は、30μmとして入出力配線LLの幅と略等しい。また、第2入出力バンプA-BUMPの当該入出力配線LLの長手方向と平行な方向の長さ:x<sub>2</sub>(x方向に沿う長さ)は、第1入出力バンプI/O-BUMPのそれと同じ60μmである。また、第1入出力バンプI/O-BUMPと第2入出力バンプA-BUMPとをx方向に離間する間隙の長さ(間隔):x<sub>d</sub>は20μmと、当該入出力バンプI/O-BUMPのx方向の長さ(x<sub>1</sub>)より短い。第2入出力バンプA-BUMPは、x方向沿いにこれに隣接する第1入出力バンプI/O-BUMPと電気的に接続されているのが望ましい。本実施例では第2入出力バンプA-BUMPは駆動回路チップIC内部で第1入出力バンプI/O-BUMPと電気的に接続されている。バンプA-BUMPが「第2入出力バンプ」と称される所以は、図2(c)に示されるように端子部LLTに接し、且つこれに示される第1入出力バンプI/O-BUMPと導通されて、端子部LLTに接続する配線LLと駆動回路チップICとの間の信号伝送に寄与することにある。この第2入出力バンプA-BUMPは、本発明に

40

50

よる表示装置を特徴付ける構造 1 として先述された「第 2 バンプ」に相当する。

【 0 0 4 7 】

本実施例のように、前記絶縁基板正面の搭載部分の一端に近付けられた端子部 L L T に接続する第 1 入出力バンプ I / O - B U M P の当該一端側に第 2 入出力バンプ A - B U M P を設けることにより、(1) 雰囲気(環境)に変化が生じても第 1 入出力バンプ I / O - B U M P と絶縁基板の配線(入出力配線 L L、LCD 端子 L L T)との圧着強度が維持される。この利点(1)により、(2) 第 1 入出力バンプ I / O - B U M P と LCD 端子 L L T との接続部分の抵抗も低減される。また、第 2 入出力バンプ A - B U M P をこれに隣接する第 1 入出力バンプ I / O - B U M P(図 2(c) 参照)と同じ電位とすることにより、(3) 当該配線 L L で伝送される信号(駆動信号)の波形に歪が生じる確率が抑えられる。

【 0 0 4 8 】

一方、本実施例の変形(Variation)の一つによる平面構造を、図 14(a) に図 2(a) に倣って示す。また、図 14(a) に示された b - b' 線沿いの断面構造を、図 14(b) に示す。図 14(b) に示された断面構造は、図 2(c) と同様に本発明による表示装置の「第 1 バンプ」に相当する第 1 入出力バンプ I / O - B U M P と「第 2 バンプ」に相当するバンプ A - B U M P を示すが、後者は図 2(c) に示されるそれと異なり、絶縁膜 I N S によりこれと対向する配線 L L と電気的に分離されている。従って、図 14(b) に示されるバンプ A - B U M P は「第 2 入出力バンプ」とならない。図 14 に示される本実施例の変形の一つにおいても、バンプ A - B U M P とこれに隣接する第 1 入出力バンプ I / O - B U M P(図 14(b) 参照) とは同じ電位に設定される。これにより、(3') 配線 L L のバンプ A - B U M P に対向する部分が、これらの間に生じる電位差による電蝕を受け、溶出する可能性もなくなる。従って、配線 L L の幅がその不測の電蝕により局所的に狭まることもなくなり、その電気的な抵抗の上昇も抑えられる。

【 0 0 4 9 】

本実施例を適用した表示装置及びその変形を適用した表示装置のいずれにおいても、駆動回路チップ I C の実装面に形成されたバンプ I / O - B U M P の当該チップ端 E G L 側に寄せられた一群とその各々に対応する絶縁基板正面の端子部との接続抵抗が低く且つ安定に保たれるために、その表示不良の発生が防がれ、高品質の画像が表示される。

【 実施例 2 】

【 0 0 5 0 】

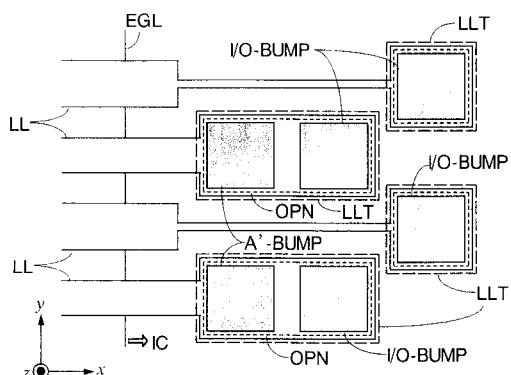

図 3 は図 1 における左側短辺の入出力配線 L L と駆動回路チップ I C に有する第 1 入出力バンプと第 2 入出力バンプの構成を説明する一部拡大平面図である。図 3 における線 E G L は図 2 と同様に駆動回路チップ I C のチップ端を示す。本実施例では、互い違いに配置された LCD 端子 L L T のうちの駆動回路チップ I C のチップ端 E G L 側に近い入出力配線 L L の LCD 端子 L L T を該駆動回路チップ I C のチップ端 E G L 側に拡大している。この LCD 端子 L L T のチップ端 E G L と平行な方向の幅は第 1 入出力バンプ A - B U M P を含む大きさ(カバーする大きさ、以下同様)とされており、チップ端 E G L に垂直な方向の長さは下記する第 1 入出力バンプ A - B U M P と第 2 入出力バンプ A - B U M P とを含む大きさである。

【 0 0 5 1 】

そして、駆動回路チップ I C の実装面には、第 1 入出力バンプ I / O - B U M P のチップ端 E G L 側に第 2 入出力バンプ A - B U M P を追加してある。第 1 入出力バンプ I / O - B U M P と第 2 入出力バンプ A - B U M P の間には 20  $\mu$ m の間隔を設けている。上記した互い違いに配置された LCD 端子 L L T のうちの駆動回路チップ I C のチップ端 E G L 側に近い拡大された LCD 端子 L L T は、第 1 入出力バンプ I / O - B U M P と追加した第 2 入出力バンプ A - B U M P を含む大きさである。なお、拡大した LCD 端子 L L T を有する入出力配線 L L に隣接する入出力配線の幅は相互の短絡を防止するために狭く形成されている。その他の構成は実施例 1 と同様である。

【 0 0 5 2 】

10

20

30

40

50

本実施例によれば、駆動回路チップICに第2入出力バンプA-BUMPを既存の第1入出力バンプI/O-BUMPよりも駆動回路チップICのチップ端側（すなわち、駆動回路チップの周縁側）に追加して設け、これに対応して絶縁基板に形成する入出力配線LLのLCD端子LLTを第1入出力バンプI/O-BUMPおよび第2入出力バンプA-BUMPを含む形状とすることによって前記した残留応力が低減され、実施例1と同様の表示不良が低減された高画質の表示装置を提供することができる。

#### 【0053】

さらに、本実施例では、駆動回路チップICのバンプI/O-BUMPの当該チップ端EGL側に寄せられた一群に夫々に接続される絶縁基板主面上の端子部LLTの面積が、当該一群のバンプI/O-BUMP及びその当該チップ端EGL側に隣接する他のバンプA-BUMPの双方に対向し得る大きさであるため、(4)絶縁基板主面上に駆動回路チップICを搭載する際のバンプI/O-BUMPと端子部LLTとの位置合わせの精度が向上する。また、(5)バンプI/O-BUMPと端子部LLT（絶縁基板側の配線）との電気的な接続裕度も確保される。

#### 【実施例3】

#### 【0054】

図4は図1における左側短辺の入出力配線LLと駆動回路チップICに有する第1入出力バンプと第2入出力バンプの構成を説明する一部拡大平面図である。本実施例は実施例2における第2入出力バンプA'-BUMPを第1入出力バンプA-BUMPと同形状としたものである。本実施例における互い違いに配置されたLCD端子LLTのうちの駆動回路チップICのチップ端EGL側に近い入出力配線LLのLCD端子LLTを該駆動回路チップICのチップ端EGL側に拡大し、第1入出力バンプI/O-BUMPと第2入出力バンプA'-BUMPを含んで接続するようにしている。その他の構成は実施例2と同様である。本実施例によっても、前記した残留応力が低減され、実施例1と同様の表示不良が低減された高画質の表示装置を提供することができる。

#### 【0055】

なお、本発明は上記した各実施例を適宜組み合わせることも含む。また、上記した各実施例では、第1入出力バンプと第2入出力バンプは全て矩形（正方形、長四角形）としているが、これに代えて円形でも、その他多角形などでもよい。そして、駆動回路チップを絶縁基板のLCD端子に異方性導電膜を介して接着するとき、第1入出力バンプと第2入出力バンプの間にも異方性導電膜が入り込むことで接着面積が大きくなる。これにより、第1入出力バンプI/O-BUMPをこれに対応する端子部LLTに接合する異方性導電膜に加わる応力が緩和される。

#### 【0056】

次に、本発明を実際の表示装置における駆動回路チップの実装に適用した具体的な例を説明する。

#### 【0057】

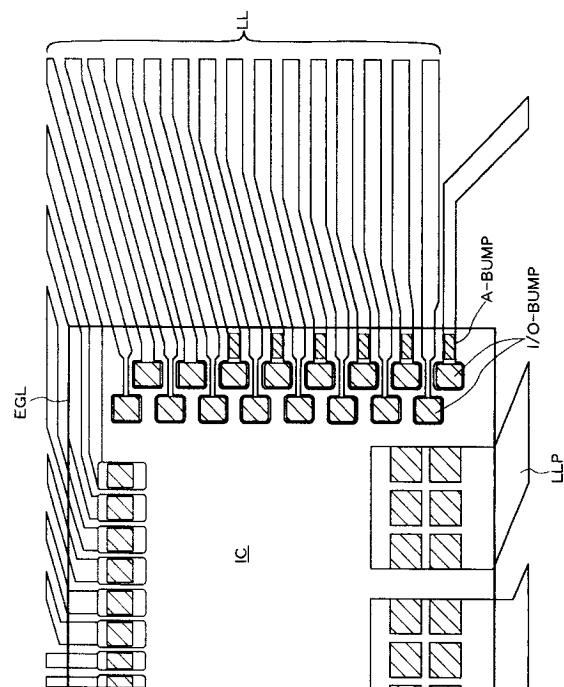

図5は図1に示した駆動回路チップの右側短辺に対応する入出力配線と駆動回路チップの一実装例の要部を拡大した平面図である。図5に示した具体例では、絶縁基板に形成される入出力配線LLは図5の右上の部分では短辺に対して斜行している。駆動回路チップICは図2の実施例で説明した第1入出力バンプI/O-BUMPと第2入出力バンプA-BUMPを有しているものである。但し、入出力配線LLが斜行している図5の右上の部分（図示しないが左上の部分も同様、ここでは右上の部分についてのみ説明する）では、隣接する入出力配線LL同士が接近している。このように駆動回路チップICのチップ端EGLに対して斜めに延びる配線LLが並ぶ領域において、その配線LLの一つに第2入出力バンプA-BUMP又はその等価物（当該一つの配線と電気的に絶縁される）を対向させると、当該一つの配線に隣接する他の配線に近付き又はこの一部にも対向し得る。従って、この隣接する他の配線が絶縁膜で覆われて、第2入出力バンプA-BUMP又はその等価物と電気的に分離されても、これらの間には当該絶縁膜を介して電位差が生じ、当該隣接する他の配線の電蝕による溶出が生じ得る。従って、図5の右上の部分には、第

10

20

30

40

50

2入出力バンプA-BUMPが設けられない。

【0058】

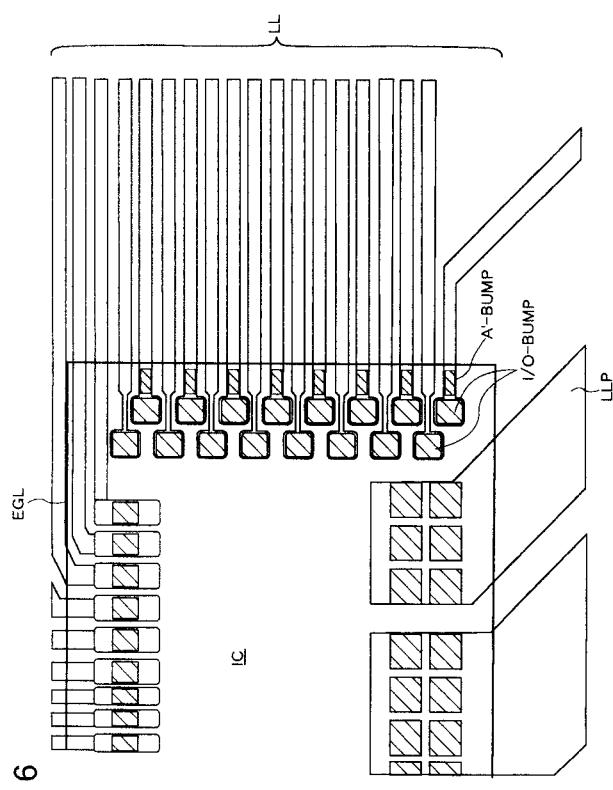

図6は図1に示した駆動回路チップの右側短辺に対応する入出力配線と駆動回路チップの他の実装例の要部を拡大した平面図である。図6に示した具体例では、絶縁基板に形成される入出力配線LLは駆動回路チップICの短辺に対して垂直に延びる。駆動回路チップICは図2の実施例で説明した第1入出力バンプI/O-BUMPと第2入出力バンプA-BUMPを有しているものを実装した場合と、図4の実施例で説明した第1入出力バンプI/O-BUMPと第2入出力バンプA'-BUMPを有しているものを実装した場合の両方を示している。なお、第2入出力バンプA-BUMPと区別するために第2入出力バンプA'-BUMPに対応する矩形のパターンには斜線を施していない。

10

【0059】

図6に示したような入出力配線LLを有する絶縁基板に第1入出力バンプI/O-BUMPと第2入出力バンプA-BUMPを有する駆動回路チップIC、または第1入出力バンプI/O-BUMPと第2入出力バンプA'-BUMPを有している駆動回路チップICを実装する場合、駆動回路チップICの短辺側に沿って互い違いに配置されたLCD端子LLTのチップ端に近いLCD端子LLTの全てに第2入出力バンプA-BUMP、または第2入出力バンプA'-BUMPを設けることができる。

【0060】

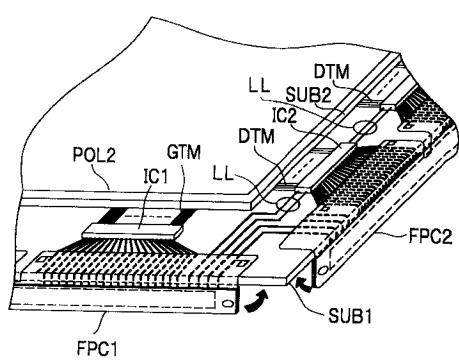

図7は本発明を液晶表示装置に適用した場合の絶縁基板への駆動回路チップを含む各部材の実装状態を説明する要部斜視図である。図7において、液晶表示パネルは一方の絶縁基板である第1の基板SUB1と他方の絶縁基板である第2の基板SUB2の貼り合わせ間に液晶層を封止して構成されている。この例では、第1の基板SUB1の内面には薄膜トランジスタを有する多数の画素をマトリクス配列した表示領域が形成され、第2の基板SUB2の上記表示領域に対向する内面には多色のカラーフィルタが形成されている。また、第1の基板SUB1と第2の基板SUB2の各表面には偏光板POL1、POL2が積層されている（図7には、偏光板POL2のみを示す）。

20

【0061】

図7における前記実施例あるいは具体例の図面の参照符号と同一参照符号は同一機能部分に対応する。液晶表示装置は、液晶表示パネルを構成する一方の絶縁基板である第1の基板SUB1にゲート線駆動用の駆動回路チップIC1と、ドレイン線駆動用の駆動回路チップIC2（前記した本発明に係る駆動回路チップICに相当）をCOG方式で実装している。これらの駆動回路チップIC1、IC2に接続する外部回路と搭載するフレキシブル基板FPC1、FPC2は上記第1の基板SUB1の端縁から同図の太矢印で示したように当該基板SUB1の裏面に折り込まれる。これにより、液晶パネルの額縁を大幅に狭くすることができる。

30

【0062】

ゲート線駆動用の駆動回路チップIC1には、図示しない外部信号源に接続するフレキシブルプリント基板FPC1から走査信号が印加され、表示領域から引き出されているゲート線GTMにゲート信号を供給する。このゲート信号の走査で選択されたゲート線に接続する薄膜トランジスタにドレイン線駆動用の駆動回路チップIC2からドレイン線DTMを通して供給される表示データで対応する画素が点灯されて画像を表示する。

40

【0063】

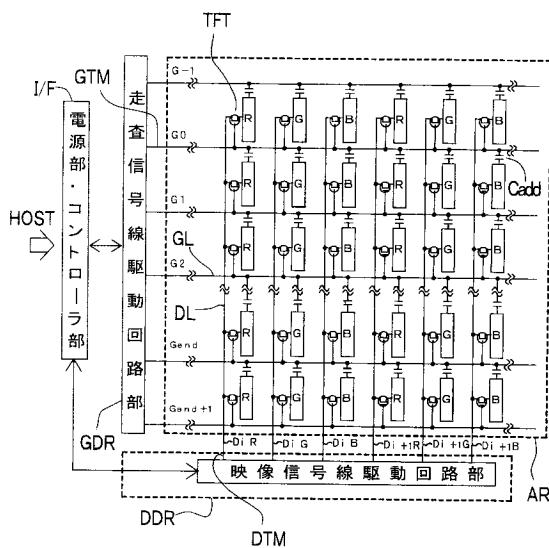

図8は液晶表示装置の等価回路例を示すブロック図である。この液晶表示パネルの表示領域ARの下側に複数のドレイン線駆動用の駆動回路チップIC2からなる映像信号線駆動回路DDRが配置され、側面側にゲート線駆動用の複数の駆動回路チップIC1からなる走査信号線駆動回路GDR、およびコントローラ部と電源部を搭載したインターフェース基板I/Fを有している。インターフェース基板I/Fからの各種信号や電圧は前記したフレキシブルプリント基板FPC1、FPC2を介して走査信号線駆動回路GDRと走査信号線駆動回路GDRに与えられる。

【0064】

50

アクティブ素子である薄膜トランジスタTFTは隣接する2本のゲート線GLの交差領域内に配置され、そのドレイン電極とゲート電極は、それぞれドレイン線DL、ゲート線GLに接続されている。GTMはゲート線引出し配線(G-1, G0, G1, G2, ..., Gend, Gend+1)、DTM(DiR, DiG, DiB, ..., Di+1R, Di+1G, Di+1B, ...)はドレイン線引出し配線、Caddは保持容量を示す。

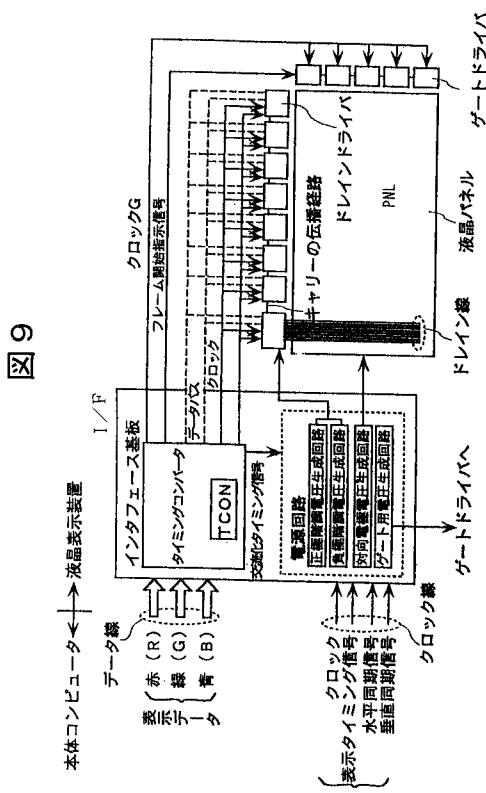

【0065】

図9はアクティブ・マトリクス型の液晶表示装置における駆動回路の構成例を説明するブロック図である。液晶表示装置は本体コンピュータ(図8のHOST)からの表示信号とクロック信号を含む制御信号を受けて液晶パネルPNLに画素データ、各種クロック信号、各種の駆動電圧を印加するインターフェース回路を搭載したインターフェース基板I/Fを備えている。

【0066】

インターフェース回路I/Fは、タイミングコンバータTCONを備えた表示制御装置と電源回路を有し、表示制御装置は液晶パネルに表示信号から生成した表示データを転送するデータバス、ドレイン線駆動用の駆動回路チップ(図9ではドレインドライバと表記)が表示データを取り込むためのクロック、該ドレイン線駆動用の駆動回路チップが液晶駆動信号を切り替えるためのクロック、ゲート線駆動用の駆動回路チップ(図9ではゲートドライバと表記)を駆動するフレーム開始指示信号とゲートクロックなどのタイミング信号を液晶表示パネル(図9では液晶パネルと表記)PNLに出力する。

【0067】

また、電源回路は正極階調電圧生成回路と負極階調電圧生成回路、対向電極電圧生成回路、ゲート用電圧生成回路で構成される。本体コンピュータからの表示信号と制御信号を受け取るインターフェース基板I/Fは、1画素単位、つまり赤(R)、緑(G)、青(b)の各データ1つを組にして単位時間に1画素分をドレイン線駆動用の駆動回路チップ(ドレインドライバ)に転送する。

【0068】

単位時間の基準になるクロック信号は本体コンピュータHOSTから液晶表示装置に送られる。具体的には、例えば1024×768画素の液晶表示装置では、通常は65MHzの周波数が用いられる。液晶表示パネルPNLの構成としては、表示画面を基準に、横方向にドレイン線駆動用の駆動回路チップを置き、このドレイン線駆動用の駆動回路チップを薄膜トランジスタTFTのドレイン線の引出し配線(DTM)に接続して液晶を駆動するための電圧を供給する。また、ゲート線にはゲート線駆動用の駆動回路チップの引出し配線(GTM)を接続し、ある一定時間(1水平動作時間)、薄膜トランジスタTFTのゲートに電圧を供給する。

【0069】

タイミングコンバータTCONは半導体チップにより構成され、本体コンピュータHOSTからの表示信号と各種制御信号を受取り、これを基にドレイン線駆動用の駆動回路チップ、ゲート線駆動用の駆動回路チップへ必要な表示データと動作クロックを出力する。なお、この例では、1画素分のデータ線は18ビット(R, G, B各6ビット)である。

【0070】

この構成では、本体コンピュータHOSTから液晶表示装置のタイミングコンバータTCONへは、低電圧振幅差動信号である、所謂LVDSで信号伝送を行う。タイミングコンバータTCONからドレイン線駆動用の駆動回路チップへはCMOSレベルの信号で伝送を行うが、この場合、65MHzの画素クロックを供給することが困難なので、32.5MHzのクロックの立上がりと立下がりの両エッジに同期して表示データの伝送を行う。

【0071】

ゲート線駆動用の駆動回路チップへは1水平時間毎に薄膜トランジスタTFTのゲート線に電圧を供給するように水平同期信号および表示タイミング信号(ディスプレイタイミング信号)に基づき、1水平時間周期のパルスを与える。1フレーム時間単位では第1ラ

10

20

30

40

50

イン目からの表示になるよう、垂直同期信号を基にフレーム開始指示信号も与える。

【0072】

電源回路の正極階調電圧生成回路と負極階調電圧生成回路は、同じ液晶に長時間同じ電圧が加わらないように、ある一定の時間毎に液晶に与える電圧を交流化するための基準電圧を生成する。実際の交流化は、ドレイン線駆動用の駆動回路チップ内で正極階調電圧と負極階調電圧を切り替えて使用することで行われる。なお、ここで言う交流化とは、対向電極電圧を基準に、ドレイン線駆動用の駆動回路チップへ与える電圧を一定時間毎に正電圧側／負電圧側に変化させることである。ここでは、この交流化の周期を1フレーム時間単位で行っている。

【0073】

この液晶表示パネルにCOG方式で駆動回路チップを上記した各実施例で説明した追加バンプを設けて異方性導電膜を介して絶縁基板（第1の基板SUB1）に実装することで、駆動回路チップの加熱圧着、あるいはフレキシブルプリント基板の加熱圧着に起因する残留応力が分散され、接続抵抗が安定化されて表示不良の発生が抑制された高画質の表示装置を提供することができる。

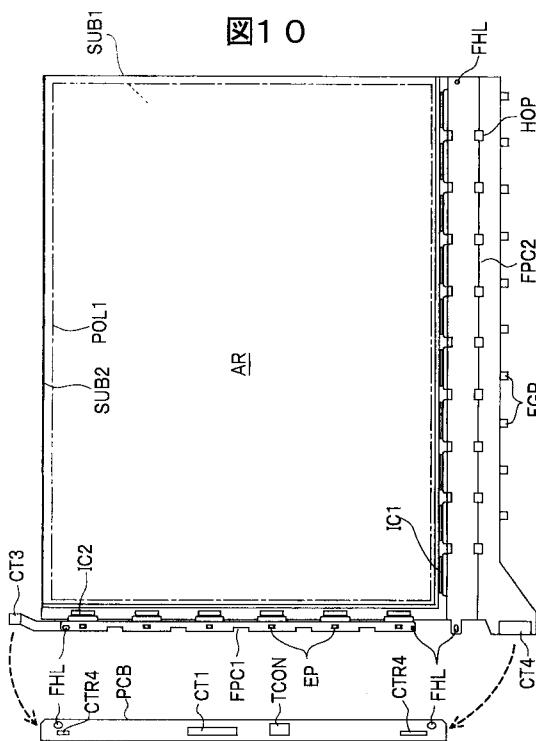

【0074】

図10は本発明に係る追加バンプを備えた駆動回路チップを実装した液晶表示パネルの平面図である。液晶表示パネルPNLは、アクティブ・マトリクス基板である第1の基板SUB1と通常はカラーフィルタを有するカラーフィルタ基板である第2の基板SUB2の貼り合わせ間隙に液晶層を封入して構成される。

【0075】

第1の基板SUB1は第2の基板SUB2よりも外形が若干大きく、第1の基板SUB1からはみ出した周辺に駆動回路チップ（ゲート線駆動用の駆動回路チップIC1、ドレイン線駆動用の駆動回路チップIC2）がフリップチップ実装方式で直接実装されている。これらの各駆動回路チップは、アクティブ素子として薄膜トランジスタを用いたものでは、薄膜トランジスタのゲート線の引出し配線に接続するゲート線駆動用の駆動回路チップ（ゲートドライバ）とドレイン線の引出し配線に接続するドレイン線駆動用の駆動回路チップ（ドレインドライバ）とからなる。

【0076】

そして、これら駆動回路チップに表示のための各種信号を供給するためのフレキシブルプリント基板FPC1とFPC2が配置されている。フレキシブルプリント基板FPC1とFPC2は、液晶表示パネルの近傍に設けたインターフェース基板PCBに接続している。インターフェース基板PCBは本体コンピュータなどの外部信号源からの表示信号を液晶表示装置のための表示信号に変換するためのタイミングコンバータ等、各種半導体回路チップやその他の電子回路素子が前記したように搭載されている。

【0077】

図10において、第1の基板SUB1の一縁（図では下縁、長手方向辺）にドレイン線駆動用の駆動回路チップ側のフレキシブルプリント基板FPC2が取り付けられ、その開口部HOPの配列に沿って液晶表示パネルPNLの裏側に折り込まれる。また、左縁（図では左縁、短手方向辺）にゲート線駆動用の駆動回路チップ側のフレキシブルプリント基板FPC1が取り付けられ、そのコネクタCT3とインターフェース基板PCBのコネクタCTR3およびドレイン線側のフレキシブルプリント基板FPC2のコネクタCT4と接続するコネクタCTR4とが結合される。

【0078】

また、インターフェース基板PCBには、ホストコンピュータなどの外部信号源からの信号を接続するインターフェースコネクタCT1、タイミングコンバータTCN等が取り付けられる。本構成例では、前記したようなLVDSS方式のデータ伝送方式を採用しているが、この場合に必要となる受信側信号変換器（LVDSS-R）はタイミングコンバータTCNと同一のチップで一体化する方法を採ることで、インターフェース基板上の実装面積を低減している。

10

20

30

40

50

## 【0079】

なお、液晶表示パネル PNL の裏面側（第 1 の基板 SUB1 の表面）と表示面側（第 2 の基板 SUB2 の表面）には下偏光板および上偏光板が積層されている。図 10 では上偏光板 POL1 のみが図示されている。そして、上偏光板 POL1 の内方に表示領域 AR が形成される。

## 【0080】

第 1 の基板 SUB1 の左辺と下辺の周縁には前記アクティブ素子に表示データを供給する多数の引出し配線、およびフレキシブルプリント基板 FPC1 と FPC2 を介して外部から入力する表示のための各種信号を接続する多数の入力配線が形成されており、前記実施例で説明したように、上記駆動回路チップ IC1 と IC2 の各バンプを上記入力配線と出力配線に異方性導電膜を介して、FCA 実装で接続している。図中、FGP はフレームグランドパッド、FHL は位置合わせ穴である。

## 【図面の簡単な説明】

## 【0081】

【図 1】液晶表示パネルの一方の基板の端縁に実装される本実施例の駆動回路チップ周りの配置構造例を模式的に説明する平面図である。

【図 2】本発明の実施例 1 を特徴付ける平面構造及び断面構造を、図 1 における絶縁基板正面に搭載された駆動回路チップの左側を部分的に拡大して示す平面図及び断面図である。

【図 3】本発明の実施例 2 を特徴付ける平面構造を、図 1 における絶縁基板正面に搭載された駆動回路チップの左側を部分的に拡大して示す平面図である。

【図 4】本発明の実施例 3 を特徴付ける平面構造を、図 1 における絶縁基板正面に搭載された駆動回路チップの左側を部分的に拡大して示す平面図である。

【図 5】図 1 に示した駆動回路チップの右側短辺に対応する入出力配線と駆動回路チップの一実装例の要部を拡大した平面図である。

【図 6】図 1 に示した駆動回路チップの右側短辺に対応する入出力配線と駆動回路チップの他の実装例の要部を拡大した平面図である。

【図 7】本発明を液晶表示装置に適用した場合の絶縁基板への駆動回路チップを含む各部材の実装状態を説明する要部斜視図である。

## 【図 8】液晶表示装置の等価回路例を示すブロック図である。

【図 9】アクティブ・マトリクス型の液晶表示装置における駆動回路の構成例を説明するブロック図である。

【図 10】本発明に係る追加バンプを備えた駆動回路チップを実装した液晶表示パネルの平面図である。

【図 11】液晶表示パネルの一方の基板の端縁に実装される駆動回路チップ周りの配置構造例を模式的に説明する平面図である。

【図 12】図 11 に示した駆動回路電源入力用配線にフレキシブルプリント基板を実装した状態を示す平面図である。

## 【図 13】実装した駆動回路チップの圧着面における残留応力の説明図である。

【図 14】本発明の実施例 1 の一変形を特徴付ける平面構造及び断面構造を、図 1 における絶縁基板正面に搭載された駆動回路チップの左側を部分的に拡大して示す平面図及び断面図である。

## 【符号の説明】

## 【0082】

IC . . . . 駆動回路チップ、I/O-BUMP . . . . 第 1 入出力バンプ I/O-BUMP、A-BUMP . . . . 第 2 入出力バンプ、DTM . . . . ドレイン端子、D-BUMP . . . . データ出力バンプ、P-BUMP . . . . 電源入力バンプ、LL . . . . 入出力配線、LLT . . . . 入出力端子部（LCD 端子）、EGL . . . . チップ端、FPC1, FPC2 . . . . フレキシブルプリント基板、LLPI . . . . 電源配線、SUB1 . . . . 第 1 の基板、SUB2 . . . . 第 2 の基板。

【図1】

図1

【図2】

図2

【図3】

図3

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【 図 9 】

【図 1 1】

1

【 図 1 0 】

【 図 1 2 】

12

【図13】

図13

【図14】

図14

---

フロントページの続き

F ターム(参考) 5F044 KK06 KK12 LL09

5G435 AA06 BB12 EE32 EE37 EE42

【要約の続き】

|                |                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2005062582A</a>                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2005-03-10 |

| 申请号            | JP2003294089                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2003-08-18 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 竹中雄一<br>中山貴徳                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 竹中 雄一<br>中山 貴徳                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G02F1/1345 G02F1/13 G02F1/133 G09F9/00 G09G3/36 G09G5/00 H01L21/60 H01L23/498 H01L51/50 H05B33/06 H05B33/14                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G02F1/13452 H01L23/49816 H01L23/49838 H01L24/83 H01L2224/13144 H01L2224/16 H01L2224/17515 H01L2224/2929 H01L2224/293 H01L2224/83851 H01L2924/00011 H01L2924/14 H01L2224/29075 H01L2924/00014 H01L2924/00                                                                                                                                                         |         |            |

| FI分类号          | G09F9/00.348.Z G02F1/1345 H01L21/60.311.S H05B33/06 H05B33/14.A                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H092/GA48 2H092/GA50 2H092/JB56 2H092/MA32 2H092/NA15 2H092/NA18 2H092/NA29 2H092/PA06 2H092/PA11 3K007/AB11 3K007/AB18 3K007/BA06 3K007/BB07 3K007/CC05 3K007/DB03 3K007/FA02 5F044/KK06 5F044/KK12 5F044/LL09 5G435/AA06 5G435/BB12 5G435/EE32 5G435/EE37 5G435/EE42 3K107/AA01 3K107/BB01 3K107/CC31 3K107/DD38 3K107/DD39 3K107/DD47Z 3K107/EE03 3K107/EE58 |         |            |

| 代理人(译)         | 小野寺杨枝                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                        |         |            |

## 摘要(译)

解决的问题：稳定设置在绝缘基板上的LCD端子与驱动电路芯片的凸块之间的连接电阻，并防止驱动电路芯片由于残余应力而从绝缘基板上剥离。解决方案：在驱动电路芯片IC的安装表面上提供的第一输入/输出凸块I/O-BUMP的驱动电路芯片的边缘EGL侧提供第二输入/输出凸块A-BUMP，并提供绝缘基板。施加于各向异性导电膜的应力被缓和，该各向异性导电膜将形成的输入/输出配线LL的输入/输出配线端子部LLT与第一输入/输出凸点I/O-BUMP接合。由于第一输入/输出凸块I/O-BUMP与驱动电路芯片IC的边缘EGL分开第二输入/输出凸块A-BUMP提供的量，因此显示了与输入/输出接线端子部分LLT的接合部分。该装置与装置的大气隔离，抑制了接头的损坏和在接头处由于该损坏而产生的驱动信号波形的失真，并且还避免了由于电解腐蚀等导致的输入/输出布线LL的损坏。[选型图]图1