(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3781967号

(P3781967)

(45) 発行日 平成18年6月7日(2006.6.7)

(24) 登録日 平成18年3月17日(2006.3.17)

(51) Int.C1.

F 1

G02F 1/1345 (2006.01)

G02F 1/1345

G09F 9/00 (2006.01)

G09F 9/00 348C

H01L 21/60 (2006.01)

H01L 21/60 311S

請求項の数 8 (全 12 頁)

(21) 出願番号

特願2000-392324 (P2000-392324)

(22) 出願日

平成12年12月25日 (2000.12.25)

(65) 公開番号

特開2002-196353 (P2002-196353A)

(43) 公開日

平成14年7月12日 (2002.7.12)

審査請求日

平成15年9月9日 (2003.9.9)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(73) 特許権者 000233088

日立デバイスエンジニアリング株式会社

千葉県茂原市早野3681番地

(74) 代理人 100083552

弁理士 秋田 収喜

(72) 発明者 山手 洋

千葉県茂原市早野3300番地 株式会社

日立製作所 ディスプレイグループ内

(72) 発明者 竹中 雄一

千葉県茂原市早野3681番地 日立デバイスエンジニアリング株式会社内

最終頁に続く

(54) 【発明の名称】表示装置

(57) 【特許請求の範囲】

【請求項 1】

対向配置される基板のうち一方の基板に、

一方向に延在し該一方向に交差する方向に並設された複数の信号線と、

信号線から供給される信号により駆動し画像を表示する表示部と、

これら信号線の一端側に形成された端子部と、前記端子部に接続されるバンプを形成した面を下にして実装された半導体チップと、を備え、

この半導体チップの複数の出力バンプは異方性導電層を介して対応する各信号線の一端側に形成された端子部と接続されているとともに、

前記各出力バンプは表示部に近い側に配列される第1出力バンプ群と表示部に遠のく側に配列される第2出力バンプ群とを有し、

第2出力バンプ群のバンプの面積は第1出力バンプ群のバンプの面積より大きく構成され、前記端子部は前記第1出力バンプ群と接続する第1端子群と前記第2出力バンプ群と接続する第2端子群とを有し、第2端子群の面積は第1端子群の面積より大きく構成されていることを特徴とする表示装置。

【請求項 2】

第1出力バンプ群および第2出力バンプ群のバンプは千鳥状に配置されていることを特徴とする請求項1に記載の表示装置。

【請求項 3】

第2出力バンプ群のバンプの幅は第1出力バンプ群のバンプの幅よりも大きく形成され 20

、これら各バンプと接続される信号線の端子の幅もそれに対応していることを特徴とする請求項1、2のいずれかに記載の表示装置。

【請求項4】

第2出力バンプ群のバンプの長さは第1出力バンプ群のバンプの長さよりも大きく形成され、これら各バンプと接続される信号線の端子の長さもそれに対応していることを特徴とする請求項1、2のいずれかに記載の表示装置。

【請求項5】

第2出力バンプ群のバンプの前記信号線の端子との対向面積を $S_i$ とし、第1出力バンプ群のバンプは前記信号線の端子との対向面積を $S_o$ とした場合、次式(1)

$$1.05S_o \geq S_i \geq 1.02S_o \dots \dots (1)$$

10

が成立していることを特徴とする請求項1に記載の表示装置。

【請求項6】

第2出力バンプ群のバンプの面積は第1出力バンプ群のバンプの面積よりも2~5%大きくなっていることを特徴とする請求項1に記載の表示装置。

【請求項7】

一方の基板に、 $x$ 方向に延在され $y$ 方向に並設されるゲート信号線と $y$ 方向に延在され $x$ 方向に並設されるドレイン信号線で囲まれた複数の画素領域からなる表示部を有し、

これら画素領域に片側のゲート信号線からの走査信号で作動するスイッチング素子と、このスイッチング素子を介して片側のドレイン信号線からの映像信号が供給される画素電極を備えたもので、

20

前記信号線はゲート信号線であり、半導体チップは走査信号駆動回路であることを特徴とする請求項1記載の表示装置。

【請求項8】

一方の基板に、 $x$ 方向に延在され $y$ 方向に並設されるゲート信号線と $y$ 方向に延在され $x$ 方向に並設されるドレイン信号線で囲まれた複数の画素領域からなる表示部を有し、

これら画素領域に片側のゲート信号線からの走査信号で作動するスイッチング素子と、このスイッチング素子を介して片側のドレイン信号線からの映像信号が供給される画素電極を備えたもので、

前記信号線はドレイン信号線であり、半導体チップは映像信号駆動回路であることを特徴とする請求項1記載の表示装置。

30

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は表示装置に係り、たとえばアクティブ・マトリクス方式と称される液晶表示装置に関する。

【0002】

【従来の技術】

この種の液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、 $x$ 方向に延在し $y$ 方向に並設される各ゲート信号線と $y$ 方向に延在し $x$ 方向に並設される各ドレイン信号線で囲まれた各領域を画素領域としている。

40

そして、各画素領域には、片側のゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介して片側のドレイン信号線からの映像信号が供給される画素電極とが備えられている。

この画素電極は前記一方の基板あるいは他方の基板側に形成された対向電極との間に電界を生じせしめ、この電界によって液晶の光透過率を制御させるようになっている。

【0003】

また、前記一方の基板の液晶側の面の周辺には、走査信号駆動回路を構成する半導体集積回路(チップ)、映像信号駆動回路を構成する半導体集積回路(チップ)が、そのバンプ形成面を下にして(フェースダウン)そのまま実装されている(COG: Chip On Glass方式)ものが知られている。

50

すなわち、フェースダウンされる走査信号駆動回路を構成する半導体集積回路の各出力バンプに対向する位置にまでゲート信号線が延在され、この延在された部分に前記出力バンプに接続される端子が形成されている。また、映像信号駆動回路を構成する半導体集積回路とドレイン信号線との関係においても同様となっている。

#### 【0004】

さらに、液晶表示装置の近年における高精細化の傾向において、画素数が多くなり、これにともないゲート信号線およびドレイン信号線の数も多くなってきている。

このため、少なくとも半導体集積回路の信号線と接続されるべくバンプ（出力バンプ）は、該信号線側に配列された第1バンプ群と該信号線と遠のく側に配列された第2バンプ群とで構成し、該バンプの数を多くしたものが知られている。

10

#### 【0005】

##### 【発明が解決しようとする課題】

このような表示装置において、前記半導体集積回路は異方性導電層を介して基板に固着させるとともに、対応する各端子との接続を図っている。

しかし、この場合、第1バンプ群を構成する各バンプとそれらに接続される各端子との接続抵抗に対して、第2バンプ群を構成する各バンプとそれらに接続される各端子との接続抵抗が大きくなるとともに、最悪の場合は接続不良を引き起こすことが指摘された。

本発明は、このような事情に基づいてなされたものであり、その目的は、実装される半導体集積回路と信号線との接続を信頼あるものとした表示装置を提供することにある。

#### 【0006】

20

##### 【課題を解決するための手段】

本発明において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

すなわち、本発明による表示装置は、対向配置される基板のうち一方の基板に、一方向に延在し該一方向に交差する方向に並設された複数の信号線と、信号線から供給される信号により駆動し画像を表示する表示部と、信号線の一端側にバンプ形成面を下にして実装された半導体チップと、を備え、この半導体チップ複数の出力バンプは異方性導電層を介して対応する各信号線と接続されるとともに、前記各出力バンプは表示部に近い側に配列される第1出力バンプ群と表示部に遠のく側に配列される第2出力バンプ群とを有し、第2出力バンプ群のバンプの面積は第1出力バンプ群の各バンプ前記信号線との接触面積より大きく構成されていることを特徴とする。

30

このように構成された表示装置は、第2出力バンプ群の各バンプの前記信号線との接触部分において、異方性導電層内の導電性微粒子が多く留まり、第1出力バンプ群の各バンプの前記信号線との接触部分における導電性微粒子の数と大差がなくなるようになる。

このため、第2バンプ群を構成する各バンプとそれらに接続される信号線との接続抵抗が大きくなったり、最悪の場合は接続不良を引き起こすということがなくなる。

#### 【0007】

##### 【発明の実施の形態】

以下、本発明による液晶表示装置の実施例を図面を用いて説明する。

##### 〔実施例1〕

40

##### 《等価回路》

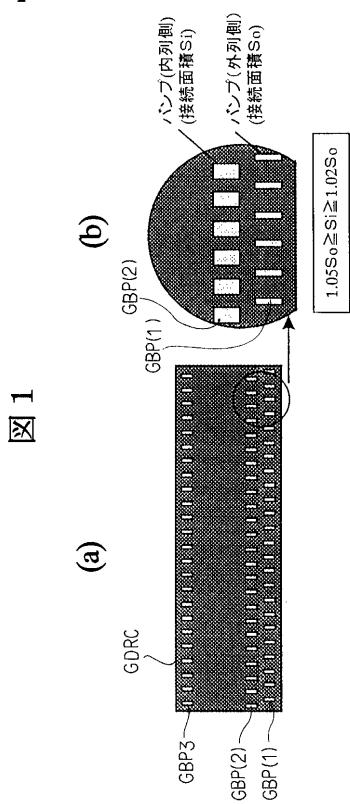

図2は本発明による液晶表示装置の一実施例を示す等価回路図である。同図は回路図であるが、実際の幾何学的配置に対応して描かれている。

同図において、透明基板SUB1があり、この透明基板SUB1は液晶を介して他の透明基板SUB2と対向して配置されている。

#### 【0008】

前記透明基板SUB1の液晶側の面には、図中x方向に延在しy方向に並設されるゲート信号線GLと、このゲート信号線GLと絶縁されてy方向に延在しx方向に並設されるドレイン信号線DLとが形成され、これら各信号線で囲まれる矩形状の領域が画素領域となり、これら各画素領域の集合によって表示部ARを構成するようになっている。

50

## 【0009】

各画素領域には、一方のゲート信号線 G L からの走査信号（電圧）の供給によって駆動される薄膜トランジスタ TFT と、この薄膜トランジスタ TFT を介して一方のドレイン信号線 D L からの映像信号（電圧）が供給される画素電極 PIX が形成されている。

## 【0010】

また、画素電極 PIX と前記一方のゲート信号線 G L と隣接する他方のゲート信号線 G L との間には容量素子 Cadd が形成され、この容量素子 Cadd によって、前記薄膜トランジスタ TFT がオフした際に、画素電極 PIX に供給された映像信号を長く蓄積させるようになっている。

## 【0011】

各画素領域における画素電極 PIX は、たとえば液晶を介して対向配置される他方の透明基板 SUB 2 の液晶側の面にて各画素領域に共通に形成された対向電極 CT ( 図示せず ) との間に電界を発生せしめるようになっており、これにより各電極の間の液晶の光透過率を制御するようになっている。

## 【0012】

各ゲート信号線 G L の一端は透明基板の一辺側 ( 図中左側 ) に延在され、その延在部は該透明基板 SUB 1 に搭載される垂直走査回路からなる半導体集積回路 GDRC のバンプと接続される端子部 GTM が形成され、また、各ドレイン信号線 D L の一端も透明基板 SUB 1 の一辺側 ( 図中上側 ) に延在され、その延在部は該透明基板 SUB 1 に搭載される映像信号駆動回路からなる半導体集積回路 DDRD がバンプと接続される端子部 DTM が形成されている。

## 【0013】

半導体集積回路 GDRC 、 DDRD はそれぞれ、それ自体が透明基板 SUB 1 上に完全に搭載されたもので、いわゆる COG ( チップオングラス ) 方式と称されている。

## 【0014】

半導体集積回路 GDRC 、 DDRD の入力側の各バンプも透明基板 SUB 1 に形成された端子部 GTM2 、 DTM2 にそれぞれ接続されるようになっており、これら各端子部 GTM2 、 DTM2 は各配線層を介して透明基板 SUB 1 の周辺のうち最も端面に近い部分にそれぞれ配置された端子部 GTM3 、 DTM3 に接続されるようになっている。

## 【0015】

前記透明基板 SUB 2 は、前記半導体集積回路が搭載される領域を回避するようにして透明基板 SUB 1 と対向配置され、該透明基板 SUB 1 よりも小さな面積となっている。

## 【0016】

そして、透明基板 SUB 1 に対する透明基板 SUB 2 の固定は、該透明基板 SUB 2 の周辺に形成されたシール材 SL によってなされ、このシール材 SL は透明基板 SUB 1 、 SUB 2 の間の液晶を封止する機能も兼ねている。

## 【0017】

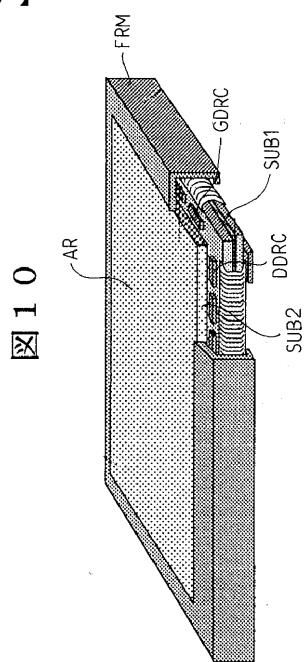

なお、このように構成された液晶表示装置は、図 10 に示すように、少なくとも表示部 AR に開口が形成されたフレーム FRM によって被われて液晶表示モジュールを構成するようになっている。

## 【0018】

## 《半導体集積回路の近傍の構成》

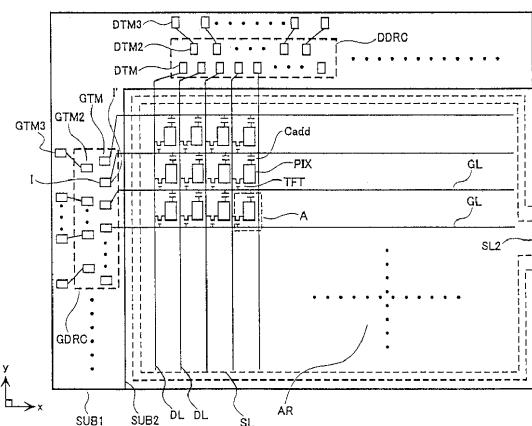

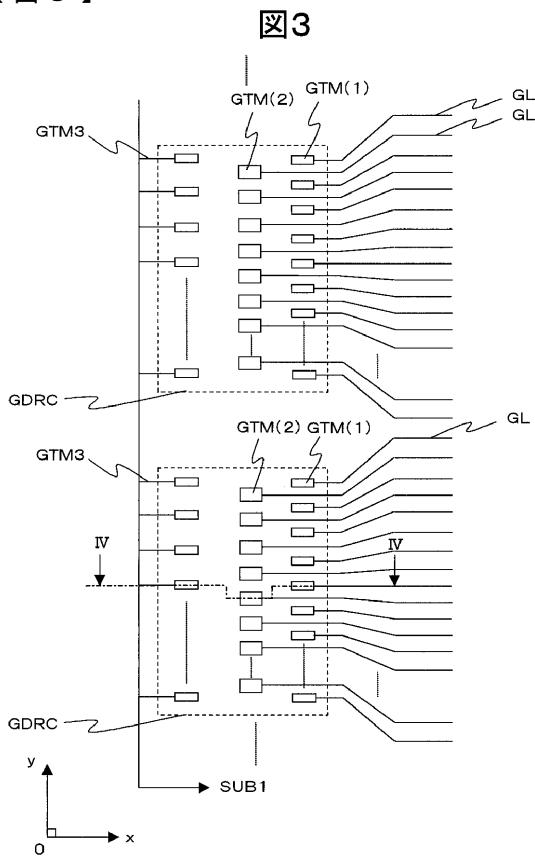

図 3 は、前記半導体集積回路 GDRC が実装される近傍の透明基板 SUB 1 面のより具体的な構成を示す平面図である。

図中 y 方向に並設される各ゲート信号線 G L は互いに隣接するもの同士でグループ化され、これら各グループの各ゲート信号線 G L は半導体集積回路 GDRC の実装領域の近傍で互いに収束するようにしたパターンで形成され、該半導体集積回路 GDRC の各出力バンプの対向する位置に端子 GTM が形成されている。

表示部 AR における各ゲート信号線 G L の間隔に対して半導体集積回路 GDRC のバンプの間隔が小さく設定されているからである。

10

20

30

40

50

## 【0019】

そして、この実施例では、半導体集積回路GDR<sub>C</sub>の各出力バンプに接続されるべく端子GTMは、列状に配置された第1端子群と第2端子群とから構成されている。

## 【0020】

第1端子群を構成する各端子GTM(1)はゲート信号線GL側に位置づけられ(後の説明では外列側と称することもある)、第2端子群を構成する各端子GTM(2)は該ゲート信号線GLに対して遠のく側に位置づけられている(後の説明では内列側と称することもある)。

## 【0021】

また、各端子GTM(2)は各端子GTM(1)の間に位置づけられて、各端子GTM(2)および各端子GTM(1)からなる各端子GTMはいわゆる千鳥状に配置されている。

10

## 【0022】

このため、端子GTM(2)と接続されるゲート信号線GLは、端子GTM(1)と接続されるゲート信号線GLの間に位置づけられるゲート信号線となり、隣接する端子GTM(1)の間を走行するようにして形成されている。

## 【0023】

さらに、第2端子群を構成する各端子GTM(2)は、その幅が第1端子群を構成する各端子GTM(1)の幅よりも大きく形成されている。

端子GTM(2)は、端子GTM(1)のようにそれに隣接してゲート信号線GLが形成されていないことから、端子GTM(1)の場合と比較して自由に幅を大きくできる。

20

## 【0024】

このように端子GTM(2)の幅を大きくするのは、半導体集積回路GDR<sub>C</sub>の対応する出力バンプとの対向面積を、端子GTM(1)の半導体集積回路GDR<sub>C</sub>の対応する出力バンプとの対向面積(たとえばこの実施例では $2400 \mu m^2$ )よりも大きく(たとえばこの実施例では2~5%)せんがためである。

## 【0025】

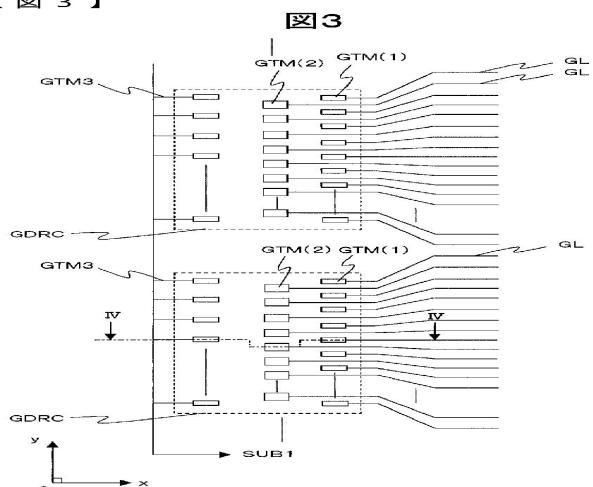

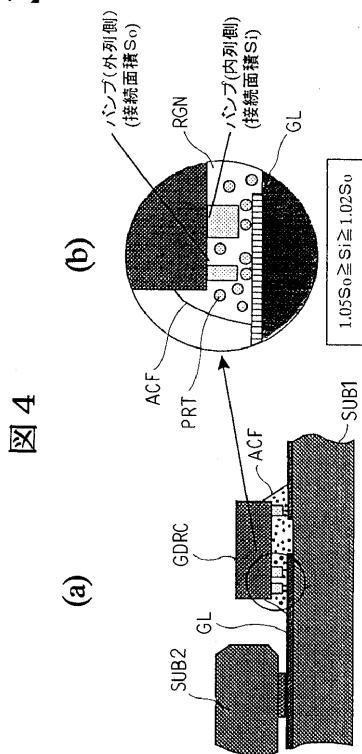

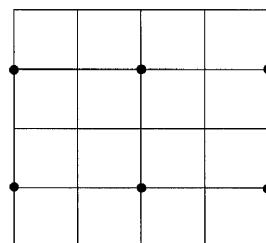

図1(a)は、前記半導体集積回路GDR<sub>C</sub>のバンプ形成面を示した平面図であり、図1(b)は図1(a)に示す実線丸の部分の拡大を示す拡大図である。同図から明らかとなるように、半導体集積回路GDR<sub>C</sub>の出力バンプGBPは列状に配置された第1バンプ群と第2バンプ群とから構成されている。

30

## 【0026】

第1バンプ群を構成する各バンプGBP(1)は前記ゲート信号線GLの端子GTM(1)に対応して位置づけられ、第2バンプ群を構成する各バンプGBP(2)は該ゲート信号線GLの端子GTM(2)に対応して位置づけられている。

このことから、前記端子GTMと同様、各バンプGBP(2)は各バンプGBP(1)の間に位置づけられて、各バンプGBP(2)および各バンプGBO(1)からなる各バンプGBPはいわゆる千鳥状に配置されている。

## 【0027】

そして、第2バンプ群を構成する各バンプGBP(2)は、その幅が第1バンプ群を構成する各バンプGBP(1)の幅よりも大きく形成されている。対応する端子GBP(2)との対向面積を、バンプGBP(1)の対応する端子GBP(1)との対向面積よりも大きくせんがためである。

40

## 【0028】

ここで、この実施例では、半導体集積回路GDR<sub>C</sub>のバンプGBP(1)の対応する端子GTM(1)との対向面積をS<sub>0</sub>、バンプGBP(2)の対応する端子GTM(2)との対向面積をS<sub>i</sub>とした場合、たとえば次式(1)が成立するように構成している。

$$1.05S_0 \gg S_i \gg 1.02S_0 \quad \dots \dots (1)$$

## 【0029】

図4(a)は、半導体集積回路GDR<sub>C</sub>を透明基板SUB1上に実装した場合の断面図を

50

示し、図3のIV-IV線における断面図に相当している。また、図4(b)は図4(a)の実線丸の部分における拡大図を示している。

【0030】

半導体集積回路GDRCと透明基板SUB1との間には異方性導電膜ACFが介在されている。この異方性導電膜ACFは導電性微粒子PRTを多数散在させた(たとえばこの実施例では30k個/mm<sup>2</sup>)樹脂膜RGNからなるものである。

【0031】

少なくともこの異方性導電膜ACFを加熱し、透明基板SUB1に対して半導体集積回路GDRCを加圧させることにより、半導体集積回路GDRCは透明基板SUB1に対して固着されるとともに、半導体集積回路GDRCの各バンプGBPと透明基板SUB1上の端子GTMは異方性導電膜ACF内の導電性微粒子を介して電気的に接続されるようになる。

10

【0032】

透明基板SUB1に対して半導体集積回路GDRCを加圧する場合、異方性導電膜ACFの樹脂膜RGN内で導電性微粒子PRTの流動が起こる。

しかし、この実施例では、半導体集積回路GDRCの内列側のバンプ群の各バンプGBP(2)とこのバンプGBP(2)と接続されるべく端子GTM(2)との間に介在される導電性微粒子PRTの数は、外列側のバンプ群の各バンプGBP(1)とこのバンプGBP(1)と接続されるべく端子GTM(1)との間に介在される導電性微粒子PRTの数と比べてほぼ同数とすることことができ、したがって、それらの接続抵抗はほぼ同じとすることができるようになる。この理由についての理論的解明および測定データに基づく解明は後に詳述する。

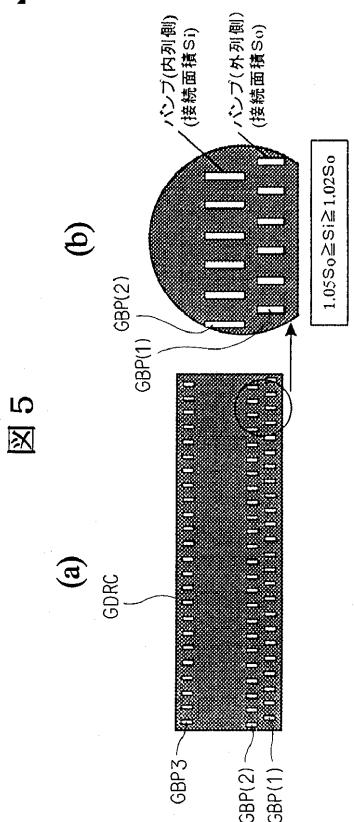

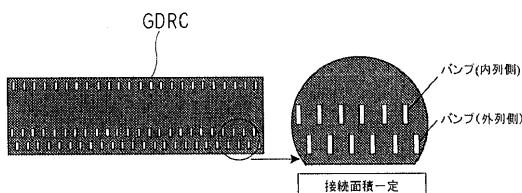

20

【0033】

なお、上述した実施例では、半導体集積回路GDLの出力バンプGBPのうち内列側のバンプGBP(2)およびこれに対向する端子GTM(2)の幅を外列側のバンプGBP(1)およびこれに対向する端子GTM(1)のそれよりも大きくしたものである。しかし、たとえば図5に示すように、内列側のバンプGBP(2)およびこれに対向する端子GTM(2)の長さを外列側のバンプGBP(1)およびこれに対向する端子GTM(1)のそれよりも大きくするようにしてもよいことはいうまでもない。

30

【0034】

また、上述した実施例では、半導体集積回路GDLの出力バンプGBPとこの出力バンプGBPと接続されるゲート信号線GLの端子BTMについて説明したものであるが、半導体集積回路DDLの出力バンプとこの出力バンプと接続されるドレイン信号線DLの端子DTMについても同様に適用できることはいうまでもない。

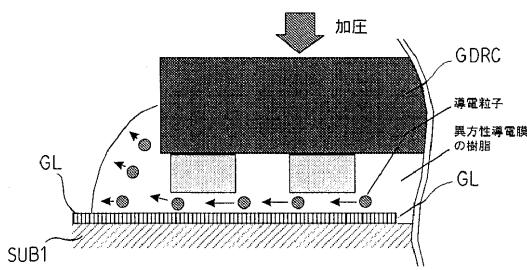

【0035】

《理論に基づく効果》

図6に示すように、いわゆるCOG方式の実装は、半導体集積回路GDRCの裏面側から圧力を加えて透明基板SUB1と該半導体集積回路GDRCとの間にある余分な樹脂を押し流して圧着し接続する。

40

【0036】

この場合内列側において、導電性粒子PRTが捕捉されにくい理由は圧着時の樹脂の流れに起因していると考えられる。圧着プロセス時に内列側のバンプ付近の樹脂は外列側のバンプよりも面内一様に押される傾向が強く、透明基板SUB1面内に平行に粒子が流動する。

【0037】

しかし、外列側のチップ端面に近い側では該端面に排出された樹脂により流動が妨げられるので流速が遅くなる。その結果、半導体集積回路GDRCのバンプ下に入ってくる樹脂に対して該バンプ下から離れる樹脂は過渡的に少なくなるので、透明基板SUB1との間に挟まれて残る導電性粒子は外列バンプで多くなると考えられる。

【0038】

50

このため、上述した実施例に示すように、内列側のバンプ G B P ( 2 ) とこのバンプ G B P ( 2 ) と接続されるべく端子 G T M ( 2 ) の面積を大きくすることによって、それらによって捕捉される導電性粒子の数は、外列側のバンプ G B P ( 1 ) とこのバンプ G B P ( 1 ) と接続されるべく端子 G T M ( 1 ) によって捕捉される導電性粒子とほぼ等しくすることができる。

## 【0039】

## 《測定データに基づく効果》

従来のバンプ構造である 2 列配列バンプ ( 図 8 参照 ) にて、実測データでは内列と外列で粒子数が異なっており、平均値として内列に比べて外列側の粒子捕捉数は 2 ~ 5 % 程度多い傾向が認められた。

10

## 【0040】

また、捕捉粒子の度数分布は理論的にポアソン分布になるので、バンプ下の残った捕捉粒子の平均値を  $m$  とすると、粒子が捕捉されていないバンプの発生確率は  $e \times p (-m)$  で計算される。

## 【0041】

この結果、内列と外列バンプが占める総面積は一定として、捕捉粒子の平均値がバンプ面積の変動に比例して変化すると仮定した場合の粒子が捕捉されていないバンプの発生確率が最も低くなる外列バンプに対する内列バンプ面積の比率を計算すると、次式 ( 2 ) に示される。

## 【0042】

20

$$F = e \times p (-m_i') / 2 + e \times p (-m_o') / 2 \dots \dots ( 2 )$$

ここで、 $m_i' = S_i / S \times m_i$  ( 捕捉粒子数とバンプ面積の関係式 ) 、 $m_o' = S_o / S \times m_o$  ( 捕捉粒子数とバンプ面積の関係式 ) 、 $S_i + S_o = 2S$  ( バンプ総面積を一定とする条件 ) 、 $dF / dS_i = 0$  ( バンプ総面積を最適化する条件 ) である。

## 【0043】

また、 $S$  ; 最適化していないバンプ面積 ( 内列と外列で面積は等しい ) 、 $m_i$  ; 内列バンプに捕捉された A C F 粒子の平均捕捉数 ( 実測データ ) 、 $m_o$  ; 外列バンプに捕捉された A C F 粒子の平均捕捉数 ( 実測データ ) 、 $S_i$  ; 最適化した内列のバンプ面積、 $S_o$  ; 最適化した外列のバンプ面積、 $m_i'$  ; 面積最適化後の内列バンプに捕捉された A C F 粒子の平均捕捉数 ( 推定値 ) 、 $m_o'$  ; 面積最適化後の外列バンプに捕捉された A C F 粒子の平均捕捉数 ( 推定値 ) 、 $F$  ; 内列バンプの平均捕捉粒子数  $m_i'$  、外列バンプの平均捕捉粒子数  $m_o'$  である場合の粒子なしバンプの推定発生率 ( 1 バンプ当たり ) である。

30

## 【0044】

そして、上式 ( 2 ) を各計測データ毎に形成した結果を図 7 に示す。計測データに基づくと比率として 2 ~ 5 % の範囲で面積に差をつけた場合が最適値となった。

なお、バンプ上粒子数の分布の近似式は次のようにして算出することができる。

## 【0045】

まず、図 9 に示した図をもとに、本圧着後の単位面積当たりの母平均粒子密度を  $n$  ( 個 /  $\text{mm}^2$  ) 、単位面積を  $n$  当分した場合の小領域の面積を  $a$  とすると、小領域に粒子が存在する確率は  $a$  である。小領域を  $n$  個サンプリングしたときに粒子有り領域が  $r$  個存在する確率  $P(r)$  は二項目分布に従うから、次式 ( 3 ) が成立する。

40

$$P(r) = {}_n C_r \cdot a^r \cdot (1 - a)^{n-r} \dots \dots ( 3 )$$

これは  $a$  より大きい面積の少領域  $b$  でも成り立つ。

## 【0046】

すなわち、次式 ( 4 ) も成立する。

$$P(r) = {}_n C_r \cdot b^r \cdot (1 - b)^{n-r} \dots \dots ( 4 )$$

この場合の平均値は  $n b$  、分散  $^2$  は  $n b (1 - b)$  となる。

$n$  が大きい場合や  $b$  が非常に小さい場合には、式 ( 3 ) はポアソン分布で近似でき、次式 ( 5 ) を得る。

## 【0047】

50

$$P(r) = (n b)^r \cdot e^{-(n b)} / r! \quad \dots \dots (5)$$

$n b$  は小領域内の平均粒子数であるから、 $n b = m$  とすると式 (5) は、次式 (6) で近似される。

【0048】

$$P(r) = m^r \cdot e^{-m} / r! \quad \dots \dots (6)$$

この場合、 $r^2 = m$  となり確率は 1 变数  $m$  のみで表せる。

ポアソン分布の応用例として、顕微鏡視野内のバクテリア数、量産品の不良等がある。

【0049】

【発明の効果】

以上説明したことから明らかなように、本発明による表示装置によれば、実装される半導体集積回路と信号線との接続を信頼あるものとすることができます。

【図面の簡単な説明】

【図 1】本発明による液晶表示装置に実装される半導体集積回路の一実施例を示す構成図である。

【図 2】本発明による液晶表示装置の一実施例を示す全体等価回路である。

【図 3】本発明による液晶表示装置に実装される半導体集積回路の近傍の透明基板表面の一実施例を示す平面図である。

【図 4】図 3 の IV - IV 線における断面図である。

【図 5】本発明による液晶表示装置に実装される半導体集積回路の他の実施例を示す構成図である。

【図 6】本発明による液晶表示装置の理論による効果を示す説明図である。

【図 7】本発明による液晶表示装置の測定データによる効果を示す説明図である。

【図 8】従来の液晶表示装置に実装される半導体集積回路の一例を示す構成図である。

【図 9】バンプ上粒子数の分布の近似式を得るための参考図である。

【図 10】本発明による液晶表示装置の一実施例を示す斜視図である。

【符号の説明】

S U B ... 透明基板、G L ... ゲート信号線、D L ... ドレイン信号線、P I T ... 画素電極、T F T ... 薄膜トランジスタ、G D R C ... 半導体集積回路（走査信号駆動回路）、D D R C ... 半導体集積回路（映像信号駆動回路）、G T M (1) ... 第 1 端子群、G T M (2) ... 第 2 端子群、G B P (1) ... 第 1 バンプ群、G B P (2) ... 第 2 バンプ群。

10

20

30

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

| 表1. 2列配列リシング下に捕捉されたACF粒子数と最適化による面積割付け結果 |                  |

|-----------------------------------------|------------------|

| ACFの仕様<br>(仕様の組み合わせで表記)                 | リシング下ACF粒子捕捉数    |

| 樹脂 ①-基準径-粒子径-粒子密度                       | 内列側 mi<br>外列側 mo |

| 樹脂 ①-基準径-低い                             | 7.72 8.08        |

| 樹脂 ②-基準径-基準                             | 8.34 8.65        |

| 樹脂 ②-基準径-基準                             | 9.91 10.25       |

| 樹脂 ③-基準径-基準                             | 11.37 11.95      |

| 樹脂 ④-基準径-基準                             | 11.13 11.68      |

| 樹脂 ②-基準径-高い                             | 13.39 13.69      |

| 樹脂 ③-小さい-高い                             | 13.56 13.86      |

図7

【図8】

図8

【図9】

図9

【図 10】

---

フロントページの続き

審査官 右田 昌士

(56)参考文献 特開2000-347206 (JP, A)

特開2000-276073 (JP, A)

特開平07-273119 (JP, A)

特開平07-235564 (JP, A)

特開平06-275123 (JP, A)

特開平06-053413 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1345

G09F 9/00 - 9/46

H01L 21/447 - 21/449

H01L 21/60 - 21/607

H05K 1/18

|                |                                                                                                                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP3781967B2</a>                                                                                                                                                                                                                                             | 公开(公告)日 | 2006-06-07 |

| 申请号            | JP2000392324                                                                                                                                                                                                                                                            | 申请日     | 2000-12-25 |

| [标]申请(专利权)人(译) | 株式会社日立制作所<br>日立器件工程株式会社                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所<br>日立设备工程有限公司                                                                                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所<br>日立设备工程有限公司                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 山手洋<br>竹中雄一                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 山手 洋<br>竹中 雄一                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/1345 G09F9/00 H01L21/60 G02F1/13 G02F1/1368                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G02F1/1345 G02F1/13452 H01L2224/16225 H01L2224/32225 H01L2224/73204 H01L2924/00014<br>H01L2924/00 H01L2224/0401                                                                                                                                                         |         |            |

| FI分类号          | G02F1/1345 G09F9/00.348.C H01L21/60.311.S G02F1/1368 G09F9/00.348.Z                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 2H092/GA41 2H092/GA48 2H092/GA60 2H092/HA25 2H092/JA24 2H092/NA11 2H092/PA06 2H192<br>/AA24 2H192/DA02 2H192/FA52 2H192/FB25 2H192/FB72 2H192/GA41 5F044/KK01 5F044/LL09<br>5F044/QQ02 5G435/AA14 5G435/AA16 5G435/BB12 5G435/EE37 5G435/EE41 5G435/EE42 5G435<br>/HH12 |         |            |

| 其他公开文献         | JP2002196353A<br>JP2002196353A5                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

要解决的问题：提高待安装的半导体集成电路与信号线之间的连接可靠性。解决方案：该液晶显示装置具有沿一个方向延伸并沿一个方向交叉的方向排列的各个信号线和安装在这些信号线的一端侧的半导体芯片，同时其凸块形成侧为指向通过液晶相对设置的基板的一个基板的液晶侧的表面向下。在该器件中，半导体芯片的各个输出凸块通过各向异性导电层连接到相应的信号线，并且具有布置在靠近信号线的一侧的第一输出凸块组和布置的第二输出凸块组。在远离信号线的一侧，并且面对具有第二输出凸块组的各个凸块的信号线的区域构成为大于具有第一输出的各个凸块的信号线的面对区域的区域碰撞组。

【图3】