(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-9393

(P2008-9393A)

(43) 公開日 平成20年1月17日(2008.1.17)

| (51) Int.CI.                                                                                                                                                                                                                      | F 1                          | テーマコード (参考)                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------|

| <b>G09G 3/36 (2006.01)</b>                                                                                                                                                                                                        | G09G 3/36                    | 2H092                               |

| <b>G09G 3/20 (2006.01)</b>                                                                                                                                                                                                        | G09G 3/20                    | 2H093                               |

| <b>G02F 1/1345 (2006.01)</b>                                                                                                                                                                                                      | G09G 3/20                    | 5C006                               |

| <b>G02F 1/133 (2006.01)</b>                                                                                                                                                                                                       | G09G 3/20                    | 5C080                               |

|                                                                                                                                                                                                                                   | G09G 3/20                    | 622E                                |

| 審査請求 未請求 請求項の数 11 O L (全 112 頁) 最終頁に続く                                                                                                                                                                                            |                              |                                     |

| (21) 出願番号                                                                                                                                                                                                                         | 特願2007-136385 (P2007-136385) | (71) 出願人 000153878                  |

| (22) 出願日                                                                                                                                                                                                                          | 平成19年5月23日 (2007.5.23)       | 株式会社半導体エネルギー研究所                     |

| (31) 優先権主張番号                                                                                                                                                                                                                      | 特願2006-155472 (P2006-155472) | 神奈川県厚木市長谷398番地                      |

| (32) 優先日                                                                                                                                                                                                                          | 平成18年6月2日 (2006.6.2)         | (72) 発明者 梅崎 敦司                      |

| (33) 優先権主張国                                                                                                                                                                                                                       | 日本国 (JP)                     | 神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内 |

| F ターム (参考) 2H092 GA59 GA60 JA21 JA25 JA26<br>JB69 KA03 KA04 KA05 MA10<br>NA21 NA22 NA27 NA29 PA06<br>2H093 NA16 NC09 NC11 NC22 NC34<br>NC35 ND39 ND48 ND49<br>5C006 BF03 BF34 FA41<br>5C080 AA10 BB05 DD22 DD29 EE28<br>JJ03 JJ04 |                              |                                     |

(54) 【発明の名称】 液晶表示装置及び電子機器

## (57) 【要約】

【課題】シフトレジスタなどに用いられる新規な回路を提供する。

【解決手段】基本構成は、第1のトランジスタ～第4のトランジスタと、第1の配線～第4の配線を有する。第1の配線には電源電位VDDが供給され、第2の配線には電源電位VSSが供給されている。第3の配線、第4の配線には2値の値を持つデジタル信号が供給される。

このデジタル信号は、高レベルのときには電源電位VDDと同電位となり、低レベルのときには電源電位VSSと同電位である。第3の配線と第4の配線の電位の組み合わせは4通りあるが、第1のトランジスタ～第4トランジスタは、いずれかの電位の組み合わせによりオフさせることができる。つまり、定的にオン状態となるトランジスタがないため、トランジスタの特性劣化が抑制することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

液晶素子を有する画素と、駆動回路とを有し、

前記駆動回路は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタとを有し、

前記第1のトランジスタのゲート及び第1端子が第1の配線に電気的に接続され、前記第1のトランジスタの第2端子が前記第4のトランジスタのゲートに電気的に接続され、

前記第2のトランジスタのゲートが第2の配線に電気的に接続され、前記第2のトランジスタの第1端子が第4の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第4のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタのゲートが第3の配線に電気的に接続され、前記第3のトランジスタの第1端子が前記第4の配線に電気的に接続され、第3のトランジスタの第2端子が前記第4のトランジスタのゲートに電気的に接続され、

前記第4のトランジスタの第1端子が前記第4の配線に電気的に接続され、前記第4のトランジスタの第2端子が第5の配線に電気的に接続されていることを特徴とする液晶表示装置。

**【請求項 2】**

請求項1において、

前記第1のトランジスタ乃至前記第4のトランジスタは同じ導電型のトランジスタであることを特徴とする液晶表示装置。

**【請求項 3】**

請求項1または請求項2において、

前記第1のトランジスタ乃至前記第4のトランジスタの半導体層に非結晶半導体が用いられていることを特徴とする液晶表示装置。

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、

前記第1のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、前記第2のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きいことを特徴とする液晶表示装置。

**【請求項 5】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、前記第3のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きいことを特徴とする液晶表示装置。

**【請求項 6】**

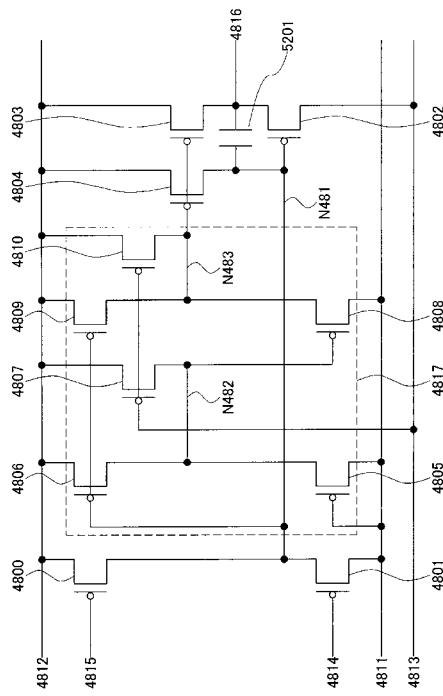

液晶素子を有する画素と、駆動回路とを有し、

前記駆動回路は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、第8のトランジスタとを有し、

前記第1のトランジスタのゲートが第1の配線に電気的に接続され、前記第1のトランジスタの第1端子が第2の配線に電気的に接続され、前記第1のトランジスタの第2端子が第2のトランジスタのゲートに電気的に接続され、

前記第8のトランジスタのゲートが第4の配線に電気的に接続され、前記第8のトランジスタの第1端子が第5の配線に電気的に接続され、前記第8のトランジスタの第2端子が前記第2のトランジスタのゲートに電気的に接続され、

前記第6のトランジスタのゲートが前記第2のトランジスタのゲートに電気的に接続され、前記第6のトランジスタの第1端子が前記第5の配線に電気的に接続され、前記第6のトランジスタの第2端子が前記第3のトランジスタのゲートおよび前記第4のトランジスタのゲートに電気的に接続され、

前記第5のトランジスタのゲート及び第1端子が前記第2の配線に電気的に接続され、前

10

20

30

40

50

記第5のトランジスタの第2端子が前記第3のトランジスタのゲートおよび前記第4のトランジスタのゲートに電気的に接続され、

前記第7のトランジスタのゲートが第3の配線に電気的に接続され、前記第7のトランジスタの第1端子が前記第5の配線に電気的に接続され、前記第7のトランジスタの第2端子が前記第3のトランジスタのゲートおよび前記第4のトランジスタのゲートに電気的に接続され、

前記第4のトランジスタの第1端子が前記第5の配線に電気的に接続され、前記第4のトランジスタの第2端子が前記第2のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタの第1端子が前記第5の配線に電気的に接続され、前記第3のトランジスタの第2端子が第6の配線に電気的に接続され、

前記第2のトランジスタの第1端子が前記第3の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第6の配線に電気的に接続されていることを特徴とする液晶表示装置。

#### 【請求項7】

請求項6において、

前記第1のトランジスタ乃至前記第8のトランジスタは同じ導電型のトランジスタであることを特徴とする液晶表示装置。

#### 【請求項8】

請求項6及び請求項7のうちいずれか一項において、

前記第1のトランジスタ乃至前記第8のトランジスタの半導体層に非結晶半導体が用いられていることを特徴とする液晶表示装置。

#### 【請求項9】

請求項6乃至請求項8のいずれか一項において、

前記第5のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、前記第6のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きいことを特徴とする液晶表示装置。

#### 【請求項10】

請求項6乃至請求項9のいずれか一項において、

前記第5のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、前記第7のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きいことを特徴とする液晶表示装置。

#### 【請求項11】

請求項1乃至請求項10のいずれか一項に記載の液晶表示装置を具備する電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置に関する。また、半導体装置を具備する表示装置、特に半導体装置を具備する液晶表示装置、及び当該液晶表示装置を具備する電子機器に関する。

##### 【背景技術】

##### 【0002】

近年、液晶表示装置や発光装置などの表示装置は、液晶テレビなどの大型表示装置の増加から、活発に開発が進められている。特に絶縁体上に非結晶半導体により形成されたトランジスタを用いて、画素回路、及びシフトレジスタ回路等を含む駆動回路（以下、内部回路という）を一体形成する技術は、低消費電力化、低コスト化に大きく貢献するため、活発に開発が進められている。絶縁体上に形成された内部回路は、FPC等を介して絶縁体の外に配置されたコントローラIC等（以下、外部回路という）と接続され、その動作が制御されている。

##### 【0003】

また、絶縁体上に一体形成された内部回路として、非結晶半導体のトランジスタを用いて構成されるシフトレジスタが考案されている（特許文献1参照）。

**【 0 0 0 4 】**

しかしながら、非結晶半導体のトランジスタの特性は、オンする時間、又は印加電圧に応じて、劣化してしまう問題があった。これを解決するために、2つのトランジスタを並列に接続して、トランジスタを順にオンすることで、トランジスタの特性劣化を抑制することが考案されている（非特許文献1参照）。

【特許文献1】特開2004-78172号公報

【非特許文献1】SID '05 DIGEST P348～P351

**【発明の開示】****【発明が解決しようとする課題】****【 0 0 0 5 】**

上記、非特許文献1では、詳しい駆動方法が開示されていない。また、並列に接続された2つのトランジスタを1つずつ制御するためには、回路規模が大きい制御回路が必要になる。

**【 0 0 0 6 】**

このような問題点に鑑み、本発明では、比較的回路規模が小さい制御回路を用いたフリップフロップ回路、シフトレジスタ、及びこのようなシフトレジスタを具備する半導体装置、並びに表示装置、及び当該表示装置を具備する電子機器を提供することを目的とする。

**【 0 0 0 7 】**

また、本発明では、従来技術とは別のトランジスタの特性劣化を抑制する駆動方法を用いたフリップフロップ回路、シフトレジスタ、及びこのようなシフトレジスタを具備する半導体装置、並びに表示装置、及び当該表示装置を具備する電子機器を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 0 8 】**

本発明の半導体装置の一は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタとを有し、第1のトランジスタのゲート及び第1端子が第1の配線に電気的に接続され、第1のトランジスタの第2端子が第4のトランジスタのゲートに電気的に接続され、第2のトランジスタのゲートが第2の配線に電気的に接続され、第2のトランジスタの第1端子が第4の配線に電気的に接続され、第2のトランジスタの第2端子が第4のトランジスタのゲートに電気的に接続され、第3のトランジスタのゲートが第3の配線に電気的に接続され、第3のトランジスタの第1端子が第4の配線に電気的に接続され、第3のトランジスタの第2端子が第4のトランジスタのゲートに電気的に接続され、第4のトランジスタの第1端子が第4の配線に電気的に接続され、第4のトランジスタの第2端子が第5の配線に電気的に接続されていることを特徴とする構成である。

**【 0 0 0 9 】**

第1のトランジスタ乃至第4のトランジスタは同じ導電型のトランジスタであっても良い。また、第1のトランジスタ乃至第4のトランジスタの半導体層に非結晶半導体が用いられても良い。

**【 0 0 1 0 】**

なお、第1のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、第2のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きくしても良い。

**【 0 0 1 1 】**

また、第1のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、第3のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きくしても良い。

**【 0 0 1 2 】**

本発明の半導体装置の一は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、第8のトランジスタとを有し、第1のトランジスタのゲートが第1の配線に電気的に接続され、第1のトランジスタの第1端子が第2の配線に電気的に接続

10

20

30

40

50

され、第1のトランジスタの第2端子が第2のトランジスタのゲートに電気的に接続され、第8のトランジスタのゲートが第4の配線に電気的に接続され、第8のトランジスタの第1端子が第5の配線に電気的に接続され、第8のトランジスタの第2端子が第2のトランジスタのゲートに電気的に接続され、第6のトランジスタのゲートが第2のトランジスタのゲートに電気的に接続され、第6のトランジスタの第1端子が第5の配線に電気的に接続され、第6のトランジスタの第2端子が第3のトランジスタのゲートおよび第4のトランジスタのゲートに電気的に接続され、第5のトランジスタのゲート及び第1端子が第2の配線に電気的に接続され、第5のトランジスタの第2端子が第3のトランジスタのゲートおよび第4のトランジスタのゲートに電気的に接続され、第7のトランジスタのゲートが第3の配線に電気的に接続され、第7のトランジスタの第1端子が第5の配線に電気的に接続され、第7のトランジスタの第2端子が第3のトランジスタのゲートおよび第4のトランジスタのゲートに電気的に接続され、第4のトランジスタの第1端子が第5の配線に電気的に接続され、第3のトランジスタの第2端子が第6の配線に電気的に接続され、第2のトランジスタの第1端子が第3の配線に電気的に接続され、第2のトランジスタの第2端子が第6の配線に電気的に接続されていることを特徴とする構成である。

10

#### 【0013】

なお、第1のトランジスタ乃至第8のトランジスタは同じ導電型のトランジスタとしてもよい。また、第1のトランジスタ乃至第8のトランジスタの半導体層に非結晶半導体が用いられていても良い。

20

#### 【0014】

なお、第5のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、第6のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きくしてもよい。

#### 【0015】

なお、第5のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、第7のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きくしてもよい。

#### 【0016】

また、本発明の半導体装置は、液晶表示装置に用いてもよい。

30

#### 【0017】

本発明の液晶表示装置の一は、液晶素子を有する画素と、駆動回路とを有し、駆動回路は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタとを有し、第1のトランジスタのゲート及び第1端子が第1の配線に電気的に接続され、第1のトランジスタの第2端子が第4のトランジスタのゲートに電気的に接続され、第2のトランジスタのゲートが第2の配線に電気的に接続され、第2のトランジスタの第1端子が第4の配線に電気的に接続され、第2のトランジスタの第2端子が第4のトランジスタのゲートに電気的に接続され、第3のトランジスタのゲートが第3の配線に電気的に接続され、第3のトランジスタの第1端子が第4の配線に電気的に接続され、第3のトランジスタの第2端子が第4のトランジスタのゲートに電気的に接続され、第4のトランジスタの第1端子が第4の配線に電気的に接続され、第4のトランジスタの第2端子が第5の配線に電気的に接続されていることを特徴とする構成である。

40

#### 【0018】

第1のトランジスタ乃至第4のトランジスタは同じ導電型のトランジスタであっても良い。また、第1のトランジスタ乃至第4のトランジスタの半導体層に非結晶半導体が用いられていても良い。

#### 【0019】

なお、第1のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、第2のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lよりも大きくしてもよい。

#### 【0020】

また、第1のトランジスタのチャネル幅Wとチャネル長Lとの比W/Lは、第3のトラン

50

ジスタのチャネル幅Wとチャネル長Lとの比W / Lよりも大きくしても良い。

【0021】

本発明の液晶表示装置の一は、液晶素子を有する画素と、駆動回路とを有し、駆動回路は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、第8のトランジスタとを有し、第1のトランジスタのゲートが第1の配線に電気的に接続され、第1のトランジスタの第1端子が第2の配線に電気的に接続され、第1のトランジスタの第2端子が第2のトランジスタのゲートに電気的に接続され、第8のトランジスタのゲートが第4の配線に電気的に接続され、第8のトランジスタの第1端子が第5の配線に電気的に接続され、第8のトランジスタの第2端子が第2のトランジスタのゲートに電気的に接続され、第6のトランジスタのゲートが第2のトランジスタのゲートに電気的に接続され、第6のトランジスタの第1端子が第5の配線に電気的に接続され、第6のトランジスタの第2端子が第3のトランジスタのゲートおよび第4のトランジスタのゲートに電気的に接続され、第5のトランジスタのゲート及び第1端子が第2の配線に電気的に接続され、第5のトランジスタの第2端子が第3のトランジスタのゲートおよび第4のトランジスタのゲートに電気的に接続され、第7のトランジスタのゲートが第3の配線に電気的に接続され、第7のトランジスタの第2端子が第3のトランジスタのゲートおよび第4のトランジスタのゲートに電気的に接続され、第7のトランジスタの第1端子が第5の配線に電気的に接続され、第7のトランジスタの第2端子が第3のトランジスタのゲートおよび第4のトランジスタのゲートに電気的に接続され、第4のトランジスタの第1端子が第5の配線に電気的に接続され、第4のトランジスタの第2端子が第2のトランジスタのゲートに電気的に接続され、第3のトランジスタの第1端子が第5の配線に電気的に接続され、第3のトランジスタの第2端子が第6の配線に電気的に接続され、第2のトランジスタの第1端子が第3の配線に電気的に接続され、第2のトランジスタの第2端子が第6の配線に電気的に接続されていることを特徴とする構成である。10

【0022】

なお、第1のトランジスタ乃至第8のトランジスタは同じ導電型のトランジスタとしてもよい。また、第1のトランジスタ乃至第4のトランジスタの半導体層に非結晶半導体が用いられていてもよい。20

【0023】

なお、第5のトランジスタのチャネル幅Wとチャネル長Lとの比W / Lは、第6のトランジスタのチャネル幅Wとチャネル長Lとの比W / Lよりも大きくしてもよい。30

【0024】

なお、第5のトランジスタのチャネル幅Wとチャネル長Lとの比W / Lは、第7のトランジスタのチャネル幅Wとチャネル長Lとの比W / Lよりも大きくしてもよい。40

【0025】

なお、本発明に示すスイッチは、様々な形態のものを用いることができ、一例として、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トランジスタでもよいし、ダイオード（例えば、P Nダイオード、P I Nダイオード、ショットキーダイオード、ダイオード接続のトランジスタなど）でもよいし、サイリスタでもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、L D D領域を設けているものやマルチゲート構造にしているもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源（V<sub>ss</sub>、GND、0Vなど）に近い状態で動作する場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源（V<sub>dd</sub>など）に近い状態で動作する場合はPチャネル型を用いることが望ましい。これは、ゲートソース間電圧の絶対値を大きくすることで、スイッチとして、動作しやすくなるからである。50

**【 0 0 2 6 】**

なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。CMOS型のスイッチにすると、Pチャネル型或いはNチャネル型のいずれかのスイッチが導通すれば電流を流すことができるため、スイッチとして機能しやすくなる。例えば、スイッチへの入力信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることが出来る。また、スイッチをオン・オフさせるための信号の電圧振幅値を小さくすることが出来るので、消費電力を小さくすることも出来る。

**【 0 0 2 7 】**

なお、スイッチとしてトランジスタを用いる場合は、入力端子（ソース端子またはドレイン端子の一方）と、出力端子（ソース端子またはドレイン端子の他方）と、導通を制御する端子（ゲート端子）とを有している。一方、スイッチとしてダイオードを用いる場合は、導通を制御する端子を有していない場合がある。そのため、端子を制御するための配線を少なくすることが出来る。

**【 0 0 2 8 】**

なお、本発明において、接続されているとは、電気的に接続されている場合と機能的に接続されている場合と直接接続されている場合とを含むものとする。したがって、本発明が開示する構成において、所定の接続関係以外のものも含むものとする。例えば、ある部分とある部分との間に、電気的な接続を可能とする素子（例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど）が1個以上配置されていてもよい。また、機能的な接続を可能とする回路（例えば、論理回路（インバータやNAND回路やNOR回路など）や信号変換回路（DA変換回路やAD変換回路やガンマ補正回路など）や電位レベル変換回路（昇圧回路や降圧回路などの電源回路やH信号やL信号の電位レベルを変えるレベルシフト回路など）や電圧源や電流源や切り替え回路や増幅回路（オペアンプや差動増幅回路やソースフォロワ回路やバッファ回路など、信号振幅や電流量などを大きく出来る回路など）や信号生成回路や記憶回路や制御回路など）が間に1個以上配置されていてもよい。あるいは、間に他の素子や他の回路を挟まずに、直接接続されて、配置されていてもよい。

**【 0 0 2 9 】**

なお、素子や回路を間に介さずに接続されている場合のみを含む場合は、直接接続されている、と記載するものとする。また、電気的に接続されている、と記載する場合は、電気的に接続されている場合（つまり、間に別の素子を挟んで接続されている場合）と機能的に接続されている場合（つまり、間に別の回路を挟んで接続されている場合）と直接接続されている場合（つまり、間に別の素子や別の回路を挟まずに接続されている場合）とを含むものとする。

**【 0 0 3 0 】**

なお、表示素子や表示装置や発光素子や発光装置は、様々な形態を用いる、或いは様々な素子を有することが出来る。例えば、表示素子や表示装置や発光素子や発光装置としては、EL素子（有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子）、電子放出素子、液晶素子、電子インク、グレーティングライトバルブ（GLV）、プラズマディスプレイ（PDP）、デジタルマイクロミラーデバイス（DMD）、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いた表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッショニングディスプレイ（FED）やSED方式平面型ディスプレイ（SED：Surface-conduct ion Electron-emitter Display）など、液晶素子を用いた表示装置としては液晶ディスプレイ、透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、電子インクを用いた表示装置としては電子ペーパーがある。

**【 0 0 3 1 】**

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることが

10

20

30

40

50

出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、例えば、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を有する薄膜トランジスタ（TFT）などを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、低コストで製造できたり、大型基板上に製造できたり、透明基板上に製造できたり、トランジスタで光を透過させたりすることが出来る。また、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを適用することが出来る。これらにより、バラツキの少ないトランジスタを製造できたり、電流供給能力の高いトランジスタを製造できたり、サイズの小さいトランジスタを製造できたり、消費電力の少ない回路を構成することが出来る。また、ZnO、a-InGaZnO、SiGe、GaAsなどの化合物半導体を有するトランジスタや、さらに、それらを薄膜化した薄膜トランジスタなどを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、室温で製造できたり、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成することが出来る。また、インクジェットや印刷法を用いて作製したトランジスタなどを適用することが出来る。これらにより、室温で製造する、真空度の低い状態で製造する、或いは大型基板で製造することなどができる。また、マスク（レチカル）を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。また、有機半導体やカーボンナノチューブを有するトランジスタ、その他のトランジスタを適用することができる。これらにより、曲げることが可能な基板にトランジスタを形成することが出来る。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタは様々な基板を用いて形成することができ、基板の種類は特定のものに限定されることはない。従って例えば、基板として、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることが出来る。また、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板に配置するようにしてもよい。これらの基板を用いることにより、特性のよいトランジスタを形成する、消費電力の小さいトランジスタを形成する、壊れにくい装置にする、或いは耐熱性を持たせたりすることが出来る。

### 【0032】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート電極が2つ以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。マルチゲート構造にすることにより、オフ電流を低減する、トランジスタの耐圧を向上させて信頼性を良くする、或いは飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることなどができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値を大きくする、或いは空乏層ができやすくなっているS値を小さくすることができる。チャネルの上下にゲート電極が配置されると、複数のトランジスタが並列に接続されたような構成となる。また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれているてもよいし、並列に接続されているてもよいし、直列に接続されているてもよい。また、チャネル（もしくはその一部）にソース電極やドレイン電極が重なっていてもよい。チャネル（もしくはその一部）にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流を低減する、トランジスタの耐圧を向上させて信頼性を良くする、或いは飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

10

20

30

40

50

## 【0033】

なお、本発明におけるトランジスタは、様々なタイプを用いることができ、様々な基板を用いて形成させることができる。したがって、回路の全てが、ガラス基板に形成されてもよいし、プラスチック基板に形成されていてもよいし、単結晶基板に形成されていてもよいし、S O I 基板に形成されていてもよいし、どのような基板に形成されていてもよい。回路の全てが同じ基板に形成されていることにより、部品点数を減らしてコストを低減する、回路部品との接続点数を減らして信頼性を向上させたりすることができる。あるいは、回路の一部が、ある基板に形成されており、回路の別の一部が、別の基板に形成されていてもよい。つまり、回路の全てが同じ基板上に形成されていなくてもよい。例えば、回路の一部は、ガラス基板にトランジスタを用いて形成し、回路の別の一部は、単結晶基板に形成し、そのI CチップをC O G ( C h i p O n G l a s s )で接続してガラス基板上に配置してもよい。あるいは、そのI CチップをT A B ( T a p e A u t o m a t e d B o n d i n g )やプリント基板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らしてコストを低減する、回路部品との接続点数を減らして信頼性を向上させたりすることができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力が高くなるのを防ぐことができる。

## 【0034】

なお、本発明においては、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R(赤) G(緑) B(青)の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。なお、色要素は、三色に限定されず、それ以上の数を用いてもよいし、RGB以外の色を追加してもよい。例えば、白色を加えて、RGBW(Wは白)としてもよい。また、RGBに、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色などを一色以上追加したものでもよい。また、例えばRGBの中の少なくとも一色について、類似した色を追加してもよい。例えば、R、G、B1、B2としてもよい。B1とB2とは、どちらも青色であるが、少し周波数が異なっている。このような色要素を用いることにより、より実物に近い表示を行うことができる、或いは消費電力を低減することが出来る。また、別の例としては、1つの色要素について、複数の領域を用いて明るさを制御する場合は、その領域一つ分を一画素とする。よって、一例としては、面積階調を行う場合、一つの色要素につき、明るさを制御する領域が複数あり、その全体で階調を表現するわけであるが、明るさを制御する領域の一つ分を一画素とする。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。また、その場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。また、一つの色要素につき複数ある、明るさを制御する領域において、つまり、一つの色要素を構成する複数の画素において、各々に供給する信号を僅かに異ならせるようにして、視野角を広げるようにもよい。なお、一画素(三色分)と記載する場合は、RとGとBの三画素分を一画素と考える場合であるとする。一画素(一色分)と記載する場合は、一つの色要素につき、複数の画素がある場合、それらをまとめて一画素と考える場合であるとする。

## 【0035】

なお、本発明において、画素は、マトリクス状に配置(配列)されている場合を含んでいる。ここで、画素がマトリクス状に配置(配列)されているとは、縦方向もしくは横方向において、直線上に並んで配置されている場合や、ギザギザな線上に並んでいる場合を含んでいる。よって、例えば三色の色要素(例えばRGB)でフルカラー表示を行う場合に、ストライプ配置されている場合や、三つの色要素のドットがいわゆるデルタ配置されている場合も含むものとする。さらに、ベイヤー配置されている場合も含んでいる。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW(Wは白)や、RGBに、イエロー、シアン、マゼンタなどを一色以上追加したものなどがある。また、色要

10

20

30

40

50

素のドット毎にその表示領域の大きさが異なっていてもよい。これにより、消費電力を低下させる、或いは表示素子の寿命を延ばすことが出来る。

#### 【0036】

なお、トランジスタとは、それぞれ、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流が流れることが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本発明においては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。10

#### 【0037】

なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2端子と表記する場合がある。

#### 【0038】

なお、ゲートとは、ゲート電極とゲート配線（ゲート線またはゲート信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域やLDD（Lightly Doped Drain）領域などを形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。ゲート配線とは、各画素のゲート電極の間を接続する、或いはゲート電極と別の配線とを接続するための配線のことを言う。20

#### 【0039】

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。30

#### 【0040】

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル領域とオーバーラップしていなかったり、別のゲート電極と接続させる機能を有してなかったりする場合がある。しかし、製造条件などの関係で、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線とつながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んでも良い。

#### 【0041】

また、例えば、マルチゲートのトランジスタにおいて、1つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。また、例えば、ゲート電極とゲート配線とを接続させている部分の導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。40

#### 【0042】

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域について、その一部分のことを言う。50

## 【0043】

なお、ソースとは、ソース領域とソース電極とソース配線（ソース線またはソース信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物（ボロンやガリウムなど）やN型不純物（リンやヒ素など）が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD（Lightly Doped Drain）領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間を接続する、或いはソース電極と別の配線とを接続するための配線のことを言う。

10

## 【0044】

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能していることになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

## 【0045】

また、ソース電極と同じ材料で形成され、ソース電極とつながっている領域や、ソース電極とソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、ソース配線と呼んでも良い。このような領域は、厳密な意味では、別のソース電極と接続させる機能を有していたりすることがない場合がある。しかし、製造条件などの関係で、ソース電極やソース配線と同じ材料で形成され、ソース電極やソース配線とつながっている領域がある。よって、そのような領域もソース電極やソース配線と呼んでも良い。

20

## 【0046】

また、例えば、ソース電極とソース配線とを接続させている部分の導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

30

## 【0047】

なお、ソース端子とは、ソース領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。

## 【0048】

なお、ドレインについては、ソースと同様である。

## 【0049】

なお、本発明において、半導体装置とは半導体素子（トランジスタやダイオードなど）を含む回路を有する装置をいう。また、半導体特性を利用して機能しうる装置全般でもよい。

40

## 【0050】

また、表示装置とは、表示素子（液晶素子や発光素子など）を有する装置のことを言う。なお、液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が同一基板上に形成された表示パネル本体のことでもよい。また、ワイヤボンディングやバンプなどによって基板上に配置された周辺駆動回路、いわゆるチップオングラス（COG）を含んでいても良い。さらに、フレキシブルプリントサーキット（FPC）やプリント配線基板（PWB）が取り付けられたもの（ICや抵抗素子や容量素子やインダクタやトランジスタなど）も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライトユニット（導光板やプリズムシートや拡散シートや反射シートや光源（LEDや冷陰極管など））を含んでいても良い。

## 【0051】

50

また、発光装置とは、特にEL素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。

#### 【0052】

なお、本発明において、ある物の上に形成されている、あるいは、～上に形成されている、というように、～の上に、あるいは、～上に、という記載については、ある物の上に直接接していることに限定されない。直接接してはいない場合、つまり、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上に（もしくは層A上に）、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。また、～の上方に、という記載についても同様であり、ある物の上に直接接していることに限定されず、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、～の下に、あるいは、～の下方に、の場合についても、同様であり、直接接している場合と、接していない場合とを含むこととする。

#### 【発明の効果】

#### 【0053】

本発明を用いることで、トランジスタの特性劣化を抑制する駆動方法を用いたフリップフロップ回路、シフトレジスタ、及びこのようなシフトレジスタを具備する半導体装置、並びに表示装置、及び当該表示装置を具備する電子機器を提供することができる。

#### 【0054】

例えば、本発明をシフトレジスタに適用した場合、非選択期間において、出力端子に電源電位を供給するトランジスタが常時オン状態であることがないので、当該トランジスタの特性劣化（例えば、しきい値電位のシフト）を抑制することができる。よって、トランジスタの特性劣化によるシフトレジスタの誤動作を抑制できる。

#### 【0055】

また、本発明を用いることで、比較的回路規模が小さい制御回路を有するフリップフロップ回路、シフトレジスタ、及びこのようなシフトレジスタを具備する半導体装置、並びに表示装置、及び当該表示装置を具備する電子機器を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0056】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。

#### 【0057】

##### (第1の実施形態)

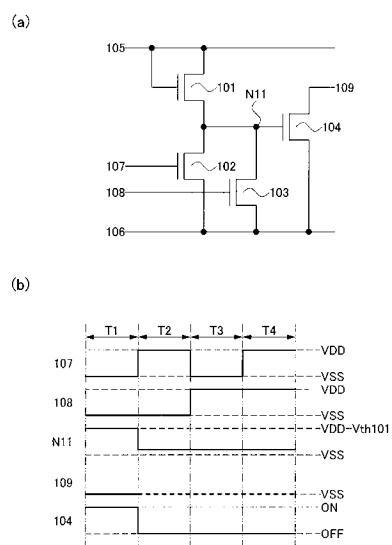

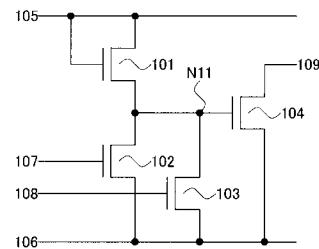

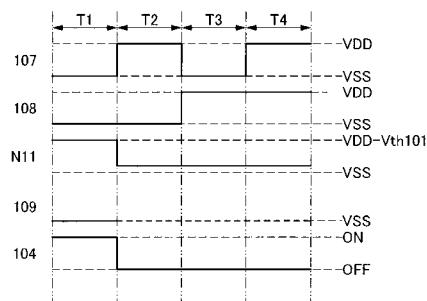

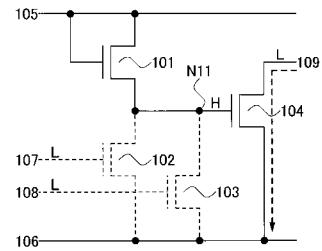

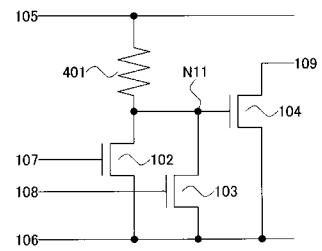

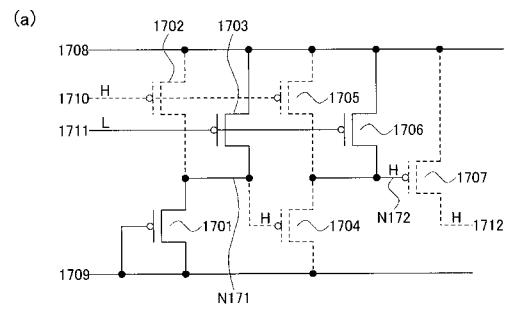

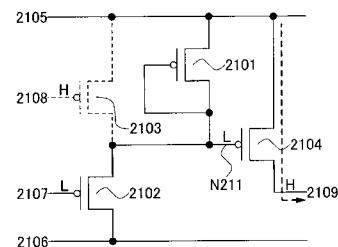

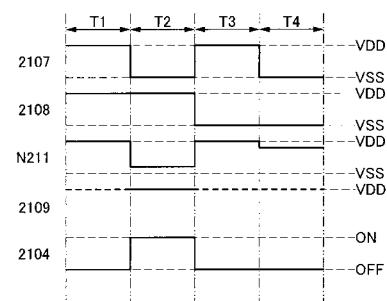

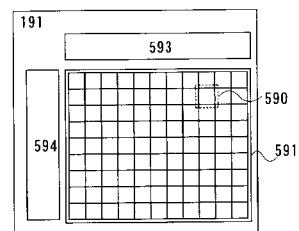

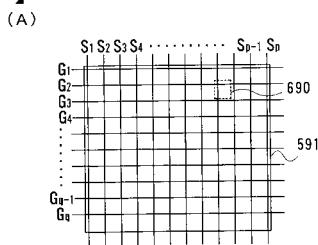

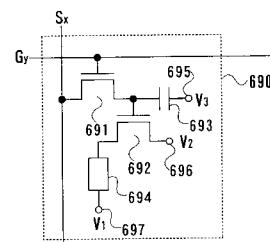

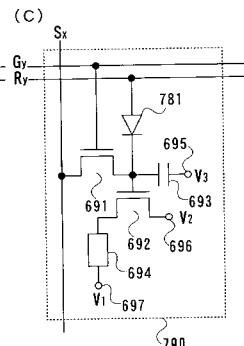

本実施形態では、本発明の基本原理について、図1(a)を参照して説明する。

#### 【0058】

図1(a)は、本発明の基本原理に基づく基本回路である。図1(a)の基本回路は、トランジスタ101、トランジスタ102、トランジスタ103、及びトランジスタ104を有している。

#### 【0059】

図1(a)の基本回路の接続関係について説明する。トランジスタ101のゲートが配線105に接続され、第1端子が配線105に接続され、第2端子がトランジスタ104のゲートに接続されている。トランジスタ102のゲートが配線107に接続され、第1端子が配線106に接続され、第2端子がトランジスタ104のゲートに接続されている。トランジスタ103のゲートが配線108に接続され、第1端子が配線106に接続され

、第2端子がトランジスタ104のゲートに接続されている。トランジスタ104の第1端子が配線106に接続され、第2端子が配線109に接続されている。なお、トランジスタ101の第2端子とトランジスタ102の第2端子とトランジスタ103の第2端子とトランジスタ104のゲートとの節点を節点N11とする。

#### 【0060】

また、トランジスタ101～トランジスタ104は、それぞれNチャネル型である。

#### 【0061】

したがって、図1(a)の基本回路はすべてNチャネル型のトランジスタで構成することができるため、図1(a)の基本回路は、半導体層にアモルファスシリコンを用いることができ、製造工程の簡略化を図ることができる。したがって、製造コストの削減や歩留まりの向上を図ることができる。さらに、大型の表示パネルなどの半導体装置を作製することも可能となる。また、図1(a)の基本回路は、半導体層にポリシリコンや単結晶シリコンを用いても製造工程の簡略化を図ることができる。

10

#### 【0062】

また、配線105には電源電位VDDが供給され、配線106には電源電位VSSが供給されている。なお、電源電位VDDは、電源電位VSSよりも高い電位である。ただし、配線105、及び配線106には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

#### 【0063】

また、配線107、及び配線108には、それぞれ信号が供給されている。なお、配線107、及び配線108に供給されている信号は、それぞれ2値の値を持つデジタル信号である。このデジタル信号は、H信号のときには電源電位VDDと同電位（以下、電位VDD、又はHレベルともいう）となり、L信号のときには電源電位VSSと同電位（以下、電位VSS、又はLレベルともいう）となる。ただし、配線107、及び配線108には、それぞれ電源電位VDD、電源電位VSS、又は他の電源電位が供給されていてもよい。また、配線107、及び配線108には、それぞれアナログ信号が供給されていてもよい。

20

#### 【0064】

次に、図1(a)に示した基本回路の動作について、図1(b)を参照して説明する。

#### 【0065】

図1(b)は、図1(a)に示した基本回路のタイミングチャートの一例である。図1(b)のタイミングチャートは、配線107の電位、配線108の電位、節点N11の電位、配線109の電位、及びトランジスタ104のオン・オフを示している。

30

#### 【0066】

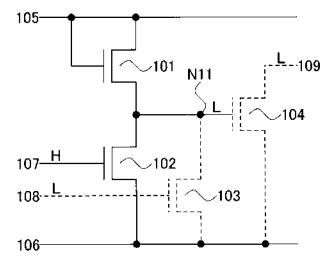

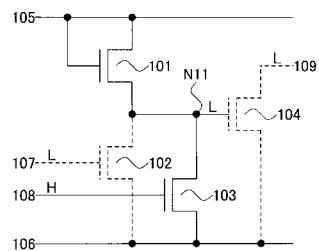

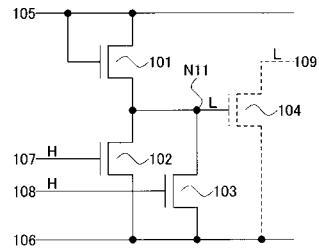

図1(b)のタイミングチャートを期間T1～期間T4に分割して説明する。また、図2(a)、図2(b)、図3(a)、及び図3(b)は、期間T1、期間T2、期間T3、及び期間T4における図1(a)の基本回路の動作を示している。

#### 【0067】

まず、期間T1の動作について、図2(a)を参照して説明する。期間T1は、配線107にL信号が供給され、配線108にL信号が供給されている。したがって、トランジスタ102がオフし、トランジスタ103がオフしている。

40

#### 【0068】

また、トランジスタ101は、ダイオード接続されているので、節点N11の電位が上昇し始める。この節点N11の電位の上昇は、トランジスタ101がオフするまで続く。トランジスタ101は、節点N11の電位が電源電位VDDからトランジスタ101のしきい値電圧Vth101を引いた値（VDD - Vth101）になるとオフする。よって、節点N11の電位はVDD - Vth101となる。

#### 【0069】

したがって、トランジスタ104がオンして、配線109の電位が電源電位VSSと等しい値になる。

50

## 【0070】

続いて、期間T2の動作について、図2(b)を参照して説明する。期間T2は、配線107にH信号が供給され、配線108にL信号が供給されている。したがって、トランジスタ102がオンし、トランジスタ103がオフしている。

## 【0071】

また、節点N11の電位は、トランジスタ101とトランジスタ102との動作点によって決定される。なお、トランジスタ102のW/L比(Wはチャネル領域のチャネル幅、Lはチャネル領域のチャネル長)を、トランジスタ101のW/L比よりも十分大きくしておけば、節点N11の電位は電源電位VSSよりも少しだけ高い値になる。

## 【0072】

したがって、トランジスタ104がオフして、配線109はフローティング(浮遊)状態となる。配線109の電位は、期間T1のときの電位を維持するため、電源電位VSSと等しい値のままである。

## 【0073】

続いて、期間T3の動作について、図3(a)を参照して説明する。期間T3は、配線107にL信号が供給され、配線108にH信号が供給されている。したがって、トランジスタ102がオフし、トランジスタ103がオンしている。

## 【0074】

また、節点N11の電位は、トランジスタ101とトランジスタ103との動作点によって決定される。なお、トランジスタ103のW/L比を、トランジスタ101のW/L比よりも十分大きくしておけば、節点N11の電位は電源電位VSSよりも少しだけ高い値になる。

## 【0075】

したがって、トランジスタ104がオフして、配線109はフローティング(浮遊)状態となる。配線109の電位は、期間T1、期間T2のときの電位を維持するため、電源電位VSSと等しい値のままである。

## 【0076】

続いて、期間T4の動作について、図3(b)を参照して説明する。期間T4は、配線107にH信号が供給され、配線108にはH信号が供給されている。したがって、トランジスタ102がオンし、トランジスタ104がオンしている。

## 【0077】

また、節点N11の電位は、トランジスタ101とトランジスタ102とトランジスタ103との動作点によって決定されるため、節点N11の電位は電源電位VSSよりも少しだけ高い値になる。

## 【0078】

したがって、トランジスタ104がオフして、配線109はフローティング(浮遊)状態となる。配線109の電位は、期間T1、期間T2、期間T3のときの電位を維持するため、電源電位VSSと等しい値のままである。

## 【0079】

以上の動作によって、期間T1では、図1(a)の基本回路は配線109に電源電位VSSを供給し、配線109の電位を電源電位VSSと等しい値にする。期間T2~期間4では、図1(a)の基本回路は、配線109をフローティング状態にし、配線109の電位を電源電位VSSと等しい値に維持する。

## 【0080】

また、図1(a)の基本回路は、期間T1~期間T4すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジスタは有していない。したがって、図1(a)の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

## 【0081】

また、トランジスタの特性は、トランジスタがアモルファスシリコンで形成されている場

10

20

30

40

50

合に劣化しやすい。したがって、図1(a)の基本回路は、トランジスタをアモルファスシリコンで形成することによって、製造コストの削減や歩留まりの向上などのメリットが得られるだけでなく、トランジスタの特性劣化の問題も解決できる。

#### 【0082】

ここで、トランジスタ101～トランジスタ104の機能を説明する。トランジスタ101は、入力端子を第1端子、及びゲートとし、出力端子を第2端子としているダイオードとしての機能を有する。トランジスタ102は、配線107の電位に応じて、配線106と節点N11とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ103は、配線108の電位に応じて、配線106と節点N11とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ104は、節点N11の電位に応じて、配線106と配線109とを接続するかしないかを選択するスイッチとしての機能を有する。

#### 【0083】

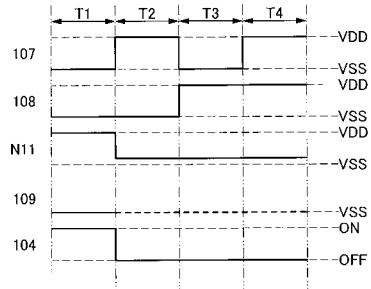

なお、トランジスタ101は、抵抗成分を持つ素子であればよい。例えば、図4(a)に示すように、抵抗素子401をトランジスタ101の代わりに用いることができる。抵抗素子401を用いることによって、節点N11の電位を期間T1において電源電位VDDと等しい値とすることができます。また、図4(a)のタイミングチャートを図4(b)に示す。

#### 【0084】

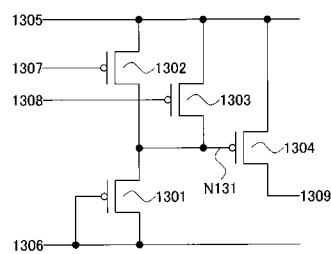

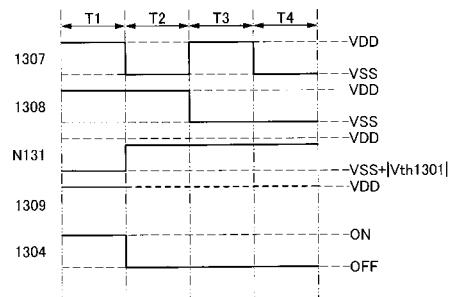

次に、図1(a)に示した基本回路をPチャネル型トランジスタで構成した場合について、図13(a)を参照して説明する。

#### 【0085】

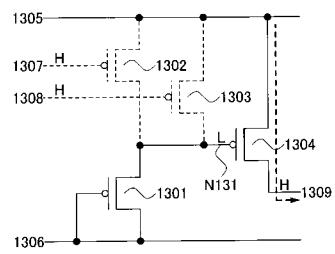

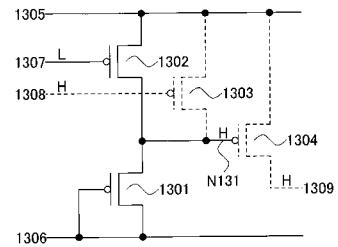

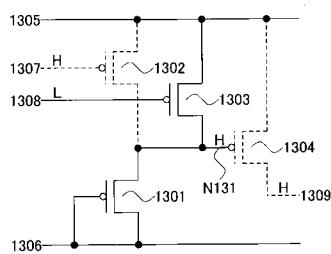

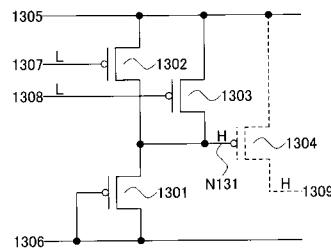

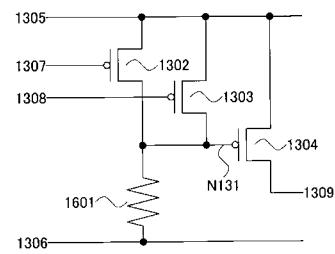

図13(a)は、本発明の基本原理に基づく基本回路である。図13(a)の基本回路は、トランジスタ1301、トランジスタ1302、トランジスタ1303、及びトランジスタ1304を有している。

#### 【0086】

図13(a)の基本回路の接続関係について説明する。トランジスタ1301のゲートが配線1306に接続され、第1端子が配線1306に接続され、第2端子がトランジスタ1304のゲートに接続されている。トランジスタ1302のゲートが配線1307に接続され、第1端子が配線1305に接続され、第2端子がトランジスタ1304のゲートに接続されている。トランジスタ1303のゲートが配線1308に接続され、第1端子が配線1305に接続され、第2端子がトランジスタ1304のゲートに接続されている。トランジスタ1304の第1端子が配線1305に接続され、第2端子が配線1309に接続されている。なお、トランジスタ1301の第2端子とトランジスタ1302の第2端子とトランジスタ1303の第2端子とトランジスタ1304のゲートとの節点を節点N131とする。

#### 【0087】

また、トランジスタ1301～トランジスタ1304は、それぞれPチャネル型である。

#### 【0088】

したがって、図13(a)の基本回路はすべてPチャネル型のトランジスタで構成することができるため、Nチャネル型のトランジスタを形成するための工程が必要ない。したがって、図13(a)の基本回路は、製造工程の簡略化を図ることができ、製造コストの削減や歩留まりの向上を図ることができる。

#### 【0089】

また、配線1305には電源電位VDDが供給され、配線1306には電源電位VSSが供給されている。

#### 【0090】

また、配線1307、及び配線1308には、それぞれ信号が供給されている。なお、配線1307、及び配線1308に供給されている信号は、それぞれ2値の値を持つデジタル信号である。

**【 0 0 9 1 】**

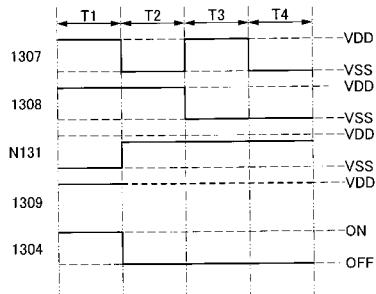

次に、図13(a)に示した基本回路の動作について、図13(b)を参照して説明する。

**【 0 0 9 2 】**

図13(b)は、図13(a)に示した基本回路のタイミングチャートの一例である。図13(b)のタイミングチャートは、配線1307の電位、配線1308の電位、節点N131の電位、配線1309の電位、及びトランジスタ1304のオン・オフを示している。

**【 0 0 9 3 】**

図13(b)のタイミングチャートを期間T1～期間T4に分割して説明する。また、図14(a)、図14(b)、図15(a)、及び図15(b)は、期間T1、期間T2、期間T3、及び期間T4における図13(a)の基本回路の動作を示している。

**【 0 0 9 4 】**

まず、期間T1の動作について、図14(a)を参照して説明する。期間T1は、配線1307にH信号が供給され、配線1308にH信号が供給されている。したがって、トランジスタ1302がオフし、トランジスタ1303がオフしている。

**【 0 0 9 5 】**

また、トランジスタ1301は、ダイオード接続されているので、節点N131の電位が減少し始める。この節点N131の電位の減少は、トランジスタ1301がオフするまで続く。トランジスタ1301は、節点N131の電位が電源電位VSSとトランジスタ1301のしきい値電圧Vth1301の絶対値との和( $VSS + |Vth1301|$ )になるとオフする。よって、節点N131の電位は $VSS + |Vth1301|$ となる。

**【 0 0 9 6 】**

したがって、トランジスタ1304がオンして、配線1309の電位が電源電位VDDと等しい値になる。

**【 0 0 9 7 】**

続いて、期間T2の動作について、図14(b)を参照して説明する。期間T2は、配線1307にL信号が供給され、配線1308にH信号が供給されている。したがって、トランジスタ1302がオンし、トランジスタ1303がオフしている。

**【 0 0 9 8 】**

また、節点N131の電位は、トランジスタ1301とトランジスタ1302との動作点によって決定される。なお、トランジスタ1302のW/L比(Wはチャネル領域のチャネル幅、Lはチャネル領域のチャネル長)を、トランジスタ1301のW/L比よりも十分大きくしておけば、節点N131の電位は電源電位VDDよりも少しだけ低い値になる。

**【 0 0 9 9 】**

したがって、トランジスタ1304がオフして、配線1309はフロー・ティング(浮遊)状態となる。配線1309の電位は、期間T1のときの電位を維持するため、電源電位VDDと等しい値のままである。

**【 0 1 0 0 】**

続いて、期間T3の動作について、図15(a)を参照して説明する。期間T3は、配線1307にH信号が供給され、配線1308にL信号が供給されている。したがって、トランジスタ1302がオフし、トランジスタ1303がオンしている。

**【 0 1 0 1 】**

また、節点N131の電位は、トランジスタ1301とトランジスタ1303との動作点によって決定される。なお、トランジスタ1303のW/L比を、トランジスタ1301のW/L比よりも十分大きくしておけば、節点N131の電位は電源電位VDDよりも少しだけ低い値になる。

**【 0 1 0 2 】**

したがって、トランジスタ1304がオフして、配線1309はフロー・ティング(浮遊)

10

20

30

40

50

状態となる。配線 1309 の電位は、期間 T1、期間 T2 のときの電位を維持するため、電源電位 VDD と等しい値のままである。

#### 【0103】

続いて、期間 T4 の動作について、図 15 (b) を参照して説明する。期間 T4 は、配線 1307 に L 信号が供給され、配線 1308 には L 信号が供給されている。したがって、トランジスタ 1302 がオンし、トランジスタ 1304 がオンしている。

#### 【0104】

また、節点 N131 の電位は、トランジスタ 1301 とトランジスタ 1302 とトランジスタ 1303 との動作点によって決定されるため、節点 N131 の電位は電源電位 VDD よりも少しだけ低い値になる。

10

#### 【0105】

したがって、トランジスタ 1304 がオフして、配線 1309 はフロー・ティング（浮遊）状態となる。配線 1309 の電位は、期間 T1、期間 T2、期間 T3 のときの電位を維持するため、電源電位 VDD と等しい値のままである。

#### 【0106】

以上の動作によって、期間 T1 では、図 13 (a) の基本回路は配線 1309 に電源電位 VDD を供給し、配線 1309 の電位を電源電位 VDD と等しい値にする。期間 T2 ~ 期間 4 では、図 13 (a) の基本回路は、配線 1309 をフロー・ティング状態にし、配線 1309 の電位を電源電位 VDD と等しい値に維持する。

20

#### 【0107】

また、図 13 (a) の基本回路は、期間 T1 ~ 期間 T4 すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジスタは有していない。したがって、図 13 (a) の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

#### 【0108】

なお、トランジスタ 1301 ~ トランジスタ 1304 は、トランジスタ 101 ~ トランジスタ 104 と同様な機能を有する。

#### 【0109】

なお、トランジスタ 1301 は、抵抗成分を持つ素子であればよい。例えば、図 16 (a) に示すように、抵抗素子 1601 をトランジスタ 1301 の代わりに用いることができる。抵抗素子 1601 を用いることによって、節点 N131 の電位を期間 T1 において電源電位 VSS と等しい値とすることができる。また、図 16 (a) のタイミングチャートを図 16 (b) に示す。

30

#### 【0110】

なお、本実施形態は、本明細書中の他の実施形態のいかなる記載とも自由に組み合わせて実施することができる。また、本実施形態中のいかなる記載も自由に組み合わせて実施することができる。

#### 【0111】

(第 2 の実施形態)

本実施形態では、第 1 の実施形態とは別の本発明の基本原理について、図 5 (a) を参照して説明する。

40

#### 【0112】

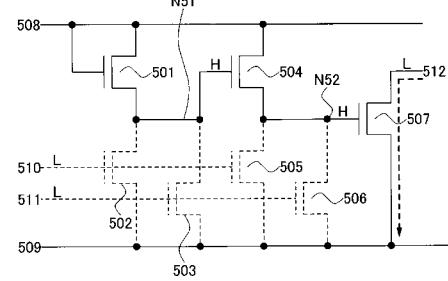

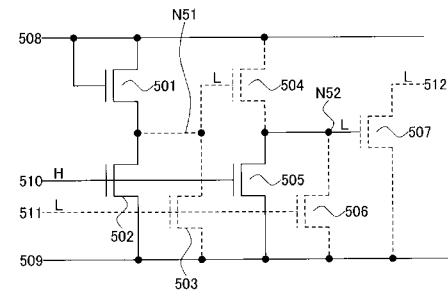

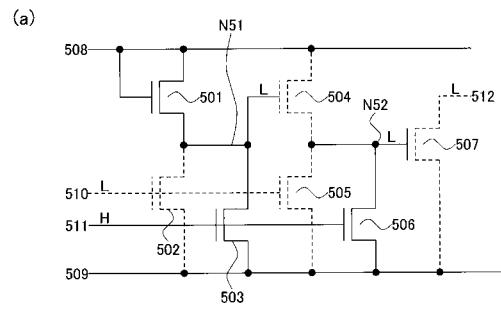

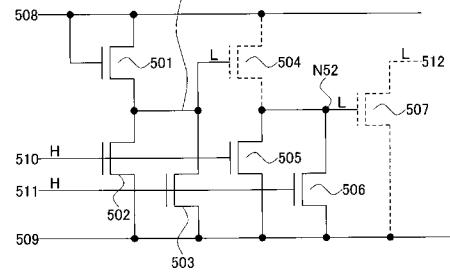

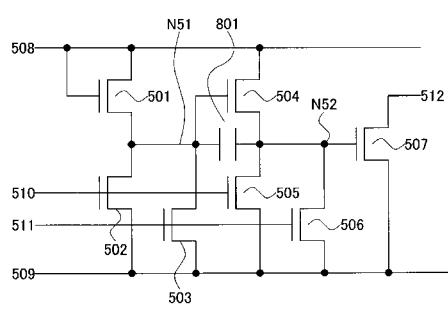

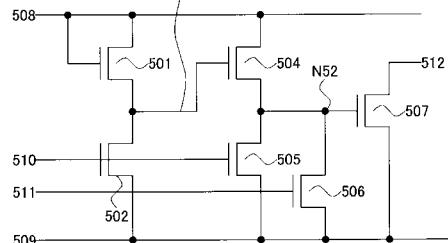

図 5 (a) は、本発明の基本原理に基づく基本回路である。図 5 (a) の基本回路は、トランジスタ 501、トランジスタ 502、トランジスタ 503、トランジスタ 504、トランジスタ 505、トランジスタ 506、及びトランジスタ 507 を有している。

#### 【0113】

図 5 (a) の基本回路の接続関係について説明する。トランジスタ 501 のゲートが配線 508 に接続され、第 1 端子が配線 508 に接続され、第 2 端子がトランジスタ 504 のゲートに接続されている。トランジスタ 502 のゲートが配線 510 に接続され、第 1 端子が配線 509 に接続され、第 2 端子がトランジスタ 504 のゲートに接続されている。

50

トランジスタ503のゲートが配線511に接続され、第1端子が配線509に接続され、第2端子がトランジスタ504のゲートに接続されている。なお、トランジスタ501の第2端子とトランジスタ502の第2端子とトランジスタ503の第2端子とトランジスタ504のゲートとの節点を節点N51とする。トランジスタ504の第1端子が配線508に接続され、第2端子がトランジスタ507のゲートに接続されている。トランジスタ505のゲートが配線510に接続され、第1端子が配線509に接続され、第2端子がトランジスタ507のゲートに接続されている。トランジスタ506のゲートが配線511に接続され、第1端子が配線509に接続され、第2端子がトランジスタ507のゲートに接続されている。トランジスタ507の第1端子が配線509に接続され、第2端子が配線512に接続されている。なお、トランジスタ504の第2端子とトランジスタ505の第2端子とトランジスタ506の第2端子とトランジスタ507のゲートとの節点を節点N52とする。

10

## 【0114】

また、トランジスタ501～トランジスタ507は、それぞれNチャネル型である。

## 【0115】

したがって、図5(a)の基本回路はすべてNチャネル型のトランジスタで構成することができるため、図5(a)の基本回路は、半導体層にアモルファスシリコンを用いることができ、製造工程の簡略化を図ることができる。したがって、製造コストの削減や歩留まりの向上を図ることができる。さらに、大型の表示パネルなどの半導体装置を作製することも可能となる。また、図5(a)の基本回路は、半導体層にポリシリコンや単結晶シリコンを用いても製造工程の簡略化を図ることができる。

20

## 【0116】

また、配線508には電源電位VDDが供給され、配線509には電源電位VSSが供給されている。なお、電源電位VDDは、電源電位VSSよりも高い電位である。ただし、配線508、及び配線509には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

## 【0117】

また、配線510、及び配線511には、それぞれ信号が供給されている。なお、配線510、及び配線511に供給されている信号は、それぞれ2値の値を持つデジタル信号である。このデジタル信号は、H信号のときには電源電位VDDと同電位（以下、電位VD、又はHレベルともいう）となり、L信号のときには電源電位VSSと同電位（以下、電位VSS、又はLレベルともいう）となる。ただし、配線510、及び配線511には、それぞれ電源電位VDD、電源電位VSS、又は他の電源電位が供給されていてもよい。また、配線510、及び配線511には、それぞれアナログ信号が供給されていてもよい。

30

## 【0118】

次に、図5(a)に示した基本回路の動作について、図5(b)を参照して説明する。

## 【0119】

図5(b)は、図5(a)に示した基本回路のタイミングチャートの一例である。図5(b)のタイミングチャートは、配線510の電位、配線511の電位、節点N51の電位、節点N52の電位、配線512の電位、及びトランジスタ507のオン・オフを示している。

40

## 【0120】

図5(b)のタイミングチャートを期間T1～期間T4に分割して説明する。また、図6(a)、図6(b)、図7(a)、及び図7(b)は、期間T1、期間T2、期間T3、及び期間T4における図5(a)の基本回路の動作を示している。

## 【0121】

まず、期間T1の動作について、図6(a)を参照して説明する。期間T1は、配線510にL信号が供給され、トランジスタ502、及びトランジスタ505がオフしている。また、配線511にL信号が供給され、トランジスタ503、及びトランジスタ506が

50

オフしている。

【0122】

また、トランジスタ501は、ダイオード接続されているので、節点N51の電位が上昇し始める。節点N51の電位が電源電位VDDからトランジスタ501のしきい値電圧V<sub>th501</sub>を引いた値(VDD - V<sub>th501</sub>)になると、トランジスタ501がオフする。したがって、節点N51がフローティング状態になる。

【0123】

このとき、トランジスタ504はオンしており、節点N52の電位も上昇している。したがって、フローティング状態になっている節点N51の電位は、トランジスタ504のゲート(節点N51)と第2端子(節点N52)との間の寄生容量によって、節点N52の電位と一緒に上昇する。この節点N51の電位の上昇は節点N52の電位の上昇が止まるまで続き、節点N51の電位が電源電位VDDとトランジスタ504のしきい値電圧V<sub>th504</sub>との和(VDD + V<sub>th504</sub>)以上になる。つまり、節点N51の電位の上昇は、節点N52の電位が電源電位VDDと等しくなるまで続く。いわゆるブーストstrap動作によって、節点N52の電位を電源電位VDDと等しくできる。

【0124】

したがって、トランジスタ507がオンして、配線509の電位が電源電位VSSと等しい値になる。ここで、節点N52の電位を電源電位VDDと等しくすることによって、トランジスタ507のゲートとソースとの間の電位差を大きくすることができる。よって、トランジスタ507をオンしやすくすることができ、広い動作条件で基本回路を動作させることができる。

【0125】

続いて、期間T2の動作について、図6(b)を参照して説明する。期間T2は、配線510にH信号が供給され、トランジスタ502、及びトランジスタ505がオンしている。また、配線511にL信号が供給され、トランジスタ503、及びトランジスタ506がオフしている。

【0126】

また、節点N51の電位は、トランジスタ501とトランジスタ502との動作点によって決定される。なお、トランジスタ502のW/L比を、トランジスタ501のW/L比よりも十分大きくしておけば、節点N51の電位は電源電位VSSよりも少しだけ高い電位になる。

【0127】

したがって、トランジスタ504はオフして、トランジスタ505がオンしているため、節点N52の電位が電源電位VSSと等しい値になる。よって、トランジスタ507がオフして、配線512はフローティング(浮遊)状態となる。配線512の電位は、期間T1のときの電位を維持するため、電源電位VSSと等しい値のままである。

【0128】

続いて、期間T3の動作について、図7(a)を参照して説明する。期間T3は、配線510にL信号が供給され、トランジスタ502、及びトランジスタ505がオフしている。また、配線511にH信号が供給され、トランジスタ503、及びトランジスタ506がオンしている。

【0129】

また、節点N51の電位は、トランジスタ501とトランジスタ503との動作点によって決定される。なお、トランジスタ503のW/L比を、トランジスタ501のW/L比よりも十分大きくしておけば、節点N51の電位は電源電位VSSよりも少しだけ高い電位になる。

【0130】

したがって、トランジスタ504はオフして、トランジスタ506がオンしているため、節点N52の電位が電源電位VSSと等しい値になる。よって、トランジスタ507がオフして、配線512はフローティング(浮遊)状態となる。配線512の電位は、期間T

10

20

30

40

50

1、期間T2のときの電位を維持するため、電源電位VSSと等しい値のままである。

【0131】

続いて、期間T4の動作について、図7(b)を参照して説明する。期間T4は、配線510にH信号が供給され、トランジスタ502、及びトランジスタ505がオンしている。また、配線511にH信号が供給され、トランジスタ503、及びトランジスタ506がオンしている。

【0132】

また、節点N51の電位は、トランジスタ501とトランジスタ502とトランジスタ503との動作点によって決定されるため、節点N51の電位は電源電位VSSよりも少しだけ高い電位になる。

【0133】

したがって、トランジスタ504はオフして、トランジスタ505、及びトランジスタ506がオンしているため、節点N52の電位が電源電位VSSと等しい値になる。よって、トランジスタ507がオフして、配線512はフローティング(浮遊)状態となる。配線512の電位は、期間T1、期間T2、期間T3のときの電位を維持するため、電源電位VSSと等しい値のままである。

【0134】

以上の動作によって、期間T1では、図5(a)の基本回路は配線512に電源電位VSSを供給し、配線512の電位を電源電位VSSと等しい値にする。期間T2～期間T4では、図5(a)の基本回路は、配線512をフローティング状態にし、配線512の電位を電源電位VSSと等しい値に維持する。

【0135】

なお、期間T1では、図5(a)の基本回路の節点N52の電位を電源電位VDDと等しい値にすることができる。したがって、広い動作条件で、図5(a)の基本回路を動作させることができる。

【0136】

また、図5(a)の基本回路は、期間T1～期間T4すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジスタは有していない。したがって、図5(a)の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

【0137】

また、トランジスタの特性は、トランジスタがアモルファスシリコンで形成されている場合に劣化しやすい。したがって、図5(a)の基本回路は、トランジスタをアモルファスシリコンで形成することによって、製造コストの削減や歩留まりの向上などのメリットが得られるだけでなく、トランジスタの特性劣化の問題も解決できる。

【0138】

ここで、トランジスタ501～トランジスタ507の機能を説明する。トランジスタ501は、入力端子を第1端子、及びゲートとし、出力端子を第2端子としているダイオードとしての機能を有する。トランジスタ502は、配線510の電位に応じて、配線509と節点N51とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ503は、配線511の電位に応じて、配線509と節点N51とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ504は、節点N51の電位に応じて、配線508と節点N52とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ505は、配線510の電位に応じて、配線509と節点N52とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ506は、配線511の電位に応じて、配線509と節点N52とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ507は、節点N52の電位に応じて、配線509と配線512とを接続するかしないかを選択するスイッチとしての機能を有する。

【0139】

10

20

30

40

50

なお、トランジスタ501～トランジスタ506によって、配線510、及び配線511を入力端子とし、出力端子を節点N52とする、2入力NOR回路を構成している。

#### 【0140】

なお、図8(a)に示すように、トランジスタ504のゲート(節点N51)と、第2端子(節点N52)との間に、容量素子801を配置してもよい。なぜなら、節点N51の電位、及び節点N52の電位はブートストラップ動作によって上昇するため、容量素子801を配置することで、基本回路がブートストラップ動作しやすくなるからである。

#### 【0141】

なお、図8(b)に示すように、トランジスタ503は、必ずしも必要ではない。なぜなら、配線510にH信号が供給されるときは、節点N52の電位が減少し、トランジスタ507がオフすればよいからである。

#### 【0142】

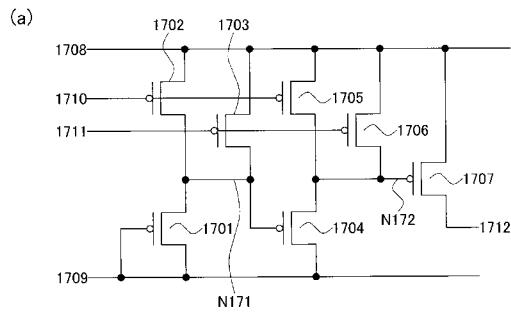

次に、図5(a)に示した基本回路をPチャネル型トランジスタで構成した場合について、図17(a)を参照して説明する。

#### 【0143】

図17(a)は、本発明の基本原理に基づく基本回路である。図17(a)の基本回路は、トランジスタ1701、トランジスタ1702、トランジスタ1703、トランジスタ1704、トランジスタ1705、トランジスタ1706、及びトランジスタ1707を有している。

#### 【0144】

図17(a)の基本回路の接続関係について説明する。トランジスタ1701のゲートが配線1709に接続され、第1端子が配線1709に接続され、第2端子がトランジスタ1704のゲートに接続されている。トランジスタ1702のゲートが配線1710に接続され、第1端子が配線1708に接続され、第2端子がトランジスタ1704のゲートに接続されている。トランジスタ1703のゲートが配線1711に接続され、第1端子が配線1708に接続され、第2端子がトランジスタ1704のゲートに接続されている。なお、トランジスタ1701の第2端子とトランジスタ1702の第2端子とトランジスタ1703の第2端子とトランジスタ1704のゲートとの節点を節点N171とする。トランジスタ1704の第1端子が配線1709に接続され、第2端子がトランジスタ1707のゲートに接続されている。トランジスタ1705のゲートが配線1710に接続され、第1端子が配線1708に接続され、第2端子がトランジスタ1707のゲートに接続されている。トランジスタ1706のゲートが配線1711に接続され、第1端子が配線1708に接続され、第2端子がトランジスタ1707のゲートに接続されている。トランジスタ1707の第1端子が配線1708に接続され、第2端子が配線1712に接続されている。なお、トランジスタ1704の第2端子とトランジスタ1705の第2端子とトランジスタ1706の第2端子とトランジスタ1707のゲートとの節点を節点N172とする。

#### 【0145】

また、トランジスタ1701～トランジスタ1707は、それぞれPチャネル型である。

#### 【0146】

したがって、図17(a)の基本回路はすべてPチャネル型のトランジスタで構成することができるため、Nチャネル型のトランジスタを形成するための工程が必要ない。したがって、図17(a)の基本回路は、製造工程の簡略化を図ることができ、製造コストの削減や歩留まりの向上を図ることができる。

#### 【0147】

また、配線1708には電源電位VDDが供給され、配線1709には電源電位VSSが供給されている。なお、電源電位VDDは、電源電位VSSよりも高い電位である。ただし、配線1708、及び配線1709には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

#### 【0148】

10

20

30

40

50

また、配線 1710、及び配線 1711には、それぞれ信号が供給されている。なお、配線 1710、及び配線 1711に供給されている信号は、それぞれ 2 値の値を持つデジタル信号である。ただし、配線 1710、及び配線 1711には、それぞれ電源電位 VDD、電源電位 VSS、又は他の電源電位が供給されていてもよい。また、配線 1710、及び配線 1711には、それぞれアナログ信号が供給されていてもよい。

#### 【0149】

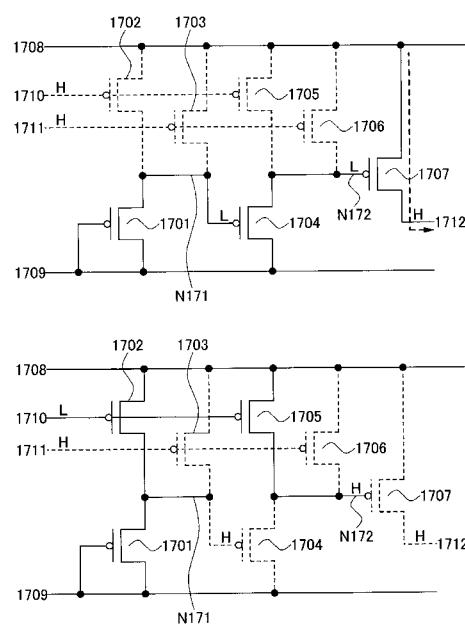

次に、図 17(a) に示した基本回路の動作について、図 17(b) を参照して説明する。

#### 【0150】

図 17(b) は、図 17(a) に示した基本回路のタイミングチャートの一例である。図 17(b) のタイミングチャートは、配線 1710 の電位、配線 1711 の電位、節点 N 171 の電位、節点 N 172 の電位、配線 1712 の電位、及びトランジスタ 1707 のオン・オフを示している。

#### 【0151】

図 17(b) のタイミングチャートを期間 T1 ~ 期間 T4 に分割して説明する。また、図 18(a)、図 18(b)、図 19(a)、及び図 19(b) は、期間 T1、期間 T2、期間 T3、及び期間 T4 における図 17(a) の基本回路の動作を示している。

#### 【0152】

まず、期間 T1 の動作について、図 18(a) を参照して説明する。期間 T1 は、配線 1710 に H 信号が供給され、トランジスタ 1702、及びトランジスタ 1705 がオフしている。また、配線 1711 に H 信号が供給され、トランジスタ 1703、及びトランジスタ 1706 がオフしている。

#### 【0153】

また、トランジスタ 1701 は、ダイオード接続されているので、節点 N 171 の電位が減少し始める。節点 N 171 の電位が電源電位 VSS とトランジスタ 1701 のしきい値電圧 Vth1701 の絶対値との和 ( $VSS + |Vth1701|$ ) になると、トランジスタ 1701 がオフする。したがって、節点 N 171 がフローティング状態になる。

#### 【0154】

このとき、トランジスタ 1704 はオンしており、節点 N 172 の電位も減少している。したがって、フローティング状態になっている節点 N 171 の電位は、トランジスタ 1704 のゲート (節点 N 171) と第 2 端子 (節点 N 172) との間の寄生容量によって、節点 N 172 の電位と一緒に減少する。この節点 N 171 の電位の減少は節点 N 172 の電位の減少が止まるまで続き、節点 N 171 の電位が電源電位 VSS からトランジスタ 1704 のしきい値電圧 Vth1704 の絶対値を引いた値 ( $VSS - |Vth1704|$ ) 以下になる。つまり、節点 N 171 の電位の減少は、節点 N 172 の電位が電源電位 VSS と等しくなるまで続く。いわゆるブートストラップ動作によって、節点 N 172 の電位を電源電位 VSS と等しくできる。

#### 【0155】

したがって、トランジスタ 1707 がオンして、配線 1712 の電位が電源電位 VDD と等しい値になる。ここで、節点 N 172 の電位を電源電位 VSS と等しくすることによって、トランジスタ 1707 のゲートとソースとの間の電位差を大きくすることができる。よって、トランジスタ 1707 をオンしやすくすることができ、広い動作条件で基本回路を動作させることができる。

#### 【0156】

続いて、期間 T2 の動作について、図 18(b) を参照して説明する。期間 T2 は、配線 1710 に L 信号が供給され、トランジスタ 1702、及びトランジスタ 1705 がオンしている。また、配線 1711 に H 信号が供給され、トランジスタ 1703、及びトランジスタ 1706 がオフしている。

#### 【0157】

また、節点 N 171 の電位は、トランジスタ 1701 とトランジスタ 1702 との動作点

10

20

30

40

50

によって決定される。なお、トランジスタ 1702 の W / L 比を、トランジスタ 1701 の W / L 比よりも十分大きくしておけば、節点 N171 の電位は電源電位 VDD よりも少しだけ低い電位になる。

#### 【0158】

したがって、トランジスタ 1704 はオフして、トランジスタ 1705 がオンしているため、節点 N172 の電位が電源電位 VDD と等しい値になる。よって、トランジスタ 1707 がオフして、配線 1712 はフローティング（浮遊）状態となる。配線 1712 の電位は、期間 T1 のときの電位を維持するため、電源電位 VDD と等しい値のままである。

#### 【0159】

続いて、期間 T3 の動作について、図 19 (a) を参照して説明する。期間 T3 は、配線 1710 に H 信号が供給され、トランジスタ 1702、及びトランジスタ 1705 がオフしている。また、配線 1711 に L 信号が供給され、トランジスタ 1703、及びトランジスタ 1706 がオンしている。

#### 【0160】

また、節点 N171 の電位は、トランジスタ 1701 とトランジスタ 1703 との動作点によって決定される。なお、トランジスタ 1703 の W / L 比を、トランジスタ 1701 の W / L 比よりも十分大きくしておけば、節点 N171 の電位は電源電位 VDD よりも少しだけ低い電位になる。

#### 【0161】

したがって、トランジスタ 1704 はオフして、トランジスタ 1706 がオンしているため、節点 N172 の電位が電源電位 VDD と等しい値になる。よって、トランジスタ 1707 がオフして、配線 1712 はフローティング（浮遊）状態となる。配線 1712 の電位は、期間 T1、期間 T2 のときの電位を維持するため、電源電位 VDD と等しい値のままである。

#### 【0162】

続いて、期間 T4 の動作について、図 19 (b) を参照して説明する。期間 T4 は、配線 1710 に L 信号が供給され、トランジスタ 1702、及びトランジスタ 1705 がオンしている。また、配線 1711 に L 信号が供給され、トランジスタ 1703、及びトランジスタ 1706 がオンしている。

#### 【0163】

また、節点 N171 の電位は、トランジスタ 1701 とトランジスタ 1702 とトランジスタ 1703 との動作点によって決定されるため、節点 N171 の電位は電源電位 VDD よりも少しだけ低い電位になる。

#### 【0164】

したがって、トランジスタ 1704 はオフして、トランジスタ 1705、及びトランジスタ 1706 がオンしているため、節点 N172 の電位が電源電位 VDD と等しい値になる。よって、トランジスタ 1707 がオフして、配線 1712 はフローティング（浮遊）状態となる。配線 1712 の電位は、期間 T1、期間 T2、期間 T3 のときの電位を維持するため、電源電位 VDD のままである。

#### 【0165】

以上の動作によって、期間 T1 では、図 17 (a) の基本回路は配線 1712 に電源電位 VDD を供給し、配線 1712 の電位を電源電位 VDD と等しい値にする。期間 T2 ~ 期間 4 では、図 17 (a) の基本回路は、配線 1712 をフローティング状態にし、配線 1712 の電位を電源電位 VDD と等しい値に維持する。

#### 【0166】

なお、期間 T1 では、図 17 (a) の基本回路の節点 N172 の電位を電源電位 VSS と等しい値にすることができる。したがって、広い動作条件で、図 17 (a) の基本回路を動作させることができる。

#### 【0167】

また、図 17 (a) の基本回路は、期間 T1 ~ 期間 T4 すべての期間でオン状態であるト

10

20

30

40

50

ランジスタは有していない。つまり、定常的、又はほぼ定常にオン状態であるトランジスタは有していない。したがって、図17(a)の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

#### 【0168】

なお、トランジスタ1701～トランジスタ1707は、トランジスタ501～トランジスタ507と同様な機能を有する。

#### 【0169】

なお、トランジスタ1701～トランジスタ1706によって、配線1710、及び配線1711を入力端子とし、出力端子を節点N172とする、2入力NAND回路を構成している。

10

#### 【0170】

なお、図20(a)に示すように、トランジスタ1704のゲート(節点N171)と、第2端子(節点N172)との間に、容量素子2001を配置してもよい。なぜなら、節点N171の電位、及び節点N172の電位はブーストアップ動作によって減少するため、容量素子2001を配置することで、基本回路がブーストアップ動作しやすくなるからである。

#### 【0171】

なお、図20(b)に示すように、トランジスタ1703は、必ずしも必要ではない。なぜなら、配線1710にL信号が供給されるときは、節点N172の電位が上昇し、トランジスタ1707がオフすればよいからである。

20

#### 【0172】

なお、本実施形態は、本明細書中の他の実施形態のいかなる記載とも自由に組み合わせて実施することができる。また、本実施形態中のいかなる記載も自由に組み合わせて実施することができる。

#### 【0173】

##### (第3の実施形態)

本実施形態では、第1の実施形態、及び第2の実施形態とは別の本発明の基本原理について、図9(a)を参照して説明する。

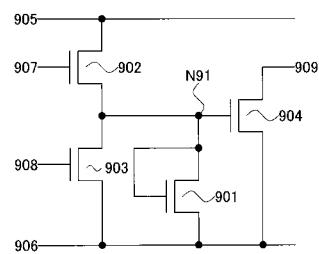

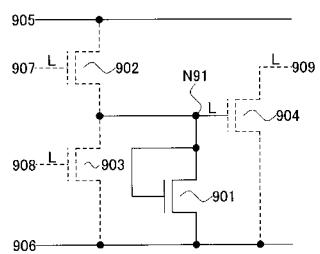

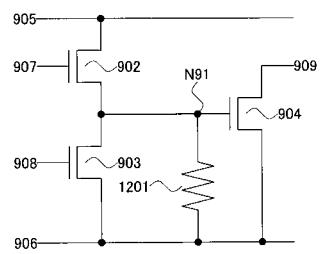

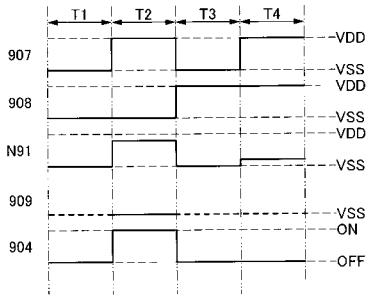

#### 【0174】

図9(a)は、本発明の基本原理に基づく基本回路である。図9(a)の基本回路は、トランジスタ901、トランジスタ902、トランジスタ903、及びトランジスタ904を有している。

30

#### 【0175】

図9(a)の基本回路の接続関係について説明する。トランジスタ901のゲートがトランジスタ904のゲートに接続され、第1端子が配線906に接続され、第2端子がトランジスタ904のゲートに接続されている。トランジスタ902のゲートが配線907に接続され、第1端子が配線905に接続され、第2端子がトランジスタ904のゲートに接続されている。トランジスタ903のゲートが配線908に接続され、第1端子が配線906に接続され、第2端子がトランジスタ904のゲートに接続されている。トランジスタ904の第1端子が配線906に接続され、第2端子が配線909に接続されている。なお、トランジスタ901の第2端子とトランジスタ901のゲートとトランジスタ902の第2端子とトランジスタ903の第2端子とトランジスタ904のゲートとの節点を節点N91とする。

40

#### 【0176】

また、トランジスタ901～トランジスタ904は、それぞれNチャネル型である。

#### 【0177】

したがって、図9(a)の基本回路はすべてNチャネル型のトランジスタで構成することができるため、図9(a)の基本回路は、半導体層にアモルファスシリコンを用いることができ、製造工程の簡略化を図ることができる。したがって、製造コストの削減や歩留まりの向上を図ることができる。さらに、大型の表示パネルなどの半導体装置を作製するこ

50

とも可能となる。また、図9(a)の基本回路は、半導体層にポリシリコンや単結晶シリコンを用いても製造工程の簡略化を図ることができる。

#### 【0178】

また、配線905には電源電位VDDが供給され、配線906には電源電位VSSが供給されている。なお、電源電位VDDは、電源電位VSSよりも高い電位である。ただし、配線905、及び配線906には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

#### 【0179】

また、配線907、及び配線908には、それぞれ信号が供給されている。なお、配線907、及び配線908に供給されている信号は、それぞれ2値の値を持つデジタル信号である。ただし、配線907、及び配線908には、それぞれ電源電位VDD、電源電位VSS、及び他の電源電位が供給されていてもよい。また、配線907、及び配線908には、それぞれアナログ信号が供給されていてもよい。

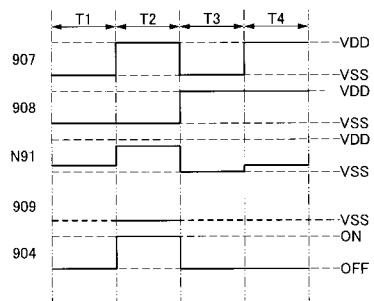

#### 【0180】

次に、図9(a)に示した基本回路の動作について、図9(b)を参照して説明する。

#### 【0181】

図9(b)は、図9(a)に示した基本回路のタイミングチャートの一例である。図9(b)のタイミングチャートは、配線907の電位、配線908の電位、節点N91の電位、配線909の電位、及びトランジスタ904のオン・オフを示している。

#### 【0182】

図9(b)のタイミングチャートを期間T1～期間T4に分割して説明する。また、図10(a)、図10(b)、図11(a)、及び図11(b)は、期間T1、期間T2、期間T3、及び期間T4における図9(a)の基本回路の動作を示している。

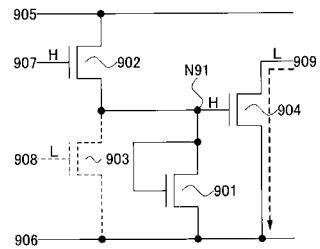

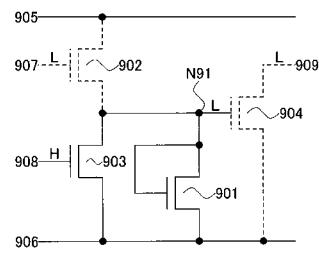

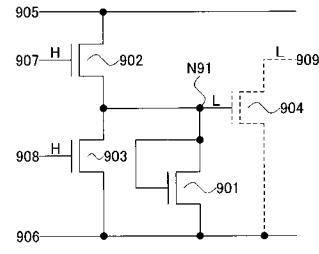

#### 【0183】

まず、期間T1の動作について、図10(a)を参照して説明する。期間T1は、配線907にL信号が供給され、配線908にL信号が供給されている。したがって、トランジスタ902がオフし、トランジスタ903がオフしている。

#### 【0184】

また、トランジスタ901は、ダイオード接続されているので、節点N91の電位が減少し始める。この節点N91の電位の減少は、トランジスタ901がオフするまで続く。トランジスタ901は、節点N91の電位が電源電位VSSとトランジスタ901のしきい値電圧Vth901の絶対値との和(VSS + |Vth901|)になるとオフする。したがって、節点N91の電位はVSS + |Vth901|となる。

#### 【0185】

したがって、トランジスタ904がオフして、配線909の電位は、期間T2の電位を維持するため、電源電位VSSと等しい値のままである。なお、期間T2の動作は次に説明する。

#### 【0186】

続いて、期間T2の動作について、図10(b)を参照して説明する。期間T2は、配線907にH信号が供給され、配線908にL信号が供給されている。したがって、トランジスタ902がオンし、トランジスタ903がオフしている。

#### 【0187】

また、節点N91の電位は、トランジスタ901とトランジスタ902との動作点によって決定される。なお、トランジスタ902のW/L比をトランジスタ901のW/L比よりも十分大きくしておけば、節点N91の電位は電源電位VDDよりも少しだけ低い値になる。

#### 【0188】

したがって、トランジスタ904がオンして、配線909の電位が電源電位VSSと等しい値になる。

#### 【0189】

10

20

30

40

50

続いて、期間T3の動作について、図11(a)を参照して説明する。期間T3は、配線907にL信号が供給され、配線908にH信号が供給されている。したがって、トランジスタ902がオフし、トランジスタ903がオンしている。

#### 【0190】

また、節点N91の電位は、トランジスタ902がオフしているため、電源電位VSSと等しい値になる。

#### 【0191】

したがって、トランジスタ904がオフして、配線909はフローティング(浮遊)状態となる。配線909の電位は、期間T1、期間T2のときの電位を維持するため、電源電位VSSと等しい値のままである。

10

#### 【0192】

続いて、期間T4の動作について、図11(b)を参照して説明する。期間T4は、配線907にH信号が供給され、配線908にはH信号が供給されている。したがって、トランジスタ902がオンし、トランジスタ904がオンしている。

#### 【0193】

また、節点N91の電位は、トランジスタ901とトランジスタ902とトランジスタ903との動作点によって決定されるため、節点N91の電位は電源電位VSSよりも少しだけ高い値になる。

#### 【0194】

したがって、トランジスタ904がオフして、配線909はフローティング(浮遊)状態となる。配線909の電位は、期間T1、期間T2、期間T3のときの電位を維持するため、電源電位VSSと等しい値のままである。

20

#### 【0195】

以上の動作によって、期間T2では、図9(a)の基本回路は配線909に電源電位VSSを供給し、配線909の電位を電源電位VSSと等しい値にする。期間T1、期間T3、及び期間4では、図9(a)の基本回路は、配線909をフローティング状態にし、配線909の電位を電源電位VSSと等しい値に維持する。

#### 【0196】

また、図9(a)の基本回路は、期間T1～期間T4すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジスタは有していない。したがって、図9(a)の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

30

#### 【0197】

また、トランジスタの特性は、トランジスタがアモルファスシリコンで形成されている場合に劣化しやすい。したがって、図9(a)の基本回路は、トランジスタをアモルファスシリコンで形成することによって、製造コストの削減や歩留まりの向上などのメリットが得られるだけでなく、トランジスタの特性劣化の問題も解決できる。

#### 【0198】

ここで、トランジスタ901～トランジスタ904の機能を説明する。トランジスタ901は、入力端子を第2端子、及びゲートとし、出力端子を第1端子としているダイオードとしての機能を有する。トランジスタ902は、配線907の電位に応じて、配線905と節点N91とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ903は、配線908の電位に応じて、配線906と節点N91とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ904は、節点N91の電位に応じて、配線906と配線909とを接続するかしないかを選択するスイッチとしての機能を有する。

40

#### 【0199】

なお、トランジスタ901～トランジスタ904によって、配線907、及び配線908を入力端子とし、出力端子を節点N91とする、2入力の論理回路を構成している。

#### 【0200】

50

なお、トランジスタ 901 は、抵抗成分を持つ素子であればよい。例えば、図 12(a) に示すように、抵抗素子 1201 をトランジスタ 901 の代わりに用いることができる。また、図 12(a) のタイミングチャートを図 12(b) に示す。

#### 【0201】

次に、図 9(a) に示した基本回路を P チャネル型トランジスタで構成した場合について、図 21(a) を参照して説明する。

#### 【0202】

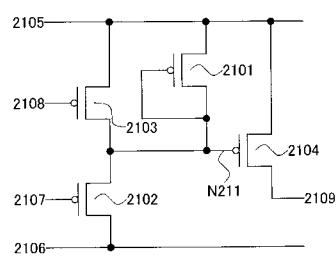

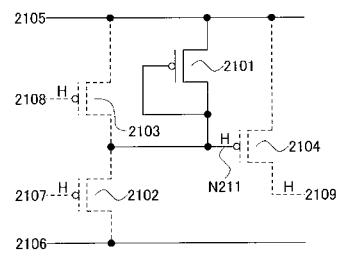

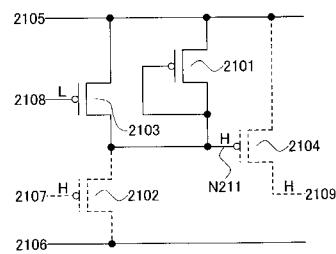

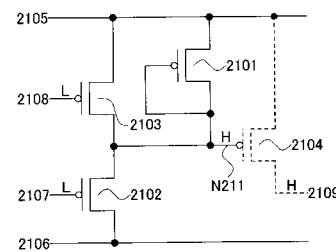

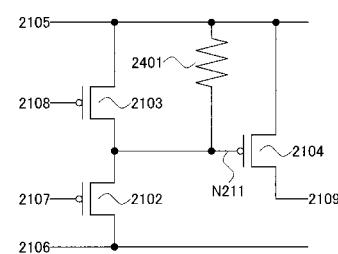

図 21(a) は、本発明の基本原理に基づく基本回路である。図 21(a) の基本回路は、トランジスタ 2101、トランジスタ 2102、トランジスタ 2103、及びトランジスタ 2104 を有している。

10

#### 【0203】

図 21(a) の基本回路の接続関係について説明する。トランジスタ 2101 のゲートがトランジスタ 2104 のゲートに接続され、第 1 端子が配線 2105 に接続され、第 2 端子がトランジスタ 2104 のゲートに接続されている。トランジスタ 2102 のゲートが配線 2107 に接続され、第 1 端子が配線 2106 に接続され、第 2 端子がトランジスタ 2104 のゲートに接続されている。トランジスタ 2103 のゲートが配線 2108 に接続され、第 1 端子が配線 2105 に接続され、第 2 端子がトランジスタ 2104 のゲートに接続されている。トランジスタ 2104 の第 1 端子が配線 2105 に接続され、第 2 端子が配線 2109 に接続されている。なお、トランジスタ 2101 のゲートとトランジスタ 2101 の第 2 端子とトランジスタ 2102 の第 2 端子とトランジスタ 2103 の第 2 端子とトランジスタ 2104 のゲートとの節点を節点 N211 とする。

20

#### 【0204】

また、トランジスタ 2101 ~ トランジスタ 2104 は、それぞれ P チャネル型である。

#### 【0205】

したがって、図 21(a) の基本回路はすべて P チャネル型のトランジスタで構成することができるため、N チャネル型のトランジスタを形成するための工程が必要ない。したがって、図 21(a) の基本回路は、製造工程の簡略化を図ることができ、製造コストの削減や歩留まりの向上を図ることができる。

30

#### 【0206】

また、配線 2105 には電源電位 VDD が供給され、配線 2106 には電源電位 VSS が供給されている。なお、電源電位 VDD は、電源電位 VSS よりも高い電位である。ただし、配線 2105、及び配線 2106 には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

40

#### 【0207】

また、配線 2107、及び配線 2108 には、それぞれ信号が供給されている。なお、配線 2107、及び配線 2108 に供給されている信号は、それぞれ 2 値の値を持つデジタル信号である。ただし、配線 2107、及び配線 2108 には、それぞれ電源電位 VDD、電源電位 VSS、又は他の電源電位が供給されていてもよい。また、配線 2107、及び配線 2108 には、それぞれアナログ信号が供給されていてもよい。

#### 【0208】

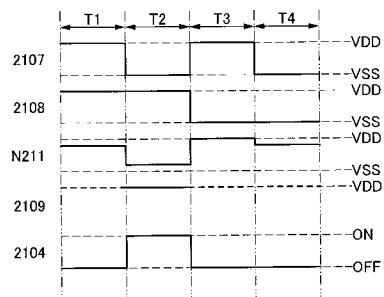

次に、図 21(a) に示した基本回路の動作について、図 21(b) を参照して説明する。

#### 【0209】

図 21(b) は、図 21(a) に示す基本回路のタイミングチャートの一例である。図 21(b) のタイミングチャートは、配線 2107 の電位、配線 2108 の電位、節点 N211 の電位、配線 2109 の電位、及びトランジスタ 2104 のオン・オフを示している。

#### 【0210】

図 21(b) のタイミングチャートを期間 T1 ~ 期間 T4 に分割して説明する。また、図 22(a)、図 22(b)、図 23(a)、及び図 23(b) は、期間 T1、期間 T2、

50

期間 T 3、及び期間 T 4 における図 2 1 ( a ) の基本回路の動作を示している。

【 0 2 1 1 】

まず、期間 T 1 の動作について、図 2 2 ( a ) を参照して説明する。期間 T 1 は、配線 2 1 0 7 に H 信号が供給され、配線 2 1 0 8 に H 信号が供給されている。したがって、トランジスタ 2 1 0 2 がオフし、トランジスタ 2 1 0 3 がオフしている。

【 0 2 1 2 】

また、トランジスタ 2 1 0 1 は、ダイオード接続されているので、節点 N 2 1 1 の電位が上昇し始める。この節点 N 2 1 1 の電位の上昇は、トランジスタ 2 1 0 1 がオフするまで続く。トランジスタ 2 1 0 1 は、節点 N 2 1 1 の電位が電源電位 V D D からトランジスタ 2 1 0 1 のしきい値電位 V t h 2 1 0 1 の絶対値を引いた値 ( V D D - | V t h 2 1 0 1 | ) となるとオフする。よって、節点 N 2 1 1 の電位は V D D - | V t h 2 1 0 1 | となる。

10

【 0 2 1 3 】

したがって、トランジスタ 2 1 0 4 がオフして、配線 2 1 0 9 の電位は、期間 T 2 の電位を維持するため、電源電位 V D D よりも少しだけ低い値のままである。また、期間 T 2 の動作は次に説明する。

【 0 2 1 4 】

続いて、期間 T 2 の動作について、図 2 2 ( b ) を参照して説明する。期間 T 2 は、配線 2 1 0 7 に L 信号が供給され、配線 2 1 0 8 に H 信号が供給されている。したがって、トランジスタ 2 1 0 2 がオンし、トランジスタ 2 1 0 3 がオフしている。

20

【 0 2 1 5 】

また、節点 N 2 1 1 の電位は、トランジスタ 2 1 0 1 とトランジスタ 2 1 0 2 との動作点によって決定される。なお、トランジスタ 2 1 0 2 の W / L 比をトランジスタ 2 1 0 1 の W / L 比よりも十分大きくしておけば、節点 N 2 1 1 の電位は電源電位 V S S よりも少しだけ高い値になる。

【 0 2 1 6 】

したがって、トランジスタ 2 1 0 4 がオンして、配線 2 1 0 9 の電位が電源電位 V D D と等しい値になる。

【 0 2 1 7 】

続いて、期間 T 3 の動作について、図 2 3 ( a ) を参照して説明する。期間 T 3 は、配線 2 1 0 7 に H 信号が供給され、配線 2 1 0 8 に L 信号が供給されている。したがって、トランジスタ 2 1 0 2 がオフし、トランジスタ 2 1 0 3 がオンしている。

30

【 0 2 1 8 】

また、節点 N 2 1 1 の電位は、トランジスタ 2 1 0 2 がオフしているため、電源電位 V D D と等しい値になる。

【 0 2 1 9 】

したがって、トランジスタ 2 1 0 4 がオフして、配線 2 1 0 9 はフロー・ティング ( 浮遊 ) 状態となる。配線 2 1 0 9 の電位は、期間 T 1 、期間 T 2 のときの電位を維持するため、電源電位 V S S と等しい値のままである。

【 0 2 2 0 】

続いて、期間 T 4 の動作について、図 2 3 ( b ) を参照して説明する。期間 T 4 は、配線 2 1 0 7 に L 信号が供給され、配線 2 1 0 8 には L 信号が供給されている。したがって、トランジスタ 2 1 0 2 がオンし、トランジスタ 2 1 0 4 がオンしている。

40

【 0 2 2 1 】

また、節点 N 2 1 1 の電位は、トランジスタ 2 1 0 1 とトランジスタ 2 1 0 2 とトランジスタ 2 1 0 3 との動作点によって決定されるため、節点 N 2 1 1 の電位は電源電位 V D D よりも少しだけ低い値になる。

【 0 2 2 2 】

したがって、トランジスタ 2 1 0 4 がオフして、配線 2 1 0 9 はフロー・ティング ( 浮遊 ) 状態となる。配線 2 1 0 9 の電位は、期間 T 1 、期間 T 2 、期間 T 3 のときの電位を維持

50

するため、電源電位VSSと等しい値のままである。

【0223】

以上の動作によって、期間T2では、図21(a)の基本回路は配線2109に電源電位VDDを供給し、配線2109の電位を電源電位VDDと等しい値にする。期間T1、期間T3、及び期間4では、図21(a)の基本回路は、配線2109をフローティング状態にし、配線2109の電位を電源電位VDDと等しい値に維持する。

【0224】

また、図21(a)の基本回路は、期間T1～期間T4すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジスタは有していない。したがって、図21(a)の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。10

【0225】

なお、トランジスタ2101～トランジスタ2104は、トランジスタ901～トランジスタ904と同様な機能を有する。

【0226】

なお、トランジスタ2101～トランジスタ2104によって、配線2107、及び配線2108を入力端子とし、出力端子を節点N211とする、2入力の論理回路を構成している。

【0227】

なお、トランジスタ2101は、抵抗成分を持つ素子であればよい。例えば、図24(a)に示すように、抵抗素子2401をトランジスタ2101の代わりに用いることができる。また、図24(a)のタイミングチャートを図24(b)に示す。20

【0228】

なお、本実施形態は、本明細書中の他の実施形態のいかなる記載とも自由に組み合わせて実施することができる。また、本実施形態中のいかなる記載も自由に組み合わせて実施することができる。

【0229】

(第4の実施形態)

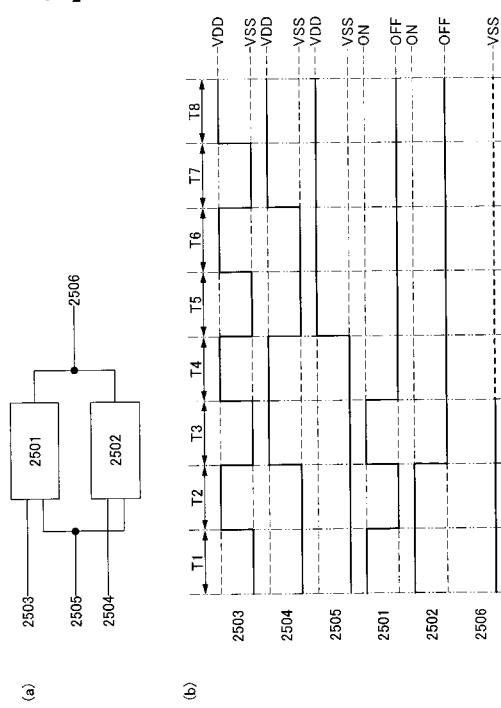

本実施形態では、第1の実施形態乃至第3の実施形態とは別の本発明の基本原理について、図25(a)を参照して説明する。30

【0230】

図25(a)は、本発明の基本原理に基づく基本回路である。図25(a)の基本回路は、回路2501、及び回路2502を有している。

【0231】

なお、回路2501、及び回路2502として、図1(a)、図4(a)、図5(a)、図8(a)、図8(b)、図9(a)、図12(a)に示した基本回路を用いることができる。

【0232】

したがって、配線2503、及び配線2504は、図1(a)の配線107、図4(a)の配線107、図5(a)の配線510、図8(a)の配線510、図8(b)の配線510、図9(a)の配線907、図12(a)の配線907に相当する。40

【0233】

また、配線2505は、図1(a)の配線108、図4(a)の配線108、図5(a)の配線511、図8(a)の配線511、図8(b)の配線511、図9(a)の配線908、図12(a)の配線908に相当する。

【0234】

また、配線2506は、図1(a)の配線109、図4(a)の配線109、図5(a)の配線512、図8(a)の配線512、図8(b)の配線512、図9(a)の配線909、図12(a)の配線909に相当する。

【0235】

10

20

30

40

50

また、図25(a)の基本回路は、すべてNチャネル型のトランジスタで構成することができるため、図9(a)の基本回路は、半導体層にアモルファスシリコンを用いることができ、製造工程の簡略化を図ることができる。したがって、製造コストの削減や歩留まりの向上を図ることができる。さらに、大型の表示パネルなどの半導体装置を作製することも可能となる。また、図25(a)の基本回路は、半導体層にポリシリコンや単結晶シリコンを用いても製造工程の簡略化を図ることができる。

#### 【0236】

また、電源電位が供給されている配線は、省略する。

#### 【0237】

また、配線2503、配線2504、及び配線2505には、それぞれ信号が供給されている。なお、配線2503、配線2504、及び配線2505に供給されている信号は、それぞれ2値の値を持つデジタル信号である。

#### 【0238】

ただし、配線2503、配線2504、及び配線2505には、それぞれ電源電位VDD、電源電位VSS、又は他の電源電位が供給されていてもよい。また、配線2503、配線2504、及び配線2505には、それぞれアナログ信号が供給されていてもよい。

#### 【0239】

次に、図25(a)に示した基本回路の動作について、図25(b)を参照して説明する。なお、図25(b)は、回路2501、回路2502として、図1(a)、図4(a)、図5(a)、図8(a)、図8(b)に示した基本回路を用いた場合について示す。

#### 【0240】

図25(b)は、図25(a)に示した基本回路のタイミングチャートの一例である。図25(b)のタイミングチャートは、配線2503の電位、配線2504の電位、配線2505の電位、回路2501の出力が浮遊(OFFで表記)か電源電位VSS(ONで表記)か、回路2502の出力が浮遊(OFFで表記)か電源電位VSS(ONで表記)か、配線2506の電位を示している。

#### 【0241】

図25(b)のタイミングチャートを期間T1～期間T8に分割して説明する。

#### 【0242】

まず、期間T1の動作について説明する。期間T1は、配線2505にL信号が供給され、配線2503にL信号が供給され、配線2504にL信号が供給されている。回路2501は配線2506に電源電位VSSを供給し、回路2502は配線2506に電源電位VSSを供給する。したがって、配線2506の電位は電源電位VSSと等しい値となる。

#### 【0243】

続いて、期間T2の動作について説明する。期間T2は、配線2505にL信号が供給され、配線2503にH信号が供給され、配線2504にL信号が供給されている。回路2501は配線2506になにも供給せず、回路2502は配線2506に電源電位VSSを供給する。したがって、配線2506の電位は電源電位VSSと等しい値となる。

#### 【0244】

続いて、期間T3の動作について説明する。期間T3では、配線2505にL信号が供給され、配線2503にL信号が供給され、配線2504にH信号が供給されている。回路2501は配線2506に電源電位VSSを供給し、回路2502は配線2506になにも供給しない。したがって、配線2506の電位は電源電位VSSと等しい値となる。

#### 【0245】

続いて、期間T4の動作について説明する。期間T4では、配線2505にL信号が供給され、配線2503にH信号が供給され、配線2504にH信号が供給されている。回路2501は配線2506になにも供給せず、回路2502は配線2506になにも供給しない。したがって、配線2506の電位は、期間T3の電位を維持するため、電源電位VSSと等しい値のままである。

10

20

30

40

50

**【 0 2 4 6 】**

続いて、期間 T 5 の動作について説明する。期間 T 5 では、配線 2 5 0 5 に H 信号が供給され、配線 2 5 0 3 に L 信号が供給され、配線 2 5 0 4 に L 信号が供給されている。回路 2 5 0 1 は配線 2 5 0 6 になにも供給せず、回路 2 5 0 2 は配線 2 5 0 6 になにも供給しない。したがって、配線 2 5 0 6 の電位は、期間 T 3 の電位を維持するため、電源電位 V SS と等しい値のままである。

**【 0 2 4 7 】**

続いて、期間 T 6 の動作について説明する。期間 T 6 では、配線 2 5 0 5 に H 信号が供給され、配線 2 5 0 3 に H 信号が供給され、配線 2 5 0 4 に L 信号が供給されている。回路 2 5 0 1 は配線 2 5 0 6 になにも供給せず、回路 2 5 0 2 は配線 2 5 0 6 になにも供給しない。したがって、配線 2 5 0 6 の電位は、期間 T 3 の電位を維持するため、電源電位 V SS と等しい値のままである。10

**【 0 2 4 8 】**

続いて、期間 T 7 の動作について説明する。期間 T 7 では、配線 2 5 0 5 に H 信号が供給され、配線 2 5 0 3 に L 信号が供給され、配線 2 5 0 4 に H 信号が供給されている。回路 2 5 0 1 は配線 2 5 0 6 になにも供給せず、回路 2 5 0 2 は配線 2 5 0 6 になにも供給しない。したがって、配線 2 5 0 6 の電位は、期間 T 3 の電位を維持するため、電源電位 V SS と等しい値のままである。

**【 0 2 4 9 】**

続いて、期間 T 8 の動作について説明する。期間 T 8 では、配線 2 5 0 5 に H 信号が供給され、配線 2 5 0 3 に H 信号が供給され、配線 2 5 0 4 に H 信号が供給されている。回路 2 5 0 1 は配線 2 5 0 6 になにも供給せず、回路 2 5 0 2 は配線 2 5 0 6 になにも供給しない。したがって、配線 2 5 0 6 の電位は、期間 T 3 の電位を維持するため、電源電位 V SS と等しい値のままである。20

**【 0 2 5 0 】**

以上の動作によって、期間 T 1 では、回路 2 5 0 1 が電源電位 V SS を配線 2 5 0 6 に供給し、回路 2 5 0 2 が電源電位 V SS を配線 2 5 0 6 に供給し、配線 2 5 0 6 の電位を電源電位 V SS と等しい値にする。期間 T 2 では、回路 2 5 0 2 が電源電位 V SS を配線 2 5 0 6 に供給し、配線 2 5 0 6 の電位を電源電位 V SS と等しい値にする。期間 T 3 では、回路 2 5 0 1 が電源電位 V SS を配線 2 5 0 6 に供給し、配線 2 5 0 6 の電位を電源電位 V SS と等しい値にする。期間 T 4 ~ 期間 T 8 では、配線 2 5 0 6 をフローティング状態にし、配線 2 5 0 6 の電位を電源電位 V SS と等しい値に維持する。30

**【 0 2 5 1 】**

また、図 2 5 ( a ) の基本回路は、期間 T 1 ~ 期間 T 8 にすべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又は定常的にオン状態であるトランジスタは有していない。したがって、図 2 5 ( a ) の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

**【 0 2 5 2 】**

また、トランジスタの特性は、トランジスタがアモルファスシリコンで形成されている場合に劣化しやすい。したがって、図 2 5 ( a ) の基本回路は、トランジスタをアモルファスシリコンで形成することによって、製造コストの削減や歩留まりの向上などのメリットが得られるだけでなく、トランジスタの特性劣化の問題も解決できる。40

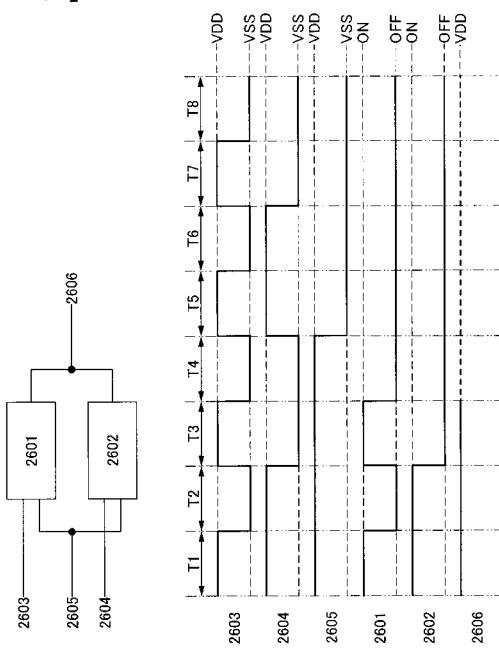

**【 0 2 5 3 】**

次に、図 2 5 ( a ) に示した基本回路を P チャネル型トランジスタで構成した場合について、図 2 6 ( a ) を参照して説明する。

**【 0 2 5 4 】**

図 2 6 ( a ) は、本発明の基本原理に基づく基本回路である。図 2 6 ( a ) の基本回路は、回路 2 6 0 1 、及び回路 2 6 0 2 を有している。

**【 0 2 5 5 】**

なお、回路 2 6 0 1 、及び回路 2 6 0 2 として、図 1 3 ( a ) 、図 1 6 ( a ) 、図 1 7 ( 50

a)、図20(a)、図20(b)、図21(a)、図24(a)に示した基本回路を用いることができる。

#### 【0256】

したがって、配線2603、および配線2604は、図13(a)の配線1307、図16(a)の配線1307、図17(a)の配線1710、図20(a)の配線1710、図20(b)の配線1710、図21(a)の配線2108、図24(a)の配線2108に相当する。

#### 【0257】

また、配線2605は、図13(a)の配線1308、図16(a)の配線1308、図17(a)の配線1711、図20(a)の配線1711、図20(b)の配線1711、図21(a)の配線2107、図24(a)の配線2107に相当する。 10

#### 【0258】

また、配線2606は、図13(a)の配線1309、図16(a)の配線1309、図17(a)の配線1712、図20(a)の配線1712、図20(b)の配線1712、図21(a)の配線2109、図24(a)の配線2109に相当する。 20

#### 【0259】

したがって、図26(a)の基本回路はすべてPチャネル型のトランジスタで構成することができるため、Nチャネル型のトランジスタを形成するための工程が必要ない。したがって、図26(a)の基本回路は、製造工程の簡略化を図ることができ、製造コストの削減や歩留まりの向上を図ることができる。 20

#### 【0260】

また、電源電位が供給されている配線は、省略する。

#### 【0261】

また、配線2603、配線2604、及び配線2605には、それぞれ信号が供給されている。なお、配線2603、配線2604、及び配線2605に供給されている信号は、それぞれ2値の値を持つデジタル信号である。

#### 【0262】

ただし、配線2603、配線2604、及び配線2605には、それぞれ電源電位VDD、電源電位VSS、又は他の電源電位が供給されていてもよい。また、配線2603、配線2604、及び配線2605には、それぞれアナログ信号が供給されていてもよい。 30

#### 【0263】

次に、図26(a)に示した基本回路の動作について、図26(b)を参照して説明する。なお、図26(b)は、回路2601、回路2602として、図13(a)、図16(a)、図17(a)、図20(a)、図20(b)に示した基本回路を用いた場合について示す。

#### 【0264】

図26(b)は、図26(a)に示した基本回路のタイミングチャートの一例である。図26(b)のタイミングチャートは、配線2603の電位、配線2604の電位、配線2605の電位、回路2601の出力が浮遊(OFFで表記)か電源電位VSS(ONで表記)か、回路2602の出力が浮遊(OFFで表記)か電源電位VSS(ONで表記)か、配線2606の電位を示している。 40

#### 【0265】

図26(b)のタイミングチャートを期間T1～期間T8に分割して説明する。

#### 【0266】

まず、期間T1の動作について説明する。期間T1では、配線2605にH信号が供給され、配線2603にH信号が供給され、配線2604にH信号が供給されている。回路2601は配線2606に電源電位VDDを供給し、回路2602は配線2606に電源電位VDDを供給する。したがって、配線2606の電位は電源電位VDDと等しい値となる。

#### 【0267】

続いて、期間T2の動作について説明する。期間T2では、配線2605にH信号が供給され、配線2603にL信号が供給され、配線2604にH信号が供給されている。回路2601は配線2606になにも供給せず、回路2602は配線2606に電源電位VDDを供給する。したがって、配線2606の電位は電源電位VDDと等しい値となる。

#### 【0268】

続いて、期間T3の動作について説明する。期間T3では、配線2605にH信号が供給され、配線2603にH信号が供給され、配線2604にL信号が供給されている。回路2601は配線2606に電源電位VDDを供給し、回路2602は配線2606になにも供給しない。したがって、配線2606の電位は電源電位VDDと等しい値となる。

#### 【0269】

続いて、期間T4の動作について説明する。期間T4では、配線2605にH信号が供給され、配線2603にL信号が供給され、配線2604にL信号が供給されている。回路2601は配線2606になにも供給せず、回路2602は配線2606になにも供給しない。したがって、配線2606の電位は、期間T3の電位を維持するため、電源電位VDDと等しい値のままである。

#### 【0270】

続いて、期間T5の動作について説明する。期間T5では、配線2605にL信号が供給され、配線2603にH信号が供給され、配線2604にH信号が供給されている。回路2601は配線2606になにも供給せず、回路2602は配線2606になにも供給しない。したがって、配線2606の電位は、期間T3の電位を維持するため、電源電位VDDと等しい値のままである。

#### 【0271】

続いて、期間T6の動作について説明する。期間T6では、配線2605にL信号が供給され、配線2603にL信号が供給され、配線2604にH信号が供給されている。回路2601は配線2606になにも供給せず、回路2602は配線2606になにも供給しない。したがって、配線2606の電位は、期間T3の電位を維持するため、電源電位VDDと等しい値のままである。

#### 【0272】

続いて、期間T7の動作について説明する。期間T7では、配線2605にL信号が供給され、配線2603にH信号が供給され、配線2604にL信号が供給されている。回路2601は配線2606になにも供給せず、回路2602は配線2606になにも供給しない。したがって、配線2606の電位は、期間T3の電位を維持するため、電源電位VDDと等しい値のままである。

#### 【0273】

続いて、期間T8の動作について説明する。期間T8では、配線2605にL信号が供給され、配線2603にL信号が供給され、配線2604にL信号が供給されている。回路2601は配線2606になにも供給せず、回路2602は配線2606になにも供給しない。したがって、配線2606の電位は、期間T3の電位を維持するため、電源電位VDDと等しい値のままである。

#### 【0274】

以上の動作によって、期間T1では、回路2601が電源電位VDDを配線2606に供給し、回路2602が電源電位VDDを配線2606に供給し、配線2606の電位を電源電位VDDと等しい値にする。期間T2では、回路2602が電源電位VDDを配線2606に供給し、配線2606の電位を電源電位VDDと等しい値にする。期間T3では、回路2601が電源電位VDDを配線2606に供給し、配線2606の電位を電源電位VDDと等しい値にする。期間T4～期間T8では、配線2606をフローティング状態にし、配線2606の電位を電源電位VDDと等しい値に維持する。

#### 【0275】

また、図26(a)の基本回路は、期間T1～期間T8すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジ

10

20

30

40

50

スタは有していない。したがって、図26(a)の基本回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

#### 【0276】

なお、本実施形態は、本明細書中の他の実施形態のいかなる記載とも自由に組み合わせて実施することができる。また、本実施形態中のいかなる記載も自由に組み合わせて実施することができる。

#### 【0277】

##### (第5の実施形態)

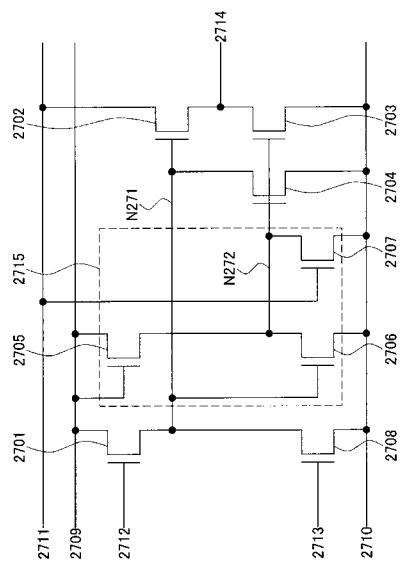

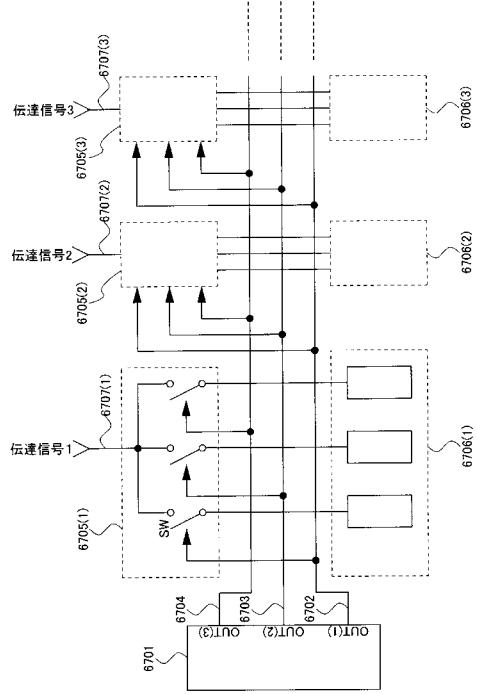

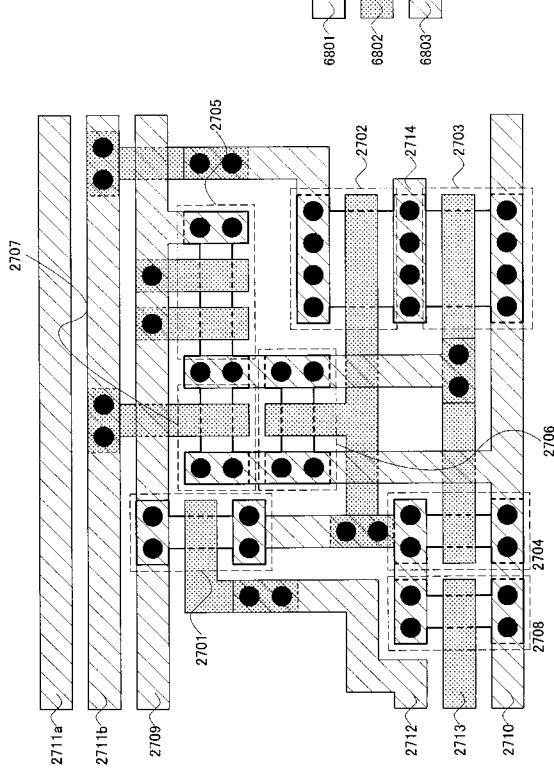

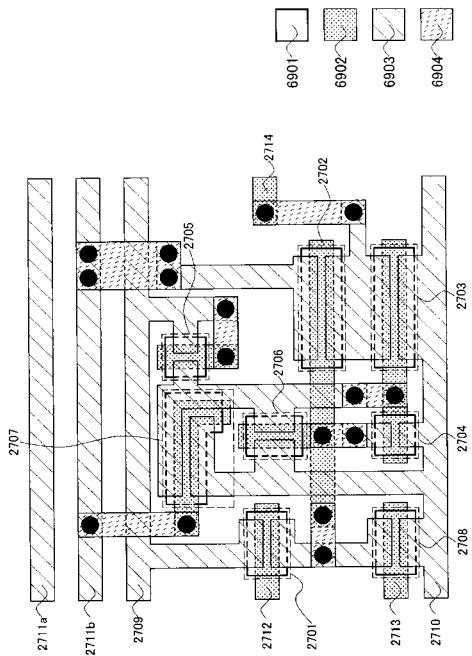

本実施形態では、第1の実施形態で説明した基本回路をフリップフロップ回路に適用した場合について、図27を参照して説明する。

10

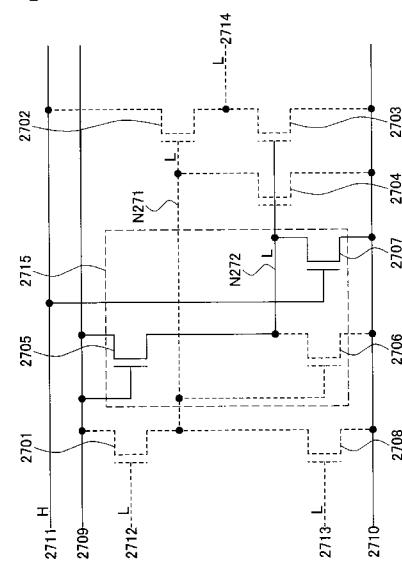

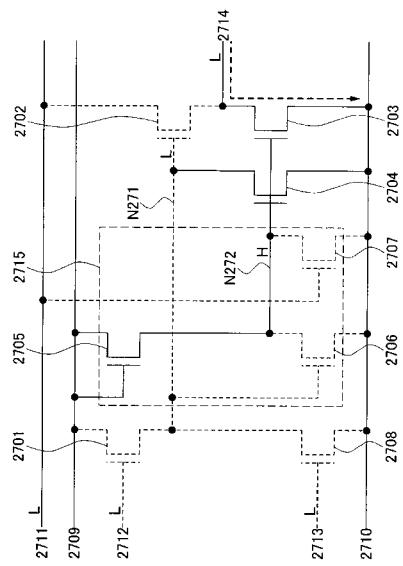

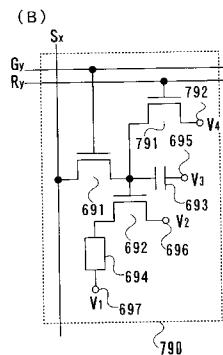

#### 【0278】

図27は、第1の実施の形態で説明した図1(a)の基本回路を適用したフリップフロップ回路の一例である。図27のフリップフロップ回路は、トランジスタ2701、トランジスタ2702、トランジスタ2703、トランジスタ2704、トランジスタ2705、トランジスタ2706、トランジスタ2707、及びトランジスタ2708を有している。

#### 【0279】

なお、トランジスタ2705が図1(a)のトランジスタ101、トランジスタ2707が図1(a)のトランジスタ103、トランジスタ2706が図1(a)のトランジスタ102に、それぞれ相当する。また、トランジスタ2703、及びトランジスタ2704が図1(a)のトランジスタ104に相当する。

20

#### 【0280】

図27のフリップフロップ回路の接続関係について説明する。なお、トランジスタ2701の第2端子とトランジスタ2708の第2端子とトランジスタ2706のゲートとトランジスタ2704の第2端子とトランジスタ2702のゲートとの節点を節点N271とする。また、トランジスタ2705の第2端子とトランジスタ2706の第2端子とトランジスタ2707の第2端子とトランジスタ2703のゲートとトランジスタ2704のゲートとの節点を節点N272とする。

#### 【0281】

トランジスタ2701のゲートが配線2712に接続され、第1端子が配線2709に接続され、第2端子が節点N271に接続されている。トランジスタ2708のゲートが配線2713に接続され、第1端子が配線2710に接続され、第2端子が節点N271に接続されている。トランジスタ2705のゲートが配線2709に接続され、第1端子が配線2709に接続され、第2端子が節点N272に接続されている。トランジスタ2706のゲートが節点N271に接続され、第1端子が配線2710に接続され、第2端子が節点N271に接続され、第2端子が節点N272に接続されている。トランジスタ2707のゲートが配線2711に接続され、第1端子が配線2710に接続され、第2端子が節点N272に接続されている。トランジスタ2704のゲートが節点N272に接続され、第1端子が配線2710に接続され、第2端子が節点N271に接続されている。トランジスタ2703のゲートが節点N272に接続され、第1端子が配線2710に接続され、第2端子が配線2714に接続されている。トランジスタ2702のゲートが節点N271に接続され、第1端子が配線2711に接続され、第2端子が配線2714に接続されている。

30

#### 【0282】

また、トランジスタ2701～トランジスタ2708は、それぞれNチャネル型である。

#### 【0283】

したがって、図27のフリップフロップ回路はすべてNチャネル型のトランジスタで構成することができため、図27のフリップフロップ回路は、半導体層にアモルファスシリコンを用いることができ、製造工程の簡略化を図ることができる。したがって、製造コストの削減や歩留まりの向上を図ることができる。さらに、大型の表示パネルなどの半導体装置を作製することも可能となる。また、図27のフリップフロップ回路は、半導体層にボ

40

50

リシリコンや単結晶シリコンを用いても製造工程の簡略化を図ることができる。

【0284】

また、配線2709には電源電位VDDが供給され、配線2710には電源電位VSSが供給されている。なお、電源電位VDDは、電源電位VSSよりも高い電位である。ただし、配線2709、及び配線2710には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

【0285】

また、配線2711、配線2712、及び配線2713には、それぞれ信号が供給されている。なお、配線2711、配線2712、及び配線2713に供給されている信号は、それぞれ2値の値を持つデジタル信号である。ただし、配線2711、配線2712、及び配線2713には、それぞれ電源電位VDD、電源電位VSS、又は他の電源電位が供給されていてもよい。また、配線2711、配線2712、及び配線2713には、それぞれアナログ信号が供給されていてもよい。

【0286】

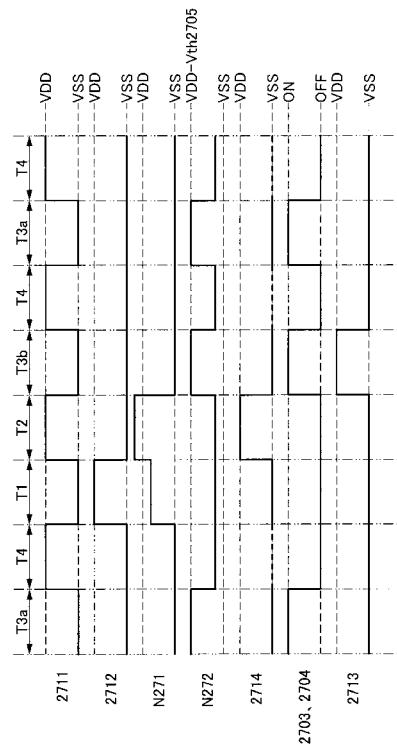

次に、図27に示したフリップフロップ回路の動作について、図28を参照して説明する。

【0287】

図28は、図27に示したフリップフロップ回路のタイミングチャートの一例である。図28のタイミングチャートは、配線2711の電位、配線2712の電位、節点N271の電位、節点N272の電位、配線2714の電位、トランジスタ2703、及びトランジスタ2704のオン、オフの関係、配線2713の電位を示している。

【0288】

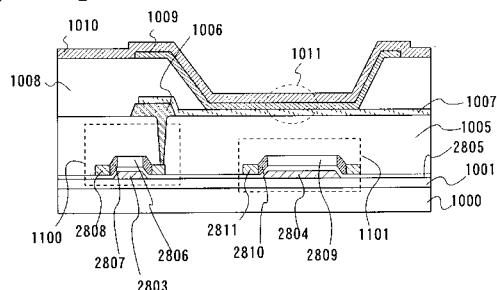

図28のタイミングチャートを期間T1～期間T4に分割して説明する。また、期間T3は、期間T3aと期間T3bとに分割して説明する。また、図29、図30、図31、図32、図33は、それぞれ、期間T1、期間T2、期間T3b、期間T4、期間T3aにおける図27のフリップフロップ回路の動作を示している。

【0289】

なお、期間T1、期間T2、期間T3b以外の期間は、期間T3aと期間T4とを順に繰り返している。

【0290】

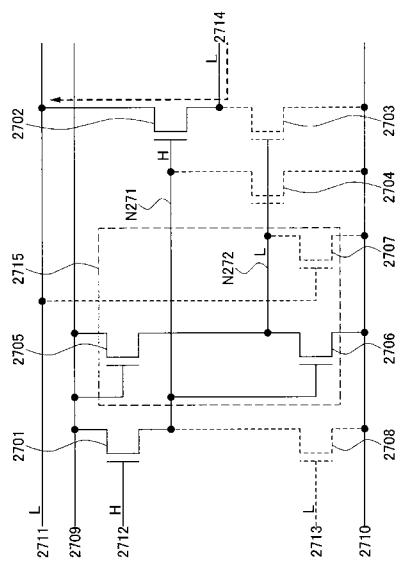

まず、期間T1の動作について、図29を参照して説明する。期間T1では、配線2711にL信号が供給され、配線2712にH信号が供給され、配線2713にL信号が供給されている。

【0291】

したがって、トランジスタ2701がオンになり、トランジスタ2708がオフになり、トランジスタ2707がオフになる。このとき、節点N271にトランジスタ2701を通して電源電位VDDが供給され、節点N271の電位が上昇する。また、トランジスタ2706が節点N271の電位の上昇によってオンして、節点N272の電位が減少する。また、トランジスタ2703、及びトランジスタ2704が節点N272の電位の減少によってオフする。

【0292】

ここで、節点N271の電位の上昇は、トランジスタ2701がオフするまで続く。トランジスタ2701は、節点N271の電位が電源電位VDDからトランジスタ2701のしきい値電圧V<sub>th2701</sub>を引いた値(VDD - V<sub>th2701</sub>)になるとオフする。したがって、節点N271の電位は、VDD - V<sub>th2701</sub>となる。また、節点N271は、フローティング状態となる。

【0293】

したがって、トランジスタ2702がオンする。また、配線2714には、配線2711のL信号が供給されるため、配線2714の電位は電源電位VSSと等しい値となる。

【0294】

10

20

30

40

50

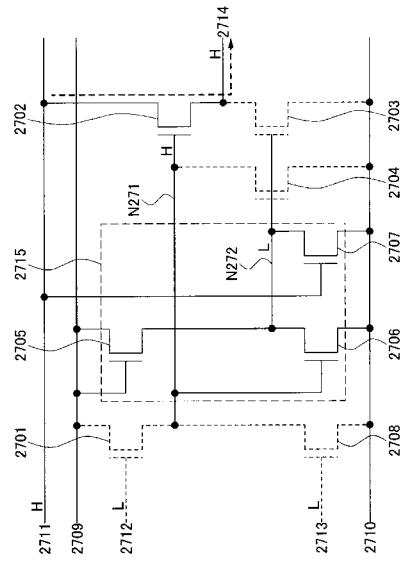

続いて、期間T2の動作について、図30を参照して説明する。期間T2では、配線2711にH信号が供給され、配線2712にL信号が供給され、配線2713にL信号が供給されている。

#### 【0295】

したがって、トランジスタ2701がオフになり、トランジスタ2708がオフのままであり、トランジスタ2707がオンになる。このとき、節点N271はフローティング状態であり、節点N271の電位はVDD-Vth2701を維持している。また、節点N272の電位は、トランジスタ2706、及びトランジスタ2707がオンしているため、Lレベルのままである。よって、節点N272がLレベルであるため、トランジスタ2703、及びトランジスタ2704がオフのままである。

10

#### 【0296】

ここで、節点N271はフローティング状態であり、Hレベルを維持している。また、トランジスタ2702は節点N271がHレベルを維持しているため、オンのままである。また、配線2714には配線2711のH信号が供給されるため、配線2714の電位が上昇している。したがって、ブートストラップ動作によって、節点N271の電位は電源電位VDDとトランジスタ2702のしきい値電圧Vth2702との和(VDD+Vth2702)以上になり、配線2714の電位は電源電位VDDと等しい値になる。

#### 【0297】

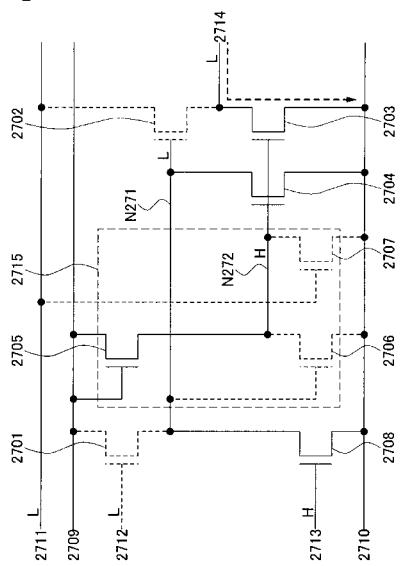

続いて、期間T3bの動作について、図31を参照して説明する。期間T3bでは、配線2711にL信号が供給され、配線2712にL信号が供給され、配線2713にH信号が供給されている。

20

#### 【0298】

したがって、トランジスタ2701がオフのままであり、トランジスタ2708がオンになり、トランジスタ2707がオフになる。このとき、節点N271にトランジスタ2708を介して電源電位VSSが供給され、節点N271の電位が減少する。また、トランジスタ2706が節点N271の電位の減少によってオフして、節点N272の電位が上昇する。また、トランジスタ2703、及びトランジスタ2704が節点N272の電位の上昇によってオンする。

#### 【0299】

また、トランジスタ2702は節点N271の電位の減少によってオフする。したがって、配線2714には、トランジスタ2703を介して電源電位VSSが供給されるため、配線2714の電位は電源電位VSSと等しい値になる。

30

#### 【0300】

続いて、期間T4の動作について、図32を参照して説明する。期間T4では、配線2711にH信号が供給され、配線2712にL信号が供給され、配線2713にL信号が供給されている。

#### 【0301】

したがって、トランジスタ2701がオフのままであり、トランジスタ2708がオフになり、トランジスタ2707がオンになる。このとき、節点N271はフローティング状態になり、節点N271の電位は電源電位VSSを維持する。したがって、トランジスタ2706、及びトランジスタ2702がオフする。また、節点N272の電位はトランジスタ2707を介して電源電位VSSが供給されるため、Lレベルになる。したがって、トランジスタ2703、及びトランジスタ2704がオフする。

40

#### 【0302】

したがって、配線2714はフローティング状態になり、配線2714の電位は電源電位VSSと等しい値を維持する。

#### 【0303】

続いて、期間T3aの動作について、図33を参照して説明する。期間T3aでは、配線2711にL信号が供給され、配線2712にL信号が供給され、配線2713にL信号が供給されている。

50

## 【0304】

したがって、トランジスタ2701がオフのままであり、トランジスタ2708がオフのままであり、トランジスタ2707がオフになる。このとき、節点N272の電位はトランジスタ2707がオフするため上昇する。したがって、トランジスタ2703、及びトランジスタ2704がオンする。また、節点N271にトランジスタ2704を介して電源電位VSSが供給され、節点N271の電位は電源電位VSSと等しい値になる。したがって、トランジスタ2702、及びトランジスタ2706はオフのままである。

## 【0305】

また、配線2714にはトランジスタ2703を介して電源電位VSSが供給され、配線2714の電位は電源電位VSSと等しい値を維持する。

10

## 【0306】

以上の動作によって、期間T1では、図27のフリップフロップ回路は、節点N271をHレベルのまま、フローティング状態にする。期間T2では、図27のフリップフロップ回路は、ブートストラップ動作によって、節点N271の電位をVDD+Vth2702以上にし、配線2714の電位を電源電位VDDと等しい値にできる。

20

## 【0307】

また、期間T3aにおいて、図27のフリップフロップ回路は、トランジスタ2703、及びトランジスタ2704がオンして、電源電位VSSを配線2714、及び節点N271に供給する。また、期間T4において、図27のフリップフロップ回路は、トランジスタ2703、及びトランジスタ2704をオフする。したがって、図27のフリップフロップ回路は、トランジスタ2703、及びトランジスタ2704が順にオンするため、トランジスタ2703、及びトランジスタ2704の特性劣化を抑制でき、節点N271、及び配線2714の電位を安定して電源電位VSSと等しい値に維持することができる。

20

## 【0308】

また、図27のフリップフロップ回路は、期間T1～期間T4すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジスタは有していない。したがって、図27のフリップ回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

30

## 【0309】

また、トランジスタの特性は、トランジスタがアモルファスシリコンで形成されている場合に劣化しやすい。したがって、図27のフリップフロップ回路は、トランジスタをアモルファスシリコンで形成することによって、製造コストの削減や歩留まりの向上などのメリットが得られるだけでなく、トランジスタの特性劣化の問題も解決できる。

30

## 【0310】

ここで、トランジスタ2701～トランジスタ2708の機能を説明する。トランジスタ2701は、配線2712の電位に応じて、配線2709と節点N271とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ2702は、節点N271の電位に応じて、配線2711と配線2714とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ2703は、節点N272の電位に応じて、配線2710と配線2714とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ2704は、節点N272の電位に応じて、配線2710と節点N271とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ2705は、入力端子を第1端子、及びゲートとし、出力端子を第2端子としているダイオードとしての機能を有する。トランジスタ2706は、節点N271の電位に応じて、配線2710と節点N272とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ2707は、配線2711の電位に応じて、配線2710と節点N272とを接続するかしないかを選択するスイッチとしての機能を有する。トランジスタ2708は、配線2713の電位に応じて、配線2710と節点N271とを接続するかしないかを選択するスイッチとしての機能を有する。

40

## 【0311】

50

なお、トランジスタ 2705、トランジスタ 2706、及びトランジスタ 2707によって、節点 N271、及び配線 2711 を入力端子とし、出力端子を節点 N272 とする 2 入力 NOR 回路 2715 を構成している。

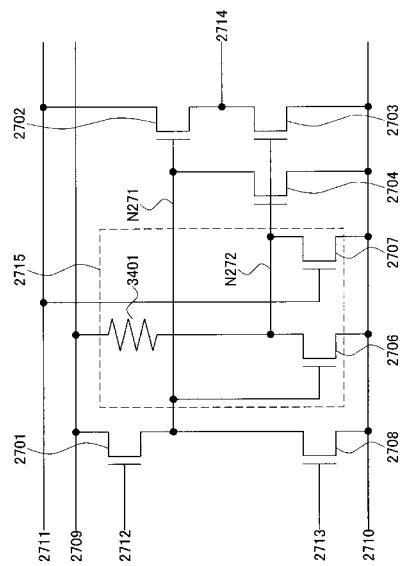

### 【0312】

なお、トランジスタ 2705 は、抵抗成分を持つ素子であればよい。例えば、図 34 に示すように、抵抗素子 3401 をトランジスタ 2705 の代わりに用いることができる。抵抗素子 3401 を用いることによって、節点 N272 の電位において電源電位 VDD と等しい値とすることができます。

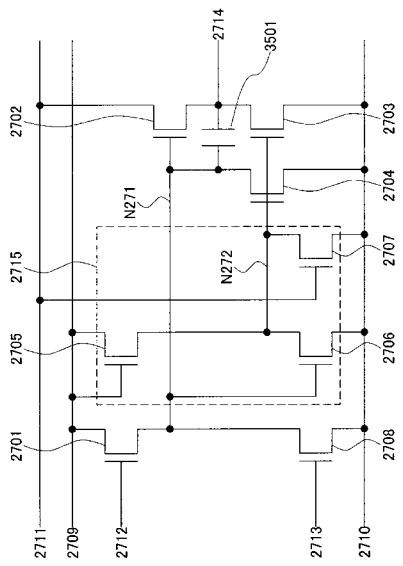

### 【0313】

なお、図 35 に示すように、トランジスタ 2702 のゲート（節点 N271）と、第 2 端子（配線 2714）との間に、容量素子 3501 を配置していてもよい。なぜなら、期間 T2 において、節点 N271 の電位、及び配線 2714 の電位はブーストアップ動作によって、上昇させるため、容量素子 3501 を配置することで、フリップフロップ回路がブーストアップ動作しやすくなるからである。

### 【0314】

なお、トランジスタ 2701 は、期間 T1 において、節点 N271 をフローティング状態にして、節点 N271 の電位を H レベルにできればよい。したがって、トランジスタ 2701 の第 1 端子を配線 2712 に接続しても、節点 N271 をフローティング状態にして、節点 N271 の電位を H レベルにできる。

### 【0315】

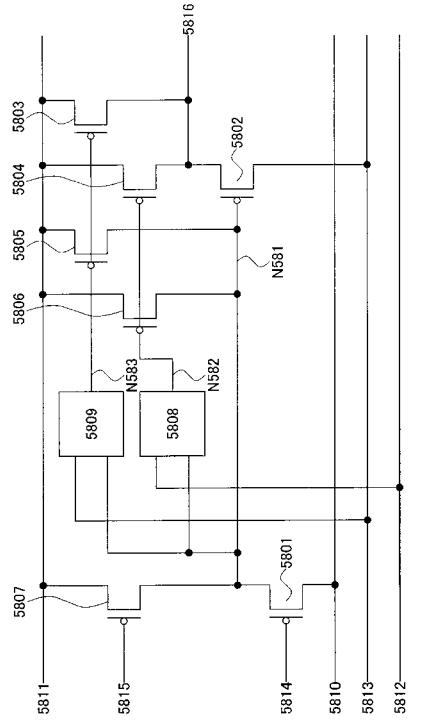

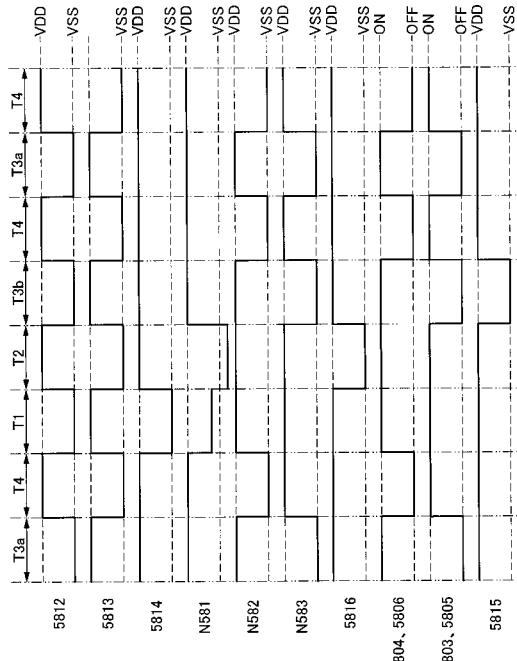

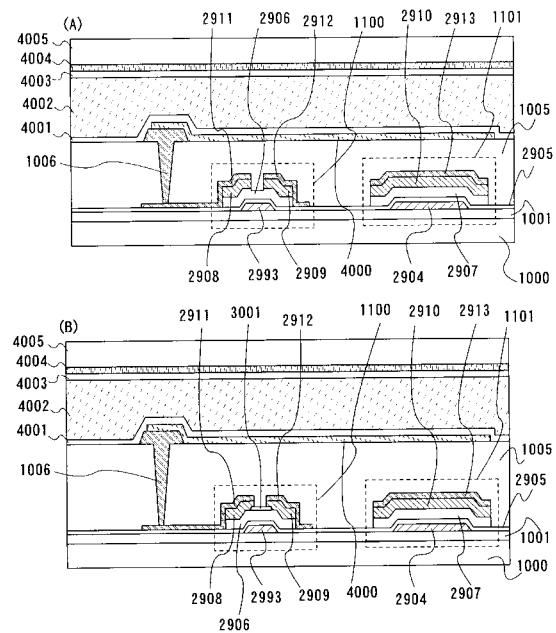

次に、図 27 に示したフリップフロップ回路を P チャネル型トランジスタで構成した場合について、図 44 を参照して説明する。

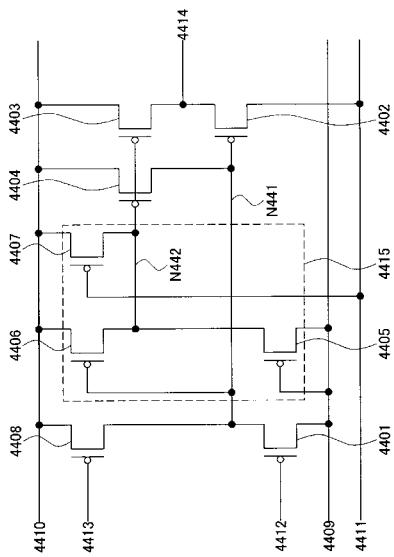

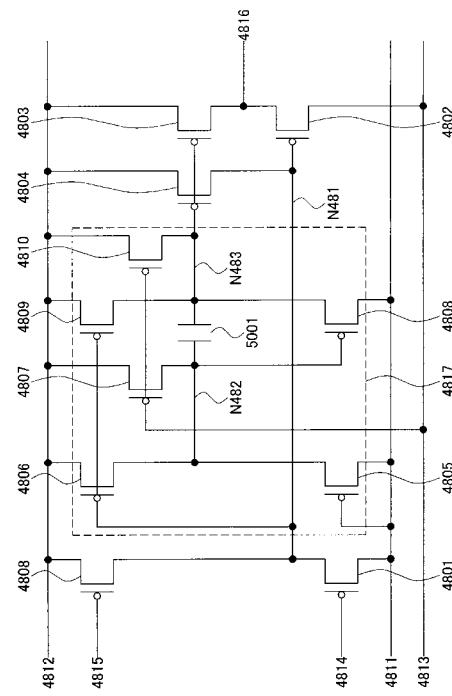

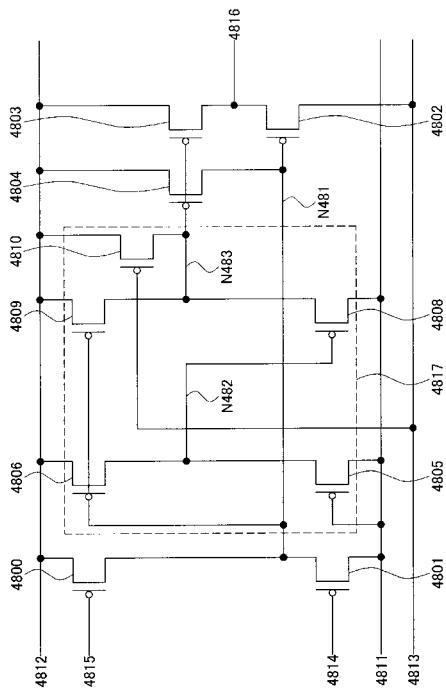

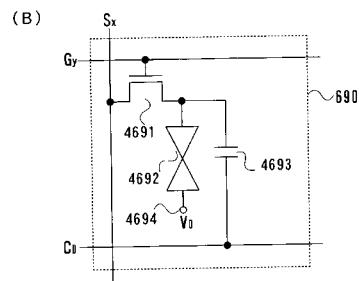

### 【0316】

図 44 は、第 1 の実施の形態で説明した図 13(a) の基本回路を適用したフリップフロップ回路の一例である。図 44 のフリップフロップ回路は、トランジスタ 4401、トランジスタ 4402、トランジスタ 4403、トランジスタ 4404、トランジスタ 4405、トランジスタ 4406、トランジスタ 4407、及びトランジスタ 4408 を有している。

### 【0317】

なお、トランジスタ 4405 が図 13(a) のトランジスタ 1301、トランジスタ 4407 が図 13(a) のトランジスタ 1302、トランジスタ 4406 が図 13(a) のトランジスタ 1303 に、それぞれ相当する。また、トランジスタ 4403、及びトランジスタ 4404 が図 13(a) のトランジスタ 1304 に相当する。

### 【0318】

図 44 のフリップフロップ回路の接続関係について説明する。なお、トランジスタ 4401 の第 2 端子とトランジスタ 4408 の第 2 端子とトランジスタ 4406 のゲートとトランジスタ 4404 の第 2 端子とトランジスタ 4402 のゲートとの節点を節点 N441 とする。また、トランジスタ 4405 の第 2 端子とトランジスタ 4406 の第 2 端子とトランジスタ 4407 の第 2 端子とトランジスタ 4403 のゲートとトランジスタ 4404 のゲートとの節点を節点 N442 とする。

### 【0319】

トランジスタ 4401 のゲートが配線 4412 に接続され、第 1 端子が配線 4409 に接続され、第 2 端子が節点 N441 に接続されている。トランジスタ 4408 のゲートが配線 4413 に接続され、第 1 端子が配線 4410 に接続され、第 2 端子が節点 N441 に接続されている。トランジスタ 4405 のゲートが配線 4409 に接続され、第 1 端子が配線 4409 に接続され、第 2 端子が節点 N442 に接続されている。トランジスタ 4407 のゲートが配線 4411 に接続され、第 1 端子が配線 4410 に接続され、第 2 端子が節点 N442 に接続されている。トランジスタ 4404 のゲートが節点 N442 に接続され、第 1 端子が配線 4410 に接続され、第 2 端子が配線 4410 に接続される。

トランジスタ 4404 のゲートが節点 N442 に接続され、第 1 端子が配線 4410 に接続され、第 2 端子が配線 4410 に接続される。

10

20

30

40

50

続され、第2端子が節点N441に接続されている。トランジスタ4403のゲートが節点N442に接続され、第1端子が配線4410に接続され、第2端子が配線4414に接続されている。トランジスタ4402のゲートが節点N441に接続され、第1端子が配線4411に接続され、第2端子が配線4414に接続されている。

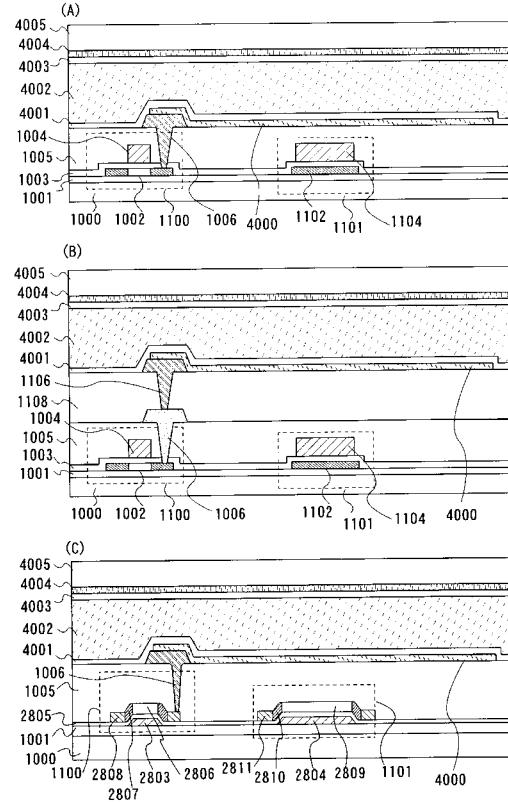

## 【0320】

また、トランジスタ4401～トランジスタ4408は、それぞれPチャネル型である。

## 【0321】

したがって、図44のフリップフロップ回路はすべてPチャネル型のトランジスタで構成することができるため、Nチャネル型のトランジスタを形成するための工程が必要ない。

したがって、図44のフリップフロップ回路は、製造工程の簡略化を図ることができ、製造コストの削減や歩留まりの向上を図ることができる。

10

## 【0322】

また、配線4410には電源電位VDDが供給され、配線4409には電源電位VSSが供給されている。なお、電源電位VDDは、電源電位VSSよりも高い電位である。ただし、配線4409、及び配線4410には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

## 【0323】

また、配線4411、配線4412、及び配線4413には、それぞれ信号が供給されている。なお、配線4411、配線4412、及び配線4413に供給されている信号は、それぞれ2値の値を持つデジタル信号である。ただし、配線4411、配線4412、及び配線4413には、それぞれ電源電位VDD、電源電位VSS、又は他の電源電位が供給されていてもよい。また、配線4411、配線4412、及び配線4413には、それぞれアナログ信号が供給されていてもよい。

20

## 【0324】

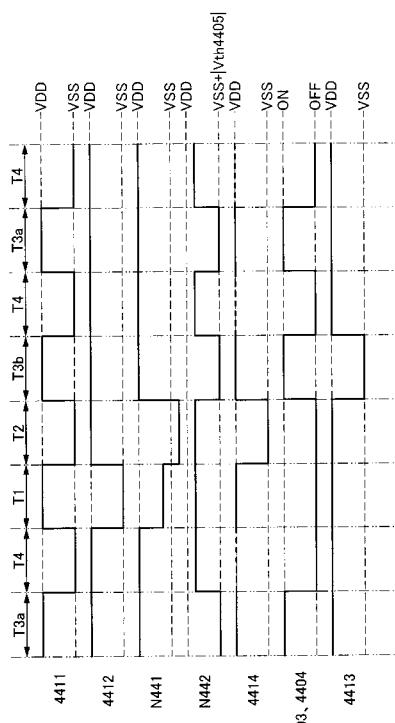

次に、図44に示したフリップフロップ回路の動作について、図45を参照して説明する。

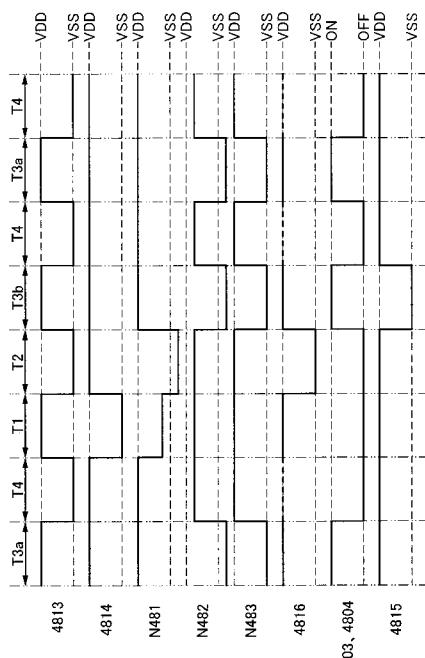

## 【0325】

図45は、図44に示したフリップフロップ回路のタイミングチャートの一例である。図45のタイミングチャートは、配線4411の電位、配線4412の電位、節点N441の電位、節点N442の電位、配線4414の電位、トランジスタ4403、及びトランジスタ4404のオン、オフの関係、配線4413の電位を示している。

30

## 【0326】

図44のタイミングチャートを期間T1～期間T4に分割して説明する。また、期間T3は、期間T3aと期間T3bとに分割して説明する。

## 【0327】

なお、期間T1、期間T2、期間T3b以外の期間は、期間T3aと期間T4とを順に繰り返している。

## 【0328】

まず、期間T1の動作について説明する。期間T1では、配線4411にH信号が供給され、配線4412にL信号が供給され、配線4413にH信号が供給されている。

40

## 【0329】

したがって、トランジスタ4401がオンになり、トランジスタ4408がオフになり、トランジスタ4407がオフになる。このとき、節点N441にトランジスタ4401を通して電源電位VSSが供給され、節点N441の電位が減少する。また、トランジスタ4406が節点N441の電位の減少によってオンして、節点N442の電位が上昇する。また、トランジスタ4403、及びトランジスタ4404が節点N442の電位の上昇によってオフする。

## 【0330】

ここで、節点N441の電位の減少は、トランジスタ4401がオフするまで続く。トランジスタ4401は、節点N441の電位が電源電位VSSとトランジスタ4401のし

50

きい値電圧  $V_{th4401}$  の絶対値との和 ( $V_{SS} + |V_{th4401}|$ ) になるとオフする。したがって、節点 N441 の電位は、 $V_{SS} + |V_{th4401}|$  となる。また、節点 N441 は、フローティング状態となる。

### 【0331】

したがって、トランジスタ 4402 がオンする。また、配線 4414 には、配線 4411 の H 信号が供給されるため、配線 4414 の電位は電源電位 VDD と等しい値となる。

### 【0332】

続いて、期間 T2 の動作について説明する。期間 T2 では、配線 4411 に L 信号が供給され、配線 4412 に H 信号が供給され、配線 4413 に H 信号が供給されている。

### 【0333】

したがって、トランジスタ 4401 がオフになり、トランジスタ 4408 がオフのままであり、トランジスタ 4407 がオンになる。このとき、節点 N441 はフローティング状態であり、節点 N441 の電位は  $V_{SS} + |V_{th4401}|$  を維持している。また、節点 N442 の電位は、トランジスタ 4406、及びトランジスタ 4407 がオンしているため、H レベルのままである。よって、節点 N442 が H レベルであるため、トランジスタ 4403、及びトランジスタ 4404 がオフのままである。

### 【0334】

ここで、節点 N441 はフローティング状態であり、L レベルを維持している。また、トランジスタ 4402 は節点 N441 が L レベルを維持しているため、オンのままである。また、配線 4414 には配線 4411 の L 信号が供給されるため、配線 4414 の電位が減少している。したがって、ブートストラップ動作によって、節点 N441 の電位は電源電位 VSS からトランジスタ 4402 のしきい値電圧  $V_{th4402}$  の絶対値を引いた値 ( $V_{SS} - |V_{th4402}|$ ) 以下になり、配線 4414 の電位は電源電位 VSS と等しい値になる。

### 【0335】

続いて、期間 T3b の動作について説明する。期間 T3b では、配線 4411 に H 信号が供給され、配線 4412 に H 信号が供給され、配線 4413 に L 信号が供給されている。

### 【0336】

したがって、トランジスタ 4401 がオフのままであり、トランジスタ 4408 がオンになり、トランジスタ 4407 がオフになる。このとき、節点 N441 にトランジスタ 4408 を介して電源電位 VDD が供給され、節点 N441 の電位が上昇する。また、トランジスタ 4406 が節点 N441 の電位の上昇によってオフして、節点 N442 の電位が減少する。また、トランジスタ 4403、及びトランジスタ 4404 が節点 N442 の電位の減少によってオンする。

### 【0337】

また、トランジスタ 4402 は節点 N441 の電位の上昇によってオフする。したがって、配線 4414 には、トランジスタ 4403 を介して電源電位 VDD が供給されるため、配線 4414 の電位は電源電位 VDD と等しい値になる。

### 【0338】

続いて、期間 T4 の動作について説明する。期間 T4 では、配線 4411 に L 信号が供給され、配線 4412 に H 信号が供給され、配線 4413 に H 信号が供給されている。

### 【0339】

したがって、トランジスタ 4401 がオフのままであり、トランジスタ 4408 がオフになり、トランジスタ 4407 がオンになる。このとき、節点 N441 はフローティング状態になり、節点 N441 の電位は電源電位 VDD を維持する。したがって、トランジスタ 4406、及びトランジスタ 4402 がオフする。また、節点 N442 の電位はトランジスタ 4407 を介して電源電位 VDD が供給されるため、H レベルになる。したがって、トランジスタ 4403、及びトランジスタ 4404 がオフする。

### 【0340】

したがって、配線 4414 はフローティング状態になり、配線 4414 の電位は電源電位

10

20

30

40

50

VDDと等しい値を維持する。

【0341】

続いて、期間T3aの動作について説明する。期間T3aでは、配線4411にH信号供給され、配線4412にH信号が供給され、配線4413にH信号が供給されている。

【0342】

したがって、トランジスタ4401がオフのままであり、トランジスタ4408がオフのままであり、トランジスタ4407がオフになる。このとき、節点N442の電位はトランジスタ4407がオフするため減少する。したがって、トランジスタ4403、及びトランジスタ4404がオンする。また、節点N441にトランジスタ4404を介して電源電位VDDが供給され、節点N441の電位は電源電位VDDと等しい値になる。したがって、トランジスタ4402、及びトランジスタ4406はオフのままである。

10

【0343】

また、配線4414にはトランジスタ4403を介して電源電位VDDが供給され、配線4414の電位は電源電位VDDと等しい値を維持する。

【0344】

以上の動作によって、期間T1では、図44のフリップフロップ回路は、節点N441をLレベルのまま、フローティング状態にする。期間T2では、図44のフリップフロップ回路は、ブートストラップ動作によって、節点N441の電位をVSS - | Vth4402 | 以下にし、配線4414の電位を電源電位VSSと等しい値にできる。

20

【0345】

また、期間T3aにおいて、図44のフリップフロップ回路は、トランジスタ4403、及びトランジスタ4404がオンして、電源電位VDDを配線4414、及び節点N441に供給する。また、期間T4において、図44のフリップフロップ回路は、トランジスタ4403、及びトランジスタ4404をオフする。したがって、図44のフリップフロップ回路は、トランジスタ4403、及びトランジスタ4404が順にオンするため、トランジスタ4403、及びトランジスタ4404の特性劣化を抑制でき、節点N441、及び配線4414の電位を安定して電源電位VDDと等しい値に維持することができる。

【0346】

また、図44のフリップフロップ回路は、期間T1～期間T4すべての期間でオン状態であるトランジスタは有していない。つまり、定常的、又はほぼ定常的にオン状態であるトランジスタは有していない。したがって、図44のフリップ回路は、トランジスタの特性劣化、及び特性劣化によるしきい値電圧のシフトを抑制することができる。

30

【0347】

なお、トランジスタ4401～トランジスタ4408は、トランジスタ2701～トランジスタ2708と同様な機能を有する。

【0348】

なお、トランジスタ4405、トランジスタ4406、及びトランジスタ4407によって、節点N441、及び配線4411を入力端子とし、出力端子を節点N442とする2入力NAND回路4415を構成している。

40

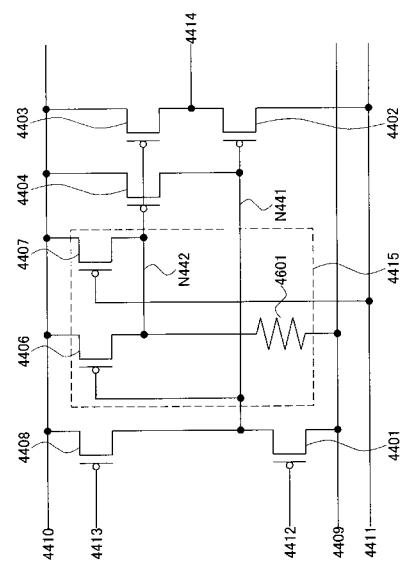

【0349】

なお、トランジスタ4405は、抵抗成分を持つ素子であればよい。例えば、図46に示すように、抵抗素子4601をトランジスタ4405の代わりに用いることができる。抵抗素子4601を用いることによって、節点N442の電位において電源電位VSSと等しい値とすることができる。

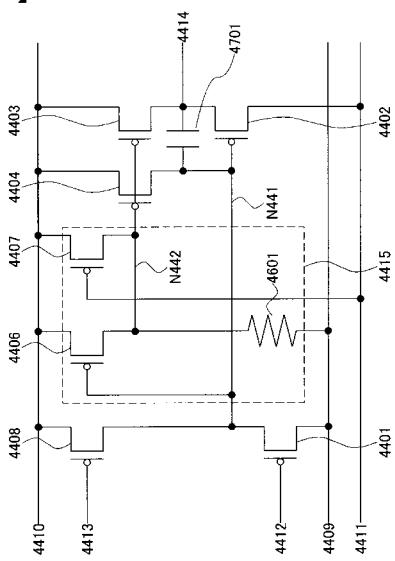

【0350】

なお、図47に示すように、トランジスタ4402のゲート（節点N441）と、第2端子（配線4414）との間に、容量素子4701を配置していくてもよい。なぜなら、期間T2において、節点N441の電位、及び配線4414の電位はブートストラップ動作によって、上昇させるため、容量素子4701を配置することで、フリップフロップ回路がブートストラップ動作しやすくなるからである。

50

## 【0351】

なお、トランジスタ4401は、期間T1において、節点N441をフローティング状態にして、節点N441の電位をLレベルにできればよい。したがって、トランジスタ4401の第1端子を配線4412に接続しても、節点N441をフローティング状態にして、節点N441の電位をLレベルにできる。

## 【0352】

なお、本実施形態は、本明細書中の他の実施形態のいかなる記載とも自由に組み合わせて実施することができる。また、本実施形態中のいかなる記載も自由に組み合わせて実施することができる。

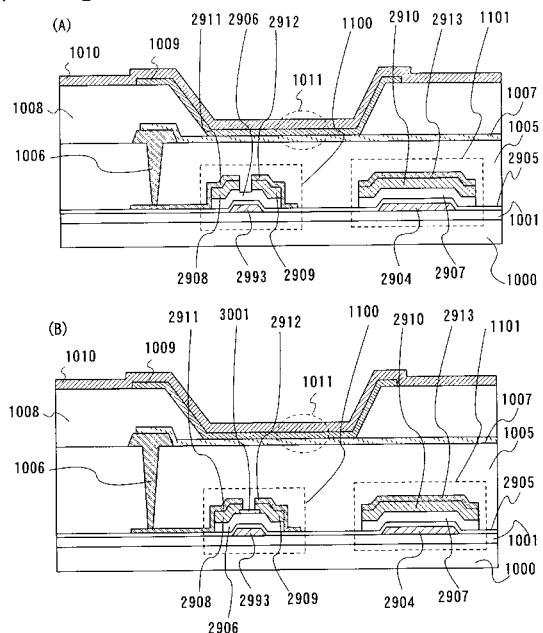

## 【0353】

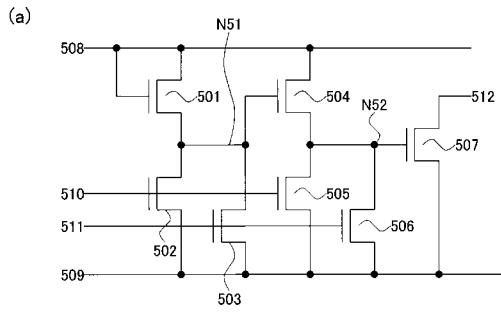

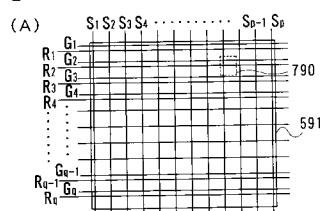

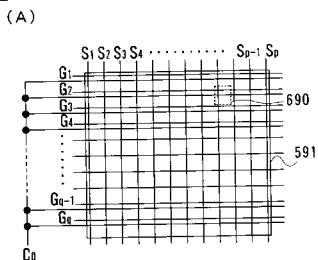

本実施形態では、第2の実施形態で説明した基本回路をフリップフロップ回路に適用した場合について、図36を参照して説明する。

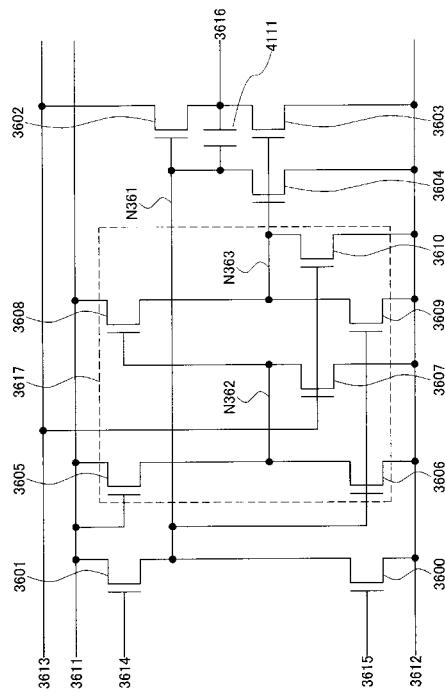

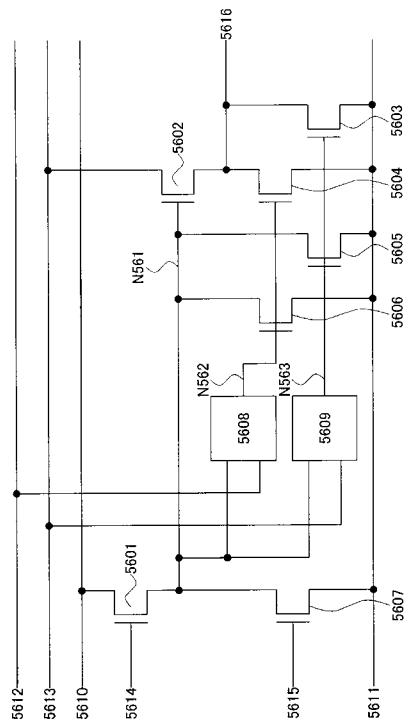

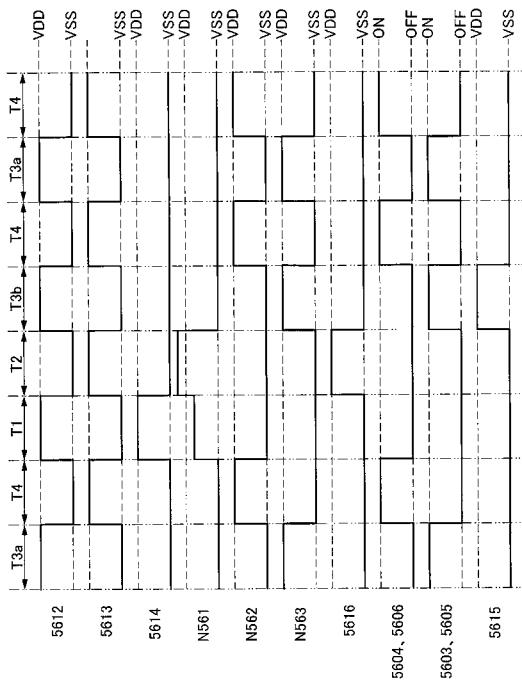

## 【0354】

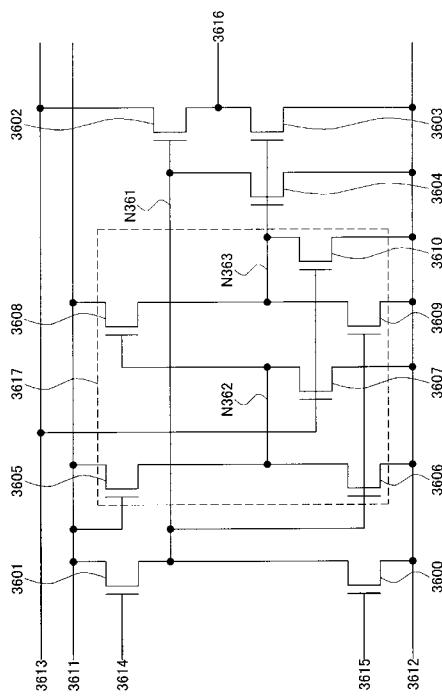

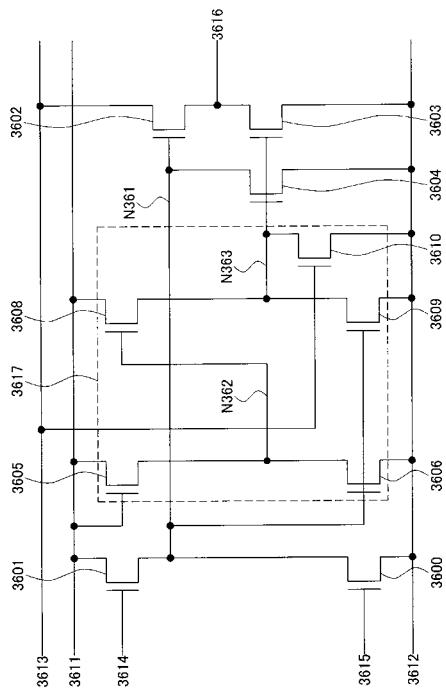

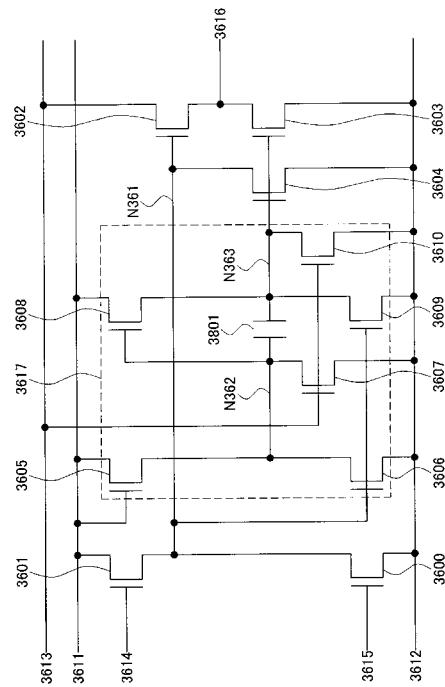

図36は、第2の実施の形態で説明した図5(a)の基本回路を適用したフリップフロップ回路の一例である。図36のフリップフロップ回路は、トランジスタ3600、トランジスタ3601、トランジスタ3602、トランジスタ3603、トランジスタ3604、トランジスタ3605、トランジスタ3606、トランジスタ3607、トランジスタ3608、トランジスタ3609、およびトランジスタ3610を有している。

## 【0355】

なお、トランジスタ3605が図5(a)のトランジスタ501、トランジスタ3607が図5(a)のトランジスタ502、トランジスタ3606が図5(a)のトランジスタ503、トランジスタ3608が図5(a)のトランジスタ504、トランジスタ3610が図5(a)のトランジスタ505、トランジスタ3609が図5(a)のトランジスタ506に、それぞれ相当する。また、トランジスタ3603、及びトランジスタ3604が図5(a)のトランジスタ507に相当する。

## 【0356】

図36のフリップフロップ回路の接続関係について説明する。なお、トランジスタ3601の第2端子とトランジスタ3600の第2端子とトランジスタ3606のゲートとトランジスタ3604の第2端子とトランジスタ3602のゲートとの節点を節点N361とする。また、トランジスタ3605の第2端子とトランジスタ3606の第2端子とトランジスタ3607の第2端子とトランジスタ3608のゲートとの節点を節点N362とする。また、トランジスタ3609の第2端子とトランジスタ3608の第2端子とトランジスタ3610の第2端子とトランジスタ3603のゲートとトランジスタ3604のゲートとの節点を節点N363とする。

## 【0357】

トランジスタ3601のゲートが配線3614に接続され、第1端子が配線3611に接続され、第2端子が節点N361に接続されている。トランジスタ3600のゲートは配線3615に接続され、第1端子が配線3612に接続され、第2端子が節点N361と接続されている。トランジスタ3606のゲートが節点N361に接続され、第1端子が配線3612に接続され、第2端子が節点N362に接続されている。トランジスタ3605のゲートが配線3611に接続され、第1端子が配線3611に接続され、第2端子が節点N362に接続されている。トランジスタ3607のゲートが配線3613に接続され、第1端子が配線3612に接続され、第2端子が節点N362に接続されている。トランジスタ3608のゲートが節点N362に接続され、第1端子が配線3611に接続され、第2端子が節点N363に接続されている。トランジスタ3609のゲートが節点N363に接続され、第1端子が配線3612に接続され、第2端子が節点N363に接続されている。トランジスタ3610のゲートが配線3613に接続され、第1端子が配線3612に接続され、第2端子が節点N363に接続される。

10

20

30

40

50

が節点N361に接続されている。トランジスタ3603のゲートが節点N363に接続され、第1端子が配線3612に接続され、第2端子が配線3616に接続されている。トランジスタ3602のゲートが節点N361に接続され、第1端子が配線3613に接続され、第2端子が配線3616に接続されている。

#### 【0358】

また、トランジスタ3600～トランジスタ3610は、それぞれNチャネル型である。

#### 【0359】

したがって、図36のフリップフロップ回路はすべてNチャネル型のトランジスタで構成することができるため、図36のフリップフロップ回路は、半導体層にアモルファスシリコンを用いることができ、製造工程の簡略化を図ることができる。したがって、製造コストの削減や歩留まりの向上を図ることができる。さらに、大型の表示パネルなどの半導体装置を作製することも可能となる。また、図36のフリップフロップ回路は、半導体層にポリシリコンや単結晶シリコンを用いても製造工程の簡略化を図ることができる。10

#### 【0360】

また、配線3611には電源電位VDDが供給され、配線3612には電源電位VSSが供給されている。なお、電源電位VDDは、電源電位VSSよりも高い電位である。ただし、配線3611、及び配線3612には、デジタル信号、アナログ信号などが供給されていてもよいし、他の電源電位が供給されていてもよい。

#### 【0361】

また、配線3613、配線3614、及び配線3615には、それぞれ信号が供給されている。なお、配線3613、配線3614、及び配線3615に供給されている信号は、それぞれ2値の値を持つデジタル信号である。ただし、配線3613、配線3614、及び配線3615には、それぞれ電源電位VDD、電源電位VSS、又は他の電源電位が供給されていてもよい。また、配線3613、配線3614、及び配線3615には、それぞれアナログ信号が供給されていてもよい。20

#### 【0362】

次に、図36に示したフリップフロップ回路の動作について、図37を参照して説明する。。

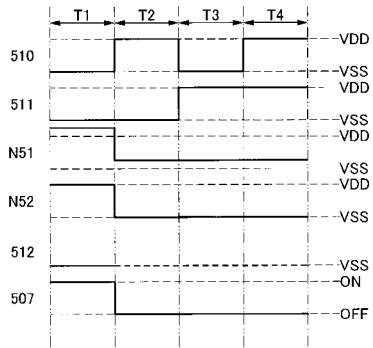

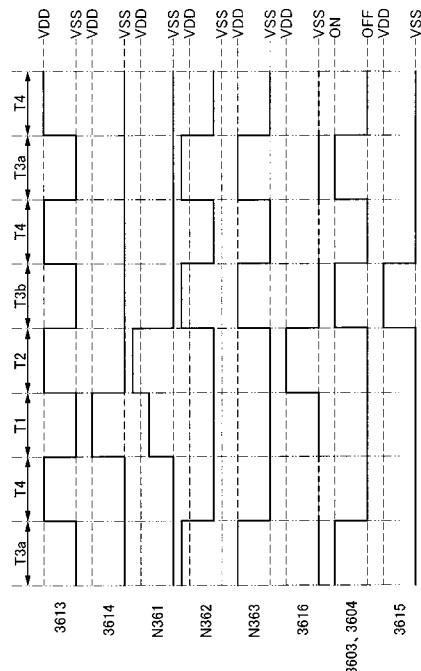

#### 【0363】

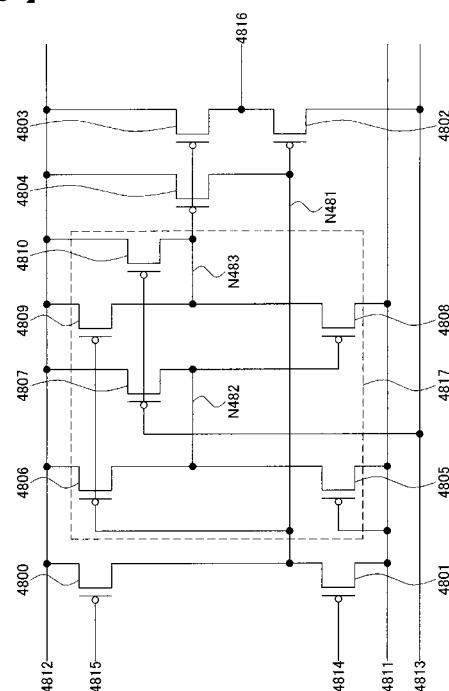

図37は、図36に示したフリップフロップ回路のタイミングチャートの一例である。図37のタイミングチャートは、配線3613の電位、配線3614の電位、節点N361の電位、節点N362の電位、節点N363、配線3616の電位、トランジスタ3603、及びトランジスタ3604のオン、オフの関係、配線3615の電位を示している。30

#### 【0364】

図37のタイミングチャートを期間T1～期間T4に分割して説明する。また、期間T3は、期間T3aと期間T3bとに分割して説明する。

#### 【0365】

なお、期間T1、期間T2、期間T3b以外の期間は、期間T3aと期間T4とを順に繰り返している。

#### 【0366】

まず、期間T1の動作について説明する。期間T1では、配線3613にL信号が供給され、配線3614にH信号が供給され、配線3615にL信号が供給されている。40

#### 【0367】

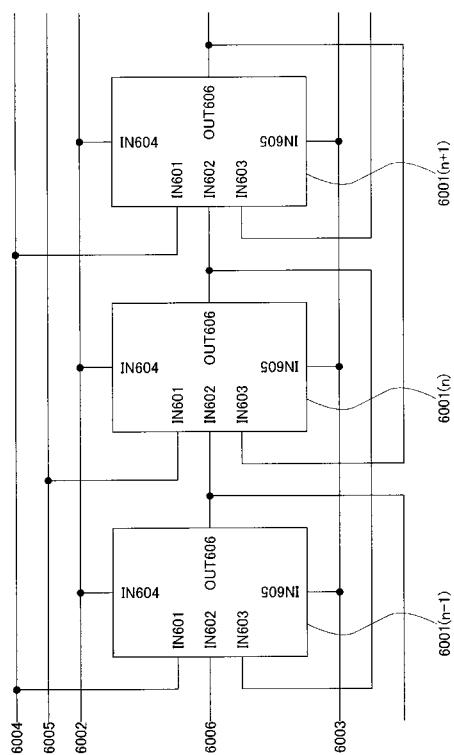

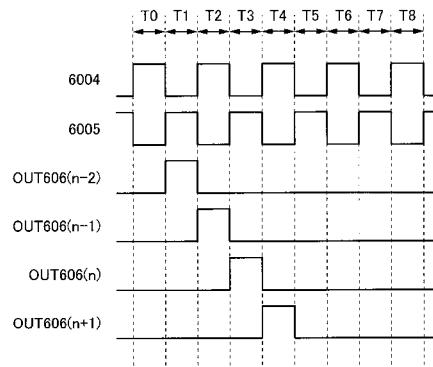

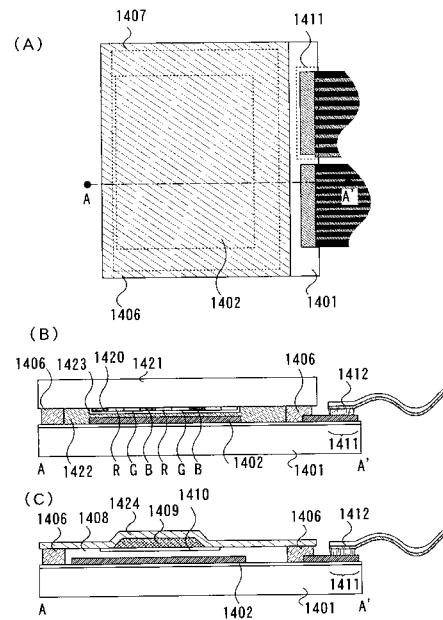

したがって、トランジスタ3601がオンになり、トランジスタ3600がオフになり、トランジスタ3607、及びトランジスタ3610がオフになる。このとき、節点N361にトランジスタ3601を介して電源電位VDDが供給され、節点N361の電位が上昇する。また、トランジスタ3606、及びトランジスタ3609が節点N361の電位の上昇によってオンして、節点N362、及び節点N363の電位が減少する。また、トランジスタ3608が節点N362の電位の減少によってオフする。また、トランジスタ3603、及びトランジスタ3604が節点N363の電位の減少によってオフする。50

**【 0 3 6 8 】**

ここで、節点 N 3 6 1 の電位の上昇は、トランジスタ 3 6 0 1 がオフするまで続く。トランジスタ 3 6 0 1 は、節点 N 3 6 1 の電位が電源電位 V DD からトランジスタ 3 6 0 1 のしきい値電圧  $V_{t h 3 6 0 1}$  を引いた値 ( $V_{DD} - V_{t h 3 6 0 1}$ ) になるとオフする。したがって、節点 N 3 6 1 の電位は、 $V_{DD} - V_{t h 3 6 0 1}$  となる。また、節点 N 3 6 1 はフローティング状態となる。

**【 0 3 6 9 】**

したがって、トランジスタ 3 6 0 2 がオンする。また、配線 3 6 1 6 には、配線 3 6 1 3 の L 信号が供給されているため、配線 3 6 1 6 の電位は電源電位 V SS と等しい値となる。

10

**【 0 3 7 0 】**

続いて、期間 T 2 の動作について説明する。期間 T 2 では、配線 3 6 1 3 に H 信号が供給され、配線 3 6 1 4 に L 信号が供給され、配線 3 6 1 5 に L 信号が供給されている。

**【 0 3 7 1 】**