(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-352455

(P2005-352455A)

(43) 公開日 平成17年12月22日(2005.12.22)

(51) Int.Cl.<sup>7</sup>G02F 1/133

G02F 1/1368

F 1

G02F 1/133 550

G02F 1/1368

テーマコード(参考)

2H092

2H093

審査請求 未請求 請求項の数 15 O L (全 27 頁)

(21) 出願番号 特願2005-124233 (P2005-124233)

(22) 出願日 平成17年4月21日 (2005.4.21)

(31) 優先権主張番号 10-2004-0042232

(32) 優先日 平成16年6月9日 (2004.6.9)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si

Gyeonggi-do, Republic

of Korea

(74) 代理人 100072349

弁理士 八田 幹雄

(74) 代理人 100110995

弁理士 奈良 泰男

(74) 代理人 100114649

弁理士 宇谷 勝幸

最終頁に続く

(54) 【発明の名称】表示装置用駆動装置及び表示板

(57) 【要約】 (修正有)

【課題】信頼性と設計マージンを確保することができる表示装置を提供する。

【解決手段】本発明は表示装置用駆動装置に関する。駆動部は、制御電極125、制御電極125上に形成されているゲート絶縁膜140、ゲート絶縁膜140上に形成されている半導体層54、半導体層54上に少なくとも一部分形成されている入力電極部72、73、半導体層54上に少なくとも一部分形成されていて制御電極125と重なる出力電極部75、76、79、入力電極部72、73及び出力電極部75、76、79上に形成されている保護膜180、そして保護膜180上に形成されていて制御電極125と連結されており、出力電極部75、76、79と重なる補助電極83を含む。このような方式で、少ない面積でも必要とする静電容量を確保することができる。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

互いに連結されていて、順次に出力信号を各々生成する複数のステージを含む表示装置の駆動装置であって、

前記各ステージは、

入力信号に応答して電圧を充電し、前記電圧の充電によって入力クロック信号に基づいて前記出力信号を生成して出す駆動部と、

後段ステージのうちのいずれか一つの出力信号に応答して前記駆動部に充電された電圧を放電する放電部とを含み、

前記入力信号は走査開始信号または前段ステージのうちのいずれか一つの出力信号であり、10

前記駆動部は、

制御電極と、

前記制御電極上に形成されている第1絶縁膜と、

前記第1絶縁膜上に形成されている半導体層と、

前記半導体層上に少なくとも一部分形成されている入力電極部と、

前記半導体層上に少なくとも一部分形成されていて、前記制御電極と重なる出力電極部と、20

前記入力電極部及び出力電極部上に形成されている第2絶縁膜と、

前記第2絶縁膜上に形成されていて前記制御電極と連結されており、前記出力電極部と重なる補助電極とを含む表示装置用駆動装置。20

**【請求項 2】**

前記入力電極部と前記出力電極部はくし型で交互に配列された複数の分枝を含み、

前記出力電極部は前記分枝が連結されて、前記制御電極及び前記補助電極と重なる拡張部をさらに含む、請求項1に記載の表示装置用駆動装置。

**【請求項 3】**

前記第1及び第2絶縁膜は前記制御電極を一部露出する接触孔を含み、

前記補助電極は前記接触孔を通じて前記制御電極と連結されている、請求項2に記載の表示装置用駆動装置。

**【請求項 4】**

前記補助電極は透明導電体を含んで成る、請求項3に記載の表示装置用駆動装置。30

**【請求項 5】**

前記補助電極はITOまたはIZOからなる、請求項4に記載の表示装置用駆動装置。

**【請求項 6】**

前記制御電極と前記出力電極部との間の静電容量が前記制御電極と前記入力電極部との間の静電容量より大きい、請求項5に記載の表示装置用駆動装置。

**【請求項 7】**

前記半導体層は非晶質シリコンからなる、請求項1に記載の表示装置用駆動装置。

**【請求項 8】**

前記駆動部は前記表示装置に集積されている、請求項7に記載の表示装置用駆動装置。40

**【請求項 9】**

基板と、

前記基板上に形成されていて、複数の第1制御電極を含むゲート線と、

前記基板上に形成されていて、前記ゲート線と分離されている第2制御電極と、

前記ゲート線及び前記第2制御電極上に形成されている第1絶縁膜と、

前記第1絶縁膜上に形成されていて、前記第1及び第2制御電極上に各々位置する第1及び第2半導体と、40

前記第1絶縁膜上に形成されていて、前記第1半導体と少なくとも一部分接する複数の第1入力電極部を含む複数のデータ線と、

前記第1半導体と少なくとも一部分接していて、前記データ線と分離されている複数の50

第1出力電極部と、

前記第2半導体と少なくとも一部分接する第2入力電極部と、

前記第2半導体と少なくとも一部分接していて、前記第2入力電極部と分離されており、前記第2制御電極と重なって、前記ゲート線と電気的に連結されている第2出力電極部と、

前記データ線、前記第2入力電極部、前記第1及び第2出力電極部上に形成されている第2絶縁膜と、

前記第2絶縁膜上に形成されていて、前記第1出力電極部と連結されている複数の画素電極と、

前記第2絶縁膜上に形成されていて、前記第2制御電極と連結されており、前記第2出力電極部と重なる補助電極とを含む表示装置用表示板。 10

**【請求項10】**

前記第2入力電極部と前記第2出力電極部はくし型で交互に配列された複数の分枝を含み、

前記第2出力電極部は前記分枝が連結され、前記第2制御電極及び前記補助電極と重なる拡張部をさらに含む、請求項9に記載の表示装置用表示板。 20

**【請求項11】**

前記第1及び第2絶縁膜は前記第2制御電極を一部露出する接触孔を含み、

前記補助電極は前記接触孔を通じて前記第2制御電極と連結されている、請求項10に記載の表示装置用表示板。 20

**【請求項12】**

前記補助電極は透明導電体からなる、請求項11に記載の表示装置用表示板。

**【請求項13】**

前記補助電極はITOまたはIZOからなる、請求項12に記載の表示装置用表示板。

**【請求項14】**

前記第2制御電極と前記第2出力電極部との間の静電容量が前記第2制御電極と前記第2入力電極部との間の静電容量より大きい、請求項13に記載の表示装置用表示板。 30

**【請求項15】**

前記半導体層は非晶質シリコンからなる、請求項9に記載の表示装置用表示板。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、表示装置に関する。

**【背景技術】**

**【0002】**

最近、重くて大きい陰極線管(CRT)の代わりに有機発光表示装置(OLED)、プラズマ表示装置(PDP)、液晶表示装置(LCD)のような平板表示装置が活発に開発されている。 40

**【0003】**

PDPは気体放電によって発生するプラズマを利用して文字や映像を表示する装置であり、OLEDは特定有機物または高分子の電界発光を利用して文字または映像を表示する。液晶表示装置は二つの表示板の間に入っている液晶層に電場を印加して、この電場の強さを調節して液晶層を通過する光の透過率を調節することによって所望の画像を得る。

**【0004】**

このような平板表示装置の中で、例えば液晶表示装置と有機EL表示装置はスイッチング素子を含む画素と表示信号線が備えられた表示板、そして表示信号線のうちのゲート線にゲート信号を出力して画素のスイッチング素子を導通/遮断するゲート駆動部、つまり、シフトレジスターを含む。

**【0005】**

シフトレジスターは互いに連結されている複数のステージを含み、各ステージは複数の 50

トランジスタを含む。

【0006】

各ステージは入力部、出力部、放電部などを含み、前段及び後段ステージの出力に基づいて複数のクロック信号のうちのいずれか一つに同期して出力を出す。

【0007】

このようなステージの出力部はゲート線及び他のステージに各々連結されている複数のトランジスタを含む。この中でゲート出力を出すトランジスタはステージ全面積の約40%乃至50%を占める。このような出力トランジスタは、ゲート線に出る出力及び前段ステージに出る出力を確保するために、他のトランジスタに比べて相対的に大きく作るためである。この時、例えば、N M O Sトランジスタの場合、ゲートドレイン間静電容量よりゲートソース間静電容量を大きく作るが、これはゲート出力をリップルなく円滑に生成することができるためである。したがって、ゲートソース間静電容量を増大させるためにゲートとソースが重なる面積を大きくすれば、出力トランジスタはステージ内で占める面積がさらに大きくなる。これによってゲート駆動部を設計して集積するのに設計マージンが不足する場合がある。また、重なる領域が広くなることによってゲートとソースが短絡される確率が高まってゲート出力を発生させない場合も生じる。

【0008】

特に、表示領域を囲む黒色層領域の小さいノートブック用表示板部には上部表示板と下部表示板を接合するための密封材工程で密封材を塗るための空間が不足することもある。

【発明の開示】

【発明が解決しようとする課題】

【0009】

したがって、本発明が目的とする技術的課題は、従来技術の問題点を解決することができて、信頼性と設計マージンを確保することができる表示装置を提供することにある。

【課題を解決するための手段】

【0010】

このような技術的課題を構成するための本発明の一つの実施例による表示装置の駆動装置は、互いに連結されていて、順次に出力信号を各々生成する複数のステージを含み、前記各ステージは、入力信号に応答して電圧を充電し、前記電圧の充電によって入力クロック信号に基づいて前記出力信号を生成して出す駆動部と、後段ステージのうちのいずれか一つの出力信号に応答して前記駆動部に充電された電圧を放電する放電部を含み、前記入力信号は走査開始信号または前段ステージのうちのいずれか一つの出力信号であり、前記駆動部は、制御電極と、前記制御電極上に形成されている第1絶縁膜と、前記第1絶縁膜上に形成されている半導体層と、前記半導体層上に少なくとも一部分形成されている入力電極部と、前記半導体層上に少なくとも一部分形成されていて、前記制御電極と重なる出力電極部と、前記入力電極部及び出力電極部上に形成されている第2絶縁膜と、前記第2絶縁膜上に形成されていて、前記制御電極と連結されており、前記出力電極部と重なる補助電極とを含む。

【0011】

この時、前記入力電極部と前記出力電極部はくし型で交互に配列された複数の分枝を含み、前記出力電極部は前記分枝が連結され、前記制御電極及び前記補助電極と重なる拡張部をさらに含むのが好ましい。

【0012】

また、前記第1及び第2絶縁膜は前記制御電極を一部露出する接触孔を含み、前記補助電極は前記接触孔を通じて前記制御電極と連結されているのが好ましい。この時、前記補助電極は透明導電体からなることができ、特にITOまたはIZOからなるのが好ましい。

【0013】

前記制御電極と前記出力電極部との間の静電容量が前記制御電極と前記入力電極部との間の静電容量より大きいのが好ましい。

10

20

30

40

50

**【 0 0 1 4 】**

一方、前記半導体層は非晶質シリコンからなることができ、前記駆動部は前記表示装置に集積されていることもある。

**【 0 0 1 5 】**

本発明の一つの特徴による表示装置用表示板は基板と、前記基板上に形成されていて複数の第1制御電極を含むゲート線と、前記基板上に形成されていて前記ゲート線と分離されている第2制御電極と、前記ゲート線及び前記第2制御電極上に形成されている第1絶縁膜と、前記第1絶縁膜上に形成されていて前記第1及び第2制御電極上に各々位置する第1及び第2半導体と、前記第1絶縁膜上に形成されていて前記第1半導体と少なくとも一部分接する複数の第1入力電極部を含む複数のデータ線と、前記第1半導体と少なくとも一部分接していて、前記データ線と分離されている複数の第1出力電極部と、前記第2半導体と少なくとも一部分接する第2入力電極部と、前記第2半導体と少なくとも一部分接していて、前記第2入力電極部と分離されており、前記第2制御電極と重なって、前記ゲート線と電気的に連結されている第2出力電極部と、前記データ線と、前記第2入力電極部と、前記第1及び第2出力電極部上に形成されている第2絶縁膜と、前記第2絶縁膜上に形成されていて、前記第1出力電極部と連結されている複数の画素電極と、前記第2絶縁膜上に形成されていて、前記第2制御電極と連結されており、前記第2出力電極部と重なる補助電極とを含む。

**【 0 0 1 6 】**

この時、前記第2入力電極部と前記第2出力電極部はくし型で交互に配列された複数の分枝を含み、前記第2出力電極部は前記分枝が連結されて、前記第2制御電極及び前記補助電極と重なる拡張部をさらに含むのが好ましい。また、前記第1及び第2絶縁膜は前記第2制御電極を一部露出する接触孔を含み、前記補助電極は前記接触孔を通じて前記第2制御電極と連結されるのが好ましい。

**【 0 0 1 7 】**

一方、前記補助電極は透明導電体からなることができ、特にITOまたはIZOからなるのが好ましい。

**【 0 0 1 8 】**

また、前記第2制御電極と前記第2出力電極部との間の静電容量が前記第2制御電極と前記第2入力電極部との間の静電容量より大きいのが好ましい。

**【 0 0 1 9 】**

一方、前記半導体層は非晶質シリコンからなることができる。

**【 発明の効果 】****【 0 0 2 0 】**

ステージの全面積のうちの約40乃至50%を占めるトランジスタの大きさを減らすことによって、ステージ一つが占める面積を同時に減らすことができる。その結果、ゲートとソースが短絡する危険を防止することができるので信頼度の高いゲート駆動部を提供し、さらにトランジスタを配置する時にも余裕をもって設計することができる。

**【 発明を実施するための最良の形態 】****【 0 0 2 1 】**

添付した図面を参照して本発明の実施例について本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。

**【 0 0 2 2 】**

なお、図面において、多様な層及び領域を明確に表現するために、厚さを誇張して示している。また、明細書全体にわたって類似する部分については同一図面符号を付けている。層、膜、領域、板などの部分が他の部分の“上”にあるとする時、これは他の部分の“すぐ上”にある場合だけでなく、その中間に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上”にあるとする時には中間に他の部分がないことを意味する。

**【 0 0 2 3 】**

以下では本発明の実施例による表示装置について添付した図面を参照して詳細に説明す

る。

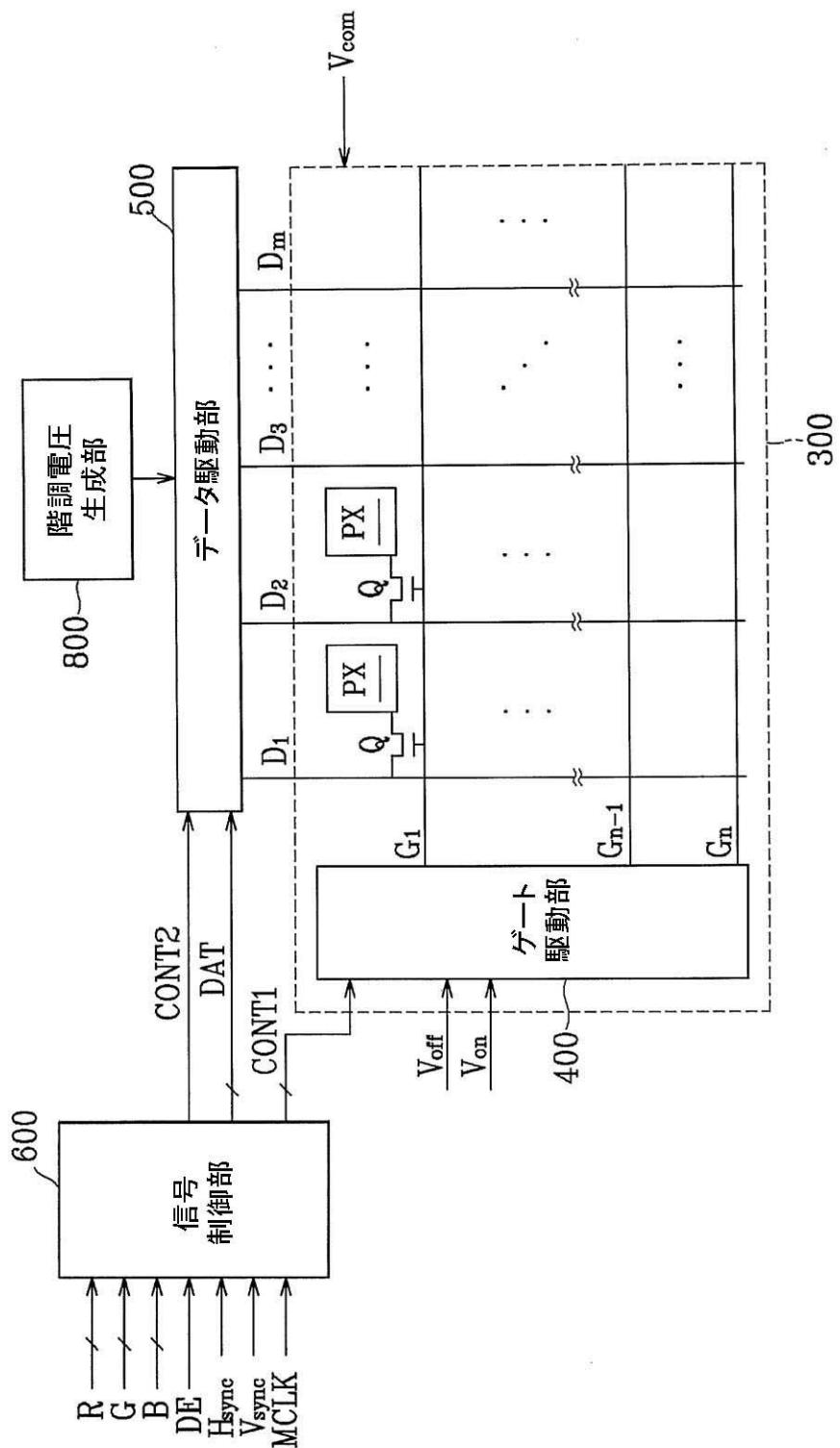

【0024】

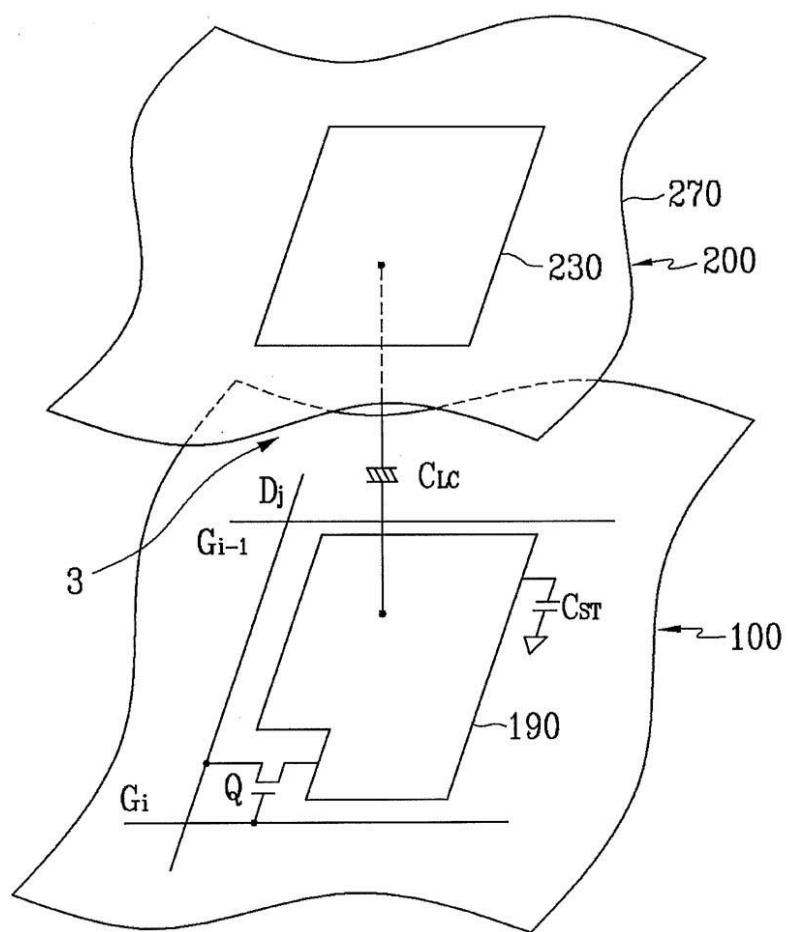

図1は本発明の一つの実施例による表示装置のブロック図であり、図2は本発明の一つの実施例による液晶表示装置の一つの画素に対する等価回路図である。

【0025】

図1に示すように、本発明の一つの実施例による表示装置は表示板部300と、これに連結されたゲート駆動部400と、データ駆動部500、データ駆動部500に連結された階調電圧生成部800と、これらを制御する信号制御部600とを含む。

【0026】

表示板部300は等価回路で見る時、複数の表示信号線 $G_1 - G_n$ 、 $D_1 - D_m$ と、これに連結されていてほぼ行列形態で配列された複数の画素 $P_x$ を含む。 10

【0027】

表示信号線 $G_1 - G_n$ 、 $D_1 - D_m$ は、ゲート信号（走査信号とも言う）を伝達する複数のゲート線 $G_1 - G_n$ とデータ信号を伝達するデータ線 $D_1 - D_m$ を含む。ゲート線 $G_1 - G_n$ はほぼ行方向に伸びていて互いにがほとんど平行しており、データ線 $D_1 - D_m$ はほぼ列方向に伸びていて互いにがほとんど平行している。

【0028】

各画素 $P_x$ は表示信号線 $G_1 - G_n$ 、 $D_1 - D_m$ に連結されたスイッチング素子Qと、これに連結された画素回路を含む。 20

【0029】

スイッチング素子Qは三端子素子で、その制御端子及び入力端子は各々ゲート線 $G_1 - G_n$ 及びデータ線 $D_1 - D_m$ に連結されており、出力端子は画素回路に連結されている。また、スイッチング素子Qは薄膜トランジスタであるのが好ましく、特に非晶質シリコンを含むのが良い。

【0030】

平板表示装置の代表格である液晶表示装置の場合、図2に示すように表示板部300が下部表示板100と上部表示板200及びその間の液晶層3を含み、表示信号線 $G_1 - G_n$ 、 $D_1 - D_m$ とスイッチング素子Qは下部表示板100に備えられている。液晶表示装置の画素回路はスイッチング素子Qに並列に連結された液晶キャパシタ $C_{Lc}$ 及びストレージキャパシタ $C_{ST}$ を含む。ストレージキャパシタ $C_{ST}$ は必要に応じて省略することができる。 30

【0031】

液晶キャパシタ $C_{Lc}$ は下部表示板100の画素電極190と上部表示板200の共通電極270を二つの端子とし、二つの電極190、270の間の液晶層3は誘電体として機能する。画素電極190はスイッチング素子Qに連結され、共通電極270は上部表示板200の全面に形成されていて共通電圧 $V_{com}$ の印加を受ける。図2とは異なって共通電極270が下部表示板100に備えられる場合もあり、この時には二つの電極190、270とも線状または棒状で作られる。

【0032】

ストレージキャパシタ $C_{ST}$ は下部表示板100に供えられた別個の信号線（図示せず）と画素電極190が重なって構成され、この別個の信号線には共通電圧 $V_{com}$ などの決められた電圧が印加される。しかし、ストレージキャパシタ $C_{ST}$ は画素電極190が絶縁体を媒介として直上の前段ゲート線と重なって構成することができる。 40

【0033】

一方、色表示を実現するためには各画素が色相を表示するようにしなければならないが、これは画素電極190に対応する領域に三原色、例えば、赤色、緑色または青色の色フィルター230を備えることによって可能である。図2における色フィルター230は上部表示板200に形成されているが、これとは異なって下部表示板100の画素電極190上または下に形成することもできる。

【0034】

20

40

50

液晶表示装置の表示板部 300 の二つの表示板 100、200 のうちの少なくとも一つの外側面には光を偏光させる偏光子（図示せず）が付着されている。

#### 【0035】

再び図 1 を参照すれば、階調電圧生成部 800 は画素の輝度と関する一対または二対の複数階調電圧を生成する。二対がある場合、二対のうちの一対は共通電圧  $V_{c_{0m}}$  に対して正の値を有し、他の一対は負の値を有する。

#### 【0036】

ゲート駆動部 400 は表示板部 300 に集積されており、ゲート線  $G_1 - G_n$  と連結されてスイッチング素子 Q を導通させることができるゲートオン電圧  $V_{on}$  とスイッチング素子 Q を遮断させることができるゲートオフ電圧  $V_{off}$  の組み合わせからなるゲート信号をゲート線  $G_1 - G_n$  に印加する。

10

#### 【0037】

データ駆動部 500 は表示板部 300 のデータ線  $D_1 - D_m$  に連結されて階調電圧生成部 800 からの階調電圧を選択してデータ信号として画素に印加する。

#### 【0038】

信号制御部 600 はゲート駆動部 400 及びデータ駆動部 500 などの動作を制御する。

。

#### 【0039】

次に、このような表示装置の表示動作についてさらに詳しく説明する。

#### 【0040】

信号制御部 600 は外部のグラフィック制御機（図示せず）から入力映像信号 R、G、B 及びその表示を制御する入力制御信号、例えば、垂直同期信号  $V_{sync}$  と水平同期信号  $H_{sync}$ 、メインクロック MCLK、データイネーブル信号 DE などの提供を受ける。信号制御部 600 は入力制御信号及び入力映像信号 R、G、B に基づいてゲート制御信号 CONT1 及びデータ制御信号 CONT2などを生成し、映像信号 R、G、B を表示板部 300 の動作条件に合わせて適切に処理した後、ゲート制御信号 CONT1 をゲート駆動部 400 に出力して、データ制御信号 CONT2 と処理した映像信号 DAT はデータ駆動部 500 に出力する。

20

#### 【0041】

ゲート制御信号 CONT1 はゲートオン電圧  $V_{on}$  の出力開始を指示する走査開始信号 STV、ゲートオン電圧  $V_{on}$  の出力時期を制御するゲートクロック信号 CPV 及びゲートオン電圧  $V_{on}$  の持続時間を限定する出力イネーブル信号 ODEなどを含む。

30

#### 【0042】

データ制御信号 CONT2 は映像データ DAT の入力開始を知らせる水平同期開始信号 STH とデータ線  $D_1 - D_m$  に当該データ電圧を印加することを命令するロード信号 LOAD 及びデータクロック信号 HCLK を含む。図 2 に示した液晶表示装置などの場合、共通電圧  $V_{c_{0m}}$  に対するデータ電圧の極性（以下、「共通電圧に対するデータ電圧の極性」を略して「データ電圧の極性」と言う）を反転させる反転信号 RVS を含むこともできる。

#### 【0043】

データ駆動部 500 は信号制御部 600 からのデータ制御信号 CONT2 によって一つの行の画素に対応する映像データ DAT の入力を順次に受けて、階調電圧生成部 800 からの階調電圧のうちの各映像データ DAT に対応する階調電圧を選択することによって、映像データ DAT を当該データ電圧に変換し、これをデータ線  $D_1 - D_m$  に印加する。

40

#### 【0044】

ゲート駆動部 400 は信号制御部 600 からのゲート制御信号 CONT1 によってゲートオン電圧  $V_{on}$  をゲート線  $G_1 - G_n$  に印加して、このゲート線  $G_1 - G_n$  に連結されたスイッチング素子 Q を導通させる。データ線  $D_1 - D_m$  に供給されたデータ電圧は導通したスイッチング素子 Q を通じて当該画素に印加される。

#### 【0045】

図2に示した液晶表示装置の場合、画素に印加されたデータ電圧と共に通電圧 $V_{c_{\text{on}}}$ の差は液晶キャパシタ $C_{LC}$ の充電電圧、つまり、画素電圧として現れる。液晶分子は画素電圧の大きさによって、その配列を異ならせ、その結果液晶層3を通過する光の偏光が変化する。このような偏光の変化は表示板100、200に付着された偏光子によって光の透過率変化で現れる。

#### 【0046】

1水平周期（または1H”：水平同期信号 $H_{sync}$ 、データタイネーブル信号DE、ゲートクロックCPVの一周期）が終わればデータ駆動部500とゲート駆動部400は次の行の画素に対して同一動作を繰り返す。このような方式で、一つのフレームの間に全てのゲート線 $G_1 - G_n$ に対して順次にゲートオン電圧 $V_{on}$ を印加して全ての画素にデータ電圧を印加する。図2に示した液晶表示装置などの場合、特に一つのフレームが終われば、次のフレームが始まり、各画素に印加されるデータ電圧の極性が直前フレームにおける極性と反対になるようにデータ駆動部500に印加される反転信号RVSの状態が制御される（“フレーム反転”）。この時、一つのフレーム内でも反転信号RVSの特性によって一つのデータ線を通じて流れるデータ電圧の極性が変わったり（コラム反転）、一つの画素行に印加されるデータ電圧の極性も互いに異なることがある（ドット反転）。

#### 【0047】

以下では本発明の実施例による表示装置のゲート駆動部について図3乃至図9を参照してさらに詳しく説明する。

#### 【0048】

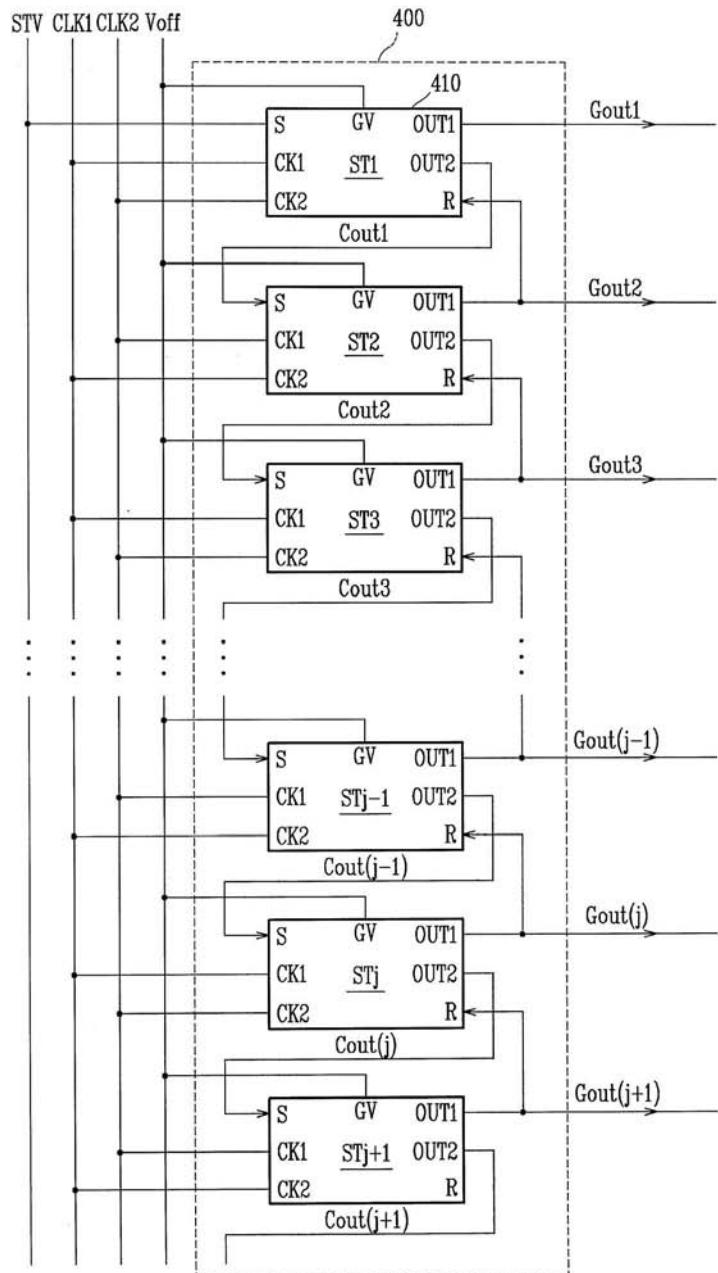

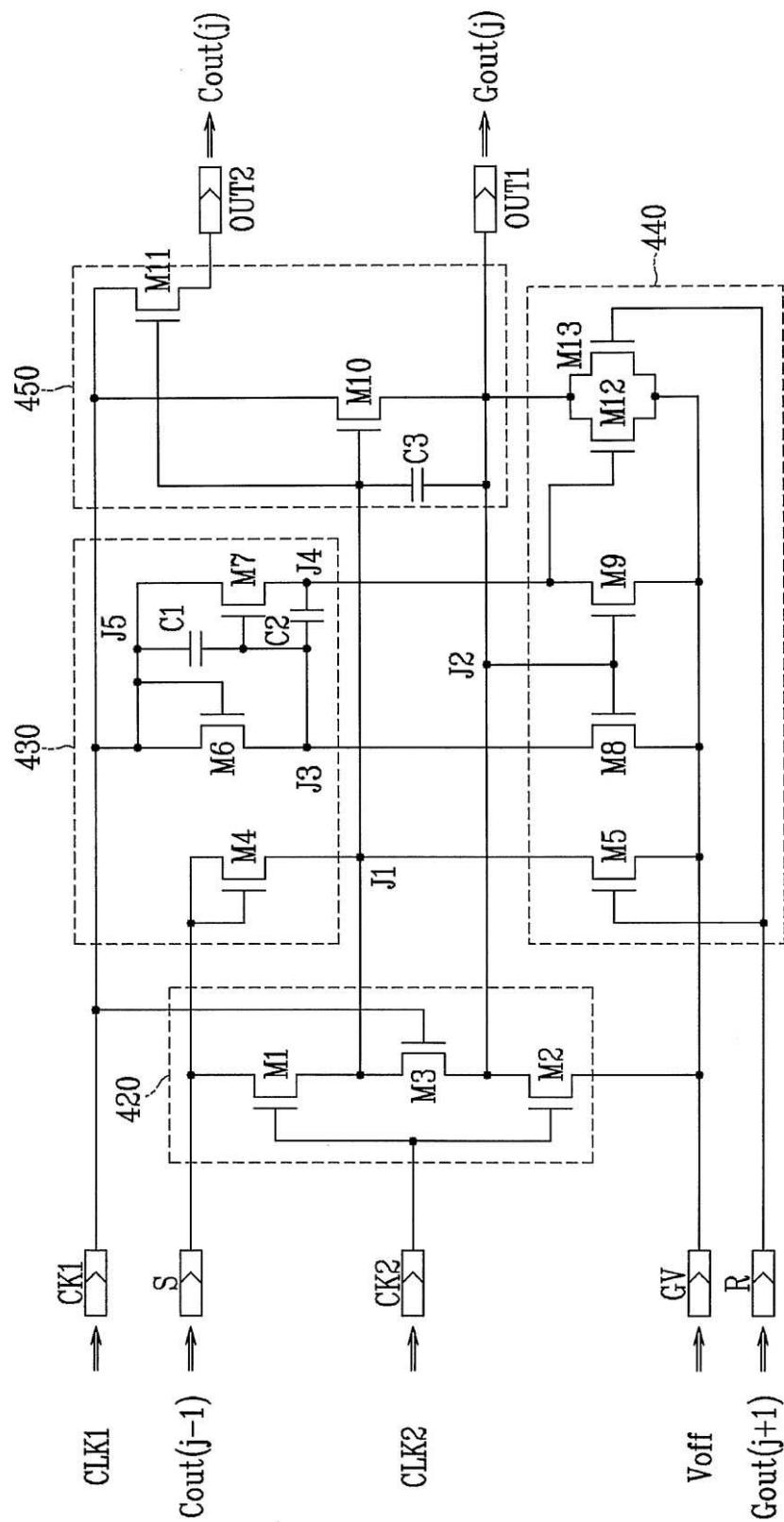

図3は本発明の一つの実施例によるゲート駆動部のブロック図である。図4は図3に示したゲート駆動部用シフトレジスターのj番目ステージの回路図の一例であり、図5は図3に示したゲート駆動部の信号波形図である。

#### 【0049】

図3に示したゲート駆動部400は一列で配列されており、ゲート線 $G_1 - G_n$ に各々連結されている複数のステージ410を含むシフトレジスターであって、走査開始信号STV、複数のクロック信号CLK1、CLK2及びゲートオフ電圧 $V_{off}$ が入力される。

#### 【0050】

各ステージ410はセット端子S、ゲート電圧端子GV、一対のクロック端子CK1、CK2、リセット端子R、そしてゲート出力端子OUT1及びキャリー出力端子OUT2を有している。

#### 【0051】

各ステージ、例えば、j番目ステージ $ST_j$ のセット端子Sには前段ステージ $ST_{j-1}$ のキャリー出力、つまり、前段キャリー出力 $Cout(j-1)$ が、リセット端子Rには後段ステージ $ST_{j+1}$ のゲート出力、つまり、後段ゲート出力 $Gout(j+1)$ が入力され、クロック端子CK1、CK2にはクロック信号CLK1、CLK2が入力され、ゲート電圧端子GVにはゲートオフ電圧 $V_{off}$ が入力される。ゲート出力端子OUT1はゲート出力 $Gout(j)$ を出力し、キャリー出力端子OUT2はキャリー出力 $Cout(j)$ を出力する。

#### 【0052】

但し、シフトレジスター400の第1ステージには前段キャリー出力の代わりに走査開始信号STVが入力される。また、j番目ステージ $ST_j$ のクロック端子CK1にクロック信号CLK1が、クロック端子CK2にクロック信号CLK2が入力される場合、これに隣接した(j-1)番目及び(j+1)番目ステージ $ST_{j-1}$ 、 $ST_{j+1}$ のクロック端子CK1にはクロック信号CLK2が、クロック端子CK2にはクロック信号CLK1が入力される。

#### 【0053】

各クロック信号CLK1、CLK2は画素のスイッチング素子Qを駆動することができるよう電圧レベルがハイである場合はゲートオン電圧 $V_{on}$ と同一であり、ローである

10

20

30

40

50

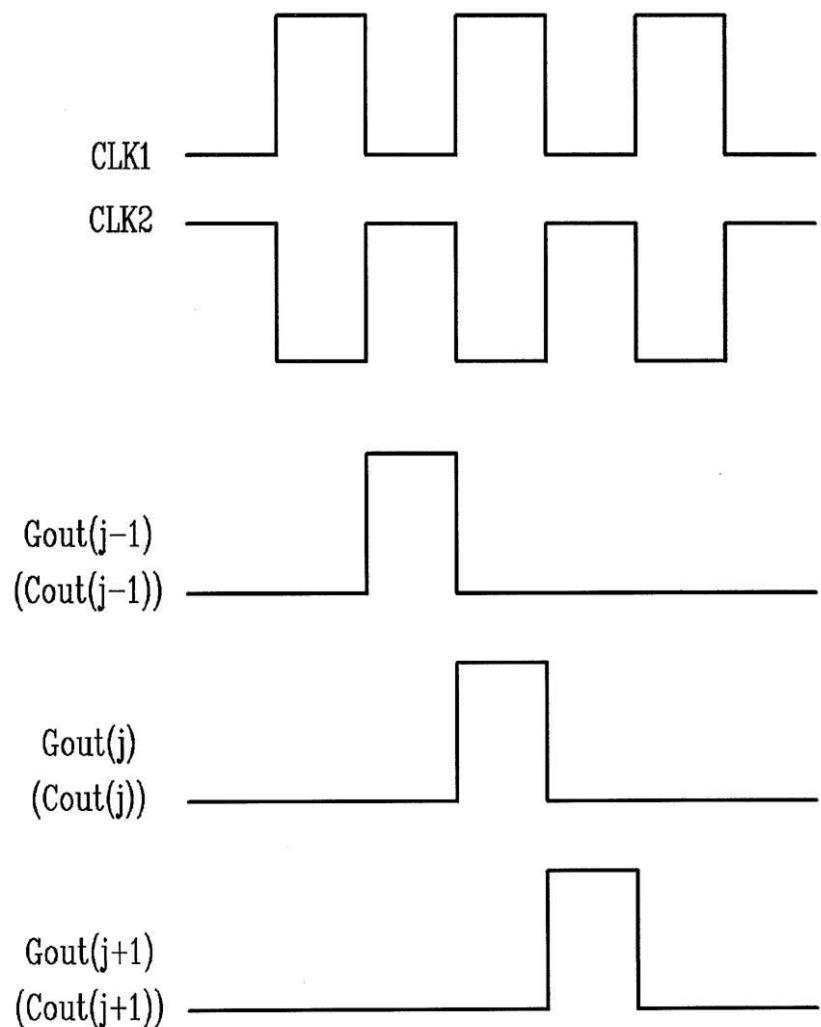

場合はゲートオフ電圧  $V_{ff}$  と同一であるのが好ましい。図5に示したように各クロック信号 CLK1、CLK2はデューティ比が50%であり、二つのクロック信号 CLK1、CLK2の位相差は180°であり得る。

#### 【0054】

図4に示すように、本発明の一つの実施例によるゲート駆動部400の各ステージ、例えば、j番目ステージは、図4に示すように入力部420、プルアップ駆動部430、プルダウン駆動部440及び出力部450を含む。これらは少なくとも一つのNMOSトランジスタM1-M13を含み、プルアップ駆動部430と出力部450はキャパシタC1-C3をさらに含む。しかし、NMOSトランジスタの代わりにPMOSトランジスタを使用することもできる。また、キャパシタC1-C3は実際に、工程時に形成されるゲートとドレイン/ソース間寄生容量であり得る。

10

#### 【0055】

入力部420はセット端子Sとゲート電圧端子GVに順次に直列に連結されている三つのトランジスタM1、M3、M2を含む。トランジスタM1、M2のゲートはクロック端子CK2に連結されており、トランジスタM2のゲートはクロック端子CK1に連結されている。トランジスタM1とトランジスタM3との間の接続点は接続点J1に連結されており、トランジスタM3とトランジスタM1との間の接続点は接続点J2に連結されている。

#### 【0056】

プルアップ駆動部430はセット端子Sと接続点J1との間に連結されているトランジスタM4と、クロック端子CK1と接続点J3との間に連結されているトランジスタM6、そしてクロック端子CK1と接続点J4との間に連結されているトランジスタM7を含む。トランジスタM4のゲートとドレインはセット端子Sに共通に連結されていて、ソースは接続点J1に連結されており、トランジスタM6のゲートとドレインはクロック端子CK1に共通に連結されており、ソースは接続点J3に連結されている。トランジスタM7のゲートは接続点J3に連結されると同時にキャパシタC1を通じてクロック端子CK1に連結されており、ドレインはクロック端子CK1に、ソースは接続点J4に連結されており、接続点J3と接続点J4との間にキャパシタC2が連結されている。

20

#### 【0057】

プルダウン駆動部440はソースを通じてゲートオフ電圧  $V_{ff}$  を受信してドレインを通じて接続点J1、J2、J3、J4に出力する複数のトランジスタM5、M8、M9、M12、M13を含む。トランジスタM5のゲートはリセット端子Rに、ドレインは接続点J1に連結されており、トランジスタM8、M9のゲートは接続点J2に共通に連結されており、ドレインは各々接続点J3、J4に連結されている。トランジスタM12のゲートは接続点J4に、トランジスタM13のゲートはリセット端子Rに連結されており、二つのトランジスタM12、M13のドレインは接続点J2に連結されている。

30

#### 【0058】

出力部450はドレインとソースが各々クロック端子CK1と出力端子OUT1、OUT2の間に連結されており、ゲートが接続点J1に連結されている一対のトランジスタM10、M11とトランジスタM10のゲートとドレインの間、つまり、接続点J1と接続点J2との間に連結されているキャパシタC3を含む。トランジスタM10のソースはまた接続点J2に連結されている。

40

#### 【0059】

次に、このようなステージの動作について説明する。

#### 【0060】

説明の便宜のためにクロック信号CLK1、CLK2のハイレベルに相当する電圧を高電圧とし、クロック信号CLK1、CLK2のローレベルに相当する電圧の大きさはゲートオフ電圧  $V_{ff}$  と同一で、これを低電圧とする。

#### 【0061】

まず、クロック信号CLK2及び前段キャリー出力Cout(j-1)がハイになれば

50

、トランジスタM1、M2とトランジスタM4が導通する。その後、二つのトランジスタM1、M4は高電圧を接続点J1に伝達し、トランジスタM2は低電圧を接続点J2に伝達する。これによって、トランジスタM10、M11が導通してクロック信号CLK1が出力端OUT1、OUT2に出力されるが、この時、接続点J2の電圧とクロック信号CLK1が全て低電圧であるので、出力電圧Gout(j)、Cout(j)は低電圧となる。これと同時に、キャパシタC3は高電圧と低電圧の差に相当する大きさの電圧を充電する。

#### 【0062】

この時、クロック信号CLK1及び後段ゲート出力Gout(j+1)はローで、接続点J2もローであるので、ゲートが連結されているトランジスタM3、M5、M6、M8、M9、M13は全てオフの状態である。

#### 【0063】

次に、クロック信号CLK2がローになればトランジスタM1、M2が遮断され、これと同時にクロック信号CLK1がハイになればトランジスタM10の出力電圧及び接続点J2の電圧が高電圧になる。この時、トランジスタM3のゲートには高電圧が印加されるが、接続点J2に連結されているソースの電位がまた同一な高電圧であるので、ゲートソース間の電位差が0になってトランジスタM3は遮断状態を維持する。したがって、接続点J1は浮遊状態になり、その結果キャパシタC3によって高電圧だけ電位がさらに上昇する。

#### 【0064】

一方、クロック信号CLK1及び接続点J2の電位が高電圧であるので、トランジスタM6、M8、M9が導通する。この状態でトランジスタM6とトランジスタM8が高電圧と低電圧との間で直列に連結され、その結果接続点J3の電位は二つのトランジスタM6、M8の導通時に抵抗状態の抵抗値によって分圧された電圧値を有する。しかし、二つのトランジスタM8の導通時に抵抗状態の抵抗値がトランジスタM6の導通時の抵抗状態の抵抗値に比べて非常に大きく、例えば約10,000倍程度に設定されているとすれば、接続点J3の電圧は高電圧とほとんど同一である。したがって、トランジスタM7が導通してトランジスタM9と直列に連結され、そのために接続点J4の電位は二つのトランジスタM7、M9の導通時に抵抗状態の抵抗値によって分圧された電圧値を有する。この時、二つのトランジスタM7、M9の抵抗状態の抵抗値がほとんど同一に設定されていれば、接続点J4の電位は高電圧と低電圧の中間値を有し、これによってトランジスタM12は遮断状態を維持する。この時、後段ゲート出力Gout(j+1)が依然としてローであるので、トランジスタM5、M13もまた遮断状態を維持する。したがって、出力端OUT1、OUT2はクロック信号CLK1にのみ連結され、低電圧とは遮断されて高電圧を出力する。

#### 【0065】

一方、キャパシタC1とキャパシタC2は両端の電位差に相当する電圧を各々充電するが、接続点J3の電圧が接続点J5の電圧より低い。

#### 【0066】

次に、後段ゲート出力Gout(j+1)及びクロック信号CLK2がハイになってクロック信号CLK1がローになれば、トランジスタM5、M13が導通して接続点J1、J2に低電圧を伝達する。この時、接続点J1の電圧はキャパシタC3が放電しながら低電圧に落ちるが、キャパシタC3の放電時間によって低電圧に完全に下がるのにはある程度の時間を必要とする。したがって、二つのトランジスタM10、M11は後段ゲート出力Gout(j+1)がハイになっても少しの間導通状態を維持し、それによって出力端OUT1、OUT2がクロック信号CLK1と連結されて低電圧を出力する。次に、キャパシタC3が完全に放電されて接続点J1の電位が低電圧に至ればトランジスタM11が遮断されて出力端OUT2がクロック信号CLK1と遮断されるので、キャリー出力Cout(j)は浮遊状態になって低電圧を維持する。これと同時に、出力端OUT1はトランジスタM10が遮断されてもトランジスタM13を通じて低電圧と連結されるので引続

10

20

30

40

50

き低電圧を出力する。

【0067】

一方、トランジスタM6、M8が遮断されるので、接続点J3が浮遊状態となる。また、接続点J5の電圧が接続点J4の電圧より低くなるが、キャパシタC1によって接続点J3の電圧が接続点J5の電圧より低い状態を維持するためにトランジスタM7は遮断される。これと同時に、トランジスタM9も遮断状態になるので、接続点J4の電圧もその程度低くなつてトランジスタM12もまた遮断状態を維持する。また、トランジスタM3はゲートがクロック信号CLK1の低電圧に連結され、接続点J2の電圧もローであるので遮断状態を維持する。

【0068】

次に、クロック信号CLK1がハイになれば、トランジスタM6、M7が導通され、接続点J4の電圧が上昇してトランジスタM12を導通させて低電圧を接続点J2に伝達するので、出力端OUT1は引続き低電圧を出力する。つまり、後段ゲート出力Gout(j+1)の出力がローであるとしても、接続点J2の電圧が低電圧になるようにする。

【0069】

一方、トランジスタM3のゲートがクロック信号CLK1の高電圧に連結されて接続点J2の電圧が低電圧であるので、導通して接続点J2の低電圧を接続点J1に伝達する。また、二つのトランジスタM10、M11のドレインにはクロック端子CK1が連結されていてクロック信号CLK1が引続き印加される。特に、トランジスタM10は残りトランジスタに比べて相対的に大きく作るが、これによってゲートドレイン間寄生容量が大きくなつてドレインの電圧変化がゲート電圧に影響を与えることがある。したがって、クロック信号CLK1がハイになる時、ゲートドレイン間寄生容量のためにゲート電圧が上昇してトランジスタM10が導通することもある。したがって、接続点J2の低電圧を接続点J1に伝達することによってトランジスタM10のゲート電圧を低電圧に維持してトランジスタM10が導通することを防止する。

【0070】

その後、前段キャリー出力Cout(j-1)がハイになるまで接続点J1の電圧は低電圧を維持し、接続点J2の電圧はクロック信号CLK1がハイで、クロック信号CLK2がローである時はトランジスタM12を通じて低電圧になり、その反対の場合にはトランジスタM2を通じて低電圧を維持する。

【0071】

このような方式で、ステージ410は前段キャリー信号Cout(j-1)及び後段ゲート信号Goutj+1に基づいてクロック信号CLK1、CLK2に同期してキャリー信号Cout(j)及びゲート信号Gout(j)を生成する。

【0072】

一方、ゲート駆動部400は表示板部300の一側周縁に集積されているが、このような表示装置の表示板部300について図6乃至図9を参照して詳細に説明する。

【0073】

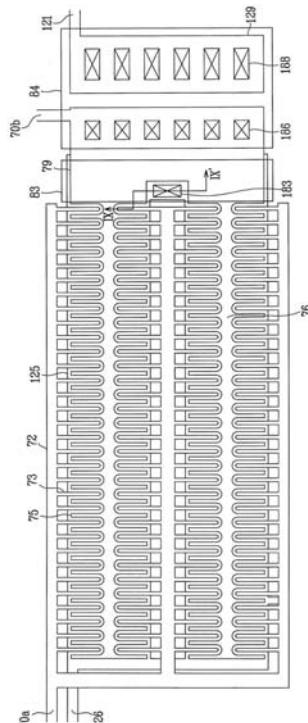

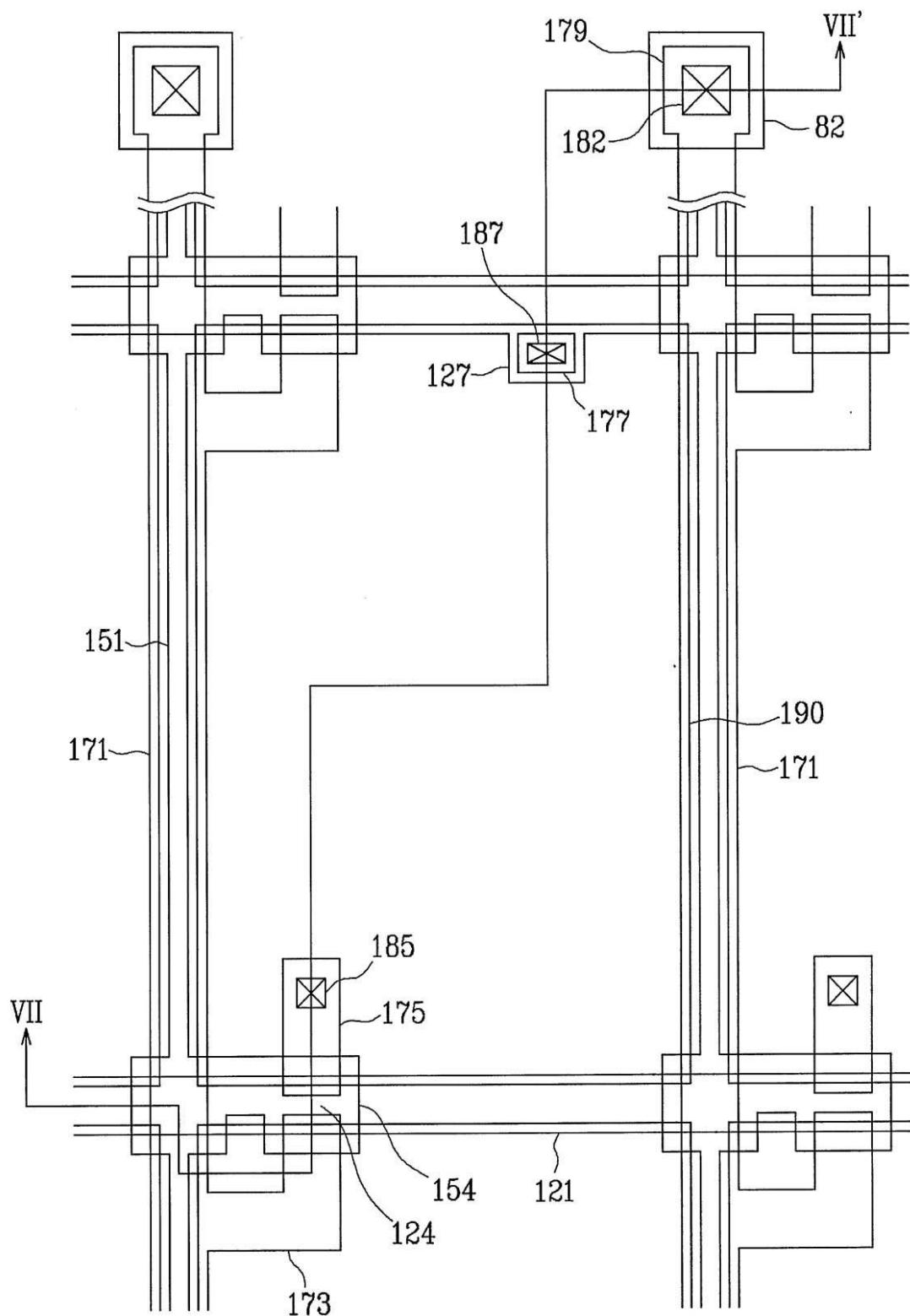

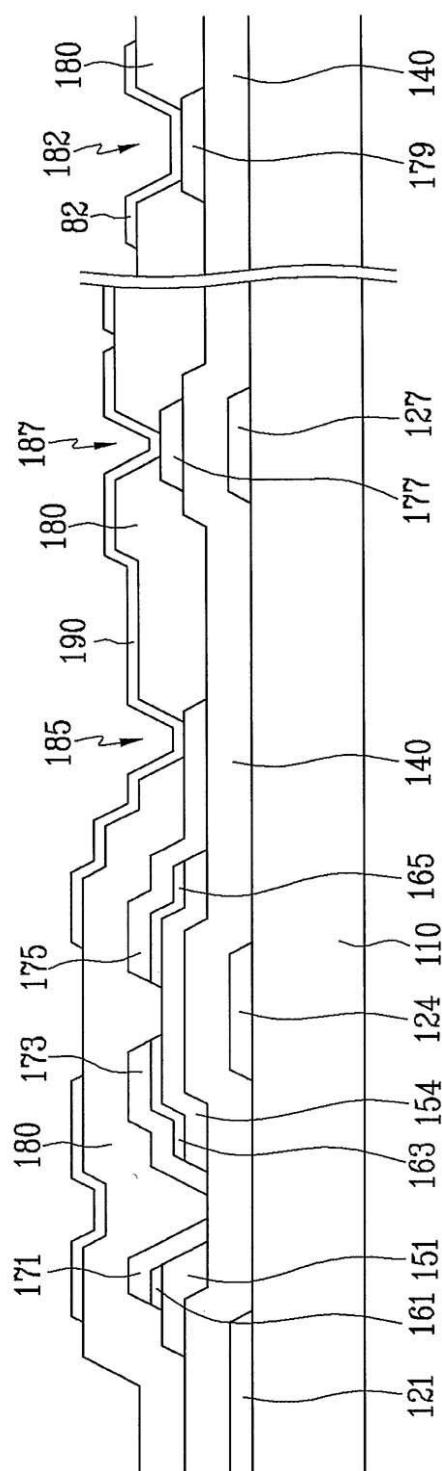

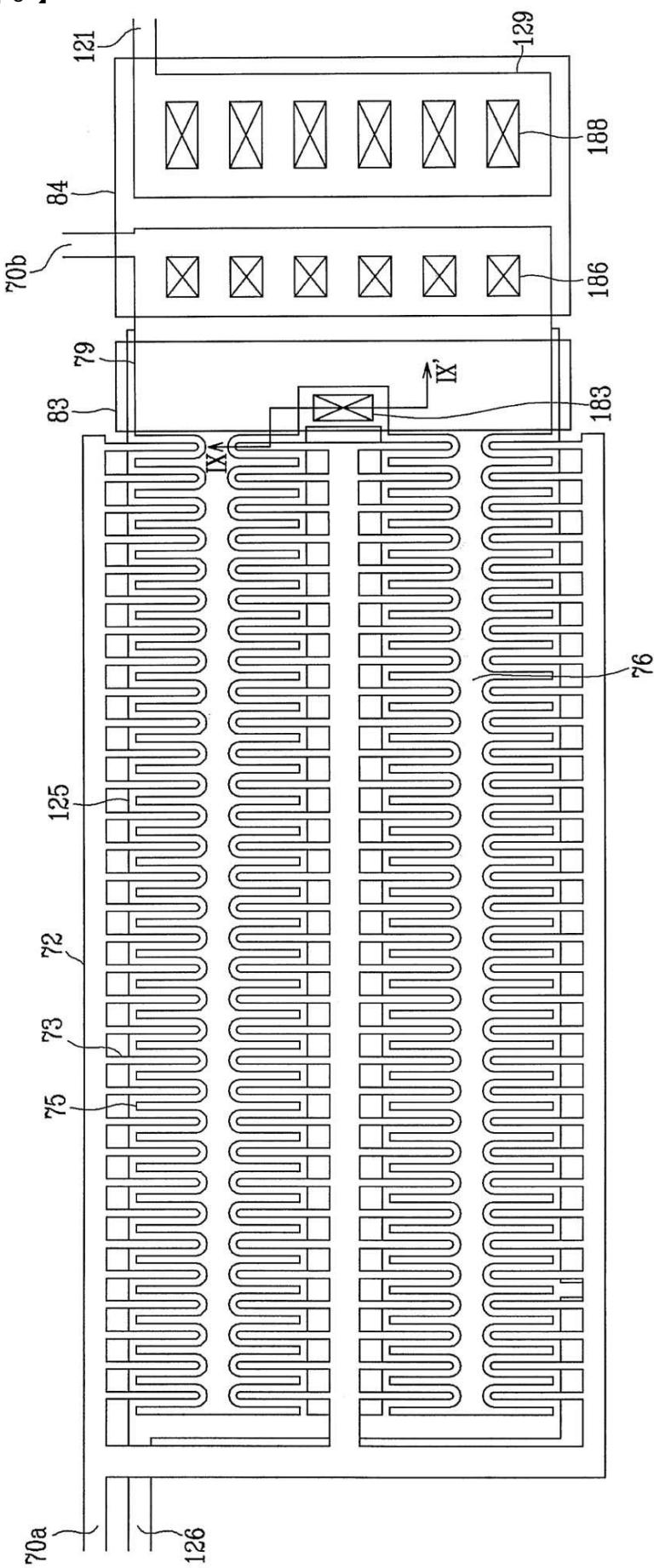

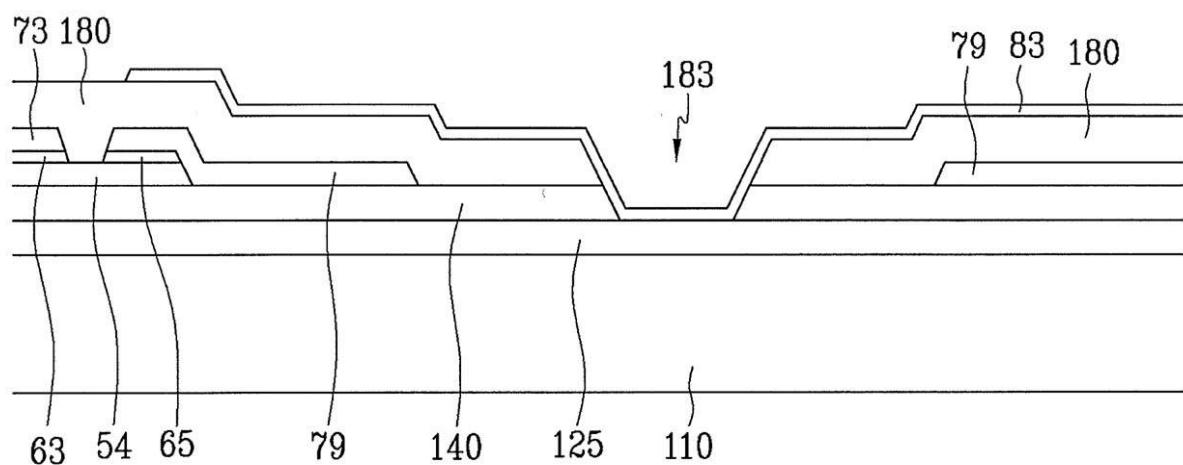

図6は本発明の一つの実施例による表示装置用薄膜トランジスタ表示板の一つの画素の配置図であり、図7は図6に示した薄膜トランジスタ表示板を図6のVII-VII'線に沿つて切斷した断面図である。図8は図4に示したゲート駆動部のステージのトランジスタM10とキャパシタC3の配置図であり、図9は図8に示したトランジスタM10とキャパシタC3をIX-IX'線に沿つて切斷した断面図である。

【0074】

絶縁基板110上に複数のゲート線121及びゲート駆動部400の制御信号線126が形成されている。

【0075】

ゲート線121はゲート信号を伝達し、主に横方向にゲート駆動部400側に伸びている。各ゲート線121の一部は複数のゲート電極124を構成し、他の一部は下方向に突出して複数の突出部127を構成する。また、各ゲート線G<sub>1</sub>-G<sub>n</sub>はゲート駆動部400

0に隣接した端部に面積の広い連結部129を有する。制御信号線126の一部は拡張されて互いに連結された複数の制御電極125を構成する。

#### 【0076】

ゲート線121及び制御信号線126は比抵抗の低い銀や銀合金などの銀系金属、アルミニウムやアルミニウム合金などのアルミニウム系金属、銅や銅合金などの銅系金属などからなる導電膜を含み、このような導電膜に加えて他の物質、特にITOまたはIZOとの物理的、化学的、電気的接触特性の良いクロム、チタニウム、タンタル、モリブデン及びこれらの合金（例：モリブデン-タンゲステン合金）などからなる他の導電膜を含む多層膜構造を有し得る。下部膜と上部膜の組み合わせの例としては、クロム／アルミニウム-ネオジム合金などがある。

10

#### 【0077】

ゲート線121及び制御信号線126の側面は基板110の表面に対して傾いており、傾斜角は約30～80°範囲である。

#### 【0078】

ゲート線121及び制御信号線126上には窒化シリコンなどからなるゲート絶縁膜140が形成されている。

#### 【0079】

ゲート絶縁膜140上部には水素化非晶質シリコン（非晶質シリコンは略してa-Siとも言う）などからなる複数の線状半導体151及び島型半導体54が形成されている。線状半導体151は主に縦方向に伸びており、これから複数の突出部154がゲート電極124に向かって伸びている。また、線状半導体151はゲート線121と会う地点の付近で幅が広くなっている。島型半導体54は制御電極125上に位置する。

20

#### 【0080】

半導体151、54の上部にはシリサイドまたはn型不純物が高濃度でドーピングされているn+水素化非晶質シリコンなどの物質で作られた複数の線状及び島型抵抗性接触部材161、165、63、65が形成されている。線状接触部材161は複数の突出部163を有しており、この突出部163と島型接触部材165は対をなして半導体151の突出部154上に位置する。島型接触部材63、65も対をなして半導体54上に位置する。

30

#### 【0081】

半導体151、54と抵抗性接触部材161、165、63、65の側面もやはり傾いており、傾斜角は30～80°である。

#### 【0082】

抵抗性接触部材161、165、63、65及びゲート絶縁膜140上には各々複数のデータ線171、複数の出力電極175、複数のストレージキャパシタ用導電体177と入力信号線70a及び出力信号線70bが形成されている。

40

#### 【0083】

データ線171は主に縦方向に伸びてゲート線121と交差し、データ電圧を伝達する。各データ線171から出力電極175に向かって伸びた複数の分枝が入力電極173を構成する。一对の入力電極173と出力電極175は互いに分離されており、ゲート電極124に対して互いに反対側に位置する。

#### 【0084】

入力信号線70aは制御電極125付近で横方向に複数の三つの主分子に分かれ入力信号線連結部72を構成する。この入力信号線連結部72から縦方向に複数の分枝がくし型で一定間隔をおいて伸びて出力電極73を構成する。入力信号線連結部72は制御電極125とほとんど重ならず、入力電極73は一部のみが制御電極125と重なる。以下では入力信号線連結部72と入力電極73を合せて入力電極部と言う。

#### 【0085】

また、出力信号線70bは入力信号線70aの分歧点の対向側で拡張されて出力電極拡

50

張部 7 9 を構成し、この出力電極拡張部 7 9 は制御電極 1 2 5 と一定面積重なっている。出力電極拡張部 7 9 から入力信号線連結部 7 2 の間に出力信号線連結部 7 6 が各々伸びており、出力信号線連結部 7 6 の間に複数の分枝が伸びて出力電極 7 5 を構成し、出力信号線連結部 7 6 と出力電極 7 5 もまた制御電極 1 2 5 と重なっている。以下では出力信号線連結部 7 6 と出力電極 7 5 及び出力電極拡張部 7 9 を合せて出力電極部と言う。

#### 【 0 0 8 6 】

ゲート電極 1 2 4 、入力電極 1 7 3 及び出力電極 1 7 5 は半導体 1 5 1 の突出部 1 5 4 と共に画素の薄膜トランジスタ（ T F T ）を構成し、薄膜トランジスタのチャンネルは各々入力電極 1 7 3 と出力電極 1 7 5 との間の突出部 1 5 4 に形成される。また、制御電極 1 2 5 、入力電極部 7 2 、 7 3 及び出力電極部 7 5 、 7 6 、 7 9 も半導体 5 4 と共に駆動部のトランジスタ M 1 0 である薄膜トランジスタを構成し、薄膜トランジスタのチャンネルは入力電極 7 3 と出力電極 7 5 との間の半導体 5 4 に形成される。出力電極 7 5 が入力電極 7 3 と交互に配列されているので、入力電極 7 3 と出力電極 7 5 との間に形成されるチャンネル部は馬蹄形状を有する。

#### 【 0 0 8 7 】

また、前述したように、出力電極部 7 5 、 7 6 、 7 9 と制御電極 1 2 5 がその間のゲート絶縁膜 1 4 0 を介在して重なるが、この部分がゲート駆動部のキャパシタ C 3 の一つの成分となる。

#### 【 0 0 8 8 】

ストレージキャパシタ用導電体 1 7 7 はゲート線 1 2 1 の拡張部 1 2 7 と重なっている。

。

#### 【 0 0 8 9 】

データ線 1 7 1 、出力電極 1 7 5 、入力信号線 7 0 a 及び出力信号線 7 0 b 、そしてストレージキャパシタ用導電体 1 7 7 もまた比抵抗の低い銀や銀合金などの銀系金属、アルミニウムやアルミニウム合金などのアルミニウム系金属などからなる導電膜を含み、このような導電膜に加えて他の物質、特に I T O または I Z O との物理的、化学的、電気的接触特性の良いクロム、チタニウム、タンタル、モリブデン及びこれらの合金（例：モリブデン - タングステン合金）などからなる他の導電膜を含む多層膜構造を有することもできる。下部膜と上部膜の組み合わせの例としてはクロム / アルミニウム - ネオジム合金などがある。

#### 【 0 0 9 0 】

データ線 1 7 1 、出力電極 1 7 5 、入力信号線 7 0 a 及び出力信号線 7 0 b 、そしてストレージキャパシタ用導電体 1 7 7 の側面もまた傾いており、傾斜角は基板 1 1 0 の表面に対して約 3 0 ~ 8 0 ° 範囲である。

#### 【 0 0 9 1 】

抵抗性接触部材 1 6 1 、 1 6 5 、 6 3 、 6 5 はその下部の半導体 1 5 1 、 5 4 とその上部のデータ線 1 7 1 及び出力電極 1 7 5 と入力信号線 7 0 a 及び出力信号線 7 0 b の間にのみ存在し、接触抵抗を下げる役割を果たす。

#### 【 0 0 9 2 】

データ線 1 7 1 と出力電極 1 7 5 、入力信号線 7 0 a と出力信号線 7 0 b 、そしてストレージキャパシタ用導電体 1 7 7 と露出された半導体 1 5 1 、 5 4 部分の上には平坦化特性が優れていて感光性を有する有機物質、プラズマ化学気相蒸着（ P E C V D ）で形成される a - S i : C : O 、 a - S i : O : F など誘電率 4 . 0 以下の低遷移率絶縁物質、または無機物質である窒化シリコンなどからなる保護膜 1 8 0 が形成されている。これとは異なって保護膜 1 8 0 は有機物と窒化シリコンの二重層からなることができる。

#### 【 0 0 9 3 】

保護膜 1 8 0 にはデータ線 1 7 1 の端部 1 7 9 と出力電極 1 7 5 、ストレージキャパシタ用導電体 1 7 7 及び出力電極拡張部 7 9 の一部分を各々露出する複数の接触孔 1 8 2 、 1 8 5 、 1 8 7 、 1 8 6 が形成されており、ゲート絶縁膜 1 4 0 と共に制御電極 1 2 5 の一部分及びゲート線 1 2 1 の連結部 1 2 9 を露出する接触孔 1 8 3 、 1 8 8 が形成されて

10

30

40

50

いる。

【0094】

保護膜180上にはITOまたはIZOからなる複数の画素電極190と複数の接触補助部材82と補助電極83及び連結補助部材84が形成されている。

【0095】

画素電極190は接触孔185、187を通じて出力電極175及びストレージキャパシタ用導電体177と各々物理的・電気的に連結されて出力電極175からデータ電圧の印加を受けて、導電体177にデータ電圧を伝達する。

【0096】

図2を再び参照すれば、データ電圧が印加された画素電極190は共通電圧の印加を受ける他の表示板200の共通電極270と共に電場を生成することによって二つの電極190、270の間の液晶層3の液晶分子を再配列させる。10

【0097】

また、前述したように画素電極190と共に電極270はキャパシタを構成して薄膜トランジスタが遮断された後にも印加された電圧を維持するが、電圧維持能力を強化するために液晶キャパシタと並列に連結された他のキャパシタを置いて、これを“ストレージキャパシタ”C<sub>ST</sub>と言う。ストレージキャパシタC<sub>ST</sub>は図2とは異なって画素電極190及びこれと隣接するゲート線121(これを“前段ゲート線”と言う)の重畠などで作られ、ストレージキャパシタの静電容量、つまり、保持容量を増やすためにゲート線121を拡張した拡張部127を置いて重畠面積を大きくする一方、画素電極190と連結されて拡張部127と重なるストレージキャパシタ用導電体177を保護膜180下に置いて二つの間の距離を近くする。20

【0098】

画素電極190はまた、隣接するゲート線121及びデータ線171と重なって開口率を高めているが、重ならないこともある。

【0099】

接触補助部材82は接触孔182を通じてデータ線の端部179と連結される。接触補助部材82はデータ線171の端部179と外部装置との接着性を補完して、これらを保護する役割を果たすもので、必須のものではなく、これらの適用可否は選択的である。30

【0100】

補助電極83は接触孔183を通じて制御電極125と連結されており、出力電極拡張部79と重なってゲート駆動部のキャパシタC3のもう一つの成分となる。このように、制御電極125に連結された補助電極83が保護膜180を間に置いて出力電極拡張部79と重なるのでトランジスタM10のゲートソース間の静電容量、つまり、キャパシタC3の静電容量が増える。増える静電容量は保護膜180の誘電率と重畠面積に比例し、保護膜180の厚さに反比例する。例えば、出力電極拡張部79を除いた残りの部分における静電容量を無視すれば、ゲート絶縁膜140の厚さがほぼ4500であり、保護膜180の厚さが約2000である場合、出力電極拡張部79と制御電極125間の距離に比べて出力電極拡張部79と補助電極83の距離が約1/2である。ゲート絶縁膜140と保護膜180の誘電率が同一であれば出力電極拡張部79と補助電極83との間の静電容量はほぼ出力電極拡張部79と制御電極125との間の静電容量の2倍である。したがって、補助電極83がない場合に比べて静電容量は3倍程度となる。40

【0101】

したがって、小さい面積でも必要な静電容量を確保することができるので、ゲート駆動部400が占める面積を減らして画素が存在する表示領域を広くすることができる。

【0102】

一方、前述したようにトランジスタM10の入力電極部72、73と制御電極125が重なる面積は出力電極部75、76、79が制御電極125と重なってなす面積に比べて非常に小さいので、トランジスタM10のゲートドレイン間寄生容量はゲートソース間寄生容量に比べて非常に小さいと言うことができる。50

## 【0103】

連結補助部材 84 は接触孔 186、188 を通じて出力電極拡張部 79 及びゲート線 121 の連結部 129 と各々物理的・電気的に連結されて出力電極拡張部 79 からゲート電圧の印加を受けてゲート線 121 にゲート電圧を伝達する。

## 【0104】

本発明の他の実施例によれば、画素電極 190 の材料として透明な導電性ポリマーなどを使用し、反射型液晶表示装置の場合、不透明な反射性金属を使用してもよい。この時、接触補助部材 82 は画素電極 190 とは異なる物質、特に ITO または IZO で作ることができる。

## 【0105】

このような方式で、ステージ 410 の全面積のうちの約 40 乃至 50 % を占めるトランジスタ M10 の大きさを減らすことによって、ステージ一つが占める面積を同時に減らすことができる。その結果、ゲートとソースが短絡される危険を減して信頼度の高いゲート駆動部を提供することができ、さらにトランジスタを配置するにも余裕を持って設計することができる。

## 【0106】

したがって、トランジスタ M10 が占める面積を減らすことによって、信頼性と設計マージンを確保することができる表示装置を提供することができる。

## 【0107】

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されず、請求範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態もまた本発明の権利範囲に属する。

## 【図面の簡単な説明】

## 【0108】

【図 1】本発明の一つの実施例による表示装置のブロック図である。

【図 2】本発明の一つの実施例による液晶表示装置の一つの画素に対する等価回路図である。

【図 3】本発明の一つの実施例によるゲート駆動部のブロック図である。

【図 4】図 3 に示したゲート駆動部用シフトレジスターの j 番目ステージの回路図の一例である。

【図 5】図 3 に示したゲート駆動部の信号波形図である。

【図 6】本発明の一つの実施例による表示装置用薄膜トランジスタ表示板の配置図である。

【図 7】図 6 に示した薄膜トランジスタ表示板を図 6 の V<sub>II</sub> - V<sub>II'</sub> 線に沿って切断した断面図である。

【図 8】図 4 に示したゲート駆動部のステージのトランジスタ M10 とキャパシタ C3 の配置図である。

【図 9】図 8 に示したトランジスタ M10 及びキャパシタ C3 を I<sub>X</sub> - I<sub>X'</sub> 線に沿って切断した断面図である。

## 【符号の説明】

## 【0109】

3 液晶層

54、151 半導体

63、65、161、165 抵抗性接触部材

70a 入力信号線

70b 出力信号線

72 入力信号線連結部

73 入力電極

76 出力信号線連結部

79 出力電極拡張部

10

20

30

40

50

|                                                        |                |    |

|--------------------------------------------------------|----------------|----|

| 8 3                                                    | 補助電極           |    |

| 1 0 0                                                  | 下部表示板          |    |

| 1 1 0                                                  | 絶縁基板           |    |

| 1 2 1                                                  | ゲート線           |    |

| 1 2 4                                                  | ゲート電極          |    |

| 1 2 5                                                  | 制御電極           |    |

| 1 2 6                                                  | 制御信号線          |    |

| 1 2 7                                                  | 突出部            |    |

| 1 2 9                                                  | 連結部            |    |

| 1 4 0                                                  | ゲート絶縁膜         | 10 |

| 1 7 1                                                  | ゲート線           |    |

| 1 7 3                                                  | 入力電極           |    |

| 1 7 5                                                  | 出力電極           |    |

| 1 7 7                                                  | ストレージキャパシタ用導電体 |    |

| 1 7 9                                                  | 端部             |    |

| 1 8 0                                                  | 保護膜            |    |

| 1 8 5、1 8 6、1 8 7、1 8 8                                | 接触孔            |    |

| 1 9 0                                                  | 画素電極           |    |

| 2 0 0                                                  | 上部表示板          |    |

| 2 3 0                                                  | 色フィルター         | 20 |

| 2 7 0                                                  | 共通電極           |    |

| 3 0 0                                                  | 表示板部           |    |

| 4 0 0                                                  | ゲート駆動部         |    |

| 4 1 0                                                  | ステージ           |    |

| 4 2 0                                                  | 入力部            |    |

| 4 3 0                                                  | プルアップ駆動部       |    |

| 4 4 0                                                  | プルダウン駆動部       |    |

| 4 5 0                                                  | 出力部            |    |

| 5 0 0                                                  | データ駆動部         |    |

| 6 0 0                                                  | 信号制御部          | 30 |

| 8 0 0                                                  | 階調電圧生成部        |    |

| C 1 - C 3                                              | キャパシタ          |    |

| C K 1、C K 2                                            | クロック端子         |    |

| C L K 1、C L K 2                                        | クロック信号         |    |

| C O N T 1                                              | ゲート制御信号        |    |

| C O N T 2                                              | データ制御信号        |    |

| C L c                                                  | 液晶キャパシタ        |    |

| C s T                                                  | ストレージキャパシタ     |    |

| C P V                                                  | ゲートクロック信号      |    |

| D A T                                                  | 映像信号           | 40 |

| D 1 - D m                                              | データ線           |    |

| G 1 - G n                                              | ゲート線           |    |

| G V                                                    | ゲート電圧端子        |    |

| H C L K                                                | データクロック信号      |    |

| J 1、J 2、J 3、J 4、J 5                                    | 接続点            |    |

| L O A D                                                | ロード信号          |    |

| M 1、M 2、M 3、M 4、M 5、M 6、M 7、M 8、M 9、M 1 0、M 1 1、M 1 2、 |                |    |

| M 1 3                                                  | トランジスタ         |    |

| M C L K                                                | メインクロック        |    |

| O U T 1、O U T 2                                        | 出力端子           | 50 |

P X 画素

S セット端子

S T V 走査開示信号

S T H 水平同期開示信号

Q スイッチング素子

R リセット端子

R V S 反転信号

V c o m 共通電圧

V o n ゲートオン電圧

V o f f ゲートオフ電圧

H s y n c 水平同期信号

V s y n c 垂直同期信号

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 李 成 榮

大韓民国ソウル特別市陽川区新月7洞331-54番地 ソンイルビラ ガ棟302号

(72)発明者 金 聖 萬

大韓民国ソウル特別市松坡区新川洞 薔薇アパート30棟508号

F ターム(参考) 2H092 JA26 JB13 JB63 PA06

2H093 NC28 NC34 NC35 NC90 ND09 ND10 ND15 ND35 ND36 ND37

ND41 ND48 ND58 NE10

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置用驱动装置及び表示板                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2005352455A</a>                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2005-12-22 |

| 申请号            | JP2005124233                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2005-04-21 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 李成榮<br>金聖萬                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 李成榮<br>金聖萬                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G02F1/1368 G02F1/133 G09G3/20 G09G3/32 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/3677 G09G3/20 G09G2310/0267 G09G2310/0286 G11C19/184                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G02F1/133.550 G02F1/1368 G02F1/1345 G11C19/00 G11C19/00.J G11C19/28.D G11C19/28.230                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H092/JA26 2H092/JB13 2H092/JB63 2H092/PA06 2H093/NC28 2H093/NC34 2H093/NC35 2H093 /NC90 2H093/ND09 2H093/ND10 2H093/ND15 2H093/ND35 2H093/ND36 2H093/ND37 2H093/ND41 2H093/ND48 2H093/ND58 2H093/NE10 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CB42 2H192 /CC04 2H192/CC12 2H192/CC52 2H192/DA02 2H192/DA12 2H192/DA42 2H192/EA43 2H192/FB03 2H193/ZA04 2H193/ZA07 2H193/ZD32 2H193/ZF23 2H193/ZH40 2H193/ZP20 5B074/AA03 5B074 /CA01 5B074/DB01 5B074/EA01 |         |            |

| 代理人(译)         | 宇谷 胜幸                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 1020040042232 2004-06-09 KR                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | JP4691387B2                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

**摘要(译)**

要解决的问题：提供一种能够确保可靠性和设计裕度的显示装置。显示装置的驱动装置技术领域本发明涉及显示装置的驱动装置。驱动单元包括控制电极125，形成在控制电极125上的栅极绝缘膜140，形成在栅极绝缘膜140上的半导体层54以及至少部分地形成在半导体层54上的输入电极单元。如图72、73所示，输出电极部分75、76、79至少部分地形成在半导体层54上并且与控制电极125重叠，形成在输入电极部分72、73和输出电极部分75、76、79上。保护膜180包括形成在保护膜180上并连接到控制电极125并且与输出电极部分75、76和79重叠的辅助电极83。通过这种方法，即使在较小的面积下也可以确保所需的电容。[选择图]图8