#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-122839 (P2008-122839A)

(43) 公開日 平成20年5月29日(2008.5.29)

| (51) Int.Cl.<br>GO9G<br>GO9G<br>GO2F | 3/36<br>3/20<br>1/133 | (2006. 01)<br>(2006. 01)<br>(2006. 01) | FI<br>G09G<br>G09G<br>G09G<br>G09G<br>G09G | 3/36<br>3/20<br>3/20<br>3/20<br>3/20<br>3/20 | 641E<br>621B<br>621A                          | OL                                                                               | テーマコー<br>2HO93<br>5COO6<br>5CO8O<br>(全 10 頁) | ド (参考)<br>最終頁に続く |

|--------------------------------------|-----------------------|----------------------------------------|--------------------------------------------|----------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------|------------------|

| (21) 出願番号(22) 出願日                    |                       | 特願2006-308963<br>平成18年11月15日           | ,                                          | (71) 出<br>(74) 代<br>(72) 発                   | 日本ビ<br>神奈川<br>番地<br>理人 100090<br>弁理士<br>明者 河田 | ク県<br>タ横<br>125<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・ | 株式会社<br>市神奈川区守屋<br>章弘<br>市神奈川区守屋<br>でアラマー株式会 | 町3丁目12           |

最終頁に続く

NG02

Fターム(参考) 2H093 NA33 NA34 NB01 NC23 NC34

ND10 ND12 ND34 ND35 ND47

5C006 AA14 AC26 AF44 AF71 BB16 EC11 FA23 FA33

# (54) 【発明の名称】画像表示装置の駆動方法

# (57)【要約】

【課題】フリッカーや直流電圧印加による液晶材料の劣 化を抑制する。

【解決手段】表面に配向膜の形成された複数の画素電極 PEと表面に配向膜が形成された対向電極 CEとを、間 に液晶LCを介して対向配置することにより複数の画素 をマトリクス状に形成した表示部42に、画素信号を印 加して画像を表示するに画像表示装置の駆動方法におい て、各フレームを複数のサブフレームにより構成し、サ ブフレームを選択的にオン、又はオフして画像を複数の 階調で表示する画像表示装置において、各サブフレーム の表示期間を前半表示期間部と後半表示期間部とに区分 して前半表示期間部と後半表示期間部とで極性を逆転し 、前半表示期間部の長さと画素電極 - 対向電極間の電位 差との積と、後半表示期間部の長さと画素電極 - 対向電 極間の電位差との積が同じになるように、前半表示期間 部の長さと後半表示期間部の長さとの比を設定する。

### 【選択図】図9

#### 【特許請求の範囲】

#### 【請求項1】

表面に配向膜が形成された複数の画素電極と表面に配向膜が形成されて共通になされた対向電極とを、間に液晶を介して対向配置することにより複数の画素をマトリクス状に形成した表示部に、デジタル化された画素信号を印加して画像を表示するに際して、前記画像信号の各フレームを1フレーム期間より短時間である表示期間をもつ複数のサブフレームにより構成し、所望のサブフレームを選択的にオン、又はオフして1フレームの画像を複数の階調で表示する画像表示装置の駆動方法において、

前記各サブフレームの表示期間を前半表示期間部と後半表示期間部とに区分して前記前半表示期間部と後半表示期間部とで極性を逆転し、前記前半表示期間部の長さと前記画素電極・対向電極間の電位差との積と、前記後半表示期間部の長さと前記画素電極・対向電極間の電位差との積が同じになるように、前記前半表示期間部の長さと後半表示期間部の長さとの比を設定するようにしたことを特徴とする画像表示装置の駆動方法。

【発明の詳細な説明】

#### 【技術分野】

#### [00001]

本発明は、家庭用、事務用、および産業用の情報表示端末と普及している液晶プロジェクタおよびプロジェクションTVに用いる画像表示装置の駆動方法に関する。

# 【背景技術】

### [0002]

一般に、液晶を用いた画像表示装置の駆動方法としては、主に振幅変調を用いたアナログ駆動方式およびパルス幅変調を用いたデジタル駆動方式の 2 つがある。デジタル駆動方式はアナログ駆動方式と比較して、電気的な調整が簡単であるなどの優位性を持っている

### [0003]

デジタル駆動方式では、画像信号の各フレームを、1フレーム期間より短時間である異なる表示期間を持つ複数のサブフレームで構成し、各サブフレームを順に選択的にオン、オフ制御することにより1フレームを表示している。この場合、各サブフレームにおいては、前半と後半とで液晶に印加する電圧の正負を反転させて交流駆動を行うようにしており、これより液晶に加わる直流成分をキャンセルしてフリッカーと呼ばれる画像のちらつきや、直流電圧印加による液晶材料の劣化を抑制するようにしている(特許文献1、2)

#### [0004]

この方法では、画素電極に印加する画素電極電圧 V \_\_ p i x および対向電極に印加する対向電極電圧 V \_\_ c o m の値を各サブフレームで正極性印加時間 t 1 と負極性印加時間 t 2 とに、時間的に 2 等分して反転駆動を行う。このとき、入力信号レベルにおいて、正極性側の飽和電圧 | V \_\_ p i x - V \_\_ c o m | について、下記の式を満たすような信号を入力することで、入力信号の対称性を図っている。尚、ここで V p は正極性を示し、 V n は 負極性を示す。

| V p \_ p i x - V p \_ c o m | - | V n \_ p i x - V n \_ c o m | = 0

#### [0005]

【特許文献1】米国2004/0174328A1公報

【特許文献2】特開2005-352457号公報

【非特許文献1】2000 S1D,ISSN1083-1312/00/2001-0 001.[Reflective Nematic LC Devices for L COS Applications] by Minhua Lu, K. H. yang, I BM T. J. Watson Reserch Center

### 【発明の開示】

【発明が解決しようとする課題】

### [0006]

20

10

30

40

50

20

30

40

50

上述したように、従来の画像表示装置では入力信号レベルにおいて駆動信号の対称性を図っている。しかしながら、画素電極、対向電極、液晶材料、配向膜から形成される反射型の画像表示装置においては、液晶層を挟み込む材料が異種材料により構成されていることから、これに起因して電圧レベルシフトが発生するため(非特許文献1)、液晶層に印加される電圧の対称性が崩れてしまう、という問題があった。このような問題は、画素電極が透明になされた透過型の画像表示装置にあっても発生していた。

#### [0007]

本発明は、以上のような問題点に着目し、これを有効に解決すべく創案されたものである。本発明の目的は、各サブフレームにおいて前半と後半とで極性を反転させて印加する際に、正極と負極の印加時間の比を最適化することにより印加電圧の対称性を向上させ、フリッカーと呼ばれる画像のちらつきや、直流電圧印加による液晶材料の劣化を抑制することが可能な画像表示装置の駆動方法を提供するものである。

【課題を解決するための手段】

### [ 0 0 0 8 ]

請求項1に係る発明は、表面に配向膜が形成された複数の画素電極と表面に配向膜が形成されて共通になされた対向電極とを、間に液晶を介して対向配置することにより複数の画素をマトリクス状に形成した表示部に、デジタル化された画素信号を印加して画像を表示するに際して、前記画像信号の各フレームを1フレーム期間より短時間である表示期間をもつ複数のサブフレームにより構成し、所望のサブフレームを選択的にオン、又はオフレインの画像を複数の階調で表示する画像表示装置の駆動方法において、前記記記書表示期間部と後半表示期間部とで極性を逆転し、前記前半表示期間部の長さと前記画素電極・対向電極間の電位差との積と、前記後半表示期間部の長さと後半表示期間部の長さとの電極間の電位差との積と、前記前半表示期間部の長さと後半表示期間部の長さと後半表示期間部の長さとの電を表示期間部の長さと後半表示期間部の長さとの電極間の電

#### 【発明の効果】

#### [0009]

本発明に係る画像表示装置の駆動方法によれば、各サブフレームにおいて前半と後半とで極性を反転させて印加する際に、正極と負極の印加時間の比を最適化することにより印加電圧の対称性を向上させ、フリッカーと呼ばれる画像のちらつきや、直流電圧印加による液晶材料の劣化を抑制することができる。

【発明を実施するための最良の形態】

#### [0010]

以下に、本発明に係る画像表示装置の駆動方法の一実施例を添付図面に基づいて詳述する。

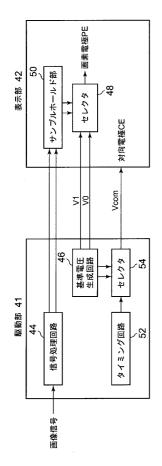

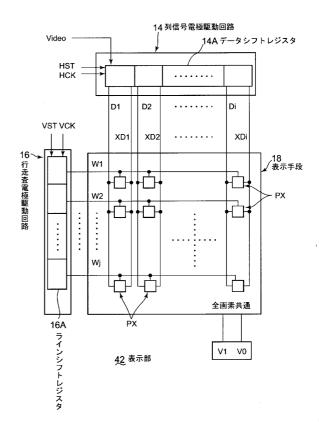

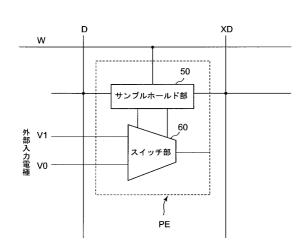

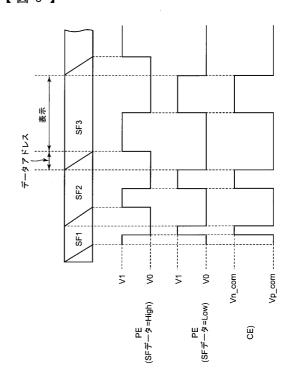

図1は画像表示装置の一例としての投射型表示装置の概略構成を示す図、図2は液晶を駆動する駆動電圧と出射光強度との関係を示すグラフ、図3は本発明における画像表示装置の駆動部と表示部を示す概略構成図、図4は本発明に適用される画像表示装置の表示部の概略ブロック構成図、図5は本発明に適用される画像表示装置の表示部における画素駆動回路の概略ブロック構成図、図6は本発明に適用される画素電極及び対向電極に与える電圧の概略的なタイミングを示すタイミングチャート、図7は階調レベルとサブフレームとの間の表示パターンの一例を示す図、図8は従来の画像表示装置の問題点を説明するための説明図、図9は本発明の画像表示装置の駆動方法の一例を示す説明図である。

# [0011]

本発明は、複数の画素がマトリクス状に配列された表示部を備えるLCD, P DP, DLP, FED, ELの如くのパネル型の画像表示装置に適用できるも のである。本実施形態では表示部としてアクティブマトリクス型の液晶素子を備えた投射型の表示部を例にとって説明する。

### [0012]

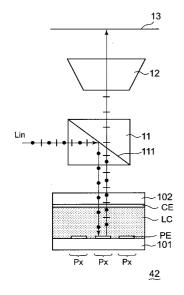

図1において、図示しない光源から発生した入射光Linは、偏光ビームスプリッタ1

20

30

40

50

1に入射される。入射光Linは""にて示すS偏光成分と、"-"にて示すP偏光成分とを含む。偏光ビームスプリッタ11の接合面111はS偏光成分を反射し、P偏光成分を透過させるよう構成されている。従って、偏光ビームスプリッタ11の接合面111で反射した入射光LinはS偏光成分のみとなり、表示部42に入射される。表示部42は、それぞれの画素Pxに対応して設けられた反射型の画素電極PEが形成された半導体基板101と透明な対向電極CEが形成された透明基板102とを画素電極PEと対向電極CEとが互いに内側に向くように対向させ、半導体基板101と透明基板102との間に液晶層LCを設けた構成である。尚、上記画素電極PEや対向電極CEの液晶層LC側には、図示しない配向膜がそれぞれ形成されている。

### [0013]

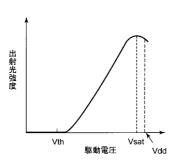

表示部42に入射したS偏光成分のみとなった光はそれぞれの画素電極PEで反射し、液晶層LCの液晶によって映像信号に応じて変調される。液晶層LCによる変調の結果、表示部42より出射する光はS偏光成分の一部がP偏光成分となり、S偏光成分とP偏光成分とを含む光として偏光ビームスプリッタ11の接合面111に入射する。偏光ビームスプリッタ11の接合面111に入射する。偏光ビームスプリッタ11の接合面111に入射する。。このP偏光成分のみの光が投射レンズ12を介してスクリーン13に投射される。このようにして画像信号に応じた画像がスクリーン13上に表示されることとなる。ここで液晶層LCからの出射光は、図2に示すように与えられる。図2中で出射光強度の閾値を与える電圧をVth、最大値(飽和電圧)を与える電圧をVsatとする。またVdddは飽和電圧Vsatよりも少し大きい電圧である。

#### [0014]

次に、図3及び図4を参照して画像表示装置の構成について説明する。図3は本実施例における画像表示装置の駆動部41と表示部42を示す概略構成図である。画像信号を信号処理回路44によりデジタル信号であるサブフレームデータに変換し、表示部42のサンプルホールド部50に与える。基準電圧発生回路46では、電極V0、V1用の電圧を発生し、この電圧を表示部42のセレクタ48に与える。また、画素電極PEの電圧としては、サンプルホールド部50に書き込まれるサブフレームデータに応じて、上記セレクタ48により電極V0、V1のいずれかの電圧が選択出力される。また上記基準電圧発生回路46は、液晶に与える実効値電圧と出射光強度の関係から対向電極CEに与える電圧Vcomを発生する。この電圧Vcomは、タイミング回路52からのタイミング信号に応じてセレクタ54によって対向電極CEに与えらえる。

# [0015]

図4は上記表示部42の全体を示しており、この表示部42は、列信号電極駆動回路14、行走査電極駆動回路16、表示手段18からなる。ここで、列信号電極駆動回路14は、内部に水平方向に延びるデータシフトレジスタ14Aを有し、各列信号電極D(D1、D2、・・・、Di)に対して、そのデータを反転した反転データを画素に供給する反転列信号電極XD(XD1、XD2、・・・、XDi)を有しており、対応する列信号電極と平行に設けられている。また、行走査電極駆動回路16は、内部に全表示行数に相当する段数のラインシフトレジスタ16Aを有し、全表示行数に相当する行走査電極W(W1、W2、・・・、Wj)が列信号電極D、XDとは直行して配列される。各列信号電極Dと行走査電極Wの交差部には、画素Pxが配置されており、従って、画素Pxは全体としてマトリクス状に配列されている。尚、外部入力電極V1、V0は全画素Pxに対して共通に接続される。

# [0016]

このような構成の列信号電極駆動回路14では、図示しない駆動タイミングパルス発生回路により供給される水平スタ・ト信号HST及び水平シフトクロックHCKにより水平方向のデータシフトレジスタが駆動され、各サブフレーム毎に入力された表示データを順次列信号電極D1、XD1、D2、XD2,・・・・、Di、XDiにサンプリングする。一方、行走査電極駆動回路16は、全表示行数に相当する段数を有するラインシフトレジスタ16Aを含んで構成されている。ラインシフトレジスタ16Aは、図示しない駆動

タイミングパルス発生回路より供給される各サブフレームのスタート信号と同期した垂直スタ・ト信号 V S T 及び水平期間に同期した垂直シフトクロック V C T により駆動され、行走査電極 W 1、 W 2、・・・、 W j に対して 1 水平期間毎に順次パルスを出力する。 その結果、行走査電極 W 1、 W 2、・・・ W j に接続された画素 P x のサンプルホ・ルド部 5 0 (図 5 参照)に 1 行ずつ表示デ・タが保持される。

### [0017]

次に1つの画素に対応する画素駆動回路の一例を図5を参照して説明する。この画素駆動回路は、列信号電極駆動回路14より供給される表示データを保持するサンプルホールド部50と、サンプルホールド部50からの出力データをスイッチ部60を通じて画素電極PEに電圧を出力する。サンプルホールド部50は、1個または複数のDRAM回路またはSRAM回路からなる。

スイッチ部60は、サンプルホールド部50から出力されるデータにより、2本の外部入力電極V0、V1のいずれか一方を選択出力する。2本の外部入力電極V0、V1は全画素共通に配線され、画像表示装置の駆動部41(図3参照)の基準電圧生成回路46から与えられる。スイッチ部60はサンプルホールド部50のデータにより2本の外部入力電極V0、V1に入力された電圧を選択し、画素電極PEに与える。

#### [0018]

さて、以上のように構成された画像表示装置の駆動方法について、図6及び図7も参照して説明する。図6は画素駆動回路中の各部の電圧波形をそれぞれ示すタイミングチャート、図7は階調レベルとサブフレームとの間の表示パターンの一例を示す図である。図7においては、1フレームはSF1~SF8までの8つの表示期間の異なるサブフレームによって構成されており、各サブフレームの表示を選択的にオン又はオフすることにより、パルス幅変調がなされて階調レベル0~255までの256種類の階調レベルを表示できるように設定されている。例えば1つの画素に対してある階調レベルで1つのフレームを表示する場合には、当該階調レベルの表示パターンでSF1から順にSF8まで表示することにより、当該階調レベルが表示されることになる。尚、縦軸の階調レベルの数が飛んでいる箇所は記載を省略している。

#### [0019]

また表示期間の単位は、例えば " µ s e c " である。表示パターンの " 0 " は " ロー " (オフ)を示し、 " 1 " は " ハイ " (オン)を示す。例えば階調レベル 0 は " 真白 " を示し、全てのサブフレーム S F 1 ~ S F 8 で表示は " 0 " となり、これに対して、階調レベル 2 5 5 は " 真黒 " を示し、全てのサブフレーム S F 1 ~ S F 8 で表示は " 1 " となっている。ここでは、 2 本の外部入力電極 V 0 、 V 1 に与えられるデジタル電圧のハイ状態の電圧を V d d 、ロー状態の電圧を 0 V とする。

# [0020]

まず、各サブフレームは、列信号電極駆動回路14から全画素にデータが転送されるデータアドレス期間と、その転送されたデータに基づき液晶を駆動させデータを表示する表示期間からなる。各サブフレームにおいてデータアドレス期間は同一であり、表示期間は異なる。ここで前述したようにサブフレームはSFで示され、1フレームを8個で構成した場合、SF1~SF8まで、サブフレーム毎に予め対応させて設定した表示期間でオン・オフ表示される。

### [0021]

図 6 は画素電極 P E と対向電極 C E に与える電圧の概略的なタイミングチャートを示す。図 6 に示すように、画素電極 P E に加わる電圧は、サブフレーム S F のデータが " H i g h "の時は表示期間の前半が電極 V 1 の電圧で、後半が電極 V 0 の電圧となり、サブフレーム S F のデータが " L o w "の時は上記とは逆に表示期間の前半が電極 V 0 の電圧で、後半が電極 V 1 の電圧となる。またデータアドレス期間では電極 V 0 の電圧となる。一方、対向電極 C E に加わる電圧は、表示期間の前半は V p \_ c o m となり、後半は V n \_ c o m となる。

# [0022]

20

10

30

40

20

30

40

50

次に、上記各サブフレームの内容を1つのサブフレームを例に取り上げて詳しく説明する。ここでは1つのサブフレームの表示期間の長さを代表してTとし、且つその内の前半表示期間部の長さ(以下「前半表示期間」とも称す)をt1とし、後半表示期間部の長さ(以下「後半表示期間」とも称す)をt2とする。

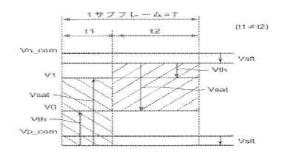

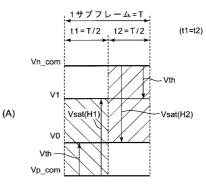

図 6 中では S F 3 に上記各期間の長さを一例として示している。図 8 は上記サブフレームの表示期間の部分を取り出して各電極間の電位を組み合わせて表示しており、画素電極と対向電極との間の電位差の推移が示されている。ここでは、対向電極の電位の正極性と負極性の電位をそれぞれ V p \_ p i x と V n \_ p i x として表している。

### [0023]

図8は従来の画像表示装置の場合を示しており、図8(A)に示すように前半表示期間t1と後半表示期間t2とは、"t1=t2=T/2"になるように設定されている。ここで基板材料に起因する電圧レベルシフトが何ら発生しない場合には、Vth、Vsatが以下の式を満たすように、各電極の電位が設定される。

V t h = V n \_\_ p i x - V p \_\_ c o m = - ( V p \_\_ p i x - V n \_\_ c o m )

V s a t = V p \_\_ p i x - V p \_\_ c o m = - ( V n \_\_ p i x - V n \_\_ c o m )

尚、V p \_\_ p i x = V 1、V n \_\_ p i x = V 0

すなわち、 " H 1 x t 1 (前半の斜線部分) = H 2 x t 2 (後半の斜線部分) "となる

# [0024]

しかしながら、実際の画像表示装置にあっては、図8(B)に示すように基板材料に起因する電圧レベルシフトVsftが発生するので上記関係は成立せず、図8(B)に示すような状態となる。すなわち、Vn\_com及びVp\_comの電位が、図示例のように同じように下方向へVsftだけ電圧レベルシフトが発生することは避けられない。このため、H1 H2となって、"H1xt1 H2xt2"となっており、前半の斜線部分と後半の斜線部分の面積が異なり(液晶に印加される電圧が異なる)、この結果、サブフレームの前半と後半とで液晶に対する印加電圧の対称性が崩れてしまい、先に説明したように、フリッカー等の発生原因となっていた。

### [0025]

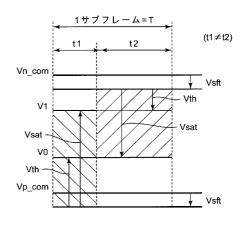

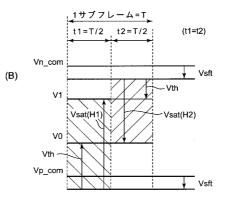

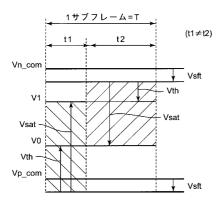

そこで、本発明では、図9に示すように上記前半表示期間 t 1 と後半表示期間 t 2 とを異ならせ(t 1 t 2)、上記電圧レベルシフトVsf t が生じた量を加味して、これを補償するようにt 1 と t 2 との比を設定し、"H 1 x t 1 = H 2 x t 2 "を満足させるようにしている。すなわち、前半の斜線部分と後半の斜線部分の面積が同じになるように上記 t 1 と t 2 との比を設定している。図9の場合には両者の印加時間の比 t 1 / t 2 は "0 . 6 "程度に設定して上記条件を満たすようにしている。ここで経験的に電圧レベルシフトVsf t の量が推測できるので、上記比 t 1 / t 2 は容易に求めることができる。

# [0026]

この印加時間の比 t 1 / t 2 は、例えば図 7 に示す表示パターンにおいて、SF1~SF8の全てにおいて同じになるように設定してもよいし、或いは、各サブフレームの表示期間の長さに対応させて、各サブフレーム毎に異なる比を設定するようにしてもよい。例えばサブフレームの表示期間が " 4 " の時は上記比 t 1 / t 2 を " 0 . 7 " とし、表示期間が " 8 " の時は上記比 t 1 / t 2 を " 0 . 7 5 " とするなど、表示期間の長さに応じて異なる比を設定する。ここで、図 7 は表示パターンの一例を示したに過ぎず、表示パターンによっては、異なるサブフレームでも表示期間が同じになるように設定する場合(表示期間が同じサブフレームが複数存在する場合)もあり、このような場合には、表示期間が同じサブフレーム同士に関しては、上記比 t 1 / t 2 を同一に設定すればよい。

#### [0027]

このように、各サブフレームにおいて前半と後半とで極性を反転させて印加する際に、 正極と負極の印加時間の比を最適化することにより印加電圧の対称性を向上させ、フリッカーと呼ばれる画像のちらつきや、直流電圧印加による液晶材料の劣化を抑制することが

20

できる。

尚、本発明方法は、反射型の画像表示装置のみならず、画素電極が透明な透過型の画像表示装置にも適用することができる。

【図面の簡単な説明】

[0028]

- 【図1】画像表示装置の一例としての投射型表示装置の概略構成を示す図である。

- 【図2】液晶を駆動する駆動電圧と出射光強度との関係を示すグラフである。

- 【図3】本発明における画像表示装置の駆動部と表示部を示す概略構成図である。

- 【図4】本発明に適用される画像表示装置の表示部の概略ブロック構成図である。

- 【図5】本発明に適用される画像表示装置の表示部における画素駆動回路の概略ブロック構成図である。

- 【図 6 】本発明に適用される画素電極及び対向電極に与える電圧の概略的なタイミングを 示すタイミングチャートである。

- 【図7】階調レベルとサブフレームとの間の表示パターンの一例を示す図である。

- 【図8】従来の画像表示装置の問題点を説明するための説明図である。

- 【図9】本発明の画像表示装置の駆動方法の一例を示す説明図である。

【符号の説明】

[0029]

4 1 … 駆動部、 4 2 … 表示部、 5 0 … サンプルホールド部、 6 0 … スイッチ部、 1 0 1 … 半導体基板、 1 0 2 … 透明基板、 C E … 対向電極、 L C … 液晶層、 P E … 画素電極、 P x … 画素。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

# 【図7】

|     | 表示期間     | 1        | 2        | 4  | 8        | 16           | 32  | . 64   | 128 |

|-----|----------|----------|----------|----|----------|--------------|-----|--------|-----|

|     | サブフレーム   | SF1      | SF2      | SF | SF4      | SF5          | SF6 | SF7    | SF8 |

|     | 階調レベル    | $\Gamma$ |          |    |          |              |     |        |     |

|     | 0        | 0        | 0        | 0  | 0        | 0            | 0   | 0      | 0   |

|     | 1        | 1        | 0        | 0  | 0        | 0            | 0   | 0      | 0   |

|     | 2        | 0        | 1        | 0  | 0        | 0            | 0   | 0      | Ö   |

| - 1 | 3        | 1        | 1        | 0  | 0        | 0            | 0   | 0      | 0   |

| ı   | 4        | 0        | 0        | 1  | 0        | 0            | 0   | 0      | 0   |

| - 1 | 5        | 1        | 0        | 1  | 0        | 0            | 0   | 0      | 0   |

| - [ | 6        | 0        | 1        | 1  | 0        | 0            | 0   | 0      | 0   |

| ı   | 7        | 1        | 1        | 1  | 0        | 0            | 0   | 0      | 0   |

| -   | 8        | 0        | 0        | 0  | 1        | 0            | 0   | 0      | 0   |

| -[  | 9        | 1        | 0        | 0  | 1        | 0            | 0   | 0      | 0   |

|     |          |          |          |    |          |              |     |        |     |

| -   | 14       | 0        | 1        | 1  | 1        | 0            | 0   | 0      | 0   |

| 1   | 15       | 1        | 1        | 1  | 1        | 0            | 0   | 0      | 0   |

|     | 16<br>17 | 0        | 0        | 0  | 0        | 1            | 0   | 0      | 0   |

| 1   | 17       | 1.1      | 0        | 0  | 0        | 1            | 0   | 0      | 0   |

| 1   | 30       | 0        | 1        | 1  | 1        | 1            | 0   | •      |     |

| ı   | 31       | 1        | 1        | 1  | 1        | 1            | 0   | 0<br>0 | 0   |

|     | 32       | Ö        | Ö        | o  | ò        | Ö            | 1   | 0      | 0   |

| 1   | 33       | 1        | 0        | 0  | 0        | 0            | 1   | 0      | 0   |

| 1   |          |          | •        | Ŭ  | •        | •            | '   | U      | 0   |

| 1   | 62       | 0        | 1        | 1  | 1        | 1            | 1   | 0      | o   |

| 1   | 63       | 1        | 1        | 1  | 1        | 1            | 1   | 0      | 0   |

|     | 64       | 0        | 0        | 0  | Ö        | o            | 0   | 1      | 0   |

|     | 65       | 1        | 0        | 0  | 0        | 0            | Ō   | 1      | ő   |

| ı   | 1        |          |          |    |          | -            | -   | •      | 0   |

| 1   | 126      | 0        | 1        | 1  | 1        | 1            | 1   | 1      | 0   |

| L   | 127      | 1        | 1        | 1  | 1        | 1            | 1   | 1      | ő   |

| L   | 128      | 0        | 0        | 0  | 0        | 0            | 0   | 0      | 1   |

| l   | 129      | 1        | 0        | 0  | 0        | 0            | 0   | 0      | 1   |

|     | 253      | 1        | 0        | 1  | 1        | 1            | 1   | 4      | . 1 |

| l   | 254      |          |          | 1  | 1        | 1            | 1   | 1      | 1   |

| 1   | 255      |          |          | i  | 1        | 1            | 1   | 1<br>1 | 1   |

| _   |          | -        | <u> </u> | -  | <u> </u> | <del>'</del> |     |        | 1   |

# 【図8】

Vth=Vn\_pix-Vp\_com = -(Vp\_pix-Vn\_com) Vsat=Vp\_pix-Vp\_com = -(Vn\_pix-Vn\_com) サブフレーム前半:Vp\_pix=V0,Vn\_pix=V1 サブフレーム後半:Vp\_pix=V1,Vn\_pix=V0

# 【図9】

# フロントページの続き

F I テーマコード (参考)

G 0 9 G 3/20 6 7 0 K

G 0 2 F 1/133 5 2 5

G 0 2 F 1/133 5 5 0

G 0 2 F 1/133 5 7 5

F ターム(参考) 5C080 AA10 BB05 DD06 DD18 EE29 FF11 JJ02 JJ04 JJ05 JJ06 KK43

| 专利名称(译)        | 用于驱动图像显示设备的方法                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|--|--|

| 公开(公告)号        | <u>JP2008122839A</u>                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2008-05-29 |  |  |  |  |  |

| 申请号            | JP2006308963                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2006-11-15 |  |  |  |  |  |

| [标]申请(专利权)人(译) | 日本胜利株式会社                                                                                                                                                                                                                                                                                                                                                                                |         |            |  |  |  |  |  |

| 申请(专利权)人(译)    | 日本有限公司Victor公司                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |  |  |  |

| [标]发明人         | 河田浩志                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |  |  |  |

| 发明人            | 河田 浩志                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |  |  |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |  |  |  |

| FI分类号          | G09G3/36 G09G3/20.641.E G09G3/20.621.B G09G3/20.621.A G09G3/20.611.E G09G3/20.670.K G02F1/133.525 G02F1/133.550 G02F1/133.575                                                                                                                                                                                                                                                           |         |            |  |  |  |  |  |

| F-TERM分类号      | 2H093/NA33 2H093/NA34 2H093/NB01 2H093/NC23 2H093/NC34 2H093/ND10 2H093/ND12 2H093 /ND34 2H093/ND35 2H093/ND47 2H093/NG02 5C006/AA14 5C006/AC26 5C006/AF44 5C006/AF71 5C006/BB16 5C006/EC11 5C006/FA23 5C006/FA33 5C080/AA10 5C080/BB05 5C080/DD06 5C080 /DD18 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C080/KK43 2H193/ZA04 2H193/ZC15 2H193/ZC20 2H193/ZR02 |         |            |  |  |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |  |  |

# 摘要(译)

要解决的问题:抑制由于闪烁或施加直流电压引起的液晶材料的劣化。解决方案:在用于通过将像素信号施加到具有以矩阵形成的多个像素的显示单元42来驱动用于显示图像的图像显示装置的方法中,通过设置在表面上形成有取向层的多个像素电极PE和反电极CE具有形成在表面上的取向层,彼此相对,液晶LC介于其间,图像显示装置通过从多个子帧构成每个帧来显示具有多个灰度的图像并且选择性地打开或关闭子帧,其中每个子帧的显示周期被分成前半显示周期和后半显示周期,极性在前半显示周期和后半显示周期之间反转,并且将上半显示周期的长度与后半显示周期的长度的比率确定为f的长度的乘积。第一半显示周期和像素电极与对电极之间的电位差等于第二半显示周期的长度与像素电极和对电极之间的电位差的乘积。Ž