(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-11336

(P2007-11336A)

(43) 公開日 平成19年1月18日(2007.1.18)

| (51) Int.C1.                | F 1                          | テーマコード (参考)                         |

|-----------------------------|------------------------------|-------------------------------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36                    | 2 H 093                             |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20                    | 5 C 006                             |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20                    | 5 C 080                             |

|                             | G09G 3/20                    | 6 2 2 E                             |

|                             | G09G 3/20                    | 6 1 1 J                             |

|                             | G09G 3/20                    | 6 2 2 D                             |

|                             | G09G 3/20                    | 6 1 2 K                             |

|                             |                              | 審査請求 有 請求項の数 41 O L (全 48 頁) 最終頁に続く |

| (21) 出願番号                   | 特願2006-171649 (P2006-171649) | (71) 出願人 599127667                  |

| (22) 出願日                    | 平成18年6月21日 (2006.6.21)       | エルジー フィリップス エルシーティー<br>カンパニー リミテッド  |

| (31) 優先権主張番号                | 10-2005-0058609              | 大韓民国 ソウル, ヨンドンポーク,<br>ヨイドードン 20     |

| (32) 優先日                    | 平成17年6月30日 (2005.6.30)       | (74) 代理人 100057874                  |

| (33) 優先権主張国                 | 韓国 (KR)                      | 弁理士 曽我 道照                           |

|                             |                              | (74) 代理人 100110423                  |

|                             |                              | 弁理士 曽我 道治                           |

|                             |                              | (74) 代理人 100084010                  |

|                             |                              | 弁理士 古川 秀利                           |

|                             |                              | (74) 代理人 100094695                  |

|                             |                              | 弁理士 鈴木 憲七                           |

|                             |                              | (74) 代理人 100111648                  |

|                             |                              | 弁理士 梶並 順                            |

|                             |                              | 最終頁に続く                              |

(54) 【発明の名称】表示装置の駆動回路及びその駆動方法

## (57) 【要約】

【課題】液晶パネルのゲートラインに供給されるスキャンパルスの歪みを防止できる表示装置及びその駆動方法を提供する。

【解決手段】表示部に備えられたゲートラインの一側に順に第1スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する第1シフトレジスタと、前記ゲートラインの他側に順に第2スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する第2シフトレジスタを備える表示装置の駆動回路を提供する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

表示部に備えられたゲートラインの一側に順に第1スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する第1シフトレジスタと、

前記ゲートラインの他側に順に第2スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する第2シフトレジスタと

を備えて構成されることを特徴とする、表示装置の駆動回路。

**【請求項 2】**

第 $n+1$ ゲートライン( $n$ は、自然数)を駆動するための第1スキャンパルスは、第 $n$ ゲートラインを駆動するための第1スキャンパルスがアクティブ状態を維持する期間内に、前記第 $n+1$ ゲートラインに供給されることを特徴とする、請求項1に記載の表示装置の駆動回路。

**【請求項 3】**

第 $n+1$ ゲートライン( $n$ は、自然数)を駆動するための第2スキャンパルスは、第 $n$ ゲートラインを駆動するための第2スキャンパルスがアクティブ状態を維持する期間内に、前記第 $n+1$ ゲートラインに供給されることを特徴とする、請求項1に記載の表示装置の駆動回路。

**【請求項 4】**

前記第1及び第2シフトレジスタに互いに位相差を有する複数のクロックパルスを供給するタイミングコントローラをさらに備えることを特徴とする、請求項1に記載の表示装置の駆動回路。

**【請求項 5】**

各クロックパルスは順に出力され、先に出力されたクロックパルスがアクティブ状態を維持する期間内に出力されることを特徴とする、請求項4に記載の表示装置の駆動回路。

**【請求項 6】**

各クロックパルス同士が同時にアクティブ状態を有する期間の大きさと各スキャンパルス同士が同時にアクティブ状態を有する期間の大きさとが同一であることを特徴とする、請求項5に記載の表示装置の駆動回路。

**【請求項 7】**

前記第1シフトレジスタは、各第1スキャンパルスを各ゲートラインの一側に供給し、一方向に配列された複数のステージを備え、

前記第2シフトレジスタは、各第2スキャンパルスを各ゲートラインの他側に供給し、一方向に配列された複数のステージを備えることを特徴とする、請求項1に記載の表示装置の駆動回路。

**【請求項 8】**

第1シフトレジスタに備えられた各ステージは、前のステージからの第1スキャンパルスに応答してイネーブルされて第1スキャンパルスを出力し、次のステージからの第1スキャンパルスに応答してディセーブルされることを特徴とする、請求項7に記載の表示装置の駆動回路。

**【請求項 9】**

第1シフトレジスタに備えられた第 $n$ ステージ( $n$ は、自然数)は、第 $n-1$ ステージからの第1スキャンパルスに応答してイネーブルされて第1スキャンパルスを出力し、第 $n+2$ ステージからの第1スキャンパルスに応答してディセーブルされることを特徴とする、請求項8に記載の表示装置の駆動回路。

**【請求項 10】**

前記第1シフトレジスタに備えられた第1ステージは、外部からの第1スタートパルスに応答してイネーブルされ、第2ステージは外部からの第2スタートパルスに応答してイネーブルされることを特徴とする、請求項9に記載の表示装置の駆動回路。

10

20

30

40

50

**【請求項 1 1】**

前記第1シフトレジスタは、

最後に位置したステージをディセーブルさせるためのスキャンパルスを出力する第1ダミーステージと、

前記最後に位置したステージの直前に位置したステージをディセーブルさせるためのスキャンパルスを出力する第2ダミーステージと

をさらに備えることを特徴とする、請求項9に記載の表示装置の駆動回路。

**【請求項 1 2】**

前記第2ダミーステージは、第1ダミーステージからのスキャンパルスに応答してイネーブルされることを特徴とする、請求項11に記載の表示装置の駆動回路。

**【請求項 1 3】**

第1シフトレジスタに備えられた各ステージは、

第1、第2及び第3ノードの論理状態を制御するノード制御部と、

前記第1、第2及び第3ノードの論理状態によって前記スキャンパルス及び非駆動用電圧源のうち一つを出力してゲートライン、次のステージ及び前のステージに供給する出力部と、

を備えることを特徴とする、請求項7に記載の表示装置の駆動回路。

**【請求項 1 4】**

前記第1シフトレジスタに備えられた第nステージのノード制御部は、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第1ノードを第1電圧源で充電させる第1スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第2ノードを第2電圧源で放電させる第2スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第3ノードを第2電圧源で放電させる第3スイッチング素子と、

フレームごとに異なる極性を有する第3電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第2ノードを第3電圧源で充電させる第4スイッチング素子と、

第3電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第3ノードを第2電圧源で放電させる第5スイッチング素子と、

第4電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第3ノードを前記第4電圧源で充電させる第6スイッチング素子と、

第4電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第2ノードを第2電圧源で放電させる第7スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第2ノードを第2電圧源で放電させる第8スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第3ノードを第2電圧源で放電させる第9スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第1ノードを第2電圧源で放電させる第10スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第1ノードを第2電圧源で放電させる第11スイッチング素子と、

第n+2ステージからのスキャンパルスに応答して、第1ノードを第2電圧源で放電させる第12スイッチング素子と

を備えることを特徴とする、請求項13に記載の表示装置の駆動回路。

**【請求項 1 5】**

前記第1シフトレジスタに備えられた第nステージの出力部は、

第1ノードに充電された第1電圧源に応答してスキャンパルスをゲートライン、第n+1ステージ及び第n-2ステージに供給する第13スイッチング素子と、

第2ノードに充電された第3電圧源に応答して第2電圧源をゲートライン、第n+1ステージ及び第n-2ステージに供給する第14スイッチング素子と、

第3ノードに充電された第4電圧源に応答して第2電圧源をゲートライン、第n+1ステージ及び第n-2ステージに供給する第15スイッチング素子と

を備えて構成されることを特徴とする、請求項14に記載の表示装置の駆動回路。

【請求項16】

前記第1シフトレジスタに備えられた第nステージのノード制御部は、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第1ノードを第1電圧源で充電させる第1スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第2ノードを第2電圧源で放電させる第2スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第3ノードを第2電圧源で放電させる第3スイッチング素子と、

フレームごとに異なる極性を有する第3電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第3電圧源を出力する第4スイッチング素子と、

前記第4スイッチング素子から出力された前記第3電圧源に応答して、第2ノードを第3電圧源で充電させる第5スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第1ノードを第2電圧源で放電させる第6スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第3ノードを第2電圧源で放電させる第7スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第5スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第5スイッチング素子をターンオフさせる第8スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第5スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第5スイッチング素子をターンオフさせる第9スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第5スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第5スイッチング素子をターンオフさせる第10スイッチング素子と、

フレームごとに異なる極性を有し、前記第3電圧源に反転された極性を有する第4電圧源に応答して、ターンオンまたはターンオフされ、ターンオン時に前記第4電圧源を出力する第11スイッチング素子と、

前記第11スイッチング素子から出力された第4電圧源に応答して、第3ノードを前記第4電圧源で充電させる第12スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第1ノードを第2電圧源で放電させる第13スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2ノードを第2電圧源で放電させる第14スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第15スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第16スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第17スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第2ノードを第2電圧源で放電させる第18スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第3ノードを第2電圧源で放電させる第19スイッチング素子と、

10

20

30

40

50

第  $n + 2$  ステージからのスキャンパルスに応答して、第 1 ノードを第 2 電圧源で放電させる第 20 スイッチング素子と

を備えることを特徴とする、請求項 13 に記載の表示装置の駆動回路。

【請求項 17】

前記第 1 シフトレジスタに備えられた第  $n$  ステージの出力部は、

第 1 ノードに充電された第 1 電圧源に応答して、スキャンパルスをゲートライン、第  $n + 1$  ステージ及び第  $n - 2$  ステージに供給する第 21 スイッチング素子と、

第 2 ノードに充電された第 3 電圧源に応答して、第 2 電圧源をゲートライン、第  $n + 1$  ステージ及び第  $n - 2$  ステージに供給する第 22 スイッチング素子と、

第 3 ノードに充電された第 4 電圧源に応答して、第 2 電圧源をゲートライン、第  $n + 1$  10 ステージ及び第  $n - 2$  ステージに供給する第 23 スイッチング素子と

を備えて構成されることを特徴とする、請求項 16 に記載の表示装置の駆動回路。

【請求項 18】

第 1 シフトレジスタに備えられた各ステージは、

第 1、第 2 及び第 3 ノードの論理状態を制御するノード制御部と、

前記第 1、第 2 及び第 3 ノードの論理状態によって前記スキャンパルス及び非駆動用電圧源のうち一つを出力してゲートラインに供給する第 1 出力部と、

前記第 1、第 2 及び第 3 ノードの論理状態によって前記スキャンパルス及び非駆動用電圧源のうち一つを出力して前のステージ及び次のステージに供給する第 2 出力部と

20 を備えることを特徴とする、請求項 7 に記載の表示装置の駆動回路。

【請求項 19】

前記第 1 シフトレジスタに備えられた第  $n$  ステージのノード制御部は、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 1 ノードを第 1 電圧源で充電させる第 1 スイッチング素子と、

第 1 ノードに充電された第 1 電圧源に応答して、第 2 ノードを第 2 電圧源で放電させる第 2 スイッチング素子と、

第 1 ノードに充電された第 1 電圧源に応答して、第 3 ノードを第 2 電圧源で放電させる第 3 スイッチング素子と、

フレームごとに異なる極性を有する第 3 電圧源に応答してターンオンまたはターンオフされ、ターンオン時に前記第 3 電圧源を出力する第 4 スイッチング素子と、

前記第 4 スイッチング素子から出力された前記第 3 電圧源に応答して、第 2 ノードを第 3 電圧源で充電させる第 5 スイッチング素子と、

第 2 ノードに充電された第 3 電圧源に応答して、第 1 ノードを第 2 電圧源で放電させる第 6 スイッチング素子と、

第 2 ノードに充電された第 3 電圧源に応答して、第 3 ノードを第 2 電圧源で放電させる第 7 スイッチング素子と、

第 1 ノードに充電された第 1 電圧源に応答して、第 5 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 5 スイッチング素子をターンオフさせる第 8 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 5 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 5 スイッチング素子をターンオフさせる第 9 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 5 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 5 スイッチング素子をターンオフさせる第 10 スイッチング素子と、

フレームごとに異なる極性を有し、前記第 3 電圧源に反転された極性を有する第 4 電圧源に応答して、ターンオンまたはターンオフされ、ターンオン時に前記第 4 電圧源を出力する第 11 スイッチング素子と、

前記第 11 スイッチング素子から出力された第 4 電圧源に応答して、第 3 ノードを前記第 4 電圧源で充電させる第 12 スイッチング素子と、

10

20

30

40

50

第3ノードに充電された第4電圧源に応答して、第1ノードを第2電圧源で放電させる第13スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2ノードを第2電圧源で放電させる第14スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第15スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第16スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第17スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第2ノードを第2電圧源で放電させる第18スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第3ノードを第2電圧源で放電させる第19スイッチング素子と、

第n+2ステージからのスキャンパルスに応答して、第1ノードを第2電圧源で放電させる第20スイッチング素子と

を備えることを特徴とする、請求項18に記載の表示装置の駆動回路。

#### 【請求項20】

前記第1シフトレジスタに備えられた第nステージの第1出力部は、

第1ノードに充電された第1電圧源に応答して、スキャンパルスをゲートラインに供給する第21スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第2電圧源をゲートラインに供給する第22スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2電圧源をゲートラインに供給する第23スイッチング素子と

を備えて構成されることを特徴とする、請求項19に記載の表示装置の駆動回路。

#### 【請求項21】

前記第1シフトレジスタに備えられた第nステージの第2出力部は、

第1ノードに充電された第1電圧源に応答してスキャンパルスを第n+1ステージ及び第n-2ステージに供給する第24スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第2電圧源を第n+1ステージ及び第n-2ステージに供給する第25スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2電圧源を第n+1ステージ及び第n-2ステージに供給する第26スイッチング素子と

を備えて構成されることを特徴とする、請求項20に記載の表示装置の駆動回路。

#### 【請求項22】

第2シフトレジスタに備えられた各ステージは、前のステージからの第2スキャンパルスに応答してイネーブルされて第2スキャンパルスを出力し、次のステージからの第2スキャンパルスに応答してディセーブルされることを特徴とする、請求項7に記載の表示装置の駆動回路。

#### 【請求項23】

第2シフトレジスタに備えられた第nステージ(nは、自然数)は、第n-1ステージからの第2スキャンパルスに応答してイネーブルされて第2スキャンパルスを出力し、第n+2ステージからの第2スキャンパルスに応答してディセーブルされることを特徴とする、請求項22に記載の表示装置の駆動回路。

#### 【請求項24】

前記第2シフトレジスタに備えられた第1ステージは、外部からの第1スタートパルス

10

20

30

40

50

に応答してイネーブルされ、第2ステージは外部からの第2スタートパルスに応答してイネーブルされることを特徴とする、請求項23に記載の表示装置の駆動回路。

【請求項25】

前記第2シフトレジスタは、最後に位置したステージをディセーブルさせるためのスキャンパルスを出力する第1ダミーステージと、

前記最後に位置したステージの直前に位置したステージをディセーブルさせるためのスキャンパルスを出力する第2ダミーステージと

をさらに備えることを特徴とする、請求項23に記載の表示装置の駆動回路。

【請求項26】

前記第2ダミーステージは、第1ダミーステージからのスキャンパルスに応答してイネーブルされることを特徴とする、請求項27に記載の表示装置の駆動回路。 10

【請求項27】

第2シフトレジスタに備えられた各ステージは、

第1、第2及び第3ノードの論理状態を制御するノード制御部と、

前記第1、第2及び第3ノードの論理状態によって前記スキャンパルス及び非駆動用電圧源のうち一つを出力してゲートライン、次のステージ及び前のステージに供給する出力部と

を備えることを特徴とする、請求項7に記載の表示装置の駆動回路。

【請求項28】

前記第2シフトレジスタに備えられた第nステージのノード制御部は、 20

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第1ノードを第1電圧源で充電させる第1スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第2ノードを第2電圧源で放電させる第2スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第3ノードを第2電圧源で放電させる第3スイッチング素子と、

フレームごとに異なる極性を有する第3電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第2ノードを第3電圧源で充電させる第4スイッチング素子と、

第3電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第3ノードを第2電圧源で放電させる第5スイッチング素子と、 30

第4電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第3ノードを前記第4電圧源で充電させる第6スイッチング素子と、

第4電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第2ノードを第2電圧源で放電させる第7スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第2ノードを第2電圧源で放電させる第8スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第3ノードを第2電圧源で放電させる第9スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第1ノードを第2電圧源で放電させる第10スイッチング素子と、 40

第3ノードに充電された第4電圧源に応答して、第1ノードを第2電圧源で放電させる第11スイッチング素子と、

第n+2ステージからのスキャンパルスに応答して、第1ノードを第2電圧源で放電させる第12スイッチング素子と

を備えることを特徴とする、請求項27に記載の表示装置の駆動回路。

【請求項29】

前記第2シフトレジスタに備えられた第nステージの出力部は、

第1ノードに充電された第1電圧源に応答してスキャンパルスをゲートライン、第n+1ステージ及び第n-2ステージに供給する第13スイッチング素子と、

第2ノードに充電された第3電圧源に応答して第2電圧源をゲートライン、第n+1ス 50

ステージ及び第  $n - 2$  ステージに供給する第 14 スイッチング素子と、

第 3 ノードに充電された第 4 電圧源に応答して第 2 電圧源をゲートライン、第  $n + 1$  ステージ及び第  $n - 2$  ステージに供給する第 15 スイッチング素子と

を備えて構成されることを特徴とする、請求項 28 に記載の表示装置の駆動回路。

【請求項 30】

前記第 2 シフトレジスタに備えられた第  $n$  ステージのノード制御部は、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 1 ノードを第 1 電圧源で充電させる第 1 スイッチング素子と、

第 1 ノードに充電された第 1 電圧源に応答して、第 2 ノードを第 2 電圧源で放電させる第 2 スイッチング素子と、

第 1 ノードに充電された第 1 電圧源に応答して、第 3 ノードを第 2 電圧源で放電させる第 3 スイッチング素子と、

フレームごとに異なる極性を有する第 3 電圧源に応答してターンオンまたはターンオフされ、ターンオン時に第 3 電圧源を出力する第 4 スイッチング素子と、

前記第 4 スイッチング素子から出力された前記第 3 電圧源に応答して、第 2 ノードを第 3 電圧源で充電させる第 5 スイッチング素子と、

第 2 ノードに充電された第 3 電圧源に応答して、第 1 ノードを第 2 電圧源で放電させる第 6 スイッチング素子と、

第 2 ノードに充電された第 3 電圧源に応答して、第 3 ノードを第 2 電圧源で放電させる第 7 スイッチング素子と、

第 1 ノードに充電された第 1 電圧源に応答して、第 5 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 5 スイッチング素子をターンオフさせる第 8 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 5 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 5 スイッチング素子をターンオフさせる第 9 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 5 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 5 スイッチング素子をターンオフさせる第 10 スイッチング素子と、

フレームごとに異なる極性を有し、前記第 3 電圧源に反転された極性を有する第 4 電圧源に応答して、ターンオンまたはターンオフされ、ターンオン時に前記第 4 電圧源を出力する第 11 スイッチング素子と、

前記第 11 スイッチング素子から出力された第 4 電圧源に応答して、第 3 ノードを前記第 4 電圧源で充電させる第 12 スイッチング素子と、

第 3 ノードに充電された第 4 電圧源に応答して、第 1 ノードを第 2 電圧源で放電させる第 13 スイッチング素子と、

第 3 ノードに充電された第 4 電圧源に応答して、第 2 ノードを第 2 電圧源で放電させる第 14 スイッチング素子と、

第 1 ノードに充電された第 1 電圧源に応答して、前記第 12 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 12 スイッチング素子をターンオフさせる第 15 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、前記第 12 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 12 スイッチング素子をターンオフさせる第 16 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、前記第 12 スイッチング素子のゲート端子に第 2 電圧源を供給することによって、前記第 12 スイッチング素子をターンオフさせる第 17 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 2 ノードを第 2 電圧源で放電させる第 18 スイッチング素子と、

スタートパルスまたは第  $n - 1$  ステージからのスキャンパルスに応答して、第 3 ノード

10

20

30

40

50

を第2電圧源で放電させる第19スイッチング素子と、

第n+2ステージからのスキャンパルスに応答して、第1ノードを第2電圧源で放電させる第20スイッチング素子と

を備えることを特徴とする、請求項27に記載の表示装置の駆動回路。

【請求項31】

前記第2シフトレジスタに備えられた第nステージの出力部は、

第1ノードに充電された第1電圧源に応答して、スキャンパルスをゲートライン、第n+1ステージ及び第n-2ステージに供給する第21スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第2電圧源をゲートライン、第n+1ステージ及び第n-2ステージに供給する第22スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2電圧源をゲートライン、第n+1ステージ及び第n-2ステージに供給する第23スイッチング素子と

を備えて構成されることを特徴とする、請求項30に記載の表示装置の駆動回路。

【請求項32】

第2シフトレジスタに備えられた各ステージは、

第1、第2及び第3ノードの論理状態を制御するノード制御部と、

前記第1、第2及び第3ノードの論理状態によって前記スキャンパルス及び非駆動用電圧源のうち一つを出力してゲートラインに供給する第1出力部と、

前記第1、第2及び第3ノードの論理状態によって前記スキャンパルス及び非駆動用電圧源のうち一つを出力して前のステージ及び次のステージに供給する第2出力部と

を備えることを特徴とする、請求項7に記載の表示装置の駆動回路。

【請求項33】

前記第2シフトレジスタに備えられた第nステージのノード制御部は、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第1ノードを第1電圧源で充電させる第1スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第2ノードを第2電圧源で放電させる第2スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第3ノードを第2電圧源で放電させる第3スイッチング素子と、

フレームごとに異なる極性を有する第3電圧源に応答してターンオンまたはターンオフされ、ターンオン時に前記第3電圧源を出力する第4スイッチング素子と、

前記第4スイッチング素子から出力された前記第3電圧源に応答して、第2ノードを第3電圧源で充電させる第5スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第1ノードを第2電圧源で放電させる第6スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第3ノードを第2電圧源で放電させる第7スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、第5スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第5スイッチング素子をターンオフさせる第8スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第5スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第5スイッチング素子をターンオフさせる第9スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第5スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第5スイッチング素子をターンオフさせる第10スイッチング素子と、

フレームごとに異なる極性を有し、前記第3電圧源に反転された極性を有する第4電圧源に応答して、ターンオンまたはターンオフされ、ターンオン時に前記第4電圧源を出力する第11スイッチング素子と、

前記第11スイッチング素子から出力された第4電圧源に応答して、第3ノードを前記

10

20

30

40

50

第4電圧源で充電させる第12スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第1ノードを第2電圧源で放電させる第13スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2ノードを第2電圧源で放電させる第14スイッチング素子と、

第1ノードに充電された第1電圧源に応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第15スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第16スイッチング素子と、10

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、前記第12スイッチング素子のゲート端子に第2電圧源を供給することによって、前記第12スイッチング素子をターンオフさせる第17スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第2ノードを第2電圧源で放電させる第18スイッチング素子と、

スタートパルスまたは第n-1ステージからのスキャンパルスに応答して、第3ノードを第2電圧源で放電させる第19スイッチング素子と、

第n+2ステージからのスキャンパルスに応答して、第1ノードを第2電圧源で放電させる第20スイッチング素子と20

を備えることを特徴とする、請求項32に記載の表示装置の駆動回路。

【請求項34】

前記第2シフトレジスタに備えられた第nステージの第1出力部は、

第1ノードに充電された第1電圧源に応答して、スキャンパルスをゲートラインに供給する第21スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第2電圧源をゲートラインに供給する第22スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2電圧源をゲートラインに供給する第23スイッチング素子と

を備えて構成されることを特徴とする、請求項33に記載の表示装置の駆動回路。30

【請求項35】

前記第2シフトレジスタに備えられた第nステージの第2出力部は、

第1ノードに充電された第1電圧源に応答してスキャンパルスを第n+1ステージ及び第n-2ステージに供給する第24スイッチング素子と、

第2ノードに充電された第3電圧源に応答して、第2電圧源を第n+1ステージ及び第n-2ステージに供給する第25スイッチング素子と、

第3ノードに充電された第4電圧源に応答して、第2電圧源を第n+1ステージ及び第n-2ステージに供給する第26スイッチング素子と

を備えて構成されることを特徴とする、請求項34に記載の表示装置の駆動回路。40

【請求項36】

表示部に備えられたゲートラインの一側に順に第1スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する段階と、

前記ゲートラインの他側に順に第2スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する段階と

を備えてなることを特徴とする、表示装置の駆動方法。

【請求項37】

第n+1ゲートライン(nは、自然数)を駆動するための第1スキャンパルスは、第nゲートラインを駆動するための第1スキャンパルスがアクティブ状態を維持する期間内に50

、前記第 n ゲートラインに供給されることを特徴とする、請求項 3 6 に記載の表示装置の駆動方法。

【請求項 3 8】

第 n + 1 ゲートライン ( n は、自然数 ) を駆動するための第 2 スキャンパルスは、第 n ゲートラインを駆動するための第 2 スキャンパルスがアクティブ状態を維持する期間内に、前記第 n ゲートラインに供給されることを特徴とする、請求項 3 6 に記載の表示装置の駆動方法。

【請求項 3 9】

前記第 1 及び第 2 シフトレジスタに互いに位相差を有する複数のクロックパルスを供給する段階をさらに備えてなることを特徴とする、請求項 3 6 に記載の表示装置の駆動方法。

【請求項 4 0】

各クロックパルスは順に出力され、先に出力されたクロックパルスがアクティブ状態を維持する期間内に出力されることを特徴とする、請求項 3 9 に記載の表示装置の駆動方法。

【請求項 4 1】

各クロックパルス同士が同時にアクティブ状態を有する期間の大きさと、各スキャンパルス同士が同時にアクティブ状態を有する期間の大きさとが同一であることを特徴とする、請求項 4 0 に記載の表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、表示装置の駆動回路に係り、特に、各スキャンパルス同士が一定時間の間に互いに重なるように各スキャンパルスのパルス幅を増加させて出力し、これによりスキャンパルスの歪みを防止することができる表示装置の駆動回路及びその駆動方法に関する。

【背景技術】

【0 0 0 2】

通常の液晶表示装置は、電界を用いて液晶の光透過率を調節することによって画像を表示する。このため、液晶表示装置は、画素領域がマトリクス状に配列された液晶パネルと、この液晶パネルを駆動するための駆動回路とを備える。

【0 0 0 3】

液晶パネルには、複数のゲートラインと複数のデータラインとが交差するように配列され、これらゲートラインとデータラインとが直交することによって定義される領域に画素領域が位置し、また、これら画素領域のそれぞれに電界を印加するための画素電極と共に電極が形成される。

【0 0 0 4】

これら画素電極のそれぞれは、スイッチング素子である薄膜トランジスタ ( TFT ; Thin Film Transistor ) のソース電極及びドレイン電極を介してデータラインに接続される。この薄膜トランジスタは、ゲートラインを介してゲート電極に印加されるスキャンパルスによってターンオンされ、データラインのデータ信号が画素電極に充電されるようする。

【0 0 0 5】

一方、駆動回路は、ゲートラインを駆動するためのゲートドライバと、データラインを駆動するためのデータドライバと、これらゲートドライバとデータドライバを制御するための制御信号を供給するタイミングコントローラと、液晶表示装置で用いられる種々の駆動電圧を供給する電源供給部とを備える。

【0 0 0 6】

ここで、タイミングコントローラは、ゲートドライバ及びデータドライバの駆動タイミングを制御するとともに、データドライバに画素データ信号を供給する。また、電源供給部は、入力電源を昇圧または降圧することによって、液晶表示装置で必要とする共通電圧

10

20

30

40

50

V C O M、ゲートハイ電圧信号V G H、ゲートロー電圧信号V G Lなどの駆動電圧を生成する。

【0007】

そして、ゲートドライバは、スキャンパルスをゲートラインに順次供給して、液晶パネル上の液晶セルを1ライン分ずつ順次駆動する。また、データドライバは、ゲートラインのいずれか一つにスキャンパルスが供給される度にデータラインのそれぞれに画素電圧信号を供給する。これにより、液晶表示装置は、液晶セル別に画素電圧信号によって画素電極と共に通電極との間に印加される電界によって光透過率を調節することによって画像を表示する。

【0008】

ここで、ゲートドライバは、上述のようなスキャンパルスを順次出力するようにシフトレジスタを備える。これを、添付の図面を参照してより具体的に説明すると、次の通りである。

【0009】

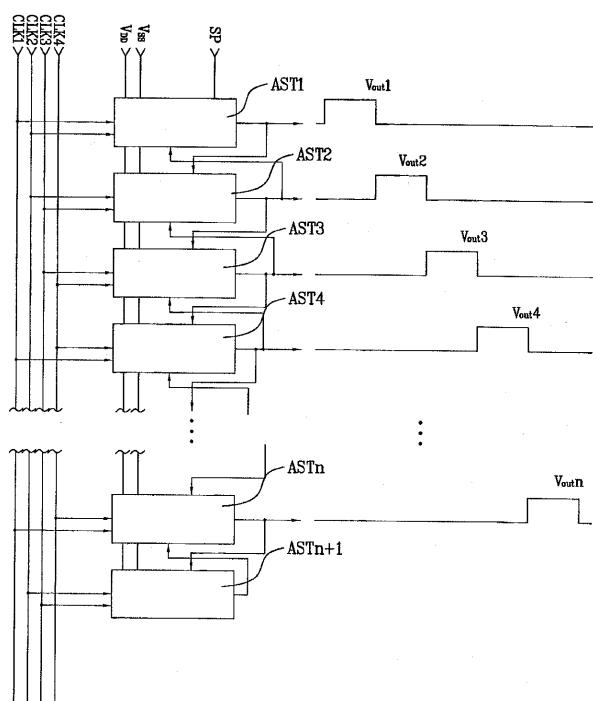

図1は、従来のシフトレジスタを示す図である。

【0010】

従来のシフトレジスタは、図1に示すように、互いに従属的に接続されたn個のステージA S T 1 ~ A S T n及び一つのダミーステージA S T n + 1で構成される。ここで、各ステージA S T 1 ~ A S T n + 1は、一つずつのスキャンパルスV o u t 1 ~ V o u t n + 1を出力する。すなわち、第1ステージA S T 1からダミーステージA S T n + 1まで順にスキャンパルスV o u t 1 ~ V o u t n + 1を出力する。このときに、ダミーステージA S T n + 1以外のステージA S T 1 ~ A S T nから出力されたスキャンパルスV o u t 1 ~ V o u t nは、液晶パネル((図示せず))のゲートラインに順次供給されてゲートラインを順次スキャニングするようになる。

【0011】

このように構成されたシフトレジスタの全体ステージA S T 1 ~ A S T n + 1には、第1電圧源V D D及び第2電圧源V S Sが印加され、互いに順次位相差を有する第1乃至第4クロックパルスC L K 1 ~ C L K 4のうち二つのクロックパルスが供給される。ここで、第1電圧源V D Dは正極性の電圧源を表し、第2電圧源V S Sは接地電圧を表す。

【0012】

ここで、ステージA S T 1 ~ A S T n + 1のうち最も上側に位置している第1ステージA S T 1には、第1電圧源V D D、第2電圧源V S S、及び二つのクロックパルスに加えてスタートパルスS Pが供給される。

【発明の開示】

【発明が解決しようとする課題】

【0013】

しかしながら、このように構成された従来のシフトレジスタには次のような問題点があった。

【0014】

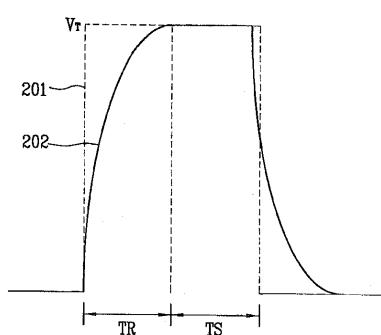

図2は、スキャンパルスの理想的な波形と歪んだスキャンパルスの波形を示す図である。

【0015】

液晶表示装置の大面積化に伴ってゲートラインの長さが増加し、これによりゲートラインの抵抗及びキャパシタンス成分も増加することになる。これにより、図2に示すように、抵抗及びキャパシタンス成分によってゲートラインに供給されるスキャンパルス201は歪むことがある。参照番号201は、ゲートラインに抵抗及びキャパシタンス成分がないと仮定したときの理想的なスキャンパルス201を表す。

【0016】

一方、スキャンパルス201が抵抗及びキャパシタンス成分によって歪むと、スキャンパルス201の立上り時間T Rが増加してその波形が歪んでしまう。参照番号202は、

10

20

30

40

50

ゲートラインの抵抗及びキャパシタンス成分によって歪んだ形態のスキャンパルスを表す。

【0017】

このように歪んだスキャンパルス202は、理想的なスキャンパルス201に比べて立ち上がり時間TRが長いため、相対的に目標電圧VTに保持される有効充電時間TSが短くなる。

【0018】

このように波形の歪んだスキャンパルス202が薄膜トランジスタのゲート電極に印加されると、該薄膜トランジスタのターンオン時間が短くなるため、ターンオンされた薄膜トランジスタがデータラインからのデータ電圧をスイッチングする時間も短くなってしまう。その結果、ターンオンされた薄膜トランジスタのドレイン／ソース端子を経由して画素電極に印加されるデータ電圧もその波形が歪み、該画素電極にはデータ電圧が十分に充電されなくなる。

【0019】

本発明は上記の問題点を解決するためのもので、その目的は、各スキャンパルス同士が一定時間互いに重なるように各スキャンパルスのパルス幅を増加させて出力し各スキャンパルスが目標電圧に保持される有効充電時間を増加させることによってスキャンパルスの歪みを防止できる表示装置の駆動回路及びその駆動方法を提供することにある。

【課題を解決するための手段】

【0020】

上記目的を達成するために、本発明に係る表示装置は、表示部に備えられたゲートラインの一側に順に第1スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する第1シフトレジスタと、前記ゲートラインの他側に順に第2スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する第2シフトレジスタとを備えて構成されることを特徴とする。

【0021】

また、上記の目的を達成するために、本発明に係る表示装置の駆動方法は、表示部に備えられたゲートラインの一側に順に第1スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する段階と、前記ゲートラインの他側に順に第2スキャンパルスを供給して前記ゲートラインを順に駆動するとともに、隣接する少なくとも二つのゲートラインを一定期間同時に駆動する段階とを備えてなることを特徴とする。

【発明の効果】

【0022】

本発明による液晶表示装置のシフトレジスタは、複数のスキャンパルスを順に出力し、このとき、隣接する時間に出力されるスキャンパルス同士のパルス幅が互いに所定区間重なるようにスキャンパルスのパルス幅を増加させて出力するため、各スキャンパルスの有効充電時間を増加させることが可能になる。しかも、上記のように各スキャンパルスの有効充電時間が増加すると、ゲートラインの抵抗及びキャパシタンス成分によってスキャンパルスに歪みが生じても、データ電圧を画素電極に正常に印加できるような充分な有効充電時間が確保可能になる。

【発明を実施するための最良の形態】

【0023】

以下、添付の図面を参照して、本発明に係る液晶表示装置の好適な実施の形態について詳細に説明する。

【0024】

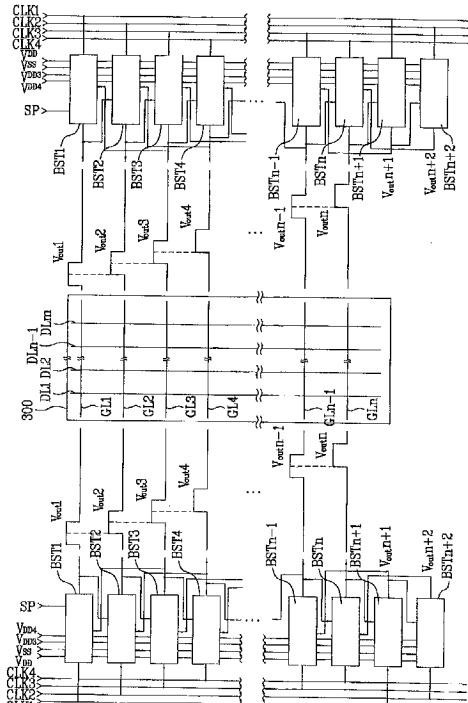

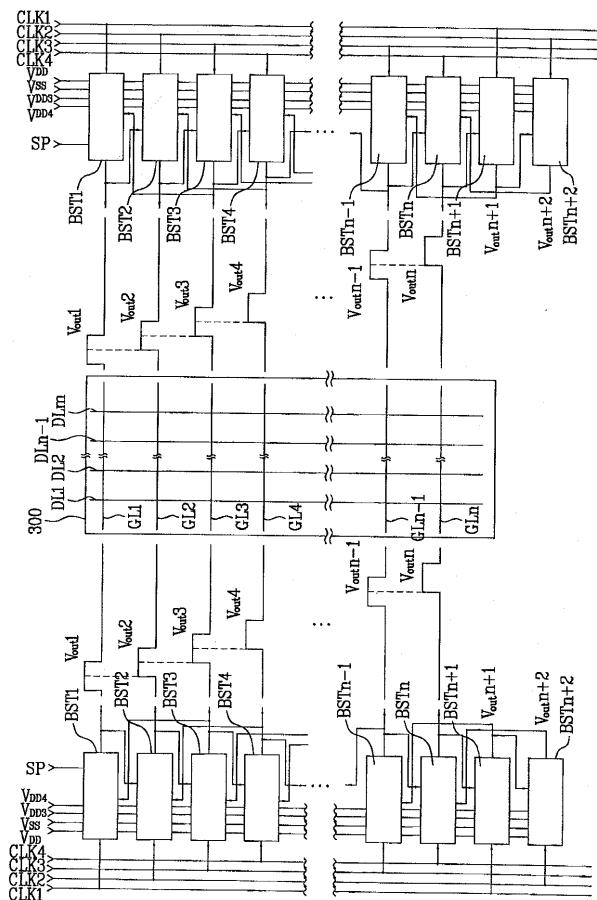

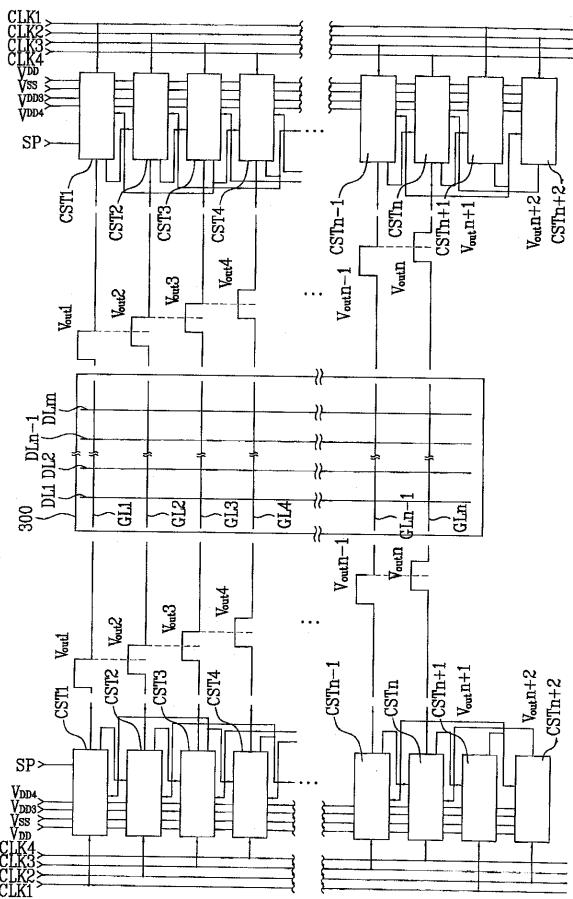

図3は、本発明の第1の実施の形態によるシフトレジスタの構成図である。

【0025】

本発明の第1の実施の形態による液晶表示装置のシフトレジスタは、図3に示すように

10

20

30

40

50

、タイミングコントローラからの各クロックパルス  $C L K 1 \sim C L K 4$  及びスタートパルス  $S P$  に応答して複数のスキャンパルス  $V_{out1} \sim V_{outn}$  を順に出力するものの、このとき、隣接するスキャンパルス  $V_{out1} \sim V_{outn}$  が一定時間だけ重なり合う区間を有するように各スキャンパルス  $V_{out1} \sim V_{outn}$  のパルス幅を増加させて液晶パネル 300 のゲートライン  $G L 1 \sim G L n$  に出力することを特徴とする。

## 【0026】

ここで、シフトレジスタは、第1及び第2シフトレジスタ  $301a, 301b$  からなる。すなわち、液晶パネル 300 の左側に配置される第1シフトレジスタ  $301a$  は、各ゲートライン  $G L 1 \sim G L n$  の一側にスキャンパルスを供給し、液晶パネル 300 の右側に配置された第2シフトレジスタ  $301b$  は、各ゲートライン  $G L 1 \sim G L n$  の他側にスキャンパルスを供給する。

## 【0027】

ここで、表示装置のサイズを減少させるには、第1及び第2シフトレジスタ  $301a, 301b$  が液晶パネル 300 に内蔵されることが好ましい。

## 【0028】

一方、液晶パネル 300 には、一方向に配列される複数のゲートライン  $G L 1 \sim G L n$  と、このゲートライン  $G L 1 \sim G L n$  に直交するように配列された複数のデータライン  $D L 1 \sim D L m$  とが形成されており、データライン  $D L 1 \sim D L m$  は、データドライバから出力されるデータ電圧によって充電される。

## 【0029】

また、ゲートライン  $G L 1 \sim G L n$  及びデータライン  $D L 1 \sim D L m$  に囲まれて定義される各画素領域にはそれぞれ、薄膜トランジスタ及び画素電極が形成される。具体的に、薄膜トランジスタは、各ゲートライン  $G L 1 \sim G L n$  と各データライン  $D L 1 \sim D L m$  とが交差する付近に形成される。薄膜トランジスタは、各ゲートライン  $G L 1 \sim G L n$  に充電されたスキャンパルス  $V_{out1} \sim V_{outn}$  に応答してデータライン  $D L 1 \sim D L m$  に充電されたデータ電圧をスイッチングして画素電極に印加することによって、液晶パネル 300 に画像が表示されるようとする。

## 【0030】

第1シフトレジスタ  $301a$  は、図3に示すように、互いに従属的に接続された  $n$  個のステージ  $B S T 1 \sim B S T n$ 、及び第1及び第2ダミーステージ  $B S T n + 1, B S T n + 2$  で構成される。ここで、各ステージ  $B S T 1 \sim B S T n + 2$  はスキャンパルス  $V_{out1} \sim V_{outn+2}$  を一つずつ出力し、このとき、第1ステージ  $B S T 1$  から第2ダミーステージ  $B S T n + 2$  まで順にスキャンパルス  $V_{out1} \sim V_{outn}$  を出力する。ここで、第1及び第2ダミーステージ  $B S T n + 1, B S T n + 2$  以外のステージ  $B S T 1 \sim B S T n$  から出力されたスキャンパルス  $V_{out1} \sim V_{outn}$  は、液晶パネル 300 (図示せず) のゲートライン  $G L 1 \sim G L n$  に順に供給され、ゲートライン  $G L 1 \sim G L n$  を順にスキャニングするようされる。

## 【0031】

第2シフトレジスタ  $301b$  も、第1シフトレジスタ  $301a$  と同じ構成を有する。したがって、第1シフトレジスタ  $301a$  に備えられた各ステージ  $B S T 1 \sim B S T n + 2$  から出力されるスキャンパルス  $V_{out1} \sim V_{outn+2}$  は、第2シフトレジスタ  $301b$  に備えられた各ステージ  $B S T 1 \sim B S T n + 2$  から出力されるスキャンパルス  $V_{out1} \sim V_{outn+2}$  と互いに同一である。

## 【0032】

例えば、第1シフトレジスタ  $301a$  に備えられた第1ステージ  $B S T 1$  から出力される第1スキャンパルス  $V_{out1}$  は、第2シフトレジスタ  $301b$  に備えられた第1ステージ  $B S T 1$  から出力される第1スキャンパルス  $V_{out1}$  と同じ時間に第1ゲートライン  $G L 1$  に供給される。

## 【0033】

これと同様に、第1シフトレジスタ  $301a$  に備えられた各ステージ  $B S T 1 \sim B S T$

10

20

30

40

50

$n + 2$ 、及び第2シフトレジスタ301bに備えられた各ステージB S T 1 ~ B S T  $n + 2$ は互いに一対一対応し、互いに同じスキャンパルスV o u t 1 ~ V o u t  $n + 2$ を出力するようになる。

【0034】

ただし、第1シフトレジスタ301aに備えられた各ステージB S T 1 ~ B S T  $n$ は、各ゲートラインG L 1 ~ G L  $n$ の一側にスキャンパルスV o u t 1 ~ V o u t  $n$ を印加し、第2シフトレジスタ301bに備えられた各ステージB S T 1 ~ B S T  $n$ は、各ゲートラインG L 1 ~ G L  $n$ の他側にスキャンパルスV o u t 1 ~ V o u t  $n$ を印加する。

【0035】

このように構成された第1シフトレジスタ301aの全体ステージB S T 1 ~ B S T  $n + 2$ には、第1乃至第4電圧源V D D、V S S、V D D 3、V D D 4そして互いに順次位相差をもって循環する第1乃至第4クロックパルスC L K 1 ~ C L K 4のうち一つのクロックパルスが印加される。ここで、第1電圧源V D Dは正極性の直流電圧源を表し、第2電圧源V S Sは負極性の電圧源を表す。そして、第3電圧源V D D 3及び第4電圧源V D D 4は、フレーム別に反転された極性を有する交流電圧源である。このとき、第3電圧源V D D 3は、第4電圧源V D D 4に反転された位相を有する。すなわち、同一フレーム内で第3電圧源V D D 3と第4電圧源V D D 4が異なる極性を表す。

【0036】

ここで、第1シフトレジスタ301aに備えられたステージC S T 1 ~ C S T  $n$ のうち最も上側に位置している第1ステージB S T 1には、第1乃至第4電圧源V D D、V S S、V D D 3、V D D 4、及び第1乃至第4クロックパルスC L K 1 ~ C L K 4のうち二つのクロックパルスのほか、スタートパルスS Pが供給される。

【0037】

一方、上述したように、第1乃至第4クロックパルスC L K 1 ~ C L K 4は互いに位相遅延されて出力される。すなわち、第2クロックパルスC L K 2は、第1クロックパルスC L K 1よりも位相遅延されて出力され、第3クロックパルスC L K 3は、第2クロックパルスC L K 2よりも位相遅延されて出力され、第4クロックパルスC L K 4は、第3クロックパルスC L K 3よりも位相遅延されて出力され、第1クロックパルスC L K 1は、第4クロックパルスC L K 4よりも位相遅延されて出力される。

【0038】

第1シフトレジスタ301aに備えられたステージC S T 1 ~ C S T  $n + 1$ のうち第1ステージB S T 1に印加されるスタートパルスS Pは、クロックパルスC L K 1 ~ C L K 4よりも先に出力される。また、スタートパルスS Pは、1フレームに一回のみ出力される。すなわち、毎フレームごとにスタートパルスS Pが最初に出力された後、第1乃至第4クロックパルスC L K 1 ~ C L K 4が順に出力される。

【0039】

このとき、第1乃至第4クロックパルスC L K 1 ~ C L K 4は順に出力され、且つ循環しながら出力される。すなわち、第1クロックパルスC L K 1から第4クロックパルスC L K 4まで順に出力された後、再び第1クロックパルスC L K 1から第4クロックパルスC L K 4まで順に出力される。したがって、第1クロックパルスC L K 1は、第4クロックパルスC L K 4と第2クロックパルスC L K 2間に該当する期間で出力される。ここで、第4クロックパルスC L K 4とスタートパルスS Pを互いに同期させ出力することができる。この場合は、第1乃至第4クロックパルスC L K 1 ~ C L K 4のうち第4クロックパルスC L K 4が最初に出力される。

【0040】

一方、本発明による第1シフトレジスタ301aは、二つ以上のクロックパルスを使用することができる。すなわち、本発明による第1シフトレジスタ301aは、第1乃至第4クロックパルスC L K 1 ~ C L K 4のうち第1及び第2クロックパルスC L K 1、C L K 2のみを使用しても良く、第1乃至第3クロックパルスC L K 1 ~ C L K 3のみを使用しても良い。また、本発明によるシフトレジスタは、順に出力される4個以上のクロック

10

20

30

40

50

パルスを使用しても良い。

【0041】

第2シフトレジスタ301bも、上述した第1シフトレジスタ301aと同じ構成を有する。

【0042】

このように構成されたシフトレジスタの動作について詳細に説明すると、次の通りである。

【0043】

ここでは、第1シフトレジスタ301aと第2シフトレジスタ301bは同一に動作するので、第1シフトレジスタ301aについてのみ説明する。

【0044】

まず、タイミングコントローラからのスタートパルスSPが第1ステージBST1に入力されると、第1ステージBST1は、スタートパルスSPに応答してイネーブルされる。続いて、イネーブルされた第1ステージBST1は、タイミングコントローラからの第1クロックパルスCLK1を受けて第1スキャンパルスVout1を出力し、これを第1ゲートラインGL1と第2ステージBST2に供給する。すると、第2ステージBST2は、第1スキャンパルスVout1に応答してイネーブルされる。

【0045】

その後、イネーブルされた第2ステージBST2は、タイミングコントローラからの第2クロックパルスCLK2を受けて第2スキャンパルスVout2を出力し、これを第2ゲートラインGL2と第3ステージBST3に供給する。すると、前記第3ステージBST3は、第2スキャンパルスVout2に応答してイネーブルされる。

【0046】

続いて、イネーブルされた第3ステージBST3は、タイミングコントローラからの第3クロックパルスCLK3を受けて第3スキャンパルスVout3を出力し、これを第3ゲートラインGL3、第4ステージBST4、及び第1ステージBST1に共に供給する。すると、第3スキャンパルスVout3に応答して第4ステージBST4はイネーブルされ、第1ステージBST1は、第3電圧源VSSを第1ゲートラインGL1に供給する。

【0047】

続いて、イネーブルされた第4ステージBST4は、タイミングコントローラからの第4クロックパルスCLK4を受けて第4スキャンパルスVout4を出力し、これを第4ゲートラインGL4と第5ステージに供給する。すると、第5ステージは、第4スキャンパルスVout4に応答してイネーブルされる。

【0048】

続いて、イネーブルされた第5ステージはタイミングコントローラからの第1クロックパルスCLK1を受けて第5スキャンパルスを出力し、これを第5ゲートライン、第6ステージ、及び第3ステージBST3に共に供給する。すると、第5スキャンパルスに応答して第6ステージはイネーブルされ、第3ステージBST3は、第3電圧源VSSを第3ゲートラインGL3に供給する。

【0049】

このような方式で、第6乃至第nステージBSTnまで順に第6乃至第nスキャンパルスVoutnを出力し、これらをそれぞれ第6乃至第nゲートラインGLnに順に供給する。このとき、隣接するスキャンパルス同士は一定時間だけ重なるパルス幅区間を有する。

【0050】

ここで、第1ダミーステージBSTn+1は、第n-1ステージBSTn-1に第n+1スキャンパルスVoutn+1を供給する役割を担い、第2ダミーステージBSTn+2300hは、第nステージBSTnに第n+2スキャンパルスVoutn+2を供給する役割を担う。すなわち、第1及び第2ダミーステージBSTn+1、BSTn+2から

10

20

30

40

50

出力された第  $n + 1$  及び第  $n + 2$  スキャンパルス  $V_{out\ n+1}$ 、 $V_{out\ n+2}$  はゲートラインには供給されなく、単に第  $n - 1$  及び第  $n$  ステージ  $BST_{n-1}$ 、 $BST_n$  が第 2 電圧源  $VSS$  を出力するようにする役割を担うダミー出力である。

#### 【0051】

このように各ステージは、スキャンパルス  $V_{out\ 1} \sim V_{out\ n}$  を出力し、これを対応するゲートライン  $GL_1 \sim GL_n$  にそれぞれ順に供給すると同時に、次のステージにスタートパルス  $SP$  として提供する。また、各ステージ  $BST_1 \sim BST_n$  は、次々のステージから出力されたスキャンパルスに応答して、対応するゲートラインに第 2 電圧源  $VSS$  を供給する。

#### 【0052】

第 2 シフトレジスタ  $301b$  も、上述した第 1 シフトレジスタ  $301a$  と同様に動作する。ただし、第 1 シフトレジスタ  $301a$  に備えられた各ステージ  $BST_1 \sim BST_n$  は、各ゲートライン  $GL_1 \sim GL_n$  の一側にスキャンパルス  $V_{out\ 1} \sim V_{out\ n}$  を印加し、第 2 シフトレジスタ  $301b$  に備えられた各ステージ  $BST_1 \sim BST_n$  は、各ゲートライン  $GL_1 \sim GL_n$  の他側にスキャンパルス  $V_{out\ 1} \sim V_{out\ n}$  を供給する。

#### 【0053】

このように第 1 及び第 2 シフトレジスタ  $301a$ 、 $301b$  に備えられた各ステージ  $BST_1 \sim BST_{n+2}$  が次のステージでなく、次々のステージから出力されたスキャンパルスを受け取る理由は、次の通りである。この理由を説明するに先立ち、各スキャンパルス  $V_{out\ 1} \sim V_{out\ n+2}$  及び第 1 乃至第 4 クロックパルス  $CLK_1 \sim CLK_4$  についてより具体的に説明する。ここで、全てのスキャンパルス  $V_{out\ 1} \sim V_{out\ n}$  はその波形が同一なので、第 1 乃至第 4 スキャンパルス  $V_{out\ 1}$  乃至  $V_{out\ 4}$  を挙げて説明するものとする。

#### 【0054】

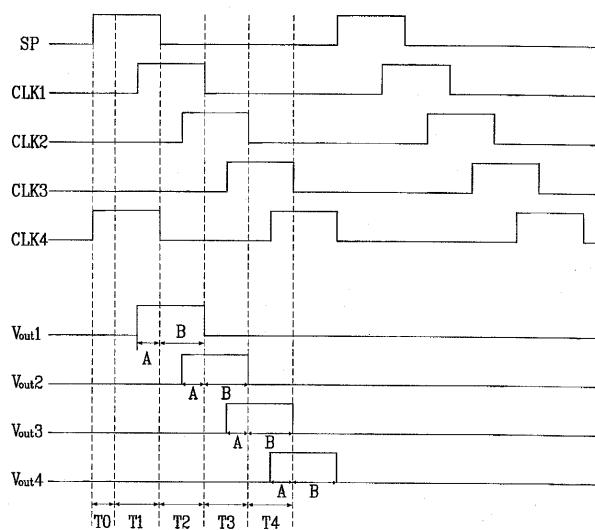

図 4 は、第 1 乃至第 4 クロックパルス、及び第 1 乃至第 4 スキャンパルスのタイミング図である。

#### 【0055】

まず、図 4 に示すように、第 1 乃至第 4 スキャンパルス  $V_{out\ 1} \sim V_{out\ 4}$  のパルス幅は、予備充電区間 A 及び有効充電区間 B に分けられ、各スキャンパルス  $V_{out\ 1} \sim V_{out\ 4}$  の予備充電区間 A は、以前スキャンパルスの有効充電区間 B と時間的に一部重なる。また、各スキャンパルス  $V_{out\ 1} \sim V_{out\ 4}$  の有効充電区間 B は、次のスキャンパルスの予備充電区間 A と時間的に一部重なる。

#### 【0056】

したがって、各スキャンパルス  $V_{out\ 1} \sim V_{out\ 4}$  は、以前スキャンパルスの有効充電区間 B で出力し始め自分の有効充電区間 B では目標電圧  $VT$  に到達するようになる。言い換えば、各スキャンパルス  $V_{out\ 1} \sim V_{out\ 4}$  は、自分の予備充電区間 A で目標電圧  $VT$  に向けて徐々に増加し、以後自分の有効充電区間 B では完全に目標電圧  $VT$  に維持される。

#### 【0057】

すなわち、第 1 スキャンパルス  $V_{out\ 1}$  は、自分の予備充電区間 A に該当するスタートパルス  $SP$  の一区間で出力し始め、自分の有効充電区間 B では目標電圧  $VT$  に完全に維持される。そして、第 2 スキャンパルス  $V_{out\ 2}$  は、自分の予備充電区間 A に該当する第 1 スキャンパルス  $V_{out\ 1}$  の有効充電区間で出力し始め、自分の有効充電区間 B では完全に目標電圧  $VT$  に維持される。

#### 【0058】

そして、第 3 スキャンパルス  $V_{out\ 3}$  は、自分の予備充電区間 A に該当する前記第 2 スキャンパルス  $V_{out\ 2}$  の有効充電区間 B で出力し始め、自分の有効充電区間 B では完全に目標電圧  $VT$  に維持される。そして、第 4 スキャンパルス  $V_{out\ 4}$  は、自分の予備充電区間 A に該当する第 3 スキャンパルス  $V_{out\ 3}$  の有効充電区間 B で出力し始め、自分の有効充電区間 B では完全に目標電圧  $VT$  に維持される。

10

20

30

40

50

## 【0059】

これにより、各スキャンパルス  $V_{out1} \sim V_{out4}$  は、従来のスキャンパルスに比べて予備充電区間 A に該当するパルス幅だけ実質的により長いパルス幅を有し、スキャンパルス  $V_{out1} \sim V_{out4}$  を受け取る液晶パネル 300 の薄膜トランジスタのターンオン時間が増加するという長所がある。

## 【0060】

一方、各スキャンパルス  $V_{out1} \sim V_{out4}$  は、タイミングコントローラから出力される第 1 乃至第 4 クロックパルス  $CLK1 \sim CLK4$  に同期して出力されるので、これら第 1 乃至第 4 クロックパルス  $CLK1 \sim CLK4$  もスキャンパルス  $V_{out1} \sim V_{out4}$  と同様に重なった区間を有する。

10

## 【0061】

ここで、第 1 乃至第 4 クロックパルス  $CLK4$  は、位相差をもって継続して循環するので、第 1 クロックパルス  $CLK1$  は第 4 クロックパルス  $CLK4$  と重なる。

## 【0062】

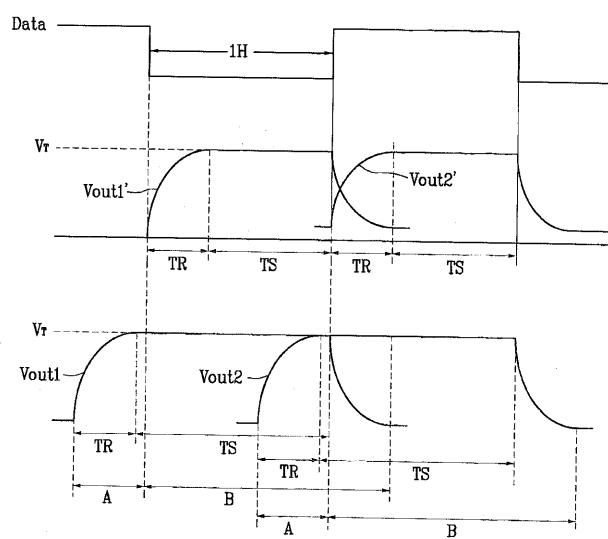

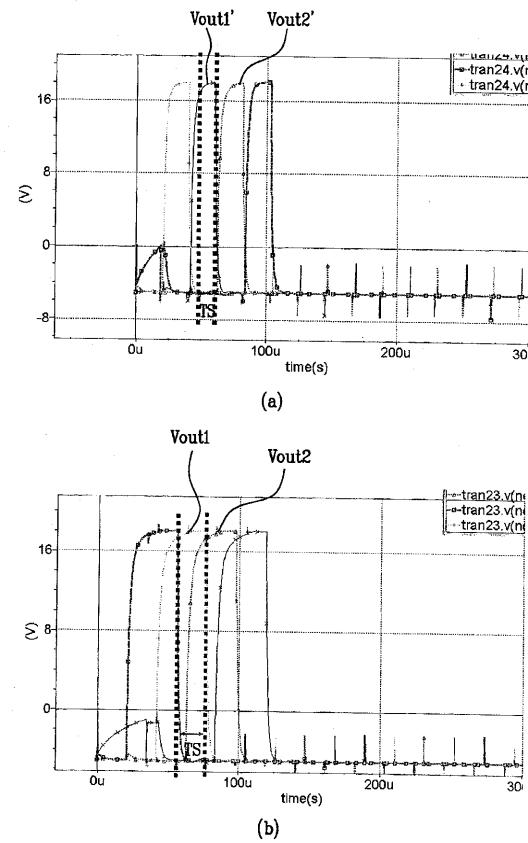

このような本発明のスキャンパルスを従来のスキャンパルスと比較して説明すると、次の通りである。ここでは、従来の第 1 及び第 2 スキャンパルス  $V_{out1}'$ 、 $V_{out2}'$ 、そして本発明の第 1 及び第 2 スキャンパルス  $V_{out1}$ 、 $V_{out2}$  を挙げて説明する。

20

## 【0063】

図 5 は、従来のスキャンパルスと本発明によるスキャンパルスとを比較説明するための図であり、図 6 は、従来のスキャンパルスと本発明のスキャンパルスに対するシミュレーション波形を示す図である。

## 【0064】

従来の第 1 及び第 2 スキャンパルス  $V_{out1}'$ 、 $V_{out2}'$  は、ゲートラインの抵抗及びキャパシタンス成分によってその波形が歪むと、図 5 に示すように、その立上り時間  $TR$  が増加し、これにより、第 1 及び第 2 スキャンパルス  $V_{out1}'$ 、 $V_{out2}'$  が目標電圧  $VT$  に維持される有効充電時間  $TS$  が減少するようになる。

20

## 【0065】

一方、データ電圧  $Data$  は周期的に正極性及び負極性に変化しつつデータラインに印加されるが、このとき、スキャンパルスの有効充電時間  $TS$  が、データ電圧が正極性に維持される時間 1H、または負極性に維持される時間 1H よりも短くなるため、データ電圧  $Data$  が画素電極に正常に印加されなくなる。

30

## 【0066】

しかしながら、本発明の第 1 スキャンパルス  $V_{out1}$  は、スタートパルス  $SP$  の一区間（第 1 スキャンパルス  $V_{out1}$  の予備充電区間 A）に該当する時点で出力し始まって徐々に増加し目標電圧  $VT$  に到達し、それ以後は自分の有効充電区間 B に該当する時間の間に完全に目標電圧  $VT$  に維持される。

## 【0067】

すなわち、第 1 スキャンパルス  $V_{out1}$  の立上り時間  $TR$  は、第 1 スキャンパルス  $V_{out1}$  の有効充電区間 B に該当する時間に含まれるのではなく、第 1 スキャンパルス  $V_{out1}$  の予備充電区間 A に該当する時間に含まれるので、第 1 スキャンパルス  $V_{out1}$  の有効充電区間 B に該当する時間が、立上り時間  $TR$  によって減少しない。

40

## 【0068】

また、第 2 スキャンパルス  $V_{out2}$  は、第 1 スキャンパルス  $V_{out1}$  の有効充電区間 B（第 2 スキャンパルス  $V_{out2}$  の予備充電区間 A）に該当する時点で出力し始め徐々に増加して目標電圧  $VT$  に到達し、それ以後は自分の有効充電区間 B に該当する時間の間に完全に目標電圧  $VT$  に維持される。

## 【0069】

すなわち、第 2 スキャンパルス  $V_{out2}$  の立上り時間  $TR$  は、第 2 スキャンパルス  $V_{out2}$  の有効充電区間 B に該当する時間に含まれるのではなく、第 2 スキャンパルス  $V_{out2}$

50

$V_{out}$  2 の予備充電区間 A に該当する時間に含まれるので、第 1 スキャンパルス  $V_{out}$  1 の有効充電区間 B に該当する時間が立上り時間  $T_R$  によって減少しない。

【0070】

したがって、図 6 の (a) 及び (b) に示すように、本発明での第 1 及び第 2 スキャンパルス  $V_{out}$  1、 $V_{out}$  2 は、従来の第 1 及び第 2 スキャンパルス  $V_{out}$  1'、 $V_{out}$  2' よりも長い有効充電時間  $T_S$  を有する。このとき、本発明の第 1 及び第 2 スキャンパルス  $V_{out}$  1、 $V_{out}$  2 の有効充電時間  $T_S$  は、データ電圧  $Data$  が正極性及び負極性に維持される時間  $1H$  よりも長いため、データ電圧  $Data$  は画素電極に正常に伝達される。

【0071】

一方、互いに隣接する時間帯に出力されるスキャンパルス  $V_{out}$  1 ~  $V_{out}$  n は、互いに重なるパルス幅区間を有するため、従来におけるように各ステージ  $BST$  1 ~  $BST$  n + 2 に次のステージから出力されたスキャンパルスが入力されると、次のような問題につながる。

【0072】

すなわち、例えば、互いに隣接する時間帯に出力される第 1 スキャンパルス  $V_{out}$  1 と第 2 スキャンパルス  $V_{out}$  2 は互いに重なるパルス幅区間を有するので、従来におけるように、第 2 ステージ  $BST$  2 から出力された前記第 2 スキャンパルス  $V_{out}$  2 が、第 1 スキャンパルス  $V_{out}$  1 を出力する第 1 ステージ  $BST$  1 に入力されると、第 1 ステージ  $BST$  1 は、自分の有効充電区間 B に該当する時点で第 2 電圧源  $VSS$  を第 1 ゲートライン  $GL$  1 に供給するようになる。

【0073】

言い換えれば、第 1 ステージ  $BST$  1 は、第 1 スキャンパルス  $V_{out}$  1 を前記第 1 ゲートライン  $GL$  1 に完全に印加する前に第 2 スキャンパルス  $V_{out}$  2 が出力される時点（具体的に、第 2 スキャンパルス  $V_{out}$  2 の予備充電区間 A に該当する時点）で第 2 電圧源  $VSS$  を第 1 ゲートライン  $GL$  1 に供給するようになる。

【0074】

これにより、第 1 ステージ  $BST$  1 は、不完全なスキャンパルスを出力することがある。すると、各ゲートラインには従来と同じパルス幅を有するスキャンパルスが供給され、よって、各スキャンパルスは歪んでしまう。この理由から、本発明による各ステージ  $BST$  1 ~  $BST$  n + 2 は、次のステージではなく、次々のステージからのスキャンパルスが入力される。すなわち、各ステージ  $BST$  1 ~  $BST$  n + 2 には、自分から出力されたスキャンパルスと重なる区間を持たないスキャンパルスが入力される。

【0075】

ここで、各ステージ  $BST$  1 ~  $BST$  n + 2、第 1 及び第 2 ダミーステージ  $BST$  n + 1、 $BST$  n + 2 に備えられた回路を詳細に説明すると、次の通りである。一方、第 1 及び第 2 シフトレジスタ  $301a$ 、 $301b$  に備えられた各ステージ  $BST$  1 ~  $BST$  n + 2 の回路構成はいずれも同一なので、第 1 シフトレジスタ  $301a$  に備えられた第 3 ステージ  $BST$  3 を例に挙げて説明する。

【0076】

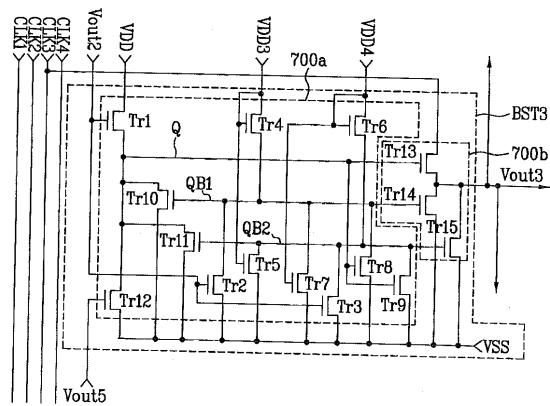

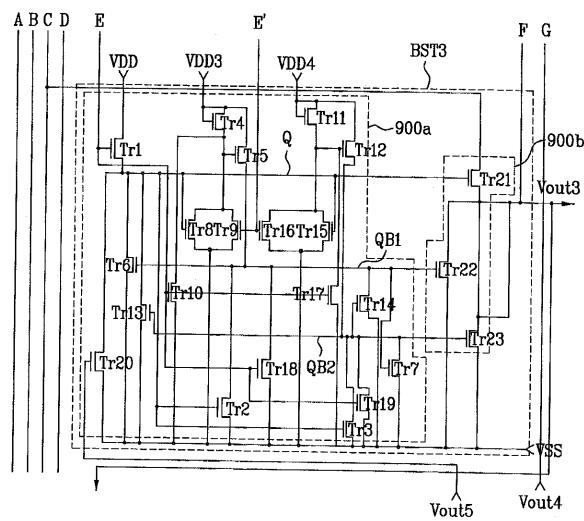

図 7 は、図 3 の第 1 シフトレジスタに備えられた第 3 ステージの回路構成図である。

【0077】

第 3 ステージ  $BST$  3 は、図 7 に示すように、大きく、第 1、第 2 及び第 3 ノード  $Q$ 、 $QB$  1、 $QB$  2 の充電及び放電を制御するノード制御部  $700a$  と、第 1、第 2、第 3 ノード  $Q$ 、 $QB$  1、 $QB$  2 の充電 / 放電状態によってターンオンされてスキャンパルスまたは第 2 電圧源  $VSS$  を選択的に出力する出力部  $700b$  と、で構成される。ここで、第 1、第 2 及び第 3 ノード  $Q$ 、 $QB$  1、 $QB$  2 は選択的に充電及び放電されるが、具体的に、第 1 ノード  $Q$  が充電状態にあると第 2 ノード  $QB$  1 及び第 3 ノード  $QB$  2 とも放電状態を維持し、第 1 ノード  $Q$  が放電状態にあると第 2 ノード  $QB$  1 及び第 3 ノード  $QB$  2 のうちいずれか一つが充電状態を維持する。

## 【0078】

すなわち、奇数番目のフレームでは、第1ノードQが放電状態のとき、第2ノードQ B 1が充電され、第3ノードQ B 2が放電され、そして、偶数番目のフレームでは、第1ノードQが放電状態の時、第2ノードQ B 1が放電され、前記第3ノードQ B 2が充電される。このように第1ノードQが放電状態のとき、第2ノードQ B 1及び第3ノードQ B 2にフレーム別に異なる極性の電圧源V D D 3、V D D 4を印加（充電及び放電）する理由は、第2ノードQ B 1及び第3ノードQ B 2にゲート端子が接続されたスイッチング素子の劣化を防止するためである。

## 【0079】

第3ステージB S T 3のノード制御部700aは、第1乃至第12N M O SトランジスタT r 1～T r 12で構成される。 10

## 【0080】

第1N M O SトランジスタT r 1は、前のステージからのスキャンパルスに応答して、第1ノードQを第1電圧源V D Dで充電させる。すなわち、第1N M O SトランジスタT r 1は、第2ステージB S T 2からの第2スキャンパルスV o u t 2に応答して、第1ノードQを第1電圧源V D Dで充電させる。このため、第1N M O SトランジスタT r 1のゲート端子は第2ステージB S T 2に接続され、ソース端子は第1電圧源V D Dを伝送する電源ラインに接続され、ドレイン端子は第1ノードQに接続される。

## 【0081】

第2N M O SトランジスタT r 2は、前のステージからのスキャンパルスに応答して、第2ノードQ B 1を第2電圧源V S Sで放電させる。すなわち、第2N M O SトランジスタT r 2は、第2ステージB S T 2からの第2スキャンパルスV o u t 2に応答して第2ノードQ B 1を第2電圧源V S Sで放電させる。このため、第2N M O SトランジスタT r 2のゲート端子は第2ステージB S T 2に接続され、ソース端子は第2ノードQ B 1に接続され、ドレイン端子は第2電圧源V S Sを伝送する電源ラインに接続される。 20

## 【0082】

第3N M O SトランジスタT r 3は、前のステージからのスキャンパルスに応答して、第3ノードQ B 2を第2電圧源V S Sで放電させる。すなわち、第3N M O SトランジスタT r 3は、第2ステージB S T 2からの第2スキャンパルスV o u t 2に応答して、第3ノードQ B 2を第2電圧源V S Sで放電させる。このため、第3N M O SトランジスタT r 3のゲート端子は第2ステージB S T 2に接続され、ソース端子は第3ノードQ B 2に接続され、ドレイン端子は第2電圧源V S Sを伝送する電源ラインに接続される。 30

## 【0083】

第4N M O SトランジスタT r 4は、第3電圧源V D D 3に応答してターンオンまたはターンオフされ、ターンオン時に第2ノードQ B 1を第3電圧源V D D 3で充電させる。このため、第4N M O SトランジスタT r 4のゲート端子は第3電圧源V D D 3を伝送する電源ラインに接続され、ソース端子は第3電圧源V D D 3を伝送する電源ラインに接続され、ドレイン端子は第2ノードQ B 1に接続される。ここで、第3電圧源V D D 3は、毎フレームごとに正極性及び負極性を交互に有する交流電圧である。すなわち、第3電圧源V D D 3は、奇数フレームには正極性を有し、偶数フレームには負極性を有する。 40

## 【0084】

第5N M O SトランジスタT r 5は、第3電圧源V D D 3に応答して、第3ノードQ B 2を第2電圧源V S Sで放電させる。このため、第5N M O SトランジスタT r 5のゲート端子は、第3電圧源V D D 3を伝送する電源ラインに接続され、ソース端子は第3ノードQ B 2に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

## 【0085】

第6N M O SトランジスタT r 6は、第4電圧源V D D 4に応答してターンオンまたはターンオフされ、ターンオン時に第3ノードQ B 2を第4電圧源V D D 4で充電させる。このため、第6N M O SトランジスタT r 6のゲート端子は第4電圧源V D D 4を伝送す 50

る電源ラインに接続され、ソース端子は第4電圧源VDD4を伝送する電源ラインに接続され、ドレイン端子は第3ノードQB2に接続される。ここで、第4電圧源VDD4は、毎フレームごとに正極性及び負極性を交互に有する交流電圧である。このとき、第4電圧源VDD4は、第3電圧源VDD3と反転された位相を有する。すなわち、第3電圧源VDD3は、奇数フレームには負極性を有し、偶数フレームには正極性を有する。

【0086】

第7NMOSトランジスタTr7は、第4電圧源VDD4に応答して、第2ノードQB1を第2電圧源VSSで放電させる。このため、第7NMOSトランジスタTr7のゲート端子は、第4電圧源VDD4を伝送する電源ラインに接続され、ソース端子は第2ノードQB1に接続され、ドレイン端子は第2電圧源VSSを伝送する電源ラインに接続される。

10

【0087】

第8NMOSトランジスタTr8は、第1ノードQに充電された第1電圧源VDDに応答して、第2ノードQB1を第2電圧源VSSで放電させる。このため、第8NMOSトランジスタTr8のゲート端子は第1ノードQに接続され、ソース端子は第2ノードQB1に接続され、ドレイン端子は第2電圧源VSSを伝送する電源ラインに接続される。

【0088】

第9NMOSトランジスタTr9は、第1ノードQに充電された第1電圧源VDDに応答して、第3ノードQB2を第2電圧源VSSで放電させる。このため、第9NMOSトランジスタTr9のゲート端子は第1ノードQに接続され、ソース端子は第3ノードQB2に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

20

【0089】

第10NMOSトランジスタTr10は、第2ノードQB1に充電された第3電圧源VDD3に応答して、第1ノードQを第2電圧源VSSで放電させる。このため、第10NMOSトランジスタTr10のゲート端子は第2ノードQB1に接続され、ソース端子は第1ノードQに接続され、ドレイン端子は第2電圧源VSSを伝送する電源ラインに接続される。

【0090】

第11NMOSトランジスタTr11は、第3ノードQB2に充電された第4電圧源VDD4に応答して、第1ノードQを第2電圧源VSSで放電させる。このため、第11NMOSトランジスタTr11のゲート端子は第3ノードQB2に接続され、ソース端子は第1ノードQに接続され、ドレイン端子は第2電圧源VSSを伝送する電源ラインに接続される。

30

【0091】

第12NMOSトランジスタTr12は、次々のステージからのスキャンパルスに応答して、第1ノードQを第2電圧源VSSで放電させる。すなわち、第12NMOSトランジスタTr12は、第5ステージからの第5スキャンパルスVout5に応答して、第1ノードQを第2電圧源VSSで放電させる。このため、第12NMOSトランジスタTr12のゲート端子は、第5ステージの出力部に接続され、ソース端子は第1ノードQに接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

40

【0092】

そして、第3ステージBST3の出力部700bは、第13乃至第15NMOSトランジスタTr13～Tr15で構成される。

【0093】

第13NMOSトランジスタTr13は、第1ノードQに充電された第1電圧源VDDに応答して、クロックパルスをスキャンパルスとしてゲートラインに出力する。また、このスキャンパルスを前々のステージと次のステージに供給する。このため、第13NMOSトランジスタTr13のゲート端子は、第1ノードQに接続され、ソース端子は、第3クロックパルスCLK3を伝送するクロックラインに接続され、ドレイン端子は、第3ゲートライン、第1ステージBST1に備えられた第12NMOSのゲート端子、及び第4

50

ステージB S T 4に備えられた第1乃至第3N M O SトランジスタT r 1～T r 3のゲート端子に接続される。

【0094】

第14N M O SトランジスタT r 1 4は、第2ノードQ B 1に充電された第3電圧源V D D 3に応答して、第2電圧源V S Sをゲートラインに供給する。すなわち、第14N M O SトランジスタT r 1 4は、第2ノードQ B 1に充電された第3電圧源V D D 3に応答して、第2電圧源V S Sを第3ゲートラインに供給する。このため、第14N M O SトランジスタT r 1 4のゲート端子は、第2ノードQ B 1に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続され、ソース端子は、第3ゲートライン、第1ステージB S T 1に備えられた第12N M O SトランジスタT r 1 2のゲート端子、及び第4ステージB S T 4に備えられた第1乃至第3N M O SトランジスタT r 1～T r 3のゲート端子に接続される。

10

【0095】

第15N M O SトランジスタT r 1 5は、第3ノードQ B 2に充電された第4電圧源V D D 4に応答して、第2電圧源V S Sをゲートラインに供給する。すなわち、第15N M O SトランジスタT r 1 5は、第3ノードQ B 2に充電された第4電圧源V D D 4に応答して、第2電圧源V S Sを第3ゲートラインに供給する。このため、第15N M O SトランジスタT r 1 5のゲート端子は、第2ノードQ B 1に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続され、ソース端子は、第3ゲートライン、第1ステージB S T 1に備えられた第12N M O Sのゲート端子、及び第4ステージB S T 4に備えられた第1乃至第3N M O SトランジスタT r 1～T r 3のゲート端子に接続される。

20

【0096】

第1及び第2ステージB S T 1、B S T 2、第4乃至第nステージB S T 4～B S T n、そして第1及び第2ダミーステージB S T n + 1、B S T n + 2も、上述した第3ステージB S T 3と同じ構成を有する。

【0097】

ただし、第1ステージB S T 1の前にはステージが存在しないため、第1ステージB S T 1に備えられた第1乃至第3N M O SトランジスタT r 1～T r 3は、タイミングコントローラからのスタートパルスS Pを受け取る。すなわち、第1ステージB S T 1の第1N M O SトランジスタT r 1は、タイミングコントローラからのスタートパルスS Pに応答して、第1ステージB S T 1の第1ノードQを第1電圧源V D Dで充電させる。

30

【0098】

そして、第2N M O SトランジスタT r 2は、タイミングコントローラからのスタートパルスS Pに応答して、第1ステージB S T 1の第2ノードQ B 1を第2電圧源V S Sで放電させる。そして、第3N M O SトランジスタT r 3は、タイミングコントローラからのスタートパルスS Pに応答して、第1ステージB S T 1の第3ノードQ B 2を第2電圧源V S Sで放電させる。

【0099】

そして、第1及び第2ステージB S T 1、B S T 2の前々にはステージが存在しない。したがって、第1ステージB S T 1は、第1スキャンパルスV o u t 1を出力し、これを第1ゲートライン及び第2ステージB S T 2に供給する。これと同様に、第2ステージB S T 2は、第2スキャンパルスV o u t 2を出力し、これを第2ゲートライン及び第3ステージB S T 3に供給する。

40

【0100】

そして、第2ダミーステージB S T n + 2の次のステージにはステージが存在しない。したがって、第2ダミーステージB S T n + 2の第13N M O SトランジスタT r 1 3のソース端子、第14N M O SトランジスタT r 1 4のドレイン端子、及び第15N M O SトランジスタT r 1 5のドレイン端子は、第nステージB S T nの第12N M O SトランジスタT r 1 2のゲート端子に接続される。

50

## 【0101】

第2シフトレジスタ301bに備えられた各ステージB S T 1 ~ B S T n + 2も、第1シフトレジスタ301aに備えられた各ステージB S T 1 ~ B S T n + 2と同じ回路構成を有する。

## 【0102】

このように構成された本発明の実施の形態によるシフトレジスタの動作を説明すると次の通りである。ここで、第1シフトレジスタ301aの動作と第2シフトレジスタ301bの動作は互いに同一なので、第1シフトレジスタ301aの動作についてのみ説明する。

## 【0103】

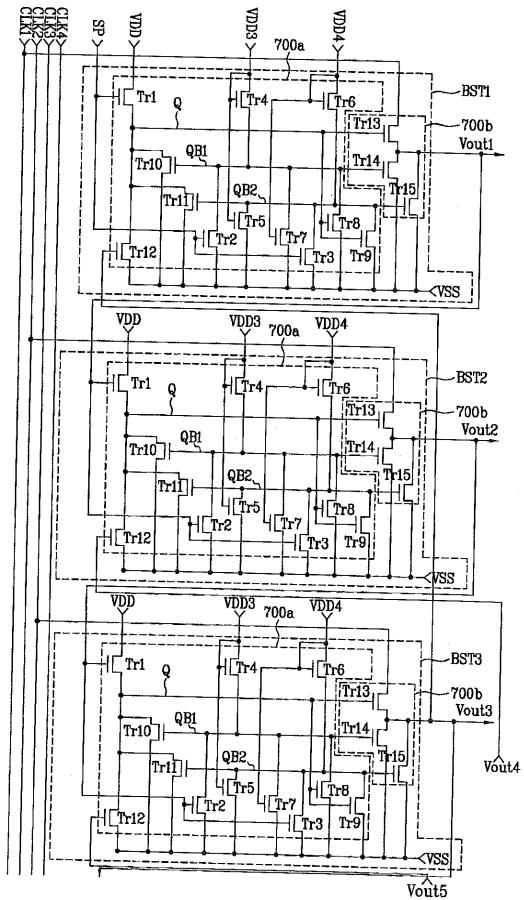

図8は、図7の回路構成を有する第1シフトレジスタの第1乃至第3ステージを示す図である。

## 【0104】

ここで、第1フレームの間に第3電圧源V D D 3が正極性の電圧に維持され、第4電圧源V D D 4が負極性の電圧に維持されると仮定し、第2フレームの間に第3電圧源V D D 3が負極性の電圧に維持され、第4電圧源V D D 4が正極性の電圧に維持されると仮定する。すなわち、奇数番目のフレームの間に、第3電圧源V D D 3が正極性に維持され、第4電圧源V D D 4が負極性に維持されると仮定し、偶数番目のフレームの間に、第3電圧源V D D 3が負極性に維持され、第4電圧源V D D 4が正極性に維持されると仮定する。

## 【0105】

まず、スタートパルスS Pは、第1N M O SトランジスタT r 1のゲート端子、第2N M O SトランジスタT r 2のゲート端子、及び第3N M O SトランジスタT r 3のゲート端子に印加され、第1、第2及び第3N M O SトランジスタT r 1、T r 2、T r 3をターンオンさせる。

## 【0106】

こうなると、ターンオンされた第1N M O SトランジスタT r 1を介して第1電圧源V D Dが第1ノードQに供給される。このとき、第1ノードQが第1電圧源V D Dで充電されることによって、第1ノードQにゲート端子が接続された第8、第9及び第13N M O SトランジスタT r 8、T r 9、T r 13が同時にターンオンされる。ここで、ターンオンされた第8N M O SトランジスタT r 8及び第2N M O SトランジスタT r 2を介して第2電圧源V S Sが第2ノードQ B 1に供給される。したがって、第2ノードQ B 1は放電状態に維持され、この第2ノードQ B 1にゲート端子が接続された第10及び第14N M O SトランジスタT r 10、T r 14がターンオフされる。

## 【0107】

そして、ターンオンされた第3及び第9N M O SトランジスタT r 3、T r 9を介して第2電圧源V S Sが第3ノードQ B 2に供給される。このとき、第3ノードQ B 2が第2電圧源V S Sで放電されることによって、第3ノードQ B 2にゲート端子が接続された第11及び第15N M O SトランジスタT r 11、T r 15はターンオフされる。

## 【0108】

また、第4N M O SトランジスタT r 4は、自分のゲート端子に第3電圧源V D D 3が印加されることによってターンオンされる。第3電圧源V D D 3は、第1フレームの間に常に正極性状態を維持するので、第4N M O SトランジスタT r 4は第1フレームの間に常にターンオン状態を維持する。

## 【0109】

ここで、ターンオンされた第4N M O SトランジスタT r 4を介して第3電圧源V D D 3が第2ノードQ B 1に供給される。その結果、第2ノードQ B 1には上述した第2電圧源V S Sと第3電圧源V D D 3が同時に供給される。ところが、第2電圧源V S Sを供給するトランジスタの数が、第3電圧源V D D 3を供給するトランジスタの数よりも多いため、第2ノードQ B 1は第2電圧源V S Sに維持される。これによって、第2ノードQ B 1は放電状態を維持する。したがって、第2ノードQ B 1にゲート端子が接続された第1

10

20

30

40

50

0 及び第 1 4 N M O S トランジスタ T r 1 0 、 T r 1 4 はターンオフされる。

【 0 1 1 0 】

また、第 3 電圧源 V D D 3 は、第 5 N M O S トランジスタ T r 5 のゲート端子にも供給される。したがって、第 5 N M O S トランジスタ T r 5 も第 1 フレームの間に常にターンオン状態を維持する。このターンオンされた第 5 N M O S トランジスタ T r 5 を介して第 2 電圧源 V S S が第 3 ノード Q B 2 に供給される。その結果、第 3 ノード Q B 2 は、第 3 、第 5 及び第 9 N M O S トランジスタ T r 3 、 T r 5 、 T r 9 によって放電状態を維持するようになる。したがって、第 3 ノード Q B 2 にゲート端が接続された第 1 1 及び第 1 5 N M O S トランジスタ T r 1 1 、 T r 1 5 はターンオフされる。

【 0 1 1 1 】

また、第 6 N M O S トランジスタ T r 6 は、自分のゲート端子に印加された第 4 電圧源 V D D 4 によってターンオフされる。ここで、第 4 電圧源 V D D 4 は第 1 フレームの間に負極性に維持されるので、第 6 N M O S トランジスタ T r 6 は第 1 フレームの間に常にターンオフ状態を維持する。

【 0 1 1 2 】

また、第 4 電圧源 V D D 4 は、第 7 N M O S トランジスタ T r 7 のゲート端子にも印加されるので、第 1 フレームの間に第 7 N M O S トランジスタ T r 7 は常にターンオフ状態を維持する。

【 0 1 1 3 】

このようにスタートパルス S P によって第 1 ステージ B S T 1 の第 1 ノード Q が第 1 電圧源 V D D で充電され、第 2 及び第 3 ノード Q B 1 、 Q B 2 が第 2 電圧源 V S S で放電されることによって、第 1 ステージ B S T 1 がイネーブルされる。

【 0 1 1 4 】

この状態で、第 1 ステージ B S T 1 の第 1 3 N M O S トランジスタ T r 1 3 に第 1 クロックパルス C L K 1 が供給されると、第 1 3 N M O S トランジスタ T r 1 3 は第 1 クロックパルス C L K 1 を第 1 スキャンパルス V o u t 1 として出力する。このとき、第 1 クロックパルス C L K 1 とスタートパルス S P は重なって出力されるので、第 1 スキャンパルス V o u t 1 は、スタートパルス S P に重なって出力される。

【 0 1 1 5 】

この第 1 スキャンパルス V o u t 1 は、第 1 ゲートライン及び第 2 ステージ B S T 2 に供給される。すなわち、第 1 ステージ B S T 1 からの第 1 スキャンパルス V o u t 1 は、第 2 ステージ B S T 2 の第 1 、第 2 及び第 3 N M O S トランジスタ T r 1 、 T r 2 、 T r 3 に供給される。これにより、第 2 ステージ B S T 2 の第 1 ノード Q が充電され、第 2 及び第 3 ノード Q B 1 、 Q B 2 が放電される。

【 0 1 1 6 】

すなわち、第 2 ステージ B S T 2 は、第 1 スキャンパルス V o u t 1 によってイネーブルされる。言い換えれば、第 1 ステージ B S T 1 がスタートパルス S P によってイネーブルされるのと同様に、第 2 ステージ B S T 2 は第 1 スキャンパルス V o u t 1 によってイネーブルされる。この状態で、第 2 ステージ B S T 2 の第 1 3 N M O S トランジスタ T r 1 3 に第 2 クロックパルス C L K 2 が供給されると、第 1 3 N M O S トランジスタ T r 1 3 は、第 2 クロックパルス C L K 2 を第 2 スキャンパルス V o u t 2 として出力する。このとき、第 2 クロックパルス C L K 2 は第 1 クロックパルス C L K 1 と重なるので、第 2 スキャンパルス V o u t 2 は第 1 スキャンパルス V o u t 1 と重なって出力される。

【 0 1 1 7 】

この第 2 スキャンパルス V o u t 2 は、第 2 ゲートライン及び第 3 ステージ B S T 3 に供給される。すなわち、第 2 ステージ B S T 2 からの第 2 スキャンパルス V o u t 2 は、第 3 ステージ B S T 3 の第 1 、第 2 及び第 3 N M O S トランジスタ T r 1 、 T r 2 、 T r 3 に供給される。これにより、第 3 ステージ B S T 3 の第 1 ノード Q が充電され、第 2 及び第 3 ノード Q B 1 、 Q B 2 が放電される。

【 0 1 1 8 】

10

20

30

40

50

すなわち、第3ステージB S T 3は第2スキャンパルスV o u t 2によってイネーブルされる。言い換えれば、第1ステージB S T 1がスタートパルスS Pによってイネーブルされるのと同様に、第3ステージB S T 3は第2スキャンパルスV o u t 2によってイネーブルされる。

【0 1 1 9】

この状態で、第3ステージB S T 3の第13N M O SトランジスタT r 1 3に第3クロックパルスC L K 3が供給されると、第13N M O SトランジスタT r 1 3は、第3クロックパルスC L K 3を第3スキャンパルスV o u t 3として出力する。このとき、第3クロックパルスC L K 3は第2クロックパルスC L K 2と重なるので、第3スキャンパルスV o u t 3は第2スキャンパルスV o u t 2と重なって出力される。

10

【0 1 2 0】

この第3スキャンパルスV o u t 3は、第3ゲートライン及び第4ステージB S T 4に供給される。すなわち、第3ステージB S T 3からの第3スキャンパルスV o u t 3は第4ステージB S T 4の第1、第2及び第3N M O SトランジスタT r 1、T r 2、T r 3に供給される。

【0 1 2 1】

これにより、第4ステージB S T 4の第1ノードQが充電され、第2及び第3ノードQ B 1、Q B 2が放電される。すなわち、第4ステージB S T 4は第3スキャンパルスV o u t 3によってイネーブルされる。言い換えれば、第1ステージB S T 1がスタートパルスS Pによってイネーブルされるのと同様に、第4ステージB S T 4は第3スキャンパルスV o u t 3によってイネーブルされる。

20

【0 1 2 2】

この状態で、第4ステージB S T 4の第13N M O SトランジスタT r 1 3に第4クロックパルスC L K 4が供給されると、第13N M O SトランジスタT r 1 3は第4クロックパルスC L K 4を第4スキャンパルスV o u t 4として出力する。このとき、第4クロックパルスC L K 4は第3クロックパルスC L K 3と重なるので、第4スキャンパルスV o u t 4は第3スキャンパルスV o u t 3と重なって出力される。

【0 1 2 3】

一方、第3ステージB S T 3から出力された第3スキャンパルスV o u t 3は、第1ステージB S T 1の第12N M O SトランジスタT r 1 2にも供給される。すなわち、第3スキャンパルスV o u t 3は、第1ステージB S T 1に備えられた第12N M O SトランジスタT r 1 2のゲート端子に供給される。これにより、第1ステージB S T 1がディセーブルされる。

30

【0 1 2 4】

具体的に、第3スキャンパルスV o u t 3は、第1ステージB S T 1に備えられた第12N M O SトランジスタT r 1 2をターンオンさせる。すると、第2電圧源V S Sが、ターンオンされた第12N M O SトランジスタT r 1 2を介して第1ステージB S T 1の第1ノードQに供給される。これにより、第1ステージB S T 1の第1ノードQが放電される。したがって、第1ステージB S T 1の第1ノードQに接続された第8、第9及び第13N M O SトランジスタT r 8、T r 9、T r 1 3がターンオフされる。また、このとき、スタートパルスS Pがローに変化することによってこのロー状態のスタートパルスS Pが供給される第1ステージB S T 1の第1、第2及び第3N M O SトランジスタT r 1、T r 2、T r 3がターンオフされる。

40

【0 1 2 5】

ここで、第1ステージB S T 1の第2及び第8N M O SトランジスタT r 2、T r 8がターンオフ状態にあるので、第1ステージB S T 1の第2ノードQ B 1は、第4N M O SトランジスタT r 4から供給される第1電圧源V D Dで充電される。したがって、第1ステージB S T 1の第2ノードQ B 1にゲート端子が接続された第10及び第14N M O SトランジスタT r 1 0、T r 1 4ともターンオンされる。このとき、ターンオンされた第14N M O SトランジスタT r 1 4を介して第2電圧源V S Sが第1ゲートラインに供給

50

される。

【0126】

一方、ターンオンされた第10N MOSトランジスタTr10を介して第2電圧源VSSが第1ノードQに供給される。その結果、第1ステージBST1の第1ノードQは、第10及び第12N MOSトランジスタTr10、Tr12によって放電される。

【0127】

このように第3ステージBST3からの第3スキャンパルスVout3によって第1ステージBST1の第1ノードQ及び第3ノードQB2は放電され、第2ノードQB1が充電される。すなわち、第1ステージBST1は、第3ステージBST3からの第3スキャンパルスVout3に応答してディセーブルされる。このディセーブルされた第1ステージBST1は、自分に備えられた第14N MOSトランジスタTr14を介して第2電圧源VSSを出力する。そして、この第2電圧源VSSを第1ゲートラインに供給する。

【0128】

このような方式で、各ステージBST1～BSTn+2は、前のステージから出力されたスキャンパルスによってイネーブルされる。そして、各ステージBST1～BSTn+2は次々のステージから出力されたスキャンパルスによってディセーブルされる。

【0129】

一方、第2フレームには、第3電圧源VDD3が負極性に維持され、第4電圧源VDD4が正極性に維持される。これにより、各ステージBST1～BSTn+2がディセーブルされる時、各ステージBST1～BSTn+2の第2ノードQB1が放電され、第3ノードQB2が充電される。

【0130】

したがって、各ステージBST1～BSTn+2がディセーブルされる時、第3ノードQB2にゲート端子が接続された第15N MOSトランジスタTr15を介して第2電圧源VSSが出力される。このようにフレーム別に第2及び第3ノードQB1、QB2が交互に充電／放電されることによって、出力部700bに備えられた第14及び第15N MOSトランジスタTr14、Tr15の劣化が防止される。

【0131】

第2シフトレジスタ301bに備えられた各ステージBST1～BSTn+2も、第1シフトレジスタ301aに備えられた各ステージBST1～BSTn+2と同様に動作する。ただし、第1シフトレジスタ301aに備えられた各ステージBST1～BSTnは、各ゲートラインGL1～GLnの一側にスキャンパルスVout1～Voutnを印加し、第2シフトレジスタ301bに備えられた各ステージBST1～BSTnは、各ゲートラインGL1～GLnの他側にスキャンパルスVout1～Voutnを供給する。

【0132】

一方、第1及び第2シフトレジスタ301a、301bの各ステージBST1～BSTn+2は、次のような回路構成を有しても良い。

【0133】

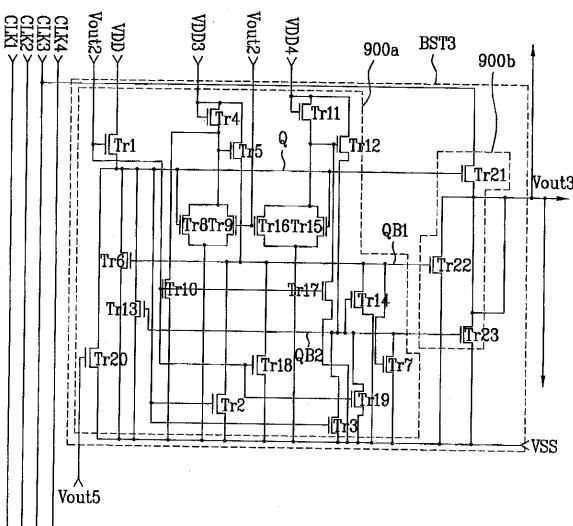

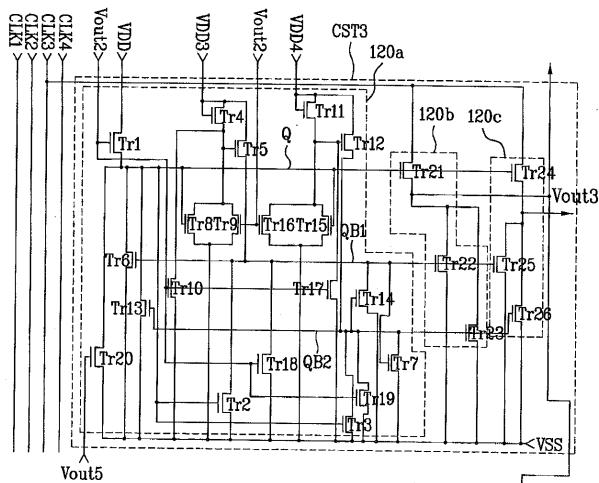

図9は、図3の第1シフトレジスタに備えられた第3ステージの他の回路構成図である。

【0134】

第3ステージCST3のノード制御部900aは、第1乃至第20N MOSトランジスタTr1～Tr20で構成される。

【0135】

第1N MOSトランジスタTr1は、前のステージからのスキャンパルスに応答して、第1ノードQを第1電圧源VDDで充電させる。すなわち、第1N MOSトランジスタTr1は、第2ステージBST2からの第2スキャンパルスVout2に応答して、第1ノードQを第1電圧源VDDで充電させる。このため、第1N MOSトランジスタTr1のゲート端子は、第2ステージBST2に接続され、ソース端子は、第1電圧源VDDを伝送する電源ラインに接続され、ドレイン端子は、第1ノードQに接続される。

10

20

30

40

50

## 【0136】

第2N MOSトランジスタTr2は、第1ノードQに充電された第1電圧源VDDに応答して、第2ノードQB1を第2電圧源VSSで放電させる。このため、第2N MOSトランジスタTr2のゲート端子は、第1ノードQに接続され、ソース端子は、第2ノードQB1に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

## 【0137】

第3N MOSトランジスタTr3は、第1ノードQに充電された第1電圧源VDDに応答して、第3ノードQB2を第2電圧源VSSで放電させる。このため、第3N MOSトランジスタTr3のゲート端子は、第1ノードQに接続され、ソース端子は前記第3ノードQB2に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

10

## 【0138】

第4N MOSトランジスタTr4は、フレームごとに異なる極性を有する第3電圧源VDD3に応答してターンオンまたはターンオフされ、ターンオン時に第3電圧源VDD3を出力する。このため、第4N MOSトランジスタTr4のゲート端子は、第3電圧源VDD3を伝送する電源ラインに接続され、ソース端子は、第3電圧源VDD3を伝送する電源ラインに接続される。

20

## 【0139】

第5N MOSトランジスタTr5は、第4N MOSトランジスタTr4から出力された第3電圧源VDD3に応答して第2ノードQB1を第3電圧源VDD3で充電させる。このため、第5N MOSトランジスタTr5のゲート端子は、第4N MOSトランジスタTr4のドレイン端子に接続され、ソース端子は、第3電圧源VDD3を伝送する電源ラインに接続され、ドレイン端子は第2ノードQB1に接続される。

20

## 【0140】

第6N MOSトランジスタTr6は、第2ノードQB1に充電された第3電圧源VDD3に応答して、第1ノードQを第2電圧源VSSで放電させる。このため、第6N MOSトランジスタTr6のゲート端子は第2ノードQB1に接続され、ソース端子は第1ノードQに接続され、ドレイン端子は第2電圧源VSSを伝送する電源ラインに接続される。

30

## 【0141】

第7N MOSトランジスタTr7は、第2ノードQB1に充電された第3電圧源VDD3に応答して、第3ノードQB2を第2電圧源VSSで放電させる。このため、第7N MOSトランジスタTr7のゲート端子は、第2ノードQB1に接続され、ソース端子は第3ノードQB2に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

30

## 【0142】

第8N MOSトランジスタTr8は、第1ノードQに充電された第1電圧源VDDに応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5N MOSトランジスタTr5をターンオフさせる。このため、第8N MOSトランジスタTr8のゲート端子は、第1ノードQに接続され、ソース端子は、第5N MOSトランジスタTr5のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

40

## 【0143】

第9N MOSトランジスタTr9は、前のステージからのスキャンパルスに応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5N MOSトランジスタTr5をターンオフさせる。すなわち、第9N MOSトランジスタTr9は、第2ステージBST2からの第2スキャンパルスVout2に応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって第5N MOSトランジスタTr5をターンオフさせる。このため、第9N MOSトランジスタTr9のゲート端子は、第2ステージBST2に接続され、ソース端子は、第50

5 NMOSトランジスタTr5のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

【0144】

第10NMOSトランジスタTr10は、前のステージからのスキャンパルスに応答して、第5NMOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5NMOSトランジスタTr5をターンオフさせる。すなわち、第10NMOSトランジスタTr10は、第2ステージBST2からの第2スキャンパルスVout2に応答して、第5NMOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5NMOSトランジスタTr5をターンオフさせる。このため、第10NMOSトランジスタTr10のゲート端子は、第2ステージBST2に接続され、ソース端子は、第5NMOSトランジスタTr5のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

【0145】

第11NMOSトランジスタTr11は、フレームごとに異なる極性を有する第4電圧源VDD4に応答してターンオンまたはターンオフされ、ターンオン時に第4電圧源VDD4を出力する。このため、第11NMOSトランジスタTr11のゲート端子は、第4電圧源VDD4を伝送する電源ラインに接続され、ソース端子は、第4電圧源VDD4を伝送する電源ラインに接続される。ここで、第4電圧源VDD4は、毎フレームごとに第3電圧源VDD3に反転された極性を有する。

【0146】

第12NMOSトランジスタTr12は、第11NMOSトランジスタTr11から出力された第4電圧源VDD4に応答して、第3ノードQB2を第4電圧源VDD4で充電させる。このため、第12NMOSトランジスタTr12のゲート端子は、第11NMOSトランジスタTr11のドレイン端子に接続され、ソース端子は、第4電圧源VDD4を伝送する電源ラインに接続され、ドレイン端子は第3ノードQB2に接続される。

【0147】

第13NMOSトランジスタTr13は、第3ノードQB2に充電された第4電圧源VDD4に応答して、第1ノードQを第2電圧源VSSで放電させる。このため、第13NMOSトランジスタTr13のゲート端子は、第3ノードQB2に接続され、ソース端子は第1ノードQに接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

【0148】

第14NMOSトランジスタTr14は、第3ノードQB2に充電された第4電圧源VDD4に応答して、第2ノードQB1を第2電圧源VSSで放電させる。このため、第14NMOSトランジスタTr14のゲート端子は、第3ノードQB2に接続され、ソース端子は第2ノードQB1に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

【0149】

第15NMOSトランジスタTr15は、第1ノードQに充電された第1電圧源VDDに応答して、第12NMOSトランジスタTr12のゲート端子に第2電圧源VSSを供給することによって、第12NMOSトランジスタTr12をターンオフさせる。このため、第15NMOSトランジスタTr15のゲート端子は、第1ノードQに接続され、ソース端子は、第12NMOSトランジスタTr12のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

【0150】

第16NMOSトランジスタTr16は、前のステージからのスキャンパルスに応答して、第12NMOSトランジスタTr12のゲート端子に第2電圧源VSSを供給することによって、第12NMOSトランジスタTr12をターンオフさせる。すなわち、第16NMOSトランジスタTr16は、第2ステージBST2からの第2スキャンパルスVout2に応答して、第12NMOSトランジスタTr12をターンオフさせる。このた

10

20

30

40

50

め、第16N MOSトランジスタTr16のゲート端子は、第2ステージBST2に接続され、ソース端子は、第12N MOSトランジスタTr12のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

【0151】

第17N MOSトランジスタTr17は、前のステージからのスキャンパルスに応答して、第12N MOSトランジスタTr12のゲート端子に第2電圧源VSSを供給することによって、第12N MOSトランジスタTr12をターンオフさせる。すなわち、第17N MOSトランジスタTr17は、第2ステージBST2からの第2スキャンパルスVout2に応答して、第12N MOSトランジスタTr12をターンオフさせる。このため、第17N MOSトランジスタTr17のゲート端子は、第2ステージBST2に接続され、ソース端子は、第12N MOSトランジスタTr12のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

10

【0152】

第18N MOSトランジスタTr18は、前のステージからのスキャンパルスに応答して、第2ノードQB1を第2電圧源VSSで放電させる。すなわち、第18N MOSトランジスタTr18は、第2ステージBST2からの第2スキャンパルスVout2に応答して、第2ノードQB1を第2電圧源VSSで放電させる。このため、第18N MOSトランジスタTr18のゲート端子は、第2ステージBST2に接続され、ソース端子は第2ノードQB1に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

20

【0153】

第19N MOSトランジスタTr19は、前のステージからのスキャンパルスに応答して、第3ノードQB2を第2電圧源VSSで放電させる。すなわち、第19N MOSトランジスタTr19は、第2ステージBST2からの第2スキャンパルスVout2に応答して、第3ノードQB2を第2電圧源VSSで放電させる。このため、第19N MOSトランジスタTr19のゲート端子は第2ステージBST2に接続され、ソース端子は第3ノードQB2に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

20

【0154】

第20N MOSトランジスタTr20は、次々のステージからのスキャンパルスに応答して、第1ノードQを第2電圧源VSSで放電させる。すなわち、第20N MOSトランジスタTr20のゲート端子は、第5ステージからの第5スキャンパルスVout5に応答して、第1ノードQを第2電圧源VSSで放電させる。このため、第20N MOSトランジスタTr20のゲート端子は第5ステージに接続され、ソース端子は第1ノードQに接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

30

【0155】

そして、第3ステージBST3の出力部900bは、第21乃至23N MOSトランジスタTr21～Tr23で構成される。

【0156】

第21N MOSトランジスタTr21は、第1ノードQに充電された第1電圧源VDDに応答して、第3クロックパルスCLK3をスキャンパルスとしてゲートラインに出力する。そして、この第3スキャンパルスVout3を前々のステージと次のステージの両方に供給する。このため、第21N MOSトランジスタTr21のゲート端子は、第1ノードQに接続され、ソース端子は、第3クロックパルスCLK3を伝送するクロックラインに接続され、ドレイン端子は、第3ゲートライン、第1ステージBST1に備えられた第20N MOSトランジスタTr20のゲート端子、及び第4ステージBST4に備えられた第1、第9、第10、第16、第17、第18、及び第19N MOSトランジスタTr1、Tr9、Tr10、Tr16、Tr17、Tr18、Tr19のゲート端子に接続される。

40

【0157】

50

第22N MOSトランジスタTr22は、第2ノードQB1に充電された第3電圧源VDD3に応答して、第2電圧源VSSをゲートラインに供給する。すなわち、第14N MOSトランジスタTr14は、第2ノードQB1に充電された第3電圧源VDD3に応答して、第2電圧源VSSを第3ゲートラインに供給する。このため、第22N MOSトランジスタTr22のゲート端子は、第2ノードQB1に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続され、ソース端子は、第3ゲートライン、第1ステージBST1に備えられた第20N MOSトランジスタTr20のゲート端子、及び第4ステージBST4に備えられた第1、第9、第10、第16、第17、第18、及び第19N MOSトランジスタTr1、Tr9、Tr10、Tr16、Tr17、Tr18、Tr19のゲート端子に接続される。

10

## 【0158】

第23N MOSトランジスタTr23は、第3ノードQB2に充電された第4電圧源VDD4に応答して、第2電圧源VSSをゲートラインに供給する。すなわち、第23N MOSトランジスタTr23は、第3ノードQB2に充電された第4電圧源VDD4に応答して、第2電圧源VSSを第3ゲートラインに供給する。このため、第23N MOSトランジスタTr23のゲート端子は、第2ノードQB1に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続され、ソース端子は、第3ゲートライン、第1ステージBST1に備えられた第20N MOSのゲート端子、及び第4ステージBST4に備えられた第1、第9、第10、第16、第17、第18、及び第19N MOSトランジスタTr1、Tr9、Tr10、Tr16、Tr17、Tr18、Tr19のゲート端子に接続される。

20

## 【0159】

第1及び第2ステージBST1、BST2、第4乃至第nステージBST4～BSTn、第1及び第2ダミーステージBSTn+1、BSTn+2も、上述した第2ステージBST2と同じ構成を有する。

## 【0160】

ただし、第1ステージBST1の前にはステージが存在しないので、第1ステージBST1に備えられた第1、第9、第10、第16、第17、第18、及び第19N MOSトランジスタTr1、Tr9、Tr10、Tr16、Tr17、Tr18、Tr19には、タイミングコントローラからのスタートパルスSPが供給される。すなわち、第1ステージBST1の第1N MOSトランジスタTr1は、タイミングコントローラからのスタートパルスSPに応答して、第1ノードQを第1電圧源VDDで充電させる。

30

## 【0161】

また、第1ステージBST1の第9N MOSトランジスタTr9は、タイミングコントローラからのスタートパルスSPに応答して、第1ステージBST1の第2ノードQB1を第2電圧源VSSで放電させる。

## 【0162】

また、第1ステージBST1の第10N MOSトランジスタTr10は、タイミングコントローラからのスタートパルスに応答して、第4N MOSトランジスタTr4のゲート端子に第2電圧源VSSを供給することによって、第4N MOSトランジスタTr4をターンオフさせる。

40

## 【0163】

また、第1ステージBST1の第16N MOSトランジスタTr16は、タイミングコントローラからのスタートパルスに応答して、第12N MOSトランジスタTr12のゲート端子に第2電圧源VSSを供給することによって、第12N MOSトランジスタTr12をターンオフさせる。

## 【0164】

また、第1ステージBST1の第17N MOSトランジスタTr17は、タイミングコントローラからのスタートパルスに応答して、第12N MOSトランジスタTr12のゲート端子に第2電圧源VSSを供給することによって、第12N MOSトランジスタTr17をターンオフさせる。

50

12をターンオフさせる。

【0165】

また、第1ステージB S T 1の第18N M O SトランジスタT r 18は、タイミングコントローラからのスタートパルスS Pに応答して、第2ノードQ B 1を第2電圧源V S Sで放電させる。

【0166】

また、第1ステージB S T 1の第19N M O SトランジスタT r 19は、タイミングコントローラからのスタートパルスS Pに応答して、第3ノードQ B 2を第2電圧源V S Sで放電させる。

【0167】

そして、第1及び第2ステージB S T 1、B S T 2の前々にはステージが存在しない。したがって、第1ステージB S T 1は第1スキャンパルスV o u t 1を出力し、これを第1ゲートライン及び第2ステージB S T 2に供給する。これと同様に、第2ステージB S T 2は、第2スキャンパルスV o u t 2を出力し、これを第2ゲートライン及び第3ステージB S T 3に供給する。

【0168】

そして、第2ダミーステージB S T n + 2の次はステージが存在しない。したがって、第2ダミーステージB S T n + 2の第21N M O SトランジスタT r 21のソース端子、第22N M O SトランジスタT r 22のドレイン端子、及び第23N M O SトランジスタT r 23のドレイン端子は、第nステージB S T nの第20N M O SトランジスタT r 20のゲート端子に接続される。

【0169】

第2シフトレジスタ3 0 1 bに備えられた各ステージB S T 1～B S T n + 2も、第1シフトレジスタ3 0 1 aに備えられた各ステージB S T 1～B S T n + 2と同じ回路構成を有する。

【0170】

このように構成された本発明の第1の実施の形態によるシフトレジスタの動作について説明すると、次の通りである。

【0171】

図10A及び図10Bは、図9の回路構成を有する第1シフトレジスタの第1乃至第3ステージを示す図である。

【0172】

ここで、第1フレームの間に第3電圧源V D D 3が正極性の電圧に維持され、第4電圧源V D D 4が負極性の電圧に維持されると仮定し、第2フレームの間に第3電圧源V D D 3が負極性の電圧に維持され、第4電圧源V D D 4が正極性の電圧に維持されると仮定する。すなわち、奇数番目のフレームの間に、第3電圧源V D D 3が正極性に維持され、第4電圧源V D D 4が負極性に維持されると仮定し、偶数番目のフレームの間に、第3電圧源V D D 3が負極性に維持され、第4電圧源V D D 4が正極性に維持されると仮定する。

【0173】

まず、スタートパルスS Pが第1N M O SトランジスタT r 1のゲート端子、第9N M O SトランジスタT r 9のゲート端子、第10N M O SトランジスタT r 10のゲート端子、第16N M O SトランジスタT r 16のゲート端子、第17N M O SトランジスタT r 17のゲート端子、第18N M O SトランジスタT r 18のゲート端子、及び第19N M O SトランジスタT r 19のゲート端子に印加されて、第1、第9、第10、第16、第17、第18、及び第19N M O SトランジスタT r 1、T r 9、T r 10、T r 16、T r 17、T r 18、T r 19をターンオンさせる。

【0174】

ここで、ターンオンされた第1N M O SトランジスタT r 1を介して第1電圧源V D Dが第1ノードQに供給される。このとき、第1ノードQが第1電圧源V D Dで充電されることによって、第1ノードQにゲート端子が接続された第2、第3、第8、第15、及び

第 2 1 N M O S トランジスタ T r 2 、 T r 3 、 T r 8 、 T r 1 5 、 T r 2 1 がターンオンされる。

【 0 1 7 5 】

そして、ターンオンされた第 2 及び第 8 N M O S トランジスタ T r 2 、 T r 8 を介して第 2 電圧源 V S S が第 2 ノード Q B 1 に供給される。これにより、第 2 ノード Q B 1 が放電され、第 2 ノード Q B 1 にゲート端子が接続された第 6 、第 7 、及び第 2 2 N M O S トランジスタ T r 6 、 T r 7 、 T r 2 2 がターンオフされる。

【 0 1 7 6 】

また、ターンオンされた第 3 及び第 1 9 N M O S トランジスタ T r 3 、 T r 1 9 を介して第 2 電圧源 V S S が第 3 ノード Q B 2 に供給される。これにより、第 3 ノード Q B 2 が放電され、第 3 ノード Q B 2 にゲート端子が接続された第 1 3 、第 1 4 及び第 2 3 N M O S トランジスタ T r 1 3 、 T r 1 4 、 T r 2 3 がターンオフされる。

【 0 1 7 7 】

そして、ターンオンされた第 8 、第 9 及び第 1 0 N M O S トランジスタ T r 8 、 T r 9 、 T r 1 0 を介して第 2 電圧源 V S S が第 5 N M O S トランジスタ T r 5 のゲート端子に供給される。また、正極性の第 3 電圧源 V D D 3 によって 1 フレームの間に常にターンオン状態を維持する第 4 N M O S トランジスタ T r 4 を介して、第 3 電圧源 V D D 3 が第 5 N M O S トランジスタ T r 5 のゲート端子に供給される。したがって、第 5 N M O S トランジスタ T r 5 のゲート端子には第 2 電圧源 V S S と第 3 電圧源 V D D 3 が供給される。このとき、第 5 N M O S トランジスタ T r 5 のゲート端子に第 2 電圧源 V S S を供給するトランジスタの数が、第 5 N M O S トランジスタ T r 5 のゲート端子に第 3 電圧源 V D D 3 を供給するトランジスタの数よりも多いので、第 5 N M O S トランジスタ T r 5 のゲート端子には第 2 電圧源 V S S が維持される。したがって、第 5 N M O S トランジスタ T r 5 はターンオフされる。

【 0 1 7 8 】

そして、ターンオンされた第 1 5 、第 1 6 及び第 1 7 N M O S トランジスタ T r 1 5 、 T r 1 6 、 T r 1 7 を介して第 2 電圧源 V S S が第 1 2 N M O S トランジスタ T r 1 2 のゲート端子に供給される。したがって、第 1 2 N M O S トランジスタ T r 1 2 はターンオフされる。一方、第 1 1 N M O S トランジスタ T r 1 1 は負極性の第 4 電圧源 V D D 4 によって 1 フレームの間に常にターンオフ状態を維持する。

【 0 1 7 9 】

このように第 1 ステージ B S T 1 の第 1 ノード Q が第 1 電圧源 V D D で充電され、第 2 及び第 3 ノード Q B 1 、 Q B 2 が第 2 電圧源 V S S で放電されることによって、第 1 ステージ B S T 1 がイネーブルされる。

【 0 1 8 0 】

この状態で、第 1 ステージ B S T 1 の第 2 1 N M O S トランジスタ T r 2 1 に第 1 クロックパルス C L K 1 が供給されると、第 2 1 N M O S トランジスタ T r 2 1 は、第 1 クロックパルス C L K 1 を第 1 スキャンパルス V o u t 1 として出力する。このとき、第 1 クロックパルス C L K 1 とスタートパルス S P は重なって出力されるので、第 1 スキャンパルス V o u t 1 はスタートパルス S P と重なって出力される。

【 0 1 8 1 】

この第 1 スキャンパルス V o u t 1 は、第 1 ゲートライン及び第 2 ステージ B S T 2 に供給される。すなわち、第 1 ステージ B S T 1 からの第 1 スキャンパルス V o u t 1 は、第 2 ステージ B S T 2 の第 1 、第 9 、第 1 0 、第 1 6 、第 1 7 、第 1 8 及び第 1 9 N M O S トランジスタ T r 1 、 T r 9 、 T r 1 0 、 T r 1 6 、 T r 1 7 、 T r 1 8 、 T r 1 9 に供給される。これにより、第 2 ステージ B S T 2 の第 1 ノード Q が充電され、第 2 及び第 3 ノード Q B 1 、 Q B 2 が放電される。すなわち、第 2 ステージ B S T 2 は第 1 スキャンパルス V o u t 1 によってイネーブルされる。言い換えれば、第 1 ステージ B S T 1 がスタートパルス S P によってイネーブルされるのと同様に、第 2 ステージ B S T 2 は第 1 スキャンパルス V o u t 1 によってイネーブルされる。この状態で、第 2 ステージ B S T 2

10

20

30

40

50

の第21N MOSトランジスタTr21に第2クロックパルスCLK2が供給されると、第21N MOSトランジスタTr21は、第2クロックパルスCLK2を第2スキャンパルスVout2として出力する。このとき、第2クロックパルスCLK2は第1クロックパルスCLK1と重なるので、第2スキャンパルスVout2は第1スキャンパルスVout1と重なって出力される。

【0182】

この第2スキャンパルスVout2は、第2ゲートライン及び第3ステージBST3に供給される。すなわち、第2ステージBST2からの第2スキャンパルスVout2は、第3ステージBST3の第1、第9、第10、第16、第17、第18及び第19N MOSトランジスタTr1、Tr9、Tr10、Tr16、Tr17、Tr18、Tr19に供給される。これにより、第3ステージBST3の第1ノードQが充電され、第2及び第3ノードQB1、QB2が放電される。すなわち、第3ステージBST3は第2スキャンパルスVout2によってイネーブルされる。言い換えれば、第1ステージBST1がスタートパルスSPによってイネーブルされるのと同様に、第3ステージBST3は第2スキャンパルスVout2によってイネーブルされる。

【0183】

この状態で、第3ステージBST3の第21N MOSトランジスタTr21に第3クロックパルスCLK3が供給されると、第21N MOSトランジスタTr21は、第3クロックパルスCLK3を第3スキャンパルスVout3として出力する。このとき、第3クロックパルスCLK3は第2クロックパルスCLK2と重なるので、第3スキャンパルスVout3は第2スキャンパルスVout2と重なって出力される。

【0184】

この第3スキャンパルスVout3は、第3ゲートライン及び第4ステージBST4に供給される。すなわち、第3ステージBST3からの第3スキャンパルスVout3は第4ステージBST4の第1、第9、第10、第16、第17、第18及び第19N MOSトランジスタTr1、Tr9、Tr10、Tr16、Tr17、Tr18、Tr19に供給される。これにより、第4ステージBST4の第1ノードQが充電され、第2及び第3ノードQB1、QB2が放電される。すなわち、第4ステージBST4は第3スキャンパルスVout3によってイネーブルされる。言い換えれば、第1ステージBST1がスタートパルスSPによってイネーブルされるのと同様に、第4ステージBST4は第3スキャンパルスVout3によってイネーブルされる。

【0185】

この状態で、第4ステージBST4の第21N MOSトランジスタTr21に第4クロックパルスCLK4が供給されると、第21N MOSトランジスタTr21は、第4クロックパルスCLK4を第4スキャンパルスVout4として出力する。このとき、第4クロックパルスCLK4は第3クロックパルスCLK3と重なるので、第4スキャンパルスVout4は第3スキャンパルスVout3と重なって出力される。

【0186】

一方、第3ステージBST3から出力された第3スキャンパルスVout3は、第1ステージBST1の第20N MOSトランジスタTr20にも供給される。すなわち、第3スキャンパルスVout3は、第1ステージBST1に備えられた第20N MOSトランジスタTr20のゲート端子に供給される。これにより、第1ステージBST1がディセーブルされる。

【0187】

具体的に、第3スキャンパルスVout3は、第1ステージBST1に備えられた第20N MOSトランジスタTr20をターンオンさせる。すると、第2電圧源VSSが、ターンオンされた第20N MOSトランジスタTr20を介して第1ステージBST1の第1ノードQに供給される。これにより、第1ステージBST1の第1ノードQが放電される。したがって、第1ステージBST1の第1ノードQに接続された第2、第3、第8、第15及び第21N MOSトランジスタTr2、Tr3、Tr8、Tr15、Tr21が

ターンオフされる。また、このとき、スタートパルス S P がローに変化することによって、ロー状態のスタートパルス S P の供給される第 1 ステージ B S T 1 の第 1、第 9、第 10、第 16、第 17、第 18 及び第 19 NMOS トランジスタ T r 1、T r 9、T r 10、T r 16、T r 17、T r 18、T r 19 がターンオフされる。

【 0 1 8 8 】

ここで、第 1 ステージ B S T 1 の第 9 及び第 10 NMOS トランジスタ T r 9、T r 10 はターンオフされることによって、第 1 ステージ B S T 1 の第 5 NMOS トランジスタ T r 5 のゲート端子にはそれ以上第 2 電圧源 V S S が供給されなくなる。その代わりに、第 1 ステージ B S T 1 の第 5 NMOS トランジスタ T r 5 のゲート端子には、第 4 NMOS トランジスタ T r 4 を介して第 3 電圧源 V D D 3 が供給される。その結果、第 5 NMOS トランジスタ T r 5 は、第 3 電圧源 V D D 3 によってターンオンされる。このターンオンされた第 5 NMOS トランジスタ T r 5 を介して第 3 電圧源 V D D 3 が第 1 ステージ B S T 1 の第 2 ノード Q B 1 に供給される。これにより、第 1 ステージ B S T 1 の第 2 ノード Q B 1 が充電され、第 1 ステージ B S T 1 の第 2 ノード Q B 1 にゲート端子が接続された第 6、第 7 及び第 22 NMOS トランジスタ T r 6、T r 7、T r 22 がターンオンされる。

【 0 1 8 9 】

一方、ターンオンされた第 6 NMOS トランジスタ T r 6 を介して第 2 電圧源 V S S が第 1 ステージ B S T 1 の第 1 ノード Q に供給される。これにより、第 1 ステージ B S T 1 の第 1 ノード Q の放電速度がより速くなる。そして、ターンオンされた第 7 NMOS トランジスタ T r 7 を介して第 2 電圧源 V S S が第 1 ステージ B S T 1 の第 3 ノード Q B 2 に供給される。これにより、第 3 ノード Q B 2 が放電され、第 3 ノード Q B 2 にゲート端子が接続された第 13、第 14 及び第 23 NMOS トランジスタ T r 13、T r 14、T r 23 がターンオフされる。

【 0 1 9 0 】

このように第 3 ステージ B S T 3 からの第 3 スキャンパルス V o u t 3 によって第 1 ステージ B S T 1 の第 1 ノード Q 及び第 3 ノード Q B 2 は放電され、第 2 ノード Q B 1 が充電される。すなわち、第 1 ステージ B S T 1 は、第 3 ステージ B S T 3 からの第 3 スキャンパルス V o u t 3 に応答して、ディセーブルされる。このディセーブルされた第 1 ステージ B S T 1 は、自分に備えられた第 22 NMOS トランジスタ T r 22 を介して第 2 電圧源 V S S を出力する。そして、この第 2 電圧源 V S S を第 1 ゲートラインに供給する。

【 0 1 9 1 】

このような方式で、各ステージ B S T 1 ~ B S T n + 2 は、前のステージから出力されたスキャンパルスによってイネーブルされる。そして、各ステージ B S T 1 ~ B S T n + 2 は、次々のステージからのスキャンパルスによってディセーブルされる。

【 0 1 9 2 】

一方、第 2 フレームには、第 3 電圧源 V D D 3 が負極性に維持され、第 4 電圧源 V D D 4 が正極性に維持される。これにより、各ステージ B S T 1 ~ B S T n + 2 がディセーブルされる時、各ステージ B S T 1 ~ B S T n + 2 の第 2 ノード Q B 1 が放電され、第 3 ノード Q B 2 が充電される。したがって、各ステージ B S T 1 ~ B S T n + 2 がディセーブルされる時、第 3 ノード Q B 2 にゲート端子が接続された第 23 NMOS トランジスタ T r 23 を介して第 2 電圧源 V S S が出力される。このようにフレーム別に第 2 及び第 3 ノード Q B 1、Q B 2 が交互に充電 / 放電されることで、出力部 900b に備えられた第 22 及び第 23 NMOS トランジスタ T r 22、T r 23 の劣化が防止される。

【 0 1 9 3 】

第 2 シフトレジスタ 301b に備えられた各ステージ B S T 1 ~ B S T n + 2 も、前記第 1 シフトレジスタ 301a に備えられた各ステージ B S T 1 ~ B S T n + 2 と同様に動作する。ただし、第 1 シフトレジスタ 301a に備えられた各ステージ B S T 1 ~ B S T n + 2 は、各ゲートライン G L 1 ~ G L n の一側にスキャンパルス V o u t 1 ~ V o u t n を印加し、第 2 シフトレジスタ 301b に備えられた各ステージ B S T 1 ~ B S T n + 2

10

20

30

40

50

2は、各ゲートライン $GL_1 \sim GL_n$ の他側にスキャンパルス $V_{out1} \sim V_{outn}$ を供給する。

【0194】

以下、本発明の第2の実施の形態によるシフトレジスタについて詳細に説明する。

【0195】

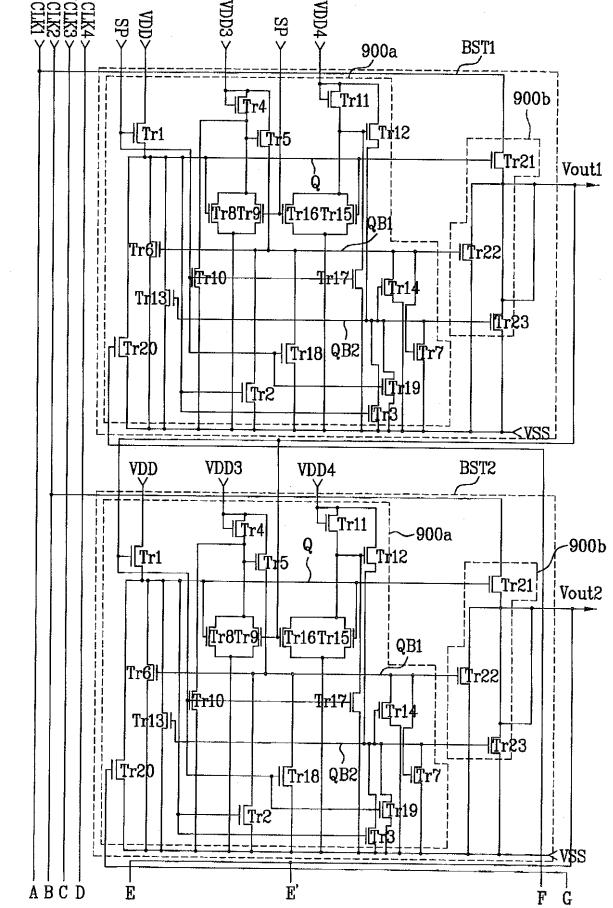

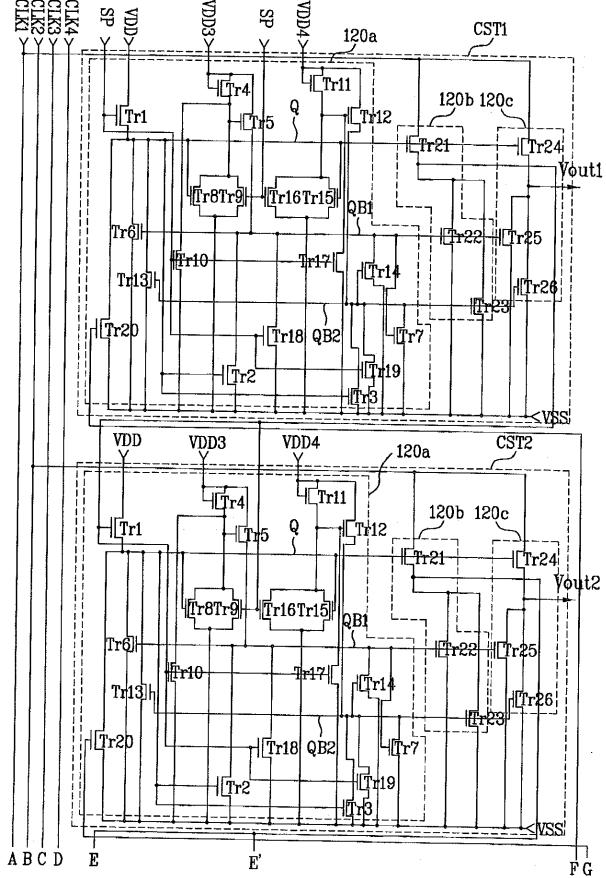

図11は、本発明の第2の実施の形態によるシフトレジスタを示す図である。

本発明の第2の実施の形態によるシフトレジスタは、図11に示すように、第1シフトレジスタ $110a$ と第2シフトレジスタ $110b$ とで構成される。

【0196】

ここで、第1シフトレジスタ $110a$ は互いに従属的に接続された $n$ 個のステージ $CS_1 \sim CST_n$ 、そして第1及び第2ダミーステージ $CST_{n+1} \sim CST_{n+2}$ で構成される。ここで、各ステージ $CST_1 \sim CST_{n+2}$ は、スキャンパルス $V_{out1} \sim V_{outn+2}$ を二つずつ出力する。すなわち、各ステージ $CST_1 \sim CST_{n+2}$ は二つのスキャンパルスを1対として同時に出力し、また、各ステージ $CST_1 \sim CST_{n+2}$ は1対のスキャンパルスを順に出力する。このとき、第1及び第2ダミーステージ $CST_{n+1} \sim CST_{n+2}$ 以外のステージ $CST_1 \sim CST_n$ から出力されたスキャンパルス $V_{out1} \sim V_{outn}$ は、液晶パネル300のゲートライン $GL_1 \sim GL_n$ に順に供給されて、ゲートライン $GL_1 \sim GL_n$ を順にスキャニングするようになる。

【0197】

すなわち、まず、第1ステージ $CST_1$ が二つの第1スキャンパルス $V_{out1}$ を同時に出力し、続いて第2ステージ $CST_2$ が二つの第2スキャンパルス $V_{out2}$ を同時に出力し、続いて第3ステージ $CST_3$ が二つの第3スキャンパルス $V_{out3}$ を同時に出力する。このような方式で、最後には第 $n$ ステージ $CST_n$ が二つの第 $n$ スキャンパルス $V_{outn}$ を同時に出力する。

【0198】

一方、第 $n$ ステージ $CST_n$ が二つの第 $n$ スキャンパルス $V_{outn}$ を同時に出力した後、第1ダミーステージ $CST_{n+1}$ が第 $n+1$ スキャンパルス $V_{outn+1}$ を出力するが、このとき、第1ダミーステージ $CST_{n+1}$ から出力された第 $n+1$ スキャンパルス $V_{outn+1}$ はゲートラインには供給されず、第 $n-1$ ステージ $CST_{n-1}$ にのみ供給される。

【0199】

そして、第1ダミーステージ $CST_{n+1}$ が二つの第 $n+1$ スキャンパルス $V_{outn+1}$ を同時に出力した後、第2ダミーステージ $CST_{n+2}$ が第 $n+2$ スキャンパルス $V_{outn+2}$ を出力するが、このとき、第2ダミーステージ $CST_{n+2}$ から出力された第 $n+2$ スキャンパルス $V_{outn+2}$ はゲートラインには供給されず、第 $n$ ステージ $CST_n$ にのみ供給される。

【0200】

また、第1シフトレジスタ $110a$ に備えられた各ステージ $CST_1 \sim CST_{n+2}$ から出力されるスキャンパルス $V_{out1} \sim V_{outn+2}$ は互いに所定区間重なって出力される。ここで、一つのステージは二つの出力端子（以下、「第1及び第2出力端子」という。）を有し、第1及び第2出力端子を介して同時に二つのスキャンパルスを出力する。

【0201】

言い換えれば、一つのステージは第1出力端子を介してスキャンパルスを出力すると同時に、第2出力端子を介してスキャンパルスを出力する。したがって、各ステージ $CST_1 \sim CST_{n+2}$ からは二つのスキャンパルスが同時に出力される。このとき、各ステージ $CST_1 \sim CST_{n+2}$ の各第1出力端子を介して出力されるスキャンパルスは、互いに所定幅重なる。もちろん、各ステージ $CST_1 \sim CST_{n+2}$ の各第2出力端子を介して出力されるスキャンパルスも、互いに所定幅重なる。例えば、第1ステージ $CST_1$ から出力された二つの第1スキャンパルス $V_{out1}$ は、第2ステージ $CST_2$ から出力さ

10

20

30

40

50

れた二つの第2スキャンパルス  $V_{out2}$  と互いに所定幅重なる。

【0202】

ここで、第1シフトレジスタ110aに備えられた各ステージ  $CST_1 \sim CST_{n+2}$  は、二つのスキャンパルスのうち一つを自分に該当するゲートラインに供給し、残りの一つを次のステージと前々のステージに供給する。例えば、第3ステージ  $CST_3$  は、二つの第3スキャンパルス  $V_{out3}$  を出力し、一つの第3スキャンパルス  $V_{out3}$  を第3ゲートラインに供給し、残り一つの第3スキャンパルス  $V_{out3}$  を第4ステージ  $CST_4$  と第1ステージ  $CST_1$  に供給する。一方、第2ダミーステージ  $CST_{n+2}$  は、二つのスキャンパルスを出力しても良く、一つのスキャンパルスを出力しても良い。

【0203】

一方、このように構成された第1シフトレジスタ110aの全体ステージ  $CST_1 \sim CST_{n+2}$  には、第1乃至第4電圧源  $V_{DD}$ 、 $V_{SS}$ 、 $V_{DD3}$ 、 $V_{DD4}$ 、そして互いに順次的な位相差をもって循環する第1乃至第4クロックパルス  $CLK_1 \sim CLK_4$  のうち一つのクロックパルスが印加される。ここで、第1電圧源  $V_{DD}$  は正極性の直流電圧源を表し、第2電圧源  $V_{SS}$  は負極性の電圧源を表す。そして、第3電圧源  $V_{DD3}$  及び第4電圧源  $V_{DD4}$  は、フレーム別に反転された極性を有する交流電圧源である。ここで、第3電圧源  $V_{DD3}$  は、第4電圧源  $V_{DD4}$  に反転された位相を有する。すなわち、同一フレーム内において第3電圧源  $V_{DD3}$  と第4電圧源  $V_{DD4}$  が相異なる極性を示す。

【0204】

一方、上述したように、第1乃至第4クロックパルス  $CLK_1 \sim CLK_4$  は互いに1パルス幅ずつ位相遅延されて出力される。すなわち、第2クロックパルス  $CLK_2$  は、第1クロックパルス  $CLK_1$  よりも1パルス幅だけ位相遅延されて出力され、第3クロックパルス  $CLK_3$  は、第2クロックパルス  $CLK_2$  よりも1パルス幅だけ位相遅延されて出力され、第4クロックパルス  $CLK_4$  は、第3クロックパルス  $CLK_3$  よりも1パルス幅だけ位相遅延されて出力され、第1クロックパルス  $CLK_1$  は、第4クロックパルス  $CLK_4$  よりも1パルス幅だけ位相遅延されて出力される。

【0205】

このとき、第1乃至第4クロックパルス  $CLK_1 \sim CLK_4$  は順に出力され、また、循環しつつ出力される。すなわち、第1クロックパルス  $CLK_1$  から第4クロックパルス  $CLK_4$  まで順に出力された後、再び第1クロックパルス  $CLK_1$  から第4クロックパルス  $CLK_4$  まで順に出力される。したがって、第1クロックパルス  $CLK_1$  は、第4クロックパルス  $CLK_4$  及び第2クロックパルス  $CLK_2$  間に該当する期間で出力される。ここで、第4クロックパルス  $CLK_4$  とスタートパルス  $SP$  を互いに同期させて出力しても良い。このときには、第1乃至第4クロックパルス  $CLK_1 \sim CLK_4$  のうち第4クロックパルス  $CLK_4$  が最初に出力される。

【0206】

一方、本発明による第1シフトレジスタ110aは、二つ以上のクロックパルスを使用することができる。すなわち、本発明によるシフトレジスタは、第1乃至第4クロックパルス  $CLK_1 \sim CLK_4$  のうち第1及び第2クロックパルス  $CLK_1$ 、 $CLK_2$  のみを使用しても良く、第1乃至第3クロックパルス  $CLK_1 \sim CLK_3$  のみを使用しても良い。また、本発明によるシフトレジスタは、順に出力される4個以上のクロックパルスを使用しても良い。

【0207】

第2シフトレジスタ110bも、上述した第1シフトレジスタ110aと同じ構成を有する。

【0208】

次に、本発明の第2の実施の形態によるシフトレジスタに備えられたステージの構成についてより具体的に説明する。

【0209】

図12は、図11の第1シフトレジスタに備えられた第3ステージを示す図である。

10

20

30

40

50

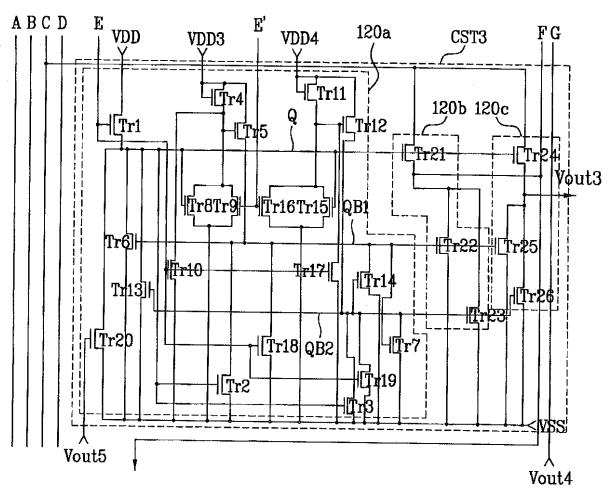

## 【0210】

第3ステージB S T 3は、図12に示すように、大きく、第1、第2及び第3ノードQ、Q B 1、Q B 2の充電及び放電を制御するノード制御部120aと、第1、第2及び第3ノードQ、Q B 1、Q B 2の充電/放電状態によってそれぞれターンオンされて、スキャンパルスまたは第2電圧源V S Sを選択的に出力する出力部120b、120cとで構成される。ここで、第1、第2及び第3ノードQ、Q B 1、Q B 2は選択的に充電及び放電されるが、具体的に、第1ノードQが充電状態にあると第2ノードQ B 1及び第3ノードQ B 2とも放電状態を維持し、第1ノードQが放電状態にあると第2ノードQ B 1及び第3ノードQ B 2のうちいずれか一つが充電状態を維持する。

## 【0211】

すなわち、奇数番目のフレームでは、第1ノードQが放電状態のとき、第2ノードQ B 1が充電され、第3ノードQ B 2が放電され、そして偶数番目のフレームでは、第1ノードQが放電状態の時、第2ノードQ B 1が放電され、第3ノードQ B 2が充電される。このように第1ノードQが放電状態にあるとき、第2ノードQ B 1及び第3ノードQ B 2にフレーム別に異なる極性の電圧源V D D 3、V D D 4を印加(充電及び放電)する理由は、第2ノードQ B 1及び第3ノードQ B 2にゲート端子が接続されたスイッチング素子の劣化を防止するためである。

## 【0212】

第3ステージC S T 3のノード制御部120aは、第1乃至第20N M O SトランジスタT r 1～T r 20で構成される。

## 【0213】

第1N M O SトランジスタT r 1は、前のステージからのスキャンパルスに応答して、第1ノードQを第1電圧源V D Dで充電させる。すなわち、第1N M O SトランジスタT r 1は、第2ステージC S T 2からの第2スキャンパルスV o u t 2に応答して、第1ノードQを第1電圧源V D Dで充電させる。このため、第1N M O SトランジスタT r 1のゲート端子は、第2ステージC S T 2に接続され、ソース端子は、第1電圧源V D Dを伝送する電源ラインに接続され、ドレイン端子は第1ノードQに接続される。

## 【0214】

第2N M O SトランジスタT r 2は、第1ノードQに充電された第1電圧源V D Dに応答して、第2ノードQ Bを第2電圧源V S Sで放電させる。このため、第2N M O SトランジスタT r 2のゲート端子は、第1ノードQに接続され、ソース端子は第2ノードQ B 1に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

## 【0215】

第3N M O SトランジスタT r 3は、第1ノードQに充電された第1電圧源V D Dに応答して、第3ノードQ B 2を第2電圧源V S Sで放電させる。このため、第3N M O SトランジスタT r 3のゲート端子は、第1ノードQに接続され、ソース端子は第3ノードQ B 2に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

## 【0216】

第4N M O SトランジスタT r 4は、フレームごとに異なる極性を有する第3電圧源V D D 3に応答してターンオンまたはターンオフされ、ターンオン時に第3電圧源V D D 3を出力する。このため、第4N M O SトランジスタT r 4のゲート端子は、第3電圧源V D D 3を伝送する電源ラインに接続され、ソース端子は、第3電圧源V D D 3を伝送する電源ラインに接続される。

## 【0217】

第5N M O SトランジスタT r 5は、第4N M O SトランジスタT r 4から出力された第3電圧源V D D 3に応答して第2ノードQ Bを第3電圧源V D D 3で充電させる。このため、第5N M O SトランジスタT r 5のゲート端子は、第4N M O SトランジスタT r 4のドレイン端子に接続され、ソース端子は、第3電圧源V D D 3を伝送する電源ラインに接続され、ドレイン端子は第2ノードQ Bに接続される。

## 【0218】

第6N MOSトランジスタTr6は、第2ノードQBに充電された第3電圧源VDD3に応答して、第1ノードQを第2電圧源VSSで放電させる。このため、第6N MOSトランジスタTr6のゲート端子は、第2ノードQBに接続され、ソース端子は第1ノードQに接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

## 【0219】

第7N MOSトランジスタTr7は、第2ノードQBに充電された第3電圧源VDD3に応答して、第3ノードQB2を第2電圧源VSSで放電させる。このため、第7N MOSトランジスタTr7のゲート端子は、第2ノードQBに接続され、ソース端子は前記第3ノードQB2に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

## 【0220】

第8N MOSトランジスタTr8は、第1ノードQに充電された第1電圧源VDDに応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5N MOSトランジスタTr5をターンオフさせる。このため、第8N MOSトランジスタTr8のゲート端子は、第1ノードQに接続され、ソース端子は、第5N MOSトランジスタTr5のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

## 【0221】

第9N MOSトランジスタTr9は、前のステージからのスキャンパルスに応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5N MOSトランジスタTr5をターンオフさせる。すなわち、第9N MOSトランジスタTr9は、第2ステージCST2からの第2スキャンパルスVout2に応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5N MOSトランジスタTr5をターンオフさせる。このため、第9N MOSトランジスタTr9のゲート端子は、第2ステージCST2に接続され、ソース端子は、第5N MOSトランジスタTr5のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

## 【0222】

第10N MOSトランジスタTr10は、前のステージからのスキャンパルスに応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5N MOSトランジスタTr5をターンオフさせる。すなわち、第10N MOSトランジスタTr10は、第2ステージCST2からの第2スキャンパルスVout2に応答して、第5N MOSトランジスタTr5のゲート端子に第2電圧源VSSを供給することによって、第5N MOSトランジスタTr5をターンオフさせる。このため、第10N MOSトランジスタTr10のゲート端子は、第2ステージCST2に接続され、ソース端子は、第5N MOSトランジスタTr5のゲート端子に接続され、ドレイン端子は、第2電圧源VSSを伝送する電源ラインに接続される。

## 【0223】

第11N MOSトランジスタTr11は、フレームごとに異なる極性を有する第4電圧源VDD4に応答してターンオンまたはターンオフされ、ターンオン時に、第4電圧源VDD4を出力する。このため、第11N MOSトランジスタTr11のゲート端子は、第4電圧源VDD4を伝送する電源ラインに接続され、ソース端子は、第4電圧源VDD4を伝送する電源ラインに接続される。ここで、第4電圧源VDD4は、毎フレームごとに第3電圧源VDD3に反転された極性を有する。

## 【0224】

第12N MOSトランジスタTr12は、第11N MOSトランジスタTr11から出力された第4電圧源VDD4に応答して、第3ノードQB2を第4電圧源VDD4で充電させる。このため、第12N MOSトランジスタTr12のゲート端子は、第11N MOSトランジスタTr11のドレイン端子に接続され、ソース端子は、第4電圧源VDD4

10

20

30

40

50

を伝送する電源ラインに接続され、ドレイン端子は第3ノードQ B 2に接続される。

【0225】

第13NMOSトランジスタTr13は、第3ノードQ B 2に充電された第4電圧源V D D 4に応答して、第1ノードQを第2電圧源V S Sで放電させる。このため、第13NMOSトランジスタTr13のゲート端子は、第3ノードQ B 2に接続され、ソース端子は第1ノードQに接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

【0226】

第14NMOSトランジスタTr14は、第3ノードQ B 2に充電された第4電圧源V D D 4に応答して、第2ノードQ Bを第2電圧源V S Sで放電させる。このため、第14NMOSトランジスタTr14のゲート端子は、第3ノードQ B 2に接続され、ソース端子は第2ノードQ Bに接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

【0227】

第15NMOSトランジスタTr15は、第1ノードQに充電された第1電圧源V D Dに応答して、第12NMOSトランジスタTr12のゲート端子に第2電圧源V S Sを供給することによって、第12NMOSトランジスタTr12をターンオフさせる。このため、第15NMOSトランジスタTr15のゲート端子は、第1ノードQに接続され、ソース端子は、第12NMOSトランジスタTr12のゲート端子に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

【0228】

第16NMOSトランジスタTr16は、前のステージからのスキャンパルスに応答して、第12NMOSトランジスタTr12のゲート端子に第2電圧源V S Sを供給することによって、第12NMOSトランジスタTr12をターンオフさせる。すなわち、第16NMOSトランジスタTr16は、第2ステージC S T 2からの第2スキャンパルスV out 2に応答して、第12NMOSトランジスタTr12をターンオフさせる。このため、第16NMOSトランジスタTr16のゲート端子は、第2ステージC S T 2に接続され、ソース端子は、第12NMOSトランジスタTr12のゲート端子に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

【0229】

第17NMOSトランジスタTr17は、前のステージからのスキャンパルスに応答して、第12NMOSトランジスタTr12のゲート端子に第2電圧源V S Sを供給することによって、第12NMOSトランジスタTr12をターンオフさせる。すなわち、第17NMOSトランジスタTr17は、第2ステージC S T 2からの第2スキャンパルスV out 2に応答して、第12NMOSトランジスタTr12をターンオフさせる。このため、第17NMOSトランジスタTr17のゲート端子は、第2ステージC S T 2に接続され、ソース端子は、第12NMOSトランジスタTr12のゲート端子に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

【0230】

第18NMOSトランジスタTr18は、前のステージからのスキャンパルスに応答して、第2ノードQ B 1を第2電圧源V S Sで放電させる。すなわち、第18NMOSトランジスタTr18は、第2ステージC S T 2からの第2スキャンパルスV out 2に応答して、第2ノードQ B 1を第2電圧源V S Sで放電させる。このため、第18NMOSトランジスタTr18のゲート端子は、第2ステージC S T 2に接続され、ソース端子は第2ノードQ B 1に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

【0231】

第19NMOSトランジスタTr19は、前のステージからのスキャンパルスに応答して、第3ノードQ B 2を第2電圧源V S Sで放電させる。すなわち、第19NMOSトランジスタTr19は、第2ステージC S T 2からの第2スキャンパルスV out 2に応答

10

20

30

40

50

して、第3ノードQ B 2を第2電圧源V S Sで放電させる。このため、第19NMOSトランジスタTr 19のゲート端子は、第2ステージC S T 2に接続され、ソース端子は第3ノードQ B 2に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

【0232】

第20NMOSトランジスタTr 20は、次々のステージからのスキャンパルスに応答して、第1ノードQを第2電圧源V S Sで放電させる。すなわち、第20NMOSトランジスタTr 20のゲート端子は、第5ステージからの第5スキャンパルスV out 5に応答して、第1ノードQを第2電圧源V S Sで放電させる。このため、第20NMOSトランジスタTr 20のゲート端子は、第5ステージに接続され、ソース端子は第1ノードQに接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続される。

10

【0233】

第3ステージC S T 3の第1出力部120bは、第21乃至23NMOSトランジスタTr 21～Tr 23で構成される。

【0234】

第21NMOSトランジスタTr 21は、第1ノードQに充電された第1電圧源V D Dに応答して、第3クロックパルスC L K 3をスキャンパルスとして出力する。そして、このスキャンパルスを前々のステージと次のステージに供給する。このため、第21NMOSトランジスタTr 21のゲート端子は、第1ノードQに接続され、ソース端子は、第3クロックパルスC L K 3を伝送するクロックラインに接続され、ドレイン端子は、第1ステージC S T 1に備えられた第20NMOSトランジスタTr 20のゲート端子、及び第4ステージC S T 4に備えられた第1、第9、第10、第16、第17、第18及び第19NMOSトランジスタTr 1、Tr 9、Tr 10、Tr 16、Tr 17、Tr 18、Tr 19のゲート端子に接続される。

20

【0235】

第22NMOSトランジスタTr 22は、第2ノードQ B 1に充電された第3電圧源V D D 3に応答して、第2電圧源V S Sを出力する。そして、この第2電圧源V S Sを前々のステージと次のステージに供給する。このため、第22NMOSトランジスタTr 22のゲート端子は、第2ノードQ B 1に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続され、ソース端子は、第1ステージC S T 1に備えられた第20NMOSトランジスタTr 20のゲート端子、及び第4ステージC S T 4に備えられた第1、第9、第10、第16、第17、第18及び第19NMOSトランジスタTr 1、Tr 9、Tr 10、Tr 16、Tr 17、Tr 18、Tr 19のゲート端子に接続される。

30

【0236】

第23NMOSトランジスタTr 23は、第3ノードQ B 2に充電された第4電圧源V D D 4に応答して、第2電圧源V S Sを出力する。そして、この第2電圧源V S Sを前々のステージと次のステージに供給する。このため、第23NMOSトランジスタTr 23のゲート端子は、第2ノードQ B 1に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続され、ソース端子は、第1ステージC S T 1に備えられた第20NMOSトランジスタTr 20のゲート端子、及び第4ステージC S T 4に備えられた第1、第9、第10、第16、第17、第18及び第19NMOSトランジスタTr 1、Tr 9、Tr 10、Tr 16、Tr 17、Tr 18、Tr 19のゲート端子に接続される。

40

【0237】

第3ステージC S T 3の第2出力部120cは、第24乃至第26NMOSトランジスタTr 24～Tr 26で構成される。

【0238】

第24NMOSトランジスタTr 24は、第1ノードQに充電された第1電圧源V D Dに応答して、第3クロックパルスC L K 3をスキャンパルスとして第3ゲートラインに出力する。このため、第24NMOSトランジスタTr 24のゲート端子は、第1ノードQ

50

に接続され、ソース端子は、第3クロックパルスC L K 3を伝送するクロックラインに接続され、ドレイン端子は第3ゲートラインに接続される。

【0239】

第25NMOSトランジスタTr25は、第2ノードQ B 1に充電された第3電圧源V D D 3に応答して、第2電圧源V S Sを第3ゲートラインに出力する。このため、第25NMOSトランジスタTr25のゲート端子は、第2ノードQ B 1に接続され、ドレイン端子は第2電圧源V S Sを伝送する電源ラインに接続され、ソース端子は、第3ゲートラインに接続される。

【0240】

第26NMOSトランジスタTr26は、第3ノードQ B 2に充電された第4電圧源V D D 4に応答して、第2電圧源V S Sを第3ゲートラインに出力する。このため、第26NMOSトランジスタTr26のゲート端子は第2ノードQ B 1に接続され、ドレイン端子は、第2電圧源V S Sを伝送する電源ラインに接続され、ソース端子は第3ゲートラインに接続される。

【0241】

第1及び第2ステージC S T 1、C S T 2、第4乃至第nステージC S T 4 ~ C S T n、第1及び第2ダミーステージC S T n + 1、C S T n + 2も、上述した第2ステージC S T 2と同じ構成を有する。

【0242】

ただし、第1ステージC S T 1の前にはステージが存在しないので、第1ステージC S T 1に備えられた第1、第9、第10、第16、第17、第18及び第19NMOSトランジスタTr1、Tr9、Tr10、Tr16、Tr17、Tr18、Tr19には、タイミングコントローラからのスタートパルスS Pが供給される。すなわち、第1ステージC S T 1の第1NMOSトランジスタTr1は、タイミングコントローラからのスタートパルスS Pに応答して、第1ノードQを第1電圧源V D Dで充電させる。

【0243】

また、第1ステージC S T 1の第9NMOSトランジスタTr9は、タイミングコントローラからのスタートパルスS Pに応答して、第1ステージC S T 1の第2ノードQ B 1を第2電圧源V S Sで放電させる。

【0244】

また、第1ステージC S T 1の第10NMOSトランジスタTr10は、タイミングコントローラからのスタートパルスに応答して、第4NMOSトランジスタTr4のゲート端子に第2電圧源V S Sを供給することによって、第4NMOSトランジスタTr4をターンオフさせる。

【0245】

また、第1ステージC S T 1の第16NMOSトランジスタTr16は、タイミングコントローラからのスタートパルスに応答して、第12NMOSトランジスタTr12のゲート端子に第2電圧源V S Sを供給することによって、第12NMOSトランジスタTr12をターンオフさせる。

【0246】

また、第1ステージC S T 1の第17NMOSトランジスタTr17は、タイミングコントローラからのスタートパルスに応答して、第12NMOSトランジスタTr12のゲート端子に第2電圧源V S Sを供給することによって、第12NMOSトランジスタTr12をターンオフさせる。

【0247】

また、第1ステージC S T 1の第18NMOSトランジスタTr18は、タイミングコントローラからのスタートパルスS Pに応答して、第2ノードQ B 1を第2電圧源V S Sで放電させる。

【0248】

また、第1ステージC S T 1の第19NMOSトランジスタTr19は、タイミングコ

10

20

30

40

50

ントローラからのスタートパルス S P に応答して、第 3 ノード Q B 2 を第 2 電圧源 V S S で放電させる。

【 0 2 4 9 】

そして、第 1 及び第 2 ステージ C S T 1 、 C S T 2 の前々にはステージが存在しない。したがって、第 1 ステージ C S T 1 は第 1 スキャンパルス V o u t 1 を出力し、これを第 1 ゲートライン及び第 2 ステージ C S T 2 に供給する。これと同様に、第 2 ステージ C S T 2 は、第 2 スキャンパルス V o u t 2 を出力し、これを第 2 ゲートライン及び第 3 ステージ C S T 3 に供給する。

【 0 2 5 0 】

そして、第 2 ダミーステージ C S T n + 2 の次にはステージが存在しない。したがって、第 2 ダミーステージ C S T n + 2 の第 2 1 N M O S トランジスタ T r 2 1 のソース端子、第 2 2 N M O S トランジスタ T r 2 2 のドレイン端子、及び第 2 3 N M O S トランジスタ T r 2 3 のドレイン端子は、第 n ステージ C S T n の第 2 0 N M O S トランジスタ T r 2 0 のゲート端子に接続される。

【 0 2 5 1 】

第 2 シフトレジスタ 1 1 0 b に備えられた各ステージ C S T 1 ~ C S T n + 2 も、第 1 シフトレジスタ 1 1 0 a に備えられた各ステージ C S T 1 ~ C S T n + 2 と同じ構成を有する。

【 0 2 5 2 】