(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-293371

(P2006-293371A)

(43) 公開日 平成18年10月26日(2006.10.26)

|                                        |                                             |             |

|----------------------------------------|---------------------------------------------|-------------|

| (51) Int.C1.                           | F 1                                         | テーマコード (参考) |

| <b>G09G 3/36</b> (2006.01)             | G09G 3/36                                   | 2 H 09 3    |

| <b>G02F 1/133</b> (2006.01)            | G02F 1/133                                  | 5 C 00 6    |

| <b>G09G 3/20</b> (2006.01)             | G09G 3/20                                   | 5 C 08 0    |

|                                        | G09G 3/20                                   | 6 2 2 B     |

|                                        | G09G 3/20                                   | 6 2 2 E     |

|                                        | G09G 3/20                                   | 6 2 1 L     |

| 審査請求 未請求 請求項の数 30 O L (全 17 頁) 最終頁に続く  |                                             |             |

| (21) 出願番号 特願2006-109210 (P2006-109210) | (71) 出願人 390019839                          |             |

| (22) 出願日 平成18年4月11日 (2006.4.11)        | 三星電子株式会社                                    |             |

| (31) 優先権主張番号 10-2005-0029903           | S a m s u n g E l e c t r o n i c s         |             |

| (32) 優先日 平成17年4月11日 (2005.4.11)        | C o . , L t d .                             |             |

| (33) 優先権主張国 韓国 (KR)                    | 大韓民国 4 4 3 - 7 4 2 京畿道水原市靈通区梅灘洞 4 1 6       |             |

|                                        | (74) 代理人 110000051                          |             |

|                                        | 特許業務法人共生国際特許事務所                             |             |

|                                        | (72) 発明者 孫 宣 圭                              |             |

|                                        | 大韓民国 京畿道 龍仁市 器興邑 靈德里 シンイルアパート 109 棟 140 5 号 |             |

|                                        | 最終頁に続く                                      |             |

(54) 【発明の名称】表示装置のゲート駆動部と駆動装置、及びこれを有する表示装置

## (57) 【要約】

【課題】二つのシフトレジスタを有するゲート駆動部を設けて奇数番目及び偶数番目の副画素を別個に駆動することにより、二つの副画素の充電時間を向上すると同時に、このような画素配置を有する液晶表示装置の視認性を改善する。

【解決手段】本発明の一特徴による表示装置の駆動装置は、行列状に配列され、それぞれ第1及び第2副画素を有する複数の画素と、第1副画素に接続され、第1ゲート信号を伝達する複数の第1ゲート線と、第2副画素に接続され、第2ゲート信号を伝達する複数の第2ゲート線と、第1及び第2ゲート信号を生成するゲート駆動部を備え、ゲート駆動部は、第1ゲート信号を生成する第1シフトレジスタと、第2ゲート信号を生成する第2シフトレジスタと、第1及び第2シフトレジスタに接続されているレベルシフタと、レベルシフタに接続されている出力バッファとを備える。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

第1及び第2副画素をそれぞれ有する複数の画素を備える表示装置のゲート駆動部であって、

第1ゲートクロック信号に従って第1ゲート信号を生成する第1シフトレジスタと、

第2ゲートクロック信号に従って第2ゲート信号を生成する第2シフトレジスタと、

前記第1及び第2シフトレジスタに接続されるレベルシフタと、

前記レベルシフタに接続される出力バッファと、を備えることを特徴とする表示装置のゲート駆動部。

**【請求項 2】**

前記第1ゲート信号は、前記第1ゲートクロック信号に同期して生成され、前記第2ゲート信号は、前記第2ゲートクロック信号に同期して生成されることを特徴とする請求項1に記載の表示装置のゲート駆動部。

**【請求項 3】**

前記第1ゲートクロック信号は、前記第2ゲートクロック信号と部分的に重畠することを特徴とする請求項2に記載の表示装置のゲート駆動部。

**【請求項 4】**

前記第1ゲートクロック信号は、前記第2ゲートクロック信号より1/4Hだけ先行することを特徴とする請求項3に記載の表示装置のゲート駆動部。

**【請求項 5】**

前記第2ゲートクロック信号は、前記第1ゲートクロック信号より1/4Hだけ先行することを特徴とする請求項3に記載の表示装置のゲート駆動部。

**【請求項 6】**

前記第1クロック信号のハイ区間の幅と前記第2クロック信号のハイ区間の幅とが互いに異なることを特徴とする請求項3に記載の表示装置のゲート駆動部。

**【請求項 7】**

前記第1及び第2シフトレジスタは、互いに接続される複数のステージをそれぞれ備え、前記ステージの第1及び最後のステージのうちの少なくとも一つは垂直同期開始信号を受信することを特徴とする請求項3に記載の表示装置のゲート駆動部。

**【請求項 8】**

第1及び第2副画素をそれぞれ有する複数の画素を備える表示装置の駆動装置であって、

前記第1副画素に接続され、第1ゲート信号を伝達する複数の第1ゲート線と、

前記第2副画素に接続され、第2ゲート信号を伝達する複数の第2ゲート線と、

前記第1及び第2ゲート信号を生成するゲート駆動部と、を備え、

前記ゲート駆動部は、

前記第1ゲート信号を生成する第1シフトレジスタと、

前記第2ゲート信号を生成する第2シフトレジスタと、

前記第1及び第2シフトレジスタに接続されるレベルシフタと、

前記レベルシフタに接続される出力バッファと、を備えることを特徴とする表示装置の駆動装置。

**【請求項 9】**

前記第1ゲート信号は、第1ゲートクロック信号に同期して生成され、前記第2ゲート信号は、第2ゲートクロック信号に同期して生成されることを特徴とする請求項8に記載の表示装置の駆動装置。

**【請求項 10】**

前記第1ゲートクロック信号は、前記第2ゲートクロック信号と部分的に重畠することを特徴とする請求項9に記載の表示装置の駆動装置。

**【請求項 11】**

前記第1ゲートクロック信号は、前記第2ゲートクロック信号より1/4Hだけ先行す

10

20

30

40

50

ることを特徴とする請求項 10 に記載の表示装置の駆動装置。

【請求項 12】

前記第 2 ゲートクロック信号は、前記第 1 ゲートクロック信号より 1 / 4 H だけ先行することを特徴とする請求項 10 に記載の表示装置の駆動装置。

【請求項 13】

前記第 1 クロック信号のハイ区間の幅と前記第 2 クロック信号のハイ区間の幅とが互いに異なることを特徴とする請求項 9 に記載の表示装置の駆動装置。

【請求項 14】

前記第 1 及び第 2 シフトレジスタは、互いに接続される複数のステージをそれぞれ備え、前記ステージの第 1 及び最後のステージのうちの少なくとも一つは垂直同期開始信号を受信することを特徴とする請求項 9 に記載の表示装置の駆動装置。 10

【請求項 15】

前記第 1 及び第 2 ゲート線のそれぞれは、前記駆動装置の第 1 側面に隣接した第 1 端と、前記駆動装置の第 2 側面に隣接した第 2 端とを有し、

前記ゲート駆動部は、前記第 1 及び第 2 ゲート線の前記第 1 端にのみ接続されていることを特徴とする請求項 8 に記載の表示装置の駆動装置。

【請求項 16】

第 1 及び第 2 副画素をそれぞれ有し、行列状に配列されている複数の主画素と、前記第 1 副画素に接続され、第 1 ゲート信号を伝達する複数の第 1 ゲート線と、前記第 2 副画素に接続され、第 2 ゲート信号を伝達する複数の第 2 ゲート線と、前記第 1 及び第 2 ゲート信号を生成するゲート駆動部と、を備え、 20

前記ゲート駆動部は、

前記第 1 ゲート信号を生成する第 1 シフトレジスタと、

前記第 2 ゲート信号を生成する第 2 シフトレジスタと、

前記第 1 及び第 2 シフトレジスタに接続されるレベルシフタと、

前記レベルシフタに接続される出力バッファと、を備えることを特徴とする表示装置。 20

【請求項 17】

前記第 1 及び第 2 副画素のそれぞれに接続された第 1 及び第 2 キャパシタを更に備え、前記第 1 及び第 2 キャパシタは同時に充電されないことを特徴とする請求項 16 に記載の表示装置。 30

【請求項 18】

後から充電される副画素の充電時間は、先に充電された副画素の充電時間だけ減少することを特徴とする請求項 17 に記載の表示装置。

【請求項 19】

前記第 1 及び第 2 副画素は、互いに異なるデータ電圧を受信することを特徴とする請求項 16 に記載の表示装置。

【請求項 20】

隣接した主画素の充電時間は重畠せず、各画素の前記第 1 及び第 2 副画素の充電時間は重畠することを特徴とする請求項 16 に記載の表示装置。

【請求項 21】

前記第 1 ゲート信号は第 1 ゲートクロック信号に同期し、前記第 2 ゲート信号は第 2 ゲートクロック信号に同期することを特徴とする請求項 16 に記載の表示装置。 40

【請求項 22】

前記第 1 ゲートクロック信号は、前記第 2 ゲートクロック信号と部分的に重畠することを特徴とする請求項 21 に記載の表示装置。

【請求項 23】

前記第 1 ゲートクロック信号は、前記第 2 ゲートクロック信号より 1 / 4 H だけ先行することを特徴とする請求項 22 に記載の表示装置。

【請求項 24】

前記第 2 ゲートクロック信号は、前記第 1 ゲートクロック信号より 1 / 4 H だけ先行す 50

ることを特徴とする請求項 2 2 に記載の表示装置。

【請求項 2 5】

前記第 1 クロック信号のハイ区間の幅と前記第 2 クロック信号のハイ区間の幅とが互いに異なることを特徴とする請求項 2 2 に記載の表示装置。

【請求項 2 6】

前記第 1 及び第 2 シフトレジスタは、互いに接続される複数のステージをそれぞれ備え、前記ステージの第 1 及び最後のステージのうちの少なくとも一つは垂直同期開始信号を受信することを特徴とする請求項 2 2 に記載の表示装置。

【請求項 2 7】

前記第 1 及び第 2 ゲート線は、前記表示装置の第 1 側面から前記表示装置の第 2 側面に延び、

前記ゲート駆動部は、前記表示装置の第 1 側面にのみ位置することを特徴とする請求項 1 6 に記載の表示装置。

【請求項 2 8】

第 1 及び第 2 副画素をそれぞれ有し、行列状に配列されている複数の主画素と、前記第 1 副画素に接続され、第 1 ゲート信号を伝達する複数の第 1 ゲート線と、前記第 2 副画素に接続され、第 2 ゲート信号を伝達する複数の第 2 ゲート線と、前記第 1 及び第 2 ゲート信号を生成するゲート駆動部と、を備え、

前記ゲート駆動部は、

前記第 1 ゲート信号を生成する第 1 シフトレジスタと、

前記第 2 ゲート信号を生成する第 2 シフトレジスタと、を備えることを特徴とする表示装置。

【請求項 2 9】

隣接した主画素の充電時間は重畠せず、各画素の前記第 1 及び第 2 副画素の充電時間は重畠することを特徴とする請求項 2 8 に記載の表示装置。

【請求項 3 0】

前記第 1 及び第 2 ゲート線のそれぞれは、前記駆動装置の第 1 側面に隣接した第 1 端と、前記駆動装置の第 2 側面に隣接した第 2 端とを有し、

前記ゲート駆動部は、前記第 1 及び第 2 ゲート線の前記第 1 端にのみ接続されていることを特徴とする請求項 2 8 に記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、表示装置のゲート駆動部と駆動装置、及びこれを有する表示装置に関する。

【背景技術】

【0 0 0 2】

液晶表示装置は、現在最も広く使用されている平板表示装置の一つであって、画素電極と共に通電極等電界生成電極が形成されている二枚の表示板と、その間に挿入されている液晶層とからなり、電界生成電極に電圧を印加して液晶層に電界を生成し、これにより液晶層の液晶分子の配向を決定し、入射光の偏光を制御することによって映像を表示する。

【0 0 0 3】

一方、このような液晶表示装置は、スイッチング素子を有する画素と表示信号線を有する表示板、並びに表示信号線のうちのゲート線にゲート信号を送出し、画素のスイッチング素子を導通／遮断させるゲート駆動部を備える。

このようなゲート駆動部は、通常、集積回路形態に実現され、シフトレジスタ、レベルシフタ及び出力バッファを備える。シフトレジスタは、互いに接続されている複数のステージを備え、各ステージは、順次に出力を生成し、生成された出力は、レベルシフタ及び出力バッファを介してゲート線に印加される。

【0 0 0 4】

また、このような液晶表示装置のうち、電界が印加されない状態で液晶分子の長軸を上

10

20

30

40

50

下表示板に対して垂直をなすように配列した垂直配向モード液晶表示装置は、コントラスト比が大きく、広い基準視野角の実現が容易であるため脚光を浴びている。ここで、基準視野角とは、コントラスト比が1:10である視野角、又は階調間の輝度反転限界角度を意味する。

#### 【0005】

垂直配向モード液晶表示装置において、広視野角を実現するための手段としては、電界生成電極に切開部を形成する方法と、電界生成電極上に突起を形成する方法等がある。切開部と突起で液晶分子の傾斜方向を決定できるので、これらを用いて液晶分子の傾斜方向を多様な方向に分散することによって基準視野角を広くすることができる。

#### 【0006】

しかし、垂直配向方式の液晶表示装置は、前面視認性に比べて側面視認性が劣るという問題点がある。例えば、切開部を有するPVA(Patterned Vertical1y Aligned)方式の液晶表示装置の場合、側面に行くほど映像が明るくなり、酷い場合には、高階調間の輝度差がなくなつて画像がぼやけてしまうことも発生する。

#### 【0007】

このような問題点を改善するために、一つの画素を二つの副画素に分割し、二つの副画素を容量性結合した後、一方の副画素には直接電圧を印加し、他方の副画素には容量性結合による電圧下降を起こして、二つの副画素の電圧が異なるようにすることによって透過率が異なるようにする方法が提案された。

#### 【0008】

ここで、二つの副画素にゲート電圧を印加する場合には、上述したゲート駆動部のステージに、一つの画素行に相当する時間間隔、つまり、1水平周期間隔で同一のゲート電圧を印加する。その結果、二つの副画素のスイッチング素子が同時に導通して、互いに異なる電圧を印加できないという問題点が発生する。また、これを改善するために、表示板の両側にゲート駆動部を設けて二つの副画素を別々に駆動する場合、液晶表示装置のコストが上昇し、ゲート駆動部が占める面積が大きくなつて、液晶表示装置のサイズが大きくなるという問題点が生じる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

そこで、本発明は上記従来の表示装置を駆動する際の問題点に鑑みてなされたものであつて、本発明の目的は、このような問題点を解決するための表示装置のゲート駆動部と駆動装置、及びこれを有する表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0010】

上記目的を達成するためになされた本発明の一特徴による表示装置のゲート駆動部は、第1及び第2副画素をそれぞれ有する複数の画素を備える表示装置のゲート駆動部であつて、第1ゲートクロック信号に従つて第1ゲート信号を生成する第1シフトレジスタと、第2ゲートクロック信号に従つて第2ゲート信号を生成する第2シフトレジスタと、前記第1及び第2シフトレジスタに接続されるレベルシフタと、前記レベルシフタに接続される出力バッファとを備える。

前記第1ゲート信号は、前記第1ゲートクロック信号に同期して生成され、前記第2ゲート信号は、前記第2ゲートクロック信号に同期して生成される。

前記第1ゲートクロック信号は、前記第2ゲートクロック信号と部分的に重畠することができる。

この時、前記第1ゲートクロック信号は、前記第2ゲートクロック信号より1/4Hだけ先行するか、前記第2ゲートクロック信号が前記第1ゲートクロック信号より1/4Hだけ先行することができる。

また、前記第1クロック信号のハイ区間と前記第2クロック信号のハイ区間の幅とが互いに異なるようにすることができる。

10

20

30

40

50

一方、前記第1及び第2シフトレジスタは、互いに接続される複数のステージをそれぞれ備え、前記ステージの第1及び最後のステージのうちの少なくとも一つは、垂直同期開始信号を受信することができる。

【0011】

上記目的を達成するためになされた本発明の一特徴による表示装置の駆動装置は、第1及び第2副画素をそれぞれ有する複数の画素を備える表示装置の駆動装置であって、前記第1副画素に接続され、第1ゲート信号を伝達する複数の第1ゲート線と、前記第2副画素に接続され、第2ゲート信号を伝達する複数の第2ゲート線と、前記第1及び第2ゲート信号を生成するゲート駆動部と、を備え、前記ゲート駆動部は、前記第1ゲート信号を生成する第1シフトレジスタと、前記第2ゲート信号を生成する第2シフトレジスタと、前記第1及び第2シフトレジスタに接続されるレベルシフタと、前記レベルシフタに接続される出力バッファとを備える。

この時、前記第1ゲート信号は、第1ゲートクロック信号に同期して生成され、前記第2ゲート信号は第2ゲートクロック信号に同期して生成されることができ、前記第1ゲートクロック信号は、前記第2ゲートクロック信号と部分的に重畠することができる。

この時、前記第1ゲートクロック信号は、前記第2ゲートクロック信号より1/4Hだけ先行することや、前記第2ゲートクロック信号が前記第1ゲートクロック信号より1/4Hだけ先行することができる。

前記第1クロック信号のハイ区間の幅と前記第2クロック信号のハイ区間の幅とが互いに異なるようにすることができる。一方、前記第1及び第2シフトレジスタは、互いに接続されている複数のステージをそれぞれ備え、前記ステージの第1及び最後のステージのうちの少なくとも一つは、垂直同期開始信号を受信することができる。

また、前記第1及び第2ゲート線のそれぞれは、前記駆動装置の第1側面に隣接した第1端と、前記駆動装置の第2側面に隣接した第2端とを有し、前記ゲート駆動部は、前記第1及び第2ゲート線の前記第1端にのみ接続されるようにすることができる。

【0012】

上記目的を達成するためになされた本発明の一特徴による表示装置は、第1及び第2副画素をそれぞれ有し、行列状に配列されている複数の主画素と、前記第1副画素に接続され、第1ゲート信号を伝達する複数の第1ゲート線と、前記第2副画素に接続され、第2ゲート信号を伝達する複数の第2ゲート線と、前記第1及び第2ゲート信号を生成するゲート駆動部とを備え、前記ゲート駆動部は、前記第1ゲート信号を生成する第1シフトレジスタと、前記第2ゲート信号を生成する第2シフトレジスタと、前記第1及び第2シフトレジスタに接続されるレベルシフタと、前記レベルシフタに接続される出力バッファとを備える。

前記表示装置は、前記第1及び第2副画素それぞれに接続された第1及び第2キャパシタを更に備え、前記第1及び第2キャパシタは、同時に充電されないようにすることもできる。

この時、後から充電される副画素の充電時間は、先に充電された副画素の充電時間だけ減少するようにすることができる。

前記第1及び第2副画素は、互いに異なるデータ電圧を受信することができる。

また、隣接した主画素の充電時間は重畠せず、各画素の前記第1及び第2副画素の充電時間は重畠することができる。

前記第1ゲート信号は、第1ゲートクロック信号に同期し、前記第2ゲート信号は、第2ゲートクロック信号に同期することができる。

前記第1ゲートクロック信号は、前記第2ゲートクロック信号と部分的に重畠するが、前記第1ゲートクロック信号は、前記第2ゲートクロック信号より1/4Hだけ先行するか、前記第2ゲートクロック信号が前記第1ゲートクロック信号より1/4Hだけ先行するようにすることができる。

前記第1クロック信号のハイ区間の幅と前記第2クロック信号のハイ区間の幅とが互いに異なるようにすることができる。

10

20

30

40

50

前記第1及び第2シフトレジスタは、互いに接続される複数のステージをそれぞれ備え、前記ステージの第1及び最後のステージのうちの少なくとも一つは垂直同期開始信号を受信することができる。

前記第1及び第2ゲート線は、前記表示装置の第1側面から前記表示装置の第2側面に延び、前記ゲート駆動部は、前記表示装置の第1側面にのみ位置することができる。

#### 【0013】

また、上記目的を達成するためになされた本発明の他の特徴による表示装置は、第1及び第2副画素をそれぞれ有し、行列状に配列されている複数の主画素と、前記第1副画素に接続され、第1ゲート信号を伝達する複数の第1ゲート線と、前記第2副画素に接続され、第2ゲート信号を伝達する複数の第2ゲート線と、前記第1及び第2ゲート信号を生成するゲート駆動部とを備え、前記ゲート駆動部は、前記第1ゲート信号を生成する第1シフトレジスタと、前記第2ゲート信号を生成する第2シフトレジスタとを備える。

この時、隣接した主画素の充電時間は重畠せず、各画素の前記第1及び第2副画素の充電時間は重畠することができる。

前記第1及び第2ゲート線それぞれは、前記駆動装置の第1側面に隣接した第1端と、前記駆動装置の第2側面に隣接した第2端とを有し、前記ゲート駆動部は、前記第1及び第2ゲート線の前記第1端にのみ接続されるようにすることができる。

#### 【発明の効果】

#### 【0014】

このような本発明の表示装置のゲート駆動部と駆動装置、及びこれを有する表示装置によれば、二つのシフトレジスタを備えるゲート駆動部を設けて、奇数及び偶数番目の副画素を別個に駆動することによって、二つの副画素の充電時間を向上すると同時に、このような画素配置を有する液晶表示装置の視認性を改善することができる。また、表示板の一方にのみゲート駆動部を位置させて奇数及び偶数番目のゲート線を駆動するので、表示板の大きさを小さくすることができる。

#### 【発明を実施するための最良の形態】

#### 【0015】

次に、本発明の表示装置のゲート駆動部と駆動装置、及びこれを有する表示装置を実施するための最良の形態の具体例を、図面を参照しながら説明する。

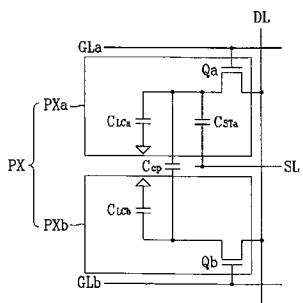

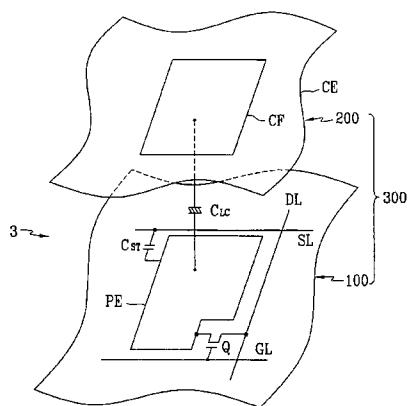

図1は、本発明の一実施形態による液晶表示装置のプロック図であり、図2及び図3は、本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図であり、図4は、本発明の一実施形態による液晶表示装置の一つの副画素に対する等価回路図である。

#### 【0016】

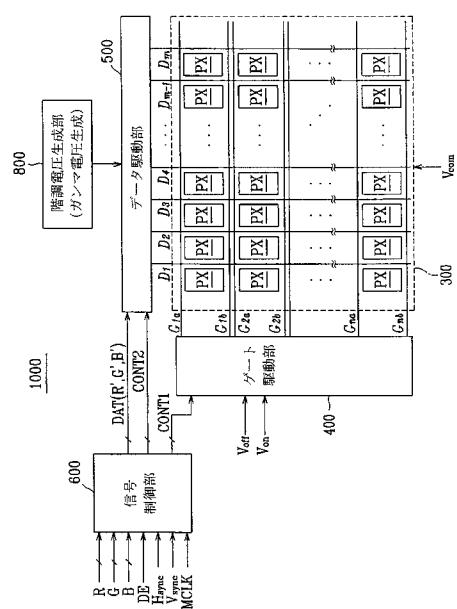

図1を参照すると、本発明の一実施形態による液晶表示装置は、液晶表示板組立体300と、これに接続されたゲート駆動部400及びデータ駆動部500、データ駆動部500に接続された階調電圧生成部800、及びこれらを制御する信号制御部600を備える。

#### 【0017】

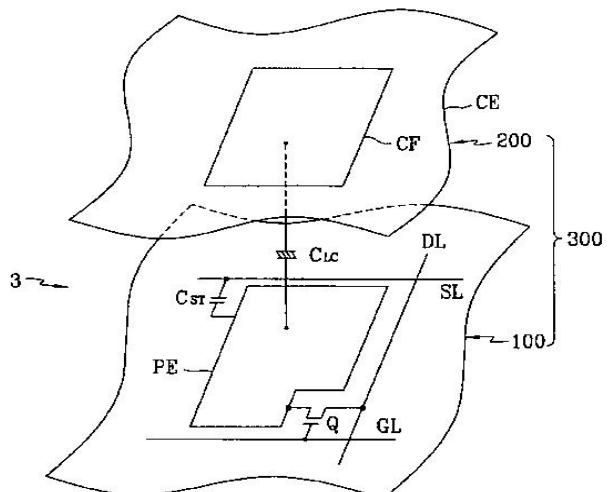

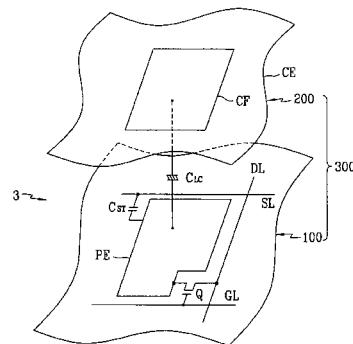

液晶表示板組立体300は、等価回路において、複数の表示信号線と、これに接続され略行列状に配列された複数の画素PXを備える。更に、図4に示す構造において、液晶表示板組立体300は、互いに対向する下部及び上部表示板100、200と、両者の間に介在する液晶層3を備える。

#### 【0018】

表示信号線は、下部表示板100に備えられ、ゲート信号（走査信号とも言う）を伝達する複数のゲート線（G<sub>1a</sub> - G<sub>nb</sub>）と、データ信号を伝達するデータ線（D<sub>1</sub> - D<sub>m</sub>）を有する。ゲート線（G<sub>1a</sub> - G<sub>nb</sub>）は略行方向に延びて互いに略平行であり、データ線（D<sub>1</sub> - D<sub>m</sub>）は略列方向に延びて互いに略平行である。

#### 【0019】

図2及び図3は、表示信号線と画素の等価回路を示し、図面符号GLa、GLbで示したゲート線と、図面符号DLで示したデータ線の他に、表示信号線として、ゲート線（G

10

20

30

40

50

$G_1 - G_{2b}$ ) と略並んで延びた維持電極線  $S_L$  を有する。

【0020】

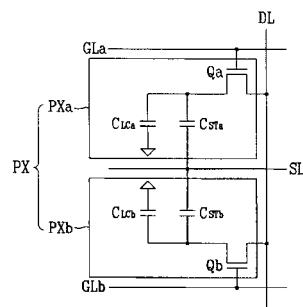

図2に示すように、各画素  $P_X$  は一対の副画素  $P_{Xa}$ 、 $P_{Xb}$  を有しており、各副画素  $P_{Xa}$ 、 $P_{Xb}$  は当該ゲート線  $G_{La}$ 、 $G_{Lb}$  及びデータ線  $D_L$  に接続されているスイッチング素子  $Q_a$ 、 $Q_b$  と、これに接続された液晶キャパシタ  $C_{Lc}a$ 、 $C_{Lc}b$  と、スイッチング素子  $Q_a$ 、 $Q_b$ 、及び維持電極線  $S_L$  に接続されているストレージキャパシタ  $C_{ST}a$ 、 $C_{ST}b$  を備える。ストレージキャパシタ  $C_{ST}a$ 、 $C_{ST}b$  は必要に応じて省略可能であり、その場合、維持電極線  $S_L$  は不要である。

【0021】

図3に示すように、各画素  $P_X$  は、一対の副画素  $P_{Xa}$ 、 $P_{Xb}$  と、これらの間に接続されている結合キャパシタ  $C_{cp}$  を有し、各副画素  $P_{Xa}$ 、 $P_{Xb}$  は、当該ゲート線  $G_{La}$ 、 $G_{Lb}$  及びデータ線  $D_L$  に接続されているスイッチング素子  $Q_a$ 、 $Q_b$  と、これに接続されている液晶キャパシタ  $C_{Lc}a$ 、 $C_{Lc}b$  を備える。なお、二つの副画素  $P_{Xa}$ 、 $P_{Xb}$  のうちの一つ  $P_{Xa}$  は、スイッチング素子  $Q_a$  及び維持電極線  $S_L$  に接続されているストレージキャパシタ  $C_{ST}a$  を備える。

【0022】

図4を参照すると、各副画素  $P_{Xa}$ 、 $P_{Xb}$  のスイッチング素子  $Q$  は、下部表示板100に備えられている薄膜トランジスタ等からなり、それぞれゲート線  $G_L$  に接続されている制御端子と、データ線  $D_L$  に接続されている入力端子と、液晶キャパシタ  $C_{Lc}$  及びストレージキャパシタ  $C_{ST}$  に接続されている出力端子を有する三端子素子である。

【0023】

液晶キャパシタ  $C_{Lc}$  は、下部表示板100の副画素電極  $P_E$  と上部表示板200の共通電極  $C_E$  を二つの端子とし、二つの電極  $P_E$ 、 $C_E$  の間の液晶層3は誘電体として機能する。副画素電極  $P_E$  はスイッチング素子  $Q$  に接続され、共通電極  $C_E$  は上部表示板200の全面に形成されて共通電圧  $V_{com}$  の印加を受ける。図4と異なって、共通電極  $C_E$  が下部表示板100に具備されることもあり、その場合は、二つの電極  $P_E$ 、 $C_E$  のうちの少なくとも一つが線形又は棒形に形成される。

【0024】

液晶キャパシタ  $C_{Lc}$  の補助的な役割を果たすストレージキャパシタ  $C_{ST}$  は、下部表示板100に具備された維持電極線  $S_L$  と画素電極  $P_E$  が絶縁体を介在して重畠してなり、維持電極線  $S_L$  には共通電圧  $V_{com}$  等の定められた電圧が印加される。更に、ストレージキャパシタ  $C_{ST}$  は、副画素電極  $P_E$  が絶縁体を媒介としてすぐ上の前段ゲート線と重畠してなることができる。

【0025】

一方、色表示を実現するために、各画素が原色のうちの一つを固有に表示するか(空間分割)、或いは各画素が時間によって交互に三原色を表示する(時間分割)ようにして、三原色の空間的、時間的な作用で所望の色相が認識されるようにする。原色の例としては、赤色、緑色及び青色がある。図4は、空間分割の例であって、各画素が上部表示板200領域に原色のうちの一つを示すカラーフィルタ  $C_F$  を備えている。図4と異なって、カラーフィルタ  $C_F$  を、下部表示板100の副画素電極  $P_E$  の上又は下に形成することもできる。

【0026】

図1に示すように、ゲート駆動部400は、ゲート線( $G_{1a}$  -  $G_{nb}$ )に接続されて外部からのゲートオン電圧  $V_{on}$  とゲートオフ電圧  $V_{off}$  の組み合わせからなるゲート信号をゲート線( $G_{1a}$  -  $G_{nb}$ )に印加する。

【0027】

階調電圧生成部800は、画素の透過率に関連する二つの階調電圧群(又は基準階調電圧群)を生成する。二つの階調電圧群は、一つの画素を構成する二つの副画素に独立的に提供されるものであって、各階調電圧群は、共通電圧  $V_{com}$  に対してプラスの値を持つものと、マイナスの値を持つものを含む。しかし、二つの(基準)階調電圧群の代わりに

10

20

30

40

50

一つの（基準）階調電圧群のみを生成することもできる。

【0028】

データ駆動部500は、液晶表示板組立体300のデータ線（D<sub>1</sub> - D<sub>m</sub>）に接続され、階調電圧生成部800からの二つの階調電圧群のうちの一つを選択し、選択された階調電圧群に属する一つの階調電圧をデータ電圧として画素に印加する。しかし、階調電圧生成部800が全階調に対する電圧を全て提供するのではなく、基準階調電圧のみを提供する場合、データ駆動部500は、基準階調電圧を分圧して全階調に対する階調電圧を生成し、その中からデータ電圧を選択する。

【0029】

ゲート駆動部400又はデータ駆動部500は、複数の駆動集積回路チップ形態で液晶表示板組立体300上に直接装着されたり、フレキシブルプリント回路膜（図示せず）上に装着されたりして、TCP（tape carrier package）の形態で液晶表示板組立体300に付着されるようになることもできる。更に、ゲート駆動部400又はデータ駆動部500が、表示信号線（G<sub>1a</sub> - G<sub>nb</sub>、D<sub>1</sub> - D<sub>m</sub>）と薄膜トランジスタスイッチング素子Qa、Qb等と共に、液晶表示板組立体300に集積されるようになることもできる。

【0030】

信号制御部600は、ゲート駆動部400及びデータ駆動部500等の動作を制御する。

次に、このような液晶表示装置の表示動作について詳細に説明する。

【0031】

信号制御部600は、外部のグラフィック制御部（図示せず）から入力映像信号R、G、B及びその表示を制御する入力制御信号、例えば垂直同期信号Vsyncと水平同期信号Hsync、メインクロックMCLK、データイネーブル信号DE等の提供を受ける。信号制御部600の入力映像信号R、G、Bと入力制御信号に基づいて入力映像信号R、G、Bを液晶表示板組立体300の動作条件に合うように適切に処理し、ゲート制御信号CONT1及びデータ制御信号CONT2等を生成した後、ゲート制御信号CONT1をゲート駆動部400に送出し、データ制御信号CONT2と処理した映像データDATとをデータ駆動部500に送出する。

ゲート制御信号CONT1は、垂直同期開始信号として走査開始を指示する走査開始信号STVとゲートオン電圧Vonの出力時間を制御する複数のゲートクロック信号CPV1、CPV2を含む。

【0032】

データ制御信号CONT2は、一群の画素PXに対するデータ伝送を知らせる水平同期開始信号STHと、データ線D<sub>1</sub> - D<sub>m</sub>に当該データ電圧の印加を指示するロード信号LOAD、及びデータクロック信号HCLKを含む。また、データ制御信号CONT2は、共通電圧Vcomに対するデータ電圧の極性（以下、共通電圧に対するデータ電圧の極性を略してデータ電圧の極性と言う。）を反転させる反転信号RVSを含んでもよい。

【0033】

信号制御部600からのデータ制御信号CONT2に従って、データ駆動部500は一群の副画素PXに対する映像データDATを受信し、階調電圧生成部800からの二つの階調電圧群のうちの一群を選択し、選択された階調電圧群の中から各映像データDATに対応する階調電圧を選択することによって映像データDATを当該データ電圧に変換した後、これを当該データ線（D<sub>1</sub> - D<sub>m</sub>）に印加する。

【0034】

ゲート駆動部400は、信号制御部600からのゲート制御信号CONT1に従ってゲートオン電圧Vonをゲート線（G<sub>1a</sub> - G<sub>nb</sub>）に印加して、該ゲート線（G<sub>1a</sub> - G<sub>nb</sub>）に接続されたスイッチング素子Qa、Qbを導通させ、これにより、データ線（D<sub>1</sub> - D<sub>m</sub>）に印加されたデータ電圧が導通したスイッチング素子Qa、Qbを介して当該副画素PXに印加される。

10

20

30

40

50

## 【0035】

副画素  $P_X a$ 、 $P_X b$  に印加されたデータ電圧と共通電圧  $V_{com}$  の差は、液晶キャパシタ  $C_{Lc}$  の充電電圧、つまり画素電圧として現れる。液晶分子は、画素電圧の大きさによってその配列が異なり、そのため、液晶層 3 を通過する光の偏光が変化する。このような偏光の変化は、下部及び上部表示板 100、200 に付着された偏光子（図示せず）によって光透過率の変化として現れる。

## 【0036】

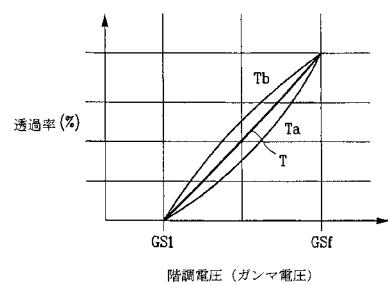

前述した二つの階調電圧群は、図 8 に示すように、互いに異なるガンマ曲線  $T_a$ 、 $T_b$  を示し、これらが一つの画素  $P_X$  の二つの副画素  $P_X a$ 、 $P_X b$  に印加されるので、一つの画素  $P_X$  のガンマ曲線は、これらを合成した曲線  $T$  となる。ここで、 $GS1$  は最低階調を示し、 $GSf$  は最高階調を示す。二つの階調電圧群を決定する際に、合成ガンマ曲線（ $T$ ）が正面での基準ガンマ曲線に近づけるようにする。例えば、正面での合成ガンマ曲線（ $T$ ）は最適に定められた正面での基準ガンマ曲線と一致するようにし、側面での合成ガンマ曲線（ $T$ ）は、正面での基準ガンマ曲線に近づけるようにする。例えば、下側に位置したガンマ曲線を低階調でより低くすると、視認性が一層向上する。

10

## 【0037】

1/2 水平周期（又は 1/2 H）（水平同期信号  $Hsync$  及びゲートクロック信号  $CPV$  の一周期）を単位としてデータ駆動部 500 とゲート駆動部 400 は同一動作を繰り返す。このような方法で、1 フレーム期間の間に全ゲート線（ $G_{1a}$  -  $G_{nb}$ ）に対して順次ゲートオン電圧  $V_{on}$  を印加して全画素にデータ電圧を印加する。1 フレームが終了すると次のフレームが開始され、各画素に印加されるデータ電圧の極性が直前フレームと逆極性になるように、データ駆動部 500 に印加される反転信号  $RVS$  の状態が制御される（フレーム反転）。この時、1 フレーム内でも反転信号  $RVS$  の特性によって一つのデータ線を通じて流れるデータ電圧の極性が変わることや（例：行反転、ドット反転）、隣接データ線を通じて同時に流れるデータ電圧の極性も互いに異なるようにしてもよい（例：列反転、ドット反転）。

20

## 【0038】

しかし、このような液晶表示装置の場合、通常の液晶表示装置に比べて 2 倍のゲート線が存在するので、通常の方法でデータ電圧を印加する場合、電圧充電時間が短くて画素が目標電圧に到達しないことも生じ、これは極性反転であるからなおさらである。この問題は、隣接した二つのゲート線にゲートオン電圧  $V_{on}$  を印加する時間を一部重畳することで解決でき、これについて図 5、図 6 及び図 7 を参照してより詳細に説明する。

30

## 【0039】

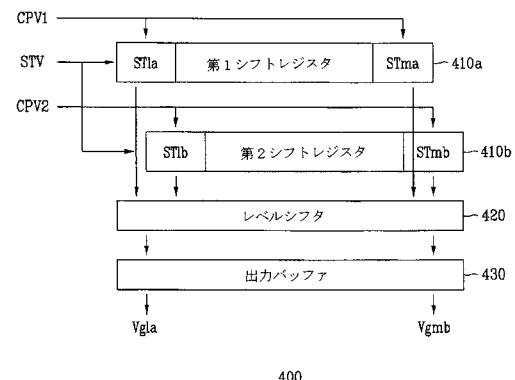

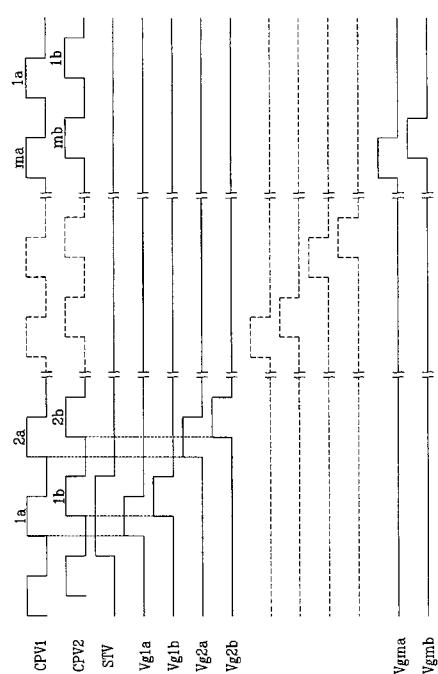

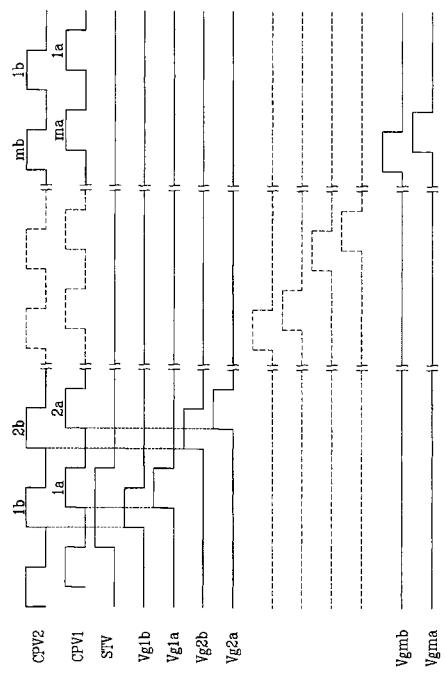

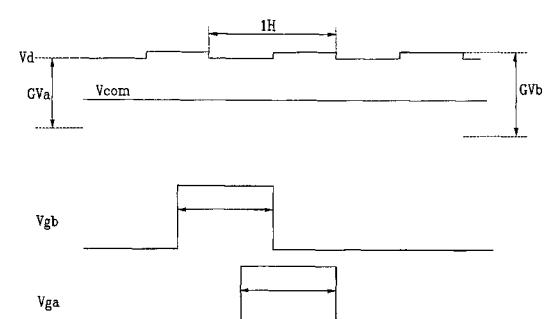

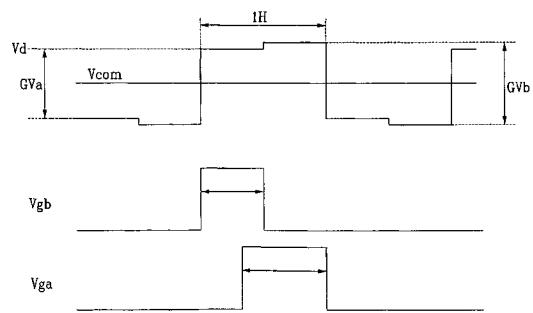

図 5 は、本発明の一実施形態によるゲート駆動部のブロック図であり、図 6 及び図 7 は、図 5 に示したゲート駆動部のタイミング図の例である。

図 5 に示すように、本発明の一実施形態によるゲート駆動部は、一対のシフトレジスタ 410a、410b、これに接続されているレベルシフタ 420、及び出力バッファ 430 を備える。

## 【0040】

1 対のシフトレジスタ 410a、410b には走査開始信号  $STV$  が印加され、一対のゲートクロック信号  $CPV1$ 、 $CPV2$  がそれぞれ印加される。

40

各シフトレジスタ 410a、410b は、複数のステージ  $ST1a$ 、…、 $STma$ 、 $ST1b$ 、…、 $STmb$  をそれぞれ備える。

レベルシフタ 420 は、二つのシフトレジスタ 410a、410b からの出力を画素のスイッチング素子を動作させるのに適切な大きさに増幅して出力バッファ 430 に送出し、出力バッファ 430 は、信号遅延によるゲート電圧の減少を考慮して減少分だけ増幅して送出する。

## 【0041】

この時、図 2 及び図 3 に示すゲート線  $GLa$  を奇数番目のゲート線  $G1a$ 、 $G2a$ 、…、 $Gma$  とし、ゲート線  $GLb$  を偶数番目のゲート線  $G1b$ 、 $G2b$ 、…、 $Gmb$  とする

50

時、シフトレジスタ410aは、奇数番目のゲート線GLaに接続されているスイッチング素子Qaを動作させるためのゲート信号を生成し、シフトレジスタ410bは、偶数番目のゲート線GLbに接続されているスイッチング素子Qbを動作させるためのゲート信号を生成する。

#### 【0042】

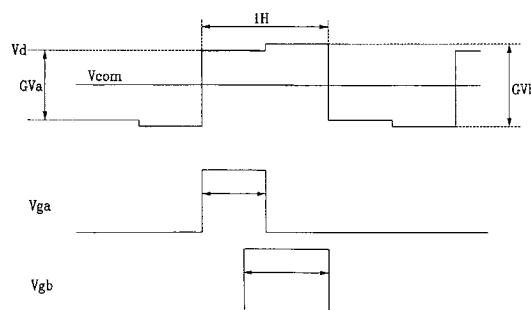

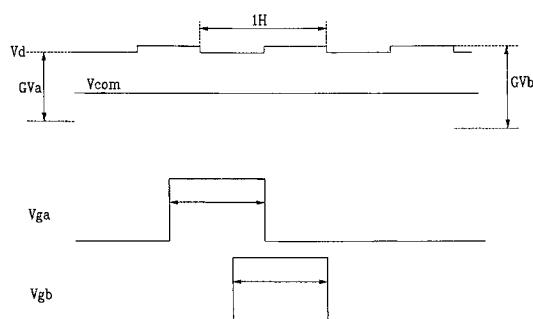

また、ゲートクロック信号CPV1、CPV2は1Hの周期を有し、50%のデューティ比を有する。図6は、クロック信号CPV2がクロック信号CPV1に比べて1/4Hだけ遅延された信号であり、図7は、クロック信号CPV1がクロック信号CPV2に比べて1/4Hだけ遅延された信号である。

ここで、シフトレジスタ410a、410b、レベルシフタ420、及び出力バッファ430を経て生成されるゲート電圧を単にシフトレジスタ410a、410bで生成される電圧として‘Vg’と表示し、Vgaは奇数番目のゲート線に印加されるゲート信号を示し、Vgbは偶数番目のゲート線に印加されるゲート信号を示す。

#### 【0043】

この時、走査開始信号STVが二つのシフトレジスタ410a、410bに入力されると、各シフトレジスタ410a、410bの第1ステージST1a、ST1bは、走査開始信号STVがハイである区間において、第1ゲートクロック信号CPV1、CPV2の上昇エッジに同期して、それぞれ出力Vg1a、Vg1bを送出する。

次に、第2ステージからは前段ステージの出力をキャリー信号とし、ゲートクロック信号CPV1、CPV2に同期して出力Vg2a、…、Vgma、Vg2b、…、Vgmbを順次送出する。

#### 【0044】

図6に示すように、クロック信号CPV1がクロック信号CPV2に比べて1/4Hだけ先行するので、一群の副画素PXa、PXbのうちの奇数番目のゲート線GLaに接続されている副画素PXaが先に充電され、偶数番目のゲート線GLbに接続されている副画素PXbが後から充電される。これに対し、図7に示す場合は、偶数番目のゲート線GLbに接続されている副画素PXbが先に充電され、奇数番目のゲート線GLaに接続されている副画素PXaが後から充電される。

#### 【0045】

一方、奇数番目のゲート出力Vg1a、Vg2a、Vgmaと偶数番目のゲート出力Vg1b、Vg2b、Vgmbとを比較すると、一群の副画素に印加されるゲート出力は重畳するが、他群の副画素に印加されるゲート出力は互いに重畳しない。例えば、図6及び図7に示すように、第1群の副画素に印加されるゲート出力Vg1a、Vg1bは互いに重畳するのに対し、これに隣接した第2群の副画素に印加される出力Vg2a、Vg2bは第1ゲート出力Vg1a、Vg1bと重畳しない。詳しくは、図6では、ゲート出力Vg1bと引続き生成されるゲート出力Vg2aが重畳せず、図7では、ゲート出力Vg1aと引続き生成されるゲート出力Vg2bが重畳しない。

#### 【0046】

このようにすると、一群の副画素PXa、PXbのうちの奇数番目のゲート線GLaに接続されている副画素PXaは1H間データ電圧の印加を受け、副画素PXbも1H間データ電圧の印加を受けて、各画素内の各副画素PXa、PXbは、十分に充電される。

一方、上述したゲートクロック信号CPV1、CPV2のデューティ比を50%としたが、このうち、特にゲートクロック信号CPV2のデューティ比を、これよりも大きくして副画素PXbの充電率を高めることができる。例えば、ゲートクロック信号CPV2のデューティ比を75%未満等にすることができる。

#### 【0047】

次に、このようなゲート駆動部を備えた液晶表示装置における様々なデータ電圧の印加類型について図9乃至図12を参照して詳細に説明する。

図9乃至図12は、本発明の一実施形態による液晶表示装置の信号波形を時間によって示した図であり、Vdは一つのデータ線に流れるデータ電圧である。

10

20

30

40

50

ここで、図9及び図10は、図6に示すように、ゲートクロック信号CPV1が先行する場合に該当するデータ電圧の印加類型を示し、図11及び図12は、図7に示すように、ゲートクロック信号CPV2が先行する場合に該当するデータ電圧の印加類型を示す。

【0048】

ドット反転の場合は、隣接画素の極性が逆であるため、隣接画素のデータ電圧の印加を受けることは、充電時間の減少にあまり寄与しない。よって、図9及び図11に示すように、隣接画素の充電時間は重畠しないようにし、一つの画素の二つの副画素の充電時間を重畠することが好ましい。その結果、後から充電される副画素の充電時間が減少するので、図9及び図11示すように、初めに充電される副画素に印加される階調電圧群の大きさ(GVa)よりも後から充電される副画素に印加される階調電圧群の大きさ(GVb)を大きくすることが好ましい。

【0049】

一方、列反転の場合は、上下に隣接した画素の極性が同一であるので、隣接画素のデータ電圧を印加してプレ充電を行うことができる。これにより、図10及び図12に示すように、全副画素の充電時間を一定時間以上重畠することができる。

【0050】

さらに、本発明の一実施形態によるゲート駆動部400は、入力されるゲートクロック信号CPV1、CPV2を重畠しないようにすることもでき、その場合には、一つの画素に一つのスイッチング素子を有する構造にも適用できる。

また、本発明の一実施形態によるゲート駆動部400は、図5に示すゲート駆動部と異なって、シフトレジスタの最後のステージSTM<sub>a</sub>、STM<sub>b</sub>に走査開始信号を印加することができ、その場合、ゲート出力が右から左に順次生成される。即ち、第1ステージSTM<sub>1a</sub>、STM<sub>1b</sub>に走査開始信号が入力される場合には、左から右に順次出力を生成し(例: Vg<sub>1a</sub>、Vg<sub>2a</sub>、...、Vg<sub>ma</sub>)、これに対し、最後のステージSTM<sub>a</sub>、STM<sub>b</sub>に入力される場合は、右から左に順次に出力を生成する(例: Vg<sub>ma</sub>、...、Vg<sub>2a</sub>、Vg<sub>1a</sub>)。

【0051】

以上、本発明を実施するため最良の形態について詳細に説明したが、本発明の権利範囲はこれに限定されず、請求の範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態も本発明の権利範囲に属するものである。

【図面の簡単な説明】

【0052】

【図1】本発明の一実施形態による液晶表示装置のブロック図である。

【図2】本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図である。

【図3】本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図である。

【図4】本発明の一実施形態による液晶表示装置の一つの副画素に対する等価回路図である。

【図5】本発明の一実施形態によるゲート駆動部のブロック図である。

【図6】図4に示したゲート駆動部のタイミング図の例である。

【図7】図4に示したゲート駆動部のタイミング図の例である。

【図8】本発明の一実施形態による液晶表示装置のガンマ曲線を示したグラフである。

【図9】本発明の一実施形態による液晶表示装置の信号波形を時間によって示した図である。

【図10】本発明の一実施形態による液晶表示装置の信号波形を時間によって示した図である。

【図11】本発明の一実施形態による液晶表示装置の信号波形を時間によって示した図である。

【図12】本発明の一実施形態による液晶表示装置の信号波形を時間によって示した図である。

10

20

30

40

50

ある。

【符号の説明】

【0 0 5 3】

3 液晶層

1 0 0 下部表示板

2 0 0 上部表示板

3 0 0 液晶表示板組立体

4 0 0 ゲート駆動部

4 1 0 a、4 1 0 b シフトレジスタ

4 2 0 レベルシフタ

10

4 3 0 出力バッファ

5 0 0 データ駆動部

6 0 0 信号制御部

7 1 0 D V R

8 0 0 階調電圧生成部

P E 画素電極

C E 共通電極

C F カラーフィルタ

R、G、B 入力映像信号

D E データイネーブル信号

20

M C L K メインクロック

H s y n c 水平同期信号

V s y n c 垂直同期信号

C O N T 1 ゲート制御信号

C O N T 2 データ制御信号

D A T 映像データ

C L c 液晶キャパシタ

C s T ストレージキャパシタ

Q スイッチング素子

C P V 1、C P V 2 ゲートクロック信号

30

S T V 走査開始信号

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

## フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 1 2 K |

|             | G 0 9 G | 3/20 6 2 4 B |

|             | G 0 9 G | 3/20 6 4 1 C |

|             | G 0 9 G | 3/20 6 4 1 G |

(72)発明者 文 勝 煥

大韓民国 京畿道 龍仁市 上ヒョン洞 マンヒョンマウル2団地 現代アイパーク6次アパート

205棟 1504号

(72)発明者 李 潤 表

大韓民国 京畿道 城南市 益唐区 亭子洞 17-2番地 ドンヤンパラゴンB棟 1320号

(72)発明者 金 宇 哲

大韓民国 京畿道 龍仁市 器興邑 三星電子(株)器興工場 ソンヒョン館 マロニ工棟 30

8号

F ターム(参考) 2H093 NA16 NA43 NC10 NC22 NC34 NC35 ND01 ND31 ND42 ND54

5C006 AA16 AC11 AC22 AC27 AC28 BB16 BC03 BC05 BF03 BF25

FA54 FA55 GA02

5C080 AA10 BB05 DD03 EE29 FF11 JJ02 JJ03 JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的门驱动单元和驱动单元以及具有该显示装置的显示装置                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2006293371A</a>                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2006-10-26 |

| 申请号            | JP2006109210                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2006-04-11 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 孫宣圭<br>文勝煥<br>李濬表<br>金宇哲                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 孫宣圭<br>文勝煥<br>李濬表<br>金宇哲                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3677 G09G3/3659 G09G2300/0439 G09G2310/0251                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.622.B G09G3/20.622.E G09G3/20.621.L G09G3/20.612.K<br>G09G3/20.624.B G09G3/20.641.C G09G3/20.641.G                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NC10 2H093/NC22 2H093/NC34 2H093/NC35 2H093/ND01 2H093<br>/ND31 2H093/ND42 2H093/ND54 5C006/AA16 5C006/AC11 5C006/AC22 5C006/AC27 5C006/AC28<br>5C006/BB16 5C006/BC03 5C006/BC05 5C006/BF03 5C006/BF25 5C006/FA54 5C006/FA55 5C006<br>/GA02 5C080/AA10 5C080/BB05 5C080/DD03 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03<br>5C080/JJ04 5C080/JJ05 5C080/JJ06 2H193/ZA04 2H193/ZF22 |         |            |

| 优先权            | 1020050029903 2005-04-11 KR                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 其他公开文献         | JP2006293371A5<br>JP4953227B2                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

### 摘要(译)

阿通过分开驱动奇数和设置有具有栅极驱动器两个移位寄存器，并在同一时间来提高两个子像素的充电时间甚至子像素，具有这种像素排列从而提高了液晶显示装置的可视性。对于根据本发明的一个方面的显示装置的驱动装置被布置在矩阵中，多个分别具有第一和第二子像素的像素的，分别连接到第一子像素，第一栅极信号多个第二栅极线连接到第二子像素并传输第二栅极信号，栅极驱动器用于产生第一和第二栅极信号，栅极驱动器包括用于产生第一门信号的第一移位寄存器，用于产生第二栅极信号的第二移位寄存器，连接到所述第一和第二移位寄存器的电平移位器被连接到电平移位器还有一个输出缓冲区。点域4