## 【特許請求の範囲】

## 【請求項 1】

液晶表示装置を駆動するための駆動電圧を発生する回路において、クロック信号に応じて入力電圧を昇圧して第1駆動電圧を出力するDC-DCコンバータと、

所定の制御電圧のレベルに応じた可変の周波数を有する前記クロック信号を発する電圧制御発振器と、

所定の基準電圧と前記第1駆動電圧を反映するフィードバック電圧との差を利用して前記制御電圧を発生する制御電圧発生器とを備えることを特徴とする液晶表示装置の駆動電圧発生回路。

10

## 【請求項 2】

前記駆動電圧発生回路は、

前記第1駆動電圧を分配して前記フィードバック電圧を発生するフィードバック電圧分配器をさらに備えることを特徴とする請求項1に記載の液晶表示装置の駆動電圧発生回路。

## 【請求項 3】

前記駆動電圧発生回路は、前記フィードバック電圧と前記基準電圧とを比較してイネーブル信号を発する比較器をさらに備え、

前記DC-DCコンバータは前記イネーブル信号に応じて動作することを特徴とする請求項1に記載の液晶表示装置の駆動電圧発生回路。

## 【請求項 4】

前記制御電圧発生器は、

前記基準電圧と前記フィードバック電圧との差を増幅する電圧増幅器を含むことを特徴とする請求項1に記載の液晶表示装置の駆動電圧発生回路。

20

## 【請求項 5】

前記駆動電圧発生回路は、

前記第1駆動電圧を分配し、前記第1駆動電圧及び接地電圧と共に液晶表示装置に入力される第2ないし第5駆動電圧を出力する駆動電圧分配器をさらに備えることを特徴とする請求項1に記載の液晶表示装置の駆動電圧発生回路。

## 【請求項 6】

前記DC-DCコンバータは、

30

第1スイッチング信号に応じて開閉される一つ以上の第1スイッチと、

第1スイッチング信号の反転信号を反映する第2スイッチング信号に応じて開閉される一つ以上の第2スイッチと、

前記第1スイッチ及び前記クロック信号の端子間に形成される一つ以上の第1キャパシタと、

前記第2スイッチ及び前記クロック信号の反転信号を反映する信号の端子間に形成される一つ以上の第2キャパシタとを含むことを特徴とする請求項1に記載の液晶表示装置の駆動電圧発生回路。

## 【請求項 7】

前記電圧制御発振器は、

40

複数のインバータが直列に連結されるインバータチェーンと、

前記複数のインバータの各出力端子にそれぞれ電気的に接続され、前記制御電圧に応じてその抵抗値が変化する複数の抵抗と、

前記複数の抵抗と接地電圧間にそれぞれ形成される複数のキャパシタとを含むことを特徴とする請求項1に記載の液晶表示装置の駆動電圧発生回路。

## 【請求項 8】

前記複数の抵抗のそれぞれは、

そのゲートに前記制御電圧が印加されるMOSトランジスタであることを特徴とする請求項7に記載の液晶表示装置の駆動電圧発生回路。

## 【請求項 9】

50

液晶表示装置を駆動するための駆動電圧を発生する回路において、クロック信号に応じて入力電圧を昇圧して第1駆動電圧を出力するDC-DCコンバータと、

前記クロック信号を発生する発振器と、

前記第1駆動電圧を分配し、前記第1駆動電圧に比べて低レベルを有し前記第1駆動電圧と共に前記液晶表示装置を駆動する複数の分配駆動電圧を出力する駆動電圧分配器とを備え、

前記クロック信号の周波数は前記液晶表示装置の負荷量に応じて変化することを特徴とする液晶表示装置の駆動電圧発生回路。

【請求項10】

前記クロック信号の周波数は、

前記液晶表示装置の負荷量が多いほど高くなることを特徴とする請求項9に記載の液晶表示装置の駆動電圧発生回路。

【請求項11】

前記駆動電圧発生回路は、

所定の基準電圧と前記第1駆動電圧を分配したフィードバック電圧との差を利用して前記液晶表示装置の負荷量を反映する制御電圧を発生する制御電圧発生器をさらに備えることを特徴とする請求項9に記載の液晶表示装置の駆動電圧発生回路。

【請求項12】

前記発振器は、

前記制御電圧に応じて周波数が変化する前記クロック信号を発生する電圧制御発振器であることを特徴とする請求項11に記載の液晶表示装置の駆動電圧発生回路。

【請求項13】

前記制御電圧は、

前記基準電圧から前記フィードバック電圧を引いた差が大きいほど高くなることを特徴とする請求項12に記載の液晶表示装置の駆動電圧発生回路。

【請求項14】

前記DC-DCコンバータは、

所定のイネーブル信号の活性化に応じて動作することを特徴とする請求項11に記載の液晶表示装置の駆動電圧発生回路。

【請求項15】

前記駆動電圧発生回路は、

前記フィードバック電圧が前記基準電圧より低い場合、前記イネーブル信号を活性化させることを特徴とする請求項14に記載の液晶表示装置の駆動電圧発生回路。

【請求項16】

液晶表示装置を駆動するための駆動電圧を発生する方法において、

クロック信号を利用し、入力電圧を昇圧して第1駆動電圧を出力する段階と、前記第1駆動電圧を分配し、前記第1駆動電圧に比べて低レベルを有し前記第1駆動電圧と共に前記液晶表示装置を駆動する複数の分配駆動電圧を出力する段階と、

前記液晶表示装置の負荷量に応じて前記クロック信号の周波数を変更する段階とを備えることを特徴とする液晶表示装置の駆動電圧発生方法。

【請求項17】

前記クロック信号の周波数は、

前記液晶表示装置の負荷量が多いほど高くなることを特徴とする請求項16に記載の液晶表示装置の駆動電圧発生方法。

【請求項18】

前記クロック信号の周波数を変更する段階は、

前記第1駆動電圧を分配してフィードバック電圧を発生する段階と、

所定の基準電圧と前記フィードバック電圧との差を利用し、前記液晶表示装置の負荷量を反映する制御電圧を発生する段階と、

10

20

30

40

50

前記制御電圧により前記クロック信号の周波数を変更する段階とを含むことを特徴とする請求項16に記載の液晶表示装置の駆動電圧発生方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は液晶表示装置 (Liquid Crystal Display、以下「LCD」とする) を駆動するための集積回路に係り、LCD駆動用集積回路 (以下、「LCDドライバIC」という) から駆動電圧を発生する回路に関する。

【0002】

【従来の技術】

LCDは携帯用コンピュータやPDA (Personal Digital Assistant) のような携帯用通信製品や一般家電製品において多用されているディスプレイ装置であり、液晶パネル両端に印加される電圧の強さにより光透過率が変わる特性を利用してデータをディスプレイする。LCDには、大きくわけて、STN (Super Twisted Nematic) - LCDとTFT (Thin Film Transistor) - LCDとがある。STN - LCDであるかTFT - LCDであるかによりLCDの駆動方法も変わる。

【0003】

LCDドライバICはLCDの液晶パネルにデータを表示するために必要な駆動電圧を発生する役割を果たすICである。

【0004】

液晶パネルの両端には電圧を印加するための電極があり、一般的に一端の電極を共通電極、他端の電極をセグメント電極という。そして、共通電極に入力される電圧を共通電圧と言い、セグメント電極に入力される電圧をセグメント電圧と言う。

【0005】

LCDドライバICは、LCD画面に表示される文字及び/または映像をマイクロプロセッサから受信して、液晶を駆動できるセグメント電圧及び共通電圧に変換して液晶パネルに印加する。これにより文字及び/または映像のディスプレイが可能になる。

【0006】

LCDパネルの共通電極及びセグメント電極に入力される駆動電圧は一般的に6つのレベルの電圧である。駆動電圧発生回路は6つのレベルの駆動電圧を生成する回路であり、そのような駆動電圧を少量の電力消耗で効率的に生成することが重要である。

【0007】

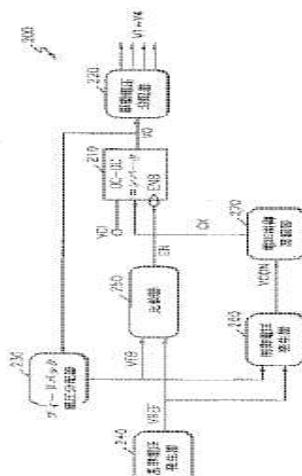

図1は従来技術によるLCDドライバICの駆動電圧発生回路を示すブロック図であり、図1に示された回路は従来のSTN - LCDドライバICに一般的に使われる回路である。

【0008】

従来技術によるLCD駆動電圧発生回路100はDC - DCコンバータ110、電圧分配器120、発振器130を備える。

【0009】

DC - DCコンバータ110は電圧ブースタとも言われる回路であり、受信される入力電圧VCIを所定量だけ昇圧して第1駆動電圧V0を発生する。第1駆動電圧V0はLCDパネル130の駆動に必要な高電圧である。

【0010】

DC - DCコンバータ110の昇圧は、基本的にスイッチングを介してキャパシタに電荷を充電してそれをポンピングすることによりなされる。スイッチング動作に必要なスイッチング信号としては一定周期のクロック信号CKが使われる。

【0011】

クロック信号CKは発振器130において生成される。

【0012】

10

20

30

40

50

D C - D C コンバータ 110において生成された第1駆動電圧 V 0 は電圧分配器 120によって分配されて第2～第5駆動電圧 V 1～V 4 として出力される。第2～第5駆動電圧 V 1～V 4 は第1駆動電圧 V 0 及び接地電圧 V SS と共に L C D パネル 130 を駆動するための電圧として使われる。

## 【0013】

L C D パネル 130 が駆動されると、パネルによって消耗される電力（または電流）のゆえに第1駆動電圧 V 0 のレベルがディスプレイパターンに応じて変わる。すなわち、パネルによって消耗される電流量が少なければ第1駆動電圧 V 0 のレベルがある程度一定に保持されるが、パネルによって消耗される電流量が多ければ第1駆動電圧 V 0 のレベルがかなり下がる。

10

## 【0014】

上記の通りに、ディスプレイパターンに応じて電流消耗量が変化し、そして電流消耗量に応じて第1駆動電圧 V 0 レベルが変化すると、ディスプレイパターンにより画面の明るさが変わるという問題が生じる。

## 【0015】

第1駆動電圧 V 0 を使って第2ないし第5駆動電圧 V 1～V 4 も生成されるので、第1駆動電圧 V 0 を一定レベルに昇圧させて発生させることが重要である。

## 【0016】

ところで、従来技術による駆動電圧発生回路 100 のように、D C - D C コンバータ 110 が固定された周波数のクロック信号 CK を利用する場合には効率的に昇圧動作を行えない。昇圧動作の効率性は電力消耗量とブースティング効率とに関係していて、電力消耗量が少なくてブースティング効率が高いことが望ましい。

20

## 【0017】

ブースティング効率というのは第1駆動電圧 V 0 の目標値に対する実際の第1駆動電圧 V 0 の比を百分率で示したものである。すなわち、所望の第1駆動電圧 V 0 の目標値が 10 V であり、L C D パネルの負荷により実際の第1駆動電圧 V 0 のレベルが 8 V に下がるならばブースティング効率は 80 % である。従って、L C D パネル 130 の負荷に関係なく第1駆動電圧 V 0 を所望のレベルに保持させることができなければブースティング効率が改善されない。

30

## 【0018】

L C D パネル 130 の電流消耗量が少ない場合には、一般的に非常に低い周波数のクロック信号 CK を用いても十分なブースティング効率を得られる。一方、L C D パネル 130 の電流消耗量が増えるほどクロック信号 CK の周波数を高めなければブースティング効率が改善されない。

## 【0019】

ところで、従来技術による駆動電圧発生回路 100 は固定周波数のクロック信号 CK を利用することにより、L C D パネル 130 の電流消耗量が少ない場合には D C - D C コンバータ 110 での不必要な電流消耗を発生させる。一般的に、クロック信号 CK の周波数が高ければ D C - D C コンバータ 110 自体で消耗される電流がさらに多くなるためである。

40

## 【0020】

一方、L C D パネル 130 の電流消耗量が非常に多い場合には、相対的に高い周波数のクロック信号 CK が必要であるが、従来技術による駆動電圧発生回路 100 は固定された周波数のクロック信号 CK でブースティングすることにより、第1駆動電圧 V 0 レベルの低下が大きくなり、結果的にディスプレイの質を下げる。

## 【0021】

## 【発明が解決しようとする課題】

よって、本発明がなそうとする技術的課題は、電力使用を減らしてブースティング効率を改善することにより、L C D パネルの電流消耗量が増えてもディスプレイ画面の質が下がらないようにする L C D 駆動電圧発生回路を提供することである。

50

**【 0 0 2 2 】**

本発明がなそうとする他の技術的課題は、前記 L C D 駆動電圧発生回路に適用される L C D 駆動電圧発生法を提供することである。

**【 0 0 2 3 】****【課題を解決するための手段】**

前記技術的課題を達成するための本発明の一面は、 L C D を駆動するための駆動電圧を発生する回路に関する。本発明の一面による駆動電圧発生回路は、クロック信号に応じて入力電圧を昇圧して第1駆動電圧を出力する D C - D C コンバータと、所定の制御電圧のレベルに応じた可変の周波数を有する前記クロック信号を発生する電圧制御発振器と、所定の基準電圧と前記第1駆動電圧を反映するフィードバック電圧との差を利用して前記制御電圧を発生する制御電圧発生器とを備えることを特徴とする。

**【 0 0 2 4 】**

望ましくは、前記駆動電圧発生回路は前記第1駆動電圧を分配して前記フィードバック電圧を発生するフィードバック電圧分配器をさらに備える。

**【 0 0 2 5 】**

また望ましくは、前記駆動電圧発生回路は、前記フィードバック電圧と前記基準電圧とを比較してイネーブル信号を発する比較器をさらに備え、前記 D C - D C コンバータは前記イネーブル信号に応じて動作する。

**【 0 0 2 6 】**

前記技術的課題を達成するための本発明の他の一面も L C D を駆動するための駆動電圧を発生する回路に関する。本発明の他の一面による駆動電圧発生回路は、クロック信号に応じて入力電圧を昇圧して第1駆動電圧を出力する D C - D C コンバータと、前記クロック信号を発生する発振器と、前記第1駆動電圧を分配し、前記第1駆動電圧に比べて低レベルを有し前記第1駆動電圧と共に前記 L C D を駆動する複数の分配駆動電圧を出力する駆動電圧分配器とを備え、前記クロック信号の周波数は前記 L C D の負荷量に応じて変化することを特徴とする。

**【 0 0 2 7 】**

望ましくは、前記クロック信号の周波数は前記 L C D の負荷量が多いほど高くなる。

**【 0 0 2 8 】**

また望ましくは、前記駆動電圧発生回路は所定の基準電圧と前記第1駆動電圧を分配したフィードバック電圧との差を利用して前記 L C D の負荷量を反映する制御電圧を発生する制御電圧発生器をさらに備え、前記発振器は前記制御電圧に応じて周波数が変化する前記クロック信号を発生する電圧制御発振器である。

**【 0 0 2 9 】**

前記他の技術的課題を達成するための本発明の一面は、 L C D を駆動するための駆動電圧を発生する方法に関する。本発明の一面による駆動電圧発生法は、クロック信号を利用し、入力電圧を昇圧して第1駆動電圧を出力する段階と、前記第1駆動電圧を分配し、前記第1駆動電圧に比べて低レベルを有し前記第1駆動電圧と共に前記 L C D を駆動する複数の分配駆動電圧を出力する段階と、前記 L C D の負荷量により前記クロック信号の周波数を変更する段階とを備えることを特徴とする。

**【 0 0 3 0 】****【発明の実施の形態】**

本発明とその動作上のメリット及び本発明の実施により達成される目的を十分に理解するためには本発明の望ましい実施形態を例示する添付図面及びそれに関連する説明を参照しなければならない。

**【 0 0 3 1 】**

以下、添付した図面を参照して本発明の望ましい実施形態を説明することにより、本発明を詳細に説明する。各図面に提示された同じ参照符号は同じ構成要素を示す。

**【 0 0 3 2 】**

図面を参照して本発明の実施形態を説明する前に、電圧のブースティングに使われるクロ

10

20

30

40

50

ック信号の周波数に対するブースティング効率の関係を考察する。クロック信号の周波数をブースティング周波数とも言う。

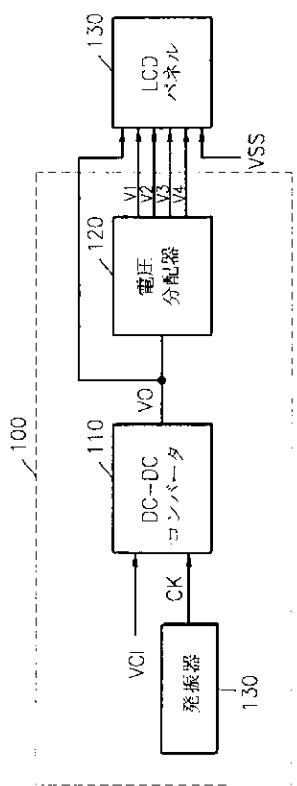

【0033】

図2はクロック信号の周波数FCKによるLCDパネルの電流消耗量ILoadに対するブースティング効率の関係を示す図面である。図2を参照すれば、クロック信号の周波数FCKがいかなる値を有しても、電流消耗量ILoadが増えればブースティング効率が下がる。しかし、クロック信号の周波数FCKが390KHzである場合における電流消耗量ILoadの増加によるブースティング効率の降下は、クロック信号の周波数FCKが230KHzである場合における電流消耗量ILoadの増加によるブースティング効率の減少に比べてはるかに少ない。すなわち、クロック信号の周波数FCKが230KHzである場合には電流消耗量ILoadの増加により第1駆動電圧V0のレベルが相当に低下するのに対して、クロック信号の周波数FCKが390KHzである場合には電流消耗量ILoadの増加による第1駆動電圧V0のレベルの低下は少ない。すなわち、LCDパネルの電流消耗量ILoadが多い場合にはブースティング周波数FCKを高くしなければブースティング効率が改善されない。

10

【0034】

一方、LCDパネルの電流消耗量ILoadが非常に少ない場合にはブースティング効率はブースティング周波数FCKにあまり影響を受けない。

【0035】

図2に示された実験結果から、LCDパネルの電流消耗量ILoadによりブースティング周波数FCKを可変にすることがブースティング効率面と電力消耗面とで効果的であることが分かる。

20

【0036】

従って、本発明はLCDパネルの負荷が変わっても駆動電圧のレベルは一定に保持されるように、LCDパネルの負荷（すなわち、電流消耗量）に応じてブースティング周波数FCKを最適に変更する。

【0037】

最も理想的な場合は図3に示されたように、電流消耗量ILoadが変わってもブースティング効率の特性低下が現れず、第1駆動電圧V0のレベルが一定に保持されることである。

30

【0038】

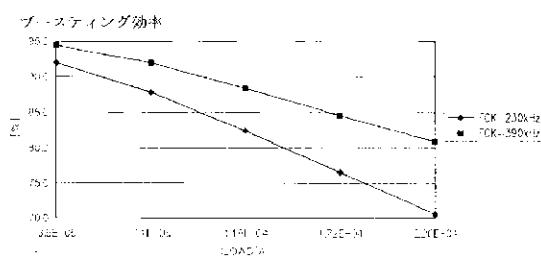

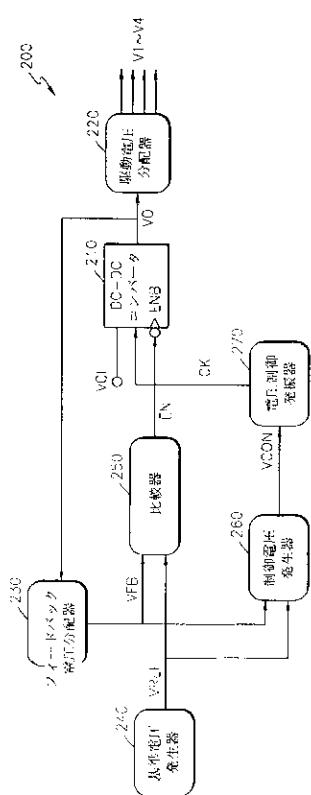

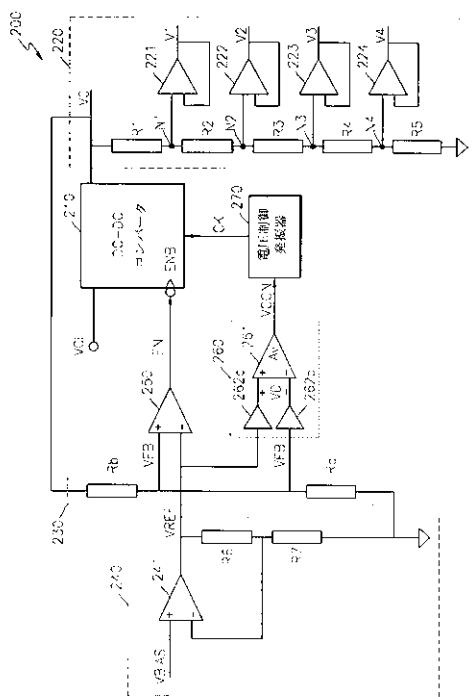

図4は本発明の一実施例によるLCD駆動電圧発生回路200を示すブロック図である。

【0039】

図4を参照すれば、本発明の一実施形態による駆動電圧発生回路200は、DC-DCコンバータ210、駆動電圧分配器220、フィードバック電圧分配器230、基準電圧発生器240、比較器250、制御電圧発生器260及び電圧制御発振器270を備える。

【0040】

DC-DCコンバータ210は入力電圧VCIを受けてこれを昇圧し、第1駆動電圧V0を発生する。DC-DCコンバータ210はイネーブル信号ENにより昇圧動作がイネーブルされ。クロック信号CKに応じて電荷をポンピングすることにより入力電圧VCIを昇圧する。DC-DCコンバータ210は入力電圧VCIをその所定倍数（以下、ブースティング倍数という）の電圧に昇圧できるように構成される。

40

【0041】

例えば、入力電圧が3Vであり、ブースティング倍数が4になるべくDC-DCコンバータ210が具現されれば、DC-DCコンバータ210は最大12Vの第1駆動電圧V0を発生できる。ところで、LCDパネルにおいて必要とする第1駆動電圧V0が前記最大電圧の12Vより低い9Vであると仮定すると、LCDパネル駆動に必要な高電圧は9Vであるので、12Vまで昇圧することは不必要的電力消耗をもたらす。

【0042】

従って、不必要的電力消耗を減らすために、第1駆動電圧V0が目標値の9Vになれば昇

50

圧動作を止めることが必要である。

【0043】

上記の通りに、必要時、すなわち第1駆動電圧V0が目標値より低い場合にだけ昇圧動作を行うために、DC-DCコンバータ210はイネーブル信号ENの活性化に応じて動作するように構成される。

【0044】

比較器250は、フィードバック電圧VFBと基準電圧VREFとを比較して、DC-DCコンバータ210に昇圧動作を行わせるか否かを制御するイネーブル信号ENを発生する。比較器250は第1駆動電圧V0を反映するフィードバック電圧VFBが基準電圧VREFに比べて低い時に活性化されるイネーブル信号ENを発生する。イネーブル信号ENはDC-DCコンバータ210に入力されてDC-DCコンバータ210を動作させるか否かを制御する。フィードバック電圧VFBは第1駆動電圧V0を分配して発生することが望ましい。10

【0045】

DC-DCコンバータ210の昇圧動作に必要なクロック信号CKは電圧制御発振器270から出力される。

【0046】

電圧制御発振器270は制御電圧VCONのレベルに応じた可変の周波数を有するクロック信号CKを発生する。制御電圧VCONは制御電圧発生器260より発生する。制御電圧VCONのレベルは第1駆動電圧V0を反映するフィードバック電圧VFBと基準電圧VREFとの差により変化する。20

【0047】

第1駆動電圧V0を分配してフィードバック電圧VFBを発生する役割はフィードバック電圧分配器230により行われる。すなわち、フィードバック電圧分配器230は第1駆動電圧V0を分配してフィードバック電圧VFBを生成し、これを比較器250及び制御電圧発生器260に提供する。

【0048】

基準電圧発生器240は比較器250及び制御電圧発生器260に入力される基準電圧VREFを発生する。基準電圧発生器240は電源電圧及び温度などに鈍感に設計されることが望ましい。30

【0049】

駆動電圧分配器220は第1駆動電圧V0を受信して分配し、第2ないし第5駆動電圧V1～V4を出力する。第1ないし第5駆動電圧V0～V4及び接地電圧VSSは液晶パネルに入力される。上記の通りに6種類の電圧V0～V4, VSSが液晶パネルを駆動するために使われる。

【0050】

図5は本発明の一実施例による駆動電圧発生回路200を詳細に示す図面である。DC-DCコンバータ210の詳細な構成は図6に示される。

【0051】

まず図5を参照すれば、駆動電圧分配器220は第1～第5分配抵抗R1～R5及び第1～第4電圧フォロア221～224を含む。第1～第5分配抵抗R1～R5は第1駆動電圧V0と接地電圧VSSとの間に直列に連結される。第1分配抵抗R1は第1駆動電圧V0と第1ノードN1との間に、第2分配抵抗R2は第1ノードN1と第2ノードN2との間に、第3分配抵抗R3は第2ノードN2と第3ノードN3との間に、第4分配抵抗R4は第3ノードN3と第4ノードNとの間に、そして、第5分配抵抗R5は第4ノードN4と接地電圧VSSとの間に位置する。各ノードN1～N4の電圧は該当する電圧フォロア221～224を介してそれぞれ第2, 第3, 第4及び第5駆動電圧V1～V4として出力される。40

【0052】

従って、第2ないし第5駆動電圧V1～V4は第1駆動電圧V0と接地電圧VSSとの間

10

30

40

50

のレベルを有する電圧になる。

【0053】

フィードバック電圧分配器230は2つの分配抵抗R<sub>a</sub>, R<sub>b</sub>を含む。フィードバック電圧分配器230において発生するフィードバック電圧VFBは第1駆動電圧V0, 分配抵抗値R<sub>a</sub>, R<sub>b</sub>の比により決まる。

【0054】

分配抵抗値R<sub>a</sub>, R<sub>b</sub>は第1駆動電圧V0が所定の目標値である時、フィードバック電圧VFBと基準電圧VREFとが同じになるように設定されることが望ましい。

【0055】

基準電圧発生器240は正端子(+)でバイアス電圧VBIASを受けて、負端子(-)では出力電圧である基準電圧VREFが2つの抵抗R<sub>6</sub>, R<sub>7</sub>により分配された電圧を受ける演算增幅器241を利用して構成される。

【0056】

比較器250は正端子(+)ではフィードバック電圧VFBを、負端子(-)では基準電圧VREFをそれぞれ受けて、フィードバック電圧VFBが基準電圧VREFより高い時はハイレベルのイネーブル信号ENを、フィードバック電圧VFBが基準電圧VREFより低い時はローレベルのイネーブル信号ENを出力する。DC-DCコンバータ210はローレベルのイネーブル信号ENに応じて昇圧動作を行う。

【0057】

従って、比較器250はフィードバック電圧VFBが基準電圧VREFに比べて低い場合に、DC-DCコンバータ210をイネーブルにするイネーブル信号ENを発生する。フィードバック電圧VFBが基準電圧VREFより低いということは第1駆動電圧V0が所望の目標値より低いということを意味する。従って、第1駆動電圧V0が目標値より低い場合はイネーブル信号ENがローレベルに活性化され、これによりDC-DCコンバータ210が昇圧動作を行い、第1駆動電圧V0を高める。DC-DCコンバータ210の昇圧動作により第1駆動電圧V0が目標値より高くなると、フィードバック電圧VFBが基準電圧VREFより高くなり、これによりイネーブル信号ENが非活性化されてDC-DCコンバータ210の昇圧動作が中断される。

【0058】

制御電圧発生器260は電圧増幅器261、2つのバッファ262a, 262bを含む。バッファ262a, 262bはフィードバック電圧VFBと基準電圧VREFとをそれぞれバッファリングする。電圧増幅器261は基準電圧VREFとフィードバック電圧VFBとの差に比例する電圧を発生する。従って、フィードバック電圧VFBが基準電圧VREFに比べて低いほど高いレベルの制御電圧VCONが発生する。フィードバック電圧VFBが基準電圧VREFより低いということは第1駆動電圧V0が目標値より低いということを意味する。また、第1駆動電圧V0が目標値より低いということは、それだけLCDパネルの負荷が多いということを意味する。

【0059】

電圧増幅器261は正端子(+)では基準電圧VREFを受け、負端子(-)ではフィードバック電圧VFBを受ける演算増幅器より構成されうる。

【0060】

電圧増幅器261から出力された制御電圧VCONは電圧制御発振器270に入力される。

【0061】

電圧制御発振器270は入力される制御電圧VCONのレベルに応じた可変の周波数を有するクロック信号CKを発生する。すなわち、制御電圧VCONのレベルが高いほど高周波数のクロック信号CKが、制御電圧VCONのレベルが低いほど低周波数のクロック信号CKが生成され出力される。電圧制御発振器270の詳細な構成は図5に示される。

【0062】

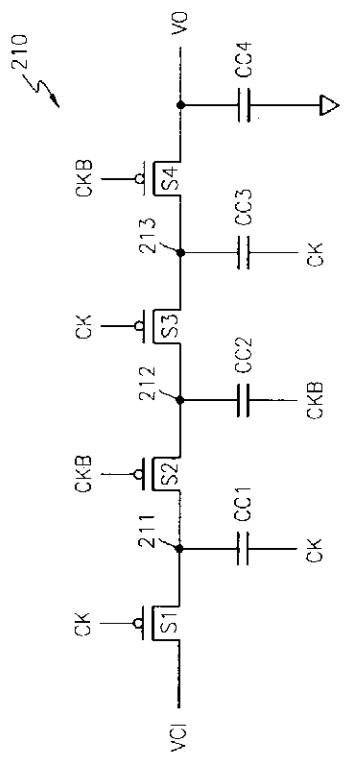

まず、図6を参照してDC-DCコンバータ210の詳細な構成を説明する。図6に示さ

10

20

30

40

50

れた D C - D C コンバータ 210 は一構成例であり、本発明の D C - D C コンバータ 210 の構成が図 6 に示された例に限定されることは自明である。

【 0 0 6 3 】

D C - D C コンバータ 210 は一つ以上のスイッチ及びキャパシタを含む。図 6 に示された D C - D C コンバータ 210 は 4 つのスイッチ及び 4 つのキャパシタを含む。説明の便宜上、D C - D C コンバータ 210 に含まれる 4 つのスイッチを第 1 ~ 第 4 スイッチ S 1 ~ S 4 、4 つのキャパシタを第 1 ~ 第 4 キャパシタ C C 1 ~ C C 4 とする。

【 0 0 6 4 】

第 1 ~ 第 4 スイッチ S 1 ~ S 4 はゲートにスイッチング信号を受ける M O S トランジスタであることが望ましいが、ここでは P M O S トランジスタより構成される。

10

【 0 0 6 5 】

第 1 ~ 第 4 スイッチ S 1 ~ S 4 は入力電圧 V C I 端子と出力電圧（すなわち、第 1 駆動電圧 V 0 ）端子間に直列に連結される。そして、第 1 ~ 第 4 スイッチ S 1 ~ S 4 の一端子には第 1 ~ 第 4 キャパシタ C C 1 ~ C C 4 がそれぞれ連結される。

【 0 0 6 6 】

第 1 及び第 3 スイッチ S 1 , S 3 のスイッチング信号としてクロック信号 C K が入力され、第 2 及び第 4 スイッチ S 2 , S 4 のスイッチング信号として反転クロック信号 C K B が入力される。そして、第 1 及び第 3 キャパシタ C C 1 , C C 3 の一端子にはクロック信号 C K が入力され、第 2 及び第 4 キャパシタ C C 2 , C C 4 の一端子には反転クロック信号 C K B が入力される。

20

【 0 0 6 7 】

そして、クロック信号 C K は接地電圧 V S S と入力電圧 V C I レベル間をスイングする信号であることが望ましい。

【 0 0 6 8 】

上記のように D C - D C コンバータ 210 を構成することにより、第 1 スイッチングノード 211 の電圧レベルは入力電圧が V C I レベルである場合に、その入力電圧レベルの 2 倍の 2 V C I の間をスイングし、第 2 スイッチングノード 212 の電圧レベルは 2 × 入力電圧レベル 2 V C I と 3 × 入力電圧レベル 3 V C I との間をスイングし、第 3 スイッチングノード 213 の電圧レベルは 3 × 入力電圧レベル 3 V C I と 4 × 入力電圧レベル 4 V C I との間をスイングする。第 3 スイッチングノード 213 の交流電圧は第 4 キャパシタ C C 4 により直流電圧に変換されて第 1 駆動電圧 V 0 として出力される。従って、第 1 駆動電圧 V 0 レベルは入力電圧 V C I レベルに比べて 3 倍ほどとなる。すなわち、図 6 に示された D C - D C コンバータ 210 はブースティング倍数が約 3 倍になるように設計された回路である。

30

【 0 0 6 9 】

ブースティング倍数は段数により調節されうる。ここで、段数とはクロック信号 C K または反転クロック信号 C K B に連結されるキャパシタ数と考えることができ、図 6 での段数は 3 である。

【 0 0 7 0 】

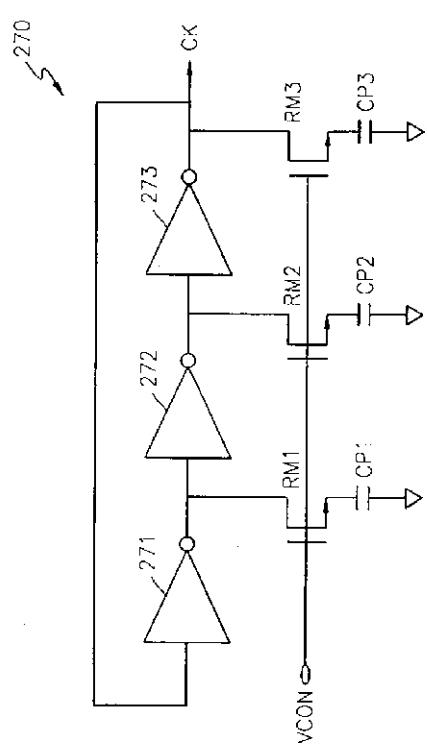

図 7 は図 4 に示された電圧制御発振器 270 の一構成例を示す回路図である。電圧制御発振器を構成する方法は様々であるが、本発明の実施例では電圧により値が変わる抵抗を利用し、インバータチェーンの出力ノードでの有効キャパシタンス値を可変にするリング発振器状の電圧制御発振器 270 が使われる。

40

【 0 0 7 1 】

図 7 を参照すれば、電圧制御発振器 270 は複数（ここでは、3 つ）のインバータ 271 , 272 , 273 が直列に連結されるインバータチェーンと各インバータの出力ノードに連結される複数（ここでは、3 ）の抵抗 R M 1 , R M 2 , R M 3 及び各抵抗 R M 1 , R M 2 , R M 3 と接地電圧間に形成される複数（ここでは、3 ）のキャパシタ C P 1 , C P 2 , C P 3 を含む。

【 0 0 7 2 】

50

インバータチェーンの出力がブースティング周波数 F C K を有するクロック信号 C K である。インバータチェーンの出力は再びインバータチェーンの入力になる。そして、抵抗 R M 1 , R M 2 , R M 3 はそのゲートには制御電圧 V C O N が、そのドレーンはインバータの出力ノードに、そのソースはキャパシタ L C P 1 , C P 2 , C P 3 の一端子にそれぞれ連結される N M O S トランジスタであることが望ましい。N M O S トランジスタ R M 1 , R M 2 , R M 3 それぞれはゲートに印加される制御電圧 V C O N のレベルが高いほど抵抗値が小さく、制御電圧 V C O N のレベルが低いほど抵抗値が大きい。制御電圧 V C O N のレベルが変化すると、それにつれてインバータ出力ノードにおける有効キャパシタンスも変化する。

## 【 0 0 7 3 】

10

上記のように制御電圧 V C O N により抵抗値が変化し有効キャパシタンスが変化すると、インバータの入力信号に対比した出力信号の遅延値が変化する。従って、インバータチェーンから出力されるクロック信号 C K の周波数が可変になる。

## 【 0 0 7 4 】

制御電圧 V C O N が高ければ抵抗値が小さくなり、これにより遅延時間が短くなるので、クロック信号 C K の周波数は高くなる。一方、制御電圧 V C O N が低ければ、抵抗値が大きくなり、これにより遅延時間が長くなつてクロック信号 C K の周波数は低くなる。

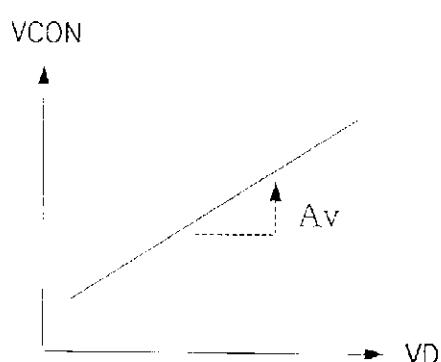

## 【 0 0 7 5 】

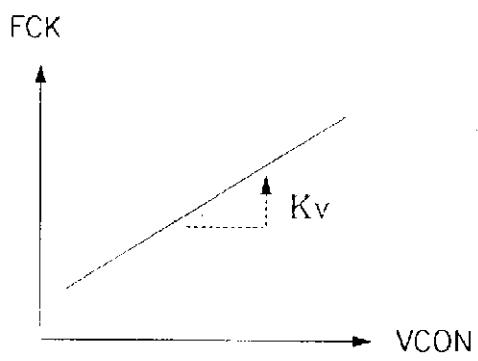

図 8 は図 5 に示された制御電圧発生器 2 6 0 の電圧増幅器 2 6 1 の特性を示す図面である。これを参照すれば、電圧増幅器 2 6 1 は基準電圧 V R E F とフィードバック電圧 V F B との差電圧 V D に比例してレベルが高くなる制御電圧 V C O N を発生する。このグラフの傾きを電圧利得 ( A v ) という。

20

## 【 0 0 7 6 】

図 9 は図 4 に示された電圧制御発振器 2 7 0 の特性を示す図面である。これを参照すれば、電圧制御発振器 2 7 0 から出力されるクロック信号の周波数 F C K は入力される制御電圧 V C O N に比例する。グラフの傾きを電圧 - 周波数感度 ( K v ) という。

## 【 0 0 7 7 】

制御電圧発生器 2 6 0 の電圧増幅器 2 6 1 の電圧利得 ( A v ) と電圧制御発振器 2 7 0 の電圧 - 周波数感度 ( K v ) とによりクロック信号の周波数 F C K の可変範囲が決まる。ブースティング周波数 F C K の可変範囲を狭くしたい場合、制御電圧発生器 2 6 0 の電圧増幅器の電圧利得 ( A v ) を小さく設定すればよく、特定の場合に減衰器として使われうる。

30

## 【 0 0 7 8 】

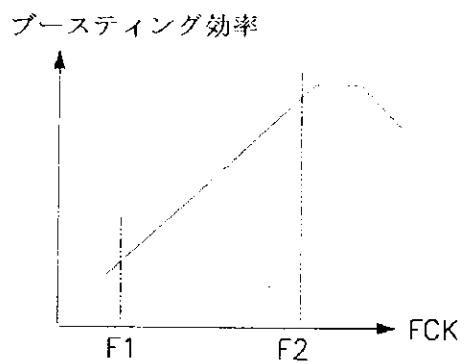

図 1 0 はクロック信号の周波数 F C K に対するブースティング効率特性を示す図面である。図 1 0 を参照すれば、ある程度の周波数 ( ここでは、F 2 ) まではクロック信号の周波数 F C K が高くなるほどブースティング効率が改善される。ブースティング効率というのは、前述のように、第 1 駆動電圧 V 0 の目標値に対する実際の第 1 駆動電圧 V 0 の比を百分率で示したものである。

## 【 0 0 7 9 】

40

図 1 0 を参照すれば、クロック信号の周波数 F C K が所定の臨界値を超えると、ブースティング周波数 F C K が高くなつてもブースティング効率が上がりずに停滞するか、むしろさらに下がる。これは、クロック信号の周波数 F C K が過度に高くなると D C - D C コンバータ 2 1 0 の昇圧効率がさらに下がるためである。すなわち、ブースティング周波数 F C K が高くなるにつれて D C - D C コンバータ 2 1 0 において消耗される自体電流も増えることにより生じる効率低下が一層支配的に現れるようになり、ブースティング周波数 F C K を高くしてもそれ以上の効率改善がなされない臨界値に達する。

## 【 0 0 8 0 】

従つて、クロック信号の周波数 F C K は図 1 0 に示されたように線形範囲 ( F 1 ~ F 2 ) 内に調節されることが望ましい。クロック信号 C K の周波数範囲は前述のように、図 8 及び図 9 に示された電圧利得 ( A v ) 及び / または電圧 - 周波数感度 ( K v ) を調整するこ

50

とにより調節されうる。

【0081】

本発明は図面に示された一実施形態を参考に説明されたがそれは例示的なものに過ぎず、本技術分野の当業者ならばそれから多様な変形及び均等な他の実施形態が可能であるという点が理解されるであろう。従って、本発明の真の技術的保護範囲は特許請求の範囲の技術的思想に基づいて決まるべきである。

【0082】

【発明の効果】

本発明によれば、例えば、文字だけのディスプレイのようにLCDパネルの電流消耗量が少ない場合には既存の固定ブースティング周波数とは異なって非常に低いブースティング周波数でDC-DCコンバータを動作させることにより、DC-DCコンバータ自体において消耗される電流損失を減らすことができる。一方、映像、特に動画のディスプレイのようにLCDパネルの電流消耗量が多い場合には、ブースティング周波数を高くして駆動電圧のレベルが下がらないようにすることで、ブースティング効率を改善する効果がある。

【0083】

従って、本発明によれば、電力使用が減ってブースティング効率が改善され、LCDパネルの電流消耗量が増えもディスプレイ画面の質が下がらない。

【図面の簡単な説明】

【図1】従来技術によるLCDドライバICの駆動電圧発生回路を示すブロック図である。

【図2】本発明の概念を説明するための図面であり、クロック信号の周波数によるLCDパネルの電流消耗量に対するブースティング効率の関係を示す図面である。

【図3】本発明の概念を説明するための図面であり、理想的なLCDパネルの電流消耗量に対する第1駆動電圧レベルを示す図面である。

【図4】本発明の一実施形態によるLCD駆動電圧発生回路を示すブロック図である。

【図5】本発明の一実施形態による駆動電圧発生回路を詳細に示す図面である。

【図6】図4に示されたDC-DCコンバータの詳細な構成を示す回路図である。

【図7】図4に示された電圧制御発振器の詳細な構成を示す回路図である。

【図8】図5に示された電圧増幅器の特性を示す図面である。

【図9】図4に示された電圧制御発振器の特性を示す図面である。

【図10】図4に示された駆動電圧発生回路でのクロック信号の周波数に対するブースティング効率特性を示す図面である。

【符号の説明】

200 駆動電圧発生回路

CK クロック信号

EN イネーブル信号

V0~4 第1~5駆動電圧

VCI 入力電圧

VCON 制御電圧

VFB フィードバック電圧

VREF 基準電圧

10

20

30

40

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

【図 10】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

H 0 4 N 5/66

F I

H 0 2 M 3/00

H

H 0 2 M 3/07

H 0 4 N 5/66 1 0 2 B

テーマコード(参考)

(72)発明者 金亨來

大韓民国京畿道水原市長安区栗田洞300番地

F ターム(参考) 2H093 NC02 NC34 NC41 ND39 NF13

5C006 AF54 AF72 BB11 BF14 BF25 BF26 BF27 BF34 BF43 BF46

BF49 FA47

5C058 AA09 BA01 BA04 BA26 BB10

5C080 AA10 BB05 DD26 FF09 JJ02 JJ03 JJ05

5H730 AA14 AS01 AS04 BB02 BB85 DD04 DD12 EE62 EE65 FD01

FF01 FG02 FG16 FG22

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示装置的驱动电压产生电路和方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2004004609A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2004-01-08 |

| 申请号            | JP2003070108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日     | 2003-03-14 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 朴在浩<br>金亨來                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 朴在浩<br>金亨來                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 H02M3/00 H02M3/07 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3696 G09G2330/02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/36 G02F1/133.520 G09G3/20.611.A G09G3/20.612.D G09G3/20.612.J H02M3/00.H H02M3/07 H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H093/NC02 2H093/NC34 2H093/NC41 2H093/ND39 2H093/NF13 5C006/AF54 5C006/AF72 5C006/BB11 5C006/BF14 5C006/BF25 5C006/BF26 5C006/BF27 5C006/BF34 5C006/BF43 5C006/BF46 5C006/BF49 5C006/FA47 5C058/AA09 5C058/BA01 5C058/BA04 5C058/BA26 5C058/BB10 5C080/AA10 5C080/BB05 5C080/DD26 5C080/FF09 5C080/JJ02 5C080/JJ03 5C080/JJ05 5H730/AA14 5H730/AS01 5H730/AS04 5H730/BB02 5H730/BB85 5H730/DD04 5H730/DD12 5H730/EE62 5H730/EE65 5H730/FD01 5H730/FF01 5H730/FG02 5H730/FG16 5H730/FG22 2H193/ZA04 2H193/ZF02 2H193/ZQ09 |         |            |

| 代理人(译)         | 大冢康弘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 1020020022323 2002-04-23 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 其他公开文献         | JP4632113B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

### 摘要(译)

提供了一种低功率高效LCD驱动电压发生电路及其方法。 DC-DC转换器210根据具有预定频率的时钟信号CK对输入电压进行升压，并输出第一驱动电压。 压控振荡器270根据控制电压的电平产生具有可变频率的时钟信号，并且控制电压产生器260利用预定参考电压与反映第一驱动电压的反馈电压之间的差。 产生控制电压。 反馈电压VFB比参考电压VREF越低，时钟信号CK的频率越高。 反馈电压低于参考电压意味着第一驱动电压的电平低于预定目标值，这意味着LCD面板消耗大量电流。 因此，通过根据电流消耗量来改变用于DC-DC转换器的升压操作的时钟信号的频率，可以降低功耗并提高升压效率。 [选择图]图4