(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4659885号

(P4659885)

(45) 発行日 平成23年3月30日(2011.3.30)

(24) 登録日 平成23年1月7日(2011.1.7)

(51) Int.Cl.

F 1

G09F 9/30 (2006.01)

G09F 9/30 308Z

G02F 1/1343 (2006.01)

G02F 9/30 338

G02F 1/1362 (2006.01)

G02F 1/1343

G02F 1/1362

請求項の数 13 (全 22 頁)

(21) 出願番号 特願2008-545319 (P2008-545319)

(86) (22) 出願日 平成19年6月8日 (2007.6.8)

(86) 国際出願番号 PCT/JP2007/061613

(87) 国際公開番号 WO2008/062575

(87) 国際公開日 平成20年5月29日 (2008.5.29)

審査請求日 平成20年10月16日 (2008.10.16)

(31) 優先権主張番号 特願2006-314533 (P2006-314533)

(32) 優先日 平成18年11月21日 (2006.11.21)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 110000040

特許業務法人池内・佐藤アンドパートナーズ

(72) 発明者 吉田 昌弘

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

審査官 福島 浩司

最終頁に続く

(54) 【発明の名称】アクティブマトリクス基板、表示パネル、及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の行及び複数の列を有するマトリクス状に複数の画素が設けられるとともに、表示パネルの基板として用いられるアクティブマトリクス基板であって、

前記マトリクス状の行方向に配線される複数の第1の信号線と、

前記第1の信号線と交差するように、前記マトリクス状の列方向に配線される複数の第2の信号線とを備え、

前記複数の画素では、矩形以外の形状に形成された表示パネルの表示領域に対応するよう、前記複数の行のうち、少なくとも1つの行の画素の設置数と他の行の画素の設置数とが相異されるとともに、前記複数の列のうち、少なくとも1つの列の画素の設置数と他の列の画素の設置数とが相異され、

前記複数の第1の信号線のうち、画素の設置数が他の行よりも少ない行に配線された第1の信号線と、前記複数の第2の信号線のうち、画素の設置数が他の列よりも少ない列に配線された第2の信号線とを、前記表示領域以外の箇所で交差させた、

ことを特徴とするアクティブマトリクス基板。

## 【請求項 2】

前記複数の第1の信号線及び前記複数の第2の信号線において、画素の設置数が他の行よりも少ない行に配線された第1の信号線及び画素の設置数が他の列よりも少ない列に配線された第2の信号線の一方の信号線を延伸させて、表示領域以外の箇所で他方の信号線と交差させている請求項1に記載のアクティブマトリクス基板。

**【請求項 3】**

前記複数の第1の信号線及び前記複数の第2の信号線の少なくとも一方の信号線には、入力される信号の信号入力方向が互いに異なる信号線が含まれている請求項1または2に記載のアクティブマトリクス基板。

**【請求項 4】**

前記信号入力方向が互いに異なる信号線が、前記複数の第1の信号線及び前記複数の第2の信号線の一方の信号線に含まれている場合において、前記一方の信号線では、前記信号の入力側が前記表示領域以外の箇所で、前記複数の第1の信号線及び前記複数の第2の信号線の他方の信号線と交差している請求項3に記載のアクティブマトリクス基板。

**【請求項 5】**

前記複数の第1の信号線及び前記複数の第2の信号線において、前記表示領域以外の箇所で交差している交差部で互いに対向する対向面積が、前記表示領域で交差している交差部で互いに対向する対向面積より大きい請求項1～4のいずれか1項に記載のアクティブマトリクス基板。

**【請求項 6】**

前記表示領域以外の箇所で交差している交差部で互いに対向する対向面積が、前記表示領域で交差している交差部で互いに対向する対向面積の2倍以上である請求項5に記載のアクティブマトリクス基板。

**【請求項 7】**

前記複数の第1の信号線及び前記複数の第2の信号線において、前記表示領域以外の箇所で交差している交差部に設けられた絶縁膜の厚さが、前記表示領域で交差している交差部に設けられた絶縁膜の厚さより薄い請求項1～6のいずれか1項に記載のアクティブマトリクス基板。

**【請求項 8】**

前記表示領域以外の箇所で交差している交差部に設けられた絶縁膜の厚さが、前記表示領域で交差している交差部に設けられた絶縁膜の厚さの1/2以下である請求項7に記載のアクティブマトリクス基板。

**【請求項 9】**

前記複数の第1の信号線及び前記複数の第2の信号線が配線される基板本体と、

前記複数の第1の信号線及び前記複数の第2の信号線に対し、信号をそれぞれ入力させる第1及び第2の駆動回路が設置される回路設置部を備えている請求項1～8のいずれか1項に記載のアクティブマトリクス基板。

**【請求項 10】**

請求項1～9のいずれか1項に記載されたアクティブマトリクス基板を備えていることを特徴とする表示パネル。

**【請求項 11】**

外形形状が、矩形以外の形状に形成された表示領域の形状を基に定められている請求項10に記載の表示パネル。

**【請求項 12】**

前記アクティブマトリクス基板に対向して配置される対向基板と、前記アクティブマトリクス基板と前記対向基板との間に設けられた液晶層とを備えている請求項10または11に記載の表示パネル。

**【請求項 13】**

表示部を備えた表示装置であって、

前記表示部には、請求項10～12のいずれか1項に記載の表示パネルが用いられていることを特徴とする表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、複数の画素がマトリクス状に設けられるアクティブマトリクス基板、及びこ

10

20

30

40

50

れを用いた表示パネル並びに表示装置に関する。

【背景技術】

【0002】

近年、液晶表示装置に代表される薄型ディスプレイの普及に伴って、その用途も益々多様化している。例えば、自動車の計器盤（インストルメントパネル）などに液晶表示装置が用いられることがある。つまり、液晶表示装置では、用途の多様化に対応すべく、既存の矩形の表示領域以外に、台形状、円形、あるいは五角形以上の多角形などの異形の表示領域をもつ表示パネルを構成することが望まれており、外形デザインの設計自由度を高めることが要望されている。さらに、液晶表示装置では、表示領域以外の領域を小さくして、表示パネル内の有効表示面積率を高めることも、コスト面や機構面の点からも望まれている。10

【0003】

一方、従来の液晶表示装置には、例えば特開2000-75257号公報または特開2004-212500号公報に記載されているように、橢円形、扇形状、あるいは多角形等の異形の形状に形成された表示領域を備えたものが提案されている。具体的には、これらの従来例では、最初に矩形の液晶表示装置を形成した後、前記矩形の液晶表示装置に対して破断処理や分断処理を施すことにより、異形の表示領域を具備した液晶表示装置を製造していた。

【0004】

また、従来の液晶表示装置には、特開2005-195788号公報に記載されているように、例えば丸形の液晶パネルにおいて、扇形の切り欠き部を形成するとともに、切り欠き部及び外周部に対して、液晶パネルをアクティブ駆動するための2種類の信号線の入力端子をそれぞれ設置することが提案されている。20

【0005】

すなわち、この従来例では、上記切り欠き部の縁に沿って、アクティブマトリクス基板上で同心円状に配線された複数の走査線にそれぞれ接続されて走査信号を入力する複数の走査線用の入力端子を設置していた。また、この従来例では、上記外周部の縁に沿って、アクティブマトリクス基板上で円の中心方向に各々延設された複数のデータ線にそれぞれ接続されてデータ信号を入力する複数のデータ線用の入力端子を設置していた。そして、この従来例では、アクティブマトリクス基板上で複数の走査線及び複数のデータ線を交差させるとともに、交差部に応じてTFT（薄膜トランジスタ；Thin Film Transistor）や画素電極などを含んだ画素を複数設け、丸形の液晶パネルにおいて画素単位のアクティブ駆動を行うことが可能とされていた。30

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上記のような従来の液晶表示装置では、輝度ムラや一走査線分の画素または一データ線分の画素の輝度のみが他の画素の輝度と異なるライン状欠陥などが発生し、表示品位が低下するという問題点があった。

【0007】

具体的にいえば、上記従来の液晶表示装置では、上記のような異形の表示領域を形成した場合、そのアクティブマトリクス基板上の複数の走査線及び複数のデータ線において、画素数が異なる走査線及びデータ線が発生した。このため、従来の液晶表示装置では、複数の走査線及び複数のデータ線において、負荷が異なる走査線及びデータ線が生じて、輝度ムラやライン状欠陥などの発生を抑制することができずに、表示品位の低下を生じることがあった。40

【0008】

また、従来の液晶表示装置において、画素数に応じて、走査線及びデータ線にそれぞれ対する信号の大きさ（電圧値）を変更することにより、複数の走査線及び複数のデータ線での各負荷の不均一を是正することも考えられる。しかしながら、このような信号電圧値50

を変更してアクティブ駆動する場合、画素数の相異に応じて走査線及びデータ線への各信号電圧値を細かく変更したり、表示すべき情報の輝度に従って各データ線への信号電圧値を変更したりすることなどが要求される。このため、信号電圧値を変更して負荷の不均一を是正することは実際上不可能であった。

**【0009】**

上記の課題を鑑み、本発明は、矩形以外の形状の表示領域に用いられるときでも、表示品位が低下するのを容易に防止することができるアクティブマトリクス基板、及びこれを用いた表示パネル並びに表示装置を提供することを目的とする。

**【課題を解決するための手段】**

**【0010】**

上記の目的を達成するために、本発明にかかるアクティブマトリクス基板は、複数の行及び複数の列を有するマトリクス状に複数の画素が設けられるとともに、表示パネルの基板として用いられるアクティブマトリクス基板であって、

前記マトリクス状の行方向に配線される複数の第1の信号線と、

前記第1の信号線と交差するように、前記マトリクス状の列方向に配線される複数の第2の信号線とを備え、

前記複数の画素では、矩形以外の形状に形成された表示パネルの表示領域に対応するよう、前記複数の行のうち、少なくとも1つの行の画素の設置数と他の行の画素の設置数とが相異されるとともに、前記複数の列のうち、少なくとも1つの列の画素の設置数と他の列の画素の設置数とが相異され、

前記複数の第1の信号線のうち、画素の設置数が他の行よりも少ない行に配線された第1の信号線と、前記複数の第2の信号線のうち、画素の設置数が他の列よりも少ない列に配線された第2の信号線とを、前記表示領域以外の箇所で交差させたことを特徴とするものである。

**【0011】**

上記のように構成されたアクティブマトリクス基板では、上記マトリクス状に設けられる複数の画素において、複数の行のうち、少なくとも1つの行の画素の設置数と他の行の画素の設置数とを相異させ、かつ、複数の列のうち、少なくとも1つの列の画素の設置数と他の列の画素の設置数とを相異させることにより、矩形以外の形状に形成された表示パネルの表示領域に対応可能に構成されている。また、複数の第1の信号線のうち、画素の設置数が他の行よりも少ない行に配線された第1の信号線と、複数の第2の信号線のうち、画素の設置数が他の列よりも少ない列に配線された第2の信号線とを、表示領域以外の箇所で交差させている。これにより、画素の設置数が少ない第1及び第2の各信号線において、表示領域以外の箇所での交差部で容量を発生させることができ、第1及び第2の各信号線への信号電圧値を変更することなく、第1及び第2の各信号線において、負荷の不均一を是正することができる。したがって、上記従来例と異なり、矩形以外の形状の表示領域に用いられるときでも、負荷の不均一に起因する輝度ムラ及びライン状欠陥などの発生を抑制することができ、表示品位が低下するのを容易に防止することができる。

**【0012】**

尚、上記画素には、ユーザに視認される有効な上記表示領域に設けられる画素だけでなく、ユーザに視認されない非表示領域（表示領域以外の箇所）に設けられるダミー画素を含ませることができる。

**【0013】**

また、上記アクティブマトリクス基板では、前記複数の第1の信号線及び前記複数の第2の信号線において、画素の設置数が他の行よりも少ない行に配線された第1の信号線及び画素の設置数が他の列よりも少ない列に配線された第2の信号線の一方の信号線を延伸させて、表示領域以外の箇所で他方の信号線と交差させてもよい。

**【0014】**

この場合、アクティブマトリクス基板のコンパクト化を簡単に図ることができる。

**【0015】**

10

20

30

40

50

また、上記アクティブマトリクス基板において、前記複数の第1の信号線及び前記複数の第2の信号線の少なくとも一方の信号線には、入力される信号の信号入力方向が互いに異なる信号線が含まれていることが好ましく、さらに信号入力方向が互いに異なる信号線を交互に配線することが好ましい。

#### 【0016】

この場合、上記信号入力方向を揃えて複数の信号線を配線する場合に比べて、当該信号線の配線作業を簡単に行わせることができる。また、信号線間の電気絶縁耐力を容易に高めることができ、信号電圧のリーク対策も容易なものとすることができます。さらには、信号入力方向が互いに異なる信号線を交互に配線した場合、信号線間の電気絶縁耐力をより容易に高めることができ、信号電圧のリーク対策もより容易なものとすることができます。

10

#### 【0017】

また、上記アクティブマトリクス基板では、前記信号入力方向が互いに異なる信号線が、前記複数の第1の信号線及び前記複数の第2の信号線の一方の信号線に含まれている場合において、前記一方の信号線では、前記信号の入力側が前記表示領域以外の箇所で、前記複数の第1の信号線及び前記複数の第2の信号線の他方の信号線と交差していることが好ましい。

#### 【0018】

この場合、上記信号の非入力側で交差させる場合に比べて、上記一方の信号線の配線作業の簡略化を図りつつ、当該一方の信号線間で信号電圧のリークが生じるのを容易に防ぐことができる。この結果、不良品の発生率が小さい製造簡単なアクティブマトリクス基板を構成することができる。

20

#### 【0019】

また、上記アクティブマトリクス基板では、前記複数の第1の信号線及び前記複数の第2の信号線において、前記表示領域以外の箇所で交差している交差部で互いに対向する対向面積が、前記表示領域で交差している交差部で互いに対向する対向面積より大きくてよい。

#### 【0020】

この場合、表示領域以外の箇所で交差している交差部において、発生する容量を確実に大きくすることができ、第1及び第2の各信号線での負荷の不均一を容易に是正することができる。

30

#### 【0021】

また、上記アクティブマトリクス基板において、前記表示領域以外の箇所で交差している交差部で互いに対向する対向面積が、前記表示領域で交差している交差部で互いに対向する対向面積の2倍以上であってもよい。

#### 【0022】

この場合、第1及び第2の各信号線での負荷の不均一をより容易に是正することができる。

#### 【0023】

また、上記アクティブマトリクス基板では、前記複数の第1の信号線及び前記複数の第2の信号線において、前記表示領域以外の箇所で交差している交差部に設けられた絶縁膜の厚さが、前記表示領域で交差している交差部に設けられた絶縁膜の厚さより薄くてもよい。

40

#### 【0024】

この場合、表示領域以外の箇所で交差している交差部において、発生する容量を確実に大きくすることができ、第1及び第2の各信号線での負荷の不均一を容易に是正することができる。

#### 【0025】

また、上記アクティブマトリクス基板において、前記表示領域以外の箇所で交差している交差部に設けられた絶縁膜の厚さが、前記表示領域で交差している交差部に設けられた絶縁膜の厚さの1/2以下であってもよい。

50

**【 0 0 2 6 】**

この場合、第1及び第2の各信号線での負荷の不均一をより容易に是正することができる。

**【 0 0 2 7 】**

また、上記アクティブマトリクス基板において、前記複数の第1の信号線及び前記複数の第2の信号線が配線される基板本体と、

前記複数の第1の信号線及び前記複数の第2の信号線に対し、信号をそれぞれ入力させる第1及び第2の駆動回路が設置される回路設置部を備えてよい。

**【 0 0 2 8 】**

この場合、複数の第1の信号線及び複数の第2の信号線と第1及び第2の駆動回路との接続作業を簡単に行えるとともに、コンパクトで取扱性に優れたアクティブマトリクス基板を構成することができる。 10

**【 0 0 2 9 】**

また、本発明の表示パネルは、上記いずれかのアクティブマトリクス基板を備えていることを特徴とするものである。

**【 0 0 3 0 】**

上記のように構成された表示パネルでは、矩形以外の形状の表示領域に用いられるときでも、表示品位の低下を容易に防止されたアクティブマトリクス基板が使用されているので、優れた表示性能を有する表示パネルを容易に構成することができる。

**【 0 0 3 1 】**

また、上記表示パネルにおいて、外形形状が、矩形以外の形状に形成された表示領域の形状を基に定められていることが好ましい。 20

**【 0 0 3 2 】**

この場合、表示領域以外の領域を小さくした高い有効表示面積率を有する表示パネルを容易に構成することができる。

**【 0 0 3 3 】**

また、上記表示パネルにおいて、前記アクティブマトリクス基板に対向して配置される対向基板と、前記アクティブマトリクス基板と前記対向基板との間に設けられた液晶層とを備えてよい。 30

**【 0 0 3 4 】**

この場合、優れた表示性能を有する液晶パネルを容易に構成することができる。

**【 0 0 3 5 】**

また、本発明の表示装置は、表示部を備えた表示装置であって、

前記表示部には、上記いずれかの表示パネルが用いられていることを特徴とするものである。

**【 0 0 3 6 】**

上記のように構成された表示装置では、矩形以外の形状の表示領域を有し、かつ、優れた表示性能を有する表示パネルが表示部に用いられているので、矩形以外の形状の表示領域を備えた高性能な表示装置を容易に構成することができる。

**【 発明の効果 】**

40

**【 0 0 3 7 】**

本発明によれば、矩形以外の形状の表示領域に用いられるときでも、表示品位が低下するのを容易に防止することができるアクティブマトリクス基板、及びこれを用いた表示パネル並びに表示装置を提供することが可能となる。

**【 図面の簡単な説明 】****【 0 0 3 8 】**

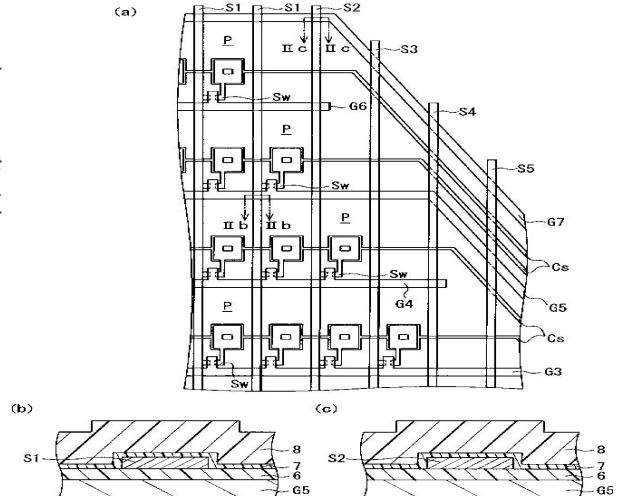

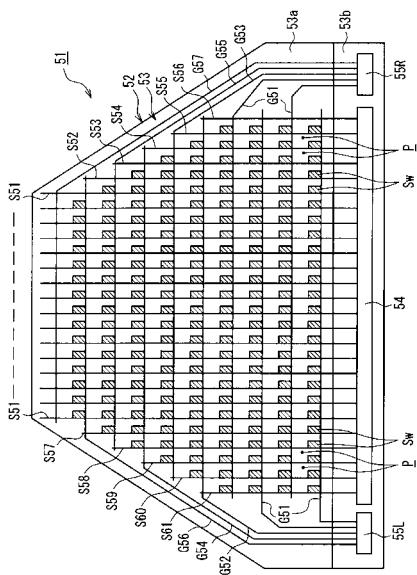

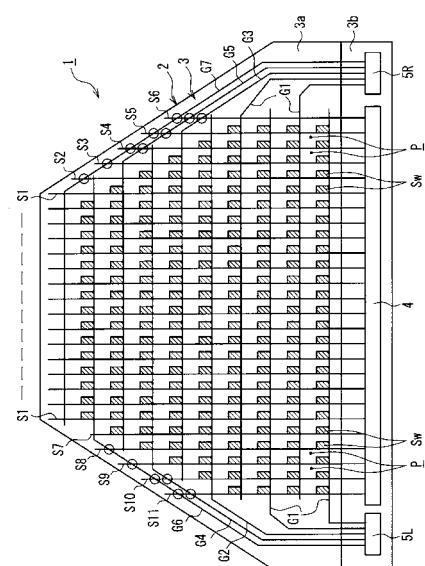

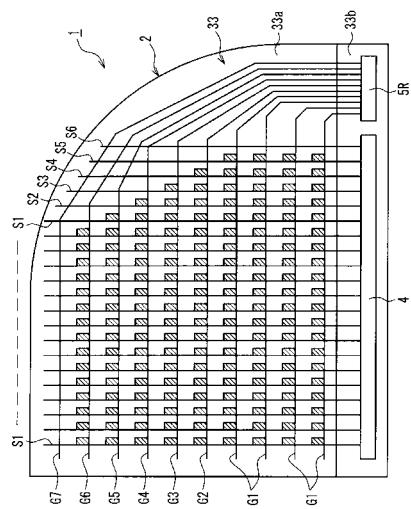

【図1】本発明の第1の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。

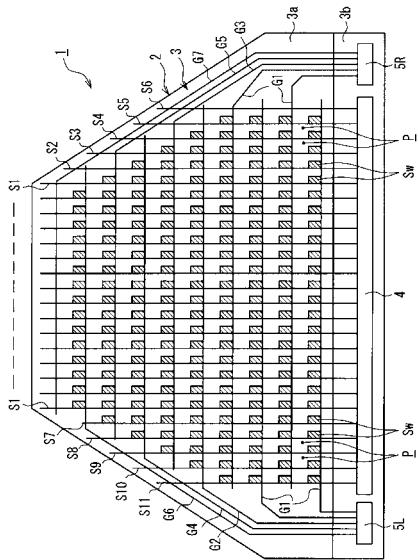

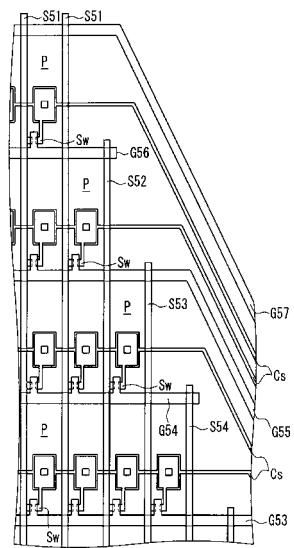

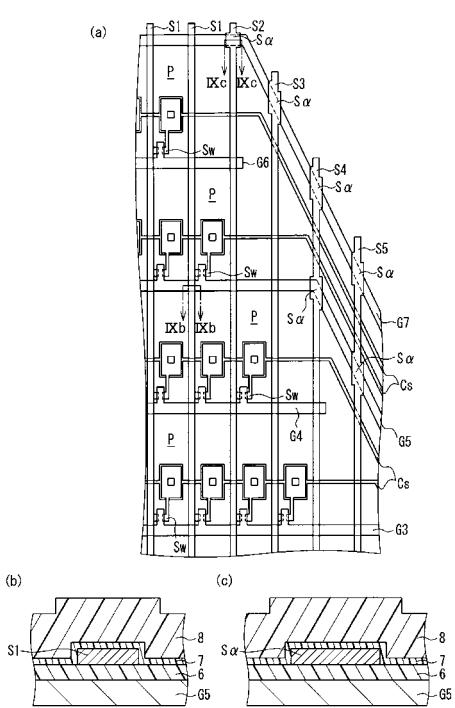

【図2】(a)は図1に示したアクティブマトリクス基板の部分拡大図であり、(b)は(a)のIIb-IIb線断面図であり、(c)は(a)のIIc-IIc線断面図である。 50

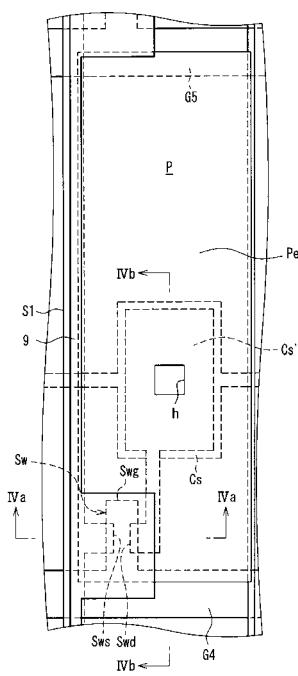

【図3】図1に示した画素の具体的な構成を説明する図である。

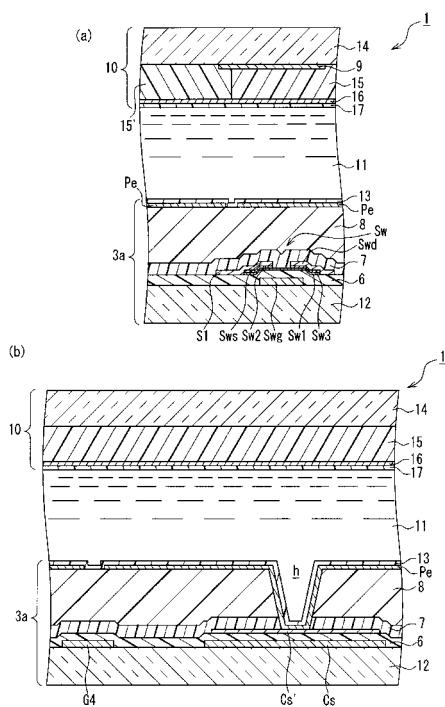

【図4】(a)は図3のIVa-IVa線断面図であり、(b)は図3のIVb-IVb線断面図である。

【図5】比較品1のアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。

【図6】図5に示したアクティブマトリクス基板の部分拡大図である。

【図7】比較品2のアクティブマトリクス基板の部分拡大図である。

【図8】本発明の第2の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。

【図9】(a)は図8に示したアクティブマトリクス基板の部分拡大図であり、(b)は(a)のIXb-IXb線断面図であり、(c)は(a)のIXc-IXc線断面図である。 10

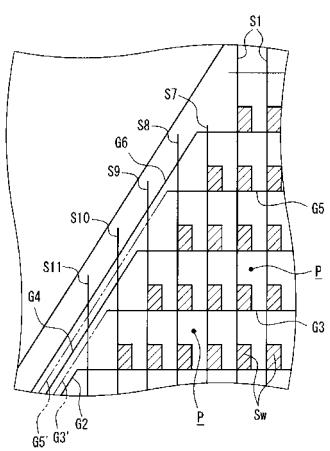

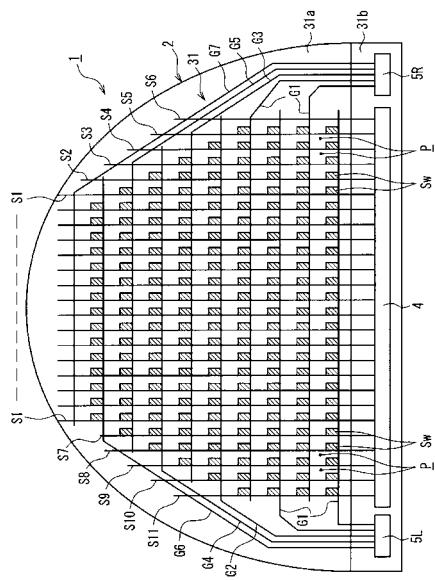

【図10】本発明の第3の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。

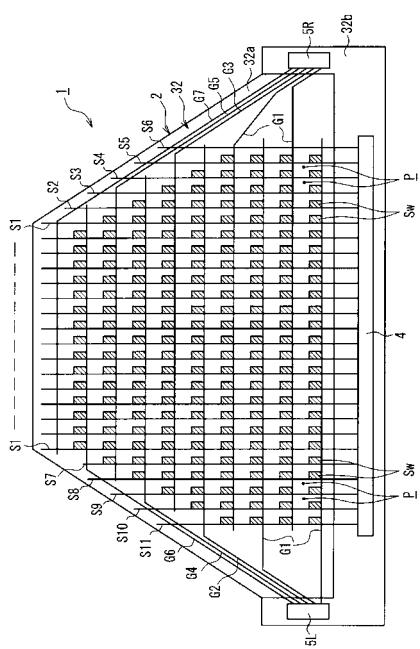

【図11】本発明の第4の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。

【図12】本発明の第5の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。

#### 【発明を実施するための最良の形態】

##### 【0039】

以下、本発明の表示装置の好ましい実施形態について、図面を参照しながら説明する。 20 なお、以下の説明では、本発明を透過型の液晶表示装置に適用した場合を例示して説明する。

##### 【0040】

###### 【第1の実施形態】

図1は、本発明の第1の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。図1において、本実施形態の液晶表示装置1は、台形状の外形形状に形成された表示部としての液晶パネル2と、本発明のアクティブマトリクス基板3とを備えており、液晶表示装置1には、複数の画素Pが複数の行及び複数の列を有するマトリクス状に設けられている。

##### 【0041】

アクティブマトリクス基板3は、図1に例示するように、複数のデータ線S1-S11(以下、“S”にて総称する。)及び複数の走査線G1-G7(以下、“G”にて総称する。)が配線された基板本体3aと、データ線Sに接続されてデータ信号を入力するソースドライバ4及び走査線Gに接続されて走査信号を入力するゲートドライバ5L及び5Rが設置されたドライバ設置部3bとを備えている。走査線G及びデータ線Sは、それぞれマトリクス状の行方向及び列方向に配線される第1及び第2の信号線を構成している。 30

##### 【0042】

基板本体3aは、長方形と台形とを組み合わせた台形状の形状に構成されており、台形状の表示領域に対応可能になっている。一方、ドライバ設置部3bは、第2の駆動回路としてのソースドライバ4及び第1の駆動回路としてのゲートドライバ5L、5Rを設置する回路設置部を構成しており、長方形の形状に構成されている。尚、図1では、基板本体3aとドライバ設置部3bとを明確にするために、それらの境界線を実線(直線)にて示しているが、実際のアクティブマトリクス基板3では、基板本体3aとドライバ設置部3bとは一体的に構成されており、上記境界線は存在しない(後掲の図5、図8、図10～図12においても同様。)。

##### 【0043】

また、基板本体3aでは、図1の上下方向に配線されたデータ線Sと、同図の左右方向に配線された走査線Gとの交差部単位に、複数のスイッチング素子Sw(図に斜線部にて図示)が設けられている。これらの各スイッチング素子Swには、例えば薄膜トランジスタ(TFT)が用いられており、各スイッチング素子Swは、上記複数の画素P毎に設け 40 50

られている。

**【0044】**

すなわち、液晶パネル2では、スイッチング素子Swが設けられ、かつ、隣接する2本のデータ線S及び隣接する2本の走査線Gにて区画された領域が、各画素Pの画素領域を構成している。そして、液晶パネル2では、図1に示すように、長方形と台形とを組み合わせた台形状の表示領域が形成されている。さらに、液晶パネル2では、その外形形状が台形状の表示領域を基に定められている。これにより、液晶パネル2では、表示領域以外の領域を小さくして、そのパネル全面(表示面)での有効表示面積率を容易に高めることができる。

**【0045】**

ここで、図3及び図4を参照して、液晶パネル2の画素Pについて具体的に説明する。

**【0046】**

図3は、図1に示した画素の具体的な構成を説明する図である。図4(a)は図3のIVa-IVa線断面図であり、図4(b)は図3のIVb-IVb線断面図である。

**【0047】**

図3に例示するように、画素Pでは、2本のデータ線S1と走査線G4、G5とで囲まれた画素領域の内部に、スイッチング素子Sw、画素電極Pe、及び補助容量対向電極Cs'が設けられている。また、データ線S1及びスイッチング素子Sw上には、ブラックマトリクス9が配置されている。尚、図3では、図面の簡略化のために、データ線S1に関して図の左側に設けられた画素の画素電極Peの図示は省略している。

**【0048】**

スイッチング素子Swでは、ソース電極SwSがデータ線S1に接続され、ゲート電極Swgが走査線G4に接続されている。また、スイッチング素子Swのドレイン電極Swdは、補助容量配線Csに対向するように設けられた補助容量対向電極Cs'に接続され、補助容量対向電極Cs'は、画素電極Peに接続されている。

**【0049】**

そして、この画素Pでは、走査線G4から走査信号がゲート電極Swgに入力されてスイッチング素子Swがオン状態にされたときに、表示すべき情報の階調に応じたデータ信号(電圧信号)がデータ線S1からソース電極SwSに入力される。その後、データ信号はソース電極SwSからドレイン電極Swd及び補助容量対向電極Cs'を経て画素電極Peに出力され、データ信号の電圧が当該画素Pにて保持される。

**【0050】**

また、図4に示すように、液晶表示装置1は、アクティブマトリクス基板3の基板本体3aと、アクティブマトリクス基板3の基板本体3aに対向して配置される対向基板10と、アクティブマトリクス基板3の基板本体3aと対向基板10との間に設けられた液晶層11とを備えている。

**【0051】**

基板本体3aには、ガラス材または合成樹脂材からなる透明基板12が含まれており、図4(a)に示すように、スイッチング素子Swの近傍では、互いに並設されたデータ線S1及びゲート電極Swgと、これらのデータ線S1及びゲート電極Swgを覆うように形成された絶縁膜6とが、透明基板12上に設けられている。さらに、絶縁膜6の上方には、スイッチング素子Swの半導体層Sw1、コンタクト層Sw2、Sw3、ソース電極SwS及びドレイン電極Swd、保護膜7、層間絶縁膜8、画素電極Pe、及び配向膜13が順次積層されている。

**【0052】**

また、対向基板10には、ガラス材または合成樹脂材からなる透明基板14が含まれており、この透明基板14上にブラックマトリクス9、RGBのいずれかのカラーフィルタ15、及び隣接する画素Pのカラーフィルタ15'が形成されている。また、互いに異なる色のカラーフィルタ15、15'上には、対向(共通)電極16及び配向膜17が順次積層されている。

10

20

30

40

50

**【 0 0 5 3 】**

また、図4（b）に示すように、補助容量対向電極C<sub>s'</sub>の近傍では走査線G<sub>4</sub>及び補助容量配線C<sub>s</sub>が透明基板12上に並設されており、絶縁膜6にて覆われている。補助容量配線C<sub>s</sub>は、絶縁膜6を介して補助容量対向電極C<sub>s'</sub>に対向配置されている。また、補助容量対向電極C<sub>s'</sub>は、コンタクトホールhにて画素電極P<sub>e</sub>に接続されている。さらに、走査線G<sub>4</sub>は、絶縁膜6を介してデータ線S<sub>1</sub>と交差するようになっている。

**【 0 0 5 4 】**

液晶層11には、例えばTNモードの液晶が使用されており、液晶表示装置1では、透明基板12の下側（非表示面側）に配置されたバックライト装置（図示せず）からの光が照射されるようになっている。さらに、透明基板12の下側表面及び透明基板14の液晶層11と逆側の上側表面には、偏光板（図示せず）が貼り付けられている。そして、液晶表示装置1では、液晶層11が表示すべき情報に応じて、画素単位に駆動されることにより、当該液晶層11を通過する光量が制御されて、液晶パネル2の表示面に情報が表示される。

10

**【 0 0 5 5 】**

図1に戻って、基板本体3aでは、上記台形状の表示領域に対応するために、図1の左右方向に平行な複数の行のうち、少なくとも1つの行の画素Pの設置数と他の行の画素Pの設置数とが相異されている。また、基板本体3aでは、図1の上下方向に平行な複数の列のうち、少なくとも1つの列の画素Pの設置数と他の列の画素Pの設置数とが相異されている。

20

**【 0 0 5 6 】**

また、基板本体3aでは、上記のような異形の画素領域を構成するために、データ線Sには、長さが異なるデータ線S<sub>1</sub>～S<sub>11</sub>を設けている。そして、ソースドライバ4が、データ線S<sub>1</sub>～S<sub>11</sub>に対して、データ信号を一方向（図の下方向）から入力させるようになっている。

**【 0 0 5 7 】**

一方、走査線Gには、ソースドライバ4を挟むように設けられたゲートドライバ5L、5Rのいずれかに接続されて、走査信号の信号入力方向が互いに異なる信号線G<sub>1</sub>～G<sub>7</sub>が含まれている。つまり、ゲートドライバ5Lには、図1に示すように、2本の走査線G<sub>1</sub>と、走査線G<sub>2</sub>、G<sub>4</sub>、G<sub>6</sub>とが接続され、ゲートドライバ5Rには、ゲートドライバ5Lに接続された2本の走査線G<sub>1</sub>、G<sub>2</sub>、G<sub>4</sub>、G<sub>6</sub>と交互に配線されるように、2本の走査線G<sub>1</sub>と、走査線G<sub>3</sub>、G<sub>5</sub>、G<sub>7</sub>とが接続されている。そして、ゲートドライバ5Lは、対応する走査線G<sub>1</sub>、G<sub>2</sub>、G<sub>4</sub>、G<sub>6</sub>に対して、図の左側から走査信号を入力させ、ゲートドライバ5Rは、対応する走査線G<sub>1</sub>、G<sub>3</sub>、G<sub>5</sub>、G<sub>7</sub>に対して、図の右側から走査信号を入力させるようになっている。

30

**【 0 0 5 8 】**

以上のように、走査線Gでは、入力される走査信号の信号入力方向が互いに異なる走査線G<sub>1</sub>、G<sub>2</sub>、G<sub>4</sub>、G<sub>6</sub>と走査線G<sub>1</sub>、G<sub>3</sub>、G<sub>5</sub>、G<sub>7</sub>とが含まれているので、信号入力方向を揃えて複数の走査線Gを基板本体3a上に配線する場合に比べて、当該走査線Gの配線作業を簡単に行わせることができる。さらに、走査線G間の電気絶縁耐力を容易に高めることができ、走査信号（電圧）のリーク対策も容易なものとすることができる。しかも、走査線G<sub>1</sub>、G<sub>2</sub>、G<sub>4</sub>、G<sub>6</sub>と走査線G<sub>1</sub>、G<sub>3</sub>、G<sub>5</sub>、G<sub>7</sub>とが交互に配線されているので、上記電気絶縁耐力及びリーク対策をより容易に高めることができる。

40

**【 0 0 5 9 】**

尚、上記の説明以外に、データ線Sについて、走査線Gと同様に、データ信号の信号入力方向が互いに異なる二つのデータ線群に分けて、二つのソースドライバからそれぞれデータ信号を入力させることもできる。

**【 0 0 6 0 】**

また、データ線S<sub>6</sub>は、ダミーデータ線であり、最外周、つまり図1の右端列の各画素Pでの寄生容量が他の画素Pの寄生容量と同様量になるように、基板本体3a上に設けら

50

れている。また、このデータ線 S 6 では、4 本の走査線 G 1 との各交差部の近傍に、図示を省略したスイッチング素子が接続されており、情報表示に寄与しないダミー画素が構成されている。そして、右端列の各画素 P において、データ線 S と画素電極 P e 間の寄生容量の相異や開口率の相異に起因して輝度ムラが発生するのを防いでいる。

#### 【 0 0 6 1 】

同様に、走査線 G 7 は、ダミー走査線であり、最外周、つまり図 1 の上端行の各画素 P での寄生容量が他の画素 P の寄生容量と同様量になるように、基板本体 3 a 上に設けられている。また、この走査線 G 7 では、16 本のデータ線 S 1 との各交差部の近傍に、図示を省略したスイッチング素子が接続されており、情報表示に寄与しないダミー画素が構成されている。そして、上端行の各画素 P において、走査線 G と画素電極 P e 間の寄生容量の相異や開口率の相異に起因して輝度ムラが発生するのを防いでいる。10

#### 【 0 0 6 2 】

尚、上記の説明では、ダミーデータ線 S 6 及びダミー走査線 G 7 の各々にスイッチング素子を接続してダミー画素を構成した場合について説明したが、本実施形態はこれに限定されるものではなく、ダミーデータ線 S 6 やダミー走査線 G 7 にスイッチング素子（さらには、画素電極）を接続しない構成でもよい。すなわち、ダミー画素を構成することなく、ダミーデータ線 S 6 やダミー走査線 G 7 だけを設けることにより、上記輝度ムラの発生を防止することもできる。

#### 【 0 0 6 3 】

さらに、基板本体 3 a では、データ線 S 及び走査線 G のうち、画素 P の設置数が少ない列に配線されたデータ線 S を適宜延伸させて、表示領域の外側で画素 P の設置数が少ない行に配線された走査線 G と交差させている。これにより、基板本体 3 a では、画素 P の設置数が少ない行及び列にそれぞれ配線された走査線 G とデータ線 S との交差部の数を増加させて、上記台形状の表示領域に応じて、複数の行及び複数の列の各々において画素 P の設置数を異ならせたときでも、輝度ムラ及びライン状欠陥などの発生を抑制できるよう構成されている（詳細は後述）。20

#### 【 0 0 6 4 】

具体的にいえば、基板本体 3 a では、データ線 S 2、S 3 が表示領域の外側で走査線 G 7 と交差するように延ばされている。また、データ線 S 4、S 5 が表示領域の外側で走査線 G 5、G 7 と各々交差するように延ばされ、データ線 S 6 が表示領域の外側で走査線 G 3、G 5、G 7 と交差するように延ばされている。また、データ線 S 8、S 9 が表示領域の外側で走査線 G 6 と交差するように延ばされ、データ線 S 10、S 11 が表示領域の外側で走査線 G 4、G 6 と各々交差するように延ばされている。30

#### 【 0 0 6 5 】

また、上記のように、画素 P の設置数が少ない行及び列にそれぞれ配線された走査線 G 及びデータ線 S を交差させているので、これらの走査線 G とデータ線 S との交差部には容量が発生して、負荷を大きくすることができます。

#### 【 0 0 6 6 】

すなわち、図 2 ( a ) に例示するように、データ線 S 2 は、走査線 G 7 と交差するように、図の上側に向かって真直ぐに延ばされている。このデータ線 S 2 と走査線 G 7 との交差部では、表示領域の内側でのデータ線 S と走査線 G との交差部と同様に、データ線 S 2 及び走査線 G 7 が、絶縁膜 6 を介して互いに対向した状態で交差する（図 2 ( b ) 及び ( c ) を参照。）。これにより、データ線 S 2 と走査線 G 7 との交差部では、これらのデータ線 S 2 と走査線 G 7 との間の絶縁膜 6 に容量が発生する。40

#### 【 0 0 6 7 】

言い換えれば、データ線 S 2 と走査線 G 7 との交差部では、表示領域の内側の交差部（例えば、図 2 ( c ) に示すデータ線 S 1 と走査線 G 5 との交差部）と同一の容量を発生させることができとなり、データ線 S 2 及び走査線 G 7 の各負荷を大きくすることができる。この結果、基板本体 3 a では、データ線 S 及び走査線 G の各々において、負荷の不均一を是正することができる。50

## 【0068】

ここで、図5～図6も参照して、本実施形態品と比較品1との対比を行うことにより、本実施形態品において、負荷の不均一が是正されていることについて具体的に説明する。

## 【0069】

まず、図5及び図6を用いて、比較品1について説明する。この比較品1の液晶表示装置51は従来相当品であり、図5に示すように、比較品1の液晶パネル52には、基板本体53a及びドライバ設置部53bを備えたアクティブマトリクス基板53が使用されている。また、アクティブマトリクス基板53では、本実施形態品と同一の台形状の表示領域に対応するように、データ線S51～S61及び走査線G51～G57が配線され、複数の画素Pが設けられている。そして、液晶表示装置51では、本実施形態品と同様に、ソースドライバ54からのデータ信号がデータ線S51～S61に入力され、ゲートドライバ55L、55Rからの走査信号が対応する走査線G51～G57に入力されることで、情報の表示が行われるようになっている。10

## 【0070】

また、比較品1の基板本体53aでは、本実施形態品と異なり、表示領域の外側で、画素Pの設置数が少ない行及び列にそれぞれ配線された走査線G52～G57とデータ線S52～S61とは交差されていない。具体的には、図6に例示するように、比較品1では、データ線S52は、図2に示した本実施形態品と異なり、走査線G57に向かって真直ぐに延ばされておらずに、表示領域の内側の画素Pの画素領域を構成するように、走査線G56と交差した箇所で止められている。20

## 【0071】

以上のように構成された比較品1では、データ線S51～S61と走査線G51～G57との交差部の数は、次の表1に示すものとなる。

## 【0072】

## 【表1】

| データ線    | 交差部の数 | 走査線    | 交差部の数 |

|---------|-------|--------|-------|

| データ線S51 | 10ヶ所  | 走査線G51 | 26ヶ所  |

| データ線S52 | 9ヶ所   | 走査線G52 | 26ヶ所  |

| データ線S53 | 8ヶ所   | 走査線G53 | 24ヶ所  |

| データ線S54 | 7ヶ所   | 走査線G54 | 22ヶ所  |

| データ線S55 | 6ヶ所   | 走査線G55 | 20ヶ所  |

| データ線S56 | 5ヶ所   | 走査線G56 | 18ヶ所  |

| データ線S57 | 9ヶ所   | 走査線G57 | 16ヶ所  |

| データ線S58 | 8ヶ所   |        |       |

| データ線S59 | 7ヶ所   |        |       |

| データ線S60 | 6ヶ所   |        |       |

| データ線S61 | 5ヶ所   |        |       |

## 【0073】

ここで、上記の各交差部で発生する容量を1pFと仮定すると、例えばデータ線S51とデータ線S56とでは、5pF(=10-5)の容量差が発生する。また、走査線G51と走査線G57とでは、10pF(=26-16)の容量差が発生する。このようにデータ線S51～S61及び走査線G51～G57では、交差部の数(つまり、画素数)の相違により、容量差が各々生じており、負荷もまた各々不均一となっている。

## 【0074】

このため、比較品1では、データ線S51～S61及び走査線G51～G57に対し、それぞれ同じ電圧値のデータ信号及び走査信号をそれぞれ入力させた場合、データ線S51～S61及び走査線G51～G57の各々において、負荷の不均一に起因して、対応す40

10

20

30

40

50

るデータ信号または走査信号の一定時間中に到達する電位に差が発生する。この結果、比較品1では、輝度ムラやライン状欠陥が発生して、表示品位の低下を招く。

#### 【0075】

これに対して、本実施形態品では、上述のように、画素Pの設置数が少ない行及び列にそれぞれ配線された走査線Gとデータ線Sとを交差させているので、データ線S1～S11と走査線G1～G7との交差部の数は、次の表2に示すものとなる。

#### 【0076】

【表2】

| データ線    | 交差部の数 | 走査線   | 交差部の数 |

|---------|-------|-------|-------|

| データ線S1  | 10ヶ所  | 走査線G1 | 26ヶ所  |

| データ線S2  | 10ヶ所  | 走査線G2 | 26ヶ所  |

| データ線S3  | 9ヶ所   | 走査線G3 | 25ヶ所  |

| データ線S4  | 9ヶ所   | 走査線G4 | 24ヶ所  |

| データ線S5  | 8ヶ所   | 走査線G5 | 23ヶ所  |

| データ線S6  | 8ヶ所   | 走査線G6 | 22ヶ所  |

| データ線S7  | 9ヶ所   | 走査線G7 | 21ヶ所  |

| データ線S8  | 9ヶ所   |       |       |

| データ線S9  | 8ヶ所   |       |       |

| データ線S10 | 8ヶ所   |       |       |

| データ線S11 | 7ヶ所   |       |       |

10

20

#### 【0077】

ここで、本実施形態品において、比較品1と同様に、上記の各交差部で発生する容量を1pFと仮定すると、例えばデータ線S1とデータ線S6との容量差は、2pF(=10-8)となり、比較品1での5pFに比べて、容量差が小さくされている。同様に、走査線G1と走査線G7との容量差は、5pF(=26-21)となり、比較品1での10pFに比べて、容量差が小さくされている。

#### 【0078】

30

このように、本実施形態品では、比較品1に比べ、データ線S1～S11及び走査線G1～G7の各々において、容量差を小さくすることが可能となり、負荷の不均一を是正することができる。この結果、本実施形態品では、輝度ムラ及びライン状欠陥の発生を抑制することができ、表示品位の低下が生じるのを防ぐことができる。

#### 【0079】

また、本実施形態品では、上述したように、データ線S及び走査線Gのうち、データ線Sだけを適宜延伸させて、表示領域の外側で走査線Gと交差させることにより、負荷の不均一を是正して表示品位の改善が図られている。すなわち、本実施形態品では、走査線Gは、走査信号の信号入力方向が交互となるように配線されるとともに、走査信号が入力されない非入力側を延ばすことなく、データ線Sと適宜交差するようになっている。これにより、走査線Gでは、その配線作業の簡単化を行うことができ、アクティブマトリクス基板3を効率よく製造することができる。

40

#### 【0080】

具体的にいえば、例えば図7に二点鎖線にて示すように、走査線G3がデータ線S11と交差するように、当該走査線G3の非入力側を延ばしたり、走査線G5がデータ線S9～S11と交差するように、当該走査線G5の非入力側を延ばしたりすることにより、走査線G1などに対する走査線G3、G5の各負荷の不均一をさらに是正することができる。

#### 【0081】

しかしながら、図7に示したように、走査線G3、G5の各非入力側を延伸させた場合

50

、これらの非入力側の配線部分は、走査線 G 2、G 4 間及び走査線 G 4、G 6 間に設ける必要がある。このため、非入力側の配線部分と対応する走査線 G 2、G 4、G 6 との間で走査信号のリークの発生などが生じ易くなる。

#### 【 0 0 8 2 】

これに対して、本実施形態では、走査線 G 3、G 5 の各非入力側を延伸させていないので、走査線 G 2 ~ G 6 の配線作業を簡単に行うことができ、さらには隣接する 2 本の走査線 G 間で走査信号のリークが生じるのを容易に防ぐことができる。この結果、不良品の発生率が小さい製造簡単なアクティブマトリクス基板 3 を構成することができる。

#### 【 0 0 8 3 】

以上のように構成された本実施形態のアクティブマトリクス基板 3 では、複数の画素 P において、複数の行のうち、少なくとも 1 つの行の画素 P の設置数と他の行の画素 P の設置数とを相異させ、かつ、複数の列のうち、少なくとも 1 つの列の画素 P の設置数と他の列の画素 P の設置数とを相異させることにより、台形状に形成された液晶パネル（表示パネル）2 の表示領域に対応可能に構成されている。10

#### 【 0 0 8 4 】

また、本実施形態のアクティブマトリクス基板 3 では、複数の走査線（第 1 の信号線）G のうち、画素 P の設置数が他の行よりも少ない行に配線された走査線 G 3 ~ G 7 と、複数のデータ線（第 2 の信号線）S のうち、画素 P の設置数が他の列よりも少ない列に配線されたデータ線 S 2 ~ S 6、S 8 ~ S 11 とを、表示領域の外側で交差させている。これにより、本実施形態のアクティブマトリクス基板 3 では、画素 P の設置数が少ない走査線 G 3 ~ G 7 とデータ線 S 2 ~ S 6、S 8 ~ S 11 との各々において、表示領域の外側での交差部で容量を発生させることができる。20

#### 【 0 0 8 5 】

この結果、本実施形態のアクティブマトリクス基板 3 では、データ線 S 及び走査線 G への各信号電圧値を変更することなく、データ線 S 及び走査線 G の各信号線において、負荷の不均一を是正することができる。したがって、本実施形態のアクティブマトリクス基板 3 では、上記従来例と異なり、台形状の表示領域に用いられるときでも、負荷の不均一に起因する輝度ムラ及びライン状欠陥などの発生を抑制することができ、表示品位が低下するのを容易に防止することができる。

#### 【 0 0 8 6 】

また、本実施形態の液晶パネル 2 では、台形状の表示領域に用いられるときでも、表示品位の低下を容易に防止されたアクティブマトリクス基板 3 が使用されているので、優れた表示性能を有する液晶パネルを容易に構成することができる。30

#### 【 0 0 8 7 】

また、本実施形態の液晶表示装置 1 では、台形状の表示領域を有し、かつ、優れた表示性能を有する液晶パネル 2 が表示部に用いられているので、矩形以外の形状の表示領域を備えた高性能な液晶表示装置を容易に構成することができる。

#### 【 0 0 8 8 】

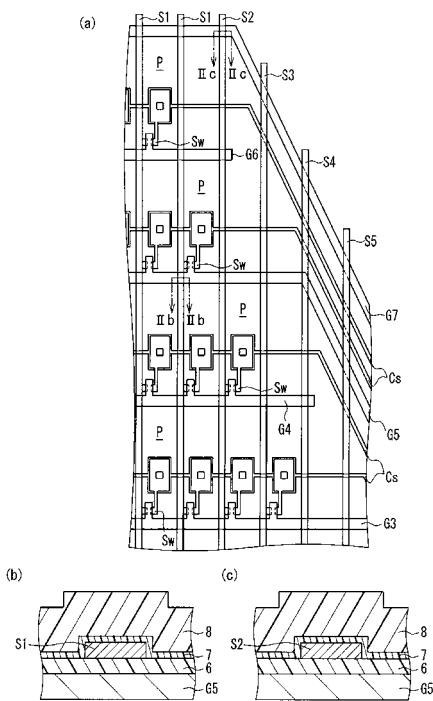

##### [ 第 2 の実施形態 ]

図 8 は、本発明の第 2 の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。図 9 ( a ) は図 8 に示したアクティブマトリクス基板の部分拡大図であり、図 9 ( b ) は図 9 ( a ) の IXb - IXb 線断面図であり、図 9 ( c ) は図 9 ( a ) の IXc - IXc 線断面図である。図において、本実施形態と上記第 1 の実施形態との主な相違点は、複数のデータ線及び複数の走査線において、表示領域の外側で交差している交差部で互いに対向する対向面積が、表示領域で交差している交差部で互いに対向する対向面積より大きくした点である。なお、上記第 1 の実施形態と共に通する要素については、同じ符号を付して、その重複した説明を省略する。40

#### 【 0 0 8 9 】

すなわち、図 8 において、本実施形態のアクティブマトリクス基板 3 では、同図にて示した表示領域の外側の交差部において、互いに対向するデータ線 S 及び走査線 G の対50

向面積が表示領域の内側の交差部での対向面積より大きくなるように構成されている。

#### 【0090】

具体的にいえば、図9(a)に例示するように、データ線S2、S3では、走査線G7と交差する交差部において、他の部分よりも大きく構成した拡大部S<sub>1</sub>が設けられている。また、データ線S4、S5では、各々走査線G5、G7と交差する交差部において、他の部分よりも大きく構成した拡大部S<sub>2</sub>が設けられている。

#### 【0091】

また、拡大部S<sub>1</sub>では、交差部において走査線Gと対向するデータ線Sの対向面積が大きく、例えば2倍となるように、拡大部S<sub>2</sub>は、他の部分よりも大きい形状に構成されている。すなわち、図9(b)に例示する表示領域の内側でのデータ線S1に比べて、拡大部S<sub>2</sub>は、図9(c)に示すように、図の左右方向の寸法が2倍とされて、走査線G5と対向するデータ線S1の対向面積を2倍としている。これにより、データ線S1と走査線G7とでは、これらのデータ線S1と走査線G7との間の絶縁膜6に発生する容量を2倍とすることができる。

10

#### 【0092】

以上の構成により、本実施形態のアクティブマトリクス基板3では、第1の実施形態に比べて、表示領域の外側で交差している交差部において、発生する容量を確実に大きくすることができ、データ線S及び走査線Gの各信号線において、負荷の不均一を容易に是正することができる。

20

#### 【0093】

具体的にいえば、第1の実施形態と同様に、上記の各交差部で発生する容量を1pFと仮定すると、データ線S1～S11及び走査線G1～G7の各信号線において、交差部で生じる容量の和は、次の表3に示すものとなる。

#### 【0094】

#### 【表3】

| データ線    | 交差部での容量和 | 走査線   | 交差部での容量和 |

|---------|----------|-------|----------|

| データ線S1  | 10pF     | 走査線G1 | 26pF     |

| データ線S2  | 11pF     | 走査線G2 | 26pF     |

| データ線S3  | 10pF     | 走査線G3 | 26pF     |

| データ線S4  | 11pF     | 走査線G4 | 26pF     |

| データ線S5  | 10pF     | 走査線G5 | 26pF     |

| データ線S6  | 11pF     | 走査線G6 | 26pF     |

| データ線S7  | 9pF      | 走査線G7 | 26pF     |

| データ線S8  | 10pF     |       |          |

| データ線S9  | 9pF      |       |          |

| データ線S10 | 10pF     |       |          |

| データ線S11 | 9pF      |       |          |

30

#### 【0095】

表3より明らかなように、本実施形態のアクティブマトリクス基板3では、データ線Sでの容量分布、つまりデータ線S1～S11での最大の容量差は、2pF(=11-9)であり、表2に示した第1の実施形態での3pF(=10-7)に比べて、容量差が小さくなっている。また、全ての走査線G1～G7において、26pFとされているため、走査線Gでの容量分布は、0pFであり、第1の実施形態での5pF(=26-21)の容量差が解消されている。

40

#### 【0096】

以上のように、本実施形態のアクティブマトリクス基板3では、第1の実施形態に比べて、データ線S及び走査線Gの各信号線での負荷の不均一がより是正されており、輝度ム

50

ラ及びライン状欠陥の発生を確実に抑制して、表示品位の低下が生じるのを確実に防ぐことができる。

#### 【0097】

尚、上記の説明では、データ線Sに拡大部S<sub>1</sub>を設けて、走査線Gに対する対向面積を2倍にした場合について説明したが、データ線S及び走査線Gの少なくとも一方に拡大部を設けて、表示領域の外側の交差部で互いに対向するデータ線S及び走査線Gの対向面積を大きくする構成でもよい。

#### 【0098】

また、上記拡大部によって対向面積を2倍以上に構成してもよい。このように構成した場合には、各画素Pに含まれるスイッチング素子S<sub>W</sub>などでの容量差を小さくすることができ、データ線S及び走査線Gの各信号線での負荷の不均一をより容易に是正することができる。

10

#### 【0099】

また、上記の説明以外に、データ線S及び走査線Gの各信号線において、表示領域の外側で交差している交差部に設けられた絶縁膜6の厚さを、表示領域で交差している交差部に設けられた絶縁膜6の厚さより薄くする構成でもよい。すなわち、図9(b)に示した絶縁膜6の厚さが、例えば $4000 \times 10^{-10}$ (m)であるとき、図9(c)に示した絶縁膜6の厚さを $2000 \times 10^{-10}$ (m)としてもよい。

#### 【0100】

以上のように、表示領域で交差している交差部に設けられた絶縁膜6の厚さに対して、表示領域の外側で交差している交差部に設けられた絶縁膜6の厚さを1/2とすることにより、データ線Sと走査線Gとの間の絶縁膜6に発生する容量を2倍にすることができる。

20

#### 【0101】

また、表示領域で交差している交差部に設けられた絶縁膜6の厚さに対して、表示領域の外側で交差している交差部に設けられた絶縁膜6の厚さを1/2以下とした場合には、上記拡大部にて対向面積を2倍以上とした場合と同様に、各画素Pに含まれるスイッチング素子S<sub>W</sub>などでの容量差を小さくすることができ、データ線S及び走査線Gの各信号線での負荷の不均一をより容易に是正することができる。

#### 【0102】

30

さらに、表示領域の外側で交差している交差部でのデータ線S及び走査線Gの対向面積及び絶縁膜6の厚さの双方を変更することにより、データ線S及び走査線Gの各信号線での負荷の不均一を是正することもできる。また、例えばデータ線Sと走査線Gとの間の絶縁膜が、絶縁膜6以外の絶縁膜を含んだ多層構造に構成されている場合には、表示領域の内側の交差部での絶縁膜の層数よりも、表示領域の外側の交差部での絶縁膜の層数を小さくすることにより、データ線S及び走査線Gの各信号線での負荷の不均一を是正することもできる。

#### 【0103】

##### [第3の実施形態]

図10は、本発明の第3の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。図において、本実施形態と上記第1の実施形態との主な相違点は、台形状に代えて、半円状の外形形状を有する液晶パネルを構成した点である。なお、上記第1の実施形態と共通する要素については、同じ符号を付して、その重複した説明を省略する。

40

#### 【0104】

すなわち、図10に示すように、本実施形態の液晶表示装置1には、半円状の外形形状に形成された液晶パネル2と、アクティブマトリクス基板31とが設けられており、複数の画素Pが、半円状の表示領域に対応するように、設置されている。

#### 【0105】

また、アクティブマトリクス基板31には、複数のデータ線S<sub>1</sub>～S<sub>11</sub>及び複数の走

50

査線 G 1 ~ G 7 が配線された基板本体 3 1 a と、データ線 S に接続されてデータ信号を入力するソースドライバ 4 及び走査線 G に接続されて走査信号を入力するゲートドライバ 5 L 及び 5 R が設置されたドライバ設置部 3 1 b とを備えている。

#### 【 0 1 0 6 】

また、アクティブマトリクス基板 3 1 では、画素 P の設置数が他の行よりも少ない行に配線された走査線 G 3 ~ G 7 と、画素 P の設置数が他の列よりも少ない列に配線されたデータ線 S 2 ~ S 6 、 S 8 ~ S 11 とを、表示領域の外側で交差させている。

#### 【 0 1 0 7 】

以上の構成により、本実施形態では、第 1 の実施形態と同様な作用効果を奏することができる。つまり、本実施形態のアクティブマトリクス基板 3 1 では、半円状の表示領域に用いられるときでも、負荷の不均一に起因する輝度ムラ及びライン状欠陥などの発生を抑制することができ、表示品位が低下するのを容易に防止することができる。したがって、半円状の表示領域を有し、かつ、優れた表示性能を有する液晶パネル 2 及び液晶表示装置 1 を容易に構成することができる。

#### 【 0 1 0 8 】

尚、上記の説明以外に、第 2 の実施形態と同様に、表示領域の外側で交差している交差部でのデータ線 S 及び走査線 G の対向面積及び絶縁膜 6 の厚さのいずれか一方を変更して、データ線 S 及び走査線 G の各信号線での負荷の不均一をより是正することもできる（後掲の各実施形態においても、同様。）。

#### 【 0 1 0 9 】

##### 〔 第 4 の実施形態 〕

図 1 1 は、本発明の第 4 の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。図において、本実施形態と上記第 1 の実施形態との主な相違点は、ドライバ設置部の形状を凹状に変更して、上記 2 つのゲートドライバを対向するように設置した点である。なお、上記第 1 の実施形態と共に通する要素については、同じ符号を付して、その重複した説明を省略する。

#### 【 0 1 1 0 】

すなわち、図 1 1 に示すように、本実施形態のアクティブマトリクス基板 3 2 には、複数のデータ線 S 1 ~ S 11 及び複数の走査線 G 1 ~ G 7 が配線された基板本体 3 2 a と、データ線 S に接続されてデータ信号を入力するソースドライバ 4 及び走査線 G に接続されて走査信号を入力するゲートドライバ 5 L 及び 5 R が設置されたドライバ設置部 3 2 b とを備えている。ドライバ設置部 3 2 b は、液晶パネル 2 の外形形状に合わせて、凹状に構成されており、ゲートドライバ 5 L 及び 5 R が互いに対向するように設けられている。これにより、基板本体 3 2 a 上で複数の走査線 G 1 ~ G 7 を容易に配線することができるとともに、液晶パネル 2 の外形寸法が不必要に大きくなるのを極力防ぐことができる。

#### 【 0 1 1 1 】

また、アクティブマトリクス基板 3 2 では、画素 P の設置数が他の行よりも少ない行に配線された走査線 G 3 ~ G 7 と、画素 P の設置数が他の列よりも少ない列に配線されたデータ線 S 2 ~ S 6 、 S 8 ~ S 11 とを、表示領域の外側で交差させている。

#### 【 0 1 1 2 】

以上の構成により、本実施形態では、第 1 の実施形態と同様な作用効果を奏することができる。

#### 【 0 1 1 3 】

##### 〔 第 5 の実施形態 〕

図 1 2 は、本発明の第 5 の実施形態にかかるアクティブマトリクス基板及びこれを用いた液晶表示装置の要部構成を示す平面図である。図において、本実施形態と上記第 1 の実施形態との主な相違点は、台形状に代えて、1 / 4 円状の外形形状を有する液晶パネルを構成した点である。なお、上記第 1 の実施形態と共に通する要素については、同じ符号を付して、その重複した説明を省略する。

#### 【 0 1 1 4 】

10

20

30

40

50

すなわち、図12に示すように、本実施形態の液晶表示装置1では、1/4円状の外形形状に形成された液晶パネル2と、アクティブマトリクス基板31とが設けられており、複数の画素Pが、1/4円状の表示領域に対応するように、設置されている。

#### 【0115】

また、アクティブマトリクス基板33は、複数のデータ線S1～S11及び複数の走査線G1～G7が配線された基板本体33aを備えている。また、本実施形態のアクティブマトリクス基板33では、液晶パネル2(液晶表示装置1)の外形形状を極力大きくしないように、例えば走査線Gに対して、走査信号を入力するゲートドライバ5Rのみがドライバ設置部33bに設置されている。つまり、図に示すように、ドライバ設置部33bには、データ線Sに接続されてデータ信号を入力するソースドライバ4と、走査線Gに接続されて走査信号を入力するゲートドライバ5Rとが設置されている。そして、ゲートドライバ5Rは、走査線Gに対して、走査信号を図の右側から入力させるようになっている。10

#### 【0116】

また、アクティブマトリクス基板33では、画素Pの設置数が他の行よりも少ない行に配線された走査線G2～G7と、画素Pの設置数が他の列よりも少ない列に配線されたデータ線S2～S6とを、表示領域の外側で交差させている。

#### 【0117】

以上の構成により、本実施形態では、第1の実施形態と同様な作用効果を奏することができる。つまり、本実施形態のアクティブマトリクス基板33では、1/4円状の表示領域に用いられるときでも、負荷の不均一に起因する輝度ムラ及びライン状欠陥などの発生を抑制することができ、表示品位が低下するのを容易に防止することができる。したがって、1/4円状の表示領域を有し、かつ、優れた表示性能を有する液晶パネル2及び液晶表示装置1を容易に構成することができる。20

#### 【0118】

尚、上記の実施形態はすべて例示であって制限的なものではない。本発明の技術的範囲は特許請求の範囲によって規定され、そこに記載された構成と均等の範囲内のすべての変更も本発明の技術的範囲に含まれる。

#### 【0119】

例えば、上記の説明では、本発明を透過型の液晶表示装置に適用した場合について説明したが、本発明の表示装置はアクティブマトリクス基板を具備した表示パネルを表示部に使用したものであれば何等限定されない。具体的には、本発明の表示パネル及び表示装置は、半透過型や反射型の液晶パネルあるいは有機EL(Electronic Luminescence)素子、無機EL素子、電界放出ディスプレイ(Field Emission Display)等のアクティブマトリクス基板を用いた各種表示パネル及びこれを表示部に用いた表示装置に適用することができる。30

#### 【0120】

また、上記の説明では、走査線(第1の信号線)G及びデータ線(第2の信号線)Sのうち、データ線Sだけを延伸させた場合について説明したが、本発明のアクティブマトリクス基板は複数の第1の信号線のうち、画素の設置数が他の行よりも少ない行に配線された第1の信号線と、複数の第2の信号線のうち、画素の設置数が他の列よりも少ない列に配線された第2の信号線との少なくとも一方の信号線を延伸させて、表示領域以外の箇所で他方の信号線と交差させたものであればよい。40

#### 【0121】

但し、上記実施形態のように、第1及び第2の信号線の一方の信号線だけを延伸させて、他方の信号線と表示領域以外の箇所で交差させる場合の方が、アクティブマトリクス基板のコンパクト化を簡単に図ることができる点で好ましい。

#### 【0122】

また、上記の説明では、ダミーデータ線S6を延伸させて交差させたり、データ線S1をダミー走査線G7に交差させたりした構成について説明したが、本発明のアクティブマトリクス基板はこれに限定されるものではなく、ユーザに視認される有効な表示領域に設50

けられる画素用の第1及び第2の信号線だけを表示領域以外の箇所で交差させる構成でもよい。

#### 【0123】

また、上記の説明では、画素の設置数が少ない第1及び第2の信号線を表示領域の外側で交差させた場合について説明したが、本発明のアクティブマトリクス基板は表示領域以外の箇所で画素の設置数が少ない第1及び第2の信号線を交差させたものであればよい。

#### 【0124】

具体的には、例えば表示領域の中心部に円形の非表示領域が形成されているドーナツ状の表示パネルに適用する場合では、表示領域内側の円形の非表示領域に対応する箇所で、画素の設置数が少ない第1及び第2の信号線を交差させねばよい。このように、本発明のアクティブマトリクス基板は、ドーナツ状や額縁状などの表示領域の内部に非表示領域が設けられた異形の表示パネルに対しても、信号電圧の大きさを変更したり、遮光部材の設置を省略したりすることなく、第1及び第2の各信号線の負荷の不均一を是正して、高品位な表示パネルを容易に構成することができる。

#### 【0125】

また、上記の説明では、マトリクス状の行方向に配線される第1の信号線として走査線を用いるとともに、マトリクス状の列方向に配線される第2の信号線としてデータ線を用いた場合について説明したが、データ線及び走査線を行方向及び列方向にそれぞれ配線して、第1及び第2の信号線としてもよい。

#### 【0126】

また、上記の説明では、スイッチング素子に薄膜トランジスタを使用した場合について説明したが、本発明のスイッチング素子はこれに限定されるものではなく、電界効果トランジスなどの他の3端子あるいは薄膜ダイオードなどの2端子のスイッチング素子を使用することもできる。

#### 【0127】

また、上記の説明では、第1及び第2の信号線が配線された基板本体と、第1及び第2の信号線に対し、信号をそれぞれ入力させる第1及び第2の駆動回路が設置された回路設置部とを設けた場合について説明したが、本発明のアクティブマトリクス基板は、これに限定されるものではなく、少なくとも上記基板本体を備えたものであればよい。

#### 【0128】

但し、上記実施形態のように、基板本体と一体的に構成される回路設置部を設ける場合の方が、複数の第1の信号線及び複数の第2の信号線と第1及び第2の駆動回路との接続作業を簡単に行えるとともに、コンパクトで取扱性に優れたアクティブマトリクス基板を構成することができる点で好ましい。

#### 【0129】

また、上記の説明では、台形状、半円状、1/4円状の表示領域を有する液晶パネルに適用した場合について説明したが、本発明のアクティブマトリクス基板はこれに限定されない。具体的には、本発明のアクティブマトリクス基板は、三角形、平行四辺形、菱形、五角形以上の多角形、あるいは円形、半円等の円弧状の形状、または多角形と円弧状の形状とを組み合わせたものなどの矩形（正方形を含む。）以外の形状である異形の表示領域をもつ表示パネルに適用することができる。

#### 【産業上の利用可能性】

#### 【0130】

本発明は、矩形以外の形状の表示領域に用いられるときでも、表示品位が低下するのを容易に防止することができるアクティブマトリクス基板、及びこれを用いた高性能な表示パネル並びに表示装置に対して有用である。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【图6】

【図7】

【 四 8 】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(56)参考文献 特開平11-297760(JP,A)

特開2006-234918(JP,A)

特開2000-347600(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09F 9/30

G02F 1/1343

G02F 1/1362

|                |                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵基板，显示面板和显示装置                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP4659885B2</a>                                                                | 公开(公告)日 | 2011-03-30 |

| 申请号            | JP2008545319                                                                               | 申请日     | 2007-06-08 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                     |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                       |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                       |         |            |

| [标]发明人         | 吉田昌弘                                                                                       |         |            |

| 发明人            | 吉田 昌弘                                                                                      |         |            |

| IPC分类号         | G09F9/30 G02F1/1343 G02F1/1362                                                             |         |            |

| CPC分类号         | G02F1/1345 G02F1/136286 G02F2001/13456 G02F2201/56 G09G3/3648 G09G2300/0426 G09G2320 /0223 |         |            |

| FI分类号          | G09F9/30.308.Z G09F9/30.338 G02F1/1343 G02F1/1362                                          |         |            |

| 审查员(译)         | 福岛浩二                                                                                       |         |            |

| 优先权            | 2006314533 2006-11-21 JP                                                                   |         |            |

| 其他公开文献         | <a href="#">JPWO2008062575A1</a>                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                  |         |            |

### 摘要(译)

在有源矩阵基板中，设置多个像素 (P)，以对应于形成为具有除矩形之外的形状的液晶面板 (显示面板) (2) 的显示区域。此外，在多条扫描线 (第一信号线) (G) 和数据线 (S2至S6, S8至S11) 中沿着具有比其他行更少的像素的行布置的扫描线 (G3至G7) 在多个数据线 (第二信号线) (S) 中沿着具有比其他列更少数量的像素的列布置在除了显示区域之外的位置处彼此交叉。