(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3730886号

(P3730886)

(45) 発行日 平成18年1月5日(2006.1.5)

(24) 登録日 平成17年10月14日(2005.10.14)

(51) Int.C1.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b>  |             |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> | <b>505</b>  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> | <b>520</b>  |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>623B</b> |

請求項の数 46 (全 43 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2001-206987 (P2001-206987) |

| (22) 出願日  | 平成13年7月6日(2001.7.6)          |

| (65) 公開番号 | 特開2003-22056 (P2003-22056A)  |

| (43) 公開日  | 平成15年1月24日(2003.1.24)        |

| 審査請求日     | 平成16年5月19日(2004.5.19)        |

|           |                                                            |

|-----------|------------------------------------------------------------|

| (73) 特許権者 | 000004237<br>日本電気株式会社<br>東京都港区芝五丁目7番1号                     |

| (73) 特許権者 | 000232036<br>NECマイクロシステム株式会社<br>神奈川県川崎市中原区小杉町1丁目403<br>番53 |

| (74) 代理人  | 100080816<br>弁理士 加藤 朝道                                     |

| (72) 発明者  | 土 弘<br>東京都港区芝五丁目7番1号 日本電気株<br>式会社内                         |

最終頁に続く

(54) 【発明の名称】 駆動回路及び液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

出力負荷を駆動する駆動回路において、

入力信号電圧が入力される一の入力端子に入力端が共通に接続され、一の出力端子に出力端が共通に接続される二つのバッファ回路であって、動作範囲として、少なくとも高位側電位の範囲を有する第1のバッファ回路と、少なくとも低位側電位の範囲を有する第2のバッファ回路と、を備え、

前記第1のバッファ回路と前記第2のバッファ回路の動作の切替えを選択するための基準データを記憶保持する記憶部と、

入力されたデータ信号と、前記基準データとを比較する比較部と、

を有し、

前記比較部の比較結果信号と制御信号とに基づき、前記第1のバッファ回路と前記第2バッファ回路を、動作可能範囲において、動作と停止の切替えを制御する手段を備えている、ことを特徴とする駆動回路。

## 【請求項2】

前記基準データは、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる範囲内の電圧に対応したデータに対応している、ことを特徴とする請求項1記載の駆動回路。

## 【請求項3】

入力信号電圧が入力される一の入力端子に入力端が共通に接続され、一の出力端子に出力

10

20

端が共通に接続される二つのバッファ回路であって、高位側電源電位にその動作範囲が及ぶ第1のバッファ回路と、低位側電源電位にその動作範囲が及ぶ第2のバッファ回路と、を備え、

入力されるデジタルデータと信号電圧との関係に対応し、予め定められた基準電圧信号からの特性を規定する第1、第2の極性ごとに、前記第1のバッファ回路と前記第2のバッファ回路の動作の切替えを判断するための第1、第2の極性の基準データをそれぞれ記憶保持する記憶部を備え、

極性を特定する極性信号を入力し、前記極性信号の値に基づき前記第1の極性又は第2の極性の基準データの一方を選択する選択部と、

入力されたデジタルデータと、前記選択部から出力される基準データとを比較する比較部と、

前記比較部の比較結果信号と制御信号に基づき、前記第1のバッファ回路と前記第2バッファ回路を、動作可能範囲において、動作と停止の切替えを制御する手段と、を備えている、ことを特徴とする駆動回路。

**【請求項4】**

前記第1の極性又は第2の極性の基準データは、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる範囲内の電圧に対応したデータに対応している、ことを特徴とする請求項3記載の駆動回路。

**【請求項5】**

入力信号電圧が入力される一の入力端子に入力端が共通に接続され、出力端が一の出力端子に共通に接続される二つのバッファ回路であって、高位側電源電位にその動作範囲が及ぶ第1のバッファ回路と、低位側電源電位にその動作範囲が及ぶ第2のバッファ回路と、を備え、

階調と信号電圧に関する特性の標準状態及び変調時のそれぞれに対して、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる範囲内の入力信号電圧に対応した基準データを記憶保持する記憶部と、

変調を特定する変調情報に基づき、標準又は変調に対応した基準データを選択出力する選択部と、

入力されたデータと前記選択部から出力される基準データとを比較する比較部と、前記比較部の比較結果信号と制御信号に基づき、前記第1のバッファ回路と前記第2バッファ回路は、動作と停止を制御する手段と、を備えている、ことを特徴とする駆動回路。

**【請求項6】**

前記記憶部が、変調種別に応じて規定される基準データを複数記憶保持しており、前記選択部において、入力された変調情報に基づき、変調種別に応じた基準データを選択出力する、ことを特徴とする請求項5記載の駆動回路。

**【請求項7】**

入力信号電圧が入力される一の入力端子に入力端が共通に接続され、出力端が一の出力端子に共通に接続される二つのバッファ回路であって、高位側電源電位にその動作範囲が及ぶ第1のバッファ回路と、低位側電源電位にその動作範囲が及ぶ第2のバッファ回路と、を備え、

階調と信号電圧に関する特性の標準状態及び変調時のそれぞれに対して、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる範囲内の入力信号電圧に対応した、正極性の基準データを記憶保持する第1の記憶部と、

階調と信号電圧に関する特性の標準状態及び変調時のそれぞれに対して、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる駆動切替可能範囲内の電圧に対応した、負極性の基準データを記憶保持する第2の記憶部と、

極性を特定する極性信号に基づき前記第1、第2の記憶部の一方を選択し、変調を特定する変調情報に基づき、標準又は変調に対応した基準データを選択出力する選択部と、

入力されたデータと前記選択部から出力される基準データとを比較する比較部と、

10

20

30

40

50

前記比較部の比較結果信号と制御信号に基づき、前記第1のバッファ回路と前記第2バッファ回路は、動作と停止を制御する手段と、

を備えている、ことを特徴とする駆動回路。

【請求項8】

前記第1の記憶部が、変調種別に応じて規定される正極性の基準データを複数記憶保持して

おり、

前記第2の記憶部が、変調種別に応じて規定される負極性の基準データを複数記憶保持して

おり、

前記選択部において、前記極性信号に基づき、前記第1の記憶部と前記第2の記憶部の一方を

選択し、入力された変調情報に基づき、変調種別に応じた基準データを選択出力する

ことを特徴とする請求項7記載の駆動回路。 10

【請求項9】

前記制御信号が、動作を指示する値である場合において、前記比較部の比較結果信号が、

前記入力されたデータが前記基準データに等しいもしくは前記基準データより大であるこ

とを示す値である場合、前記第1のバッファ回路を動作状態とし、前記第2バッファ回路

を停止させ、

前記比較部の比較結果信号が、前記入力されたデータが前記基準データより小であるこ

とを示す値である場合、前記第2バッファ回路を動作状態とし、前記第1のバッファ回路

を停止させる、構成とされている、ことを特徴とする請求項1乃至7のいずれかに記載の

駆動回路。 20

【請求項10】

前記極性信号が、液晶表示装置の対向電極の共通電位( $V_{com}$ )の反転駆動における極性

を示す論理値とされている、ことを特徴とする請求項7又は8に記載の駆動回路。

【請求項11】

前記第1の記憶部と、前記第2の記憶部と、前記選択部との少なくとも一つが、前記駆動

回路の外部に設けられ前記駆動回路と電気的に接続される構成とされている、ことを特徴

とする請求項7記載の駆動回路。

【請求項12】

第1、第2の参照電圧間に直列形態に接続されている複数の抵抗を備え、各タップから階

調電圧を生成する階調電圧発生手段と、 30

デジタルデータ信号を入力し前記階調電圧発生手段の出力電圧から対応する電圧を選択出

力するデコード回路を備え、

前記デコード回路の出力を入力し、出力負荷を駆動する駆動回路であって、請求項2乃至

7のいずれかに記載の前記駆動回路を複数備え、

前記第1及び第2の記憶部、前記選択部を、前記駆動回路の所定個数に対して、共通に少

なくとも一つ備えている、ことを特徴とする駆動回路。

【請求項13】

出力負荷を駆動する駆動回路において、

入力信号電圧が入力される一の入力端子に入力端が共通に接続され、一の出力端子に出力

端が共通に接続される二つのバッファ回路であって、動作範囲として、少なくとも高位側

電位の範囲を有する第1のバッファ回路と、少なくとも低位側電位の範囲を有する第2の

バッファ回路と、を備え、 40

前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる電圧範囲に

対応した基準電圧を発生する基準電圧発生手段と、

前記基準電圧発生手段から出力される基準電圧と、前記入力信号電圧とを比較する比較部

と、

前記比較部の比較結果信号と制御信号に基づき、前記第1のバッファ回路と前記第2バッ

ファ回路を、動作可能範囲において、動作と停止を制御する手段と、

を備えている、ことを特徴とする駆動回路。

【請求項14】

10

20

30

40

50

前記制御信号が、動作を指示する値である場合において、前記比較部の比較結果信号が、前記入力信号電圧が前記基準電圧と等しいもしくは前記基準電圧より高いことを示す値である場合、前記第1のバッファ回路を動作状態とし、前記第2バッファ回路を停止させ、前記比較部の比較結果信号が、前記入力信号電圧が前記基準電圧よりも低いことを示す値である場合、前記第2バッファ回路を動作状態とし、前記第1のバッファ回路を停止させる、構成とされている、ことを特徴とする請求項13記載の駆動回路。

【請求項15】

入力信号電圧が入力される一の入力端子に入力端が共通に接続され、一の出力端子に出力端が共通に接続される二つのバッファ回路であって、高位側電源電位に動作範囲が及ぶ第1のバッファ回路と、低位側電源電位に動作範囲が及ぶ第2のバッファ回路と、

10

を備え、

前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる電圧範囲の基準電圧を発生する基準電圧発生手段と、

前記基準電圧発生手段から出力される基準電圧と、入力信号電圧とを比較する比較部と、前記比較器の比較結果信号と制御信号とを入力とし、前記制御信号がアクティブのときに、前記比較結果信号の論理演算結果を、前記第1のバッファ回路に出力する第1の論理回路と、

前記比較器の比較結果信号を反転した信号と前記制御信号とを入力とし、前記制御信号がアクティブのときに、前記比較結果信号の反転信号の論理演算結果を、前記第2バッファ回路に出力する第2の論理回路と、

20

を備えている、ことを特徴とする駆動回路。

【請求項16】

前記基準電圧発生手段が前記駆動回路の外部に設けられている、ことを特徴とする請求項15記載の駆動回路。

【請求項17】

第1、第2の参照電圧間に直列形態に接続されている複数の抵抗を備え各タップから階調電圧を生成する階調電圧発生手段と、

デジタルデータ信号を入力し前記階調電圧発生手段の出力電圧から対応する電圧を選択出力するデコード回路を備え、

前記デコード回路の出力を入力し、出力負荷を駆動する駆動回路であって、請求項13又は15記載の前記駆動回路を複数備え、

30

前記基準電圧発生手段が、前記駆動回路の所定個数に対して共通に少なくとも一つ設けられている、ことを特徴とする駆動回路。

【請求項18】

前記比較器が、前記入力信号電圧と前記基準電圧を差動入力する差動増幅回路と、

前記差動増幅回路の出力にスイッチを介して接続される保持回路と、

を備えている、ことを特徴とする請求項13又は15記載の駆動回路。

【請求項19】

前記比較器が、

前記入力信号電圧と前記基準電圧とを差動入力する差動増幅回路と、

40

前記差動増幅回路の一の出力端に第1のスイッチを介して接続されるフリップフロップ回路と、

を備え、

前記フリップフロップが、

前記第1のスイッチに入力端が接続されている第1のインバータと、

前記第1のインバータの出力端に入力端が接続されている第2のインバータと、

前記第2のインバータの出力端と前記第1のインバータの入力端との間に接続されている第2のスイッチを備え、

前記第2のインバータの出力信号が比較結果信号として出力され、

前記差動増幅回路が動作時、前記第1のスイッチをオン状態とし、前記差動増幅回路の出

50

力を受けてラッチする際に、前記第1のスイッチをオフし、前記第2のスイッチをオン状態とする制御が行われる、ことを特徴とする請求項13又は15記載の駆動回路。

【請求項20】

前記比較器が、

入力信号電圧と前記基準電圧を差動入力する差動増幅回路と、

フリップフロップ回路と、

を備え、

前記差動増幅回路が、

前記入力信号電圧と前記基準電圧とを差動入力とする差動対と、

前記差動対を駆動する電流源の電源バスに挿入されている第1のスイッチと、

前記差動対の出力を受ける出力段トランジスタと、

前記出力段トランジスタの電源バスに挿入されている第2のスイッチと、

を備え、

前記フリップフロップが、

第3のスイッチを介して、前記出力段トランジスタの出力端に入力端が接続される第1のインバータと、

前記第1のインバータの出力端に入力端が接続されている第2のインバータと、

前記第2のインバータの出力端と前記第1のインバータの入力端間に接続されている第4のスイッチと、

を備え、

前記第2のインバータの出力端の信号、及び／又は、前記第1のインバータの出力端の信号が比較結果信号として出力され、

前記差動増幅回路が動作時、前記第1、第2、第3のスイッチをすべてオン状態とし、

前記差動増幅回路の出力を受けて前記フリップフロップが前記出力をラッチする際に、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチをオフし、前記第4のスイッチをオン状態とする制御が行われる、構成とされている、ことを特徴とする請求項13又は15記載の駆動回路。

【請求項21】

前記比較器が、

入力信号電圧と前記基準電圧を差動入力する差動増幅回路と、

フリップフロップ回路と、

を備え、

前記差動増幅回路が、

前記入力信号電圧と前記基準電圧を差動入力とする差動対と、

前記差動対を駆動する電流源の電源バスに挿入されている第1のスイッチと、

前記差動対の出力を受ける出力段トランジスタと、

前記出力段トランジスタの電源バスに挿入されている第2のスイッチと、

を備え、

前記フリップフロップが、

第3のスイッチを介して、前記出力段トランジスタの出力端に接続される第1のクロックドインバータと、

前記第1のクロックドインバータの出力端に入力端が接続されている第2のクロックドインバータと、

を備え、

前記第2のクロックドインバータの出力端が前記第1のクロックドインバータの入力端に接続され、

前記第2のクロックドインバータの出力端の信号、及び／又は前記第1のクロックドインバータの出力端の信号が、比較結果信号として出力され、

前記差動増幅回路が動作時、前記第1、第2、第3のスイッチをすべてオン状態とし、前記差動増幅回路の出力を受けてラッチする際に、前記第1、第2、第3のスイッチをオフ

10

20

30

40

50

する制御が行われる、構成とされている、ことを特徴とする請求項 13 又は 15 記載の駆動回路。

【請求項 2 2】

前記比較器が、

入力信号電圧と前記基準電圧を差動入力する差動増幅回路と、

フリップフロップ回路と、

を備え、

前記差動増幅回路が、

前記入力信号電圧と前記基準電圧を差動入力とする差動対と、

前記差動対を駆動する電流源の電流バスに挿入されている第 1 のスイッチと、

10

前記差動対の出力を受ける出力段トランジスタと、

前記出力段トランジスタの電源バスに挿入されている第 2 のスイッチと、

を備え、

前記フリップフロップが、

第 3 のスイッチを介して、前記出力段トランジスタの出力端に入力端が接続される第 1 のクロックドインバータであって、CMOS インバータを構成する P チャネル MOS トランジスタのソースと前記高位側電源間に接続される第 4 のスイッチと、前記 CMOS インバータを構成する N チャネル MOS トランジスタのソースと低位側電源間に接続される第 5 のスイッチと、を備えた第 1 のクロックドインバータと、

前記第 1 のクロックドインバータの出力端に入力端が接続されている第 2 のクロックドインバータであって、CMOS インバータを構成する P チャネル MOS トランジスタのソースと高位側電源間に接続される第 6 のスイッチと、CMOS インバータを構成する N チャネル MOS トランジスタのソースと低位側電源間に接続される第 7 のスイッチを備えた第 2 のクロックドインバータと、

20

前記第 2 のクロックドインバータの出力端が前記第 1 のクロックドインバータの入力端に接続され、

前記第 2 のクロックドインバータの出力端の信号、又は、前記第 1 、第 2 のクロックドインバータの出力端の信号が比較結果信号として出力され、

前記差動増幅回路が動作時、前記第 1 、第 2 、第 3 のスイッチをオン状態とし、前記差動増幅回路の出力を受けてラッチする際に、前記第 1 、第 2 、第 3 のスイッチをオフし、前記第 4 、第 5 、第 6 、第 7 のスイッチをオンする、ことを特徴とする請求項 13 又は 15 記載の駆動回路。

30

【請求項 2 3】

前記第 2 のクロックドインバータの出力端の負荷容量の容量値が、前記第 1 のクロックドインバータの出力端の負荷容量の容量値よりも大とされている、ことを特徴とする請求項 21 又は 22 記載の駆動回路。

【請求項 2 4】

前記第 1 のバッファ回路が、低位側電源と前記出力端子間に接続されるソースフォロワ構成のトランジスタと、

入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧を供給する第 1 のゲートバイアス制御手段と、

40

前記出力端子を予備充電する手段と、を備えている、ことを特徴とする請求項 1 、 2 、 3 、 4 、 5 、 6 、 7 、 13 、 15 のいずれか一に記載の駆動回路。

【請求項 2 5】

前記第 2 のバッファ回路が、高位側電源と前記出力端子間に接続されるソースフォロワ構成のトランジスタと、

入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧を供給する第 2 のゲートバイアス制御手段と、

前記出力端子を予備放電する手段と、を備えている、ことを特徴とする請求項 1 、 2 、 3 、 4 、 5 、 6 、 7 、 13 、 15 のいずれか一に記載の駆動回路。

50

## 【請求項 2 6】

前記第1のバッファ回路が、低位側電源と前記出力端子間に接続されるソースフォロワ構成の第1のトランジスタと、

前記入力信号電圧を入力し前記ソースフォロワ構成の第1のトランジスタにゲートバイアス電圧を供給する第1のゲートバイアス制御手段と、

前記出力端子を充電する手段と、

を備え、

前記第2のバッファ回路が、高位側電源と前記出力端子間に接続されるソースフォロワ構成の第2のトランジスタと、

前記入力信号電圧を入力し前記ソースフォロワ構成のトランジスタに第2のゲートバイアス電圧を供給する第2のゲートバイアス制御手段と、

前記出力端子を予備放電する手段と、

を備えている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

## 【請求項 2 7】

前記第1のバッファ回路が、前記入力端子と高位側電源間に直列形態に接続されている第1の電流源、及び第1のスイッチと、

前記入力端子にソースが接続され、ゲートとドレインが接続されている第1導電型の第1のMOSトランジスタと、

前記第1のMOSトランジスタのドレインと低位側電源間に直列形態に接続されている第2の電流源、及び第2のスイッチと、

前記出力端子と前記高位側電源間に直列形態に接続されている第3の電流源、及び第3のスイッチと、

前記出力端子にソースが接続され、前記第1のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第4スイッチを介して低位側電源に接続されている第1導電型の第2のMOSトランジスタと、

を備え、

前記出力端子と前記高位側電源間には前記出力端子の充電制御用の第5のスイッチを備えている、ことを特徴とする請求項請求項1、2、3、9、4、5、6、7、13、15のいずれか一に記載の駆動回路。

## 【請求項 2 8】

前記第2のバッファ回路が、前記入力端子と低位側電源間に直列形態に接続されている第4の電流源、及び第6のスイッチと、

前記入力端子にソースが接続され、ゲートとドレインが接続されている第2導電型の第3のMOSトランジスタと、

前記第3のMOSトランジスタのドレインと高位側電源間に直列形態に接続されている第5の電流源、及び第7のスイッチと、

前記出力端子と前記低位側電源間に直列形態に接続されている第6の電流源、及び第8のスイッチと、

前記出力端子にソースが接続され、前記第3のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第9スイッチを介して前記高位側電源に接続されている第2導電型の第4のMOSトランジスタと、

を備え、

前記出力端子と前記低位側電源間には前記出力端子の放電制御用の第10のスイッチを備えている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

## 【請求項 2 9】

前記第1のバッファ回路が、前記入力端子と高位側電源間に直列に接続されている第1の電流源、及び第1のスイッチと、

前記入力端子にソースが接続され、ゲートとドレインが接続されている第1導電型の第1

10

20

30

40

50

のMOSトランジスタと、

前記第1のMOSトランジスタのドレインと低位側電源間に直列に接続されている第2の電流源、及び第2のスイッチと、

前記出力端子と前記高位側電源間に直列に接続されている第3の電流源、及び第3のスイッチと、

前記出力端子にソースが接続され、前記第1のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第4スイッチを介して低位側電源に接続されている第1導電型の第2のMOSトランジスタと、

を備え、

前記出力端子と前記高位側電源間には前記出力端子の充電用の第5のスイッチを備え、

10

前記第2のバッファ回路が、前記入力端子と低位側電源間に直列に接続されている第4の電流源、及び第6のスイッチと、

前記入力端子にソースが接続され、ゲートとドレインが接続されている第2導電型の第3のMOSトランジスタと、

前記第3のMOSトランジスタのドレインと高位側電源間に直列に接続されている第5の電流源、及び第7のスイッチと、

前記出力端子と前記低位側電源間に直列に接続されている第6の電流源、及び第8のスイッチと、

前記出力端子にソースが接続され、前記第3のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第9スイッチを介して前記高位側電源に接続されている第2導電型の第4のMOSトランジスタと、

を備え、

前記出力端子と前記低位側電源間には前記出力端子の放電制御用の第10のスイッチを備えている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

#### 【請求項30】

前記第1のバッファ回路が、第2導電型のMOSトランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなるボルテージフォロワ回路を含んで構成されている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

30

#### 【請求項31】

前記第2のバッファ回路が、第1導電型のMOSトランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなるボルテージフォロワ回路を含んで構成されている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

#### 【請求項32】

前記第1のバッファ回路が、第2導電型のMOSトランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなる第1のボルテージフォロワ回路を含んで構成されており、

前記第2のバッファ回路が、第1導電型のMOSトランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなる第2のボルテージフォロワ回路を含んで構成されている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

40

#### 【請求項33】

前記出力端子を予備充電、及び、予備放電する手段を備えている、ことを特徴とする請求項30、31、32のいずれか一に記載の駆動回路。

#### 【請求項34】

前記第1のバッファ回路が、

第2導電型のMOSトランジスタ対からなる差動対と、

前記差動対の出力と高位側電源間に接続される負荷回路と、

50

前記差動対を駆動する電流源と、前記電流源と低電位電源間の電流パスをオン及びオフ制御する第1のスイッチと、

を備えた差動段と、

前記差動対の一の出力を入力とし、出力が前記出力端子に接続されているMOSトランジスタと、

前記出力端子と低位側電源間に接続されている電流源、及びスイッチと、

を備え、

前記差動対のMOSトランジスタ対のゲートには前記入力端子と前記出力端子が接続されている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

10

【請求項35】

前記第2のバッファ回路が、

第1導電型のMOSトランジスタ対からなる差動対と、

前記差動対の出力と低位側電源間に接続される負荷回路と、

前記差動対を駆動する電流源と、

前記電流源と高電位電源間の電流パスをオン及びオフ制御するスイッチと、

を備えた差動段と、

前記差動対の一の出力を入力とし、出力が前記出力端子に接続されているMOSトランジスタと、

前記出力端子と低位側電源間に接続されている電流源、及びスイッチと、

を備え、

20

前記差動対のMOSトランジスタ対のゲートには前記入力端子と前記出力端子が接続されている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

【請求項36】

前記第1のバッファ回路が、

第2導電型の第1、第2のMOSトランジスタからなる第1の差動対と、

前記差動対の出力と高位側電源間に接続される第1の負荷回路と、

前記第1の差動対を駆動する第1の電流源と、

前記第1の電流源と低電位電源間の電流パスをオン及びオフ制御する第1のスイッチと、

を備えた第1の差動段と、

30

前記第1の差動対の一の出力を入力とし、出力が前記出力端子に接続されている第3のMOSトランジスタと、

前記出力端子と低位側電源間に接続されている第2の電流源及び第2のスイッチと、

を備え、

前記第1の差動対のMOSトランジスタ対のゲートには前記入力端子と前記出力端子が接続されており、

前記第2のバッファ回路が、

第1導電型の第4、第5のMOSトランジスタ対からなる第2の差動対と、

前記第2の差動対の出力と低位側電源間に接続される第2の負荷回路と、

前記第2の差動対を駆動する第3の電流源と、

前記第3の電流源と高電位電源間の電流パスをオン及びオフ制御する第3のスイッチと、

を備えた第2の差動段と、

40

前記第2の差動対の一の出力を入力とし、出力が前記出力端子に接続されている第6のMOSトランジスタと、

前記出力端子と低位側電源間に接続されている第4の電流源及び第4のスイッチと、

を備え、

前記第2の差動対のMOSトランジスタ対のゲートには前記入力端子と前記出力端子が接続されている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

50

## 【請求項 3 7】

前記出力端子を予備充電、及び予備放電する手段を備えている、ことを特徴とする請求項 3 4、3 5、3 6 のいずれか一に記載の駆動回路。

## 【請求項 3 8】

前記第 1 のバッファ回路が、

第 2 導電型の M O S トランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなるボルテージフォロワ回路と、

低位側電源と前記出力端子に接続されるソースフォロワ構成のトランジスタと、

前記入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧 10 を供給する第 1 のゲートバイアス制御手段と、

を備えている、ことを特徴とする請求項 1、2、3、4、5、6、7、13、15 のいずれか一に記載の駆動回路。

## 【請求項 3 9】

前記第 2 のバッファ回路が、

第 1 導電型の M O S トランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなるボルテージフォロワ回路よりなり、

高位側電源と前記出力端子に接続されるソースフォロワ構成のトランジスタと、

前記入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧 20 を供給する第 2 のゲートバイアス制御手段を備えている、ことを特徴とする請求項 1、2、3、4、5、6、7、13、15 のいずれか一に記載の駆動回路。

## 【請求項 4 0】

前記第 1 のバッファ回路が、第 2 導電型の M O S トランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなる第 1 のボルテージフォロワ回路と、

低位側電源と前記出力端子に接続されるソースフォロワ構成の第 1 のトランジスタと、前記入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧を供給する第 1 のゲートバイアス制御手段を備え、

前記第 2 のバッファ回路が、第 1 導電型の M O S トランジスタ対からなる差動対を備え、前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなるボルテージフォロワ回路よりなり、

高位側電源と前記出力端子に接続されるソースフォロワ構成のトランジスタと、

前記入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧を供給する第 2 のゲートバイアス制御手段を備えている、ことを特徴とする請求項 1、2、3、4、5、6、7、13、15 のいずれか一に記載の駆動回路。

## 【請求項 4 1】

前記出力端子を予備充電、予備放電する手段を備えたことを特徴とする請求項 3 8、3 9、4 0 のいずれか一に記載の駆動回路。

## 【請求項 4 2】

前記第 1 のバッファ回路が、

第 2 導電型の第 1、第 2 の M O S トランジスタ対からなる差動対と、

前記差動対の出力と高位側電源間に接続される能動負荷回路と、

前記差動対を駆動する第 1 の電流源と、

前記第 1 の電流源と低電位電源間の電流バスをオン及びオフ制御する第 1 のスイッチと、を備えた差動段と、

前記差動対の出力を入力とし、出力が前記出力端子に接続されている第 3 の M O S トランジスタと、

を備え、前記第 1、第 2 の M O S トランジスタ対のゲートには前記入力端子と前記出力端子が接続されており、

前記入力端子と高位側電源間に直列に接続されている第2の電流源、及び第2のスイッチと、

前記入力端子にソースが接続され、ゲートとドレインが接続されている第1導電型の第4のMOSトランジスタと、

前記第4のMOSトランジスタのドレインと低位側電源間に直列形態に接続されている第3の電流源、及び第3のスイッチと、

前記出力端子と前記高位側電源間に直列形態に接続されている第4の電流源、及び第4のスイッチと、

前記出力端子にソースが接続され、前記第4のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第5スイッチを介して低位側電源に接続されている第1導電型の第5のMOSトランジスタと、

を備えている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

【請求項43】

前記第2のバッファ回路が、

第1導電型の第6、第7のMOSトランジスタ対からなる差動対と、

前記差動対の出力と低位側電源間に接続される能動負荷回路と、

前記差動対を駆動する第5の電流源と、

前記第5の電流源と高電位電源間の電流パスをオン及びオフ制御する第6のスイッチと、

を備えた差動段と、

前記差動対の出力を入力とし、出力が前記出力端子に接続されている第8のMOSトランジスタと、

を備え、前記第6、第7のMOSトランジスタ対のゲートには前記入力端子と前記出力端子が接続されており、

前記入力端子と低位側電源間に直列に接続されている第6の電流源、及び第7のスイッチと、

前記入力端子にソースが接続され、ゲートとドレインが接続されている第2導電型の第9のMOSトランジスタと、

前記第9のMOSトランジスタのドレインと高位側電源間に直列形態に接続されている第7の電流源、及び第8のスイッチと、

前記出力端子と前記低位側電源間に直列形態に接続されている第8の電流源、及び第9のスイッチと、

前記出力端子にソースが接続され、前記第9のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第10スイッチを介して高位側電源に接続されている第1導電型の第10のMOSトランジスタと、

を備えている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

【請求項44】

前記第1のバッファ回路が、

第2導電型の第1、第2のMOSトランジスタ対からなる差動対と、

前記差動対の出力と高位側電源間に接続される能動負荷回路と、

前記差動対を駆動する第1の電流源と、

前記第1の電流源と低電位電源間の電流パスをオン及びオフ制御する第1のスイッチと、

を備えた第1の差動段と、

前記第1の差動対の一の出力を入力とし、出力が前記出力端子に接続されている第3のMOSトランジスタと、

を備え、前記第1、第2のMOSトランジスタ対のゲートには前記入力端子と前記出力端子が接続されおり、

前記入力端子と前記高位側電源間に直列形態に接続されている第2の電流源、及び第2のスイッチと、

10

20

30

40

50

前記入力端子にソースが接続され、ゲートとドレインが接続されている第1導電型の第4のMOSトランジスタと、

前記第4のMOSトランジスタのドレインと前記低位側電源間に直列形態に接続されている第3の電流源、及び第3のスイッチと、

前記出力端子と前記高位側電源間に直列形態に接続されている第4の電流源、及び第4のスイッチと、

前記出力端子にソースが接続され、前記第4のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第5スイッチを介して低位側電源に接続されている第1導電型の第5のMOSトランジスタと、

を備え、

10

前記第2のバッファ回路が、

第1導電型の第6、第7のMOSトランジスタ対からなる第2の差動対と、

前記第2の差動対の出力と低位側電源間に接続される能動負荷回路と、

前記第2の差動対を駆動する第5の電流源と、

前記第5の電流源と高電位電源間の電流パスをオン及びオフ制御する第6のスイッチと、

を備えた第2の差動段と、

前記第2の差動対の一の出力を入力とし、出力が前記出力端子に接続されている第8のMOSトランジスタと、

を備え、前記第6、第7のMOSトランジスタ対のゲートには前記入力端子と前記出力端子が接続されており、

20

前記入力端子と低位側電源間に直列形態に接続されている第6の電流源、及び第7のスイッチと、

前記入力端子にソースが接続され、ゲートとドレインが接続されている第2導電型の第9のMOSトランジスタと、

前記第9のMOSトランジスタのドレインと高位側電源間に直列形態に接続されている第7の電流源、及び第8のスイッチと、

前記出力端子と前記低位側電源間に直列形態に接続されている第8の電流源、及び第9のスイッチと、

前記出力端子にソースが接続され、前記第9のMOSトランジスタのゲートにゲートが共通接続され、ドレインが第10スイッチを介して高位側電源に接続されている第1導電型の第10のMOSトランジスタと、

30

を備えている、ことを特徴とする請求項1、2、3、4、5、6、7、13、15のいずれか一に記載の駆動回路。

#### 【請求項45】

前記基準電圧発生手段が、第1、第2の参照電圧の間に接続されている複数の抵抗と、スイッチを備え、前記スイッチがオン状態のとき、前記抵抗の接続点から、前記第1、第2のバッファ回路の動作範囲の重なりで規定される駆動切替範囲内の電圧が出力される、ことを特徴とする請求項13又は15に記載の駆動回路。

#### 【請求項46】

請求項1乃至45のいずれか一に記載の駆動回路を、データ線の駆動に用いてなることを特徴とする液晶表示装置。

40

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、駆動回路に関し、特に、容量負荷の駆動に好適な駆動回路に関する。

##### 【0002】

##### 【従来の技術】

この発明に関連する技術の刊行物として、

(1)文献(H.Tsuchi,N.Ikeda,H.Hayama,"A New Low Power TFT-LCD Dirver for Portable Devices," SID 00 DIGEST PP146~149)、

50

(2) 特開2000-338461号公報

等が参照される。

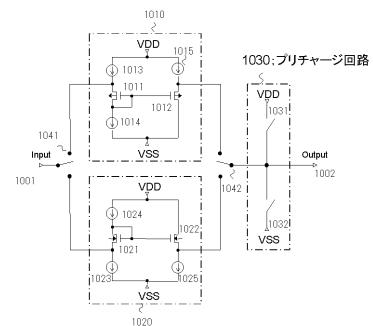

【0003】

図24は、液晶表示装置の映像デジタルデータを駆動する駆動回路の構成の一例を示す図である(文献(1)のFigure1.参照)。

【0004】

図24に示すバッファは、アナログバッファ単体ではフルレンジ出力できない場合でも、二つのアナログバッファ回路(単に、「バッファ回路」という)を切替え、フルレンジ出力を可能としたものである。なおフルレンジ出力とは駆動回路の電源電圧範囲のほぼ全領域での出力を意味する。図24を参照すると、第1のバッファ回路1010は、入力端子1001に固定端が接続され、第1、第2の切替用端子を有する第1の切替スイッチ1041と、第1の切替スイッチ1041の切替用の第1端子と高位側電源VDDとの間に直列形態に接続されてなる第1の定電流源1013と、第1のスイッチ1041の第1端子にソースが接続され、ゲートとドレインが接続されているPチャネルMOSトランジスタ1011と、PチャネルMOSトランジスタ1011のドレインと低位側電圧源VSS間に接続されている第2の定電流源1014と、出力端子1002に固定端が接続され第1、第2の切替用端子を有する第2の切替スイッチ1042と、第2の切替スイッチ1042の切替用の第1端子と高位側電源VDDとの間に直列形態に接続されている第3の定電流源1015と、第2の切替スイッチ1042の第1端子にソースが接続され、PチャネルMOSトランジスタ1011のゲートにゲートが接続され、ドレインが低位側電圧源VSSに接続されているPチャネルMOSトランジスタ1012と、を備えている。

10

【0005】

第2のバッファ回路1020は、入力端子1001に固定端が接続された第1の切替スイッチ1041の切替用の第2端子と低位側電圧源VSSとの間に直列形態に接続されてなる第4の定電流源1023と、第1のスイッチ1041の第2端子にソースが接続され、ゲートとドレインが接続されているNチャネルMOSトランジスタ1021と、NチャネルMOSトランジスタ1021のドレインと高位側電源VDD間に接続されている第5の定電流源1024と、出力端子1002に固定端が接続された第2の切替スイッチ1042の切替用の第2端子と低位側電圧源VSSとの間に直列形態に接続されている第6の定電流源1025と、第2の切替スイッチ1042の第2端子にソースが接続され、NチャネルMOSトランジスタ1021のゲートにゲートが接続され、ドレインが高位側電圧源VDDに接続されているNチャネルMOSトランジスタ1022と、を備えている。

20

【0006】

さらに出力端子1002と高位側電源VDD間のスイッチ1031と、出力端子1002と低位側電圧源VSS間のスイッチ1032とからなり、出力端子1002を予備放電、予備充電する予備充放電回路1030(プリチャージ回路)を備えている。

【0007】

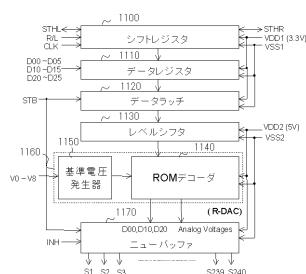

図25は、6ビットデジタルデータドライバの構成を示しており(文献(1)のFigure3.参照)、シフトレジスタ1100、データレジスタ1110、ラッチ1120、レベルシフト回路1130、R-DAC1160(基準電圧発生回路1150とROMデコーダ1140)、ニュー(New)バッファ1170を備えている。ニューバッファ1170は図24の構成からなる。アナログ電圧は、ROMデコーダ1140からニューバッファ1170に供給され、RGB各6ビットのデータの上位各1ビット(D00, D10, D20)がROMデコーダ1140からニューバッファ1170に供給され、この1ビットに基づき、プリチャージ回路1030は、データ線を適切な電源電圧(VDD, VSS)を供給し、スイッチ1041、1042を選択し、バッファの回路1010又は回路1020を選択する。

40

【0008】

図24に示した駆動回路は、コモン反転駆動方式(対向電極Vcomの電圧を反転する駆動方式)の液晶表示回路に適用すると、低消費電力となり、例えば携帯電話端末などモバイ

50

ル端末の液晶表示装置の駆動回路として好適である。また、フルレンジ出力の駆動回路を用いることにより電源電圧を下げて更に低消費電力化を行うことができる。すなわち、図24の駆動回路は、第1のバッファ回路1010、第2のバッファ回路1020を切り替えて、フルレンジ出力を行うことのできる駆動回路である。

【0009】

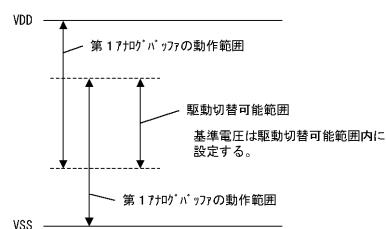

第1のバッファ回路1010、第2のバッファ回路1020は、それぞれ、トランジスタの閾値電圧 $V_{th}$ によって、動作範囲に制約が存在しており、バッファ回路1010とバッファ回路1020の切替は、バッファ回路1010とバッファ回路1020がともに動作する電圧範囲内( $V_{lim1} \sim V_{lim2}$ )で、駆動切替を行わなければならない。

【0010】

周囲温度等、条件が一定の場合、映像デジタルデータに応じて、バッファ回路1010とバッファ回路1020を切替えて駆動を行うことができる。

【0011】

以下では、本発明の理解のために、図6を参照して、液晶表示パネルのデータ線の駆動用に図24に示した駆動回路を用いた場合のバッファ回路1010、1020の切替えについて説明しておく。

【0012】

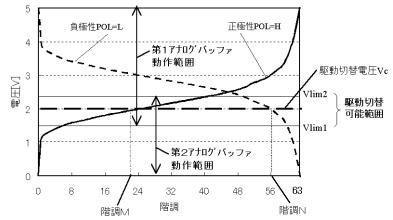

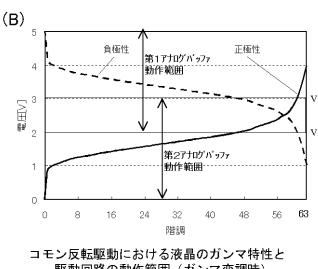

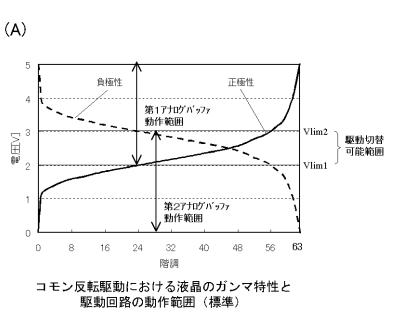

図6(A)は、コモン反転駆動(液晶表示装置の対向電極の電位 $V_{com}$ を高位側電源電圧と低位側電源電圧に切り替える)における液晶ガンマ特性(階調と信号電圧)と、駆動回路の動作範囲(標準)を説明するための図である。なお同図を含む以下の同様の図において、階調は映像デジタルデータと1対1に関連付けられており、極性に対応した2つのアナログ電圧をもつものとする。図6(B)は、コモン反転駆動における液晶ガンマ特性と駆動回路の動作範囲(ガンマ変調時)を説明するための図である。

【0013】

第1アナログバッファ(図24のバッファ回路1010に対応)の動作範囲は、電圧2V～5V(階調24～63)、第2アナログバッファ(図24のバッファ回路1020)の動作範囲は、電圧0V～3V(階調24～63)であり、駆動切替可能範囲は電圧2V～3Vであり、例えば映像デジタルデータの上位1ビットを用いて階調32で、第1アナログバッファと第2アナログバッファの動作を切替えて、切替時の電圧(映像デジタルデータに対応した入力電圧)は、正極性、負極性それぞれで第1アナログバッファと第2アナログバッファとがともに動作可能な範囲内にあるため、階調に対応したアナログ電圧を出力することができる。

【0014】

よって、図6(A)に示すような、液晶のガンマ特性(階調、電圧の特性)である場合、映像デジタルデータの上位1ビットにより32階調を境に、第1アナログバッファと第2アナログバッファを切替えることができる。

【0015】

しかしながら、図6(B)を示すように、ガンマ特性を変調する場合、正極性の特性(実線)において32階調の電圧は、第1アナログバッファ(図24のバッファ回路1010に対応)の動作範囲外であり、負極性の特性(破線)において32階調の電圧は、第2アナログバッファ(図24のバッファ回路1020に対応)の動作範囲外であり、32階調で、切替ることができなくなる。すなわち、第1アナログバッファの動作範囲は、電圧2V～5V(階調48～63)、第2アナログバッファの動作範囲は、電圧0V～3V(階調48～63)であり、32階調で第1アナログバッファと第2アナログバッファを切替えると、正極性では階調32～48の間で第1アナログバッファの出力は電圧 $V_{lim1}$ に固定され、負極性では階調32～48の間で第2アナログバッファの出力は電圧 $V_{lim2}$ に固定される。すなわち階調32～48の間では、当該階調に対応する映像デジタル信号が入力されても、階調に対応したアナログ電圧が出力されず、いわゆる階調に飛びが生じる。なお図6(B)では正極性と負極性でほぼ同様のガンマ特性の変調を行う場合の例を示しているが、極性により異なる変調も起こりうることは容易に理解できる。

10

20

30

40

50

**【0016】**

モバイル端末等では、広い温度動作条件での動作に対応するために、温度に対してのガンマ特性の変調により表示品質を維持したり、電源電圧を変調する等して電力消費を抑える等、様々な変調が必要とされる。この場合、映像デジタルデータ（階調データ）に応じた固定切替はできない、という問題点がある。

**【0017】****【発明が解決しようとする課題】**

したがって、この発明が解決しようとする課題は、動作範囲として、少なくとも高位側電位の範囲を有する第1のバッファ回路と少なくとも低位側電位の範囲を有する第2のバッファ回路とを駆動切替範囲で確実に行えるようにした駆動回路並びに該駆動回路を備えた液晶表示装置を提供することにある。

10

**【0018】****【課題を解決するための手段】**

上記課題を解決するための手段を提供する本発明は、その一つのアспектによれば、出力負荷を駆動する駆動回路において、入力信号電圧が入力される一の入力端子に入力端が共通に接続され、出力端子に出力端が共通に接続される二つのバッファ回路であって、動作範囲として、少なくとも高位側電位の範囲を有する第1のバッファ回路と、少なくとも低位側電位の範囲を有する第2のバッファ回路と、を備え、前記第1のバッファ回路と前記第2のバッファ回路の切替えを判断するための基準データであって、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる範囲内の電圧に対応した基準データを記憶保持する記憶部と、入力されたデータ信号と基準データとを比較する比較部と、が付加され、前記第1のバッファ回路と前記第2バッファ回路は、前記比較部の比較結果信号と制御信号に基づき、その動作と停止が制御される。

20

**【0019】**

本発明は、その別のアспектによれば、入力信号電圧が入力される一の入力端子に入力端が共通に接続され、出力端が一の出力端子に共通に接続される二つのバッファ回路であって、高位側電源電位にその動作範囲が及び第1のバッファ回路と、低位側電源電位にその動作範囲が及び第2のバッファ回路と、を備え、入力されるデジタルデータと信号電圧との関係に対応して、低位側電源電位からの特性を規定する正極性、高位側電源電位からの特性を規定する負極性のそれぞれについて、前記第1のバッファ回路と前記第2のバッファ回路の切替えを判断するための基準データであって、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる駆動切替可能範囲内の電圧に対応した、正極性、負極性の基準データを記憶保持する記憶部を備え、極性を特定する極性信号を入力し、前記極性信号の値に基づき正極性又は負極性の基準データを選択する選択部と、入力されたデジタルデータと、前記選択部から出力される基準データとを比較する比較部と、をさらに備え、前記第1のバッファ回路と前記第2バッファ回路は、前記比較部の比較結果信号と制御信号に基づき、その動作と停止が制御される。

30

**【0020】**

さらに別のアспектによれば、本発明に係る駆動回路は、入力信号電圧が入力される一の入力端子に入力端が共通に接続され、出力端子に出力端が共通に接続される二つのバッファ回路であって、動作範囲として、少なくとも高位側電位の範囲を有する第1のバッファ回路と、少なくとも低位側電位の範囲を有する第2のバッファ回路と、を備え、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる電圧範囲に対応した基準電圧を発生する基準電圧発生手段と、前記基準電圧発生手段から出力される基準電圧と、前記入力信号電圧とを比較する比較部と、を備え、前記第1のバッファ回路と前記第2バッファ回路は、前記比較部の比較結果信号と制御信号に基づき、その動作と停止が制御される。

40

**【0021】**

本発明において、前記制御信号が、動作を指示している場合において、前記比較部の比較結果信号が、前記入力信号電圧が前記基準電圧と等しいもしくは前記基準電圧より高いこ

50

とを示す値の場合、前記第1のバッファ回路を動作状態とし、前記第2バッファ回路を停止させ、前記比較部の比較結果信号が、前記入力信号電圧が前記基準電圧よりも低いことを示す値の場合、前記第2バッファ回路を動作状態とし、前記第1のバッファ回路を停止させる、構成とされている。

【0022】

さらに別のアスペクトによれば、液晶表示装置は、第1、第2の参照電圧間に直列形態に接続されている複数の抵抗を備え、各タップから階調電圧を生成する階調発生手段と、デジタルデータ信号を入力し前記階調発生手段の出力電圧から対応する電圧を選択出力するデコード回路を備え、上記した本発明に係る駆動回路は前記デコード回路の出力を入力し、出力負荷をなすデータ線を駆動する。

10

【0023】

【発明の実施の形態】

発明の実施の形態について説明する。本発明は、個々のアナログバッファでは、フルレンジ出力できなくても、二つのバッファを切替え、フルレンジ出力が可能な駆動回路において、さまざまな変調に対しても、二つのバッファの最適な方を選択して、常に正常な駆動を可能としている。すなわち、様々な条件の変調を複数のステップに分け、各変調ステップごとに、二つのバッファを、切替える階調に対応したデジタルデータを記憶したテーブルを設けておき、このテーブルのデータを基準データとし、映像デジタルデータと比較し、比較結果に基づき、最適なバッファを選択する。

【0024】

20

様々な条件の変調に対して、二つのバッファの切替可能範囲内にある電圧を基準電圧とし、選択された階調電圧と基準電圧を比較し、その大小に応じて二つのバッファのうち最適な一方を選択する。

【0025】

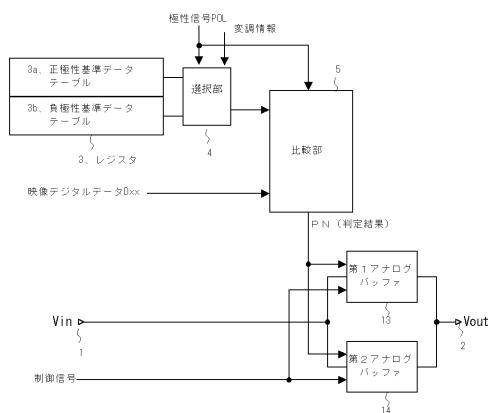

本発明に係る駆動回路は、その一実施の形態において、容量負荷等の出力負荷を駆動する駆動回路において、入力信号電圧( $V_{in}$ )が入力される一の入力端子(1)に入力端が共通に接続され、出力端子(2)に出力端が共通に接続される二つのアナログバッファ回路であって、動作範囲として、少なくとも高位側電位の範囲を有する第1のバッファ回路(13)と、少なくとも低位側電位の範囲を有する第2のバッファ回路(14)と、を備え、第1、第2のバッファ回路(13、14)の切替えを判断するための基準データであって、第1、第2のバッファ回路(13、14)がともに動作可能とされる範囲内の電圧に対応した基準データを記憶保持する記憶部(3)と、入力されたデータ信号と、基準データとを比較する比較部(5)と、が付加されている。第1、第2のバッファ回路(13、14)は、比較部(5)の比較結果信号(PN)と制御信号に基づき、その動作と停止が制御される構成とされている。

30

【0026】

あるいは、本発明は、その好ましい一実施の形態において、入力信号電圧が入力される一の入力端子に入力端が共通に接続され、出力端が一の出力端子に共通に接続される二つのバッファ回路であって、高位側電源電位にその動作範囲が及ぶ第1のバッファ回路(13)と、低位側電源電位にその動作範囲が及ぶ第2のバッファ回路(14)とを備え、階調と信号電圧に関する特性の標準状態及び変調時のそれぞれに対して、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる範囲内の入力信号電圧に対応した基準データを記憶保持する記憶部(3)と、変調を特定する変調情報に基づき、標準又は変調に対応した基準データを選択出力する選択部(4)と、入力されたデータと前記選択部から出力される基準データとを比較する比較部(5)と、前記比較部の比較結果信号と制御信号に基づき、前記第1のバッファ回路と前記第2バッファ回路は、動作と停止を制御する構成とされている。

40

【0027】

記憶部(3)は、入力されるデジタルデータ(映像デジタルデータ)と信号電圧との関係に対応して、低位側電源電位からの特性を規定する正極性、高位側電源電位からの特性を

50

規定する負極性のそれぞれについて、第1、第2のバッファ回路の切替えを判断するための基準データであって、第1、第2のバッファ回路がともに動作可能とされる駆動切替可能範囲内(図4参照)の電圧に対応した、正極性、負極性の基準データを記憶保持する記憶部(3a、3b)を備えている。

【0028】

選択部(4)は、極性を特定する極性信号(POL)を入力し、前記極性信号の値に基づき正極性又は負極性の基準データを選択する。

【0029】

記憶部(3a)は、好ましくは、階調と信号電圧に関するガンマ特性の標準時及び変調時のそれぞれに対して、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる範囲内の入力信号電圧に対応した、正極性の基準データを記憶保持する。

10

【0030】

記憶部(3b)は、好ましくは、階調と信号電圧に関するガンマ特性の標準時及び変調時のそれぞれに対して、前記第1のバッファ回路と前記第2のバッファ回路がともに動作可能とされる駆動切替可能範囲内の電圧に対応した、負極性の基準データを記憶保持する。

【0031】

選択部(4)は、極性を特定する極性信号(POL)に基づき、記憶部(3a、3b)の一方を選択し、変調を特定する変調情報に基づき、標準又は変調に対応した基準データを選択出力する。

【0032】

記憶部(3a)に、ガンマ特性の変調種別に応じて規定される正極性の基準データを複数記憶保持しておき、記憶部(3b)に、変調種別に応じて規定される負極性の基準データを複数記憶保持しておき、選択部(4)において、極性信号に基づき、記憶部(3a、3b)の一方を選択し、変調情報に基づき、変調種別に応じた基準データを選択出力するようにしてよい。

20

【0033】

制御信号が、動作を指示している場合において、比較部(5)の比較結果信号が、前記入力されたデータが前記基準データに等しいもしくは前記基準データより大であることを示す場合、第1のバッファ回路(13)を動作状態とし、第2バッファ回路(14)を停止させ、比較部の比較結果信号が、前記入力されたデータが前記基準データより小であることを示す場合、第2バッファ回路(14)を動作状態とし、第1のバッファ回路(13)を停止させる。

30

【0034】

本発明の実施の形態において、極性信号(POL)は、液晶表示装置の対向電極の共通電位(Vcom)の反転駆動における極性を示す論理値とされている。

【0035】

この実施の形態において、記憶部(3)と、選択部(4)とが、駆動回路の外部に設けられており、前記駆動回路とは電気的に接続される構成とされていてよい。なお、記憶部(3)はレジスタのほか、ROMあるいは、書き込み可能なEEPROM等不揮発性に半導体記憶装置であってよい。

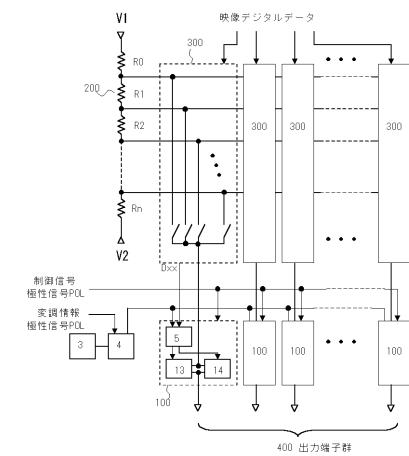

40

【0036】

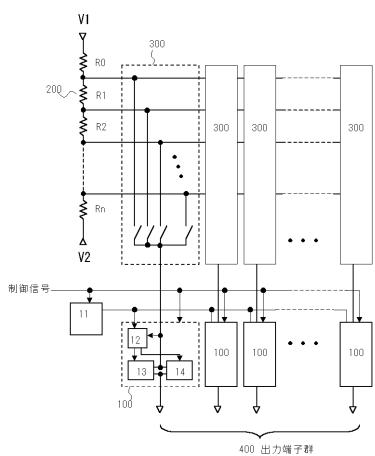

図3を参照すると、この実施の形態において、第1、第2の参照電圧間に直列形態に接続されている複数の抵抗(R0、R1、...、Rn)を備え、各タップから階調電圧を生成する階調発生手段(200)と、デジタルデータ信号を入力し前記階調発生手段(200)の出力電圧から対応する電圧を選択出力するデコード回路(300)を備え、本発明に係る駆動回路は、デコード回路(300)の出力を入力し、出力負荷を駆動する。記憶部(3)、選択部(4)を、駆動回路の複数個に対して、共通に一つ備え、駆動回路は、好ましくは、比較部(5)を内蔵している。

【0037】

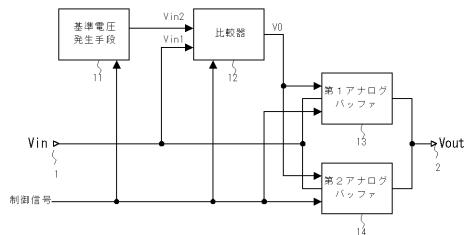

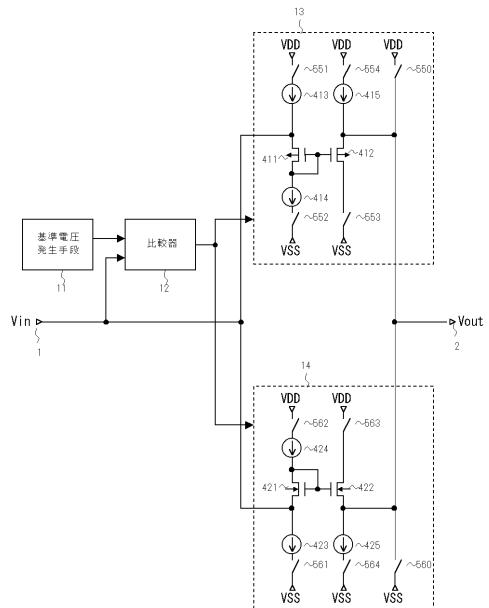

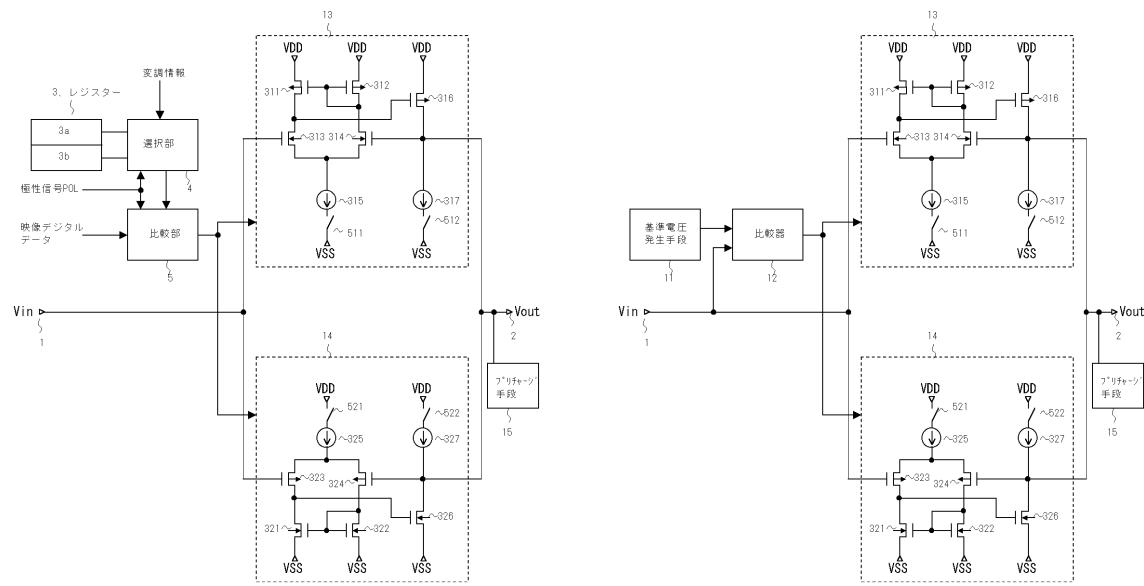

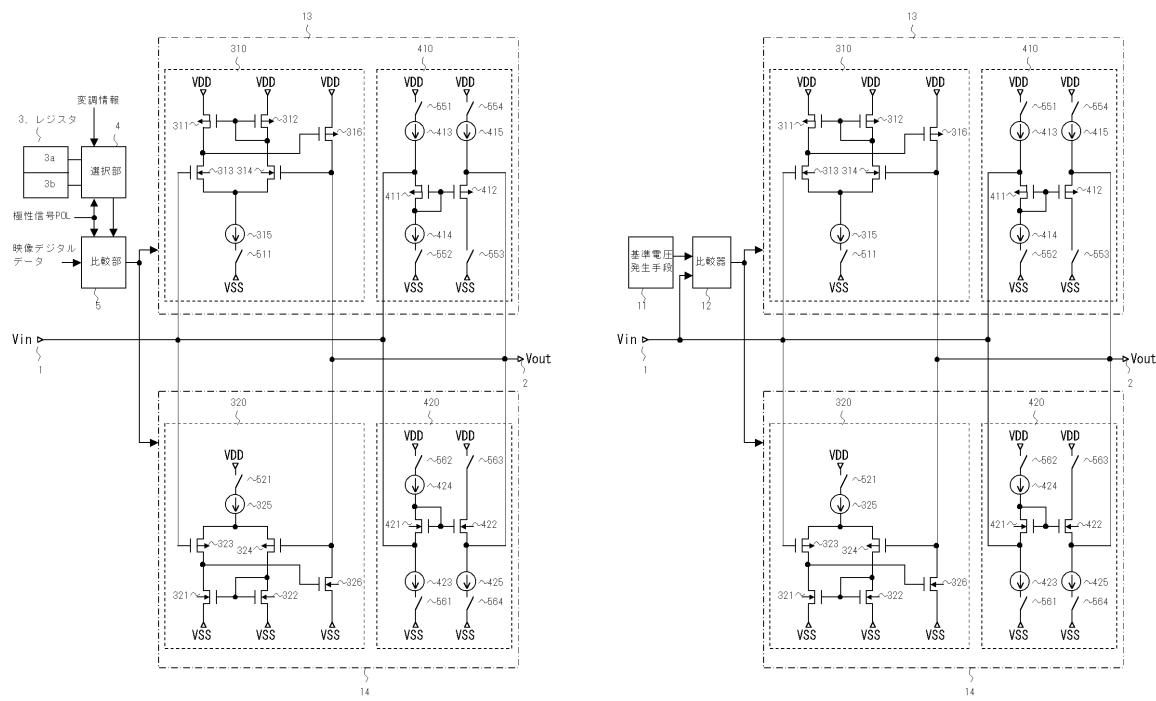

本発明は、別の実施の形態において、図7を参照すると、入力信号電圧Vinが入力され

50

る一の入力端子(1)に入力端が共通に接続され、出力端子(2)に出力端が共通に接続される二つのアナログバッファ回路であって、動作範囲として、少なくとも高位側電位の範囲を有する第1のバッファ回路(13)と、少なくとも低位側電位の範囲を有する第2のバッファ回路(14)と、を備え、第1、第2のバッファ回路と前記第2のバッファ回路がともに動作可能とされる電圧範囲に対応した基準電圧 $V_{in2}$ を発生する基準電圧発生手段(11)と、基準電圧発生手段(11)から出力される基準電圧 $V_{in2}$ と、入力信号電圧 $V_{in}$ (= $V_{in1}$ )とを比較する比較部(12)と、を備え、第1、第2のバッファ回路は、比較部(12)の比較結果信号( $VO$ )と制御信号に基づき、その動作と停止が制御される。制御信号が、動作を指示している場合において、比較部(12)の比較結果信号( $VO$ )が、入力信号電圧 $V_{in}$ が基準電圧以上であることを示す値の場合、第1のバッファ回路(13)を動作状態とし、第2バッファ回路(14)を停止させ、比較部(12)の比較結果信号が、入力信号電圧 $V_{in}$ が基準電圧 $V_{in2}$ よりも低いことを示す値の場合、第2バッファ回路(14)を動作状態とし、第1のバッファ回路(13)を停止させる、構成とされている。10

#### 【0038】

この実施の形態においては、比較器(12)の比較結果信号( $VO$ )と制御信号とを入力とし、前記制御信号がアクティブのときに、前記比較結果信号の論理演算結果を、前記第1のバッファ回路に出力する第1の論理回路(図16の22)と、比較器(12)の比較結果信号( $VO$ )を反転した信号と制御信号とを入力とし、制御信号がアクティブのときに、前記比較結果信号の反転信号の論理演算結果を、前記第2バッファ回路に出力する第2の論理回路(図16の23)と、を備えた構成としてもよい。20

#### 【0039】

この実施の形態において、液晶表示装置は、図9を参照すると、第1、第2の参照電圧間に直列形態に接続されている複数の抵抗( $R0$ 、 $R1$ 、...、 $Rn$ )を備え各タップから階調電圧を生成する階調発生手段(200)と、デジタルデータ信号を入力し階調発生手段(200)の出力電圧から対応する電圧を選択出力するデコード回路(300)を備え、本発明に係る駆動回路は、デコード回路(300)の出力を入力し、出力負荷を駆動する。基準電圧発生手段(11)を、駆動回路の複数個に対して共通に一つ備え、駆動回路は、好ましくは、比較器(12)を内蔵している。30

#### 【0040】

この実施の形態において、比較器(12)は、図10を参照すると、入力信号電圧 $V_{in}$ (= $V_{in1}$ )と基準電圧 $V_{in2}$ を差動入力する差動增幅回路と、前記差動增幅回路の出力にスイッチを介して接続される保持回路と、を備えている。保持回路は、差動增幅回路の一の出力端にスイッチ(113)を介して接続されるフリップフロップ回路からなる。フリップフロップは、スイッチ(113)に入力端が接続されている第1のインバータ(111)と、第1のインバータの出力端に入力端が接続されている第2のインバータ(112)と、前記第2のインバータの出力端と前記第1のインバータの入力端との間に接続されているスイッチ(114)を備え、第2のインバータ(112)の信号が比較結果信号( $VO$ )として出力され、差動增幅回路が動作時、スイッチ(113)をオン状態とし、前記差動增幅回路の出力を受けてラッチする際に、スイッチ(113)をオフし、スイッチ(114)をオンする。40

#### 【0041】

差動增幅回路は、差動対に駆動する電流源(105)と電源間に設けられるスイッチ(108)と、差動対の出力を受ける出力段トランジスタ(106)の電源バスに挿入されているスイッチ(109)と、を備え、比較動作時にのみこれらのスイッチがオンされ、低消費電力化が図られている。

#### 【0042】

差動增幅回路が動作時、スイッチ(108、109、113)をオン状態とし、差動增幅回路の出力を受けてラッチする際に、スイッチ(108、109、113)をオフし、スイッチ(114)をオンする制御が行われる。50

## 【0043】

この実施の形態において、比較器のフリップフロップは、図12を参照すると、スイッチ(113)を介して、差動増幅回路の前記出力段トランジスタの出力端に接続される第1のクロックドインバータ(111)と、第1のクロックドインバータの出力端に入力端が接続されている第2のクロックドインバータ(112)と、を備え、第2のクロックドインバータ(112)の出力端が前記第1のクロックドインバータ(111)の入力端に接続され、第2のクロックドインバータの出力端の信号(VO)、及び/又は前記第1のクロックドインバータの出力端の信号が、比較結果信号として出力され、差動増幅回路が動作時、(108、109、113)をすべてオン状態とし、前記差動増幅回路の出力を受けてラッチする際に、(108、109、113)をオフする制御が行われる、構成とされている。第2のクロックドインバータ(112)の出力端の負荷容量(C2)の容量値が、前記第1のクロックドインバータ(11)の出力端の負荷容量(C1)の容量値よりも大とされている。10

## 【0044】

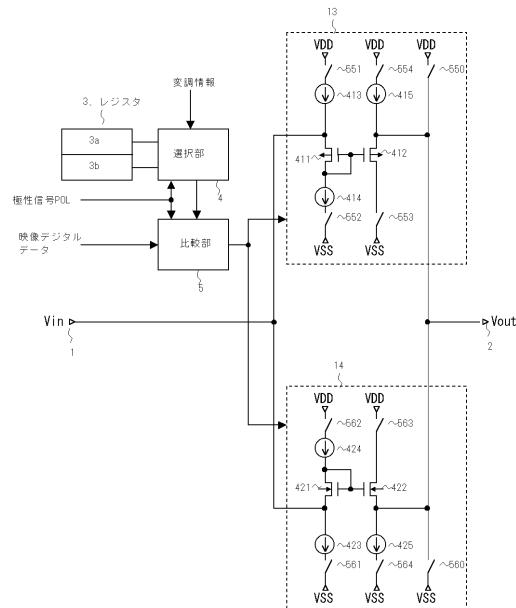

この実施の形態において、図17、図18を参照すると、第1のバッファ回路(13)は、低位側電源(VSS)と出力端子(2)に接続されるソースフォロワ構成のトランジスタ(412)と、入力信号電圧を入力し前記ソースフォロワ構成のトランジスタ(412)にゲートバイアス電圧を供給する第1のゲートバイアス制御手段(トランジスタ411、電流源414、413、スイッチ551、552)と、出力端子(2)を充電する手段(550)と、を備えている。20

## 【0045】

第2のバッファ回路(14)は、高位側電源(VDD)と出力端子(2)に接続されるソースフォロワ構成のトランジスタ(422)と、入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧を供給する第2のゲートバイアス制御手段(トランジスタ421、電流源424、423、スイッチ561、562)と、出力端子(2)を放電する手段(560)と、を備えている。

## 【0046】

この実施の形態において、図19、図20を参照すると、第1のバッファ回路(13)は、NチャネルMOSトランジスタ対(313、314)からなる差動対を備え、入力端子(1)が非反転入力端に接続され、出力端子(2)が反転入力端に接続されてなる差動増幅回路よりなる第1のボルテージフォロワ回路で構成され、第2のバッファ回路(14)は、PチャネルのMOSトランジスタ対(323、324)からなる差動対を備え、入力端子(1)が非反転入力端に接続され、出力端子(2)が反転入力端に接続されてなる差動増幅回路よりなる第2のボルテージフォロワ回路で構成されている。出力端子(2)を充電、放電する手段(15)を備えている。30

## 【0047】

より詳細には、第1のバッファ回路(13)は、NチャネルMOSトランジスタ対(313、314)からなる差動対と、前記差動対の出力と高位側電源間に接続される負荷回路(311、312)と、前記差動対を駆動する電流源(315)と、前記電流源と低電位電源間の電流パスをオン及びオフ制御する第1のスイッチ(511)と、を備えた差動段と、前記差動対の出力を入力とし、出力が前記出力端子に接続されているMOSトランジスタ(316)と、出力端子(2)と低位側電源間に接続されている電流源(317)及びスイッチ(512)と、を有する出力段と、を備え、差動対のMOSトランジスタ対(313、314)のゲートには入力端子(1)と出力端子(2)が接続されている。第2のバッファ回路(14)は、PチャネルMOSトランジスタ対からなる差動対(323、324)と、前記差動対の出力と低位側電源間に接続される負荷回路(321、322)と、前記差動対を駆動する電流(325)源と、電流源と高電位電源間の電流パスをオン及びオフ制御するスイッチ(521)と、を備えた差動段と、差動対の出力を入力とし、出力が前記出力端子に接続されているMOSトランジスタ(326)と、出力端子(2)と低位側電源間に接続されている電流源(327)及びスイッチ(522)と、を有する40

出力段と、を備え、前記差動対のMOSトランジスタ対(323、324)のゲートには前記入力端子(1)と前記出力端子(2)が接続されている。

【0048】

この実施の形態において、図21、図22を参照すると、第1のバッファ回路(13)は、NチャネルMOSトランジスタ対(313、314)からなる差動対を備え、入力端子(1)が非反転入力端に接続され、前記出力端子(2)が反転入力端に接続されてなる差動増幅回路よりなる第2のボルテージフォロワ回路と、低位側電源と出力端子に接続されるソースフォロワ構成のトランジスタ(412)と、入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧を供給する第1のゲートバイアス制御手段(トランジスタ411、電流源414、413、スイッチ551、552)とを備えている。第2のバッファ回路(14)は、PチャネルのMOSトランジスタ対(323、324)からなる差動対を備え、段前記入力端子が非反転入力端に接続され、前記出力端子が反転入力端に接続されてなる差動増幅回路よりなる第2のボルテージフォロワ回路よりなり、高位側電源と前記出力端子に接続されるソースフォロワ構成のトランジスタ(422)と、入力信号電圧を入力し前記ソースフォロワ構成のトランジスタにゲートバイアス電圧を供給する第2のゲートバイアス制御手段(トランジスタ421、電流源424、423、スイッチ561、562)と、を備えている。

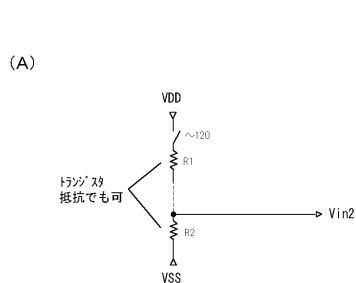

【0049】

この実施の形態において、基準電圧発生手段(11)は、第1、第2の参照電圧の間に接続されている複数の抵抗素子(R1、R2)と、スイッチ(120)を備え、スイッチ(120)がオン状態のとき、抵抗の接続点から、第1、第2のバッファ回路の動作範囲の重なりで規定される駆動切替範囲内の電圧が基準電圧として出力される。なお複数の抵抗素子(R1、R2)としては、ダイオード接続したトランジスタ等を用いてもよい。

【0050】

【実施例】

上記した実施の形態についてさらに詳細に説明すべく、本発明の実施例について図面を参照して以下に説明する。図1は、本発明に係る駆動回路の一実施例の構成を示す図である。図1を参照すると、この実施例の駆動回路は、階調と電圧特性の変調の種別毎(標準時も含んでもよいことは勿論である)に、第1、第2のアナログバッファ回路13、14を切り替える階調に対応する基準データ(正極性基準データ、負極性基準データ)を格納する正極性基準データテーブル3a、負極性基準データテーブル3bを備えたレジスタ3と、正極性基準データテーブル3aと負極性基準データテーブル3bの出力を入力し、極性信号POLに基づき、一方を選択し、変調情報に基づき変調に対応した基準データを選択出力する選択部4と、入力される映像デジタルデータと、選択部4の出力を比較する比較部5と、比較部5の比較結果出力と、制御信号を入力し、動作、停止が制御され、入力端子1に入力端が共通に接続され、出力端が、出力端子2に共通に接続されている、正極性、負極性駆動用の第1、第2のアナログバッファ回路13、14と、を備えている。正極性基準データテーブル3a、負極性基準データテーブル3bのデータは、映像デジタルデータと、そのビット幅、2進表示形式は同一とされる。比較器5は、二つのデジタルデータの大小関係を比較する公知のデジタルコンパレータよりなる。入力端子1には比較部5に入力される映像デジタルデータに対応したアナログ電圧が入力される。

【0051】

任意の変調ステップにおいて、変調ステップに対応した基準データ(正極性、負極性)を、極性信号POLに応じて選択部4で選択し、選択された基準データと映像デジタルデータを比較部5で比較し、映像デジタルデータに対応した階調が切替階調よりも、低位か高位かを判別し、比較部5から出力される判別信号PNにより、第1、第2のアナログバッファ回路13、14の一方を選択して駆動する。制御信号は、第1、第2のアナログバッファ回路13、14の動作制御を行う。極性信号POLは、Vcom反転駆動制御において、Vcom電圧が低位側電位(正極駆動)、高位側電位(負極駆動)であるかによってHigh、Lowレベルとされる。

## 【0052】

図2は、図1の回路の制御動作を示す図である。制御信号がLowレベルのとき、第1、第2のアナログバッファ回路13、14は比較部5の出力PNに関係なく動作が停止（非活性化）される。制御信号がHighレベルのとき、比較部5の出力PNがHighレベルのとき、第1のアナログバッファ回路13が動作し、第2のアナログバッファ回路14が停止（非活性化）される。

## 【0053】

制御信号がHighレベルのとき、比較部5の出力PNがLowレベルのとき、第2のアナログバッファ回路14が動作し、第1のアナログバッファ回路13が停止（非活性化）される。

10

## 【0054】

図3は、本発明の一実施例の駆動回路を、多出力駆動回路に適用した構成を示す図である。この多出力駆動回路は、例えば液晶表示装置のデータ線の駆動に用いられる。図3を参照すると、この多出力駆動回路は、参照電圧として例えば電源V1と電源V2間に複数の抵抗素子R0～Rnが直列に接続されて抵抗ストリングを構成し、抵抗ストリングのタップから、極性に対応したアナログ電圧を出力する階調電圧発生手段200を備えている。階調電圧発生手段200からの階調電圧（アナログ電圧）は、デコーダ300に入力され、デコーダ300は、映像デジタル信号を入力し、映像デジタル信号に対応する階調電圧を選択出力し、駆動回路100に入力される。なお階調電圧発生手段200は、電源V1と電源V2がそれぞれ固定電圧とし、階調数の2倍の抵抗ストリングのタップから極性に対応したアナログ電圧を出力する構成でもよく、また電源V1と電源V2を極性反転と同期して電位レベルを反転させ、階調数と同数の抵抗ストリングのタップから極性に対応したアナログ電圧を出力する構成としてもよい。

20

## 【0055】

駆動回路100は、図1を参照して説明した前記実施例の構成からなり、第1、第2のアナログバッファ回路13、14、比較部5を備え、レジスタ3と比較部4は、駆動回路100に共通に備えている。

## 【0056】

図4は、コモン反転駆動における液晶のガンマ特性と駆動回路の動作範囲の一例を示す図である。正極性動作時のガンマ特性を実線（極性信号POL=H）、負極性動作時のガンマ特性を破線（極性信号POL=L）で表し、駆動切替電圧Vcが駆動切替可能範囲V1im1、V1im2の範囲内にあるように、正極性基準データ、負極性基準データがレジスタ3に格納されている。すなわち、この実施例によれば、第1アナログバッファ回路13と第2のアナログバッファ回路14の切替えは、変調の種別ごとに、駆動切替可能範囲V1im1、V1im2内の電圧Vcに対応する基準データを設けている。図4の例（標準状態とする）では、駆動切替電圧Vcを正極性と負極性で共通とし、極性ごとに電圧Vcに最も近い階調M、N（正極性は階調M、負極性は階調N）に対応するデジタルデータを標準状態の基準データとして予め設定している。そして、入力される映像デジタルデータが、基準データと等しいもしくは基準データより大の値となるときに第1アナログバッファ回路13を動作させ、基準データより小の値となるときに第2のアナログバッファ回路14を動作させる。

30

## 【0057】

一方、比較例として、図6（A）、（B）を参照すると、第1アナログバッファ（図1のバッファ回路13に対応）と第2アナログバッファ（図1のバッファ回路14に対応）の動作切替えを、0～63階調のうち、例えば映像デジタルデータの上位1ビットにより階調32で行う場合、図6（A）では、階調32に対応する信号電圧（入力される階調電圧）は、第1アナログバッファ、第2アナログバッファの駆動切替可能範囲（V1im1、V1im2）内で切替が可能であるが、変調が行われた図6（B）では、階調32に対応する信号電圧は駆動切替可能範囲（V1im1、V1im2）外となり、正極性では階調32～48の間で第1アナログバッファの出力は電圧V1im1に固定され、負極性では

40

50

階調 32～48 の間で第2アナログバッファの出力は電圧 V1im2 に固定される。すなわち階調 32～48 の間では、当該階調に対応する映像デジタル信号が入力されても、階調に対応したアナログ電圧が出力されず、いわゆる階調に飛びが生じる。これに対して、本発明によれば、第1アナログバッファと第2アナログバッファの動作切替えを駆動切替可能範囲 (V1im1, V1im2) 内の電圧で行っており、すなわち変調ごとに、切替え時の階調データは可変される制御が行われ、階調とび等は生じない。

【0058】

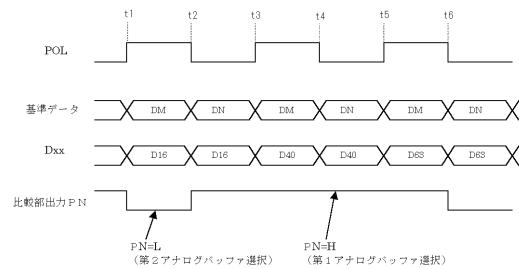

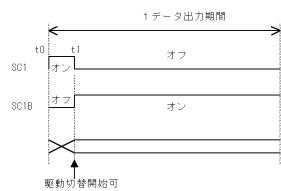

図5は、図4のガンマ特性をもつ変調ステップ時におけるタイミングチャートを示す図である。図5を参照すると、時刻(タイミング) t1 では、極性信号 P0L が High レベルとなり、基準データは正極性データ DM (階調 M に対応するデータ) となり、階調 16 に対する映像デジタルデータ D16 と比較され、比較部出力 PN は High レベルから Low レベルとなり、第1のアナログバッファ回路 13 から第2のアナログバッファ回路 14 に切替えられ、第2のアナログバッファ回路 14 が動作する。

【0059】

時刻 t2 では極性信号 P0L が Low レベルとなり、基準データは負極性データ DN (階調 N に対応するデータ) となり、階調 16 に対する映像デジタルデータ D16 と比較され、比較部出力 PN は High レベルとなり、第1のアナログバッファ回路 13 が選択される。

【0060】

時刻 t3 において極性信号 P0L が High レベルとなり、基準データは正極性データ (DM) となり、階調 40 に対する映像デジタルデータ D40 と比較され、比較部出力 PN は High レベルとなり、第1のアナログバッファ回路 14 が選択されて動作する。

【0061】

時刻 t4 では極性信号 P0L が Low レベルとなり、基準データは負極性データ (DN) となり、階調 40 に対する映像デジタルデータ D40 と比較され、比較部出力 PN は High レベルとなり、第1のアナログバッファ回路 13 が選択される。

【0062】

時刻 t5 において極性信号 P0L が High レベルとなり、基準データは正極性データ (DM) となり、階調 63 に対する映像デジタルデータ D63 と比較され、比較部出力 PN は High レベルとなり、第1のアナログバッファ回路 14 が選択されて動作する。

【0063】

時刻 t6 では極性信号 P0L が Low レベルとなり、基準データは負極性データ (DN) となり、階調 63 に対する映像デジタルデータ D63 と比較され、比較部出力 PN は High レベルとなり、第1のアナログバッファ回路 13 が選択される。

【0064】

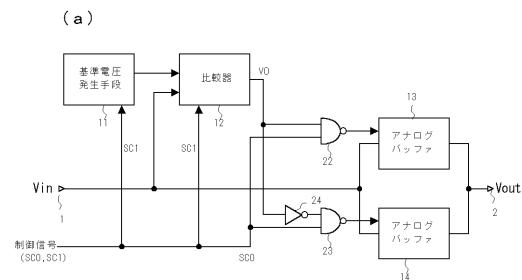

図7は、本発明の別の実施例の構成を示す図である。図7を参照すると、基準電圧発生手段 11 と、基準電圧発生手段 11 の出力電圧と、入力信号電圧 Vin (= Vin1) を比較する比較器 12 と、比較器 12 の出力と、制御信号を入力し、動作、停止が制御され、入力端子 1 に入力端が共通に接続され、出力端が、出力端子 2 に共通に接続されている、正極性、負極性駆動用の第1、第2のアナログバッファ回路 13、14 と、を備えている。

【0065】

基準電圧発生手段 11 は、様々な変調ステップ毎に、第1、第2のアナログバッファ 13、14 が切替駆動できる基準電圧 Vc を生成する。すなわち、基準電圧 Vc は第1、第2のアナログバッファ 13、14 がともに動作可能な電圧範囲内に設ける。

【0066】

比較器 12 では、映像デジタルデータにより選択された階調電圧 Vin を基準電圧 Vc と比較し、その大小に応じて第1、第2のアナログバッファ 13、14 の一方を選択して駆動する。制御信号は、基準電圧発生手段 11、比較器 12、第1、第2のアナログバッファ回路 13、14 の動作を制御し、必要時以外、動作は停止される。なお、比較器 12 の

10

20

30

40

50

比較処理の遅延時間分、入力信号電圧  $V_{in}$  を遅延回路（図示されない）で遅延させて第1、第2のアナログバッファ回路13、14に供給する構成としてもよいことは勿論である。

#### 【0067】

図8は、図7の構成の制御動作を示す図である。制御信号がLowレベルのとき、第1、第2のアナログバッファ回路13、14は動作を停止（非活性化）される。制御信号がHighレベルのとき、比較器12の出力がHighレベルのとき、第1のアナログバッファ回路13が動作し、第2のアナログバッファ回路14が停止（非活性化）される。

#### 【0068】

制御信号がHighレベルのとき、比較部12の出力がLowレベルのとき、第2のアナログバッファ回路14が動作し、第1のアナログバッファ回路13が停止（非活性化）される。

10

#### 【0069】

図9は、図7に示した駆動回路を多出力駆動回路に適用した図である。多出力駆動回路は、例えば液晶表示装置のデータ線の駆動に用いられる。図9を参照すると、この多出力駆動回路は、参照電圧として例えば電源V1と電源V2間に抵抗R1～Rnが複数接続され抵抗ストリングを構成し、抵抗ストリングのタップから、極性に対応したアナログ電圧を出力する階調電圧発生手段200を備えている。階調電圧発生手段200からの階調電圧（アナログ電圧）は、デコーダ300に入力され、デコーダ300は、映像デジタル信号を入力し、映像デジタル信号に対応する階調電圧を選択出力し、駆動回路100に入力される。なお階調電圧発生手段200は、電源V1と電源V2がそれぞれ固定電圧とし、階調数の2倍の抵抗ストリングのタップから極性に対応したアナログ電圧を出力する構成でもよく、また電源V1と電源V2を極性反転と同期して電位レベルを反転させ、階調数と同数の抵抗ストリングのタップから極性に対応したアナログ電圧を出力する構成としてもよい。

20

駆動回路100は、図7を参照して説明した前記実施例の構成からなり、第1、第2のアナログバッファ回路13、14、比較器12を備え、基準電圧発生手段11は、駆動回路100に共通に備えている。

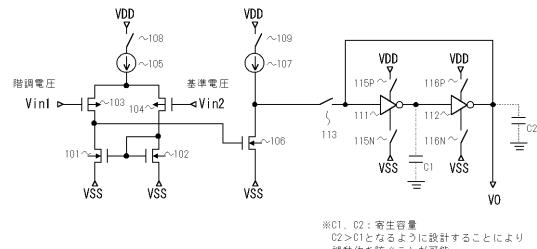

#### 【0070】

図10は、図7に示した実施例における比較器12の構成の一例を示す図である。図10を参照すると、この比較器12は、ソースが共通接続され、定電流源105の一端に接続され、差動対を構成するPチャネルMOSトランジスタ103、104を備え、PチャネルMOSトランジスタ103、104のゲートには、階調電圧（入力信号電圧  $V_{in}$  ）、基準電圧が入力され、PチャネルMOSトランジスタ103、104のドレインは、カレントミラー回路を構成するNチャネルMOSトランジスタ101、102（トランジスタ102が入力側、トランジスタ101が出力側）に接続されている。定電流源105の他端はスイッチ108を介して高位側電源VDDに接続されている。

30

#### 【0071】

PチャネルMOSトランジスタ103のドレインは、ソースが低位側電源VSSに接続され、ドレインが、定電流源107の一端に接続されたNチャネルMOSトランジスタ106のゲートに接続されており、定電流源107の他端はスイッチ109を介して高位側電源VDDに接続されている。

40

#### 【0072】

NチャネルMOSトランジスタ106のドレインはスイッチ113の一端に接続され、スイッチ113（トランスファスイッチ）の他端は、入力と出力を互いに接続した二つのインバータよりなるフリップフロップに接続されている。すなわち、スイッチ113（トランスファスイッチ）の他端は、インバータ111の入力端に接続され、インバータ111の出力端は、インバータ112の入力端に接続され、インバータ112の出力端は、スイッチ114を介してインバータ111の入力端に接続されている。インバータ111、112の出力端は、出力VOB、VOとして取り出される。

50

## 【0073】

図11は、図10にその回路構成を示した比較器12の動作を説明するタイミング図である。制御信号により、スイッチ108、109、113がオン、スイッチ114がオフのとき、差動増幅回路が活性化し、比較結果が、フリップフロップに伝達される。

## 【0074】

図10の比較器12の回路動作について説明する。はじめに、スイッチ108、109、スイッチ113がオンとされ、スイッチ114がオフとされ、差動回路が動作し、階調電圧と基準電圧の電圧比較が行われる。階調電圧 $V_{in1}$ の方が基準電圧 $V_{in2}$ よりも低いときは、トランジスタ103の方が、トランジスタ104よりも、多くのドレイン電流が流れ、NチャネルMOSトランジスタ106のゲート電圧が増大し、トランジスタ105のドレインと定電流源107の接続点電位が低電位レベルとなる。 $V_{in}$ の方が基準電圧 $V_{in2}$ よりも高いときは、トランジスタ104の方に多くのドレイン電流が流れ、NチャネルMOSトランジスタ106のゲート電圧が減少し、トランジスタ105のドレインと定電流源107の接続点電位が高電位レベルとなる。差動回路の出力は、スイッチ113を介して、インバータ111に入力される（このときスイッチ114はオフ）。

10

## 【0075】

スイッチ113がオフし（スイッチ108、109もオフする）、スイッチ114がオンし、インバータ2段によるフリップフロップが構成され、インバータ111の入力データ（比較結果）がラッチされ、 $V_0$ として出力される。

## 【0076】

20

図12は、本発明の一実施例の比較器12の別の構成を示す図である。この回路は、図10の比較器よりも低消費電力とされる。

## 【0077】

図12において、差動回路の構成は、図11に示したものと同様である。フリップフロップにおいて、インバータ111の電源バスの高位側電源 $V_{DD}$ との間にスイッチ115P、低位側電源 $V_{SS}$ との間にスイッチ115Nが設けられており、インバータ112の電源バスの高位側電源 $V_{DD}$ の間にスイッチ116P、低位側電源 $V_{SS}$ との間に116Nが設けられており、図11のスイッチ114が削除されている。インバータ111の出力の寄生容量 $C_1$ 、インバータ112の出力の寄生容量 $C_2$ の蓄積電荷を利用して記憶動作をしている。容量 $C_2$ は容量 $C_1$ よりも大とされる。インバータ111による容量 $C_1$ の充放電の期間は、インバータ112による容量 $C_2$ の充放電の期間よりも短時間とされ、フリップフロップは安定動作する。

30

## 【0078】

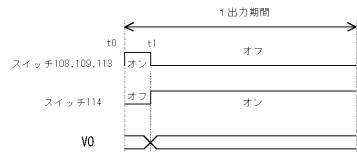

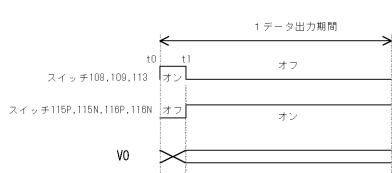

図13は、図12の回路の動作を示すタイミング図である。1出力期間の最初の期間で、スイッチ108、109、113がオンし、差動回路の比較結果がフリップフロップのインバータ111の入力端にまで伝達され、その期間、スイッチ115P、115N、116P、116Nはオフとされる。次に、スイッチ108、109、113がオフし、スイッチ115P、115N、116P、116Nはオンし、フリップフロップがデータを記憶する。

## 【0079】

40

なお、インバータ112の負荷容量 $C_2$ とインバータ111の負荷容量 $C_1$ について、 $C_2 > C_1$ とすることで、誤動作を防ぐことができる。すなわち、インバータ111の出力負荷に充電、放電による信号の立ち上り、立下り時間はインバータ112よりも短く設定され、フリップフロップは安定動作する。

## 【0080】

スイッチ113がオンとされている時点で、差動比較回路の出力が、容量 $C_2$ を充電、又は放電し、比較器の出力 $V_0$ は、スイッチ113がオフする時刻 $t_1$ の前に値を変化させている。

なお図12の比較器は、定電流源105、107で制御される電流を十分小さく抑えた場合、スイッチ108、109、113がオンしている期間のインバータ111の入力電位

50

変化が緩やかとなる場合があるが、スイッチ 115P、115N、116P、116Nがオフとなっているためインバータ 111、112の貫通電流は生じない。そしてインバータ 111の入力電位が High 又は Low に安定後にスイッチ 108、109、113をオフし、スイッチ 115P、115N、116P、116Nをオンすれば、インバータ 111、112は速やかに動作し、貫通電流による消費電力のロスなく比較器を動作させることができるために、低消費電力化が実現できる。また図 12 には記載されていないが、比較器の出力 VO が入力される回路の電源バスにスイッチを設け、スイッチ 115P、115N、116P、116N と同期して制御すれば更によい。一方、図 10 の比較器では、定電流源 105、107で制御される電流を十分小さく抑えた場合、インバータ 111、112の貫通電流による消費電力のロスが増し、十分な低消費電力を実現できない。 10

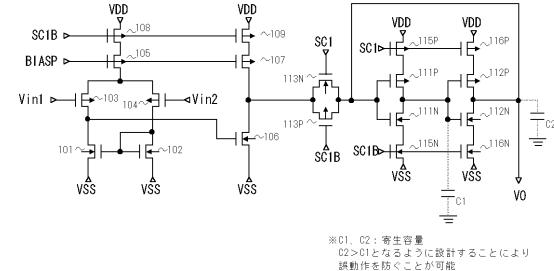

#### 【0081】

図 14 は、図 12 に示した回路構成のトランジスタレベルの構成の一例を示す図である。図 14 を参照すると、図 12 の定電流源 105、107 は、ゲートにバイアス電圧 BIA SP が供給される P チャネル MOS トランジスタで構成されており、図 12 のスイッチ 108、109 は、ゲートに制御信号 SC1B (SC1 の反転信号) が供給される P チャネル MOS トランジスタで構成されている。

#### 【0082】

また図 14 を参照すると、図 12 のスイッチ 113 は、CMOS トランジスタゲートよりも、P チャネル MOS トランジスタ 113P のゲートには、制御信号 SC1B が供給され、N チャネル MOS トランジスタ 113N のゲートには、制御信号 SC1 が供給される。スイッチ 113 は制御信号 SC1 が High のときオンする。 20

#### 【0083】

インバータ 111 は、クロックドインバータよりも、ゲートが共通接続され、ドレインが共通接続され、CMOS (complementary MOS) インバータを構成する P チャネル MOS トランジスタ 111P 及び N チャネル MOS トランジスタ 111N と、ソースが電源 VDD に接続され、ゲートが制御信号 SC1 に接続され、ドレインが P チャネル MOS トランジスタ 111P のソースに接続された P チャネル MOS トランジスタ 115P と、ゲートが制御信号 SC1B に接続され、ドレインが N チャネル MOS トランジスタ 111N のソースに接続された N チャネル MOS トランジスタ 115N からなる。

#### 【0084】

インバータ 112 は、クロックドインバータよりも、ゲートが共通接続され、ドレインが共通接続され、CMOS インバータを構成する P チャネル MOS トランジスタ 112P 及び N チャネル MOS トランジスタ 112N と、ソースが電源 VDD に接続され、ゲートが制御信号 SC1 に接続され、ドレインが P チャネル MOS トランジスタ 112P のソースに接続された P チャネル MOS トランジスタ 116P と、ゲートが制御信号 SC1B に接続され、ドレインが N チャネル MOS トランジスタ 112N のソースに接続された N チャネル MOS トランジスタ 116N からなる。 30

#### 【0085】

図 15 は、図 14 に示した比較器のタイミング動作を示す図である。一出力期間の最初の期間 (t0 ~ t1) において、制御信号 SC1 が High レベル (オン) とされ (SC1B は Low レベル)、つづいて Low レベルとされる (SC1B は High レベル)。制御信号 SC1 が High レベルで、差動回路が活性化し、スイッチ 13 はオンとされ、インバータ 111、112 は非活性状態とされ、制御信号 SC1 が Low レベルでスイッチ 13 はオフし、インバータ 111、112 が活性化する。 40

#### 【0086】

図 16 は、本発明の別の実施例の構成を示す図である。図 16 (a) を参照すると、この回路は、基準電圧発生手段 11、比較器 12、第 1 のアナログバッファ回路 13、第 2 のアナログバッファ回路 14、を備え、比較器 12 の出力 VO と制御信号 SC0 を入力とする NAND 回路 22 と、比較器 12 の出力 VO をインバータ 24 で反転した信号と制御信号 SC0 を入力とする NAND 回路 23 を備え、NAND 回路 22、NAND 回路 23 の 50

出力が第1のアナログバッファ回路13、第2のアナログバッファ回路14に制御信号として供給される。

【0087】

なお、制御信号のSC1は、図14に示した比較器12の動作を制御する信号である。

【0088】

図16(b)は、図の動作を説明するためのタイミング図である。SC0は制御信号、VOは比較器12の出力である。SC0がLowレベルのとき、NAND22, 23の出力はHighレベルであり、SC0がHighレベルのとき、NAND22はVOの反転信号を出力し、NAND23はVOを出力する。

【0089】

図17は、図1に示した構成において、アナログバッファ回路13、14の構成の一例を示す図である。図17を参照すると、第1のアナログバッファ回路13は、入力端子1と高位側電源VDD間に直列に接続された定電流源413、及びスイッチ551と、入力端子1にソースが接続され、ゲートとドレインが接続されたPチャネルMOSトランジスタ411と、PチャネルMOSトランジスタ411のドレインと低位側電源VSS間に直列に接続された定電流源414、及びスイッチ552と、出力端子2と高位側電源VDD間に直列に接続された定電流源415、及びスイッチ554と、出力端子2にソースが接続され、PチャネルMOSトランジスタ411のゲートにゲートが共通接続され、ドレインがスイッチ553を介して低位側電源VSSに接続されたPチャネルMOSトランジスタ412と、を備え、電流源415とスイッチ554の直列回路と並列に、出力端子2と高位側電源VDD間にスイッチ550が接続されている。

10

【0090】

第2のアナログバッファ回路14は、入力端子1と低位側電源VSS間に直列に接続された定電流源423、及びスイッチ561と、入力端子1にソースが接続され、ゲートとドレインが接続されたNチャネルMOSトランジスタ421と、NチャネルMOSトランジスタ421のドレインと高位側電源VDD間に直列に接続された定電流源424、及びスイッチ562と、出力端子2と低位側電源VSS間に直列に接続された定電流源425、及びスイッチ564と、出力端子2にソースが接続され、NチャネルMOSトランジスタ421のゲートにゲートが共通接続され、ドレインがスイッチ563を介して高位側電源VDDに接続されたNチャネルMOSトランジスタ422とを備え、電流源425とスイッチ564の直列回路と並列に、出力端子2と低位側電源VSS間にスイッチ560が接続されている。

20

【0091】

第1のアナログバッファ回路13の動作の一例を以下に説明する。制御信号により、スイッチ550がオンし、スイッチ551、552、553、554がオフとされ、つづいてスイッチ551、552がオン状態とされ、つづいてスイッチ550をオフ、スイッチ553、554がオンとされる制御が行われる。

30

【0092】

スイッチ551、552がオンとされると、トランジスタ411の作用により、トランジスタ411、412の共通ゲート電位VG1は入力信号電圧Vinからトランジスタ411のゲート・ソース間電圧Vgs1だけずれた電圧となり、

$$VG1 = Vin + Vgs1 \dots (1)$$

40

で表される。なおゲート・ソース間電圧Vgsはソースに対するゲートの電位で表す。

【0093】

このとき、トランジスタはドレイン・ソース間電流Idsとゲート・ソース間電圧Vgsとの間に固有のVI特性を有し、トランジスタ411のゲート・ソース間電圧Vgs1は、トランジスタ411のIds-Vgs特性と電流源414で制御される電流I1によって一意に定まる。

【0094】

トランジスタ411のドレイン・ソース間電流がI1(電流源414の電流値)となる時

50

のゲート・ソース間電圧を  $V_{GS1}$  ( I 1 ) とすると、トランジスタ 1 のゲート電圧  $V_1$  は、

$$V_{G1} = V_{in} + V_{GS1} \quad \dots (2)$$

で安定となる。

【 0 0 9 5 】

トランジスタ 412 のゲートに電圧  $V_{G1}$  が印加されると、出力電圧  $V_{out}$  は電圧  $V_G$  1 からトランジスタ 412 のゲート・ソース間電圧  $V_{GS2}$  だけずれた電圧となり、

$$V_{out} = V_{G1} - V_{GS2} \quad \dots (3)$$

で表される。出力電圧  $V_{out}$  はトランジスタ 412 のドレン・ソース間電流が  $I_3$  ( 電流源 415 の電流値 ) と等しくなるところで安定する。このときのトランジスタ 412 のゲート・ソース間電圧  $V_{GS2}$  は、トランジスタ 412 の  $I_{ds} - V_{GS}$  特性と電流  $I_3$  により、 $V_{GS2}$  ( I 3 ) となり、出力電圧  $V_{out}$  は、

$$V_{out} = V_{G1} - V_{GS2} ( I_3 ) \quad \dots (4)$$

で安定となる。

【 0 0 9 6 】

上式 (2) と (4) から、入力信号電圧  $V_{in}$  が一定のときの出力電圧  $V_{out}$  は、

$$V_{out} = V_{in} + V_{GS1} ( I_1 ) - V_{GS2} ( I_3 ) \quad \dots (5)$$

となる。

【 0 0 9 7 】

このとき、出力電圧範囲は、電源電圧  $V_{DD}$  と電源電圧  $V_{SS}$  の電圧範囲から少なくともトランジスタ 412 のゲート・ソース間電圧  $V_{GS2}$  ( I 3 ) の電圧差だけ狭い電圧範囲となる。ここでトランジスタ 411、412 のそれぞれのゲート・ソース間電圧  $V_{GS1}$  ( I 1 )、 $V_{GS2}$  ( I 3 ) が等しくなるように電流源 414 と 415 の電流  $I_1$ 、 $I_3$  を制御すれば、式 (5) より出力電圧  $V_{out}$  は入力信号電圧  $V_{in}$  と等しい電圧となる。また、トランジスタの特性変動が生じても、

$$V_{GS1} ( I_1 ) - V_{GS2} ( I_3 )$$

が変化しないようなトランジスタ 411、412 の素子サイズ及び電流  $I_1$ 、 $I_3$  を設定することで、トランジスタの特性変動によらずに、高精度の電圧出力が可能である。

【 0 0 9 8 】

具体的には、トランジスタ 411、412 の素子サイズ及び電流  $I_1$ 、 $I_3$  をそれぞれ等しく設定する、あるいはトランジスタ 411、412 のチャネル長を揃えて、チャネル幅比に応じて電流  $I_1$ 、 $I_3$  を設定する等を行うことで、トランジスタの閾値電圧変動によらない電圧出力が可能である。また、電流源 413 の電流  $I_2$  を電流源 414 の電流  $I_1$  と等しくなるように制御すれば、入力信号電圧  $V_{in}$  を供給する外部回路の電流供給能力が低い場合でも、バッファ回路を容易に動作させることができる。なお、電流源 413 がない場合でもバッファ回路は動作可能であるが、その場合は入力信号電圧  $V_{in}$  を供給する外部回路に十分な電流供給能力が必要となる。

【 0 0 9 9 】

また、第 1 のアナログバッファ回路 13 の動作では、一出力期間の前半に、スイッチ 550 の制御により出力端子 2 を電圧  $V_{DD}$  に充電しておくことにより、任意の入力信号電圧  $V_{in}$  に対してトランジスタ 412 をソースフォロワ動作させ、出力端子 2 を上式 (5) で表される電圧に速やかに駆動することができる。

【 0 1 0 0 】

なお、トランジスタ 412 のソースフォロワ動作による電流供給能力は、トランジスタ 412 のゲート・ソース間電圧が閾値電圧に近づくにつれて低下するが、最低でも電流  $I_3$  の電流供給能力をもつ。したがって電流  $I_3$  を調整することで、バッファ回路の駆動能力や消費電流を変化させることができる。以上のようにバッファ回路は、簡単な構成で高い駆動能力をもつことができ、トランジスタの特性変動を考慮してトランジスタ 421、422 の素子サイズ及び電流  $I_1$ 、 $I_3$  を設定することで、トランジスタの特性変動によらずに、高精度な電圧出力を実現できる。

10

20

30

40

50

## 【0101】

第2のアナログバッファ回路14の動作の一例を以下に説明する。制御信号により、スイッチ560がオンし、スイッチ561、562、563、564がオフとされ、つづいてスイッチ561、562がオン状態とされ、つづいてスイッチ560をオフ、スイッチ563、564がオンとされる制御が行われる。

## 【0102】

スイッチ561、562がオンとされると、トランジスタ421の作用により、トランジスタ421、422の共通ゲート電位VG2は入力信号電圧Vinからトランジスタ421のゲート・ソース間電圧Vgs3だけずれた電圧となり、

$$VG2 = Vin + Vgs3 \quad \dots (1)$$

10

で表される。

## 【0103】

このとき、トランジスタはドレイン・ソース間電流Idsとゲート・ソース間電圧Vgsとの間に固有のVI特性を有し、トランジスタ421のゲート・ソース間電圧Vgs3は、トランジスタ421のIds-Vgs特性と電流Iによって一意に定まる。

## 【0104】

トランジスタ421のドレイン・ソース間電流がI4(電流源424の電流値)となる時のゲート・ソース間電圧をVgs3(I4)とすると、トランジスタ1のゲート電圧VG2は、

$$VG2 = Vin + Vgs3 (I4) \quad \dots (2)$$

20

で安定となる。

## 【0105】

トランジスタ422のゲートに電圧VG2が印加されると、出力電圧Voutは電圧VG2からトランジスタ422のゲート・ソース間電圧Vgs4だけずれた電圧となり、

$$Vout = VG2 - Vgs4 \quad \dots (3)$$

で表される。

## 【0106】

そして、出力電圧Voutはトランジスタ422のドレイン・ソース間電流がI5(電流源425の電流値)と等しくなるところで安定する。このときのトランジスタ422のゲート・ソース間電圧Vgs4は、トランジスタ422のIds-Vgs特性と電流I5により、Vgs4(I5)となり、出力電圧Voutは、

$$Vout = VG2 - Vgs4 (I5) \dots (4)$$

30

で安定となる。

## 【0107】

上式(2)と上式(4)より、入力信号電圧Vinが一定のときの出力電圧Voutは、

$$Vout = Vin + Vgs3 (I4) - Vgs4 (I5) \dots (5)$$

となる。

## 【0108】

このとき、出力電圧範囲は、高位側電源電圧VDDと低位側電源電圧VSSの電圧範囲から少なくともトランジスタ422のゲート・ソース間電圧Vgs4(I5)の電圧差だけ狭い電圧範囲となる。ここでトランジスタ421、422のそれぞれのゲート・ソース間電圧Vgs3(I4)、Vgs4(I5)が等しくなるように電流源424と425の電流I4、I5を制御することで、上式(5)より出力電圧Voutは入力信号電圧Vinと等しい電圧となる。また、トランジスタの特性変動が生じても、

Vgs3(I4) - Vgs4(I5)が変化しないようなトランジスタ421、422の素子サイズ及び電流I4、I5を設定することで、トランジスタの特性変動によらない高精度の電圧出力が可能である。具体的には、トランジスタ421、422の素子サイズ及び電流I4、I5をそれぞれ等しく設定したり、またはトランジスタ421、422のチャネル長を揃えて、チャネル幅比に応じて電流I4、I5を設定する等を行うことで、ト

40

50

ランジスタの閾値電圧変動によらない電圧出力が可能である。また、電流源 423 の電流  $I_6$  を電流源 424 の電流  $I_4$  と等しくなるように制御することで、入力信号電圧  $V_{in}$  を供給する外部回路の電流供給能力が低い場合でも、バッファ回路を容易に動作させることができる。なお、電流源 423 がない場合でもバッファ回路は動作可能であるが、その場合は入力信号電圧  $V_{in}$  を供給する外部回路に十分な電流供給能力が必要となる。

【0109】

また、第2のアナログバッファ回路14の動作では、一出力期間の前半に、スイッチ560の制御により出力端子2を電圧  $V_{SS}$  に放電しておくことにより、任意の入力信号電圧  $V_{in}$  に対してトランジスタ422をソースフォロワ動作させ、出力端子2を上式(5)’で表される電圧に速やかに駆動することができる。

10

【0110】

なお、トランジスタ422のソースフォロワ動作による電流供給能力は、トランジスタ422のゲート・ソース間電圧が閾値電圧に近づくにつれて低下するが、最低でも電流  $I_5$  の電流供給能力をもつ。したがって電流  $I_5$  を調整することで、バッファ回路の駆動能力や消費電流を変化させることができる。以上のようにバッファ回路は、簡単な構成で高い駆動能力をもつことができ、トランジスタの特性変動を考慮してトランジスタ421、422の素子サイズ及び電流  $I_4$ 、 $I_5$  を設定すれば、トランジスタの特性変動によらない高精度出力を実現できる。

【0111】

図18は、図7に示した実施例における第1、第2のアナログバッファ回路13、14の構成の一例を示す図である。図17を参照して説明したものと同じ構成、動作であるため説明は省略する。

20

【0112】

図19は、図1に示した実施例における第1、第2のアナログバッファ回路13、14の構成の一例を示す図である。この回路構成では、第1、第2のアナログバッファ回路13、14を、差動増幅回路を用いたボルテージフォロワで構成し、出力端子2の予備放電、予備充電を行うプリチャージ手段15を備えている。

【0113】

図19を参照すると、第1のアナログバッファ回路13は、差動段と出力段から構成されている。差動段は、PチャネルMOSトランジスタ311、322よりなるカレントミラー回路と、互いにサイズが等しいNチャネルMOSトランジスタよりなる差動対313、314と、定電流回路315と、スイッチ511を備えて構成されている。より詳細には、ソースが共通接続され、定電流源315の一端に接続され、ゲートが、入力端子1( $V_{in}$ )、出力端子2( $V_{out}$ )にそれぞれ接続され差動対をなすNチャネルMOSトランジスタ313、314と、ソースが高位側電源  $V_{DD}$  に接続され、ゲートがPチャネルMOSトランジスタ312のゲートに接続され、ドレインがNチャネルMOSトランジスタ313のドレインに接続されたPチャネルMOSトランジスタ311(カレントミラー回路の電流出力側トランジスタをなす)と、ソースが高位側電源  $V_{DD}$  に接続され、ドレインとゲートが接続されてNチャネルMOSトランジスタ314のドレインに接続されたPチャネルMOSトランジスタ312(カレントミラー回路の電流入力側トランジスタ)と、定電流源315の他端と低位側電源  $V_{SS}$ との間に接続されるスイッチ511と、を備えている。差動対をなすNチャネルMOSトランジスタ313、314は、サイズが等しい。NチャネルMOSトランジスタ313のドレインを出力端とする。

30

【0114】

また出力段は、ソースが出力端子2に接続され、差動回路の出力電圧(NチャネルMOSトランジスタ313のドレイン電圧)がゲートに入力され、ドレインが高位側電源  $V_{DD}$  に接続されるPチャネルMOSトランジスタ316を備え、出力端子2と低位側電源  $V_{SS}$ 間に接続された電流源317と、スイッチ512を備えている。なお、PチャネルMOSトランジスタ316は、昇圧回路をドレインに接続したNチャネルMOSトランジスタで置き換えてよい。なお差動回路の出力端と出力端子2の間に出力を安定させるための

40

50

位相補償容量を設けてもよい。

【0115】

スイッチ511、512は、制御端子が制御信号に接続されてオン、オフ制御され、スイッチがオフのときに電流が遮断され動作が停止される。各スイッチは電流を遮断する配置であれば、図19と異なる配置でもよい。

【0116】

第2のアナログバッファ回路14は、NチャネルMOSトランジスタ321、322よりなるカレントミラー回路と、互いにサイズが等しいPチャネルMOSトランジスタよりなる差動対323、324と、定電流回路325とを備えて構成されている。より詳細には、ソースが共通接続され、定電流源325の一端に接続され、ゲートが、入力端子1( $V_{in}$ )、出力端子2( $V_{out}$ )にそれぞれ接続され差動対をなすPチャネルMOSトランジスタ323、324と、ソースが低位側電源 $V_{SS}$ に接続され、ゲートがNチャネルMOSトランジスタ322のゲートに接続され、ドレインがPチャネルMOSトランジスタ323のドレインに接続されたNチャネルMOSトランジスタ321(カレントミラー回路の電流出力側トランジスタをなす)と、ソースが低位側電源 $V_{SS}$ に接続され、ドレインとゲートが接続されてPチャネルMOSトランジスタ324のドレインに接続されたNチャネルMOSトランジスタ322(カレントミラー回路の電流入力側トランジスタ)と、定電流源325の他端と高位側側電源 $V_{DD}$ との間に接続されるスイッチ521と、を備えている。差動対をなすPチャネルMOSトランジスタ323、324は、サイズが等しい。PチャネルMOSトランジスタ323のドレインを出力端とする。

10

20

【0117】

また出力段は、ソースが出力端子2に接続され、差動回路の出力電圧(PチャネルMOSトランジスタ323のドレイン電圧)がゲートに入力され、ドレインが低位側電源 $V_{DD}$ に接続されるNチャネルMOSトランジスタ326を備え、出力端子2と高位側電源 $V_{DD}$ 間に接続された電流源327と、スイッチ522を備えている。なお、NチャネルMOSトランジスタ326は、降圧回路をドレインに接続したPチャネルMOSトランジスタで置き換えてよい。なお差動回路の出力端と出力端子2の間に出力を安定させるための位相補償容量を設けてもよい。

【0118】

スイッチ521、522は、制御端子が制御信号に接続されてオン、オフ制御され、スイッチがオフのときに電流が遮断され動作が停止される。各スイッチは電流を遮断する配置であれば、図19と異なる配置でもよい。

30

【0119】

プリチャージ手段15は、低電位データの出力時に出力端子2を予備充電し、高電位データ出力時、出力端子2を予備放電する。好ましくは、プリチャージ手段15の予備充電電圧及び予備放電電圧を、第1のアナログバッファ回路13と第2のアナログバッファ回路14がともに動作可能な電圧範囲内に設けた駆動切替電圧 $V_c$ 付近に設定すれば、第1のアナログバッファ回路13は充電動作による駆動となり、第2のアナログバッファ回路14は放電動作による駆動となり、ともに高速動作が可能となる。

【0120】

40

図20は、図7の構成において、第1、第2のアナログバッファ回路13、14を図19に示した構成とした例を示す図である。第2のアナログバッファ回路13、14の構成、動作は、図19を参照して説明したものと同じであり、ここでは、その説明は省略する。

【0121】

図21は、図1に示した実施例における第1、第2のアナログバッファ回路13、14のさらに別の構成例を示す図である。

【0122】

図21を参照すると、第1のアナログバッファ回路13は、差動段と出力段とを備えたボルテージフォロワ構成の差動増幅回路310と、ソースフォロワ放電手段410とを備えて構成される。第2のバッファ14は、差動段と出力段とを備えたボルテージフォロワ構

50

成の差動増幅回路 320 と、ソースフォロワ充電手段 420 とを備えて構成される。

【0123】

第1のアナログバッファ回路 13 の差動回路 310 は、定電流源 315、スイッチ 511、差動対 NチャネルMOSトランジスタ 313、314、カレントミラー回路 311、312 と、差動段の出力電圧をゲートに受ける PチャネルMOSトランジスタ 316 よりなり、PチャネルMOSトランジスタ 316 のソースが高位側電源 VDD に接続され、ドレインが出力端子 2 に接続され、差動対の NチャネルMOSトランジスタ 313、314 のゲートは、入力端子 1、出力端子 2 に接続されている。この差動回路は、図19のバッファ回路の差動回路と基本的に同一の構成である（ただし、放電作用を行う電流源 317、スイッチ 512 は備えていない）。

10

【0124】

ソースフォロワ放電手段 410 は、入力端子 1 と高位側電源 VDD 間に直列に接続された定電流源 413、及びスイッチ 551 と、入力端子 1 にソースが接続され、ゲートとドレインが接続された PチャネルMOSトランジスタ 411 と、PチャネルMOSトランジスタ 411 のドレインと低位側電源 VSS 間に直列に接続された定電流源 414、及びスイッチ 552 と、出力端子 2 と高位側電源 VDD 間に直列に接続された定電流源 415、及びスイッチ 554 と、出力端子 2 のソースが接続され、PチャネルMOSトランジスタ 411 のゲートにゲートが共通接続され、ドレインがスイッチ 553 を介して低位側電源 VSS に接続された PチャネルMOSトランジスタ 412 と、を備えている。

【0125】

第2のアナログバッファ回路 14 の差動回路 320 は、定電流源 325、スイッチ 521、差動対 PチャネルMOSトランジスタ 323、324、カレントミラー回路 321、322 と、差動段の出力電圧をゲートに受ける NチャネルMOSトランジスタ 326 よりなり、NチャネルMOSトランジスタ 326 のソースが高位側電源 VDD に接続され、ドレインが出力端子 2 に接続され、差動対の PチャネルMOSトランジスタ 323、324 のゲートは、入力端子 1、出力端子 2 に接続されている。この差動回路は、図19のバッファ回路の差動回路と基本的に同一の構成である（ただし、充電作用を行う電流源 327、スイッチ 522 は備えていない）。

20

ソースフォロワ放電手段 420 は、入力端子 1 と低位側電源 VSS 間に直列に接続された定電流源 423、及びスイッチ 561 と、入力端子 1 にソースが接続され、ゲートとドレインが接続された NチャネルMOSトランジスタ 421 と、NチャネルMOSトランジスタ 421 のドレインと高位側電源 VDD 間に直列に接続された定電流源 424、及びスイッチ 562 と、出力端子 2 と低位側電源 VSS 間に直列に接続された定電流源 425、及びスイッチ 564 と、出力端子 2 のソースが接続され、NチャネルMOSトランジスタ 421 のゲートにゲートが共通接続され、ドレインがスイッチ 563 を介して高位側電源 VDD に接続された NチャネルMOSトランジスタ 422 と、を備えている。

30

【0126】

本実施例においては、ボルテージフォロワ回路（差動増幅回路）に、出力電圧を安定させる作用をもつソースフォロワ構成回路を組合せたことにより、位相補償手段（位相補償容量）を不要とし、低消費電力で高速駆動が可能となる。

40

【0127】

第1のアナログバッファ回路 13 は、入力信号電圧 Vin と出力電圧 Vout の二つの入力により充電作用を生じて出力電圧 Vout を引き上げることのできるボルテージフォロワ構成の差動増幅回路 310 と、差動増幅回路 310 とは独立した動作で入力信号電圧 Vin と出力電圧 Vout との電圧差に応じてトランジスタのソースフォロワ動作による放電作用を生じるソースフォロワ放電手段 410 とを備えている。

差動増幅回路 310 は、入力信号電圧 Vin と出力電圧 Vout の二つの電圧差に応じて動作する差動段と、差動段の出力に応じて放電作用を生じる充電手段（トランジスタ 316）とを備えている。差動増幅回路 310 は、Vin と Vout との電圧差に応じて動作し、出力電圧 Vout が電圧 Vin よりも低い場合に充電作用により出力電圧 Vout を

50

電圧  $V_{in}$  に引き上げる。

【0128】

差動増幅回路 310 は、位相補償手段を設けないことにより高速動作可能であるが、帰還型の構成では回路素子の寄生容量等により、出力電圧  $V_{out}$  の変化が充電作用に反映されるまでのわずかな応答遅延があり、オーバーシュート（過充電）を生じる場合がある。

【0129】

一方、ソースフォロワ放電手段 410 は、入力信号電圧  $V_{in}$  と出力電圧  $V_{out}$  の電圧差に応じた放電能力をもち、出力電圧  $V_{out}$  が入力電圧  $V_{in}$  よりも高い場合に、トランジスタ 412 のソースフォロワ動作による放電作用により出力電圧  $V_{out}$  を電圧  $V_{in}$  まで引き下げる 10 ことができる。

【0130】

ソースフォロワ放電手段 410 は、入力信号電圧  $V_{in}$  と出力電圧  $V_{out}$  の電圧差が大きいときは放電能力も高く、電圧差が小さくなるにつれて放電能力も小さくなるため、放電作用による出力電圧  $V_{out}$  の変化は電圧  $V_{in}$  に近づくにつれて緩やかになる。そのため、ソースフォロワ放電手段 410 は、出力電圧  $V_{out}$  を電圧  $V_{in}$  に速やかに変化させるとともに、電圧  $V_{in}$  に安定させる作用をもつ。

【0131】

すなわち、出力電圧  $V_{out}$  が入力電圧  $V_{in}$  よりも低い場合において、出力電圧  $V_{out}$  は差動増幅回路 310 により高速に電圧  $V_{in}$  に引き上げられ、このときにオーバーシュート（過充電）を生じても、ソースフォロワ放電手段 410 により、速やかに所望の電圧まで引き下げられて安定な出力となる。 20

【0132】

一方、出力電圧  $V_{out}$  が所望の電圧よりも高い場合では、差動増幅回路 310 は動作せず、出力電圧  $V_{out}$  は、ソースフォロワ放電手段 410 により、 $V_{in}$  と  $V_{out}$  の電圧差に応じたソースフォロワ放電作用により所望の電圧まで引き下げられて安定な出力となる。

【0133】

また、ボルテージフォロワ構成の差動増幅回路 310 は、位相補償容量をもたないことにより、回路素子の寄生容量等によるわずかな応答遅延しかないため、オーバーシュートを生じた場合でも、十分小さいレベルに抑えられる。そのため、出力電圧の安定化を容易にしている。さらに位相補償容量をもたないことにより、位相補償容量を充放電するための電流を不要とし、消費電流を抑えて低消費電力化を図ることができる。 30

【0134】

このように、差動回路 310 とソースフォロワ放電手段 410 の組合せにより、充電時にあいては、高速充電とともに出力電圧  $V_{out}$  を入力信号電圧  $V_{in}$  と等しい電圧に高速安定させることができる。

【0135】

第 2 のアナログバッファ回路 14 は、入力信号電圧  $V_{in}$  と出力電圧  $V_{out}$  の二つの入力により放電作用を生じて出力電圧  $V_{out}$  を引き下げる 40 ことのできるボルテージフォロワ構成の差動増幅回路 320 と、差動増幅回路 320 とは独立した動作で入力信号電圧  $V_{in}$  と出力電圧  $V_{out}$  との電圧差に応じてトランジスタのソースフォロワ動作による充電作用を生じるソースフォロワ充電手段 420 とを備えている。

【0136】

差動増幅回路 320 は、入力信号電圧  $V_{in}$  と出力電圧  $V_{out}$  の二つの電圧差に応じて動作する差動段と、差動段の出力に応じて放電作用を生じる放電手段（トランジスタ 326）とを備えている。差動増幅回路 320 は、 $V_{in}$  と  $V_{out}$  との電圧差に応じて動作し、出力電圧  $V_{out}$  が電圧  $V_{in}$  よりも高い場合に放電作用により出力電圧  $V_{out}$  を電圧  $V_{in}$  に引き下げる。

【0137】

差動増幅回路 320 は、位相補償手段を設けない構成としたことにより高速に動作可能で 50

あるが、帰還型の構成では回路素子の寄生容量等により、出力電圧  $V_{out}$  の変化が充電作用に反映されるまでのわずかな応答遅延があり、アンダーシュート（過放電）を生じる場合がある。

【0138】

一方、ソースフォロワ充電手段 420 は、入力信号電圧  $V_{in}$  と出力電圧  $V_{out}$  の電圧差に応じた充電能力をもち、出力電圧  $V_{out}$  が入力電圧  $V_{in}$  よりも低い場合に、トランジスタのソースフォロワ動作による充電作用により出力電圧  $V_{out}$  を電圧  $V_{in}$  まで引き上げることができる。

【0139】

ソースフォロワ充電手段 420 は、入力信号電圧  $V_{in}$  と出力電圧  $V_{out}$  の電圧差が大きいときは充電能力も高く、電圧差が小さくなるにつれて充電能力も小さくなるため、充電作用による出力電圧  $V_{out}$  の変化は電圧  $V_{in}$  に近づくにつれて緩やかになる。そのため、ソースフォロワ充電手段 420 は、出力電圧  $V_{out}$  を電圧  $V_{in}$  に速やかに変化させるとともに、電圧  $V_{in}$  に安定させる作用をもつ。

【0140】

すなわち、出力電圧  $V_{out}$  が入力電圧  $V_{in}$  よりも高い場合において、出力電圧  $V_{out}$  は差動增幅回路 320 により高速に電圧  $V_{in}$  に引き下げられ、このときにアンダーシュート（過放電）を生じても、ソースフォロワ充電手段 420 により、速やかに所望の電圧まで引き上げられて安定な出力となる。

【0141】

一方、出力電圧  $V_{out}$  が所望の電圧よりも低い場合では、差動增幅回路 320 は動作せず、出力電圧  $V_{out}$  は、ソースフォロワ充電手段 420 により、 $V_{in}$  と  $V_{out}$  の電圧差に応じたソースフォロワ充電作用により所望の電圧まで引き上げられて安定な出力となる。

【0142】

また、ボルテージフォロワ構成の差動增幅回路 320 は、位相補償容量をもたないことにより、回路素子の寄生容量等によるわずかな応答遅延しかないため、アンダーシュートを生じても十分小さいレベルに抑えられる。そのため、出力電圧の安定化を容易にしている。さらに位相補償容量をもたないことにより、位相補償容量を充放電するための電流を不要とし、消費電流を抑えて低消費電力化を図ることができる。

【0143】

このように、差動增幅回路 320 とソースフォロワ放電手段 420 の組合せにより、放電時においては、高速放電とともに出力電圧  $V_{out}$  を入力信号電圧  $V_{in}$  と等しい電圧に高速安定させることができる。

また、図 21 の駆動回路において、低電位データの出力時に出力端子 2 を予備充電し、高電位データ出力時、出力端子 2 を予備放電するプリチャージ手段を設けてもよい。好ましくは、プリチャージ手段の予備充電電圧及び予備放電電圧を、第 1 のアナログバッファ回路 13 と第 2 のアナログバッファ回路 14 がともに動作可能な電圧範囲内に設けた駆動切替電圧  $V_c$  付近に設定すれば、第 1 のアナログバッファ回路 13 は差動增幅回路 310 の充電動作による駆動となり、第 2 のアナログバッファ回路 14 は差動增幅回路 320 の放電動作による駆動となり、ともに高速動作が可能となる。

【0144】

図 22 は、図 7 の実施例において、第 1、第 2 のアナログバッファ回路 13、14 の構成を、図 21 に示した構成としたものである。

【0145】

図 23 (a) は、図 7 に示した実施例における基準電圧発生手段 11 の構成を模式的に示す図である。VDD と VSS 間にスイッチ 120 と分圧用の抵抗 R1、R2 が接続され、分圧値  $V_{in}2$  が出力される。この  $V_{in}2$  (基準電圧) は、図 23 (b) に示すように、第 1、第 2 のアナログバッファ回路 13、14 の動作範囲の重なり範囲に対応する駆動切替可能範囲 (第 1 の) 内の電圧とされる。抵抗 R1、R2 は、トランジスタ、ダイオード

10

20

30

40

50

ド等の能動素子を用いて構成してもよいことは勿論である。

【0146】

なお、上記図面を参照して説明したアナログバッファ回路13、14の回路構成として、各実施例のそれぞれの回路を組合せて用いてもよいことは勿論である。また本発明に係る駆動回路は、液晶表示装置のデータラインドライバにその適用が限られるものでない。すなわち、高電位側と低電位側の二つのバッファ回路の切替えを両バッファ回路がともに動作する電圧範囲で確実に行う構成とし、高精度なフルレンジ電圧出力を実現しており、任意の用途の高精度電圧出力バッファ回路に適用できる。

【0147】

以上、本発明を上記実施例に即して説明したが、本発明は、上記実施例にのみ限定されるものではなく、特許請求の範囲の請求項の範囲内で当業者であればなし得るであろう各種変形、修正を含むことは勿論である。特に上記実施例において、2つの極性に関する説明は、アクティブマトリクス型液晶表示装置のデータ線駆動回路に好適な例として挙げたものであり、極性切替を必要としないアクティブマトリクス型有機EL表示装置のデータ線駆動回路等に適用する場合には、2つの極性の一方のみ常時活性とし、他方を非活性として用いることにより容易に適用できることはいうまでもない。更には非活性部分を取り除いて用いてもよい。

【0148】

【発明の効果】

以上説明したように本発明の駆動回路によれば、表示素子特性の変調時等に、変調種別によらず、常に、第1、第2のバッファ回路が動作する電圧範囲内で、切替えを行うことができ、アクティブマトリクス型表示装置のデータ線の駆動回路に用いた場合に、階調飛び等の発生を回避することができる。

【図面の簡単な説明】

【図1】本発明の一実施例の駆動回路の構成を示す図である。

【図2】図1の本発明の一実施例の駆動回路の動作を説明するための図である。

【図3】図1の本発明の一実施例の駆動回路を複数有する多出力駆動回路の構成を示す図である。

【図4】本発明の駆動回路における駆動切替電圧を説明するための図である。

【図5】図1の本発明の一実施例の駆動回路の動作を説明するためのタイミング図である。

【図6】比較例として従来の駆動回路における駆動切替電圧を説明するための図であり、(A)は、コモン反転駆動における液晶ガンマ特性と駆動回路の動作範囲(標準)を示す図であり、(B)は、コモン反転駆動における液晶ガンマ特性と駆動回路の動作範囲(変調)を示す図である。

【図7】本発明の他の実施例の駆動回路の構成を示す図である。

【図8】図7の本発明の他の実施例の駆動回路の動作を説明するための図である。

【図9】図7の本発明の他の実施例の駆動回路を複数有する多出力駆動回路の構成を示す図である。

【図10】図7の本発明の他の実施例の駆動回路の比較器の構成の一例を示す図である。

【図11】図10の比較器の動作を説明する図である。

【図12】図7の本発明の他の実施例の駆動回路の比較器の構成の一例を示す図である。

【図13】図12の比較器の動作を説明する図である。

【図14】図12の本発明の他の実施例の駆動回路の比較器の構成の一例を示す図である。

【図15】図14の比較器の動作を説明する図である。

【図16】(a)は図7の本発明の他の実施例の駆動回路の構成例を示す図であり、(b)は、動作を説明する図である。

【図17】図1の本発明の一実施例の駆動回路におけるアナログバッファ回路の構成の一例を示す図である。

10

20

30

40

50

【図18】図7の本発明の他の実施例の駆動回路におけるアナログバッファ回路の構成の一例を示す図である。

【図19】図1の本発明の一実施例の駆動回路におけるアナログバッファ回路の構成の他の例を示す図である。

【図20】図7の本発明の他の実施例の駆動回路におけるアナログバッファ回路の構成の他の例を示す図である。

【図21】図1の本発明の一実施例の駆動回路におけるアナログバッファ回路の構成の他の例を示す図である。

【図22】図7の本発明の他の実施例の駆動回路におけるアナログバッファ回路の構成の他の例を示す図である。

【図23】図7の本発明の他の実施例の駆動回路における基準電圧派生手段の構成の一例を示す図である。

【図24】文献1 ( H.Tsuchi,N.Ikeda,H.Hayama, "A New Low Power TFT-LCD Dirver for Portable Devices," SID 00 DIGEST PP146~149 ) に記載されるバッファの構成を示す図である。

【図25】文献1に記載されるデジタルデータラインドライバの構成を示す図である。

【符号の説明】

1 入力端子

2 出力端子

3 レジスタ

3 a 正極性基準データテーブル

3 b 負極性基準データテーブル

4 選択部

5 比較部

1 1 基準電圧発生手段

1 2 比較部

1 3 第1のアナログバッファ回路

1 4 第2のアナログバッファ回路

1 5 プリチャージ手段(予備充電放電手段)

2 2、2 3 N A N D

2 4 インバータ

1 0 0 駆動回路

1 0 1、1 0 2、1 1 3 N NチャネルMOSトランジスタ

1 0 3、1 0 4、1 1 3 P PチャネルMOSトランジスタ

1 0 5、1 0 7 電流源(電流制御回路)

1 0 8、1 0 9、1 1 3、1 1 4、1 1 5 P、1 1 5 N、1 1 6 P、1 1 6 N

スイッチ

1 1 1、1 1 2 インバータ

1 2 0 スイッチ

2 0 0 階調電圧発生手段

3 0 0 デコーダ

4 0 0 出力端子群

4 1 1、4 1 2 PチャネルMOSトランジスタ

4 2 1、4 2 2 NチャネルMOSトランジスタ

4 1 3、4 1 4、4 1 5、4 2 3、4 2 4、4 2 5 電流源(電流制御回路)

5 5 0、5 5 2、5 5 3、5 5 1、5 5 4、5 6 0、5 6 2、5 6 3、5 6 4 スイッチ

3 1 1、3 1 2、3 2 3、3 2 4、3 1 6 PチャネルMOSトランジスタ

3 1 3、3 1 4、3 2 1、3 2 2、3 2 6 NチャネルMOSトランジスタ

5 1 1、5 1 2、5 2 1、5 2 2 スイッチ

1 0 0 1 入力端子

10

20

30

40

50

1 0 0 2 出力端子

1 0 1 0、1 0 2 0 バッファ回路

1 0 1 1、1 0 1 2 P チャネルMOSトランジスタ

1 0 2 1、1 0 2 2 N チャネルMOSトランジスタ

1 0 1 3、1 0 1 4、1 0 1 5、1 0 2 3、1 0 2 4、1 0 2 5 電流源（電流制御回路

）

1 0 3 0 予備充放電回路

1 0 3 1、1 0 3 2、1 0 4 1、1 0 4 2 スイッチ

1 1 0 0 シフトレジスタ

1 1 1 0 データレジスタ 10

1 1 2 0 データラッチ

1 1 3 0 レベルシフタ

1 1 4 0 ROM デコーダ

1 1 5 0 規準電圧発生器

1 1 6 0 R DAC

1 1 7 0 ニューバッファ

【図1】

【図2】

| 制御信号        | L      | H  | H  |

|-------------|--------|----|----|

| 比較部5出力 (PN) | L or H | H  | L  |

| 第1アナログバッファ  | 停止     | 動作 | 停止 |

| 第2アナログバッファ  | 停止     | 停止 | 動作 |

【 図 3 】

【 四 4 】

【図5】

〔 四 6 〕

【 四 7 】

【 义 8 】

| 制御信号     | L      | H  | H  |

|----------|--------|----|----|

| 比較器12出力  | L or H | H  | L  |

| 第1アナログ入力 | 停止     | 動作 | 停止 |

| 第2アナログ入力 | 停止     | 停止 | 動作 |

〔 四 9 〕

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 15】

【図 16】

【図 17】

【図 18】

【 図 1 9 】

【 図 2 0 】

【 図 2 1 】

## 【図22】

【図 2 3】

【図 2 4】

(B)

【図 2 5】

---

フロントページの続き

(72)発明者 内山 義規

神奈川県川崎市中原区小杉町一丁目403番53 エヌイーシーマイクロシステム株式会社内

審査官 西島 篤宏

(56)参考文献 特開2002-169501(JP, A)

特開2001-004974(JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00- 3/38

G02F 1/133 505-580

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 驱动电路和液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP3730886B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2006-01-05 |

| 申请号            | JP2001206987                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2001-07-06 |

| [标]申请(专利权)人(译) | NEC微系统有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | NEC公司<br>Enui海微系统有限公司                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | NEC公司<br>NEC微系统有限公司                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 土弘<br>内山義規                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 土弘<br>内山 義規                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 H03K19/0175                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/3688 G09G3/3614 G09G3/3696 G09G2310/0248 G09G2310/027 G09G2310/0291                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/36 G02F1/133.505 G02F1/133.520 G09G3/20.623.B H03K19/00.101.F H03K19/0175.220                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 2H093/NC01 2H093/NC15 2H093/NC16 2H093/ND31 2H193/ZF01 5C006/AF13 5C006/AF75 5C006/BB16 5C006/BC13 5C006/BF14 5C006/BF26 5C006/BF27 5C006/BF33 5C006/BF34 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD08 5C080/DD26 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5J056/AA05 5J056/BB21 5J056/CC00 5J056/CC01 5J056/CC09 5J056/CC19 5J056/DD13 5J056/DD29 5J056/DD52 5J056/EE08 5J056/FF07 5J056/FF08 5J056/GG07 5J056/KK01 5J056/KK03 |         |            |

| 其他公开文献         | JP2003022056A                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

提供一种驱动电路和驱动电路，其能够在驱动切换范围内的操作范围扩展到较高电源电位和较低电源电位的第一和第二缓冲电路之间可靠地切换。输入端子共同连接到输入信号电压的一个输入端子，输出端子共同连接到一个输出端子，操作范围设置为更高的电源电位，更低的电源电位第一和第二缓冲电路113和114，对应于第一和第二缓冲电路都可操作的范围内的电压，相对于伽马特性的标准时间和调制时间，用于存储和保持负极性的基准数据的存储单元3，选择所述极性信号POL，选择图3B中，基于用于指定调制的调制信息的基础上，存储部3a中，选择性地输出对应于标准或调制的基准数据部分4和比较部分5，用于比较输入数据和从选择部分输出的参考数据，其中第一和第二缓冲电路比较部分5的比较结果信号和控制信号，它的操作和停止是受控制的。

|           |      |    |    |

|-----------|------|----|----|

| 制御信号      |      | H  | H  |

| 比較部5出力(?) | - or | H  |    |

| 第一比較部1    | 停止   | 動作 | 停止 |

| 第二比較部2    | 停止   | 停止 | 動作 |