(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-165223

(P2008-165223A)

(43) 公開日 平成20年7月17日(2008.7.17)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36  | 2 H 09 3    |

| <b>G02F 1/133 (2006.01)</b> | G02F 1/133 | 5 C 006     |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20  | 5 C 08 0    |

|                             | G09G 3/20  | 6 2 1 L     |

|                             | G09G 3/20  | 6 2 2 B     |

審査請求 未請求 請求項の数 22 O L (全 24 頁) 最終頁に続く

(21) 出願番号 特願2007-320105 (P2007-320105)

(22) 出願日 平成19年12月11日 (2007.12.11)

(31) 優先権主張番号 10-2006-0125334

(32) 優先日 平成18年12月11日 (2006.12.11)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

最終頁に続く

(54) 【発明の名称】ゲート駆動信号の遅延を補償する方法減少方法及び液晶表示装置

## (57) 【要約】 (修正有)

【課題】従来のシングル駆動方式の液晶表示装置はゲートライン遅延及びASG遅延によって、ディスプレイに横線が見えてしまう、いわゆる横線視認現象を改善する。

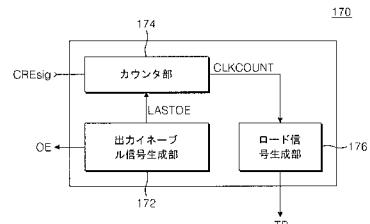

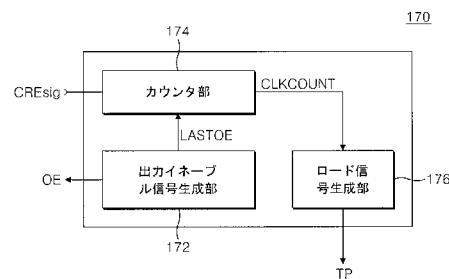

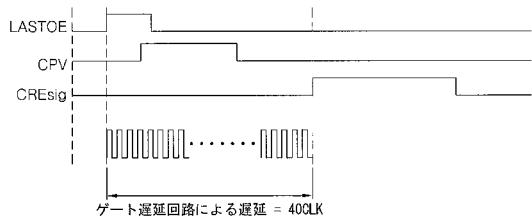

【解決手段】タイミングコントローラ170は出力イネーブル信号OE及びゲートクロックを生成し、データ出力時点を決定するロード信号のタイミングを調節する。出力イネーブル信号生成部172は、1フレームの最後の出力イネーブル信号LASTOEをカウンタ部174に供給する。カウンタ部174は、クリップされたりセット信号CREsigのライジング時点と、最後の出力イネーブル信号LASTOEのライジング時点との差異をクロックカウント信号CLKCOUNTを生成し、これをロード信号生成部176に供給する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

出力イネーブル信号及びゲートクロックを生成し、該当活性化されたディスプレイローにデータ信号が出力される時、データ出力時点を決定するロード信号のタイミングを調節するタイミングコントローラと、

前記出力イネーブル信号とゲートクロックに応答してゲートクロックパルスを生成するレベルシフタと、

前記ディスプレイローを一つずつ活性化し、前記ゲートクロックパルスに応答してリップルダウンされた第1ゲート駆動信号を生成して複数のゲートラインを順次駆動するゲート駆動回路と、

前記第1ゲート駆動信号が前記ゲート駆動回路の最後のステージから出力される時、前記第1ゲート駆動信号をクリップした第2ゲート駆動信号を前記タイミングコントローラに供給するクリップ部とを含み、

前記タイミングコントローラが前記第2ゲート駆動信号と前記出力イネーブル信号との比較により、前記ゲート駆動回路による第1ゲート駆動信号の遅延時間を算出し、前記遅延時間を測定及び利用して前記ロード信号のタイミングを調節する液晶表示装置。

**【請求項 2】**

前記レベルシフタが、

前記ゲートクロックパルスをゲートオン電圧及びゲートオフ電圧レベルのパルスとして生成する請求項1に記載の液晶表示装置。

**【請求項 3】**

前記ゲートクロックパルスは、

前記ゲートクロックパルスの位相が反転した位相を有する反転ゲートクロックパルスを含む請求項2に記載の液晶表示装置。

**【請求項 4】**

前記第1ゲート駆動信号が、

前記ゲート駆動回路をリセットするリセット信号を含む請求項3に記載の液晶表示装置。

**【請求項 5】**

前記ゲート駆動回路は、

前記ゲートラインが形成された液晶パネルに集積され、前記ゲートラインの両端にデュアルに形成されて前記ゲートラインをデュアル駆動する請求項4に記載の液晶表示装置。

**【請求項 6】**

前記ゲート駆動回路が、

互いに従属的に接続された複数のステージから構成されるシフトレジスタを含む請求項5に記載の液晶表示装置。

**【請求項 7】**

前記複数のステージが、

前記複数のゲートラインにそれぞれ対応して接続される請求項6に記載の液晶表示装置。

**【請求項 8】**

前記複数のステージが、

前記リセット信号を生成するダミーステージを含む請求項7に記載の液晶表示装置。

**【請求項 9】**

前記タイミングコントローラが、

1フレームの最後の出力イネーブル信号を供給する出力イネーブル信号生成部と、

前記クリップされたリセット信号と前記1フレームの最後の出力イネーブル信号とを比較してクロックカウント信号を生成するカウンタ部と、

前記クロックカウント信号に応答して前記ロード信号のタイミングを調節するロード信号生成部とを含む請求項8に記載の液晶表示装置。

10

20

30

40

50

**【請求項 10】**

リセット信号を含むゲート駆動信号を生成するゲート駆動回路と、

前記リセット信号と前記リセット信号に対応する出力イネーブル信号を比較して前記ゲート駆動回路による前記ゲート駆動信号の遅延時間を算出し、前記遅延時間に応答してデータ出力時点を決定するロード信号のタイミングを調節するタイミングコントローラとを含む液晶表示装置。

**【請求項 11】**

前記リセット信号をクリップしたクリップされたリセット信号を前記タイミングコントローラに供給するクリップ部をさらに含む請求項 10 に記載の液晶表示装置。

**【請求項 12】**

前記タイミングコントローラが、

前記出力イネーブル信号を供給する出力イネーブル信号生成部と、

前記クリップされたリセット信号と前記 1 フレームの最後の出力イネーブル信号を比較してクロックカウント信号を生成するカウンタ部と、

前記クロックカウント信号に応答して前記ロード信号のタイミングを調節するロード信号生成部とを含む請求項 11 に記載の液晶表示装置。

**【請求項 13】**

前記ゲート駆動回路が互い従属的に接続された複数のステージから構成されるシフトレジスタであり、

前記複数のステージが前記複数の前記リセット信号を生成するダミーステージを含む請求項 12 に記載の液晶表示装置。

**【請求項 14】**

前記カウンタ部が、

前記出力イネーブル信号のライジング時点から前記クリップされたリセット信号のライジング時点までの区間に該当するクロック数をカウントして前記クロックカウント信号として生成する請求項 13 に記載の液晶表示装置。

**【請求項 15】**

前記ロード信号生成部は、

前記ゲート駆動信号が供給されるゲートライン数を前記クロックカウント信号値で除算して前記ゲート駆動信号の遅延時間を算出し、算出されたゲート駆動信号遅延時間に該当する時間だけ前記ロード信号のフォーリング時点を遅延させる請求項 14 に記載の液晶表示装置。

**【請求項 16】**

ゲート駆動回路のダミーステージの出力信号であるリセット信号をタイミングコントローラにフィードバックするリセット信号フィードバック段階と、

前記リセット信号と前記リセット信号に対応する出力イネーブル信号とを比較して前記ゲート駆動回路によるゲート駆動信号の遅延時間を算出する遅延時間算出段階と、

前記遅延時間に応答してデータの出力時点を決定するロード信号のタイミングを調節するロード信号タイミング調節段階とを含むゲート駆動信号遅延減少方法。

**【請求項 17】**

前記リセット信号フィードバック段階が、

前記リセット信号を一定の電圧レベルにクリップし、クリップされたリセット信号を前記タイミングコントローラにフィードバックするクリップ段階を含む請求項 16 に記載のゲート駆動信号遅延減少方法。

**【請求項 18】**

前記遅延時間算出段階が、

前記出力イネーブル信号のライジング時点から前記クリップされたリセット信号のライジング時点までの区間に該当するクロック数をカウントしてクロックカウント信号を生成する段階を含む請求項 17 に記載のゲート駆動信号遅延減少方法。

**【請求項 19】**

10

20

30

40

50

前記ロード信号タイミング調節段階は、

前記ゲート駆動信号が供給されるゲートライン数を前記クロックカウント信号値で除算して前記ゲート駆動信号の遅延時間を算出し、前記遅延時間に該当する時間だけ前記ロード信号のフォーリング時点を遅延させる段階を含む請求項18に記載のゲート駆動信号遅延減少方法。

#### 【請求項20】

前記リセット信号フィードバック段階は、

前記ゲート駆動回路が複数のゲートラインに順次前記ゲート駆動信号を印加するとき、前記ゲート駆動回路による遅延によってデータの出力時点より前記ゲート駆動信号が遅延して印加されることにより発生する横線視認現象を分析する横線現象分析段階をさらに含む請求項19に記載のゲート駆動信号遅延減少方法。

10

#### 【請求項21】

ディスプレイフレームの間垂直スキャンの第1時点で初期化した後、ロー活性化パルスまたはダミの最後のロー活性化パルスに対応されたシフトレジスタの最後のステージまたはダミの最後のステージが出力される時第2時点を確認する段階と、

第1及び第2時点の差異とスキャンされたディスプレイローの数から複数個のシフトレジスタのステージのリップルスル遅延(ripple-through delay)と関連されたディスプレイロー当たり遅延を決定する段階と、

前記決定されたディスプレイロー当たり遅延及び現在スキャンの間活性化されたディスプレイローの数に従って前記シフトレジスタに対応され活性化されたディスプレイローにディスプレイデータがローディングされる時の第3時点と現在ディスプレイフレームの行の活性化を調節する段階と、

20

を含むことを特徴とするシフトレジスタの複数個のステージのリップルスル遅延を補償してスキャンスルとディスプレイフレームの順次的に活性化された行に使用する方法。

#### 【請求項22】

ディスプレイフレームの垂直スキャンスルの第1時点で初期化に応答するものの、シフトレジスタの最後のステージまたはダミの最後のステージが最後の行またはダミの最後の行の活性化信号に対応され出力される時、第2時点を確認する確認手段と、

前記確認手段に駆動的に結合され前記第1及び第2時点の差異とスキャンされたディスプレイローの数から、前記シフトレジスタの複数個のステージのリップルスル遅延と関連されたディスプレイロー当たり遅延またはその等価物を決定する差異決定手段と、

30

前記差異決定手段に応答して前記決定されたディスプレイローの遅延及び現在スキャンされる間活性化されたディスプレイローの数に従って前記シフトレジスタに対応して活性化されたディスプレイローにディスプレイデータがローディングされる時の第3時点と現在ディスプレイフレームの行の活性化を調節する調節手段と、

を含むことを特徴とするシフトレジスタの複数個のステージの多様なリップルスル遅延を補償してスキャンスル及び順次的に活性化されたディスプレイの行に使用するためのシステム。

#### 【発明の詳細な説明】

##### 【技術分野】

40

##### 【0001】

本発明は液晶表示装置に関する。

##### 【背景技術】

##### 【0002】

一般に液晶表示装置は、映像を表示するための液晶パネルと、液晶パネルを駆動するデータ駆動部と、ゲート駆動部とを備える。液晶パネルは複数のゲートライン、複数のデータライン、及び複数の画素を含む。画素は薄膜トランジスタ及び液晶キャパシタからなる。データ駆動部はデータラインにデータ信号を出力し、ゲート駆動部はゲート駆動信号を出力する。

##### 【0003】

50

ゲート駆動部は同一工程で薄膜トランジスタと同時に液晶パネル上に形成され、データ駆動部はチップ状に形成されて液晶パネルの周辺領域に接続される。ゲート駆動部は複数のステージからなるシフトレジスタを含み、ステージのそれぞれは対応するゲートラインに接続されてゲート駆動信号を出力する。

ゲート駆動部は複数のゲートラインにゲート駆動信号を順次出力するために互い従属的に接続される。すなわち、現ステージの入力端子は前のステージの出力端子に接続され、次のステージの出力端子は現ステージの制御端子に接続される。複数のステージのうち第1ステージには開始信号が入力される。

#### 【0004】

このようなゲート駆動部は液晶パネルの左右側に形成され、左側のゲート駆動回路が奇数番目のゲートラインを駆動し、右側のゲート駆動回路が偶数番目のゲートラインを駆動するシングル駆動方式で動作する。

従来のシングル(Single)駆動方式の液晶表示装置はゲートライン遅延(Gate Line Delay)及びASG遅延(Amorphous Silicon Gate Delay)によって、ディスプレイに横線が見えてしまう、いわゆる横線視認現象が発生するという問題がある。

#### 【0005】

ゲートライン遅延とは、左右側のゲート駆動回路から交互に出力されるゲート駆動信号がゲートラインの端部に近づくほど遅延して出力されることをいう。ゲートライン遅延はゲートラインの端部に接続された画素の充電時間の不足を招き、これにより画素の輝度が低下する。このため、ゲートラインの左右側の両端部で隣接する両ゲートライン間に輝度差が発生し、これが横線視認現象として現れる。

#### 【0006】

ASG遅延とは、ゲート駆動回路が複数のゲートラインにゲート駆動信号を順次印加するとき、ゲート駆動回路自体の遅延によってデータ出力よりゲート駆動信号が遅延して印加されることをいう。これにより、液晶パネルの下端部、つまりデータ駆動回路から離れた部分に位置するゲートラインに接続された画素が本来表示されるべきデータに対応する輝度より暗い輝度で表示するという問題がある。例えば、ゲートライン単位で緑Gと青Bのデータ信号がそれぞれ供給される場合、複数のゲートラインにゲート駆動信号を順次印加すると液晶パネルの下端部に近づくほど青Bのデータ信号が本来表示されるべき青Bに対応する輝度より暗い輝度の青Bを表示するという問題がある。

10

20

30

40

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

従って、本発明は従来の問題を解決するために案出されたものであり、画像品質が向上した液晶表示装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

前記目的を達成するために本発明1の液晶表示装置は、出力イネーブル信号及びゲートクロックを生成し、該当活性化されたディスプレイローにデータ信号が出力される時、データ出力時点を決定するロード信号のタイミングを調節するタイミングコントローラと、前記出力イネーブル信号とゲートクロックに応答してゲートクロックパルスを生成するレベルシフタと、前記ディスプレイローを一つずつ活性化し、前記ゲートクロックパルスに応答してリップルダウンされた第1ゲート駆動信号を生成して複数のゲートラインを順次駆動するゲート駆動回路と、前記第1ゲート駆動信号が前記ゲート駆動回路の最後のステージから出力される時、前記第1ゲート駆動信号をクリップした第2ゲート駆動信号を前記タイミングコントローラに供給するクリップ部とを含み、前記タイミングコントローラが前記第2ゲート駆動信号と前記出力イネーブル信号との比較により、前記ゲート駆動回路による第1ゲート駆動信号の遅延時間を算出し、前記遅延時間を測定及び利用して前記ロード信号のタイミングを調節する。

#### 【0009】

50

具体的に、前記タイミングコントローラはディスプレイフレームのスキャンスタートから最後までの前記ゲート駆動回路の実際遅延時間を測定し、前記ゲート駆動回路のステージに割り当てられた行当り (per - row) 遅延時間を計算し、前記計算された行当り遅延時間を用いて与えられたフレームの間に蓄積された行数による前記ロード信号のタイミングを調節できる。

【0010】

このように本発明の液晶表示装置は、ゲート駆動回路のリセット信号のフィードバックを受ける。また、フィードバックに基づいて読出時間を調節し、ゲート駆動回路によるゲート駆動信号の出力遅延を補償できる。そのため、ゲート駆動回路自体の遅延によって、データが出力されるよりもゲート駆動信号が遅延して印加される問題を解消できる。これにより、液晶パネルの下端部に位置するゲートラインに接続された画素が本来表示されるべきデータに対応する輝度より暗い輝度で表示するという問題を解消できる。

10

【0011】

具体的には、タイミングコントローラは、各ゲートライン G L 1 ~ G L n に順次供給されるゲート駆動信号がハイレバルにライジングする時点に、ロード信号 T P のフォーリング時点を同期させ、データ駆動部が階調表示電圧をデータラインに供給するようとする。従って、ゲート駆動回路によってゲート駆動信号が遅延すると、ゲート駆動信号が遅延した時間だけロード信号 T P のフォーリング時点を遅延させる。これにより、ゲート駆動回路によってゲート駆動信号が遅延することにより発生する問題を解消できる。

20

発明 2 は、発明 1 において、前記レベルシフタは前記ゲートクロックパルスをゲートオン電圧及びゲートオフ電圧レベルのパルスとして生成することが好ましい。

【0012】

発明 3 は、発明 2 において、前記ゲートクロックパルスは前記ゲートクロックパルスの位相が反転した位相を有する反転ゲートクロックパルスを含む。これらの信号は、ゲートラインを駆動する速度を調整し、例えば速くするために使用される。

発明 4 は、発明 3 において、前記第 1 ゲート駆動信号はゲート駆動回路をリセットするリセット信号を含む。

【0013】

発明 5 は、発明 4 において、前記ゲート駆動回路は前記ゲートラインが形成された液晶パネルに蓄積され、前記ゲートラインの両端にデュアルに形成されて前記ゲートラインをデュアル駆動することが好ましい。

30

発明 6 は、発明 5 において、前記ゲート駆動回路は互いに従属的に接続された複数のステージから構成されるシフトレジスタである。つまり、前記ゲート駆動回路はリップル進行方式で互いに直列に接続された複数のステージから構成されるシフトレジスタである。

【0014】

発明 7 は、発明 6 において、前記複数のステージは前記複数のゲートラインにそれぞれ対応して接続される。

発明 8 は、発明 7 において、リセット信号を生成するダミーステージを含む。

ダミーステージは、ディスプレイフレームの垂直スキャンの終点でリセットするために全てのステージに再度接続されるのが好ましい。

40

【0015】

発明 9 は、発明 8 において、前記タイミングコントローラは、1 フレームの最後の出力イネーブル信号を供給する出力イネーブル信号生成部と、前記クリップされたリセット信号と前記 1 フレームの最後の出力イネーブル信号とを比較してクロックカウント信号を生成するカウンタ部と、前記クロックカウント信号に応答して前記ロード信号のタイミングを調節するロード信号生成部と、を含む。

【0016】

前記カウンタ部は、クロックカウント信号を生成して実際遅延が理想的なものからどれほど差異があるのかを決定する。また、ロード信号生成部は、前記クロックカウント信号

50

に応答して全てのフレームに対する測定されたリップルスル遅延を基準にして行当りスキャンされた基準の前記ロード信号のタイミングを調節する。

発明 10 は、リセット信号を含むゲート駆動信号を生成するゲート駆動回路と、前記リセット信号と前記リセット信号に対応する出力イネーブル信号を比較して前記ゲート駆動回路による前記ゲート駆動信号の遅延時間を算出し、前記遅延時間に応答してデータ出力時点を決定するロード信号のタイミングを調節するタイミングコントローラとを含む。

#### 【 0 0 1 7 】

発明 11 は、発明 10 において、前記リセット信号をクリップしたクリップされたりセット信号を前記タイミングコントローラに供給するクリップ部をさらに含む。

発明 12 は、発明 11 において、前記タイミングコントローラが、前記出力イネーブル信号を供給する出力イネーブル信号生成部と、前記クリップされたりセット信号と前記 1 フレームの最後の出力イネーブル信号を比較してクロックカウント信号を生成するカウンタ部と、前記クロックカウント信号に応答して前記ロード信号のタイミングを調節するロード信号生成部とを含む。

#### 【 0 0 1 8 】

発明 13 は、発明 12 において、前記ゲート駆動回路が互い従属的に接続された複数のステージから構成されるシフトレジスタであり、前記複数のステージが前記複数の前記リセット信号を生成するダミーステージを含む。

発明 14 は、発明 13 において、前記カウンタ部は、前記出力イネーブル信号のライジング時点から前記クリップされたりセット信号のライジング時点までの区間に該当するクロック数をカウントして前記クロックカウント信号として生成することが好ましい。

#### 【 0 0 1 9 】

発明 15 は、発明 14 において、前記ロード信号生成部は前記ゲート駆動信号が供給されるゲートライン数を前記クロックカウント信号値で除算して前記ゲート駆動信号の遅延時間を算出し、算出されたゲート駆動信号遅延時間に該当する時間だけ前記ロード信号のフォーリング時点を遅延させる。

また、前記算出されたゲート駆動信号遅延時間に該当し、1つのフレームが進行される時スキャンされた行の数に対等する分だけ前記ロード信号のフォーリング時点をそれぞれ遅延させることが好ましい。

#### 【 0 0 2 0 】

本発明 16 のゲート駆動信号遅延減少方法は、ゲート駆動回路のダミーステージの出力信号であるリセット信号をタイミングコントローラにフィードバックするリセット信号フィードバック段階と、前記リセット信号と前記リセット信号に対応する出力イネーブル信号とを比較して前記ゲート駆動回路によるゲート駆動信号の遅延時間を算出する遅延時間算出段階と、前記算出されたゲート駆動信号の遅延時間に応答してデータの出力時点を決定するロード信号のタイミングを調節するロード信号タイミング調節段階とを含む。

#### 【 0 0 2 1 】

発明 17 は、発明 16 において、リセット信号フィードバック段階は、前記リセット信号を一定の電圧レベルにクリップし、クリップされたりセット信号を前記タイミングコントローラにフィードバックするクリップ段階をさらに含む。

発明 18 は、発明 17 において、前記遅延時間算出段階は、前記出力イネーブル信号のライジング時点から前記クリップされたりセット信号のライジング時点までの区間に該当するクロック数をカウントしてクロックカウント信号を生成する段階を含む。

#### 【 0 0 2 2 】

発明 19 は、発明 18 において、前記ロード信号タイミング調節段階は、前記ゲート駆動信号が供給されるゲートライン数を前記クロックカウント信号値で除算して前記ゲート駆動信号の遅延時間を算出し、算出されたゲート駆動信号遅延時間に該当する時間だけ前記ロード信号のフォーリング時点を遅延させる段階を含む。

発明 20 は、発明 19 において、前記リセット信号フィードバック段階は、前記ゲート駆動回路が複数のゲートラインに順次前記ゲート駆動信号を印加するとき、前記ゲート駆

10

20

30

40

50

動回路による遅延によってデータの出力時点より前記ゲート駆動信号が遅延して印加されることにより発生する横線視認現象を分析する横線現象分析段階をさらに含む。

#### 【0023】

発明21は、ディスプレイフレームの間垂直スキャンの第1時点で初期化した後、ロー活性化パルスまたはダミの最後のロー活性化パルスに対応されたシフトレジスタの最後のステージまたはダミの最後のステージが出力される時第2時点で確認する段階と、第1及び第2時点で差異とスキャンされたディスプレイローの数から複数個のシフトレジスタのステージのリップルスル遅延(ripple-through delay)と関連されたディスプレイロー当たり遅延を決定する段階と、前記決定されたディスプレイロー当たり遅延及び現在スキャンの間活性化されたディスプレイローの数に従って前記シフトレジスタに対応され活性化されたディスプレイローにディスプレイデータがローディングされる時の第3時点で現在ディスプレイフレームの行の活性化を調節する段階と、を含むことを特徴とするシフトレジスタの複数個のステージのリップルスル遅延を補償してスキャンスルとディスプレイフレームの順次的に活性化された行に使用する方法を提供する。10

#### 【0024】

発明22は、ディスプレイフレームの垂直スキャンスルの第1時点で初期化に応答するものの、シフトレジスタの最後のステージまたはダミの最後のステージが最後の行またはダミの最後の行の活性化信号に対応され出力される時、第2時点で確認する確認手段と、前記確認手段に駆動的に結合され前記第1及び第2時点で差異とスキャンされたディスプレイローの数から、前記シフトレジスタの複数個のステージのリップルスル遅延と関連されたディスプレイロー当たり遅延またはその等価物を決定する差異決定手段と、前記差異決定手段に応答して前記決定されたディスプレイローの遅延及び現在スキャンされる間活性化されたディスプレイローの数に従って前記シフトレジスタに対応して活性化されたディスプレイローにディスプレイデータがローディングされる時の第3時点で現在ディスプレイフレームの行の活性化を調節する調節手段と、を含むことを特徴とするシフトレジスタの複数個のステージの多様なリップルスル遅延を補償してスキャンスル及び順次的に活性化されたディスプレイの行に使用するためのシステムを提供する。20

#### 【発明の効果】

#### 【0025】

本発明の液晶表示装置は、画像品質が向上した液晶表示装置を提供することができる。30

#### 【発明を実施するための最良の形態】

#### 【0026】

本発明の詳細な説明では本発明の好ましい実施形態に基づいて説明するが、該当技術分野の習熟した当業者又は該当技術の分野における通常の知識を有する者であれば、特許請求の範囲に記載された本発明の思想及び技術領域から外れない範囲内で本発明を多様に修正及び変更できることを理解するであろう。

従って、本発明の技術的範囲は明細書の詳細な説明に記載された内容に限定されるものではなく、特許請求の範囲により定められるべきである。

#### 【0027】

以下、添付図面を参照して本発明の好ましい一実施形態について詳細に説明する。40

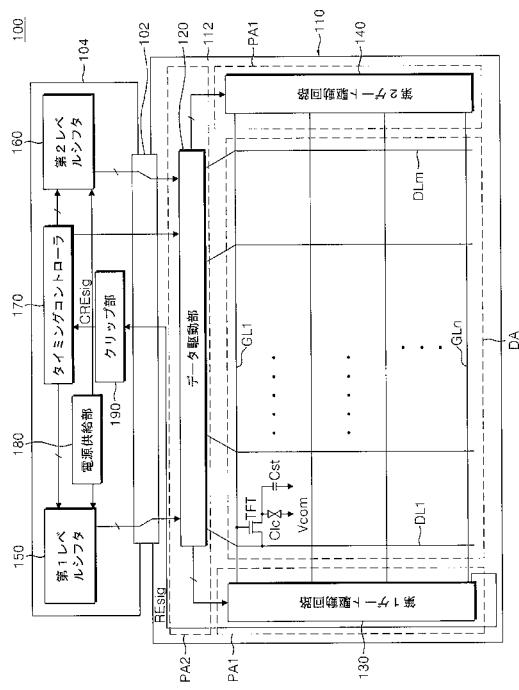

図1は本発明の一実施形態による液晶表示装置の構成を示すブロック図である。図1に示すように、本発明の一実施形態による液晶表示装置100は、液晶パネル110、データ駆動部120、第1ゲート駆動回路130、第2ゲート駆動回路140、第1レベルシフタ150、第2レベルシフタ160、タイミングコントローラ170、電源供給部180、及びクリップ部190を含む。

#### 【0028】

前記液晶パネル110は、薄膜トランジスタ基板112、カラーフィルタ基板(図示せず)、及び薄膜トランジスタ基板112とカラーフィルタ基板間に介在する液晶(図示せず)を含む。

薄膜トランジスタ基板112は、表示領域DA、第1周辺領域PA1、及び第2周辺領50

域 P A 2 を含む。表示領域 D A には、第 1 方向に伸長されたゲートライン G L 1 ~ G L n 、第 1 方向と異なる第 2 方向に伸長されたデータライン D L 1 ~ D L m 、並びにゲートライン G L 1 ~ G L n 及びデータライン D L 1 ~ D L m にそれぞれ接続される複数の画素が形成される。第 1 周辺領域 P A 1 には、ゲートライン G L 1 ~ G L n を駆動する第 1 ゲート駆動回路 1 3 0 及び第 2 ゲート駆動回路 1 4 0 が形成される。第 2 周辺領域 P A 2 には、データライン D L 1 ~ D L m を駆動するデータ駆動部 1 2 0 が実装される。ここで、第 1 周辺領域 P A 1 はゲートライン G L 1 ~ G L n の両端部に隣接する領域であり、第 1 ゲート駆動回路 1 3 0 は表示領域 D A の両側に配置される。また、第 2 周辺領域 P A 2 はデータライン D L 1 ~ D L m の一端部に隣接する領域である。

## 【 0 0 2 9 】

10

各画素、例えば 1 つの画素は、ゲートライン G L 1 とデータライン D L 1 に接続される薄膜トランジスタ T F T 、薄膜トランジスタ T F T に接続される液晶キャパシタ C L C 、及びストレージキャパシタ C S T を含む。薄膜トランジスタ T F T のゲート及びソースはゲートライン G L 1 及びデータライン D L 1 にそれぞれ接続され、ドレインは液晶キャパシタ C L C とストレージキャパシタ C S T に接続される。液晶キャパシタ C L C は画素電極と共に通電極を二端子とし、二端子間に誘電体として機能する液晶を含む。

## 【 0 0 3 0 】

カラーフィルタ基板には、光漏れ防止のためのブラックマトリクス、色を実現するためのカラーフィルタ、及び共通電極が形成される。液晶は誘電率異方性を有する物質であり、共通電極と画素電極に印加された電圧の差により回転して光の透過率を調節する。

20

前記第 1 ゲート駆動回路 1 3 0 及び第 2 ゲート駆動回路 1 4 0 は、ゲートライン G L 1 ~ G L n を介して液晶パネル 1 1 0 の一方側及び他方側である第 1 周辺領域 P A 1 に集積されて形成され、その出力がゲートライン G L 1 ~ G L n の両端にそれぞれに接続される。第 1 ゲート駆動回路 1 3 0 及び第 2 ゲート駆動回路 1 4 0 は、ゲートライン G L 1 ~ G L n の両端からゲート駆動パルスを一度に一つのゲートラインに順次供給してゲートライン G L 1 ~ G L n をデュアル駆動させ、垂直スキャン動作に影響を与える。少なくとも第 1 ゲート駆動回路 1 3 0 及び第 2 ゲート駆動回路 1 4 0 の一方は、例えば、垂直スキャンの終点でゲート駆動回路 1 3 0 はゲート駆動回路 1 3 0 をリセットするリセット信号 R E s i g を提供する。示されたようにこのフレームの終点のリセット信号 R E s i g はクリップ部 1 9 0 に駆動的に接続できる。このように、ゲート駆動回路 1 3 0 は、フレームの終点を示すリセット信号 R E s i g を出力する。クリップ部 1 9 0 は、リセット信号 R E s i g を受信し、リセット信号 R E s i g に基づく C R E s i g 信号を最後のタイミングコントローラ 1 7 0 に出力する。

30

## 【 0 0 3 1 】

前記データ駆動部 1 2 0 は、タイミングコントローラ 1 7 0 からデータ制御信号及びデータを受信し、データに該当するアナログ駆動電圧を選択してデータライン D L 1 ~ D L m に階調表示電圧として供給する。データ駆動部 1 2 0 は集積化されたチップで実現され、薄膜トランジスタ基板 1 1 2 の第 2 周辺領域 P A 2 に実装される。データ駆動部 1 2 0 は第 2 周辺領域 P A 2 に接続されるフレキシブルプリント基板 1 0 2 を介してタイミングコントローラ 1 7 0 及び電源供給部 1 8 0 に接続される。

40

## 【 0 0 3 2 】

一方、本実施形態において、データ駆動部 1 2 0 が薄膜トランジスタ基板 1 1 2 に C O G (Chip On Glass) 方式で実装される場合を例示したが、これに限定されるものではなく、T C P (Tape Carrier Package) 方式で実装されたり、第 1 ゲート駆動回路 1 3 0 及び第 2 ゲート駆動回路 1 4 0 のように直接薄膜トランジスタ基板 1 1 2 に集積化されて形成されてもよい。

## 【 0 0 3 3 】

前記第 1 レベルシフタ 1 5 0 及び第 2 レベルシフタ 1 6 0 は、タイミングコントローラ 1 7 0 からゲート制御信号が入力され、電源供給部 1 8 0 から駆動電圧が印加され、ゲート駆動回路 1 3 0 、 1 4 0 を駆動させるゲート駆動信号を生成して第 1 ゲート駆動回路 1

50

30 及び第2ゲート駆動回路140にそれぞれ供給する。図1では、ゲート駆動信号は、データ駆動部120を介してゲート駆動回路130、140に供給される。

#### 【0034】

前記タイミングコントローラ170には、外部からデータ及び入力制御信号が入力され、ゲート制御信号及びデータ制御信号を生成して第1レベルシフタ150及び第2レベルシフタ160並びにデータ駆動部120に供給する。ここで、データはRGB映像信号であり、データ制御信号はロード信号を含み、入力制御信号は垂直同期信号、水平同期信号、メインクロック、及びデータタイネーブル信号を含む。タイミングコントローラ170は、クリップ部190からリセット信号RESIGに基づくりセット信号CRESIGが供給され、データ駆動部120に供給されるロード信号のタイミングを調節する。

10

#### 【0035】

前記電源供給部180は、外部から供給された電源電圧を利用してアナログ駆動電圧、共通電圧VCOM、ゲート駆動電圧を生成する。電源供給部180は、アナログ駆動電圧をデータ駆動部120に供給し、共通電圧VCOMを液晶パネル110の共通電極に供給し、ゲート駆動電圧を第1レベルシフタ150及び第2レベルシフタ160に供給する。

前記クリップ部190は、第1ゲート駆動回路130からリセット信号RESIGを取得し、リセット信号RESIGに基づいてリセット信号CRESIGを生成してタイミングコントローラ170に供給する。

#### 【0036】

ここで、リセット信号CRESIGは、リセット信号RESIGをタイミングコントローラ170が処理できる電圧レベルに制限した信号である。また、リセット信号RESIGは、ゲート駆動回路130のダミーステージから出力されるゲートオン電圧VONまたはとゲートオフ電圧VOFFレベルの信号であり、ディスプレイの各垂直スキャンの終点で第1ゲート駆動回路130をリセットする信号である。従って、前記リセット信号RESIGは、スキャン信号（垂直同期信号）と組合せられ、全てのディスプレイ上の行（以下、ディスプレイローという）を順次に活性化する動作において、第1ゲート駆動回路130の蓄積された遅延を示す。また、行（ライン）当りの遅延（per-line delay）は、測定された総遅延をスキャンされた行（ライン）の総数で割ることで計算することができる。示されていないが、適切な演算論理部またはマイクロコントローラまたはマイクロプロセッサが、行当りの遅延、収集された遅延の総量を算出するのに使用されることがある。これらの計算手段は、与えられたディスプレイの所定の行数を算出することもできる。ダミーステージn+1の出力は、クリップ回路190に入力されるだけではなく、全てのステージにリセット入力として入力されることもできる。全てのステージが前記ダミーステージn+1の出力をリセット入力として取り込むことで、全てのステージが同様の動作を行うことができる。前記ダミーステージn+1のゲートラインGLn+1は、他のステージの出力負荷に近接するために適切な数か少ない数のダミゲートパッドを有することができる。

20

30

#### 【0037】

例えば、クリップ部190は、ゲートオン電圧VONとゲートオフ電圧VOFFレベルのリセット信号RESIGを、3.3Vレベルに振幅を制限し、クリップされたリセット信号CRESIGとして出力するクリップ回路を含む。このような機能を実行するクリップ回路は前述した説明から当業者が容易に実現できるので、詳細な説明は省略する。

40

前記タイミングコントローラ170、第1レベルシフタ150、第2レベルシフタ160、電源供給部180、及びクリップ部190はコントロールプリント基板104に実装される。コントロールプリント基板104はフレキシブルプリント基板102を介して薄膜トランジスタ基板112の第2周辺領域PA2に接続される。液晶パネル110に形成された第1ゲート駆動回路130及び第2ゲート駆動回路140は、データ駆動部120を介してタイミングコントローラ170及び電源供給部180に接続されるか、又はフレキシブルプリント基板102を介して直接タイミングコントローラ170及び電源供給部180に接続される。

50

## 【0038】

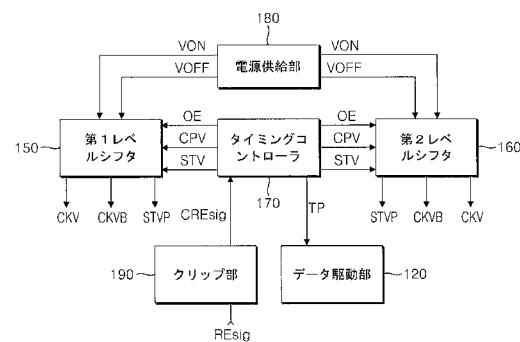

図2は図1に示すタイミングコントローラの入出力信号の関係を示す図である。図2に示すように、タイミングコントローラ170は第1レベルシフタ150及び第2レベルシフタ160に出力イネーブル信号O E、ゲートクロックC P V、及びゲートスタート信号S T Vをそれぞれ供給する。また、タイミングコントローラ170はクリップ部190から供給されるクリップされたリセット信号C R E s i gに応答してロード信号T Pのタイミングを調節してデータ駆動部120に供給する。

## 【0039】

一方、第1レベルシフタ150及び第2レベルシフタ160は、電源供給部180からゲート駆動電圧のゲートオン電圧V O Nとゲートオフ電圧V O F Fが供給され、タイミングコントローラ170からゲート制御信号である出力イネーブル信号O E、ゲートクロックC P V、及びゲートスタート信号S T Vが供給され、ゲートオン電圧V O Nとゲートオフ電圧V O F Fレベルの開始パルスS T V P、ゲートクロックパルスC K V、及び反転ゲートクロックパルスC K V Bを生成し、これをデータ駆動部120を介して第1ゲート駆動回路130及び第2ゲート駆動回路140に供給する。

10

## 【0040】

ここで、ゲートスタート信号S T Vは1フレーム(Frame)の開始を通知する信号であり、開始パルスS T V Pはゲート駆動回路130、140が1フレームの最初のゲート駆動信号を生成するようにする信号である。また、ゲートクロックパルスC K V及び反転ゲートクロックパルスC K V Bは、互いに位相が反転したクロックであり、ゲートラインを駆動する速度を調整し、例えば速くするために使用される。

20

## 【0041】

図3は図2に示すタイミングコントローラの構成を示すブロック図である。図3に示すように、タイミングコントローラ170は、出力イネーブル信号生成部172、カウンタ部174、及びロード信号生成部176を含む。

30

前記出力イネーブル信号生成部172は、1フレームの最後の出力イネーブル信号L A S T O Eをカウンタ部174に供給する。ここで、ゲートラインを活性化するためのシフトレジスタは、複数のステージが直列に接続されて形成されており、最後のステージはダミーステージである。1フレームの最後の出力イネーブル信号L A S T O Eとは、ダミーステージに供給されるゲートクロックパルスC K Vを生成するために使用された出力イネーブル信号O Eに時間的に対応した信号である。前記ダミーステージは、前記シフトレジストの他のステージと同一の工程で製造され、その応答遅延は他のステージの応答遅延と同じである。

## 【0042】

前記カウンタ部174は、クリップされたリセット信号C R E s i gのライジング時点と、最後の出力イネーブル信号L A S T O Eのライジング(Rising)時点との差異を示すクロックカウント信号C L K C O U N Tを生成し、これをロード信号生成部176に供給する。ここで、クロックカウント信号C L K C O U N Tは、ゲート駆動回路130、140によるゲート駆動信号の遅延時間をクロックに基づいて算出した信号である。

40

## 【0043】

具体的に説明すると、リセット信号R E s i gは、ゲート駆動回路のダミーステージから出力される信号であり、リセット信号C R E s i gはリセット信号R E s i gに基づいて生成されるため、リセット信号R E s i gに時間的に対応した信号である。また、最後の出力イネーブル信号L A S T O Eは、ダミーステージをイネーブルにするための出力イネーブル信号O Eに時間的に対応した信号である。よって、リセット信号C R E s i gのライジング時点と、最後の出力イネーブル信号L A S T O Eのライジング時点との差異を算出することで、ダミーステージがイネーブルされてから信号が出力されるまでの応答時間が算出され、最終的にゲート駆動信号の遅延時間が算出される。

## 【0044】

前記ロード信号生成部176は、クロックカウント信号C L K C O U N Tに応答してロード信号T Pを生成する。

50

ード信号 T P のフォーリング (Falling) 時点を調節する。データ駆動部 1 2 0 はロード信号 T P のフォーリング時点にデータを出力するからである。

従って、本発明の一実施形態による液晶表示装置は、ゲート駆動回路のリセット信号のフィードバックを受ける。また、フィードバックに基づいてロード時間（即ち、T P パルスフォーリングエッジ）を調節してゲート駆動回路によるゲート駆動信号の出力遅延を補償できる。そのため、ゲート駆動回路自体の遅延によって、データが出力されるよりもゲート駆動信号が遅延して印加される問題を解消できる。これにより、液晶パネルの下端部に位置するゲートラインに接続された画素が本来表示されるべきデータに対応する輝度より暗い輝度で表示するという問題を解消できる。

#### 【0045】

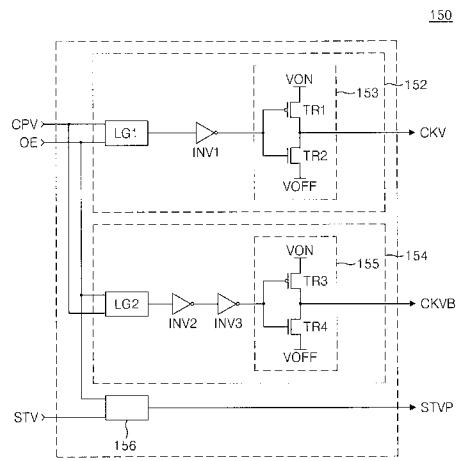

図 4 は図 1 に示す第 1 レベルシフタの例を示す回路図である。図 4 に示すように、第 1 レベルシフタ 1 5 0 は、第 1 レベルシフト部 1 5 2 、第 2 レベルシフト部 1 5 4 、及び第 3 レベルシフト部 1 5 6 を含む。

第 1 レベルシフト部 1 5 2 は、出力イネーブル信号 O E とゲートクロック C P V を論理演算し、電圧のレベルを増幅して第 1 ゲート駆動回路に供給するゲートクロックパルス C K V を発生する。このために第 1 レベルシフト部 1 5 2 は、論理演算部 L G 1 、駆動インバータ I N V 1 、及びフルスインギングインバータ 1 5 3 を含む。

#### 【0046】

論理演算部 L G 1 は出力イネーブル信号 O E とゲートクロック C P V とをオア演算する。駆動インバータ I N V 1 は、論理演算部 L G 1 の出力の位相を反転させてフルスインギングインバータ 1 5 3 の駆動レベルに増幅する。フルスインギングインバータ 1 5 3 は、駆動インバータ I N V 1 の出力に応答してゲートオン電圧 V O N 及びゲートオフ電圧 V O F F レベルのゲートクロックパルス C K V を生成する。

#### 【0047】

第 2 レベルシフト部 1 5 4 は、出力イネーブル信号 O E とゲートクロック C P V を論理演算し、電圧のレベルを増幅して第 1 ゲート駆動回路に供給する反転ゲートクロックパルス C K V B を発生する。このために第 2 レベルシフト部 1 5 4 は、論理演算部 L G 2 、反転インバータ I N V 2 、駆動インバータ I N V 3 、及びフルスインギングインバータ 1 5 5 を含む。ここで、反転ゲートクロックパルス C K V B はゲートクロックパルス C K V の位相が反転したクロックである。

#### 【0048】

論理演算部 L G 2 は出力イネーブル信号 O E とゲートクロック C P V をオア演算する。反転インバータ I N V 2 は論理演算部 L G 2 の出力の位相を反転させて出力する。駆動インバータ I N V 3 は反転インバータ I N V 2 の出力の位相を反転させてフルスインギングインバータ 1 5 5 の駆動レベルに増幅する。フルスインギングインバータ 1 5 5 は駆動インバータ I N V 3 の出力に応答してゲートオン電圧 V O N 及びゲートオフ電圧 V O F F レベルの反転ゲートクロックパルス C K V B を生成する。

#### 【0049】

第 3 レベルシフト部 1 5 6 は、出力イネーブル信号 O E とゲートスタート信号 S T V が入力され、ゲートオン電圧 V O N 及びゲートオフ電圧 V O F F レベルの開始パルス S T V P を発生する。ここで、開始パルス S T V P は、ゲートスタートパルス S T V と同一の周期とパルス幅を有し、ゲートオン電圧 V O N 及びゲートオフ電圧 V O F F のレベルを有する。これは論理演算部 L G 1 が A N D 機能に置換された第 1 レベルシフト部 1 5 2 と類似した回路によって具現されることができる。

#### 【0050】

一方、第 2 レベルシフタ 1 6 0 の構成は前述した第 1 レベルシフタ 1 5 0 の構成及び動作から当業者が容易に実施できるので、詳細な説明は省略する。

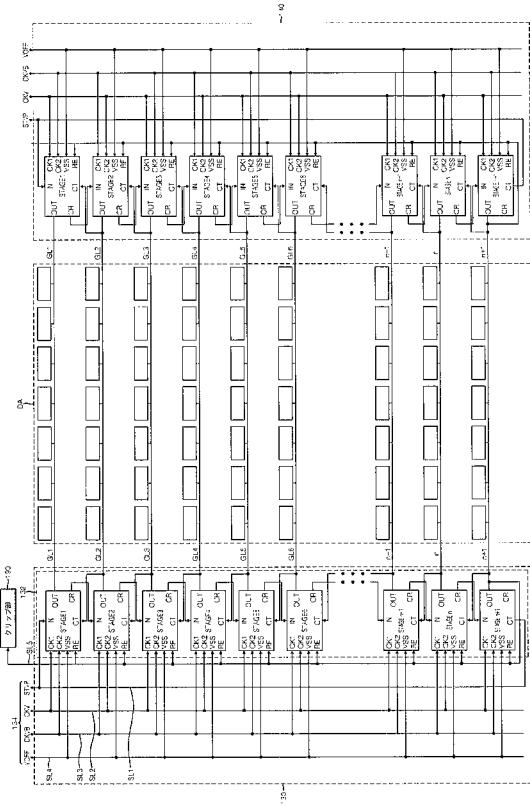

図 5 は図 1 に示す第 1 及び第 2 ゲート駆動回路の構成を示すブロック図である。図 5 に示すように、第 1 ゲート駆動回路 1 3 0 及び第 2 ゲート駆動回路 1 4 0 は、ゲートライン G L 1 ~ G L n を両側からデュアル駆動できるように表示領域 D A の両側に隣接して配置

10

20

30

40

50

される。しかし、示されたように、ゲートライン  $GL_{n+1}$  及び駆動ステージ  $n+1$  が一つずつ各端部に追加されることもできる。第1ゲート駆動回路 130 及び第2ゲート駆動回路 140 は、ゲートライン  $GL_1 \sim GL_n$  を基準に対称の構造を有する。

#### 【0051】

第1ゲート駆動回路 130 は、データ駆動部から各種信号が入力されて回路部 132 に伝達する配線部 134 と、配線部 134 を介して伝達される各種信号に応答してゲート駆動信号を順次出力する回路部 132 とを含む。

前記回路部 132 は、互いに従属的に接続された複数のステージ STAGE 1 ~ STAGE  $n+1$  から構成されるシフトレジスタを含む。第1ステージ STAGE 1 ~ 第  $n$  ステージ STAGE  $n$  は、第1ゲートライン  $GL_1 \sim GL_n$  に電気的に接続されてゲート駆動信号を順次出力する。ここで、 $n+1$  ステージ STAGE  $n+1$  はダミーステージであり、 $n$  は偶数である。

#### 【0052】

複数のステージ STAGE 1 ~ STAGE  $n+1$  は、それぞれ第1クロック端子 CK1、第2クロック端子 CK2、入力端子 IN、制御端子 CT、出力端子 OUT、リセット端子 RE、キャリー端子 CR、及び接地電圧端子 VSS を含む。

複数のステージ STAGE 1 ~ STAGE  $n+1$  のうち奇数番目のステージ STAGE 1、STAGE 3 ~ STAGE  $n+1$  は、第1クロック端子 CK1 にゲートクロックパルス CKV が供給され、第2クロック端子 CK2 に反転ゲートクロックパルス CKVB が供給される。複数のステージ STAGE 1 ~ STAGE  $n$  のうち偶数番目のステージ STAGE 2、STAGE 4 ~ STAGE  $n$  は、第1クロック端子 CK1 に反転ゲートクロックパルス CKVB が供給され、第2クロック端子 CK2 にゲートクロックパルス CKV が供給される。

#### 【0053】

複数のステージ STAGE 1 ~ STAGE  $n+1$  の入力端子 IN は前のステージのキャリー端子 CR に接続されて前のステージのキャリー信号が供給され、制御端子 CT は次のステージの出力端子 OUT に接続されて次のステージの出力信号が供給される。第1ステージ STAGE 1 は、前のステージが存在しないので入力端子 IN に開始パルス STVP が供給される。キャリー端子 CR から出力されるキャリー信号は次のステージを駆動させる役割を果たす。

#### 【0054】

$n$  番目のステージ STAGE  $n$  の制御端子 CT にキャリー信号を供給するダミーステージ STAGE  $n+1$  の制御端子 CT には開始パルス STVP が供給されることが好ましい。複数のステージ STAGE 1 ~ STAGE  $n+1$  の接地電圧端子 VSS にはゲートオフ電圧 VOFF が供給されており、リセット端子 RE には  $n+1$  ステージ STAGE  $n+1$  の出力信号が供給される。

#### 【0055】

また、複数のステージ STAGE 1 ~ STAGE  $n+1$  のうち奇数番目のステージ STAGE 1、STAGE 3 ~ STAGE  $n+1$  の出力端子 OUT はゲートクロックパルス CKV をゲート駆動信号として出力し、キャリー端子 CR はゲートクロックパルス CKV をキャリー信号として出力する。複数のステージ STAGE 1 ~ STAGE  $n$  のうち偶数番目のステージ STAGE 2、STAGE 4 ~ STAGE  $n$  の出力端子 OUT は反転ゲートクロックパルス CKVB をゲート駆動信号として出力し、キャリー端子 CR は反転ゲートクロックパルス CKVB をキャリー信号として出力する。

#### 【0056】

すなわち、第1ゲート駆動回路 130 は、奇数番目のステージ STAGE 1、STAGE 3 ~ STAGE  $n+1$  がゲートクロックパルス CKV に同期してゲート駆動信号を出力し、偶数番目のステージ STAGE 2、STAGE 4 ~ STAGE  $n$  が反転ゲートクロックパルス CKVB に同期してゲート駆動信号を出力する構造を有する。

第1ゲート駆動回路 130 の複数のステージ STAGE 1 ~ STAGE  $n$  の出力端子 O

10

20

30

40

50

U T は表示領域 D A に形成されたゲートライン G L 1 ~ G L n にそれぞれ対応して接続され、ゲート駆動信号をゲートライン G L 1 ~ G L n に順次供給してゲートライン G L 1 ~ G L n を順次駆動する。

#### 【 0 0 5 7 】

前記配線部 1 3 4 は回路部 1 3 2 に隣接して形成される。配線部 1 3 4 は、互いに平行に伸びた開始パルス配線 S L 1 、ゲートクロックパルス配線 S L 2 、反転ゲートクロックパルス配線 S L 3 、接地電圧配線 S L 4 、及びリセット配線 S L 5 を含む。

開始パルス配線 S L 1 は、第 1 レベルシフタ 1 5 0 から開始パルス S T V P が伝達されて第 1 ステージ S T A G E 1 の入力端子 I N と n + 1 ステージ S T A G E n + 1 の制御端子 C T に入力する。

#### 【 0 0 5 8 】

ゲートクロックパルス配線 S L 2 は、第 1 レベルシフタ 1 5 0 からゲートクロックパルス C K V が伝達されて奇数番目のステージ S T A G E 1 、 S T A G E 3 ~ S T A G E n + 1 の第 1 クロック端子 C K 1 に供給し、偶数番目のステージ S T A G E 2 、 S T A G E 4 ~ S T A G E n の第 2 クロック端子 C K 2 に供給する。

反転ゲートクロックパルス配線 S L 3 は、第 1 レベルシフタ 1 5 0 から反転ゲートクロックパルス C K V B が伝達されて奇数番目のステージ S T A G E 1 、 S T A G E 3 ~ S T A G E n + 1 の第 2 クロック端子 C K 2 に供給し、偶数番目のステージ S T A G E 2 、 S T A G E 4 ~ S T A G E n の第 1 クロック端子 C K 1 に供給する。

#### 【 0 0 5 9 】

接地電圧配線 S L 4 は、電源供給部 1 8 0 からゲートオフ電圧 V O F F が伝達されて第 1 ステージ S T A G E 1 ~ 第 n + 1 ステージ S T A G E n + 1 の接地電圧端子 V S S に供給する。

リセット配線 S L 5 は、第 n + 1 ステージ S T A G E n + 1 の出力端子 O U T の出力信号を複数のステージ S T A G E 1 ~ S T A G E n + 1 のリセット端子 R E にリセット信号 R E s i g として供給する。また、リセット配線 S L 5 は、第 n + 1 ステージ S T A G E n + 1 の出力端子 O U T の出力信号をクリップ部 1 9 0 に供給する。

#### 【 0 0 6 0 】

第 1 ゲート駆動回路 1 3 0 及び第 2 ゲート駆動回路 1 4 0 は、ゲートライン G L 1 ~ G L n を基準に対称の構造を有する。前述した第 1 ゲート駆動回路 1 3 0 についての説明から当業者は第 2 ゲート駆動回路 1 4 0 の構成を容易に実施できるので、第 2 ゲート駆動回路 1 4 0 の詳細な説明は省略する。

例えば、右側回路部分 1 4 0 のリセットラインはクリップ部 1 9 0 に連結される必要がない。これとは異なり、クリップ部 1 9 0 は、左側の代わりに右側回路部分 1 9 0 のリセットパルスを受けることができる。

#### 【 0 0 6 1 】

本発明の一実施形態による液晶表示装置は、同じ構成のゲート駆動回路をゲートラインの両端に配置してゲートラインをデュアル駆動する構成を有する。そのため、ゲート駆動信号がゲートラインの端部に近づくほど遅延出力されてゲートラインの左右側の両端部で隣接する両ゲートライン間に輝度差が発生する従来の問題を解消することができる。例えば、右側のゲート駆動回路からゲートラインにゲート駆動信号を供給された場合、左側にいくほど信号遅延が生じる。同様に、左側のゲート駆動回路からゲートラインにゲート駆動信号を供給された場合、右側にいくほど信号遅延が生じる。しかし、右側及び左側のゲート駆動回路が交互に駆動されるため、隣接するラインで遅延から生じる輝度差が互いに補償される。

#### 【 0 0 6 2 】

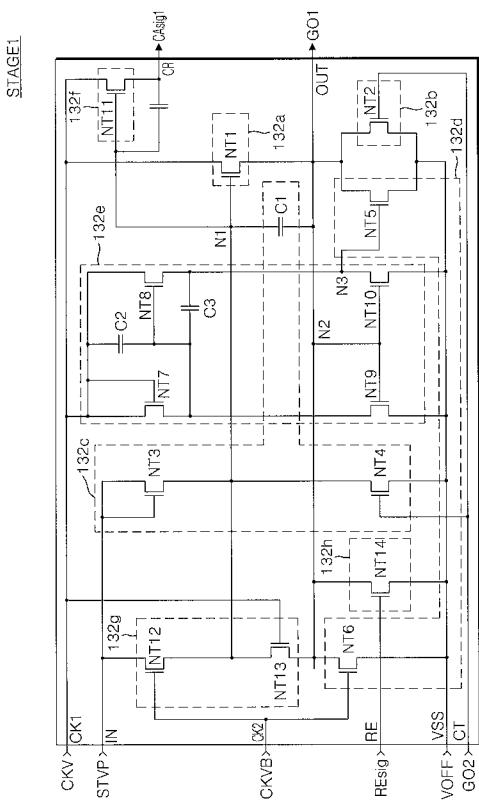

図 6 は図 5 に示す第 1 ステージの例を示す回路図である。図 6 に示すように、第 1 ステージ S T A G E 1 は、プルアップ部 1 3 2 a 、プルダウン部 1 3 2 b 、駆動部 1 3 2 c 、ホールド部 1 3 2 d 、スイッチ部 1 3 2 e 、及びキャリー部 1 3 2 f を含む。

前記プルアップ部 1 3 2 a は、第 1 クロック端子 C K 1 から供給されるゲートクロック

10

20

30

40

50

パルス C K V をプルアップして出力端子 O U T からゲート駆動信号 G O 1 として出力する。プルアップ部 1 3 2 a は、ゲートが第 1 ノード N 1 に接続され、ドレインが第 1 クロック端子 C K 1 に接続され、ソースが出力端子 O U T に接続される第 1 トランジスタ N T 1 を含む。

#### 【 0 0 6 3 】

前記プルダウン部 1 3 2 b は、第 2 ステージからのゲート駆動信号 G O 2 に応答してプルアップされたゲート駆動信号 G O 1 を接地電圧端子 V S S から供給されたゲートオフ電圧 V O F F にプルダウンする。プルダウン部 1 3 2 b は、ゲートが制御端子 C T に接続され、ドレインが出力端子 O U T に接続され、ソースが接地電圧端子 V S S に接続された第 2 トランジスタ N T 2 を含む。

10

#### 【 0 0 6 4 】

前記駆動部 1 3 2 c は、入力端子 I N から供給される開始パルス S T V P に応答してプルアップ部 1 3 2 a をターンオンさせ、第 2 ステージのゲート駆動信号 G O 2 に応答してプルアップ部 1 3 2 a をターンオフさせる。このために駆動部 1 3 2 c は、バッファ部、充電部、及び放電部を含む。

バッファ部は、ゲート及びドレインが入力端子 I N に共通接続され、ソースが第 1 ノード N 1 に接続された第 3 トランジスタ N T 3 を含む。充電部は、第 1 電極が第 1 ノード N 1 に接続され、第 2 電極が第 2 ノードに接続された第 1 キャパシタ C 1 を含む。放電部は、ゲートが制御端子 C T に接続され、ドレインが第 1 ノード N 1 に接続され、ソースが接地電圧端子 V S S に接続される第 4 トランジスタ N T 4 を含む。

20

#### 【 0 0 6 5 】

入力端子 I N に開始パルス S T V P が入力されると、これに応答して第 3 トランジスタ N T 3 がターンオンし、開始パルス S T V P が第 1 キャパシタ C 1 に充電される。第 1 キャパシタ C 1 に第 1 トランジスタ N T 1 の閾電圧以上の電荷が充電されると、第 1 トランジスタ N T 1 がターンオンして第 1 クロック端子 C K 1 から供給されるゲートクロックパルス C K V を出力端子 O U T に出力する。

#### 【 0 0 6 6 】

ここで、第 1 ノード N 1 の電位は、第 2 ノード N 2 の突然の電位の変化による第 1 キャパシタ C 1 のカップリング (Coupling) により、第 2 ノード N 2 の電位変化量だけブートストラップ (Boot Strap) される。従って、第 1 トランジスタ N T 1 は、ドレインに印加された第 1 ゲートクロックパルス C K V を出力端子 O U T に容易に出力できる。出力端子 O U T に出力されたゲートクロックパルス C K V はゲートラインに供給されるゲート駆動信号 G O 1 となる。ここで、開始パルス S T V P は、第 1 ゲート駆動信号を生成するために第 1 トランジスタ N T 1 を予備に充電する信号として使用される。

30

#### 【 0 0 6 7 】

その後、制御端子 C T から入力される第 2 ステージの出力信号であるゲート駆動信号 G O 2 に応答して第 4 トランジスタ N T 4 がターンオンすると、第 1 キャパシタ C 1 に充電された電荷は接地電圧端子 V S S から供給されるゲートオフ電圧 V O F F レベルで放電される。

40

前記ホールド部 1 3 2 d は、ゲート駆動信号 G O 1 をゲートオフ電圧 V O F F レベル状態でホールドする第 5 トランジスタ N T 5 及び第 6 トランジスタ N T 6 を含む。第 5 トランジスタ N T 5 は、ゲートが第 3 ノード N 3 に接続され、ドレインが第 2 ノード N 2 に接続され、ソースが接地電圧端子 V S S に接続される。第 6 トランジスタ N T 6 は、ゲートが第 2 クロック端子 C K 2 に接続され、ドレインが第 2 ノード N 2 に接続され、ソースが接地電圧端子 V S S に接続される。

#### 【 0 0 6 8 】

前記スイッチ部 1 3 2 e は、第 7 トランジスタ N T 7 、第 8 トランジスタ N T 8 、第 9 トランジスタ N T 9 、及び第 10 トランジスタ N T 10 と、第 2 キャパシタ C 2 及び第 3 キャパシタ C 3 を含み、ホールド部 1 3 2 d の駆動を制御する。第 7 トランジスタ N T 7 は、ゲートとドレインが第 1 クロック端子 C K 1 に接続され、ソースは第 9 トランジス

50

タN T 9 のドレインと第 8 トランジスタN T 8 のゲートに共通接続される。第 8 トランジスタN T 8 は、ドレインが第 1 クロック端子C K 1 に接続され、ゲートは第 2 キャパシタ C 2 を介して前記第 7 トランジスタN T 7 のドレインと接続され、ソースは第 3 ノードN 3 に接続され、ゲートとソースは第 3 キャパシタ C 3 を介して互いに接続される。第 9 トランジスタN T 9 は、ドレインが第 7 トランジスタN T 7 のソースに接続され、ゲートは第 2 ノードN 2 に接続され、ソースは接地電圧端子V S S に接続される。第 1 0 トランジスタN T 1 0 は、ドレインが第 3 ノードN 3 に接続され、ゲートは第 2 ノードN 2 に接続され、ソースは接地電圧端子V S S に接続される。

## 【0 0 6 9】

出力端子O U T にハイ状態のゲートクロックパルスC K V がゲート駆動信号G O 1 として出力されると、第 2 ノードN 2 の電位はハイ状態に上昇する。第 2 ノードN 2 の電位がハイ状態に上昇すると、第 9 トランジスタN T 9 及び第 1 0 トランジスタN T 1 0 はターンオン状態に切り替えられる。ここで、第 1 クロック端子C K 1 に供給されるゲートクロックパルスC K V によって第 7 トランジスタN T 7 及び第 8 トランジスタN T 8 がターンオンした状態に切り替えられても、第 7 トランジスタN T 7 及び第 8 トランジスタN T 8 から出力された信号は第 9 トランジスタN T 9 及び第 1 0 トランジスタN T 1 0 を介して接地電圧V O F F 状態で放電される。従って、ハイ状態のゲート駆動信号G O 1 が出力される間、第 3 ノードN 3 の電位はロー状態に維持されるので、第 5 トランジスタN T 5 はターンオフ状態を維持する。

## 【0 0 7 0】

その後、制御端子C T から入力された第 2 ステージのゲート駆動信号G O 2 に応答してゲート駆動信号G O 1 が接地電圧端子V S S から放電され、第 2 ノードN 2 の電位はロー状態に徐々に下降する。従って、第 9 トランジスタN T 9 及び第 1 0 トランジスタN T 1 0 はターンオフ状態に切り替えられ、第 7 トランジスタN T 7 及び第 8 トランジスタN T 8 から出力された信号によって第 3 ノードN 3 の電位はハイ状態に上昇する。第 3 ノードN 3 の電位が上昇するにつれて第 5 トランジスタN T 5 がターンオンし、第 2 ノードN 2 の電位は第 5 トランジスタN T 5 を介してゲートオフ電圧V O F F 状態で放電される。

## 【0 0 7 1】

この状態で、第 2 クロック端子C K 2 に供給される反転ゲートクロックパルスC K V B によって第 6 トランジスタN T 6 がターンオンすると、第 2 ノードN 2 の電位は接地電圧端子V S S から完全に放電される。

その結果、ホールド部1 3 2 d の第 5 トランジスタN T 5 及び第 6 トランジスタN T 6 は、第 2 ノードN 2 の電位をゲートオフ電圧V O F F 状態でホールドする。スイッチ部1 3 2 e は、第 5 トランジスタN T 5 がターンオンする時点を決定する。

## 【0 0 7 2】

前記キャリー部1 3 2 f は、ドレインが第 1 クロック端子C K 1 に接続され、ゲートが第 1 ノードN 1 に接続され、ソースがキャリー端子C R に接続された第 1 1 トランジスタN T 1 1 を含む。第 1 1 トランジスタN T 1 1 は、第 1 ノードN 1 の電位が上昇するにつれてターンオンし、ドレインに入力されたゲートクロックパルスC K V をキャリー信号C A s i g 1 として出力する。キャリー信号は次のステージの入力端子I N に供給され、次のステージの駆動のための開始パルスS T V P として使用される。

## 【0 0 7 3】

一方、第 1 ステージS T A G E 1 は、リップル防止部1 3 2 g とリセット部1 3 2 h をさらに含む。前記リップル防止部1 3 2 g は、既にゲートオフ電圧V O F F 状態に維持されたゲート駆動信号G O 1 が入力端子I N から入力されるノイズによってリップルされることを防止する。このためにリップル防止部1 3 2 g は、第 1 2 トランジスタN T 1 2 と、第 1 3 トランジスタN T 1 3 とを含む。第 1 2 トランジスタN T 1 2 は、ドレインが入力端子I N に接続され、ゲートが第 2 クロック端子C K 2 に接続され、ソースは第 1 ノードN 1 に接続される。第 1 3 トランジスタN T 1 3 は、ドレインが第 1 ノードN 1 に接続され、ゲートが第 1 クロック端子C K 1 に接続され、ソースが第 2 ノードN 2 に接続され

10

20

30

40

50

る。

#### 【0074】

前記リセット部132hは、ドレインが第1ノードN1に接続され、ゲートがリセット端子REに接続され、ソースが接地電圧端子VSSに接続された第14トランジスタNT14を含む。第14トランジスタNT14は、リセット端子REから入力された第n+1ステージSTAGE n+1の出力信号であるリセット信号REsingに応答して第1ノードN1をゲートオフ電圧VOFF状態で放電させる。第n+1ステージSTAGE n+1の出力信号であるリセット信号REsingは1フレームの最後を意味するので、リセット部132hは1フレームが終わる時点に複数のステージSTAGE 1～STAGE nの全ての第1ノードN1を同時に放電させる。

10

#### 【0075】

すなわち、前記リセット部132hは、複数のステージSTAGE 1～STAGE nから順次ゲート駆動信号が出力され、その後第n+1ステージSTAGE n+1の出力信号によって複数のステージSTAGE 1～STAGE nの第14トランジスタNT14をターンオンさせることにより、複数のステージSTAGE 1～STAGE nの第1ノードN1をゲートオフ電圧VOFFの状態にリセットする。従って、その後回路部132の複数のステージSTAGE 1～STAGE n+1は初期化した状態で再び動作を始めることができる。

#### 【0076】

本実施形態において、前記リセット信号REsingは、ゲート駆動回路によるゲート駆動信号の遅延時間を算出するために、タイミングコントローラにフィードバックされる信号として使用される。一方、図5に示す第2～第n+1ステージは前述した第1ステージの構成から当業者が容易に実施できるので、詳細な説明は省略する。

20

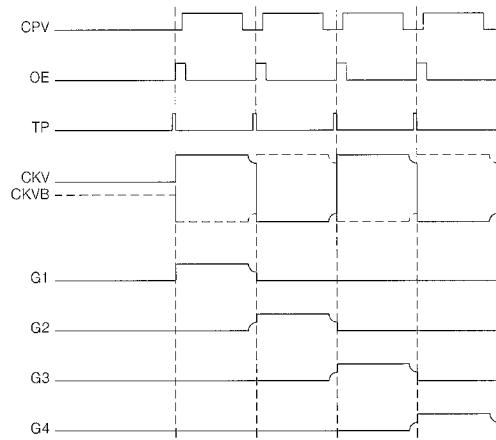

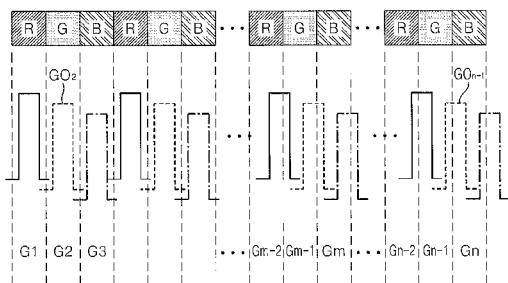

図7は図1に示す液晶表示装置の動作タイミング図である。図7に示すように、第1レベルシフタ150及び第2レベルシフタ160は、タイミングコントローラ170から供給された出力イネーブル信号OEとゲートクロックCPVをオア演算し、ゲートオン電圧VON及びゲートオフ電圧VOFFのゲートクロックパルスCKV及び反転ゲートクロックパルスCKVBを生成する。第1ゲート駆動回路130及び第2ゲート駆動回路140の奇数番目のステージSTAGE 1、STAGE 3～STAGE n+1はゲートクロックパルスCKVをゲート駆動信号として出力し、偶数番目のステージSTAGE 2、STAGE 4～STAGE nは反転ゲートクロックパルスCKVBをゲート駆動信号として出力する。

30

#### 【0077】

一方、タイミングコントローラ170は、各ゲートラインGL1～GLnに順次供給されるゲート駆動信号がハイレベルにライジングする時点にロード信号TPのフォーリング時点を同期させ、データ駆動部120が階調表示電圧をデータラインに供給するようする。従って、ゲート駆動回路130、140によってゲート駆動信号が遅延すると、ゲート駆動信号が遅延した時間だけロード信号TPのフォーリング時点を遅延させ、ゲート駆動回路130、140によってゲート駆動信号が遅延することにより発生する問題が解消できる。

40

#### 【0078】

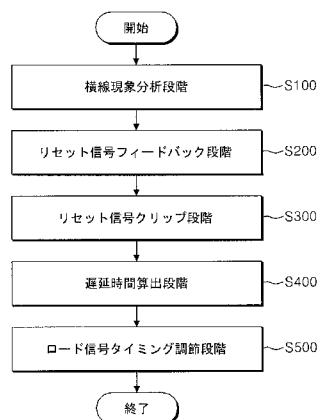

本発明の一実施形態による液晶表示装置を利用し、ゲート駆動回路のリセット信号のフィードバックを受けてゲート駆動回路による遅延を補償する方法について、図8～図12を参照してより詳細に説明する。図8は本発明の一実施形態によるASG遅延減少方法の手順を示すフローチャートであり、図9～図12はASG遅延減少方法を説明するための信号タイミング図である。

#### 【0079】

図8に示すように、本発明の一実施形態によるASG遅延減少方法は、横線現象分析段階(S100)、リセット信号フィードバック段階(S200)、リセット信号クリップ段階(S300)、遅延時間算出段階(S400)、及びロード信号タイミング調節段階

50

(S500)を含む。

前記横線現象分析段階(S100)は、ゲート駆動回路130、140が複数のゲートラインG<sub>L</sub>1～G<sub>L</sub>nに順次ゲート駆動信号を印加するとき、ゲート駆動回路130、140自体の遅延によってデータ出力よりゲート駆動信号が遅延して印加されることにより発生する横線現象を分析する段階である。

#### 【0080】

具体的には、図9に示すように、複数のゲートラインG<sub>L</sub>1～G<sub>L</sub>nに供給されるゲート駆動信号は、液晶パネル110の下端部に近づくほどゲート駆動回路130、140自体の遅延によって出力が遅延する現象が発生する。例えば、ゲートラインを順次駆動しながら赤R、緑G、及び青Bに該当する階調表示電圧を該当ゲートラインに接続された画素にそれぞれ供給する場合、液晶パネル110の下端部に近づくほどゲート駆動信号が遅延してゲートラインに接続された画素には本来表示されるべき色相と異なる色相が表示される。

#### 【0081】

より詳細には、緑Gの階調表示電圧が印加されるG2ゲートラインとG<sub>n</sub>-1ゲートラインを比較すると、G2ゲートラインに接続された画素には、ゲート駆動信号G<sub>O</sub>2がハイである区間の間、緑に該当する階調表示電圧が正常に供給される。それに対して、G<sub>n</sub>-1ゲートラインに接続された画素には、ゲート駆動信号G<sub>O</sub><sub>n</sub>-1がハイである区間の間、緑に該当する階調表示電圧だけでなく、青に該当する階調表示電圧が同時に供給され、本来表示されるべき色相が表示されなくなる。これは、ゲート駆動回路130、140自体の遅延によってデータ出力よりゲート駆動信号が遅延して印加されることによって発生する現象である。従って、ゲート駆動回路130、140自体の遅延によってゲート駆動信号が遅延した時間だけロード信号のタイミングを遅延させることにより前記問題を解決できることが分かる。

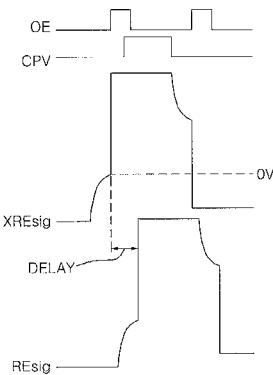

#### 【0082】

前記リセット信号フィードバック段階(S200)は、ゲート駆動回路130、140のダミーステージSTAGE<sub>n</sub>+1の出力信号であるリセット信号REsingをクリップ部190に供給する段階である。具体的には、図10に示すように、ゲート駆動回路130、140によってゲート駆動信号の遅延(DELAY)が発生した場合、リセット信号REsingにはゲート駆動回路130、140による遅延が発生し、ダミーステージSTAGE<sub>n</sub>+1の出力信号XREsingに対応して一定の遅延DELAYが発生することが分かる。ここで、OEとCPVは出力信号XREsingを生成するために使用された出力イネーブル信号とゲートクロックである。つまり、ダミーステージSTAGE<sub>n</sub>+1において、遅延が発生しない場合の出力信号XREsingと、実際のリセット信号REsingとに差がある場合は、遅延が生じていることが分かる。

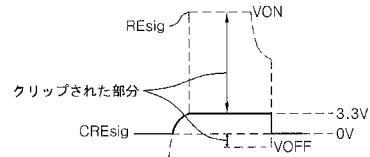

#### 【0083】

前記リセット信号クリップ段階(S300)は、クリップ部190によりリセット信号REsingを一定の電圧レベルにクリップしてタイミングコントローラ170に供給する段階である。具体的には、図11に示すように、リセット信号REsingはゲートオン電圧VON及びゲートオフ電圧VOFFレベルを有するため、リセット信号REsingをタイミングコントローラ170で処理できる電圧レベル、例えば0V及び3.3Vレベルの信号に変換してクリップされたリセット信号CREsingを生成する。

#### 【0084】

前記遅延時間算出段階(S400)は、クリップされたリセット信号CREsingと、最後の出力イネーブル信号LASTOEと、を利用してゲート駆動信号の遅延時間を測定し算出する段階である。ゲート駆動信号の遅延がない場合、ダミーステージSTAGE<sub>n</sub>+1から出力されるリセット信号REsingは最後の出力イネーブル信号LASTOEのライジング時点に出力され、データはロード信号TPのフォーリング時点に出力されなければならない。従って、クリップされたリセット信号CREsingと最後の出力イネーブル信号LASTOEを利用してゲート駆動信号の遅延時間を算出できる。ここで、ダミー

10

20

30

40

50

ステージのゲート駆動信号から測定された遅延時間は、行当たり遅延を計算するのに使用されることができ、ロード信号TPのフォーリングエッジのタイミングを累積して調節することに使用する。従って、ゲート駆動信号の遅延時間は下記の数式(1)～数式(3)によって算出できる。

【0085】

【数1】

$$1H_{ideal} = 1Frame_{ideal} \div Gn \quad \dots \quad (1)$$

数式(1)において、 $1H_{ideal}$ はゲート駆動回路130、140による遅延がない場合の1水平周期であり、 $1Frame_{ideal}$ はゲート駆動回路130、140による遅延がない場合の1フレーム周期であり、Gnはゲートラインの総数である。

【0086】

【数2】

$$1H_{real} = 1Frame_{real} \div Gn \quad \dots \quad (2)$$

数式(2)において、 $1H_{real}$ はゲート駆動回路130、140による遅延が発生した場合の1水平周期であり、 $1Frame_{real}$ はゲート駆動回路130、140による遅延が発生した場合の1フレーム周期であり、Gnはゲートラインの総数である。

【0087】

【数3】

$$T_{TP} = 1H_{ideal} \times Gm + (1H_{real} - 1H_{ideal}) \times Gm \div Gn \quad \dots \quad (3)$$

数式(3)において、 $T_{TP}$ はm番目のゲートラインに接続された画素にデータが印加されるべき時点、すなわちロード信号のフォーリング時点であり、Gmはm番目のゲートラインまでのゲートラインの数である。

【0088】

具体的には、図12に示すように、クリップされたリセット信号CREsingと、最後の出力イネーブル信号LASTOEと、を比較してゲート駆動信号の遅延時間を算出する。

ゲート駆動回路130、140による遅延がない場合、クリップされたリセット信号CREsingのライジング時点は最後の出力イネーブル信号LASTOEのライジング時点と同一でなければならないが、実際にはゲート駆動回路130、140によりリセット信号REsingが遅延して出力されるため、クリップされたリセット信号CREsingのライジング時点と最後の出力イネーブル信号LASTOEのライジング時点は一致しない。

【0089】

従って、クリップされたリセット信号CREsingのライジング時点を、最後の出力イネーブル信号LASTOEのライジング時点と比較し、出力イネーブル信号LASTOEのライジング時点から、クリップされたリセット信号CREsingのライジング時点までの区間に該当するクロック数をカウントしてクロックカウント信号CLKCOUNTを生成することにより、ゲート駆動信号の遅延時間を算出することができる。

【0090】

前記ロード信号タイミング調節段階(S500)は、クロックカウント信号CLKCOUNTに応答してロード信号TPのフォーリング時点を調節する段階である。例えば、ゲートライン数が768、クロックカウント信号CLKCOUNTが40の場合、768ライン/40クロック = 19.2と計算され、19.2ライン毎に1クロックずつ遅延が発生することが分かる。これを切り上げ処理すると、20ライン毎に1クロックずつ遅延が

10

20

30

40

50

発生することになる。

**【0091】**

従って、第1ゲートラインG L 1～第20ゲートラインG L 20に接続された画素には、各ゲートラインに該当する出力イネーブル信号O Eのライジング時点に、ロード信号T Pのフォーリング時点を同期してデータを出力する。また、第21ゲートラインG L 21～第40ゲートラインG L 40に接続された画素には、各ゲートラインに該当する出力イネーブル信号O Eのライジング時点より1クロック遅延した時点に、ロード信号T Pのフォーリング時点を同期してデータを出力する。

**【0092】**

また、第41ゲートラインG L 41～第60ゲートラインG L 60に接続された画素には、各ゲートラインに該当する出力イネーブル信号のライジング時点より2クロック遅延した時点に、ロード信号T Pのフォーリング時点を同期してデータを出力する。残りのゲートラインG L 61～G L 768に接続された画素にも同様の方式でロード信号T Pのフォーリング時点を調節してゲート駆動回路130、140によるゲート駆動信号の遅延を補償できる。

**【0093】**

すなわち、設定された1フレーム時間と実際のダミーステージS T A G E n + 1でリセット信号R E s i gが出力される時点を利用して1水平周期で出力されるロード信号T Pのフォーリング時点を調節することにより、ゲート駆動回路130、140自身の遅延によるゲート駆動信号の遅延を補償できる。

上記本発明の液晶表示装置によれば、同じ構成のゲート駆動回路をゲートラインの両端に配置してゲートラインをデュアル駆動し、ゲート駆動回路のリセット信号のフィードバックを受けてゲート駆動回路によるゲート駆動信号の遅延を補償できるので、ゲートライン遅延及びゲート駆動回路の遅延による横線視認現象を防止できるという効果がある。

**【図面の簡単な説明】**

**【0094】**

【図1】本発明の一実施形態による液晶表示装置の構成を示すブロック図である。

【図2】図1に示すタイミングコントローラの入出力信号の関係を示す図である。

【図3】図2に示すタイミングコントローラの構成を示すブロック図である。

【図4】図1に示す第1レベルシフタの例を示す回路図である。

【図5】図1に示す第1及び第2ゲート駆動回路の構成を示すブロック図である。

【図6】図5に示す第1ゲート駆動回路のステージの例を示す回路図である。

【図7】図1に示す液晶表示装置の動作タイミング図である。

【図8】本発明の一実施形態によるA S G遅延減少方法の手順を示すフローチャートである。

【図9】図8のA S G遅延減少方法を説明するための信号タイミング図である。

【図10】図8のA S G遅延減少方法を説明するための信号タイミング図である。

【図11】図8のA S G遅延減少方法を説明するための信号タイミング図である。

【図12】図8のA S G遅延減少方法を説明するための信号タイミング図である。

**【符号の説明】**

**【0095】**

100：液晶表示装置

110：液晶パネル

120：データ駆動部

130：第1ゲート駆動回路

140：第2ゲート駆動回路

150：第1レベルシフタ

160：第2レベルシフタ

170：タイミングコントローラ

180：電源供給部

10

20

30

40

50

190 : クリップ部

【 図 1 】

【 図 2 】

【 図 3 】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 10】

【図 11】

【図 9】

【図 12】

---

フロントページの続き

|              |         |              |

|--------------|---------|--------------|

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|              | G 0 9 G | 3/20 6 2 2 E |

|              | G 0 9 G | 3/20 6 4 2 A |

|              | G 0 9 G | 3/20 6 4 1 C |

|              | G 0 9 G | 3/20 6 1 1 J |

(72)発明者 呂 章 磐

大韓民国ソウル特別市江北区彌阿3洞305-39番地

(72)発明者 金 宇 哲

大韓民国京畿道議政府市佳陵1洞642-17号

(72)発明者 朴 宰 亨

大韓民国京畿道龍仁市器興区農書洞7-1番地

F ターム(参考) 2H093 NA16 NA80 NB16 NC10 NC25 NC34 NC35 NC59 NC90 ND34

ND36

5C006 AA16 BB16 BF22 FA16 FA22

5C080 AA10 BB05 EE29 FF11 JJ02 JJ04 JJ07

|                |                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2008165223A5</a>                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2010-12-09 |

| 申请号            | JP2007320105                                                                                                                                                                                                                                                                                                                                | 申请日     | 2007-12-11 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 呂章鉉<br>金宇哲<br>朴宰亨                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 呂 章 鉉<br>金 宇 哲<br>朴 宰 亨                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G3/3677 G09G2310/0281 G09G2310/0289 G09G2310/08 G09G2320/0223 G09G2320/0233                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.612.J G09G3/20.621.L G09G3/20.622.B G09G3/20.622.E G09G3 /20.642.A G09G3/20.641.C G09G3/20.611.J                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA80 2H093/NB16 2H093/NC10 2H093/NC25 2H093/NC34 2H093/NC35 2H093 /NC59 2H093/NC90 2H093/ND34 2H093/ND36 5C006/AA16 5C006/BB16 5C006/BF22 5C006/FA16 5C006/FA22 5C080/AA10 5C080/BB05 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080 /JJ07 2H193/ZA04 2H193/ZE31 2H193/ZF22 5B074/AA10 5B074/CA01 5B074/DB01 5B074/EA01 |         |            |

| 优先权            | 1020060125334 2006-12-11 KR                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | JP2008165223A<br>JP5676069B2                                                                                                                                                                                                                                                                                                                |         |            |

**摘要(译)**

常规的单驱动型液晶显示装置改善了所谓的水平线视觉识别现象，其中由于栅极线延迟和ASG延迟而在显示器上看到水平线。时序控制器170产生输出使能信号OE和选通时钟，并且调整确定数据输出时间点的负载信号的时序。输出使能信号发生器172将一帧的最后输出使能信号LASTOE提供给计数器174。计数器单元174生成指示削波后的复位信号CREsig的上升时间与最后输出使能信号LASTOE的上升时间之间的差的时钟计数信号CLKCOUNT，并将其提供给负载信号产生单元176。[选择图]图3