(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-242359

(P2005-242359A)

(43) 公開日 平成17年9月8日(2005.9.8)

(51) Int.Cl.<sup>7</sup>

G09G 3/36

G02F 1/133

G09G 3/20

F 1

G09G 3/36

G02F 1/133 5 7 5

G09G 3/20 6 1 1 E

G09G 3/20 6 2 1 B

G09G 3/20 6 2 3 F

テーマコード(参考)

2 H 0 9 3

5 C 0 0 6

5 C 0 8 0

審査請求 未請求 請求項の数 22 O L (全 18 頁) 最終頁に続く

(21) 出願番号 特願2005-50805 (P2005-50805)

(22) 出願日 平成17年2月25日 (2005.2.25)

(31) 優先権主張番号 2004-012739

(32) 優先日 平成16年2月25日 (2004.2.25)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 503447036

サムスン エレクトロニクス カンパニー

リミテッド

大韓民国キヨンギード、スウォンーシ、ヨ

ントン-ク、マエタンードン 416

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100076691

弁理士 増井 忠式

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

(74) 代理人 100096013

弁理士 富田 博行

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】 フレームレートの制御による表示装置の画質悪化を減らす。

【解決手段】 本発明は複数のフレームレート制御 ( F R C ) データパターンを信号制御部のルックアップテーブルに記憶させた後、 F R C 処理を実施する液晶標識装置に関する。ルックアップテーブルに記憶された F R C データパターンは  $4 \times 4$  データ行列を基本単位とし、各データエレメントは “ 1 ” または “ 0 ” のデータ値を有する。この  $4 \times 4$  データ行列に対応する  $4 \times 4$  画素行列は  $2 \times 1$  ドット反転とフレーム反転が行なわれ、毎フレームに相当する F R C データパターンで、「 + 」極性を有する画素に対応し、「 1 」の値を有するデータエレメントの数と「 - 」極性を有する画素に対応し、「 1 」の値を有するデータエレメントの数は互いにじである。これによって、同じ F R C データ値を有する相反した極性の画素数が互いにじになる。

【選択図】 図 3

| LSB 2ビット | フレーム番号 |   |   |   |

|----------|--------|---|---|---|

|          | 1      | 2 | 3 | 4 |

| 01       |        |   |   |   |

| 10       |        |   |   |   |

| 11       |        |   |   |   |

**【特許請求の範囲】****【請求項 1】**

複数の画素を含む液晶表示板組立体と、

第1値または第2値をそれぞれに有する複数のデータエレメントからなるフレームレート制御(FRC)データパターンを複数個記憶し、複数の前記FRCデータパターンの中から、第1ビット数を有する入力映像データに対応するFRCデータパターンを選択し、前記選択されたFRCデータパターンに基づいて、前記入力映像データを、前記第1ビット数より少ない第2ビット数を有する出力映像データに変換して出力する信号制御部と、

前記信号制御部から出力される前記出力映像データに関連する前記FRCデータパターン内の前記データエレメントに対応して定めたデータ電圧を、前記データエレメントに対応する画素に印加するデータ駆動部と、

10

を含み、

前記データ電圧は第1極性または第2極性を有し、

前記出力映像データに関連する前記FRCデータパターン内の前記第1値を有する前記データエレメントに対応する前記画素において、前記第1極性を有するデータ電圧が印加される画素の数は、前記第2極性を有するデータ電圧が印加される画素の数と同じである、

液晶表示装置。

**【請求項 2】**

前記信号制御部は、前記複数のFRCデータパターンを記憶するルックアップテーブルと、前記ルックアップテーブルに記憶された前記複数のFRCデータパターンに基づいて前記入力映像データを変換するデータ処理部とを含む、請求項1に記載の液晶表示装置。

**【請求項 3】**

それぞれの前記FRCデータパターンは $4 \times 4$ 行列形態を有する、請求項1または2に記載の液晶表示装置。

**【請求項 4】**

前記第1ビット数と前記第2ビット数との差は2ビットである、請求項1ないし3の何れかに記載の液晶表示装置。

**【請求項 5】**

前記複数のFRCデータパターンの中から選択される、前記入力映像データに対応するFRCデータパターンは、前記入力映像データの下位2ビットとフレーム番号に基づいて選択される、請求項1ないし4の何れかに記載の液晶表示装置。

**【請求項 6】**

前記データ処理部は、前記入力映像データの下位2ビット値が「00」である時、前記下位2ビットを除いた上位ビットを出力映像データのデータ値とする、請求項5に記載の液晶表示装置。

**【請求項 7】**

前記下位2ビットが「01」である時の各フレームに対応するFRCデータパターンがそれぞれに異なり、

前記下位2ビットが「11」である時の各フレームに対応するFRCデータパターンがそれぞれに異なり、

40

前記下位2ビットが「10」である時の各フレームに対応するFRCデータパターンの中で少なくとも二つのFRCデータパターンは同一である、

請求項5または6に記載の液晶表示装置

**【請求項 8】**

前記下位2ビットの各値に対して、4つのフレームに対する四つのFRCデータパターンが存在し、

前記下位2ビットが「01」である場合、前記四つのFRCデータパターンのうちの二つのFRCデータパターンは互いに反転対称で、残り二つのFRCデータパターンも互いに反転対称であり、

前記下位2ビットが「11」である場合、前記四つのFRCデータパターンのうちの二つ

10

20

30

40

50

のFRCデータパターンは互いに反転対称で、残り二つのFRCデータパターンも互いに反転対称である。

請求項 5ないし7の何れかに記載の液晶表示装置。

【請求項 9】

それぞれの前記FRCデータパターンは一対の $4 \times 2$ データ行列を含み、

前記下位2ビットが「01」である時、それぞれの前記 $4 \times 2$ データ行列のデータエレメントのうちの二つのデータエレメントが前記第1値を有し、前記一対の $4 \times 2$ データ行列のうちの一方のデータ行列における前記第1値を有するデータエレメントの間の距離は、前記一対の $4 \times 2$ データ行列のうちの他方のデータ行列における前記第1値を有するデータエレメントの間の距離と同一である、

10

請求項 5ないし8の何れかに記載の液晶表示装置。

【請求項 10】

それぞれの前記FRCデータパターンは一対の $4 \times 2$ データ行列を含み、

前記下位2ビットが「11」である時、それぞれの前記 $4 \times 2$ データ行列のデータエレメントのうちの二つのデータエレメントが前記第2値を有し、前記一対の $4 \times 2$ データ行列のうちの一方のデータ行列における前記第2値を有するデータエレメントの間の距離は、前記一対の $4 \times 2$ データ行列のうちの他方のデータ行列における前記第2値を有するデータエレメントの間の距離と同一である、

20

請求項 5ないし9の何れかに記載の液晶表示装置。

【請求項 11】

それぞれの前記FRCデータパターンは一対の $4 \times 2$ データ行列を含み、

前記下位2ビットが「01」である時、それぞれの前記 $4 \times 2$ データ行列のデータエレメントのうちの二つのデータエレメントが前記第1値を有し、前記一対の $4 \times 2$ データ行列のうちの一方のデータ行列における前記第1値を有するデータエレメントの間の距離は、前記一対の $4 \times 2$ データ行列のうちの他方のデータ行列における前記第1値を有するデータエレメントの間の距離と異なる、

20

請求項 5ないし8の何れかに記載の液晶表示装置。

【請求項 12】

それぞれの前記FRCデータパターンは一対の $4 \times 2$ データ行列を含み、

前記下位2ビットが「11」である時、それぞれの前記 $4 \times 2$ データ行列のデータエレメントのうちの二つのデータエレメントが前記第2値を有し、前記一対の $4 \times 2$ データ行列のうちの一方のデータ行列における前記第2値を有するデータエレメントの間の距離は、前記一対の $4 \times 2$ データ行列のうちの他方のデータ行列における前記第2値を有するデータエレメントの間の距離と異なる、

30

請求項 5、6、7、8または11に記載の液晶表示装置。

【請求項 13】

それぞれの前記FRCデータパターンは四つの $2 \times 2$ データ行列を含み、

前記下位2ビットが「10」である時、前記四つの $2 \times 2$ データ行列の中で、2つの $2 \times 2$ データ行列が同じであり、残りの2つの $2 \times 2$ データ行列が同じであり、これら二対の $2 \times 2$ データ行列は互いに反転対称である、

40

請求項 5ないし8の何れかに記載の液晶表示装置。

【請求項 14】

それぞれの前記FRCデータパターンは四つの $2 \times 2$ データ行列を含み、

それぞれの前記 $2 \times 2$ データ行列において、一方の行の2つのデータエレメントは互いに同じ値を有し、他方の行の2つのデータエレメントは互いに異なる値を有する、

40

請求項 5、6、7、8または13に記載の液晶表示装置。

【請求項 15】

それぞれの前記FRCデータパターンは四つの $2 \times 2$ データ行列を含み、

それぞれの前記 $2 \times 2$ データ行列において、一方の列の2つのデータエレメントは互いに同じ値を有し、他方の列の2つのデータエレメントは互いに異なる値を有する、

50

請求項 5、6、7、8 または 13 に記載の液晶表示装置。

【請求項 16】

縦方向および横方向の隣接した  $2 \times 2$  データ行列が互いに反転していて、対角線方向の  $2 \times 2$  データ行列が互いに同一である、請求項 13 に記載の液晶表示装置。

【請求項 17】

それぞれの前記 FRC データパターンは四つの  $2 \times 2$  データ行列を含み、

それぞれの前記  $2 \times 2$  データ行列の全てのデータエレメントは同じ値を有する、

請求項 5、6、7、8 または 16 に記載の液晶表示装置。

【請求項 18】

それぞれの前記 FRC データパターンは四つの  $2 \times 2$  データ行列を含み、

前記 FRC データパターンのうちの少なくとも一つの FRC データパターンの各  $2 \times 2$  データ行列で、対角線方向のデータエレメントは同じ値を有し、縦方向および横方向の隣接したデータエレメントは前記対角線方向のデータエレメントと異なる値を有する、請求項 5、6、7、8 または 16 に記載の液晶表示装置。

【請求項 19】

複数の画素を含む液晶表示板組立体と、

第 1 値または第 2 値をそれぞれに有するデータエレメントからなるフレームレート制御 (FRC) データパターンを複数個記憶し、複数の前記 FRC データパターンの中から、第 1 ビット数を有する入力映像データに対応する FRC データパターンを選択し、選択された前記 FRC データパターンに基づいて、前記入力映像データを前記第 1 ビット数より少ない第 2 ビット数を有する出力映像データに変換して出力する信号制御部と、

前記信号制御部から出力される前記出力映像データに関連する前記 FRC データパターン内の前記データエレメントに対応して定めたデータ電圧を、前記データエレメントに対応する画素に印加するデータ駆動部と、

を含み、

前記第 1 ビット数と前記第 2 ビット数との差は 2 ビットであり、

前記入力映像データに対応する FRC データパターンは、前記入力映像データの下位 2 ビットとフレーム番号とによって決められ、

前記 FRC データパターンは一対の  $4 \times 2$  データ行列を含み、

前記下位 2 ビットが「01」である時、それぞれの前記  $4 \times 2$  データ行列のデータエレメントのうちの二つが前記第 1 値を有し、前記一対のデータ行列のうちの一方のデータ行列における前記第 1 値を有するデータエレメントの間の距離は、前記一対のデータ行列のうちの他方のデータ行列における前記第 1 値を有するデータエレメントの間の距離と同じであり、前記下位 2 ビットが「11」である時、それぞれの前記  $4 \times 2$  データ行列のデータエレメントのうちの二つが前記第 2 値を有し、前記一対の  $4 \times 2$  データ行列のうちの一方のデータ行列における前記第 2 値を有するデータエレメントの間の距離は、前記一対の  $4 \times 2$  データ行列のうちの他方のデータ行列における前記第 2 値を有するデータエレメントの間の距離と同じである、

液晶表示装置。

【請求項 20】

複数の画素を含む液晶表示板組立体と、

第 1 値または第 2 値をそれぞれに有するデータエレメントからなるフレームレート制御 (FRC) データパターンを複数個記憶し、複数の前記 FRC データパターンの中から、第 1 ビット数を有する入力映像データに対応する FRC データパターンを選択し、選択された前記 FRC データパターンに基づいて、前記入力映像データを前記第 1 ビット数より少ない第 2 ビット数を有する出力映像データに変換して出力する信号制御部と、

前記信号制御部から出力される前記出力映像データに関連する前記 FRC データパターン内の前記データエレメントに対応して定めたデータ電圧を、前記データエレメントに対応する画素に印加するデータ駆動部と、

を含み、

10

20

30

40

50

前記第1ビット数と前記第2ビット数との差は2ビットであり、

前記入力映像データに対応するFRCデータパターンは、前記入力映像データの下位2ビットとフレーム番号とによって決められ、

前記FRCデータパターンは一対の $4 \times 2$ データ行列を含み、

前記下位2ビットが「01」である時、それぞれの前記 $4 \times 2$ データ行列のデータエレメントのうちの二つが前記第1値を有し、前記一対のデータ行列のうちの一方のデータ行列における前記第1値を有するデータエレメントの間の距離は、前記一対のデータ行列のうちの他方のデータ行列における前記第1値を有するデータエレメントの間の距離と異なり、前記下位2ビットが「11」である時、それぞれの前記 $4 \times 2$ データ行列のデータエレメントのうちの二つが前記第2値を有し、前記一対の $4 \times 2$ データ行列のうちの一方のデータ行列における前記第2値を有するデータエレメントの間の距離は、前記一対の $4 \times 2$ データ行列のうちの他方のデータ行列における前記第2値を有するデータエレメントの間の距離と異なる、

10

液晶表示装置。

#### 【請求項21】

複数の画素を含む液晶表示板組立体と、

第1値または第2値をそれぞれに有するデータエレメントからなるフレームレート制御(FRC)データパターンを複数個記憶し、複数の前記FRCデータパターンの中から、第1ビット数を有する入力映像データに対応するFRCデータパターンを選択し、選択された前記FRCデータパターンに基づいて、前記入力映像データを前記第1ビット数より少ない第2ビット数を有する出力映像データに変換して出力する信号制御部と、

20

前記信号制御部から出力される前記出力映像データに関連する前記FRCデータパターン内の前記データエレメントに対応して定めたデータ電圧を、前記データエレメントに対応する画素に印加するデータ駆動部と、

を含み、

前記第1ビット数と前記第2ビット数との差は2ビットであり、

前記入力映像データに対応するFRCデータパターンは、前記入力映像データの下位2ビットとフレーム番号とによって決められ、

前記FRCデータパターンは四つの $2 \times 2$ データ行列を含み、

それぞれの前記 $2 \times 2$ データ行列において、一方の行の2つのデータエレメントは互いに同じ値を有し、他方の行の2つのデータエレメントは互いに異なる値を有する、

30

液晶表示装置。

#### 【請求項22】

複数の画素を含む液晶表示板組立体と、

第1値または第2値をそれぞれに有するデータエレメントからなるフレームレート制御(FRC)データパターンを複数個記憶し、複数の前記FRCデータパターンの中から、第1ビット数を有する入力映像データに対応するFRCデータパターンを選択し、選択された前記FRCデータパターンに基づいて、前記入力映像データを前記第1ビット数より少ない第2ビット数を有する出力映像データに変換して出力する信号制御部と、

40

前記信号制御部から出力される前記出力映像データに関連する前記FRCデータパターン内の前記データエレメントに対応して定めたデータ電圧を、前記データエレメントに対応する画素に印加するデータ駆動部と、

を含み、

前記第1ビット数と前記第2ビット数との差は2ビットであり、

前記入力映像データに対応するFRCデータパターンは、前記入力映像データの下位2ビットとフレーム番号とによって決められ、

前記FRCデータパターンは四つの $2 \times 2$ データ行列を含み、

それぞれの前記 $2 \times 2$ データ行列において、一方の列の2つのデータエレメントは互いに同じ値を有し、他方の列の2つのデータエレメントは互いに異なる値を有する、

液晶表示装置。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は液晶表示装置に関する。

**【背景技術】****【0002】**

一般的な液晶表示装置（LCD）は画素電極及び共通電極が備えられた二枚の表示板と、その間に入っている誘電率異方性を有する液晶層とを含む。画素電極は行列形態で配列されていて、薄膜トランジスタ（TFT）などのスイッチング素子に接続されて一行ずつ順次にデータ電圧の印加を受ける。共通電極は表示板の全面にかけて形成されており、共通電圧の印加を受ける。画素電極と共通電極及びその間の液晶層は回路的に見ると、液晶キャパシタを構成し、液晶キャパシタはこれに接続されたスイッチング素子と共に画素を構成する基本単位となる。

**【0003】**

このような液晶表示装置では、二つの電極に電圧を印加して液晶層に電界を生成し、この電界の強さを調節して液晶層を通過する光の透過率を調節することによって、所望の画像を得る。この時、液晶層に一方向の電界が長く印加されることによって発生する劣化現象などを防止するために、フレーム別に、行別に、または画素別に共通電圧に対するデータ電圧の極性を反転させる。

**【0004】**

このような液晶表示装置で外部のグラフィックソースの赤色、緑色、青色の映像データが入力される。液晶表示装置の信号制御部は、この映像データを適切に処理した後、データ駆動ICなどからなるデータ駆動部に提供する。データ駆動部は、印加された映像データに相当するアナログ階調電圧を選択して、液晶表示板組立体に印加する。

**【0005】**

一般に、信号制御部に入力される映像データのビット数とデータ駆動部で処理できるビット数とが同一であるのが理想的であるが、液晶表示装置の製造原価を下げるするために処理能力の低いデータ駆動部を利用することができる。例えば、信号制御部に印加される映像データが8ビットである場合、8ビットの映像データを処理するデータ駆動部は非常に高価であるために、8ビットより低い処理能力、例えば6ビットの映像データを処理するデータ駆動部を利用すれば、製品の単価が低くなる。

**【0006】**

このために提案された技術がフレームレート制御（FRC）である。フレームレート制御は、入力された映像データのビットの中でデータ駆動部で処理可能なビット数に相当する上位ビットのみを取って作った映像データを、下位ビットに基づいてフレーム単位で再構成することである。

**【0007】**

そのために、信号制御部は、下位ビット値による各画素に対する映像データの補正值をルックアップテーブルなどに記憶させて置く。フレームレート制御の基本画素単位に対応する補正值集合を、FRCデータパターンと言う。

**【0008】**

しかし、現在FRCデータパターンを利用してこのようなFRCを実施する時には、画素に印加されるデータ電圧の差や極性などにより縞、フリッカーなどが発生しないように、FRCデータパターンを決めることが重要である。

**【発明の開示】****【発明が解決しようとする課題】****【0009】**

したがって、本発明が解決しようとする技術的課題は、フレームレートの制御により表示装置の画質悪化を減らすことである。

**【課題を解決するための手段】**

10

20

30

40

50

## 【0010】

このような技術的課題を構成するための本発明の一つの特徴による液晶表示装置は、複数の画素を含む液晶表示板組立体と、第1値または第2値をそれぞれに有するデータエレメントからなるFRCデータパターンを複数個記憶し、複数のFRCデータパターンの中から、第1ビット数を有する入力映像データに対応するFRCデータパターンを選択し、選択されたFRCデータパターンに基づいて、入力映像データを第1ビット数より少ない第2ビット数を有する出力映像データに変換して出力する信号制御部と、信号制御部から出力される出力映像データに関連するFRCデータパターン内のデータエレメントに対応して定めたデータ電圧を、データエレメントに対応する画素に印加するデータ駆動部と、を含み、データ電圧は第1極性または第2極性を有し、出力映像データに関連するFRCデータパターン内の第1値を有するデータエレメントに対応する画素において、第1極性を有するデータ電圧が印加される画素の数は、第2極性を有するデータ電圧が印加される画素の数と同じである。 10

## 【0011】

信号制御部は、複数のFRCデータパターンを記憶するルックアップテーブルと、ルックアップテーブルに記憶された複数のFRCデータパターンに基づいて入力映像データを変換するデータ処理部とを含むのが好ましい。

## 【0012】

各FRCデータパターンは $4 \times 4$ 行列形態を有するのが好ましく、第1ビット数と第2ビット数との差は2ビットであり得る。 20

複数のFRCデータパターンのうちの、入力映像データに対応するFRCデータパターンは、入力映像データの下位2ビットとフレーム番号とによって決めることができる。

## 【0013】

データ処理部は、入力映像データの下位2ビットの値が(00)である時、下位2ビットを除いた上位ビットを出力映像データのデータ値として決めるのが好ましい。

本発明の一つの特徴として、下位2ビットが(01)である時のFRCデータパターンが異なり、下位2ビットが(11)である時のFRCデータパターンが異なり、下位2ビットが(10)である時のFRCデータパターンの中で少なくとも二つのFRCデータパターンは互いに同じであることができる。 30

## 【0014】

下位2ビットの各値に対して四つのFRCデータパターンが存在し、下位2ビットが(01)である場合、四つのFRCデータパターンのうちの二つのFRCデータパターンは互いに反転対称であり、残りの二つのFRCデータパターンも互いに反転対称であり、下位2ビットが(11)である場合、四つのFRCデータパターンのうちの二つのFRCデータパターンは互いに反転対称であり、残りの二つのFRCデータパターンも互いに反転対称であり得る。

## 【0015】

また、各FRCデータパターンは一対の $4 \times 2$ データ行列を含み、下位2ビットが(01)である時、各 $4 \times 2$ データ行列のデータエレメントのうちの二つが第1値を有し、一対の $4 \times 2$ データ行列のうちの一方のデータ行列で第1値を有するデータエレメントの間の距離は、一対の $4 \times 2$ データ行列のうちの他方のデータ行列で前記第1値を有するデータエレメントの間の距離と同じであり得る。また、下位2ビットが(11)である時、各 $4 \times 2$ データ行列のデータエレメントのうちの二つが第2値を有し、一対の $4 \times 2$ データ行列のうちの一方のデータ行列で第2値を有するデータエレメントの間の距離は、一対の $4 \times 2$ データ行列のうちの他方のデータ行列で第2値を有するデータエレメントの間の距離と同じであり得る。 40

## 【0016】

また、一例としては、下位2ビットが(01)である時、各 $4 \times 2$ データ行列のデータエレメントのうちの二つが第1値を有し、一対の $4 \times 2$ データ行列のうちの一方のデータ行列で第1値を有するデータエレメントの間の距離は、一対の $4 \times 2$ データ行列のうちの他方のデータ行列で第1値を有するデータエレメントの間の距離と異なっていても良く、 50

下位 2 ビットが (11) である時、各  $4 \times 2$  データ行列のデータエレメントのうちの二つが第 2 値を有し、一対の  $4 \times 2$  データ行列のうちの一方のデータ行列で第 2 値を有するデータエレメントの間の距離は、一対の  $4 \times 2$  データ行列のうちの他方のデータ行列で第 2 値を有するデータエレメントの間の距離と異なっていても良い。

## 【0017】

また、一例としては、各 FRC データパターンは四つの  $2 \times 2$  データ行列を含み、下位 2 ビットが (10) である時、四つの  $2 \times 2$  データ行列の中で 2 つの  $2 \times 2$  データ行列が同じであり、残りの 2 つの  $2 \times 2$  データ行列が同じであり、これら二対の  $2 \times 2$  データ行列は互いに反転対称であり得る。

## 【0018】

この時、それぞれの  $2 \times 2$  データ行列において、一方の行の 2 つのデータエレメントは互いに同じ値を有し、他方の行の 2 つのデータエレメントは互いに異なる値を有し、また、それぞれの  $2 \times 2$  データ行列において、一方の列の 2 つのデータエレメントは互いに同じ値を有し、他方の列の 2 つのデータエレメントは互いに異なる値を有することもできる。さらに、縦方向および横方向の隣接した  $2 \times 2$  データ行列が互いに反転していて、対角線方向の  $2 \times 2$  データ行列が互いに同じであり得る。この時、各  $2 \times 2$  データ行列の全てのデータエレメントは同じ値を有することもできる。

## 【0019】

また、FRC データパターンのうちの少なくとも一つの FRC データパターンの各  $2 \times 2$  データ行列で、対角線方向のデータエレメントは同じ値を有し、縦方向および横方向の隣接したデータエレメントは互いに異なる値を有することができる。

## 【0020】

本発明の他の特徴による液晶表示装置は、複数の画素を含む液晶表示板組立体と、第 1 値または第 2 値をそれぞれに有するデータエレメントからなる FRC データパターンを複数個記憶し、複数の FRC データパターンの中から、第 1 ビット数を有する入力映像データに対応する FRC データパターンを選択し、選択した FRC データパターンに基づいて、入力映像データを第 1 ビット数より少ない第 2 ビット数を有する出力映像データに変換して出力する信号制御部と、信号制御部から出力される出力映像データに関連する FRC データパターン内のデータエレメントに対応して定めたデータ電圧を、データエレメントに対応する画素に印加するデータ駆動部とを含み、第 1 ビット数と第 2 ビット数との差は 2 ビットであり、入力映像データに対応する FRC データパターンは、入力映像データの下位 2 ビットとフレーム番号とによって決められ、FRC データパターンは一対の  $4 \times 2$  データ行列を含み、下位 2 ビットが (01) である時、各  $4 \times 2$  データ行列のデータエレメントのうちの二つが第 1 値を有し、一対のデータ行列のうちの一方のデータ行列で第 1 値を有するデータエレメントの間の距離は、一対のデータ行列のうちの他方のデータ行列で第 1 値を有するデータエレメントの間の距離と同じであり、下位 2 ビットが (11) である時、各  $4 \times 2$  データ行列のデータエレメントのうちの二つが第 2 値を有し、一対の  $4 \times 2$  データ行列のうちの一方のデータ行列で第 2 値を有するデータエレメントの間の距離は、一対の  $4 \times 2$  データ行列のうちの他方のデータ行列で第 2 値を有するデータエレメントの間の距離と同じである。

## 【0021】

また、本発明の他の特徴による液晶表示装置は、複数の画素を含む液晶表示板組立体と、第 1 値または第 2 値をそれぞれに有するデータエレメントからなる FRC データパターンを複数個記憶し、複数の FRC データパターンの中から、第 1 ビット数を有する入力映像データに対応する FRC データパターンを選択し、選択した FRC データパターンに基づいて、入力映像データを第 1 ビット数より少ない第 2 ビット数を有する出力映像データに変換して出力する信号制御部と、信号制御部から出力される出力映像データに関連する FRC データパターン内のデータエレメントに対応して定めたデータ電圧を、データエレメントに対応する画素に印加するデータ駆動部とを含み、第 1 ビット数と第 2 ビット数との差は 2 ビットであり、入力映像データに対応する FRC データパターンは、入力映像データの下位 2 ビ

10

20

30

40

50

ットとフレーム番号とによって決められ、FRCデータパターンは一対の $4 \times 2$ データ行列を含み、下位2ビットが(01)である時、各 $4 \times 2$ データ行列のデータエレメントのうちの二つが第1値を有し、一対のデータ行列のうちの一方のデータ行列で第1値を有するデータエレメントの間の距離は、一対のデータ行列のうちの他方のデータ行列で第1値を有するデータエレメントの間の距離と異なり、下位2ビットが(11)である時、各 $4 \times 2$ データ行列のデータエレメントのうちの二つが第2値を有し、一対の $4 \times 2$ データ行列のうちの一方のデータ行列で第2値を有するデータエレメントの間の距離は、一対の $4 \times 2$ データ行列のうちの他方のデータ行列で第2値を有するデータエレメントの間の距離と異なっていても良い。

【0022】

本発明の他の特徴による液晶表示装置は、複数の画素を含む液晶表示板組立体と、第1値または第2値をそれぞれに有するデータエレメントからなるFRCデータパターンを複数個記憶し、複数のFRCデータパターンの中から、第1ビット数を有する入力映像データに対応するFRCデータパターンを選択し、選択したFRCデータパターンに基づいて、入力映像データを第1ビット数より少ない第2ビット数を有する出力映像データに変換して出力する信号制御部と、信号制御部から出力される出力映像データに関連するFRCデータパターン内のデータエレメントに対応して定めたデータ電圧を、データエレメントに対応する画素に印加するデータ駆動部とを含み、第1ビット数と第2ビット数との差は2ビットであり、入力映像データに対応するFRCデータパターンは、入力映像データの下位2ビットとフレーム番号とによって決められ、FRCデータパターンは四つの $2 \times 2$ データ行列を含み、それぞれの $2 \times 2$ データ行列において、一方の行の2つのデータエレメントは互いに同じ値を有し、他方の行の2つのデータエレメントは互いに異なる値を有する。

【0023】

本発明の他の特徴による液晶表示装置は、複数の画素を含む液晶表示板組立体と、第1値または第2値をそれぞれに有するデータエレメントからなるFRCデータパターンを複数個記憶し、複数のFRCデータパターンの中から、第1ビット数を有する入力映像データに対応するFRCデータパターンを選択し、選択したFRCデータパターンに基づいて、入力映像データを第1ビット数より少ない第2ビット数を有する出力映像データに変換して出力する信号制御部と、信号制御部から出力される出力映像データに関連するFRCデータパターン内のデータエレメントに対応して定めたデータ電圧を、データエレメントに対応する画素に印加するデータ駆動部とを含み、第1ビット数と第2ビット数との差は2ビットであり、入力映像データに対応するFRCデータパターンは、入力映像データの下位2ビットとフレーム番号とによって決められ、FRCデータパターンは四つの $2 \times 2$ データ行列を含み、それぞれの $2 \times 2$ データ行列において、一方の列の2つのデータエレメントは互いに同じ値を有し、他方の列の2つのデータエレメントは互いに異なる値を有する。

【発明の効果】

【0024】

本発明によれば、FRCのためのFRCデータパターンが $4 \times 4$ データ行列を基本単位として各フレームに対するFRCデータパターンを作るので、多様なFRCデータパターンを実現することができる。また、各フレームごとに同一の階調値が与えられる画素の間の極性差による画素電圧の差が減るので、輝度差による画質悪化が減少する。

【発明を実施するための最良の形態】

【0025】

添付した図面を参照して、本発明の実施例について本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。

図面では、多様な層及び領域を明確に表現するために、厚さを拡大して示した。明細書全体にわたり、類似の部分については同じ図面符号を付けた。層、膜、領域、板などの部分が他の部分の「上」にあるとする時、これは他の部分の「すぐ上」にある場合だけでなく、その中間に他の部分がある場合も含む。ある部分が他の部分の「すぐ上」にあるとする時には、中間に他の部分がないことを意味する。

10

20

30

40

50

## 【0026】

以下で本発明の実施例による液晶表示装置について図面を参照して詳細に説明する。

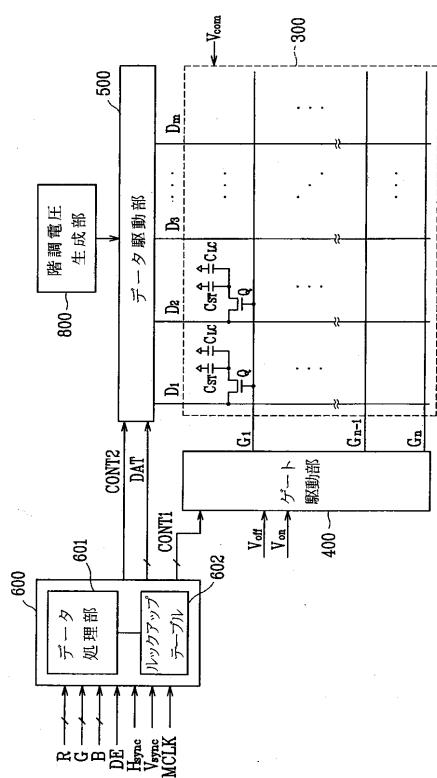

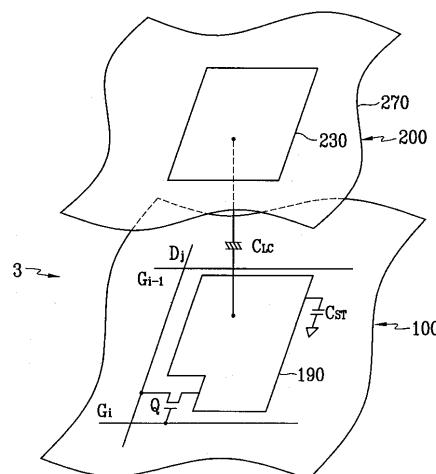

図1は本発明の一実施例による液晶表示装置のブロック図であり、図2は本発明の一実施例による液晶表示装置の一つの画素に対する等価回路図である。

## 【0027】

図1に示したように、本発明の一実施例による液晶表示装置は、液晶表示板組立体300と、これに接続されたゲート駆動部400及びデータ駆動部500、データ駆動部500に接続された階調電圧生成部800、そしてこれらを制御する信号制御部600を含む。

## 【0028】

液晶表示板組立体300は等価回路で見る時、複数の表示信号線 $G_1 - G_n$ 、 $D_1 - D_m$ と、これらに接続されており、ほぼ行列形態で配列された複数の画素とを含む。

表示信号線 $G_1 - G_n$ 、 $D_1 - D_m$ は、ゲート信号（「走査信号」とも言う）を伝達する複数のゲート線 $G_1 - G_n$ と、データ信号を伝達するデータ信号線またはデータ線 $D_1 - D_m$ とを含む。ゲート線 $G_1 - G_n$ はほぼ行方向に伸びていて、互いにほとんど平行であり、データ線 $D_1 - D_m$ はほぼ列方向に伸びていて、互いにほとんど平行である。

## 【0029】

各画素は表示信号線 $G_1 - G_n$ 、 $D_1 - D_m$ に接続されたスイッチング素子Qと、これに接続された液晶キャパシタ $C_{LC}$ 及びストレージキャパシタ $C_{ST}$ とを含む。ストレージキャパシタ $C_{ST}$ は必要に応じて省略することができる。

## 【0030】

薄膜トランジスタなどのスイッチング素子Qは下部表示板100に備えられており、三端子素子であり、その制御端子及び入力端子は各々ゲート線 $G_1 - G_n$ 及びデータ線 $D_1 - D_m$ に接続されており、出力端子は液晶キャパシタ $C_{LC}$ 及びストレージキャパシタ $C_{ST}$ に接続されている。

## 【0031】

液晶キャパシタ $C_{LC}$ は、下部表示板100の画素電極190と上部表示板200の共通電極270とを二つの端子とし、二つの電極190、270の間の液晶層3は誘電体として機能する。画素電極190はスイッチング素子Qに接続され、共通電極270は上部表示板200の全面に形成されており、共通電圧 $V_{com}$ の印加を受ける。また、図2とは違つて、共通電極270が下部表示板100に備えられる場合もあり、この時には二つの電極190、270の少なくとも一つが線形または棒形で作られても良い。

## 【0032】

液晶キャパシタ $C_{LC}$ の補助的な役割を果たすストレージキャパシタ $C_{ST}$ は、下部表示板100に備えられた別個の信号線（図示せず）と画素電極190が絶縁体を間に置いて重なって構成され、この別個の信号線には共通電圧 $V_{com}$ などの決められた電圧が印加される。また、ストレージキャパシタ $C_{ST}$ は、画素電極190が絶縁体を媒介として真上の前段ゲート線と重なって構成されることもできる。

## 【0033】

一方、色表示を実現するためには各画素が三原色のうちの一つを固有に表示したり（空間分割）、各画素が時間によって交互に三原色を表示するように（時間分割）して、これら三原色の空間的、時間的合計で所望の色相を認識させる。図2は空間分割の一例であつて、各画素が画素電極190に対応する領域に赤色、緑色、または青色の色フィルター230を備えることを示している。また、図2とは異なつて、色フィルター230は下部表示板100の画素電極190上または下に形成しても良い。

## 【0034】

液晶表示板組立体300の二枚の表示板100、200のうちの少なくとも一つの外側面には、光を偏光させる偏光子（図示せず）が付着されている。

階調電圧生成部800は画素の透過率と関連された二対の複数階調電圧を生成する。二対のうちの一対は共通電圧 $V_{com}$ に対して正の値を有し、他の一対は負の値を有する。

10

20

30

40

50

## 【0035】

ゲート駆動部400は、液晶表示板組立体300のゲート線 $G_1$  -  $G_n$ に接続され、外部からのゲートオン電圧 $V_{on}$ とゲートオフ電圧 $V_{off}$ の組み合わせからなるゲート信号をゲート線 $G_1$  -  $G_n$ に印加するものであり、通常複数の集積回路からなる。

## 【0036】

データ駆動部500は、液晶表示板組立体300のデータ線 $D_1$  -  $D_m$ に接続され、階調電圧生成部800からの階調電圧を選択してデータ信号として画素に印加するものであり、通常複数の集積回路からなる。

## 【0037】

複数のゲート駆動集積回路またはデータ駆動集積回路は、チップの形態でTCP(図示せず)に実装して、TCPを液晶表示板組立体300に付着させることもでき、TCPを使用せずにガラス基板上にこれら集積回路チップを直接付着させることもでき(COG実装方式)、また、これら集積回路チップと同じ機能をする回路を画素の薄膜トランジスタと共に液晶表示板組立体300に直接形成しても良い。

## 【0038】

信号制御部600はゲート駆動部400及びデータ駆動部500などの動作を制御し、データ処理部601とルックアップテーブル602とを含む。ルックアップテーブル602には、フレームレート制御に必要なFRCデータパターンが記憶されている。

## 【0039】

次に、このような液晶表示装置の表示動作について詳細に説明する。

信号制御部600は、外部のグラフィック制御器(図示せず)から、入力映像信号(R、G、B)及びその表示を制御する入力制御信号、例えば、垂直同期信号 $V_{sync}$ と水平同期信号 $H_{sync}$ 、メインクロックMCLK、データイネーブル信号DEなどを受け取る。信号制御部600のデータ処理部601は、所定ビット数の入力映像信号(R、G、B)と入力制御信号とに基づいて、映像信号(R、G、B)を液晶表示板組立体300の動作条件に合うように適切に処理し、ゲート制御信号CONT1及びデータ制御信号CONT2などを生成した後、ゲート制御信号CONT1をゲート駆動部400に出力し、データ制御信号CONT2と処理した映像信号DATをデータ駆動部500に出力する。

## 【0040】

信号制御部600のデータ処理には、ルックアップテーブル602に保存したFRCデータパターンを利用したフレームレート制御が含まれるが、このフレームレート制御とは、データ駆動部500で処理できるデータのビット数が入力映像信号(R、G、B)のビット数より少ない場合に、データ駆動部500で処理できるビット数の上位ビットのみを選択して、残り下位ビットが示すデータはこのような上位ビットの時間的、空間的平均として実現することを意味する。例えば、入力映像信号(R、G、B)のビット数が8であり、データ駆動部500が処理できるデータのビット数が6であれば、入力映像信号(R、G、B)のビットの中で上位6ビットのみを出力する。この時、下位2ビットは、この上位6ビットデータの空間的、時間的配列を決定し、このパターンがルックアップテーブル602に保存されているFRCデータパターンである。このようなフレームレート制御については後述する。

## 【0041】

ゲート制御信号CONT1は、ゲートオン電圧 $V_{on}$ の出力開始を指示する垂直同期開始信号STV、ゲートオン電圧 $V_{on}$ の出力時期を制御するゲートクロック信号CPV、及びゲートオン電圧 $V_{on}$ の持続時間を限定する出力イネーブル信号OEなどを含む。

## 【0042】

データ制御信号CONT2は、映像データDATの入力開始を知らせる水平同期開始信号STHとデータ線 $D_1$  -  $D_m$ に当該データ電圧を印加することを命令するロード信号LOAD、共通電圧 $V_{com}$ に対するデータ電圧の極性(以下、「共通電圧に対するデータ電圧の極性」を「データ電圧の極性」と言う)を反転させる反転信号RVS、及びデータクロック信号HCLKなどを含む。

10

20

30

40

50

## 【0043】

データ駆動部500は、信号制御部600からのデータ制御信号CONT2によって一行の画素に対する映像データDATの入力を順次に受けてシフトさせ、階調電圧生成部800から得られる階調電圧のうちから各映像データDATに対応する階調電圧を選択することによって映像データDATを当該データ電圧に変換した後、これを当該データ線D<sub>1</sub> - D<sub>m</sub>に印加する。即ち、入力される映像データ(DAT)をシフトレジスタにシフトさせて、一行に該当する全ての映像データ(DAT)の入力を受け、その後、一行に該当する複数の映像データ(DAT)に対するデータ電圧が同時にデータ線D<sub>1</sub> - D<sub>m</sub>を通じて一行の該当画素へ伝達される。

## 【0044】

ゲート駆動部400は、信号制御部600からのゲート制御信号CONT1によってゲートオン電圧V<sub>on</sub>をゲート線G<sub>1</sub> - G<sub>n</sub>に印加して、このゲート線G<sub>1</sub> - G<sub>n</sub>に接続されたスイッチング素子Qを導通させ、これによりデータ線D<sub>1</sub> - D<sub>m</sub>に印加されたデータ電圧が、導通したスイッチング素子Qを通じて当該画素に印加される。

## 【0045】

画素に印加されたデータ電圧と共通電圧V<sub>com</sub>の差は、液晶キャパシタC<sub>LC</sub>の充電電圧、つまり、画素電圧として現れる。液晶分子は画素電圧の大きさによってその配列が異なり、そのために液晶層3を通過する光の偏光が変化する。このような偏光の変化は、表示板100、200に付着された偏光子(図示せず)によって光の透過率変化として現れる。

## 【0046】

1水平周期(または「1H」)[水平同期信号H<sub>sync</sub>、データイネーブル信号DE、ゲートクロックCPVの一周期]が経過すれば、データ駆動部500とゲート駆動部400は次の行の画素に対して同じ動作を繰り返す。このような方式で1フレームの間に全てのゲート線G<sub>1</sub> - G<sub>n</sub>に対して順次にゲートオン電圧V<sub>on</sub>を印加して全ての画素にデータ電圧を印加する。1フレームが終われば、次のフレームが始まり、各画素に印加されるデータ電圧の極性が直前フレームにおける極性と反対になるように、データ駆動部500に印加される反転信号RVSの状態が制御される(「フレーム反転」)。この時、1フレーム内でも反転信号RVSの特性によって一つのデータ線を通じて流れるデータ電圧の極性が変わったり(「ライン反転」)、一つの画素行に印加されるデータ電圧の極性も互いに異なることがある(「ドット反転」)。

## 【0047】

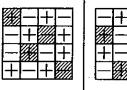

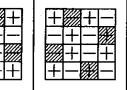

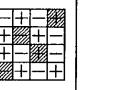

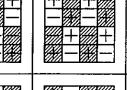

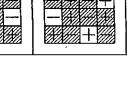

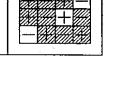

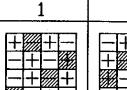

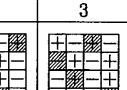

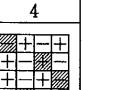

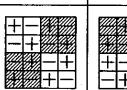

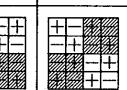

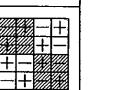

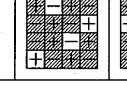

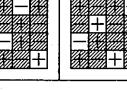

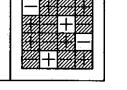

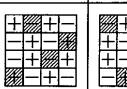

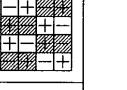

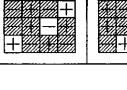

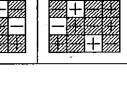

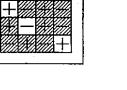

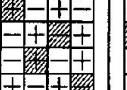

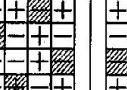

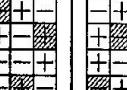

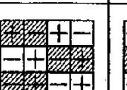

次に、図3乃至図8を参照して、本発明の一実施例における信号制御部600のデータ処理部601で実施されるフレームレート制御について説明する。

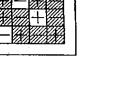

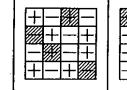

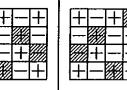

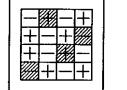

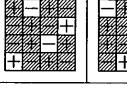

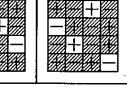

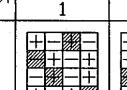

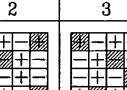

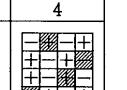

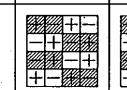

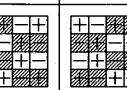

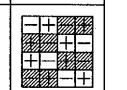

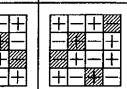

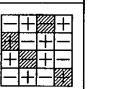

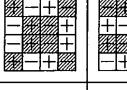

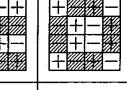

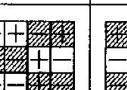

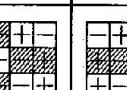

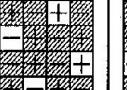

図3乃至図8は本発明の互いに異なる実施例によるFRCデータパターンの集合を示している。図3乃至図8のうちのいずれか一つに示したFRCデータパターン集合が信号制御部600のルックアップテーブルに記憶され、各FRCデータパターン集合に属するFRCデータパターンの各々は、入力映像データの下位2ビット値とフレーム番号によって決められる。連続する四つのフレームについて、下位2ビット値が(01)、(10)、(11)のものに対して一つずつのFRCデータパターンが存在し、合計12つのFRCデータパターンが存在する。下位2ビットが(00)である時のデータパターンは別に決められていない。

## 【0048】

図3乃至図8に示したように、各々のFRCデータパターンでは空間的配列の基本単位は4×4データ行列であり、これは対応する4×4画素行列を基本単位としてFRCデータパターンを反復的に適用することを意味する。各FRCデータパターンのデータエレメントは“1”または“0”的値を有する。図面において、“0”的値を有するデータエレメントは白色で、“1”的値を有するデータエレメントは斜線で示した。

## 【0049】

信号処理部601は、ある画素の入力映像データ(R、G、B)に対して入力映像信号(R、G、B)の下位2ビットの値及びフレーム番号によって、複数のFRCデータパターンのうちの一つを選択し、その画素の位置に相当するデータエレメントのデータ値を読み込んで

10

20

30

40

50

、これに基づいてデータ駆動部 500 に出力する出力映像データDATを決める。

【0050】

具体的には、選択された位置のデータ値が“0”である場合、データ処理部 601 は映像データ (R, G, B) の上位 6 ビットによって決められた階調の値を最終階調と決める。しかし、当該位置に記憶されたデータ値が“1”である場合、データ処理部 601 は、上位 6 ビットの決められた階調値に“1”を足した値を最終階調として決める。信号制御部 600 は、この最終階調に相当する 6 ビットの映像データDATをデータ駆動部 500 に出力する。

【0051】

但し、入力映像データ (R, G, B) の下位 2 ビットが (00) である場合には、データ処理部 601 は、ルックアップテーブル 602 に記憶されたFRCデータパターンを読み込みます、直ちに映像データ (R, G, B) の上位 6 ビットによって決められた階調値を最終階調として決める。

【0052】

以下では図 3 乃至図 8 に示したFRCデータパターンについて具体的に説明する。

下位 2 ビットが (01) であれば、各FRCデータパターンの 16 個のデータエレメントの 3 / 4 、つまり、16 個のうちの 12 個のデータエレメントが“0”的値を有し、残り四つのデータエレメントが“1”的値を有する。また、下位 2 ビットが (10) であれば各FRCデータパターンの全体の 2 / 4 、つまり、16 個のうちの 8 個のデータエレメントが“0”的値を有し、残り 8 個のデータエレメントが“1”的値を有し、(11) であれば全体の 1 / 4 、つまり、16 個のうちの四つのデータエレメントが“0”的値を有し、残り 12 個のデータエレメントが“1”的値を有する。このような規則はディザーリング (dithering) と言う空間的フレームレート制御の原則による。

【0053】

また、各々の下位 2 ビット値に対して存在する四つのFRCデータパターンの各FRCデータパターンにおける或る 1 つの位置のデータエレメントを参照すると、下位 2 ビット値によって、“0”または“1”的値を有する回数が決められることが分かる。つまり、或る 1 つの位置にある一つのデータエレメントを見れば、下位 2 ビットが (01) である時に与えられる四つのFRCデータパターンのうちの一つのFRCデータパターンでは“1”的値を有し、残り 3 個のFRCデータパターンでは“0”的値を有する。その位置のデータエレメントは、下位 2 ビットが (10) である時には、与えられる四つのFRCデータパターンのうちの二つのFRCデータパターンで“1”的値を有し、残り二つのFRCデータパターンで“0”的値を有する。また、その位置のデータエレメントは、下位 2 ビットが (11) である時に与えられる四つのFRCデータパターンのうちの 3 個のFRCデータパターンで“1”的値を有し、一つのFRCデータパターンで“0”的値を有する。このように規則は時間的フレームレート制御の規則によるものである。

【0054】

一方、下位 2 ビットが (00) である場合に対して作られるFRCデータパターンではデータエレメントの値が全て“0”であるので、別途のFRCデータパターンを作らなくても良い。したがって、8 ビット映像データ (R, G, B) を 6 ビット映像データDATに変換する時、空間的、時間的フレームレート制御のために必要な全FRCデータパターンの数は実質的に 16 個であるが、ルックアップテーブル 602 には下位 2 ビットが (00) である時のFRCデータパターン四つを除いた合計 12 個のFRCデータパターンのみが記憶されている。

【0055】

次に、図 3 乃至図 8 に示したFRCデータパターンの特徴を見てみる。

各図面に示した 12 個のFRCデータパターンでは、下位 2 ビットが (01) である場合に対する四つのFRCデータパターンは互いに異なっており、また、下位 2 ビットが (11) である場合に対する四つのFRCデータパターンも互いに異なっている。また、下位 2 ビットが (01) である場合と (11) である場合において、それぞれ、四つのFRCデータ

10

20

30

40

50

パターンのうちの二つのFRCデータパターンは互いに反転対称であり、残り二つのFRCデータパターンも互いに反転対称である。

【0056】

一方、下位2ビットが(10)である場合に対する四つのFRCデータパターンでは、少なくとも二つのFRCデータパターンは互いに同一であり得る。例えば、図3乃至図5に示したFRCデータパターン集合では、それぞれ、第1フレームと第3フレームに対するFRCデータパターンが同一であり、第2フレームと第4フレームに対するFRCデータパターンが同一である。また、図6と図7各々に示したFRCデータパターン集合では、第1フレームと第2フレームに対するFRCデータパターンが同一であり、第3フレームと第4フレームに対するFRCデータパターンが同一である。

10

【0057】

一方、 $4 \times 4$ データ行列からなるFRCデータパターンは、二つの $4 \times 2$ データ行列に分けることができ、このような $4 \times 2$ データ行列に対しても時間的、空間的フレームレート制御の原則によって配列が決められいる。

【0058】

図3及び図4で、下位2ビットが(01)である時の各FRCデータパターンを参照すると、一方の $4 \times 2$ データ行列で“1”的値を有するデータエレメントの間の距離は、他方の $4 \times 2$ データ行列で“1”的値を有するデータエレメントの間の距離と同一である。下位2ビットが(11)である時の各FRCデータパターンを参照すると、一方の $4 \times 2$ データ行列で“0”的値を有するデータエレメントの間の距離は、他方の $4 \times 2$ データ行列で“0”的値を有するデータエレメントの間の距離と同一である。

20

【0059】

これとは異なり、図5乃至図8では、下位2ビットが(01)である時の各FRCデータパターンを参照すると、一方の $4 \times 2$ データ行列で“1”的値を有するデータエレメントの間の距離は、他方の $4 \times 2$ データ行列で“1”的値を有するデータエレメントの間の距離と異なる。下位2ビットが(11)である時の各FRCデータパターンを参照すると、一方の $4 \times 2$ データ行列で“0”的値を有するデータエレメントの間の距離は、他方の $4 \times 2$ データ行列で“0”的値を有するデータエレメントの間の距離と異なる。

【0060】

図3乃至図8に示した $4 \times 4$ データ行列のFRCデータパターンは、四つの $2 \times 2$ データ行列に分けることもできる。このような $2 \times 2$ データ行列に対しても時間的、空間的フレームレート制御の原則によって配列が決められいる。

30

【0061】

図3乃至図8に示したように、下位2ビットが(01)である場合と(11)である場合とに対する各々のFRCデータパターンを構成する四つの $2 \times 2$ データ行列は全て相異である。

【0062】

まず、下位2ビットが(10)である時の、各々のFRCデータパターンを構成する四つの $2 \times 2$ データ行列の相互関係を説明する。

図8の場合を除けば、各々のFRCデータパターンを構成する四つの $2 \times 2$ データ行列の中では、2つの $2 \times 2$ データ行列は同一であり、残りの2つの $2 \times 2$ データ行列は互いに反転対称である。例えば、図3、図6及び図7に示した場合において、列方向に配列された二つの $2 \times 2$ データ行列が同一で、行方向に配列された二つの $2 \times 2$ データ行列が互いに反転している。図4の場合には、列方向に配列された二つの $2 \times 2$ データ行列が互いに反転していて、行方向に配列された二つの $2 \times 2$ データ行列が同一である。図5の場合には、縦方向および横方向の隣接した $2 \times 2$ データ行列が互いに反転していて、対角線方向の $2 \times 2$ データ行列が互いに同一である。

40

【0063】

図8の場合には、一対の $2 \times 2$ データ行列が互いに反転対称であり、他の一対の $2 \times 2$ データ行列も互いに反転対称である。

50

次に、下位 2 ビットが (10) である時の、各々の  $2 \times 2$  データ行列のデータエレメントを説明する。

【0064】

図 3、図 6 及び図 7 に示した各  $2 \times 2$  データ行列では、同一行のデータエレメントは同一の値を有し、他の行のデータエレメントは異なる値を有する。また、図 4 の場合、各  $2 \times 2$  データ行列で同一列のデータエレメントは同一の値を有し、他の列のデータエレメントは異なる値を有する。図 5 を参照すれば、 $2 \times 2$  データ行列のそれぞれにおいて、全てのデータエレメントの値は同一である。

【0065】

それに対して、図 8 を参照すると、第 1 及び第 3 フレームの場合、各  $2 \times 2$  データ行列 10 は、対角線方向のデータエレメントが同じ値を有し、縦方向および横方向の隣接したデータエレメントは互いに異なる値を有し、第 2 及び第 4 フレームの場合には、各  $2 \times 2$  データ行列は、同一行のデータエレメントが同一の値を有し、他の行のデータエレメントは異なる値を有する。

【0066】

図 3 乃至図 8 に示した FRC データパターンは本発明の幾つかの実施例を示すものであり、入力映像信号 (R、G、B) のビット数とデータ駆動部 500 が処理できるデータのビット数との差、液晶表示装置の特性などによって、他の形態の FRC データパターンが利用できる。

【0067】

一方、図 3 乃至図 8 の FRC データパターンに示した「+」表示と「-」表示は、これら 40  $4 \times 4$  データ行列に対応する  $4 \times 4$  画素行列で  $2 \times 1$  ドット反転とフレーム反転が行なわれた時に各画素が有することができる画素電圧の極性、つまり、正極性と負極性を示したものである。図示したように、入力映像データ (R、G、B) が全ての画素に対して同一であると仮定すれば、各フレームごとに同一な階調値が与えられる画素の中で「+」極性の画素電圧を有する画素数と、「-」極性の画素電圧を有する画素数が同一である。同一な階調値に対して正極性の画素電圧と負極性の画素電圧の大きさが実際に多少異なるという点を考慮する時、正極性の画素電圧を有する画素数と負極性の画素電圧を有する画素数が同一であれば、これらの平均輝度が常に一定になるので画質が向上する。

【0068】

本発明の実施例において、 $2 \times 1$  ドット反転の他に、他の形態の反転が行えるのは当然のことである。

また、図 3 乃至図 8 に示した FRC データパターンは、その構造や順序を、行または列単位で変えることができ、また、フレーム単位などで変えることもできる。

【0069】

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されものではなく、請求範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態もまた本発明の権利範囲に属する。

【図面の簡単な説明】

【0070】

【図 1】本発明の一実施例による液晶表示装置のブロック図である。

【図 2】本発明の一実施例による液晶表示装置の一つの画素に対する等価回路図である。

【図 3】本発明の実施例による 1 つの FRC データパターンである。

【図 4】本発明の実施例による 1 つの FRC データパターンである。

【図 5】本発明の実施例による 1 つの FRC データパターンである。

【図 6】本発明の実施例による 1 つの FRC データパターンである。

【図 7】本発明の実施例による 1 つの FRC データパターンである。

【図 8】本発明の実施例による 1 つの FRC データパターンである。

【符号の説明】

【0071】

10

20

30

40

50

## 3 液晶層

190 画素電極

230 色フィルター

270 共通電極

300 液晶表示板組立体

400 ゲート駆動部

500 データ駆動部

600 信号制御部

601 データ処理部

602 ルックアップテーブル

700 駆動電圧生成部

800 階調電圧生成部

10

【図1】

【図2】

【図3】

| LSB 2ビット | フレーム番号 |   |   |   |

|----------|--------|---|---|---|

|          | 1      | 2 | 3 | 4 |

| 01       | +      | + | + | + |

| 10       | +      | + | + | + |

| 11       | +      | + | + | + |

【図4】

| LSB 2ビット | フレーム番号                                                                            |                                                                                   |                                                                                   |                                                                                   |

|----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|          | 1                                                                                 | 2                                                                                 | 3                                                                                 | 4                                                                                 |

| 01       |  |  |  |  |

| 10       |  |  |  |  |

| 11       |  |  |  |  |

【図6】

| LSB 2ビット | フレーム番号                                                                            |                                                                                     |                                                                                     |                                                                                     |

|----------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|          | 1                                                                                 | 2                                                                                   | 3                                                                                   | 4                                                                                   |

| 01       |  |  |  |  |

| 10       |  |  |  |  |

| 11       |  |  |  |  |

【図5】

| LSB 2ビット | フレーム番号                                                                            |                                                                                   |                                                                                   |                                                                                   |

|----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|          | 1                                                                                 | 2                                                                                 | 3                                                                                 | 4                                                                                 |

| 01       |  |  |  |  |

| 10       |  |  |  |  |

| 11       |  |  |  |  |

【図7】

| LSB 2ビット | フレーム番号                                                                            |                                                                                     |                                                                                     |                                                                                     |

|----------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|          | 1                                                                                 | 2                                                                                   | 3                                                                                   | 4                                                                                   |

| 01       |  |  |  |  |

| 10       |  |  |  |  |

| 11       |  |  |  |  |

【図8】

| LSB 2ビット | フレーム番号                                                                              |                                                                                     |                                                                                     |                                                                                     |

|----------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|          | 1                                                                                   | 2                                                                                   | 3                                                                                   | 4                                                                                   |

| 01       |  |  |  |  |

| 10       |  |  |  |  |

| 11       |  |  |  |  |

## フロントページの続き

(51) Int.CI.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 3 K |

| G 0 9 G | 3/20 | 6 3 1 U |

| G 0 9 G | 3/20 | 6 4 2 A |

(74)代理人 100096068

弁理士 大塚 住江

(72)発明者 権 秀 現

大韓民国京畿道水原市八達区梅灘3洞 梅灘グリーンビル101棟504号

(72)発明者 金 明 淑

大韓民国京畿道水原市八達区遠川洞 遠川三星アパート2棟909号

F ターム(参考) 2H093 NA16 NA34 NA53 NA55 NC13 NC34 NC35 ND06 ND49

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5C006 | AA16 | AC21 | AC27 | AC28 | AF13 | AF23 | AF42 | AF43 | AF44 | AF45 |

| AF46  | AF51 | AF52 | AF53 | AF61 | AF71 | AF83 | BB16 | BC03 | BC11 |      |

| BC20  | BF08 | BF14 | BF24 | FA22 | FA23 |      |      |      |      |      |

| 5C080 | AA10 | BB05 | DD05 | DD06 | EE29 | FF11 | JJ02 | JJ05 |      |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2005242359A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2005-09-08 |

| 申请号            | JP2005050805                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2005-02-25 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 權秀現<br>金明洙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 權秀現<br>金明洙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| CPC分类号         | G09G3/3648 G09G3/2025 G09G3/3614 G09G2320/0285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/36 G02F1/133.575 G09G3/20.611.E G09G3/20.621.B G09G3/20.623.F G09G3/20.623.K<br>G09G3/20.631.U G09G3/20.642.A                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA34 2H093/NA53 2H093/NA55 2H093/NC13 2H093/NC34 2H093/NC35 2H093/ND06 2H093/ND49 5C006/AA16 5C006/AC21 5C006/AC27 5C006/AC28 5C006/AF13 5C006/AF23 5C006/AF42 5C006/AF43 5C006/AF44 5C006/AF45 5C006/AF46 5C006/AF51 5C006/AF52 5C006/AF53 5C006/AF61 5C006/AF71 5C006/AF83 5C006/BB16 5C006/BC03 5C006/BC11 5C006/BC20 5C006/BF08 5C006/BF14 5C006/BF24 5C006/FA22 5C006/FA23 5C080/AA10 5C080/BB05 5C080/DD05 5C080/DD06 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ05 2H193/ZA04 2H193/ZC20 2H193/ZD23 2H193/ZD25 |         |            |

| 代理人(译)         | 小林泰<br>千叶昭夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 优先权            | 1020040012739 2004-02-25 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

要解决的问题：减少由于帧速率的控制而导致的显示设备的图像质量下降。液晶标记装置技术领域本发明涉及一种在将多个帧率控制(FRC)数据图案存储在信号控制单元的查找表中之后执行FRC处理的液晶标记装置。存储在查找表中的FRC数据模式具有 $4 \times 4$ 数据矩阵作为基本单位，并且每个数据元素具有“1”或“0”的数据值。对于该 $4 \times 4$ 数据矩阵的 $4 \times 4$ 像素矩阵经过 $2 \times 1$ 点反转和帧反转，并且在与每一帧相对应的FRC数据模式中，它对应于具有“+”极性的像素，值为“+”的数据元素的数量和值为“1”的数据元素的数量相同，对应于极性为“-”的像素。结果，具有相同FRC数据值的具有相反极性的像素的数量变得相同。[选择图]图3

| LSB 2ビット | フレーム番号                                                                               |                                                                                       |                                                                                       |                                                                                       |

|----------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|          | 1                                                                                    | 2                                                                                     | 3                                                                                     | 4                                                                                     |

| 01       |  |  |  |  |

| 10       |  |  |  |  |

| 11       |  |  |  |  |