#### (19)日本国特許庁(JP)

# (12) **公開特許公報**(A) (11)特許出願公開番号

特開2001 - 337639

(P2001 - 337639A)

(43)公開日 平成13年12月7日(2001.12.7)

| (51) Int .CI <sup>7</sup> | 識別記号 | FI            | テーマコード(参考)      |

|---------------------------|------|---------------|-----------------|

| G 0 9 G 3/20              | 612  | G 0 9 G 3/20  | 612 E 2 H 0 9 3 |

|                           | 611  |               | 611 H 5 C 0 0 6 |

| G 0 2 F 1/133             | 550  | G 0 2 F 1/133 | 550 5 C 0 8 0   |

|                           | 570  |               | 570             |

| G 0 9 G 3/30              |      | G 0 9 G 3/30  | J               |

|                           | 審査請求 | 未請求 請求項の数 50  | L(全5数) 最終頁に続く   |

(21)出願番号 特願2000 - 156435(P2000 - 156435)

(22)出願日 平成12年5月26日(2000.5.26)

(71)出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(71)出願人 000221339

東芝電子エンジニアリング株式会社 神奈川県横浜市磯子区新杉田町8番地

(72)発明者 佐藤清一

神奈川県川崎市川崎区日進町7番地1 東芝

電子エンジニアリング株式会社内

(74)代理人 100064285

弁理士 佐藤 一雄 (外3名)

最終頁に続く

# (54)【発明の名称】 平面表示装置

# (57)【要約】

【課題】 シフトパルスと映像信号とのずれを防止し、 予期せぬ電位の書き込みを防止して表示品位を保障す る。

【解決手段】 液晶表示装置 1 は、複数の信号線 4 を駆動する信号線駆動回路 1 2 と、複数の走査線 3 を駆動する走査線駆動回路 1 1 とを液晶表示パネル 2 と一体に設けて構成されている。信号線駆動回路 4 および走査線駆動回路 3 内にそれぞれ設けられている電源 V D D , G N D にそれぞれ定電流回路 1 8 , 2 5 , 2 6 が設けられている。定電流回路 1 8 は、駆動回路 3 または 4 内のクロック回路 1 5 におけるクロックバッファ 1 6 , 1 7 とその電源 V D D , G N D間に設けられていても良いし、駆動回路を構成するシフトレジスタ 2 1 と電源 V D D 間およびシフトレジスタ 2 1 と接地電源 G N D との間に、第1および第2の定電流回路 2 5 , 2 6 として設けられていても良い。

1

#### 【特許請求の範囲】

【請求項1】複数の信号線を駆動する信号線駆動回路 と、複数の走査線を駆動する走査線駆動回路とを液晶表 示パネルと一体に設けた平面表示装置において、 前記信号線駆動回路および走査線駆動回路内にそれぞれ

設けられている電源にそれぞれ定電流回路が設けられて いることを特徴とする平面表示装置。

【請求項2】前記定電流回路は、前記信号線駆動回路お よび走査線駆動回路を含む駆動回路内に設けられたクロ ック回路に設けられ、前記クロック回路を構成するクロ 10 ためには、例えばクロックと反転クロックとを用い、走 ックバッファと電源との間に設けられていることを特徴 とする請求項1に記載の平面表示装置。

【請求項3】前記定電流回路は、前記信号線駆動回路お よび走査線駆動回路を含む駆動回路内に設けられたタイ ミング回路としてのシフトレジスタと電源との間に設け られていることを特徴とする請求項1に記載の平面表示 装置。

【請求項4】前記シフトレジスタは、スタートパルスを 入力する第1のクロックドインバータと、その出力側に 接続されると共に電源に対して第1のクロックドインバ 20 ータと並列に接続された第2のクロックドインバータ と、出力に対して第2のクロックドインバータと逆並列 に接続されたインバータとを備え、前記電源と前記シフ トレジスタとの間に第1の定電流回路が設けられ、前記 シフトレジスタと接地電源との間に第2の定電流回路が 設けられていることを特徴とする請求項3に記載の平面 表示装置。

【請求項5】前記定電流回路は、カレントミラー回路に より構成されていることを特徴とする請求項1に記載の 平面表示装置。

#### 【発明の詳細な説明】

# [0001]

【発明の属する技術分野】本発明は、液晶表示パネルお よび駆動回路等を備える平面表示装置に係り、特に液晶 表示パネル等を駆動する駆動回路が液晶表示パネルの基 板上に一体的に形成された駆動回路一体型液晶表示装置 に関するものである。

#### [0002]

【従来の技術】薄型,軽量の表示装置は、パーソナルワ ードプロセッサやパーソナルコンピュータ等のパーソナ 40 トパルスと映像信号とのタイミングのずれを防止するこ ルOA (Office - Automation)機器や、パーソナルテレ ビジョン用またはモニタ用のディスプレイデバイスとし て数多く利用されるようになってきている。

【0003】特に、液晶表示装置は、薄型,軽量,低消 費電力化が容易なことから研究開発が盛んに行なわれて いる。この液晶表示装置の分野においては、絶縁基板上 に多結晶シリコンまたはアモルファス(非晶質)シリコ ン等の薄膜半導体層によりスイッチング用のTFT(Th in-Film Transistor)マトリックスを形成したアクティ ブマトリックスパネルの開発が進められてきており、製 50 れ定電流回路が設けられていることを特徴としている。

造コスト低減のため、信号線駆動回路および走査線駆動 回路をTFTマトリックスと同一の絶縁基板上に形成す る技術も開発されている。

【0004】前述したTFTマトリックスを形成した絶 縁基板上に形成された信号線駆動回路および走査線駆動 回路は、複数のタイミング回路またはバッファ回路を並 列に配置して構成されている。

【0005】一般に、タイミング回路としてはシフトレ ジスタ型が知られている。シフトレジスタを動作させる 査線駆動回路においては、外部からクロックを取り込ん で反転クロックを生成している。

【0006】走査線駆動回路のシフトレジスタを動作さ せるクロックの配線は、その画面サイズに応じてある程 度は長くなってしまうために、配線の途中にクロックバ ッファ回路を挿入することが一般的に行なわれており、 このクロックバッファ回路はTFTにより構成されてい る。

#### [0007]

【発明が解決しようとする課題】このように構成された クロックバッファ回路においては、回路を構成している TFTの特性にばらつきがある場合には、クロックに遅 延が発生してしまい、シフトレジスタのタイミングがず れてしまう可能性がある。

【0008】また、タイミング回路がシフトレジスタ型 の駆動回路一体型液晶表示装置の動作は、シフトパルス がオン状態のときに映像信号を画素電極に書き込み、シ フトパルスがオフ状態になったときの電位を保持して表 示がなされる。シフトパルスと映像信号のタイミングは 30 シフトパルスが立ち下がってから映像信号が変化するよ うに外部の駆動回路により決定されており、外部駆動回 路により決定された信号が絶縁基板上に形成された駆動 回路に入力されているが、絶縁基板上のTFT特性にば らつきがあると、シフトパルスと映像信号とのタイミン グがずれてしまい、対応しない映像信号画素に書き込む 虞れがあり、これに伴い平面表示装置の表示品位を損ね てしまうという問題点があった。

【0009】本発明は、上記問題点を解決するために、 駆動回路内の電源に定電流回路を設けることによりシフ とにより、表示品位を保障することができる平面表示装 置を提供することを目的としている。

#### [0010]

【課題を解決するための手段】上記目的を達成するた め、本発明の基本的構成に係る平面表示装置は、複数の 信号線を駆動する信号線駆動回路と、複数の走査線を駆 動する走査線駆動回路とを液晶表示パネルと一体に設け た平面表示装置において、前記信号線駆動回路および走 査線駆動回路内にそれぞれ設けられている電源にそれぞ 3

【0011】上記記基本的構成において、前記定電流回 路は、前記信号線駆動回路および走査線駆動回路を含む 駆動回路内に設けられたクロック回路に設けられ、前記 クロック回路を構成するクロックバッファと電源との間 に設けられていても良い。

【0012】また、上記基本的構成において、前記定電 流回路は、前記信号線駆動回路および走査線駆動回路を 含む駆動回路内に設けられたタイミング回路としてのシ フトレジスタと電源との間に設けられていても良い。

レジスタは、スタートパルスを入力する第1のクロック ドインバータと、その出力側に接続されると共に電源に 対して第1のクロックドインバータと並列に接続された 第2のクロックドインバータと、出力に対して第2のク ロックドインバータと逆並列に接続されたインバータと を備え、前記電源と前記シフトレジスタとの間に第1の 定電流回路が設けられると共に、前記シフトレジスタと 接地電源との間に第2の定電流回路が設けられていても

【0014】なお、上記基本的構成において、前記定電 20 流回路は、カレントミラー回路により構成されていても 良い。

【0015】本発明に係る平面表示装置によれば、駆動 回路内の電源に停電流源が設けられているので、駆動回 路を構成するTFTの特性にばらつきが発生しても、シ フトレジスタの出力やクロック等の信号の遅延ばらつき を低減することができ、平面表示装置の表示品位を著し く損ねることがなくなる。

# [0016]

【発明の実施の形態】以下、添付図面を参照しながら本 30 発明に係る平面表示装置の実施形態について詳細に説明 する。

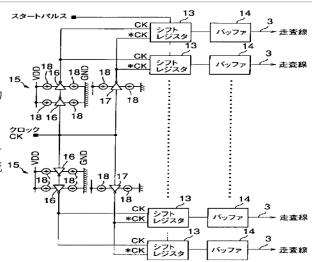

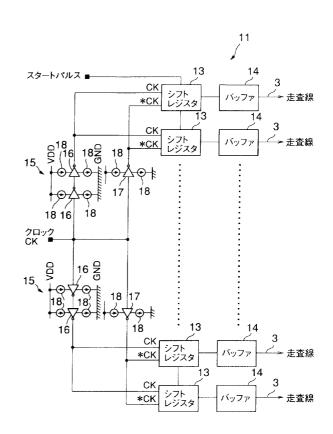

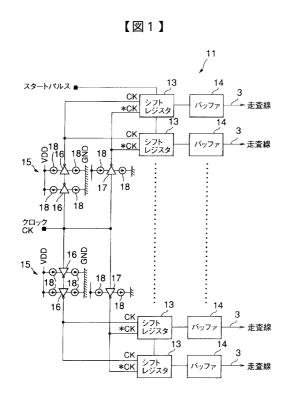

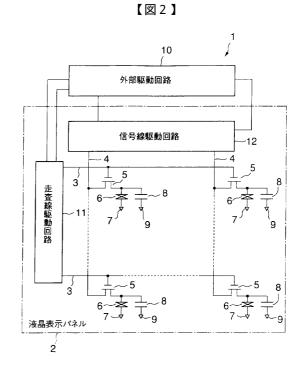

【0017】図1および図2は、本発明の第1実施形態 に係る平面表示装置を示すものであり、図1は第1実施 形態に係る液晶表示装置の要部としての走査線駆動回路 の概略的な構成を示す回路図、図2は第1実施形態の駆 動回路一体型液晶表示装置の概略的な構成を示す回路ブ ロック図である。

【0018】まず、図2を用いて液晶表示装置の全体の 構成について説明する。図2において、液晶表示装置1 40 示されず)から入力されたクロックCKを2段構成のク は、透明基板状に形成された液晶表示パネル2とパネル 2の外部に設けられる外部駆動回路10とを備えてい る。液晶表示パネル2は透明基板上に複数の走査線3と 複数の信号線4とがマトリックス状に配置されており、 各交点にはスイッチング素子としてのTFT5と、この TFT5に接続された画素電極および補助容量電極9が 設置された基板と共通電極7が設置された基板との間に 液晶を挟持して形成された液晶セル (画素)に設けられ た画素電極6と、TFT5と補助容量電極9との間に接 続された補助容量8と、を備えている。

【0019】図2に示される液晶表示装置1は、駆動回 路一体型であるので、液晶表示パネル2は、走査線3に アドレス信号を供給する走査線駆動回路11と、信号線 4に映像信号を供給する信号線駆動回路12と、を備え ている。液晶表示パネル2の外部に設けられた外部駆動 回路10は、走査線駆動回路11および信号線駆動回路 12に対してそれぞれアドレス信号および映像信号を所

定のタイミングで供給している。

【0020】上記のように構成された液晶表示装置を駆 【0013】さらに、上記の構成において、前記シフト 10 動する場合、走査線3には外部駆動回路10より走査線 駆動回路11を介してアドレス信号が供給され、信号線 4には外部駆動回路10より信号線駆動回路12を介し て映像信号が供給され、この映像信号はアドレス信号に よりオン・オフされるTFT5を介して各画素電極6に 書き込まれる。画素電極6に供給される電圧と、共通電 極7が設置された基板との間の電位差により、それぞれ の画素電極6上の液晶が映像信号に応じて駆動されてい る。

> 【0021】図1は、図2に示された液晶表示装置1の 全体構成に対して液晶パネル2内に一体的に設けられた 内部駆動回路の構成を走査線駆動回路11を例にして示 す詳細な回路構成図である。なお、走査線駆動回路11 は内部駆動回路の一例であり、信号線駆動回路12にも 同様の構成が設けられているものとする。

> 【0022】図1において、各走査線3毎にシフトレジ スタ13が設けられており、シフトレジスタ13より出 力されるアドレス信号はバッファ14に一時的に蓄積さ れてから走査線3を介して画素電極6(図1には図示さ れず)に供給されている。シフトレジスタ13には、外 部駆動回路10(図1には図示されず)よりスタートパ ルスが供給されると共に、クロック回路15よりクロッ クCKおよび\*CKが供給されている。なお、この明細 書および図面においては『\*』は反転符号として用いて おり、クロック\*CKはクロックCKの反転信号である ことを示している。

【0023】本発明は電源VDDおよびGNDを含むク ロック回路15のクロックバッファ16,17に定電流 回路18を設けたものであり、この第1実施形態に係る 液晶表示装置においては外部駆動回路10(図1には図 ロックバッファ16,16および1段構成のクロックバ ッファ17を介してシフトレジスタ13に入力させてい る。1段構成のクロックバッファ17を介してシフトレ ジスタ13に供給される信号は反転クロック\*CKとな っており、2段構成のクロックバッファ16,16を介 してシフトレジスタ13に供給される信号はクロックC Kとなっている。ここで、特徴的な構成は各クロックバ ッファ16,17毎に定電流回路18,18が設けられ ていることである。定電流回路18の具体的な構成とし 50 てはカレントミラー回路等を用いることができる。

5

【0024】上記第1実施形態に係る液晶表示装置にお いては、クロックバッファ16または17に定電流回路 18が設けられているので、バッファを構成しているT FTの特性にばらつきが生じても、クロックの立ち上が りおよび立ち下がりを一定に制御することができる。し たがって、クロックのタイミングにずれを生じさせるこ となく、シフトレジスタへのクロックの供給が可能とな る。これにより、シフトレジスタの安定した動作を保障 することができる。

【0025】次に、図3を用いて本発明の第2実施形態10係る平面表示装置によれば、その駆動回路内に設けられ に係る液晶表示装置について説明する。図3に示す第2 実施形態は、駆動回路20内の電源に定電流回路を設け るものであり、駆動回路20が設けられる液晶表示装置 1の全体構成は図2を用いて説明した第1実施形態の液 晶表示装置と同様の構成であるので、重複説明を証略す

【0026】図3において、駆動回路20は、タイミン グ回路としてのシフトレジスタ21を構成するクロック ドインバータ22,23およびインバータ24の電源に 定電流回路25,26を設けたものである。

【0027】前記シフトレジスタ21は、スタートパル スを入力する第1のクロックドインバータ22と、その 出力側に接続されると共に電源に対して第1のクロック ドインバータと並列に接続された第2のクロックドイン バータ23と、出力に対して第2のクロックドインバー タと逆並列に接続されたインバータ24とを備え、前記 電源VDDと前記シフトレジスタ21との間に第1の定 電流回路25が設けられ、前記シフトレジスタ21と接 地電源GNDとの間に第2の定電流回路26が設けられ ている。

【0028】複数のシフトレジスタ21は電源VDDお よびGND間に並列に複数接続されており、定電流回路 25は電源VDD側に設けられ、定電流回路26は接地 電源GND側に設けられている。定電流回路25,26 としては、図1に示した第1実施形態に係る定電流回路 と同様に、カレントミラー回路等を用いれば良い。

【0029】以上のように、図3に示す第2実施形態に 係る液晶表示装置においても、駆動回路20の電源に定 電流回路が設けられているので、後段に設けられている バッファ等を構成するTFTの特性にばらつきがあって 40 25,26 定電流回路 も、出力波形の立ち上がりおよび立ち下がりを一定に制 御することができ、出力波形における遅延のばらつきを 低減させることが可能となる。

【0030】なお、上述した第1および第2実施形態に 係る平面表示装置は、何れも液晶画素にアドレス信号を 供給する走査線を駆動する走査線駆動回路を例にとって 説明したが、本発明はこれに限定されず、映像信号を供 給する信号線を駆動する信号線駆動回路内の構成に適用 しても良いことは勿論である。また、この発明は有機E Lディスプレイ等の平面表示装置にも適用可能である。

#### [0031]

【発明の効果】以上、詳細に説明したように、本発明に た電源に定電流回路を設けるようにしたので、駆動回路 を構成するTFTの特性にばらつきが生じても電源に設 けられた定電流回路により波形の立ち上がりおよび立ち 下がりを制御することができるようになり、遅延ばらつ きを低減させることができ、これにより著しい表示品位 の低下を防止することができる。

# 【図面の簡単な説明】

【図1】本発明の第1実施形態に係る平面表示装置の駆 動回路の構成を示す回路ブロック図である。

20 【図2】本発明の第1および第2実施形態に係る平面表 示装置の全体構成を示すブロック図である。

【図3】本発明の第2実施形態に係る平面表示装置の駆 動回路の構成を示す回路ブロック図である。

#### 【符号の説明】

- 1 液晶表示装置

- 2 液晶表示パネル

- 3 走杳線

- 信号線

- 5 TFT

- 30 6 画素電極

- 11 走査線駆動回路

- 12 信号線駆動回路

- 15 クロック回路

- 16,17 クロックバッファ

- 18 定電流回路

- 20 駆動回路

- 21 シフトレジスタ

- 22,23 クロックドインバータ

- 24 インバータ

- VDD 電源

- GND 接地電源

# VDD 20 21 21 21 21 22 24 24 77 GND

# フロントページの続き

| 专利名称(译)        | 平面表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | JP2001337639A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2001-12-07 |  |  |

| 申请号            | JP2000156435                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2000-05-26 |  |  |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |

| 申请(专利权)人(译)    | 东芝公司<br>东芝电子工程有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |

| [标]发明人         | 佐藤清一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |

| 发明人            | 佐藤清一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/30 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |

| FI分类号          | G09G3/20.612.E G09G3/20.611.H G02F1/133.550 G02F1/133.570 G09G3/30.J G09G3/36 G09G3 /3225 G09G3/3266                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NC01 2H093/NC13 2H093/NC16 2H093/NC22 2H093/NC34 2H093 /NC68 2H093/ND33 2H093/ND34 2H093/NE10 5C006/AA01 5C006/BB16 5C006/BC03 5C006/BC12 5C006/BC20 5C006/BF03 5C006/BF27 5C006/BF42 5C006/BF50 5C006/FA16 5C006/FA20 5C006 /FA23 5C006/FA26 5C080/AA06 5C080/AA10 5C080/BB05 5C080/DD06 5C080/DD09 5C080/FF11 5C080/JJ02 5C080/JJ03 2H193/ZA04 2H193/ZF01 2H193/ZH40 2H193/ZH42 2H193/ZP20 5C380 /AA01 5C380/AB06 5C380/AB18 5C380/AC07 5C380/AC08 5C380/BA32 5C380/BA37 5C380/CB14 5C380/CE04 5C380/CF07 5C380/CF26 |         |            |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |

# 摘要(译)

解决的问题:为防止移位脉冲和视频信号之间发生移位,防止电位意外写入,并保证显示质量。 液晶显示装置1是在液晶显示面板2上一体地设置有用于驱动多条信号线4的信号线驱动电路12和用于驱动多条扫描线3 15的扫描线驱动电路11而构成的。 已经完成了。 在分别设置在信号线驱动电路4和扫描线驱动电路3中的电源VDD,GND中设置有恒流电路18、25、26。 恒流电路18可以设置在驱动电路3或4中的时钟电路15的时钟 缓冲器16和17与它们的电源VDD和GND之间,或者设置在形成驱动电路的移位寄存器21与电源VDD之间。 第一恒定电流电路25和第二恒定电流 15、电路26可以设置在移位寄存器21与接地电源GND之间。