(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4154611号

(P4154611)

(45) 発行日 平成20年9月24日(2008.9.24)

(24) 登録日 平成20年7月18日(2008.7.18)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G09G 3/20 (2006.01)**

**G11C 19/00 (2006.01)**

GO9G 3/36

GO2F 1/133 505

GO9G 3/20 622E

GO9G 3/20 670E

G11C 19/00 G

請求項の数 8 (全 15 頁) 最終頁に続く

(21) 出願番号

特願2004-374584 (P2004-374584)

(22) 出願日

平成16年12月24日(2004.12.24)

(65) 公開番号

特開2005-338758 (P2005-338758A)

(43) 公開日

平成17年12月8日(2005.12.8)

審査請求日

平成16年12月24日(2004.12.24)

(31) 優先権主張番号

2004-037724

(32) 優先日

平成16年5月27日(2004.5.27)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者

501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンパーク, ヨ

イドードン 20

(74) 代理人

100110423

弁理士 曽我 道治

(74) 代理人

100084010

弁理士 古川 秀利

(74) 代理人

100094695

弁理士 鈴木 憲七

(74) 代理人

100111648

弁理士 梶並 順

最終頁に続く

(54) 【発明の名称】シフトレジスタ及び液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート駆動パルスを順次出力する複数のステージを具備したシフトレジスタにおいて、少なくとも1つのステージは、

第1クロック信号によりターンオンしてスタートパルスを第1ノードに印加する第1スイッチング素子と、

前記第1クロック信号によりターンオンして第1供給電圧を第2ノードに印加する第2スイッチング素子と、

前記第1ノードに印加したスタートパルスによりターンオンして第2クロック信号を出力する第3スイッチング素子と、

前記第2ノードに印加した第1供給電圧によりターンオンして第2供給電圧を出力する第4スイッチング素子と、

前記スタートパルスによりターンオンして前記スタートパルスを前記第1ノードに印加する第5スイッチング素子と、

前記第1ノードの充電状態によりターンオンして前記第2供給電圧を導通させる第6スイッチング素子と、

前記第2クロック信号の論理によりターンオンして前記第6スイッチング素子を経由する第2供給電圧を前記第2ノードに充電させる第7スイッチング素子と

を含んで構成することを特徴とするシフトレジスタ。

## 【請求項 2】

10

20

前記第1乃至第7スイッチング素子はPMOSトランジスタまたはNMOSトランジスタのうち何れか1つである

ことを特徴とする請求項1に記載のシフトレジスタ。

【請求項3】

前記第1スイッチング素子と第5スイッチング素子とは互いに並列に接続することを特徴とする請求項1に記載のシフトレジスタ。

【請求項4】

前記第1スイッチング素子のソースと前記第5スイッチング素子のソースとが互いに接続し、前記第1スイッチング素子のドレインと前記第5スイッチング素子のドレインとが互いに接続し、前記第5スイッチング素子のゲートは前記第5スイッチング素子のソースに接続する

ことを特徴とする請求項3に記載のシフトレジスタ。

【請求項5】

前記少なくとも1つのステージは前記複数のステージの全てに該当することを特徴とする請求項1に記載のシフトレジスタ。

【請求項6】

前記少なくとも1つのステージは最初のステージに該当することを特徴とする請求項1に記載のシフトレジスタ。

【請求項7】

互いに垂直交差する複数のゲートライン及びデータラインが具備された液晶パネルと、前記液晶パネルの各ゲートラインにゲート駆動パルスを順次供給するゲートドライバーと、

前記各ゲートドライバーのシフトレジスタに具備された複数のステージを具備し、少なくとも1つのステージは、

第1クロック信号によりターンオンしてスタートパルスを第1ノードに印加する第1スイッチング素子と、

前記第1クロック信号によりターンオンして第1供給電圧を第2ノードに印加する第2スイッチング素子と、

前記第1ノードに印加したスタートパルスによりターンオンして第2クロック信号を出力する第3スイッチング素子と、

前記第2ノードに印加した第1供給電圧によりターンオンして第2供給電圧を出力する第4スイッチング素子と、

前記スタートパルスによりターンオンして前記スタートパルスを前記第1ノードに印加する第5スイッチング素子と、

前記第1ノードの充電状態によりターンオンして前記第2供給電圧を導通させる第6スイッチング素子と、

前記第2クロック信号の論理によりターンオンして前記第6スイッチング素子を経由する第2供給電圧を前記第2ノードに充電させる第7スイッチング素子と

を含んで構成することを特徴とする液晶表示装置。

【請求項8】

前記第5スイッチング素子は、前記複数のステージのうち、前記スタートパルスが印加される最初のステージにのみ具備する

ことを特徴とする請求項7に記載の液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置に関し、特にスタートパルスとクロック信号の同期化が不要なシフトレジスタ及びこれを用いた液晶表示装置に関する。

【背景技術】

【0002】

10

20

30

40

50

情報化社会が発展するにつれ、表示装置に対する要求も多様な形態に広がってきており、これに相応して、近来では、LCD、PDP、ELD、VFD等様々な平板表示装置が研究され、一部は既に様々な装備で表示装置として活用されている。そのうち、現在、画質が優れ、軽量、薄型、低消費電力の長所により移動型画像表示装置の用途としてCRTを代替してLCDが最も多く用いられており、ノートパソコンのモニターのような移動型の用途以外にも放送信号を受信してディスプレイするテレビ及びコンピュータのモニターなどに多様に開発されている。

【0003】

このように液晶表示装置が様々な分野で画面表示装置としての役割を果たすために色々な技術的な発展が成されたにもかかわらず、画面表示装置として画像の品質を高める作業は前記長所と相反する面が多くある。したがって、液晶表示装置が一般的な画面表示装置として多様な部分に用いられるためには、軽量、薄型、低消費電力の特徴を維持しながらも、高精細、高輝度、大画面等、高品位画像をどの程度表すことができるかが発展の鍵になると言える。

【0004】

このような液晶表示装置は、画像を表示する液晶パネルと前記液晶パネルに駆動信号を印加するための駆動部とに大別することができ、前記液晶パネルは所定空間をもって貼り合わされた第1及び第2ガラス基板と、前記第1基板と第2ガラス基板間に注入された液晶層とで構成される。

【0005】

ここで、前記第1ガラス基板（TFTアレイ基板）には、所定間隔をもって一方向に配列される複数のゲートラインと、画素領域を定義するために前記各ゲートラインと垂直方向に一定の間隔をもって配列される複数のデータラインと、前記画素領域にマトリックス状に形成される複数の画素電極と、前記各ゲートラインとデータラインが交差する部分に形成されて前記ゲートラインのスキャン信号によりスイッチングされ、前記データラインのデータ信号を前記各画素電極に伝達する複数の薄膜トランジスタが形成される。また、第2ガラス基板（カラーフィルター基板）には、前記画素領域を除外した部分の光を遮断するためのブラックマトリックス層と、カラー色相を表現するためのR、G、Bカラーフィルター層と、画像を表すための共通電極とが形成される。

【0006】

このような前記第1及び第2ガラス基板は、スペーサにより所定空間をもって液晶注入口を有するシール材により貼り合わされて前記2基板間に液晶が形成される。

【0007】

以下、添付された図面を参考として従来の液晶表示装置の駆動回路を説明すると次の通りである。

【0008】

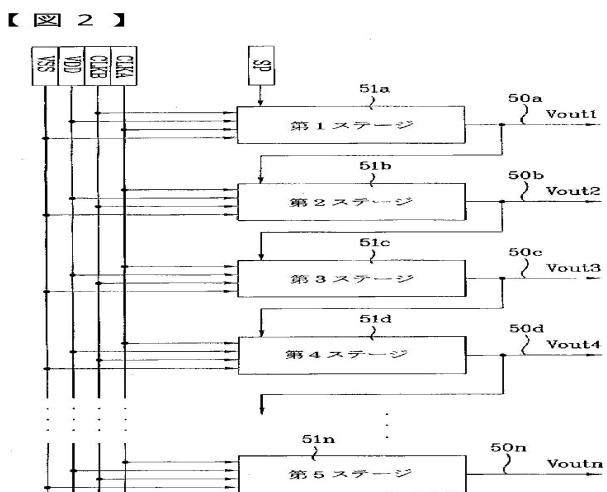

図1は、一般的な液晶表示装置の駆動回路を示したブロック構成図である。図1に示したように、複数のゲートラインGとデータラインDが互いに垂直方向に配列されてマトリックス状の画素領域を有する液晶表示パネル21と、前記液晶表示パネル21にスキャン信号とデータ信号を供給する駆動回路部22と、前記液晶表示パネル21に一定の光源を提供するバックライト28とで区分される。

【0009】

ここで、前記駆動回路部22は、前記液晶表示パネル21の各データラインにデータ信号を入力するデータドライバー21bと、前記液晶表示パネル21の各ゲートラインGにスキャン信号を印加するゲートドライバー21aと、液晶表示パネルの駆動システム27から入力されるディスプレイデータR、G、Bと、垂直及び水平同期信号Vsync、Hsync、クロック信号DCLK等の制御信号が入力されて前記液晶表示パネル21の各データドライバー21bとゲートドライバー21aとが画面を再生するに適合するタイミングで各ディスプレイデータとクロック及び制御信号をフォーマットして出力するタイミングコントローラ23と、前記液晶表示パネル21及び各部に必要な電圧を供給する電

10

20

30

40

50

源供給部 24 と、前記電源供給部 24 から電源が印加されて前記データドライバー 21b が入力されるデジタルデータをアナログデータと変換する時、必要な基準電圧を前記データドライバー 21b に供給するガンマ基準電圧部 25 と、前記電源供給部 24 から出力された電圧を用いて液晶表示パネル 21 に用いられる定電圧 VDD、ゲート高電圧 VGH、ゲート低電圧 VGL、基準電圧 Vref 及び共通電圧 Vcom などを出力する DC/DC 変換部 26 と、前記バックライト 28 を駆動するインバータ 29 を具備して構成される。

#### 【0010】

このように構成された一般的な液晶表示装置の駆動回路の動作は次の通りである。

すなわち、タイミングコントローラ 23 が液晶表示パネルの駆動システム 27 から入力されるディスプレイデータ R、G、B と垂直及び水平同期信号 Vsync、Hsync、クロック信号 DCLK 等の制御信号が入力されて前記液晶表示パネル 21 の各データドライバー 21b とゲートドライバー 21a とが画面を再生するに適合するタイミングで各ディスプレイデータとクロック及び制御信号を提供するため、前記ゲートドライバー 21a が前記液晶表示パネル 21 の各ゲートライン G にスキャン信号を印加し、これに同期して前記データドライバー 21b が前記液晶表示パネル 21 の各データライン D にデータ信号を入力し、入力された映像信号をディスプレイする。ここで、前記ゲートドライバーは、前記各ゲートラインに順次スキャニング信号を供給するためのシフトレジスタを含む。

#### 【0011】

以下、添付した図面を参照して従来のシフトレジスタを詳細に説明すると次の通りである。

#### 【0012】

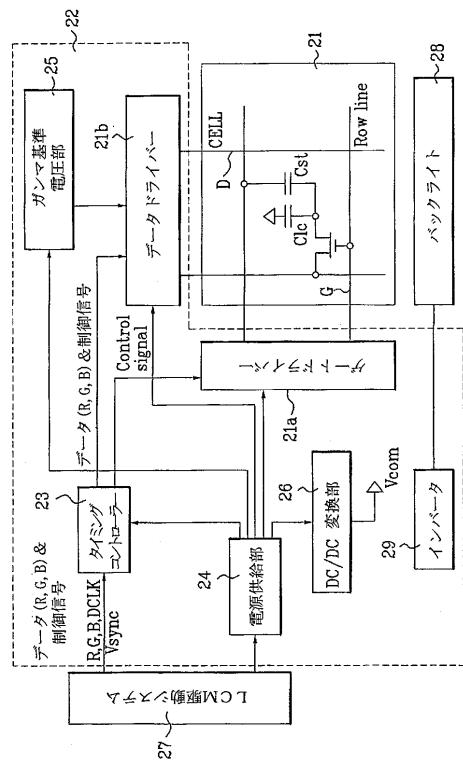

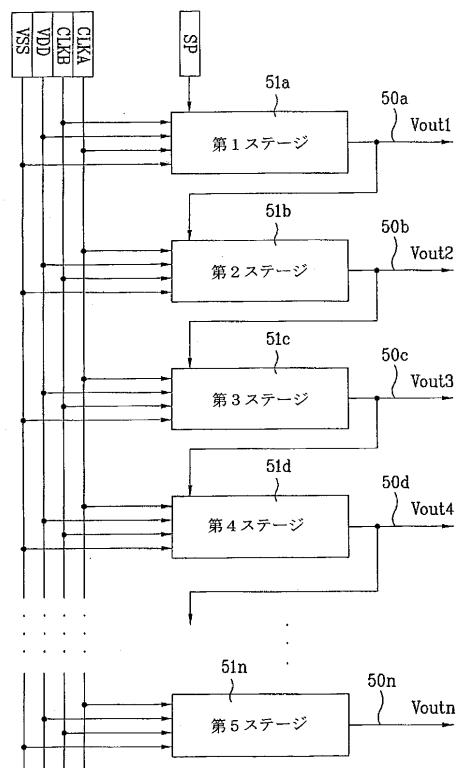

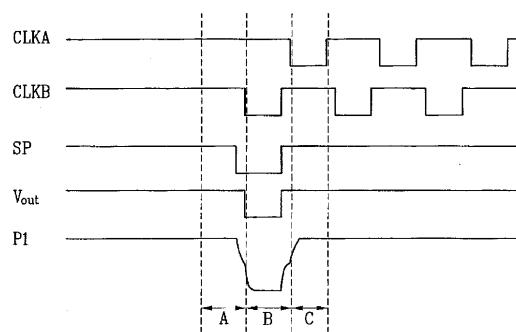

図 2 は、従来のシフトレジスタの概略的な構成図で、図 3 は、図 2 の各ステージに対する概略的な回路構成図である。従来のシフトレジスタは、図 2 に示したように、各種クロック信号 CLKA、CLKB 及び供給電圧 VDD、VSS が印加されて各ゲートライン G を駆動するためのゲート駆動パルスを順次出力する複数のステージ 51a、51b、51c、51d、…、51n を具備している。

#### 【0013】

ここで、第 1 ステージ 51a は、スタートパルス SP、第 1 クロック信号 CLKA、第 2 クロック信号 CLKB、第 1 供給電圧 VDD 及び第 2 供給電圧 VSS が印加されて第 1 ゲート駆動パルス Vout1 を出力し、前記第 2 ステージ 51b は、前記第 1 ステージ 51a の第 1 ゲート駆動パルス Vout1、第 1 クロック信号 CLKA、第 2 クロック信号 CLKB、第 1 供給電圧 VDD 及び第 2 供給電圧 VSS が印加されて前記第 1 ゲート駆動パルス Vout1 より一周期遅れた第 2 ゲート駆動パルス Vout2 を出力し、…、第 n ステージ 51n は第 n-1 ステージ 51n-1 の第 n-1 ゲート駆動パルス Voutn-1、第 1 クロック信号 CLKA、第 2 クロック信号 CLKB、第 1 供給電圧 VDD 及び第 2 供給電圧 VSS が印加されて前記第 n-1 ゲート駆動パルス Voutn-1 より一周期遅れた第 n ゲート駆動パルス Voutn を出力する。

#### 【0014】

要約すると、前記第 1 ステージ 51a のみスタートパルス SP が供給されて、残りの第 2 乃至第 n ステージ (51b 乃至 51n) は各々その前段のステージの出力 (ゲート駆動パルス (Vout1 乃至 Voutn-1)) を入力として用いて、各前段の出力 (ゲート駆動パルス (Vout1 乃至 Voutn-1)) より一周期遅れたゲート駆動パルス (Vout2 乃至 Voutn) を出力する。したがって、前記各ステージ 51a、51b、51c、51d、…、51n から出力される各ゲート駆動パルス (Vout1 乃至 Voutn) は前記各ゲートライン G に供給されて各ゲートライン G を順次スキャニングするようになる。このため、各ステージ 51a、51b、51c、51d、…、51n には図 3 に示したような回路が構成されている。

#### 【0015】

ここで、各ステージ 51a、51b、51c、51d、…、51n の回路構成は全

10

20

30

40

50

て同一で、単に第1、第2クロック信号CLKA、CLKBのみ奇数番目のステージ51a、51c、51e、…と偶数番目のステージ51b、51d、…とで互いに異なるように印加するため、第1ステージ51aに構成された回路を例を挙げて説明する。

【0016】

すなわち、図3に示したように、前記第1ステージ51aは、第1クロック信号CLKAの論理によりターンオンまたはターンオフし、ターンオンの時、スタートパルスSPを導通させて第1ノードP1に充電させる第1PMOSトランジスタT1と、第1クロック信号CLKAの論理によりターンオンまたはターンオフし、ターンオンの時、第1供給電圧VDDを導通させて第2ノードP2に充電させる第2PMOSトランジスタT2と、前記第1ノードP1に充電した前記スタートパルスSPの論理によりターンオンまたはターンオフし、ターンオンの時、第2クロック信号CLKBを導通させて出力ライン50aに供給する第3PMOSトランジスタT3と、前記第2ノードP2の充電状態によりターンオンまたはターンオフし、ターンオンの時、第2供給電圧VSSを導通させて前記出力ライン50aに供給する第4PMOSトランジスタT4と、前記第1ノードP1に充電したスタートパルスSPの論理によりターンオンまたはターンオフし、ターンオンの時、前記第2供給電圧VSSを導通させる第5PMOSトランジスタT5と、前記第2クロック信号CLKBの論理によりターンオンまたはターンオフし、ターンオンの時、前記第5PMOSトランジスタT5を経由する第2供給電圧VSSを導通させて前記第2ノードP2を放電させる第6PMOSトランジスタT6をさらに具備する。

【0017】

ここで、前記第2ノードP2には、前記第1供給電圧VDDまたは第2供給電圧VSSを充電でき、前記第2ノードP2にロー論理を有する第2供給電圧VSSが充電された場合、前記第2ノードP2にゲートを通して連結した第4PMOSトランジスタT4はターンオンし、前記第2ノードP2にハイ論理を有する第1供給電圧VDDが充電された場合、前記第4PMOSトランジスタT4はターンオフする。一方、前記第3または第4PMOSトランジスタ(T3、T4)を経由して第1ステージ51aの出力ライン50aに供給する第2クロック信号CLKBは、前記第1ゲート駆動パルスVout1として用いるとともに、次のステージ51bのスタートパルスSPとして用いる。

【0018】

そして、上述したように、奇数番目のステージ51a、51c、51e、…では前記第1、第2PMOSトランジスタ(T1、T2)のゲート端子に前記第1クロック信号CLKAが印加され、前記第3PMOSトランジスタT3のソース端子に第2クロック信号CLKBが印加される。そして、偶数番目のステージ51b、51d、…では前記第1、第2PMOSトランジスタ(T1、T2)のゲート端子に前記第2クロック信号CLKBが印加され、前記第3PMOSトランジスタT3のソース端子に第1クロック信号CLKAが印加される。このように構成された従来のシフトレジスタの動作を詳細に説明すると次の通りである。

【0019】

図4は、従来のシフトレジスタに供給される各種信号に対するタイミング図である。まず、第1周期(A)間に、前記シフトレジスタの動作を説明すると次の通りである。すなわち、図4に示したように、第1周期(A)間にスタートパルスSP及び第1クロック信号CLKAはロー論理状態を維持し、第2クロック信号CLKBはハイ論理状態を維持している。前記ロー論理の第1クロック信号CLKAは第1及び第2PMOSトランジスタ(T1、T2)のゲートに印加する。そして、前記第1及び第2PMOSトランジスタ(T1、T2)は前記ロー論理の第1クロック信号CLKAによりターンオンし、前記第1PMOSトランジスタT1のソースに印加したロー論理のスタートパルスSPは前記ターンオンした第1PMOSトランジスタT1を経由して第1ノードP1に充電し、前記第2PMOSトランジスタT2のソースに印加したハイ論理の第1供給電圧VDDは前記ターンオンした第2PMOSトランジスタT2を経由して第2ノードP2に充電する。

【0020】

10

20

30

40

50

その後、前記第1ノードP1に充電したロー論理のスタートパルスSPは前記第1ノードP1にゲートを通して連結した第3及び第5PMOSトランジスタ(T3、T5)をターンオンさせ、前記第2ノードP2に充電したハイ論理の第1供給電圧VDDは第4PMOSトランジスタT4をターンオフさせる。したがって、前記第3PMOSトランジスタT3のソースに印加したハイ論理の第2クロック信号CLKBは前記ターンオンした第3PMOSトランジスタT3を経由して出力ライン50aに供給される。

【0021】

この時、前記ハイ論理の第2クロック信号CLKBは第6PMOSトランジスタT6のゲートに印加して前記第6PMOSトランジスタT6をターンオフさせる。一方、前記第2ノードP2に充電されたハイ論理の第1供給電圧VDDは第4PMOSトランジスタT4のゲートに印加して前記第4PMOSトランジスタT4をターンオフさせる。結局、第1周期(A)間、前記第3PMOSトランジスタT3はターンオンし、かつ前記第4PMOSトランジスタT4はターンオフし、前記出力ライン50aにはハイ論理の第2クロック信号CLKBが供給される。

10

【0022】

次に、第2周期(B)間のシフトレジスタの動作は次の通りである。第2周期(B)間には前記スタートパルスSP及び第1クロック信号CLKAが全てハイ論理状態に変化し、前記第2クロック信号CLKBはロー論理状態に変化する。したがって、前記ハイ論理の第1クロック信号CLKAが各ゲートを通して印加する前記第1及び第2PMOSトランジスタ(T1、T2)は全てターンオフし、前記第1ノードP1は第1周期(A)間充電されたロー論理のスタートパルスSPをそのまま維持するようになる。

20

【0023】

したがって、前記第1ノードP1に充電したロー論理のスタートパルスSPにより前記第3及び第5PMOSトランジスタ(T3、T5)は全てターンオン状態をそのまま維持する。そして、第2周期(B)間上述したように、前記第2クロック信号CLKBがロー論理に変化するにつれ、前記第6PMOSトランジスタT6がターンオンし、これにより前記第2ノードP2には前記ターンオンした第5及び第6PMOSトランジスタ(T5、T6)を経由するハイ論理の第2供給電圧VSS(+V)が充電される。結局、前記第2ノードP2に充電されたハイ論理の第2供給電圧VSSにより前記第4PMOSトランジスタT4はターンオフするため、前記出力ライン50aには前記ターンオンした第3PMOSトランジスタT3を経由するロー論理の第2クロック信号CLKBが供給される。

30

【0024】

この時、前記第2周期(B)間、前記第1及び第2PMOSトランジスタ(T1、T2)がターンオフして前記第1ノードP1はフローティング状態になり、前記第3PMOSトランジスタT3のゲートとドレイン間の寄生キャパシターにより前記第1ノードP1のスタートパルスSPは前記出力ライン50aに供給したロー論理の第2クロック信号CLKBだけさらに離れるようになる。したがって、前記第3PMOSトランジスタT3のゲートにはより高い電圧のスタートパルスSPが印加して前記第3PMOSトランジスタT3の閾値電圧が小さくなり、これにより前記出力ライン50aには前記ロー論理の第2クロック信号CLKBが殆ど損失無く供給される。

40

【0025】

次に、第3周期(C)間シフトレジスタの動作は次の通りである。第3周期(C)間にはスタートパルスSPがハイ論理状態をそのまま維持し、前記第1クロック信号CLKAはロー論理状態に変化し、前記第2クロック信号CLKBはハイ論理状態に変化する。したがって、前記ロー論理の第1クロック信号CLKAにより前記第1及び第2PMOSトランジスタ(T1、T2)は再度ターンオンし、前記ハイ論理のスタートパルスSPが前記ターンオンした第1PMOSトランジスタT1を経由して第1ノードP1に充電され、前記ロー論理の第1供給電圧VDD(-V)が前記ターンオンした第2PMOSトランジスタT2を経由して前記第2ノードP2に充電する。

【0026】

50

その後、前記第1ノードP1に充電したハイ論理のスタートパルスSPは第3及び第5PMOSトランジスタ(T3、T5)をターンオフさせ、第2ノードP2に充電したロー論理の第1供給電圧VDDは第4PMOSトランジスタT4をターンオンさせる。また、ハイ論理の第2クロック信号CLKBは前記第6PMOSトランジスタT6のゲートに印加されて前記第6PMOSトランジスタT6をターンオフさせる。したがって、前記出力ライン50aには前記ターンオンした第4PMOSトランジスタT4を経由するハイ論理の第2供給電圧VSSが印加される。

【0027】

ここで、前記第2周期(B)間に第1ステージ51aの出力ライン50aに供給されたロー論理の第2クロック信号CLKBが上述したゲートラインGを駆動する第1ゲート駆動パルスVout1に該当する。そして、これと同時に、前記第1ステージ51aの出力ライン50aから出力した前記第1ゲート駆動パルスVout1は第2ステージ51bの第1PMOSトランジスタT1のソース端に印加され、前記第2クロック信号CLKBが前記第1、第2PMOSトランジスタ(T1、T2)のゲート端に印加するため、前記第2ステージ51bの出力ライン50bには前記第1ステージ51aのロー論理の第1クロック信号CLKAより一周期遅れた(シフトされた)ロー論理の第1クロック信号CLKAが第2ゲート駆動パルスVout2として出力される。したがって、前記のようなシフトレジスタにより前記ゲートラインGには順次第1乃至第nゲート駆動パルス(Vout1乃至Voutn)が供給される。

【0028】

一方、前記スタートパルスSPは前記第1クロック信号CLKAの論理によりその出力可否が決定されるため、特に第1ステージに供給されるスタートパルスSPは前記第1クロック信号CLKAと同期して出力しなければならない。すなわち、上述したように、前記第1クロック信号CLKAは前記第1PMOSトランジスタT1のゲートに供給され、前記第1PMOSトランジスタT1をターンオンまたはターンオフさせるようになるが、前記第1周期(A)間、前記第1ノードP1に前記スタートパルスSPを充電させるためには前記スタートパルスSPが導通することができるよう前記第1PMOSトランジスタT1がターンオン状態を維持しなければならず、このためには前記第1周期(A)間、前記第1PMOSトランジスタT1のゲートに供給する第1クロック信号CLKAは必ずロー論理を有さなければならない。

【発明の開示】

【発明が解決しようとする課題】

【0029】

したがって、従来のシフトレジスタが正常に動作するためには前記第1クロック信号CLKAと前記スタートパルスSPが必ず同期化されなければならないという制約があった。

【0030】

本発明は上記の問題点を解決するためのもので、その目的は、第1ステージに供給するスタートパルスとクロック信号が同期しなくてもゲート駆動パルスを出力することができるシフトレジスタ及びこれを用いた液晶表示装置を提供することにある。

【課題を解決するための手段】

【0031】

上記目的を達成するために、本発明に係るシフトレジスタは、ゲート駆動パルスを順次出力する複数のステージを具備したシフトレジスタにおいて、少なくとも1つのステージは第1クロック信号によりターンオンしてスタートパルスを第1ノードに印加する第1スイッチング素子と、前記第1クロック信号によりターンオンして第1供給電圧を第2ノードに印加する第2スイッチング素子と、前記第1ノードに印加したスタートパルスによりターンオンして、第2クロック信号を出力ラインに印加する第3スイッチング素子と、前記第2ノードに印加した第1供給電圧によりターンオンして第2供給電圧を出力ラインに印加する第4スイッチング素子と、前記スタートパルスによりターンオンして前記スター

10

20

30

40

50

トパルスを前記第1ノードに印加する第5スイッチング素子と、前記第1ノードの充電状態によりターンオンして前記第2供給電圧を導通させる第6スイッチング素子と、前記第2クロック信号の論理によりターンオンして前記第6スイッチング素子を経由する第2供給電圧を前記第2ノードに充電させる第7スイッチング素子とを含んで構成することにその特徴がある。

【発明の効果】

【0032】

本発明のシフトレジスタ及びこれを用いた液晶表示装置には次のような効果がある。本発明に係るシフトレジスタはスタートパルスの論理に拘わらず、前記スタートパルスの論理によりターンオンする別途のスイッチング素子をさらに具備するため、前記スタートパルスとクロック信号が同期して出力しなくても前記スタートパルスが正常にノードに充電する。

10

【発明を実施するための最良の形態】

【0033】

以下、本発明に係るシフトレジスタの好適な実施の形態について、添付の図面に基づいて詳細に説明する。

【0034】

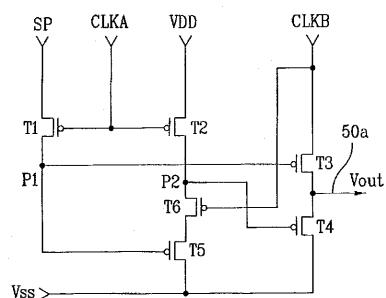

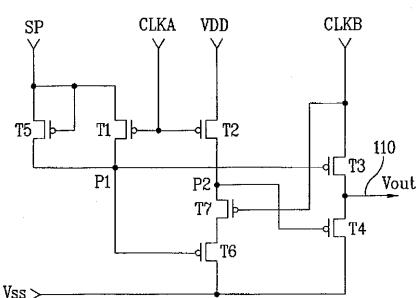

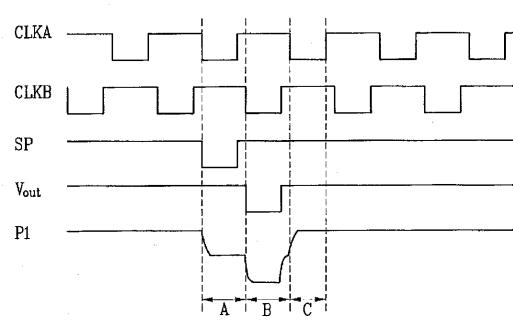

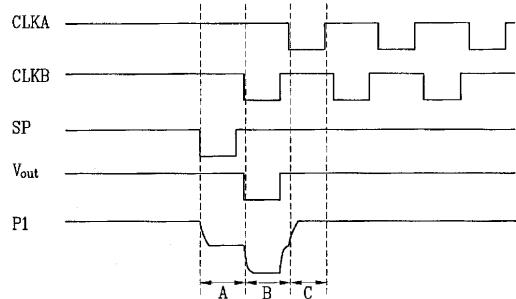

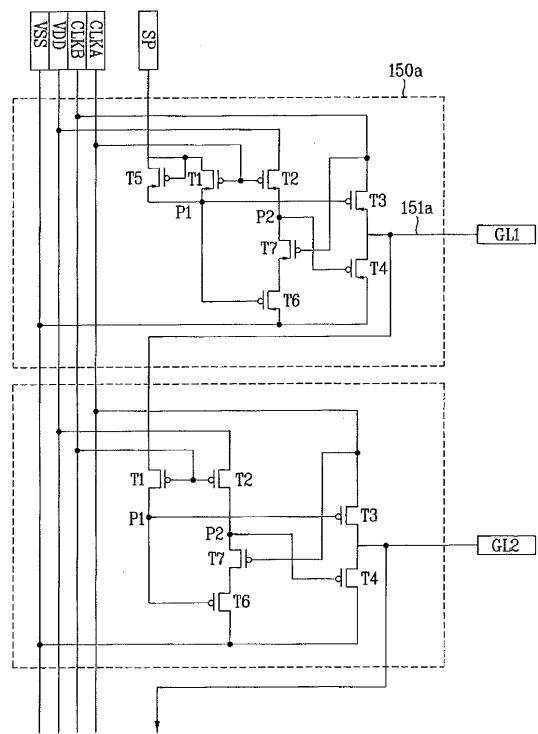

図5は、本発明の実施の形態に係るシフトレジスタのステージの概略的な回路構成図で、図6は、本発明の実施の形態に係るスタートパルスと第1クロック信号が互いに同期していない状態を説明するための各種信号のタイミング図で、図7は本発明の実施の形態に係るスタートパルスのタイミングがずれた状態を説明するための各種信号のタイミング図である。また、図8は本発明の実施の形態に係るシフトレジスタを用いた液晶表示装置の概略的な要部構成図である。

20

【0035】

本発明の実施の形態に係るシフトレジスタは各種クロック信号C L K A、C L K B及び供給電圧V D D、V S Sが印加されて各ゲートラインGを駆動するためのゲート駆動パルスを順次出力する複数のステージを具備している。

【0036】

各ステージは、図5に示したように、第1クロック信号C L K A（または第2クロック信号C L K B）の論理によりターンオンまたはターンオフし、ターンオン時、スタートパルスS P（または以前のステージの出力）を導通させて第1ノードP 1に充電させる第1P M O SトランジスタT 1と、前記第1クロック信号C L K A（または第2クロック信号C L K B）の論理によりターンオンまたはターンオフし、ターンオン時、第1供給電圧V D Dを導通させて第2ノードP 2に充電させる第2P M O SトランジスタT 2と、前記第1ノードP 1の充電状態によりターンオンまたはターンオフし、ターンオン時、第2クロック信号C L K B（または第1クロック信号C L K A）を導通させて出力ライン1 1 0に供給する第3P M O SトランジスタT 3と、前記第2ノードP 2の充電状態によりターンオンまたはターンオフして第2供給電圧V S Sを前記出力ライン1 1 0に供給する第4P M O SトランジスタT 4と、前記スタートパルスS P（または以前のステージの出力）の論理によりターンオンまたはターンオフし、ターンオン時、前記スタートパルスS P（または以前のステージの出力）を前記第1ノードP 1に充電させる第5P M O SトランジスタT 5と、前記第1ノードP 1の充電状態によりターンオンまたはターンオフし、ターンオン時、前記第2供給電圧V S Sを導通させる第6P M O SトランジスタT 6と、前記第2クロック信号C L K B（または第1クロック信号C L K A）の論理によりターンオンまたはターンオフし、ターンオン時、前記第6P M O SトランジスタT 6を経由する第2供給電圧V S Sを前記第2ノードP 2に充電させる第7P M O SトランジスタT 7を具備して構成する。

30

【0037】

ここで、前記第2ノードP 2には前記第1供給電圧V D Dまたは第2供給電圧V S Sを

40

50

充電することができ、前記第2ノードP2にロー論理を有する第1供給電圧VDDが充電された場合、前記第2ノードP2にゲートが連結した第6PMOSトランジスタT6はターンオンし、前記第2ノードP2にハイ論理を有する第2供給電圧VSSが充電された場合、前記第6PMOSトランジスタT6はターンオフする。

【0038】

そして、上述した通り、奇数番目のステージ51a、51c、51e、・・・では前記第1、第2PMOSトランジスタ(T1、T2)のゲート端子に前記第1クロック信号CLKAが印加され、前記第3PMOSトランジスタT3のソース端子に第2クロック信号CLKBが印加される。そして、偶数番目のステージ51b、51d、・・・では前記第1、第2PMOSトランジスタ(T1、T2)のゲート端子に前記第2クロック信号CLKBが印加し、前記第3PMOSトランジスタT3のソース端子に第1クロック信号CLKAが印加する。ここで、前記第5PMOSトランジスタT5のソース及びゲートには共通して前記スタートパルスまたは以前のステージの出力信号が印加される。

10

【0039】

このように前記第5PMOSトランジスタT5と前記第1PMOSトランジスタT1が互いに並列に連結されることにより、前記スタートパルスSPと前記第1クロック信号CLKAが同期しない時、前記スタートパルスSPが出力されないという従来の問題点を解決できる。

【0040】

すなわち、従来技術で前記スタートパルスSPを導通させる第1PMOSトランジスタT1は、第1クロック信号CLKAの論理により制御されるため、前記スタートパルスSPとロー論理の第1クロック信号CLKAが同時に印加されなければならないという制約があったが、本発明のシフトレジスタは前記第1クロック信号CLKAの論理に拘わらず前記スタートパルスSP自体によりターンオンする第5PMOSトランジスタT5をさらに具備しているため、上述したような従来の問題点を解決できる。

20

【0041】

これを上記のように構成した本発明の実施の形態に係るシフトレジスタの動作と連関してさらに具体的に説明すると次の通りである。

【0042】

まず、図5のように構成した本発明のシフトレジスタの回路でスタートパルスと第1クロック信号CLKAが同期して入力された場合を説明すると次の通りである。すなわち、前記本発明のシフトレジスタに供給される各種クロック信号CLKA、CLKB及び供給電圧VDD、VSSとスタートパルスSPが図4に示した従来のタイミング図と同様であると仮定すると次の通りである。

30

【0043】

まず、第1周期(A)間、前記シフトレジスタの動作を説明すると次の通りである。すなわち、図4に示したように、第1周期(A)間にスタートパルスSP及び第1クロック信号CLKAはロー論理状態を維持し、第2クロック信号CLKBはハイ論理状態を維持している。前記ロー論理のスタートパルスSPは前記第5PMOSトランジスタT5のソース及びゲートに印加する。すると、前記第5PMOSトランジスタT5は前記ロー論理のスタートパルスSPによりターンオンし、前記第5PMOSトランジスタT5のソースに印加した前記ロー論理のスタートパルスSPは前記ターンオンした第5PMOSトランジスタT5を経由して第1ノードP1に充電する。

40

【0044】

また、前記第1周期(A)間、ロー論理の第1クロック信号CLKAが第1PMOSトランジスタT1及び第2PMOSトランジスタT2のゲートに同時に印加され、前記第1PMOSトランジスタT1及び第2PMOSトランジスタT2を全てターンオンさせる。したがって、前記ロー論理のスタートパルスSPは前記ターンオンした第1PMOSトランジスタT1を経由して前記第1ノードP1に充電され、前記ロー論理の第1供給電圧VDDは前記ターンオンした第2PMOSトランジスタT2を経由して第2ノードP2に充

50

電される。したがって、従来技術で説明したような動作で各ゲートラインにゲート駆動パルスを印加するようになる。

【0045】

次に、スタートパルスSPとクロック信号が同期しない状態を説明すると次の通りである。図6に示したように、前記第1周期(A)間、ロー論理ではないハイ論理の第1クロック信号CLKAが前記第1PMOSトランジスタT1のゲートに印加されたり、図7に示したように、スタートパルスSPのタイミングとずれたクロック信号が前記第1PMOSトランジスタT1のゲートに印加すると、前記第1PMOSトランジスタT1はターンオフして前記スタートパルスSPを導通させることができなくなる。

【0046】

しかし、前記第5PMOSトランジスタT5は前記第1クロック信号CLKAの論理に影響を受けず、前記スタートパルスSPの論理により、ターンオンしたり、ターンオフするため、前記第1PMOSトランジスタT1がターンオフしても、前記スタートパルスSPは前記スタートパルスSP自体によりターンオンした第5PMOSトランジスタT5を経由して前記第1ノードP1に充電する。したがって、前記ロー論理の第1クロック信号CLKAが必ず前記スタートパルスSPと同期して出力される必要がない。

【0047】

続いて、前記第1ノードP1に充電したロー論理のスタートパルスSPは第3及び第6PMOSトランジスタ(T3、T6)のゲートに印加して前記第3及び第6PMOSトランジスタ(T3、T6)をターンオンさせる。また、前記第2ノードP2に充電したロー論理の第1供給電圧VDDは、第4PMOSトランジスタT4のゲートに印加して前記第4PMOSトランジスタT4をターンオンさせる。

【0048】

したがって、前記出力ライン110には前記ターンオンした第3PMOSトランジスタT3を経由するハイ論理の第2クロック信号CLKB及び前記ターンオンした第4PMOSトランジスタT4を経由するハイ論理の第2供給電圧VSSが同時に供給される。結局、前記出力ライン110にはハイ論理の第2クロック信号CLKBが供給される。一方、前記ハイ論理の第2クロック信号CLKBは第7PMOSトランジスタT7に印加して前記第7PMOSトランジスタT7をターンオフさせる。

【0049】

次に、第2周期(B)間のシフトレジスタの動作を説明すると次の通りである。第2周期(B)間には前記スタートパルスSP及び第1クロック信号CLKAが全てハイ論理状態に変化し、前記第2クロック信号CLKBはロー論理状態に変化する。したがって、前記ハイ論理の第1クロック信号CLKA及びハイ論理のスタートパルスSPにより、前記第1、第2及び第5PMOSトランジスタ(T1、T2、T5)が全てターンオフして、前記第1ノードP1は第1周期(A)間の充電したロー論理のスタートパルスSPをそのまま維持するようになり、前記第1ノードP1のロー論理のスタートパルスSPがゲートを通して印加する第3及び第6PMOSトランジスタ(T3、T6)はターンオン状態を維持するようになる。

【0050】

これに反して、第2周期(B)間、上述したように前記第2クロック信号CLKBがロー論理に変化することにより、前記ロー論理の第2クロック信号CLKBがゲートを通して印加する前記第7PMOSトランジスタT7がターンオンし、これにより前記第2ノードP2には前記ターンオンした第6及び第7PMOSトランジスタ(T6、T7)を経由するハイ論理の第2供給電圧VSSが充電される。したがって、前記第2ノードP2に充電したハイ論理の第2供給電圧VSSにより前記第4PMOSトランジスタT4はターンオフする。結局、前記出力ライン110には、前記ターンオンした第3PMOSトランジスタT3を経由するロー論理の第2クロック信号CLKBが供給される。

【0051】

この時、前記第2周期(B)間、前記第1、第2及び第7PMOSトランジスタ(T1

10

20

30

40

50

、T2、T7)が遮断されて、前記第1ノードP1はフローティング状態になり、前記第3PMOSトランジスタT3のゲートとドレイン間の寄生キャパシターにより、図6に示したように、前記第1ノードP1のスタートパルスSPは前記出力ライン110に供給したロー論理の第2クロック信号CLKB程度さらに離れるようになる。したがって、前記第3PMOSトランジスタT3のゲートにはさらに高い電圧のスタートパルスSPが印加されて前記第3PMOSトランジスタT3の閾値電圧が小さくなり、これにより前記出力ライン110には前記ロー論理の第2クロック信号CLKBが殆ど損失無く供給される。

#### 【0052】

次に、第3周期(C)間シフトレジスタの動作を説明すると次の通りである。第3周期(C)間にはスタートパルスSPがハイ論理状態をそのまま維持し、前記第1クロック信号CLKAはロー論理状態に変化し、前記第2クロック信号CLKBはハイ論理状態に変化する。したがって、前記ハイ論理のスタートパルスSPがゲートを通して印加する前記第5PMOSトランジスタT5はターンオフし、ロー論理の第1クロック信号CLKAがゲートを通して印加する前記第1及び第2PMOSトランジスタ(T1、T2)は再度ターンオンする。

#### 【0053】

すると、前記ハイ論理のスタートパルスSPは前記ターンオンした第1PMOSトランジスタT1を経由して前記第1ノードP1に充電され、ロー論理の第1供給電圧VDDが前記ターンオンした第2PMOSトランジスタT2を経由して前記第2ノードP2に充電される。そして、前記第1ノードP1に充電したハイ論理のスタートパルスSPにより第3及び第6PMOSトランジスタ(T3、T6)がターンオフし、前記第2ノードP2に充電したロー論理の第1供給電圧VDDにより第4PMOSトランジスタT4がターンオンする。したがって、前記出力ライン110には前記ターンオンした第4PMOSトランジスタT4を経由するハイ論理の第2供給電圧VSSが供給される。

#### 【0054】

このように本発明に係るシフトレジスタは上述したように、前記第1クロック信号CLKAの論理に拘わらずスタートパルスSPを出力することができる第5PMOSトランジスタT5をさらに具備し、前記第1クロック信号CLKAとスタートパルスSPが互いに同期しない時の問題点を解決している。図7のように、スタートパルスとクロック信号のタイミングがずれた場合にも、前記第1PMOSトランジスタT1がターンオフしても、前記スタートパルスSPは前記スタートパルスSP自体によりターンオンした第5PMOSトランジスタT5を経由して前記第1ノードP1に充電する。そして、第1ノードP1にロー論理が充電された状態では前記第3PMOSトランジスタのソース端に印加した第2クロック信号CLKBを出力端に出力するため、前記第2クロック信号CLKBのロー論理状態が出力端に出力される。

#### 【0055】

また、このように構成したシフトレジスタを用いた液晶表示装置は、図8に示したように、互いに垂直交差する複数のゲートライン(G1、G2、・・・)及びデータライン(図示せず)により定義される複数の画素領域を有する液晶パネル(図示せず)と、前記液晶パネルの各ゲートライン(G1、G2、・・・)に順にゲート駆動パルスを供給するための複数のステージ(150a、150b、・・・)とで構成される。この時、前記複数のステージ(150a、150b、・・・)が全て前記図5で説明したような構成を有することができ、複数のステージのうち最初の第1ステージ150aのみ前記図5のような構成を有し、残りのステージは従来技術で説明した図3と同様の構成を有することが可能である。

#### 【0056】

すなわち、前記第1ステージ150aにのみスタートパルスSPが印加され、残りの第2乃至第nステージ(150b、・・・)はその前段のステージの出力信号が入力される。そして、前記第1ステージ150aのみ前記第5PMOSトランジスタT5を具備し、第2ステージ150b乃至第nステージ150nは前記第1ステージ150aの出力を入

10

20

30

40

50

力として用いるようになるため、前記第5PMOSトランジスタT5が不要である。すなわち、前記第1ステージ150aのみスタートパルスSPが印加され、残りの第2乃至第nステージ(150b、・・・)は各々その前の段のステージの出力(ゲート駆動パルス)を入力として用いて各その前の段の出力(ゲート駆動パルス)より一周期遅れたゲート駆動パルスを出力する。

#### 【0057】

したがって、前記各ステージ(150a、150b、・・・)から出力する各ゲート駆動パルスは前記液晶パネルの各ゲートライン(G1、G2、・・・)に供給されて各ゲートライン(G1、G2、・・・)を順次スキャニングするようになる。一方、本発明では各スイッチング素子としてPMOSトランジスタを用いたが、前記PMOSトランジスタ代りにNMOSトランジスタを用いても構わない。

10

#### 【0058】

以上で説明した本発明は上述した実施の形態及び添付した図面に限定されるものではなく、本発明の技術的思想を逸脱しない範囲内で様々な置換、変形及び変更が可能であるということが本発明が属する技術分野で通常の知識を有する者にとって明白である。

#### 【図面の簡単な説明】

#### 【0059】

【図1】一般的な液晶表示装置の駆動回路を示したブロック構成図である。

【図2】従来のシフトレジスタの概略的な構成図である。

【図3】図2のステージに対する概略的な回路構成図である。

20

【図4】従来のシフトレジスタに供給される各種信号に対するタイミング図である。

【図5】本発明の実施の形態に係るシフトレジスタのステージの概略的な回路構成図である。

【図6】本発明の実施の形態に係るスタートパルスと第1クロック信号とが互いに同期されない状態を説明するための各種信号のタイミング図である。

【図7】本発明の実施の形態に係るスタートパルスのタイミングがずれた状態を説明するための各種信号のタイミング図である。

【図8】本発明の実施の形態に係るシフトレジスタを用いた液晶表示装置の概略的な要部構成図である。

#### 【符号の説明】

30

#### 【0060】

T1 第1PMOSトランジスタ、T2 第2PMOSトランジスタ、T3 第3PMOSトランジスタ、T4 第4PMOSトランジスタ、T5 第5PMOSトランジスタ、T6 第6PMOSトランジスタ、T7 第7PMOSトランジスタ、SP スタートパルス、CLKA 第1クロック信号、CLKB 第2クロック信号、VDD 第1供給電圧、VSS 第2供給電圧、P1 第1ノード、P2 第2ノード。

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

G 11 C 19/00

(72)発明者 金 性均

大韓民国ソウル冠岳區新林1洞1615-12

審査官 後藤 亮治

(56)参考文献 特開平07-182891 (JP, A)

米国特許第06339631 (US, B1)

特開平10-031202 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

G 02 F 1 / 133

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 移位寄存器和液晶显示器件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP4154611B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2008-09-24 |

| 申请号            | JP2004374584                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2004-12-24 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 金性均                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 金性均                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 G11C19/00 G11C19/28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| CPC分类号         | G09G3/3677 G11C19/00 G11C19/28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/36 G02F1/133.505 G09G3/20.622.E G09G3/20.670.E G11C19/00.G G11C19/00.J G11C19/00 G11C19/00.K G11C19/28.D G11C19/28.230                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NA53 2H093/NC03 2H093/NC10 2H093/NC12 2H093/NC22 2H093 /NC34 2H093/NC35 2H093/NC49 2H093/ND06 2H093/ND37 2H093/ND60 2H193/ZA04 2H193/ZD23 2H193/ZF03 2H193/ZF22 2H193/ZF36 5B074/AA01 5B074/CA01 5B074/DA01 5B074/DB01 5C006 /AA16 5C006/AA22 5C006/AF46 5C006/AF72 5C006/AF83 5C006/BB16 5C006/BC03 5C006/BC12 5C006/BF03 5C006/BF34 5C006/BF43 5C006/BF46 5C006/EB05 5C006/FA16 5C006/FA20 5C080 /AA10 5C080/BB05 5C080/CC03 5C080/DD09 5C080/DD25 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 1020040037724 2004-05-27 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 其他公开文献         | JP2005338758A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

要解决的问题：提供即使提供给第一级的起始脉冲不与时钟信号同步也能输出栅极驱动脉冲的移位寄存器，并提供使用该移位寄存器的液晶显示装置。SOLUTION：在具有多个阶段的移位寄存器中，顺序输出栅极驱动脉冲，至少一个阶段包括：第一开关装置，由第一时钟信号导通，以将起始脉冲施加到第一节点；第二开关装置，其由第一时钟信号导通，以将第一电源电压施加到第二节点；第三开关装置，其通过施加到第一节点的起始脉冲导通，以输出第二时钟信号；第四开关器件，其通过施加到第二节点的第一电源电压导通，以输出第二电源电压；第五开关装置，其通过起始脉冲导通，以将起始脉冲施加到第一节点。Z