(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-114496

(P2007-114496A)

(43) 公開日 平成19年5月10日(2007.5.10)

| (51) Int.C1.                | F 1                                                        | テーマコード (参考) |

|-----------------------------|------------------------------------------------------------|-------------|

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36                                                  | 2 H 09 3    |

| <b>G02F 1/133 (2006.01)</b> | G02F 1/133 5 5 0                                           | 5 C 00 6    |

| <b>G09G 3/20 (2006.01)</b>  | G02F 1/133 5 1 0<br>G09G 3/20 6 2 3 F<br>G09G 3/20 6 4 1 C | 5 C 08 0    |

審査請求 未請求 請求項の数 10 O L (全 21 頁) 最終頁に続く

|           |                              |          |                                                          |

|-----------|------------------------------|----------|----------------------------------------------------------|

| (21) 出願番号 | 特願2005-306003 (P2005-306003) | (71) 出願人 | 502356528<br>株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地            |

| (22) 出願日  | 平成17年10月20日 (2005.10.20)     | (74) 代理人 | 100093506<br>弁理士 小野寺 洋二                                  |

|           |                              | (72) 発明者 | 片山 ゆかり<br>神奈川県川崎市麻生区王禅寺1099番地<br>株式会社日立製作所<br>システム開発研究所内 |

|           |                              | (72) 発明者 | 工藤 泰幸<br>神奈川県川崎市麻生区王禅寺1099番地<br>株式会社日立製作所<br>システム開発研究所内  |

最終頁に続く

## (54) 【発明の名称】表示装置

## (57) 【要約】

【課題】RGB時分割駆動を導入した低温ポリシリコン TFT 液晶パネルを用いた表示装置において、消費電力を低減する。

【解決手段】RGB 3 色の表示画素に供給するRGBデータを時分割して液晶パネルに入力するRGB時分割駆動方式の表示装置において、(1) 1 ライン信号毎にRGB、BGR と液晶パネルにデータを入力し、1 ライン期間の切れ目において、オン状態の選択信号SCを次のライン期間までオン状態のまま保つ。また(2) パーシャル表示において、パーシャル非表示期間は、常に選択信号SA, SB, SCをオフ状態とし、イコライズ信号EQGをオン状態とする。これにより、RGBデータを選択する選択信号SA, SCの動作周波数を大幅に下げることができ、低消費電力化する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

液晶層を介して対向して配置される2枚の基板のうち、一方の基板の内面に対向電極を形成し、他方の基板の内面に互いに交差する複数本の行電極と列電極を形成し、前記行電極と列電極の交差部に3端子のスイッチング素子を形成し、前記スイッチング素子の第1端子は行電極に、第2端子は列電極に、第3端子は液晶層の一方と保持容量に接続され、前記液晶層の他方は対向電極に接続される画素部と、

外部装置から入力される表示データを列電圧に変換すると共に、液晶駆動用の表示同期信号を生成し、前記表示同期信号に従って、1行分の列電圧を時分割して出力する列駆動部と、

前記列駆動部からの時分割された列電圧を分配して列電極へ出力する分配部と、

前記分配部とは反対側の列電極に接続されるイコライズ回路と、

前記スイッチング素子のオン・オフを制御するための行電圧を表示同期信号に従って、行電極へ1行づつ順次出力する行駆動部と、

前記表示同期信号に従って、前記表示同期信号を行駆動部に出力し、対向電圧を対向電極に出力し、選択信号を分配部へ出力する電源部とを備えた表示装置において、

前記外部装置は行単位で表示期間と非表示期間を列駆動部と電源部に設定し、電源部は非表示期間において、分配部へ出力する選択信号をオフ状態とし、イコライズ回路に出力するイコライズ信号をオン状態とすることを特徴とする表示装置

**【請求項 2】**

前記分配部は、選択信号によりオン・オフが制御される複数のスイッチング素子を備え、非表示期間において、選択信号により複数のスイッチング素子をオフ状態とし、

前記イコライズ回路は、イコライズ信号によりオン・オフが制御される複数のスイッチング素子を備え、非表示期間において、イコライズ信号により複数のスイッチング素子をオン状態とすることを特徴とする請求項1に記載の表示装置

**【請求項 3】**

前記イコライズ回路から列電極に与えられる電位は、対向電圧の電位又は列電圧として許容される電位の中で最も対向電圧に近い電位とすることを特徴とする請求項2に記載の表示装置

**【請求項 4】**

液晶層を介して対向して配置される2枚の基板のうち、一方の基板の内面に対向電極を形成し、他方の基板の内面に互いに交差する複数本の行電極と列電極を形成し、前記行電極と列電極の交差部に3端子のスイッチング素子を形成し、前記スイッチング素子の第1端子は行電極に、第2端子は列電極に、第3端子は液晶層の一方と保持容量に接続され、前記液晶層の他方は対向電極に接続される画素部と、

外部装置から入力される表示データを列電圧に変換すると共に、液晶駆動用の表示同期信号を生成し、前記表示同期信号に従って、1行分の列電圧を時分割して出力する列駆動部と、

前記列駆動部からの時分割された列電圧を分配して列電極へ出力する分配部と、

前記スイッチング素子のオン・オフを制御するための行電圧を表示同期信号に従って、行電極へ1行づつ順次出力する行駆動部と、

前記表示同期信号に従って、前記表示同期信号を行駆動部に出力し、対向電圧を対向電極に出力し、選択信号を分配部へ出力する電源部とを備えた表示装置において、

前記電源部から分配部へ出力される選択信号は、任意の行電極で最後に選択された列電極が次の行電極において最初に選択されるまで、そのレベルを変えないことを特徴とする表示装置

**【請求項 5】**

前記選択信号のレベルを変えない場合には、低階調で表示し、変える場合には、多階調で表示すると共に、選択信号の切り替わり時に、分配部のスイッチング素子を1度オフとする選択信号を用いて、多階調表示時と低階調表示時において切り替えることを特徴とす

10

20

30

40

50

る請求項 4 に記載の表示装置

【請求項 6】

液晶層を介して対向して配置される 2 枚の基板のうち、一方の基板の内面に対向電極を形成し、他方の基板の内面に互いに交差する複数本の行電極と列電極を形成し、前記行電極と列電極の交差部に 3 端子のスイッチング素子を形成し、前記スイッチング素子の第 1 端子は行電極に、第 2 端子は列電極に、第 3 端子は液晶層の一方と保持容量に接続され、前記液晶層の他方は対向電極に接続される画素部と、

外部装置から入力される表示データを列電圧に変換すると共に、液晶駆動用の表示同期信号を生成し、前記表示同期信号に従って、1 行分の列電圧を時分割して出力する列駆動部と、

前記列駆動部からの時分割された列電圧を分配して列電極へ出力する分配部と、

前記スイッチング素子のオン・オフを制御するための行電圧を表示同期信号に従って、行電極へ 1 行づつ順次出力する行駆動部と、

前記表示同期信号に従って、前記表示同期信号を行駆動部に出力し、対向電圧を対向電極に出力し、選択信号を分配部へ出力する電源部とを備えた表示装置において、

前記表示データが複数行毎に切り替えられ、

前記電源部から分配部へ出力される選択信号は、任意の行電極で最後に選択された列電極が次の行電極において最初に選択されるまで、そのレベルを変えないことを特徴とする表示装置

【請求項 7】

複数の行電極と、前記複数の行電極と交差する複数の列電極と、前記交差する部分に配置された表示素子と、前記列電極を複数に分割した分割単位で列電極を選択する分配部とを備えた表示装置において、

前記分配部は、複数の選択信号に従って、分割単位でそれぞれの列電極を順次選択し、

前記選択信号は、任意の行電極で最後に選択された列電極が次の行電極において最初に選択されるまで、そのレベルを変えないことを特徴とする表示装置

【請求項 8】

前記選択信号を、パーシャル表示での非表示期間において、オフ状態とすることを特徴とする請求項 7 に記載の表示装置

【請求項 9】

互いに交差する複数本の行電極と列電極を形成し、前記行電極と列電極の交差部に対応して形成された画素部と、

外部装置から入力される表示データを列電圧に変換すると共に、駆動用の表示同期信号を生成し、前記表示同期信号に従って、1 行分の列電圧を時分割して出力する列駆動部と、

前記列駆動部からの時分割された列電圧を分配して列電極へ出力する分配部と、

前記分配部とは反対側の列電極に接続されるイコライズ回路と、

前記スイッチング素子のオン・オフを制御するための行電圧を表示同期信号に従って、行電極へ 1 行づつ順次出力する行駆動部と、

前記表示同期信号に従って、前記表示同期信号を行駆動部に出力し、対向電圧を対向電極に出力し、選択信号を分配部へ出力する電源部とを備えた表示装置において、

前記外部装置は行単位で表示期間と非表示期間を列駆動部と電源部に設定し、電源部は非表示期間において、分配部へ出力する選択信号をオフ状態とし、イコライズ回路に出力するイコライズ信号をオン状態とすることを特徴とする表示装置

【請求項 10】

互いに交差する複数本の行電極と列電極を形成し、前記行電極と列電極の交差部に対応して形成された画素部と、

外部装置から入力される表示データを列電圧に変換すると共に、駆動用の表示同期信号を生成し、前記表示同期信号に従って、1 行分の列電圧を時分割して出力する列駆動部と、

10

20

30

40

50

前記列駆動部からの時分割された列電圧を分配して列電極へ出力する分配部と、前記スイッチング素子のオン・オフを制御するための行電圧を表示同期信号に従って、行電極へ1行づつ順次出力する行駆動部と、

前記表示同期信号に従って、前記表示同期信号を行駆動部に出力し、対向電圧を対向電極に出力し、選択信号を分配部へ出力する電源部とを備えた表示装置において、

前記電源部から分配部へ出力される選択信号は、任意の行電極で最後に選択された列電極が次の行電極において最初に選択されるまで、そのレベルを変えないことを特徴とする表示装置

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、低消費電力の表示装置に係り、特に、液晶素子、EL素子、プラズマを用いた表示装置に関する。

【背景技術】

【0002】

携帯電話などで用いられる小型液晶ディスプレイは、消費電力を小さく抑えることが重要である。そこで、下記特許文献1に示されるように、待ち受け時には、液晶ディスプレイの一部分のみを表示し、他の部分を非表示とすることにより、低消費電力化を図る方式が提案されていた。このようなディスプレイの一部のみを表示状態とする方式を、以下パーシャル表示という。この特許文献1では、非表示部分の走査を数フレームに分けて行うことで1フレーム当たりの駆動周波数を下げ、低消費電力化していた。

【0003】

一方、現在携帯電話などで用いられる小型液晶ディスプレイは、TFT (Thin Film Transistor) を用いているものが一般的である。従来、TFT材料としては、アモルファスシリコンを用いていた。このアモルファスシリコンは、安価に製造できるメリットがあるが、電子移動度が遅いため、液晶駆動回路は外付けのLSIで対応していた。近年、電子移動度の大きい低温ポリシリコン (LTPS (Low Temperature Poly Silicon)) が開発され、駆動回路などを液晶パネルに取り込めるようになってきた。そこで、下記特許文献2に示すように、走査線駆動回路を液晶パネル内に取り込むことにより、部品点数を下げコストを低減する方式が提案されている。

【0004】

また、下記特許文献3に示すように、液晶パネルにRGB (Red, Green, Blue) 3色の液晶素子に与える信号を時分割して入力し、配線数を下げるによりコストを下げる方式が提案されている。この方式を、以下RGB時分割駆動という。

【0005】

しかし、このRGB時分割駆動を導入することにより、液晶パネル内で1本の信号線からRGBそれぞれの液晶素子に接続された信号線に信号を分配するRGB分配スイッチが必要となる。このRGB分配スイッチは、水平周期で操作されるため、消費電力が大きい。そのため、消費電力を低減するためのパーシャル表示であっても、RGB時分割駆動を採用したLTPS-TFT液晶パネルの方が、RGB時分割駆動を採用しないアモルファスシリコンTFT液晶パネルよりも消費電力が大きくなるという問題があった。

【0006】

それを解決するために、下記特許文献4に示すように、パーシャル表示において、非表示部分への信号入力時には、全てのRGB分配スイッチをオン状態とし、RGB分配スイッチへの制御信号の変動をなくすことにより、消費電力を低減する技術が提案されている。

【0007】

また、RGB時分割駆動を導入することにより、各信号線からリークする電荷量が不均一になり、フリッカを発生するなどの問題が発生していた。この問題を解決するために、下記特許文献5に示されるように、各信号線への表示信号電圧の印加順序を1水平期間毎

10

20

30

40

50

に反転するように制御する技術が提案されている。

#### 【0008】

また、下記特許文献6に示されるように、ドレイン信号線の電圧書き込み効率の向上と、ドライバ出力負荷軽減による消費電力を低減するために、イコライズ回路を設ける方式が提案されている。

【特許文献1】特開2003-57277号公報

【特許文献2】特開2002-215118号公報

【特許文献3】特開2003-255904号公報

【特許文献4】特開2003-029715号公報

【特許文献5】特開2005-195703号公報

【特許文献6】特開2003-222891号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

上記特許文献4の技術においては、信号線を駆動するアンプの消費電力の低減については考慮されておらず、消費電力があまり低減できないという問題があった。また、上記特許文献5の技術においては、低消費電力化に関しては考慮されておらず、消費電力があまり低減できないという問題があった。

#### 【0010】

本発明は上記問題点を解決するために、RGB時分割駆動を導入したLTPS-TFT液晶パネルを用いた表示装置において、消費電力を低減することを課題とする。

#### 【課題を解決するための手段】

#### 【0011】

上記課題を解決するために本発明は、RGB分配スイッチを選択するRGB選択信号の順番を1水平期間毎に、例えば、RGBからBGRに入れ替え、さらに、1水平期間の切れ目において、最後に選択される、例えば、B選択信号を選択状態のまま保ち、B選択信号の周波数を下げることにより、消費電力を低減するものである。

#### 【0012】

さらに、上記課題を解決するために本発明は、パーシャル表示において、非表示部分の信号入力時には、全てのRGB分配スイッチをオフ状態とし、イコライズ回路をオン状態として、ドレイン信号線への電圧書き込みを行い、このドレイン信号線を駆動するアンプの電源を切断することにより、低消費電力化を行うものである。

#### 【発明の効果】

#### 【0013】

以上説明したように、RGB分配スイッチへの選択信号の周波数を低下させることにより、LTPS-TFT液晶パネルを用いた表示装置の場合であっても、その表示装置の消費電力を低減することができる。

#### 【0014】

また、本発明は、液晶パネルに入力するRGB選択信号の入力の順番を変更するだけで実施できるので、パーシャル表示において、液晶パネルでの表示部分と非表示部分の位置及び範囲を自由に変更できるという効果がある。

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、図面を用いて、本発明の実施例を説明する。

#### 【実施例1】

#### 【0016】

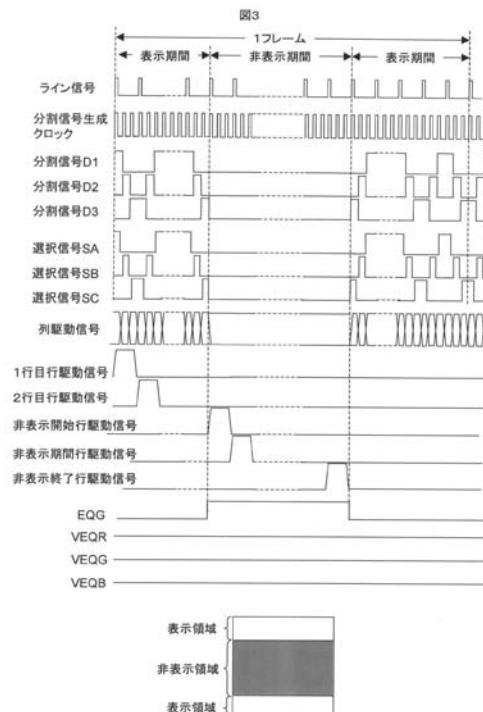

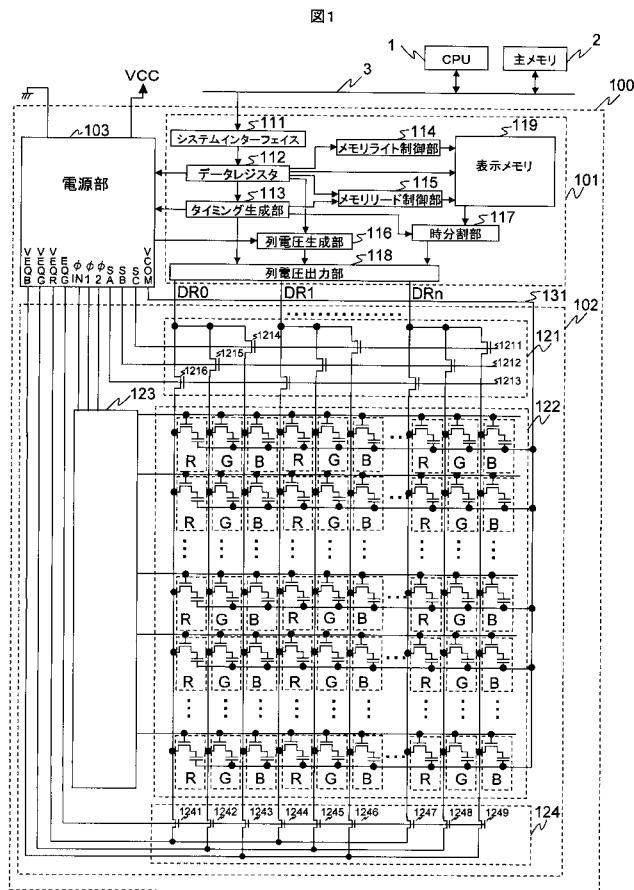

以下、本発明の実施例1について説明する。図1は、本実施例の表示装置のブロック図であって、100は表示装置、101は列駆動部、102はパネル部、103は電源部である。

#### 【0017】

10

20

30

40

50

図1に示す列駆動部101において、111はシステムインターフェイス、112はデータレジスタ、113はタイミング生成部、114はメモリライト制御部、115はメモリリード制御部、116は列電圧生成部、117は時分割部、118は列電圧出力部、119は表示メモリである。

【0018】

また、図1に示すパネル102において、121は分配部、122は画素部、123は行駆動部、124はイコライズ回路であり、これらは、例えば、低温ポリシリコンTFT素子で、ガラス基板上に一体形成されているものとする。

【0019】

このパネル102内の分配部121において、1214, 1215, 1216はTFT素子であり、また、イコライズ回路124において、1241~1249はTFT素子である。

【0020】

また、パネル102内の画素部122には、複数本の行電極と列電極との交差部に3端子のスイッチング素子が形成され、このスイッチング素子の第1端子は行電極に、第2端子は列電極に、第3端子は液晶層の一方と図示しない保持容量に接続され、液晶層の他方は対向電極131に接続される。

【0021】

なお、画素部122で駆動される表示素子は、例えば、TN型の液晶であり、所定の電圧レベルを印加することで、表示を行うものとする。また、表示装置に入力する表示データは、R(赤)G(緑)B(青)各8ビットのデジタルデータとする。ただし、各色のビット数はこれに限定されない。

【0022】

また、列駆動部101、電源部103は1チップのLSIで構成してもよく、実際1チップのLSIで構成される場合が多い。

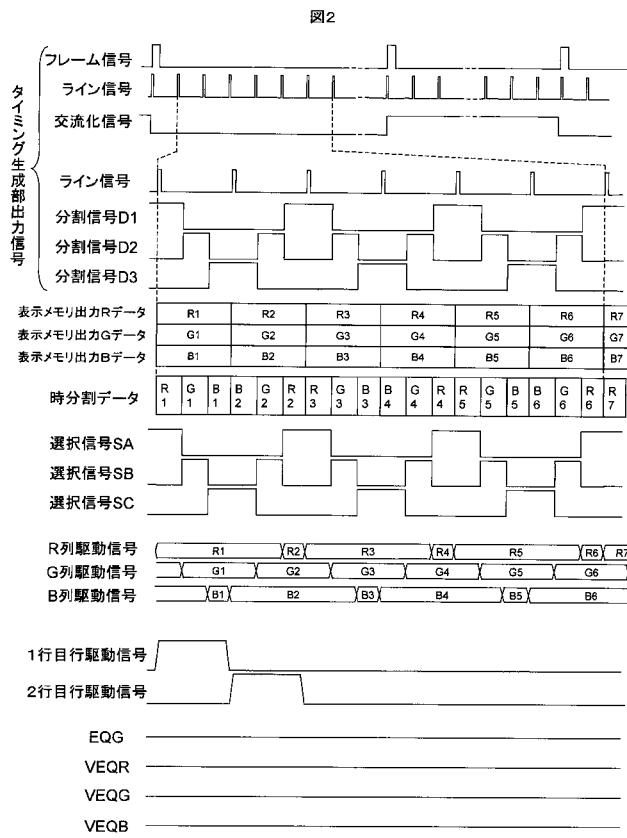

【0023】

図1において、通常表示時の動作について、図2を用いて説明する。まず、列駆動部101の動作について説明する。

【0024】

列駆動部101へは、外部装置のCPU1から表示装置の動作を制御する制御データがシステムバス3を介して与えられる。この制御データには、表示データとその表示位置、駆動ライン数、フレーム周波数などに関するデータが含まれている。

【0025】

システムインターフェイス111は、制御データをデータレジスタ112内のCPU1によって指定されたアドレスに書き込む。そして、データレジスタ112に格納された各種制御データは、各ブロックへ出力される。例えば、表示データは表示メモリ119へ、表示位置データはメモリライト制御部114へ、駆動ライン数、フレーム周波数などに関するデータはタイミング生成部113へ出力される。

【0026】

メモリライト制御部114は、表示位置データをデコードし、これに相当する表示メモリ119内のビット線とワード線を選択する。これと同時にデータレジスタ112から表示データを表示メモリ119へ出力し、書き込み動作を完了する。

【0027】

タイミング制御部113は、データレジスタ112から与えられる駆動情報に基づき、図2に示すタイミング信号群を自ら生成し、メモリリード制御部115、時分割部117、列電圧出力部118へ出力する。

【0028】

メモリリード制御部115は、タイミング制御部113が出力する信号をデコードし、該当する表示メモリ119内のワード線を選択する。この動作は、例えば、画面の先頭行の表示データが格納されているワード線から順に1行ずつ選択し、最終行の次は、再び先

10

20

30

40

50

頭行に戻ってこの動作を繰り返す。そして、ワード線の選択動作と同時に表示メモリ 119 のデータ線から 1 行分の表示データが順次一括して出力される。ここで、ワード線の切り替えタイミングは、タイミング生成部 113 から与えられるライン信号に同期し、先頭行のワード線を選択するタイミングは、タイミング生成部 113 から与えられるフレーム信号に同期するものとする。

#### 【0029】

時分割部 117 は、表示メモリ 119 から与えられる 1 行分の表示データを時分割（マルチブレクサ）する。この動作はタイミング生成部 113 から与えられた図 2 に示す分割信号 D1 ~ D3 を用いてライン信号の周期を 3 分割し、表示メモリ 119 から出力された表示データを、R データ、G データ、B データとして出力する。この時、R データ、G データ、B データの順番は、図 2 に示す時分割データのように、1 ラインごとに入れ替わる。すなわち、あるラインで R G B の順番に出力したら、次のラインでは B G R の順番で出力する。さらに、次のラインでは R G B の順番となり、1 ラインごとに入れ替わる。

#### 【0030】

列電圧生成部 116 は、時分割データを電圧レベルへ変換する際に必要な列電圧を生成するブロックである。このブロックでは、表示データである各デジタルデータに対応する電圧が生成される。例えば、表示データは本実施例においては 8 ビットで表されているので、256 種類のデータとなる。このブロックでは基準電圧を抵抗分圧し、V0 から V255 の 256 種類の電圧を作り出す。ここで、V0 はデータ 0 に対応する電圧であり、V255 はデータ 255 に対応する電圧である。

#### 【0031】

列電圧出力部 118 は、タイミング生成部 113 から与えられる交流化信号および時分割データに応じ 256 種類の列電圧から 1 レベルを選択し、内蔵するアンプにてドライブ能力を増強して出力するブロックである。これらアンプは列駆動信号 DR0 ~ DRm 毎に設けられており、定常的に直流電流を流さなくてはならないため、非常に消費電力が大きい。

#### 【0032】

次に、パネル部 102 の動作について説明する。まず、画素部 122 は、3 端子の TFT 素子、液晶層、保持容量から構成され、3 端子の TFT 素子のドレイン端子は列電極、ゲート端子は行電極、ソース端子は液晶層と図示しない保持容量に接続される。また、液晶層の対向側には共通の対向電極があり、液晶層と電気的に接続されている。さらに、保持容量の他方の端子は、図示しないストレージ線と呼ばれる電極に接続されている。この構成を実現するため、例えば、列電極、行電極、ストレージ線は、液晶層を保持する 2 枚の透明基板のうち、一方の透明基板の内面にマトリクス上に形成され、対向電極は他方の透明基板の内面に形成される。なお、この画素の回路構成はいわゆる Cst 構造と呼ばれる構成であるが、保持容量の他方の端子を前段の行電極に接続する、いわゆる Cad d 構造と呼ばれる構成へも適用可能である。

#### 【0033】

分配部 121 は、列駆動部 101 から与えられる列電圧を分配（デマルチブレクサ）し、画素部 122 の列電極へ出力するブロックであり、TFT 素子 1214, 1215, 1216 のスイッチを用いた回路構成で実現可能である。その動作は、図 2 に示す選択信号 SA, SB, SC が、分配制御線 1211, 1212, 1213 に供給され、選択信号が“ハイ”的状態でスイッチがオンとなり、列電極へ列電圧が印加される。なお、選択信号 SA ~ SC は後述する電源部 503 から与えられる。本実施例の分配部は、スイッチとして 1 つの TFT 素子を用いたスイッチ回路で説明するが、スイッチ回路は電圧レベルを伝達できるスイッチであれば、CMOS など 2 つ以上の MOS の組み合わせによるスイッチであっても、また他のどのような構成のスイッチであっても良く、限定されない。

#### 【0034】

行駆動部 123 は、列駆動部 101 内のタイミング生成部 113 から転送されたフレーム信号に同期して、先頭の行電極に“ハイ”的行電圧を印加し、その後、同じく転送され

10

20

30

40

50

たライン信号に同期して、順次“ハイ”の行電圧を次段の行電極へ印加する。なお、行駆動部123の動作は、シフトレジスタ回路を応用することで、容易に実現可能である。

【0035】

イコライズ回路124は、TFT素子1241～1249で構成され、電源部103から与えられるイコライズ信号（以下「EQG信号」という。）が“ハイ”的ときに、R色の液晶素子に接続されている列電極にVEQR信号を供給し、G色の液晶素子に接続されている列電極にVEQG信号を供給し、B色の液晶素子に接続されている列電極にVEQB信号を供給する。本実施例では、通常表示時、EQG信号は、常に“ロー”に保たれ、列電極は、VEQR、VEQG、VEQB信号とは遮断されている。

【0036】

次に電源部103の動作について説明する。電源部103は、対向電極131への印加電圧である対向電圧VCOM、図示しないストレージ線への印加電圧であるストレージ電圧、行駆動部123の入力クロックである1、2、行駆動部123のシフトレジスタスタート信号IN、選択信号SA～SC、EQG信号、VEQR、VEQG、VEQB信号を生成する。

【0037】

まず、対向電圧VCOMの生成においては、タイミング生成部113から転送される交流信号を液晶駆動に必要なレベルに変換して出力する。対向電圧VCOMの振幅は、一般的に、列電圧の振幅よりも大きくなるように変換される。なお、液晶印加電圧の極性は、対向電圧からみた列電圧の極性であることから、交流信号に連動して液晶印加電圧の極性が反転する。図2に示す交流化信号はフレーム反転駆動に相当するが、交流周期はこれに限定されない。

【0038】

なお、ストレージ電圧については、対向電圧と同様、タイミング生成部113から転送される交流化信号を対向電圧と同じレベルに変換して出力する。対向電極は液晶素子と直接接続され、平面状に広く配線されているので、非常にノイズが載りやすいが、ストレージ線は行毎に配線を分け、大きな保持容量に接続されているため、安定している。ストレージ線は液晶の表示を安定する機能を担う。

【0039】

次に、行駆動部123の入力クロックである1、2は、タイミング生成部113から転送されるライン信号で反転する2相クロックである。この2相クロックの“ハイ”レベルはゲート信号の“ハイ”レベルに等しく、“ロー”レベルはゲート信号の“ロー”レベルに等しい。また、シフトレジスタスタート信号INは、タイミング生成部113から転送されるフレーム信号に同期し、2相クロック1、2の1周期分だけ“ハイ”となる信号である。

【0040】

選択信号SA～SCについては、タイミング生成部113からの図2に示す分割信号D1～D3をもとに生成する。この選択信号SA～SCの“ハイ”は、分配部121のTFT素子1214, 1215, 1216がオン、“ロー”はオフとなるような電圧レベルとする。選択信号SA～SCは、図2に示す波形であるので、1行目（ある行）において、RGBの順で列電圧が印加されたら、2行目（その次の行）においては、BGRの順で列電圧が印加される。すなわち、ある行において最後に選択された列は、次の行において最初に選択される。また、行の切れ目において“ハイ”であった選択信号は“ハイ”的であり、次の行で最初の列選択が終了するまで“ハイ”的である。

【0041】

このようにRGB、BGR、RGBの順で動作することにより、通常動作時、選択信号SA, SCの動作周波数は、RGB、BGR、RGBの順で動作する場合に比べ2分の1となる。したがって、全体では、選択信号の周波数を2/3とすることができる、分配部121のTFT素子による充放電電力を2/3に削減することができる。

【0042】

10

20

30

40

50

なお、電源部 103 は、このような動作の他に本発明の表示装置に必要な電源電圧を生成し、各ブロックへ出力する。例えば、外部から与えられる電源電圧を昇圧する手段、昇圧された電圧を調整する手段により、実現可能である。また、電圧調整の制御情報は列駆動部 101 内のデータレジスタ 112 から転送されるものとする。

【0043】

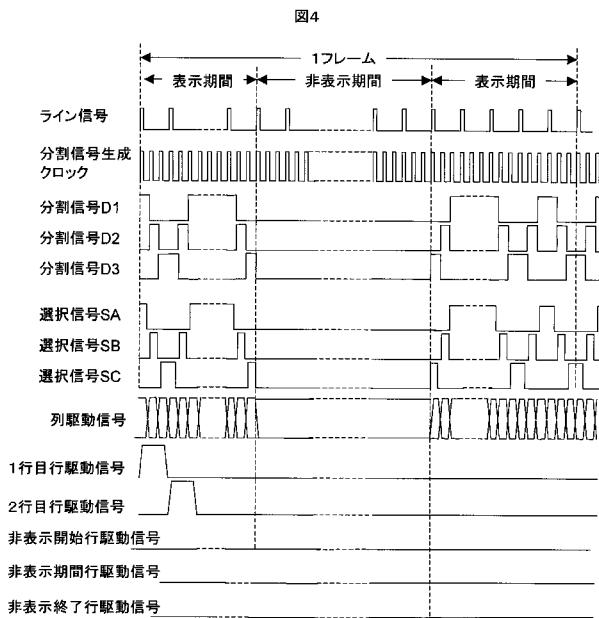

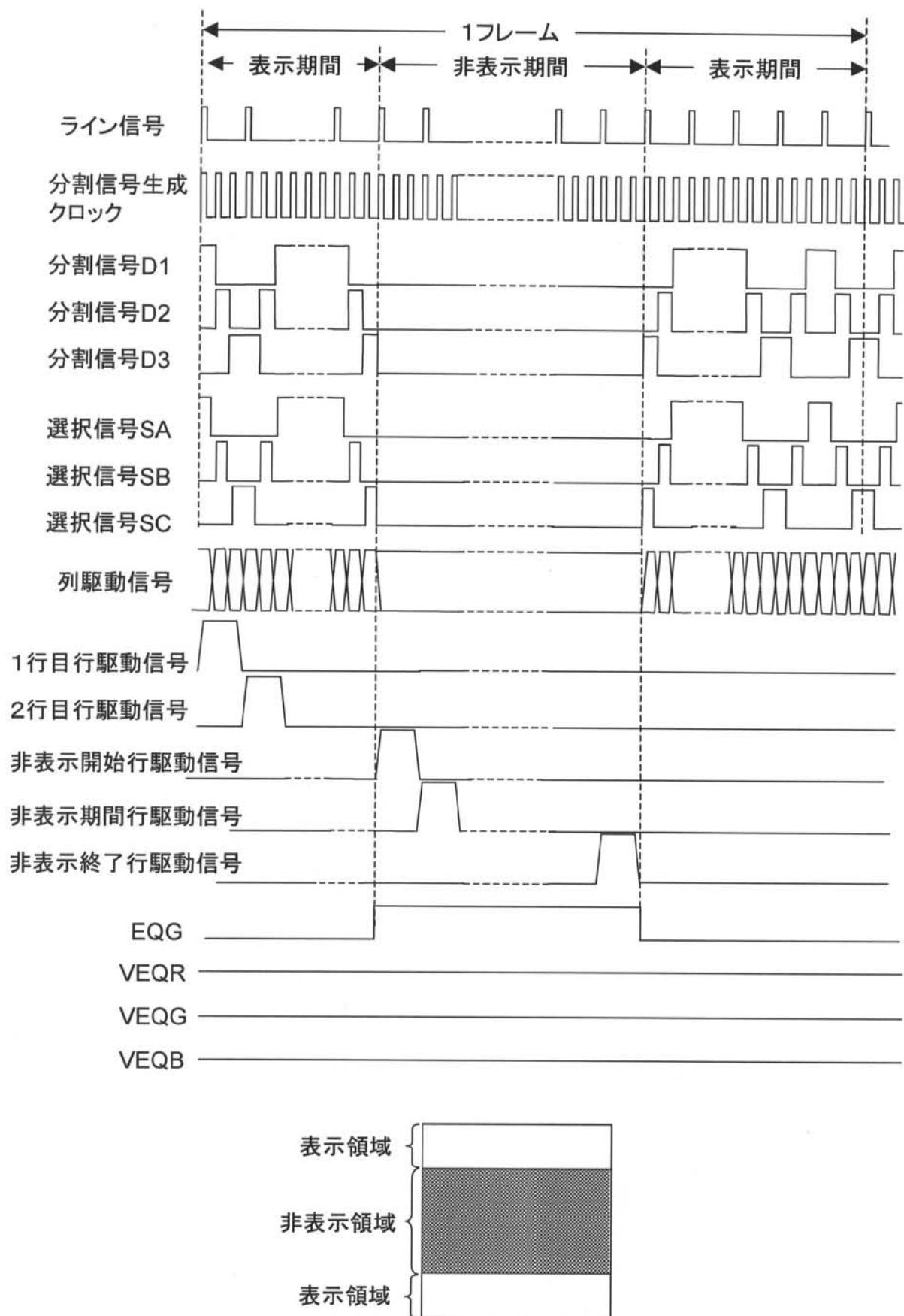

次に、待ち受け画面、すなわち、パーシャル表示における本実施例の動作について、図 3 及び図 4 を用いて説明する。パーシャル表示とは、表示装置の一部を非表示状態とし、消費電力を抑える方式である。本実施例では、図 3 下側に示すように縦方向に表示画面を 3 分割し、中央部分を非表示領域、上下の部分を表示領域とする。本実施例の表示装置は、図 3 に示す動作を最初のフレームで 1 回、図 4 に示す動作を次のフレーム以降で  $n - 1$  回と、これらの動作を繰り返す。

【0044】

まず、CPU1 は、システムインターフェイス 111 を介してデータレジスタ 112 に内蔵される非表示開始アドレスレジスタ、非表示終了アドレスレジスタに、非表示領域開始行番号と非表示領域終了行番号を書き込んだ後、データレジスタ 112 に内蔵される表示開始レジスタを開始状態にセットする。表示開始レジスタが開始状態にセットされると、タイミング生成部 113 は内蔵するカウンタのカウントを開始する。カウンタは、フレーム信号でリセットされ、ライン信号が“ハイ”となるたびに 1 ブツカウントアップする。カウンタの値がパーシャル非表示開始アドレスレジスタの設定値よりも低い時は通常動作を行う。

【0045】

タイミング生成部 113 が内蔵するカウンタの値が非表示開始アドレスレジスタと同じになったら、最初の 1 フレーム目では、タイミング生成部 113 は、分割信号 D1, D2、D3 を“ロー”とする。それと同時に、列電圧出力部 118 内のアンプの電源を切り、アンプへの定常電流が流れないようにする。また、イコライズ回路 124 へのイコライズ信号 EQG を“ハイ”とし、VEQR, VEQG, VEQB 信号は対向電極の電位レベル又は“0”に相当する列電圧に固定する。このようにすることにより、充放電電力は最も低くなり、また、消費電力を最も低く抑えることが可能となる。アンプの個数は、QVG A サイズのパネルで 240 個、VGA サイズのパネルで 480 個であるので、これらアンプの定常電流が削減される。また、VEQR, VEQG, VEQB 信号を駆動する電源部 103 の 3 個のアンプのみを動作状態にするので、消費電力を大きく削減できる。

【0046】

この時、行駆動信号は図 3 に示すように、各行に出力される。これにより、非表示部分に“黒”などの消費電力の低い電圧に対応する色が書き込まれる。ここで、書き込まれる色が何色になるかは液晶の方式によって異なり、特に限定しない。

【0047】

タイミング生成部 113 が内蔵するカウンタの値がパーシャル非表示終了アドレスレジスタと同じになったら、タイミング生成部 113 は、列電圧出力部 118 内のアンプの電源を入れ通常動作準備を行う。また、イコライズ回路 124 の入力信号 EQG を“ロー”とし、分割信号 D1, D2、D3 を通常動作の波形に戻す。

【0048】

次に、2 フレーム目から  $n$  フレーム目までの動作を説明する。タイミング生成部 113 が内蔵するカウンタは、フレーム信号でリセットされ、ライン信号が“ハイ”となるたびに 1 ブツカウントアップする。カウンタの値がパーシャル非表示開始アドレスレジスタの設定値よりも低い時は通常動作を行う。

【0049】

タイミング生成部 113 が内蔵するカウンタの値が非表示開始アドレスレジスタと同じになったら、タイミング生成部 113 は、分割信号 D1, D2、D3 を“ロー”とする。それと同時に、列電圧出力部 118 内のアンプの電源を切り、アンプへの定常電流が流れないようにする。また、イコライズ回路 124 へのイコライズ信号 EQG を“ハイ”とし

、 V E Q R , V E Q G , V E Q B 信号は対向電極の電位レベル又は“ 0 ”に相当する列電圧に固定する。このようにすることにより、充放電電力は最も低くなり、消費電力を最も低く抑えることが可能となる。また、この時、行駆動信号は図 4 に示すように、非表示期間中は各行に出力されない。このようにすることにより、行駆動信号の充放電電力を大幅に削減できる。また、非表示期間中は同じ色が書かれるだけであるので、このように数フレームに 1 回の書き込みでも表示には問題ない。

#### 【 0 0 5 0 】

このように動作することによりパーシャル表示の表示部分においては、選択信号 S A , S C の動作周波数は、 R G B R G B と繰り返す場合に比べ 2 分の 1 となる。したがって、全体では、選択信号の周波数を 2 / 3 とすることができる、分配部 121 の T F T 素子による充放電電力を 2 / 3 に削減することができる。また、パーシャル表示の非表示部分においては、選択信号 S A 、 S B 、 S C の動作周波数は“ 0 ”となる。このように、周波数を著しく落とすことができ、また、非表示部分においては、多くのアンプの電源を切り、またイコライズ回路を用いて列電極を対向電極の電位レベル又は“ 0 ”に相当する列電圧に固定することにより、消費電力を大幅に抑えることができる。

10

#### 【 実施例 2 】

#### 【 0 0 5 1 】

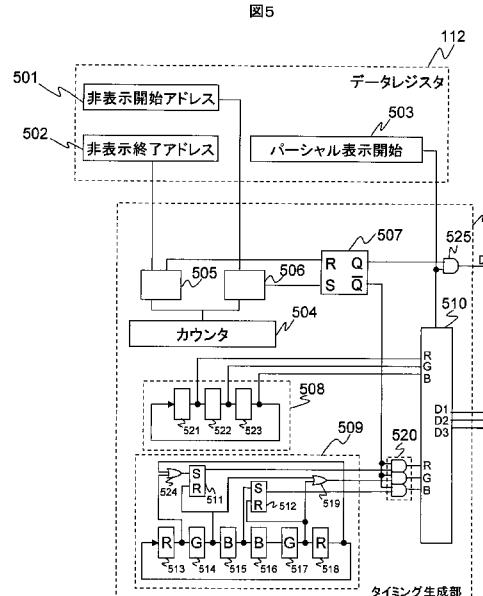

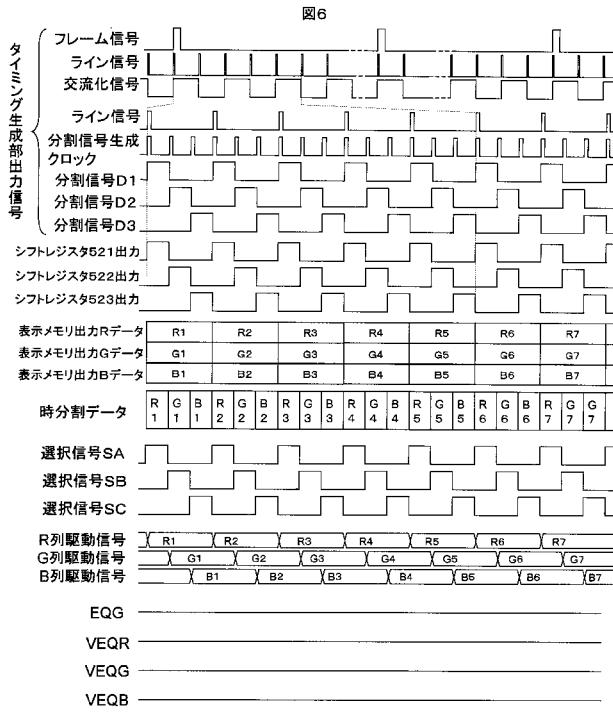

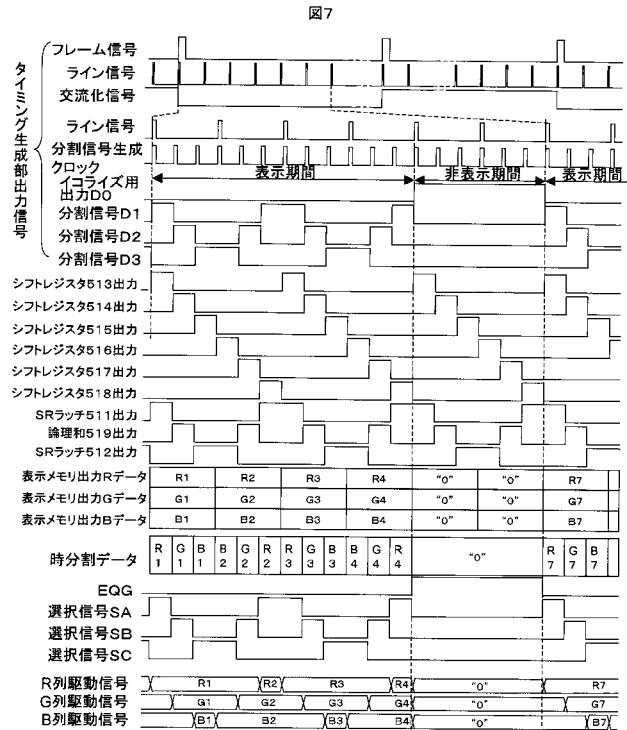

次に、本発明の実施例 2 について、図 1 、図 5 、図 6 、図 7 を用いて説明する。本実施例においては、通常動作時には、図 6 に示すように時分割データの順番が R G B 、 R G B と一定である点で、実施例 1 と異なる。また、通常動作時には、図 6 に示すように対向電極の電位レベルが 1 ライン毎に逆相となるライン反転であり、パーシャル表示時には、図 7 に示すようにフレーム毎に逆相となるフレーム反転である点で、実施例 1 と異なる。

20

#### 【 0 0 5 2 】

図 1 は、実施例 1 でも用いたが、本実施例においても適用できるブロック図であり、各回路は以後特に断らない限り、実施例 1 と同じ機能を持ち、同じ動作を行う。

#### 【 0 0 5 3 】

図 5 は、本実施例のデータレジスタ 112 、タイミング生成部 113 の一部を詳細に示したブロック図である。501 はパーシャル表示時の非表示領域開始行番号を格納する非表示開始アドレスレジスタ、502 はパーシャル表示時の非表示領域終了行番号を格納する非表示終了アドレスレジスタ、503 はパーシャル表示開始状態を示すパーシャル表示開始レジスタ、504 はカウンタ、505 , 506 は比較器、507 , 511 , 512 は S R ラッチ、508 は通常表示時用分割信号生成シフトレジスタ、509 はパーシャル表示時用分割信号生成シフトレジスタ、510 は選択器、513 ~ 518 、521 ~ 523 は 1 ビットシフトレジスタ、519 , 524 は論理和回路、520 、525 は論理積回路である。

30

#### 【 0 0 5 4 】

図 5 において、通常表示時には、パーシャル表示開始レジスタ 503 は“ 0 ”であり、選択器 510 は、通常表示時用分割信号生成シフトレジスタ 508 の出力を選択して分割信号 D 1 , D 2 , D 3 に出力する。通常表示時用分割信号生成シフトレジスタ 508 は、フレーム信号により、左端の 1 ビットシフトレジスタ 521 のみが“ ハイ ” 、中央と右端の 1 ビットシフトレジスタ 522 と 523 が“ ロー ” にセットされ、ライン信号の 1 周期を 3 等分した周期を持つ分割信号生成クロックにより、シフト動作を行う。その結果として、図 6 に示す分割信号 D 1 , D 2 , D 3 が生成される。

40

#### 【 0 0 5 5 】

この分割信号 D 1 , D 2 , D 3 をもとに、図 6 に示す選択信号 S A , S B 、 S C が、電源部 103 にて生成される。選択信号 S A , S B 、 S C は分割信号 D 1 , D 2 , D 3 より、“ ハイ ” の期間が短くなるように作られる。そして、選択信号 S A , S B 、 S C が“ ロー ” となることによって、 R 列駆動信号、 G 列駆動信号、 B 列駆動信号が確定し、その後に、行駆動信号が“ ロー ” となるので、 R , G , B の 3 色ともに液晶素子への印加電圧は同じ条件で書き込まれることとなり、 R , G , B それぞれ 256 階調づつの多階調表示の

50

場合でも、R, G, Bによる色の偏りがなくなり、美しい表示ができる。

【0056】

通常表示時は、パーシャル表示開始レジスタ503は“0”であり、論理積回路525のイコライズ用出力D0は“ロー”となる。この出力D0をもとにEQG信号が作られ、通常表示時は、常に“ロー”に保たれる。したがって、列電極は、VEQR、VEQG、VEQB信号と切断されている。

【0057】

次に、パーシャル表示の時には、R, G, Bそれぞれ2階調で2色づつの8色表示とし、列電圧生成部116に内蔵されている中間調(V1~V254)の電圧生成のための回路に供給する電源を切ることにより、消費電力を削減しているものとする。このパーシャル表示の時に表示部をR, G, B2色づつの8色表示とすることを、以下8色パーシャル表示という。

【0058】

この8色パーシャル表示の動作について、図5及び図7を用いて説明する。このパーシャル表示は、図3下側に示すように縦方向に3つのブロックに区切られるものとし、中央のブロックを非表示領域、上下のブロックを表示領域とするものとする。

【0059】

図5において、8色パーシャル表示時は、パーシャル表示開始レジスタは“1”であり、選択器510はパーシャル表示時用分割信号生成シフトレジスタ509の出力を選択して分割信号D1, D2, D3として出力する。また、論理積回路525はSRラッチ507の出力をイコライズ用出力D0として出力する。

【0060】

パーシャル表示時用分割信号生成シフトレジスタ509は、フレーム信号により、左端の1ビットシフトレジスタ513のみが“ハイ”、514~518は“ロー”にセットされ、ライン信号の周期を3等分した周期で生成される分割信号生成クロックにより、シフト動作を行う。SRラッチ511は、1ビットシフトレジスタ513又は518が“ハイ”的ときに“ハイ”にセットされ、1ビットシフトレジスタ514が“ハイ”的ときに“ロー”にリセットされるSRラッチである。SRラッチ512は、1ビットシフトレジスタ515が“ハイ”的ときに“ハイ”にセットされ、1ビットシフトレジスタ517が“ハイ”的ときに“ロー”にリセットされるSRラッチである。

【0061】

カウンタ504は、フレーム信号で1にセットされ、ライン信号が入力されると1づつインクリメントするインクリメントカウンタであり、カウンタの値は、現在書き込みを行っている行番号を表す。比較器505は、カウンタ504の値と非表示終了アドレスレジスタ502の値を比較し、一致した時のみ“ハイ”を出力し、一致しない時は“ロー”を出力する。比較器506は、カウンタ504の値と非表示開始アドレスレジスタ501の値を比較し、一致した時のみ“ハイ”を出力し、一致しない時は“ロー”を出力する。その結果として、RSラッチ507は、パーシャル表示の表示行書き込み時には出力Qに“ロー”、反転出力Qバーに“ハイ”を出力する。また、非表示行書き込み時には、出力Qに“ハイ”、反転出力Qバーに“ロー”を出力する。

【0062】

フレームの開始行は表示行であるので、RSラッチ507の反転出力Qバーは“ハイ”となるため、論理積回路520の出力は、パーシャル表示時用分割信号生成シフトレジスタ509の出力となり、選択器510の出力は、図7の表示期間で示される分割信号D1, D2, D3となる。この分割信号D1, D2, D3をもとに、選択信号SA, SB, SCが電源部103にて作られる。

【0063】

選択信号SA, SB, SCは分割信号D1, D2, D3より“ハイ”的期間が短くなるように作られる。この場合、行駆動信号が“ロー”になる時、選択信号SA又はSCが“ハイ”であり、厳密にはR, G, B3色の列駆動信号線の状態が一致しないので、R, G

10

20

30

40

50

、Bによる色の偏りが出てくるが、パーシャル表示時は8色表示とし、最低の階調と最高の階調のみを使っているので、多少の色の偏りは気にならず、問題はない。

#### 【0064】

また、フレームの開始行は表示行であるので、RSラッチ507のQ出力は“ロー”、論理積回路525のイコライズ用出力D0は“ロー”となり、この出力D0をもとに電源部103にて作られるEQG信号も“ロー”となる。したがって、列電極は、VEQR、VEQG、VEQB信号と切断されている。

#### 【0065】

表示行の書き込みが進んで、カウンタ504の値が非表示開始アドレスレジスタ501の値と一致すると、比較器506が“ハイ”を出力するので、SRラッチ507の反転出力Qバーは“ロー”となる。したがって、論理積回路520の出力は“ロー”となるため、選択器510の出力である分割信号D1、D2、D3は、図7の非表示期間に示されるように“ロー”固定となる。

#### 【0066】

また、SRラッチ507の出力Qは“ハイ”となるため、論理積回路525のイコライズ用出力D0は“ハイ”となり、この出力D0は図7の非表示期間に示されるように“ハイ”固定となる。この出力D0をもとに電源部103にて作られるEQG信号も“ハイ”となる。したがって、列電極には、VEQR、VEQG、VEQB信号が印加される。

#### 【0067】

EQG信号が“ハイ”的間、電源部103は、VEQR、VEQG、VEQB信号の電圧を、対向電圧VCOMの電位レベルなど最も電力を消費しない値に固定する。VEQR、VEQG、VEQB信号は“0”に相当する信号レベルでもよく、電力をなるべく消費しない値であればよい。したがって、列電極は、対向電圧VCOMの電位レベルなど最も電力を消費しない値になる。また、列電圧出力部118は、イコライズ用出力D0が“ハイ”的間、内蔵するアンプの電源を切り、アンプに定常電流が流れないようにする。

#### 【0068】

次に、表示行の書き込みが進んで、カウンタ504の値が非表示終了アドレスレジスタ502の値と一致すると、比較器505が“ハイ”を出力するので、SRラッチ507の出力Qは“ロー”、反転出力Qバーは“ハイ”となる。そこで、選択器510の分割信号D1、D2、D3は、パーシャル表示時用分割信号生成シフトレジスタ509の出力となり、図7の表示期間で示される波形となる。また、列電圧出力部118は、内蔵するアンプの電源を入れ、表示期間の動作に戻る。

#### 【0069】

以上のように動作することにより、パーシャル表示の表示期間において、選択信号SA、SCの動作周波数は、RGBRGBと繰り返し出す場合に比べ2分の1となる。また、非表示期間においては、選択信号SA、SB、SCの動作周波数は“0”となる。このように、周波数を著しく落とすことができるので、消費電力を大幅に抑えることができる。さらに、定常電流を必要とし消費電力の大きいアンプの電源を切ることができるので、消費電力を大きく削減できる。また、パーシャル表示において、縦方向の分割位置などを自由にCPUから設定でき、使い勝手の良い表示装置を作成できる。

#### 【実施例3】

#### 【0070】

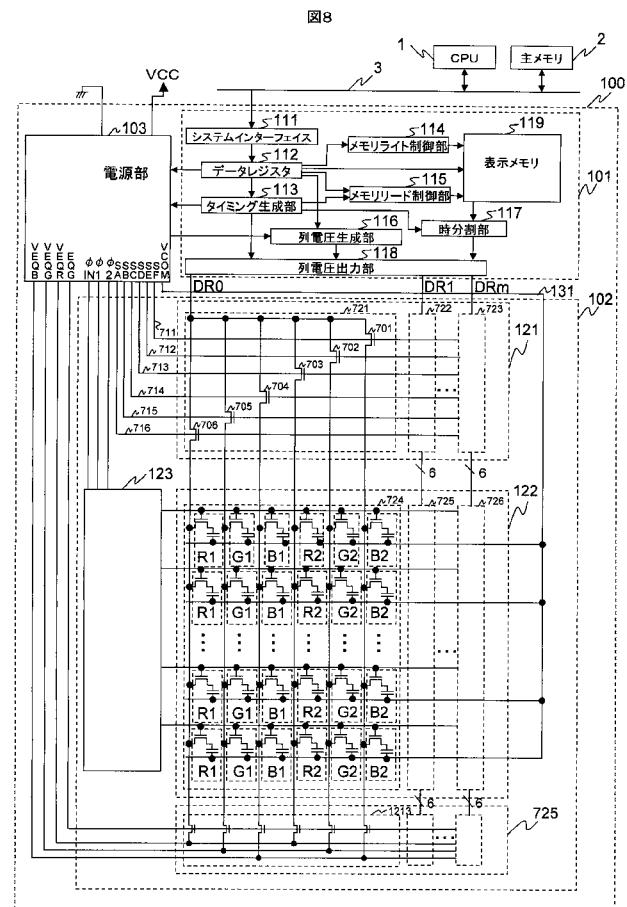

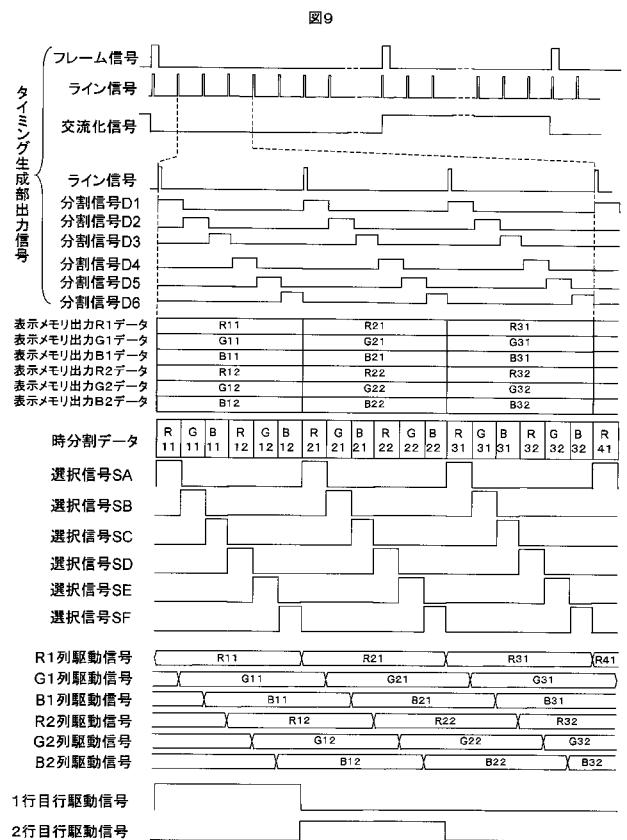

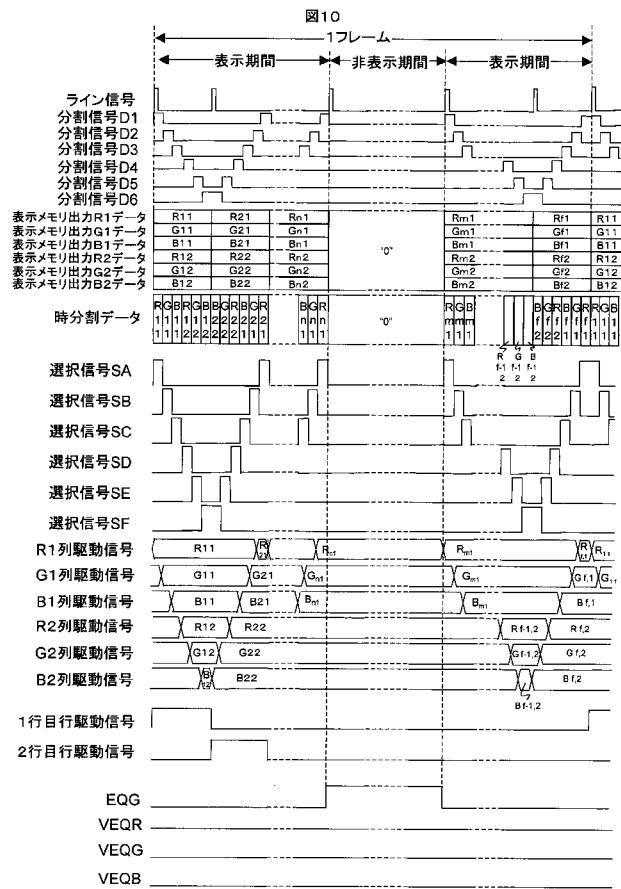

本発明の実施例3について、図8、図9、図10を用いて説明する。本実施例は、時分割データとして6列分のデータが時分割して入力されており、1本の列電圧は6個の分配スイッチにより、6列の列電極へ接続されている点が、実施例1、2と異なる。

#### 【0071】

図8は、本実施例の表示装置のブロック図であって、液晶パネル102上の分配部121には、列電圧出力部118から与えられた1つの信号を6つの列駆動信号に変換するスイッチ回路721、722、723が設けられている。これらのスイッチ回路の構成は同じであるので、代表してスイッチ回路721について説明する。列駆動回路101からの

10

20

30

40

50

1つの信号は、スイッチ 701, 702, 703, 704, 705, 706 に接続されている。これらのスイッチは、それぞれ、分配制御線 711, 712, 713, 714, 715, 716 が“ハイ”的ときオン状態となるスイッチである。そして、スイッチ 701, 702, 703, 704, 705, 706 は、それぞれ、B2, G2, R2, B1, G1, R1 列の画素に列駆動信号を与える。

#### 【0072】

本実施例では、列駆動信号 DR0 として、R の 1 列目、G の 1 列目、B の 1 列目、R の 2 列目、G の 2 列目、B の 2 列目の各信号が時分割され、液晶パネルに入力される。同様に、列駆動信号 DR1 として、R、G、B の 3 列目及び 4 列目、列駆動信号 DRm として、R、G、B の 2m+1 列目及び 2m+2 列目が時分割されて入力される。

10

#### 【0073】

次に、通常表示時の動作について、図 9 を用いて説明する。図 8 に示す表示メモリ 119 は、ライン信号に同期して 1 行分のデータを時分割部 117 に出力する。図 9 では、特に、1 列目と 2 列目の動作に着目して説明する。

#### 【0074】

図 9において、R11 と書いてあるのは R1 列の 1 行目に書き込むべき値であることを示す。同様に R12 は R2 列の 1 行目に書き込むべき値、R21 は R1 列の 2 行目に書き込むべき値であることを示す。

#### 【0075】

1 行目のデータは同時に出力されるので、時分割部 117 はタイミング生成部 113 で生成された分割信号 D1 ~ D6 に従って R11, G11, B11, R12, G12, B12 を時分割し、時分割データを生成する。この時分割データを列電圧出力部 118 で列電圧に変換し、列駆動信号 DR0 ~ DRm として出力する。

20

#### 【0076】

電源部 103 では、分割信号 D1 ~ D6 をもとに、選択信号 SA ~ SF を生成する。選択信号 SA が“ハイ”的とき、スイッチ 706 がオン状態となり、その時、列電圧は R1 1 に対応する値となっているので、R1 列に列電圧 R11 が書き込まれる。同様に、G1 1, B1 1, R1 2, G1 2, B1 2 が G1 列、B1 列、R2 列、G2 列、B2 列に書き込まれる。最後の B2 列の駆動信号が確定してから、1 行目行駆動信号は“ロー”となり、1 行目の R1, G1, B1, R2, B2, G2 列目の液晶画素に、それぞれ R11, G11, B11, R12, G12, B12 に対応する列電圧が書き込まれる。

30

#### 【0077】

このような構成とすることにより、本実施例の液晶装置は実施例 1, 2 の液晶装置に比べ、列駆動部 101 と液晶パネル 102 間の配線数を半減させることができ、低コスト化できる。

#### 【0078】

次に、8 色パーシャル表示時の動作について、図 10 を用いて説明する。表示期間において、図 8 に示す表示メモリ 119 は、ライン信号に同期して 1 行分のデータを時分割部 117 に出力する。1 行目のデータは同時に出力されるので、時分割部 117 はタイミング生成部 113 で生成された分割信号 D1 ~ D6 に従って R11, G11, B11, R12, G12, B12 を時分割し、時分割データを生成する。この時、分割信号 D1 ~ D6 は図 10 に示す波形であるので、時分割データは、1 行目では、R11, G11, B11, R12, G12, B12, 2 行目では、B22, G22, R22, B21, G21, R21 の順番で時分割される。

40

#### 【0079】

また、選択信号 SA ~ SF は分割信号 D1 ~ D6 をもとに生成され、図 10 に示す波形となる。したがって、R1 列、G1 列、B1 列、R2 列、G2 列、B2 列に R11, G11, B11, R12, G12, B12 に対応する列電圧が書き込まれたときに、1 行目の行駆動信号は“ロー”となるので、1 行目の R1, G1, B1, R2, B2, G2 列目の液晶画素に、それぞれ R11, G11, B11, R12, G12, B12 に対応する列電

50

圧が書き込まれる。次の2行目は、R1列、G1列、B1列、R2列、G2列、B2列にR21, G21, B21, R22, G22, B22に対応する列電圧が書き込まれたときに、2行目の行駆動信号は“ロー”となるので、2行目のR1, G1, B1, R2, B2, G2列目の液晶画素に、それぞれR21, G21, B21, R22, G22, B22に対応する列電圧が書き込まれる。

#### 【0080】

以上説明したように、本実施例において、1行目では、B2列を駆動する選択信号SFが最後に“ハイ”となり、B2列に最後に列電圧が分配されたあと、2行目では、最初に選択信号SFが“ハイ”となり、B2列に最初に列電圧が分配される。

#### 【0081】

また、2行目では、R1列を駆動する選択信号SAが最後に“ハイ”となり、R1列に最後に列電圧が分配されたあと、3行目では、最初に選択信号SAが“ハイ”となり、R1列に最初に列電圧が分配される。

#### 【0082】

このように、ある行で最後に分配した列に、次の行では最初に分配し、行の変わり目で選択信号を“ハイ”的ままでつことで、選択信号SAとSFの駆動周波数を2分の1に減らすことができる。また、本実施例においても、実施例1, 2と同様、非表示期間においては、選択信号SA～SFのレベルを“ロー”に固定することで、非表示期間の駆動周波数を“0”とすることができる。また、非表示期間において、イコライズ回路のEQG信号を“ハイ”とし、列電圧出力部のアンプの電源を切ることができるので、消費電力を大幅に削減できる。

#### 【0083】

本実施例においては、選択信号が“ハイ”になる順番は、奇数行目はSA, SB, SC, SD, SE, SF、偶数行目はSF, SE, SD, SC, SB, SAと逆順であったが、違う順番であっても、隣り合う行で最後と最初の選択信号が同じであり同じ列を選択すれば同じように効果を得ることができる。例えば、奇数行目はSA, SB, SC, SD, SE, SF偶数行目はSF, SE, SD, SC, SB, SAという場合でも同じように効果を得ることは明白であり、最初と最後の列以外の選択順は本発明にはなんら制限を与えない。また、実施例1, 2においては、時分割数を3、実施例3においては、時分割数を6としたが、時分割数は3の倍数でなくともよく、他の数においてもある行の最後に分配した列に、次の行では最初に分配することにより、同じ効果を得ることは、明白である。したがって、時分割の分割数は本発明になんら制限を与えるものではなく、どのような整数であっても、本発明は適用できる。

#### 【実施例4】

#### 【0084】

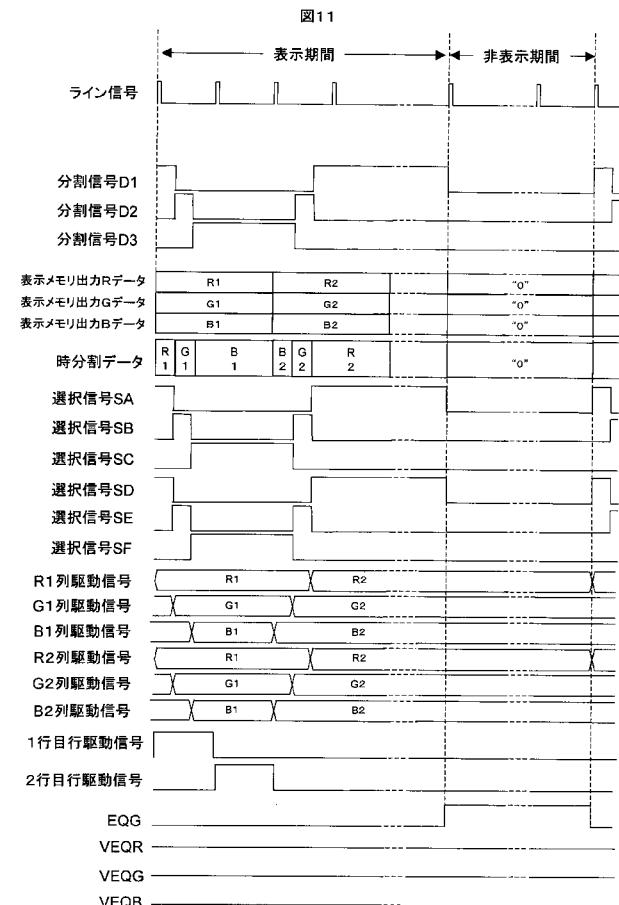

次に、本発明の実施例4について、図8、図9、図11を用いて説明する。図8は、実施例3と同様に、本実施例のブロック図である。本実施例において、通常表示時は、実施例3と同様に、図9に示す動作を行う。また、本実施例において、8色パーシャル表示時は、図11に示す動作を行う。

#### 【0085】

本実施例の8色パーシャル表示は、縦方向、横方向共に2分の1の解像度で表示する。例えば、通常表示時、VGA(640ピクセル×480ピクセル)の高精細表示であるとすると、8色パーシャル表示時は、QVGA(320ピクセル×240ピクセル)表示となる。このような低精細度化は、縦横2ピクセルづつ計4ピクセルに同じ値を書き込むとする。

#### 【0086】

まず、図8に示す表示メモリ119は、1行目と2行目に書き込むべきデータを時分割部117に出力する。タイミング生成部113は図11に示す分割信号D1, D2, D3を生成する。

#### 【0087】

10

20

30

40

50

そこで、1行目の書き込み時、1ライン周期を3つに分け、3つに分けた最初の期間を分割信号D1の“ハイ”期間、次の期間を分割信号D2の“ハイ”期間、次の期間を分割信号D3の“ハイ”期間とする。これら分割信号D1、D2、D3により、時分割データは図11に示すように生成される。また、選択信号SA～SFは分割信号D1、D2、D3をもとに生成され、選択信号SAとSD、選択信号SBとSE、選択信号SCとSFは同じ信号が出力される。これにより、R1列とR2列、G1列とG2列、B1列とB2列には、同じ列電圧が書き込まれる。各列電圧が確定した後、1行目駆動信号は“ロー”となり、液晶画素1行目のR1列とR2列には列電圧R1が、液晶画素1行目のG1列とG2列には列電圧G1が、液晶画素1行目のB1列とB2列には列電圧B1が書き込まれる。

10

## 【0088】

次に、2行目の書き込み時には、表示メモリ119の出力データ、分割信号D1、D2、D3は変化せず、選択信号SA～SFも電位を保ったまます。それにより、液晶素子R1、G1、B1、R2、G2、B2の列駆動信号の電位は変化せず、2行目の行駆動信号が“ロー”となり液晶画素2行目のR1列とR2列には列電圧R1が、液晶画素2行目のG1列とG2列には列電圧G1が、液晶画素2行目のB1列とB2列には列電圧B1が書き込まれる。

## 【0089】

次の3行目の書き込み時には、1ライン周期を3つに分け、3つに分けた最初の期間を分割信号D3の“ハイ”期間、次の期間を分割信号D2の“ハイ”期間、次の期間を分割信号D1の“ハイ”期間とする。これら分割信号D1、D2、D3により、時分割データは図11に示すようにB2、G2、R2の順で生成される。また、選択信号SA～SFは分割信号D1、D2、D3をもとに生成され、選択信号SAとSD、選択信号SBとSE、選択信号SCとSFは同じ信号が出力される。これにより、R1列とR2列、G1列とG2列、B1列とB2列には同じ列電圧が書き込まれる。各列電圧が確定した後、3行目の行駆動信号は“ロー”となり液晶画素3行目のR1列とR2列には列電圧R2が、液晶画素3行目のG1列とG2列には列電圧G2が、液晶画素3行目のB1列とB2列には列電圧B2が書き込まれる。

20

## 【0090】

以上のように動作することにより、8色パーシャル表示において、選択信号SB、SEの動作周波数は、図8に示す通常表示時の2分の1、また、選択信号SA、SC、SD、SFの動作周波数は、通常表示時の4分の1となり、大幅に動作周波数を削減できるので、低消費電力化することができる。

30

## 【0091】

なお、本実施例では、8色パーシャル表示の表示期間において、行駆動信号の“ハイ”を1行分づつ別々のタイミングで入力したが、“ハイ”的時間を2倍にし、同時に入力してもよい。特に、行駆動信号の入力方式に限定されない。

## 【0092】

以上本実施例で示したように、複数行に同じデータを書き込み、複数行毎に書き込みデータを変える表示方法においても、本方式は適用可能であり、表示が切り替わる行において、最後に分配した列に、次に表示が切り替わる行において、最初に分配し、かつ、行の切り替わり時、または、表示が切り替わらない行においては、選択信号の電位を保つことにより、適用できる。

40

## 【0093】

以上、本発明の実施例においては、TN型液晶とLTPS-TFTを例にとり説明したが、表示画素への表示信号を時分割して入力し、分配して書き込み表示する表示装置であればIPS液晶、OCB液晶など他の液晶方式、またOLEDなど他の表示原理を用いた表示装置であっても適用可能であることはいうまでもない。

## 【図面の簡単な説明】

## 【0094】

50

【図1】本発明に係る表示装置の実施例1,2の構成を示すブロック図

【図2】実施例1での通常表示時の動作を表すタイミングチャート

【図3】実施例1でのパーシャル表示時の動作を表すタイミングチャート

【図4】実施例1でのパーシャル表示時の動作を表すタイミングチャート

【図5】実施例2でのデータレジスタ、タイミング生成部の一部分の詳細ブロック図

【図6】実施例2での通常表示時の動作を表すタイミングチャート

【図7】実施例2でのパーシャル表示時の動作を表すタイミングチャート

【図8】本発明に係る表示装置の実施例3,4の構成を示すブロック図

【図9】実施例3,4での通常表示時の動作を表すタイミングチャート

【図10】実施例3での8色パーシャル表示時の動作を表すタイミングチャート

【図11】実施例4での8色パーシャル表示時の動作を表すタイミングチャート

【符号の説明】

【0095】

1...CPU、2...主メモリ、3...システムバス、100...表示装置、101...列駆動部、

102...液晶パネル、103...電源部、111...システムインターフェイス、112...データレジスタ、113...タイミング生成部、114...メモリライト制御部、115...メモリリード制御部、116...列電圧生成部、117...時分割部、118...列電圧出力部、119...表示メモリ、121...分配部、122...画素部、123...行駆動部、124...イコライズ回路、131...対向電極、501...パーシャル非表示開始アドレスレジスタ、502...パーシャル非表示終了アドレスレジスタ、503...パーシャル表示開始レジスタ、504...カウンタ、505,506...比較器、507,511,512...SRラッチ、508...通常表示時用分割信号生成シフトレジスタ、509...パーシャル表示時用分割信号生成シフトレジスタ、510...選択器、513,514,515,516,517,518,521,522,523...シフトレジスタ、519,524...OR回路、520,525...AND回路、1211,1212,1213...分配制御線、1214,1215,1216...TFT素子

【 四 1 】

【 図 2 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【図3】

図3

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 3 R |

| G 0 9 G | 3/20 | 6 2 3 D |

| G 0 9 G | 3/20 | 6 2 3 C |

| G 0 9 G | 3/20 | 6 1 2 U |

| G 0 9 G | 3/20 | 6 2 2 K |

| G 0 9 G | 3/20 | 6 2 3 U |

| G 0 9 G | 3/20 | 6 2 1 D |

| G 0 9 G | 3/20 | 6 1 1 B |

| G 0 9 G | 3/20 | 6 1 1 A |

(72)発明者 萬場 則夫

神奈川県川崎市麻生区王禅寺1099番地

研究所内

株式会社日立製作所システム開発

(72)発明者 松戸 利充

千葉県茂原市早野3300番地

株式会社日立ディスプレイズ内

F ターム(参考) 2H093 NA16 NA43 NA53 NA62 NC13 NC14 NC16 NC28 NC34 NC35

ND39

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5C006 | AA16 | AA22 | AC27 | AC28 | AF14 | AF31 | AF42 | AF43 | AF45 | AF68 |

| AF69  | AF72 | AF73 | AF83 | BB16 | BC12 | BC20 | BC23 | BF02 | BF03 |      |

| BF04  | BF06 | BF14 | BF22 | BF24 | BF25 | BF26 | BF33 | BF34 | BF43 |      |

| FA42  | FA48 | FA51 |      |      |      |      |      |      |      |      |

| 5C080 | AA10 | BB06 | BB08 | CC03 | DD23 | DD26 | DD28 | EE26 | EE29 | EE30 |

| FF11  | GG12 | JJ01 | JJ02 | JJ03 | JJ04 | KK07 |      |      |      |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2007114496A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2007-05-10 |

| 申请号            | JP2005306003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2005-10-20 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 片山 ゆかり<br>工藤 泰幸<br>萬場 則夫<br>松戸 利充                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 片山 ゆかり<br>工藤 泰幸<br>萬場 則夫<br>松戸 利充                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G3/3688 G09G3/20 G09G3/2092 G09G2310/0275 G09G2310/0297 G09G2310/04 G09G2310/06<br>G09G2320/0247 G09G2330/021 G09G2360/18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.510 G09G3/20.623.F G09G3/20.641.C G09G3/20.623.R G09G3<br>/20.623.D G09G3/20.623.C G09G3/20.612.U G09G3/20.622.K G09G3/20.623.U G09G3/20.621.D<br>G09G3/20.611.B G09G3/20.611.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NA53 2H093/NA62 2H093/NC13 2H093/NC14 2H093/NC16 2H093<br>/NC28 2H093/NC34 2H093/NC35 2H093/ND39 5C006/AA16 5C006/AA22 5C006/AC27 5C006/AC28<br>5C006/AF14 5C006/AF31 5C006/AF42 5C006/AF43 5C006/AF45 5C006/AF68 5C006/AF69 5C006<br>/AF72 5C006/AF73 5C006/AF83 5C006/BB16 5C006/BC12 5C006/BC20 5C006/BC23 5C006/BF02<br>5C006/BF03 5C006/BF04 5C006/BF06 5C006/BF14 5C006/BF22 5C006/BF24 5C006/BF25 5C006<br>/BF26 5C006/BF33 5C006/BF34 5C006/BF43 5C006/FA42 5C006/FA48 5C006/FA51 5C080/AA10<br>5C080/BB06 5C080/BB08 5C080/CC03 5C080/DD23 5C080/DD26 5C080/DD28 5C080/EE26 5C080<br>/EE29 5C080/EE30 5C080/FF11 5C080/GG12 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04<br>5C080/KK07 2H193/ZA04 2H193/ZD23 2H193/ZG34 |         |            |

| 代理人(译)         | 小野寺杨枝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 其他公开文献         | JP4786996B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

**摘要(译)**

要解决的问题：使用引入了RGB分时驱动的冷多晶硅TFT液晶面板来降低显示装置的功耗。 ŹSOLUTION：在RGB分时驱动方法的显示装置中，以分时方式输入用于提供RGB三种颜色的RGB数据以向液晶面板显示像素，(1)将数据输入到液晶面板按照每一行信号中的RGB和BGR的顺序，并且在一个行周期的中断中，处于ON状态的选择信号SC保持直到下一行周期。另外，(2)在部分显示中，选择信号SA，SB，SC总是保持在OFF状态持续部分非显示时段，并且均衡器信号EQG保持在ON状态。因此，可以显著降低用于选择RGB数据的选择信号SA，SC的操作频率，并且获得低功耗。 Ź