(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-264677

(P2004-264677A)

(43) 公開日 平成16年9月24日(2004.9.24)

(51) Int.Cl.<sup>7</sup>**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G02F 1/133 575

G09G 3/20 611E

G09G 3/20 612R

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 6 O L (全 15 頁) 最終頁に続く

(21) 出願番号

特願2003-55910 (P2003-55910)

(22) 出願日

平成15年3月3日 (2003.3.3)

(71) 出願人 502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(74) 代理人 100083552

弁理士 秋田 収喜

(72) 発明者 高橋 洋之

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内F ターム(参考) 2H093 NA32 NA34 NA51 NC34 ND10

ND39

5C006 AA16 AC11 AC25 AC26 AF52

AF54 AF59 AF64 BB16 BC06

EB00 FA20 FA21

5C080 AA10 BB05 DD06 DD28 EE29

FF11 JJ02 JJ03 JJ04 JJ06

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】受光素子を設けることなく、共通電極に印加する共通電圧を自動的に調整して、表示画面にちらつき(フリッカ)が発生するのを防止することが可能な液晶表示装置を提供する。

【解決手段】画像表示部の周囲に配置される複数のダミー画素が画素電極を有し、前記複数のダミー画素の中で正極性の階調電圧が書き込まれたダミー画素の画素電極の電圧と前記共通電極に印加される共通電圧との間の電位差を検出する第1の手段と、前記複数のダミー画素の中で負極性の階調電圧が書き込まれたダミー画素の画素電極の電圧と、前記共通電圧との間の電位差を検出する第2の手段と、前記第1の手段で検出された電位差と、前記第2の手段で検出された電位差とが等しくなるように、前記共通電圧を制御する制御手段とを備える。

【選択図】 図3

図3

**【特許請求の範囲】****【請求項 1】**

画像を表示する画像表示部と、

前記画像表示部の周囲に配置される複数のダミー画素とを有する液晶表示装置であって、前記複数のダミー画素は画素電極を有し、

前記複数のダミー画素の中で正極性の所定の階調電圧が書き込まれたダミー画素の画素電極の電圧と、共通電極に印加される共通電圧との間の電位差を検出する第1の手段と、

前記複数のダミー画素の中で負極性の所定の階調電圧が書き込まれたダミー画素の画素電極の電圧と、前記共通電極に印加される共通電圧との間の電位差を検出する第2の手段と、

、

前記第1の手段で検出された電位差と、前記第2の手段で検出された電位差とが等しくなるように、前記共通電極に印加する共通電圧を制御する制御手段とを備えることを特徴とする液晶表示装置。

**【請求項 2】**

前記液晶表示装置は、交流化駆動方法として、共通電極反転法を採用しており、

前記制御手段は、前記第1の手段で検出された電位差と、前記第2の手段で検出された電位差とが等しくなるように、前記複数のダミー画素に前記正極性の所定の階調電圧を書き込むときの負極性の共通電圧と、前記複数のダミー画素に前記負極性の所定の階調電圧を書き込むときの正極性の共通電圧とを制御することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記液晶表示装置は、交流化駆動方法として、共通電極対称法を採用しており、

前記制御手段は、前記第1の手段で検出された電位差と、前記第2の手段で検出された電位差とが等しくなるように、前記複数のダミー画素に前記正極性あるいは負極性の所定の階調電圧を書き込むときの共通電圧を制御することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 4】**

前記所定の階調電圧は、最大階調の階調電圧であることを特徴とする請求項1ないし請求項3のいずれか1項に記載の液晶表示装置。

**【請求項 5】**

前記所定の階調電圧は、最小階調の階調電圧であることを特徴とする請求項1ないし請求項3のいずれか1項に記載の液晶表示装置。

**【請求項 6】**

前記所定の階調電圧は、最大階調の階調電圧と最小階調の階調電圧との間の任意の階調電圧であることを特徴とする請求項1ないし請求項3のいずれか1項に記載の液晶表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、携帯機器（例えば、携帯電話機）などに搭載される液晶表示装置に係わり、特に、共通電極に印加する共通電圧を自動的に調整する際に有効な技術に関する。

**【0002】****【従来の技術】**

TFT (Thin Film Transistor) 方式の液晶表示モジュールであって、画素数が、例えば、カラー表示で  $100 \times 150 \times 3$  程度の小型の液晶表示パネルを有する液晶表示モジュールは、例えば、携帯電話機などの携帯機器の表示部として広く使用されている。

図10は、従来のTFT方式の液晶表示モジュールの回路構成を示すブロック図である。同図に示すように、従来の液晶表示モジュールは、液晶表示パネル100と、表示制御装置110と、電源回路120と、ドレインドライバ130と、ゲートドライバ140とで

10

20

30

40

50

構成される。

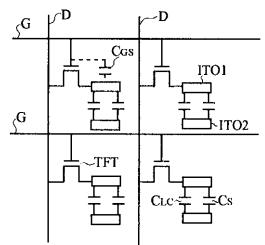

図11は、図1に示す液晶表示パネル100の一例の等価回路を示す図である。

図11に示すように、液晶表示パネル100は、マトリクス状に形成される複数の画素を有する。

各画素は、隣接する2本の信号線（ドレイン信号線Dまたはゲート信号線G）と、隣接する2本の信号線（ゲート信号線Gまたはドレイン信号線D）との交差領域内に配置される。

### 【0003】

各画素は薄膜トランジスタ（TFT）を有し、各画素の薄膜トランジスタ（TFT）のソース電極は、画素電極（ITO1）に接続される。10

また、画素電極（ITO1）と共通電極（対向電極、またはコモン電極ともいう）（ITO2）との間に液晶層が設けられるので、画素電極（ITO1）と共通電極（ITO2）との間には、液晶容量（ $C_{Lc}$ ）が等価的に接続される。

さらに、薄膜トランジスタ（TFT）のソース電極と共通電極（ITO2）との間には、蓄積容量（ $C_s$ ）が接続される。

図10に示す液晶表示パネル100において、列方向に配置された各画素の薄膜トランジスタ（TFT）のドレイン電極は、それぞれドレイン信号線（映像信号線ともいう）Dに接続され、各ドレイン信号線Dは、列方向の各画素の液晶に階調電圧を印加するドレインドライバ130に接続される。

また、行方向に配置された各画素における薄膜トランジスタ（TFT）のゲート電極は、それぞれゲート信号線（走査信号線ともいう）Gに接続され、各ゲート信号線Gは、1水平走査時間、行方向の各画素の薄膜トランジスタ（TFT）のゲート電極に走査駆動電圧（正のバイアス電圧あるいは負のバイアス電圧）を供給するゲートドライバ140に接続される。20

### 【0004】

表示制御装置110は、外部から送信されてくるクロック信号、ディスプレイタイミング信号、水平同期信号、垂直同期信号の各表示制御信号および表示用デ-タ（R・G・B）を基に、ドレインドライバ130、および、ゲートドライバ140を制御・駆動する。

電源回路120は、階調基準電圧をドレインドライバ130に対して供給するとともに、ゲートドライバ140に対して走査駆動電圧を供給し、さらに、共通電極（ITO2）に共通電圧を供給する。30

また、電源回路120は、ドレインドライバ130とゲートドライバ140の電源電圧を、ドレインドライバ130とゲートドライバ140とに対して供給する。

### 【0005】

ゲートドライバ140は、ゲート信号線Gに対して、1水平走査ライン毎に、1水平走査時間、薄膜トランジスタ（TFT）をオンとする走査信号電圧を順次供給して、薄膜トランジスタ（TFT）をオンとする。

また、ドレインドライバ130は、ドレイン信号線Dに対して映像信号電圧を供給し、オンとされた薄膜トランジスタ（TFT）を介して画素電極（ITO1）に映像信号電圧を印加し、各画素に映像信号電圧を書き込み、画素電極（ITO1）と共通電極（ITO2）との間の液晶容量（ $C_{Lc}$ ）を所定の電圧に充電する。40

この充電電圧に基づき、各画素の液晶分子の配向方向を変化させて画像を表示する。以上の動作により、液晶表示パネル100に画像が表示される。

なお、液晶は、直流電圧が印加されると、寿命が短くなる。これを防止するために、液晶表示モジュールにおいては、液晶層に印加する電圧をある一定時間毎に交流化、即ち、共通電極に印加する電圧を基準にして、画素電極に印加する電圧を、一定時間毎に正電圧側（以下、正極性の階調電圧という）、および負電圧側（以下、負極性の階調電圧という）に変化させるようにしている。

### 【0006】

前述したような構成において、理想的には、書き込み時に液晶に印加した電圧は次の書き50

込み時まで保持されるべきであるが、実際には、図11に破線で示すようにTFTのゲート・ソース間に浮遊容量( $C_{GS}$ )が存在するために、薄膜トランジスタ(TFT)がオフした後に、この浮遊容量( $C_{GS}$ )により画素電極の電圧が変動する。この浮遊容量( $C_{GS}$ )による電圧変動量 $V$ は、下記(1)式で表される。

## 【数1】

$$V = C_{GS} / (C_{Lc} + C_{GS}) \times V_G \quad \dots \dots \dots \dots \quad (1)$$

但し、 $V_G$ は、薄膜トランジスタ(TFT)がオンの時と、オフの時のゲート電圧の差を表す。

このように、実際に液晶に保持される電圧(即ち、画素電極(ITO1)の電圧)は、ドレイン信号線(D)に印加した液晶印加電圧から $V$ だけ変動する。なお、画素電極(ITO1)の電圧はその他の浮遊容量の影響により変動するが、ここでは最も影響の大きい薄膜トランジスタ(TFT)のゲート・ソース間の浮遊容量 $C_{GS}$ に関してのみ説明することにする。

## 【0007】

そして、共通電極(ITO2)に印加する電圧( $V_{com}$ )は、本来、液晶印加電圧の中心値に設定されるべきであるが、画素電極(ITO1)の電圧が液晶印加電圧に対して $V$ だけ変動するため、正極性の時の画素電極(ITO1)の電圧と共通電極(ITO2)の電圧( $V_{com}$ )との間の電位差と、負極性の時の画素電極(ITO1)の電圧と共通電極(ITO2)の電圧( $V_{com}$ )との間の電位差が異なり、正極性の場合と負極性の場合とで、共通電極(ITO2)の電圧( $V_{com}$ )に対して、非対称な電圧が液晶に印加されることになる。

かかる非対称な電圧が液晶に印加されると、画面のちらつき(フリッカ)が発生する。例えば、垂直同期信号が60Hzの信号源を用いて表示する場合に、隣合う全ての画素に同じ極性の電圧を印加し、その電圧極性を1画面毎に反転させると、30Hzの周期で電圧極性が変化する。つまり、30Hzの周期で非対称な電圧が液晶に保持され、その電圧差に応じた分だけ輝度が変化し、それがフリッカとして観測されることになる。

## 【0008】

そのため、共通電極(ITO2)に印加する電圧( $V_{com}$ )を、前述の電圧変動量 $V$ に応じて調整する必要があるが、この調整量は各製品(LCD)毎にそれぞれ微妙に異なるために、各々の液晶パネル毎に調整が必要である。

一般に、この共通電極(ITO2)に印加する電圧( $V_{com}$ )の調整の方法として、オペレータが実際に液晶パネルのフリッカの状態を確認しながら手動で行う方法と、自動的に行う方法とがある。

手動で行う場合には、可変抵抗の抵抗値を変化させて、共通電極(ITO2)に印加する電圧( $V_{com}$ )を調整するのが一般的であり、この場合に、調整方法を容易にする方法が下記特許文献1に記載されている。

また、自動的に行う場合には、ダミー画素を設け、このダミー画素に特定の階調電圧を印加し、このダミー画素の発光を受光素子で電圧に変換し、この電圧に基づいて、共通電極(ITO2)に印加する電圧( $V_{com}$ )を調整する方法が下記特許文献2、3に記載されている。

## 【0009】

なお、本願発明に関連する先行技術文献情報としては以下のものがある。

## 【特許文献1】

特開平8-63128号公報

## 【特許文献2】

特開平10-246879号公報

## 【特許文献3】

特開平8-286169号公報

## 【0010】

## 【発明が解決しようとする課題】

10

20

30

40

50

しかしながら、オペレータが手動で、共通電極（ITO2）に印加する電圧（Vcom）を調整する方法は、製品出荷時に個々の液晶パネル毎に行う必要があり、前述の特許文献1に記載されているように、この調整方法を容易にする方法が公知であったとしても、その調整作業が困難であり、このため、作業効率が低下するといった問題点があった。

また、自動的に行う場合には、前述の特許文献2、3に記載されているように、ダミー画素の発光を受光素子で電圧に変換する必要があり、受光素子が必要になるという問題点があった。

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、受光素子を設けることなく、共通電極に印加する共通電圧を自動的に調整して、表示画面にちらつき（フリッカ）が発生するのを防止することが可能な液晶表示装置を提供することにある。10

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によつて明らかにする。

### 【0011】

#### 【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

本発明の液晶表示装置は、画像を表示する画像表示部の周囲に、画素電極を有する複数のダミー画素を設け、前記複数のダミー画素の中で正極性の階調電圧が書き込まれたダミー画素の画素電極の電圧と、前記共通電極に印加される共通電圧との間の電位差と、前記複数のダミー画素の中で負極性の階調電圧が書き込まれたダミー画素の画素電極の電圧と、前記共通電極に印加される共通電圧との間の電位差とを検出し、この2つの電位差が等しくなるように、共通電極に印加する共通電圧を制御することを特徴とする。20

### 【0012】

#### 【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

なお、実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

#### [本発明の前提となる液晶表示モジュールの構成]

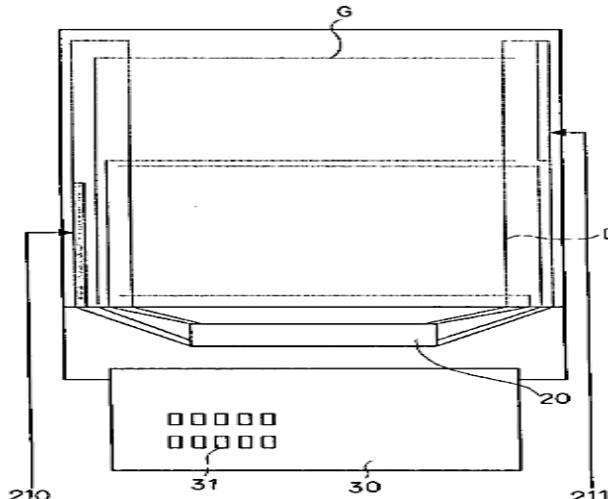

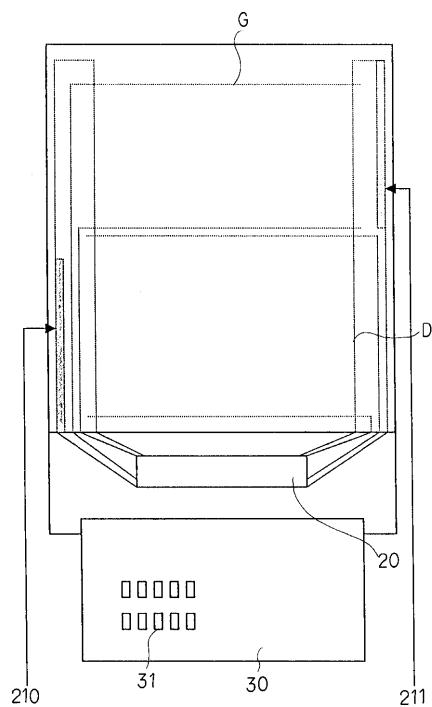

図1は、本発明の前提となる液晶表示モジュールの一例の概略構成を示すブロック図であり、同図(a)は正面図、同図(b)は側面図である。30

なお、図1に示すTFT方式の液晶表示モジュールは、携帯電話機の表示部として使用される液晶表示モジュールである。

図1に示す液晶表示モジュール(TFT-LCD)において、液晶表示パネル100は、一方の基板(TFT基板ともいう)10と、他方の基板(フィルタ基板ともいう)11とを、所定の間隙を隔てて重ね合わせ、該両基板間の周縁部近傍に枠状に設けたシール材により、両基板を貼り合わせると共に、シール材の一部に設けた液晶封入口から両基板間のシール材の内側に液晶を封入、封止し、さらに、両基板の外側に偏光板を貼り付けて構成される。

### 【0013】

ここで、一方の基板10は、例えば、ガラス基板から成り、画素電極(ITO1)、薄膜トランジスタ(TFT)等が形成され、また、他方の基板11は、例えば、ガラス基板から成り、共通電極(ITO2)、カラーフィルタ等が形成される。

一方の基板10上には、液晶ドライバ20が搭載されており、この液晶ドライバ20は、図10に示す表示制御装置110、電源回路120、ドレインドライバ130、並びに、ゲートドライバ140の機能を、1チップ内に集積したものである。なお、図1において、Dがドレン信号線を、Gがゲート信号線を示す。

また、一方の基板10の端部には、フレキシブル配線基板30が実装されており、このフレキシブル配線基板30上には、抵抗素子、容量素子などのチップ素子31が実装されている。4050

さらに、フレキシブル配線基板 30 の端部は折り曲げられており、この折り曲げ部には、携帯電話機の本体部に接続されるコネクタ 32 が設けられる。

なお、図 1 に示す液晶表示モジュールの回路構成、並びに、液晶表示パネル 100 の等価回路は、図 10、図 11 と同じであるので、再度の説明は省略する。

#### 【0014】

前述したように、液晶層は、長時間同じ電圧（直流電圧）が印加されると、液晶層の傾きが固定化され、結果として残像現象を引き起こし、液晶層の寿命を縮めることになる。

10

これを防止するために、液晶表示モジュールにおいては、液晶層に印加する電圧をある一定時間毎に交流化、即ち、共通電極に印加する電圧を基準にして、画素電極に印加する電圧を、一定時間毎に正電圧側／負電圧側に変化させるようにしている。

この液晶層に交流電圧を印加する駆動方法として、共通電極対称法と共通電極反転法の 2 通りの方法が知られている。

共通電極反転法とは、共通電極に印加される電圧と画素電極に印加する電圧とを、交互に正、負に反転させる方法である。

また、共通電極対称法とは、共通電極に印加される電圧を一定とし、画素電極に印加する電圧を、共通電極に印加される電圧を基準にして、交互に正、負に反転させる方法である。

20

図 1 に示す液晶表示モジュールでは、交流化駆動方法として、共通電極反転法を使用している。以下、共通電極反転法について説明する。

#### 【0015】

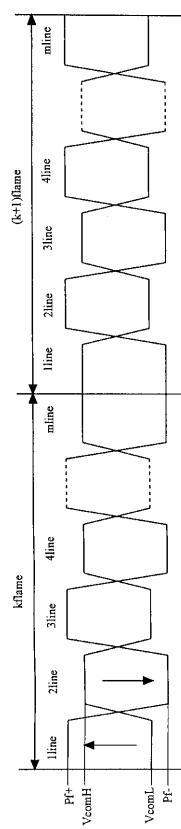

図 2 は、共通電極反転法を説明するための図である。なお、図 2 では、1 水平走査ライン（以下、単に、ラインという）毎に、極性を反転させる場合について説明する。

30

図 2 に示すように、k フレームの奇数番目のライン（例えば、1、3、5 ラインなど）では、各画素の画素電極（ITO 1）（即ち、各ドライン信号線 D）に正極性の階調電圧が印加されるとともに、共通電極（ITO 2）に負極性の共通電圧（Vcom L）が印加される。

また、偶数番目のライン（例えば、2、4、6 ラインなど）では、各画素の画素電極（ITO 1）に負極性の階調電圧が印加されるとともに、共通電極（ITO 2）に正極性の共通電圧（Vcom H）が印加される。

30

そして、k フレームに連続する（k+1）フレームの奇数番目のライン（例えば、1、3、5 ラインなど）では、各画素の画素電極（ITO 1）に負極性の階調電圧が印加されるとともに、共通電極（ITO 2）に正極性の共通電圧（Vcom H）が印加される。

また、偶数番目のライン（例えば、2、4、6 ラインなど）では、各画素の画素電極（ITO 1）に正極性の階調電圧が印加されるとともに、共通電極（ITO 2）に負極性の共通電圧（Vcom L）が印加される。

なお、図 2 において、矢印は、液晶に印加される電圧の極性を示している。

#### 【0016】

##### [実施の形態]

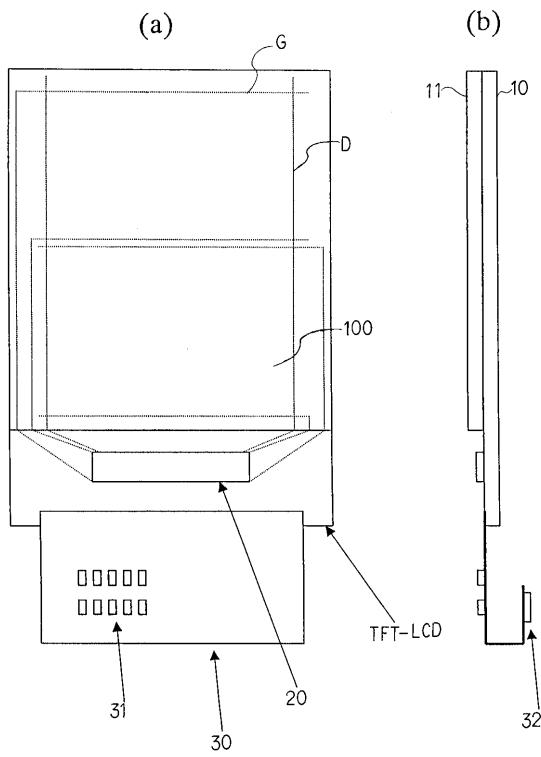

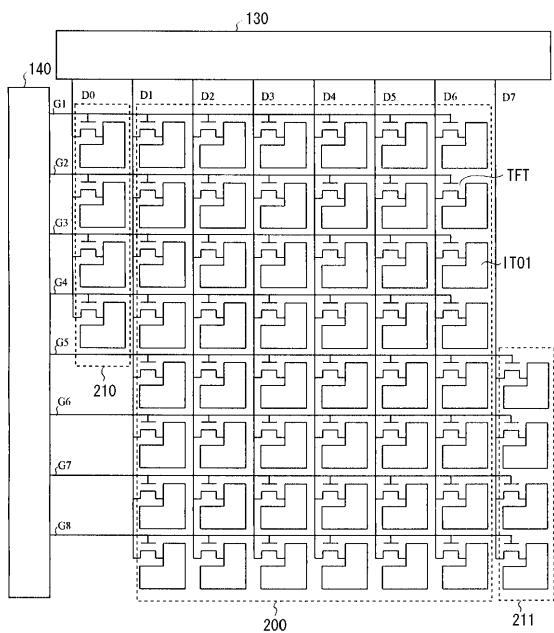

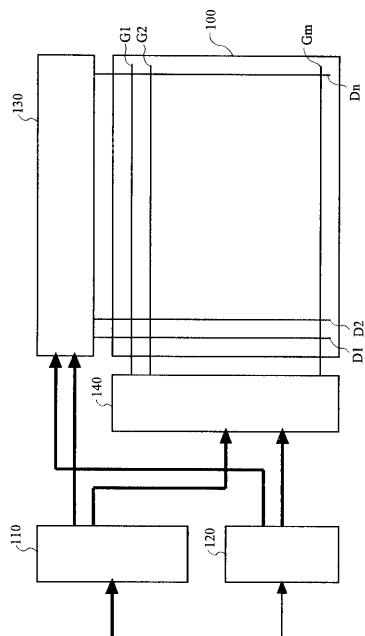

図 3 は、本発明の実施の形態の液晶表示モジュールの概略構成を示すブロック図である。

40 同図に示すように、本実施の形態の液晶表示モジュールでは、液晶表示パネル 100 の有効表示領域の外側にダミー画素（210，211）が配置される。

各ダミー画素（210，211）は、薄膜トランジスタ（TFT）を有し、各ダミー画素（210，211）の薄膜トランジスタ（TFT）のソース電極は、画素電極（ITO 1）に接続される。

また、画素電極（ITO 1）と共に電極（ITO 2）との間に液晶層が設けられるので、画素電極（ITO 1）と共に電極（ITO 2）との間には、液晶容量（C<sub>Lc</sub>）（図示せず）が等価的に接続される。さらに、薄膜トランジスタ（TFT）のソース電極と共に電極（ITO 2）との間には、蓄積容量（C<sub>s</sub>）（図示せず）が接続される。

図 4 は、本実施の形態のダミー画素の配置状態の一例を説明するための模式図であり、こ

50

の図4では、有効表示領域内に、 $8 \times 6$ 個の画素200が配置され、その有効表示領域の外側に4個のダミー画素210と、4個のダミー画素211とを配置した状態を示している。また、この図4において、130はドレインドライバ、140はゲートドライバ、ITO1は画素電極を示す。

この図4に示す例では、ダミー画素(210, 211)の各薄膜トランジスタ(TFT)のゲート電極は、有効表示領域内の各画素200に走査信号電圧を供給するゲート信号線(G1~G8)に接続される。

しかしながら、ダミー画素(210, 211)の各薄膜トランジスタ(TFT)のドレン電極は、専用のドレン信号線(D0, D7)に接続され、この専用のドレン信号線(D0, D7)には、ドレインドライバ130から、正極性、あるいは負極性の階調電圧であって、最大階調の階調電圧と最小階調の階調電圧との間の任意の階調の階調電圧が供給される。

10

#### 【0017】

なお、以下の説明では、ドレインドライバ130から専用のドレン信号線(D0, D7)に対して、正極性、あるいは負極性の階調電圧であって、最大階調の階調電圧(以下、単に、最大階調電圧という)を供給する場合について説明するが、ドレインドライバ130から専用のドレン信号線(D0, D7)に対して供給する階調電圧は、正極性、あるいは負極性の階調電圧であって、最小階調の階調電圧であってもよい。

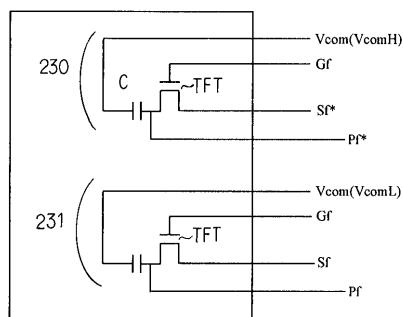

図5は、本実施の形態のダミー画素に書き込まれる映像信号電圧の極性を説明するための図である。

20

この図5において、第1群のダミー画素230と、第2群のダミー画素231とは、1フレーム内において、互いに異なる極性の最大階調の階調電圧が書き込まれる画素群を表す。

例えば、本実施の形態の交流化駆動方法として、前述の図2に示す方法を採用する場合に、図4に示す液晶表示パネルでは、第1群のダミー画素230は、薄膜トランジスタのゲート電極が、G1、G3、G5、G7のゲート信号線に接続されるダミー画素群に相当し、第2群のダミー画素231は、薄膜トランジスタのゲート電極が、G2、G4、G6、G8のゲート信号線に接続されるダミー画素群に相当する。

なお、図5では、第1群のダミー画素230に、負極性の最大階調電圧が書き込まれ、第2群のダミー画素231に、正極性の最大階調電圧が書き込まれた場合を示している。

30

#### 【0018】

図5において、有効表示領域200内の各画素に正極性の階調電圧が書き込まれるときには、第2群のダミー画素231の薄膜トランジスタ(TFT)のゲート電極に印加される走査信号電圧(Gf)がHighレベルとなり、第2群のダミー画素231の薄膜トランジスタ(TFT)がオンし、画素電極に、正極性の最大階調電圧(Sf)が印加される。この場合に、共通電極に印加される共通電圧(Vcom)は、負極性の共通電圧(VcomL)である。

その後、薄膜トランジスタ(TFT)がオフとなると、前述したように、ダミー画素の画素電極の電圧が、V変動し、ダミー画素の画素電極の電圧が、(Pf)となる。

同様に、有効表示領域200内の各画素に負極性の階調電圧が書き込まれるときに、第1群のダミー画素230の薄膜トランジスタ(TFT)のゲート電極に印加される走査信号電圧(Gf)がHighレベルとなり、第1群のダミー画素230の薄膜トランジスタ(TFT)がオンし、画素電極に、負極性の最大階調電圧(Sf\*)が印加される。この場合に、共通電極に印加される共通電圧(Vcom)は、正極性の共通電圧(VcomH)である。

40

その後、薄膜トランジスタ(TFT)がオフとなると、前述したように、ダミー画素の画素電極の電圧が、V変動し、ダミー画素の画素電極の電圧が、(Pf\*)となる。

なお、図5において、図11に示す液晶容量(CLC)と、蓄積容量(Cs)とは、一つの容量素子(C)で表している。

#### 【0019】

図5に示すように、本実施の形態では、(Pf)と(Pf\*)の電圧が液晶表示パネルに取り出される。そして、この電圧に基づき、共通電極に印加する共通電圧を調整する。

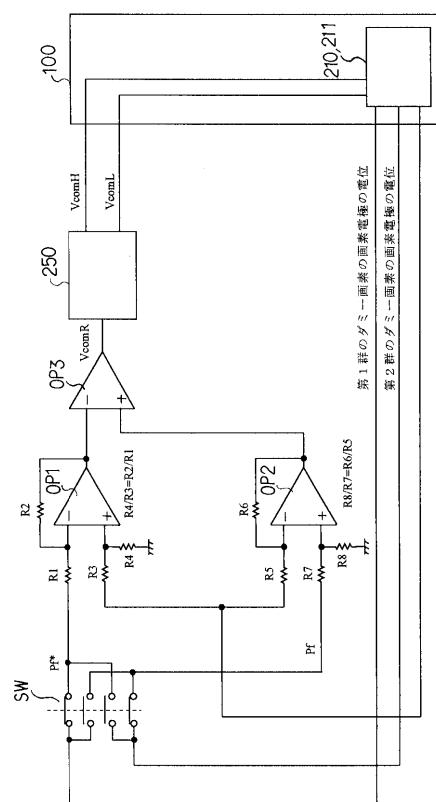

図6は、本実施の形態において、共通電極に印加する共通電圧を調整する回路の一例を示す図である。

例えば、図5に示す第1群の画素群の画素電極の電圧(Pf\*)は、図6に示すオペアンプ(OP1)の反転端子(-)に入力され、また、第2群の画素群の画素電極の電圧(Pf)は、図6に示すオペアンプ(OP2)の非反転端子(+)に入力される。

また、オペアンプ(OP1)の非反転端子(+)と、オペアンプ(OP2)の反転端子(-)には、共通電極の共通電位(Vcom)が入力される。

図6に示す回路において、 $R_4 / R_3 = R_2 / R_1$ 、および $R_8 / R_7 = R_6 / R_5$ の関係があるとき、オペアンプ(OP1)からは、( $V_{com} - Pf^*$ )の電圧が出力され、オペアンプ(OP2)からは、( $Pf - V_{com}$ )の電圧が出力される。

これらの電圧は、オペアンプ(OP3)に入力され、オペアンプ(OP3)からは、( $V_{com} - Pf^* = Pf - V_{com}$ )となるように、 $V_{comR}$ の電圧が出力される。

#### 【0020】

共通電圧生成回路250は、入力される $V_{comR}$ の電圧に基づき、正極性の共通電圧( $V_{comH}$ )と、負極性の共通電圧( $V_{comL}$ )を生成する。

具体的には、共通電圧生成回路250は、正極性の共通電圧( $V_{comH}$ )と負極性の共通電圧( $V_{comL}$ )との間の電位差 $V_1 (= V_{comH} - V_{comL})$ を固定とし、正極性の共通電圧( $V_{comH}$ )を $V_{comR}$ の電圧とする。したがって、図6の回路では、( $V_{com} - Pf^* = Pf - V_{com}$ )となるように、正極性の共通電圧( $V_{comH}$ )と、負極性の共通電圧( $V_{comL}$ )が調整される。

これにより、本実施の形態の液晶表示パネルでは、正極性の場合と負極性の場合とで、共通電極(ITO2)の電圧( $V_{com}$ )に対して、対称な電圧が液晶に印加されることになるので、画面のちらつき(フリッカ)が発生するのを防止することができる。

#### 【0021】

なお、交流化駆動方法として、前述の図2に示す方法を採用する場合に、共通電極の電圧( $V_{com}$ )は、正極性の共通電圧( $V_{comH}$ )から負極性の共通電圧( $V_{comL}$ )、あるいは、負極性の共通電圧( $V_{comL}$ )から正極性の共通電圧( $V_{comH}$ )に変動する。

したがって、図6に示す回路において、オペアンプ(OP1, OP2)に入力される共通電極の電圧( $V_{com}$ )は変動するが、ダミー画素に階調電圧(正極性あるいは負極性の階調電圧)を書き込んだ後に、薄膜トランジスタ(TFT)がオフとなり、ダミー画素の画素電極はフローティング状態となる。

したがって、ダミー画素の画素電極の電圧も、共通電極の電圧( $V_{com}$ )に応じて変動するので、ダミー画素の画素電極と共に共通電極との間の電圧はほぼ一定になる。

また、前述の図2で説明したように、第1群のダミー画素230、あるいは、第2群のダミー画素231に書き込まれる階調電圧の極性は、1フレーム毎に反転する。

そのため、図6に示す回路では、スイッチ(SW)を設け、交流化信号(M)により、このスイッチ(SW)のオン・オフを制御し、オペアンプ(OP1)の反転端子(-)に、負極性の最大階調電圧が書き込まれたダミー画素の画素電極の電圧が印加され、かつ、オペアンプ(OP2)の非反転端子(+)に、正極性の最大階調電圧が書き込まれたダミー画素の画素電極の電圧が印加されるようにしている。

#### 【0022】

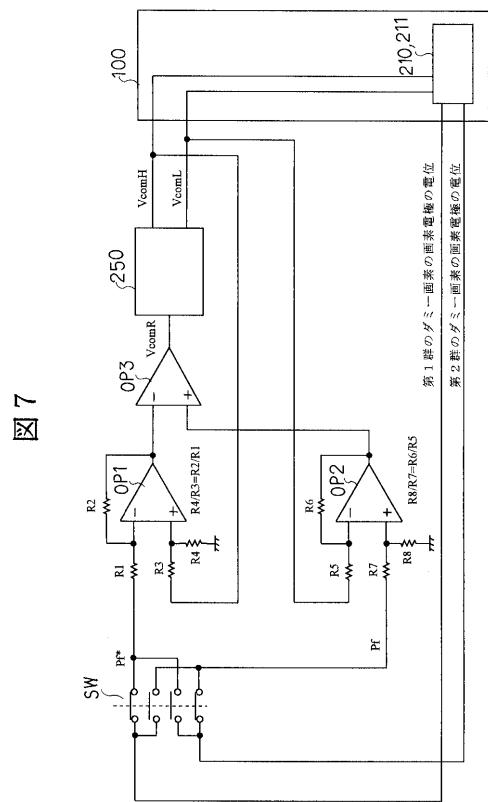

図7は、本実施の形態において、共通電極に印加する共通電圧を調整する回路の他の例を示す図である。

図7に示す回路は、オペアンプ(OP1)の非反転端子(+)に、共通電圧生成回路250から出力される正極性の共通電圧( $V_{comH}$ )が印加され、オペアンプ(OP2)の反転端子(-)に、共通電圧生成回路250から出力される負極性の共通電圧( $V_{comL}$ )が印加される点で、図6に示す回路と相異する。

10

20

30

40

50

図 7 に示す回路の動作は、図 6 と同じであるので再度の説明は省略する。

しかしながら、前述したように、交流化駆動方法として、前述の図 2 に示す方法を採用する場合に、共通電極の電圧 ( $V_{com}$ ) が変動するので、図 7 に示す回路では、有効表示領域 200 内の各画素に正極性の階調電圧が書き込まれるときにのみ、オペアンプ (OP 1) の反転端子 (-) にダミー画素の画素電極の電圧が印加、あるいは、有効表示領域 200 内の各画素に負極性の階調電圧が書き込まれるときにのみ、オペアンプ (OP 2) の非反転端子 (+) にダミー画素の画素電極の電圧が印加されるように、スイッチ (SW) を制御する必要がある。

#### 【0023】

[本発明の前提となる液晶表示モジュールのその他の構成]

10

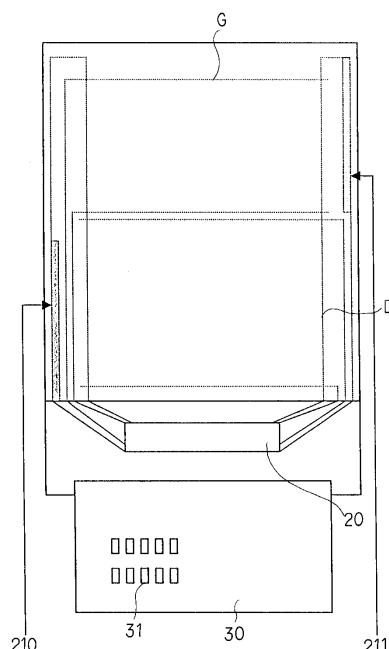

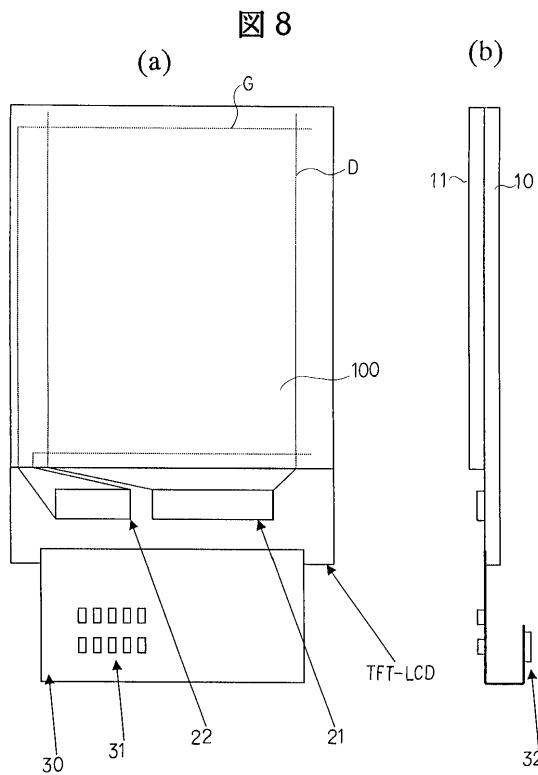

図 8 は、本発明の前提となる液晶表示モジュールの他の例の概略構成を示すブロック図であり、同図 (a) は正面図、同図 (b) は側面図である。

図 8 に示す液晶表示モジュールは、図 1 に示す 1 つの液晶ドライバ 20 に代えて、液晶ドライバ 21 と、液晶ドライバ 22 の 2 つの液晶ドライバを使用した点で、図 1 に示す液晶表示モジュールと相異する。

図 8 に示す液晶表示モジュールのその他の構成は、図 1 に示す液晶表示モジュールと同じであるので再度の説明は省略する。

ここで、液晶ドライバ 21 は、図 10 に示すドレインドライバ 130 の機能を内蔵し、液晶ドライバ 22 は、図 10 に示すゲートドライバ 140 の機能を内蔵する。また、図 10 に示す表示制御装置 110、および、電源回路 120 は、液晶ドライバ 21、または、液晶ドライバ 22 の少なくとも一方に内蔵されればよいが、図 8 に示す液晶表示モジュールでは、図 10 に示す表示制御装置 110 は液晶ドライバ 21 に、また、図 10 に示す電源回路 120 は液晶ドライバ 22 に内蔵されている。

#### 【0024】

なお、前述の説明では、交流化駆動方法として、共通電極反転法を採用した液晶表示モジュールに本発明を適用した実施の形態について説明したが、本発明はこれに限定されるものではなく、本発明は、交流化駆動方法として、共通電極対称法を採用した液晶表示モジュールにも適用可能である。

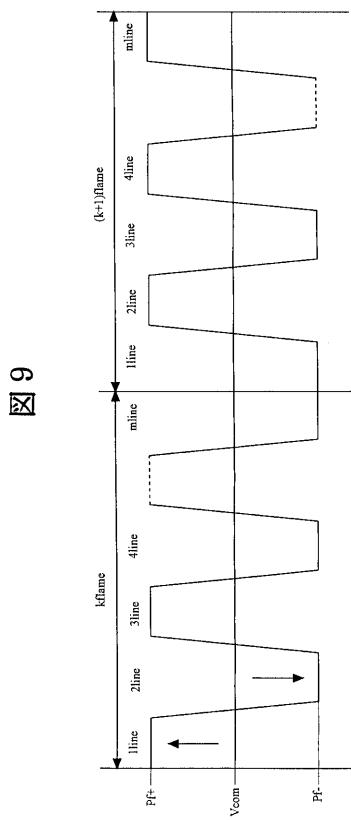

図 9 は、液晶表示モジュールの交流化駆動方法における、共通電極対法を説明するための図である。なお、図 9 では、1 水平走査ライン（以下、単に、ラインという）毎に、極性を反転させる場合について説明する。

30

図 9 に示すように、共通電極対法では、 $k$  フレームの奇数番目のライン（例えば、1、3、5 ラインなど）では、各画素の画素電極 (ITO 1)（即ち、各ドレイン信号線 D）に正極性の階調電圧が印加され、また、偶数番目のライン（例えば、2、4、6 ラインなど）では、各画素の画素電極 (ITO 1) に負極性の階調電圧が印加される。

また、 $k$  フレームに連続する ( $k + 1$ ) フレームの奇数番目のライン（例えば、1、3、5 ラインなど）では、各画素の画素電極 (ITO 1) に負極性の階調電圧が印加され、また、偶数番目のライン（例えば、2、4、6 ラインなど）では、各画素の画素電極 (ITO 1) に正極性の階調電圧が印加される。

しかしながら、共通電極対法では、共通電極 (ITO 2) に印加される共通電圧 ( $V_{com}$ ) は一定とされる。

40

なお、図 9 において、矢印は、液晶に印加される電圧の極性を示している。

#### 【0025】

このように、共通電極対称法は、画素電極 (ITO 1) に印加される電圧の振幅が、共通電極反転法の場合に比べ 2 倍となり、低耐圧のドライバが使用できないと言う欠点があるが、低消費電力と表示品質の点で優れているドット反転法あるいは N ライン反転法が使用可能である。

本発明を、交流化駆動方法として、共通電極対称法を採用した液晶表示モジュールに適用する場合には、共通電圧 ( $V_{com}$ ) として、図 6、図 7 に示す共通電圧生成回路 250 から出力される正極性の共通電圧 ( $V_{comH}$ )、あるいは負極性の共通電圧 ( $V_{com}$ )

50

L ) の一方の電圧を使用し、この電圧と正極性の最大階調電圧が書き込まれたダミー画素の画素電極の電圧との間の電位差と、この電圧と負極性の最大階調電圧が書き込まれたダミー画素の画素電極の電圧との間の電位差とが一致するように、図 6 、図 7 に示す共通電圧生成回路 250 から出力される正極性の共通電圧 (V<sub>comH</sub>) 、あるいは負極性の共通電圧 (V<sub>comL</sub>) の一方の電圧を調整すればよい。

#### 【0026】

以上説明したように、本実施の形態によれば、受光素子を設けることなく、共通電極に印加する共通電圧を自動的に調整して、表示画面にちらつき（フリッカ）が発生するのを防止することが可能となる。

また、共通電極に印加する共通電圧を調整するために、可変抵抗などの別部品が必要がないので、部品点数を少なくすることができ、それにより、製品（例えば、携帯電話機）の外径寸法を小さくすることが可能となる。10

また、ダミー画素の画素電極の電圧から、共通電極に印加する共通電圧を調整するようにしたので、温度、外光などの外的要因により、ダミー画素の画素電極の電圧が変動しても、それに追従して、共通電極に印加する共通電圧を自動的に調整することができる所以、外的要因により表示画面にちらつき（フリッカ）が発生するのを防止することが可能となる。したがって、製品の使用温度範囲を広くすることが可能となる。

以上、本発明者によってなされた発明を、前記実施の形態に基づき具体的に説明したが、本発明は、前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。20

#### 【0027】

##### 【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明の液晶表示装置によれば、受光素子を設けることなく、共通電極に印加する共通電圧を自動的に調整して、表示画面にちらつき（フリッカ）が発生するのを防止することが可能となる。

##### 【図面の簡単な説明】

【図 1】本発明の前提となる液晶表示モジュールの一例の概略構成を示すブロック図である。30

【図 2】液晶表示モジュールの交流化駆動方法における、共通電極反転法を説明するための図である。

【図 3】本発明の実施の形態の液晶表示モジュールの概略構成を示すブロック図である。

【図 4】本発明の実施の形態のダミー画素の配置状態の一例を説明するための模式図である。

【図 5】本発明の実施の形態のダミー画素に書き込まれる映像信号電圧の極性を説明するための図である。

【図 6】本発明の実施の形態において、共通電極に印加する共通電圧を調整する回路の一例を示す図である。

【図 7】本発明の実施の形態において、共通電極に印加する共通電圧を調整する回路の他の例を示す図である。40

【図 8】本発明の前提となる液晶表示モジュールの他の例の概略構成を示すブロック図である。

【図 9】液晶表示モジュールの交流化駆動方法における、共通電極対法を説明するための図である。

【図 10】従来の TFT 方式の液晶表示モジュールの回路構成を示すブロック図である。

【図 11】図 1 に示す液晶表示パネルの一例の等価回路を示す図である。

##### 【符号の説明】

10 、 11 … 基板、 20 , 21 , 22 … 液晶ドライバ、 30 … フレキシブル配線基板、 31 … チップ素子、 32 … コネクタ、 100 … 液晶表示パネル、 110 … 表示制御装置、 150

20...電源回路、130...ドレインドライバ、140...ゲートドライバ、200...有効表示領域の画素、210, 211...ダミー画素、230...第1群のダミー画素、231...第2群のダミー画素、250...共通電圧生成回路、D...ドレイン信号線、G...ゲート信号線、ITO1...画素電極、ITO2...共通電極、 $C_{LC}$ ...液晶容量、 $C_S$ ...蓄積容量、TFT...薄膜トランジスタ、OP...オペアンプ、SW...スイッチ。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

【図8】

【図9】

【図10】

【図11】

図11

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

| F I         | テークコード(参考) |

|-------------|------------|

| G 09 G 3/20 | 621B       |

| G 09 G 3/20 | 621M       |

| G 09 G 3/20 | 624B       |

| G 09 G 3/20 | 624C       |

| G 09 G 3/20 | 624Z       |

| G 09 G 3/20 | 641C       |

| G 09 G 3/20 | 642P       |

| G 09 G 3/20 | 670Q       |

| G 09 G 3/20 | 680G       |

|                |                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2004264677A</a>                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2004-09-24 |

| 申请号            | JP2003055910                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2003-03-03 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 高橋洋之                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 高橋 洋之                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 G09G5/00                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G3/3655 G09G3/3614 G09G2320/0247 G09G2320/029                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.575 G09G3/20.611.E G09G3/20.612.R G09G3/20.621.B G09G3/20.621.M G09G3/20.624.B G09G3/20.624.C G09G3/20.624.Z G09G3/20.641.C G09G3/20.642.P G09G3/20.670.Q G09G3/20.680.G                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H093/NA32 2H093/NA34 2H093/NA51 2H093/NC34 2H093/ND10 2H093/ND39 5C006/AA16 5C006/AC11 5C006/AC25 5C006/AC26 5C006/AF52 5C006/AF54 5C006/AF59 5C006/AF64 5C006/BB16 5C006/BC06 5C006/EB00 5C006/FA20 5C006/FA21 5C080/AA10 5C080/BB05 5C080/DD06 5C080/DD28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H193/ZA04 2H193/ZB08 2H193/ZC02 2H193/ZC20 2H193/ZD21 2H193/ZH26 2H193/ZH53 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

## 摘要(译)

解决的问题：提供一种液晶显示装置，该液晶显示装置能够自动地调节施加到公共电极的公共电压，而无需设置光接收元件以防止在显示屏上发生闪烁。布置在图像显示单元周围的多个虚拟像素具有像素电极，并且在多个虚拟像素中写入有正灰度电压的虚拟像素的像素电极的电压。第一装置，用于检测施加到公共电极的公共电压与其中在多个虚设像素中写入负灰度电压的虚设像素的像素电极的电压之间的电势差，第二装置，用于检测公共电压，由第一装置检测到的电位差和由第二装置检测到的电位差之间的电势差，从而使公共电压，和控制手段进行控制。

[选择图]图3