(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4356750号

(P4356750)

(45) 発行日 平成21年11月4日(2009.11.4)

(24) 登録日 平成21年8月14日(2009.8.14)

(51) Int.Cl.

F 1

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)G02F 1/1343

G02F 1/1368

請求項の数 8 (全 18 頁)

(21) 出願番号 特願2007-14660 (P2007-14660)

(22) 出願日 平成19年1月25日 (2007.1.25)

(65) 公開番号 特開2008-180928 (P2008-180928A)

(43) 公開日 平成20年8月7日 (2008.8.7)

審査請求日 平成19年12月17日 (2007.12.17)

(73) 特許権者 304053854

エプソンイメージングデバイス株式会社

長野県安曇野市豊科田沢6925

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 堀口 正寛

東京都港区浜松町二丁目4番1号 三洋エ

プソンイメージングデバイス株式会社内

(72) 発明者 金子 英樹

東京都港区浜松町二丁目4番1号 三洋エ

プソンイメージングデバイス株式会社内

審査官 福田 知喜

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

液晶層を挟持した一対の透明基板を備え、前記一対の透明基板のうちの一方の前記液晶層側には、表示領域にマトリクス状に配置された複数の走査線及び信号線と、前記表示領域の周縁部に沿って形成されたコモン配線と、少なくとも表示領域の全体に亘って形成された平坦化膜と、前記平坦化膜より下層に、複数の前記走査線及び信号線の交差点近傍に設けられたスイッチング素子と、前記平坦化膜の表面に形成された第1電極と、前記第1電極上に形成された絶縁膜と、前記絶縁膜上に形成され、前記複数の走査線及び信号線で区画された領域に対応する位置毎に複数のスリットを有する第2電極と、が形成されており、前記第2電極は前記絶縁膜及び平坦化膜に形成された第1のコンタクトホールを介して前記コモン配線又はスイッチング素子に電気的に接続されており、前記第1電極は、前記絶縁膜に形成された第2のコンタクトホール、前記絶縁膜の表面、前記絶縁膜及び平坦化膜に形成された第3のコンタクトホールを経るように形成された前記第2電極と同じ材料で形成された橋渡し構造の導電路を経て、第2電極とは異なる前記スイッチング素子又はコモン配線に電気的に接続されていることを特徴とする液晶表示装置。

## 【請求項 2】

前記第1電極は前記表示領域の平坦化膜の表面において前記複数の走査線及び信号線で区画された領域に対応する位置毎に形成されており、それぞれの前記第1電極は複数の前記スイッチング素子のそれぞれに電気的に接続されており、前記第2電極は前記絶縁膜の少なくとも表示領域の表面全体に亘って形成されていると共に前記コモン配線に接続されて

10

20

いることを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 3】

前記橋渡し構造の導電路は前記複数の走査線及び信号線で区画された領域に対応する位置毎に形成されていることを特徴とする請求項 2 に記載の液晶表示装置。

【請求項 4】

前記第 2 電極と前記コモン配線との接続箇所は複数個形成されていることを特徴とする請求項 2 に記載の液晶表示装置。

【請求項 5】

前記第 1 電極は前記表示領域の平坦化膜の表面全体に亘って形成されていると共に前記コモン配線に接続されており、前記第 2 電極は前記表示領域の絶縁膜の表面において前記複数の走査線及び信号線で区画された領域に対応する位置毎に形成されており、それぞれの前記第 2 電極は複数の前記スイッチング素子のそれぞれに電気的に接続されていることを特徴とする請求項 1 に記載の液晶表示装置。 10

【請求項 6】

前記橋渡し構造の導電路は前記コモン配線と前記表示領域との境界部に形成されていることを特徴とする請求項 5 に記載の液晶表示装置。

【請求項 7】

前記橋渡し構造の導電路は複数個形成されていることを特徴とする請求項 5 に記載の液晶表示装置。 20

【請求項 8】

以下の (1) ~ (7) の工程を有することを特徴とする液晶表示装置の製造方法。(1) 表示領域にマトリクス状に形成された複数の走査線及び信号線と、複数の前記走査線及び信号線の交差点近傍に設けられたスイッチング素子と、前記表示領域の周縁部に沿って形成されたコモン配線と、を備える第 1 の透明基板を用意する工程、(2) 前記第 1 の透明基板の少なくとも表示領域の全体に亘って平坦化膜を形成する工程、(3) 前記平坦化膜の表面に第 1 電極を形成する工程、(4) 前記(3)の工程を経た第 1 の透明基板の表面全体に亘って絶縁膜を形成する工程、(5) 前記絶縁膜及び平坦化膜に前記スイッチング素子及びコモン配線が露出するように第 1 及び第 3 のコンタクトホールを形成すると共に、前記絶縁膜に前記第 1 電極が露出するように第 2 コンタクトホールを形成する工程、(6) 前記(5)の工程で得られた透明基板の表面全体に亘って導電性材料からなる膜を形成した後、エッチングすることによって、前記複数の走査線及び信号線で区画された領域に対応する位置毎に複数のスリットを有する第 2 電極を形成すると共に、前記第 1 のコンタクトホールを介して前記第 2 電極と前記スイッチング素子又はコモン配線とを電気的に接続し、前記第 2 コンタクトホール、前記絶縁膜上及び前記第 3 コンタクトホールを経るよう形成された橋渡し構造の導電路を経て前記第 1 電極と前記コモン配線又はスイッチング素子とを電気的に接続する工程、(7) 前記(6)の工程で得られた第 1 の透明基板の表面に第 2 の透明基板を所定距離隔てて対向配置させ、前記第 1 及び第 2 の透明基板間に液晶を封入する工程。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、製造工数を増やすことなく製造し得る、平坦化膜上に画素電極及び共通電極を配置した高開口率及び高表示画質を達成することができる FFS モードの液晶表示装置及びその製造方法に関する。 40

【背景技術】

【0002】

液晶表示装置は、表面に電極等が形成された一対の透明基板と、この一対の基板間に挟持された液晶層とを有し、両基板上の電極に電圧を印加することによって液晶を再配列させて種々の情報を表示する縦方向電界方式のものが多く使用されている。このような縦方向電界方式の液晶表示装置は、TN (Twisted Nematic) モードのものが一般的であるが 50

、視野角が狭いという問題点が存在するため、V A (Vertical Alignment) モードや M V A (Multidomain Vertical Alignment) モード等、種々の改良された縦方向電界方式の液晶表示装置が開発されている。

#### 【 0 0 0 3 】

一方、上述の縦方向電界方式の液晶表示装置とは異なり、一方の基板にのみ画素電極及び共通電極からなる一対の電極を備えた I P S (In-Plane Switching) モードないし F F S (Fringe Field Switching) モードの液晶表示装置も知られている。

#### 【 0 0 0 4 】

このうち I P S モードの液晶表示装置は、一対の電極を同一層に配置し、液晶に印加する電界の方向を基板にほぼ平行な方向として液晶分子を基板に平行な方向に再配列するものである。そのため、この I P S モードの液晶表示装置は、横方向電界方式の液晶表示装置ともいわれ、前述の縦方向電界方式の液晶表示装置と比すると非常に広視野角であるという利点を有している。しかしながら、I P S モードの液晶表示装置は、液晶に電界を印加するため一対の電極が同一層に設けられているため、画素電極の上側に位置する液晶分子は十分に駆動されず、透過率等の低下を招いてしまうといった問題点が存在している。

10

#### 【 0 0 0 5 】

このような I P S モードの液晶表示装置の問題点を解決するために、いわゆる斜め電界方式ともいるべき F F S モードの液晶表示装置が開発されている（下記特許文献 1 及び 2 参照）。この F F S モードの液晶表示装置は液晶層に電界を印加するための画素電極と共通電極をそれぞれ絶縁膜を介して異なる層に配置したものである。

20

#### 【 0 0 0 6 】

この F F S モードの液晶表示装置は、I P S モードの液晶表示装置よりも広視野角かつ高コントラストであり、更に低電圧駆動ができると共に高透過率であるため明るい表示が可能となるという特徴を備えている。加えて、F F S モードの液晶表示装置は、I P S モードの液晶表示装置よりも平面視で画素電極と共通電極との重複面積が大きいために、より大きな保持容量が副次的に生じ、別途補助容量線を設ける必要がなくなるという長所も存在している。

【特許文献 1】特開 2001-235763 号公報

【特許文献 2】特開 2002-182230 号公報

#### 【発明の開示】

30

#### 【発明が解決しようとする課題】

#### 【 0 0 0 7 】

しかしながら、従来の F F S モードの液晶表示装置は、スイッチング素子やコモン配線と重なる画素電極の表面には段差が形成されているため、その段差の部分では液晶分子の配向が乱れてしまう。そのため、従来の F F S モードの液晶表示装置においては、段差の部分は、実質的に表示に寄与しない領域となるので、カラーフィルタ基板においてプラックマトリクスによって遮光する必要があるため、この段差の部分の分だけ開口率が低下してしまう。

#### 【 0 0 0 8 】

このような段差をなくすためには、上述の V A 方式ないし M V A 方式の液晶表示装置で使用されているような平坦化膜を用い、この平坦化膜上に画素電極や共通電極を配置することも考えられる。しかしながら、このような構成を採用すると、スイッチング素子及びコモン配線は平坦化膜の下部に形成されているため、画素電極とスイッチング素子との間及び共通電極とコモン配線との間を電気的に接続するためにコンタクトホールを 2箇所形成する必要が生じる。この 2箇所のコンタクトホールは、画素電極及び共通電極が異なる層に配置されているため、通常は同時に形成することができず、それぞれ別個の工程で形成する必要があるという問題点が存在する。

40

#### 【 0 0 0 9 】

本発明は、以上の点に鑑みてなされたものであり、平坦化膜上に画素電極及び共通電極を配置した際に、単一の工程で複数のコンタクトホールを形成することができ、高開口率

50

で表示画質が良好な FFS モードの液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するため、本発明の液晶表示装置は、液晶層を挟持した一対の透明基板を備え、前記一対の透明基板のうちの一方の前記液晶層側には、表示領域にマトリクス状に配置された複数の走査線及び信号線と、

前記表示領域の周縁部に沿って形成されたコモン配線と、

少なくとも表示領域の全体に亘って形成された平坦化膜と、

前記平坦化膜より下層に、複数の前記走査線及び信号線の交差点近傍に設けられたスイッチング素子と、

10

前記平坦化膜の表面に形成された第1電極と、

前記第1電極上に形成された絶縁膜と、

前記絶縁膜上に形成され、前記複数の走査線及び信号線で区画された領域に対応する位置毎に複数のスリットを有する第2電極と、が形成されており、

前記第2電極は前記絶縁膜及び平坦化膜に形成された第1のコンタクトホールを介して前記コモン配線又はスイッチング素子に電気的に接続されており、

前記第1電極は、前記絶縁膜に形成された第2のコンタクトホール、前記絶縁膜の表面、前記絶縁膜及び平坦化膜に形成された第3のコンタクトホールを経るように形成された前記第2電極と同じ材料で形成された橋渡し構造の導電路を経て、第2電極とは異なる前記スイッチング素子又はコモン配線に電気的に接続されていることを特徴とする。

20

【0011】

本発明の液晶表示装置においては、絶縁膜の表面に設けられる第2電極は複数の走査線及び信号線で区画された領域に対応する位置毎(以下、「サブ画素領域毎」という。)に複数のスリットを有することが必要である。本発明の液晶表示装置は、このスリットを介してサブ画素領域毎に第1電極と第2電極との間に印加される電界によってフリンジフィールド効果を発揮させることができる。

【0012】

この複数のスリットは、互いに平行な方向に形成されている必要があるが、一つの画素内で異なる複数の方向に形成されている群が存在していてもかまわない。このような構成とすると、視角による画質の変化を低減することができる。

30

【0013】

また、本発明においては、第1電極及び第2電極として、ITO (Indium Tin Oxide) 又はIZO (Indium Zinc Oxide) 等を使用することができる。この場合、第1電極と第2電極とは同組成のものであっても異なる組成のものであっても良い。

【0014】

また、本発明においては、スイッチング素子として、p-Si (ポリシリコン) 型の薄膜トランジスタ (TFT : Tin Film Transistor) 素子、a-Si (アモルファスシリコン) 型の TFT 素子、低温ポリシリコン (LTPS : Low Temperature Poly Silicon) 型の TFT 素子などの三端子型素子、或いは薄膜ダイオード (TFD : Thin Film Diode) 素子などに代表される二端子型非線形素子などを用いることができる。

40

【0015】

また、本発明における平坦化膜は、少なくとも表面が平坦性を有する透明な絶縁膜であれば使用することができ、例えばアクリル樹脂やポリイミド等の透明樹脂を使用することができる。更に、本発明における絶縁膜としては酸化硅素や窒化硅素等の無機絶縁膜を使用することができる。

【0016】

そして、本発明の液晶表示装置によれば、コンタクトホールは3箇所形成されているが、これらのコンタクトホールは全て第1電極上の絶縁膜を貫通しているため、一度の工程で3箇所のコンタクトホールを同時に形成できる。しかも、本発明の液晶表示装置によれば、橋渡し構造の導電路は第2電極と同じ材料で形成されているため、第2電極の形成と

50

同時に各コンタクトホールを介して第1電極とスイッチング素子又はコモン配線との間、第2電極とコモン配線又はスイッチング素子との間の電気的導通を達成できる。そのため、本発明の液晶表示装置によれば、特に製造工数を増やすことなく製造し得る平坦化膜上に第1電極及び第2電極が形成されたFFSモードの液晶表示装置を提供することができる。

【0017】

また、本発明の液晶表示装置によれば、第1電極と第2電極との間の絶縁膜は補助容量を形成する誘電体膜として機能する。そのため、本発明の液晶表示装置によれば、この絶縁膜の厚さを調整することにより補助容量の大きさを容易に調整することができるようになる。例えば各画素の面積を小さくして高精細化された液晶表示装置とする場合など、単位面積当たりの補助容量を大きくする必要がある場合、誘電体として機能する絶縁膜の厚さを薄くすることで十分な大きさの補助容量を得ることができる。

【0018】

加えて、電界強度は第1電極と第2電極との間に印加される電圧が一定であれば電極間距離に反比例して大きくなるから、絶縁膜の厚さを薄くすると第1電極と第2電極との間の電界強度が強くなる。そのため、絶縁膜の厚さを薄くすると、第1電極と第2電極との間に印加される電圧を低くしても液晶分子を駆動するための所定の電界強度を得ることができる。従って、本発明の液晶表示装置によれば、表示品質が向上すると共に、低電圧駆動が可能となり、さらに低消費電力化を図ることができる液晶表示装置を提供することができる。

【0019】

しかも、本発明の液晶表示装置によれば、スイッチング素子及びコモン配線の表面は平坦化膜によって被覆されているため、第2電極には従来例のFFSモードの液晶表示装置のような段差が生じない。そのため、本発明の液晶表示装置によれば、他方の透明基板と第2の電極との間の間隔、すなわちセルギャップが均一となり、更に、表示領域内においてブラックマトリクスで遮光しなければならない領域の面積が減少するために開口率が大きくなる。従って、本発明の液晶表示装置によれば、明るく表示画質が良好な、小型化及び高精細化された液晶表示装置として好適に用いることができるFFSモードの液晶表示装置が得られる。

【0020】

また、上記発明の一態様によれば、前記第1電極は前記表示領域の平坦化膜の表面において前記複数の走査線及び信号線で区画された領域に対応する位置毎に形成されており、それぞれの前記第1電極は複数の前記スイッチング素子のそれぞれに電気的に接続されており、前記第2電極は前記絶縁膜の表示領域の表面全体に亘って形成されていると共に前記コモン配線に接続されていることを特徴とする。

【0021】

この態様の液晶表示装置によれば、絶縁膜の表面の第2電極を共通電極と共に、絶縁膜の下面のサブ画素領域毎に形成された第1電極をスイッチング素子に接続された画素電極とした、上記本発明の効果を奏するFFSモードの液晶表示装置が得られる。

【0022】

また、上記発明の他の態様によれば、前記橋渡し構造の導電路は前記サブ画素領域毎に形成されていることを特徴とする。

【0023】

この態様の液晶表示装置によれば、画素電極として機能するサブ画素領域毎の第1電極を絶縁膜の表面において第2電極との間に絶縁状態を確保しつつスイッチング素子に電気的に接続することができる。

【0024】

また、上記発明の他の態様によれば、前記第2電極と前記コモン配線との接続箇所は複数個形成されていることを特徴とする。

【0025】

10

20

30

40

50

この態様の液晶表示装置によれば、第2電極とコモン配線間の接続抵抗を小さくすることができるため、コモン配線を経て第2電極に印加される信号が配線抵抗によって劣化する度合いを小さくすることができるため、表示画質が良好な液晶表示装置が得られる。

【0026】

また、上記発明の他の態様によれば、前記第1電極は前記表示領域の平坦化膜の表面全体に亘って形成されていると共に前記コモン配線に接続されており、前記第2電極は前記表示領域の絶縁膜の表面において前記複数の走査線及び信号線で区画された領域に対応する位置毎に形成されており、それぞれの前記第2電極は複数の前記スイッチング素子のそれぞれに電気的に接続されていることを特徴とする。

【0027】

この態様の液晶表示装置によれば、絶縁膜の表面のサブ画素領域毎に形成された第2電極をスイッチング素子に接続された画素電極と共に、絶縁膜の下面の第1電極をコモン配線に接続された共通電極とした、上記本発明の効果を奏するFFSモードの液晶表示装置が得られる。

【0028】

また、上記発明の他の態様によれば、前記橋渡し構造の導電路は前記コモン配線と前記表示領域との境界部に形成されていることを特徴とする。

【0029】

この態様の液晶表示装置によれば、画素電極として機能する第2電極は表示領域のみに形成されるから、共通電極として機能する第1電極を絶縁膜の表面において第2電極との間に絶縁状態を確保しつつコモン配線に電気的に接続することができる。

【0030】

また、上記発明の他の態様によれば、前記橋渡し構造の導電路は複数個形成されていることを特徴とする。

【0031】

この態様の液晶表示装置によれば、第1電極とコモン配線間の接続抵抗を小さくすることができるため、コモン配線を経て第1電極に印加される信号が配線抵抗によって劣化する度合いを小さくすることができるため、表示画質が良好な液晶表示装置が得られる。

【0032】

更に、上記目的を達成するため、本発明の液晶表示装置の製造方法は、以下の(1)～(7)の工程を有することを特徴とする。

以下の(1)～(7)の工程を有することを特徴とする液晶表示装置の製造方法。

(1) 表示領域にマトリクス状に形成された複数の走査線及び信号線と、複数の前記走査線及び信号線の交差点近傍に設けられたスイッチング素子と、前記表示領域の周縁部に沿って形成されたコモン配線と、を備える第1の透明基板を用意する工程、

(2) 前記第1の透明基板の表示領域全体に亘って平坦化膜を形成する工程、

(3) 前記平坦化膜の表面に第1電極を形成する工程、

(4) 前記(3)の工程を経た第1の透明基板の表面全体に亘って絶縁膜を形成する工程、

(5) 前記絶縁膜及び平坦化膜に前記スイッチング素子及びコモン配線が露出するよう第1及び第3のコンタクトホールを形成すると共に、前記絶縁膜に前記第1電極が露出するよう第2コンタクトホールを形成する工程、

(6) 前記(5)の工程で得られた透明基板の表面全体に亘って導電性材料からなる膜を形成した後、エッチングすることによって、前記複数の走査線及び信号線で区画された領域に対応する位置毎に複数のスリットを有する第2電極を形成すると共に、前記第1のコンタクトホールを介して前記第2電極と前記スイッチング素子又はコモン配線とを電気的に接続し、前記第2コンタクトホール、前記絶縁膜上及び前記第3コンタクトホールを経るよう形成された橋渡し構造の導電路を経て前記第1電極と前記コモン配線又はスイッチング素子とを電気的に接続する工程、

(7) 前記(6)の工程で得られた第1の透明基板の表面に第2の透明基板を所定距離隔

てて対向配置させ、前記第1及び第2の透明基板間に液晶を封入する工程。

【0033】

本発明の液晶表示装置の製造方法によれば、第1～第3コンタクトホールを同一の工程で製造することができるため、特に製造工数を増やすことなく上記発明の効果を奏する液晶表示装置を製造することができる。

【発明を実施するための最良の形態】

【0034】

以下、図面を参照して本発明の最良の実施形態を実施例より説明する。但し、以下に示す実施例は、本発明の技術思想を具体化するための液晶表示装置としてFFSモードの液晶表示装置を例示するものであって、本発明をこのFFSモードの液晶表示装置に特定することを意図するものではなく、特許請求の範囲に含まれるその他の実施形態のものにも等しく適応し得るものである。

【実施例1】

【0035】

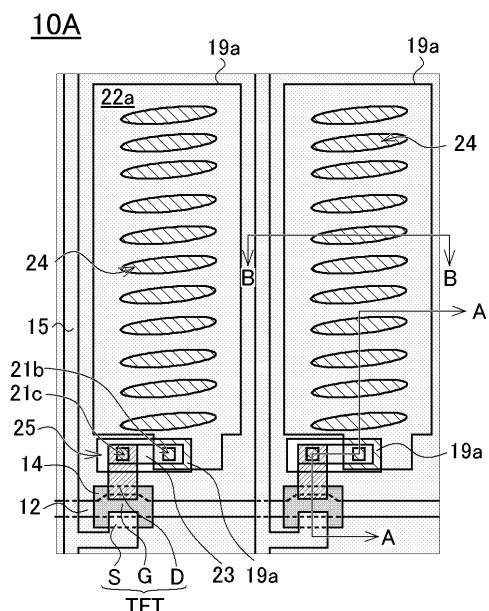

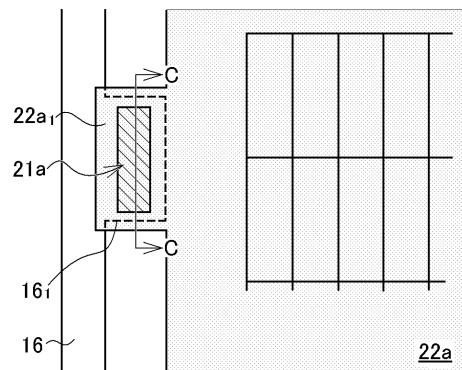

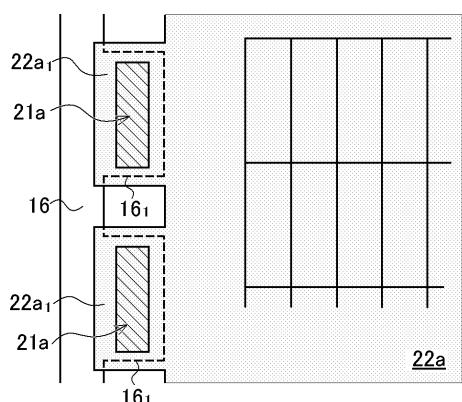

実施例1のFFSモードの液晶表示装置として、平坦化膜を有し、上電極を共通電極としてコモン配線に接続したFFSモード液晶表示装置の例を製造工程順に図1～図5を用いて説明する。なお、図1は実施例1の液晶表示装置10Aのアレイ基板の2画素分の模式平面図である。図2は実施例1の液晶表示装置のコモン配線と共に接続位置Xを示す図である。図3は実施例1の液晶表示装置10AのX部分におけるアレイ基板の拡大平面図である。図4(a)は図1のA-A線に沿った模式断面図、図4(b)は図1のB-B線に沿った模式断面図、図4(c)は図3のC-C線に沿った模式断面図である。また、図5は実施例1の液晶表示装置の変形例におけるX部分のアレイ基板の拡大平面図である。

【0036】

この実施例1のFFSモードの液晶表示装置10Aにおけるアレイ基板ARの製造に際しては、最初にガラス基板等の透明基板11の表面全体に亘って金属膜等の導電性層を形成する。その後、周知のフォトリソグラフィー法及びエッチング法によって、表示領域に複数の走査線12を互いに平行になるように形成すると共に、表示領域の周囲(以下、「額縁領域」という。)にゲート配線(図示せず)を形成する。このゲート配線は、必ずしも走査線用の配線として使用されるものではなく、走査線と同じ材質の配線であるため、「ゲート配線」と称されているものであり、適宜各種の配線用に使用されるものである。

【0037】

次いで、この表面全体に窒化硅素層ないし酸化硅素層からなるゲート絶縁膜13を被覆する。その後、CVD法によりたとえばアモルファス・シリコン(以下「a-Si」という。)層をゲート絶縁膜13の表面全体に亘って被覆した後、同じくフォトリソグラフィー法及びエッチング法によって、TFT形成領域にa-Si層からなる半導体層14を形成する。この半導体層14が形成されている位置の走査線12の領域がTFTのゲート電極Gを形成する。

【0038】

次いで、金属膜で構成された導電性層を半導体層14を形成した透明基板11の表面全体に亘って被覆する。更に、その金属膜で構成された導電性層を、フォトリソグラフィー法及びエッチング法により、表示領域D<sub>issp</sub>において走査線12に直交するようにソース電極Sを含む信号線15を形成し、TFT形成領域にドレイン電極Dを形成し、更に、額縁領域T<sub>rim</sub>にソース配線(図示せず)及びコモン配線16を形成する。このコモン配線16には、以下に示す共通電極22aとの接続位置X(図2参照)に対応する位置に部分的に幅が広くされた接続部16<sub>1</sub>が形成されている。なお、信号線15のソース電極S部分及びドレイン電極D部分はいずれも半導体層14の表面に部分的に重なっている。

【0039】

その後、上記工程で得られた透明基板11の表面全体にパッシベーション膜17を被覆する。このパッシベーション膜17としては、窒化硅素層ないし酸化硅素層からなるもの

10

20

30

40

50

を使用することができるが、絶縁性の観点からは窒化硅素層の方が望ましい。更に、パッシベーション膜17の表面全体に例えればアクリル樹脂ないしポリイミド樹脂から成る平坦化膜（層間膜とも称される）18及びITOないしIZOからなる透明導電性層を順次積層する。

【0040】

次いで、透明導電性層に対して、フォトリソグラフィー法及びエッチング法によって、サブ画素領域毎に画素電極19aを形成する。実施例1の液晶表示装置10Aにおいては、この画素電極19aが本発明の第1電極に対応する。

【0041】

更に、画素電極19aが形成された基板11の表面全体に亘り窒化硅素層ないし酸化硅素層からなる絶縁膜20を所定の厚さに形成する。この絶縁膜20は、後の工程で絶縁膜20の表面に形成される透明な共通電極との間で補助容量を形成する誘電体膜として機能する。そのため、この絶縁膜の厚さを適宜調整することにより補助容量の大きさが所望の値となるように調整することができる。

【0042】

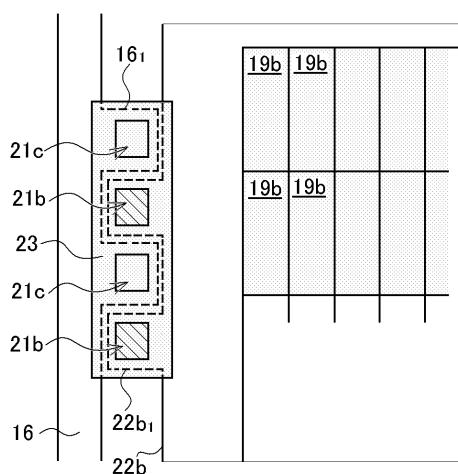

次いで、この絶縁膜20の表面から、絶縁膜20、平坦化膜18及びパッシベーション膜17を貫通してコモン配線16の接続部16<sub>1</sub>の表面に達する第1のコンタクトホール21a、絶縁膜20を貫通して画素電極19aの表面に達する第2のコンタクトホール21b、絶縁膜20、平坦化膜18及びパッシベーション膜17を貫通してドレイン電極Dの表面に達する第3のコンタクトホール21cを、それぞれ同時に形成する。このコンタクトホール21a～21cの形成には、乾式エッチング法の1種であるプラズマエッチング法を採用し得る。

【0043】

次いで、コンタクトホール21a～21cが形成された基板11の表面全体に亘りITOないしIZOからなる透明導電性層を形成する。このとき、透明導電性層によってコンタクトホール21a～21cを介してコモン配線16、画素電極19a及びドレイン電極Dは互いに電気的に互いに接続された状態となる。

【0044】

その後、フォトリソグラフィー法及びエッチング法によって、前記透明導電性層をエッチングすることにより、表示領域の実質的に全体を被覆する共通電極22aを形成する。このとき同時に、共通電極22aには、サブ画素領域毎に、互いに平行にフリンジフィールド効果を発生させるための複数のスリット24を形成すると共に、導電路23の周囲に枠状の切欠部25を設けて導電路23と共に共通電極22aとを電気的に絶縁する。また、この共通電極22aには、コモン配線16と共に共通電極22aとの接続位置Xにおいて、平面視でコモン配線16の部分的に幅が広くされた接続部16<sub>1</sub>と重複するように接続部22a<sub>1</sub>が形成される。なお、図3においてはスリット24及び枠状の切欠部25は図示省略してある。実施例1の液晶表示装置10Aにおいては、この共通電極22aが本発明の第2電極に対応する。

【0045】

このようにして、共通電極22aは第1のコンタクトホール21aを介してコモン配線16と電気的に接続され、画素電極19aは第2のコンタクトホール21b、導電路23及び第3のコンタクトホール21cを経てTFTのドレイン電極Dに接続される。この後、共通電極22a側の表面全体に配向膜（図示せず）を設けることにより実施例1の液晶表示装置10Aのアレイ基板ARが完成される。

【0046】

上記のアレイ基板ARに対向するカラーフィルタ基板は、図示省略したが、従来のFFSモードの液晶表示パネル用のカラーフィルタ基板と実質的に同様のものを使用できる。すなわち、このカラーフィルタ基板は、それぞれの画素電極に対向する位置には各色のカラーフィルタ層が形成され、そして、カラーフィルタ層の表面には配向膜が設けられている。そして、カラーフィルタ層と透明基板との間の走査線12及び信号線15に対向する

10

20

30

40

50

位置、TFTに対向する位置にはそれぞれブラックマトリクスが設けられている。

【0047】

特に実施例1の液晶表示装置10A用のカラーフィルタ基板とするには、前記の導電路23ないし枠状の第2スリット25に対向する位置に更にブラックマトリクスを設けることにより、この部分からの漏れ光を遮光するようにすればよい。次いで、上述のアレイ基板及びカラーフィルタ基板をそれぞれ対向させて内部に液晶を封入することにより実施例1の液晶表示装置10Aが得られる。

【0048】

このようにして製造された実施例1の液晶表示装置10Aによれば、コンタクトホールは3箇所形成されているが、これらのコンタクトホールは全て画素電極19a上の絶縁膜20を貫通しているため、一度の工程で3箇所のコンタクトホールを同時に形成できる。しかも、この液晶表示装置10Aによれば、橋渡し構造の導電路23は共通電極22aと同じ材料で形成されているため、共通電極22aの形成と同時に各コンタクトホール21a～21cを介して各画素電極19aとドレン電極Dとの間、共通電極22aとコモン配線16との間の電気的導通を達成できる。そのため、実施例1の液晶表示装置10Aによれば、特に製造工数を増やすことなく製造し得る、平坦化膜18上に画素電極19a及び共通電極22aが形成されたFFSモードの液晶表示装置10Aが得られる。

【0049】

また、実施例1の液晶表示装置10Aによれば、画素電極19aと共通電極22aとの間の絶縁膜20は補助容量を形成する誘電体膜として機能する。そのため、この絶縁膜20の厚さを調整することにより補助容量の大きさを容易に調整することができるようになる。加えて、電界強度は、画素電極19aと共通電極22aとの間に印加される電圧が一定であれば、電極間距離に反比例して大きくなるから、絶縁膜20の厚さを薄くすると画素電極19aと共通電極22aとの間の電界強度が強くなる。そのため、絶縁膜20の厚さを薄くすると、画素電極19aと共通電極22aとの間に印加される電圧を低くしても液晶分子を駆動するための所定の電界強度を得ることができる。従って、実施例1の液晶表示装置10Aによれば、表示品質が向上すると共に、低電圧駆動が可能となり、さらに低消費電力化を図ることができる液晶表示装置10Aが得られる。

【0050】

しかも、実施例1の液晶表示装置10Aによれば、TFT等の表面は平坦化膜によって被覆されているため、共通電極22aには従来例のFFSモードの液晶表示装置のような段差が生じない。そのため、実施例1の液晶表示装置10Aによれば、図示しないカラーフィルタ基板と共通電極22aとの間の間隔、すなわちセルギャップが均一となり、更に、表示領域内においてブラックマトリクスで遮光する領域の面積が減少するために開口率が大きくなる。従って、実施例1の液晶表示装置10Aによれば、明るく、表示画質が良好で、小型化及び高精細化された液晶表示装置として好適に用いることができるFFSモードの液晶表示装置10Aが得られる。

【実施例2】

【0051】

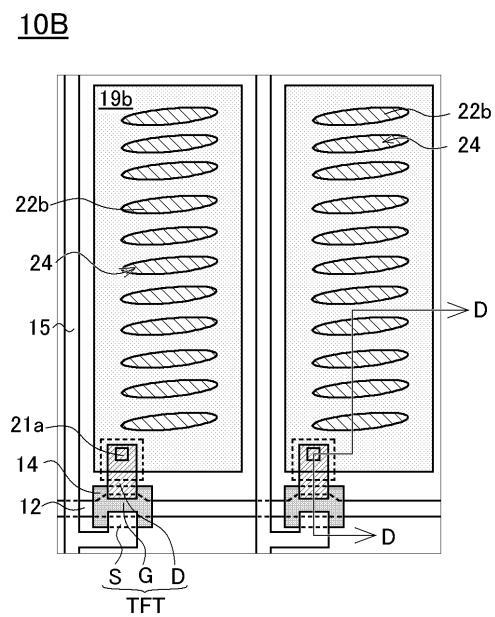

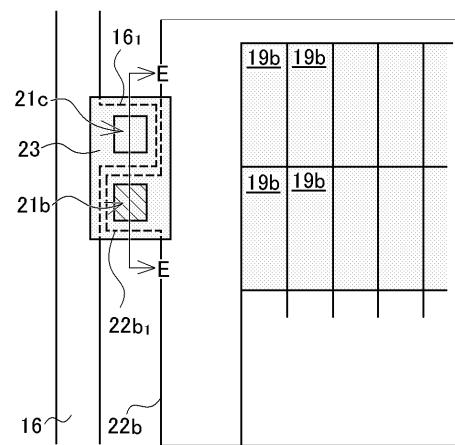

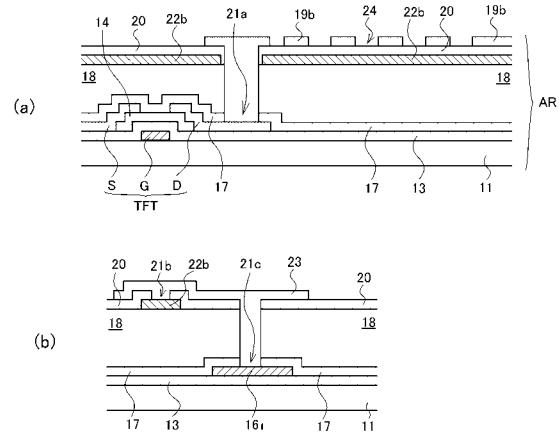

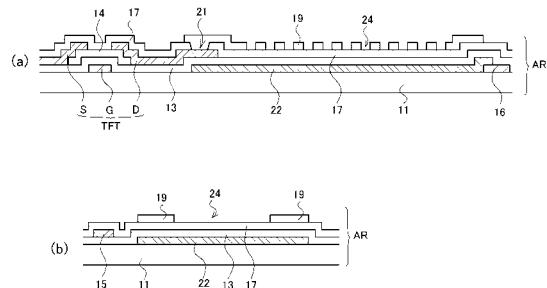

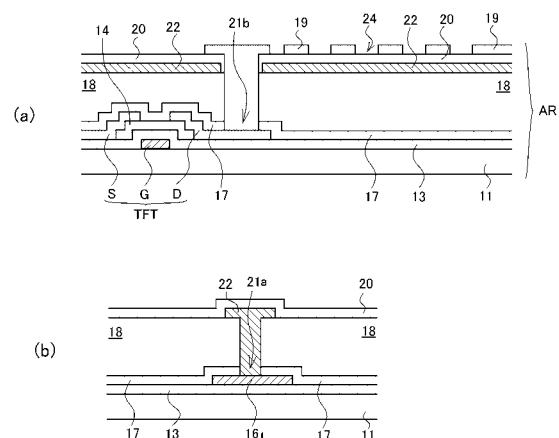

次に、平坦化膜を有し、下電極を共通電極としてコモン配線に接続した実施例2のFFSモードの液晶表示装置の例を製造工程順に図6～図9を用いて説明する。なお、図6は実施例2の液晶表示装置のアレイ基板の2画素分の模式平面図である。図7は実施例2の液晶表示装置のコモン配線と共通電極との接続位置におけるアレイ基板の拡大平面図である。図8(a)は図6のD-D線に沿った模式断面図であり、図8(b)は図7のE-E線に沿った模式断面図である。また、図9は実施例2の液晶表示装置10Bの変形例における共通電極との接続位置のアレイ基板の拡大平面図である。なお、実施例2の液晶表示装置10Bにおけるコモン配線と共通電極との接続位置は、図2に示した実施例1の液晶表示装置10Aのコモン配線と共通電極との接続位置Xと同様であるので、必要に応じて図2を援用して説明することとする。

【0052】

10

20

30

40

50

この実施例 2 の FFS モードの液晶表示装置 10B のアレイ基板 A R は、透明基板 11 の表面に、走査線 12、ゲート絶縁膜 13、半導体層 14、ソース電極 S を含む信号線 15、ドレイン電極 D、ソース配線、コモン配線 16 及びその接続部 16<sub>1</sub>、パッシベーション膜 17 及び平坦化膜 18 の形成工程は、実施例 1 の FFS モードの液晶表示装置 10A のアレイ基板 A R の製造方法と実質的に同一であるので、その詳細な説明は省略する。

#### 【0053】

平坦化膜 18 を形成した後、平坦化膜 18 の表面全体に亘り ITO ないし IZO からなる透明導電性層を形成し、フォトリソグラフィー法及びエッティング法によって共通電極 22b を所定のパターンに形成する。この共通電極 22b には、コモン配線 16 と共通電極 22b との接続位置 X (図 2 参照) において、平面視でコモン配線 16 及びその接続部 16<sub>1</sub> とは重複せず、コモン配線 16 及びその接続部 16<sub>1</sub> に隣接した位置となるように、接続部 22b<sub>1</sub> が形成される。また、同時に、共通電極 22b の以下に述べる第 1 のコンタクトホール 21a の形成位置には、第 1 のコンタクトホール 21a よりも僅かに大きい孔を形成する。実施例 2 の液晶表示装置 10B においては、この共通電極 22b が本発明の第 1 電極に対応する。なお、図 7 において、スリット 24 は図示を省略してある。

#### 【0054】

次いで、共通電極 22b が形成された基板 11 の表面全体に亘り窒化硅素層ないし酸化硅素層からなる絶縁膜 20 を所定厚さに形成する。このとき、共通電極 22b に形成した第 1 のコンタクトホール 21a の大きさよりも大きい穴内は絶縁膜 20 で埋められる。次いで、この絶縁膜 20 の表面から、絶縁膜 20、平坦化膜 18 及びパッシベーション膜 17 を貫通してドレイン電極 D の表面に達する第 1 のコンタクトホール 21a、絶縁膜 20 を貫通して共通電極 22b の表面に達する第 2 のコンタクトホール 21b、絶縁膜 20、平坦化膜及びパッシベーション膜 17 を貫通してコモン配線 16 の接続部 16<sub>1</sub> の表面に達する第 3 のコンタクトホール 21c を、それぞれ同時に形成する。このとき、共通電極 22b はコンタクトホール 21a の周囲壁に露出しない。このコンタクトホール 21a ~ 21c の形成には、乾式エッティング法の 1 種であるプラズマエッティング法を採用し得る。

#### 【0055】

次いで、コンタクトホール 21a ~ 21c が形成された基板 11 の表面全体に亘り ITO ないし IZO からなる透明導電性層を形成する。このとき、透明導電性層によってコンタクトホール 21a ~ 21c を介してコモン配線 16、画素電極 19b 及びドレイン電極 D は互いに電気的に接続された状態となる。

#### 【0056】

その後、フォトリソグラフィー法及びエッティング法によって、サブ画素領域毎に画素電極 19b を形成する。このとき同時に、各画素電極 19b には平行にフリンジフィールド効果を発生させるための複数のスリット 24 を形成すると共に、接続位置 X において導電路 23 が形成されるように、導電路 23 の周囲の透明導電性層を取り除く。このような構成とすることにより、導電路 23 と各画素電極 19b との間の絶縁性が確保される。実施例 2 の液晶表示装置 10B においては、この各画素電極 19b が本発明の第 2 電極に対応する。

#### 【0057】

このようにして、各画素電極 19b は第 1 のコンタクトホール 21a を介してドレイン電極 D と電気的に接続され、共通電極 22b は第 2 のコンタクトホール 21b、導電路 23 及び第 3 のコンタクトホール 21c を経てコモン配線 16 に接続される。この後、共通電極 22 側の表面全体に配向膜 (図示せず) を設けることにより実施例 2 の液晶表示装置 10B のアレイ基板 A R が完成される。これ以降の製造工程は、実施例 1 の液晶表示装置 10A の製造工程と同一であるので、詳細な説明を省略する。

#### 【0058】

このようにして製造された実施例 2 の液晶表示装置 10B によれば、コンタクトホールは 3箇所形成されているが、これらのコンタクトホールは全て共通電極 22b 上の絶縁膜 20 を貫通しているため、一度の工程で 3箇所のコンタクトホールを同時に形成できる。

10

20

30

40

50

しかも、この液晶表示装置 10B によれば、橋渡し構造の導電路 23 は画素電極 19b と同じ材料で形成されているため、画素電極 19b の形成と同時に各コンタクトホール 21a ~ 21c を介して各画素電極 19b とドレイン電極 D との間、共通電極 22b とコモン配線 16 との間の電気的導通を達成できる。そのため、実施例 2 の液晶表示装置 10B によれば、特に製造工数を増やすことなく製造し得る、平坦化膜上に画素電極 19b 及び共通電極 22b が形成された FFS モードの液晶表示装置 10B が得られる。なお、他の実施例 2 の液晶表示装置 10B の作用・効果は、実施例 1 の液晶表示装置の場合と同様であるので、その詳細な説明は省略する。

## 【0059】

## 【比較例 1】

10

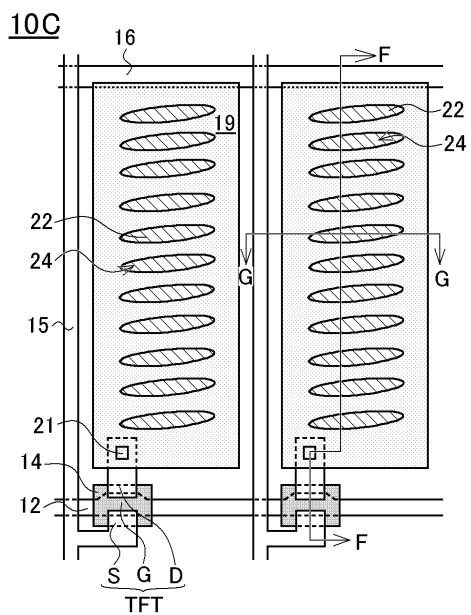

次に、本発明の液晶表示装置の効果を確認するために、比較例 1 の FFS モードの液晶表示装置として、平坦化膜を備えない FFS モード液晶表示装置の例を製造工程順に図 10 及び図 11 を用いて説明する。なお、図 10 は比較例 1 の FFS モードの液晶表示装置のアレイ基板の 2 画素分の概略平面図であり、図 11 (a) は図 10 の F-F 線に沿った概略断面図、図 11 (b) は図 10 の G-G 線に沿った概略断面図である。なお、図 10 及び図 11 においては、図 1 ~ 図 5 に示した実施例 1 の液晶表示装置と同一の構成部分には同一の参照符号を付与して説明する。

## 【0060】

この比較例 1 の FFS モードの液晶表示装置 10C のアレイ基板 AR は、ガラス基板等の透明基板 11 の表面全体に亘って下部が金属膜等の導電性層を形成した後、フォトリソグラフィー法及びエッティング法によってゲート部分を有する複数の走査線 12 及び複数のコモン配線 16 を互いに平行になるように形成する。

20

## 【0061】

次いで、走査線 12 及びコモン配線 16 を形成した透明基板 11 の表面全体に亘って例えば ITO ないし IZO からなる透明導電性層を被覆し、同じくフォトリソグラフィー法及びエッティング法によって共通電極 22 を形成する。この共通電極 22 はコモン配線 16 とは電気的に接続されているが、走査線 12 ないしゲート電極 G とは接続されていない。

## 【0062】

更に、この表面全体に窒化硅素層ないし酸化硅素層からなるゲート絶縁膜 13 を被覆し、次いで、CVD 法によりたとえば a-Si 層をゲート絶縁膜 13 の表面全体に亘って被覆した後に、同じくフォトリソグラフィー法及びエッティング法によって、TFT 形成領域に a-Si 層からなる半導体層 14 を形成する。この半導体層 14 が形成されている位置の走査線 12 の領域が TFT のゲート電極 G を形成する。

30

## 【0063】

次いで、金属膜等で構成されている導電性層を半導体層 14 を形成した透明基板 11 の表面全体に亘って被覆し、同じくフォトリソグラフィー法及びエッティング法によって、ソース電極 S を含む信号線 15 及びドレイン電極 D を形成する。この信号線 15 のソース電極 S 部分及びドレイン電極 D 部分は、いずれも半導体層 14 の表面に部分的に重なっている。更に、この基板の表面全体に窒化硅素層からなるパッシベーション膜 17 を被覆する。

40

## 【0064】

次いで、ドレイン電極 D に対応する位置のパッシベーション膜 17 にコンタクトホール 21 を形成してドレイン電極 D の一部を露出させる。更に、この表面全体に亘って例えば ITO ないし IZO からなる透明導電性層を被覆する。このとき、ドレイン電極 D はコンタクトホール 21 を介して導電性物質層と電気的に接続された状態となる。次いで、フォトリソグラフィー法及びエッティング法によって、図 10 に示したパターンとなるように、信号線 15 で囲まれたそれぞれの領域毎のパッシベーション膜 17 上に互いに平行に複数のスリット 24 が形成された画素電極 19 を形成する。この状態で、それぞれの画素電極 19 はコンタクトホール 21 を介してドレイン電極 D と電気的に接続された状態となる。

## 【0065】

50

この後、画素電極 19 側の表面全体に配向膜（図示せず）を設けることにより比較例 1 の液晶表示装置 10C のアレイ基板 A R が完成される。これ以降の製造工程は、実施例 1 の液晶表示装置 10A の製造工程と同一であるので、詳細な説明を省略する。

#### 【 0 0 6 6 】

このような構成の比較例 1 の液晶表示装置 10C は、共通電極 22 とコモン配線 16 は直接接続されているため、コンタクトホール 21 は 1 箇所しか必要ないが、コモン配線 16 の近傍で画素電極 19 の一部に段差が生じており、また、TFT の表面が凹凸状態となっている。そのため、この比較例 1 の液晶表示装置 10C は、カラーフィルタ基板には TFT に対向する部分だけでなく、段差部に対向する部分にもブラックマトリクスを設けて遮光する必要があるので、少なくともこの段差部の分だけ開口率が低下してしまう。 10

#### 【 0 0 6 7 】

加えて、遮光性材料からなるコモン配線 16 が走査線 12 間に平行に配置されているため、このコモン配線 16 によっても開口率が低下してしまう。そのため、比較例 1 の液晶表示装置 10C は、実施例 1 及び 2 の液晶表示装置 10A 及び 10B と比すると、開口率は必然的に低くなってしまう。

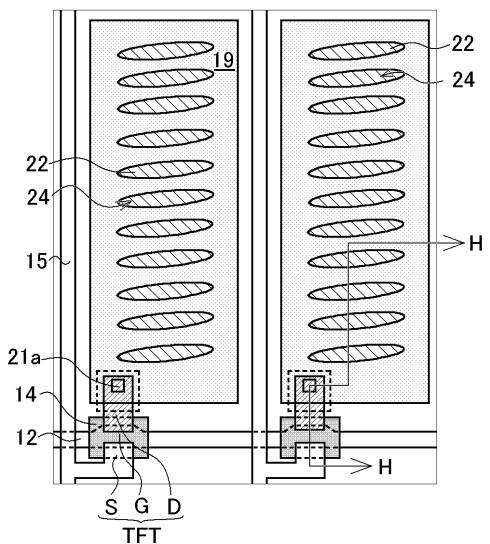

#### 【 0 0 6 8 】

#### 【 比較例 2 】

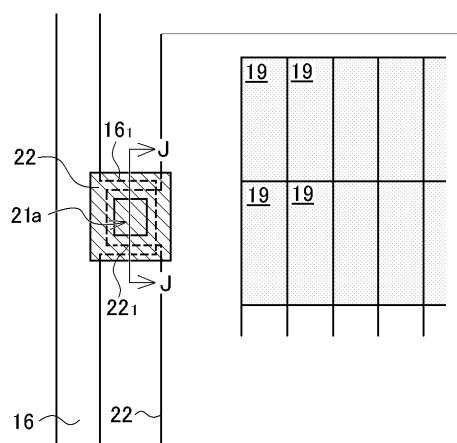

次に、本発明の効果を確認するために、比較例 2 として、平坦化膜を備えた FFS モード液晶表示装置の例を製造工程順に図 12 ~ 図 14 を用いて説明する。なお、図 12 は比較例 2 の液晶表示装置のアレイ基板の 2 画素分の模式平面図である。図 13 は比較例 2 の液晶表示装置の X 部分におけるアレイ基板の拡大平面図である。図 14 ( a ) は図 12 の H - H 線に沿った概略断面図、図 14 ( b ) は図 12 の J - J 線に沿った概略断面図である。なお、図 12 ~ 図 14 においては図 1 ~ 図 3 に示した実施例 1 の FFS モードの液晶表示装置 10A と同一の構成部分については同一の参照符号を付与してその詳細な説明は省略する。また、比較例 2 の液晶表示装置におけるコモン配線と共通電極との接続位置は、図 2 に示した実施例 1 の液晶表示装置 10A のコモン配線と共通電極との接続位置 X と同様であるので、必要に応じて図 2 を援用して説明することとする。 20

#### 【 0 0 6 9 】

この比較例 2 の FFS モードの液晶表示装置 10D のアレイ基板 A R の製造工程のうち、透明基板 11 の表面に、ゲート電極 G を含む走査線 12 、ゲート絶縁膜 13 、半導体層 14 、ソース電極 S を含む信号線 15 、ドレイン電極 D 、ソース配線、コモン配線 16 及びその接続部 16<sub>1</sub> 、パッシベーション膜 17 及び平坦化膜 18 の形成工程は、実施例 1 の FFS モードの液晶表示装置 10A のアレイ基板 A R の製造工程と実質的に同一であるので、その詳細な説明は省略する。 30

#### 【 0 0 7 0 】

平坦化膜 18 を形成した後、以下に述べる共通電極 22 とコモン配線 16 との接続位置 X ( 図 2 参照 ) において、接続部 16<sub>1</sub> 上の平坦化膜 18 及びパッシベーション膜 17 を貫通するように第 1 のコンタクトホール 21a を形成し、接続部 16<sub>1</sub> の表面を露出させる。次いで、この平坦化膜 18 を形成した透明基板 11 の表面全体に亘り ITO ないし IZO からなる透明導電性層を形成し、フォトリソグラフィー法及びエッチング法によって共通電極 22 を所定のパターンに形成する。これと同時に、以下に示す第 2 のコンタクトホール 21b の形成位置に、この第 2 のコンタクトホール 21b の大きさよりも大きい穴を形成する。このとき、共通電極 22 とコモン配線 16 の接続部 16<sub>1</sub> とは第 1 のコンタクトホール 21a 内の透明導電性層によって電気的に接続された状態となる。 40

#### 【 0 0 7 1 】

次いで、共通電極 22 が形成された基板 11 の表面全体に亘り窒化硅素層ないし酸化硅素層からなる絶縁膜 20 を所定厚さに形成する。このとき、共通電極 22 に形成した第 2 のコンタクトホール 21b の大きさよりも大きい穴内は絶縁膜 20 で埋められる。更に、この絶縁膜 20 の表面から、絶縁膜 20 、平坦化膜 18 及びパッシベーション膜 17 を貫通してドレイン電極 D の表面に達する第 2 のコンタクトホール 21b を形成する。このと 50

き、共通電極 22 はコンタクトホール 21b の周囲壁に露出しない。

【0072】

次いで、第2のコンタクトホール 21b が形成された基板 11 の表面全体に亘りITO ないしIZO からなる透明導電性層を形成する。このとき、透明導電性層は第2のコンタクトホール 21b を介してドレイン電極 D と電気的に接続された状態となる。

【0073】

その後、フォトリソグラフィー法及びエッチング法によって、サブ画素領域毎に所定のパターンの画素電極 19 を形成する。このとき、同時に各画素電極 19 には平行にフリンジフィールド効果を発生させるための複数のスリット 24 を形成する。このようにして、各画素電極 19 は第2のコンタクトホール 21b を介してドレイン電極 D と電気的に接続された状態となる。

【0074】

この後、画素電極 19 側の表面全体に配向膜（図示せず）を設けることにより比較例 2 の液晶表示装置 10D のアレイ基板 AR が完成される。これ以降の製造工程は、実施例 1 の液晶表示装置 10A の製造工程と同一であるので、詳細な説明を省略する。

【0075】

このようにして作製された比較例 2 のFFS モードの液晶表示装置 10D は、実質的に実施例 1 及び 2 のFFS モードの液晶表示装置 10A 及び 10B と同様の光学特性を備えている。しかしながら、この比較例 2 の液晶表示装置 10D にはコンタクトホールは 2箇所存在しているが、この 2箇所のコンタクトホールはそれぞれ別工程で形成する必要がある。そのため、比較例 2 のFFS モードの液晶表示装置 10D を製造するには、実施例 1 及び 2 の液晶表示装置 10A 及び 10B を製造する工程と比するとコンタクトホールの製造工程が一工程増加していることが分かる。

【0076】

なお、実施例 1 及び 2 においては画素電極 19 に設けるスリット 24 として長さ方向の両端が閉じた形状とした例を示したが、スリットを一方端側が開いているものとすることもできる。この場合、このスリットが開いた一方側の端部にまでフリンジ効果を発揮させることができ、しかも、このスリットの端部が開いている側での液晶分子の配向の乱れが少ないので、スリットの両端側が閉じている液晶表示装置と比するとカラーフィルタ基板に設けたブラックマトリクスにより遮光しなければならない部分の面積が減るため、表示開口率が大きく、明るい表示の液晶表示装置が得られるようになる。

【図面の簡単な説明】

【0077】

【図 1】実施例 1 の液晶表示装置のアレイ基板の 2 画素分の模式平面図である。

【図 2】液晶表示装置のコモン配線と共に通電極との接続位置 X を示す図である。

【図 3】実施例 1 の液晶表示装置の X 部分におけるアレイ基板の拡大平面図である。

【図 4】図 4 (a) は図 1 の A - A 線に沿った模式断面図、図 4 (b) は図 1 の B - B 線に沿った模式断面図、図 4 (c) は図 3 の C - C 線に沿った模式断面図である。

【図 5】実施例 1 の液晶表示装置の変形例における X 部分のアレイ基板の拡大平面図である。

【図 6】実施例 2 の液晶表示装置のアレイ基板の 2 画素分の模式平面図である。

【図 7】実施例 2 の液晶表示装置の X 部分におけるアレイ基板の拡大平面図である。

【図 8】図 8 (a) は図 6 の D - D 線に沿った模式断面図であり、図 8 (b) は図 7 の E - E 線に沿った模式断面図である。

【図 9】実施例 2 の液晶表示装置の変形例における X 部分におけるアレイ基板の拡大平面図である。

【図 10】比較例 1 のFFS モードの液晶表示装置のアレイ基板の 2 画素分の概略平面図である。

【図 11】図 11 (a) は図 10 の F - F 線に沿った概略断面図、図 11 (b) は図 10 の G - G 線に沿った概略断面図である。

10

20

30

40

50

【図12】比較例2の液晶表示装置のアレイ基板の2画素分の模式平面図である。

【図13】比較例2の液晶表示装置のX部分におけるアレイ基板の拡大平面図である。

【図14】図14(a)は図12のH-H線に沿った概略断面図、図14(b)は図12のJ-J線に沿った概略断面図である。

【符号の説明】

【0078】

10A～10D：液晶表示装置、11：透明基板、12：走査線、13：ゲート絶縁膜、

14：半導体層、15：信号線、16：コモン配線、17：パッシバーション膜、

18：平坦化膜、19、19a、19b：画素電極、20：絶縁膜、21、21a～21c：コンタクトホール、

22、22a、22b：共通電極、23：導電路、24：スリット、

25：枠状の切欠部、Disp：表示領域、Trim：額縁領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

10D

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2005-338256 (JP, A)

特開2002-221736 (JP, A)

特開2003-195352 (JP, A)

特開2005-300821 (JP, A)

特開2001-083540 (JP, A)

特開2001-330844 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1343

G 02 F 1 / 1368

|                |                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP4356750B2</a>                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2009-11-04 |

| 申请号            | JP2007014660                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2007-01-25 |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 爱普生影像设备公司                                                                                                                                                                                                                                                                                                                                            |         |            |

| 当前申请(专利权)人(译)  | 爱普生影像设备公司                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 堀口正寛<br>金子英樹                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 堀口 正寛<br>金子 英樹                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G02F1/134309 G02F1/136227 G02F2001/133357 G02F2001/134372 G02F2001/134381 G02F2201/40                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/GA17 2H092/GA29 2H092/HA02 2H092/JA24 2H092/JA46 2H092/JB58 2H092/KA04 2H092/KA05 2H092/KA18 2H092/KB22 2H092/KB25 2H092/NA07 2H092/QA06 2H192/AA24 2H192/BB12 2H192/BB13 2H192/BB73 2H192/BB81 2H192/BC32 2H192/BC42 2H192/CB05 2H192/CC04 2H192/DA32 2H192/DA63 2H192/EA22 2H192/EA43 2H192/EA67 2H192/FA35 2H192/FA46 2H192/HA47 |         |            |

| 代理人(译)         | 宫坂和彦                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 审查员(译)         | 福田 知喜                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | JP2008180928A                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

要解决的问题：提供一种FFS模式液晶显示器，其具有像素电极和布置在平坦膜上的公共电极，以及用于显示器的制造方法，其可以在一个步骤中同时形成接触孔。SOLUTION：该制造方法首先在平坦化膜18的表面上形成每个子像素的像素电极19a，并在整个表面上形成绝缘膜20，然后同时形成第一至第三接触孔21a-21c，以暴露从该绝缘膜20的表面开始，漏电极D和公共布线接头16 &gt; 1 &lt;/SB&gt;和像素电极19a，随后在整个表面上形成由透明导电材料构成的膜。此外，在完成这些步骤之后，它具有形成具有用于每个子像素的狭缝的公共电极22a的步骤，以及分别通过导电路径23桥接连接像素电极19a和漏电极D的步骤。公共电极22和接头16 &gt; 1 &lt;/SB&gt;通过第一接触孔21a并穿过第二接触孔21b，在绝缘膜20和第三接触孔21c上。Z

図 2

10A(10B,10D)